# Wormhole Run-Time Reconfiguration: Conceptualization and VLSI Design of a High Performance Computing System

By

Ray A. Bittner Jr.

Dissertation submitted to the faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in

**Electrical Engineering**

| APPRO | OVED:            |                    |

|-------|------------------|--------------------|

|       | Peter M. Ath     | anas, Chairman     |

| _     |                  |                    |

|       | A. Lynn Abbott   | Nathaniel J. Davis |

| _     |                  |                    |

|       | Scott F. Midkiff | Calvin J. Ribbens  |

January 23, 1997 Blacksburg, Virginia

Keywords: Data Flow, DSP, FPGA, Wormhole Run-Time Reconfiguration, VLSI Copyright 1997, Ray A. Bittner Jr.

Wormhole Run-Time Reconfiguration: Conceptualization and VLSI

Design of a High Performance Computing System

By

Ray A. Bittner Jr.

Committee Chairman:

Peter M. Athanas

Bradley Department of Electrical Engineering

#### (Abstract)

In the past, various approaches to the high performance numerical computing problem have been explored. Recently, researchers have begun to explore the possibilities of using Field Programmable Gate Arrays (FPGAs) to solve numerically intensive problems. FPGAs offer the possibility of customization to any given application, while not sacrificing applicability to a wide problem domain. Further, the implementation of data flow graphs directly in silicon makes FPGAs very attractive for these types of problems. Unfortunately, current FPGAs suffer from a number of inadequacies with respect to the task. They have lower transistor densities than ASIC solutions, and hence less potential computational power per unit area. Routing overhead generally makes an FPGA solution slower than an ASIC design. Bit-oriented computational units make them unnecessarily inefficient for implementing tasks that are generally word-

oriented. And finally, in large volumes, FPGAs tend to be more expensive per unit due to their lower transistor density.

To combat these problems, researchers are now exploiting the unique advantage that FPGAs exhibit over ASICs: reconfigurability. By customizing the FPGA to the task at hand, as the application executes, it is hoped that the cost-performance product of an FPGA system can be shown to be a better solution than a system implemented by a collection of custom ASICs. Such a system is called a Configurable Computing Machine (CCM). Many aspects of the design of the FPGAs available today hinder the exploration of this field.

This thesis addresses many of these problems and presents the embodiment of those solutions in the Colt CCM. By offering word grain reconfiguration and the ability to partially reconfigure at computational element resolution, the Colt can offer higher effective utilization over traditional FPGAs. Further, the majority of the pins of the Colt can be used for both normal I/O and for chip reconfiguration. This provides higher reconfiguration bandwidth contrasted with the low percentage of pins used for reconfiguration of FPGAs. Finally, Colt uses a distributed reconfiguration mechanism called Wormhole Run-Time Reconfiguration (RTR) that allows multiple data ports to simultaneously program different sections of the chip independently. Used as the primary example of Wormhole RTR in the patent application, Colt is the first system to employ this computing paradigm.

#### **Dedication**

This dissertation is dedicated to all those who have supported me throughout my education. My family has played a large part in that role. My father, mother and my sister Valerie have provided me with financial and emotional support throughout my stay here. There have also been countless little things, like helping me to cart my stuff back and forth to Cumberland endless times and all those turkey dinners at Thanksgiving. For these things I wish to thank them and I pray God's blessings on each of them.

In recent years, Intervarsity Christian Fellowship (IVCF) has played a large role in my life as I have become an active member of that organization. Through IV I have met a large number of people who are believers in God and His Son Jesus Christ and who generally know how to have a good time. Most of my free time here is now spent with that group of people and they have taught me many things about myself, the world and my place in it. My only regret now is that I did not become involved with them sooner. But, in God's perfect timing, through many of them I have now seen the love of God and His love for me. To God's people, this dissertation is dedicated as well.

I was baptized in the last year on March 31, 1996 at the 11:10 service at Blacksburg Christian Fellowship. There I told a bit of the story of how God has become a part of my life. I could not do justice to the story then, and so I can scarce hope to here in a few sentences. There have been many times when I would have quit this degree if left to my own devices, but each time God has been faithful to me and has seen me through. He has revealed things to me many and beautiful and yet sin is still prevalent in my life. How I can know God and still allow sin in

my life is a mystery, but I know that it is for that reason that Jesus died on the cross, once for all.

So though I speak of Him last, certainly my dedication to Him should be first for in this past year.

He has revealed to me the sureness of my salvation as well.

#### Acknowledgments

I would like to thank Dr. Peter Athanas for helping me through the mundane processes of attaining this degree and also for offering insights into the problems at hand. More importantly, I would like to thank him for his patience with me and for his endurance through our tens of hours of "discussion" about the many facets of this work. But, most of all I would like to thank him for his personable nature and his open attitude towards me and his other students.

Several people have assisted me in the realization of this project. Mark "Grover" Musgrove performed most of the VLSI layout work for the Colt device, and his efforts are documented in [1]. Dr. Peter Athanas performed all of the VLSI layout work for the crossbar. Also Mark "Chewie" Cherbaka was responsible for the majority of the testing of the Colt device and some work with mapping applications to the architecture. Chewie's work is described in [2]. Finally, Tsun Han Yang designed and performed the VLSI layout for the multiplier. These efforts were all greatly appreciated and made Colt a reality. I wish to express my thanks and gratitude to each of those involved.

I would also like to thank the other members of my committee for their time and patience as this degree has slowly taken form. In some ways it was not a conventional approach and I appreciate their understanding of my situation. I would like to thank Dr. Cal Ribbens who taught

<sup>1</sup> Musgrove, Mark D., "VLSI Implementation of a Run-Time Reconfigurable Custom Computing Integrated Circuit," Master's Thesis, Virginia Tech, Department of Electrical and Computer Engineering, Blacksburg, Virginia, November 7, 1996.

<sup>2</sup> Cherbaka, Mark F., "Verification and Configuration of a Run-Time Reconfigurable Custom Computing Integrated Circuit for DSP Applications," Master's Thesis, Virginia Tech, Department of Electrical and Computer Engineering, Blacksburg, Virginia, July 1996.

me about assemblers and didn't bail out when I desperately needed an out of department committee member. I would also like to thank Dr. Nat Davis for teaching me about computer architecture and for informing me that Kai Hwang really isn't a very big man. Equal thanks go to Dr. Lynn Abbott who taught me about pattern recognition and who also served on my Master's committee. And, of course, the data port state machine would not have been possible without Dr. Scott Midkiff who taught me all I ever needed to know about digital design.

Finally, I would like to thank Loretta Estes, Pam Crewey, Bob Lineberry, Joe Blum, Dr. John Bay, Dr. Ioannis M. Besieris and the many other people of the Bradley Department of Electrical Engineering who have helped and taught me in my many years at Virginia Tech. Through an act of God they decided to grant me a Bradley Fellowship through which the burden of the Ph.D. was eased, I would like to thank them for that and Marion Via who made it possible. Lastly, I would be remiss if I didn't mention Tom Drayer who *might* get his degree before me.

This work was funded by grant J-FBI-94-219 from the DARPA Information Technologies Office.

# **Table of Contents**

| 1. Introduction                                        | 1  |

|--------------------------------------------------------|----|

| 1.1 Scope                                              | 1  |

| 1.2 Problem Overview                                   | 1  |

| 1.3 Proposed Solution                                  | 4  |

| 1.4 Contributions & Claims                             | 8  |

| 1.5 Dissertation Outline                               | 10 |

| 2. Background                                          | 12 |

| 2.1 Prior Work                                         | 12 |

| 2.1.1 ASIC Solutions                                   | 12 |

| 2.1.1.1 Harris Semiconductor HSP45256                  | 13 |

| 2.1.1.2 Logic Devices Incorporated LF2242              | 14 |

| 2.1.2 DSP Solutions                                    | 14 |

| 2.1.2.1 Analog Devices ADSP-21060 SHARC                | 19 |

| 2.1.3 FPGA Solutions                                   | 20 |

| 2.1.3.1 Altera FLEX 8000                               | 25 |

| 2.1.3.2 Xilinx XC4000                                  | 27 |

| 2.1.3.3 Altera EPF8050M                                | 28 |

| 2.1.3.4 Xilinx XC6200                                  | 29 |

| 2.1.4 Hybrid Solutions                                 | 35 |

| 2.1.4.1 Infinite Technology Corporation RAD5A4         | 36 |

| 2.1.4.2 CMU Programmable Systolic Chip                 | 39 |

| 2.1.4.3 USC Multiprocessor DSP Chip                    | 40 |

| 2.1.4.4 Penn State Micro-Grained VLSI Signal Processor | 41 |

| 2.1.4.5 DPGA                                           | 42 |

| 2.1.4.6 CAM DPGA                                       | 45 |

| 2.1.5 Systems                                       | 46          |

|-----------------------------------------------------|-------------|

| 2.1.5.1 Splash 2                                    | 47          |

| 2.1.5.2 Cheops                                      | 48          |

| 2.1.5.3 Teramac                                     | 51          |

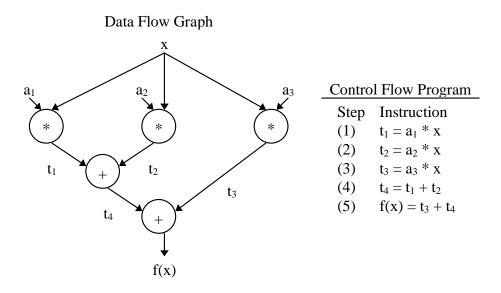

| 2.2 Data Driven vs. Control Driven Concepts         | 52          |

| 2.3 Data Flow vs. Control Flow Tradeoffs            | 55          |

| 2.4 Recent Control Flow Trends                      | 57          |

| 2.5 Data Flow Architecture Classifications          | 59          |

| 2.5.1 Static Data Flow Architectures                | 59          |

| 2.5.2 Dynamic Data Flow Architectures               | 60          |

| 2.5.3 Direct Communication Architectures            | 61          |

| 2.5.4 Packet Communication Architectures            | 61          |

| 2.6 Data Structures For Data Flow                   |             |

| 2.6.1 Scalars                                       |             |

| 2.6.2 Streams                                       |             |

| 2.6.3 Arrays                                        | 62          |

| 3. Solution Approach                                | 64          |

|                                                     |             |

| 3.1 Data Flow Implementation                        |             |

| 3.2 Virtualized Hardware                            |             |

| 3.3 Wormhole RTR                                    | 74          |

| 3.3.1 Motivation                                    | 74          |

| 3.3.2 Wormhole Run-Time Reconfiguration Description | on77        |

| 3.3.3 System Perspective                            | 82          |

| 3.3.4 Advantages & Disadvantages                    | 84          |

| 3.3.4.1 Function Evaluation vs. Opcode Fetch Ratio  | 85          |

| 3.3.4.2 Support For Heterogeneous Computing Envi    | ironments86 |

| 3.3.4.3 Dynamic Implementation Sizing               | 87          |

| 3.3.4.4 Object Oriented Streams                     | 89          |

| 3.3.4.5 Distributed Control.          | 92  |

|---------------------------------------|-----|

| 3.3.4.6 Self-Timed Streams            | 93  |

| 3.3.4.7 "Localized" Communications    | 93  |

| 3.3.4.8 Fault Tolerance               | 94  |

| 3.3.4.9 Design Complexity             | 95  |

| 3.3.4.10 Stream Controller Design     | 96  |

| 3.3.4.11 Data Flow Computing Paradigm | 97  |

| 3.3.5 Relationship To Message Passing | 99  |

| 3.3.6 Data Dependent Computation      | 101 |

| 4. Colt Architectural Overview        | 104 |

| 4.1 Factors Affecting Speedup         | 104 |

| 4.2 Data Flow Implementation          | 113 |

| 4.3 Word vs. Bit-Oriented Approach    | 114 |

| 4.4 Partial Reconfiguration           | 116 |

| 4.5 Arithmetic Computations           | 117 |

| 4.6 Colt Architecture                 | 118 |

| 4.6.1 Data Ports                      | 119 |

| 4.6.1.1 Raw Mode                      |     |

| 4.6.1.2 Synchronization Mode          | 123 |

| 4.6.1.3 Loop Mode                     | 124 |

| 4.6.1.4 External Programming          | 125 |

| 4.6.1.5 Internal Programming          | 125 |

| 4.6.2 Crossbar Network                | 126 |

| 4.6.3 Multiplier                      | 129 |

| 4.6.4 FU Mesh                         |     |

| 4.7 FU Architecture                   | 135 |

| 4.8 Addressing                        | 137 |

| 4.9 Broadcast Programming             | 139 |

| 4.10 The Valid Bit                               | 143 |

|--------------------------------------------------|-----|

| 5. Example Applications                          | 145 |

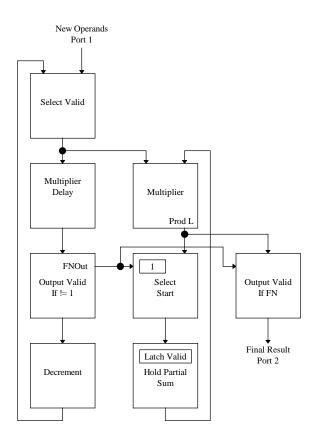

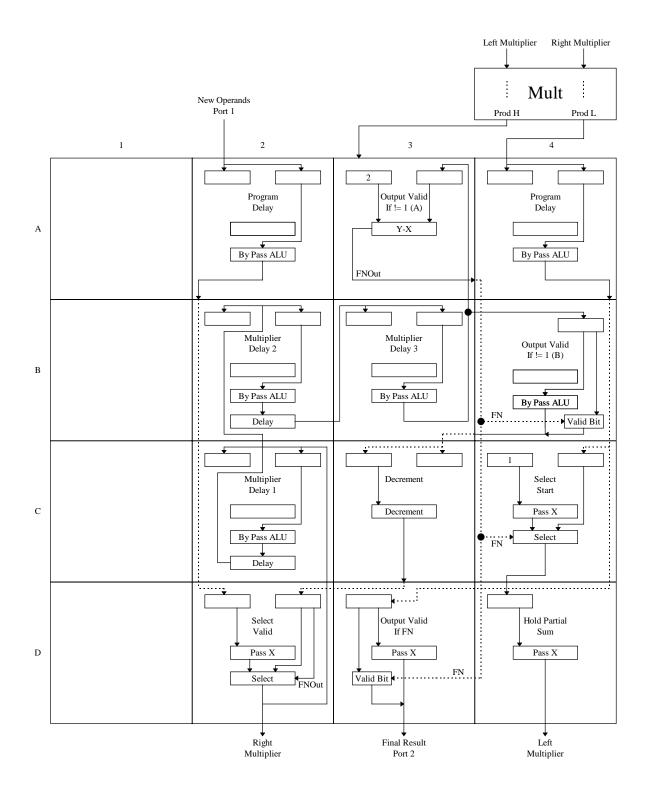

| 5.1 Dot Product Example                          | 145 |

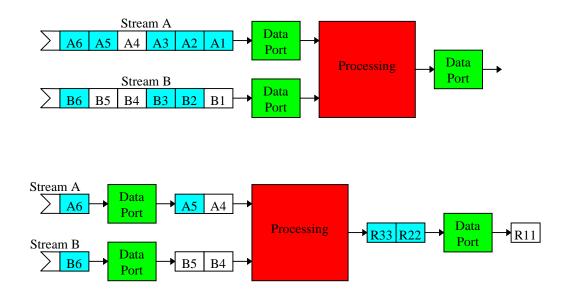

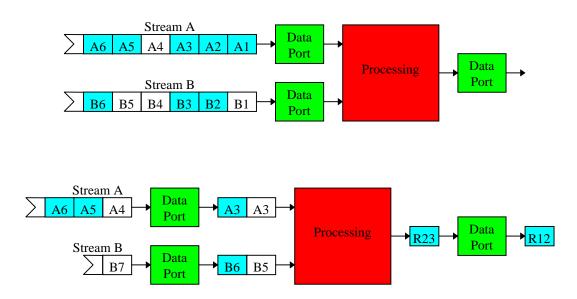

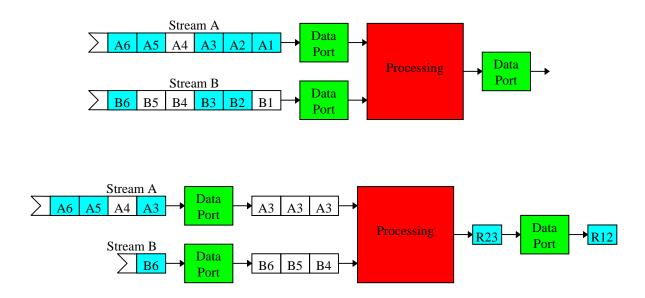

| 5.1.1 Data Port Synchronization                  | 148 |

| 5.1.2 Summing Node Initialization                | 151 |

| 5.1.3 Output Data Port Control                   | 153 |

| 5.1.4 Page Re-initialization                     | 156 |

| 5.2 Floating Point Multiplication Example        | 157 |

| 5.2.1 Format                                     | 157 |

| 5.2.2 Implementation                             | 159 |

| 5.2.3 Programming Method                         | 167 |

| 5.2.4 Improved Implementation                    | 169 |

| 5.3 Conditional Execution                        | 172 |

| 5.3.1 Factorial Concept                          | 173 |

| 5.3.2 Mapping Strategies                         | 175 |

| 5.3.2.1 Broadcasting Using The Crossbar          | 178 |

| 5.3.2.2 Broadcasting Using An Intermediate FU    | 179 |

| 5.3.2.3 Broadcasting Using The Skip Bus Directly | 182 |

| 6. Experimental Results                          | 186 |

| 6.1 CDMA - A DSP Processing Example              | 186 |

| 6.2 Relative Performance                         | 193 |

| 6.2.1 Performance Metrics                        | 193 |

| 6.2.2 FIR Implementations                        | 195 |

| 6.3 Colt vs. Microprocessors                     | 208 |

| 6.3.1 Computational Density                      | 209 |

| 6.3.2 Execution Overhead                         | 211 |

| 633 Clock Pate                                   | 212 |

| ,                                                                                                                                                                                                                                                                  | 213                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| 6.3.5 Colt vs. Microprocessors Summary                                                                                                                                                                                                                             | 214                                 |

| 6.4 Colt vs. CCMs                                                                                                                                                                                                                                                  | 216                                 |

| 6.4.1 Configuration Time                                                                                                                                                                                                                                           | 217                                 |

| 6.4.1.1 Configuration I/O Rate                                                                                                                                                                                                                                     | 218                                 |

| 6.4.1.2 Configuration Storage Density                                                                                                                                                                                                                              | 220                                 |

| 6.4.1.3 Broadcast Programming                                                                                                                                                                                                                                      | 222                                 |

| 6.4.1.4 Partial Run-Time Reconfiguration                                                                                                                                                                                                                           | 223                                 |

| 6.4.1.5 Routing Overhead                                                                                                                                                                                                                                           | 225                                 |

| 6.4.1.6 Bit-Sliced Design Advantage                                                                                                                                                                                                                                | 226                                 |

| 6.4.2 Execution Speed                                                                                                                                                                                                                                              | 226                                 |

| 6.4.2.1 Clock Frequency                                                                                                                                                                                                                                            | 227                                 |

| 6.4.2.2 CCM Die Size vs. Number Of Configurations                                                                                                                                                                                                                  | 228                                 |

| 6.4.3 Colt vs. CCMs Summary                                                                                                                                                                                                                                        | 231                                 |

| 7. Conclusions                                                                                                                                                                                                                                                     | 241                                 |

|                                                                                                                                                                                                                                                                    |                                     |

| 7.1 Future Enhancements                                                                                                                                                                                                                                            | 241                                 |

| 7.1 Future Enhancements                                                                                                                                                                                                                                            |                                     |

|                                                                                                                                                                                                                                                                    | 242                                 |

| 7.1.1 Flip Flop Design                                                                                                                                                                                                                                             | 242<br>242                          |

| 7.1.1 Flip Flop Design                                                                                                                                                                                                                                             |                                     |

| <ul><li>7.1.1 Flip Flop Design</li><li>7.1.2 Super-Pipelining</li><li>7.1.3 Relative Addressing</li><li>7.1.4 Unit Stream Header Response</li></ul>                                                                                                                |                                     |

| <ul><li>7.1.1 Flip Flop Design</li><li>7.1.2 Super-Pipelining</li><li>7.1.3 Relative Addressing</li></ul>                                                                                                                                                          |                                     |

| <ul> <li>7.1.1 Flip Flop Design</li> <li>7.1.2 Super-Pipelining</li> <li>7.1.3 Relative Addressing</li> <li>7.1.4 Unit Stream Header Response</li> <li>7.1.5 Pipeline Stalling</li> <li>7.1.6 Stream Packet Format</li> </ul>                                      |                                     |

| <ul> <li>7.1.1 Flip Flop Design</li> <li>7.1.2 Super-Pipelining</li> <li>7.1.3 Relative Addressing</li> <li>7.1.4 Unit Stream Header Response</li> <li>7.1.5 Pipeline Stalling</li> <li>7.1.6 Stream Packet Format</li> <li>7.1.7 Crossbar Multicasting</li> </ul> |                                     |

| 7.1.1 Flip Flop Design                                                                                                                                                                                                                                             |                                     |

| 7.1.1 Flip Flop Design                                                                                                                                                                                                                                             |                                     |

| 7.1.1 Flip Flop Design                                                                                                                                                                                                                                             | 242 242 243 243 244 245 245 246 249 |

| 7.1.13 Multiplier Improvements                                                                                                                                                                                                         | 253 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.1.14 Barrel Shifter Inputs                                                                                                                                                                                                           | 254 |

| 7.1.15 Barrel Shifter Data Path                                                                                                                                                                                                        | 255 |

| 7.1.16 Conditional Unit Modes                                                                                                                                                                                                          | 256 |

| 7.1.17 Flag Clocking                                                                                                                                                                                                                   | 256 |

| 7.1.18 Generalized Flags                                                                                                                                                                                                               | 257 |

| 7.1.19 Arbitrary Flag Logic Functions                                                                                                                                                                                                  | 258 |

| 7.1.20 Data Port Loop Back Mode                                                                                                                                                                                                        | 259 |

| 7.1.21 Data Port Control Pin Timing                                                                                                                                                                                                    | 259 |

| 7.1.22 Data Port Operand Counters                                                                                                                                                                                                      | 260 |

| 7.1.23 Data Port Initialization                                                                                                                                                                                                        | 260 |

| 7.2 Known Colt Bugs                                                                                                                                                                                                                    | 261 |

| 7.3 Future Research Directions                                                                                                                                                                                                         | 262 |

| 7.4 Final Words                                                                                                                                                                                                                        | 264 |

|                                                                                                                                                                                                                                        |     |

| A. Detailed Colt Design                                                                                                                                                                                                                | 268 |

| A. Detailed Colt Design  A.1 Design Philosophy                                                                                                                                                                                         |     |

|                                                                                                                                                                                                                                        | 268 |

| A.1 Design Philosophy                                                                                                                                                                                                                  | 268 |

| A.1.1 Pseudo-NMOS Circuitry                                                                                                                                                                                                            |     |

| A.1.1 Pseudo-NMOS Circuitry  A.1.2 High Strength Drivers                                                                                                                                                                               |     |

| A.1.1 Pseudo-NMOS Circuitry  A.1.2 High Strength Drivers  A.1.3 Flip Flop Design                                                                                                                                                       |     |

| A.1 Design Philosophy                                                                                                                                                                                                                  |     |

| A.1 Design Philosophy                                                                                                                                                                                                                  |     |

| A.1 Design Philosophy  A.1.1 Pseudo-NMOS Circuitry  A.1.2 High Strength Drivers  A.1.3 Flip Flop Design  A.1.4 Clock Driver Design  A.1.5 Stream Conventions  A.1.6 Address Comparators                                                |     |

| A.1 Design Philosophy  A.1.1 Pseudo-NMOS Circuitry  A.1.2 High Strength Drivers  A.1.3 Flip Flop Design  A.1.4 Clock Driver Design  A.1.5 Stream Conventions  A.1.6 Address Comparators  A.2 Multiplier                                |     |

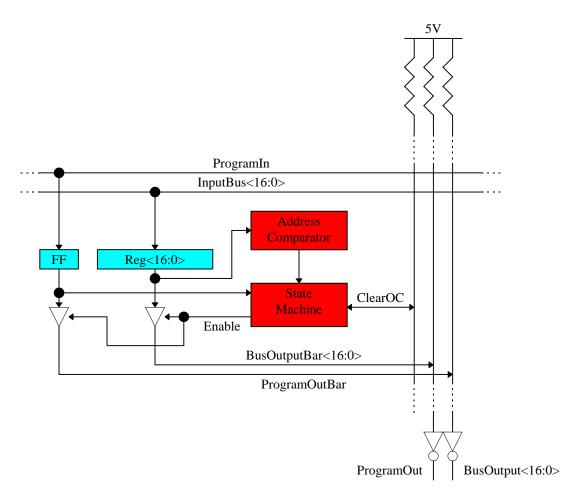

| A.1 Design Philosophy  A.1.1 Pseudo-NMOS Circuitry  A.1.2 High Strength Drivers  A.1.3 Flip Flop Design  A.1.4 Clock Driver Design  A.1.5 Stream Conventions  A.1.6 Address Comparators  A.2 Multiplier  A.3 Crossbar                  |     |

| A.1 Design Philosophy  A.1.1 Pseudo-NMOS Circuitry  A.1.2 High Strength Drivers  A.1.3 Flip Flop Design  A.1.4 Clock Driver Design  A.1.5 Stream Conventions  A.1.6 Address Comparators  A.2 Multiplier  A.3 Crossbar  A.3.1 Data Path |     |

| A.4.1 Data Path                            | 294 |

|--------------------------------------------|-----|

| A.4.2 Flow Control                         | 295 |

| A.4.3 State Machine                        | 303 |

| A.4.3.1 Description of Signals             | 312 |

| A.4.3.2 Programming                        | 316 |

| A.4.3.3 Raw Mode                           | 318 |

| A.4.3.4 Synchronization Mode               | 319 |

| A.4.3.5 Loop Mode                          | 321 |

| A.4.3.6 Programming Peculiarities          | 323 |

| A.4.4 Electrical Design                    | 324 |

| A.5 Mesh                                   | 326 |

| A.6 Interconnected Functional Unit         | 329 |

| A.6.1 Data Path                            | 329 |

| A.6.2 Programming                          | 331 |

| A.6.3 Electrical Design                    | 337 |

| A.7 Functional Unit                        | 339 |

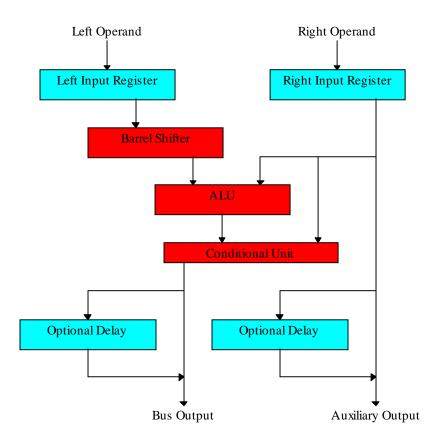

| A.7.1 Data Path                            | 340 |

| A.7.1.1 Left Input Register Latch Function | 341 |

| A.7.1.2 Barrel Shifter                     | 343 |

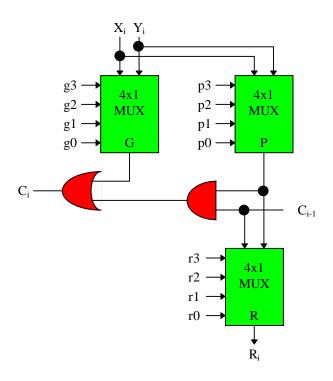

| A.7.1.3 ALU                                | 345 |

| A.7.1.4 Conditional Select Function        | 349 |

| A.7.1.5 Control Flags                      | 351 |

| A.7.2 Programming Path                     | 358 |

| A.7.3 FU State Machine                     | 361 |

| B. FP Multiplier & Tool Overview           | 365 |

| Vita                                       | 415 |

# **List of Figures**

| Figure 1.1 - Computing Implementation Alternatives.                           | 4   |

|-------------------------------------------------------------------------------|-----|

| Figure 2.1 - Microprocessor Floorplan                                         | 22  |

| Figure 2.2 - FPGA Floorplan.                                                  | 23  |

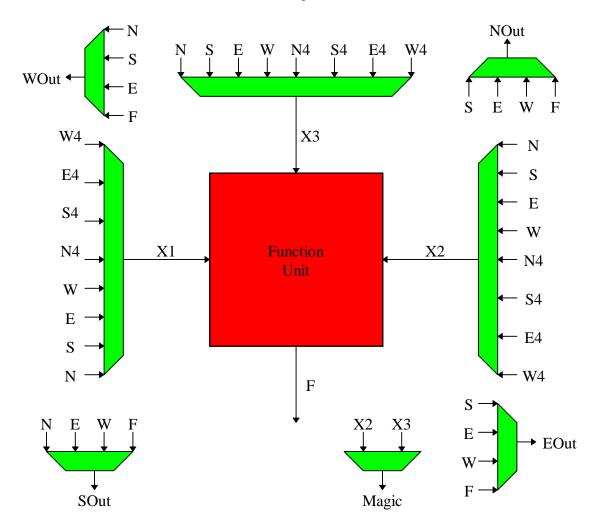

| Figure 2.3 - XC6200 Standard Cell Connectivity.                               | 31  |

| Figure 2.4 - XC6200 Function Unit.                                            | 33  |

| Figure 2.5 - RAD5A4 Chip Architecture.                                        | 36  |

| Figure 2.6 - CAM DPGA Cell.                                                   | 45  |

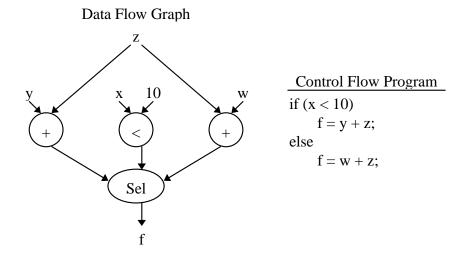

| Figure 2.7 - Data Driven vs. Control Driven Example.                          | 53  |

| Figure 2.8 - Example Of Data Dependent Execution                              | 56  |

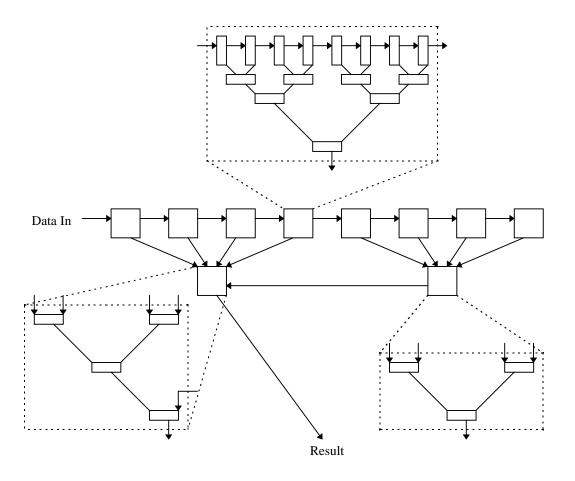

| Figure 3.1 - Pipelined Net Architecture [37]                                  | 67  |

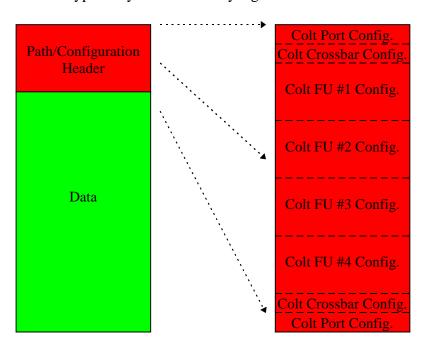

| Figure 3.2 - Stream Format.                                                   | 78  |

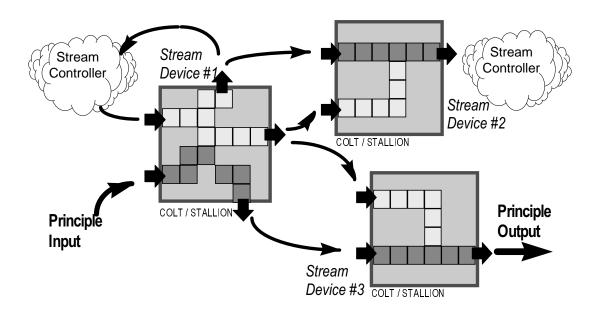

| Figure 3.3 - Generalized Colt/Stallion Wormhole RTR Stream Processing Concept | 80  |

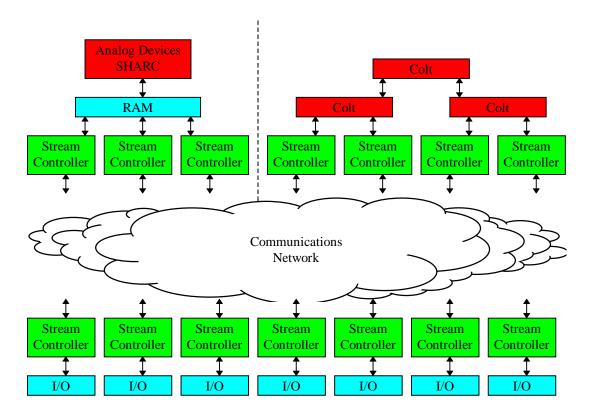

| Figure 3.4 - Wormhole RTR System Perspective.                                 | 82  |

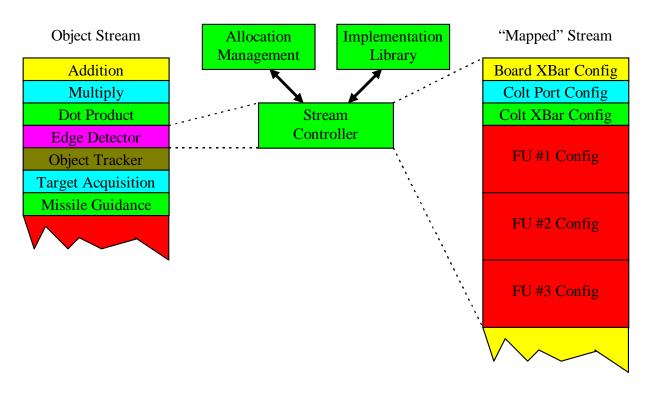

| Figure 3.5 - Object Oriented Stream Concept.                                  | 89  |

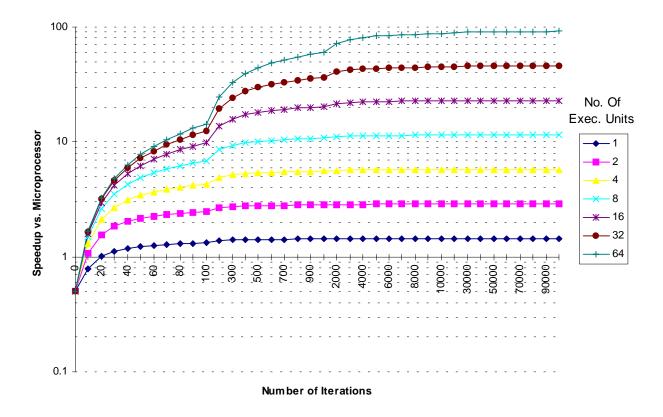

| Figure 4.1 - CCM vs. CPU Speedup For Various Numbers Of CCM Execution Units   | 109 |

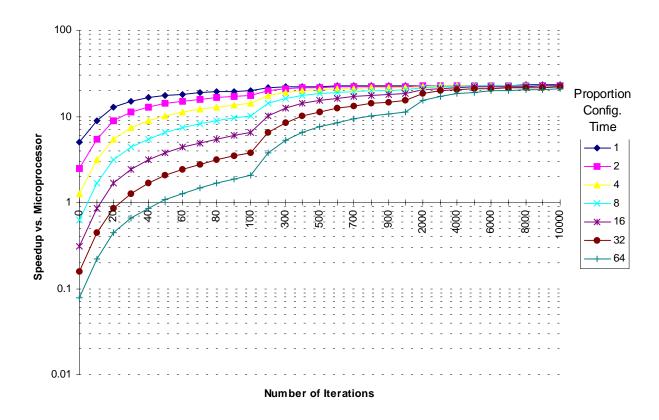

| Figure 4.2 - CCM vs. CPU Relative Setup Time Effects.                         | 111 |

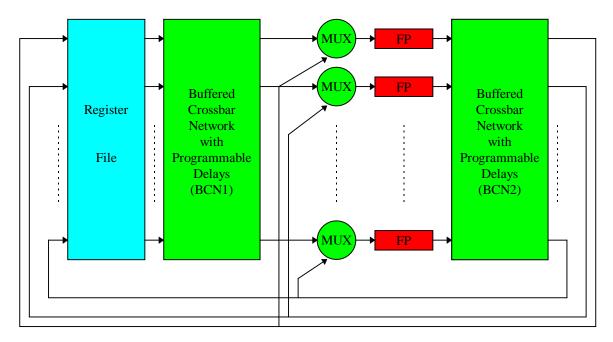

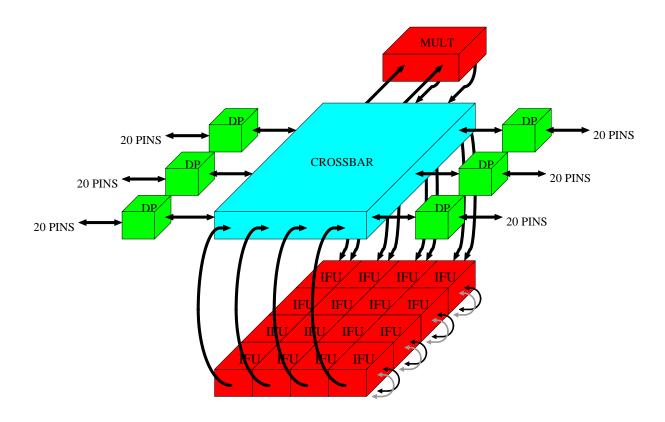

| Figure 4.3 - Colt Architecture Overview                                       | 118 |

| Figure 4.4 - Data Port Raw Mode Operation.                                    | 122 |

| Figure 4.5 - Data Port Synchronization Mode Operation                         | 123 |

| Figure 4.6 - Data Port Loop Mode Operation.                                   | 124 |

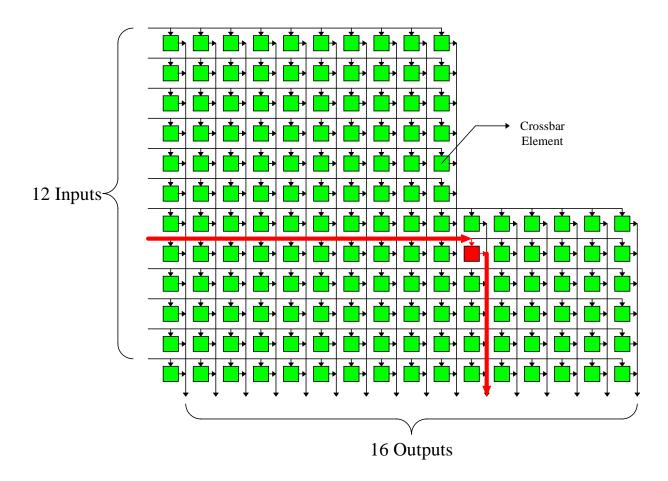

| Figure 4.7 - Basic Crossbar Construction.                                     | 126 |

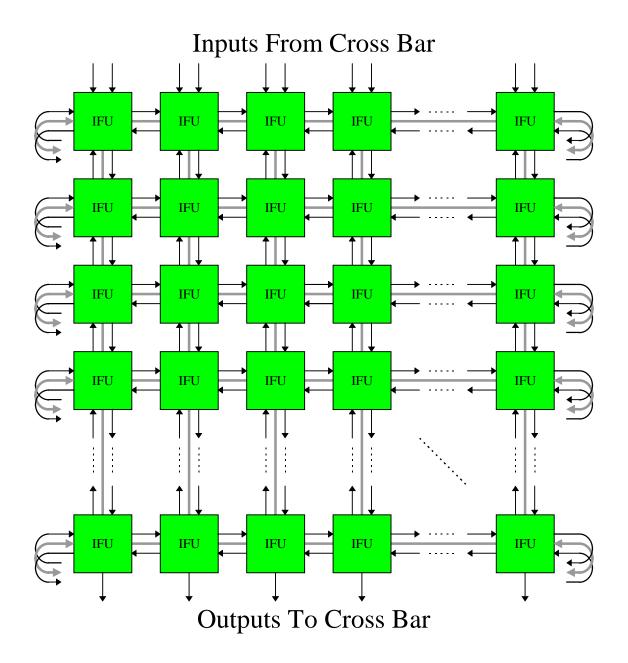

| Figure 4.8 - Extended Mesh Topology.                                          | 132 |

| Figure 4.9 - Simplified FU Schematic                                          | 135 |

| Figure 4.10 - ALU Bit Slice.                                                  | 136 |

| Figure 4.11 - Mesh Broadcast Programming.                                     | 140 |

| Figure 4.12 - Controlled Mesh Broadcast Programming.                          | 141 |

| Figure 5.1 - Dot Product Implementation #1.                                   | 147 |

| Figure 5.2 - Pipeline Halting Problem                                   | 148 |

|-------------------------------------------------------------------------|-----|

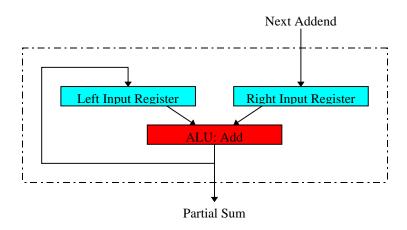

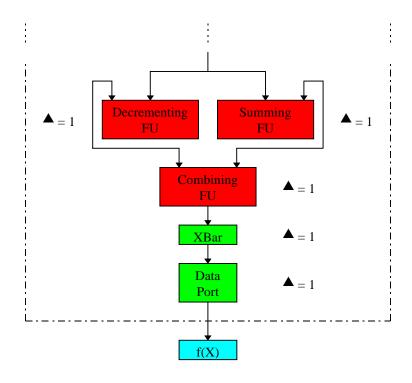

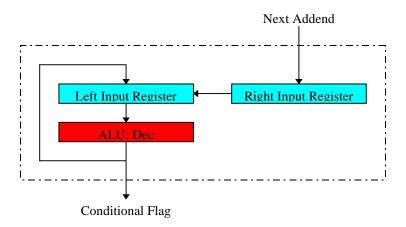

| Figure 5.3 - Summing FU Logical Diagram                                 | 151 |

| Figure 5.4 - Data Counting Selection Scheme.                            | 154 |

| Figure 5.5 - Decrementing FU                                            | 154 |

| Figure 5.6 - Floating Point Format.                                     | 157 |

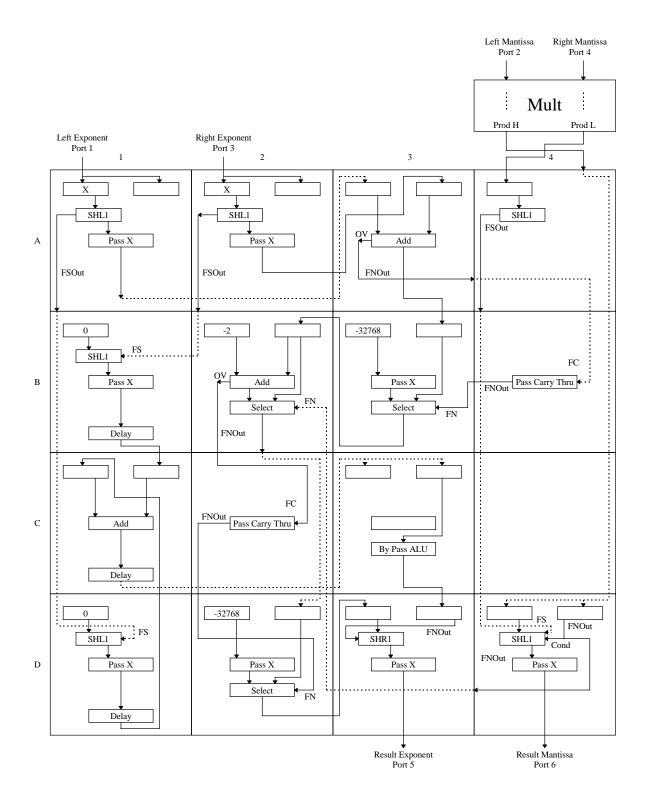

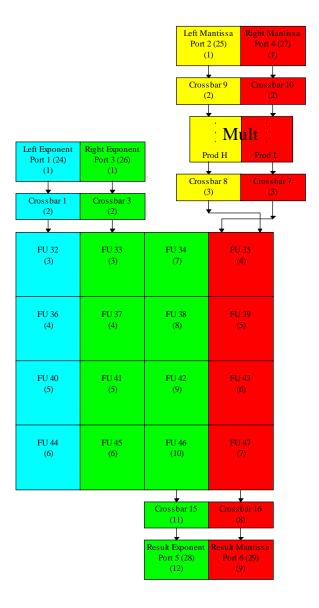

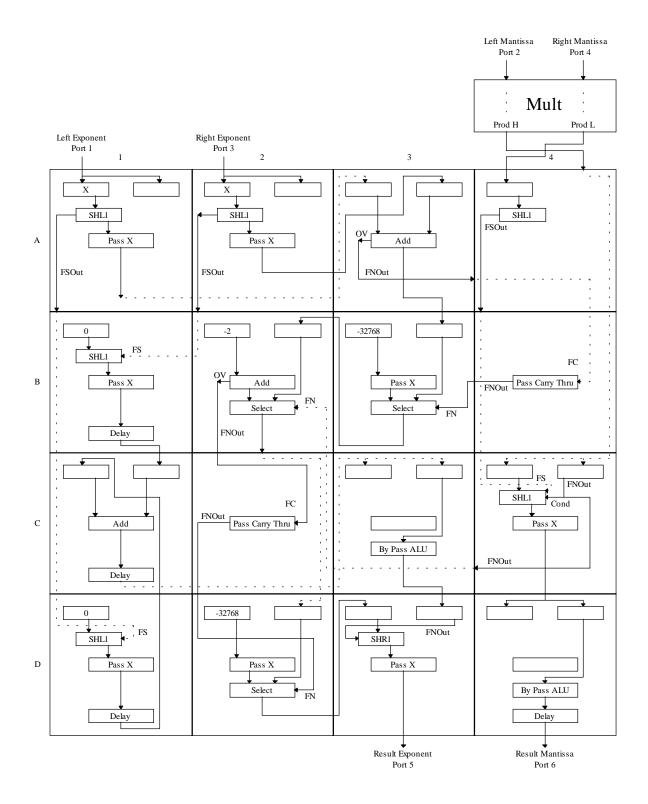

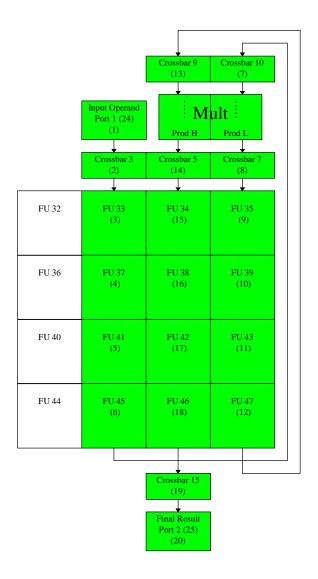

| Figure 5.7 - Floating Point Multiplier Implementation.                  | 160 |

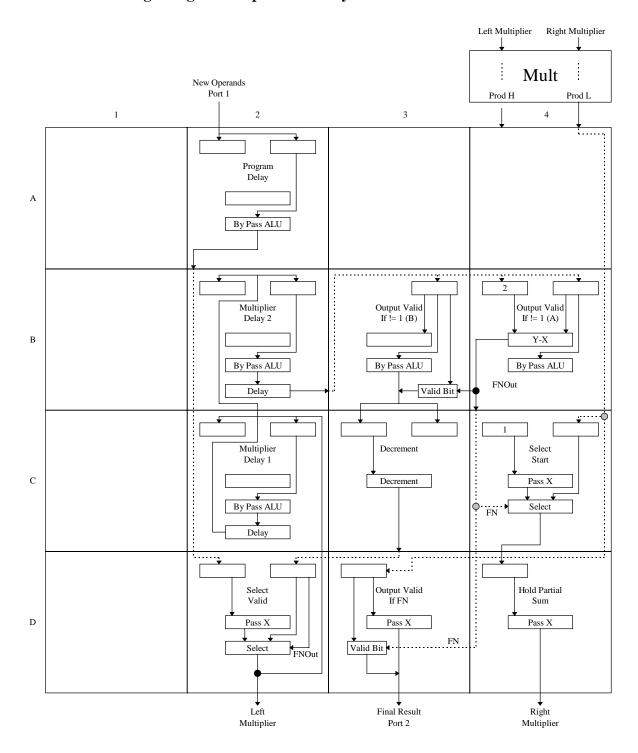

| Figure 5.8 - Floating Point Multiplier Programming Method.              | 167 |

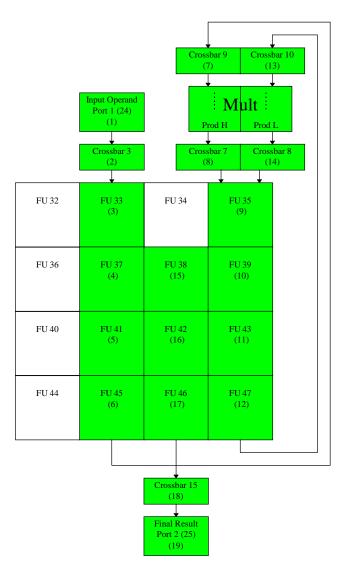

| Figure 5.9 - Improved Floating Point Multiplier Design.                 | 171 |

| Figure 5.10 - Conceptual Factorial Implementation                       | 173 |

| Figure 5.11 - Colt Factorial Implementation (Intermediate FU).          | 176 |

| Figure 5.12 - Configuration Path (Intermediate FU)                      | 180 |

| Figure 5.13 - Colt Factorial Implementation (Direct Skip Bus)           | 182 |

| Figure 5.14 - Configuration Path (Direct Skip Bus).                     | 184 |

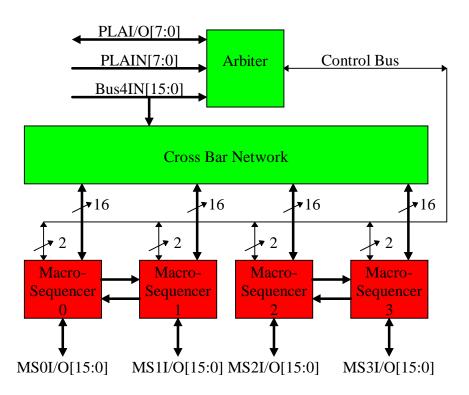

| Figure 6.1 - System Concept.                                            | 187 |

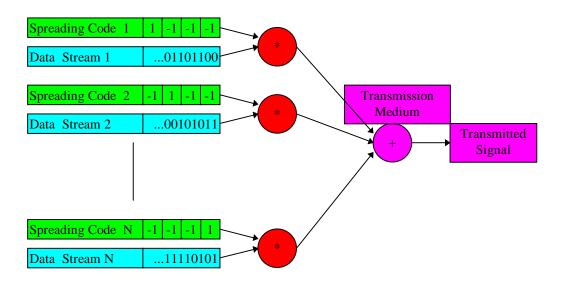

| Figure 6.2 - CDMA Transmission.                                         | 188 |

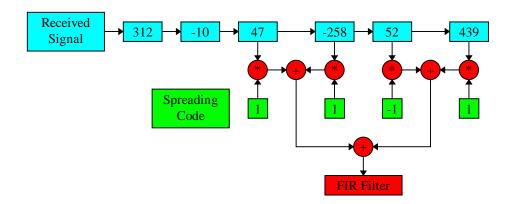

| Figure 6.3 - Matched (FIR) Filter.                                      | 190 |

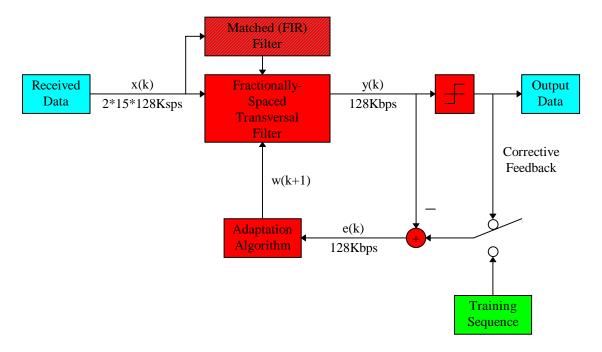

| Figure 6.4 - Mobile Unit Receiver Architecture.                         | 191 |

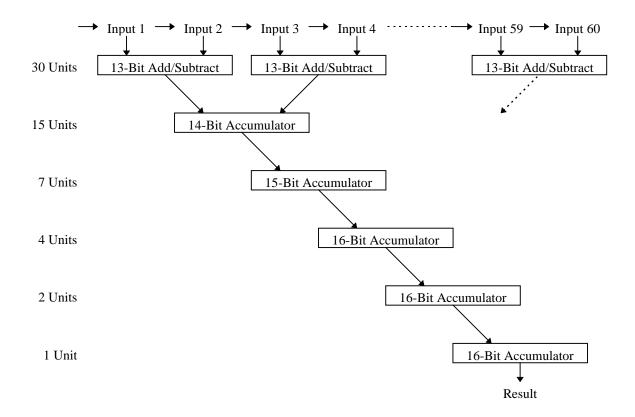

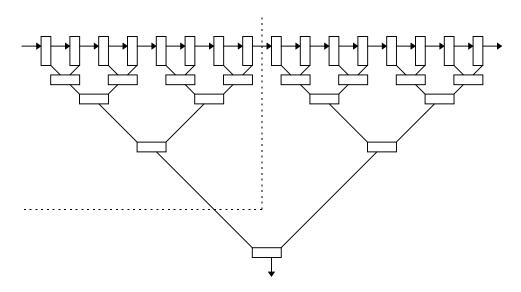

| Figure 6.5 - CCM Adder Tree Implementation.                             | 196 |

| Figure 6.6 - Xilinx XC4013E & XC6216 FIR Filter Partitioning            | 197 |

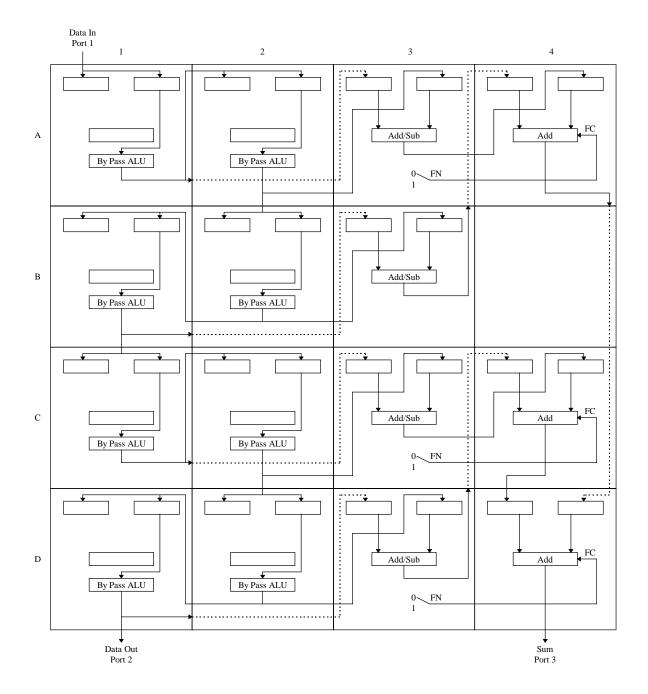

| Figure 6.7 - 8:1 FIR Filter Implementation on Colt.                     | 202 |

| Figure 6.8 - Colt FIR Filter Partitioning.                              | 204 |

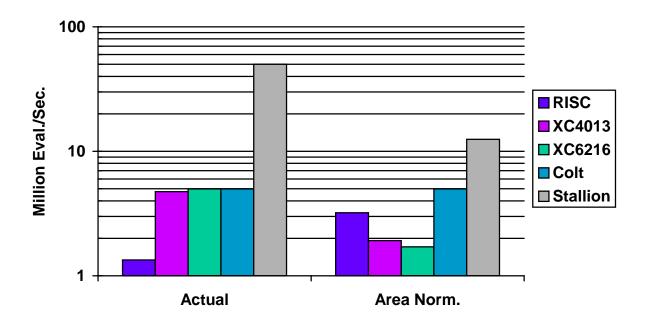

| Figure 6.9 - Actual and Area Normalized FIR Evaluation Performance.     | 208 |

| Figure 6.10 - Computational Density Comparison.                         | 210 |

| Figure 6.11- Colt/Stallion vs. Microprocessor Speedup Factor Comparison | 214 |

| Figure 6.12 - FIR Configuration Speedup Factor Comparison.              | 231 |

| Figure 6.13 - Overall FIR Configuration Speedup Comparison.             | 234 |

| Figure 6.14 - Reconfiguration Time Comparison.                          | 237 |

| Figure 6.15 - FIR Execution Speedup Factor Comparison.                  | 238 |

| Figure 6.16 - Overall FIR Execution Rate Comparison.     | . 240 |

|----------------------------------------------------------|-------|

| Figure 7.1- Alternate Barrel Shifter Design.             | 255   |

| Figure 7.2 - Generalized Flag Concept.                   | . 257 |

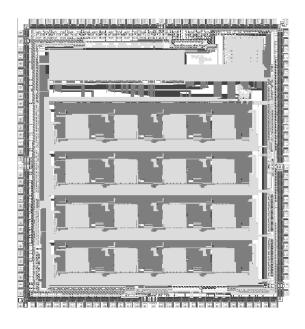

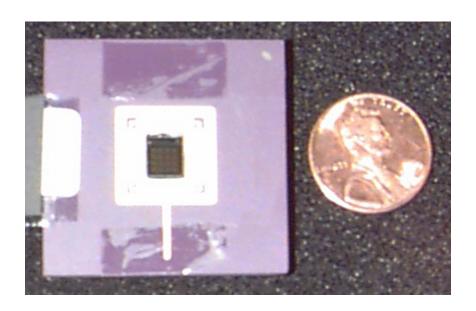

| Figure 7.3 - The Colt CCM.                               | . 266 |

| Figure 7.4 - The Colt CCM in Perspective                 | . 266 |

| Figure 7.5 - Ray Bittner and Peter Athanas.              | 267   |

| Figure 7.6 - Ray Bittner and the Test Apparatus.         | 267   |

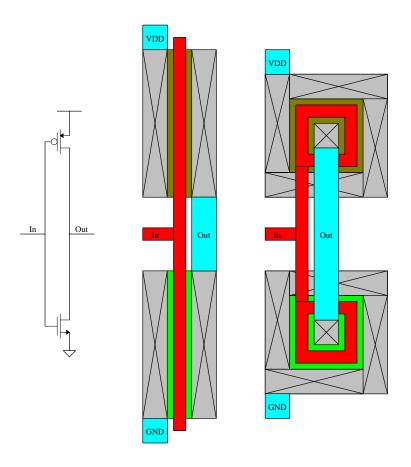

| Figure A.1 - Alternative High Strength Driver Designs    | . 270 |

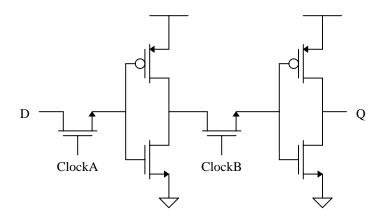

| Figure A.2 - D Flip Flop Design.                         | . 271 |

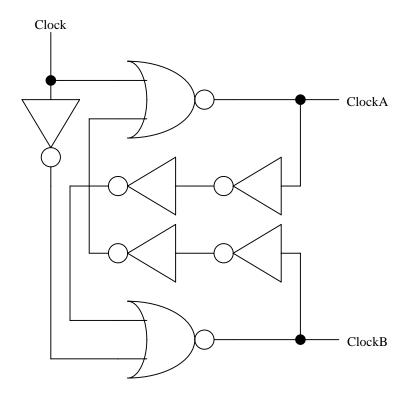

| Figure A.3 - Clock Generator Circuit.                    | . 274 |

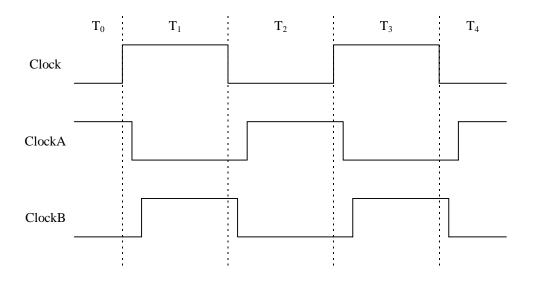

| Figure A.4 - Clock Generator Timing.                     | . 275 |

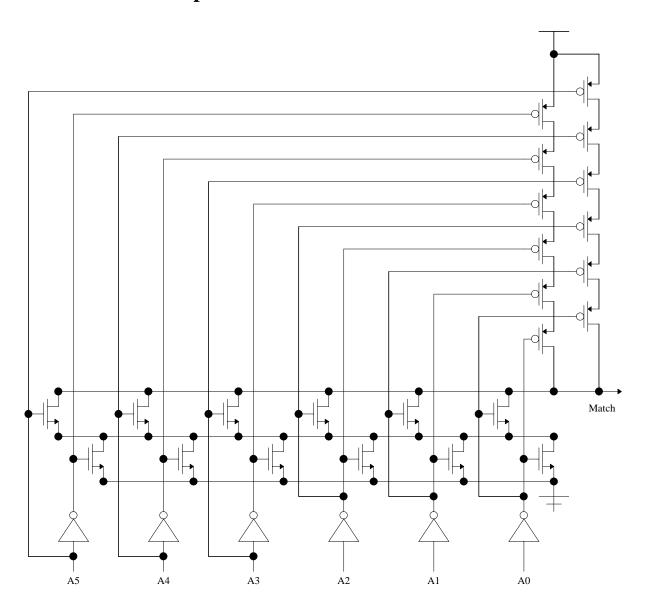

| Figure A.5 - Address Comparator Circuit.                 | . 281 |

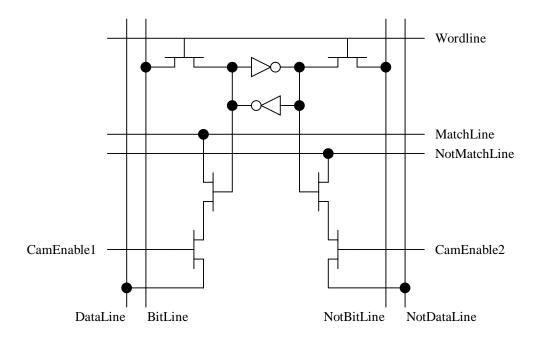

| Figure A.6 - Crossbar Intersection.                      | . 284 |

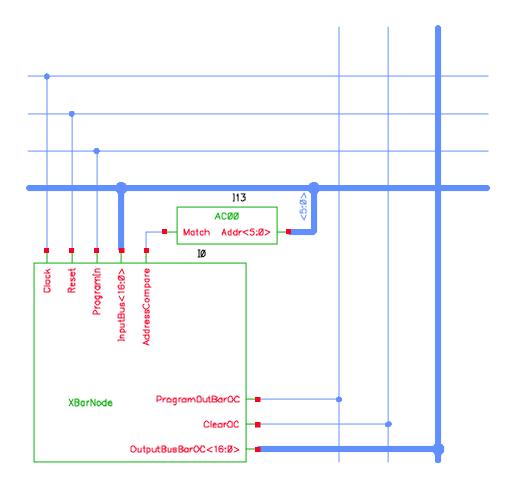

| Figure A.7 - Detailed XBarNode Intersection.             | 286   |

| Figure A.8 - XBarNode State Transition Diagram           | . 288 |

| Figure A.9 - Crossbar Column Output Inverter             | . 292 |

| Figure A.10 - Data Port Overview.                        | . 294 |

| Figure A.11 - Programming a port as an input.            | . 299 |

| Figure A.12 - Programming a port as an output.           | . 301 |

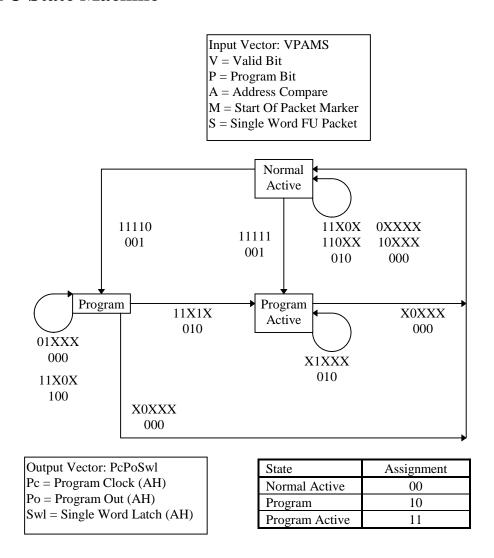

| Figure A.13 - Data Port State Machine Transitions.       | . 307 |

| Figure A.14 - Data Port State Machine Equations.         | . 311 |

| Figure A.15 - Bi-Directional Pin Model.                  | . 325 |

| Figure A.16 - High Strength Bi-Directional Driver.       | . 327 |

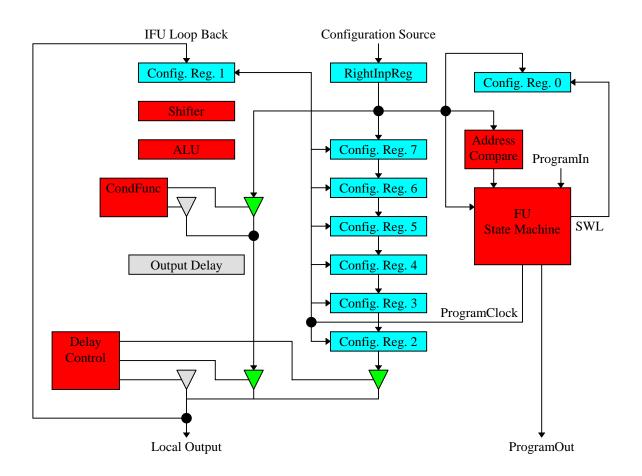

| Figure A.17 - IFU Connectivity.                          | . 329 |

| Figure A.18 - IFU State Machine Schematic.               | 332   |

| Figure A.19 - IFU Right Input Register Priority Encoder. | . 335 |

| Figure A.20 - Detail of East Skip Bus Design.            | . 338 |

| Figure A.21 - Detailed FU Data Path.                     | . 340 |

| Figure A.22 - Left Input Register Latch Function PLA File. | . 342 |

|------------------------------------------------------------|-------|

| Figure A.23 - Barrel Shifter Construction.                 | . 343 |

| Figure A.24 - General ALU Bit Slice.                       | 345   |

| Figure A.25 - Even ALU Bit Slice.                          | 347   |

| Figure A.26 - Odd ALU Bit Slice.                           | 348   |

| Figure A.27 - Conditional Unit PLA File                    | . 350 |

| Figure A.28 - Floating Point Mantissa Alignment.           | . 355 |

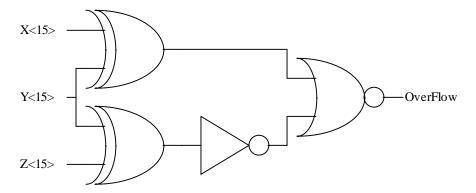

| Figure A.29 - ALU Overflow Function.                       | 356   |

| Figure A.30 - FU Configuration Path.                       | . 358 |

| Figure A.31 - FU State Machine Transition Diagram.         | . 361 |

| Figure A.32 - FU State Machine PLA File                    | 363   |

| Figure B.1 - Coltgui Initial Window.                       | . 365 |

| Figure B.2 - Coltgui Mesh Configuration Window.            | . 366 |

| Figure B.3 - Coltgui Stream Sequencing Window.             | . 367 |

| Figure B.4 - Coltgui Crossbar Control Window.              | . 368 |

| Figure B.5 - General DFC Program Format.                   | 369   |

# **List of Tables**

| Table 2.1 - General Purpose Processor Unit Sizes [7].                                   | 17  |

|-----------------------------------------------------------------------------------------|-----|

| Table 2.2 - Xilinx XC4000 Series Specifications.                                        | 27  |

| Table 2.3 - Xilinx XC6200 Series Specifications [13].                                   | 30  |

| Table 3.1 - Chebyshev Terms Required To Approximate Elementary Functions                | 69  |

| Table 4.1 - Comparison of 16-bit Unsigned FPGA Multiplier Implementations               | 129 |

| Table 6.1 - Xilinx XC4013E FIR Adder Resource Requirements.                             | 197 |

| Table 6.2 - Xilinx XC6216 FIR Adder Resource Requirements.                              | 199 |

| Table 6.3 - FIR Evalutation Performance By Device                                       | 207 |

| Table 6.4 - Area Normalized FIR Evalutation Performance.                                | 208 |

| Table 6.5 - Colt Unit Layout Sizes                                                      | 209 |

| Table 6.6 - Comparison of Speedup vs. Microprocessor Results for FIR filter application | 215 |

| Table 6.7 - Peak Configuration I/O Rate Comparison.                                     | 218 |

| Table 6.8 - Basic Configuration Storage Density Comparison.                             | 220 |

| Table 6.9 - Configuration Time Speedup Due To Partial Reconfiguration.                  | 225 |

| Table 6.10 - Operating Frequencies of FIR filter Implemenations vs. XC4013E             | 228 |

| Table 6.11 - Number of FIR Filter Configurations Speedup vs. XC4013E                    | 230 |

| Table 6.12 - Calculated Configuration Time Speedup Factors vs. XC4013E                  | 231 |

| Table 6.13 - CCM Reconfiguration Time Ranges.                                           | 235 |

| Table 6.14 - Colt Reconfiguration Times Relative To Other FPGAs.                        | 237 |

| Table 6.15 - Calculated Execution Speedup Factors vs. XC4013E.                          | 239 |

| Table 7.1 - Communication Network Sizing Strategies                                     | 249 |

| Table A.1 - Colt Unit Addresses                                                         | 279 |

| Table A.2 - XBarNode State Equations.                                                   | 289 |

| Table A.3 - Data Port State Machine Inputs.                                             | 308 |

| Table A.4 - Data Port State Machine Outputs                                             | 308 |

| Table A.5 - Data Port State Machine State Assignment.                                   | 309 |

| Table A.6 - IFU Input Select Encoding.                                                  | 336 |

| Table A.7 - Left Input Register Latch Function.  | 341 |

|--------------------------------------------------|-----|

| Table A.8 - Latch Function Output Equations.     | 342 |

| Table A.9 - Shift Condition Input Select.        | 344 |

| Table A.10 - Conditional Unit Control Equations. | 351 |

| Table A.11 - Control Flag Multiplexer Values.    | 352 |

| Table A.12 - FNOut Input Sources.                | 354 |

| Table A.13 - FU State Machine Equations.         | 364 |

# 1. Introduction

## 1.1 Scope

The goal of this research is to develop the computational core of a hardware platform for performing high speed Digital Signal Processing (DSP). The effort is driven by the need to attain higher computational performance to meet the escalating demand for such things as wireless communication systems. The computational needs of the DSP platform are met by the solution presented here. At the same time, the solution maintains enough flexibility to be applicable to a much broader domain of computing. The computing platform will be used in a prototype communications system that will demonstrate many algorithms designed to provide higher utilization of communications channels. Many of the demands of DSP applications are also common to more general processing tasks such as numerical scientific computing, image processing and many types of simulation.

### 1.2 Problem Overview

The problem of high performance computation has been a field of intense research for almost a half century. While improvements in computational ability have been gained, most of these have been achieved through the development of better manufacturing processes that allow higher speed computational cores to be constructed economically. Speedup gains through architectural innovation have been modest by comparison. One of the great enigmas of computer

architecture has been scalability; the question of how to successfully apply more than a single computational element to a problem to gain speedup without greatly sacrificing utilization efficiency. Efficiency may be lost to inherently sequential sections of the algorithm and is therefore bounded by Amdahl's law [3]. Efficiency may also be lost to communications overhead between processing elements. This communications overhead can take the form of data overlap between processors that must exchange operands in a lock-step fashion, or simply long latencies in the communications network. Many of these issues are addressed by the architectural implementation proposed.

Silicon utilization is a second domain where the efficiency of available processing elements often suffers. As will be shown in Section 2.1.2, only a small percentage of the active silicon on a microprocessor of today is devoted to actual computation of data. Most of the area is used to support the Von Neumann fetch-execute cycle by either performing a form of address decoding or some type of speedup of this process. Even within the computational circuitry itself there is a loss of efficiency. During normal operation many of the processing functions of a chip lie idle while a few are in use. Some processors can make better use of available resources simultaneously, but only at the cost of additional support hardware.

Finally, a concern in all portable systems today is power consumption. This particularly applies to systems that need to be deployed in portable radios and cellular phones. Here, power is at a premium and lower power consumption translates into longer battery life and better

<sup>3</sup> Amdahl, G., "Validity of Single Processor Approach to Achieving Large Scale Computing Capabilities," *Proceedings of the Spring Joint Computer Conference*, pp. 483-485, April 1967.

customer satisfaction. Another use of low power systems is in space-based systems such as communications satellites where all available power must often come from solar power panels. Low power systems are also found in autonomous systems such as sonar nets and buoys that are isolated in the ocean waiting for a local disturbance to awaken them. On a more earthly note, low power design becomes more critical as VLSI process technology increases the density of transistors on a chip. As the transistors are moved closer together, more heat per unit area is generated and the potential for melt-down increases.

CMOS technology is noted for low quiescent power dissipation. As long as a fully complementary CMOS design remains in the same state, almost no power is consumed. Here again, the high overhead of implementing a processor based on a Von Neumann architecture leads to undue waste. Since such a small percentage of the processor is actually used for computation, all the activity in the chip that is used to support that computation is consuming power that could be used for other purposes. The area consumed by the support circuitry leads to poor computational density, and the power it dissipates leads to shortened chip and battery life. The architecture proposed in this research will attempt to address these issues as well.

## 1.3 Proposed Solution

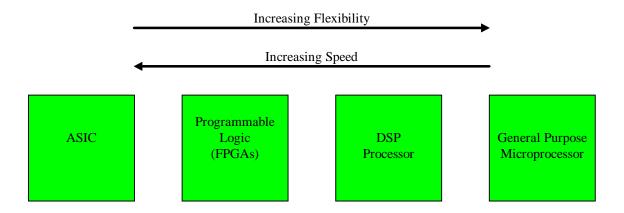

**Figure 1.1 - Computing Implementation Alternatives.**

Figure 1.1 is one vision of the lineup of available computing solutions today. Unquestionably, the fastest way to solve any problem is through the use of an Application Specific Integrated Circuit (ASIC), shown on the left. ASICs have a high Non-Recurring Engineering (NRE) cost initially as well as a long development cycle. These costs, coupled with the fact that silicon is an irreversible design medium, make the frequent changes during development cycles, corrections and upgrades difficult to justify. At the other end of the computing spectrum are general purpose microprocessors. These are typically based upon a Von Neumann style instruction sequence and can be quickly shifted from one computational task to the next. Unfortunately, the generality of design in these components makes them poorly suited to fit any particular computing niche. In between are Programmable Logic and Digital Signal Processors (DSPs). DSPs still execute the fetch-execute cycle, but they are geared towards a computational environment by the inclusion of extra hardware for performing fixed and floating point computations much faster. The makers of these chips can justify the extra silicon used by

citing the higher proportion of mathematical instructions typically present in numerically intensive applications.

Programmable Logic Devices (PLDs) bridge the gap between ASICs and microprocessors. Typified by Field Programmable Gate Arrays (FPGAs), Programmable Logic Devices are constructed in a generic manner to facilitate programming at the logic gate level after manufacture. The exact form of the function of the chip is determined by a large number of static RAM cells that connect and create whatever logic functions are required. Thus, the function performed by the chip is a simple matter of changing the values of these RAM cells. By allowing programming at such a low level, the hardware on the chip can be tailored to exactly fit the task at hand. Thus, for some applications an FPGA can outperform a DSP. However, programmable routing and associated overhead often leave FPGA performance in the wake of a well designed ASIC.

One way to improve the overall flexibility-speed product of FPGAs is to decrease the reconfiguration time, i.e. the time spent changing the value of the memory cells to perform a new task. In the past, most FPGA designs have been static in nature. A single design is loaded into the FPGA and it remains unchanged for the duration of circuit operation. Many efforts are currently underway to employ run-time reconfiguration with FPGAs to dynamically change the programming of the FPGA while the circuit is in use. The exact function of the FPGA can be targeted and re-targeted to accelerate the solution of whatever problem the system is currently trying to solve. This allows emulation of a large hardware platform using a small device. Obviously, the faster the re-targeting operation can occur, the more instances in which FPGA acceleration can be employed, and hence the faster the overall execution.

Existing methods for performing this reconfiguration are primitive. Typically, only a small percentage of the pins on an FPGA can be used for reconfiguring the design, thus the operation is I/O bound. Further, most FPGAs can only be reconfigured as a unit, or as blocks that represent a large percentage of the overall computational resources to be had. This limits both the degree of parallel configuration that is possible as well as fixing the degree of resource fragmentation for a given configuration. Also, while reconfiguration takes a coarse grain approach, the actual computations take a very fine grain approach, resulting in large amounts of silicon area being devoted to routing resources and configuration storage.

One of the unique contributions of this research is Wormhole Run-Time Reconfiguration (RTR). Wormhole RTR is a method for reconfiguring an FPGA, or an entire system, in an entirely distributed fashion. Routing and programming are handled at a local rather than at a global level. Without the need for global control, the amount of hardware necessary to control the configuration process on-chip diminishes greatly; thus it is possible to practically achieve finer grain divisions between computational resources and limit resource fragmentation. Further, because Wormhole RTR is a distributed paradigm, it allows different parts of the same resource, an FPGA for example, to be independently configured through many different data paths simultaneously. While care must be taken to ensure that resource allocations do not overlap, multiple independent configuration paths greatly increase the configuration bandwidth of a given device, enhancing reconfiguration speed and overall system performance. The paradigm also enhances the fault tolerance of a device. The lack of a central controller means that there are fewer single point failures that can lead to total system failure. Also, when a failure does occur, the local nature of Wormhole RTR allows it to route around the problem area and use other

resources that are functional. This has possibilities not only for faults that occur over a period of time, but also for faults in parts that are fresh off the assembly line, improving chip yields through dynamic reconfiguration around manufacturing defects. These advantages and more will be further expounded upon later.

The Colt chip embodies the Wormhole RTR concept. Fitting somewhere between an FPGA and a DSP in the computational spectrum, the Colt contains elements of both. Nearly all of the pins on the device serve both as configuration as well as data I/O resources, providing six independent paths onto the chip that can simultaneously be used to configure computational resources. Further, the resources on the chip are word-oriented rather than bit-oriented, giving several advantages. First, the chip requires less routing control, giving better overall propagation delay times and allowing faster operation than a bit-oriented FPGA. Second, fewer memory storage elements are required for configuration information since all bits in a given word are configured en masse, as opposed to the typical bit by bit configuration in a typical FPGA. This saves silicon area that can then be used for computation. A further benefit of this is that fewer bits need to be moved onto the chip to specify a new configuration, allowing faster reconfiguration times than with a typical FPGA. The Colt includes some aspects of DSPs by including a number of computational resources that are specialized for mathematical functions. A 16x16 fixed point multiplier has been incorporated in the design to enhance performance for mathematical operations. Further, the basic computational elements (Functional Units or FUs) include additional hardware, such as a barrel shifter, to aid in floating point processing as well as some integer multiplication operations. Colt architectural features and implementation will constitute a second major thrust of this work.

#### 1.4 Contributions & Claims

There are two contributions to the Configurable Computing Machine (CCM) field that will be presented in this thesis. The first is the Wormhole Run-Time Reconfiguration paradigm. More than a simple extension of the traditional FPGA concept, Wormhole RTR explores new ground in the use of reconfigurable logic. Through the implementation of Wormhole RTR on the Colt CCM, improvements have been made with regard to microprocessor and/or FPGA performance in terms of:

- Execution Overhead

- Configuration I/O Rate

- Broadcast Programming

- Partial Run-Time Reconfiguration

- Degrees of Concurrency

- Global Routing Complexity

- Overall Speed of Reconfiguration

The second contribution is the design and development of the Colt CCM itself. There are many features that have been designed into this device that are unique. For one, it is the first device to incorporate Wormhole Run-Time Reconfiguration. All of the various resources available on Colt have been designed for use with the Wormhole RTR paradigm and so stand as examples of how this can be done. Also, Colt incorporates the idea of the Skip Bus. This segmented interconnection scheme has been superimposed over the normal mesh topology in

order to allow the greater connectivity required to map data flow graphs while not consuming vast amounts of area for routing. Finally, Colt is word-oriented rather than bit-oriented, and it has been designed with complex calculations in mind. No commercial CCM devices existing today can claim a word-oriented architecture. The benefits of this improvement alone with regard to contemporary FPGAs are seen in terms of:

- Computational Density

- Overall Speed of Execution

- Configuration I/O Rate

- Configuration Storage Density

- Routing Overhead

- Operating Clock Frequency

- Overall Speed of Reconfiguration

- Overall Speed of Execution

The Wormhole Run-Time Reconfiguration paradigm that is discussed at length in Chapter 3 has many promising characteristics that could be applied to a much broader class of computing platforms than simply traditional FPGAs. The characteristics listed here are quantified in Chapter 6; however, there are several more that are not so easily quantified, particularly as they might apply to designs larger than a single Colt device. These have been expounded upon in Chapter 3 and throughout this thesis as possible points of departure for future research. Likewise, the Skip Bus and some other Colt specific features will be difficult to

quantify until such time as the completed system has been built. It will remain for those who follow to judge the merits of these contributions.

#### 1.5 Dissertation Outline

This work will describe a solution to the problem discussed in Chapter 1. Chapter 2 will begin with an overview of existing technologies, focusing mainly on commercial products. Some commentary on the relative merits of the various approaches will be included. This is followed by an overview of the data flow computing paradigm and some of the merits and drawbacks thereof. Chapter 3 introduces the particular implementation of the data flow paradigm used for this research. A discussion of the implementation strategy indicates how a limited data flow paradigm can be readily mapped to an FPGA style architecture giving benefits for communication overhead and pipelined implementation. Following this will be a discussion of the Wormhole Run-Time Reconfiguration (RTR) method. The method is expounded upon at length, with a great deal of time spent in delineating the benefits and how it fits in with existing research and technology. Chapter 4 presents the Colt architecture, a chip that has been designed based on the Wormhole RTR concept. An overall system perspective of the Colt is presented followed by sections on the major units of the chip with some features of their design that have been incorporated for various computational tasks. Chapter 5 discusses several key applications that illustrate various concepts of the Colt architecture. These include the implementation of a simple dot product of two vectors, and an example of floating point arithmetic. The chapter concludes with an example of conditional data flow execution. Chapter 6 gives a comparison of Colt performance versus other architectures both in terms of raw computing power and of normalized measures of performance. Chapter 7 gives ideas for future research directions and design improvements that could be made in the Colt architecture and some ideas for the larger system. The first appendix contains an in-depth look at the design of the entire chip, discussing design tradeoffs, state machine implementation and critical path design of each unit on the Colt. The second appendix contains documentation and source code required for the implementation of a floating point multiplier on Colt.

# 2. Background

This chapter discusses various implementation approaches that could be taken to solve the DSP problem and their relative merits. Three possibilities are delineated: ASICs, DSPs and CCMs. The second half of the chapter begins with a discussion of recent trends in the design of microprocessors and the place of data flow computation in their evolution. Current data flow processing is reviewed as the chapter concludes.

### 2.1 Prior Work

#### 2.1.1 ASIC Solutions

Assuming that the data paths, operators and pin functions are predefined, an Application Specific Integrated Circuit (ASIC) can be used to achieve the most efficient use of hardware resources in terms of speed, power, silicon area consumed or whatever other criteria are important for meeting the goals of a given task. Because of these factors an ASIC can also achieve the lowest cost per part for mass production usage. However, the design of an ASIC requires a large Non-Recurring Engineering (NRE) cost in terms of time and man power to produce final silicon. Further, once the design is completed, it is final. It is impractical to make changes in the finished silicon to correct errors in either the original concept or in the implementation of the original vision. Even in the absence of any design flaws, an ASIC is

limiting in that it allows no variations in functionality beyond those foreseen at the beginning of the design process. If better algorithms or techniques are discovered, they cannot be applied in the existing parts.

This final point is really the best case against using an ASIC for prototyping any system. There may be different algorithms that the end users of the system may wish to employ. Indeed, the exact algorithms that will be needed may remain unknown until a prototype is built. Such is the case for the communications system that this platform is targeted for. Furthermore, as will be explained in Section 2.1.3, though one of the advantages of an ASIC implementation is the ability to tailor it to a specific application, the fixed nature of an ASIC can ultimately lead to poorly utilized silicon area even for the application to which has been tailored. As points of reference, two specific ASIC devices will be examined in the remainder of this section.

#### 2.1.1.1 Harris Semiconductor HSP45256

It is relatively common to find DSP kernels implmented as ASICs. One such chip is the Harris Semiconductor HSP45256, which is being used for prototype systems at Virginia Tech [4]. This chip can be used to implement FIR filters of the type needed in power of two sizes including 32, 64, 128 or 256 taps depending on the bit width of the input data. Input data widths of 1, 2, 4 or 8 bits are supported. To determine the number of taps that can be implemented, divide 256 by the input data bit width. For purposes of an FIR filter as described in Section 6.1, the spreading code is programmed as a single bit "reference" for each tap in the filter.

<sup>4</sup> Harris Semiconductor, *Harris Semiconductor Digital Signal Processing Databook*, 1994, pp. 7-21 - 7-33.

The Virginia Tech Glomo project [5] requires at least 12 bit samples and a 60 tap FIR filter with 7.86 million samples per second arriving from the antenna. Using creative reconfiguration of the ASIC, four different configurations could be used to perform the desired computation which would allow approximately 10 million samples per second to be processed. Of course, additional memory and control hardware would be required.

#### 2.1.1.2 Logic Devices Incorporated LF2242

The LF2242 is an FIR filter designed to implement a low pass filter [6]. The weights of the filter are fixed so that it implements low pass filtering exclusively. This chip, in contrast with the Harris chip, demonstrates the tradeoff of performance verses flexibility. Both chips operate at 40 MHz; however, the LF2242 accepts 12 bit samples into a 55 tap FIR as opposed to 8 bit samples into a 32 tap FIR in the Harris chip. In the Harris, the weights are programmable, but in the LF2242 they are fixed. Greater flexibility comes at the expense of overall performance. The LF2242 is not suited for some tasks in the Virginia Tech Glomo project, such as the remote unit FIR application, since the spreading code vector could not be programmed into it.

### 2.1.2 DSP Solutions

Digital Signal Processing (DSP) chips have been developed in recent years in an attempt to address the large computational requirements of digitally based communications systems and

<sup>5</sup> Rappaport, T. S., Athanas, P. M., Reed, J. H. and Woerner, B. D., "A High Capacity Adaptive Wireless Receiver Implemented with a Reconfigurable Computer Architecture," *ARPA Principle Investigators Meeting*, Fort Lauderdale, Florida, July 1995.

<sup>6</sup> Logic Devices Incorporated, *DSP Data Book*, July, 1995, pp. 2-3 - 2-10.

some other types of processing. These chips are modeled after conventional microprocessors with extra silicon devoted to specific operations in order to achieve higher performance. Typically, fixed or floating point computations can be handled with equal ease and in comparable amounts of time. A multiply-accumulate (MAC) unit is usually included for the computation of dot product like formulations.

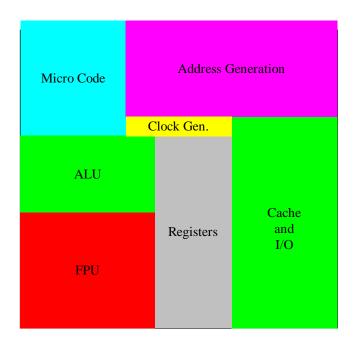

The main argument against using a DSP as the processing element of a computationally intensive system is that DSP processors, and general purpose processors for that matter, focus on sequential execution of applications. In so doing, DSPs devote most of their silicon area to non-computational tasks. Microprocessor's of today incorporate cache, memory I/O units, instruction decoders, pipeline and superscalar control units, large register files, etc.; all in an effort to bring the operands to the arithmetic units faster so that the program will execute faster. An effort has been made by Flynn to empirically quantify the distribution of the amounts of silicon used on a general purpose processor for all the various functions that people have come to expect [7].

Though Flynn uses the relative sizes to describe a floor planning methodology, the same information can be used to show the amount of overhead that is incorporated into today's processors. The dimensions for various units that are described are given in terms of a unit A, defined by Flynn as being 4 million  $\lambda^2$ . The unit  $\lambda$  is used in VLSI terminology to abstract the minimum length of a transistor in a given process. This unit was proposed by Mead and Conway as a means of dealing with the problem of quantifying the size of a circuit in the face of ever

<sup>7</sup> Flynn, Michael J., *Computer Architecture: Pipelined and Parallel Processor Design*, Boston, MA, Jones and Bartlett Publishers, Inc., 1995, pp. 90-99.

changing process specifications [8]. It is defined as the distance by which a geometric feature on any one layer of implementation may stray from another geometric feature. For example, in a  $0.8\mu m$  process the minimum length of a transistor is  $0.8\mu m$ , which is defined to be  $2\lambda$ , so for that process  $\lambda = 0.4\mu m$ . There is some variation in the relative distances between features from process to process, but on the whole this system gives a good means for comparing relative circuit sizes between two different processes.

Flynn defines a basic RISC style microprocessor with 32 registers of 32 bits each, an integer ALU and an integrated floating point unit. It is assumed that the processor has an instruction pipeline of 4 or 5 stages to implement a load/store architecture that are referred to as being typical of the early 1990s. He states that the complexity of the instruction set will only affect the relative area of the control units modestly. Below are the relative sizes of various units as he tabulates them.

<sup>8</sup> Mead, C. and Conway, L., *Introduction to VLSI Systems*, Series in Computer Science, Reading, MA, Addison-Wesley, 1980.

Table 2.1 - General Purpose Processor Unit Sizes [7].

| Integer Unit            |        |  |  |  |

|-------------------------|--------|--|--|--|

| Unit                    | Area   |  |  |  |

| Integer ALU (32 bit)    | 1.0A   |  |  |  |

| Bypass                  | 0.15A  |  |  |  |

| Integer Registers       | 1.0A   |  |  |  |

| Shifter                 | 0.5A   |  |  |  |

| Incrementor             | 0.4A   |  |  |  |

| I-fetch/PC unit         | 0.85A  |  |  |  |

| 2 Translation Look      | 2 * 3A |  |  |  |

| Aside Buffers           |        |  |  |  |

| (For Memory Paging)     |        |  |  |  |

| Decode and Control      | 1.0A   |  |  |  |

| Cache Controller        | 1.0A   |  |  |  |

| Bus Logic               | 2.0A   |  |  |  |

| Store Buffer and Bypass | 1.0A   |  |  |  |

| Load/Store Byte Support | 0.2A   |  |  |  |

| Clock Generator         | 1.0A   |  |  |  |

| Subtotal                | 16.1A  |  |  |  |

| Floating Point Unit     |        |  |  |  |

| Register File           | 1.0A   |  |  |  |

| Adder                   | 13.5A  |  |  |  |

| Multiplier              | 20.3A  |  |  |  |

| Division Support        | 3.0A   |  |  |  |

| Subtotal                | 37.8A  |  |  |  |

| Complete Processor      |        |  |  |  |

| Integer Unit            | 16.1A  |  |  |  |

| Floating Point Unit     | 37.8A  |  |  |  |

| Latches and Buses       | 27A    |  |  |  |

| Total Area              | 80.9A  |  |  |  |

Table 2.1 indicates that in the integer processor the actual data processing units, consisting of the ALU, shifter and incrementer occupy 1.9A of the silicon resources. The one unit that is conspicuously absent from the table is cache. Flynn computes an area estimate of

15.9A for a rather modest 4K cache. For the processor as a whole, adding in the active units in the floating point hardware, (1.9A+36.8A)/(80.9A+15.9A) = 40% of the processor is actually used for computation of data. The rest of the area is used to feed that hardware at the fastest rate possible with new data. In effect, it is overhead needed by the control driven Von Neumann architecture to keep the data computation rates at acceptable levels.

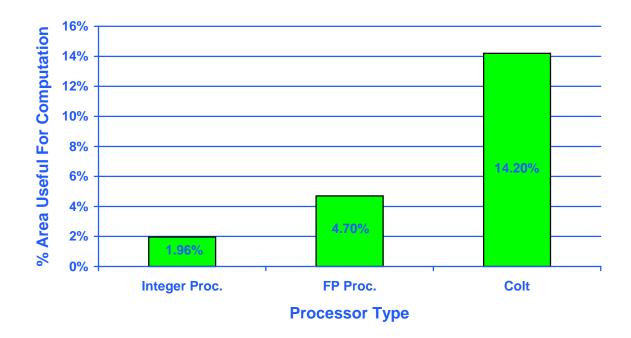

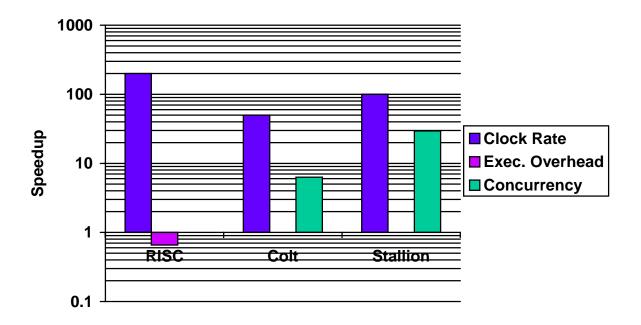

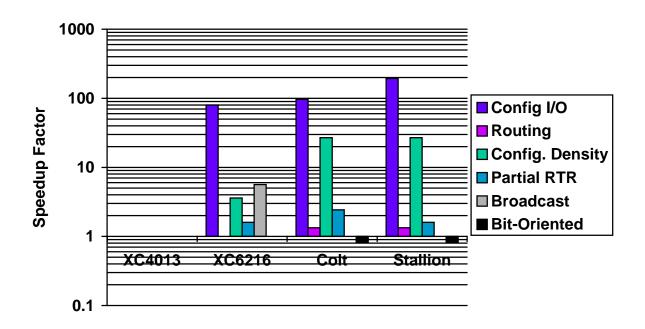

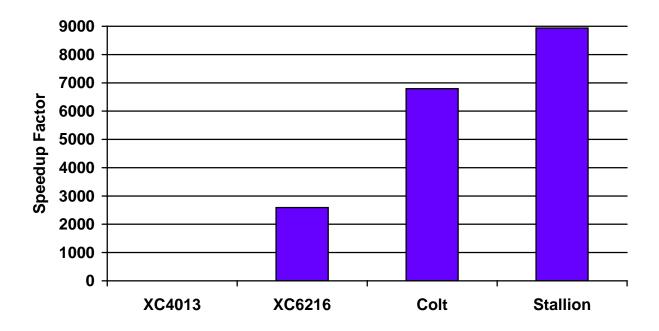

For the purposes of many DSP applications it may not be necessary to implement floating point arithmetic at all, in which case the amount of silicon dedicated to computation is only 1.9A/(80.9A+15.9A) = 1.96%. This is an abysmally low number for silicon utilized. To be fair, if it is known that floating point computation will not be required, a processor that does not have a dedicated floating point unit could be chosen. Using Flynn's approximation of adding 10% to the unit area for latches and another 40% for buses and control, we get an approximate total area estimate of 16.1A\*150% = 24.15A for a purely fixed point processor. Thus, the amount of silicon devoted to computation in such a processor would be 1.9A/(24.15A+15.9A) = 4.7%. Note that even these numbers are generous because 4K is a rather conservatively sized cache. Also, this is just the level 1 cache, which is usually augmented by a level 2 cache of 256K or more. Again, the problem is obvious: to much silicon is being used for overhead processing and not enough for computation. This is the main argument against general purpose and DSP processors.

## 2.1.2.1 Analog Devices ADSP-21060 SHARC

The 21060 Super Harvard Architecture Computer (SHARC) typifies a contemporary high-performance DSP [9]. Running at 40 MHz, the chip achieves 120 MFLOPs peak with a sustained throughput of 80 MFLOPs. IEEE 32-bit floating point format is supported throughout the system. A multiply and add of two independent sets of floating point operands can be issued and completed in a single clock cycle, achieving 80 MFLOPS operation. For the purposes of computing Fast Fourier Transforms (FFTs), an independent multiplication can be done at the same time as the addition and subtraction of the same set of operands; all in one clock cycle giving 120 MFLOP peak performance. Data is supplied to the computing engine by a Super Harvard Architecture using three buses. One bus (DM) fetches data from memory each clock cycle. The second bus (PM) can fetch either a data operand from data memory or an operation from program memory if there is a cache miss. The third bus fetches op codes from the cache when possible. 4 Mbits of RAM are built into the chip, which can be used in several different word widths including 16, 32 and 48 bits. Using the 32-bit configuration, there are 128K words of onboard RAM. There are also extensive communications and I/O resources; including independent DMA controllers, serial ports and additional parallel data ports.

This chip was chosen by the communications groups in the Virginia Tech Glomo project for use in implementing their prototype systems. By making a number of simplifying assumptions in the algorithms, they have been able to produce a system that can operate at a maximum data rate of 30Kbps; less than ¼ of the 128Kbps rate required in the final system. It is

<sup>9</sup> Analog Devices, DSP/MSP Products Reference Manual, 1995, pp. 2-215 - 2-250.

difficult to determine the amount of silicon resources that have been used in the 21060 to implement the floating point unit(s); however, accomplishing a full floating point multiplication or addition in 25 ns is quite a feat. The 21060 can do both, indicating the amount of resources that have been thrown at the problem. In the 60 tap FIR filter example needed for the base station, the SHARC can do a MAC operation every clock cycle, so it could do 40MHz/60 = 0.67 million evaluations per second; a bit short of the required 7.86 million evaluations per second. To be fair, the SHARC can do this using full floating point weights and data points, whereas the other benchmarks presented here can only operate with integer operands and in some cases the weights may only be one bit wide.

### 2.1.3 FPGA Solutions

An interesting alternative to ASIC and DSP devices are Field Programmable Gate Arrays (FPGAs). These chips are programmable at the logic gate level. In a standard microprocessor, the logic gates which comprise the functionality are set at the time of manufacture. Groups of gates perform dedicated functions and the functionality of these gates never changes over the life of the chip. Instead, the microprocessor iterates through the Von Neumann fetch-execute cycle. Instructions are read (fetched) from memory by the microprocessor in an order specified by the programmer. These instructions dictate which set of gates to apply to the data at the current time step.

In contrast, the gates in an FPGA are not connected in a particular configuration at the time of manufacture. Instead, the chip can be loaded with new configurations at will. This allows the operations performed on the data by a given set of gates to be tailored to a particular

application. The exact function required can be performed with the exact precision required. A microprocessor typically performs functions on a fixed bit width (8, 16, 32 or 64 bits), regardless of the number of bits of precision required. The Virginia Tech Glomo project, for example, requires 12-bit fixed point data operands. The mathematical operations performed on these can be guaranteed never to exceed certain bounds. If a set of 8 such numbers are added, the precision requirements for the sum can be guaranteed not to exceed 15 bits. Knowing this, the FPGA programmer can create mathematical units on the chip that operate with 15 bit sums rather than some number of bits set by a power of two. The end result is a net savings in the number of gates required to implement the algorithm and hence the final cost in terms of silicon consumed.

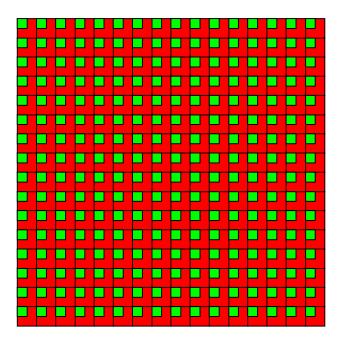

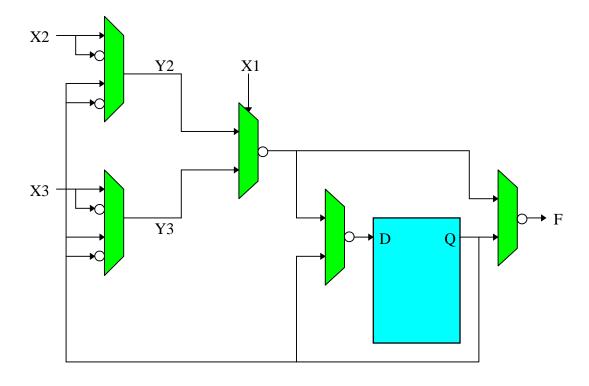

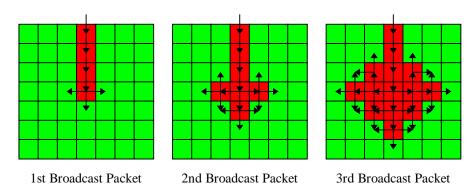

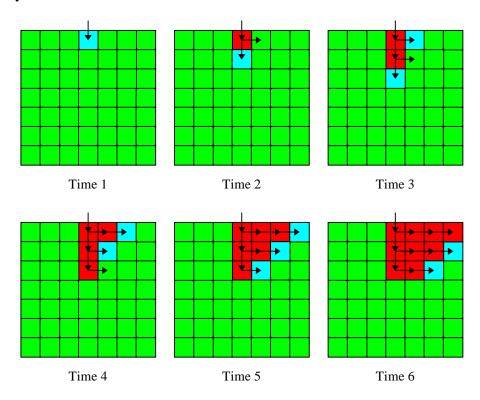

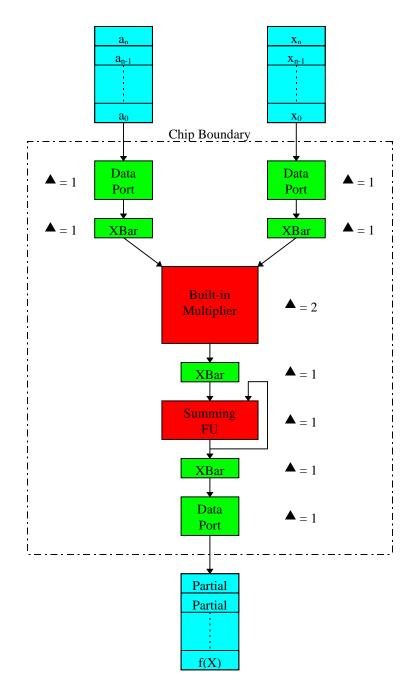

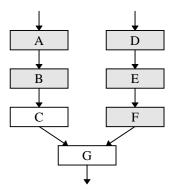

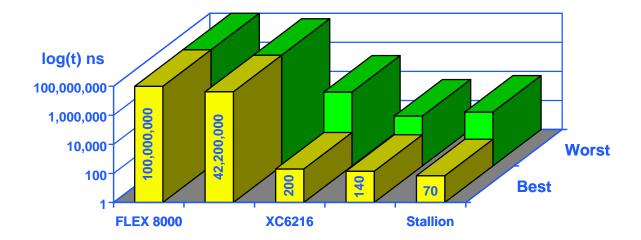

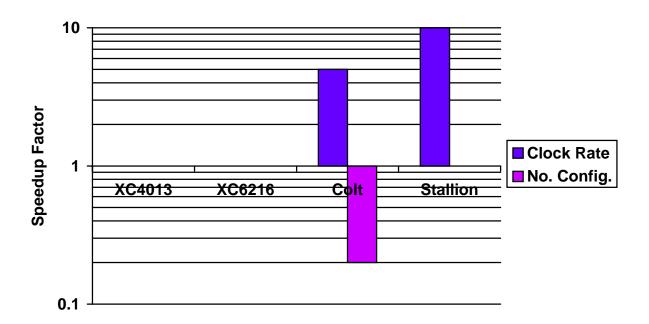

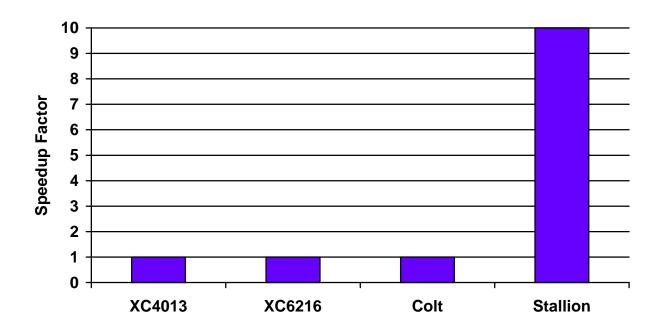

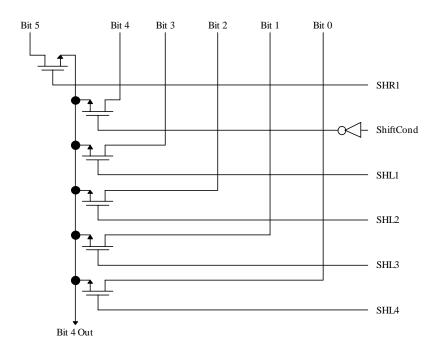

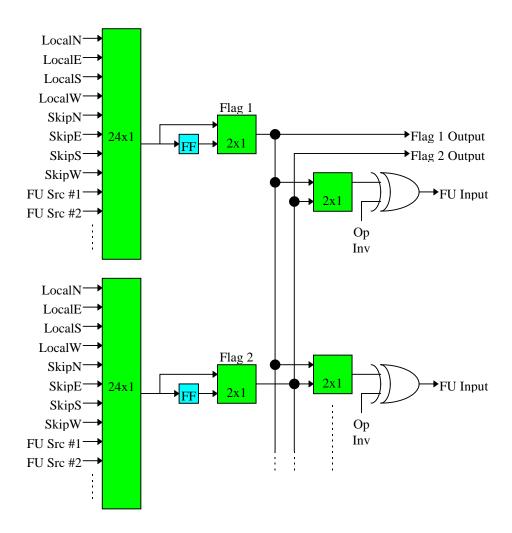

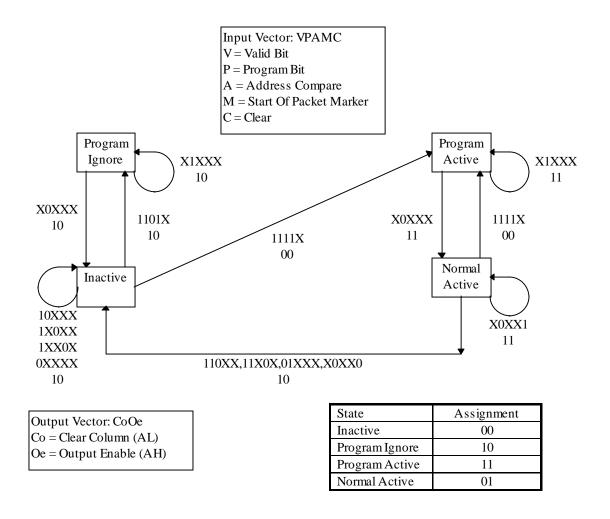

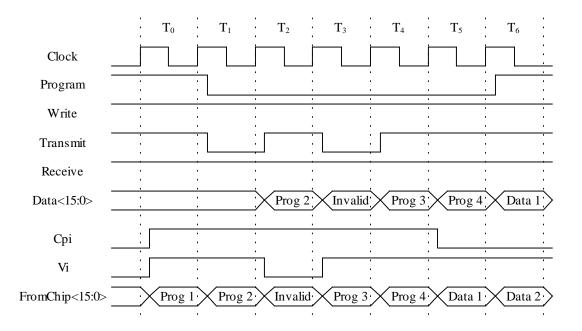

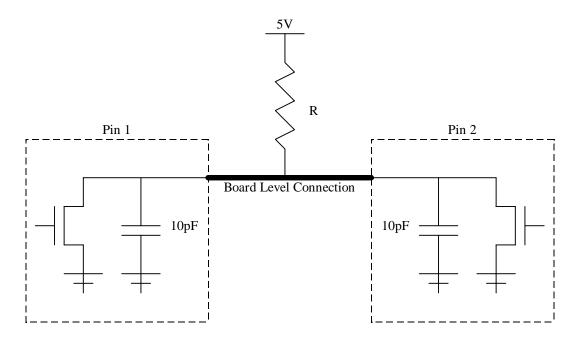

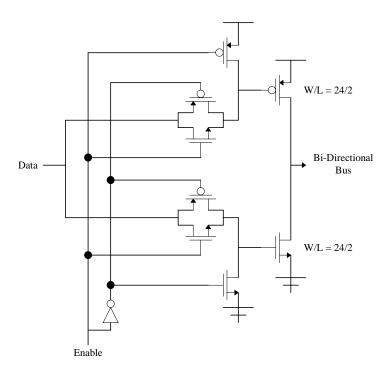

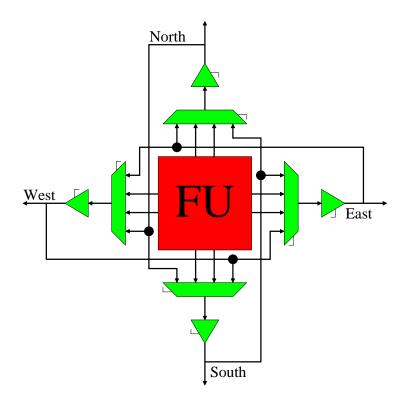

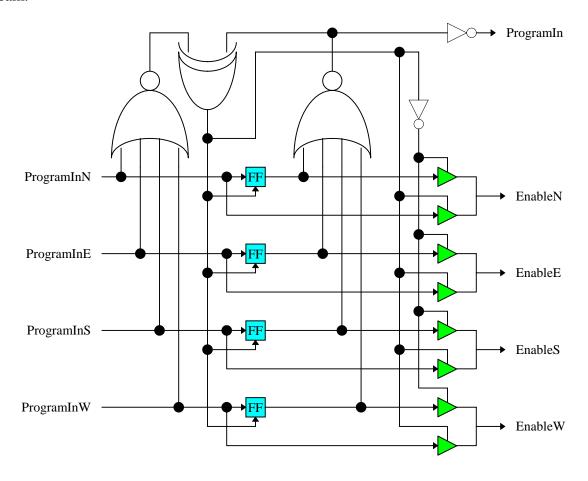

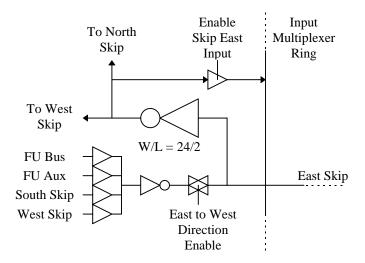

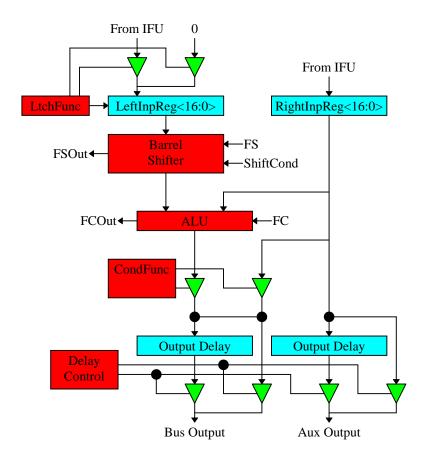

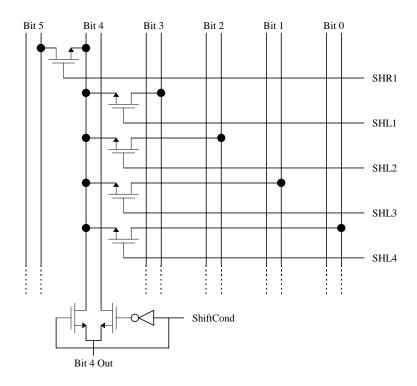

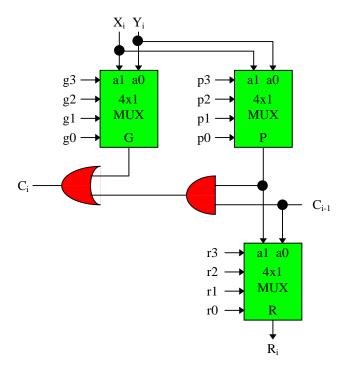

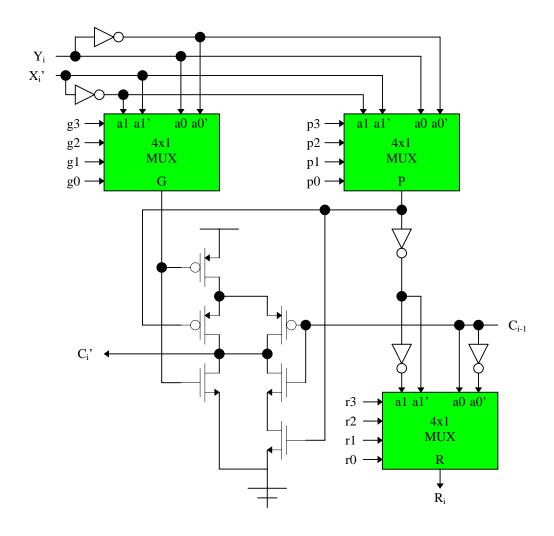

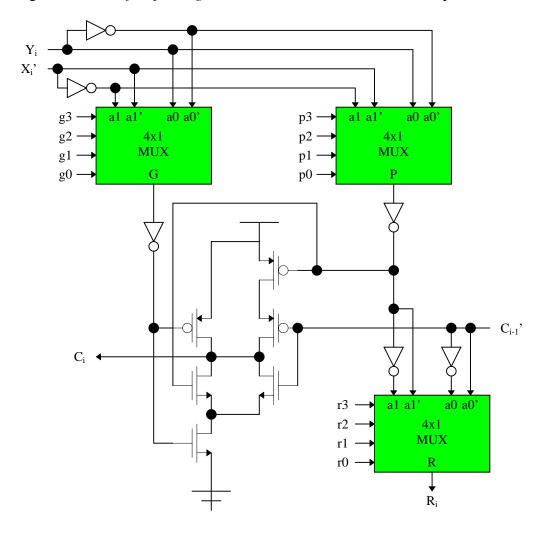

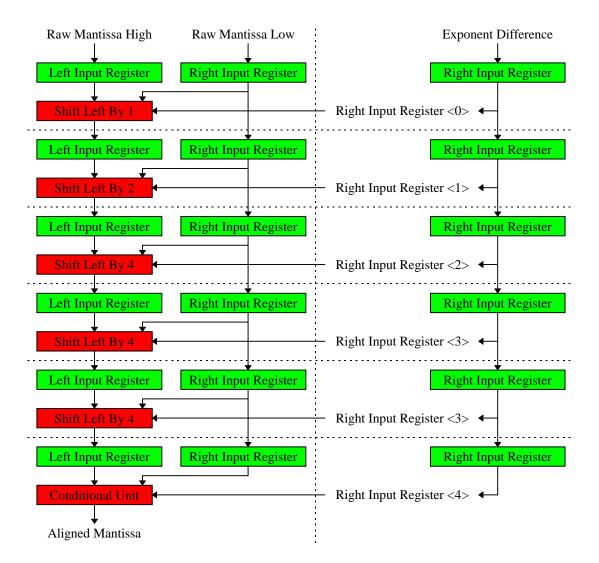

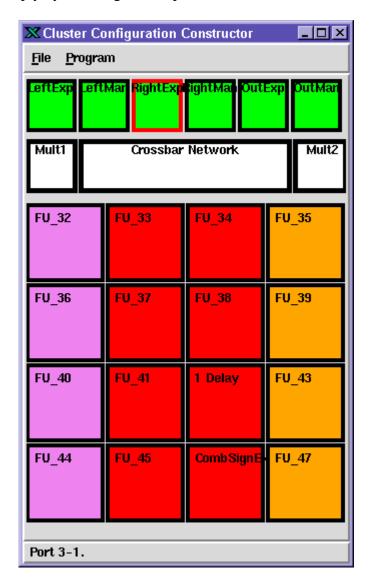

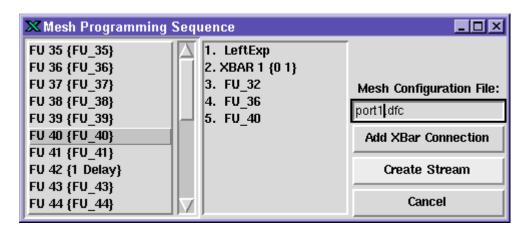

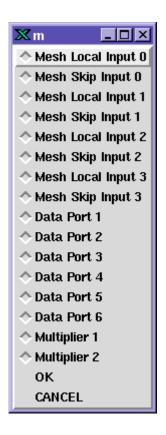

However, the savings in silicon is not quite as dramatic as has been implied. A gate in an FPGA consumes more area than the same gate in an ASIC or microprocessor. There are two factors contributing to this: programmability and routing. First, in order to provide the ability to program the gates with arbitrary functions it is necessary to include memory storage elements that set the function that a gate will perform. These storage elements are not required in an ASIC since the function can be fixed at design time. Alternatively, there are FPGAs in which a single functionally complete gate is used throughout the chip (perhaps they are all NANDs), thus no memory elements are required to set the function. However, more gates are then required to perform arbitrary functions. These FPGAs also suffer even more greatly from the second problem of routing.