# Table of Contents

| 1  | INTRODUCTION                 |                     |

|----|------------------------------|---------------------|

| 5  | INDUSTRY CONSORTIUM OVERVIEW |                     |

| 13 | RESEARCH                     |                     |

| 22 | INTELLECTUAL PROPERTY        |                     |

| 26 | FACILITIES                   |                     |

| 30 | SPOTLIGHT ON ALUMNI          |                     |

| 35 | PEOPLE                       |                     |

| 13 | HONORS & ACHIEVEMENTS        |                     |

| 15 | PUBLICATIONS                 |                     |

| 52 | CHARTER                      |                     |

| 56 | RESEARCH NUGGETS             |                     |

|    | 56                           | PMC Mini Consortium |

|    | 83                           | HDI Mini Consortium |

|    | 95                           | REN Mini Consortium |

|    |                              |                     |

Sponsored Research

# Introduction

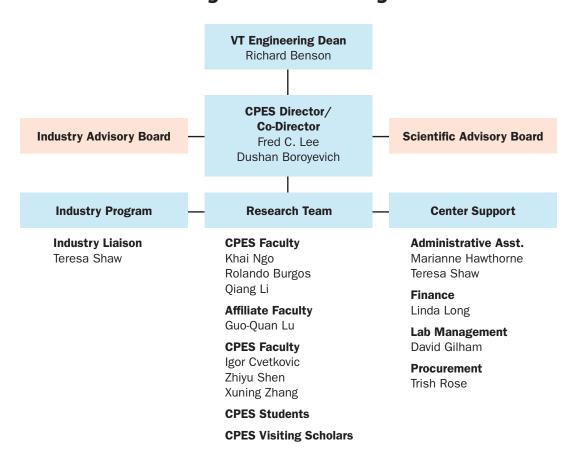

he Center for Power Electronics Systems (CPES) was established as a National Science Foundation Engineering Research Center (ERC) in 1998, and since then has become world-renowned for its research and education/outreach programs.

The power electronics program was first initiated in 1977 under the name PERG (Power Electronics Research Group). Later, in 1983, the program was renamed to VPEC (Virginia Power Electronics Center) when it became a university center. In 1987, VPEC became a Technology Development Center (TDC) of Virginia's Center for Innovative Learning (CIT).

The CPES mission is to provide leadership through global collaborative research and education in creating advanced electric power processing systems of the highest value to society. The Center believes it can make dramatic improvements in the performance, reliability, and cost-effectiveness of electric energy processing systems using an integrated approach via integrated power electronics modules (IPEMs), whose impact will mirror that of integrated circuits to microelectronics. The advances CPES makes in power electronics reduce power conversion losses and in turn increase the energy efficiency of equipment and processes using electrical power. According to the Electric Power Research Institute (EPRI), the widespread use of power electronics technology in the United States would reduce energy consumption by an estimated 33 percent, generating enormous economic, environmental and social benefits.

# **Statistics**

\$150M+

Research expenditures

**\*\*\* 215**

Companies have belonged to the CPES Industry Consortium

150

PhD degrees awarded

Patents awarded

25

Startup companies founded by CPES alumni

**1** 275+

Visiting professors, students, and industry members

**National Academy** of Engineering members

20,000

Square feet of space

**Ø** 875+

Research projects sponsored by government and industry

2800+

Conference and journal papers

171

Masters degrees awarded

**0°** 278

Invention disclosures filed

CPES alumni in academia

35

Countries with technical exchange

**IEEE Fellows**

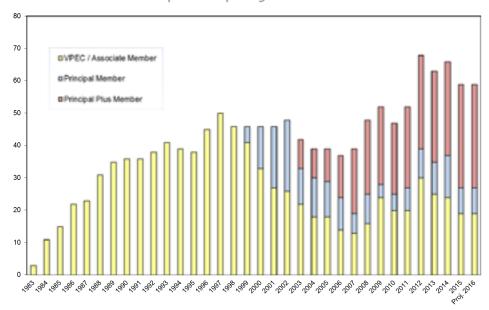

## CPES Membership Company Growth

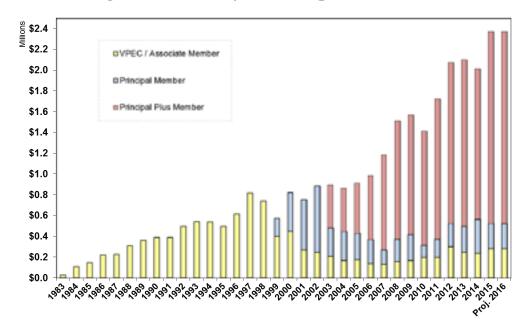

## Industry Membership Funding Growth

## **OVERVIEW**

## CPES Industry Consortium

he CPES industrial consortium is designed to cultivate connectivity among researchers in academia and industry, as well as create synergy within the network of industry members. The CPES industrial consortium offers the best mechanism to stay abreast of technological developments in power electronics.

## The CPES connection provides the competitive edge to industry members via:

Access to state-of-the-art facilities, faculty expertise, top-notch students

\$4M+

Leveraged research funding of more than \$4.5 million per year

Industry influence via Industry Advisory Board

Intellectual properties with early access for Principal Plus and Principal members via CPES IPPF (Intellectual Property Protection Fund)

Technology transfer made possible via special access to the Center's multidisciplinary team of researchers, and resulting publications, presentations and intellectual properties

Continuing education opportunities via professional short courses offered at a significant discount

Option to send engineers to work with CPES researchers on campus via the Industry Residence Program

The CPES industrial consortium offers the ideal forum for networking with leading-edge companies and top-notch researchers and provides the best mechanism to stay abreast of technological developments in power electronics.

### **MEMBERSHIP STRUCTURE**

#### **Principal Plus Members**

Annual contribution - \$50,000

Principal Plus Members gain tangible benefits via research collaboration with CPES as a member of one of the mini-consortia on focused research—PMC (Power Management Consortium), HDI (High Density Integration), or REN (Renewable Energy and Nanogrids). Companies interested in more than one focused research areas may join another mini-consortium for an additional annual contribution of \$50,000 each. In addition to all the benefits offered to Principal and Associate Members, Principal Plus Members have easy access to cutting-edge IPs via CPES IPPF (Intellectual Property Protection Fund).

#### **Principal Members**

Annual contribution - \$30,000

Principal Members are well positioned to influence and guide CPES as Industry Advisory Board (IAB) members. Principal Members also have cutting-edge IP advantage via automatic IPPF (Intellectual Property Protection Fund), in addition to all the benefits offered to Associate Members.

#### **Associate Members**

Annual contribution - \$15,000

Associate Members gain the competitive edge, not only through easy access to CPES research results, researchers, and state-of-the-art facilities, but also opportunities for technical exchanges via the Industry Residence Program and continuing education via CPES short course to stay abreast of new technologies. Companies participating in the Industry Residence Program must be actively engaged in collaborative research with the Center in technical areas that are of mutual interest, to be determined jointly with CPES faculty host.

**Affiliate Members** make in-kind hardware/software donations to CPES equivalent to \$10,000 per year. Their contributions must be relevant to CPES research. Membership participation at this level requires Center Director approval.

# **CPES**

## **Industry members**

February 2015–February 2016

## **Principal Plus Members**

3M Company

ABB, Inc.

Alstom Transport

Altera - Enpirion Power

Chicony Power Technology Co., Ltd.

Crane Aerospace & Electronics

CSR Zhuzhou Institute Co., Ltd.

Delta Electronics, Inc.

Dowa Metaltech Co., Ltd.

Fltek

**Emerson Network Power**

GE Global Research

GE Power Conversion, Inc.

**General Motors**

Groupe SAFRAN

Huawei Technologies Co., Ltd.

Intel

International Rectifier/Infineon

Inventronics, Inc.

Keysight Technologies

Linear Technology

Lockheed Martin Corporation

Murata Manufacturing Co., Ltd.

Nissan Motor Co., Ltd.

**NXP Semiconductors**

ON Semiconductor

Panasonic Corporation

Richtek Technology Corporation

**Rockwell Automation**

Siemens Corporate Research

Sonos, Inc.

Sumitomo Electric Industries, Ltd.

Texas Instruments

United Technologies Research Center

### **Principal Members**

AcBel Polytech, Inc.

China Nat'l Electric

Apparatus Res. Inst.

Fairchild Semiconductor Corp.

Halliburton

LG Electronics China R&D Center

Macroblock, Inc.

MKS Instruments, Inc.

Toshiba Corporation

**ZTE Corporation**

### **Affiliate Members**

ANSYS, Inc.

CISSOID

DfR Solutions

**Electronic Concepts**

Mentor Graphics Corporation

Navitas Semiconductor

NEC TOKIN Corporation

Plexim GmbH

Powersim, Inc.

Rohde & Schwarz

Simplis Technologies, Inc.

Synopsys, Inc.

Taiyo Yuden Co., Ltd.

Tektronix, Inc.

Transphorm, Inc.

Vesta System

VPT, Inc.

### **Associate Members**

**Analog Devices**

Calsonic Kansei Corporation

Crown International

Cummins. Inc.

Dyson Technology Ltd.

Eaton Corporation, Innovation Center

Efficient Power Conversion

Ford Motor Company

Fuji Electric Co., Ltd.

Johnson Controls, Inc.

Lite-On Technology Corporation

LS Industrial Systems Co., Ltd.

Maxim Integrated Products

Microsoft Corporation

Mitsubishi Electric Corporation

NetPower Technologies, Inc.

Schaffner EMV AG

Shindengen Electric Mfg. Co., Ltd.

Silergy Technology

**Toyota Motor Corporation**

Toyota Motor Engineering

& Manufacturing North America, Inc.

United Silicon Carbide, Inc.

Universal Lighting Technologies, Inc.

## **Current Mini-consortium members**

As of February 1, 2016

# Renewable Energy & Nanogrids (REN)

ABB, Inc.

Delta Electronics, Inc.

GE Power Conversion, Inc.

Huawei Technologies

Keysight Technologies

**Rockwell Automation**

Siemens Corporate Research

# High Density Integration (HDI)

ABB, Inc.

**ALSTOM Transport**

Crane Aerospace & Electronics

Delta Electronics, Inc.

Dowa Metaltech Co., Ltd.

GF Global Research

**General Motors**

Groupe SAFRAN

Huawei Technologies

Lockheed Martin Corporation

Nissan Motor Co., Ltd.

Sumitomo Electric Industries, Ltd.

Texas Instruments

United Technologies Research Center

## Power Management Consortium (PMC)

3M Company

Altera - Enpirion Power

Chicony Power Technology Co., Ltd.

CSR Zhuzhou Institute Co., Ltd.

Delta Electronics, Inc.

**Emerson Network Power**

Eltek

Huawei Technologies

Intel

International Rectifier/Infineon

Inventronics, Inc.

Linear Technology

Murata Manufacturing Co., Ltd.

**ON Semiconductor**

Panasonic Corporation

Richtek Technology

Sonos, Inc.

Texas Instruments

\$2.4 Million 2016

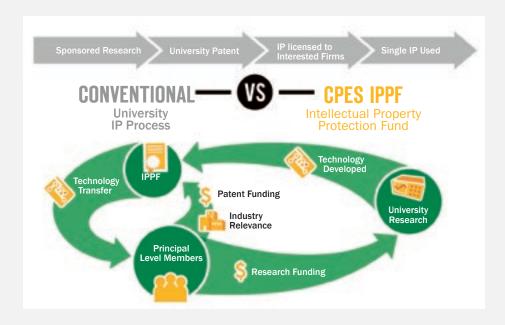

## **Intellectual Property Protection Fund**

**IPPF** is a unique IP access mechanism that provides extraordinary IP advantage to all Principal-level members. IPPF is available automatically, at no additional cost, to Principal Plus and Principal members. IPPF members meet quarterly with inventors to discuss invention disclosures and jointly decide which technologies to protect, with patenting costs covered by IPPF.

Once a technology is protected, IPPF members are granted a royalty-free, non-exclusive, non-transferable license to use the technology. IPPF is applicable only to technologies developed by CPES-VT researchers under the CPES industry consortium.

## CPES Mini-Consortium Program

he CPES mini-consortium program provides a unique forum for creating synergy among industries and defining new research directions to meet future industry needs. The formation of the mini-consortium allows CPES to pool resources and focus on developing pre-competitive technologies to address common challenges, and sharing the research results among mini-consortium members.

Mini-consortium members are enrolled in CPES as Principal Plus Members, with annual contribution

of \$50,000. They gain tangible benefits via research collaboration with CPES as a member of one of the mini-consortia on focused research:

- PMC (Power Management Consortium)

- HDI (High Density Integration)

- REN (Renewable Energy and Nanogrids)

Companies interested in more than one focused research area may join another mini-consortium for an additional annual contribution of \$50,000 each.

#### Power Management Consortium (PMC)

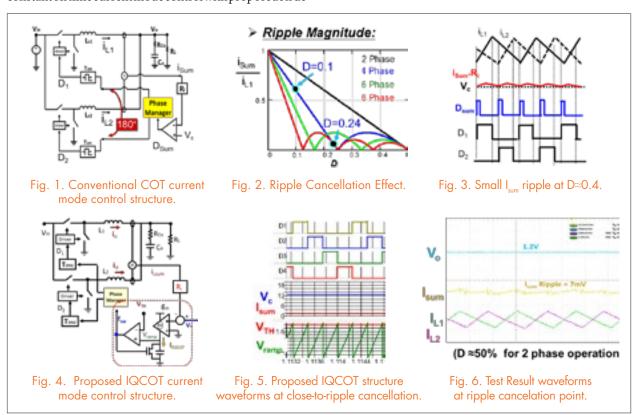

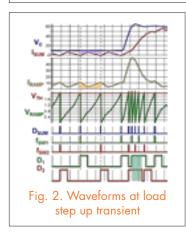

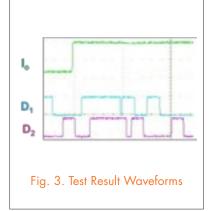

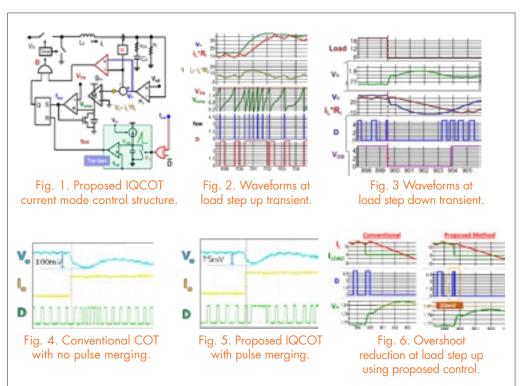

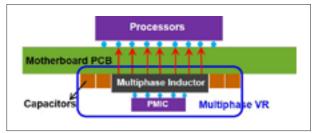

In 1997, at the request of Intel, CPES established a VRM mini-consortium to address the issue of power management for future generations of microprocessors, targeting sub-1 volt and 100-200 amps current. As a result of this focused research, the CPES team has developed a multi-phased voltage regulator module (VRM). Instead of paralleling power semiconductor devices to meet the current demand and efficiency requirements, the research team proposed to parallel a number of mini-converters. By paralleling the mini-converters and phase-shifting the clock signal, the team was able to both cancel the significant part of the output current ripple and increase the ripple frequency by N time, where N is the number of channels paralleled. This resulted in significant demonstrated improvement—specifically:

- 4 times improvement in transient response

- 10 times reduction in output filter inductors

- 6 times reduction in output capacitors

- 6 times improvement in power density, and 3 times improvement in profile

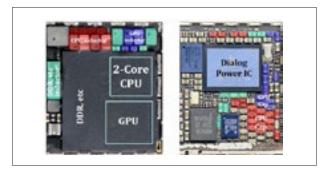

The new generation of Intel's microprocessor is operating at a much lower voltage and higher current, with a fast dynamic response in order to implement the sleep/ power mode of operation. This mode of operation is necessary to conserve energy, and to extend the operation time for battery-operated equipment. The challenge for the voltage regulator module in this case is to provide a precisely regulated output with fast ,dynamic response in order to transfer energy as fast as possible to the microprocessor. Today, every Intel processor is powered by such multiphased VRMs developed by CPES.

Power Management Consortium (PMC) is an outgrowth of the early VRM mini-consortium initiated in 1997. The goal is to extend its research scope with a focus on developing precompetitive technologies in the areas of power management for distributed power system architectures, EMI/EMC, power quality, ac/dc converters, dc/dc converters, POL converters in applications including microprocessors, tablets, notebooks, desktops, servers, data centers, networking products, telecom equipment, solid state lighting, battery chargers and other industrial and consumer electronic applications.

The PMC mini-consortium has accumulated a wealth of knowledge and made significant contributions to the power management industry. Since its inception, the program has been supported by more than 30 major semiconductor and

power supplies companies. PMC currently has 17 members. In the past year three new members joined the PMC, Inventronics, Intel, and ON Semiconductor.

The PMC places a significant emphasis on developing high-efficiency, high-power density switch-mode power supplies based on recent developments in wide-bandgap power devices such as gallium-nitride (GaN) devices and silicon carbide (SiC) devices. This emphasis will be highly leveraged with the recent DOE award of "PowerAmerica." CPES is a partner in this multi-industry multi-university collaboration program for a period of five years. The CPES role is to work with the wide-bandgap (WBG) manufacturing industry to explore potential applications and impacts of GaN and SiC devices to power conversion technologies.

The proposed GaN-based research will use several test beds to demonstrate the benefit of GaN-based power converters:

- (a) High frequency adapter with 26W/in<sup>3</sup> power density and above 93% efficiency.

- (b) High frequency 1-3kW off-Line distributed power systems with 200-300W/in<sup>3</sup> power density and above 96% efficiency.

- (c) High frequency 6.6kW bidirectional on-board charger (OBC) for plug-in electric vehicles (PEVs) with 95% efficiency and 30-50% volume reduction.

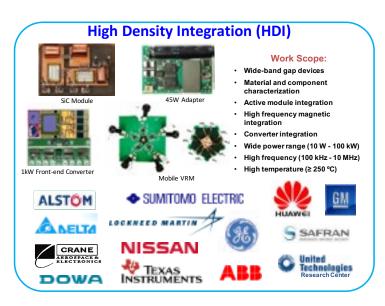

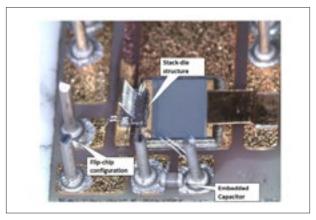

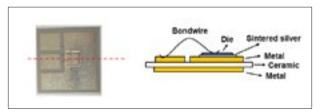

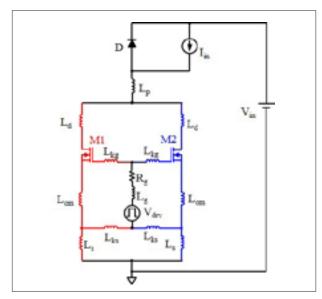

#### Mini-Consortium on High Density Integration (HDI)

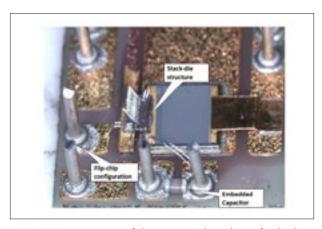

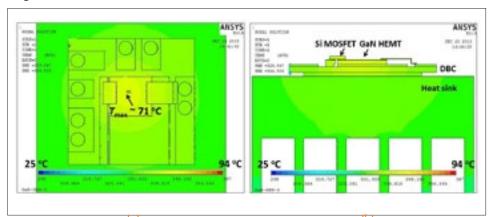

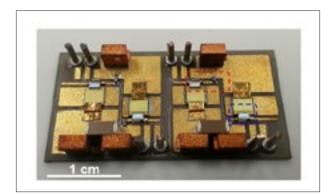

**HDI was created in 2011** as a mechanism for CPES and industry members to address emerging or long-term challenges in power-electronic integration.

Over the past two decades, CPES has secured research funding from major industries, such as GE, Rolls-Royce, Boeing, Alstom, ABB, Toyota, Nissan, Raytheon, Groupe Safran and MKS, as well as from government agencies including the NSF, DOE, DARPA, ONR, U.S. Army, and the U.S. Air Force, for research pursuing high-density system design. CPES has developed unique high-temperature packaging technology critical to the future power-electronic industry.

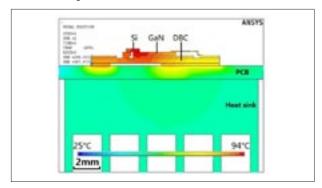

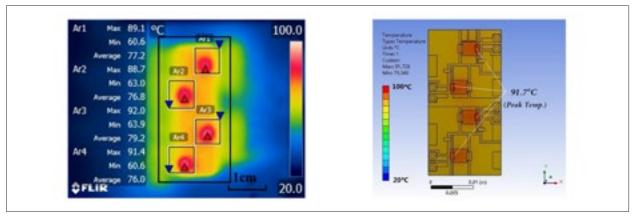

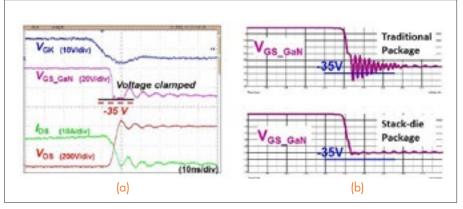

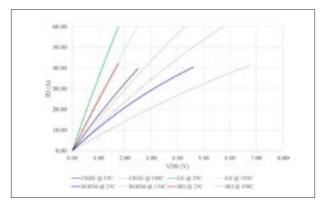

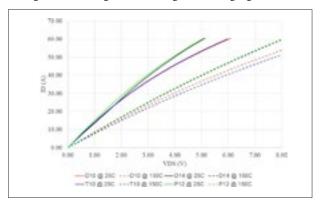

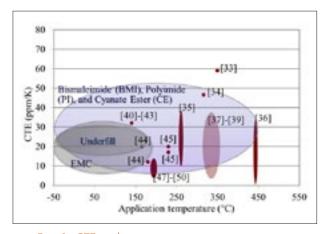

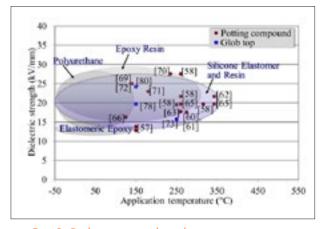

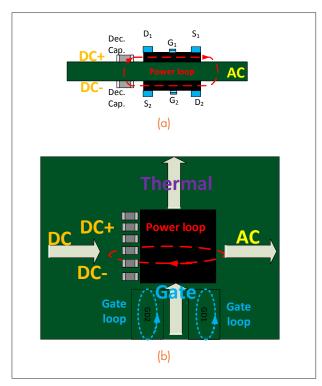

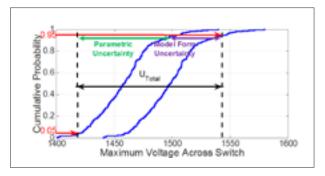

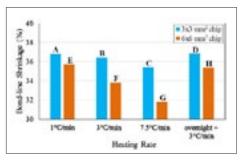

The commercialization of wide-bandgap semiconductors as Silicon Carbide (SiC) and Gallium Nitride (GaN) has shifted switching frequency beyond tens of megahertz, power rating beyond megawatts, and junction temperature beyond 250°C. The switches' ancillaries, characterization metrology, modeling method, packaging process, and manufacturing paradigm need to be transformed.

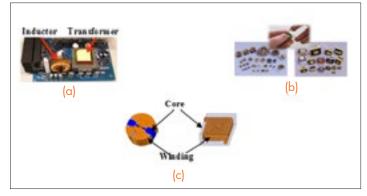

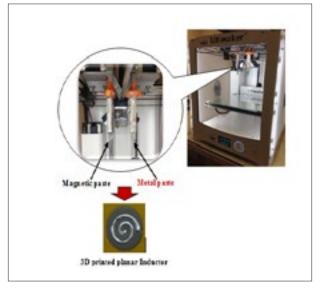

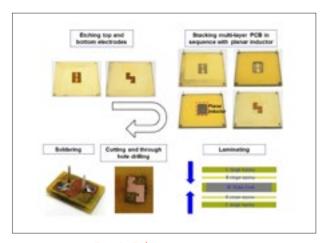

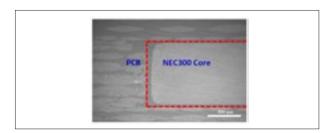

In the past, HDI has developed die-attach materials that can be processed at low temperatures, yet are reliable at the temperature of the wide-bandgap junction. Processes have been developed to encapsulate ultra-thin planar packages with polymer having high glass transition temperature and dielectric strength. Techniques to decouple the noise loops have been identified to enable high dv/dt commutation. Magnetic powder with low core loss density has been synthesized from magnetic metals for 1-5 MHz operation. Inductors have been integrated into the converter package as a substrate to achieve power density approaching 1kW/in³. Design methodologies for high-temperature capacitors, power buses, protection, sensing, digital control, etc., have also been documented.

HDI has been experimenting with new breeds of gate drivers, sensors, active and passive filters, magnetic materials and components, encapsulants, substrates, and additive manufacturing. A wide range of products, from power adapters to power-electronic building blocks, are expected to see significant improvement in power density, efficiency, and signal integrity, thanks to the adoption of the technological advances.

HDI tasks are scoped to advance Wide-Bandgap Systems, Magnetic Components, and Module Integration.

This current scope of work includes the following topics:

#### Wide-Bandgap Systems

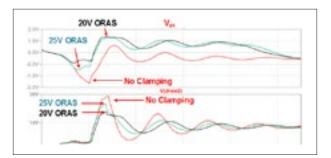

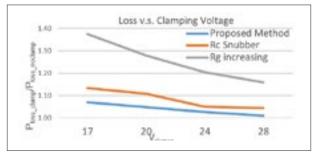

- · Active dv/dt Control of 600 V GaN Switches

- · Characterization of Multi-kV SiC MOSFETs

- High-Density 65 W Laptop Adaptor

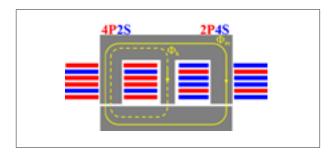

- Integrated Multi-Phase Inductor for Voltage Regulator for Small Portables

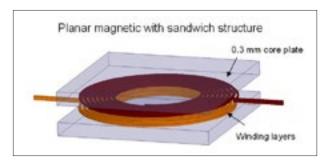

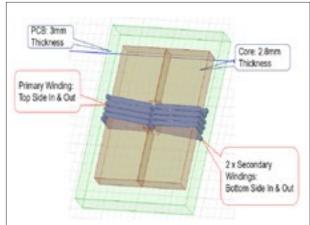

- PCB-Integrated Magnetics for High-Efficiency, High-Density Front-End Power Supply

#### Components

- Characterization and modeling of wide-bandgap semiconductor devices (SiC and GaN)

- · Low profile magnetic substrate

- Magnetic structures with high energy density

#### **Magnetic Components**

- · Additive Manufacturing of Magnetic Components

- Integrated Design of Power Transfer and Fringing Attenuation for Weakly Coupled Coils

- Integrated Multi-Phase Inductor for Voltage Regulator for Small Portables

- PCB-Integrated Magnetics for High-Efficiency, High-Density Front-End Power Supply

- · Characterization of High-Power Inductors

#### Module Integration

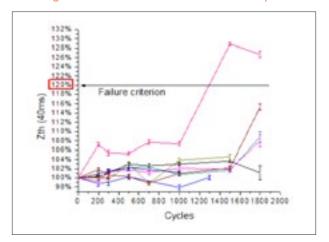

- Reliability Measurement of Metal-Ceramic Substrates with Sintered Silver Joint

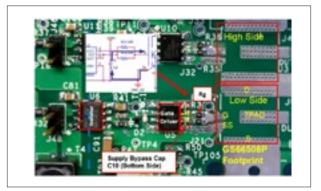

- Current Sensor Integrated with SiC MOSFET Module

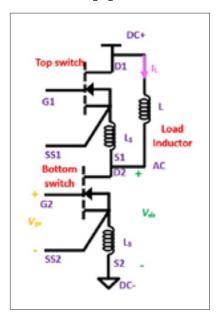

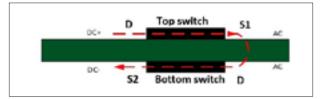

- High-Efficiency, Diode-Less 1.2 kV SiC MOSFET Half-Bridge Module

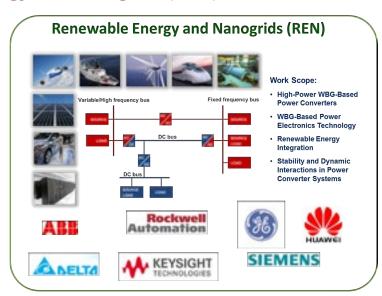

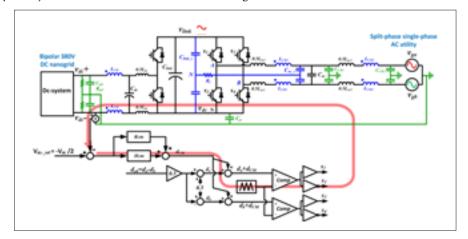

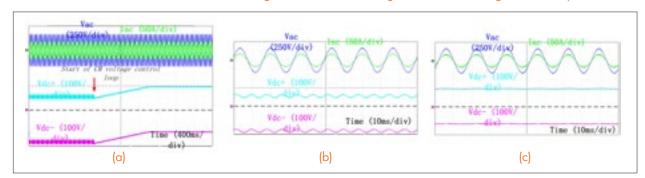

#### Mini-Consortium on Renewable Energy and Nanogrids (REN)

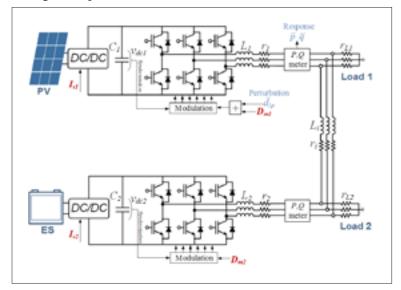

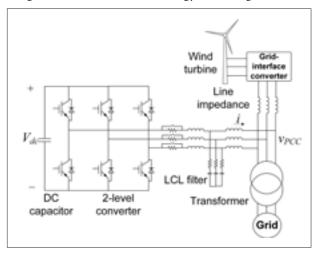

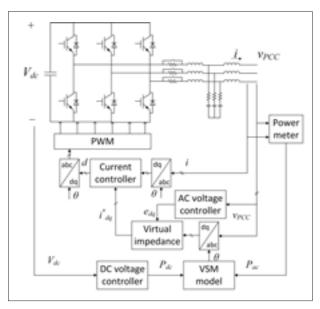

This CPES mini-consortium program provides a unique forum for creating synergy among industries and defining new research directions to meet future industry needs. The REN mini-consortium allows CPES to pool resources and focus on developing pre-competitive technologies to address common challenges, and sharing the research results among mini-consortium members. The main objective of the REN mini-consortium is to expand CPES' expertise in autonomous electric power systems (already established for transportation and IT), into the area of renewable energy and storage systems integration in the electric grid through power electronic converters, while providing competitive research and education in that area.

The current research directions of the REN mini-consortium comprise three different topics listed below with corresponding sub-topics. Additionally a REN system testbed structure is planned to be designed and built in the near future for experimental validation purposes.

The current scope of work includes the following topics:

#### High-Power WBG-Based Power Converters

- Evaluation and design of Si based and SiC impact on modular multilevel converters for MV drives

- High frequency control of modular multilevel converters in ac-dc and dc-dc mode

- Design of SiC based modular multilevel converters with 1.7Kv, 3.3 kV 10kV devices (package, gat-drive, PEBB, converter, system)

#### WBG-Based Power Electronics Technology

- Characterization of MV SiC devices

- · Design and evaluation of SiC-based SST

- Design of high-efficiency SiC-based ECC-G2, single-phase to LVDC

- Static and dynamic nonlinear droop control for LVDC distribution systems

#### Renewable Energy integration

- Design of Si-based multilevel ECC for grid-tied applications (ac-dc + dc-dc)

- Impact of PV inverters at distribution and transmission level

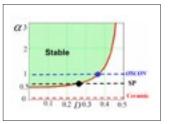

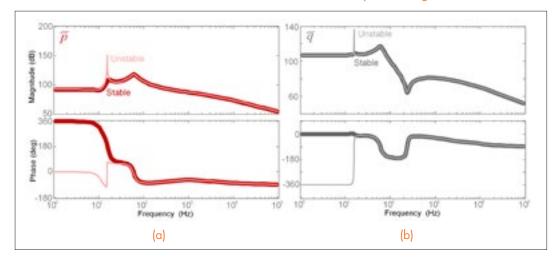

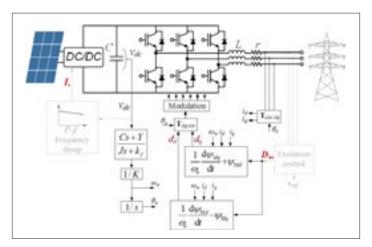

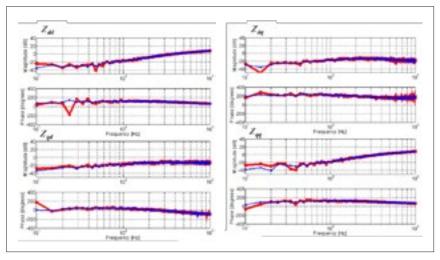

#### Stability and Dynamic Interactions in Power Converter Systems

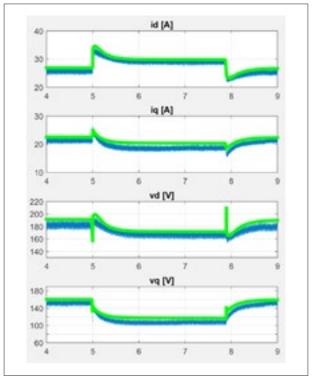

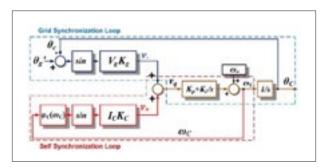

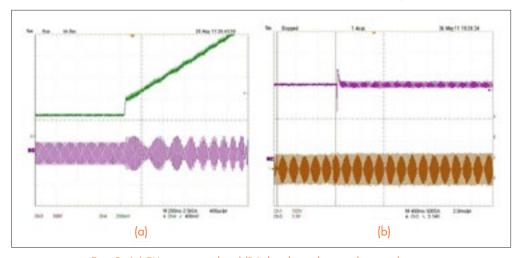

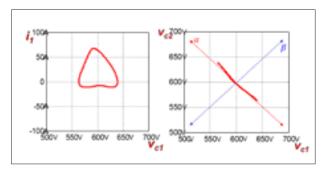

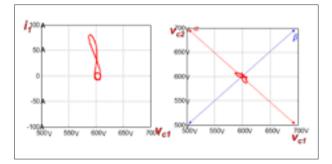

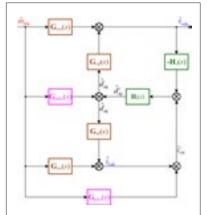

- VSM modeling and converter control design for grid-tied inverters

- VSM modeling and converter control for STATCOM

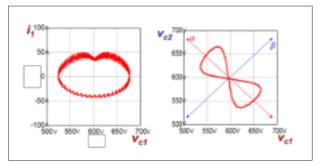

- Stability assessment and investigation of AC and DC systems

- · SiC-based IMU design

- Evaluation of dynamic interactions between multiple STATCOM units

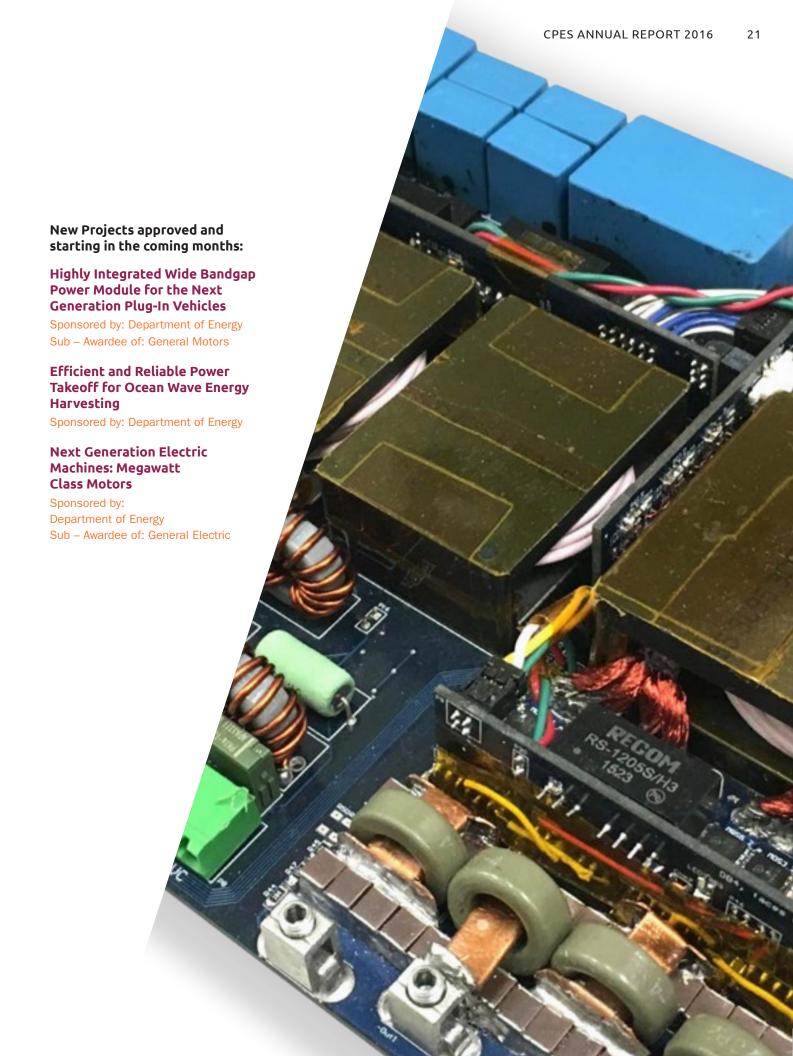

# **RESEARCH**

**n its effort to develop power processing systems** to take electricity to the next step, CPES has cultivated research expertise encompassing five technology areas: (1) power conversion technologies and architectures; (2) power electronics components; (3) modeling and control; (4) EMI and power quality; and (5) high density integration.

These technology areas target applications that include: (1) Power management for information and communications technology; (2) Point-of-load conversion for power supplies; (3) Vehicular power converter systems; and (4) High-power conver-

In 2016, CPES sponsored research totaled approximately \$2.1 million. The following abstracts provide a quick insight to the current research efforts.

## **Application Areas**

Power Management for Computers, Telecommunications & Others

**Vehicle Power** Converter Systems

Point-of-Load Conversion

High-Power **Conversion Systems**

## **Technology Areas**

**Power Conversion Topologies & Architectures**

**Power Electronics** Components

Modeling and Control

**EMI and Power** Quality

**High Density** Integration

## Sponsored Research

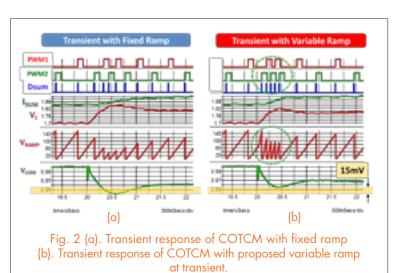

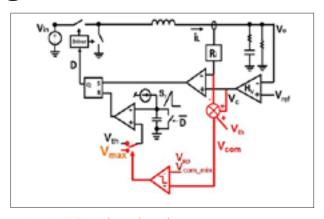

#### Multi-Phase Auto-Tuning Self Compensating Power Supply Control Systems

Sponsored by: Energy Research Corporation (September 1, 2012 – August 31, 2015)

The multi-phase voltage regulator (VR) has been widely used to power microprocessors. For multi-phase VR, a constant output impedance design is usually used to reduce the output capacitor bank. Conventionally, a fixed analog compensation network is chosen to compensate the worst-case component (such as inductor and output capacitor) variations on the plant, which will limit the converter bandwidth. Furthermore, since a microprocessor runs into sleep mode very frequently, several green-mode functions have been used to improve the light load efficiency such as phase shedding, discontinuous mode operation, and frequency changes. However, the plant characteristic will also change with these techniques under sleep mode, and will influence the stability and transient response during mode transitions. Therefore, it is very challenging and attractive to investigate multi-phase self-tuning power supply control systems which can compensate the component variation and mode transition without suffering from the worst-case design compromises. In this project, a self-tuning power supply control system is developed to self-identify the plant characteristic change from component variation and operating mode transitions, and then adaptively adjust the compensation parameters to maintain stability and system performance. Therefore, external compensation circuitry and the output capacitor bank can be reduced to reduce total cost. We have already proposed several control methods with auto-tuning function to improve transient performance of voltage regulator, including self-compensated DCR current sensing, adaptive PLL loop for variable frequency control, and high bandwidth DDR VR with adaptive zero positioning. The proposed control concepts have been validated with Intel CPU emulator (Gen4 VTT tool).

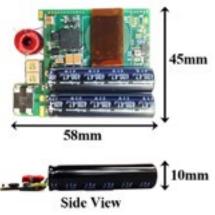

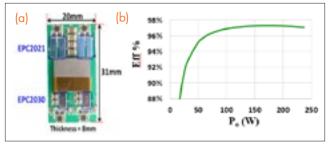

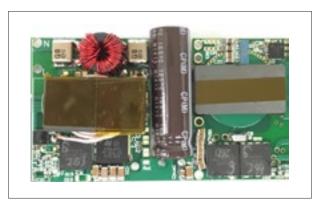

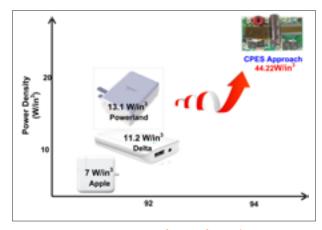

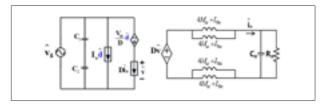

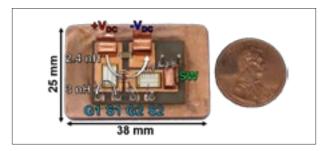

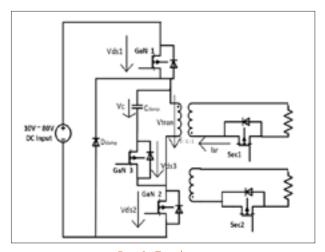

#### High Density High Efficiency Adapter

Sponsored by: Department of Energy thru PowerAmerica Institute (February 1, 2015 – March 31, 2016)

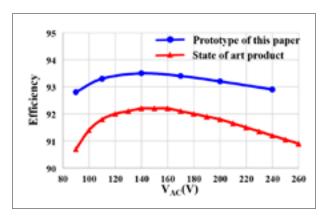

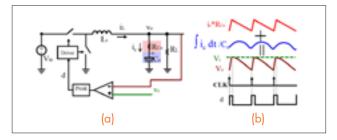

The adapter is highly driven by efficiency and power density for all forms of portable electronics. The adapter below 65W power level is chosen for the demonstration for its potential economic impact, with wide range applications covering a large section of mobile devices, including tablet, notebook, and many other portable electronics equipment. Today, most of the adapters are only operating at relative low frequency (<100 kHz) with the state-of-the-art efficiency up to 91.5%. However, the low frequency operation limits the adapter power density at 6-11W/in³.

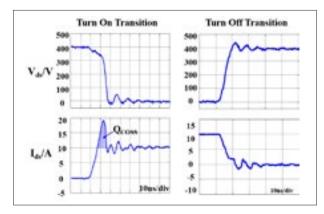

High efficiency and high frequency are the catalysts for size reduction. The emerging GaN device, with much improved figures of merit, opens the door for an operating frequency well into the MHz range. To realize the full benefits of GaN, a number of issues have to be addressed carefully, including softswitching topology selection, high-frequency magnetics, control, packaging, gate drives and thermal management. During Year 1 of this program, we have successfully demonstrated that the GaN-based adapter design is capable of operating at 1-2 MHz frequencies with an improved efficiency up to 93.5%. Subsequently, a power density of 27W/in³, which is a three-fold improvement over the state-of-the-art product, was successfully demonstrated at 45W and 65W levels. In this MHz adapter design, we have implemented a number of unique features:

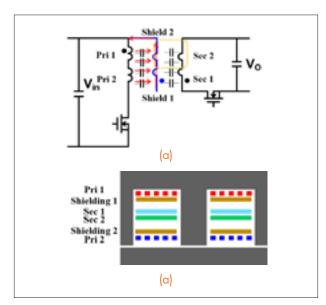

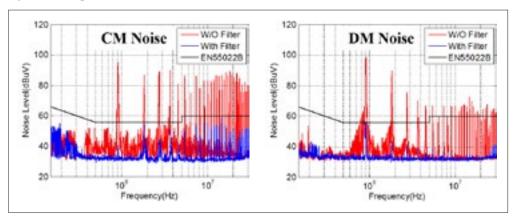

A flyback with active clamp circuit is applied to recycle the transformer leakage energy and, thus, realize softswitching for the primary switches, which brings over 90% reduction of switching losses. This enables the circuit to operate at 1-2 MHz while achieving high efficiency. The noise associated

- with high di/dt and dv/dt are also significantly reduced.

- 6-layer PCB board based high-frequency transformer design to enable high power density.

- Common-mode noise is significantly reduced using the patented transformer shielding technique. The shielding provides more than 20 dB common-mode EMI reduction across the full frequency range (150 kHz-30MHz), thus reducing the EMI filter to a single-stage filter.

- With the exception of the EMI filter and bulk energy storage capacitor, everything can be fully automated in the manufacturing process.

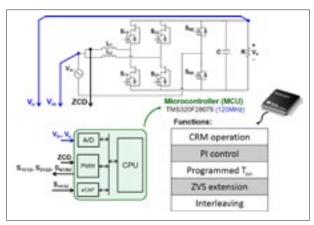

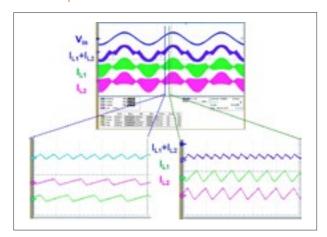

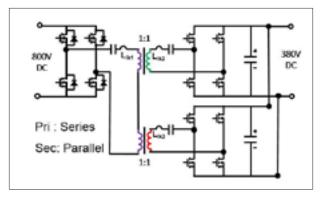

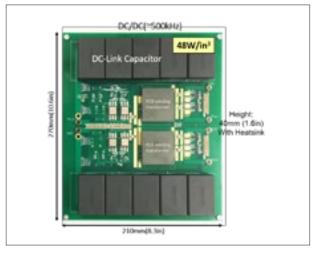

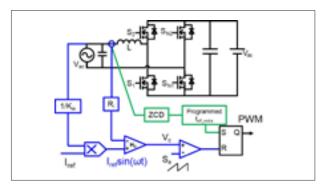

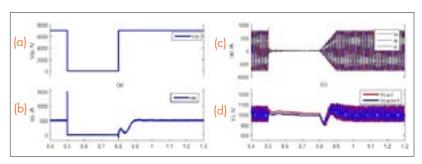

#### High Frequency GaN Converters for Distributed Power Systems

Sponsored by: Department of Energy thru PowerAmerica Institute (February 1, 2015 – March 31, 2016

The ever increasing demand for highefficiency and high-density switch-mode AC/DC power supplies includes but is not limited to computers, telecommunication, data centers, electrical vehicle battery chargers, PV inverters, numerous industrials, and aerospace applications. Collectively, these products consume more than 10% of the total electric power. In the proposed effort, we will use high voltage GaN devices for the

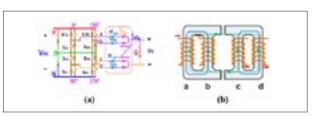

1MHz 65W active clamp flyback converter for AC-DC adapter application

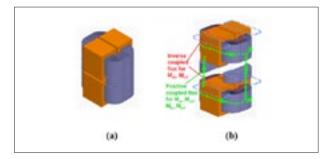

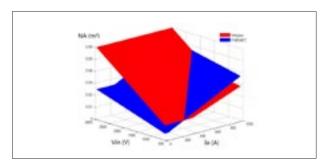

server power supplies to push its frequency 20 folds, from today's 50-100 kHz to 1-5 MHz. As a result, the power density of frontend converter can be dramatically increased from today's 30-50 W/in<sup>3</sup> to 100-150 W/in<sup>3</sup>. Furthermore, it is envisioned that the frontend power processing to be fully modularized. In this manner, a customized power system can be synthesized by using simple modular building blocks such as multi-phase power factor correction (PFCs), and high voltage DC/DC converters and DC/DC transformers (DCXs) for input/output isolation. These front-end converters are followed with already standardized multi-phase distributed Pointof-Load (POL) converters. In the Year 1 of this program, we have successfully developed a 1kW, 1-3MHz critical mode PFC with 99% peak efficiency and more than 200W/in<sup>3</sup> power density. A PCB integrated coupled-inductor has also been proposed for this PFC circuit to further improve its power density and achieve balance control on the circuit parameters to greatly reduce common mode EMI noise. For the DC/DC stage, we have developed a 1kW, 1MHz 400V/12V DCX with PCB winding based matrix transformer. It achieves 97% peak efficiency and 700W/in<sup>3</sup> power density.

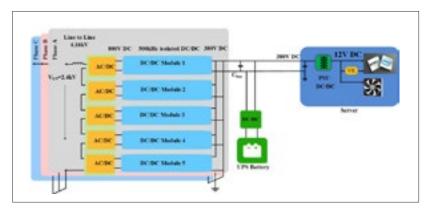

This high density DCX will be further improved to meet the specifications. proposed by iNEMI for future DC datacenter with onboard 380V/12V module. (Recently, the International Electronics Manufacturing Initiative (iNEMI) at the behest of IBM and other server manufacturers undertook a project to develop an industry standard for DC-DC converters. This converter is used to step down 380V directly to 12V and is placed directly on the motherboard). Compare to today's AC datacenter, the DC datacenter with onboard 380V/12V module will bring at least 7% improvement in system efficiency.

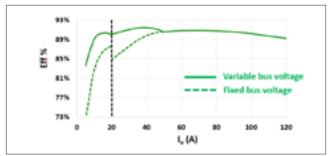

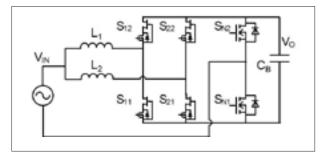

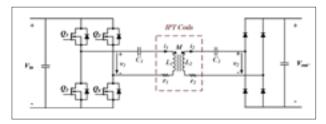

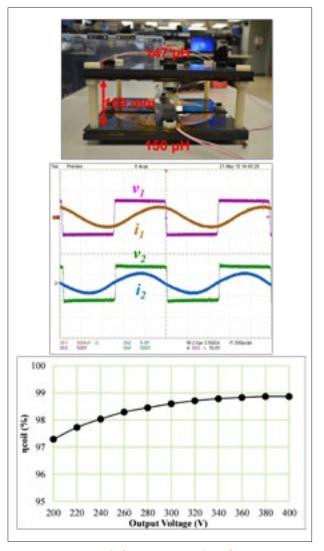

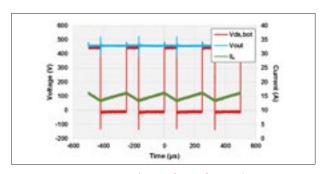

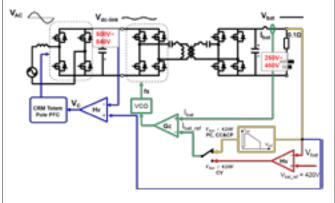

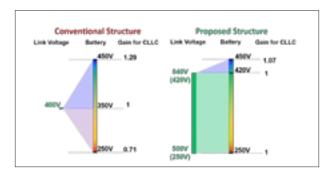

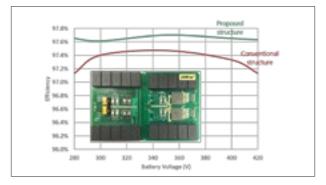

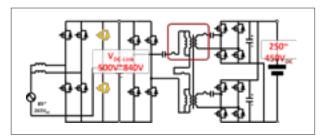

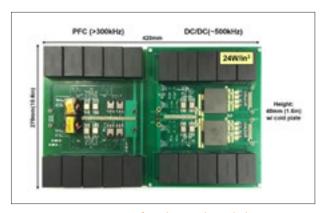

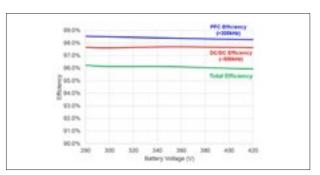

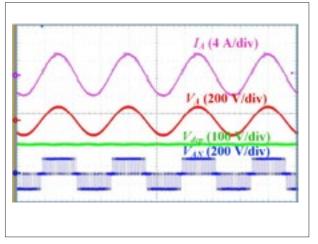

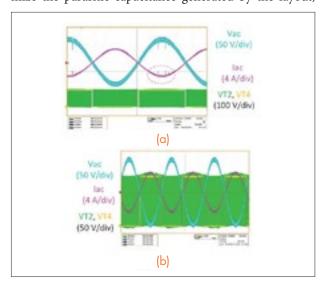

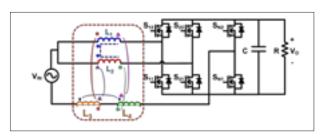

# High Efficiency High Density GaN Based 6.6kW Bi-Directional On-board Charger for Plug-in Electric Vehicles (PEVs)

Sponsored by: Department of Energy Sub-Awardee of: Delta Products Corporation

(October 1, 2014 - September 30, 2017)

This project involves the development and commercialization of a lightweight, compact and efficient bidirectional on-board charger (OBC) for plug-in electric vehicles (PEVs). PEV hereafter refers to plug-in hybrid electric vehicles (PHEV) and battery electric vehicles (BEV).

The OBC uses novel circuit architectures and control schemes enabled by Gallium Nitride (GaN) based wide- bandgap (WBG) semiconductors to obtain charger efficiency better than 95% and reduce volume and mass by approximately 30% to 50% of the existing state-of-the-art silicon (Si) based chargers by pushing converter switching frequency to the MHz range. A Si-based bidirectional OBC is typically implemented with two separate modules: a charger and an inverter. A GaN-based bidirectional OBC can integrate both functions in a single module. It will result in substantial reductions in size, weight and cost.

With Chrysler's commitment, this project aimes to demonstrate the viability and commercial potential for WBG semiconductors in PEV applications. The core charger/ inverter technology will also provide the added consumer benefits of providing emergency or convenience ac power on a vehicle, a feature that is strongly desired by consumers. In addition, it supports effective vehicle-togrid (V2G) integration. V2G enables more efficient energy management practices, such as wind and solar photovoltaic distributed generation, peak shaving, and discounted off-hour charging rates for customers. All of which will help support the mainstream commercialization of PEVs. This project brings together four world-class organizations including: the

A 6.6kW 500kHz Level 2 on board battery charger is built using a novel variable DC-link voltage structure.

Center for Power Electronics Systems (CPES); Transphorm, Inc.; Delta Products Corporation; and Chrysler LLC.

In this project, CPES will focus on developing advanced circuit architectures and control schemes for GaN based battery charger. The main tasks included high-frequency GaN device and driver evaluation; topology selection and evaluation; high-frequency magnetic components development; reference design of high frequency PFC stage, dc/dc stage and EMC filters.

#### Research of High-Efficiency High Density Power Conversion Architecture

Sponsored by: Huawei Technologies Co., Ltd. (August 19, 2015 – February 19, 2017)

This project will develop a high frequency (>MHz) 48V/1V power module with an efficiency target of 91%. A PCB winding based high frequency transformer structure will be used to help increasing power density as high as 400W/in<sup>3</sup>. A detailed analysis about the trade-off between system efficiency and power density will also be completed.

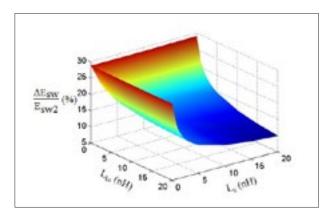

#### SiC Module EMI Control by Transient Shaping and Shielding Technique

Sponsored by: Toyota Motor Engineering Manufacturing NA, Inc. (August 15, 2014 – March 31, 2015)

The transition edges of PWM gate current and gate-source voltage will be synthesized from such basis functions as linear, exponential, and sinusoidal. The resultant gate-drive waveforms will excite silicon and silicon-carbide modules in a bidirectional boost converter over specified voltage and power ranges. Selected transition shapes will be synthesized using commercial parts for experimental verification. The project will document the tradeoffs among transition shapes, switch materials, interconnects, loss, and noise, along with recommendations for preferred practices.

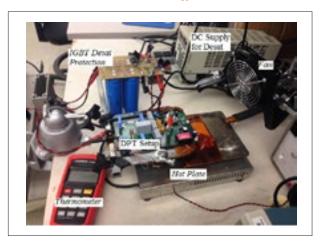

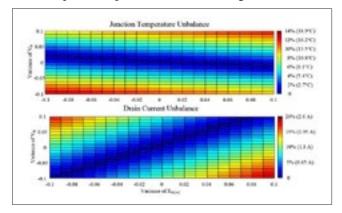

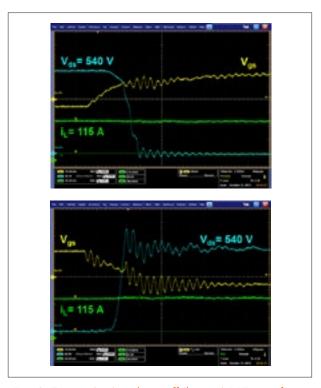

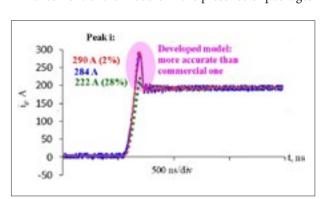

## Control of Modules of Parallel SiC Switching Cells

Sponsored by: Toyota Motor Engineering Manufacturing NA, Inc. (August 15, 2014 – March 31, 2016)

The objective of the project is to develop a gate driver/controller that would commutate a large number of paralleled SiC MOSFETs reliably, as well as balance the performance of the dies with respect to power or thermal distributions. Development of guiding principles for the design and fabrication of a power module of such paralleled MOSFETs will also be achieved.

Double-pulse tester for current balancing

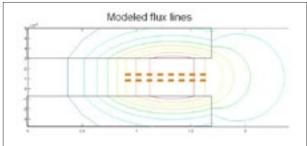

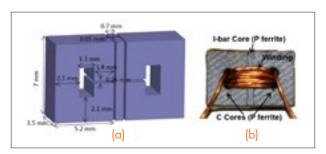

## Constant-Flux Magnetics for Power Conversion

Sponsored by:

National Science Foundation

(November 15, 2012 – April 30, 2016)

At least 30% of the volume in commercial inductors store no or negligible energy. The "constant-flux" concept improves energy density by filling the available volume with as much magnetic (core) materials as practically feasible, then dispersing the windings to shape the distribution of magnetic flux, e.g., to distribute magnetic flux uniformly. In this project, guiding principles will be developed from the structural and field standpoints to realize the constant-flux concept. Performance metrics, such as inductances, capacitances, and quality factor will be modeled, quantified, and compared with the corresponding benchmarks.

#### Tunable Energy Efficient Electronics (TE3)

Sponsored by: DARPA (December 1, 2015 – November 30, 2018)

In modern defense systems, processing of electrical power to suitable voltage level and frequency is a key factor in achieving high performance, light weight, improved reliability and high efficiency. A majority of defense applications often require power processors to operate with fluctuating source, load or environment. Passive components with addedtunability are sought to provide adaptability to different circuit conditions. They will add a major leap in size optimization, controllability and circuit design strategies. This project is going to design and make tunable power inductors, transformers, capacitors and current sensors to reduce weight of power passives and increase power handling capacity. TE3-based dc-dc power converter system will be designed for achieving high power density and efficiency with adaptability to fluctuations in source, load and environment.

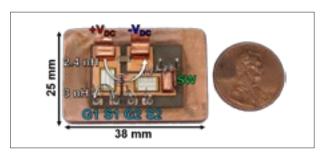

## Power Integration by Multifunctional Molding

Sponsored by: National Science Foundation (August 1, 2015 – July 31, 2017)

Power Modules are employed in electronic systems to lower part count, improve reliability, and reduce cost. The type of power module addressed herein comprises a complete dc-dc switched-mode converter in one package. Power switches, gate drivers, sensors, controllers, lead frames, and filter inductor are integrated into one building block that is encapsulated in molding compound. A 50W module with efficiency exceeding 90% would fit into a volume of 1.5 x 1.8 x 0.6 cm<sup>3</sup>.

While the filter inductor is known to be undesirably bulky, the unused space filled up by the molding compound might actually be larger than the inductor's volume. Power density would be improved significantly if the molding compound also stores energy so that, with appropriately designed winding, the module case also functions as the inductor. Such power integration by multifunctional molding has not been demonstrated so far because of two reasons. First, magnetic materials are usually kept away from a switching loop for fear that the increased in stray magnetic field would adversely affect converter's operation. Second, an encapsulant with significant relative permeability (20-30) is difficult to synthesize using low temperature and low or no pressure.

The objective of the research is to integrate the energy-storage function into the encapsulating case of the power module, thereby reducing material usage and possibly simplifying manufacturing process. Fundamental contributions are anticipated in materials and electrical engineering, education, and application. Encapsulation material that integrates mechanical/chemical (protective) and electrical (energy storage) functions are to be synthesized using low temperature and low pressure. Multi-magnetics module (MMM) with unexplored electromagnetic properties

Prototype of a 1.2 kW three-phase isolated AC/DC converter with 97% efficiency and 22W/in<sup>3</sup> power density.

and design methodology are to be devised to take advantage of such material. Operability of power-electronic converters are to be assessed the presence of magnetic media. Converter topologies are to be synthesized to leverage the field couplings inside an MMM. All fundamental advances are to culminate in a manufacturing process of multi-magnetics module with less materials and cost, possibly.

## MHz GaN Converter with Isolation Sponsored by: Texas Instruments

This project starts with the design of the converter for zero-voltage switching over the full range of input voltage and output power to establish component requirements. Magnetic design of leakage inductance and harmonic losses in the coupled inductors with different winding structures are analyzed by finite-element simulation. The design of gate drive, loss analysis, effect of layout impedance, and other issues are addressed, leading to hardware verification with efficiency exceeding 85% at 5MHz and 30W output.

### High-Density Integrated Inductor

Sponsored by: Texas Instruments

The "constant-flux" concept proposed recently is leveraged to distribute magnetic flux to improve energy density, lowering the profile of an inductor. The optimal flux distribution is identified mathematically, and verified by simulation. It is then applied to reduce

the dc resistance of a commercial inductor by a factor of two, keeping the outer dimensions and inductance the same. Thermal-limited current rating is improved by 50%, whereas saturation-limited current rating is improved by 20% thanks to the suppression of flux crowding.

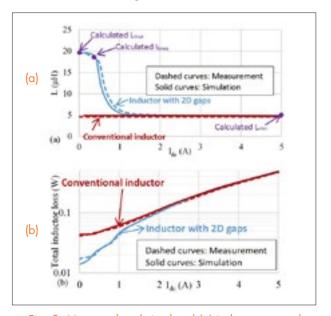

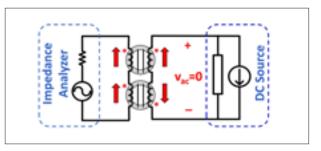

#### Point-of-Load Inductor with Two-Dimensional Gapping

Sponsored by: Texas Instruments

Point-of-load converter at light load has low efficiency owing to the "fixed losses" such as core loss and ac winding loss. Two-dimensional (2D) gapping is applied for a ferrite core to shape inductance versus load current to reduce inductor loss at light load. Since the maximum inductance of conventional stepped gap is limited by the cross-sectional area of the thin gap, a 2D gap is formed by joining two orthogonal gaps to gain flexibility. Higher inductance is achieved at light load compared with uniform-gap and stepped-gap geometries having the same volume and dc

Double pulse tester for DrGaN

resistance. AC resistance is reduced at light load thanks to a magnetic path that steers ac flux away from the winding. Two C-cores with 2D gap were fabricated and tested on a buck converter with 50% reduced total inductor loss at 10% load current.

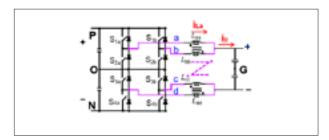

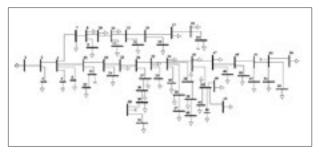

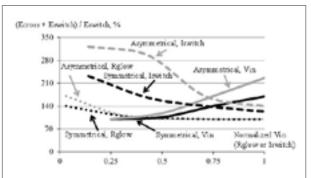

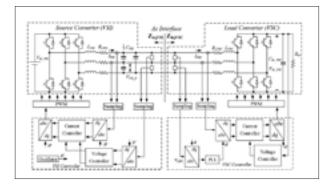

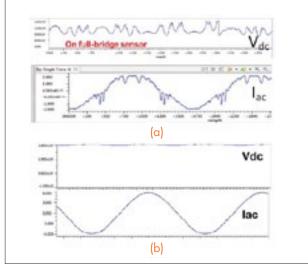

#### Optimization of ac/ac Motor Controller Power Quality and EMI Filter Topology

Sponsored by: United Technologies Aerospace Systems (January 1, 2012—December 31, 2015)

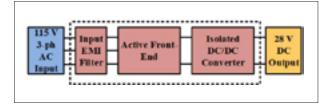

The objective of this work has been the development and optimization of modular power converters for aerospace applications. This has included the development of new power conversion topologies; the design of high-efficiency, high power density topologies based on wide-bandgap power semiconductors; the combined design of power quality and EMI filters; as well as the effect of the thermal and electrical characteristics associated with these new materials and semiconductors. Extensive modeling and optimization work has been conducted too as part of this effort. The focus of the first year was specifically aimed at the design and evaluation of three-phase ac-to-ac power conversion topologies from an EMI filter standpoint, seeking the best solution for motor drive applications.

The second phase of this work honed its efforts on the optimization of small local converters, each built on PCB cards addressing the combined power quality, EMI and thermal requirements and fed by variable frequency ac or higher voltage dc power bus and output power circuits that provide regulated 28 V dc power. The effect of the thermal and electrical characteristics associated with a number of power topologies and the trade off in their performance in terms of weight, size and perceived reliability was investigated. Addressing single-phase power conversion first, a novel three-level semi-bridgeless PFC topology was developed to achieve 99% efficiency. For three-phase power conversion, a dual channel Vienna-type three-level converter was developed and tested surpassing 99% efficiency too.

The third phase of this project, also targeting PCB-based power converters, addressed the efficient power conversion from 270 VDC to 28 VDC, for which a multi-kilowatt

resonant converter with isolation was designed and developed achieving 98% efficiency. The focus in this case was on the transformer design, high current operation (>100A), and EMI filter design to meet input and output requirements.

The fourth phase of this project, completed in 2015, consolidated the work of the previous two years and merged the ac-dc and dc-dc power conversion stages to design a three-phase 115V ac to 28V dc isolated power converter of maximum power density and maximum efficiency for a given form factor, which has required the reformulation of the design optimization procedure used to explore the potential of PCB-based power conversion systems. A significant effort was spent in the optimization procedure itself that conversely, with existent design approaches, sought to maximize the power processing capability of the converter in question while keeping as hard limits the size and volume of the unit, pursuing to a target efficiency of 98 %.

In what is a new phase just started in 2016, a similar approach will be used to develop a modular card-based dc-ac inverter system capable of feeding and driving motor loads. A key addition to the problem has been the incorporation of an onboard digital controller to the converter card system.

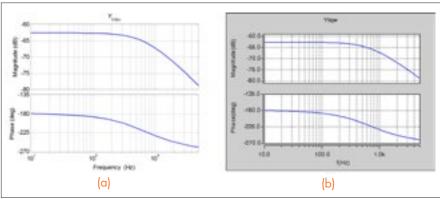

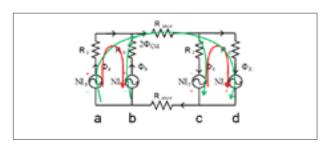

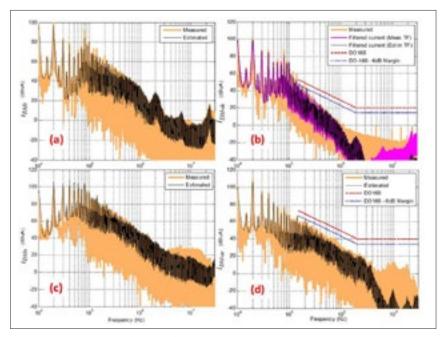

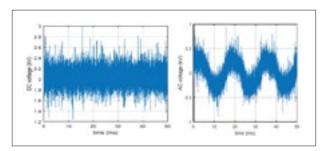

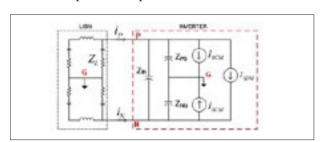

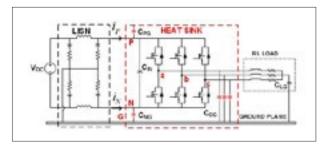

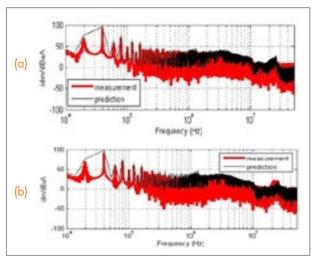

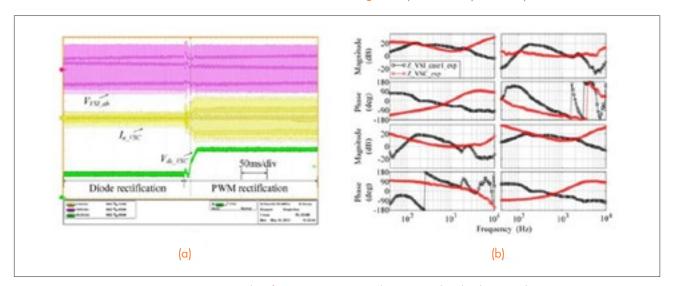

## Terminal Modeling of Noise Source in Switching Power Converters

Sponsored by: Hispano Suiza, SAFRAN (October 1, 2010—September 30, 2016)

The main objective of this research over the past years has been on the development of terminal models of noise sources in switching converters for simplified EMI analysis, models which must be scalable for different load and source conditions. Conventional methods of EMI modeling on the other hand use physics based models of semi-conductor devices and EMI coupling paths. Due to the complex nature of these models the simulations often fail to converge or lead to unusable results.

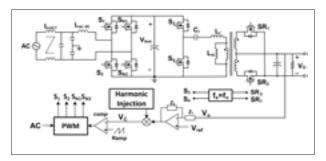

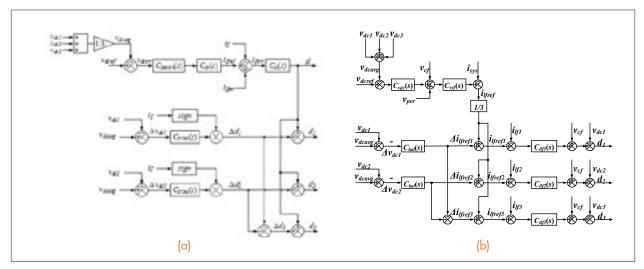

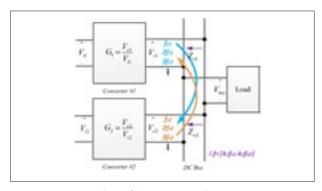

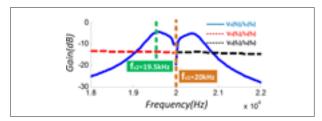

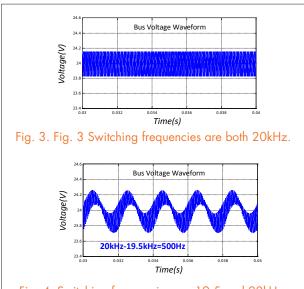

In its last two phases, this project has

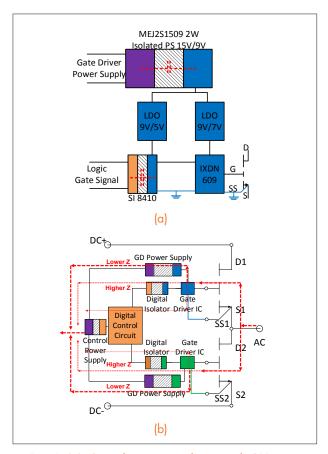

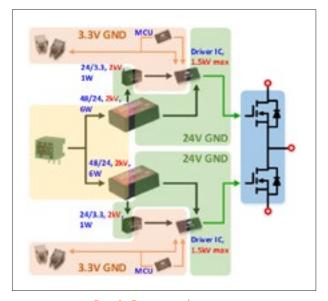

explored the use of terminal models for the development of EMI filter design procedure. Its main focus was the design of filters for parallel inverters using interleaved PWM techniques. Research efforts aimed at simplifying the simulations by using Thevenin or Norton models of these noise cells. Here "noise-cell" may refer to both device level (single device or a Phase-leg) and converter level abstraction. This method has been successfully demonstrated so far on an industrial low-voltage 10kW motor drive, for which the unterminated EMI model of its 3-phase voltage source inverter (VSI) was built showing how it could predict the EMI behavior of the motor drive under varying conditions. In 2014, the method developed was extended to enable the modeling and prediction of EMI noise generated by converters operating at higher switching frequency (50-100 kHz) enabled by the use of SiC devices. This required the complete reformulation of the measuring techniques and modeling methodology employed, rendering the approach capable of predicting common-mode (CM) up to 30 MHz; a feat which had not been achieved before. In its new phase, planned from 2015-2016, this project will make use of the EMI modeling and filter design procedures developed in the past year to support the design of integrated power supplies for gate-drive and avionics applications operating in harsh environment in terms of dv/dt transients and also high temperature. Specifically, the gate-drive power supply will be used to power an active gatedriver circuit with dv/dt and di/dt control to be developed for 600V GaN semiconductors, while the avionic power supply will additionally have to withstand high input voltage variability (10-100%). The project will also conduct a system study to determine the tradeoffs between switching frequency, dv/dt rate, inverter efficiency, EMI filter, and harness and motor size.

After a year of execution, the project has successfully demonstrated the active gate-drive control method for GaN power devices, as well

as the integration of gate-drive and general purpose power supplies with reinforced-isolation, PCB embedded transformers, and active stage switching at 1 MHz thanks to the use of GaN power semiconductors.

#### Strategies for Wide-Bandgap, Inexpensive Transistors for Controlling High Efficiency Systems (Switches)

Sponsored by: ARPA-E, ADEPT Program (Advanced Research Projects Agency Energy, Agile Delivery of Electrical Power Technology) Sub–Awardee of: HRL (March 6, 2014—March 7, 2017)

With the sponsorship of ARPA-E, CPES has partnered with HRL Laboratories to demonstrate ultra-high efficiency, low-cost power modules for future 1.2kV, 100A, vertical Gallium-Nitride (GaN) devices under development at HRL. These devices, expectedly capable of commutation speeds in the 100-200 V/ns range, will minimize switching losses to the extent were system efficiencies of >99 % are expected at the power converter level. To this end, CPES will build a 30kW, 800V dc, three-phase boost rectifier demonstrator. In its first year, CPES has developed several ultra-low parasitic inductance package concepts using ribbon topside interconnections for the GaN devices and Flex PCB for the gate-terminals, with which it has reduced this parasitic component to less than 5 nH. Similarly, the module design has targeted the minimization of the parasitic capacitances to ground as an EMI containment strategy. A first prototype of the power module using 1.2kV, 90A, SiC MOSFET devices was recently built to validate the module design. An advanced module concept utilizing ribbon bonding for the power terminals and a flex-PCB for the gate-loop of the power module attained ultra minimized parasitic components. These power modules will now be built to demonstrate in the last year of execution of the project the 30 kW boost rectifier.

#### Thermal-Electrical-Mechanical Modeling of IGBT Module Failure Modes

Sponsored by: Huazhong University of Science and Technology (August 8, 2014 – July 31, 2017)

Insulated Gate Bipolar Transistors (IGBT) are one of the major players in modern power conversion, especially for medium and high power applications. The reliability of these devices remains to be a major concern, topic which Huazhong University of Science and Technology (HUST) has been studying jointly with Techsem Semiconductor Co., and now is interested in pursuing jointly with CPES. The primary goal of this research will be to investigate the possible failure modes of commercial IGBTs, including:

1) module layout and its influence on the electric field and thermal distribution; 2) wire bond structure and its impacts on the internal current distribution; 3) Direct Bond Copper (DBC) substrate preparation and its reliability; 4) thermal interface material (TIM) selection and its influence on the module reliability; 5) encapsulation of high voltage IGBT modules.

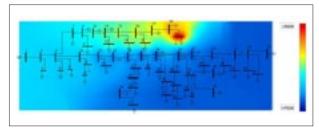

## Optimal Magnetic Component Design for Boost Converters

Sponsored by: General Motors (September 5, 2014 – March 31, 2015)

The push towards higher power, while simultaneously targeting higher power density in drive systems for traction applications, has resulted in the need to rise the dc-bus voltage of the converter system, to increase efficiency as well as to provide the needed design flexibility for the traction inverter and electrical motor. This is enabled by the use of a boost dc-dc converter to interface the battery pack and the inverter, which regulates the dc bus voltage under varying battery voltage and state of charge (SOC). The boost ratio required ranges from 2:1 to 4:1, for power levels ranging from 60–100 kW. The

Three-phase inverter system used for validating EMI models.

electrothermal stress on the boost inductor of this converter is hence significant, which has become a key barrier in the accomplishment of the system power density goals. CPES has accordingly initiated a focused effort to explore alternative dc-dc boost converter and boost inductor topologies, ultimately pursuing the formulation of new design criteria that can minimize the inductor weight. To this end, the research conducted focused on the development of new electrothermal models for the inductors, pursuing the use of closed-form analytical equations instead of the time-consuming finite-element method conventionally used. Optimization procedures developed in CADES, an optimization software suite, were successfully used for this purpose.

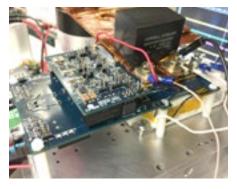

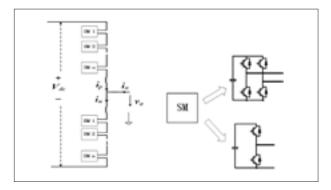

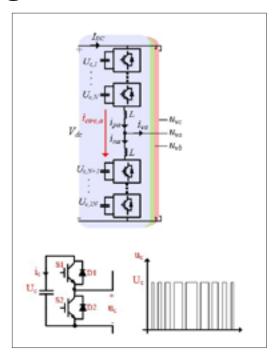

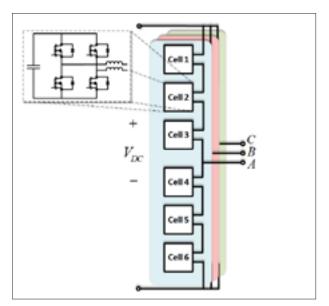

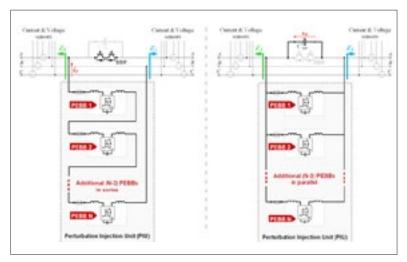

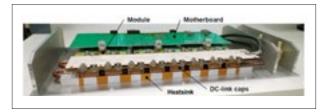

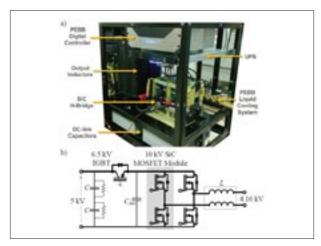

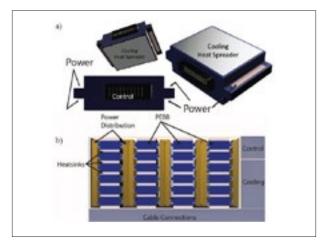

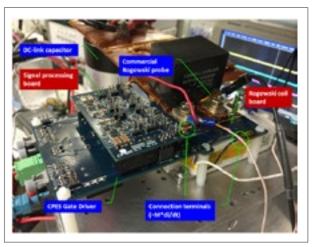

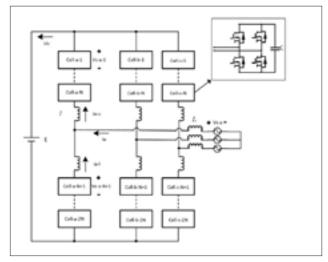

# SiC-PEBB Modules for Next Generation MVDC Integrated Power Systems—Development of the SiC-Based PEBB 1000

Sponsored by: Office of Naval Research (August 1, 2014 – July 31, 2016)

This project will develop 1kV Silicon-Carbide (SiC) based power electronics building block (PEBB) modules, named PEBB 1000. These SiC-PEBBs will truly enable, for the first time, the notion of a high power density PEBB-only integrated power system for future Navy ships, profiting doubly from the system and commercial advantages featured by the PEBB modular concept, and from the power processing advantages offered

by SiC semiconductors. As such, power density, efficiency, high control bandwidth, modularity, voltage and current scalability, reconfiguration flexibility, simplicity, and the potential for low-cost commercial offthe-shelf technology become a factual reality. For demonstration and evaluation purposes, multiple PEBB 1000 units will be developed by CPES to evaluate the performance of the PEBB in ac-dc, dc-ac and dc-dc applications. This will allow for a comprehensive assessment of the PEBBs, converters, and their systemlevel impact. The project is also evaluating alternative SiC devices, and will target the use of 1.7 kV, 300 A, SiC MOSFET power modules from CREE, as well as 1.5 kV 200 A, SiC MOSFET power modules from GE. In a parallel effort funded by ONR, GE Global Research will develop the PEBB 6000 unit using 10kV SiC MOSFET power modules from Powerex, using CREE devices, which will enable the comprehensive evaluation of the SiC-PEBB integrated power systems for future Navy ships. The first PEBB 1000 prototype will be fully tested in March 2016, and converter level tests are expected to follow soon thereafter.

#### **High Power Solid State Circuits**

Sponsored by: Office of Naval Research Sub-Awardee of: ABB (May 1, 2015 – October 31, 2016)

The main goal of the team at CPES, Virginia Tech, has been to develop a power converter concept with current limiting capability that can effectively withhold its stored energy during fault conditions. The converter has a modular structure being capable of scaling up its operation in both voltage and current by the series and parallel connection of its modules. At the system level, the main goal will be to demonstrate the current-limiting capability of the converter both under fault and overload conditions, demonstrating as well potential to expand the safe operating area of the system by sharing the limited load current among multiple power converters.

Lastly, coordination aspects among power converters with current-limiting function and solid state circuit breakers will be investigated in order to formulate the system level circuit protection scheme.

To this end, CPES has been devoted to the design, modeling and simulation of power converters rated at 1 kV DC. System level simulations were conducted to evaluate the current-limiting functionality both during faults and overload conditions. These simulations were run within the same power system environments used to test the solid state circuit breaker. Accordingly, joint simulations will be run to investigate the coordination requirements among the power converters and solid state circuit breakers.

The last 9 months of execution of the project have been devoted to the construction of a 45 kW three-phase modular converter demonstrator based on the PEBB 1000 units developed at CPES using 1.7 kV SiC MOSFET power devices. This converter prototype will be used to demonstrate the fault handling capabilities of the converter when controlled under the proposed methods developed.

#### Developing the Future of Wide Bandgap Power Electronics Engineering Workforce

Sponsored by: Department of Energy (January 1, 2015 – July 31, 2021)

The goals of the proposed project are first to train the next generation of U.S. citizen power engineers with WBG power semiconductor expertise, thus aiding in fulfilling the future workforce needs in this field. Second,

to broaden the range of WBG-based power electronics by conducting research and development on high-efficiency grid apparatus and high-efficiency electrical power systems. And third, to enhance the power engineering curriculum by formalizing WBG-oriented design procedures for power electronics components and systems that can effectively integrate the inherent, challenging material characteristics of these devices, which have effectively rendered design procedures for Silicon (Si) based power electronics obsolete.

This project expects to graduate 10 MS students during its 5 years of execution, fund the first two years of 10 PhD students, and fund the first year of 5 additional MS and PhD students. In this period of time, 3-5 PhD students will expectedly graduate from Virginia Tech having passed through the proposed traineeship, and 5-10 more will do so in the following years. In all, a total of 45 graduate student assistantships will expectedly have been granted throughout the five years of the WBGen program. This will not only have an immense impact on the success of the WBGs research programs at Virginia Tech, but will consequently spring immeasurably positive effect on the power engineering workforce over the next 5 to 10 years. Furthermore, the DOE and DOD laboratory and industrial partnership established in the traineeship will also benefit significantly from the interaction with the participating graduate students, cementing what are already strong relationships between the partners and CPES, and CPE, into a solid network of power engineering training, research and development.

Gate driver, Rogowski current sensor board and signal processing board for 1.7 kV SiC MOSFETs used for PEBB 1000

# INTELLECTUAL PROPERTY

## U.S. Patents Awarded

#### 12-010

## Algorithm and Implementation System for Measuring Impedance in the D-Q Domain

By Gerald Francis, Rolando Burgos, Dushan Boroyevich, Fred Wang, Zhiyu Shen, Paolo Mattavelli, Kamiar Karimi, Sheau-Wei Johnny Fu

U.S. PATENT: 9,140,731 *Issued: September 22, 2015*

#### 12-009

#### Method of Evaluating and Ensuring Stability of AC/DC Power Systems

By Rolando Burgos, Dushan Boroyevich, Fred Wang, Kamiar Karimi U.S. PATENT: 9,136,773 Issued: September 15, 2015

#### 11-075

#### Two-Stage Bi-Directional Single-Phase Converter with DC-Link Capacitor Reduction

By Dong Dong, Dushan Boroyevich, Ruxi Wang, Fred Wang

U.S. PATENT: 9,071,141 *Issued: June 30, 2015*

#### 11-113

#### DC-Side Leakage Current Reduction for Single-Phase Full-bridge Power Converter/Inverter

By Dong Dong, Fang Luo, Dushan Boroyevich, Paolo Mattavelli U.S. PATENT: 9,048,756 Issued: June 2, 2015

#### 13-046

#### Multi-Channel Two-Stage Controllable Constant Current Source and Illumination Source

By Weiyi Feng, Fred C. Lee U.S. PATENT: 9,000,673 *Issued: April 7, 2015*

#### 13-025

#### Anti-Islanding Protection in Three-Phase Converters Using Grid Synchronization Small-Signal Stability

By Dong Dong, Dushan Boroyevich, Paolo Mattavelli, Bo Wen U.S. PATENT: 8,957,666

Issued: February 17, 2015

## Patents Pending

#### 16-062

1/28/2016

**Low Frequency Common Mode Voltage Control for Systems Interconnected with Power Converters**

Fang Chen, Rolando Burgos, Dushan Boroyevich

[Patent application sponsored by IPPF]

12/11/2015

#### **Omni-Directional Wireless Power Transfer System**

Junjie Feng, Qiang Li, Fred C. Lee [Patent application sponsored by IPPF]

#### 16-047

11/19/2015

**Parasitic Inductances Coupling to Reduce Transient Current Unbalance** in Semiconductor Power Switches

Yincan Mao, Zichen Miao, Khai Ngo, Chi-Ming Wang (TEMA)

[Patent application sponsored by TEMA]

#### 16-022

9/15/2015

#### A Nonlinear Droop Method to Improve **Voltage Regulation and Load Sharing** in DC Systems

Fang Chen, Rolando Burgos, Dushan Boroyevich

[Patent application sponsored by IPPF]

#### 16-008

8/6/2015

#### Method and Apparatus for Driving a **Power Device**

Jongwon Shin, Khai D.T. Ngo [Patent application sponsored by TEMA]

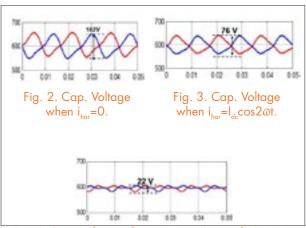

#### 16-007

7/27/2015

#### A Method of Capacitor Voltage **Ripple Reduction for Modular Multilevel Converter**

Yadong Lyu, Fred C. Lee, Qiang Li [Patent application sponsored by IPPF]

#### 16-005

7/13/2015

#### **Drivers with Equalizers** for Paralleled Switches

Khai D.T. Ngo, Lujie Zhang, Zichen Miao [Patent application sponsored by IPPF]

#### 15-071 (includes 15-070)

1/27/2015

#### **Multi-Step Simplified Optimal** Trajectory Control Based on Only V and $I_{load}$

Chao Fei, Fred C, Lee, Weiyi Feng, Qiang Li [Patent application sponsored by IPPF]

#### 15-069

2/2/2015

#### **Universal System Structure for Low Power Adapters**

Fred C. Lee, Xiucheng Huang, Qiang Li [Patent application sponsored by IPPF]

#### 15-068

2/2/2015

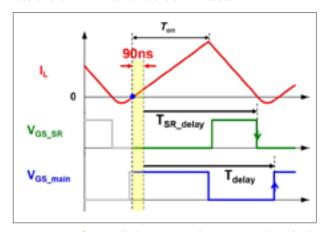

#### A Novel Driving Scheme for **Synchronous Rectifier in CRM Flyback** Converters

Xiucheng Huang, Fred C. Lee, Oiang Li [Patent application sponsored by IPPF]

#### 15-067

1/26/2015

#### New Current Mode Control Based on Charge Control Concept

Syed Bari, Fred C. Lee, Qiang Li [Patent application sponsored by IPPF]

#### 15-064

1/21/2015

#### Improved Current-Mode Control with Single-Step Load Transient

Virginia Li, Pei-Hsin Liu, Qiang Li, Fred C. Lee

[Patent application sponsored by IPPF]

#### 15-053

12/1/2014

#### **Optimal Battery Current Waveform** for Bidirectional PHEV Battery Charger

Lingxiao Xue, Paolo Mattavelli, Dushan Boroyevich

[Patent application sponsored by IPPF]

#### 15-049

11/12/2014

#### Coupled Inductor for Interleaved Multiphase Three-Level DC-DC **Converters and Its Integrated Designs**

Mingkai Mu, Sizhao Lu, Yang Jiao, Fred C. Lee

[Patent application sponsored by IPPF]

#### 14-144

5/27/2014

#### **Low Profile Coupled Inductor Substrate with Transient Speed Improvement**

Yipeng Su, Dongbin Hou, Fred C. Lee, Qiang Li [Patent application sponsored by IPPF; CIP to 13-169]

#### 14-101

3/4/2014

#### Transient Performance Improvement for Constant On Time Control

Syed Bari, Fred C. Lee, Qiang Li, Pei-Hsin Liu

[Patent application sponsored by IPPF]

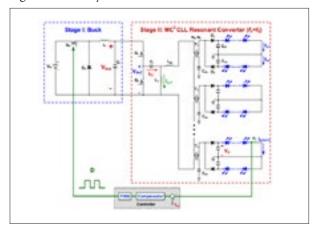

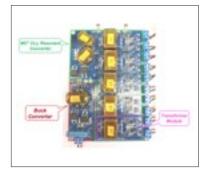

2/24/2014

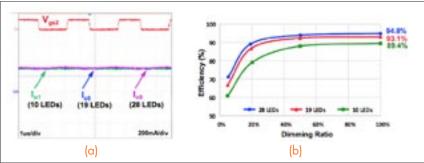

#### 2-Stage LED Driver with Multi-Channel Constant Current **CLL Resonant Converter**

Xuebing Chen, Daocheng Huang, Qiang Li, Fred C. Lee [Patent application sponsored by Panasonic1

#### 14-075

1/6/2014

#### **Magnetic Geometry** with Programmed Field Distribution Khai Ngo, Han Cui

[Patent application sponsored by IPPF]

#### 14-066

11/18/2013

Hybrid Interleaving Structure with adaptive PLL Loop for Constant On-Time Switching Converter

Pei-Hsin Liu, Fred C. Lee, Qiang Li [Patent application sponsored by IPPF]

#### 14-065

11/18/2013

Avoiding Internal Switching Loss in Cascode Structure Device under Soft-Switching Condition

Xiucheng Huang, Weijing Du, Qiang Li, Fred C. Lee

[Patent application sponsored by IPPF]

#### 14-053 (includes 14-147)

10/16/2013

## Switching-Cycle Control For The Modular Multi-Level Converter

Jun Wang, Rolando Burgos, Dushan Boroyevich, Bo Wen [Patent application sponsored by IPPF]

#### 13-169

6/14/2013

High-Frequency Integrated

Point-of-Load (POL) Module with PCB

Embedded Inductor Substrate

Yipeng Su, Qiang Li, Fred C. Lee, Wenli Zhang

[Patent application sponsored by IPPF]

#### 13-167

6/13/2013

System and Method for Impedance Measurement Using Chirp Signal Injection

Zhiyu Shen, Marko Jaksic, Paolo Mattavelli, Dushan Boroyevich, Jacob Verhulst, Mohamed Belkhayat [Patent application sponsored by NNS]

#### 13-166

6/13/2013

System and Method for Impedance Measurement Using Series and Shunt Injection

Zhiyu Shen, Marko Jaksic, Paolo Mattavelli, Dushan Boroyevich, Jacob Verhulst, Mohamed Belkhayat [Patent application sponsored by NNS]

#### 13-085

1/4/13

V<sup>2</sup> Control with Capacitor Current Ramp Compensation using Self-Calibrated Lossless Capacitor Current Sensing

Yingyi Yan, Pei-Hsin Liu, Fred C. Lee [Patent application sponsored by IPPF]

#### 13-032

9/12/12

Transformer Shielding Technique for Common-Mode Noise Reduction in Isolated Converters

Yuchen Yang, Daocheng Huang, Qiang Li, Fred C. Lee

[Patent application sponsored by IPPF]

#### 13-014

8/15/12

I<sup>2</sup> Average Current Mode Control for Switching Converters

Yingyi Yan, Fred C. Lee, Paolo Mattavelli [Patent application sponsored by IPPF]

#### 12-152

5/18/12

Optimal Trajectory Control of LLC Resonant Converter for LED PWM

Weiyi Feng, Fred C. Lee, Shu Ji [Patent application sponsored by IPPF]

#### 12-131

5/18/12

Optimal Trajectory Control of LLC Resonant Converter for Soft Start-Up

Weiyi Feng, Fred C. Lee [Patent application sponsored by IPPF]

#### 12-130

5/18/12

External Ramp Auto-Tuning for Current Mode Control of Switching Converter

Pei-Hsin Liu, Fred C. Lee, Yingyi Yan, Paolo Mattavelli [Patent application sponsored by IPPF]

#### 12-122

4/23/12

Common Input Voltage Control and Output Power Maximum Power Point Tracking (MPPT) for Sub-panel Converters with Series Outputs

Xinke Wu, Zijian Wang, Fred C. Lee, Feng Wang [Patent application sponsored by IPPF]

#### 12-044

10/7/11

Energy Storage for PFC by EV Motor/ Generator

Khai Doan The Ngo, Hui Wang [Patent application sponsored by IPPF]

#### 12-024

9/1/11

Anti-islanding Detection Algorithm and Modeling Approach for Three-Phase Distributed Generation Unit Dong Dong, Dushan Boroyevich, Paolo

Mattavelli

[Patent application sponsored by IPPF]

## Invention Disclosures

#### 16-084

1/21/2016

Integrated Rogowski Current Sensor for Shortcircuit Protection and Converter Control

Jun Wang, Zhiyu Shen, Rolando Burgos, Dushan Boroyevich

#### 16-030

1/20/2016

Distributed Kelvin-Source Resistance to Reduce Dynamic Power/ Current Imbalance in Paralleled Semiconductor Power Switches

Yincan Mao, Zichen Miao, Khai Ngo, Chi-Ming Wang (TEMA)

#### 16-062

1/28/2016

Low Frequency Common Mode Voltage Control for Systems Interconnected with Power Converters

Fang Chen, Rolando Burgos, Dushan Boroyevich

#### 16-061

12/16/2015

Use Parasitic Inductance Coupling to Eliminate Power Device Switching Operation Reliability Issues such as Cross-talk,Self Turn-On, and Self-Sustained Oscillation

Yincan Mao, Zichen Miao, Khai Ngo, Chi-Ming Wang (TEMA)

#### 16-057

12/11/2015

Omni-Directional Wireless Power Transfer System

Junjie Feng, Qiang Li, Fred C. Lee

#### 16-047

11/19/2015

Parasitic Inductances Coupling to Reduce Transient Current Unbalance in Semiconductor Power Switches Yincan Mao, Zichen Miao, Khai Ngo, Chi-Ming Wang (TEMA)

#### 16-022

9/15/2015

A Nonlinear Droop Method to Improve Voltage Regulation and Load Sharing in DC Systems

Fang Chen, Rolando Burgos, Dushan Boroyevich

#### 16-008

8/6/2015

Ramp Current Driver

Jongwon Shin, Khai D.T. Ngo

#### 16-007

7/27/2015

A Method of Capacitor Voltage Ripple Reduction for Modular Multilevel Converter

Yadong Lyu, Fred C. Lee, Qiang Li

#### 16-005

7/13/2015

Drivers with Equalizers for Paralleled Switches

Khai D.T. Ngo, Lujie Zhang, Zichen Miao

#### 15-102

5/27/2015

**Charge-Limited Switch Driver** Khai D.T. Ngo, Zichen Miao

# VIRGINIA TECH FACILITIES

## Introduction

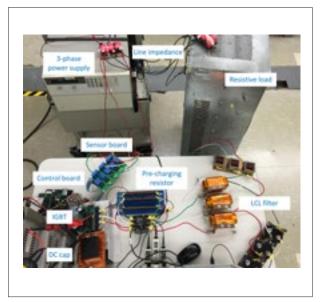

The Center headquarters are located at Virginia Tech, occupying office and lab facilities encompassing more than 20,000 sq ft of space in one building. Research space at CPES-VT includes an electrical research lab, an integrated packaging lab, and computer lab. In addition to the headquarters labs and offices, a research library, and a large conference room with voice and video conferencing capabilities supporting remote site course instruction as well as interaction among CPES collaborators is maintained. Interactive collaboration is routinely facilitated through conference calls, WebEx online conferencing, student and faculty exchanges, and face-to-face research project review meetings.

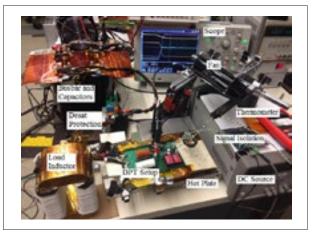

## Electrical Research Laboratory

The electrical research laboratory is equipped with state-of-the-art tools and equipment for development of power electronic circuits and systems of all sizes from sub-volts, sub-watts to 6kV, 1MW. It also includes PWB manufacturing equipment, an EMI chamber, a clean room and a mechanical shop. New this year is a state of the art curve tracer that is capable of characterizing up to 10kV and 1500A. Each student bench is equipped with Dell computers with an i7 core and up to 16 GB of RAM for running complex simulations. Standard instrumentation includes: GHz oscilloscopes, multi-channel function generators, electronic loads, network, spectrum, impedance, logic, and power analyzers, thermal sensors, and ac/dc bench supplies of all sizes. Specialized test room equipment includes: thermal imaging, thermal cycling chambers, Hi-Pot tester, 3D magnetic field scanner, EMI/EMC analyzer, large and small dynamometers, automatic circuit board routing equipment, magnetic core loss testing, programmable and variable loads, and liquid cooled heat-exchanger.

## **Integrated Packaging Lab**

The Integrated Packaging (IP) Lab supports all CPES students, faculty, visiting scholars, and sponsors for their advanced needs in power electronics packaging research. The lab was established to create and evaluate alternative approaches to the design and manufacture of Integrated Power Electronics Modules (IPEMs) and provide the state-of-the-art electronic manufacturing and assembly equipment. The IP lab itself has installed a sealed ceiling and HEPA filtration to create over 1,600 square feet of classroom 10,000 clean room space, and the addition of a dark room for photolithography processing. It has the capability to produce FR4, DBC, and thick film hybrid substrates, perform metallization using RF sputtering thin film deposition and electro/electro-less plating, and develop substrate patterns by virtue of laser ablation machining, chemical metal etching, and screen printing. The IP lab also has the ability to mount bare dies and SMT components using high precision pick-n-place machine, solder reflow belt furnace, and convection reflow oven. The advanced vacuum solder reflow system provides another technical solution for die-attachment in a flux-less, void-less process. The wire bonding machines equipped in the IP lab provide interconnect options of heavy aluminum wire bonding, gold wire ball bonding, and aluminum/gold ribbon bonding for manufacturing IPEMs. For accurate and controlled dispensing of adhesives and encapuslants, an automated precision dispensing system and a spin coater have been added in the lab. In addition, the IP lab has the full capability for low temperature co-fired ceramic (LTCC) processing from tape cutting, via drilling, screen printing, laminating, to co-firing. The components and module-level test and evaluation of electrical, thermal, and reliability performance for the assembled IPEMs are also available in the IP lab. Low and high power curve tracers, impedance analyzers, and precision multimeters can be used for electrical property measurements. Thermal performance evaluation can be made by the setup of thermocouples, optic-fiber sensors, IR imaging, and thermal diffusivity test system. Reliability analysis is performed using multi-purpose bond tester on as-made modules and ones after certain numbers of temperature/humidity cycling. An array of crosssectioning and grinding/polishing equipment has been used to better understand the microstructure of electronic packaging materials.

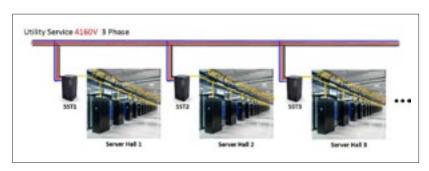

## **High Power Lab**

High power, high voltage power conversion technologies are attracting increasing attention in academia as well as industry in response to a need for more emerging power electronics applications, including alternative energy and power conversion such as wind power generations, fuel cells, hybrid electric vehicles and allelectric ships. Enabled by a 2002 award of \$839,337 from the Defense University Research Instrumentation Program (DURIP) paired with CPES cost sharing of more than \$250,000 for renovations, the electrical research lab area at Virginia Tech has been renovated and upfit to accommodate medium voltage, megawatts power capability. The facility has two medium voltage 1 MVA reconfigurable transformers, corresponding reactors, capacitors, switchgears, and controllers. A 1 MW Innovation Series medium voltage IGBT drive donated by GE is installed as a programmable load. The complete set-up is capable of testing power converters in various active and reactive operation modes continuously at 1 MVA, 4160V level. The unique installation distinguishes Virginia Tech as one of a few select universities in the nation with this capability and enhances its position as a leader in power electronics research well beyond the NSF ERC life expectancy.

## **Library and Computer Lab**

The computer lab supports all major software used in power electronics design including: SPICE, Saber, Simplis, Code Composer, Math products – Matlab and Mathcad, Ansys Products – Workbench and Mechanical, Ansys Electromagnetics – Maxwell, Electronics Desktop (Q3D, HFSS), Simplorer, SIWave, Mentor Graphics Flowtherm, PLECS, and Altium Designer.

## **SPOTLIGHT ON ALUMNI**

#### Chen, Qing (Que)

Affiliation:

Flextronics International FlexPower

Position title:

VP of Engineering

Last degree

from Virginia Tech:

Ph.D.

Year Graduated:

1994

#### **CAREER HIGHLIGHTS**

1994: Member of Technical Staff, Lucent Technologies

1998: Technical Manager, Distinguished Member of Technical Staff, Lucent Technologies

2001: VP of Engineering & one of original founding members, Innoveta Technologies

2003: VP of Engineering, TDK Innoveta, Inc. (Innoveta acquired by TDK)

2005: Chief Technical Officer, Emerson Network Power -Embedded Power

2009: General Manager, Delta Electronics – China New Energy/Megawatt/Wind Power BU

2014: VP of Engineering, Flextronics International – FlexPower

#### **QUOTE**

"The graduate study at VPEC changed my life profoundly. The center created an environment that is characterized by intellectual stimuli and team spirit. It was an enjoyable place to study and work. Thanks to Dr. Lee, all the faculty and staff, and fellow students, I learned so much during my stay at VPEC, which laid a solid foundation for my professional career in various companies and different geographical locations."

#### Chen, Wei

Affiliation:

Silergy Corp.

Position title:

CEO

Last degree

from Virginia Tech:

Ph.D.

Year Graduated:

1998

#### **CAREER HIGHLIGHTS**

1995-1998: VPT Inc.: Design Engineer

1998-2003: Linear Technology Corp. : Applications

Engineer/Section Manager, Developed industry first power module chip

2004-2007: Monolithic Power System: VP of System

and Applications

2008-now: Silergy Corp.: Founder and CEO, founded

the analog IC design house in 2008, brought the company IPO in 2013 and achieved \$148M revenue in 2015

#### **QUOTE**

"Over decades, VPEC/CPES has persistently pursued the best power conversion technologies to achieve the highest efficiency and power density. The single-minded approach has guided me throughout my career and contributed to business success."

#### Hua, Gary

Affiliation: Inventronics. Inc. Position title: CEO Last degree from Virginia Tech: Ph.D. Year Graduated: 1993

#### **CAREER HIGHLIGHTS**

1993: Cofounded VPT with Dr. Fred Lee and Dr. Dan Sable

1999: Founded e-Power Co., Ltd. in Hangzhou, China

2001: Sold e-Power to Bel Fuse Inc. which is a NASDAQ listed company

2007: Founded Inventronics Inc. in Hangzhou China

2009: Selected as member of China One Thousand Elite Program

2011: Elected as Top 20 China CCTV Economy Person of the Year

#### Jovanovic, Milan M.

Affiliation:

Delta Products Corporation

Position title:

Senior Vice President R&D

Last degree

from Virginia Tech:

Ph.D.

Year Graduated:

1988

#### **CAREER HIGHLIGHTS**

1976: Research Assistant, University of Novi Sad, Yugoslavia

1988: Research Scientist, Virginia Tech

1991: Director, Delta Power Electronics Lab.,

Blacksburg, VA

1998: Vice President R&D, Delta Products Corporation, Research Triangle Park, NC

2001: Fellow IEEE

2004: CTO, Delta Power Supply Business Group

2015: National Academy of Engineering

#### **QUOTE**

"In hindsight, joining the Power Electronics Research Group (PERG) at Virginia Tech led by Dr. Lee has been the defining moment of my career. Besides receiving an outstanding power electronics education, as a member of PERG, I was given the opportunity to perform cutting-edge research for leading technology companies and government entities. This involvement helped me discover the satisfaction of innovative work that has been the major inspiration for dedicating my entire career to R&D."

#### Lotfi, Ashraf

Affiliation: Intel Corporation Position title: VP/Fellow Last degree from Virginia Tech: Ph.D. Year Graduated: 1993

#### **CAREER HIGHLIGHTS**

1993-1998: Member of the Technical Staff, Power Systems Research Dept., AT&T Power

Systems

1998-2000: Department Head, Power Systems Re-

search Dept., Bell Laboratories, Lucent

Technologies

2000-2002: Director, Analog and Power Management

Research, Bell Laboratories, Lucent Tech-

nologies

2002-2013: Founder, President and CEO, Enpirion Inc. 2014-2016: Chief Technology Officer, Power Products

Business, Altera Corporation

2016: VP / Fellow, Intel Corporation

#### QUOTE

"VPEC and Professor Lee's luminary leadership have been the primary drivers forging my passion for this field of power electronics and more importantly my intense commitment to continue its advancement with innovative technologies. It was the broad spectrum of projects, new technologies, advanced lab capabilities, industry sponsorships and most importantly the open, undictated, creative research direction at VPEC that laid the foundation for me to continue to technologically advance the field many years after graduating. I am very proud to say that my entire career has been a direct and continuous advancement on the themes of my early research years at VPEC. Looking back today, Virginia Tech has been a profound pillar in my professional career, one I am certain could not have been achieved at any other University anywhere else in the world. I would never have it any other way."

#### Qian, Jinrong

Affiliation:

Texas Instruments

Position title:

Business Unit Manager,

Battery Charging Products

Last degree

from Virginia Tech:

Ph.D.

Year Graduated:

1997

#### **CAREER HIGHLIGHTS**

2003: Apps Manager, at Intersil Corp

2005: Apps manager, elected as Senior Member of

Technical Staff, Texas Instruments

2007: Elected as Distinguished Member of Technical

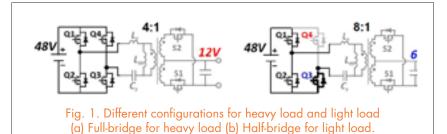

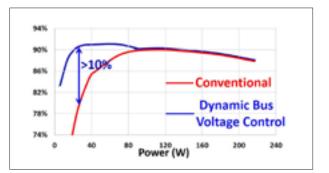

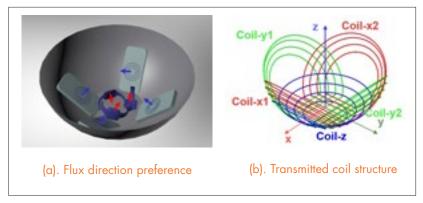

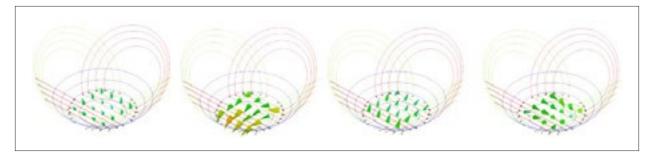

Staff at Texas Instruments