#### A Cross Platform Method for FPGA Integrity Checking

#### Matthew Aaron Benz

Thesis submitted to the faculty of the

Virginia Polytechnic Institute and State University

in partial fulfillment of the requirements for the degree of

Master of Science

In

**Computer Engineering**

Dr. Mark T. Jones, Chair

Dr. Peter M. Athanas

Dr. Cameron D. Patterson

August 30, 2007

Bradley Department of Electrical and Computer Engineering

Blacksburg, Virginia

Keywords: FPGA, security, configuration, integrity, portable, fault-injection, configurable, reconfigurable, partial, dynamic, embedded system, platform Copyright 2007 ©, Matthew Aaron Benz

#### A Cross Platform Method for FPGA Integrity Checking

#### Matthew Aaron Benz

#### (ABSTRACT)

As embedded systems continue to evolve and the number of applications they support continues to increase, so does the diversity of the hardware they employ. As a result, the Field Programmable Gate Arrays (FPGAs), which have become fundamental elements in their design, have advanced in size and complexity as well. Because of this, it is now impossible to ignore the security implications that accompany such a progression. It is then not only important to prevent malicious attacks targeted at FPGAs from extracting the intellectual property contained in their configuration, but to now extend the research in this field by providing a cross-platform solution capable of securing the integrity of FPGA configurations at run-time. Today, there exist myriad attack strategies employed against FPGAs, the majority of which are seen in the form of semi-invasive attacks. These attacks manipulate the configuration of an FPGA and typically modify the state of the transistors that make up said configuration.

This thesis introduces a multi-platform method for checking the integrity of an FPGA's configuration. The details of the system's design and implementation are discussed in addition to the analysis of the design trade-offs met when employing the system across multiple FPGA families. The system is implemented entirely in hardware and resides on-chip, providing an FPGA the ability to act as private entity capable of successfully detecting when it has been maliciously attacked.

## Acknowledgements

The contributions presented in this thesis would not have been possible if it were not for the support, guidance and motivation given to me from a very long list of friends, family and Virginia Tech faculty. For those who are not mentioned explicitly, the support you have given me has not gone unnoticed, and I would like to take this time to thank you.

To begin, I would like to thank my advisor Dr. Mark Jones for his guidance throughout my graduate academic career. Under his direction, I have learned the value of patience and thoroughness, and I am surely better off personally and professionally for it. In addition, I would like to thank Dr. Peter Athanas for his patience, knowledge and advice during my time as both a graduate and undergraduate student at Virginia Tech. Also, I would like to thank Dr. Cameron Patterson for serving on my graduate committee.

Next, I would like to acknowledge each member of the Virginia Tech faculty who played a role in furthering my education over the past 6 years. Without your guidance and wisdom this work would not have been possible.

I could not go without thanking Brac Webb for the role he played as both a friend and comember on the Harris Design team at the Virginia Tech CCM lab. The contributions presented in this thesis could not have been possible if not for his work.

I am forever grateful to my parents, Linda and Larry Benz, for not only providing me the opportunity to obtain a graduate education, but for their love, patience and encouragement throughout my collegiate career and life. If it were not for you, there is no way I would be where I am today. In addition, I would like to thank my grandparents Ann and Conrad Benz for their continued interest, encouragement and support in both my academic career and growth as a

person. I would also like to thank Wendy Cruzan for enlightening me with her grammatical prowess. This work would have never been completed without your assistance.

Lastly, I would like to thank my friends and brothers of the Pi Kappa Alpha Fraternity. It was through the relationships I formed and the experiences I had while being a PIKE at Virginia Tech that helped make me the person I am today. I would like to specifically thank Eugene Shim for his continued social encouragement, as well as Michael Perry for his advice and academic timeline (a great source of inspiration and motivation). Last, but not least, I would like to thank Byron Baptist for being the best friend anyone could ask for. If it was not for your advice, trust and willingness to continually motivate, I defiantly could not have accomplished all that I have. In the bonds,  $\varphi\varphi\kappa\alpha$ .

## **Contents**

| List of Figu | res                                                            | хi |  |

|--------------|----------------------------------------------------------------|----|--|

| List of Tabl | List of Tables                                                 |    |  |

| Chapter 1    | Introduction                                                   | 1  |  |

| 1.1          | Motivation                                                     | 1  |  |

| 1.2          | Contributions                                                  | 2  |  |

| 1.3          | Thesis Organization                                            | 3  |  |

| Chapter 2    | Background and Previous Work                                   | 5  |  |

| 2.1          | FPGAs                                                          | 5  |  |

| 2.2          | Security Profiles and Classification                           | 6  |  |

| 2.3          | FPGA Attack and Protection Strategies                          | 8  |  |

|              | 2.3.1 Extracting Secure Information from FPGA Configurations . | 9  |  |

|              | Side Channel Attacks                                           | 9  |  |

|              | Data Extraction Attacks                                        | 10 |  |

|              | Bitstream Interception Attacks                                 | 11 |  |

|           | 2.3.2  | Alteri    | ng FPGA Configurations                                             | 11 |

|-----------|--------|-----------|--------------------------------------------------------------------|----|

|           |        | Invasi    | ve Attacks on FPGA Configurations                                  | 12 |

|           |        | Semi-     | Invasive Attacks on FPGA Configurations                            | 12 |

| 2.4       | Softw  | are Port  | ability                                                            | 13 |

|           |        | 2.4.1     | Software Platform Portability                                      | 13 |

|           |        |           | Java Based GUIs and APIs                                           | 14 |

|           |        |           | C / C++ Based Applications                                         | 14 |

|           |        |           | Scripting Languages                                                | 15 |

|           |        | 2.4.2     | Extending Software Tools Across Multiple FPGA Devices and Families | 15 |

| 2.5       | FPGA   | Config    | guration Integrity Checking                                        | 16 |

|           | 2.5.1  | SEU I     | Discovery and Repair                                               | 16 |

|           | 2.5.2  | Config    | guration Integrity Checking on the Virtex 4 Platform.              | 17 |

|           |        | Dynar     | nic Data Identification                                            | 17 |

|           |        | CLB I     | Block Hash Generation and Comparator                               | 18 |

|           |        | Provid    | ling Assurance of Correct Operation                                | 18 |

| 2.6       | Applio | cations ' | That Can Benefit From Configuration Integrity                      | 19 |

|           | Checl  | king      |                                                                    |    |

| Chapter 3 | Metho  | od for S  | Securing FPGA Configurations on the Virtex 4                       | 20 |

|           | Platfo | rm        |                                                                    |    |

| 3.1       | FPGA   | Config    | guration Readback Control                                          | 20 |

| 3.2       | Detect | tion of I | Malicious Configuration Modifications                              | 23 |

|           | 3.2.1  | MD5       | Hashing Algorithm                                                  | 23 |

|           | 3.2.2 Hash Value Granularity Considerations               | 25 |

|-----------|-----------------------------------------------------------|----|

|           | 3.2.3 Attack Locality Determination                       | 26 |

| 3.3       | Ensuring Reliable Operation                               | 26 |

| 3.4       | Coverage of Future Work                                   | 27 |

| Chapter 4 | Multi-Platform Configuration Integrity Checker Design and | 28 |

|           | Implementation                                            |    |

| 4.1       | Dynamic Data Identification and Masking                   | 28 |

|           | 4.1.1 Dynamic Data Identification Strategy                | 29 |

|           | 4.1.2 Memory Considerations                               | 31 |

|           | 4.1.3 FPGA Configuration Bitstream Layout                 | 33 |

| 4.2       | Platform Independent Dynamic Data Masking                 | 35 |

|           | 4.2.1 Approach                                            | 35 |

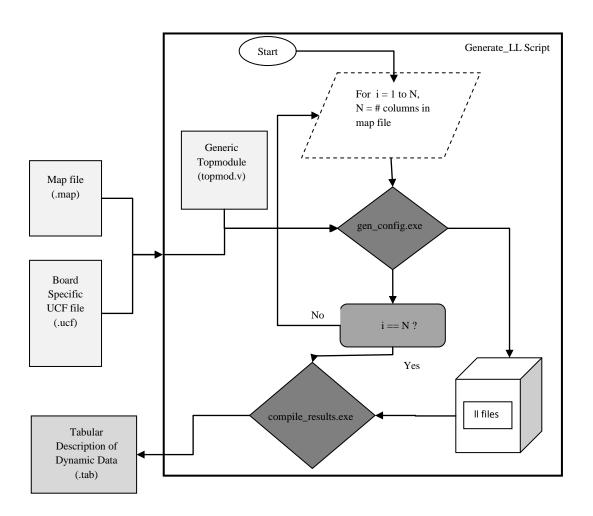

|           | 4.2.2 Automating the Dynamic Data Mapping Process         | 37 |

|           | Map File Generation                                       | 37 |

|           | Generate_Config Executable                                | 38 |

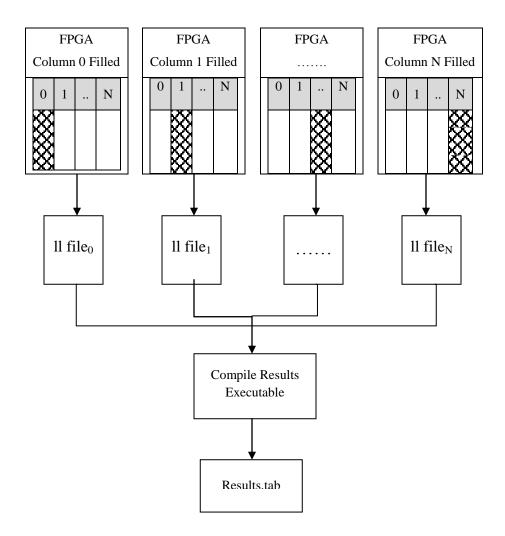

|           | Logic Allocation File Generation Script                   | 38 |

|           | Compile_Results Executable                                | 39 |

|           | 4.2.3 Identifying Auxilary Dynamic Data                   | 40 |

|           | Virtex II and II Pro Platforms                            | 41 |

|           | Virtex 4 Platform                                         | 41 |

|           | Hard Core Processor Instantiation                         | 41 |

| 4.3       | Platform Independent Configuration Integrity Checking     | 42 |

|           | 4.3.1 Active Configuration Readback                       | 42 |

|           |        | ICAP Readback Commands                             | 43 |

|-----------|--------|----------------------------------------------------|----|

|           |        | Internal Readback FSM Control Parameters           | 43 |

|           | 4.3.2  | Checksum Computation Design and Considerations     | 44 |

|           |        | Hash Value Generation                              | 44 |

|           |        | Platform and Device Specific Dynamic Data Masking  | 45 |

|           | 4.3.3  | Resource Allocation                                | 46 |

|           | 4.3.4  | Challenge Response Subsystem                       | 46 |

|           |        | Shared Memory Considerations                       | 46 |

|           | 4.3.5  | Serial I/O Subsystem                               | 47 |

| Chapter 5 | Valid  | ation and Multi-platform Analysis                  | 49 |

| 5.1       | Result | ts of Previous Work                                | 50 |

|           | 5.1.1  | Resource and Timing Analysis                       | 50 |

|           |        | Resource Analysis                                  | 50 |

|           |        | Timing Analysis and Critical Path Considerations   | 50 |

|           |        | Security Level Classification                      | 52 |

| 5.2       | Platfo | rm Independent Dynamic Data Identification Process | 52 |

| 5.3       | Valida | ation                                              | 54 |

|           | 5.3.1  | Testbed                                            | 54 |

|           | 5.3.2  | Radix-4 FFT                                        | 54 |

|           | 5.3.3  | Testbed Standardization                            | 57 |

|           | 5.3.4  | Results                                            | 59 |

| 5.4       | Dorfor | mance Analysis                                     | 63 |

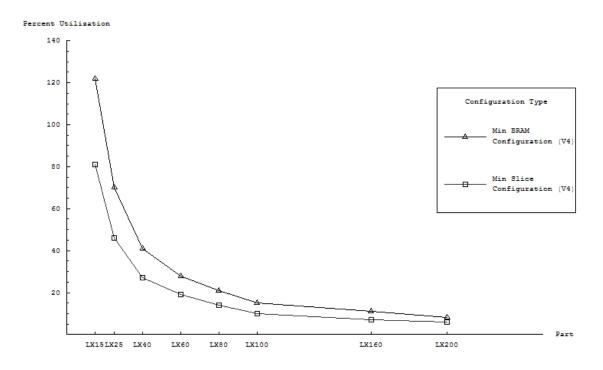

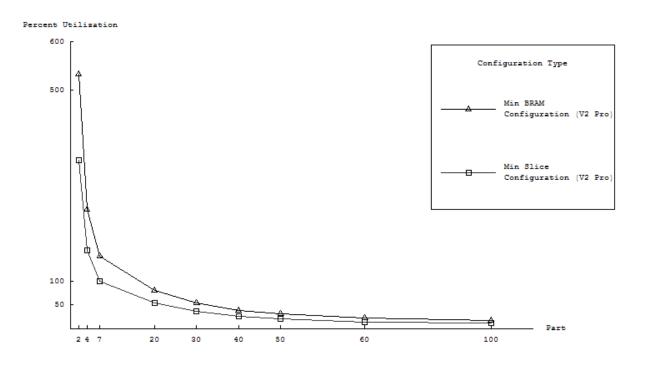

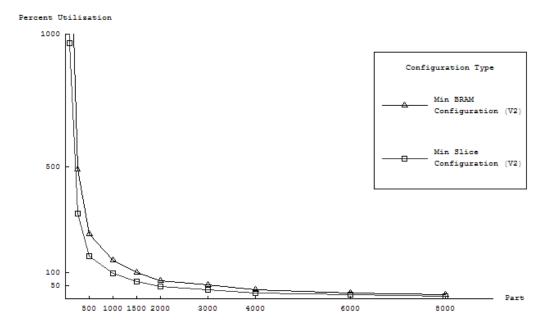

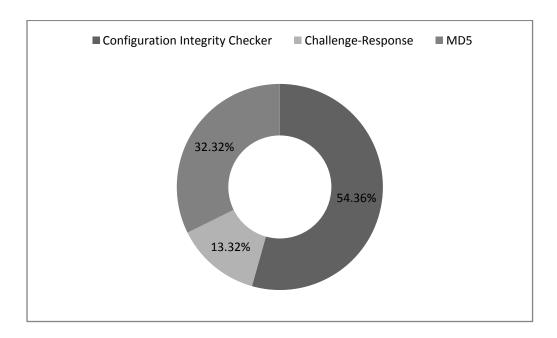

|        |        | 5.4.1   | Resource Utilization                                        | 63                   |

|--------|--------|---------|-------------------------------------------------------------|----------------------|

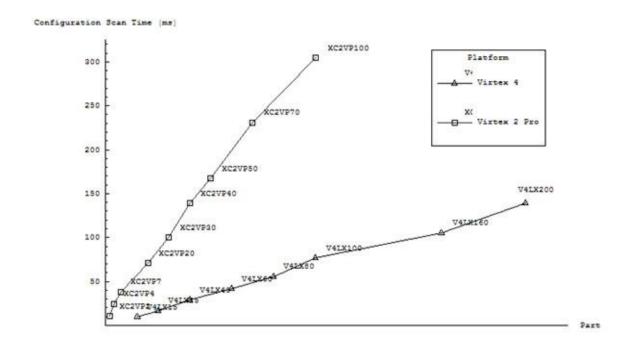

|        |        | 5.4.2   | Multi-platform Latency Analysis                             | 68                   |

|        |        |         | Subsystem Execution Time Analysis                           | 68                   |

|        |        |         | Configuration Integrity Checker Subsystem                   | 68                   |

|        |        |         | Challenge Response Subsystem                                | 72                   |

|        | 5.5    | System  | m Security Analysis and Classification                      | 73                   |

|        | 5.6    | Platfo  | rm Analysis and Considerations                              | 74                   |

|        |        | 5.6.1   | Granularity Considerations                                  | 74                   |

|        |        | 5.6.2   | Memory Architecture                                         | 75                   |

|        | 5.7    | Summ    | nary of Results                                             | 76                   |

| Chapte | er 6   | Concl   | usion                                                       |                      |

| -      | 77     |         |                                                             |                      |

|        | 6.1 Su | mmary   |                                                             | 77                   |

|        |        |         |                                                             |                      |

|        | 6.2 Fu | ture Wo | ork                                                         | 79                   |

|        | 6.2 Fu | ture Wo | Addressing Security Weaknesses Due to Extensive Scan        | 79                   |

|        | 6.2 Fu |         |                                                             | 79<br>79             |

|        | 6.2 Fu |         | Addressing Security Weaknesses Due to Extensive Scan        |                      |

|        | 6.2 Fu |         | Addressing Security Weaknesses Due to Extensive Scan  Times | 79                   |

|        | 6.2 Fu |         | Addressing Security Weaknesses Due to Extensive Scan  Times | 79<br>79             |

|        | 6.2 Fu | 6.2.1   | Addressing Security Weaknesses Due to Extensive Scan  Times | 79<br>79<br>80       |

|        | 6.2 Fu | 6.2.1   | Addressing Security Weaknesses Due to Extensive Scan  Times | 79<br>79<br>80<br>80 |

| Appendix A | Xilinx Virtex-II Pro Configuration Details            | 94  |

|------------|-------------------------------------------------------|-----|

| Appendix B | Xilinx Virtex-4 Configuration Details                 | 99  |

| Appendix C | Generate_Config User Guide                            | 105 |

| Appendix D | Generate_ll Script Source                             | 108 |

| Appendix E | <b>Auxiliary Configuration Implementation Details</b> | 110 |

## **List of Figures**

| 3.1 | Outline of the FSM used to read to / write from the ICAP on the |    |

|-----|-----------------------------------------------------------------|----|

|     | Virtex 4 platform <sup>1</sup>                                  | 22 |

| 3.2 | MD5 hash function finite state machine outline <sup>1</sup>     | 24 |

| 3.3 | Challenge response subsystem architecture                       | 27 |

| 4.1 | Virtex 4 frame address description                              | 30 |

| 4.2 | Xilinx block type layout                                        | 32 |

| 4.3 | Outline of the Virtex 4 readback configuration data stream      | 34 |

| 4.4 | Diagram of Automated Dynamic Data Identification Process        | 36 |

| 4.5 | Diagram of Logic Allocation File to Tabular Results Process     | 37 |

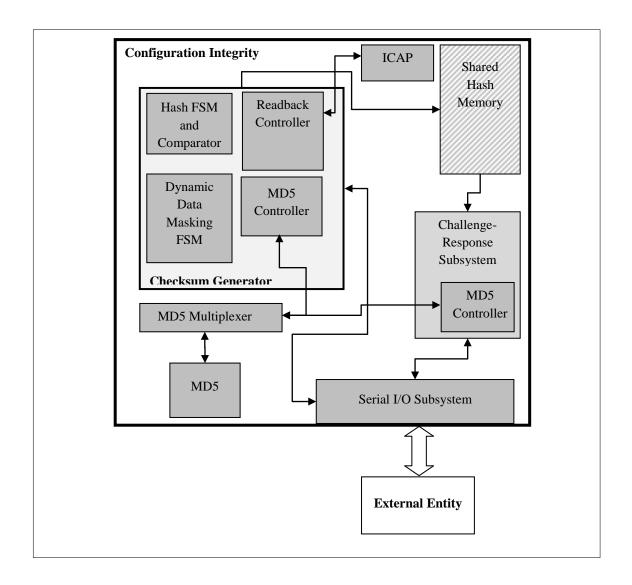

| 4.6 | Block Diagram of Platform Independent Configuration Integrity   |    |

|     | Checker                                                         | 48 |

| 5.1 | Radix- 4 FFT output ordering                                    | 55 |

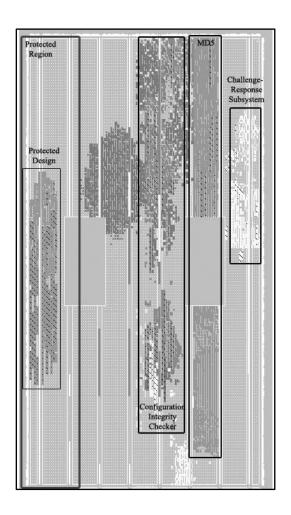

| 5.2 | Design layout on the Xilinx XC2VP30 FPGA with protected design  |    |

|     |                                                                 |    |

<sup>&</sup>lt;sup>1</sup> Figures and images used, which are not my own, are of fair use

|     | in secured region                                                  | 58  |

|-----|--------------------------------------------------------------------|-----|

| 5.3 | Virtex 4 system slice utilization                                  | 65  |

| 5.4 | Virtex II Pro system slice utilization                             | 66  |

| 5.5 | Virtex II system slice utilization                                 | 66  |

| 5.6 | Design utilization percentage breakdown by subsystem               | 67  |

| 5.7 | Time required to scan a entire FPGA configuration for the Virtex 4 |     |

|     | and Virtex II Pro Platforms                                        | 71  |

| 6.1 | Random readback successive block readback scenario                 | 80  |

| A.1 | Configuration Frames Containing Dynamic Data on the Virtex II      |     |

|     | XC2V250                                                            | 95  |

| A.2 | Bit positions containing dynamic data in Virtex II XC2V250         | 96  |

| B.1 | Xilinx formatted frame addresses of flip-flop data on the Virtex   |     |

|     | 4 LX25                                                             | 100 |

| B.2 | Absolute frame address' of flip flop data on the Virtex 4 LX25     |     |

|     | device                                                             | 101 |

| B.3 | Bit positions containing dynamic data in Virtex 4 LX25 device      | 102 |

| B.4 | Virtex 4 LX25 FPGA frame address layout                            | 103 |

| B.5 | Hash number to physical location mapping for the Virtex 4 LX25     |     |

|     | davica                                                             | 104 |

## **List of Tables**

| 3.1  | Readback commands used to startup and shutdown the Virtex 4     |     |

|------|-----------------------------------------------------------------|-----|

|      | ICAP                                                            | 21  |

| 5.1: | Resource consumption breakdown for the PDCIC                    | 51  |

| 5.2  | Execution time for generate_ll script across multiple platforms | 53  |

| 5.3  | FFT resource utilization                                        | 59  |

| 5.4: | Minimum, average, and maximum scan times required to detect a   |     |

|      | malicious alteration to the FPGAs configuration                 | 61  |

| 5.5  | System resource utilization under reduced BRAM consumption      |     |

|      | configuration                                                   | 63  |

| 5.6  | System resource utilization under reduced slice consumption     |     |

|      | configuration                                                   | 64  |

| A.1  | Map File for the Xilinx Virtex II Pro XC2VP30 Device            | 97  |

|      |                                                                 |     |

| A.2  | Example Table Generated by Compile Results Executable for the   |     |

|      | Xilinx Virtex II Pro XC2VP7,                                    | 98  |

| C.1  | Gen_Config Executable Parameter Description                     | 106 |

|      |                                                                 |     |

| C.2 | Example Topmodule and UCF Header Files                        | 107 |

|-----|---------------------------------------------------------------|-----|

| D.1 | Example "generate_ll" Script Configured for the Xilinx XC2VP7 | 109 |

## Chapter 1

#### Introduction

#### 1.1 Motivation

Since their introduction in the 1980s, Field Programmable Gate Arrays (FPGAs) have evolved from small configurable chips with limited application into run-time reconfigurable (RTR) multimillion gate hardware devices. Consequently, a significant share of the market, which has been historically dominated by Application Specific Integrated Circuits (ASICs), Digital Signal Processors (DSPs) and microprocessor based systems, is now occupied by FPGAs [55,71,73,74]. Modern FPGAs are capable of housing entire System-on-Chip (SoC) designs and are now used in the medical, industrial, networking, digital computing, telecommunications, wireless and defense fields [72]. FPGAs have now shifted from being an intermediate step in the design process to frequently appearing in the final product, making it imperative to consider the security implications they present.

Historically, the majority of the research in the field of configurable computing has focused on areas outside of the topic of FPGA security. However, as FPGAs begin to become the

backbone of many real world applications, the need for research on the topic of FPGA security has been recognized. A number of research efforts have begun to investigate the security of, not only the intellectual property contained in FPGA configurations [40,41,42,43,44], but auxiliary topics such as network traffic filtering [71], partial bitstreams [45] and using FPGAs to develop secure software platforms [39]. While these areas represent significant progress in this field, there have been few efforts that have succeeded in securing the integrity of FPGA configurations.

A system that has succeeded in securing aspects of the integrity of FPGA configurations on the Xilinx Virtex-4 platform is presented in [2]. This system is comprised of three parts. The first subsystem actively monitors the configuration of a FPGA, checking for malicious alterations made by an attacker. Next, a subsystem for securing partial bitstreams, which are used to reconfigure portions of the device's configuration, is presented. Finally, an implementation of a classic challenge-response protocol is outlined. This subsystem can be used by an external entity to ensure that the system is operating correctly.

#### 1.2 Contributions

While systems such as the one presented in [2] have successfully secured the integrity of FPGA configurations, they have only done so on one particular platform for one specific device. This provides a solution that lacks portability and parameterizability.

Presented in this thesis is a cross platform method by which dynamic data can be actively masked from FPGA configuration bitstreams. In addition, an approach to extending the configuration readback and hash generation/comparison methodologies outlined in [2] across multiple platforms is presented. Also, a flow designed to automatically generate the relative readback bitstream locations of all dynamic flip-flop data present on any device in any Xilinx FPGA family is described. As a final contribution, a cross platform implementation of the challenge-response subsystem presented in [2] is outlined. When combined, these contributions

demonstrate that a FPGA configuration integrity checking solution can be developed that supports multiple devices spanning multiple platforms.

The cross-platform configuration integrity checking method presented supports two configurations, each of which is optimized to consume opposing sets of resources. This serves to provide system designers a security solution that best fits the resources they have available. Platform specific configurations of the dynamic data masking subsystem are also provided. These configurations are provided to increase portability and relieve the system designer of the burden of performing complex parameterizations when porting system to a new platform.

The cross-platform integrity checking solution presented was developed and tested under a series of simulated fault injection attacks generated though the use of partial reconfiguration. An analysis of the results of these experiments is described. In addition, a complete analysis of the systems resource consumption, timing characteristics and platform portability is presented. Finally, potential future work that could be used to improve the system is presented.

#### 1.3 Thesis Organization

The remaining five chapters of this thesis are arranged as follows. Chapter 2 provides an overview of FPGAs and FPGA security. Also presented is an outline of the previous work performed in the area of securing the integrity of FPGA configurations. Chapter 3 describes the design and implementation of the platform dependent configuration integrity checker presented in [2]. In Chapter 4, a flow designed to automate the process of identifying the relative locations of all dynamic data in an FPGA readback configuration is described. Also, the method by which the configuration readback, hash computation and challenge-response components presented in [2] were extended across multiple platforms is described. To conclude this chapter, the approach to combining these contributions to form a platform independent solution to securing the integrity of FPGA configurations is presented. Chapter 5 provides a comprehensive multiplatform analysis of the resource requirements, timing characteristics and security strengths and

weaknesses of the system. Finally, in Chapter 6, a summarization of the research performed, as well as a discussion of potential future work is detailed.

### Chapter 2

## **Background and Previous Work**

The content of this chapter serves to provide a background of current and previous work on the topics covered in this thesis. These topics include FPGAs, security profiles and classifications, attack strategies commonly employed against FPGAs, extending tools across multiple FPGA devices/platforms and previous work in the field of FPGA configuration integrity checking.

#### 2.1 FPGAs

Field Programmable Gate Arrays (FPGAs) are devices that contain programmable logic blocks and interconnect which can be configured to realize designs ranging from basic logic gates to complex embedded systems. As the name implies, FPGAs are "field programmable", meaning that a system designer can re-program the device to model different sets of hardware as many times as needed. In general, designs instantiated on FPGAs draw more power and exhibit higher latencies than those implemented using application specific integrated circuits (ASICs). The tradeoffs for this lack in performance include shorter time to market due to rapid prototyping, cost efficiency, throughput and resource efficiency [47]. Another benefit FPGAs provide to

offset their lack in performance is dynamic partial reconfigurability [28]. Dynamic partial reconfiguration refers to the process of reconfiguring a portion of the design running on the FPGA in parallel with the execution of the rest of the design. The ability to reconfigure a portion of a hardware design at run-time provides limitless possibilities, and many research efforts have targeted this field [57,58,59,60,61]. Applications typically supported by FPGAs include digital signal processing (DSPs) [55,63,73,74], digital imaging and computer vision [33,69], cryptography [65,80], bioinformatics [64,76,77], software-defined radios [62,78,79] and software algorithm modeling [1,19,24,25].

#### 2.2 Security Profiles and Classification

As the methods used to secure embedded systems and the intellectual property they contain continue to advance in robustness and complexity, so have the attacks that have been developed to compromise their security. In order to classify the ability of a security system to resist these attacks, IBM's security classification strategy, detailed in [2] and defined in [66], is presented.

In this classification strategy, IBM groups attackers into three classes, based on the attacker's ability successfully compromise the security of a design. These classes are outlined as follows:

#### **Class I** – "Clever Outsiders":

Class I attackers are typically well trained, but lack knowledge specific to the system being attacked. These attackers are limited to moderately sophisticated equipment and typically attempt to take advantage of the pre-existing weaknesses the system exhibits. Class I attackers do not have sufficient knowledge or resources to create a weakness in the system.

#### Class II – "Knowledgeable Insiders":

Class II attackers have extensive technical training and experience specific to the system being attacked. These attackers have access to highly sophisticated equipment used to analyze the system. While these attackers may not fully understand the design of each of the systems components, they do have access to the majority of these components for analysis.

#### **Class III** – "Funded Organizations":

Class III attackers are commonly seen as a diverse team of specialists, with each member of this team possessing related skills. When combined, these individual members form a team with the ability to perform in-depth analysis of each of the system's components. These attackers are capable of designing advanced attack strategies which produce weaknesses in the system using sophisticated analysis tools. Attackers in this class are also typically extremely well-funded, and are often times government backed.

Also provided in this security classification is a metric of how resistant a design is to potential attacks. In this metric, security ratings are based on the level of care put into the design of the system being evaluated, as well as the level of resources required to compromise the security of the system. This rating system is outlined as follows:

#### Level – LOW

Security features are in place, but can be compromised with the use of easily obtainable equipment costing no more than \$2,768.

#### Level – MODERATE-LOW

Most inexpensive attacks are withstood. Successful attacks typically require an attacker with some special knowledge and moderately expensive equipment not to exceed \$8,459.

#### Level - MODERATE

Only Level II and III attackers have a chance to successfully compromise the system. Special tools and skills are required, and the total equipment required to produce the attack costs up to, but not exceeding \$84,590.

#### Level - MODERATE - HIGH

Detailed analysis of the system is needed to compromise its security. The equipment required to produce the attack costs up to \$422,950. The attack may also require several Level II attackers with a wide range of skills to launch.

#### Level - HIGH

No known attacks that have the potential to compromise the system exist, and a new attack strategy must be developed. The total cost of supporting the attack may be over 2.77 million dollars<sup>2</sup> and the success of the attack is not guaranteed. Only large heavily funded organizations can support such an attack and are typically associated with government.

Using the security classification strategy outlined in this section it is possible to classify the level of security a system designed to protect an FPGAs configuration provides. Subsequently, the profile of attackers with the potential to succeed in an attack against the system can also be determined.

#### 2.3 FPGA Attack and Protection Strategies

As FPGAs begin to appear as the backbone of many computing systems, the set of applications containing secure information that they support is growing as well. Because most FPGAs are SRAM-based, these attacks, which were previously designed to target embedded systems, can now be used to target not only the memories contained in FPGAs, but the configuration data of

-

<sup>&</sup>lt;sup>2</sup> The monetary values presented were adjusted from the original values presented in [66] based on an inflation rate of 50.38%. This rate was based on the 16 year period starting at January 1<sup>st</sup>, 1991 and ending on January 1<sup>st</sup>, 2007

the device as well. This configuration data is a physical representation of the functionality achieved by the design contained in the FPGA. If an alteration is made to a portion of the configuration data that corresponds to a portion of the design instantiated on the device, the functionality of this design will also be modified. Not only does this provide attackers the ability to modify the contents of an FPGA's on-chip memories, but the operation of the design running on the device as well. The scope of the attacks used against SRAM-based devices is extremely wide, and contains a number of invasive, non-invasive and semi-invasive strategies [17]. The objectives these attacks aim to accomplish include obtaining secure information from the design [70], reverse engineering the design contained in the FPGA's configuration [47], cloning the configuration of the FPGA [44] and simply rendering the executing design inoperable [17]. In Sections 2.3.1 and 2.3.2, attack methodologies used to maliciously extract and modify FPGA configuration data are presented. In addition, neutralization strategies used to prevent these attacks are outlined.

#### 2.3.1 Extracting Secure Information from a FPGA Configuration

A significant number of attacks that attempt to clone or reverse engineer the design contained in the configuration of an FPGA, using semi-invasive and non-invasive methods, exist. The most significant of these attacks include side channel, data extraction and bitstream interception attacks.

#### Side-Channel Attacks

Side-channel attacks are typically considered non-invasive or passive attacks [17]. These attacks typically attempt to obtain information from a cryptosystem by taking advantage of its physical attributes instead of the theoretical weaknesses in the algorithm it employs. The two most prominent physical properties typically targeted by side-channel attacks are timing characteristics and power consumption [67].

Side-channel attacks that target a system's timing characteristics are referred to as timing analysis attacks. These attacks typically take advantage of the fact that many cryptographic algorithms, while secure in the algorithm they employ, do not exhibit consistency throughout their operation. Breaks in timing consistency can stem from conditional branches in the cryptographic algorithm, optimization techniques and caching systems [67]. Timing analysis attacks have been used against cryptographic algorithms such as RSA and DES [68].

A power analysis attack is a form of side-channel attack that typically targets variations in gate-level power consumption. Among the devices which have become a target of these attacks, digital integrated circuits using CMOS technology are among the most prominent [75]. The power analysis attacks, which are typically employed against such devices, include simple (SPA) and differential power analysis (DPA) attacks [67].

To prevent side-channel attacks there are a number of security strategies that can be employed. Increasing measurement noise [81], power signal filtering [82,85] and asynchronous circuits [83,84] are all viable options for protecting a device.

#### **Data Extraction Attacks**

From [70], it can be seen that there are a number of semi-invasive attacks that have been proven successful at actively reading the contents of not only SRAM cells, but also Flash and even registers. As a result, these attacks are directly applicable to most SRAM-based FPGAs. One of the easier of these attacks to perform involves the use of a red laser and a relatively inexpensive microscope. This attack first removes the casing of the chip, and then focuses the laser on the chip's surface using the microscope. Once a map is made of the SRAM locations on the chip, the laser is swept across the mapped portions of the chip's surface and the states of the SRAM cells can then be observed. When observing a particular cell, if the luminosity of the top and bottom portions of the cell are compared, it is possible to determine the state of the cell. When the top portion of the cell is brighter, the state is a '1', and when the bottom portion is brighter, the state

is a'0' [70]. Because most commercial FPGAs are SRAM-based, if an attacker can actively readback the state of a SRAM cell, with enough time, large portions of the chip's configuration could also be determined. This would then provide an attacker a method by which they can clone the design contained on the device.

#### **Bitstream Interception Attacks**

One of the most straightforward attacks used against FPGAs involves intercepting the bitstream used to program the device between the root ROM and the FPGA at power on [44]. Bitstreams used to configure FPGAs contain the physical description of the design being programmed on the device. If an attacker obtains this bitstream, then the entire design contained within the bitstream is compromised unless additional security measures are taken. The most common method of preventing such an attack involves encrypting the bitstream prior to programming the device. The bitstream is encrypted using a secret key which is only known by the encrypting device and the corresponding decryption device used on the FPGA. FPGA vendors typically provide some form of bitstream encryption to help combat such attacks. Xilinx FPGAs use triple DES for the Virtex-II and Virtex-II Pro platforms and AES for the Virtex-4 and Virtex-5 platforms [10,11,12].

#### 2.3.2 Altering FPGA Configurations

This thesis is primarily concerned with attacks with the potential to compromise the integrity of FPGA configurations. These attacks generally tend to be either invasive or semi-invasive. Invasive attacks, or attacks that physically modify the device being attacked, typically render the device inoperable [17].

#### Invasive Attacks on FPGA Configurations

Because invasive attacks suspend the execution of the design running on the device, they can be detected through the use of a challenge-response protocol. This protocol is implemented in the configuration integrity checker presented in this thesis. Preventing said attacks is much more difficult. Invasive attacks can prove successful against microprocessor-based systems because the layout of the system can been easily mapped, and the underlying hardware probed.

The configuration of a modern FPGA can contain millions of bits of configuration data. Thus, for an attacker to successfully probe this configuration data, they must have detailed knowledge of the design instantiated on the device, as well as how the components of this design are mapped to the configuration. Due to the level of complexity involved with probing the configuration of a FPGA, invasive attacks are not often used against these devices. For this reason, the prevention of invasive attacks is outside the scope of this thesis.

#### Semi-Invasive Attacks on FPGA Configurations

Semi-invasive attacks, which have the ability to alter the contents of SRAM-based devices (such as FPGAs), present the greatest threat to the configuration integrity checker outlined in this thesis. These attacks are relatively new to the computing industry and tend to be less expensive than classic invasive attacks, but as easily repeatable as non-invasive attacks. These attacks require the packaging of the chip to be removed, but their application does not damage the chip, as they do not require de-passivation or creating contacts on the chip [17].

Fault injection attacks are a form of semi-invasive attacks. Fault injection attacks can be defined as a method to systematically produce changes in the state of the transistors of which typically make up a larger component in a system. From [17,69] it can be seen that there exist inexpensive and effective methods to induce changes in transistor state so precise that the state of individual SRAM memory cells can be altered. As a result, an attacker employing such a strategy

has the ability to maliciously modify the configuration of an SRAM-based FPGA on a bit-by-bit basis. This attack could potentially compromise the configuration integrity checker presented in this thesis if the right approach is taken. If the goal of an attacker was simply to induce unintended behavior in the system, this attack could find great success. However, if the aim of the attacker were to manipulate bits of the FPGAs configuration to determine information about the system, they would most likely not have success. In order for such an attack to prove successful, the attacker would need to have extensive knowledge of, not only the composition of FPGA bitstreams, but also of the SRAM cells used in the FPGAs design. Such an attacker would require a detailed layout of how the attacked design was mapped and routed for the device being used as well.

#### 2.4 Software Portability

As the number of systems that utilize FPGAs continues to increase, so does the number of software platforms that must be supported by the applications used in their development. With modern FPGAs beginning to become third, fourth and even fifth generation devices, the range of FPGA devices and families that must be supported by this software is rapidly increasing as well. Today, software designers must then produce solutions that are not only correct in functionality, but that support a wide array of software platforms and FPGA devices used in today's modern designs. In Sections 2.4.1 and 2.4.2, previous work in promoting software portability across various software platforms and hardware devices is described.

#### 2.4.1 Software Platform Portability

In today's configurable computing industry, system designers require new software to support platforms such as Microsoft Windows, Mac OS X, common flavors of Linux such as Red Hat and Debian, as well as other UNIX based systems. Software used in FPGA development such as JBits [52], the Xilinx XST [56] and Altera Quartus toolkits [90], ADB [48] and PARBIT [49] have all begun to provide software solutions capable of running on these platforms. While the

approach taken to providing this portability is not uniform across the FPGA software design industry, there are a few common methods used when developing said software.

#### Java Based GUIs and APIs

Applications such as JBits [52] and ADB [48] were designed as Java APIs to take advantage of the native portability Java provides. This approach defines a set of platform independent function calls that can be used by a software designer to perform specific tasks. This is the easiest approach to ensuring a high level of portability, as back end applications written in Java are compatible on almost every platform. GUI applications written in Java, such as some of the accessory application front ends provided in the Xilinx XST [56] and Altera Quartus [90] tool kits, are not as portable by nature. While still relatively portable across multiple platforms, applications designers face the choice of using either the 1.1 or 1.2 versions of the Java Development Kit. The 1.1 version is rather poorly designed but boasts great portability, while the 1.2 version contains a superior toolkit and greater capabilities, but at the cost of some portability loss.

#### C / C++ Based Applications

A common software approach to ensuring portability utilizes the native C and C++ programming languages, as well as additional standard C/C++ libraries, to develop powerful backend applications. Applications such as PARBIT [49] and the back ends of the Xilinx XST [56] and Altera Quartus [90] tool kits utilize this approach. The core C programming language and the standard C libraries themselves are extremely portable. Typically, it is up to the programmer, however, to manage the function calls used to ensure that the application will be supported by compilers across multiple platforms. The portability limitations of this approach begin to become apparent when inter-process communication and multi-threading are done. C++ features such as templates, standard I/O libraries and exception handling are also typically not well supported across multiple platforms [91].

#### Scripting Languages

Scripting languages have reasonably good portability, but are not as strong as Java or C. Perl offers good portability and provides programmers a set of bindings to the Tk toolkit that supports portable GUIs across Unix, Mac OS X and Windows [92]. As a downside, some Perl scripts require add-on libraries that may not be included in standard distributions of many platforms. An example application that uses Perl scripts can be seen in the database creation functionality of the ADB [48] application.

Shell scripting, however, does not provide a high level or portability. The bash shell has become standard across many platforms, and native shell commands are widely supported. Problems arise however when shell scripts make use of other auxiliary commands which may not be standard on many platforms.

The approach used in developing the automated dynamic data mapping method presented in this thesis uses C applications controlled by standard shell scripts. The shell script implemented ensures portability through the use native bash shell commands and calls to auxiliary lightweight C applications.

#### 2.4.2 Extending Software Tools Across Multiple FPGA Devices and Families

Many software applications used in the FPGA design process require advanced knowledge of the make up of the FPGAs for which they are used. Applications such as JBits [52] and ADB [48] rely on determining proprietary information about the bitstream makeup used to program Xilinx FPGAs. Determining this information for new devices within a family is a reasonable task, however producing this information across multiple FPGA platforms can prove to be very challenging. Typically, applications such as these provide native support for the most current FPGAs on the market at the time of their deployment, and leave future platforms generally unsupported. It is for this reason that it becomes very challenging to utilize the advanced features of modern FPGAs in conjunction with popular third party FPGA design tools that only support

previous generations of the hardware. Because the interworkings of most FPGAs are kept proprietary, and updates to third-party FPGA related software are infrequent at best, system designers are commonly left to rely on software provided by FPGA vendors to support designs implemented on next generation devices. This not only discourages future third-party FPGA related software development, but allows vendors to control the power of new FPGA designs by selecting which subsets of configuration information they wish to make public.

#### 2.5 FPGA Configuration Integrity Checking

While there has not been an enormous amount of research done in the area of FPGA configuration security, there has been work done in single-event upset (SEU) detection and recovery, as well as configuration integrity checking on the Xilinx Virtex 4 platform.

#### 2.5.1 SEU Discovery and Repair

When used in space and high altitude applications, SRAM based devices, such as FPGAs, are susceptible to small faults that may alter their configuration. These faults are commonly referred to as single-event upsets, or SEUs. SEUs are typically radiation-induced and are seen in both low earth orbit and in the presence of solar flares [89].

In order to detect and recover from an SEU, an approach was developed in [87] that actively monitors the configuration of an FPGA through the use of a cyclic redundancy check (CRC) computation. This computation was performed on frame-by-frame basis for the entire configuration of the device that was read back. If the resulting CRC value of a frame was different, it was known that an SEU had occurred and effected this portion of the devices configuration. After the detection of such an event, the system utilized RTR to correct the alteration. Most modern FPGAs can withstand exposure to large amounts of radiation without being subjected to an SEU [89]. However, for high-reliability applications, Xilinx has provided its own SEU discovery and repair module [88]. This module operates in a similar fashion to the

system described in [87], and has the capability to correct SEUs. Altera's SEU detection and repair strategy is present on all Stratix and Cyclone FPGAs. This approach provides built-in dedicated circuitry to check the FPGAs configuration for SEUs. While these strategies can successfully detect SEUs on SRAM based FPGAs, they cannot, however, detect and recover from malicious semi-invasive fault injection attacks [2]. This shortcoming forms the basis for which the configuration integrity checking solution presented in this thesis was founded upon.

#### 2.5.2 Configuration Integrity Checking on the Virtex 4 Platform

In [2], a system capable of securing FPGA configurations against such semi-invasive attacks on the Xilinx Virtex 4 platform is presented. The core of this system is defined to include the readback controller, hash generator, hash comparator and challenge-response components of the system. For the remainder of this thesis, this core will be referred to as the Platform Dependent Configuration Integrity Checker, or PDCIC. A significant portion of the work presented in this thesis serves to extend the components of the PDCIC core across multiple platforms. These extended components combined with a platform independent dynamic data masking controller form the multi-platform configuration integrity checker presented in this thesis.

#### Dynamic Data Identification

When designing a system that can actively detect when a malicious alteration to an FPGA configuration has occurred, the configuration data of the FPGA must be continuously monitored for malicious changes. This is typically achieved through the use of active read back via the FPGA's internal configuration access port (ICAP). In order to effectively produce a static readback configuration, the dynamic data located in the FPGA's configuration bitstream being read back must be masked out. The static readback configuration is then analyzed to determine if a malicious attack was being performed. The process by which this dynamic data was identified and removed is the basis for the automated, platform independent solution presented in this thesis.

#### CLB Block Hash Generation and Comparator

If readback configuration data is being accurately masked for dynamic data, it is possible to generate checksums which represent segments of the data. These checksums can then be used to determine exactly when and what specific portion of an FPGA has been maliciously attacked. The MD5 hashing algorithm, used by the PDCIC to generate these checksums, was also used in the platform independent integrity checker presented in this thesis. This hashing algorithm is typically used to produce a unique, fixed-length representation of a message of arbitrary length. The implementation of the algorithm used was obtained from [15]. The method by which the hashes produced by the MD5 algorithm were generated, stored and compared also form the foundation for the methods used in the multi-platform version.

#### Providing Assurance of Correct Operation

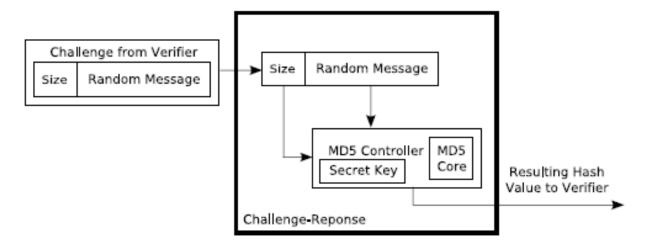

The PDCIC employs a classic challenge-response subsystem for providing an entity external to the FPGA, a method by which the health of the security system can be polled. There are many ways that this protocol can be implemented [21], however, the particular design that was used was obtained from [2]. This challenge-response system, which acts as the claimant, accepts an arbitrary length challenge from the verifier and responds by returning a hash of a secret key concatenated with the original message to the user. While the structure of this challenge-response system was significantly altered in the multi-platform version of the configuration integrity checker presented in this thesis, its general concept and framework were used as a foundation for the design of the new subsystem.

## 2.6 Applications That Can Benefit From Configuration Integrity Checking

There has been a significant amount of work done to secure user and system IP contained in embedded systems on FPGA platforms. The majority of the system design in this area focuses on protecting embedded systems containing a processor core as the central point of the protected design. In [40], a FPGA based network processor is presented that takes advantage of RTR to provide both user based operation and concealment of the intellectual property (IP) contained in a users design. This functionality is achieved through the use of a modular approach to the design of the processor core. When a valid user of the system is not present, the design can effectively remove user IP from the device, preventing malicious reverse engineering of the design. A system presented in [41] implements a key management system instantiated on an FPGA that can provide secure user sessions. This design can effectively prevent an outsider from discovering the implementation details of an embedded application or CPU that is being protected.

These designs have successfully secured user and system IP on several FPGA platforms. Many non-invasive attacks that were commonly used against embedded processing systems can now be neutralized by the security strategies they employ. Unfortunately, the level of security these systems proved does not protect against invasive and semi-invasive attacks against an FPGAs configuration. If a configuration integrity checking strategy was utilized as an auxiliary method for protecting the integrity of these systems, great success in providing resistance against such attacks could be seen. Due to the disparity in the FPGA platforms such security systems are implemented on, a multi-platform integrity checking solution would be needed to realize such an auxiliary security solution. The cross-platform FPGA configuration integrity checking solution presented in this thesis provides a solution that satisfies both these requirements.

## Chapter 3

# Method for Securing FPGA Configurations on the Virtex 4 Platform

This chapter outlines the design and implementation of the platform dependent configuration integrity checking core (PDCIC) presented in [2]. In this chapter, the configuration readback controller, hash generator/comparator and challenge-response components in this core are outlined. These components are later extended to support the design of the cross-platform integrity checker presented in this thesis. This chapter is intended to provide insight into the origins of the multi-platform configuration integrity checker's design outlined in Chapter 4.

#### 3.1 FPGA Configuration Readback Control

The FPGA configuration data, which must be monitored for malicious modifications, is obtained using active readback from the FPGAs internal configuration access port (ICAP). The ICAP module provided by the FPGA manufacturer (in this case Xilinx) provides an interface to the

FPGA's internal status and configuration registers [10,11,14]. To begin active readback of the FPGA's configuration, several commands needed to be written to a number of different configuration registers. These commands specify the parameters of the data that is to be read back. These readback initiation commands correspond to commands 0 though 19 in Table 3.1. Once written, the ICAP will begin to clock out the internal configuration data of the FPGA starting at the address written to the frame address register (FAR) in command 17. The ICAP will then proceed to read back the number of bytes specified by the write to the FDRO register in command 19. Once all the desired configuration data has been read back, the ICAP is shutdown though the use of commands 20 through 25 outlined in Table 3.1.

|               | Command Index | Command Description                             | Command Value |

|---------------|---------------|-------------------------------------------------|---------------|

| Startup ICAP  | command[0]    | Synchronize the ICAP                            | 0xAA_99_55_66 |

|               | command[1]    | No Operation                                    | 0x20_00_00_00 |

|               | command[2]    | Write 1 word to Command Register                | 0x30_00_80_01 |

|               | command[3]    | Write RCRC Command To Command Register          | 0x00_00_00_07 |

|               | command[4]    | No Operation                                    | 0x20_00_00_00 |

|               | command[5]    | No Operation                                    | 0x20_00_00_00 |

|               | command[6]    | No Operation                                    | 0x20_00_00_00 |

|               | command[7]    | No Operation                                    | 0x20_00_00_00 |

|               | command[8]    | No Operation                                    | 0x20_00_00_00 |

|               | command[9]    | No Operation                                    | 0x20_00_00_00 |

|               | command[10]   | No Operation                                    | 0x20_00_00_00 |

|               | command[11]   | No Operation                                    | 0x20_00_00_00 |

|               | command[12]   | No Operation                                    | 0x20_00_00_00 |

|               | command[13]   | No Operation                                    | 0x20_00_00_00 |

|               | command[14]   | Write 1 word to Command Register                | 0x30_00_80_01 |

|               | command[15]   | Write RCFT Command to Command Register          | 0x00_00_00_04 |

|               | command[16]   | Write 1 word to the Frame Address Register      | 0x30_00_20_01 |

|               | command[17]   | Write Type 2 Frame Start Address                | 0x00_00_00_00 |

|               | command[18]   | Read From FDRO Register                         | 0x28_00_60_00 |

|               | command[19]   | Read N Words From FDRO Register                 | 0x48_02_B5_7A |

| Shutdown ICAP | command[20]   | No Operation                                    | 0x20_00_00_00 |

|               | command[21]   | No Operation                                    | 0x20_00_00_00 |

|               | command[22]   | No Operation                                    | 0x20_00_00_00 |

|               | command[23]   | Write 1 word to Command Register                | 0x30_00_80_01 |

|               | command[24]   | Write RCRC Command To Command Register          | 0x00_00_00_07 |

|               | command[25]   | Write 1 word to Command Register                | 0x30_00_80_01 |

|               | command[26]   | Write Desynchronize command to Command Register | 0x00_00_00_0D |

|               | command[27]   | No Operation                                    | 0x20_00_00_00 |

|               | command[28]   | No Operation                                    | 0x20_00_00_00 |

Table 3.1: Readback commands used to startup and shutdown the Virtex 4 ICAP

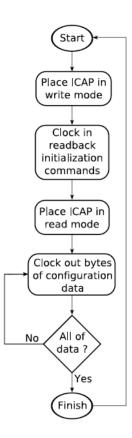

A finite state machine (FSM) was designed to write the commands shown in Table 3.1, one byte at a time, to the ICAPs input data port. This FSM also is used to process the readback configuration data output by the ICAP on its output data port. The layout of the internal registers written to / read from by these commands can be found in [11]. The operation of this FSM is outlined in Figure 3.1, which was described in [2].

Figure 3.1: Outline of the FSM used to read to / write from the ICAP on the Virtex 4 platform [2].

## 3.2 Detection of Malicious Configuration Modifications

The strategy employed by the PDCIC for detecting when and where a malicious attack on the FPGA's configuration has occurred involves continuously computing hash values on blocks of configuration data. As these hash values are computed, they are compared against "trusted" hash values for the same blocks of configuration data which are known to represent the unaltered configuration of the device. Any difference between the two hash values would represent a maliciously altered portion of the FPGA's configuration data. To compute these hashes values, first a hash function needed to be selected. This hash function must not only provide sufficient latency and resource utilization characteristics, but excellent resistance against brute force and design-based attacks.

#### 3.2.1 MD5 Hashing Algorithm

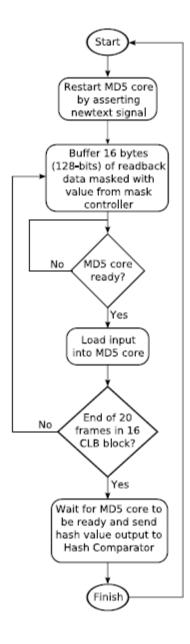

The hash algorithm selected for the PDCIC is the MD5 hash computation algorithm. Typically, the MD5 hash algorithm takes an input message of arbitrary length (in 512 bit chunks of data) and produces a fixed length (128 bits in the PDCIC) unique representation of that message. The characteristics one would look for in selecting such an algorithm are speed of computation, low resource requirements and the level of security provided by the algorithm. For hashing algorithms, there are two main security related properties which are desirable. The first is the algorithm's "one-wayness" [21]. The second, and in relation to the security of the components in the PDCIC being the most important, is the ability of the hash function to minimize collisions [20]. A collision is defined to be two distinct sets of input messages that produce the same hash value as a result. The MD5 algorithm exhibits both of these properties, and because it also demonstrates sufficient slice utilization and computation latency characteristics, it was chosen for this design [2]. The MD5 module used in the PDCIC was obtained from [15]. Its operation was controlled by a FSM, whose operation is outlined in Figure 3.2, described in [2].

Figure 3.2: MD5 hash function finite state machine outline [2]

#### 3.2.2 Hash Value Granularity Considerations

When considering the granularity at which hash values should be computed, there are several factors that must be considered. These factors include, but are not limited to, the precision of the locality of the attack that can be detected, the overhead of the hash computation algorithm which is incurred and amount of memory consumed by the system.

The smallest granularity that could be selected on the Virtex 4 platform would be an nlength partition of the readback bitstream, where n is the minimum size of an input message to the MD5 hashing algorithm (512 bits in this case) [15]. Choosing such a small granularity would allow one to precisely determine the area(s) of the FPGA's configuration that were modified, as well as provide fast configuration restoration times. The price a system designer would pay for choosing such small granularity size would be the huge overhead from hash computations that would be incurred. If this granularity were set at one hash per readback configuration frame, this would also result in a very large memory requirement. On the LX25 device, the readback configuration bitstream contains 6256 frames. As a result, all 6256 of the corresponding 128-bit trusted hash values for these frames would have to be stored in memory. Conversely, choosing the largest possible granularity size would result in one hash value that would represent the entire CLB section of the readback bitstream. Such a granularity would minimize the overhead of hash computations and reduce the amount of memory needed to store the resulting hash values. Unfortunately, it would also make run-time repair of the malicious alterations difficult to perform. This is because the entire FPGA would have to be reconfigured to correct malicious alterations, even if they are as small as a few bits. A granularity this large would also make it difficult to determine exactly which portion of the FPGA is being attacked. This would prevent the systems designer from making design alterations to combat attacks that are being employed. To achieve a middle ground, the the PDCIC set the granularity at a block of 20 frames for the Virtex 4 platform. This corresponds to 1 block of 16 CLBs per hash, resulting in 168 hashes being used to represent the entire CLB configuration.

#### **3.2.3** Attack Locality Determination

When a malicious alteration of the FPGA's configuration is detected by the hash comparator of the PDCIC, the number of the hash containing altered configuration data is output. In order to identify the location relative to layout of the FPGA which was attacked, it is necessary to understand how the hash values produced correspond to physical portions of the FPGA. From Figure B.4, it can be seen that frame addresses increase from left to right and bottom to top on the FPGA. As a result, frames are readback starting at the lower left corner of the FPGA and ending in the upper right corner. It would then follow that the index of resulting hash values would increase in the same manner. The layout of the physical dimensions of the chip, in proportion to hash value indices, is outlined in Figure B.5.

## 3.3 Ensuring Reliable Operation

An attacker with the ability to maliciously alter the configuration data of an FPGA can potentially disrupt the operation of the PDCICs components, and thereby leave the configuration of the FPGA and any design it contains exposed. Thus, a method was put in place that allows an entity external to the FPGA to poll the health of the configuration integrity checker. The method selected was a classic challenge response subsystem. In the challenge-response component of the PDCIC, a challenge is issued from an external entity containing an input message of arbitrary length prepended with the length of the message. This message is then concatenated with a secret key to which only the entity issuing the challenge and the challenge-response subsystem have access. The message formed by this concatenation is then processed by the MD5 hash function, and its result returned in the form of a response to the challenger. In the PDCIC, the secret key used by the challenge-response subsystem was selected to be a hash of all 168 current hash values. This requires the PDCIC to store 168 128-bit words in the form of the current hash values. In addition, the 168 trusted hash values are also stored. Storing both the current and trusted hash values not only provides the challenger the ability to poll the systems health, but also allows this external entity to determine if the current FPGA configuration has been altered.

This is possible because the secret key used in forming the response is a hash of the 168 current hash values. Any divergence between these values and the trusted hash values would result in a different secret key being produced. This would then result in a different response, which is received by the challenger. An outline of this system can be seen in Figure 3.3, which was taken from [2].

Figure 3.3: Challenge response subsystem architecture

## 3.4 Coverage of Future Work

In [2], several areas of potential future work to improve the design of the PDCIC were outlined. These areas include improving upon the initial conditions the system is dependent upon, increasing the frequency at which the system operates, and increasing portability/parameterizability of the system. The work presented in this thesis focuses primarily on increasing the portability and parameterizability of the components that were inherited from the PDCIC. However, adjustments to conditional stipulations put on portions of the design, such as the challenge-response subsystem, were addressed as well.

# **Chapter 4**

# Multi-Platform Configuration Integrity Checker Design and Implementation

This chapter describes the design methodologies used in developing the components of the cross-platform configuration integrity checker presented in this thesis. First, the dynamic data identification and masking strategy is outlined. The methodology for automating this process and extending it across multiple FPGA platforms is then presented. Next, the approach used to extending the configuration readback, hash generation/comparison and challenge-response components of the design, outlined in [2], across multiple platforms is described. The chapter is concluded with a discussion of the design and implementation of the serial I/O subsystem employed by the cross-platform integrity checker.

## 4.1 Dynamic Data Identification and Masking

As with any hardware design, a design running on an FPGA contains two parts, a static portion and a dynamic portion. The dynamic portion of a design contains values that are constantly changing according to the operation of the static portion of the design. As a result, this dynamic

portion of the design must not be considered when checking the design's readback configuration for malicious alterations. If these dynamic portions of the configuration are considered, upon detection of a change in the design's configuration, it would be extremely difficult to determine the source of the alteration. Moreover, it would then be impossible to tell if the configuration of the design changed due to these dynamic components or due to a malicious attack. Once these dynamic portions of a design are masked from the configuration data being monitored for malicious attacks, one can reliably determine when a design's configuration data has been maliciously altered.

#### 4.1.1 Dynamic Data Identification Strategy

To determine where dynamic data is located in the configuration bitstream of a Xilinx FPGA, an approach was developed which takes advantage of Xilinx logic allocation (.ll) files. These logic allocation files can be generated using the Xilinx Bitgen software (with the "-l" option specified) [56]. This software is typically used to take a user's design that has been synthesized, mapped, and routed, and generate a bitfile (.bit), which can be used to configure the target FPGA with the user's design [56]. Logic allocation files provide the frame address and bitstream offsets of all data that is considered to be dynamic in FPGA bitstreams. As a result, they are a critical component in the dynamic data identification strategy outlined.

In the method developed, a design was created which occupies one column of combinational logic blocks (CLBs) on the FPGA being mapped for dynamic data. This design was developed in such a way as to occupy all flip-flop resources in this CLB column. Because these resources are utilized, their relative locations, and therefore the locations of all dynamic data in this column, will be displayed in the resulting logic allocation file. This provides the information necessary to appropriately mask out all possible dynamic data locations in this column of CLBs. It should be noted that not all flip-flops in every column are utilized as dynamic data in every design, resulting in small static portions of the configuration that are not included in hash computations. When these flip-flop locations are left unutilized, it typically

means that they are not a part of the design being implemented, and therefore it is a valid assumption that leaving them unprotected by the configuration integrity checker does not present a security threat to the system.

In this strategy it is assumed that LUTs in the column be analyzed are not configured to act as RAM modules. If this assumption were not present, the bitstream locations of the dynamic data in these modules would need to be determined as well. This would be advantageous if a dynamic data masking strategy custom to a particular design was being developed. However, it is not advantageous to mask every possible location of this data in the design-independent version of the dynamic data masking strategy. Even if LUTs contained in each CLB column had not been configured as portions of a RAM module, they would still be masked using this approach. This would result in large static portions of the FPGAs configuration that are not included in the hash value computation for each block of hash data. Because this data is not considered in these computations, these static portions of the design contained in the configuration would be left unprotected from malicious attacks.

After the location of all dynamic data in this particular column was determined, the design was iteratively constrained to occupy each CLB column on the FPGA being mapped. The resulting absolute frame addresses, as well as relative (to the frame being addressed) bitstream offsets were copied from the generated logic allocation file for each column. The frame addresses, which correspond to locations of the dynamic data in each CLB column, are by default in the Xilinx specific format used to read and write to/from the FPGA's frame address register. An example of this format for the Xilinx Virtex 4 family is shown in Figure 4.1.

| Address<br>Type | Top / Bottom<br>Bit | Block Type |    |    | Row Address |    |    |    |    | Column Address |    |    |    |   |   |   | Minor Address |   |   |   |   |   |   |

|-----------------|---------------------|------------|----|----|-------------|----|----|----|----|----------------|----|----|----|---|---|---|---------------|---|---|---|---|---|---|

| Bit Index       | 22                  | 21         | 20 | 19 | 18          | 17 | 16 | 15 | 14 | 13             | 12 | 11 | 10 | 9 | 8 | 7 | 6             | 5 | 4 | 3 | 2 | 1 | 0 |

Figure 4.1: Virtex 4 frame address description

The frame address and bitstream offsets obtained from the method outlined in Section 4.1.1 were then be converted to frame addresses relative to configuration bitstream that is read back from the FPGA's ICAP. The conversion method performed is outlined in Equation 4.1. This conversion process was automated using lightweight software. A detailed description of this automation process is contained in Section 4.2.2. An example of both the Xilinx formatted frame addresses and resulting relative frame addresses for the LX25 device on the Virtex 4 platform can be seen in Figures B.1 and B.2, respectively.

Absolute Frame Offset =

$$\frac{(Absolute\ Bitstream\ Offset-Frame\ Relative\ Bit\ Offset)}{(Words\ per\ frame\ \cdot Bits\ per\ word)} \quad (4.1)$$

Once all the relative frame addresses that contain dynamic data were obtained, all that was needed to be done was to find the bit locations inside these frames that corresponded to bits of dynamic data that must be masked out. These bits are provided in the logic allocation file, and form regular patterns inside frames that contain dynamic data. These patterns are uniform inside each platform, and only differ in length for platforms such as the Virtex II and II Pro platforms that do not have uniform frame lengths. To demonstrate the difference in bit patterns across multiple platforms, examples of these bits that must be masked for both the Virtex II XC2VP30 and Virtex 4 LX25 devices can be seen in Figures A.2 and B.3, respectively.

After all frame addresses relative to the FPGAs readback configuration bitstream were determined, a FSM was created to mask the corresponding data. This FSM systematically determined when data that was being read back belongs to a frame that must be masked. If needed, this dynamic data was then selectively masked from the configuration data that was being read back before being used in hash value computation.

#### **4.1.2** Memory Considerations

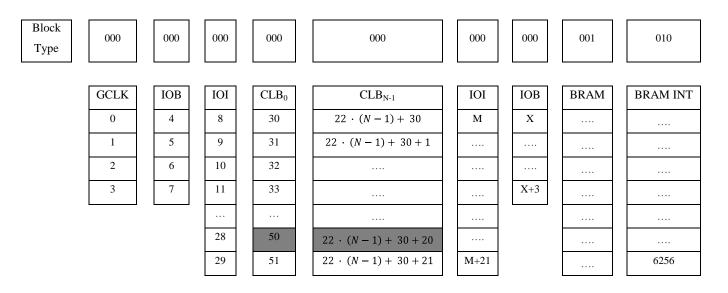

From a configuration standpoint, the FPGA is divided into three major sections: (1) clock / IO / CLB data, (2) BRAM data, and (3) BRAM interconnect. From the Xilinx frame address

description in Figure 4.1, it can be seen that a frame is the smallest addressable segment in the device. This is true for all devices in all Xilinx FPGA families. Frames are arranged into block types, row addresses, column addresses and minor addresses. Block types correspond to type of data that is stored in the corresponding frames they address. As one would expect, block types are arranged into the three major categories previously mentioned, with the assigned addresses shown in Figure 4.2.

| Block Type            | Assigned Address |

|-----------------------|------------------|

| Clock / IO / CLB data | 000              |

| BRAM data             | 001              |

| BRAM interconnect     | 010              |

Figure 4.2: Xilinx block type layout