# Quantitative Metrics and Measurement Methodologies for System Security Assurance

#### Salman Ahmed

Dissertation submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in

Computer Science and Applications

Danfeng (Daphne) Yao, Chair

Matthew Hicks

Gang Wang

Patrick R. Schaumont

Fabian Monrose

December 9, 2021 Blacksburg, Virginia

Keywords: Security Measurement, Attack Surface Quantification, Metrics, Methodologies,

Attack Vectors, Data Pointers, Taint Analysis, LLVM, ROP, JITROP, Data-Oriented

Attacks, Gadgets, ASLR, Pointer Authentication, Memory Tagging

Copyright 2021, Salman Ahmed

# Quantitative Metrics and Measurement Methodologies for System Security Assurance

Salman Ahmed

(ABSTRACT)

Proactive approaches for preventing attacks through security measurements are crucial for preventing sophisticated attacks. However, proactive measures must employ qualitative security metrics and systemic measurement methodologies to assess security guarantees, as some metrics (e.g., entropy) used for evaluating security guarantees may not capture the capabilities of advanced attackers. Also, many proactive measures (e.g., data pointer protection or data flow integrity) suffer performance bottlenecks. This dissertation identifies and represents attack vectors as metrics using the knowledge from advanced exploits and demonstrates the effectiveness of the metrics by quantifying attack surface and enabling ways to tune performance vs. security of existing defenses by identifying and prioritizing key attack vectors for protection. We measure attack surface by quantifying the impact of fine-grained Address Space Layout Randomization (ASLR) on code reuse attacks under the Just-In-Time Return-Oriented Programming (JITROP) threat model. We conduct a comprehensive measurement study with five fine-grained ASLR tools, 20 applications including six browsers, one browser engine, and 25 dynamic libraries. Experiments show that attackers only need several seconds (1.5-3.5) to find various code reuse gadgets such as the Turing Complete gadget set. Experiments also suggest that some code pointer leaks allow attackers to find gadgets more quickly than others. Besides, the instruction-level single-round randomization can restrict Turing Complete operations by preventing up to 90% of gadgets. This dissertation also identifies and prioritizes critical data pointers for protection to enable the capability to tune between performance vs. security. We apply seven rule-based heuristics to prioritize externally manipulatable sensitive data objects/pointers. Our evaluations using 33 ground truths vulnerable data objects/pointers show the successful detection of 32 ground truths with a 42% performance overhead reduction compared to AddressSanitizer. Our results also suggest that sensitive data objects are as low as 3%, and on average, 82% of data objects do not need protection for real-world applications.

# Quantitative Metrics and Measurement Methodologies for System Security Assurance

#### Salman Ahmed

#### (GENERAL AUDIENCE ABSTRACT)

Proactive approaches for preventing attacks through security measurements are crucial to prevent advanced attacks because reactive measures can become challenging, especially when attackers enter sophisticated attack phases. A key challenge for the proactive measures is the identification of representative metrics and measurement methodologies to assess security guarantees, as some metrics used for evaluating security guarantees may not capture the capabilities of advanced attackers. Also, many proactive measures suffer performance bottlenecks. This dissertation identifies and represents attack elements as metrics using the knowledge from advanced exploits and demonstrates the effectiveness of the metrics by quantifying attack surface and enabling the capability to tune performance vs. security of existing defenses by identifying and prioritizing key attack elements. We measure the attack surface of various software applications by quantifying the available attack elements of code reuse attacks in the presence of fine-grained Address Space Layout Randomization (ASLR), a defense in modern operating systems. ASLR makes code reuse attacks difficult by making the attack components unavailable. We perform a comprehensive measurement study with five fine-grained ASLR tools, real-world applications, and libraries under an influential code reuse attack model. Experiments show that attackers only need several seconds (1.5-3.5) to find various code reuse elements. Results also show the influence of one attack element over another and one defense strategy over another strategy. This dissertation also applies seven rule-based heuristics to prioritize externally manipulatable sensitive data objects/pointers – a type of attack element – to enable the capability to tune between performance vs. security. Our evaluations using 33 ground truths vulnerable data objects/pointers show the successful identification of 32 ground truths with a 42% performance overhead reduction compared to AddressSanitizer, a memory error detector. Our results also suggest that sensitive data objects are as low as 3% of all objects, and on average, 82% of objects do not need protection for real-world applications.

## **Dedication**

To my wife (Nasrin Sultana), who sacrificed most and inspired me all the time to get through each step of the most challenging journey of my life and gave me a precious gift during this journey, our son, Nazhan Ahmed.

To my parents (Akbar Ali and Jabeda Begum) for their all-time unyielding support, love, and encouragement.

## **Acknowledgments**

I am forever grateful to my parents for their continuous support and encouragement for my education. Being in a society where sons tend to support their families right after the bachelor's degree, my parents never asked me for that support. They always encouraged me to move forward and pursue my passion, no matter how bad the situation was for them. This journey would not have been possible without their support and encouragement.

I want to express my sincere gratitude to my Ph.D. advisor Dr. Danfeng (Daphne) Yao, for believing me and guiding me throughout my Ph.D. study with her continuous support and extraordinary patience. Her prompt and timely suggestions have enabled me to complete this dissertation on time. Her support went beyond academic settings. She trained me not only how to do research but also how to make myself fit for the next chapter of my life from scratch. She taught me to express myself, be professional in valuing other people and their work, and prioritize my goals. My sincerest thanks to my committee members, who have encouraged me and helped pave the pathway. Thanks to Dr. Matthew Hicks, Dr. Gang Wang, Dr. Patrick R. Schaumont, and Dr. Fabian Monrose for serving in my Ph.D. committee and guiding me over the years. Their insights, feedback, and advice were influential and essential for shaping the dissertation.

I would also like to thank all my mentors, collaborators, and fellow labmates, including Dr. Gang Tan, Dr. Kevin Snow, Dr. Long Chen, Dr. Sazzadur Rahaman, Dr. Hans Liljestrand, Dr. Haipeng Cai, Dr. Trent Jaeger, Dr. N. Asokan, Dr. Michael Le, Dr. Dan Williams, Dr. Hani Jamjoom, Dr. Xiaodong Yu, Ya Xiao, Sharmin Afrose, Miles Frantz, Wenjia Song, Tanmoy Sarkar Pias, Jingyuan Qi, and Wyatt Sweat.

Finally, my special thanks to my wife, Nasrin Sultana, who encouraged, inspired, and pushed me towards my goals with her selfless sacrifices.

**Funding Acknowledgment:** The work in this dissertation was supported in part by the National Science Foundation under grant No. CNS-1838271, Grant No. CNS- 1929701, Grants OAC-1541105, and CNS-1801534, and by the Office of Naval Research under Grant ONR-N00014-17-1-2498.

**Declaration of Collaboration:** In addition to my advisor Danfeng (Daphne) Yao, the research presented in this dissertation benefited from several collaborators:

- Ya Xiao (VT), Gang Tan (PSU), Kevin Snow (ZeroPoint Dynamics), and Fabian Monrose (UNC) contributed to the work included in Chapter 3.

- Long Chen (ClemsonU), Hans Liljestrand (UW), Thomas Nyman (Aalto University), Haipeng Cai (WSU), Trent Jaeger (PSU), and N. Asokan (UW) contributed to the work in Chapter 4.

- Hans Liljestrand (UW) and N. Asokan (UW) contributed to the work included in Chapter 5.

## **List of Publications From This Thesis**

- [ACM TOPS'21] Long Cheng, Salman Ahmed, Hans Liljestrand, Thomas Nyman, Haipeng Cai, Trent Jaeger, N. Asokan, and Danfeng (Daphne) Yao. 2021. Exploitation Techniques for Data-oriented Attacks with Existing and Potential Defense Approaches. ACM Trans. Priv. Secur. 24, 4, Article 26 (November 2021), 36 pages. DOI:https://doi.org/10.1145/3462699

- [ACM CCS'20] Salman Ahmed, Ya Xiao, Kevin Z. Snow, Gang Tan, Fabian Monrose, and Danfeng (Daphne) Yao. 2020. Methodologies for Quantifying (Re-)randomization Security and Timing under JIT-ROP. In Proceedings of the 2020 ACM SIGSAC Conference on Computer and Communications Security (CCS '20). Association for Computing Machinery, New York, NY, USA, 18031820. DOI:https://doi.org/10.1145/3372297.3417248

- [IEEE SecDev'19] Long Cheng, Hans Liljestrand, Salman Ahmed, Thomas Nyman, Trent Jaeger, N. Asokan, and Danfeng Yao, "Exploitation Techniques and Defenses for Data-Oriented Attacks," 2019 IEEE Cybersecurity Development (SecDev), 2019, pp. 114-128, doi: 10.1109/SecDev.2019.00022.

## **Contents**

| Ll | St of 1        | rigures  |                                               | XII  |  |  |  |  |  |  |

|----|----------------|----------|-----------------------------------------------|------|--|--|--|--|--|--|

| Li | List of Tables |          |                                               |      |  |  |  |  |  |  |

| 1  | Intr           | oductio  | on                                            | 1    |  |  |  |  |  |  |

|    | 1.1            | Proble   | em Definitions                                | . 1  |  |  |  |  |  |  |

|    | 1.2            | Contri   | bution                                        | . 3  |  |  |  |  |  |  |

| 2  | Lite           | rature ] | Review                                        | 9    |  |  |  |  |  |  |

|    | 2.1            | Attack   | xers' and Defenders' Games                    | . 10 |  |  |  |  |  |  |

|    |                | 2.1.1    | Code Injection Attacks and Defenses           | . 10 |  |  |  |  |  |  |

|    |                | 2.1.2    | Code Reuse Attacks and Defenses               | . 11 |  |  |  |  |  |  |

|    |                | 2.1.3    | Control-Flow Integrity                        | . 17 |  |  |  |  |  |  |

|    |                | 2.1.4    | Powerful and Influential Attacks              | . 18 |  |  |  |  |  |  |

|    | 2.2            | Data-0   | Oriented Attacks                              | . 20 |  |  |  |  |  |  |

|    | 2.3            | Techni   | iques for Protecting Object/Pointer Integrity | . 21 |  |  |  |  |  |  |

|    |                | 2.3.1    | Pointer Integrity                             | . 21 |  |  |  |  |  |  |

|    |                | 2.3.2    | Pointer Authentication (PA)                   | . 22 |  |  |  |  |  |  |

|    |                | 2.3.3    | Memory Safety Defenses                        | . 23 |  |  |  |  |  |  |

|    |                | 2.3.4    | Hardware-based Defenses                       | . 24 |  |  |  |  |  |  |

|   | 2.4 | Sensiti  | ve/Critical Data Protection               | 25 |

|---|-----|----------|-------------------------------------------|----|

| 3 | Qua | ntifying | g (Re-)Randomization Security and Timing  | 26 |

|   | 3.1 | Introdu  | action                                    | 26 |

|   | 3.2 | Threat   | Model and Definitions                     | 29 |

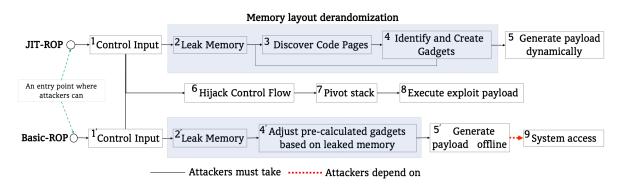

|   | 3.3 | JIT-RO   | OP vs. Basic ROP Attacks                  | 33 |

|   |     | 3.3.1    | Memory Layout Derandomization             | 34 |

|   |     | 3.3.2    | System Access                             | 36 |

|   |     | 3.3.3    | Payload Generation                        | 36 |

|   | 3.4 | Measu    | rement Methodologies                      | 37 |

|   |     | 3.4.1    | Methodology for Derandomization           | 38 |

|   |     | 3.4.2    | Methodology for System Access             | 42 |

|   |     | 3.4.3    | Methodology for Payload Generation        | 42 |

|   | 3.5 | Evalua   | ation Results and Insights                | 46 |

|   |     | 3.5.1    | Re-randomization Upper Bound              | 47 |

|   |     | 3.5.2    | Impact of the Location of Pointer Leakage | 51 |

|   |     | 3.5.3    | Impact on the Availability of Gadgets     | 54 |

|   |     | 3.5.4    | Impact on Performance Overhead            | 56 |

|   |     | 3.5.5    | Impact on the Quality of a Gadget Chain   | 57 |

|   |     | 3.5.6    | Availability of Libc Pointers             | 58 |

|   | 3.6 | Discus   | sion                                      | 60 |

|   | 2 7 | Dalata   | d Worls                                   | 62 |

| 4 | Data | a-Orien  | ted Attacks: Exploitation Techniques and Defenses                         | 64  |

|---|------|----------|---------------------------------------------------------------------------|-----|

|   | 4.1  | Introdu  | action                                                                    | 64  |

|   | 4.2  | Data-o   | oriented Attacks                                                          | 66  |

|   |      | 4.2.1    | Why Do Data-oriented Attacks Receive Attention?                           | 66  |

|   |      | 4.2.2    | Classification of Data-Oriented Attacks                                   | 67  |

|   |      | 4.2.3    | Automatically Generating Data-oriented Exploits                           | 71  |

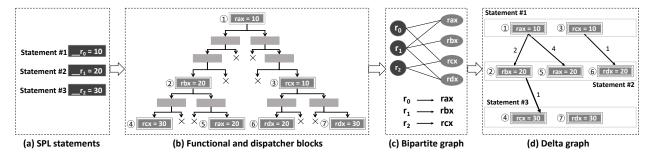

|   |      | 4.2.4    | Block-Oriented Programming (BOP) Attack                                   | 74  |

|   |      | 4.2.5    | Comparison Between DOP and BOP                                            | 75  |

|   |      | 4.2.6    | Data-oriented Attacks on Real-World Applications                          | 77  |

|   | 4.3  | Existir  | ng Defenses Against Data-Oriented Attacks                                 | 78  |

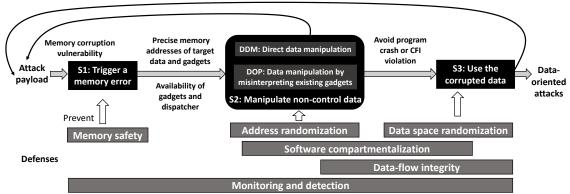

|   |      | 4.3.1    | Three-stage Model for Launching Data-oriented Attacks                     | 79  |

|   |      | 4.3.2    | S1 Defense – Preventing the Exploitation of Memory Errors                 | 81  |

|   |      | 4.3.3    | S2 Defense – Providing a Barrier to Access to Data or Guess Memory Layout | 87  |

|   |      | 4.3.4    | S3 Defense – Preventing/Detecting Use of Corrupted Data                   | 89  |

|   |      | 4.3.5    | Defense Mechanisms Especially Against Data-oriented Attacks               | 91  |

|   |      | 4.3.6    | Anti-specification Database for Detecting Data-Oriented Attacks           | 94  |

| 5 | Data | a Pointe | er Prioritization                                                         | 96  |

|   | 5.1  | Introd   | uction                                                                    | 96  |

|   | 5.2  | Backg    | round and Threat Model                                                    | 100 |

|   |      | 5.2.1    | Pointer Manipulation                                                      |     |

|   |      | 5.2.2    |                                                                           | 103 |

|   |      |          |                                                                           |     |

| Bi | bliogi | aphy      |                                                  | 142   |

|----|--------|-----------|--------------------------------------------------|-------|

| 7  | Con    | clusion   | and Future Work                                  | 137   |

| 6  | Guio   | delines a | and Practical Considerations                     | 134   |

|    | 5.5    | Discus    | sion                                             | . 133 |

|    |        | 5.4.3     | Performance Evaluation                           | . 130 |

|    |        | 5.4.2     | Prioritization Effectiveness                     | . 123 |

|    |        | 5.4.1     | Implementation                                   | . 123 |

|    | 5.4    | Evalua    | tion                                             | . 123 |

|    |        | 5.3.5     | Rule Design                                      | . 118 |

|    |        | 5.3.4     | Taint Analysis                                   | . 114 |

|    |        | 5.3.3     | Data Flow Construction                           | . 112 |

|    |        | 5.3.2     | Completeness and Representativeness of the Rules | . 110 |

|    |        | 5.3.1     | Rule-based Prioritization                        | . 106 |

|    | 5.3    | Data C    | Object Prioritization                            | . 106 |

|    |        | 5.2.4     | Threat Model                                     | . 105 |

|    |        | 5.2.3     | Hardware-based Defenses                          | . 104 |

## **List of Figures**

| 3.1 | An illustration of the commonalities and differences between a conventional (or                  |    |

|-----|--------------------------------------------------------------------------------------------------|----|

|     | basic) ROP attack (bottom) and a JIT-ROP attack (top). The top gray-box high-                    |    |

|     | lights the key steps in JIT-ROP to overcome fine-grained ASLR                                    | 33 |

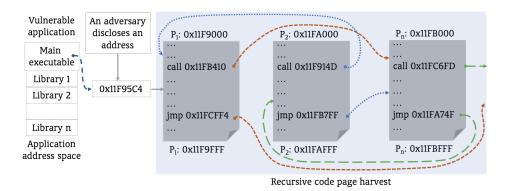

| 3.2 | An illustration of the recursive code harvest process of JIT-ROP [185]. An adver-                |    |

|     | sary discloses an address from the main executable or libraries (in this case from               |    |

|     | the main executable) of an application through a vulnerability                                   | 36 |

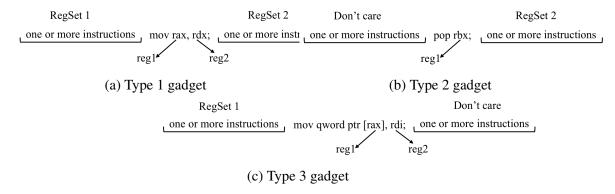

| 3.3 | A set of gadget types for measuring the quality of individual gadgets through the                |    |

|     | register corruption analysis                                                                     | 43 |

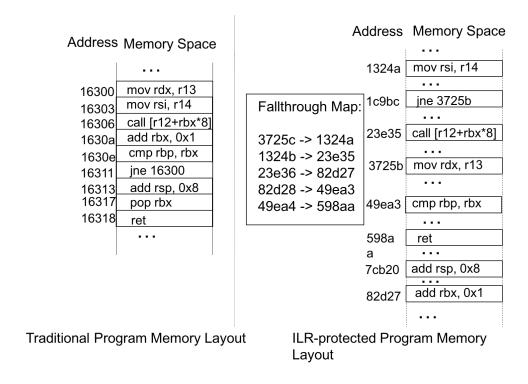

| 3.4 | Instruction location randomization. This figure is adopted from ILR [97]                         | 45 |

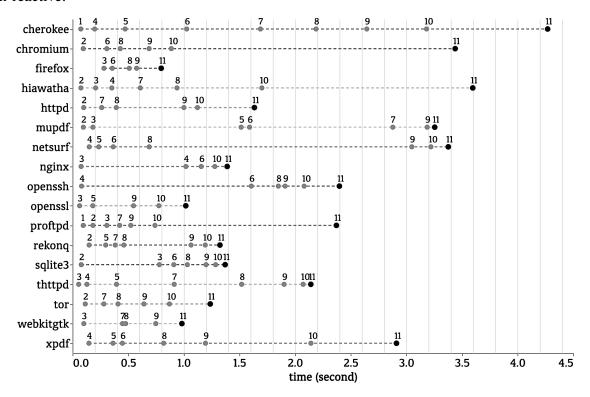

| 3.5 | Minimum time to obtain the Turing-complete gadget set with a timeline for new                    |    |

|     | gadget type leaks. Each gray filled circle $(\bullet)$ with a number $n$ on top of it represents |    |

|     | the time to leak $n$ gadget types. The bold filled circle ( $ullet$ ) indicates the time to leak |    |

|     | all gadget types. Applications and browsers are randomized with a function-level                 |    |

|     | scheme [47]                                                                                      | 49 |

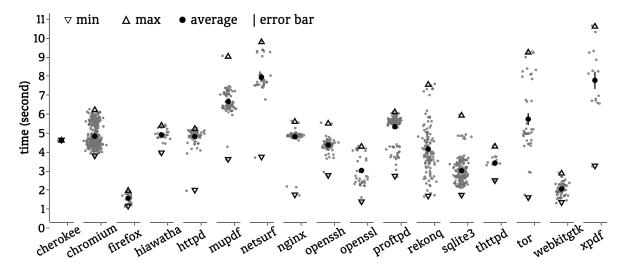

| 3.6 | Impact of starting code pointer locations on gadget harvesting time. Each • in-                  |    |

|     | dicates the time for harvesting the Turing-complete gadget set. The minimum,                     |    |

|     | maximum, and average time is calculated by starting code harvest process from                    |    |

|     | multiple code pointer locations. A small amount of jitter has been added to the                  |    |

|     | x-axis for each application/browser for better visibility of times along the y-axis              | 53 |

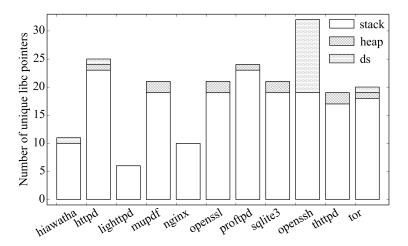

| 3.7 | Libc pointers in the stack, heap and data segment of a program. Stacks contain                   |    |

|     | more pointers, carrying higher risks of pointer leakage                                          | 59 |

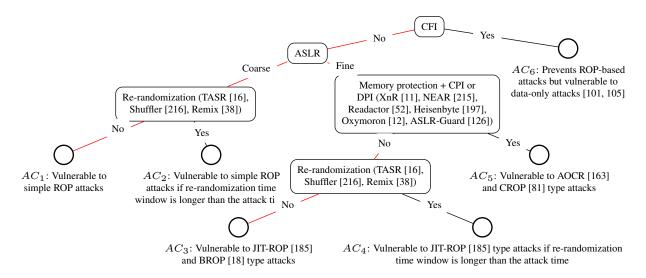

| 3.8 | High-level view of the types of ROP attacks and attack-paths based on various               |

|-----|---------------------------------------------------------------------------------------------|

|     | security measures. Each rectangle and circle indicate security measures and attack          |

|     | types, respectively. AC stands for attack condition. All the attack conditions have         |

|     | W⊕X, PIE, Canary, and RELRO implicitly                                                      |

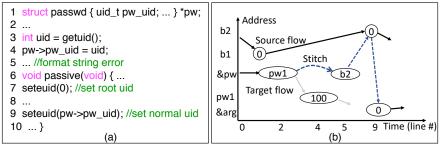

| 4.1 | Example of FlowStitch [100]                                                                 |

| 4.2 | Four major components of a BOP Compiler. The double and single border boxes                 |

|     | $(\Box)$ indicate functional and dispatcher blocks. The number inside a circle $(\bigcirc)$ |

|     | represents the functional block number. The X represents irrelevant basic blocks 74         |

| 4.3 | Stages in data-oriented attacks and mitigation in different stages 80                       |

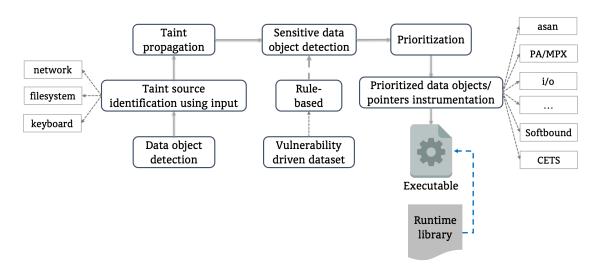

| 5.1 | High-level overview of the data object prioritization technique                             |

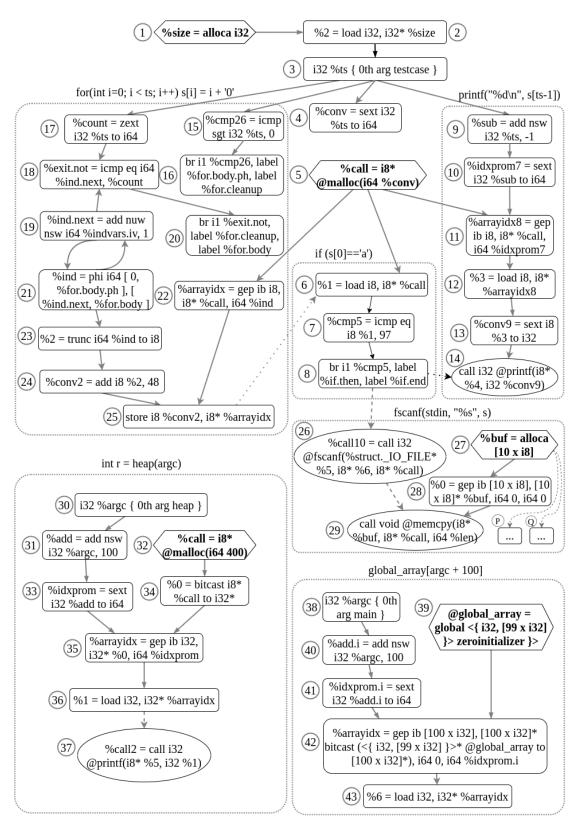

| 5.2 | A sample program with LLVM IR, program assignment graph, and constraint graph. 111          |

| 5.3 | Motivating example (C program)                                                              |

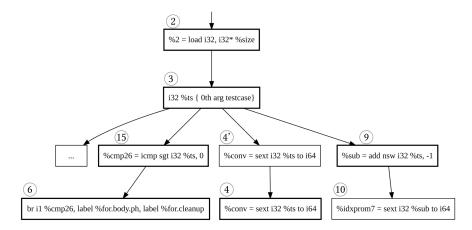

| 5.4 | Static Value Flow Graph (SVFG) of the motivating example in Figure 5.3. gep ib              |

|     | $\rightarrow$ getelementptr inbounds                                                        |

| 5.5 | Taint source identification and propagation                                                 |

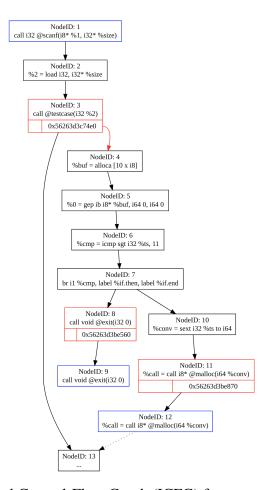

| 5.6 | Interprocedural Control-Flow Graph (ICFG) for testcase function in Figure 5.3 122           |

| 5.7 | Partial SVF graph. Common ancestor of node 4 and node 15 is node 3                          |

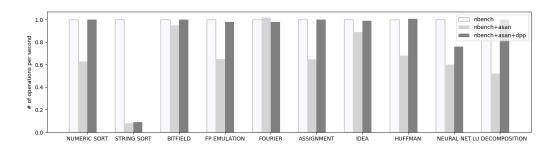

| 5.8 | The number of operations per second in three scenarios after normalizing with the           |

|     | baseline (i.e., nbench)                                                                     |

## **List of Tables**

| 2.1 | Countermeasures against ROP attacks. CRAs $\rightarrow$ Code Reuse Attacks                                                                                                                                                                                                                                                                                                                          | 13 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Leakage-resilient defenses in four categories                                                                                                                                                                                                                                                                                                                                                       | 15 |

| 2.3 | Practical CFI solutions with their average performance overhead                                                                                                                                                                                                                                                                                                                                     | 18 |

| 2.4 | Powerful and influential attacks demonstrated to bypass different countermeasures such as coarse-grained ASLR, fine-grained ASLR, CPI, Destructive read (i.e., execute-only memory), and CFI.                                                                                                                                                                                                       | 19 |

| 3.1 | Gadgets used in advanced ROP attacks [18, 27, 28, 86, 185] . $\triangle$ indicates an addition/subtraction/multiply/division. $\phi$ indicates logical operations such as and, or, left-shift, and right-shift. $\nabla$ indicates any operation that modifies stack pointer (SP). SN $\rightarrow$ Short name. TC? indicates whether a gadget is included in the Turing-complete gadget set or not | 39 |

| 3.2 | Gadgets with gadget types in the priority and MOV TC gadget sets                                                                                                                                                                                                                                                                                                                                    | 40 |

| 3.3 | Key differences in various randomization and re-randomization schemes evaluated.                                                                                                                                                                                                                                                                                                                    | 40 |

| 3.4 | Numbers of the applications and dynamic libraries for experiments                                                                                                                                                                                                                                                                                                                                   | 47 |

| 3.5 | Minimum and average time to leak all gadget types from TC, priority, MOV TC, and payload gadget sets. The percentage (%) of time is spent for leaking gadgets versus analyzing gadgets. The minimum, average, and percentages for each set are calculated using 17 applications including browsers. Payload* — average of                                                                           |    |

|     | three payload sets                                                                                                                                                                                                                                                                                                                                                                                  | 48 |

| 3.6 | Impact of locations of pointer leaks on gadget availability. The same application                      |

|-----|--------------------------------------------------------------------------------------------------------|

|     | has different numbers of address leaks for different schemes due to different back-                    |

|     | ends (i.e., compilers) that produce different sized executables of the same program.                   |

|     | The size of an executable is proportional to the number of code pages. Also, the                       |

|     | numbers of gadgets from the function-level scheme [47] and function + register-                        |

|     | level scheme [52, 98] are not comparable due to their different backends 51                            |

| 3.7 | Impact of fine-grained single-round randomization on the availability of gadgets                       |

|     | in various applications and dynamic libraries. Instruction-level randomization                         |

|     | scheme [95] is applied on 15 applications and 14 dynamic libraries, function-level                     |

|     | scheme [47] on 17 applications and 21 dynamic libraries, function + register-level                     |

|     | scheme [52, 98] on 12 applications and 13 dynamic libraries, and basic block-level                     |

|     | scheme [111] on 15 applications and 15 dynamic libraries. The data of each ap-                         |

|     | plication or library is the average result of 100 runs/loads/rewrites. The standard                    |

|     | deviations vary between 0.3~3.4 for minimum footprint and 5.04~22.85 for ex-                           |

|     | tended footprint gadgets.   ↓ indicates reduction                                                      |

| 3.8 | Register corruption for various gadgets. The numbers before and after the vertical                     |

|     | bar (I) represent the average number of unique register usage and register corrup-                     |

|     | tion rate in a gadget, respectively. $CG \rightarrow Coarse$ -grained. $FG \rightarrow Fine$ -grained. |

|     | Fine-grained versions prepared using SR [47]                                                           |

| 4.1 | Recent data-oriented attacks pose serious threats against real-world programs 79                       |

| 5.1 | Simple rules to detect sensitive data objects and pointers                                             |

| 5.2 | Vulnerable data objects/pointers in various programs with their definition functions                   |

|     | and line numbers. The * in some source file names and function names indicate                          |

|     | that parts of the file name or function name have been truncated for space 125                         |

| 5.3 | The number and percentage of top k prioritized objects needed for detecting/flag-    |

|-----|--------------------------------------------------------------------------------------|

|     | ging ground truth data objects in 18 programs including five real-world server ap-   |

|     | plications and 10 testcases from SAR dataset                                         |

| 5.4 | Performance improvement of our prioritization technique over Address Sanitizer . 131 |

| 5.5 | Reduction of instrumentation size and number of Loads/Stores when applying           |

|     | ARM PA considering prioritized data/object pointers compared to all data/object      |

|     | pointers                                                                             |

## Chapter 1

## Introduction

### 1.1 Problem Definitions

Despite the protections such as stack canaries [50], Write XOR execute or W⊕X (aka No-execute (NX) [204] or Data Execution Prevention (DEP) [65]), and Address Space Layout Randomization (ASLR) [199] deployed in modern computer systems, we have observed many advanced and influential code reuse attacks (CRAs). Most of these CRAs utilize Return-Oriented Programming (ROP) technique. These advanced and influential attacks include Just-In-Time ROP or JIT-ROP [185], Blind ROP or BROP [18], Address Oblivious Code Reuse or AOCR [163], CrashResistant Oriented Programming or CROP [81], Position Independent ROP or PIROP [89], Return to Zombie Gadget or ZombieG [186], Counterfeit Object-Oriented Programming or COOP [169], Typed ROP or TROP [75], Control-Flow Bending or CFB [27], StackDefiler [46], Back To The Epilogue or BATE [17], and others [28, 31]. Each of these attacks has unique capabilities. For example, JIT-ROP [185] enables one to reuse code even under fine-grained address space layout randomization (ASLR). JIT-ROP attacks can discover new code pages dynamically, by leveraging control-flow transfer instructions, such as *call* and *jmp*.

To protect systems from these advanced attacks, researchers have proposed variants or fine-grained version of existing defenses (*e.g.*, fine-grained ASLR [47, 60, 62, 84, 92, 95, 97, 98, 108, 111, 151, 157, 213], re-randomization [16, 36, 38, 125, 216], execute-only memory(XOM) (aka destructive read) [11, 53, 197, 215]) and Code Pointer Integrity (CPI) [12, 49, 115, 126, 130]. However, many of these defenses focus on specific attacks, e.g., the XOM-based defenses aim to hinder the JIT-

ROP's repeated memory disclosure capability. Thus, XOM-based defenses evaluate their security guarantees only based on stopping disclosure attacks on executable binaries without rigorous and metric-based evaluation. That is why we have observed a code inference attack [186] that can work in the presence of XOM-based defenses.

Besides, some metrics used for evaluating security guarantees of defenses do not capture the capabilities of advanced attackers. As a result, new attacks emerge to bypass those defenses. For example, both coarse-grained code randomizations (e.g., PaX ASLR [199]) and fine-grained code randomizations (e.g., Selfrando [47], Compiler-assisted Code Randomization [111], Remix [38], STIR [213], ILR [97] and ASLP [108]) use entropy to measure the effectiveness of hindering code-reuse attacks. However, such an entropy measure is not useful under the JIT-ROP threat model, as chunks of code are still available. Inclusion of distances between permuted functions or basic blocks for computing entropy would not work either, because the code's semantic connectivity (e.g., through *call* and *jmp*) is still not captured. Code connectivity is what JIT-ROP attacks leverage to discover code pages. Metrics and measurement methodologies that accurately reflect JIT-ROP capabilities are more meaningful under the JIT-ROP model. Thus, the fundamental needs are representative security metrics and methodologies for evaluating defenses. This is why recently we have observed a new metric called tunable entropy [157] to measure security guarantee.

Another criterion to build robust and new defense mechanisms is to analyze the assumptions and requirements of threats [39, 40]. This analysis can lead to developing robust and efficient countermeasures. For example, a requirement for many typical and advanced code reuse attacks [18, 169, 185] is memory disclosure or more specifically code pointer leak. To stop attackers from fulfilling this requirement, researchers have proposed effective CPI-related countermeasures [12, 49, 115, 126, 130]. The CPI-based countermeasures are effective because these countermeasures incur as low as less than 1% overhead [126] and keep an application safe by protecting the integrity of a code pointer. Hardware-based techniques such as Intel's CET [103], ARM Pointer Authentication (PA) [158], and MPX [104]) can further reduce the overhead to make the slowdown imperceptible. For example, ARM PA [158] costs on average less than 0.5% for code

pointer authentication [121]. Thus, both software and hardware-based code pointer protection countermeasures are practical.

Due to this practical code pointer protection countermeasures [12, 49, 103, 104, 115, 126, 130, 158] as well as the advances towards practical CFI [24, 83, 124, 130, 132, 152, 222, 224], we anticipate a shift towards the use of data object/pointer manipulation as the attack vector as the manipulation works in the presence of these countermeasures. In recent years, we have also observed data-oriented attacks (also known as non-control attacks) [35, 100, 101, 133, 168, 196, 219] that manipulate data objects/pointers to exploit a system/application. While the software-based code pointer protection countermeasures are practical, software-based data object/pointer protection can cost a significant amount of overhead, from 48-116% [29, 134, 135]. Thus, software-based data object/pointer protection, in general, is not practical due to a high runtime overhead. On the other hand, hardware-based solutions can reduce the overhead significantly. For example, ARM pointer authentication [158] and Intel's MPX [104] cost on average around 19.5% [121] and 50% [145] overhead, respectively, for protecting data pointers. The 19.5% overhead for a hardware-based technique is still critical for performance-critical applications. Due to a huge number of data objects/pointers in an application compared to code pointers, one source of the overhead for protecting data objects/pointers is protecting many data objects/pointers that do not need protection as those objects/pointers do not lead to vulnerability. One way to reduce the performance overhead is to figure out the sensitive (i.e., vulnerable) data objects/pointers and prioritize them for protection.

## 1.2 Contribution

The goal of this dissertation is to demonstrate the feasibility of methodologies for quantitatively measuring the security properties of advanced system defenses. In particular, we quantify the impact of fine-grained ASLR through attack surface measurement and improve the performance of in-memory data integrity defenses by identifying, quantifying, and prioritizing key attack vectors

extracted using knowledge from advanced exploits. To be specific, this dissertation aims to tackle three problems: *i*) designing security metrics and measurement methodologies for evaluating defense mechanisms, *ii*) analyzing the assumptions and requirements of advanced threats (e.g., data-oriented exploits), and *ii*) designing a data object/pointer prioritization technique to improve the existing defenses by reducing overhead by prioritizing sensitive data objects/pointers and filtering out non-sensitive ones.

To address the first problem, we have proposed four security metrics and four measurement methodologies to quantitatively evaluate the impact of fine-grained ASLR or code randomization defenses on various applications (see details on chapter 3). Besides, we have addressed some in-depth questions regarding the impact of fine-grained ASLR on code reuse attacks that have not been addressed before. For example, what impact do fine-grained ASLR have on the Turing-complete expressiveness of JIT-ROP payloads? How do attack vectors (e.g., code pointer leaks) impact the code reuse attacks? How would one compute the re-randomization interval effectively to defeat JIT-ROP attacks? We designed a measurement mechanism that allows us to perform JIT-ROP's code page discovery in a scalable fashion. This mechanism enables us to compare results from many programs and libraries under multiple ASLR conditions (coarse-grained, fine-grained function level, fine-grained basic block level, fine-grained instruction level, and register level). Our evaluation involves up to 20 applications, including six browsers, one browser engine, and 25 dynamic libraries. Our key experimental findings and technical contributions are summarized as follows.

- A multi-step attack workflow that captures the common tasks and goals in ASLR bypasses.

- We define multiple new concepts, e.g., minimum footprint gadgets, extended footprint gadgets, and quality of gadgets, and describe methods for evaluating important properties of ROP gadgets, e.g., register corruption rate. We also summarize and experiment with common and specialized gadget types used in recent attacks. These contributions are useful beyond this specific ASLR study.

- We provide a methodology to compute the upper bound  $\mathcal{T}$  for re-randomization intervals. If the re-randomization interval is less than  $\mathcal{T}$ , then a JIT-ROP attacker is unable to obtain various gadget sets such as the Turing complete gadget set, priority gadget set, MOV TC gadget set, and gadgets from real-world payloads (see the definitions of gadget sets in Section 3.2). We compute the upper bound  $\mathcal{T}$  by measuring the minimum time for an attacker to find a specific gadget set, i.e., the shortest time to reach gadget convergence for the gadget set. The upper bound ranges from 1.5 to 3.5 seconds in our tested applications such as nginx, proftpd, firefox, etc.

- Our findings show that starting code pointers do not have any impact (i.e., zero standard deviations) on the reachability from one code page to another. Every code pointer leak is equally viable for revealing an address space layout, suggesting that attackers' discovered gadgets eventually converge to a gadget set no matter where the starting pointer is.

- Our findings also show that the starting code pointers have an impact on the speed of convergence. That means the time needed for a JIT-ROP attacker to discover a gadget set varies with the locations of starting code pointers. In our experiments, the time for obtaining the Turing-complete gadget set ranges from 2.2 to 5.8 seconds.

- We also present a general methodology for quantifying the number of JIT-ROP gadgets.

Our results show that a single-round instruction-level randomization scheme can limit the availability of gadgets up to 90% and break the Turing-complete operations of JIT-ROP payloads. Also, fine-grained randomization slightly degrades the gadget quality, in terms of register-level corruption.

A stack has a higher risk of revealing dynamic libraries than a heap or data segment because our experiments show that stacks contain 16 more libc pointers than heaps or data segments on average. This finding indicates the necessity of randomizing stack over heap or global variables.

We systemized data-oriented attacks [35, 100, 101, 133, 168, 196, 219] with their assumptions/requirements and attack capabilities to address the second problem. Our work provides a comprehensive description of the assumptions and requirements of data-oriented attacks and a comparison of existing defenses known to prevent data-oriented attacks. Our analysis in this work offers new directions to look at data-oriented attacks because these attacks do not tamper with the control flow of a victim program and are far more advantageous than return-oriented programming. The main contributions of this work are as follows.

- We systemized various data-oriented exploits by classifying their exploit techniques.

- We discussed various automatic data-oriented exploit generation tools [105, 154, 172] and compared the tools in terms of their flexibility and practicality.

- We discuss various representative data-oriented exploits on real-world applications and existing defense approaches to prevent those exploits in different stages.

To address the third problem, i.e., prioritizing sensitive or vulnerable data objects/pointers, we develop a prioritization framework (see details on chapter 5). The goal of the framework is to prioritize data pointers that are sensitive and may potentially lead to vulnerability. Our goal is to ensure security through data object/pointer protection through various security mechanisms (e.g., ARM PA [158], MPX [104], Softbound [134], etc.) while keeping the overhead low. The main contributions of this work are as follows.

• We proposed a prioritization framework that is both *i*) generic and *ii*) adaptable. The generic nature of the framework ensures that it does not rely on underlying operating systems, platforms, or programming languages. The adaptability feature makes the framework adaptable with minimum changes so that it can be used with other defenses such as ARM PA [158], MPX [104], Softbound [134], AddressSanitizer [175], and many more. One key use case of the framework is to tune the performance vs security in an application.

- We extracted seven vulnerability- and exploit-driven rule-based heuristics to prioritize data objects/pointers that are sensitive and could potentially lead to vulnerabilities.

- We implemented our framework using eight analysis passes (one for taint analysis and seven

for data object/pointer identification using our rules), and one instrumentation pass on top of

LLVM 12. We also implemented one instrumentation pass for instrumenting our prioritized

pointers using ARM PA [158] and modified AddressSanitizer [175] tool to support instrumenting only the prioritized data objects/pointers in addition to AddressSanitizer's default

behavior.

- To evaluate the prioritization framework, we constructed ground truths by manually analyzing vulnerable programs considering local/global data objects/pointers, inter-functional analysis, and corner cases. We constructed 33 ground truths data objects from 18 programs including real-world server applications and 10 test cases from Software Assurance Reference (SAR) dataset.

- We found that as low as only 3% of total data objects are needed to protect for real-world applications. We achieved a 42% performance overhead reduction compared to Address-Sanitizer while protecting 100% of the prioritized data objects. We can reduce the instrumentation size by around 62% and the number of pointers in Load/Store IR instructions (for ARM PA) by 56% and 96%, respectively, without compromising security.

The structure of this report is as follows. Chapter 2 related work on defense mechanisms against advanced ROP-based code reuse attacks, control-flow integrity, data-oriented attacks, pointer authentication, and sensitive data protection approaches. Chapter 3 presents our work on quantifying attack surface of various applications and libraries and assessing the impact of fine-grained ASLR or code randomization on code reuse attacks under the JIT-ROP threat model using quantitative metrics and measurement methodologies. Chapter 4 systemizes the knowledge of various data-oriented attacks by analyzing their requirements and assumptions. Chapter 5 presents our

technique for a data pointer prioritization framework including motivation, design, and evaluation. And, finally Chapter 6 outlines the guidelines and practical considerations that we need to make for making our measurement results effective as well as the practical implication of the measurements.

## Chapter 2

## **Literature Review**

The war games between attackers and defenders have been prevalent for decades. Due to legacy C/C++ code, memory corruption vulnerabilities are still prevalent in complex software such as browsers (e.g., Internet Explorer, Mozilla Firefox, etc.) and servers (e.g., Nginx, Apache, ProFTPD, etc.). Modern computer systems deploy various defenses (e.g., stack canaries [50], Write XOR eXecute or W⊕X (aka No-eXecute (NX) [204] or Data Execution Prevention (DEP) [65]), and Address Space Layout Randomization (ASLR) [199] to defend the attacks that exploit the memory corruption vulnerabilities. These defenses prevent attacks such as stack smashing [147] (e.g., return address overwrite), exception handler overwrite [122], and heap vulnerabilities (e.g., heap unlinking).

Unfortunately, the deployment of these defenses (*i.e.*, stack canaries, W⊕, NX, and ASLR) could not repress advanced attackers because some attackers have proved their capabilities to bypass modern defenses. For example, coarse-grained code reuse attacks [153] or fine-grained code reuse attacks such as Return-Oriented Programming (ROP) [18, 28, 31, 62, 75, 81, 86, 161, 163, 178, 185, 186] can bypass the NX defense. At the same time, researchers have proposed various defenses such as fine-grained ASLR, Continuous address space randomization, Code Pointer Integrity (CPI), and Control Flow Integrity (CFI). Thus, the research conducted in the system security area primarily has two themes: 1) demonstrating attacks and 2) discovering countermeasures.

#### 2.1 Attackers' and Defenders' Games

Attackers have primarily demonstrated two types of attacks: *i)* code injection attacks and *ii)* code reuse attacks. Besides, attackers also demonstrated attacks against a defense solution (*i.e.*, ASLR or CFI) to disclose the limitation of the defense.

### 2.1.1 Code Injection Attacks and Defenses

Code injection attacks [122, 147] inject shellcode into a writable segment of memory (e.g., stack or heap) of a program and redirect the control flow to the injected shellcodes, usually by overwriting a return address or function pointer. Attacks that overwrite a return address are called stack smashing attacks. Stack canaries [50, 72] protect a program from stack smashing attacks. Besides, countermeasures such as StackGuard [50], Stack Shield [208], ProPolice [71] RAD [44], TRUSS [184], IBMAC [78], StackGhost [79], and Binary-Rewriting [156] aimed to protect return address integrity through shadow stack-based, compiler-based, and instrumentation-based techniques. To enforce canaries, compilers place a canary value before the stored return address in a stack and add a canary verification routine to function epilogues. Whenever the verification routine finds a mismatch in the function of a program, the program terminates by redirecting the control flow to a developer-defined exception handler. If the developer-defined exception handler is not present, the Operating System's exception handler handles the exception. In a consequent fashion, attackers overwrote the exception handler to construct an alternative control-flow hijack or the Structured Exception Handler (SEH) attacks [122]. In response, Windows Operating System (OS) added an overwrite protection feature called Structured Exception Handling Overwrite Protection (SEHOP). However, the major response came as hardware support called no-execute or NX bit [204]. CPUs segregate code and data regions based on the NX bit, and ensure the execution space protection. DEP or W\(\prepta\)X [65] utilizes the NX bit for marking some modules (i.e., heap, stack, etc.) as nonexecutable. As a result, the writable segments of a binary are no longer executable. Thus, injecting shellcodes in a stack or heap no longer works. To circumvent this DEP or  $W \oplus X$  security feature, attackers invented code reuse attacks (e.g., return-to-libc).

#### 2.1.2 Code Reuse Attacks and Defenses

Code reuse attacks (CRAs) can circumvent the DEP or W⊕X security feature. The first form of CRAs utilizes the whole library functions to construct exploits. Since the GNU C library, commonly known as Glibc or libc, is one of the largest libraries known to have diverse functionalities required by an attacker, attackers used the libc library for their attacks. This type of attack is called return-to-libc [112, 139, 153, 217]. Hovav Shacham extended the idea of code reuse by introducing a fine-grained code reuse technique called gadget chain. A gadget chain is a sequence of gadgets that can express arbitrary program logic. A gadget is a set of short instructions ending with the ret instruction. This technique is called Return Oriented Programming (ROP) [22, 155, 161, 178] and the gadgets are called ROP gadgets. Soon attackers adopted this technique and conducted many ROP-based code reuse attacks [18, 28, 31, 62, 75, 81, 86, 163, 185, 186] and its variants (*i.e.*, Jump Oriented Programming (JOP) [20]). Following are the four flavors of gadget-oriented CRAs.

- Return-Oriented Programming (ROP) attacks. Hovav Shacham first demonstrated the capability of ROP gadgets to construct Turing-complete operations [178]. The Turing-complete operations include memory operations, assignments, arithmetic operations, logical operations, control flow, function calls, and system calls [161]. Due to the capability of ROP gadgets, we have observed some influential ROP gadget-based attacks such as Just-In-Time ROP or JIT-ROP [185], Blind ROP or BROP [18], Address Oblivious Code Reuse or AOCR [163], CrashResistant Oriented Programming or CROP [81], Position Independent ROP or PIROP [89], and others [28, 31].

- Jump-Oriented Programming (JOP) attacks. JOP-based attacks [20, 33, 109, 131, 164] avoid the reliance of attacks on the stack and ret instructions by introducing JOP gadgets (a

sequence of instructions followed by a jmp instruction) as the building blocks for exploits. However, stack plays an important role in ROP-based attacks by allowing attackers to chain the ROP gadgets. To achieve the same capability, JOP-based attacks require dispatcher gadgets, in addition to the JOP gadgets.

- Call-Oriented Programming (COP) attacks. Carlini *et al.* [28] introduced and demonstrated the COP-based attacks using COP gadgets. COP gadgets are similar to ROP gadgets but end with call instructions. Unlike JOP-based attacks, COP attacks do not require dispatcher gadgets because call instructions usually use memory-indirect locations instead of values from registers as the targets. By preparing the memory in advance, attackers can chain the COP gadgets. Another COP-based attack is Pure-Call Oriented Programming or PCOP [165].

- Counterfeit Object-Oriented Programming (COOP) attack. Schuster *et al.* [169] introduced the COOP attack by demonstrating that C++ virtual functions can be chained together like gadgets to achieve malicious program behavior.

Address Space Layout Randomization (ASLR). Code reuse or gadget-based attacks require the locations of shared-library functions or gadgets in memory. The PaX team introduced Address Space Layout Randomization (ASLR) [199] to make the code-reuse attacks difficult. ASLR, also known as coarse-grained ASLR, randomizes the base addresses of code (*i.e.*, .text) and data (*i.e.*, stack, heap, etc.) segments. As a result, it becomes difficult for attackers to know the locations of shared-library functions or gadgets without knowing how the locations of the modules are randomized by ASLR. ASLR is the most efficient and widely deployed security feature in modern operating systems. For example, OpenBSD added ASLR support in 2003, Linux in 2005, Android from Android 4.0, DragonFly BSD in 2010, iOS in 2011, Windows in 2007, NetBSD in 2009, macOS in 2007, and Solaris in 2012. The Position Independent Executable (PIE) option allows the main executable to be run as position-independent code, i.e., PIE relocates the code and data segments of the main executable.

ASLR makes the code reuse attacks difficult, but ASLR is vulnerable to information leaks. Since the coarse-grained ASLR only randomizes the base addresses of various segments and modules of a program, the internal layout of the segments and modules remains unchanged. Thus, a single leak can essentially reveal all the contents of a module. For example, the leak of a single function from the libc library can reveal all the other functions in libc because the offset of a function from the base address of libc is the same regardless of the different randomized base addresses of libc. An adversary can launch a basic ROP attack [198] using gadgets given a leaked address from the code segment of interest. The adversary only needs to adjust the addresses of pre-computed gadgets w.r.t. the leaked address.

**Defenses against ROP attacks**. Due to the prevalence of ROP attacks, researchers have proposed a wide range of countermeasures using both static software hardening and runtime monitoring techniques to prevent ROP attacks. Table 2.1 shows the key solutions. These solutions restrict the abnormal control flow transfers through return address protection, removing unaligned control transfer instructions, removing return address, ensuring the integrity of stack using shadow stack [79, 208] and detecting gadget chains by counting ret instructions or measuring gadget chain length.

Table 2.1: Countermeasures against ROP attacks. CRAs  $\rightarrow$  Code Reuse Attacks.

| Tool              | Technique                                                    | Protection<br>Against | Performance<br>Overhead |

|-------------------|--------------------------------------------------------------|-----------------------|-------------------------|

|                   | Performs runtime checks for ensuring integrity of stack      |                       |                         |

| ROPGuard [80]     | pointer, invocation of critical functions, return address,   | ROP                   | <5%                     |

|                   | and call stack when any critical function gets called.       |                       |                         |

|                   | Eliminates unaligned free-branch instructions and protects   |                       |                         |

| G-Free [146]      | aligned free-branch instructions using alignment sleds,      | ALL CRAs              | 3%                      |

|                   | return address encryption, frame cookies and code rewriting. |                       |                         |

| DROP [32]         | Detects an unusually high frequency of ret instructions      | ROP                   | 5.3x                    |

| ROPdefender [64]  | Ensures integrity of stack using shadow stack[79, 208]       | ROP                   | 2x                      |

| D-4 [110]         | Removes return instructions by replacing return addresses    | DOD                   | A C 01                  |

| Return-less [118] | to return indices.                                           | ROP                   | 4.6%                    |

| DyIMA [63]        | Detects an unusually high frequency of ret instructions      | ROP                   |                         |

|                   | Detects ROP gadget chains by analyzing the past and          |                       |                         |

| ROPecker [43]     | future execution flows of a process and extracting history   | ALL CRAs              | 2.6%                    |

|                   | of taken branches from Last Branch Record (LBR) registers.   |                       |                         |

|                   | Detects abnormal control flow transfers by analyzing         |                       |                         |

| kBouncer [150]    | executed indirect branches at critical points recorded       | ALL CRAs              | 4%                      |

|                   | by Last Branch Record (LBR) registers.                       |                       |                         |

Most of the defense solutions discussed above (Table 2.1) are applicable for only ROP-based attacks. ROPecker [43] and kBouncer [150] are applicable for all control-oriented attacks but attackers can circumvent them [28, 87] using manually crafted long gadgets. G-Free [146] is also applicable for all control-oriented attacks, but it requires source code which is often unavailable. Besides, some of the solutions have high performance overheads.

Leakage resilient defenses. One prime requirement of code reuse attacks is information leaks. That means an attacker must derandomize the address space layout for mounting code-reuse or ROP attacks. To do so, an attacker first exploits a memory corruption vulnerability to leak information [9, 82, 96, 190, 192, 196] about the memory layout of a program. Then the attacker constructs an exploit leveraging the knowledge from the information leak and mount the attack using the same or another memory vulnerability. Under coarse-grained ASLR, a single leak can essentially reveal all the memory layout of a module. To stop revealing everything from a single leak, researchers introduced various leakage-resilient defenses. The leakage-resilient defenses unlock only a small portion of the code region and seriously limit an attack's ability to obtain gadgets for code reuse purposes. The leakage-resilient defenses fall into the following five categories.

1) Fine-grained ASLR or code randomization. Fine-grained ASLR, aka fine-grained code randomization or code diversification, relocates all the segments of the main executable of a process, including shared libraries, heap, stack, and memory-mapped regions, and restructures the internal layouts of these segments. Thus, simply adjusting the addresses of pre-computed gadgets (as in the basic ROP) no longer works. The granularity of fine-grained randomization varies, e.g., at the level of functions [47, 84, 108], basic blocks [38, 111, 213], instructions [97], or machine registers [52, 98]. Table 2.2 shows the summary of fine-grained code randomization defenses. However, few advanced attacks demonstrated their capability to perform memory disclosure attacks at runtime. For example, JIT-ROP [185] can recursively traverse code pages in an application using call and jump links. Other techniques such as BROP [18] and CROP [81] attacks can read memory contents dynamically using the so-called stack reading and memory probing techniques, respectively.

Table 2.2: Leakage-resilient defenses in four categories

| Tools                    | Performance<br>Overhead                                                                                                                                                                                                                                             |                  |  |  |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|--|

|                          | Fine-grained code randomization                                                                                                                                                                                                                                     |                  |  |  |

| SBR [157]                | <ul> <li>Limits the utility of any disclosed code address by partitioning a function</li> <li>Uses a configurable parameter to indicate partitions and offers tunable entropy</li> </ul>                                                                            | 2.26% [157]      |  |  |

| Selfrando [47]           | - Reorders functions at load time using metadata extracted by selfrando library                                                                                                                                                                                     | <1% [47]         |  |  |

| CCR [111]                | - Reorders functions and basic-block based on extracted metadata during compilation - Keeps the same layout unless re-randomized again                                                                                                                              | 0.28% [111]      |  |  |

| Zipr [95]                | <ul> <li>Reorders the location of each instruction in an executable.</li> <li>Applies block-level instruction layout randomization during binary rewriting</li> </ul>                                                                                               | <5% [95]         |  |  |

| Multicompiler [98]       | - Reorders functions and machine registers during link time optimization                                                                                                                                                                                            | 1% [98]          |  |  |

| Isomeron [62]            | - Performs code randomization with execution path randomization.                                                                                                                                                                                                    | 19% [62]         |  |  |

| ASLP [108]               | <ul> <li>Permutes all sections, modules, and memory mapped regions by binary rewriting</li> <li>Reorders functions, data objects within their segments using relocation information</li> </ul>                                                                      | <1% [108]        |  |  |

| ILR [97]                 | <ul> <li>Reorders the location of each instruction in an executable or library.</li> <li>A fall-through map guides the execution of instructions in the right order.</li> </ul>                                                                                     | 13% [97]         |  |  |

| ORP [151]                | <ul><li>Reorders instructions within a basic block.</li><li>Employs narrow-scope code transformations using in-place code randomization</li></ul>                                                                                                                   | ~0% [151]        |  |  |

| Marlin [92]              | - Extracts function symbols and shuffles the symbols                                                                                                                                                                                                                | 0% [92]          |  |  |

| XIFER [60]               | - Transforms a control flow graph by randomizing contiguous basic blocks (bbls) - Also, splits some bbls and injects dummy instructions in some bbls.                                                                                                               | 1.2% [60]        |  |  |

| STIR [213]               | - Transforms a binary into a self-randomizable form using binary rewriting - Self-randomizable form triggers randomization of basic blocks at program start                                                                                                         | 1.6% [213]       |  |  |

| ASR [84]                 | - Employs link-time transformation to randomize code and data for OSes - Performs live re-randomization of a process' layout by runtime state migration.                                                                                                            | <5% [84]         |  |  |

| Continuous randomization |                                                                                                                                                                                                                                                                     |                  |  |  |

| TASR [16]                | - Randomizes a process' memory layout when the process inputs or outputs something                                                                                                                                                                                  | 2.1% [16]        |  |  |

| Shuffler [216]           | - Loads itself as a user space program and shuffles a process' functions continuously.                                                                                                                                                                              | 14.9% [216]      |  |  |

| Remix [38]               | - Reorders the basic blocks within a function to avoid adjusting function pointers                                                                                                                                                                                  | 2.8% [38]        |  |  |

| CodeArmor [36]           | <ul> <li>Maps a code pointer to any one of multiple diversified code spaces</li> <li>Periodically changes the mapping from pointers to code space at runtime</li> </ul>                                                                                             | 6.9% [36]        |  |  |

| RuntimeASLR [125]        |                                                                                                                                                                                                                                                                     | 0% [125]         |  |  |

| STABILIZER [55]          | - Re-randomizes functions, stack frames, and heap objects periodically at runtime.                                                                                                                                                                                  | <7% [55]         |  |  |

|                          | Memory protection                                                                                                                                                                                                                                                   |                  |  |  |

| XnR [11]                 | - Executes code but restricts reading code as data by modifying page fault handlers - Identifies bad code read through a CPU performance feature called demand paging                                                                                               | 2.2-3.4% [11]    |  |  |

| NEAR [215]               | <ul> <li>Allows the reading code, but does not allow to execute the read code</li> <li>A data swap process replaces any read instructions with invalid opcode</li> <li>Also, the process recovers the original opcodes on legitimate read and execution.</li> </ul> | 4.7% [215]       |  |  |

| Readactor [53]           | - Enforces execute-only (XO) memory using Intel's Extended Page Tables (EPT) - Converts code pointers into direct branches and hides them in an XO trampoline                                                                                                       | 6.4% [53]        |  |  |

| Heisenbyte [197]         | - Marks code as execute-only and prevents reading after the execution of the code - Allows legitimate reading of code by keeping a separate view of each page.                                                                                                      | 16.5-18.3% [197] |  |  |

|                          | Code Pointer Integrity                                                                                                                                                                                                                                              |                  |  |  |

| CPI [115]                | - Identifies memory objects used to access code pointers and securely stores them                                                                                                                                                                                   | 2.9-8.4% [115]   |  |  |

| Oxymoron [12]            | <ul> <li>Replaces all the direct references to other code and data into indices.</li> <li>Redirects calls and jumps through a translation table that store actual mappings</li> </ul>                                                                               | 2.7% [12]        |  |  |

| ASLR-Guard [126]         | - Protects the leakage of code pointers by separating sensitive code or data pointers                                                                                                                                                                               | <1% [126]        |  |  |

| CCFI [130]               | - Maintains the integrity of a CFG by ensuring the integrity of control-flow pointers - Enforces integrity of control-flow pointers using cryptographic MACs for pointers.                                                                                          | 3-18% [130]      |  |  |

| PointGuard [49]          | <ul><li>- Ensures the integrity of pointers</li><li>- Encrypts when a pointer is initialized or modified and decrypts before use.</li></ul>                                                                                                                         | 0-20% [49]       |  |  |

|                          |                                                                                                                                                                                                                                                                     |                  |  |  |

2) *Continuous code randomization*. Re-randomization (aka continuous code randomization) techniques [16, 36, 38, 55, 125, 216] continuously shuffle the address space at runtime. This continuous

shuffling breaks direct and indirect memory disclosure. It also breaks the runtime code discovery process by making the already discovered code pages obsolete. Re-randomization techniques are similar to fine-grained randomization techniques. However, re-randomization techniques pose one key challenge, which is the identification of all the pointer references and updating them at runtime. Table 2.2 shows a summary of continuous code randomization defenses.

*3) Memory protection*. The memory protection-related leakage-resilient defenses [11, 53, 197, 215] are variant of the W⊕X defense. The key goal of the memory protection leakage-resilient defenses is to prevent direct or indirect memory disclosure attacks [185]. The key goal of these memory protection techniques is to ensure execute-only memory for code pages. Table 2.2 shows a summary of memory protection-related leakage-resilient defenses.

However, attackers can still access zombie gadgets [186] that are available after applying destructive read defenses (i.e., XnR [11], NEAR [215], Readactor [52], and Heisenbyte [197]). Destructive read defenses only allow code execution. Any attempt to read code pages terminates a process. In this way, destructive reads destroy the availability of gadgets to attackers. However, destructive read defenses cannot completely eliminate all gadgets. For example, the runtime code generation capability of JIT compilers allows the creation of multiple copies of the same code (e.g., two native code regions can be created from the same JavaScript code, one copy is used for disclosing layout, and another copy is used for mounting attacks). Besides, loading and unloading features of dynamic libraries allow attackers to load, disclose, destroy, and unload code pages. A fresh loading of the destroyed code pages can be used in attacks utilizing the layout information of the disclosed code pages. Similarly, attackers can infer code layout by creating new processes (e.g., creating new tabs in browsers using JavaScript) and making an informed guess about neighboring bytes after disclosing a few bytes (i.e., implicit reads [186]). Thus, JIT compilers, load/unload features, new process creation, and implicit reads allow attackers to get gadgets even in the presence of destructive read defenses.

4) Code Pointer Integrity (CPI). CPI defenses aim to ensure the integrity of code pointers either

from leaking through disclosure attacks or from modifying by attackers. To do so, code pointer obfuscation techniques identify sensitive memory objects that could lead to code pointers, encrypt the sensitive memory objects [49, 126, 130], store the memory objects in a translation table [12], and hide the memory objects in a secure and isolated memory region [115, 126]. Table 2.2 shows a summary of CPI-based leakage-resilient defenses. CPI is a powerful defense but there are few attacks (e.g., Isomeron [62] and COOP [169]) that have demonstrated their capability to bypass some CPI-based defenses.

5) Data Pointer Integrity (DPI) Recent attention on non-control-oriented or data-only attacks [101, 105] motivated researchers to develop practical Data-Flow-Integrity (DFI) [29] solutions (details of non-control attacks in [40]). Currently, it is challenging to implement a practical DFI solution considering the overhead of data-flow tracking.

### 2.1.3 Control-Flow Integrity

Completely orthogonal to defenses like ASLR, DEP, stack cookies, and leakage-resilient solutions, Control Flow Integrity (CFI) [2] has gained interest due to its capability to prevent all control-oriented attacks in its ideal form. However, the requirement of source code/debug information and expensive performance overhead restrict CFI from being practical. In practice, imprecision in resolving indirect control-flow transfers impacts CFI's security guarantees. Besides, there are trade-offs between using coarse-grained CFI (performance overhead is low when enforced) and precise CFI (performance overhead is high when enforced). To make CFI fast and practical, many researchers have focused on developing the coarse-grained version of CFI [54, 83, 130, 132, 140, 222, 224]. Table 2.3 shows several practical CFI defenses with their costs.

Even with the great promise of CFI for protecting control-oriented attacks, attackers may find ways to launch new exploits such as control-oriented [46, 75, 86, 169] and non-control-oriented [27, 101, 105] exploits as demonstrated before, where the exploits conform with CFI. The latest advancement in control-flow transfers such as MLTA [124] significantly advances CFI

that can prevent most control-oriented attacks.

Table 2.3: Practical CFI solutions with their average performance overhead

| CFI Tools                    | bin-CFI | CCFIR | CFL  | KCoFI  | XFI   | CCFI  | O-CFI | MCFI  | RockJIT | Lockdown |

|------------------------------|---------|-------|------|--------|-------|-------|-------|-------|---------|----------|

| CFI 100IS                    | [224]   | [222] | [19] | [54]   | [70]  | [130] | [132] | [140] | [141]   | [152]    |

| Avg. Performance<br>Overhead | 8.54%   | 3.6%  | 4.5% | 13-27% | 5-10% | 3-18% | 4.7%  | 5%    | 14.6%   | 19.09%   |

#### 2.1.4 Powerful and Influential Attacks

The deployment of defenses like stack canaries,  $W \oplus X$ , ASLR, fine-grained ASLR, CPI, execute-only memory (XOM), and CFI is not enough for some advanced attackers because some attackers have proved their capabilities to bypass many modern defenses. For example, attackers have demonstrated advanced exploits such as JIT-ROP [185], CROP [81], BROP [18], PIROP [89], COOP [169], AOCR [163], ZombieG [186], CFB [27] and many more on the machines that are equipped with the modern defenses. Table 2.4 shows these attacks along with their techniques and capability.

Snow et al. demonstrated a Just-In-Time Code Reuse attack (JIT-ROP) that can bypass the fine-grained ASLR defense [108, 151, 209] by leveraging a memory corruption vulnerability (e.g., heap overflows, use-after-free, etc.) [185]. The attack is particularly strong because it starts with an information leak and ends with generating an exploit payload by just-in-time compiling a custom attack program.

Bittau et al. demonstrated that a remote unknown binary (equipped with the canary, NX, and ASLR) can be exploited using a stack vulnerability and a 1-bit information leakage if the binary restarts from a crash and does not re-randomize its address space [18]. More recently, Gawlik et al. showed that the ASLR defense can be bypassed without the information leakage for fault-tolerant programs [81]. They developed a memory probing technique (so-called memory oracles) to search for reference-less sensitive data (e.g., Process Environment Block (PEB), Thread Environment Block (TEB), etc. that contain addresses of the mapped modules, stack boundaries, and exception

Table 2.4: Powerful and influential attacks demonstrated to bypass different countermeasures such as coarse-grained ASLR, fine-grained ASLR, CPI, Destructive read (i.e., execute-only memory), and CFI.

| Attack            | Technique Used                                     | Ability to Bypass                  |

|-------------------|----------------------------------------------------|------------------------------------|

| JIT-ROP [185]     | - ROP gadgets                                      | - Fine-grained ASLR                |