## Next Generation Frequency Disturbance Recorder Design and Timing Analysis

Lei Wang

Dissertation submitted to the faculty of Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of:

Doctor of Philosophy

in

**Electrical Engineering**

Committee Members:

Yilu Liu (Co-Chair)

Virgilio Centeno (Co-Chair)

Richard W. Conners

Patrick Schaumont

Shu-Ming Sun

May 21<sup>st</sup>, 2010

Blacksburg, Virginia

Keywords: synchronized sampling, phasor measurements, time synchronization, indoor GPS, Oscillator, RTAI

Copyright 2010, Lei Wang

# Next Generation Frequency Disturbance Recorder Design and Timing Analysis

Lei Wang

#### **Abstract**

In recent years, the subject of wide-area synchronized measurements has gained a significant amount of attention from the power system researchers. All of this started with the introduction of the Phasor Measurement Unit (PMU), which added a new perspective in the field of wide-area measurement systems (WAMS). With the ever evolving technologies over the years and the need for a more cost effective solution for synchronized frequency measurements, the Frequency Monitoring Network (FNET) was developed and introduced by the Power IT laboratory at Virginia Tech. The FNET is comprised of many Frequency Disturbance Recorders (FDR) geographically distributed throughout the United States. The FDR is a dedicated data acquisition device deployed at the distribution level, which allows for a lower cost and easily deployable WAMS solution. With Internet connectivity and GPS timing synchronization, the FDR provides high accuracy frequency, voltage magnitude and voltage angle data to the remote servers.

Although the current FDR design is up to the standard in terms of the measurement accuracy and portability, it is of interest to further the research into alternative architectures and leverage the ever advancing technologies in high speed computing. One of the purposes of this dissertation is to present novel design options for a new generation of FDR hardware design. These design options will allow for more flexibility and to lower reliance on some vendor specific components. More importantly, the designs seek to allow for more computation processing capabilities so that more accurate frequency and angle measurements may be obtained.

Besides the fact that the accuracy of frequency and angle measurement is highly dependent on the hardware and the algorithm, much can be said about the role of timing synchronization and its effects on accurate measurements. Most importantly, the accuracy

of the frequency and angle estimation is highly dependent on the sampling time of local voltage angles. The challenges to accurate synchronized sampling are two folds. One challenge has to do with the inherent fallbacks of the GPS receiver, which is relatively high cost and limited in availability when the satellite signal is degraded. The other challenge is related to the timing inaccuracies of the sampling pulses, which is attributed to the remainder that results from the imperfect division of the processor counter. This dissertation addresses these issues by introducing the implementation of the high sensitivity (indoor) GPS and network timing synchronization, which aims to increase the availability of frequency measurements in locations that would not have been possible before. Furthermore, a high accuracy timing measurement system is introduced to characterize the accuracy and stability of the conventional crystal oscillator. To this end, a new method is introduced in close association with some prior work in generating accurate sampling time for FDR. Finally, a new method is introduced for modeling the FDR based on the sampling time measurements and some results are presented in order to motivate for more research in this area.

## **Acknowledgement**

First and foremost I would like to express my sincere appreciations to my primary advisor, Dr. Yilu Liu, for her invaluable guidance and encouragements throughout my studies in the graduate school. In addition, she did not only allow me the flexibility to pursue my research interests but also gave me the opportunity to work in the industries where I have obtained valuable experiences in many different fields. Much can be said about her support throughout my studies and I will be forever in her debt for her advice, time and most of all friendship.

My sincere appreciation goes out to Dr. Richard Conners for his continuous support and invaluable guidance in all aspects of my research studies. Even upon retirement, he selflessly offered a tremendous amount of time to meet with me over the weekends to accommodate for my full-time work schedule. I would also like to send my sincere appreciation to Dr. Virgilio Centeno for serving as the co-advisor of my committee and provided the support throughout the years of my graduate studies. Finally, I would like to send my sincere appreciation to Dr. Patrick Schaumont and Dr. Shu-Ming Sun for serving as my committee members. The research work would not have been possible without their guidance and assistance.

Special thanks goes out to all of the past and present FNET team members, especially Javier Fernandez who initiated the testing of network time protocol and Bruce Billian for paving the way for the next generation FDR design. In addition, I would like to send special thanks to Dr. Kevin Zhong, Dr. Ryan Zuo, Dr. Emily Xu, Dr. Henry Zhang, Vivian Liang, Jon Burgett, Dr. Matt Gardner, Dr. Josh Wang, Dr. Will Kook, Dr. Mark Baldwin, Kevin Khan, Dr. Jason Bank, Dr. Jingyuan Dong, Dr. Tao Xia, Dr. Il-Yop Chung, Dr. Alan Yuan, Yingcheng Zhang, Lang Chen, Joanna Wu, Kelly Ye and Penn Markham. For it has been a great pleasure and an honor to have known and worked with these talented and dedicated colleagues.

This is dedicated to my parents, for whom education always comes first.

## **Table of Contents**

| Abstract  |                                                                | ii   |

|-----------|----------------------------------------------------------------|------|

| Acknow    | ledgement                                                      | iv   |

| Table of  | Contents                                                       | vi   |

| Table of  | Figures                                                        | ix   |

| List of T | ables                                                          | xii  |

| Chapter   | 1 Introduction                                                 |      |

| 1.1       | Motivation and Background                                      | 1    |

| 1.1.1     | Frequency Monitoring Network (FNET) and Frequency Disturbation | ance |

| Reco      | rder (FDR)                                                     | 2    |

| 1.1.2     | FDR Algorithm Review                                           | 3    |

| 1.1.3     | FDR Algorithm Implementation                                   | 9    |

| 1.1.4     | FDR Software Architecture                                      | 12   |

| 1.2       | Objectives                                                     | 13   |

| 1.3       | Organization                                                   | 15   |

| Chapter   | 2 Frequency Disturbance Recorder Design Requirements           | 16   |

| 2.1       | Background                                                     | 16   |

| 2.2       | FDR System Level Requirements                                  | 17   |

| 2.2.1     | Analog Input Subsystem                                         | 18   |

| 2.2.2     | Central Processing Unit                                        | 21   |

| 2.2.3     | Timing Subsystem                                               | 27   |

| 2.2.4     | Network Communication Subsystem                                | 28   |

| 2.3       | Limitations of the First and Second Generation FDR             | 28   |

| 2.3.1     | Timing Subsystem Limitations                                   | 29   |

|           | Computation Limitations                                        |      |

| 2.3.3     | Voltage Level and Communication Limitations                    | 35   |

| Chapter   | _                                                              |      |

| 3.1       | Background                                                     |      |

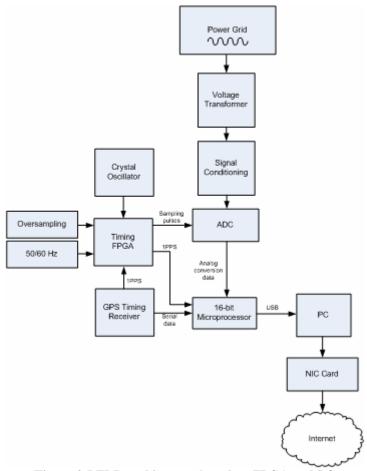

| 3.2       | Microcontroller Based Design                                   | 39   |

| 3.2.1     | Analog Subsystem                                               | 40   |

| 3.2.2     | Microcontroller                                                | 41   |

| 3.2.3     | Network Subsystem                                              | 43   |

| 3.3       | Digital Signal Processor Based Design                          | 43   |

| 3.3.1     | Analog Subsystem                                               | 45   |

| 3.3.2     | Microcontroller and DSP Co-processor                           | 45   |

| 3.3.3     | Network Communication Subsystem                                | 47   |

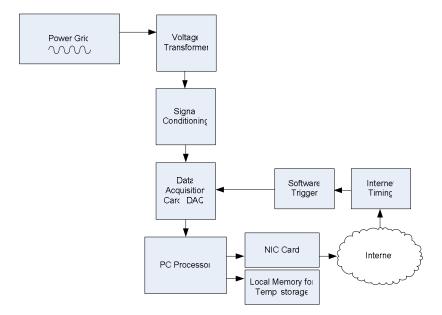

| 3.4       | Commodity Personal Computer Based Design with FPGA             | 47   |

| 3.4.1     | Microcontroller                                                |      |

| 3.4.2     | FPGA                                                           | 49   |

| 3.4.3     | Commodity PC                                                   | 50   |

| 3.5       | Standalone Commodity Personal Computer Based Design            |      |

| Chapter   |                                                                |      |

| -         | curacy Timing Reference for Frequency Disturbance Recorder     |      |

| 4.1       | Background                                                     |      |

| 4.1.1     | Global Positioning System                                      |      |

| 4.1.2      | Limitations of the GPS Accuracy                                     | 58         |

|------------|---------------------------------------------------------------------|------------|

| 4.1.3      | Alternative Global Navigation Satellite Systems                     | 60         |

| 4.2        | GPS Time Synchronization for FDR                                    | 61         |

| 4.2.1      | First Generation FDR GPS Receiver                                   | 61         |

| 4.2.2      | Second Generation FDR GPS Receiver                                  | 62         |

| 4.3        | Introduction to High Sensitivity GPS                                | 64         |

| 4.4        | Implementation of a High Sensitivity GPS for FDR                    | 67         |

| 4.5        | Availability and Accuracy Analysis                                  | 70         |

| 4.6        | Frequency and Angle Measurements with Indoor GPS                    |            |

| 4.7        | Recommendations                                                     | 85         |

| Chapter    | 5 Timing Measurement Based on a High Stability and High Resolution  | tion       |

| PC Cour    | nter                                                                | 88         |

| <b>5.1</b> | Background                                                          | 88         |

| 5.1.1      | Oscillator Characteristics and its Accuracy                         | 89         |

| 5.1.2      | Factors Affecting Crystal Oscillator Frequency Accuracy             | 92         |

| <b>5.2</b> | Timekeeping for COTS PC                                             |            |

| 5.2.1      | Hardware Clock                                                      |            |

| 5.2.2      | Software Clock                                                      | 96         |

| 5.3        | The Measurement Infrastructure                                      | 99         |

| 5.3.1      | RTAI (Real Time Application Interface) for Linux and Timers         | 101        |

| 5.3.2      | Measurement Software and RTAI Latency Mitigation                    | 102        |

| 5.4        | Measurement Results and Time Domain Analysis                        | 106        |

| 5.4.1      | PC Oscillator Accuracy and Stability Analysis                       | 109        |

| 5.5        | Summary                                                             | 115        |

| Chapter    | 6 Analysis of Frequency and Phasor Angle Measurements Based         | on         |

| Timing o   | of Conversion                                                       | 117        |

| 6.1        | Background                                                          | 117        |

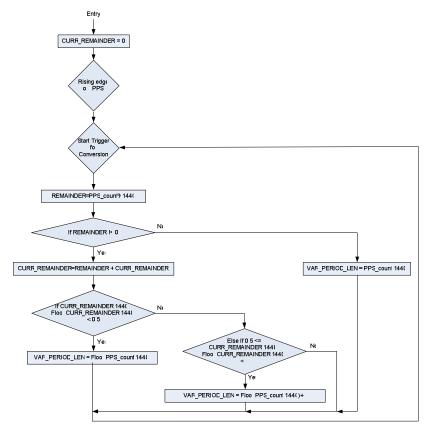

| 6.2        | Clock Division Algorithm                                            | 119        |

| 6.3        | Development of FDR Model                                            | 125        |

| 6.3.1      | Conceptual Design of FDR Model                                      | <b>126</b> |

| 6.3.2      | Measurement of FDR Timing for Conversion                            | <b>130</b> |

| 6.4        | Discussion of Results                                               | 136        |

| 6.5        | Summary                                                             | 139        |

| Chapter    | 7 PC Time Synchronization                                           | 141        |

| <b>7.1</b> | Background                                                          | 141        |

| 7.1.1      | Network Synchronizations                                            | 142        |

| 7.2        | An Overview of Network Time Protocol (NTP)                          | 144        |

| 7.2.1      | NTP version 4                                                       | 148        |

| 7.3        | Evaluation of NTP accuracy                                          |            |

| 7.3.1      | Characterization of NTP Time Synchronization on Different Operation | ting       |

|            | ems                                                                 |            |

| 7.3.2      | Measurement of TSC clock skew                                       | 158        |

| 7.4        | Summary                                                             |            |

| Chapter    | 8 Conclusions and Future Work                                       | 165        |

| 8.1        | Conclusions and Contribution                                        | 165        |

| 8.2        | Future Works                                                        | 168        |

| References                                                        | 170 |

|-------------------------------------------------------------------|-----|

| Appendix A                                                        | 176 |

| GPS Signals and Positioning Analysis                              |     |

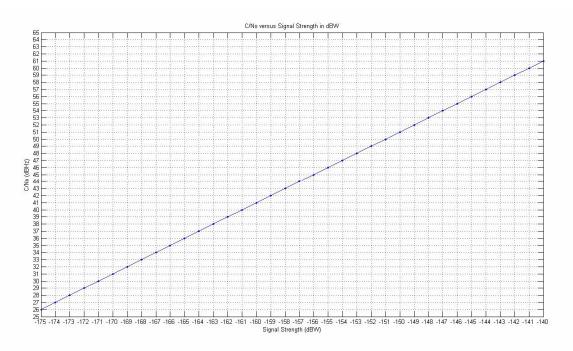

| I Review of GPS Signal Power Levels                               |     |

| II Relationship between Carrier to Noise Ratio and Power Levels   | 177 |

| IIIIndoor GPS positioning                                         |     |

| Appendix B                                                        |     |

| I NTP Servers                                                     |     |

| Appendix C                                                        |     |

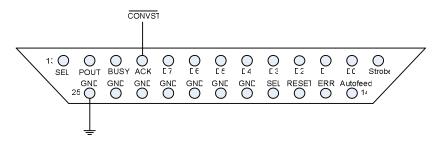

| I Parallel Port Connection with FDR Trigger for Conversion Signal |     |

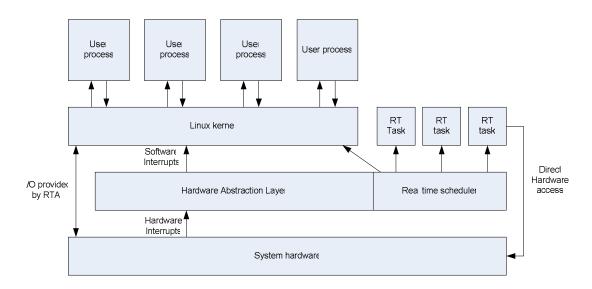

| II Brief Summary of RTAI                                          |     |

| IIIC Code for Measurement PC                                      |     |

## **Table of Figures**

| Figure 1.1 Frequency Monitoring Network (FNET) Architecture                    | 2    |

|--------------------------------------------------------------------------------|------|

| Figure 1.2 Illustration of resampling                                          | 8    |

| Figure 1.3 Flowchart of phasor estimation algorithm                            | .11  |

| Figure 1.4 Flowchart of initialization for phasor estimation algorithm         | .12  |

| Figure 1.5 Top level state machine of FDR                                      |      |

| Figure 2.1 Top-down design approach                                            | .16  |

| Figure 2.2 System block diagram of FDR                                         | .17  |

| Figure 2.3 Frequency and angle measurements using double precision arithmetic  | .23  |

| Figure 2.4 Frequency and angle measurement differences between two FDR un      | nits |

| using double precision arithmetic                                              | .23  |

| Figure 2.5 Frequency and angle measurements using single and double precis     | ion  |

|                                                                                | .24  |

| Figure 2.6 Frequency and angle measurement differences with single and dou     | ıble |

| precision arithmetic                                                           | .24  |

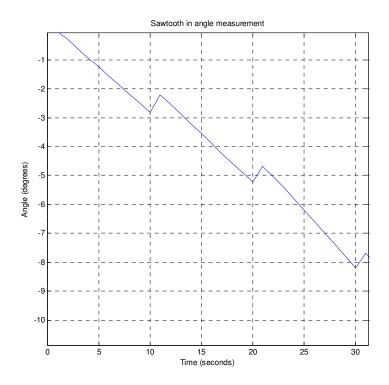

| Figure 2.7 Effect of sampling point residues                                   | .30  |

| Figure 2.8 Effect of waiting a constant time for each sampling second          | .31  |

| Figure 2.9 Phasor angle measurement from first generation FDR                  | 32   |

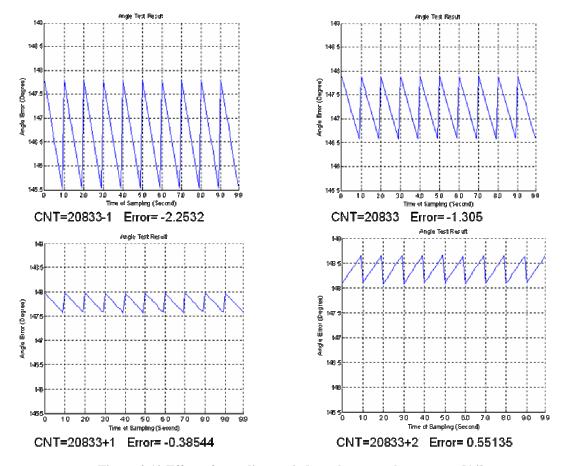

| Figure 2.10 Effect of sampling period on phasor angle accuracy [14]            | 33   |

| Figure 3.1 First generation FDR architecture                                   | .39  |

| Figure 3.2 Photo of first generation FDR                                       | .40  |

| Figure 3.3 Second generation FDR architecture                                  | .44  |

| Figure 3.4 Photo of the second generation FDR                                  | .44  |

| Figure 3.5 FDR architecture based on FPGA and PC                               | .48  |

| Figure 3.6 PC based FDR design block diagram                                   | 52   |

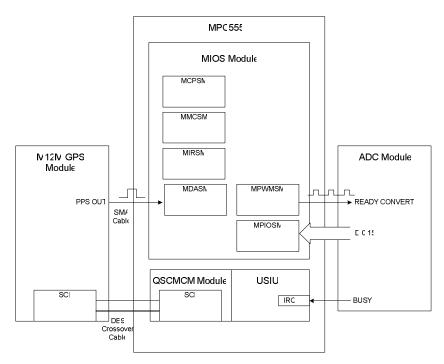

| Figure 4.1 M12M GPS module interface to the MPC555 and ADC                     | .63  |

| Figure 4.2 Test setup for comparing M12+ and M12M                              |      |

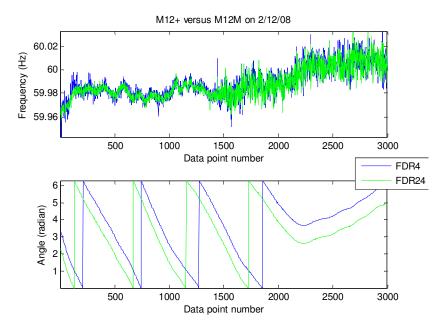

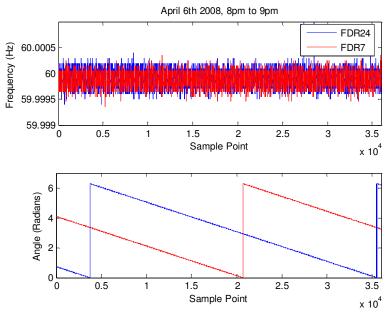

| Figure 4.3 FDR4 with M12+ versus FDR24 with M12M                               | .64  |

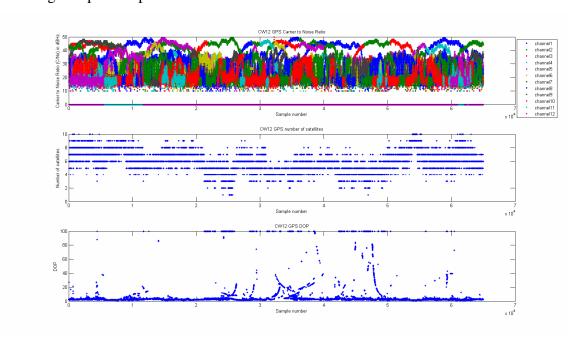

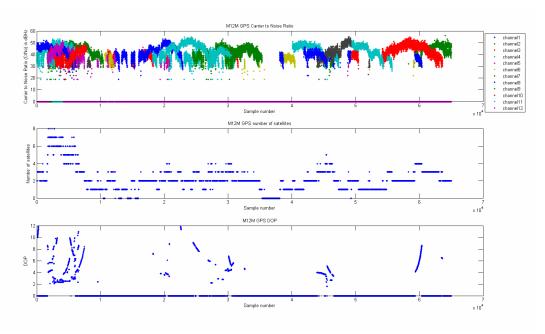

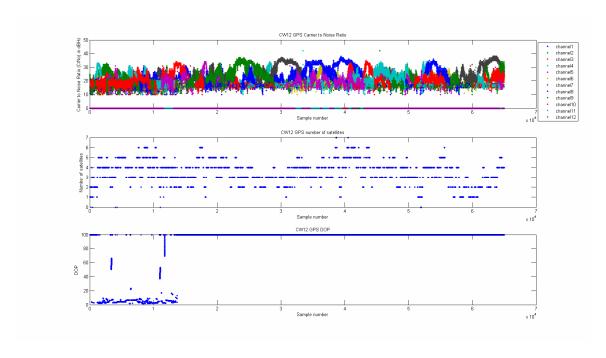

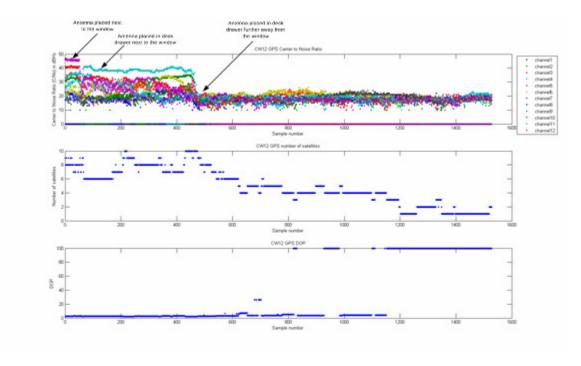

| Figure 4.4 Indoor GPS receiver data with antenna placed next to window         | .71  |

| Figure 4.5 Conventional GPS receiver data with antenna placed next to the wind | low  |

|                                                                                | .72  |

| Figure 4.6 Indoor GPS receiver data with antenna placed in a desk drawer       | .73  |

| Figure 4.7 Indoor GPS receiver data with signal degradation                    | .74  |

| Figure 4.8 Indoor GPS test setup using the AC source                           | .75  |

| Figure 4.9 Frequency and phasor angle measurements of the AC source signal us  | ing  |

| indoor GPS                                                                     |      |

| Figure 4.10 Indoor GPS test setup for completely isolated environment          | .77  |

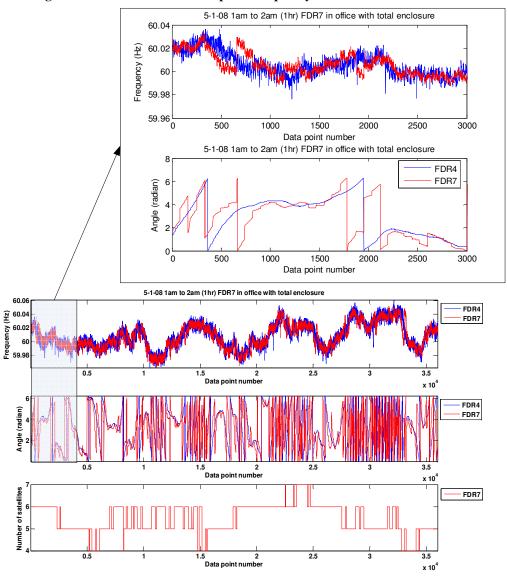

| Figure 4.11 Frequency and angle measurements with the number of acqui          |      |

| satellites on May 1 <sup>st</sup> from 1AM to 2AM                              |      |

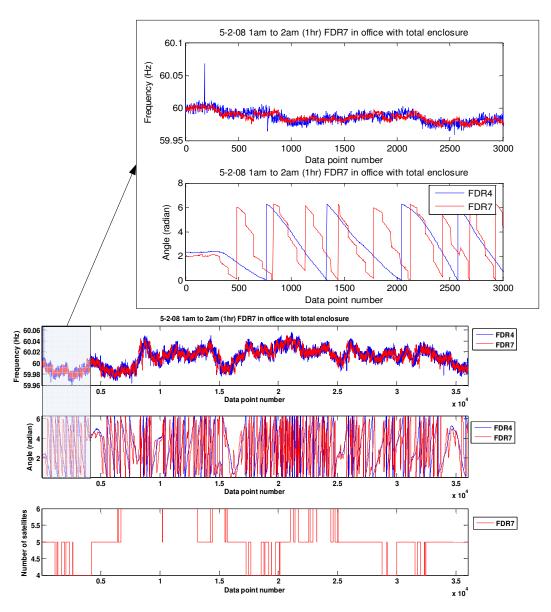

| Figure 4.12 Frequency and angle measurements with the number of acqui          |      |

| satellites on May 2 <sup>nd</sup> from 1AM to 2AM                              |      |

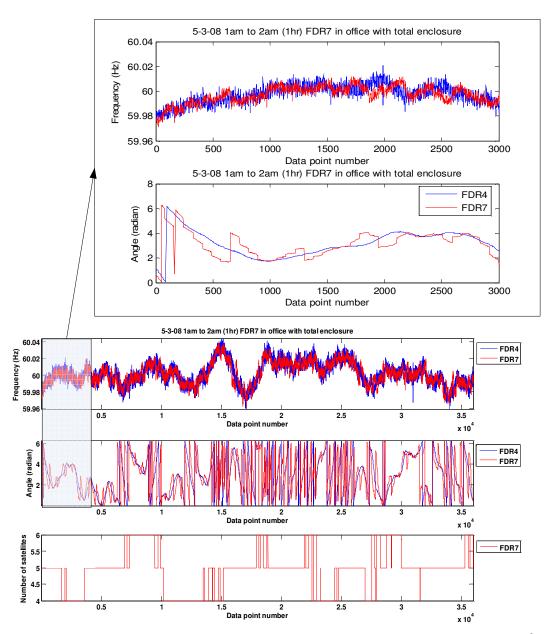

| Figure 4.13 Frequency and angle measurements with the number of acqui          | red  |

| satellites on May 3 <sup>rd</sup> from 1AM to 2AM                              | .79  |

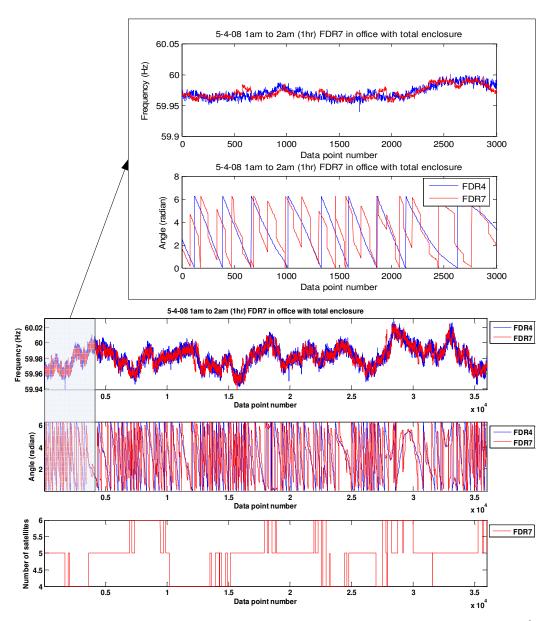

| Figure 4.14 Frequency and angle measurements with the number of acquired satellites on May 4 <sup>th</sup> from 1AM to 2AM80 |

|------------------------------------------------------------------------------------------------------------------------------|

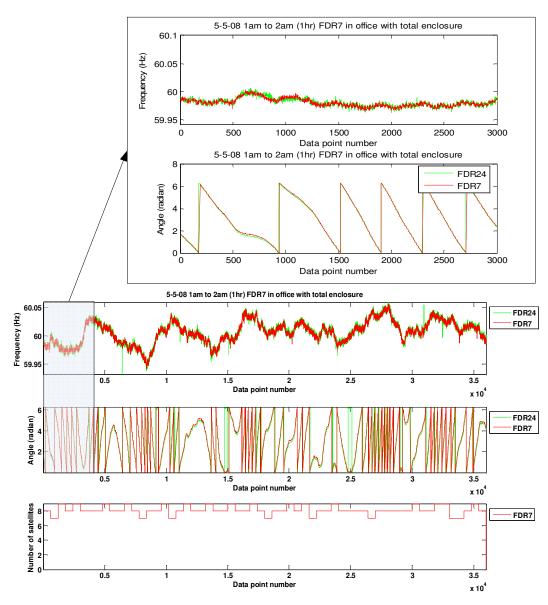

| Figure 4.15 Frequency and angle measurements with the number of acquired                                                     |

| satellites on May 5 <sup>th</sup> from 1AM to 2AM81                                                                          |

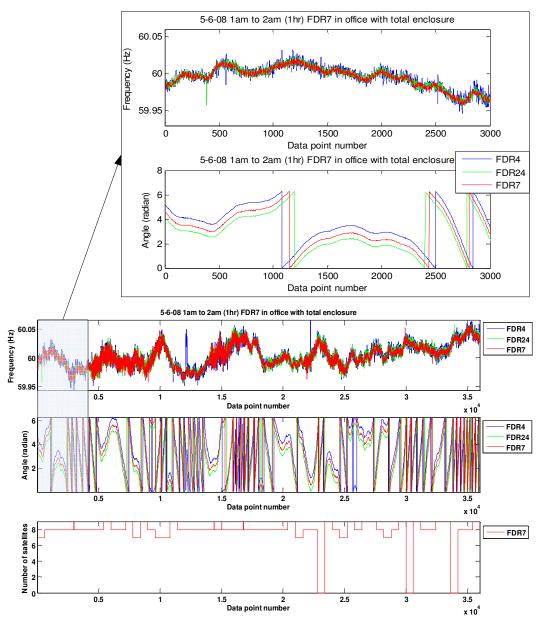

| Figure 4.16 Frequency and angle measurements with the number of acquired                                                     |

| satellites on May 6 <sup>st</sup> from 1AM to 2AM                                                                            |

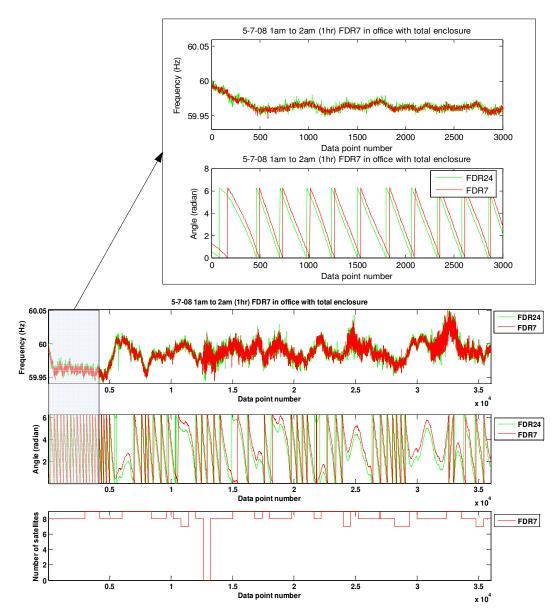

| Figure 4.17 Frequency and angle measurements with the number of acquired                                                     |

| satellites on May 7 <sup>st</sup> from 1AM to 2AM83                                                                          |

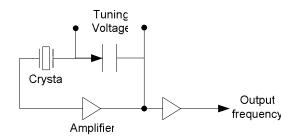

| Figure 5.1 Crystal Oscillator Block Diagram90                                                                                |

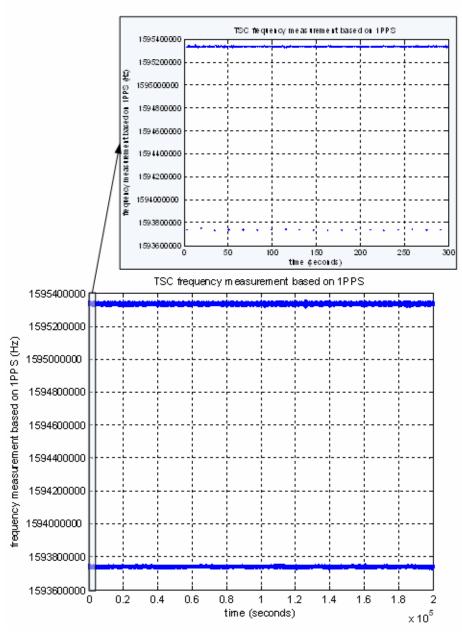

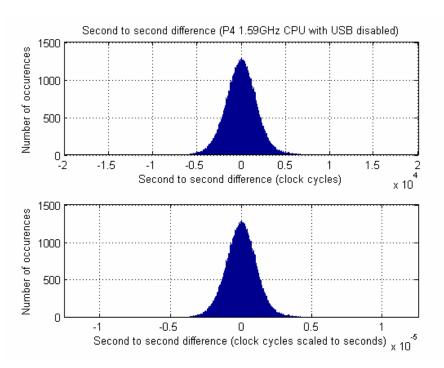

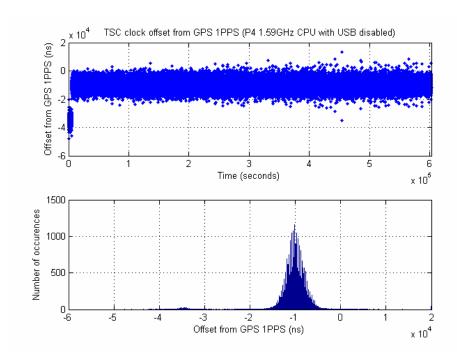

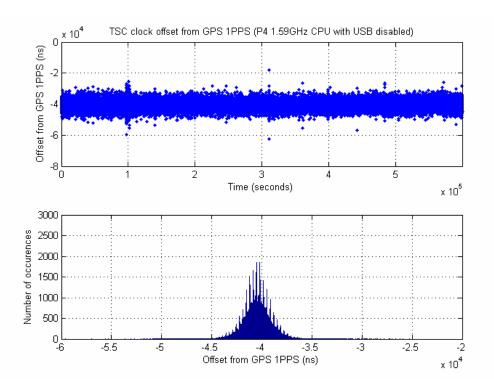

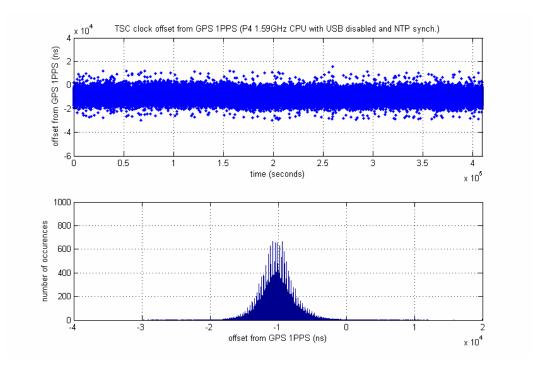

| Figure 5.2 Measured TSC frequency with USB controller enabled105                                                             |

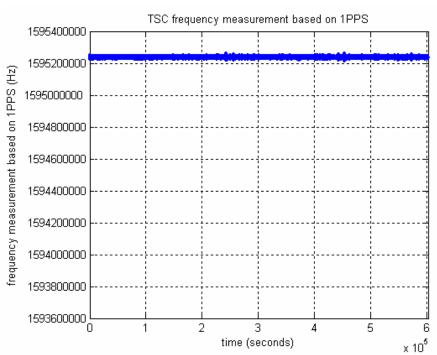

| Figure 5.3 Measured TSC frequency with USB controller disabled106                                                            |

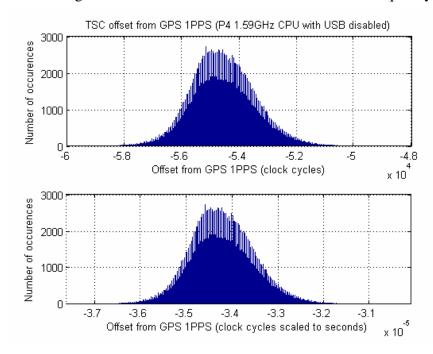

| Figure 5.4 Histogram of TSC frequency measurements – offset from nominal CPU                                                 |

| frequency110                                                                                                                 |

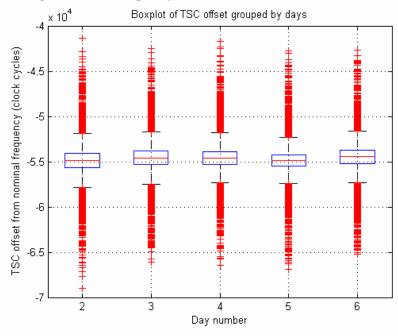

| Figure 5.5 Boxplot of TSC frequency measurements – offset from nominal CPU                                                   |

| frequency grouped by days110                                                                                                 |

| Figure 5.6 Histogram of TSC frequency measurements – second to second difference                                             |

| 112                                                                                                                          |

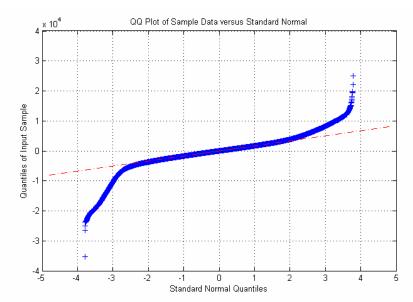

| Figure 5.7 Q-Q Plot of TSC frequency measurements – second to second difference                                              |

| 112                                                                                                                          |

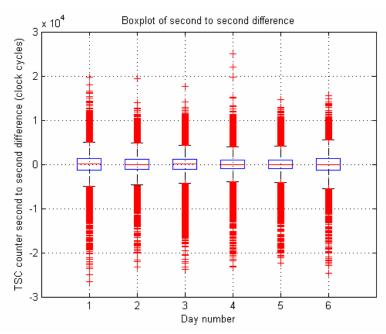

| Figure 5.8 Boxplot of TSC frequency measurements – second to second difference                                               |

| grouped by days113                                                                                                           |

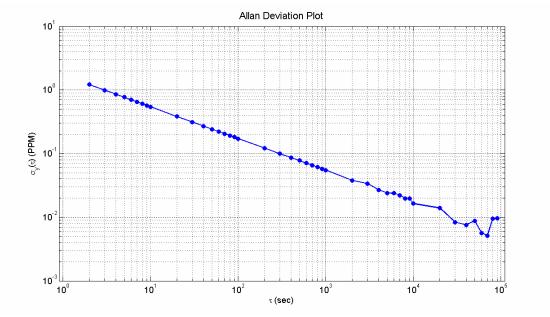

| Figure 5.9 Allan deviation plot of TSC frequency measurements with $\tau_0 = 1$                                              |

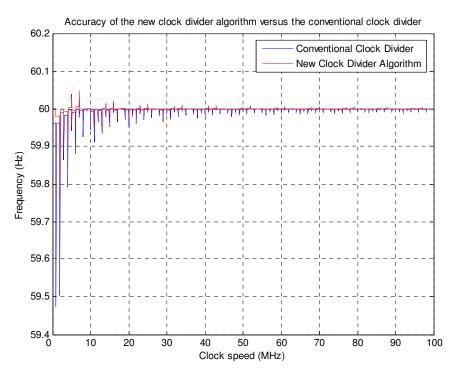

| Figure 6.1 Flowchart of clock divider algorithm121                                                                           |

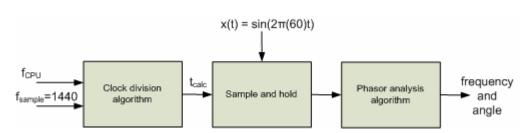

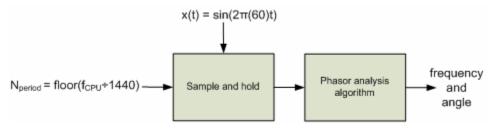

| Figure 6.2 Simulation of clock division algorithm for frequency and phasor angle                                             |

| measurements122                                                                                                              |

| Figure 6.3 Simulation of conventional PWM method for frequency and phasor angle                                              |

| measurements                                                                                                                 |

| Figure 6.4 Effect of sampling clock speed on frequency estimation – clock division                                           |

| algorithm versus conventional PWM method123                                                                                  |

| Figure 6.5 Effect of sampling clock speed on phasor angle estimation – clock division                                        |

| algorithm versus conventional PWM method124                                                                                  |

| Figure 6.6 Illustration of developing sampling time histogram128                                                             |

| Figure 6.7 Procedure for developing FDR model based on sampling time                                                         |

| measurement129                                                                                                               |

| Figure 6.8 Illustration of random sampling129                                                                                |

| Figure 6.9 Procedure for simulating FDR model based on sampling time                                                         |

| Figure 6.10 Timing measurement setup for FDR trigger for conversion signal 131                                               |

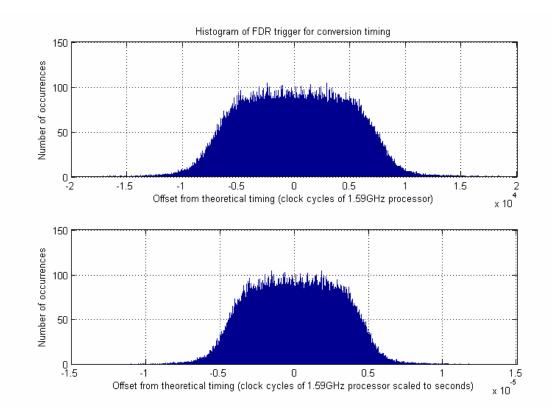

| Figure 6.11 Histogram of timing measurements for FDR trigger for conversion –                                                |

| offset from theoretical timing                                                                                               |

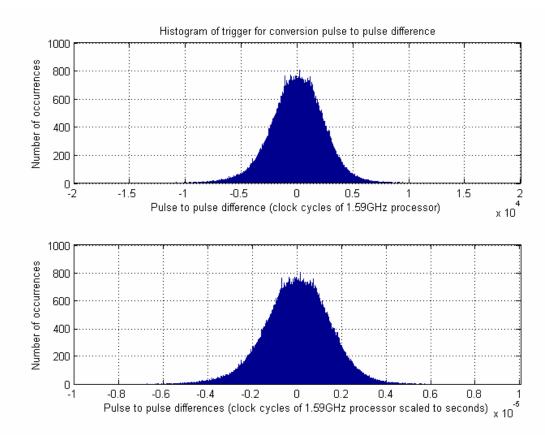

| Figure 6.12 Histogram of timing measurements for FDR trigger for conversion -                                                |

| pulse to pulse timing differences                                                                                            |

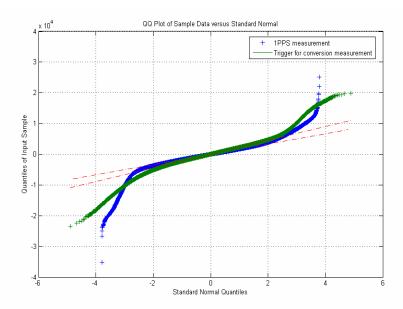

| Figure 6.13 Q-Q Plot of 1PPS measurement versus Q-Q Plot of trigger for                                                      |

| conversion measurement – pulse to pulse timing difference                                                                    |

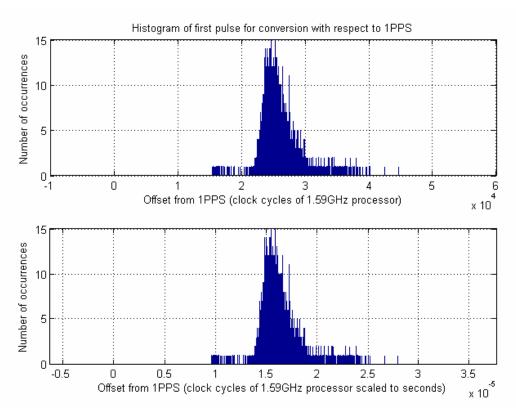

| Figure 6.14 First trigger for conversion latency with respect to 1PPS135                                                     |

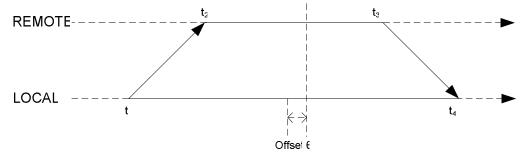

| Figure 7.1 NTP message format                                                                                                |

| Figure 7.2 NTP message exchange                                                                                              |

| <del></del>                                                                                                                  |

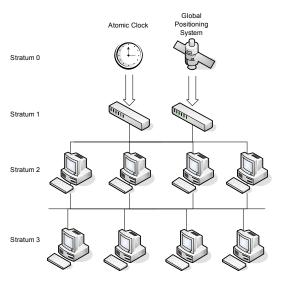

| Figure 7.3 Typical NTP Network Topology                                     | 147       |

|-----------------------------------------------------------------------------|-----------|

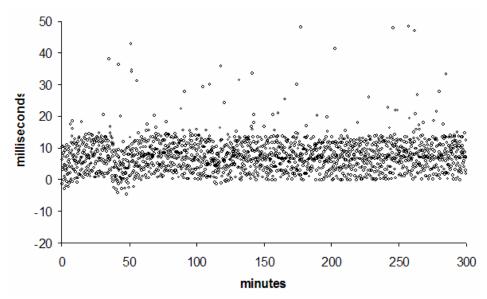

| Figure 7.4 Local clock synchronized by NTPD - offset given by W32Time       | 152       |

| Figure 7.5 NTP local clock offset from server clock for Windows XP Pro      | . – first |

| week of synchronization                                                     | 153       |

| Figure 7.6 NTP local clock offset from server clock for Windows XP Pro      | second    |

| week of synchronization                                                     | 154       |

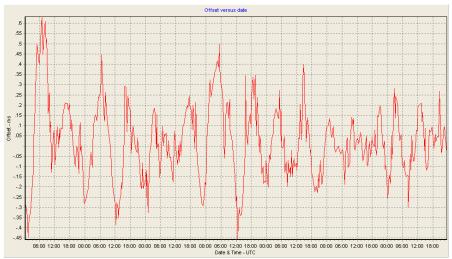

| Figure 7.7 NTP local clock offset from server clock for Ubuntu – first      | week of   |

| synchronizationsynchronization                                              | 156       |

| Figure 7.8 NTP local clock offset with respect to server clock for Ubuntu - | - second  |

| week of synchronization                                                     | 157       |

| Figure 7.9 TSC clock skew (with reboot)                                     | 161       |

| Figure 7.10 TSC clock skew measurement case 1                               |           |

| Figure 7.11 TSC clock skew measurement case 2                               | 162       |

|                                                                             |           |

| Figure A.1 Relationship between carrier to noise ratio and signal strength  | 177       |

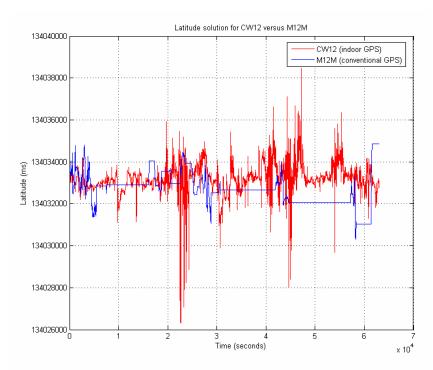

| Figure A.2 Comparison of CW12 with M12M in latitude solution                | 179       |

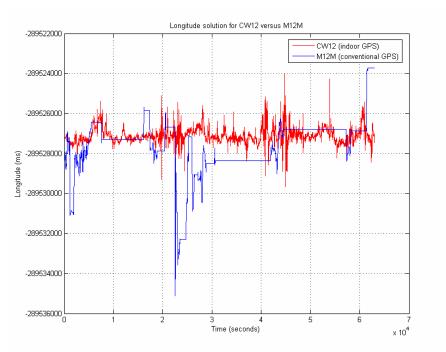

| Figure A.3 Comparison of CW12 with M12M in longitude solution               | 179       |

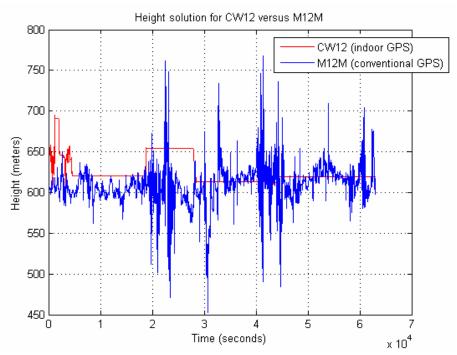

| Figure A.4 Comparison of CW12 with M12M in altitude solution                | 180       |

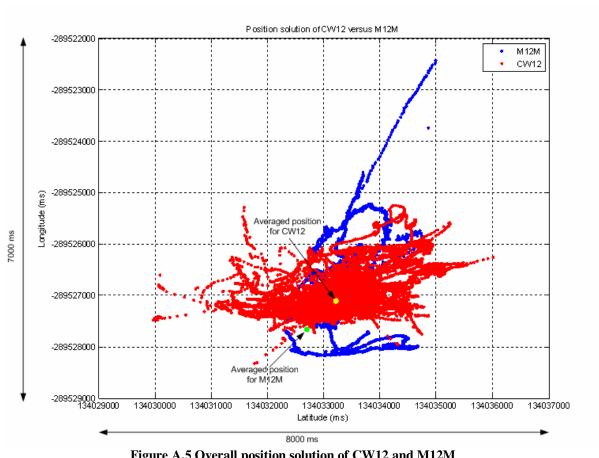

| Figure A.5 Overall position solution of CW12 and M12M                       | 180       |

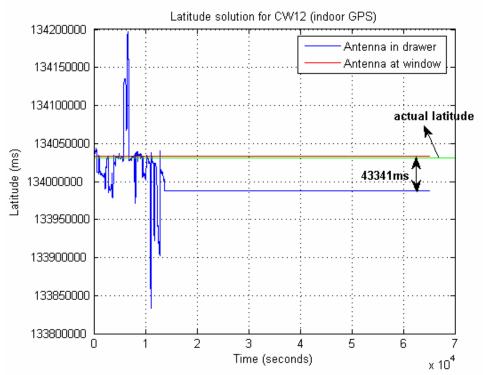

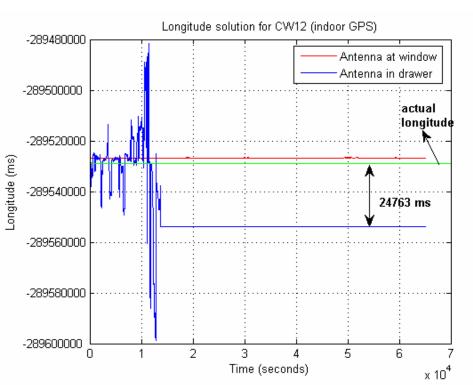

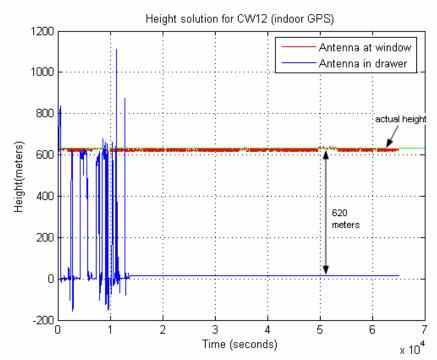

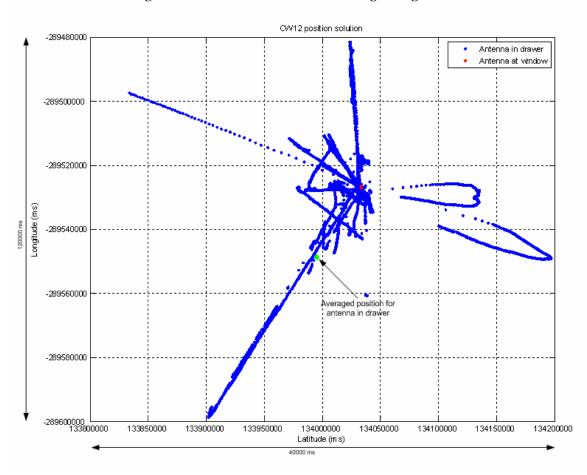

| Figure A.6 CW12 latitude solution with signal degradation                   | 182       |

| Figure A.7 CW12 longitude solution with signal degradation                  | 182       |

| Figure A.8 CW12 altitude solution with signal degradation                   | 183       |

| Figure A.9 Overall position solution of CW12 with signal degradation        |           |

| Figure C.1 PC interface with FDR trigger for conversion signal              |           |

| Figure C.2 RTAI Functional Block Diagram                                    |           |

## **List of Tables**

| Table 2-1 ADC architectures and attributes                                                       | 20         |

|--------------------------------------------------------------------------------------------------|------------|

| Table 2-2 Statistics of the differences in frequency measurements between FDR v                  |            |

| double precision arithmetic and FDR with single precision arithmetic                             | 25         |

| Table 3-1 Options for direct upgrade of Freescale MPC555                                         | 42         |

| Table 4-1 Initialization characteristics of indoor GPS receivers and FDR (                       | <b>GPS</b> |

| receiver                                                                                         | 67         |

| Table 4-2 Characteristics of GPS receivers - M12+, M12M and CW12                                 | 69         |

| Table 5-1 Oscillator characteristics                                                             | 92         |

| Table 5-2 Measurement PC specifications                                                          | 101        |

| Table 5-3 Statistics of the TSC frequency measurements                                           | 114        |

| Table 6-1 Frequency and phasor angle measurements using the new clock divis                      | sion       |

| algorithm with actual processor clock (input 60Hz with no phase shift)                           | 125        |

| Table 6-2 Statistics for the measurement of the trigger for conversion signal                    | 136        |

| Table 7-1 NTP local clock offset statistics for the first week - Windows XP I                    | Pro.       |

| versus Ubuntu                                                                                    | 156        |

| Table 7-2 NTP local clock offset statistics for the first week – Ubuntu                          | 157        |

| Table A-1 Statistics of M12M and CW12 position solution (ms)                                     | 181        |

| Table A-2 Statistics of CW12 position solution when operating under significant degradation (ms) | gnal       |

|                                                                                                  |            |

## **Chapter 1 Introduction**

### 1.1 Motivation and Background

The power transmission network is a highly complex and vast system, yet it is one of the most important networks in the world. However, experiences such as the August 14, 2003 blackout has shown a dire need of an improved power transmission network with high reliability and efficiency. In fact, billions of dollars were bid in the recent years to improve the reliability of the creaking system in the United States alone. To this end, power system researchers around the world are looking for methods to ensure stability in a much heavily loaded power transmission network. One method that has been increasingly attracting attention in the recent years is the wide area measurement system (WAMS). Such monitoring tool can be used to accurately capture real-time events and system dynamics. The need for monitoring and recording of power system data has been recognized for a long time and one of the most well known methods is the synchronized phasor measurements or also known as synchrophasors. Synchronized phasor measurements provide a standard of referring the phasor representation of a power system voltage or current to an absolute time reference. The absolute reference is provided in the form of common high accuracy clocks synchronized to coordinated universal time (UTC). The first high accuracy phasor measurement was made possible by the invention of phasor measurement units (PMU).

The invention of the PMU goes back to 1988, when the first PMU prototypes were developed at Virginia Tech and was later commercialized in the early 1990's. In order to monitor a complex wide area system like the power transmission network, there is a need for a synchronized monitoring solution with highly dynamic phasor measurement technique. To meet these needs, a Global Positioning System (GPS) receiver is used in the PMU in conjunction with the frequency estimation algorithm invented under the leadership of Dr. Arun Phadke. However, the high installation cost of PMU's limits its deployment capabilities. Early studies clearly point to the need for much wide system measurement coverage, coverage that can be quickly and economically obtained. To meet

these goals, an Internet based Frequency Monitoring Network (FNET) was proposed in 2001 by the PowerIT group at Virginia Tech, and has since been implemented [1].

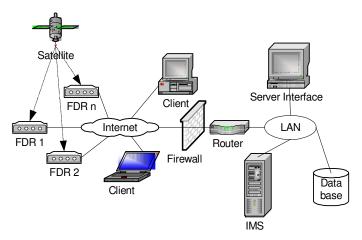

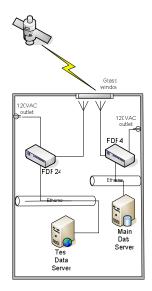

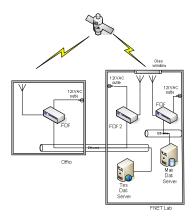

The FNET is composed of mainly the Frequency Disturbance Recorder (FDR) and the Information Management System (IMS) as it is shown in Figure 1.1. Somewhat similar to the PMU, the FDR acts as the sensor that performs local frequency data measurements and transmits the data to remote servers on the Internet. The FDR's are synchronized to the GPS and installed at 110V or 220V distribution voltage level of a typical office outlet. The IMS works as a central server, which provides data collection, storage, web service, post disturbance analysis and other information management functions. Working together, the FDR's and IMS provides continuous, real-time, wide area gathering of GPS time stamped frequency data for power system monitoring [1]. Based on these valuable data, the power system researchers can investigate a variety of protection and control applications, which can be used to improve the performance of the power transmission network.

Figure 1.1 Frequency Monitoring Network (FNET) Architecture

## 1.1.1 Frequency Monitoring Network (FNET) and Frequency Disturbance Recorder (FDR)

The FNET developed at Virginia Tech consists of several FDRs distributed across the United States and Canada as well as a central data collection server. The advantages of the FNET implementation are twofold. Firstly, each FDR interfaces with the electric grid

at low voltage levels with easily accessible wall sockets. Secondly, the cost of FDR hardware is on the order of \$1000 whereas the PMU ranges in several times of \$1000. However, there are tradeoffs to be made for such a low cost installation and design. On the low voltage level, the FDR will not be able to measure the three-phase quantities and increases the vulnerability to noises of various forms, including high frequency switching loads and electromagnetic interference (EMI). Overall, with the FNET's capability for mass coverage, its shortcomings are overwhelmingly overshadowed.

#### 1.1.2 FDR Algorithm Review

The phasor measurement algorithm has its roots from the days of Charles Proteus Steinmetz, who presented a paper on simplified mathematical description of the waveforms of alternating electricity. Since then, the word 'phasor' was invented and was eventually evolved into the calculation of real time phasor measurements.

The first generation of the FDR device was developed in 2002-2003 and there have been more than 40 units deployed in the United States power grid and a few 50Hz units in Europe and Africa. The first generation FDRs have virtually no algorithm error at 60Hz and their calculated frequency accuracy is better than  $\pm 0.0005$ Hz [1].

With the ever increasing advances in microprocessor technologies, more and more digital algorithms have been applied to calculating power system frequency, such as Modified Zero Crossing [8], Level Crossing [7], Least Squares Error [10], Newton Method [11], Kalman Filtering [12], Discrete Fourier Transform [6] and Smart Discrete Fourier Transform [9]. Each algorithm has its unique advantages and disadvantages. Nevertheless, phasor angle analysis provides fast and accurate frequency estimation over a wide range of frequency and the computation requirement is kept at a minimum for real-time implementation. From practical point of view, phasor angle analysis is recognized as the most appropriate for FDR measurement applications.

The phasor computation algorithm is based on the relationship that small frequency perturbation can be approximated by measuring the rate of the change of its phasor angle [6]. In mathematical terms this can be represented by the equation:

$$\frac{(d\phi)}{(dt)} \approx 2\pi(\Delta f)$$

Equation 1-1

Note that the phasor angle to frequency relationship in equation 1-1 is based on the assumption that frequency deviation from nominal is relatively small. To illustrate this, let's assume the input signal is a sinusoidal waveform written as:

$$x(t) = \sqrt{2}X\sin(2\pi(f_0 + \Delta f)t + \phi)$$

Equation 1-2

Where  $f_0$  is the nominal system frequency,  $\Delta f$  is the deviation from nominal frequency and  $\varphi$  is phasor angle.

Using the recursive discrete fourier transform, the new *rth* phasor can be expressed as [4]:

$$\overrightarrow{X}_{f_0+\Delta f}^{(r)} = \overrightarrow{X}_{f_0}^{(r)} e^{j(N-1)\pi} \frac{\Delta f}{Nf_0} e^{j\frac{2\pi\Delta f}{Nf_0}r} \frac{\sin\pi\frac{\Delta f}{f_0}}{N\sin\pi\frac{\Delta f}{Nf_0}} - \overrightarrow{X}_{f_0}^{*(r)} e^{-j\frac{2\pi\Delta f}{Nf_0}r} e^{-j(N-1)\left(\frac{2\pi}{N} + \frac{\pi\Delta f}{Nf_0}\right)} \frac{\sin\frac{\pi\Delta f}{f_0}}{N\sin\left(\frac{2\pi}{N} + \pi\frac{\Delta f}{Nf_0}\right)}$$

Equation 1-3

Where N is the number of samples taken per cycle. Now assuming that  $\Delta f$  is relatively small, the following relationships are introduced [4]:

$$\frac{\sin\frac{\pi\Delta f}{60}}{N\sin\frac{\pi\Delta f}{60N}} \approx 1$$

Equation 1-4

$$\frac{\sin\frac{2\pi\Delta f}{60N}}{N\sin\left(\frac{2\pi}{N} + \pi\frac{\Delta f}{60N}\right)} \approx 0$$

Equation 1-5

As a result, the second term of Equation 1-3 can be eliminated and the simplified expression can be written as [4]:

$$X_{f_0+\Delta f}^{(r)} = X_{f_0}^{(r)} e^{j(N-1)\pi \frac{\Delta f}{Nf_0}} e^{\frac{j2\pi\Delta fr}{Nf_0}}$$

Equation 1-6

Since  $\varphi_r$  and  $\varphi_{r+1}$  are defined as the phasor angle of the *rth* and (r+1)th phasor respectively, the change in phasor angle can be calculated as [3]:

$$\frac{d\phi}{dt} = \lim_{t \to 0} \frac{\phi_r - \phi_{r-1}}{t}$$

Equation 1-7

The denominator t can be represented by the time between consecutive samples and can be approximated by [3]:

$$t \approx \frac{1}{Nf_0}$$

Equation 1-8

Therefore as N is increased, t will approach zero and establish the relationship represented in Equation 1-1. Finally, the relationship between the frequency deviation and phasor angles can be obtained [3]:

$$f = f_0 + \Delta f = f_0 + \frac{1}{2\pi} \frac{d\phi}{dt}$$

Equation 1-9

At this point, it is important to note that as the system frequency approaches nominal system frequency, the phasor angle algorithm reaches its highest accuracy and conversely, the accuracy degrades as system frequency deviates from nominal system frequency. However, it will be seen later that a multiple resampling method can be used to minimize this error [3].

Given the relationship between phasor angle and frequency deviation, the implementation of the algorithm is discussed in [3] and being introduced here to provide as a reference. To illustrate phasor representation, one can write a sinusoidal input signal of frequency w in the form:

$$x(t) = \sqrt{2}x\sin(wt + \phi)$$

Equation 1-10 and its equivalent representation in phasor form:

$$Xe^{(j\phi)} = X\cos\phi + jX\sin\phi$$

Equation 1-11 Assuming that the signal  $x(t)$  is sampled N times per cycle of the nominal voltage

waveform to produce the sample set shown below:

$$x_k = \sqrt{2}x \sin\left(\frac{(2\pi)}{N}k + \phi\right)$$

Equation 1-12

The discrete fourier transform (DFT) of equation 1-10 can be written as:

$$X = \frac{1}{\left(\sqrt{2}\right)} \left(X_c + jX_s\right)$$

Equation 1-13

Where

$$X_{c} = \frac{2}{N} \sum_{k=0}^{(N-1)} X_{k} \cos\left(\frac{(2\pi)}{N}k\right)$$

Equation 1-14

$$X_{s} = -\frac{2}{N} \sum_{k=0}^{(N-1)} X_{k} \sin\left(\frac{(2\pi)}{N}k\right)$$

Equation 1-15

To obtain more phasor results the recursive phasor computation technique is used to obtain the successive phasor:

$$(X_c)^{(k+1)} = (X_c)^{(k)} + \frac{2}{N} \left( x_{(k+1)} - x_{(k+1-N)} \right) \cos \left( \frac{(2\pi)}{N} k \right)$$

$$(X_s)^{(k+1)} = (X_s)^{(k)} - \frac{2}{N} \left( x_{(k+1)} - x_{(k+1-N)} \right) \sin \left( \frac{(2\pi)}{N} k \right)$$

Equation 1-16

Where  $k = Nf_0 t$

Then the angle of the kth phasor can be calculated by:

$$\phi(k) = \tan^{-1}\left(-\frac{X_s^k}{X_c^k}\right)$$

Equation 1-18

Assuming that voltage phasor angles vary as a quadratic function with respect to the sample number,

$$\phi(k) = a_0 + a_1k + a_2k^2$$

Equation 1-19 Using a computation window of  $M$  phasor angles, the relationship between the phasor

angles and the sample number can be put into matrix form:

$$\begin{bmatrix} \phi_1 \\ \phi_2 \\ \phi_3 \\ \vdots \\ \phi_M \end{bmatrix} = \begin{bmatrix} 1 & 1 & 1 \\ 1 & 2 & 2^2 \\ \vdots & \vdots & \vdots \\ 1 & M & M^2 \end{bmatrix} \begin{bmatrix} a_0 \\ a_1 \\ a_2 \\ \vdots \\ M & M^2 \end{bmatrix}$$

**Equation 1-20**

Equation 1-18 can also be simply written as:

$\phi = Xa$  Equation 1-21

The unknown matrix a can be solved using the least error square solution:

$$a = \left[X^T X\right]^{-1} X^T \phi$$

Equation 1-22

Where the pseudo-inverse matrix  $[X^TX]^{-1}X^T$  is known as the gain matrix and can be computed offline.

Once the values of  $a_1$  and  $a_2$  are calculated, the frequency and rate of change of frequency can be calculated. Taking the derivative of Equation 1-17 with respect to k:

$$\frac{d\phi}{dk} = a_1 + 2a_2k$$

Equation 1-23

Then taking the derivative of Equation 1-21 with respect to time *t*:

$$\frac{dk}{dt} = Nf_0$$

Equation 1-24

The derivative of phasor angle with respect to time t can be written as:

$$\frac{d\phi}{dt} = \frac{d\phi}{dk}\frac{dk}{dt} = Nf_0\frac{d\phi}{dk} = Nf_0(a_1 + 2a_2Nf_0t)$$

Equation 1-25

Deviation in frequency,  $\Delta f$  can be obtained by:

$$\Delta f \approx \frac{1}{2\pi} N f_0(a_1 + 2a_2 N f_0 t)$$

Equation 1-26

$$\frac{df}{dt} \approx \frac{1}{2\pi} 2(N f_0)^2 a_2$$

Equation 1-27

Where *t* determines which instant inside the computation window the computed frequency corresponds to.

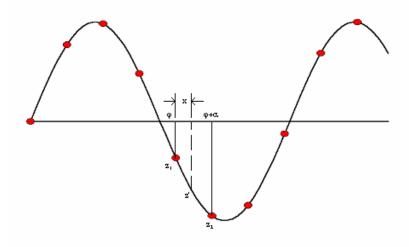

As mentioned before, the simplification of Equation 1-4 is made to obtain the relationship between phasor angle and deviated frequency. However, this approximation will introduce some error in estimation. The frequency estimation will be more accurate when the actual frequency approaches the frequency established for the sampling rate. Therefore, resampling the waveform with the estimated frequency and using the new phasor to perform corrections to the final estimation is rather an attractive solution [3]. In detail, assume the nominal frequency is 60Hz and the number of samples per cycle N is 24, resulting in 1440 samples taken per second. When the frequency has changed to 55 Hz, each cycle will now have about 26.18 samples instead of the 24 samples as indicated. To resolve this issue, re-normalization through resampling can be implemented to

interpolate the points so that there will always be 24 samples per cycle regardless of waveform frequency. The resampling algorithm can be summarized as the following:

$$Z_1 = Z_m \sin(\phi)$$

Equation 1-28

$$Z_2 = Z_m \sin(\phi + \alpha) = Z_m \sin \phi \cos \alpha + Z_m \cos \phi \sin \alpha$$

Equation 1-29 Where

$Z_m$  is the amplitude of the waveform

$\varphi$  is a sample instant and is an arbitrary known value

$\alpha$  is the interval between two samples at the new frequency and is equal to  $2\pi f_{new}/(Nf_0)$

Combining Equations 1-26 and 1-27 results in:

$$Z_m \cos \phi = \frac{(z_2 - z_1 \cos \alpha)}{\sin \alpha}$$

Equation 1-30

Let x be the fractional distance between  $z_1$  and  $z_2$ , the resampled point z' is then given by:

$$z' = Z_m \sin(\phi + x \alpha)$$

Equation 1-31

$$z' = Z_m \sin \phi \cos x \, \alpha + Z_m \cos \phi \sin x \, \alpha$$

Equation 1-32

$$z' = Z_1 \cos x \,\alpha + (z_2 - z_1 \cos \alpha) \,\frac{\sin x \,\alpha}{\sin \alpha}$$

Equation 1-33

Figure 1.2 Illustration of resampling

After the resampling points are found, the phasor angles of the new resampled data are computed and another estimation is made using Equation 1-20, Equation 1-24 and Equation 1-25 to obtain the correction frequency,  $\Delta f'$ , and the final rate of change of frequency. As a result, the final frequency estimation is computed by:

$f_{final} = f_0 + \Delta f + \Delta f'$  Equation 1-34

### 1.1.3 FDR Algorithm Implementation

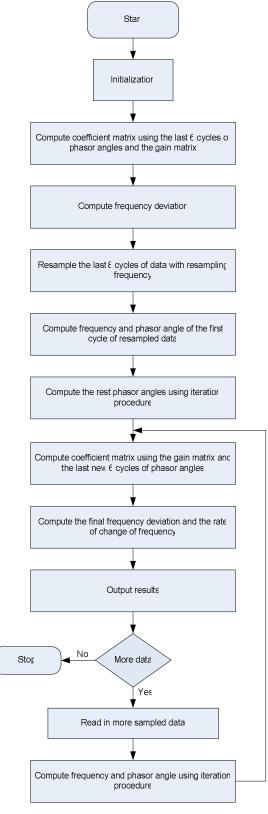

The FDR phasor algorithm is composed of three stages [4]:

- 1) Compute rough frequency estimation using raw voltage from sampled data.

- 2) Resample the waveform using the resampling frequency

- 3) Compute the correction frequency using the new resampled voltage and apply the correction to the rough estimation in step 1.

In the first two generation FDRs, embedded processors were used for phasor computation to allow for a compact and small size design. However, since a large amount of voltage is being collected and computation time is limited, considerations need to be given to maximizing computation speed and measurement accuracy. Hence, the actual implementation of the algorithm only uses certain selected phasors. This speeds up the computation time tremendously without significant losses in accuracy.

In the first two generation FDRs, the number of cycles to compute a frequency estimate was decided to be 6 nominal cycles. The number of samples per cycle used to compute a phasor is 24. So after initialization, a new phasor will be obtained every 1/1440 = 0.6944 millisecond. The whole estimation proceeds recursively with a sliding window length of 8 cycles and 6 cycles for estimating frequency. The reason to use an 8 cycle sliding window is because it takes one cycle of sampled data to compute the first phasor value. In addition, when the actual frequency is below nominal 60Hz (i.e. 55Hz), more data is needed to fulfill the 6 cycles criterion for resampling.

The implementation of the resampling is rather tricky. Since the resampling and subsequent frequency deviation computations are based on the first approximate frequency estimation, it is required to locate the exact instant in the waveform where the resampling frequency is used. This is not so significant when the waveform frequency is constant but is crucial when the frequency undergoes major frequency swings. Under such special circumstances it is practical to designate t in Equation 1-25 to be an appropriate value for the application. Since the measured frequency will exhibit an

oscillatory behavior due to its phasor angles, it is necessary to minimize this error by using the average of the estimated frequency as the resampling frequency. The average of the estimated frequency can be computed as:

$$f_r = \frac{\sum_{k=1}^{24} f_k}{24}$$

Equation 1-35

Where  $f_k$  is the first frequency estimate for k = 1 to 24 and  $f_r$  as the resampling frequency. At this point, it is necessary to make an assumption that the resampling frequency  $f_r$  is the frequency at the end of two and a half cycle in the first computation window. Such an assumption is valid for power system phasor measurement since the power system frequency deviation within the window is so small that the contribution to frequency estimation error is insignificant. Therefore, the second frequency estimation can be computed in the same manner as the first frequency estimation:

$$\Delta f' \approx \frac{1}{2\pi} N f_r(a_1 + 2a_2 C)$$

Equation 1-36 Where  $C$  is the sample instant of the estimation and is computed by:

$$C = \left( \left( N \left( \frac{6}{2} - \frac{1}{2} \right) - \left( 6N - 6N \cdot \frac{f_0}{f_r} \right) \right) \frac{f_r}{f_0} + \frac{N}{2} \right)$$

Equation 1-37

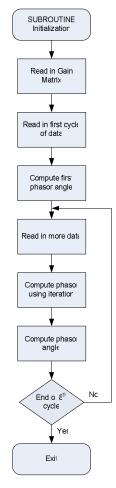

To illustrate the phasor measurement algorithm, Figure 1.3 and Figure 1.4 show a flowchart of the algorithm in [4].

Figure 1.3 Flowchart of phasor estimation algorithm

Figure 1.4 Flowchart of initialization for phasor estimation algorithm

#### 1.1.4 FDR Software Architecture

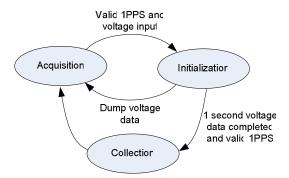

The FDR software architecture is composed of three states of operation including acquisition, initialization and collection. The state machine diagram of FDR is shown in Figure 1.5 and each state is summarized below.

Figure 1.5 Top level state machine of FDR

#### Acquisition

The acquisition state is obtained by meeting the requirement of GPS satellite acquisition. Since the voltage measurements need to be aligned to the UTC time, the FDR should not begin phase measurement until a valid GPS 1PPS is obtained. An internal timer is used to verify the accuracy of the 1PPS by measuring the length between one PPS rising edge to the next. If the length is within the bound of a pre-determined acceptable error range the measurement continues for the next PPS until four consecutive PPS meets the requirement, at which point the system begins phasor measurement.

#### **Initialization**

Once the FDR establishes an accurate 1PPS, the system begins the sampling process to feed the phasor measurement algorithm. The initialization process is allocated one second so that the synchronized phasor measurement can begin the next second. If GPS signal is still valid as verified in the acquisition state, the FDR will switch to collection state. If the GPS 1PPS is not valid, the FDR will reset to acquisition state and discard all measurements. This ensures the FDR is making phasor measurement only when accurate time synchronization is established.

#### **Collection**

When the initialization process ends, the FDR is capable of making phasor measurements continuously until either a loss of GPS or input voltage signal. If either errors occurs, the FDR will dump the current phasor measurements and go back to acquisition state.

## 1.2 Objectives

This introduction has covered the theoretical basis for frequency and phasor angle estimation, as well as the implementation of the algorithm along with the FDR software architecture. The goal of this dissertation is divided into several parts but the focus is on the design of the next generation FDR with emphasis on improving the accuracy and availability of synchronized sampling. In order to approach the subject of FDR design, it is essential to first understand the requirements at the system level. Then the top-down

design approach can be used. In addition, it is equally as important to address the drawbacks of the current FDR designs so that those drawbacks can be mitigated in the next generation design. Also, some FDR architectures are being proposed based on the design requirements and an evaluation is conducted to seek out the advantages and disadvantages of each.

Given the fact that the crystal oscillator is inaccurate in long term timekeeping and phasor angle measurement requires microseconds synchronization accuracy with respect to Universal Coordinated Time (UTC), the conventional GPS is used as a precision timing reference for FDR synchronized sampling. However, the conventional GPS is very much limited with respect to availability and cost. The signal attenuation effects are more pronounced for FDR applications since some of the newer office buildings comes with energy efficient glass windows, which prohibits the conventional GPS from acquiring GPS satellite signals. It is of interest to seek out alternate timing references that provides higher availability with similar level of accuracy.

What is also important to the accuracy of frequency and phasor angle measurement is the subject of oscillator characteristics since it is used to generate sampling pulses for synchronized measurements. To this end, it is important to provide some insights into its accuracy and stability. Thus far, there has not been any study conducted in characterizing the oscillator to produce accurate FDR sampling time. Ultimately, the characterization of the conventional oscillator should provide valuable insights to improve the FDR sampling time accuracy. Specifically, a high resolution timing measurement system can be used to measure accuracy and stability of the conventional oscillator. Furthermore, it is intended that such a measurement system will be able to not only measure the accuracy and stability of the crystal oscillator, but also provide some insights into the accuracy of different precision time synchronization sources as well as the FDR sampling time. To this end, models can be developed based on the sampling time and simulations can be performed to observe the effect of the sampling time on frequency and angle measurements. Ultimately, any errors associated with timing reference and sampling time will be directly reflected in the frequency and angle measurements.

#### 1.3 Organization

This dissertation is organized into 8 chapters starting with the introduction in the first chapter. The second chapter provides the background in FDR design requirements and specifications and addresses the limitations in the current FDR design. The third chapter goes over the evaluation of different FDR architectures with respect to its advantages and disadvantages. The fourth chapter addresses the issue with the obsolete GPS receiver and introduces the high sensitivity GPS receiver for high availability frequency and angle measurements. The fifth chapter summarizes the development of a high resolution and low cost timing measurement system. At the same time, measurements are taken from the processor clock counter to estimate the crystal oscillator accuracy and stability. The sixth chapter goes over the methodology to measure the FDR sampling time and takes the initial effort in modeling the FDR with the measurement data. The seventh chapter presents the network timing synchronization and proposes the use of network time protocol (NTP) for frequency estimation. Finally, the eighth chapter concludes the dissertation with a summary of the dissertation and future works.

# Chapter 2 Frequency Disturbance Recorder Design Requirements

## 2.1 Background

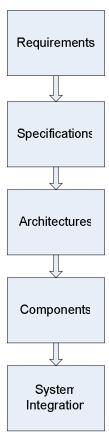

One of the most popular system design method for real-time and embedded systems is the top-down design approach. The top-down method is a natural way to approach a complex design task, mainly because it relies on multiple levels of abstraction to limit the number of independent concepts at each level of the design. Such design approach is very much required for the next generation FDR design as all of the requirements and specifications are being refined over many years of experience with the first and second generation FDRs. Major levels of abstraction in the design process can be visualized in Figure 2.1.

Figure 2.1 Top-down design approach

Starting at the very top, the requirements block gives an informal description of the FDR functionalities. The type of requirements should include both functional and non-

functional requirements. Functional requirements are solely the I/O (input/output) relationships and the non-functional requirements include timing, performance, cost, power consumption and physical size and weight. In the second block from the top, specifications should accurately define the application requirements. The specification should be simple and easily understood so that one can verify that it meets the system and overall expectation of the application requirements.

This chapter is focused on an overview of the requirements and specifications of FDR design. Also, some of the drawbacks of the present FDR designs will be presented so that the next generation design will be able to address these fallbacks and make the necessary improvements.

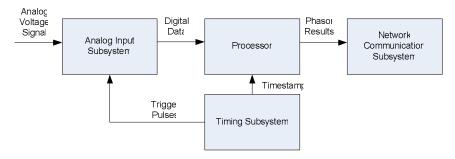

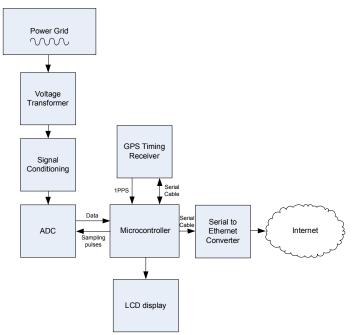

### 2.2 FDR System Level Requirements

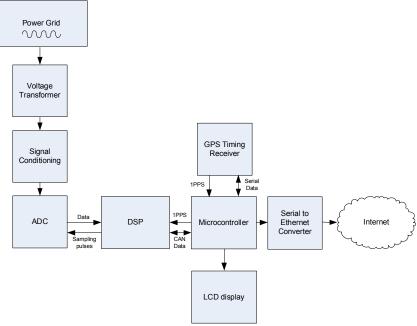

Similar to the PMU design but with some different design goals mainly focused on portability and ease of deployment, the FDR is composed of four major subsystems as it is shown in Figure 2.2, these include the processor, analog input subsystem, timing subsystem and network communication subsystem. The analog input subsystem is composed of the analog to digital converter, the transformer and the signal conditioning system. The timing subsystem is composed of an accurate frequency and time reference that is synchronized with the UTC time. Additionally, the timing subsystem should be capable of generating variable frequency pulses synchronized to UTC time for triggering the ADC for conversion. Finally, the network communication subsystem provides the means to transmit the measurement results to the central server at Virginia Tech.

Figure 2.2 System block diagram of FDR

Since portability and ease of deployment are the some of the main goals of the FDR design philosophy, an embedded system is the most obvious choice for such a design and it has been the norm for the first and second generation FDR design. As a result, should the next generation FDR continue to follow the embedded trend, it is worthwhile to highlight the requirements for the system.

At the minimum, the system should be able to perform floating point arithmetic. Furthermore, a counter with input capture is required to count the number of clock cycles in between each 1 PPS output from the GPS. In the case such that the counter register overflows, an interrupt will need to be generated to count the number of overflows in between pulses. The resultant number of clock cycles and overflows as measured by the timing subsystem is used to validate the accuracy of 1PPS, which is also a GPS status indicator. Additionally, a pulse width modulator subsystem with output compare is needed to trigger the external ADC for conversion. It is crucial for the counter, PWM and input capture and output compare to have at least 16 bits register for high resolution timing. Depending on the resolution of the ADC to be used, one external interrupt pin is needed to indicate the external ADC has latched data into its output register and a general purpose input/output (GPIO) subsystem is needed to receive data from external ADC. To allow for transmission of data to the main server and receiving timestamps from the GPS, there needs to be two serial communication interfaces (SCI). To allow for efficient I/O processing the system should also have an interrupt controller that is capable of assigning priorities to the interrupts. One such example would be a hierarchical interrupt system. For the external interfaces, there should be a liquid crystal display (LCD) interface circuit and its physical port for ribbon cable connection, a port for mounting the external ADC, and some breadboard area for input filter circuitry.

### 2.2.1 Analog Input Subsystem

The analog to digital converter is at the heart of the analog input subsystem. There is a variety of ADC's available today. However, some of the most widely used ADC architectures are the integrating ADC (Dual slope) [109], Flash ADC (Parallel ADC) [105], Pipelined ADC [108], Sigma Delta ADC [107], and SAR (Successive

Approximation Register) ADC [106]. The five architectures differ in conversion algorithm and encoding method, but what's more important to the design of FDR are characteristics of each ADC such as speed of conversion, resolution, size and price. Tradeoffs need to be made to select the device meeting all of the criteria. However, the relationship between such factors and the phasor estimation accuracy is rather complicated. So far there is no absolute requirement established for neither the resolution nor the synchronized data samples in the IEEE synchrophasor standards [2]. However, what is required by these standards is the phasor measurement be within 1% of TVE (total vector error) at the reporting times specified. TVE can be calculated by [2]:

$$TVE_{(k)} = 100\% \cdot \frac{\left| X_{MEAS(k)} - X_{IDEAI} \right|}{\left| X_{IDEAI} \right|}$$

**Equation 2-1**

Furthermore, the resolution of the ADC is not the only determining factor of phasor measurement accuracy, characteristics such as linearity, noise and gain stability provides the fundamental limitations on performance. Upon past experiences with the first and second generation FDR, 16 bits of SAR ADC resolution is more than adequate with 14 bits as the minimum resolution required for accurate FDR frequency measurement. Finally, a throughput rate of at least 100kSPS and minimized conversion time, power consumption and size is needed to meet portable real-time requirements.

In general, the SAR ADC is widely used for nearly all multiplexed data acquisition systems as well as in instrumentation applications. Due to its ease of interfacing and integration, it is being used in both the first generation and second generation FDRs. It has no pipeline delay and is available with resolutions up to 18 bits and sampling rates up to 5Msps [106].

For a wide variety of industrial measurement applications, the Sigma Delta and Integrating ADCs are the ideal candidates. With respect to the other ADC architectures, the integrating ADC is slow in speed with typical conversion speed of 20 milliseconds and low input bandwidths but their capability to reject high frequency noise and fixed low frequencies makes them attractive for certain industrial applications [107][109]. In

addition its popularity in the industrial applications, the Sigma Delta converter dominates in audio and voiceband markets. The inherent oversampling capability in these converters lowers the requirements on the ADC anti-aliasing filter. Nevertheless, the Sigma Delta converter has several drawbacks. Firstly, the filter does not provide attenuation at integer multiples of the modulator sampling frequency. Also, the speed of the conversion and filtering results in long latency between the start of the sampling cycle and the first digital output [107].

Flash ADCs and pipelined ADCs are known to be high speed converters. In particular, flash ADCs are more accustomed to converting signals with large bandwidths at high speeds. However, the Flash ADCs has relatively low resolution, consumes more power and can be comparatively expensive [105]. This drawback alone limits the Flash ADC market to high frequency applications that typically cannot be addressed any other way. On the other hand, the pipelined ADCs are used in applications requiring sampling rates ranging from approximately 5 Msps to greater than 100 Msps and have lower power consumption than that of the Flash ADC. The pipeline ADC has a good balance of size, speed, resolution and power dissipation, and has become increasingly popular to major data converter manufacturers [105]. Finally Table 2-1 summarizes some of the characteristics of the commonly used ADC architectures in [105][106][107][108][109].

Table 2-1 ADC architectures and attributes

| ADC types  | Flash         | SAR           | Integrating | Pipelined     | Sigma Delta     |

|------------|---------------|---------------|-------------|---------------|-----------------|

| Method     | Cascaded      | Binary search | Integration | Parallel      | Modulator and   |

|            | comparators   |               | and         | comparators   | filter          |

|            |               |               | comparator  |               |                 |

| Encoding   | Thermometer   | Successive    | Analog      | Digital       | Oversampling,   |

|            | code          | approximation | integration | Correction    | decimation      |

|            |               |               |             |               | filter          |

| Conversion | Constant      | Increase      | Constant    | Increase      | Tradeoff        |

| time       | with increase | linearly with | with        | linearly with | between data    |

|            | in resolution | resolution    | increase in | resolution    | output rate and |

|            |               |               | resolution  |               | resolution      |

| Resolution | Limited to 8  | 8 to 18       | 10 to 18    | 8 to 16       | 12 to 24        |

| Size       | Increases     | Increase      | Constant    | Increase      | Constant with   |

|            | exponentially | linearly with | with        | linearly with | increase in     |

|            | with          | resolution    | increase in | resolution    | resolution      |

|            | resolution    |               | resolution  |               |                 |

In addition to the ADC circuitry, the analog input subsystem has a signal conditioning component that is used to filter the transformer output, before it is being input to the ADC. Depending on the ADC and the transformer that is being implemented, the filter design could vary. However, the basic requirement remains the same, and that is to take a signal from the transformer and attenuate it to a lower voltage level acceptable to the ADC. Generally a simple voltage divider circuit can take care of this. In addition, to get rid of the high frequency noise that's associated with outlet voltages, a low pass filter is needed. In general, the low pass filter is essentially a second order anti-aliasing filter. An anti-aliasing filter could be passive or active but the smaller package size of active filter is rather attractive for FDR design. As a matter of fact, the first generation FDR used a passive filter design and the second generation FDR improvised by implementing an active filter design. Nevertheless, the design requirements remains the same, with a specified DC gain of unity, the filter needs to have a cutoff frequency of 720Hz [4].

#### 2.2.2 Central Processing Unit

The Central Processing Unit (CPU) in the FDR design can vary by a great deal and with the drastic improvements in digital processor technologies, many different solutions are available. Nevertheless, there are several criteria that need to be addressed in the processor selection process.

The very first criterion is deciding whether a floating point or fixed point processor is needed. The fundamental difference between the two is their respective numeric representation of data. While fixed point hardware performs strictly integer arithmetic, floating point hardware supports either integer or real arithmetic. Therefore, fixed point hardware has less bit width and it is more hardware efficient to implement than its floating point counterpart. Furthermore, a fixed point processor requires less hardware resources resulting in a smaller package and some cost reduction comparing with that of floating point. As a result, fixed point processors are more favored for high volume applications like digitized voice and telecom. However, the fixed point processor requires fixed point implementation in software, which requires careful consideration in precision

losses and overflow as a result of fixed point arithmetic. Although recent advances in more sophisticated C compilers has merged the gap between the software complexity of floating point and fixed point processor [18]. To this end, the fixed point processor still maintains an edge in cost savings compared to the floating point processor, with the trade-off of less precision.

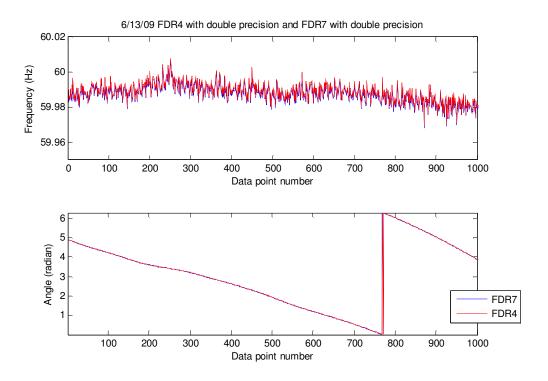

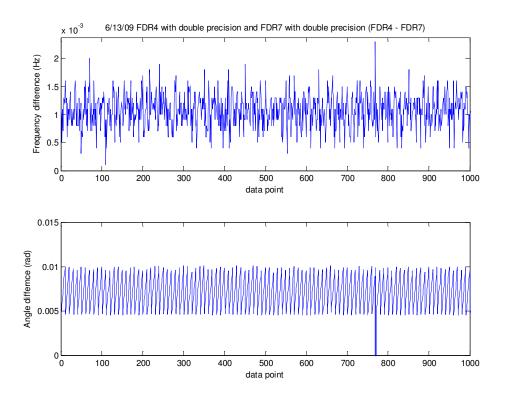

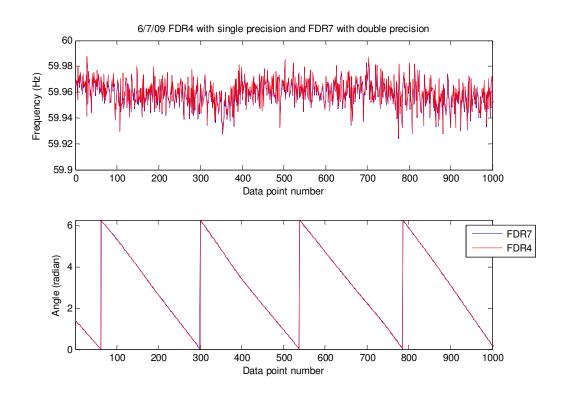

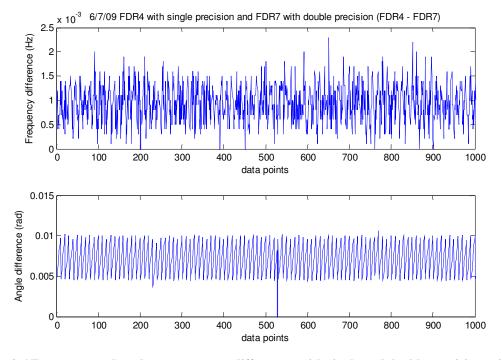

Another important factor to consider in the selection of processors is the number of bits for floating point arithmetic. The IEEE Standard for Binary Floating Point Arithmetic (IEEE 754-1985) is the most widely used standard for floating point computation with two commonly used formats, single precision and double precision. Almost all of today's microcontrollers and DSPs come with either single precision or double precision floating point unit (FPU). At this point it is necessary to take a look at the accuracy of phasor algorithm using both single precision and double precision arithmetic. Figure 2.3 shows the frequency and angle measurements conducted by two different FDRs with the same input. Also, Figure 2.4 shows the frequency and angle difference between the two FDRs. In comparison, Figure 2.5 and Figure 2.6 show the measurement results using single and double precision arithmetic, and the resulting differences between the two units respectively. If the measurements were perfect, the results would match each other between the two units. Nevertheless, the measurement differences between two FDRs with double precision arithmetic are similar in magnitudes compared to the measurement differences between two FDRs with single precision and double precision. Specifically, the average frequency measurement for the two units is within 0.1 mHz of each other, which is negligible for any FNET application. It is clear that single precision arithmetic is adequate for FDR algorithm implementation.

Figure 2.3 Frequency and angle measurements using double precision arithmetic

Figure 2.4 Frequency and angle measurement differences between two FDR units using double precision arithmetic

Figure 2.5 Frequency and angle measurements using single and double precision arithmetic

Figure 2.6 Frequency and angle measurement differences with single and double precision arithmetic

Table 2-2 Statistics of the differences in frequency measurements between FDR with double precision arithmetic and FDR with single precision arithmetic

|                    | 6/13/09 FDR4 – FDR7 freq. 6/7/09 FDR4 – FDR7 freq |           |

|--------------------|---------------------------------------------------|-----------|

| Minimum            | 0.0001                                            | -0.0005   |

| Maximum            | 0.0023                                            | 0.0024    |

| Mean               | 0.00108                                           | 0.0009527 |

| Median             | 0.0011                                            | 0.001     |

| Standard deviation | 0.0002826                                         | 0.0003576 |

| Range              | 0.002                                             | 0.0029    |

Generally processor crystal frequency is one of the characteristics that have being emphasized in determining the processor speed. However, there is often a misconception that the processor crystal frequency is the main contributor in processor performance. The fact of the matter is that with the ever improving technologies in multi-processor architecture and the addition of peripherals and micros running directly off the crystal oscillator circuitry, the crystal frequency value becomes more and more meaningless.

In order to help designers to better evaluate processors, the Embedded Microprocessor Benchmark Consortium (EEMBC) has established many common benchmarks to easily quantify microprocessor performance with respect to each other. Nevertheless, considering the speed requirement of the FDR with 4 phasor angles computed per cycle, each new frequency has to be computed approximately every 0.00417 seconds. This means that the first phasor angle computation, the first Least Error Square fit, the resampling process, the second phasor angle computation and the second Least Error Square fit all have to be completed in approximately 0.00417 seconds. The initialization process can be ignored for the moment since it only has to be done once. A rough estimate of number of floating point operations in the algorithm is about 15000 operations per frequency estimation.

With 4 phasor angles computed per cycle, the processor needs to be able to perform at least 3.6 MFLOPS (million floating point operations per second) [3]. With today's fast processors, this requirement can be easily met. However, this requirement is rather misleading due to architecture differences of the processor. A study was conducted in [80] to evaluate the MFLOPS measurement in computer systems and the study indicates

that MFLOPS was a consistent measure of performance in computer systems up till 1984. For systems produced after 1985, MFLOPS became more dependent on architecture, configuration, and application so that a simplified model can be used to evaluate MFLOPS measure. Generally, MFLOPS measurement can be used more consistently for processors of the same architecture but the comparison becomes more complex across different architectures. Due to this reason alone, it is important to limit the architecture selection to a certain type and only then will the comparison in MFLOPS be valid.

There are two classification groups for the instruction set of processors. These include the CISC (complex instruction set computer) and the RISC (reduced instruction set computer). For the embedded version of FDR design, justifications can be made to use the RISC based processors. This is mainly due to considerations in simplicity, speed and short development cycle. The simplified instruction set has much emphasis on software whereas the complex instruction set puts its emphasis on hardware. As a result, the RISC based processor tends to spend more transistors on memory registers whereas the CISC based processor spends more transistors on storing complex instructions. As the price of memory chips decrease over the years, the RISC architecture has been gaining more attention in the embedded market. Additionally, the standard feature of pipelining in RISC processors allows for higher efficiency and faster processing speeds. Ultimately, with the exception of embedded processors, the boundary between RISC and CISC is becoming blurred in the recent years due to the fact that both architectures are evolving for the common goal of high performance computing.

Most of the processors today have some form of built in ROM (Read Only Memory) and RAM (Random Access Memory). An approximation of the amount of data memory needed can be approximated by the data size of the variables. With single precision representation, the amount of RAM is approximated to be 3120 bytes with the program memory estimated to be around 64000 bytes. However, additional memories are needed for either a high precision trigonometric look up table (LUT) or a math library for implementing the trigonometric functions. Specifically there needs to be at least functions for sine, cosine and arc tangent and the precision needs to be around 0.00001 radians [3].

To store a table with all of these values require a large amount of ROM. The alternative is to tradeoff speed against memory by approximate the trigonometric functions using methods such as polynomials approximation or Goertzels algorithm.

#### 2.2.3 Timing Subsystem

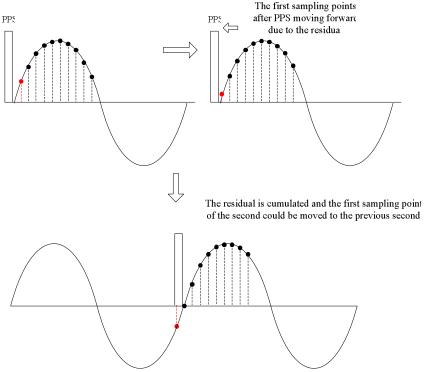

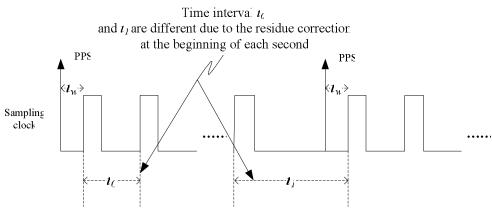

Phase angle measurement accuracy is highly dependent on the sampling of local voltage angles. To provide high accuracy absolute time for synchronized sampling and timestamps for frequency and angle measurements, the FDR uses a GPS timing receiver in the first and second generation design. In order to synchronize the sampling of voltages to GPS timing, the processor uses the pulse width modulation (PWM) subsystem to generate the trigger for conversion signal for the ADC upon the rising edge of 1PPS. Such sampling scheme is used in both of the first two generations FDR.

The challenges to the design of the timing subsystem are two folds, one requirement being the need for a common and accurate timing reference and the other is related to the accuracy of the trigger for conversion signal. The IEEE synchrophasor standard states that the timing signal shall be accurate enough to keep the Total Vector Error (TVE) within the limits defined by the user-required compliance level. In connection to this it is important to note that an uncertainty of 1 microsecond on the synchronization signal leads to a phase angle error of 0.022/0.018 degrees for a 60/50Hz system [2]. In order to meet the 1% TVE requirement, assuming that the input voltage is free of noise, a maximum synchronization uncertainty of 26 microseconds is required for a 60Hz system and 31 microseconds for a 50Hz system (phase error of 0.57 degree causes 1% TVE) [2].

In order to obtain a common timing reference for the FDR acquisition process, it is essential to achieve an accurate synchronization of the sampling pulses. This requires the deployment of a timing source that may be internal or external to the FDR. In addition, the timing signal should provide enough information to provide the second-of-century in agreement with UTC. It must be available with minimum interruption at all measurement locations throughout the interconnected grid [17].

An obvious solution to synchronized sampling would be using a GPS disciplined oscillator with the nominal frequency in integer multiples of the sampling frequency. However, such a design is not practical as the oscillator will need to be changed when the sampling frequency is changed to a number that is not wholly divisible by the oscillator clock. In addition, restrictions are set to the oscillator frequency based on the sampling frequency. Past experience has shown that while using the internal processor oscillator clock to generate trigger for conversion signals is effective, it still has some intrinsic drawbacks in accuracy and flexibility.

At last, in assessing the performance of synchronization sources for FDR, it is important to consider factors such as accuracy, availability, continuity, reliability, integrity and the coverage [17].

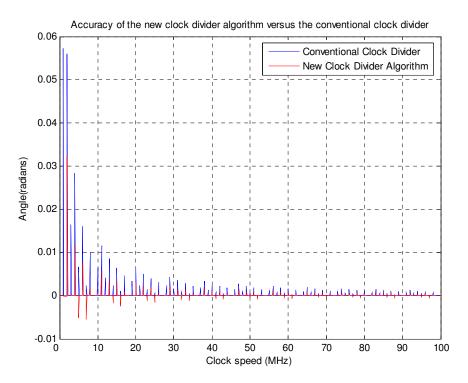

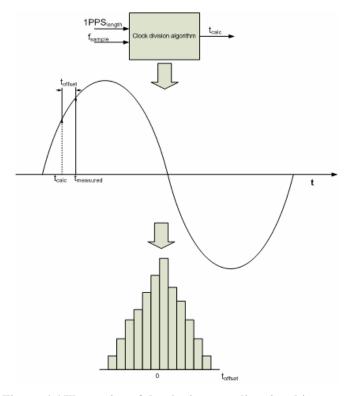

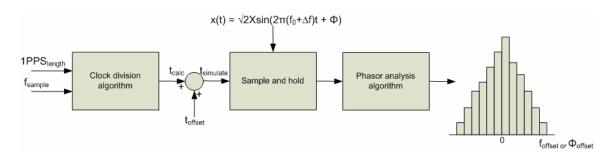

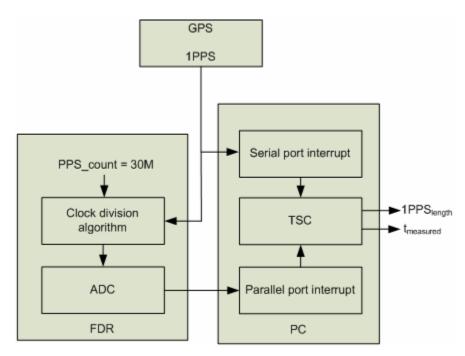

#### 2.2.4 Network Communication Subsystem