## Directive-Based Data Partitioning, Pipelining and Auto-Tuning for High-Performance GPU Computing

Xuewen Cui

Dissertation submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in

Computer Science and Application

Wu-chun Feng, Chair Calvin J. Ribbens Adrian Sandu Hao Wang Thomas R. W. Scogland Bronis R. de Supinski

September 11, 2020 Blacksburg, Virginia

Keywords: Pipelining, GPUs, Partitioning, OpenMP, Streaming Multiprocessor, Multi-core, Persistent Thread Blocks, Auto-Tuning, Machine Learning Copyright 2020, Xuewen Cui

### Directive-Based Data Partitioning, Pipelining and Auto-Tuning for High-Performance GPU Computing

#### Xuewen Cui

#### (ABSTRACT)

The computer science community needs simpler mechanisms to achieve the performance potential of accelerators, such as graphics processing units (GPUs), field-programmable gate arrays (FPGAs), and co-processors (e.g., Intel Xeon Phi), due to their increasing use in stateof-the-art supercomputers. Over the past 10 years, we have seen a significant improvement in both computing power and memory connection bandwidth for accelerators. However, we also observe that the computation power has grown significantly faster than the interconnection bandwidth between the central processing unit (CPU) and the accelerator.

Given that accelerators generally have their own discrete memory space, data needs to be copied from the CPU host memory to the accelerator (device) memory before computation starts on the accelerator. Moreover, programming models like CUDA, OpenMP, OpenACC, and OpenCL can efficiently offload compute-intensive workloads to these accelerators. However, achieving the overlapping of data transfers with computation in a kernel with these models is neither simple nor straightforward. Instead, codes copy data to or from the device without overlapping or requiring explicit user design and refactoring.

Achieving performance can require extensive refactoring and hand-tuning to apply data transfer optimizations, and users must manually partition their dataset whenever its size is larger than device memory, which can be highly difficult when the device memory size is not exposed to the user. As the systems are becoming more and more complex in terms of heterogeneity, CPUs are responsible for handling many tasks related to other accelerators, computation and data movement tasks, task dependency checking, and task callbacks. Leaving all logic controls to the CPU not only costs extra communication delay over PCI-e bus but also consumes the CPU resources, which may affect the performance of other CPU tasks. This thesis work aims to provide efficient directive-based data pipelining approaches for GPUs that tackle these issues and improve performance, programmability, and memory management.

### Directive-Based Data Partitioning, Pipelining and Auto-Tuning for High-Performance GPU Computing

#### Xuewen Cui

#### (GENERAL AUDIENCE ABSTRACT)

Over the past decade, parallel accelerators have become increasingly prominent in this emerging era of "big data, big compute, and artificial intelligence." In more recent supercomputers and datacenter clusters, we find multi-core central processing units (CPUs), many-core graphics processing units (GPUs), field-programmable gate arrays (FPGAs), and co-processors (e.g., Intel Xeon Phi) being used to accelerate many kinds of computation tasks.

While many new programming models have been proposed to support these accelerators, scientists or developers without domain knowledge usually find existing programming models not efficient enough to port their code to accelerators. Due to the limited accelerator on-chip memory size, the data array size is often too large to fit in the on-chip memory, especially while dealing with deep learning tasks. The data need to be partitioned and managed properly, which requires more hand-tuning effort. Moreover, performance tuning is difficult for developers to achieve high performance for specific applications due to lack of domain knowledge. To handle these problems, this dissertation aims to propose a general approach to provide better programmability, performance, and data management for the accelerators. Accelerator users often prefer to keep their existing verified C, C++, or Fortran code rather than grapple with the unfamiliar code. Since 2013 [57], OpenMP has provided a straightforward way to adapt existing programs to accelerated systems. We propose multiple associated clauses to help developers easily partition and pipeline the accelerated code. Specifically, the proposed extension can overlap kernel computation and data transfer between host and device efficiently. The extension supports memory over-subscription, meaning the memory

size required by the tasks could be larger than the GPU size. The internal scheduler guarantees that the data is swapped out correctly and efficiently. Machine learning methods are also leveraged to help with auto-tuning accelerator performance.

# Acknowledgments

First, I would like to thank my advisor, Professor Wu-chun Feng. Throughout my Ph.D. career, Wu has provided me with invaluable support and knowledge. He has been leading me to the HPC area and providing me with opportunities to learn techniques as well as better communication skills. I've learned a lot from him about how to write and review papers, how to present my work, and how to establish productive collaboration with others.

My sincere thanks to my other committee members: Professor Calvin J. Ribbens, Professor Adrian Sandu, Dr. Hao Wang, Dr. Thomas RW Scogland, and Dr. Bronis R. de Supinski for all their time, comments, suggestions and assistance about my research work during my Ph.D. journey.

I have also spent valuable time collaborating with Lawrence Livermore National Laboratory throughout my Ph.D. as an intern at LLNL, which also had a significant impact on my research and technique knowledge. Special thanks go to Dr. Thomas RW Scogland(again) and Dr. Bronis de Supinski(again).

I am so fortunate to have been around wonderful researchers during my Ph.D.. We lived and fought together during those hard but happy days. Especially thanks to Dr. Hao Wang(again), Kaixi Hou, Jing Zhang, Xiaodong Yu, Da Zhang, Sarunya (Kwang) Pumma, and Sajal Dash. I cannot forget those nights that we worked together to catch paper submission deadlines.

I owe a debt of gratitude to Dr. James Lin for leading me to the area of HPC when I was still a third-year undergraduate student.

Finally, and most importantly, I wish to thank my family for their unconditional love, support, and encouragement. I will be forever grateful to my parents, Yanjun Cui and Zhijie Ma for teaching and supporting me during the last 29 years.

**Funding Acknowledgment** This thesis work was in part performed under the auspices of the U.S. Department of Energy by Lawrence Livermore National Laboratory under Contract DE-AC52-07NA27344. It was also supported in part by AFOSR BRI Project and AFOSR Machine Learning Project.

# Contents

| Li | List of Figures xii |                                                                             |    |  |  |

|----|---------------------|-----------------------------------------------------------------------------|----|--|--|

| Li | st of               | Tables xvi                                                                  | ii |  |  |

| 1  | Intr                | oduction                                                                    | 1  |  |  |

|    | 1.1                 | Motivation                                                                  | 1  |  |  |

|    | 1.2                 | Directive-based Partitioning and Pipelining for Graphics Processing Units . | 6  |  |  |

|    | 1.3                 | Block-Level Data Pipelining for Graphic Processing Units                    | 7  |  |  |

|    | 1.4                 | IterML: Iterative Machine Learning for Intelligent Parameter Pruning and    |    |  |  |

|    |                     | Tuning in Graphics Processing Units                                         | 9  |  |  |

|    | 1.5                 | Dissertation Organization                                                   | 0  |  |  |

| 2  | Bac                 | cground and Literature Review 1                                             | 1  |  |  |

|    | 2.1                 | Programming Models of Accelerators                                          | 1  |  |  |

|    | 2.2                 | Memory Access of Accelerators and Data Pipelining Techniques                | 2  |  |  |

|    |                     | 2.2.1 Unified Virtual Addressing                                            | 3  |  |  |

|    |                     | 2.2.2 CUDA Streams                                                          | 3  |  |  |

|    |                     | 2.2.3 Unified Memory                                                        | 4  |  |  |

|    | 2.3                 | Related Work                                                                | 5  |  |  |

| 3 | Dire       | ective-                                      | based Partitioning and Pipelining for Graphics Processing Units | <b>21</b>                                                        |

|---|------------|----------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------|

|   | 3.1        | Introd                                       | uction                                                          | 21                                                               |

|   | 3.2        | Pipelii                                      | ne Extension API and Usage                                      | 23                                                               |

|   | 3.3        | Protot                                       | ype Implementation and Technical Details                        | 25                                                               |

|   | 3.4        | Protot                                       | ype Evaluation Results on Modern GPUs                           | 27                                                               |

|   |            | 3.4.1                                        | Initial study of the pipeline technique                         | 28                                                               |

|   |            | 3.4.2                                        | Performance and Memory Evaluation                               | 31                                                               |

|   |            | 3.4.3                                        | Comparison to the Unified Memory Technique                      | 41                                                               |

|   |            | 3.4.4                                        | Summary and Discussion of Experiments                           | 50                                                               |

|   | 3.5        | Conclu                                       | nsion                                                           | 51                                                               |

| 4 | Blo        |                                              | el Data Pipelining for Graphic Processing Units                 | 53                                                               |

|   |            | ck-Lev                                       | er Data Eipenning för Graphic Frocessing Onits                  | 00                                                               |

|   | 4.1        |                                              |                                                                 | 53                                                               |

|   | 4.1<br>4.2 | Introd                                       |                                                                 |                                                                  |

|   |            | Introd<br>Desigr                             | uction                                                          | 53                                                               |

|   |            | Introd<br>Desigr                             | uction                                                          | 53<br>55                                                         |

|   |            | Introd<br>Design<br>4.2.1<br>4.2.2           | uction                                                          | 53<br>55<br>55                                                   |

|   | 4.2        | Introd<br>Design<br>4.2.1<br>4.2.2           | uction                                                          | 53<br>55<br>55<br>58                                             |

|   | 4.2        | Introd<br>Design<br>4.2.1<br>4.2.2<br>Expert | uction                                                          | <ul><li>53</li><li>55</li><li>55</li><li>58</li><li>60</li></ul> |

|   |      | 4.3.4  | Block-Level Pipelining Optimizations                                 | 63          |

|---|------|--------|----------------------------------------------------------------------|-------------|

|   |      | 4.3.5  | Application Performance                                              | 66          |

|   |      | 4.3.6  | Performance with Larger Datasets                                     | 71          |

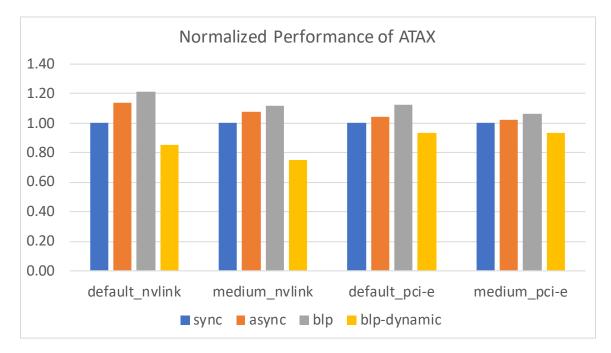

|   |      | 4.3.7  | Static vs. Dynamic Task Scheduling                                   | 74          |

|   |      | 4.3.8  | Summary and Discussion                                               | 76          |

|   | 4.4  | Conclu | usion                                                                | 79          |

| 5 | Iter | ML: It | erative Machine Learning for Intelligent Parameter Pruning and       | 1           |

| Ŭ |      |        | Graphics Processing Units                                            | 80          |

|   |      | Ũ      |                                                                      |             |

|   | 5.1  | Introd | uction                                                               | 80          |

|   |      | 5.1.1  | Motivating Example                                                   | 81          |

|   | 5.2  | Appro  | ach and Design                                                       | 84          |

|   |      | 5.2.1  | Choosing the Parameter Search Space                                  | 84          |

|   |      | 5.2.2  | Iterative Machine-Learning (IterML) Algorithm for Pruning and Tuning | <b>g</b> 84 |

|   |      | 5.2.3  | Regression Models                                                    | 86          |

|   | 5.3  | Exper  | iments                                                               | 88          |

|   |      | 5.3.1  | Benchmarks Studied                                                   | 88          |

|   |      | 5.3.2  | Hardware Platform                                                    | 89          |

|   |      | 5.3.3  | Dataset Analysis                                                     | 89          |

|   |      | 5.3.4  | Pruning Procedure                                                    | 94          |

|   |      | 5.3.5  | Case Studies                                                         | 96          |

|   | 5.4 | Evaluation                        |

|---|-----|-----------------------------------|

|   | 5.5 | $\operatorname{Conclusion}$       |

| 6 | Con | lusion and Future Work 107        |

|   | 6.1 | Summary                           |

|   | 6.2 | Future Work                       |

|   |     | 6.2.1 Source-to-Source Translator |

|   |     | 6.2.2 Inter-Node Pipelining       |

|   |     |                                   |

### Bibliography

# List of Figures

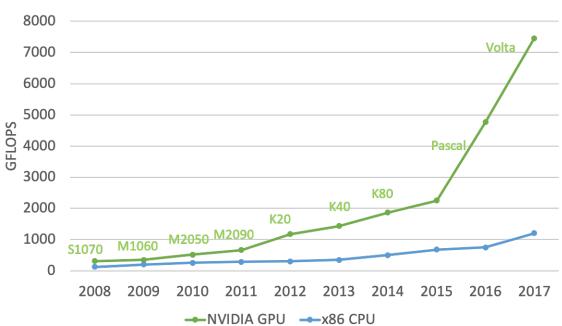

| 1.1  | GPU Double-Precision Peak FLOPs (data from [56])                         | 3  |

|------|--------------------------------------------------------------------------|----|

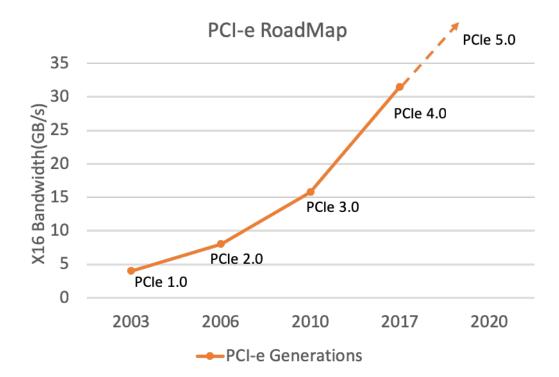

| 1.2  | PCI-e generations (data from [61])                                       | 4  |

| 1.3  | PCI-e bandwidth details (data from [61])                                 | 5  |

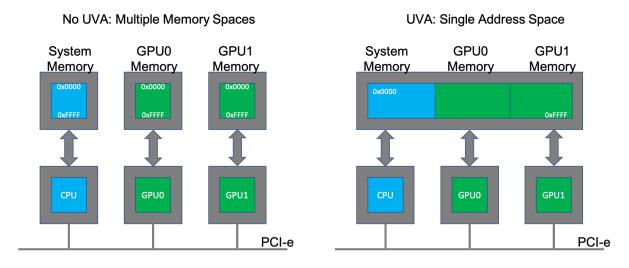

| 2.1  | Unified Virtual Addressing                                               | 13 |

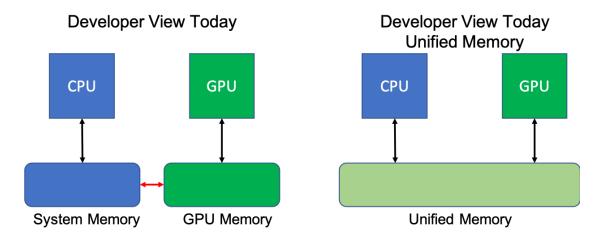

| 2.2  | Developer View with/out Unified Memory                                   | 14 |

| 3.1  | Our Proposed Pipeline Extension for OpenMP                               | 24 |

| 3.2  | A Stencil Benchmark Example                                              | 25 |

| 3.3  | Lattice QCD Time Distribution (left) and Normalized Speedup (right) on   |    |

|      | Nvidia K40m                                                              | 29 |

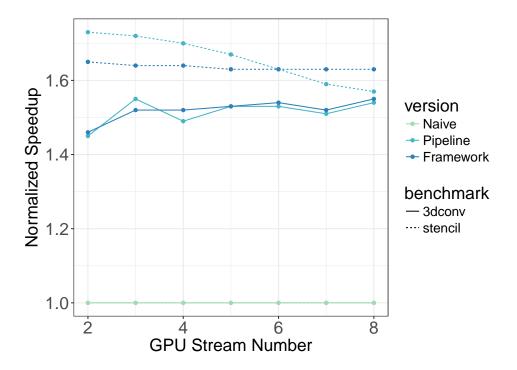

| 3.4  | Different Chunk Sizes and GPU Stream Counts on Nvidia K40m               | 30 |

| 3.5  | Performance Evaluation on Nvidia K40m                                    | 32 |

| 3.6  | GPU Memory Usage Evaluation on Nvidia K40m                               | 33 |

| 3.7  | Execution Time Varying GPU Stream Count on Nvidia K40m                   | 34 |

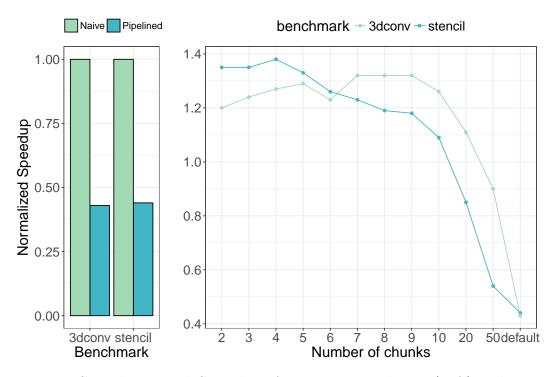

| 3.8  | 3D Convolution and Stencil Performance Degradation (Left) and Normalized |    |

|      | Speedup , Varying Number of Chunks (Right) on AMD HD 7970 $\hdots$       | 35 |

| 3.9  | Matrix Multiplication Performance on Nvidia K40m                         | 40 |

| 3.10 | Matrix Multiplication Memory Consumption on Nvidia K40m                  | 41 |

| 3.11 | 3D Convolution on K40m vs. P100                             | 43 |

|------|-------------------------------------------------------------|----|

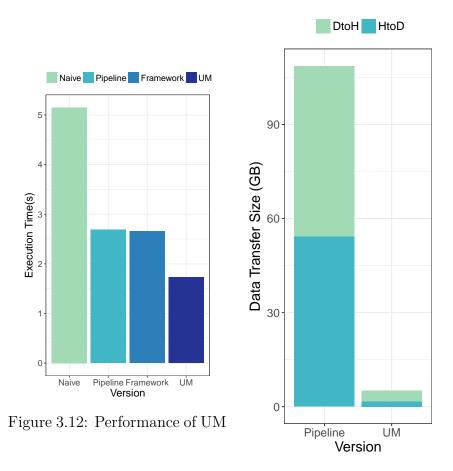

| 3.12 | Performance of UM                                           | 45 |

| 3.13 | Data Transfer                                               | 45 |

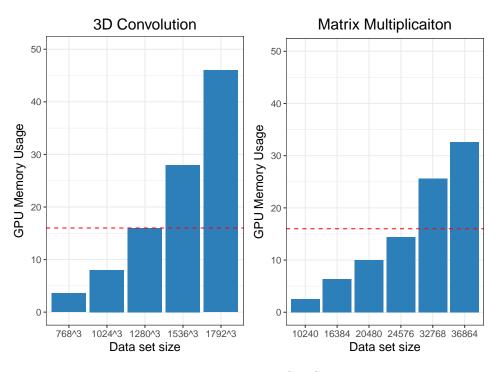

| 3.14 | Data Set Size                                               | 46 |

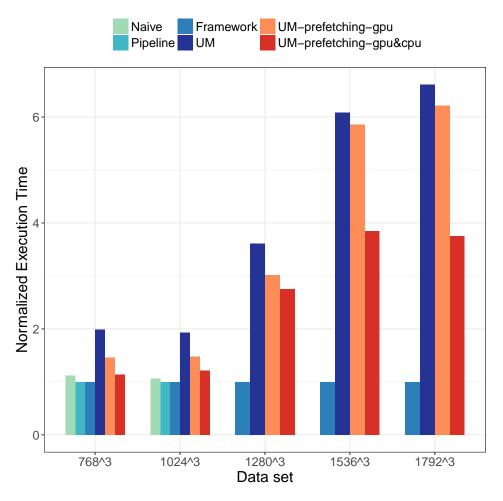

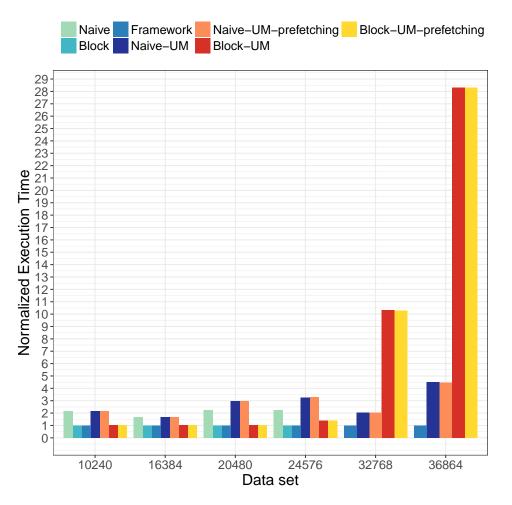

| 3.15 | 3D Convolution Normalized Execution Time                    | 47 |

| 3.16 | Matrix Multiplication Normalized Execution Time             | 49 |

| 4.1  | Proposed OpenMP Extension for Block-Level Data Pipelining   | 56 |

| 4.2  | A Stencil Code with our Proposed Extension                  | 57 |

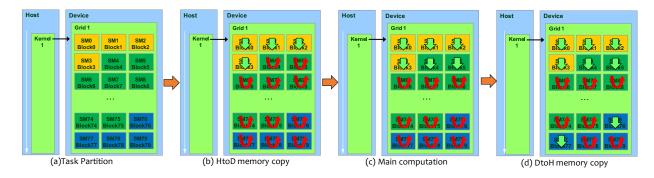

| 4.3  | Block-level Pipelining Workflow                             | 58 |

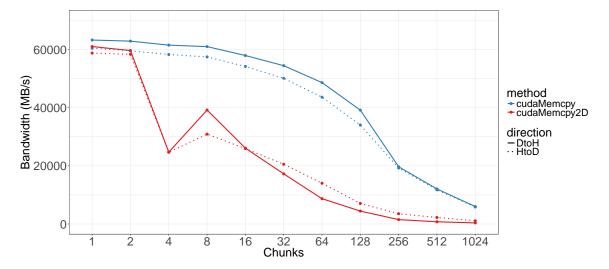

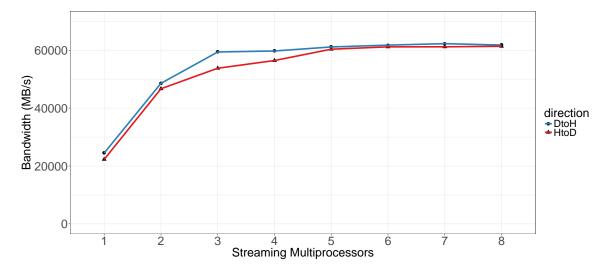

| 4.4  | cuda<br>Memcpy and cuda<br>Memcpy2D Bandwidth with NVLink2  | 62 |

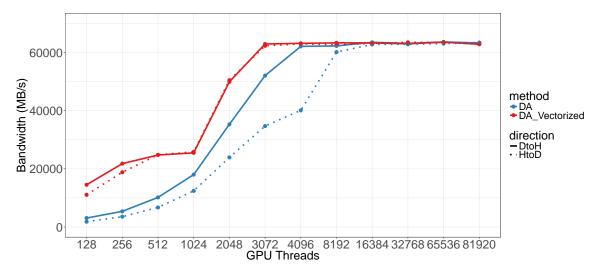

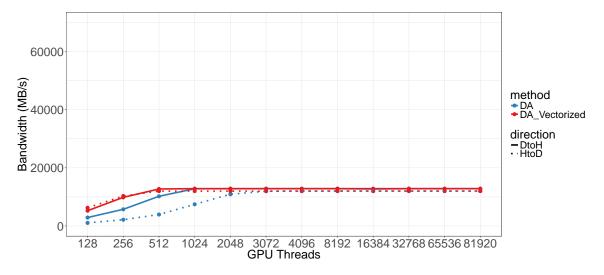

| 4.5  | Direct Access Bandwidth with NVLink2                        | 63 |

| 4.6  | Direct Chunk Access Bandwidth with NVLink2                  | 64 |

| 4.7  | Direct Access Bandwidth with PCI-E                          | 65 |

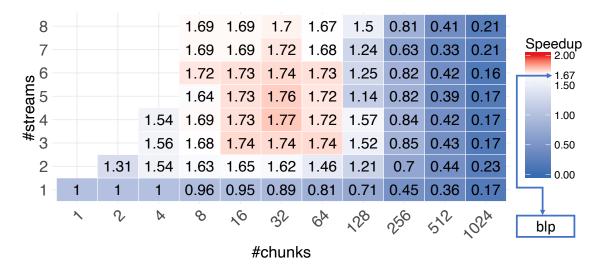

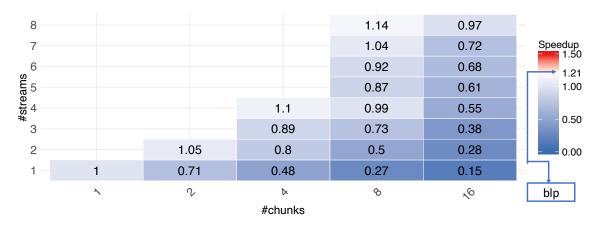

| 4.8  | Normalized Speedup of Asynchronous 2D Convolution (NVLink2) | 67 |

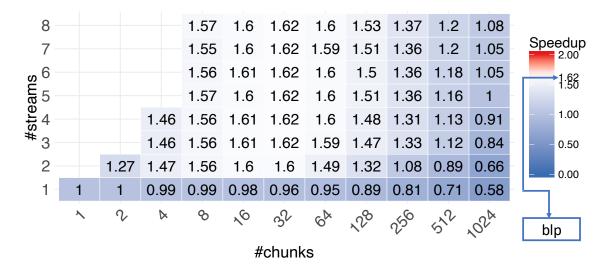

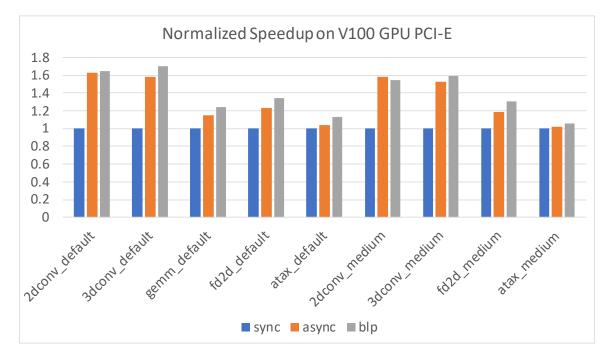

| 4.9  | Normalized Speedup of Asynchronous 2D Convolution (PCI-E)   | 68 |

| 4.10 | Normalized Speedup of Asynchronous 3D Convolution (NVLink2) | 68 |

| 4.11 | Normalized Speedup of Asynchronous 3D Convolution (PCI-E)   | 69 |

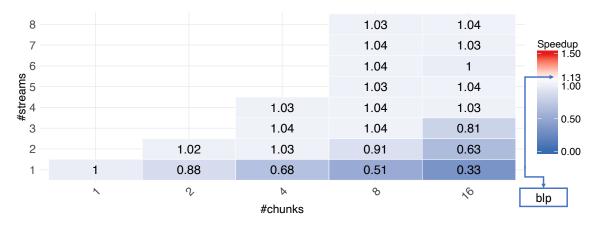

| 4.12 | Normalized Speedup of GEMM                                  | 70 |

| 4.13 | Memory Bandwidth of Interleaved Access                      | 71 |

| 4.14 | Normalized Speedup of Asynchronous 2D FDTD (NVLink2)                                                     | 72 |

|------|----------------------------------------------------------------------------------------------------------|----|

| 4.15 | Normalized Speedup of Asynchronous 2D FDTD (PCI-E)                                                       | 72 |

| 4.16 | Normalized Speedup of Asynchronous ATAX (NVLink2)                                                        | 73 |

| 4.17 | Normalized Speedup of Asynchronous ATAX (PCI-E)                                                          | 73 |

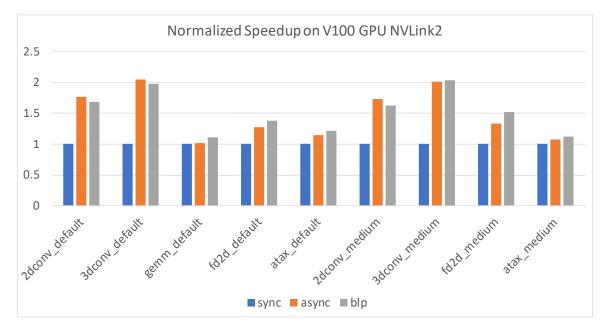

| 4.18 | Overall Normalized Speedup (NVLink2)                                                                     | 75 |

| 4.19 | Overall Normalized Speedup (PCI-E)                                                                       | 76 |

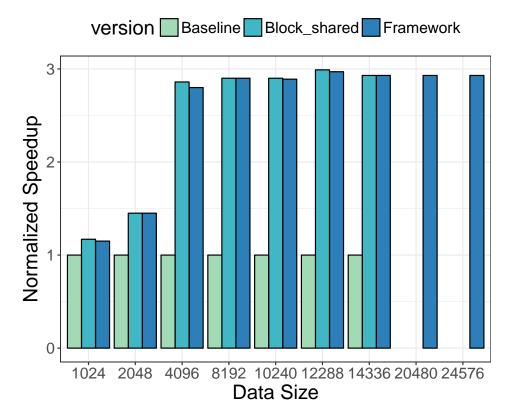

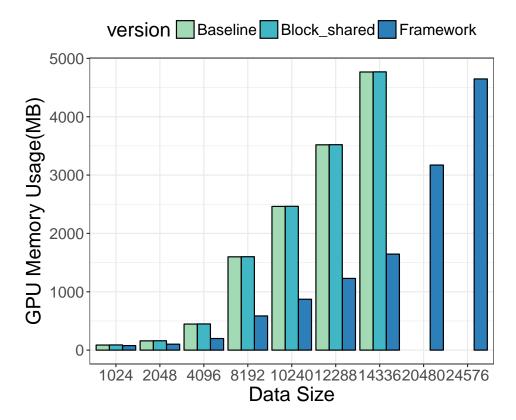

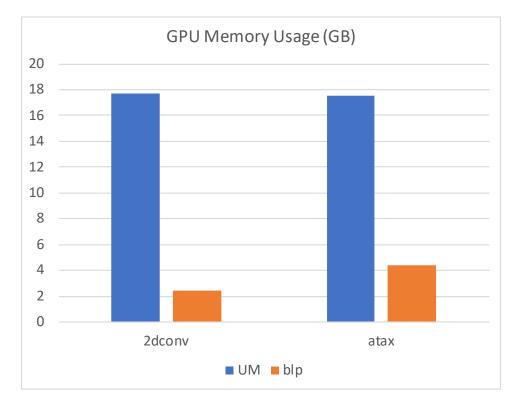

| 4.20 | GPU Memory Usage Comparison                                                                              | 77 |

| 4.21 | Performance Evaluation of Dynamic Task Scheduling for BLP                                                | 78 |

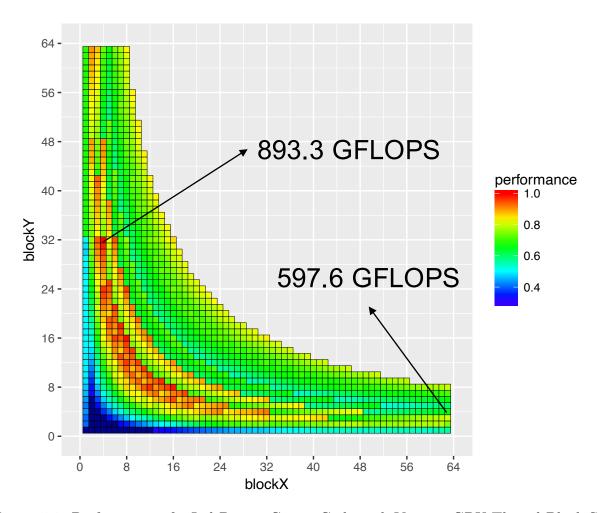

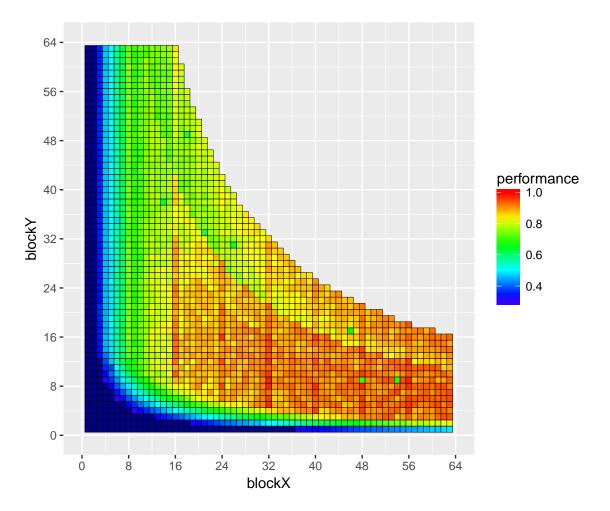

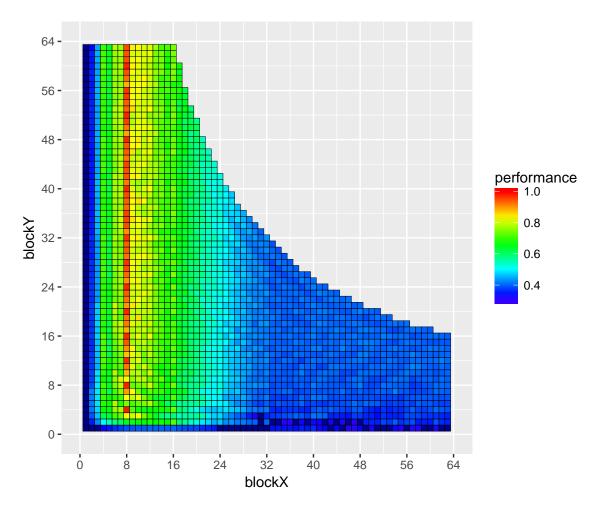

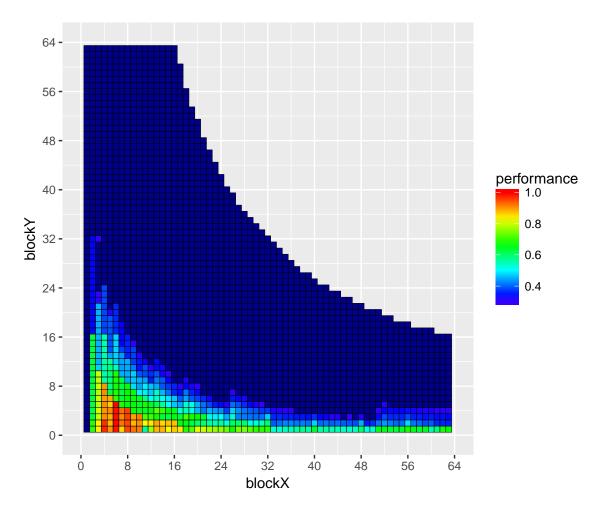

| 5.1  | Performance of a Lid-Driven Cavity Code with Varying GPU Thread-Block<br>Size on an Nvidia V100 GPU      | 82 |

| 5.2  | Performance of the 2D Convolution Benchmark with Varying GPU Thread-<br>Block Size on an Nvidia V100 GPU | 83 |

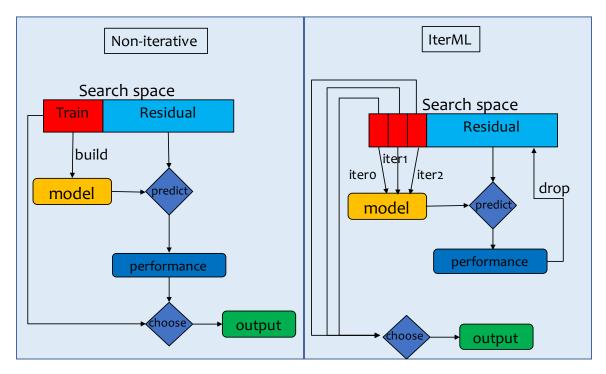

| 5.3  | Iterative Machine-Learning Algorithm (IterML)                                                            | 85 |

| 5.4  | Comparison of Non-Iterative and Iterative Machine Learning                                               | 86 |

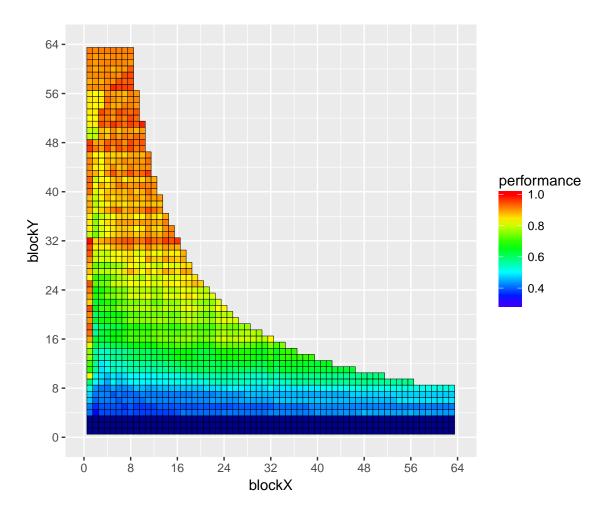

| 5.5  | Performance of the EPCC Benchmark with Varying GPU Thread-Block Size<br>on an Nvidia V100 GPU            | 90 |

| 5.6  | Performance of the MVT Benchmark with Varying GPU Thread-Block Size<br>on an Nvidia P100 GPU             | 91 |

| 5.7  | Performance of the SYR2K Benchmark with Varying GPU Thread-Block Size<br>on an Nvidia V100 GPU           | 92 |

| 5.8  | Performance of the GESUMMV Benchmark with Varying GPU Thread-Block       |     |

|------|--------------------------------------------------------------------------|-----|

|      | Size on an Nvidia V100 GPU                                               | 93  |

| 5.9  | Performance of the 2MM Benchmark with Varying GPU Thread-Block Size      |     |

|      | on an Nvidia P100 GPU                                                    | 94  |

| 5.10 | Performance of the GEMM Benchmark with Varying GPU Thread-Block Size     |     |

|      | on an Nvidia V100 GPU                                                    | 95  |

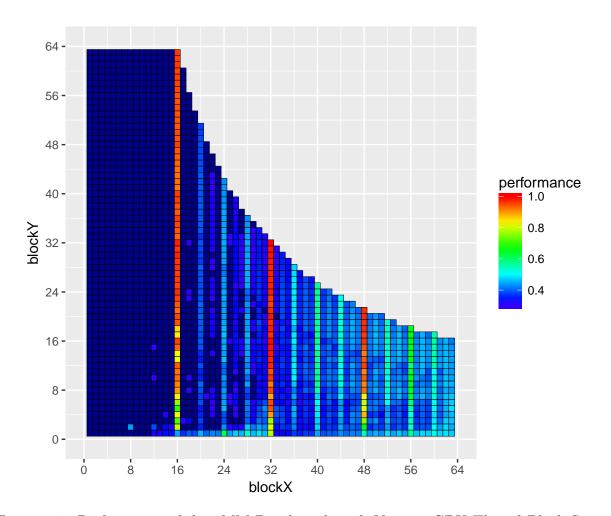

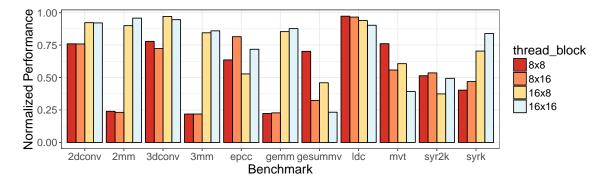

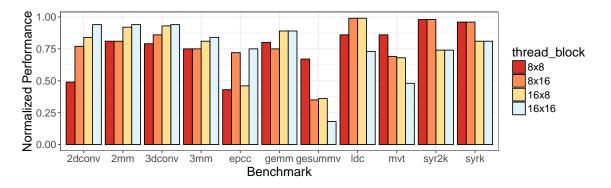

| 5.11 | Normalized Performance Across Varying Thread-Block Sizes on the P100 GPU | 97  |

| 5.12 | Normalized Performance Across Varying Thread-Block Sizes on the V100 GPU | 97  |

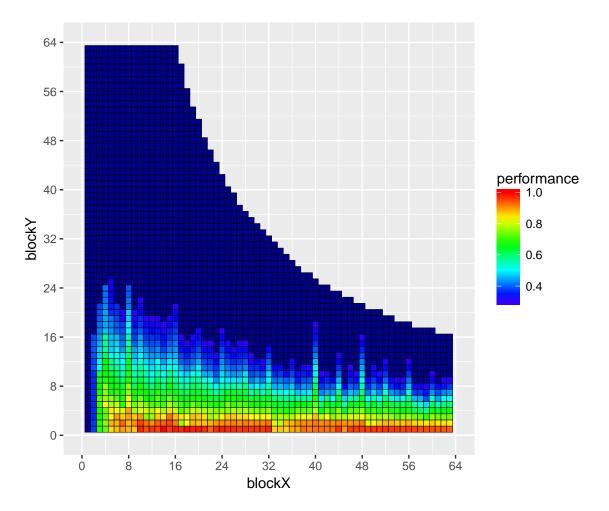

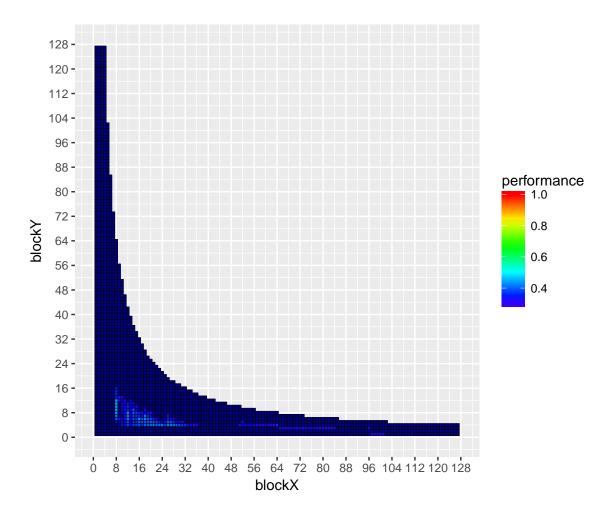

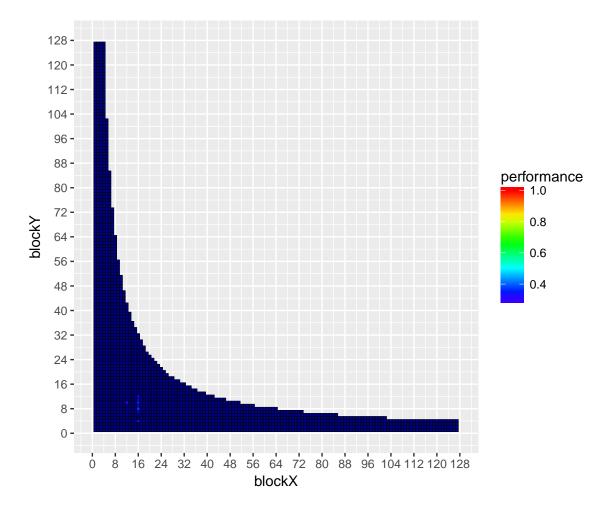

| 5.13 | Minimum Performance Heatmap Across All Benchmarks on V100 GPU $\ . \ .$  | 98  |

| 5.14 | Minimum Performance Heatmap Across All Benchmarks on P100 GPU $\ . \ .$  | 99  |

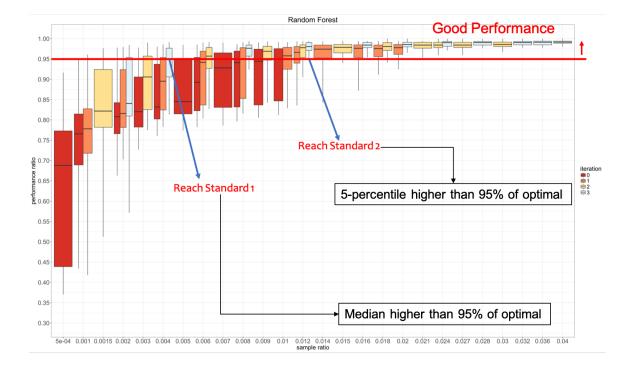

| 5.15 | Performance of SYR2K Benchmark with Random Forest (RF) and Varying       |     |

|      | the Number of Iterations (see legend) Using IterML and the Total Sample  |     |

|      | Ratio (X-axis) on the V100 GPU                                           | 101 |

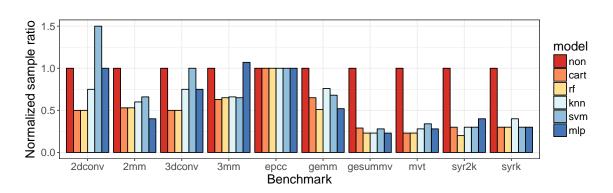

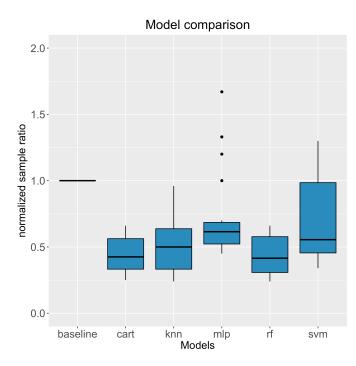

| 5.16 | Normalized Sample Ratio to Achieve Standard 1 on the V100 GPU (Lower is  |     |

|      | Better.)                                                                 | 102 |

| 5.17 | Normalized Sample Ratio to Achieve Standard 2 on the V100 GPU (Lower is  |     |

|      | Better.)                                                                 | 102 |

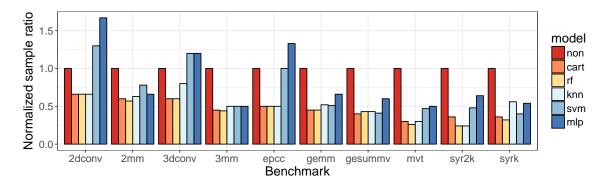

| 5.18 | Normalized Sample Ratio to Achieve Standard 1 on the P100 GPU (Lower is  |     |

|      | Better.)                                                                 | 103 |

| 5.19 | Normalized Sample Ratio to Achieve Standard 2 on the P100 GPU (Lower is  |     |

|      | Better.)                                                                 | 103 |

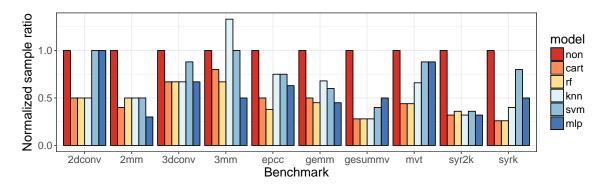

| 5.20 | Comparison of Machine-Learning (ML) Models for IterML, Relative to the  |     |

|------|-------------------------------------------------------------------------|-----|

|      | Normalized Sample Ratio (Lower is better.)                              | 104 |

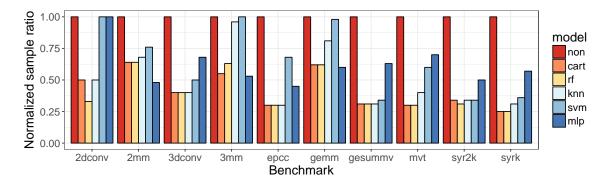

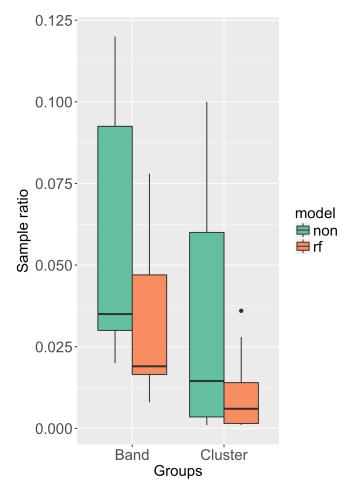

| 5.21 | Comparison of Benchmark Performance Distribution Group, Relative to the |     |

Raw Sample Ratio to Achieve Standard 1 (Lower is Better)  $\ldots \ldots \ldots \ldots 105$

xvi

# List of Tables

| 4.1 | Flag Read/Write Operations                                | 64  |

|-----|-----------------------------------------------------------|-----|

| 4.2 | Dataset GPU Memory Usage                                  | 74  |

| 4.3 | GPU Execution Time (sec) when Data Set Exceeds GPU Memory | 74  |

| 5.1 | Benchmarks Used                                           | 89  |

| 5.2 | Distribution of Application Benchmark Performance         | 96  |

| 5.3 | P100 Ideal Thread-block Size on V100                      | 100 |

| 5.4 | V100 Ideal Thread-block Size on P100                      | 100 |

# List of Abbreviations

accelerator High performance accelerator hardware, e.g., GPUs, FPGAs, and APUs.

BLP Block-level data partitioning and pipelining.

device Same as accelerator.

DToH Device to host memory transfer.

FLOPS Floating point operations per second.

HPC High performance computing.

*HtoD* Host to device memory transfer.

*IterML* Iterative machine learning.

NVLink Nvidia's wire-based communications protocol.

PCIe Peripheral Component Interconnect Express.

*UM* Nvidia's Unified Memory for GPUs.

UVA Nvidia's Unified Virtual Addressing technique.

## Chapter 1

## Introduction

In this chapter, we will motivate our work on "Directive-Based Data Partitioning and Pipelining and Auto-Tuning for High-Performance GPU Computing." We will outline the challenges and existing drawbacks of accelerator programming models and also describe the contribution of this dissertation.

### 1.1 Motivation

High Performance Computing has been evolving fast for its wide application in a lot of domain areas, including healthcare, engineering, space research, urban planning, finance and business, machine learning and AI, among others. The success of high performance computing in the last two decades significantly improved the computation power, which highly pushed the related domain areas to evolve even further. One of these areas, machine learning and AI, has been really popular in the last couple decades. It has been changing all other domain areas including HPC, not only improving the consumer market of HPC, but also affecting the research and development of HPC.

If we look at the history of these theories (e.g., neural networks, backpropagation, LSTM), mostly utilized by current techniques in machine learning and AI, most of them were published in the early 1970s. It was not until the late 2000s that machine learning and AI started to become useful because of limited data storage and computation power. Neural networks have the advantages of continuing to improve as more training data is added. Model training usually takes a lot computation power.

Back in the 1970s, the computers at that time were not capable of supporting that huge computation power requirement. One of the most successful supercomputers in history, Cray-1 [70], was announced in 1975 at Los Alamos National Laboratory. It could achieve 160 MFLOPS computation power with 303MB storage. The current fastest supercomputer, Summit [85] at Oak Ridge National Laboratory achieves 200 PFLOPS computer power with 250PB storage. That is 1.25 billion times computation power speedup and 8.25 million times capacity improvement. Being able to analyze behavior in real-time and act directly based on that is really a game-changer for machine learning and AI. Part of this significant computation power increase was due to the success of recent accelerators such as GPUs, Co-processors, APUs, FPGAs, TPUs. On the other part, the success of distributed systems (since Google released the key 3 papers about GFS, MapReduce, Bigtable) provides us scalability, throughput, and reliability for operating big data.

We can see that the recent success of HPC and machine learning and AI have been promoting each other reciprocally and finally made the era of "big data, big compute, and artificial intelligence." However, determining how to achieve high performance and portability remains difficult for developers without domain knowledge. Currently, we see that heterogeneous systems with accelerators (GPUs, co-processors, APUs, TPUs, FPGAs, etc.) are prominent on the Top500 list [25]. Supercomputers are becoming more and more complex to speed up different computational requirements. Accelerators have been widely used in recent computational tasks including scientific simulation, image processing, finance strategy prediction, data mining, deep learning, and reinforcement learning. Due to their huge performance/power efficiency benefit, a supercomputer may contain multiple different accelerator chips in one system. Mostly, operating systems treat these accelerators as input/output(I/O) devices, which means these accelerators own their high-bandwidth memory. High-bandwidth memory chips are usually expensive and have limited capacity. Current computing tasks, especially simulation, machine learning, and deep learning tasks usually require a large size of input data, which can not fit into these high-bandwidth memory chips. Determining how to move these data efficiently between the host and device could be significantly important to get optimal performance. On the other side, the CPU needs to take responsibility for copying the input data to the accelerators, launch jobs to the accelerators to process these data, and then copy the results back to the main host memory to output. The CPU host memory and device accelerator memory is usually connected by Peripheral Component Interconnect Express (PCI-e), which is a high-speed serial computer expansion bus standard. Both computation power and data transfer bandwidth are important to achieve high-performance improvement while using accelerators.

#### Peak Double Precision FLOPs

Figure 1.1: GPU Double-Precision Peak FLOPs (data from [56])

Figure 1.1 shows the peak double-precision FLOPs of Nvidia GPUs and CPUs since 2008 when the first few GPUs were released for general-purpose computing. We can observe that over the years, the GPU computation power grows significantly better than CPUs. The first GPU designed for server, Tesla S1070 (released on 2008) could achieve 311 GFLOPs performance on double-precision operations. Over the years, the GPU performance increased significantly. We also saw a huge increase around 2015. We think it probably was because of the high demand for computational power from the popular machine learning and AI tasks, which pushes the communities to grow even faster. We can also see that the most recent GPU in the Tesla product line, Tesla V100 can achieve 7450 GFLOPs. This means  $24 \times$  performance improvement in the last 10 years.

Figure 1.2: PCI-e generations (data from [61])

Figure 1.2 shows the peak data transfer bandwidth provided by the PCIe connection between host memory and device memory. The first generation of PCIe (1.0) was released in 2003.

| PCle Version | x1 Bandwidth | x4 Bandwidth | x8 Bandwidth | x16 Bandwidth |

|--------------|--------------|--------------|--------------|---------------|

| 1.0          | 250 MB/s     | 1 GB/s       | 2GB/s        | 4 GB/s        |

| 2.0          | 500 MB/s     | 2 GB/s       | 4 GB/s       | 8 GB/s        |

| 3.0          | 984.6 MB/s   | 3.938 GB/s   | 7.877 GB/s   | 15.754 GB/s   |

| 4.0          | 1.969 GB/s   | 7.877 GB/s   | 15.754 GB/s  | 31.508 GB/s   |

Figure 1.3: PCI-e bandwidth details (data from [61])

Up to today, it has already been evolved by three generations. However, even though the recent release is PCIe 4.0 in 2017, most servers are still equipped with PCIe 3.0 to provide better compatibility to other devices. Figure 1.3 shows the peak transfer bandwidth provided by PCIe. We observe that PCIe 1.0 provides 4-GB/s bandwidth while PCIe 4.0 provides 31.5-GB/s bandwidth, approximately an 8X bandwidth improvement in 14 years.

We can clearly observe that computation power has grown significantly faster than the data connection during the past 10 years. Moreover, we also observe computing patterns (e.g, convolution, pooling, transpose) that cost as much time to compute as that of data movement. The data movement overhead could potentially become the bottleneck of the accelerators, especially in the near future. Therefore, efficiently handling data movement for accelerators is very important.

On the other side, the burden of the CPU increases a lot, due to the increasing number of accelerators. Since the systems treat these accelerators as I/O devices, the CPU has to handle the data movement, task launching, and even synchronization problems. This significantly increases the CPU resource usage, harming other tasks that might be handled on the CPU side. How to bypass the CPU control in most operations of the accelerators, thus releasing as much CPU resources as possible, has become a popular topic in recent years [63, 83].

While many new programming models are proposed to support accelerators, rather than

grapple with the unfamiliar, scientists often prefer to keep their existing verified C, C++, or Fortran code. Since version 4.0 [52, 58], OpenMP has provided directive-based accelerator support that is similar to OpenACC [86] and provides a straightforward way to adapt existing programs to these systems. These models provide multiple options to pipeline data but still have drawbacks in terms of performance, programmability, and memory management.

Even though "big data" is bringing us "magic" projects that improved our research methods using high-performance computing, we can see that the significantly increased data size is becoming a big hurdle to the development of these systems. It may become the bottleneck of overall performance even with faster computation power. Developers need a better way to store and move the data efficiently. The community needs a better mechanism for accelerators to achieve better overall performance, programmability, and portability.

This dissertation aims to provide efficient data transfer pipelining frameworks and extensions to help developers overlap kernel computation with data transfer in an efficient, heuristic, and easy-to-use way. Since 2013 [57], OpenMP has provided a straightforward way to adapt existing programs to accelerated systems. We aim to extend the current OpenMP standard to provide better data pipelining approaches for accelerators in terms of programmability, performance, and memory management. Detailed work will be discussed in the following chapters.

# 1.2 Directive-based Partitioning and Pipelining for Graphics Processing Units

In directive-based offload models, users annotate their data with mapping or copying directives to ensure that the accelerator can access the data. They then launch computation on the accelerator and ensure that the results are available on the host when needed. If the accelerator cannot directly access host memory or if using the accelerator memory can improve performance, the data is copied to the device memory. The naive offload model synchronously performs these copies, which can take significant execution time. Furthermore, the data may not fit in the device memory because scientific applications frequently use huge data arrays or matrices. However, overlapping the transfers with computation and/or partitioning the data and computation can require extensive coding changes. To offload data in directive-based models, we associate the existing host variable name with a corresponding variable of the same name on the device. The result is that only one such mapping can exist for a given name or for a name and a slice range for arrays (in which case they must not overlap). Thus, users have limited control of memory mapping, partitioning, and pipelining with this mechanism.

To tackle these issues, we propose a directive-based pipelining extension for OpenMP specification on GPUs. Our extension supports automated data partitioning and overlapping of transfers through pipelining. It allows data to be mapped into a smaller buffer to reduce memory use and offers a simple interface to pipeline a parallel loop with an index handler and a kernel scheduler. We also provide a detailed evaluation including a comparison with state-of-the-art implementations.

# 1.3 Block-Level Data Pipelining for Graphic Processing Units

OpenMP [24, 52, 58] currently supports the data copy and computation pipeline in an asynchronous way but requires users to modify their code manually. Users must split the

task into chunks and launch multiple sub-kernels with different GPU streams. This manual task partitioning and sub-kernel launching entail extra code re-factoring and may introduce programming errors. Furthermore, splitting code to process multiple chunks causes extra function-call overhead. The hyper-parameters, e.g., #streams and #chunks, must be carefully tuned to achieve optimal performance; otherwise, poor choices may significantly harm performance. Moreover, as the growth of heterogeneity on supercomputers, systems are becoming more and more complex with various accelerators, co-processors, and other devices with discrete memory. These devices drastically increase the burden of the CPU to cooperate with all kinds of drivers for the data movement among these discrete memory spaces. Bypassing the CPU is an efficient way to deal with offloading tasks on accelerators [43, 81, 83, 88]. However, traditional kernel-level data pipelining still requires the CPU to be involved in the data movement, sub-kernel launch, and task dependency control between each task, with significant CPU resource utilization. The GPU-bound processes may hurt CPU processes and CPU-bound processes may hurt GPU performance in the other ways [69].

We propose a block-level pipelining mechanism to resolve these issues: Our block-level pipelining performs data communication and computation inside one GPU kernel and can totally bypass CPU control after this single kernel launch. The task dependencies between sub-tasks are maintained by flag arrays on the GPU and the sub-tasks are executed in the topology order of the program, with no extra requirement on developers to serialize the tasks to map to traditional GPU streams. We also implemented block-level pipelining mechanism in OpenMP by introducing a directive-based pipeline syntax to provide better programmability for block-level pipelining programming. We completed a detailed evaluation using our approach for various benchmarks, as well as providing a detailed comparison between our work and the current state-of-the-art implementations. 1.4. IterML: Iterative Machine Learning for Intelligent Parameter Pruning and Tuning in Graphics Processing Units

# 1.4 IterML: Iterative Machine Learning for Intelligent Parameter Pruning and Tuning in Graphics Processing Units

With the rise of graphics processing units (GPUs), the parallel computing community needs better tools to productively extract performance from the GPU. While modern compilers provide flags to activate different optimizations to improve performance, the effectiveness of such automated optimization has been limited at best.

Consequently, extracting the best performance from an algorithm on a GPU requires significant expertise and manual effort to exploit both spatial and temporal sharing of computing resources. In particular, maximizing the performance of an algorithm on a GPU requires extensive hyperparameter (e.g., thread-block size) selection and tuning. Given the myriad of hyperparameter dimensions to optimize across, the search space of optimizations is extremely large, making it infeasible to evaluate exhaustively.

As we mentioned, machine learning and AI have been successful these years. It has been changing all other domain areas including HPC, not only improving the consumer market of HPC, but also affecting the research and development of HPC. Most machine learning and AI tasks contain two stages, training and inference. Both stages require a large amount of data flow to go through the same neural network model iteratively, which means the computation patterns do not change through the process. This feature makes it possible to adjust the hyperparameters of the hardware accelerators during the iterations to achieve better performance, which could also be implemented using machine learning methods.

We propose an approach that uses statistical analysis with iterative machine learning (IterML) to prune and to tune hyperparameters to achieve better performance. During each itera-

tion, we leveraged machine-learning models to guide the pruning and tuning for subsequent iterations. We evaluated our IterML approach on the GPU thread-block size across many benchmarks running on an Nvidia P100 or V100 GPU. Our experimental results showed that our automated IterML approach reduced search effort by 40% to 80% when compared to traditional (non-iterative) ML and that the performance of our (unmodified) GPU applications can improve significantly — between 67% and 95% — simply by changing the thread-block size.

### 1.5 Dissertation Organization

The remaining dissertation chapters cover the following topics. Chapter 2 shows the background information of parallel accelerators, programming models and memory management techniques. It also provides the related work of existing solutions to achieve high performance data movement between discrete memory space (between CPUs and Accelerators) on supercomputers. Chapter 3 presents our directive-based partitioning and pipelining for graphics processing units. Chapter 4 covers our block-level data pipelining for graphic processing units work. Chapter 5 elaborates our performance auto-tuning work with machine learning methods. Chapter 6 summarizes the dissertation and future work.

## Chapter 2

## **Background and Literature Review**

In this chapter, we provide a brief background introduction regarding state-of-the-art heterogeneous computing and programming models for various accelerators. Related memory access techniques are also covered in this chapter. Overall, this chapter discuss the state-ofthe-art research work related to this dissertation.

### 2.1 Programming Models of Accelerators

Supercomputers increasingly have accelerators, such as GPUs, FPGAs, APUs, and coprocessors like the Intel Xeon Phi to increase their performance per watt and performance per dollar. Accelerators have been applied in many cutting-edge research areas, such as scientific simulations [60], medical solution development [94], machine learning [89], and regular expression [91, 92] matching. Programming these accelerators requires the use of alternate programming models or language extensions such as CUDA, OpenMP, OpenACC, and OpenCL.

**OpenMP** is a directive-based extension for Fortran, C and C++ that is best known for providing portable multithreading on shared-memory multicore systems. Insertion of an OpenMP directive can parallelize a loop. OpenMP 4.0 introduced device constructs that *target* offload to devices with potentially distinct memory spaces. OpenMP support for accelerators is still relatively nascent and, so, offers opportunities for improvement [20, 21, 34, 74].

**OpenACC** is a directive-based model that Cray, CAPS, Nvidia, and PGI developed specifically to address heterogeneous CPU/GPU systems. As with OpenMP, a user can annotate C, C++ and Fortran code with compiler directives to identify areas that should be accelerated. Current OpenACC implementations are more mature than existing support for OpenMP 4.X. Thus, several studies have compared its directive-based approach to CUDA in terms of performance, portability, and programmability [45, 84].

**CUDA** is an application programming interface (API) that Nvidia created. It supports general purpose processing on CUDA-enabled GPUs – an approach termed GPGPU (General-Purpose computing on Graphics Processing Units). CUDA is designed to work with programming languages such as C, C++, and Fortran. It provides a powerful, flexible API with low-level GPU control. GPU threads are grouped as a grid of thread blocks, which are mapped to GPU streaming multiprocessors. CUDA often requires users to refactor their code significantly [11, 31, 34, 36, 90, 93].

**OpenCL** (Open Computing Language) [77] is a standard, low-level model similar to CUDA that the Khronos group maintains. OpenCL implementations offer portability across GPUs, multicore CPUs, DSPs, co-processors, and FPGAs. However, OpenCL's complex, low-level API, often requires significantly more code than even CUDA.

# 2.2 Memory Access of Accelerators and Data Pipelining Techniques

In this section, we will cover a few new features and techniques of memory access on accelerators and related data pipelining techniques.

#### 2.2.1 Unified Virtual Addressing

Figure 2.1: Unified Virtual Addressing

Unified Virtual Addressing (UVA) [56] was first introduced with CUDA 4. It is a memory address management system that enables Fermi and Kepler GPUs running 64-bit processes. UVA means that a single memory address is used for the host and all devices as shown in Figure 2.1. The physical memory location can be determined by the pointer itself. It also enables libraries to simplify their interfaces (e.g. cudaMemcpy). UVA also enables the Zero-Copy Memory feature, which means Pointers returned by cudaHostAlloc() can be used directly from within kernels running on UVA enabled devices (i.e., no need to obtain a device pointer via cudaHostGetDevicePointer()).

#### 2.2.2 CUDA Streams

A CUDA Stream is a sequence of operations that execute on the device in the order in which they are issued by the host code. While operations within a stream are guaranteed to execute in the prescribed order, operations in different streams can be interleaved and, when possible, even run concurrently. As long as the device is capable of "concurrent copy and execution," developers may launch the kernel computation and the data transfer in different, non-default CUDA streams asynchronously. The tasks should also be first partitioned to multiple chunks, then assigned to different GPU streams, which may entail extra code refactoring that often introduces significant programming errors.

#### 2.2.3 Unified Memory

Figure 2.2: Developer View with/out Unified Memory

Unified Memory (UM) [56], as shown in Figure 2.2, which was introduced in 2014 with CUDA 6 defines a managed memory space in which all processors see a coherent memory address space. This hardware/software technology allows applications to allocate data that can be read or written from code running on either CPUs or GPUs (often called CUDA managed data). CUDA system software and/or the hardware automatically migrates memory pages to memory that the device can access. The Pascal GPU architecture is the first system with hardware support for virtual memory page faults and migration. Older GPUs based on the Kepler and Maxwell architectures support a more limited form of UM [49]. Since CUDA 9, the runtime supports a few optimization functions for Unified Memory to be more efficient in terms of data movement between host memory and device memory (e.g.,

#### 2.3. Related Work

prefetching). Nvidia claims that the data transfer occurs on demand for both GPU and CPU, requiring the use of only one array of data and no need for duplicate pointers as data is transferred between the two processors. Furthermore, they emphasize that this new method simplifies the programming model, as well as enables close to maximum bandwidth for the data transfer. On-demand migration is powerful in the way it enables fine-grain overlap between data transfers and kernel execution. However, on-demand data migration will never beat explicit memory copies in terms of large data regions. If the application's access pattern is well defined and structured, developers may use the prefetching technique of Unified Memory to tile the data and to overlap the data movement with computation kernel to achieve optimal performance [55].

#### 2.3 Related Work

We first proposed an extension to support compiler-implemented pipelining for data transfer and compute overlap in directive-based models such as OpenMP [58] and OpenACC [86]. Previous work [21] presents some of the benefits of this approach. While double buffering, and pipelining in general, is a common manual optimization, it is not a common facility of either production programming models or research prototypes although some researchers have explored mechanisms that could show support.

Higher-level logically global models like Legion [6] encode the structure of their data and computation as part of the base model and can apply optimizations like those that we discuss in their runtimes. The challenge is that they cannot be incrementally applied to existing codes, thus requiring significant refactoring if not rewriting. Similarly, global models like Chapel [15] could logically support optimization of abstract loop computations through custom domain maps and other policies, but existing codes must be significantly modified in order to use them.

Recent studies on MPI libraries such as MVAPICH2 [81, 82, 83], MPICH2 [2, 39], and OpenMPI [88] provide support to pipeline data transfers between PCIe with the data transfer on high performance interconnects to optimize bandwidth. Some of the custom data-type facilities of these libraries provide similar specification facilities to those that we propose, but differ in that they represent the data type as a whole rather than as something tied to computation and thus indexable as part of one. MPI-ACC [1] is an integrated and extensible framework. It allows end-to-end data movement in accelerator-based systems. The runtime system provides good performance by integrating support for an accelerator memory space into MPI with several optimizations, such as pipelining and parameter tuning.

On the system level, studies such as ADSM [27], CGCM [38], Spark-GPU [97], and RSVM [40] provide compiler-based optimizations for data management and movement between CPUs and GPUs, depending on static or dynamic compile-time analysis or on programmer supplied annotations. Instead of only focusing on data movement and management only, our research work focuses more on the techniques to overlap the data movement with computation efficiently.

Existing literature [66, 67, 68] has studied and tackled the data movement problem—specifically the file I/O bottleneck—in large-scale deep learning systems. We can observe that data movement plays an important role in providing good overall performance. These research studies inspired some of our research work to focus on data movement to prevent it from becoming the hurdle of computation.

The Nvidia's Unified Memory (UM) mechanism might impact performance, compared to a standard implementation without it. Typically, solutions that increase flexibility and ease of programming impose some performance overhead. Li et al. [49] evaluated UM by comparing

#### 2.3. Related Work

a selected set of applications with and without UM run on the Nvidia K40 and Jetson TK1 GPU platforms. The applications tested were Diffusion3D Benchmark, Parboil Benchmark Suite and Matrix Multiplication. This paper shows that Unified Memory versions cause 10% performance loss on average for these benchmarks. They also validated that the performance loss is caused by redundant memory transfers and page faults when adopting the Unified

performance loss on average for these benchmarks. They also valuated that the performance loss is caused by redundant memory transfers and page faults when adopting the Unified Memory programming model. This performance loss turned out to be the cost for an easier programming model. Landaverde et al. [47] investigate the performance and behavior of UM on a variety of common memory access patterns, especially the communication behavior between a host CPU and GPU. They develop multiple customized microbenchmarks for the GPU architecture with the Rodinia benchmark suite. They categorize the benchmarks by their behaviors and apply UM to these benchmarks and evaluate the change in performance. They find that for the vast majority of applications, UMA generates significant overhead and results in notable performance loss. Furthermore, the UMA model only marginally simplifies the programming model for most applications. However, for individual tests, it was demonstrated that application of UM may bring performance benefits. Specifically, if a subset of data is queried by multiple kernels multiple times before some other data are accessed. The authors state that in such case the UM mechanism can place data favorably which brings benefits compared to the standard API.

CoreTSAR [72, 73] explores automated coscheduling between devices with potentially disjoint memory spaces. CoreTSAR uses mapping functionality that associates data to computation along a single dimension for certain specific patterns. Our specifications take similar information to the array association pattern employed by CoreTSAR. However, CoreTSAR uses this information to divide computation across devices rather than to overlap computation and communication and to reduce memory use. Task-based models like OmpSs [14] and StarPU [5] construct graphs of "tasks" composed of statically sized chunks of data and computation, which are then scheduled. A user can achieve overlap by subdividing a given loop into multiple tasks, as long as they select the size and translate addresses manually.

Bauer et al. [7] study CudaDMA, an extensible API for efficiently managing data transfers between the on-chip shared memory and off-chip global memory of CUDA-enabled GPUs. They partitioned the warps in a thread block to compute warps and DMA warps. Both sequential and stride DMA patterns are supported to improve flexibility. The approach achieves good speedup (3.2x) for the SGEMV benchmark with small matrices due to the increased sustained memory bandwidth. Results with larger matrices or other benchmarks show 0.87X to 1.15X overall speedup because the benefit from reduced register pressure was not enough to overcome the overhead of the additional CudaDMA transfer through shared memory.

Aji et al. [3] proposed a scheduling attribute to OpenCL context and the runtime could automatically generate an ideal queue for different tasks. Part of our research work related to "dynamic queue" was inspired by this work.

Several papers focus on improving the computational task execution pipeline to utilize the hardware resource better. Wu et al. [87] proposed an SM-centric scheme for task scheduling. The tasks that a thread executes is based on the ID of the SM on which the thread runs. The approach provides more opportunities for optimizing GPU programs with scheduling strategies. Some of the research work in this dissertation is using similar techniques during the Persistent Thread Blocks implementations.

Zheng et al. [98] proposed VersaPipe, which leverages the combination of persistent threads and the SM-centric mechanism [87]. VersaPipe supports coarse-grain pipelining, fine–grain pipelining and a hybrid pipeline mode that assigns different pipeline stages to different SMs to utilize SM resources fully. It significantly improves the computation performance of

#### 2.3. Related Work

several applications including Pyramid, face detection, CFD, image rasterization and LDPC. Belviranli, et al. [8] introduced Juggler, a dependence-aware, in-device task execution runtime for GPUs. The runtime uses in-GPU dependence resolution and task placement. They also implemented a compiler transformation to integrate their runtime into OpenMP 4.5.

The Whippletree Megakernel [76] inherits some traits from persistent megakernels [46]. Unlike traditional persistent megakernels, Whippletree assigns available threads to work on the incoming tasks by implementing a dynamic queue and a new scheduling policy. It provides an abstraction to implement complex software pipelines, recursive algorithms and many other applications. The megakernel implementations inspired our implementation to use Nvidia's cooperative thread groups while implementing the block-level data partitioning and pipelining.

Nowadays, accelerators other than GPUs are also widely used. Bo et al. [10] proposed automata identify gRNA off-targets in Bioinfomatices and achieved over 10x speedups compared with the state-of-the art approaches. They also found that using spatial architectures (FPGAs and Micron's Automata Processor) could provide additional speedups. ANMLZoo and AutomataZoo [79, 80] are two benchmark suites that are designed for evaluating and validating automata processing engines. They are composed of various applications from different domains besides regular expressions. They also provide sample input files including the automata description files and the input streams. Researchers working on network or system security problems are also leveraging GPUs to seek better and more efficient solutions [95, 96]. We observe that the recent success of GPU has drawn more attention from researchers in various of areas. This observation also motivates some of the work in this dissertation to provide better programmability, performance and data management.

Choi et al. [18], Li et al. [51], and Tran et al. [78] auto-tune the performance of a particular algorithm or application on accelerators. However, their auto-tuning still requires exten-

sive expertise (or intuition) to select the key parameters manually as well as the compiler flags. To address this problem, we propose an approach that automatically identifies a much smaller (pruned) search space that contains a (near-)optimal setting, which can then be searched. Cui et al. [22, 23] utilized linear regression and decision tree approaches to help with tuning on accelerators. Specifically, given a large search space, our iterative machinelearning (IterML) approach gathers information during each iteration, builds models, and finds the best interaction between the parameters and performance. This, in turn, provides automated guidance as to how to tune performance in the context of a large parameter search space.

Various statistical or machine-learning (ML) methods have been applied to help with autotuning parameters to get better performance. Joseph et al. propose a linear regression model to predict processor performance based on micro-architectural parameters [42], however, it requires a large amount of processor profiling data as input to build the linear model. Li et al. utilized deep-reinforcement learning approaches to identify the optimal values of tunable parameters in computer systems — from a simple client-server system to a large data center [50]. While this approach can be deployed into a production system to collect training data and suggest tuning actions during the system's daily operation, it requires the system to be mostly static — less applicable to new algorithms or libraries that target new devices like GPUs. There are pheromone models based on the profiling data of GPUs [32, 71], but these models require large training sets across many programs and with a wide variety of performance counters. Moreover, they require developers to have intimate knowledge about the programs. Other related research focuses on designing coding machines to handle the programming tasks [48]. In contrast, our goal in this dissertation is to help developers productively tune their programs to achieve near-optimal performance with the least amount of effort and domain knowledge.

## Chapter 3

# Directive-based Partitioning and Pipelining for Graphics Processing Units

## 3.1 Introduction

Systems with accelerators, particularly GPUs, are now prominent on the Top500 [25]. While many programming models support these systems, rather than grapple with the unfamiliar, scientists often prefer to keep their existing verified C, C++ or Fortran code. OpenMP version 4.0 [52, 58] introduced directive-based accelerator support that is similar to that provided in OpenACC [86] and that provides a straightforward way to adapt existing code to use these systems.

In directive-based offload models, users annotate their data with mapping or copying directives to ensure that the accelerator can access the data. They then launch computation on the accelerator and ensure that the results are available on the host when needed. If the accelerator cannot directly access host memory or if using the accelerator memory can improve performance, the data is copied to device memory. The naive offload model synchronously performs these copies, which can take significant execution time. Furthermore, the data may

not fit in device memory because scientific applications frequently use huge data arrays or matrices. However, overlapping the transfers with computation and/or partitioning the data and computation can require extensive coding changes.

To offload data in directive-based models, we associate the existing host variable name (e.g., of an array) with a corresponding variable of the same name on the device. Result is, only one such mapping can exist for a given name, or a name and a slice range for arrays in which case they must not overlap. Thus, users have limited control of memory mapping, partitioning and pipelining with this mechanism.

Our extension to this model supports automated data partitioning and overlapping of transfers through pipelining. It allows data to be mapped into a smaller buffer to reduce memory use and offers a simple interface to pipeline a parallel loop with an index handler and a kernel scheduler.

We evaluate our partitioning and pipelining extension using four applications on multiple accelerators. Our results show that it significantly reduces memory use and improves performance. We also compare it to CUDA 9 Unified Memory (UM) [30], which supports GPU page faults with optimizations like prefetching and duplication, thus offering an automated alternative for memory oversubscription, on the Pascal P100 GPU [13] using multiple data sets. Our extension outperforms UM in most cases, especially when the data set size significantly exceeds the GPU memory limit.

This chapter makes the following contributions:

- A new directive-based pipelined extension that automates the overlap of data transfers and kernel computation and reduces GPU memory use;

- A prototype of the proposed extension;

- Evaluation of our prototype of the extension with four applications on Nvidia K40m,

P100, and AMD Radeon HD 7970 GPUs;

• Evaluation of CUDA-9 Unified Memory and its optimization methods and a comparison to the performance with our framework on the P100 GPU.

### **3.2** Pipeline Extension API and Usage

Figure 3.1 presents the syntax of our extension. The pipeline map-type modifier extends the semantics of the map clause, which makes all data available at the beginning and/or at the end of the region. Our modifier splits the data updates and subsequent loop computation into multiple subtasks.

The *list\_items* parameters to map have a new option to take an expression based on an iterator as their *begin* parameter. The format of this parameter is <var>[(iterator\_expr|begin):len]. The <var> is the variable or base pointer of an array. The [iterator\_expr:len] parameter identifies the dimension to split and size required for the given iteration to function. The function defines the split starting offset in that dimension while the len defines the range. The split currently can be performed in one or two dimensions since our runtime system supports 1D and 2D memory copies. This len parameter helps us determine the array offset. We use different internal APIs for data movement based on the subsequent loop, which we discuss later.

The chunk\_size is the number of indices in the subsequent loop that we handle in each device buffer (potentially fewer in the last chunk). The overlap parameter determines the number of GPU streams. This parameter determines the number of chunks that we launch asynchronously. We choose these two parameters as the key components of our framework not only because they provide information to improve the data transfer between host and device, but also because they can significantly affect performance and memory use.

The overlap and chunk\_size parameters determine the size of the device buffer, which we tune before we allocate the buffer to fit the total memory usage within the available GPU memory size. The other target clauses, for example, device or private, work as previously.

| <pre>#pragma omp target teams distribute   map(pipeline(iterator[,chunk_size[,overLap]]):items)   iterator(ident = begin:end[:step])</pre> |                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|                                                                                                                                            | pipeline() inputs                                                  |

| overlap                                                                                                                                    | number of blocks or streams to overlap while copying               |

| chunk_size                                                                                                                                 | number of iterations in a chunk (possibly less in last)            |

| iterator                                                                                                                                   | iterator, defined on same directive, representing range and stride |

| map() inputs                                                                                                                               |                                                                    |

| list_items                                                                                                                                 | array declaration arr[iterator_expr[:len]   begin:len]             |

| iterator() inputs                                                                                                                          |                                                                    |

| ident                                                                                                                                      | identifier for the iterator                                        |

| begin/end/step                                                                                                                             | bounds and step of the iteration space                             |

Figure 3.1: Our Proposed Pipeline Extension for OpenMP

Figure 3.2 shows a three-level nested loop that performs a stencil computation in which pipeline(k,1,3) sets chunk\_size to 1 and the number of GPU streams to 3. The to specifies that the three-dimensional input array A0 will be pipelined. iterator(k = 1:nz-1) indicates that the outermost loop is split and pipelined. Here we denote the outer loop variable as k. We use a function of k and <num> to indicate the data chunks that we must copy before launch of the kth chunk's kernel. For instance, the [k-1:3] indicates that we must copy the k-1, k and k+1 chunks in that dimension to the device before the kth kernel executes. The [k-1:3] in the first set of brackets on A0 means that we split this array by its Z dimension. It defines the dependency relationship between the array and the outermost

loop. For example, before kernel iteration k=t, we must copy chunk t-1, t, and t+1 of A0 to device memory. The [0:ny-1][0:nx-1] defines the other dimensions of array A0. The from in the map clause defines the output array Anext. For this array, the [k:1] indicates that each iteration only stores its corresponding chunk. The teams distribute parallel for clause still parallelizes the nested loop i and j inside loop k.

```

#pragma omp target \

1

2

map(pipeline(k,1,3),to:A0[k-1:3][0:ny-1][0:nx-1])\

map(pipeline(k,1,3), from:Anext[k:1][0:ny-1][0:nx-1])\

3

iterator(k = 1:nz-1)

4

5

for(k=1;k<nz-1;k++) {</pre>

6

#pragma omp target teams distribute parallel for

7

for(i=1;i<nx-1;i++) {</pre>

for(j=1;j<ny-1;j++) {</pre>

8

9

Anext[Index3D (i,

k)] =

i,

10

(A0[Index3D (i,

k + 1)] +

j,

11

A0[Index3D (i,

k - 1)] +

j,

j + 1, k)] +

12

A0[Index3D (i,

13

A0[Index3D (i,

j - 1, k)] +

14

AO[Index3D (i + 1, j,

k)] +

A0[Index3D (i - 1, j,

15

k)])*c1

16

A0[Index3D (i,

k)]*c0;

i.

17

} }

18 }

```

Figure 3.2: A Stencil Benchmark Example

A powerful code analysis engine capable of deep analysis of code and dependencies [53] could significantly simplify our proposed extension. Potentially the compiler could determine the array definition information and even the data dependencies. However, the assumption of these capabilities would limit the applicability of our extension to code that can be analyzed completely at compile time and complicate its adoption into the OpenMP specification. Thus, our prototype allows all parameters to be passed explicitly.

## **3.3** Prototype Implementation and Technical Details

Our prototype runtime framework of our proposed extension splits each loop into configurablesized chunks that are handled by different streams. Each chunk has data dependencies that must be present on the device before its kernel executes. We map the data from the original data space to the buffer data space and copy each chunk to its corresponding location in the buffer. Currently, we use the mod operator (%) to get the offset of each chunk inside the buffer. For example, if we have a buffer that can hold four chunks, so it has positions 0, 1, 2, and 3, then, we copy chunk i to position (i % 4). Once a data chunk is not needed for later partitions (kernels), we replace it. As long as the data is present, we schedule the corresponding subtask kernel to launch on the GPU.

Based on the stream numbers and array declaration information, we pre-allocate a fixed-size buffer. Each array defined by the **pipeline** modifier in the **map()** clause in the OpenMP region is associated with a data region. The array dimensions, **chunk\_size** and **num\_stream** determine the size of the device buffer for this data region. Once created, our runtime records the array's information for later use. We use a static pointer for the device buffer, which we allocate in GPU memory with cudaMalloc() on Nvidia devices. We use **cudaHostalloc()** to allocate pinned host memory, which avoids the data movement time from virtual to pinned buffer memory. The asynchronous memory copy is handled by **cudaMemcpyAsync()** for contiguous data movement; We also implement a 2D array interface using **cudaMallocPitch()** and **cudaMemcpy2DAsync()** to support non-contiguous data transfer. Currently, our prototype handles non-contiguous copies for 2D arrays, which means buffering a "Block" of a matrix. If **split\_iter** is applied to both dimensions of a 2D array, we mark it as a 2D data region and record the corresponding information, e.g., **x\_offset** and **y\_offset**. Depending on the data dependencies of each subtask, we map the required data to this buffer and then pass the offsets in the buffer to the corresponding computation kernels.

To compare to Nvidia's Unified Memory (UM), we also need to apply UM to multiple benchmarks. We compile and link with the -ta=tesla:managed flag provided by the PGI compiler. This command line option allocates all dynamic memory in CUDA Unified (Man-

#### 3.4. Prototype Evaluation Results on Modern GPUs

aged) Memory. To make sure there is no explicit data transfer, we also eliminate all data movement clauses and check the runtime information provided by the PGI compiler.

On Pascal and later GPUs, managed memory may not be physically allocated when allocation API is called; it may only be populated on access (or prefetching). In other words, pages and page table entries may not be created until they are accessed by the GPU or the CPU. So we also use cudaMemPrefetchAsync() to prefetch the data. To compare fairly, we make sure that the data are prefetched in the way that our pipelining does. In other words, the number of cudaMemPrefetchAsync() function calls is the same as that of cudaMemcpyAsync() for contiguous data movement. However, cudaMemPrefetchAsync() does not support noncontiguous data movement, we here simply prefetch the entire array.

We also notice that directive-based extensions are becoming more complex as we incrementally incorporate more functionality into the design to make it more powerful. On the other side, Unified Memory focus on reducing the complexity of the programmability while trying to offer compatible performance. However, Unified Memory requires underlying hardware/software technology since it is transparent to the programmer. The goal of our work is to provide portable performance whether Unified Memory is available or not. In our experiments, which are discussed in the evaluation section, we also observe that the Unified Memory can provide good enough performance in some cases, especially when kernels are launched multiple times with little data motion. We are also considering implementing an auto-scheduler to help the developer to make choices under different circumstances.

## 3.4 Prototype Evaluation Results on Modern GPUs

In this section, we evaluate the performance and memory consumption of our proposed extension and compare to Nvidia's Unified Memory. We first evaluate our approach on four

benchmarks: a 3D Convolution benchmark; a stencil benchmark; a matrix multiplication benchmark; and a production Lattice QCD application. We run our experiments on three types of GPUs: Nvidia Tesla K40m, AMD Radeon 7970 and Nvidia Tesla P100.

Our Nvidia experiments run on one of two platforms: an x86\_64 node containing two Nvidia Tesla K40m GPUs, each of which has 2880 stream cores and 12GB of on-board memory; and a Power-8 platform with NVLink containing four Nvidia Tesla P100 GPUs, each of which has 3584 stream cores and 16GB of on-board memory.

Our AMD experiments run on a node with an AMD Radeon HD 7970 GPU, which has 2048 stream processors and 3GB of on-board memory.

For each benchmark, we measure the performance in terms of the function that contains the GPU operations, including all transfers but ignoring time for code that is identical in all versions. We execute all test runs six times and use their average as the final result. The error in the performance numbers is within 0.2 seconds in all cases. For memory usage, we use the Nvidia System Management Interface nvidia-smi to inspect memory usage during execution.

#### 3.4.1 Initial study of the pipeline technique

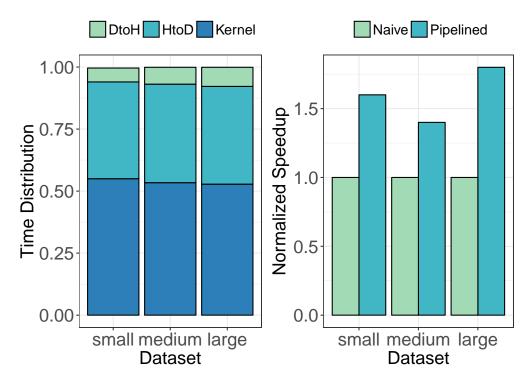

The naive offload model, i.e., synchronously copying and executing, is inefficient. Figure 3.3 shows a time distribution on an Nvidia K40m of different phases in a naive *Lattice Quantum Chromodynamics (QCD)* application written with OpenACC. Data transfers consume nearly 50% of execution time, during which no computation is performed. This execution model wastes GPU and CPU compute resources during data transfers. Thus, the current standard interface still has limitations in terms of performance, programmability, and memory usage. To understand the pipeline technique and the impact of stream counts and data sizes, we

Figure 3.3: Lattice QCD Time Distribution (left) and Normalized Speedup (right) on Nvidia K40m

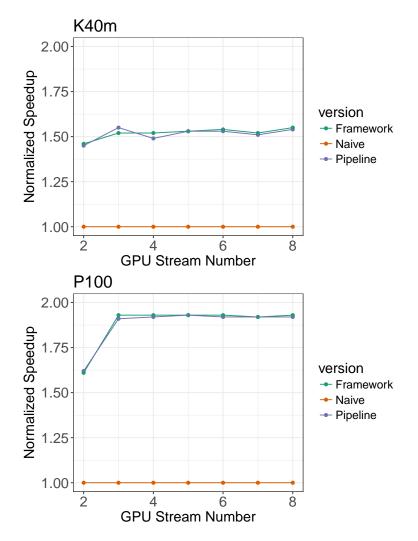

first use the Lattice QCD application as a case study on the Nvidia Tesla K40m GPU. From Figure 3.3, we observe that pipelining achieves a  $1.6 \times$  speedup for the small test case. As the problem size grows, the speedup increases, indicating that larger cases may approach the theoretical upper bound of  $2 \times$ , which would be achieved if data transfers and computation were perfectly overlapped.

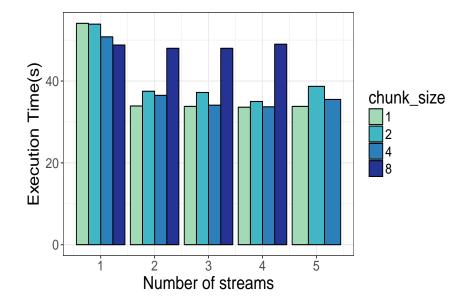

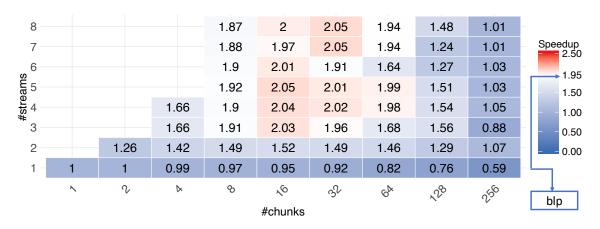

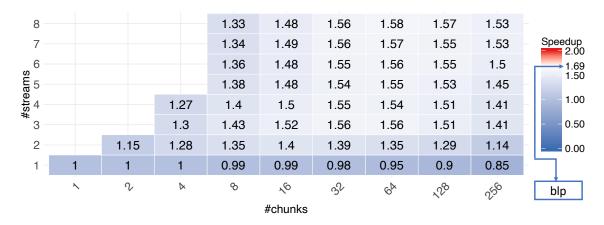

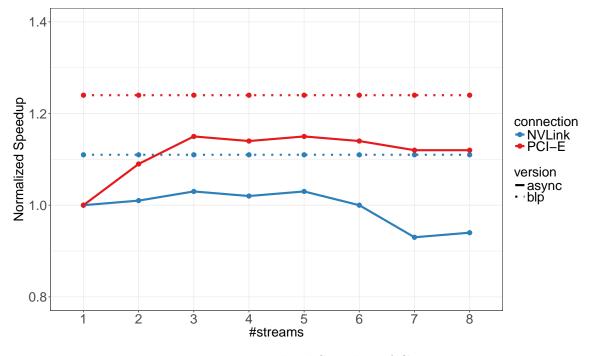

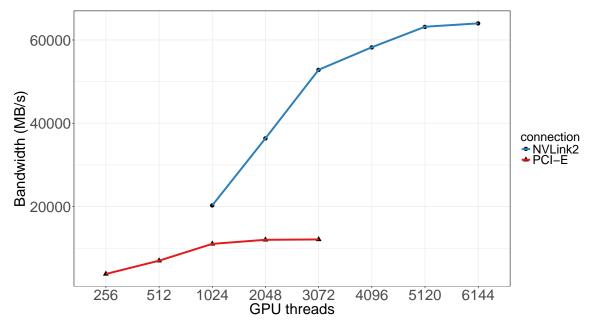

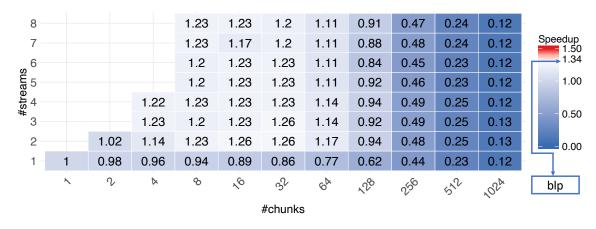

We also vary chunk size and number of streams in Figure 3.4. These two parameters can significantly affect performance. The number of streams value is the number of GPU streams that we use in parallel, which is the number of transfers and kernels that may simultaneously be in flight. More GPU streams could potentially hide more "bubbles" in the pipeline. However, more GPU streams requires more scheduling overhead. As we divide the task into multiple chunks, chunk size determines the size of each chunk and, thus, the number of chunks. More chunks requires more API calls, and thus more overhead. Few chunks

mean that the transfers of the first input chunk and the last output chunk, which cannot be overlapped, are larger and account for more of the runtime which can degrade performance. Thus, we vary these parameters to explore the trade-off.

Figure 3.4: Different Chunk Sizes and GPU Stream Counts on Nvidia K40m

Figure 3.4 shows the results for the large test case on the K40m. Using two streams generally performs significantly better than one, showing the benefits of overlapping data transfers and computation. However, using more than four streams offers no further benefit due to increasing API and scheduling overheads while only slightly increasing potential overlap. Increasing the chunk size reduces API call and kernel launch overhead but makes load balancing harder. Increasing the chunk size usually does not adversely impact performance. Thus, we can ignore the additional overhead to use more chunks for this case. The K40m needs two streams to reach its best performance for this application.

#### 3.4.2 Performance and Memory Evaluation

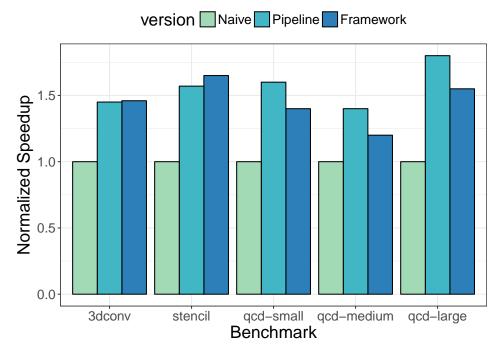

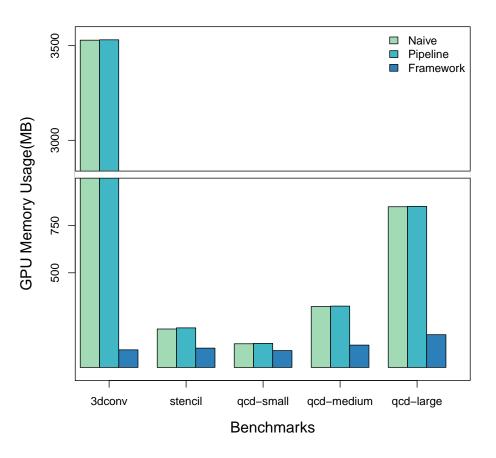

We evaluate our framework on four benchmarks on Nvidia and AMD GPUs. We denote the baseline version as "Naive". We overlap the data transfer and kernel computation and implement a "Pipeline". We then apply our framework to these benchmarks thus implement a "Framework". We have to note that the "Pipeline" version of the Matrix-Multiplication benchmark also benefits from the algorithm change. To utilize the idea of saving memory better, we replace the Naive Matrix-Multiplication algorithm by a Block Matrix-Multiplication.

#### **3D** Convolution