### Using Workload Characterization to Guide High Performance Graph Processing

Mohamed W. Hassan

Dissertation submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

> Doctor of Philosophy in Computer Engineering

Peter M. Athanas, Chair

Yasser Y. Hanafy

Michael Hsiao

Paul Plassmann

Hoda Eldardiry

May 12, 2021

Blacksburg, Virginia

Keywords: Configurable Computing, Graph Processing, Heterogeneous Systems, High Performance Computing Copyright 2021, Mohamed W. Hassan

### Using Workload Characterization to Guide High Performance Graph Processing

Mohamed W. Hassan

#### (ABSTRACT)

Graph analytics represent an important application domain widely used in many fields such as web graphs, social networks, and Bayesian networks. The sheer size of the graph data sets combined with the irregular nature of the underlying problem pose a significant challenge for performance, scalability, and power efficiency of graph processing. With the exponential growth of the size of graph datasets, there is an ever-growing need for faster more power efficient graph solvers. The computational needs of graph processing can take advantage of the FPGAs' power efficiency and customizable architecture paired with CPUs' general purpose processing power and sophisticated cache policies. CPU-FPGA hybrid systems have the potential for supporting performant and scalable graph solvers if both devices can work coherently to make up for each other's deficits.

This study aims to optimize graph processing on heterogeneous systems through interdisciplinary research that would impact both *the graph processing community*, and the *FPGA/heterogeneous computing community*. On one hand, this research explores how to harness the computational power of FPGAs and how to cooperatively work in a CPU-FPGA hybrid system. On the other hand, graph applications have a data-driven execution profile; hence, this study explores how to take advantage of information about the graph input properties to optimize the performance of graph solvers.

The introduction of High Level Synthesis (HLS) tools allowed FPGAs to be accessible to the masses but they are yet to be performant and efficient, especially in the case of irregular graph applications. Therefore, this dissertation proposes automated frameworks to help integrate FPGAs into mainstream computing. This is achieved by first exploring the optimization space of HLS-FPGA designs, then devising a domain-specific performance model that is used to build an automated framework to guide the optimization process. Moreover, the architectural strengths of both CPUs and FPGAs are exploited to maximize graph processing performance via an automated framework for workload distribution on the available hardware resources.

### Using Workload Characterization to Guide High Performance Graph Processing

Mohamed W. Hassan

#### (GENERAL AUDIENCE ABSTRACT)

Graph processing is a very important application domain, which is emphasized by the fact that many real-world problems can be represented as graph applications. For instance, looking at the internet, web pages can be represented as the graph vertices while hyper links between them represent the edges. Analyzing these types of graphs is used for web search engines, ranking websites, and network analysis among other uses. However, graph processing is computationally demanding and very challenging to optimize. This is due to the irregular nature of graph problems, which can be characterized by frequent indirect memory accesses. Such a memory access pattern is dependent on the data input and impossible to predict, which renders CPUs' sophisticated caching policies useless to performance.

With the rise of heterogeneous computing that enabled using hardware accelerators, a new research area was born, attempting to maximize performance by utilizing the available hardware devices in a heterogeneous ecosystem. This dissertation aims to improve the efficiency of utilizing such heterogeneous systems when targeting graph applications. More specifically, this research focuses on the collaboration of CPUs and FPGAs (Field Programmable Gate Arrays) in a CPU-FPGA hybrid system. Innovative ideas are presented to exploit the strengths of each available device in such a heterogeneous system, as well as addressing some of the inherent challenges of graph processing. Automated frameworks are introduced to efficiently utilize the FPGA devices, in addition to distributing and scheduling the workload across multiple devices to maximize the performance of graph applications.

## Dedication

I dedicate this dissertation to my mother "Rasmia" and my wife "Rana" whose words of encouragement pushed me forward all the way to the finish line. Their unwavering support was the pillar that helped me throughout this journey.

I also dedicate all my work to my late father, Prof. Wasfy Abouelmakarem, who inspired me to walk this path. His knowledge and wisdom motivated me throughout my entire life.

### Acknowledgments

I am deeply grateful for my advisor, Prof. Peter Athanas, for giving me the chance to be a member of the Configurable Computing Machines (CCM) lab and for his unwavering support and belief in me. He provided me with valuable guidance and continuous support throughout my PhD. I would like to express my sincere gratitude to Prof. Yasser Hanafy for mentoring and supporting me by shining a light when tackling a new research area. I would also like to thank Prof. Wu-chun Feng for his assistance and insightful comments and suggestions that allowed me to contribute in multiple research areas. I would also like to thank Prof. Michael Hsiao, Prof. Paul Plassmann, and Prof. Hoda Eldardiry for their guidance that helped shape this dissertation.

I would like to offer my special thanks to Dr. Scott Pakin for his mentoring and guidance during and after my internship at Los Alamos National Lab. Introducing me to the field of quantum computing turned out to be one of the best research projects I have ever worked on. I would like to extend my sincere thanks to Dr. Andrew Schmidt who provided me with an amazing working environment that helped bring out the best in me. He also taught me a well-structured way to conduct my research which was exactly what I needed to push me over the top.

I would like to express my gratitude to the Intel Innovator program, especially Sujata Tiberwala, for granting me access to Intel's Devcloud cluster and accommodating my hardware and software requests to support my research. They provided me with state of the are hardware and the latest software that was very helpful in completing my research.

vi

# Contents

| Li | List of Figures xi |                                                        |    |  |

|----|--------------------|--------------------------------------------------------|----|--|

| Li | st of              | Tables                                                 | xv |  |

| 1  | Intr               | oduction                                               | 1  |  |

|    | 1.1                | Research Problems                                      | 2  |  |

|    | 1.2                | Methodology                                            | 4  |  |

|    | 1.3                | Contributions                                          | 6  |  |

|    | 1.4                | Dissertation outline                                   | 9  |  |

| 2  | Bac                | kground and Related Work                               | 10 |  |

|    | 2.1                | Graph Processing Background                            | 11 |  |

|    | 2.2                | Heterogeneous Computing &                              |    |  |

|    |                    | Workload Partitioning                                  | 14 |  |

|    | 2.3                | Graph-Input Aware Research                             | 16 |  |

|    | 2.4                | HLS Design and Optimization on FPGAs                   | 17 |  |

|    | 2.5                | HLS Performance Modelling and Design Space Exploration | 19 |  |

|    | 2.6                | Discussion                                             | 21 |  |

| 3  | Wor                | kload Distribution on CPU-FPGA Hybrid Systems          | 23 |  |

| 3.1 | Motiva | ation & Goal                            | 24 |

|-----|--------|-----------------------------------------|----|

|     | 3.1.1  | Challenges                              | 24 |

|     | 3.1.2  | Approach                                | 25 |

|     | 3.1.3  | Contributions                           | 25 |

| 3.2 | Backg  | round                                   | 26 |

|     | 3.2.1  | PageRank Algorithm                      | 26 |

|     | 3.2.2  | Graph Data-set and Features             | 28 |

|     | 3.2.3  | Workload Distribution Configurations    | 29 |

| 3.3 | Graph  | Processing on Hybrid Systems Using GAHS | 31 |

|     | 3.3.1  | Execution Profile Library               | 32 |

|     | 3.3.2  | Analysis Engine                         | 32 |

|     | 3.3.3  | Correlation Engine                      | 33 |

|     | 3.3.4  | Recommendation System                   | 35 |

|     | 3.3.5  | Fine-Tuning Feedback                    | 36 |

| 3.4 | Result | s & Evaluation                          | 36 |

|     | 3.4.1  | Hardware Platform                       | 36 |

|     | 3.4.2  | Testing Data-Set                        | 37 |

|     | 3.4.3  | Total Execution Time Analysis           | 37 |

|     | 3.4.4  | Recommendation Accuracy                 | 38 |

|     | 3.4.5  | Comparison with State-of-the-Art        | 40 |

|   | 3.5 | Summ    | ary                                                                                  | 42 |

|---|-----|---------|--------------------------------------------------------------------------------------|----|

| 4 | HLS | 5 Desig | gn Space and Optimization Exploration                                                | 43 |

|   | 4.1 | Motiva  | ation & Goal                                                                         | 44 |

|   |     | 4.1.1   | Challenges                                                                           | 44 |

|   |     | 4.1.2   | Approach                                                                             | 45 |

|   |     | 4.1.3   | Contributions                                                                        | 47 |

|   | 4.2 | Backg   | round                                                                                | 48 |

|   |     | 4.2.1   | Parallelism Optimizations                                                            | 49 |

|   |     | 4.2.2   | Floating-Point Optimizations                                                         | 50 |

|   |     | 4.2.3   | Data Movement Optimizations                                                          | 51 |

|   | 4.3 | Evalua  | ation & Analysis of Irregular Applications                                           | 51 |

|   |     | 4.3.1   | Graph Traversal                                                                      | 52 |

|   |     | 4.3.2   | Sparse Linear Algebra                                                                | 56 |

|   |     | 4.3.3   | Combinational Logic                                                                  | 60 |

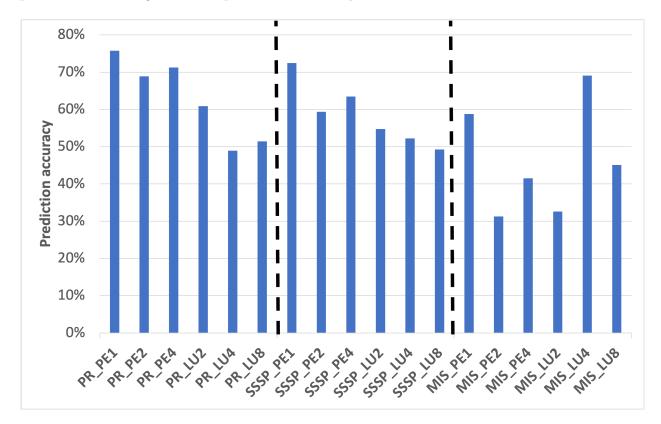

|   | 4.4 | Discus  | $\operatorname{ssion}$                                                               | 64 |

|   | 4.5 | Summ    | ary                                                                                  | 66 |

| _ | P   | • •     |                                                                                      |    |

| 5 |     |         | pecific Performance Modelling for FPGA designs and automated<br>on space exploration | 68 |

|   | 5.1 |         | ation & Goal                                                                         | 69 |

|   |     |         |                                                                                      |    |

|     | 5.1.1  | Challenges                           | 69 |

|-----|--------|--------------------------------------|----|

|     | 5.1.2  | Approach                             | 70 |

|     | 5.1.3  | Contributions                        | 71 |

| 5.2 | Backg  | round                                | 71 |

|     | 5.2.1  | Graph Applications                   | 72 |

|     | 5.2.2  | Graph Data-set & features            | 73 |

|     | 5.2.3  | Hardware Parallelism Extensions      | 74 |

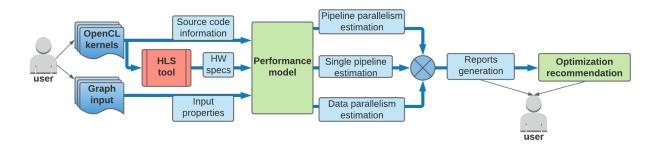

| 5.3 | The P  | erformance Model Framework           | 75 |

|     | 5.3.1  | Information Collection & Terminology | 75 |

|     | 5.3.2  | Performance Model Construction       | 77 |

|     | 5.3.3  | Parallelism Extension                | 79 |

| 5.4 | Evalua | ation & Analysis of the Framework    | 81 |

|     | 5.4.1  | Experimental Setup                   | 81 |

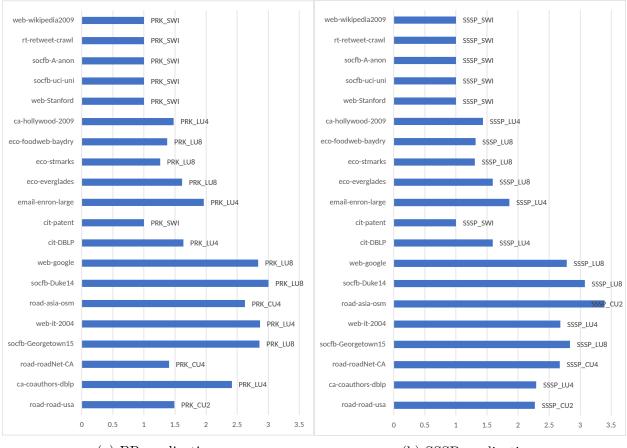

|     | 5.4.2  | Optimizations & Performance Analysis | 82 |

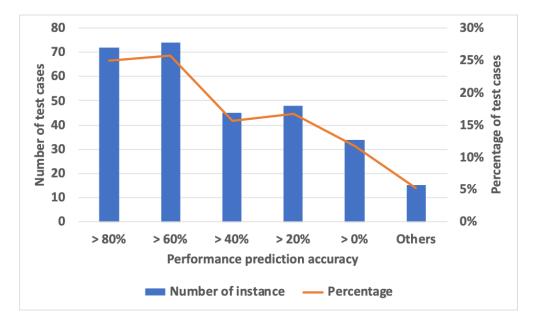

|     | 5.4.3  | Overall Performance Model Accuracy   | 84 |

|     | 5.4.4  | Parallelism Extensions Evaluation    | 85 |

|     | 5.4.5  | Discussion                           | 86 |

| 5.5 | Summ   | ary                                  | 88 |

#### 6 Conclusion

| 6.2 Future Work | 90 |

|-----------------|----|

|                 | 92 |

### Bibliography

93

# List of Figures

| 1.1 | High level abstraction of the scope of graph processing                                                                                                                                                                     | 1          |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1.2 | Dissertation overview.                                                                                                                                                                                                      | 5          |

| 2.1 | Graph (a) Logical representation (b) Adjacency matrix (c) In-degree calcula-<br>tion as SPMV (adopted from [69]).                                                                                                           | 11         |

| 2.2 | Overview of graph solvers: classification of hardware platforms                                                                                                                                                             | 13         |

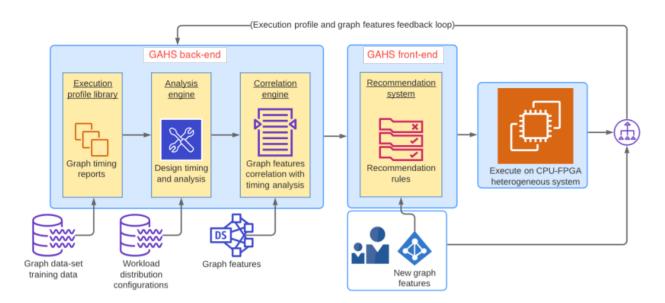

| 3.1 | GAHS framework general structure and its associated components                                                                                                                                                              | 31         |

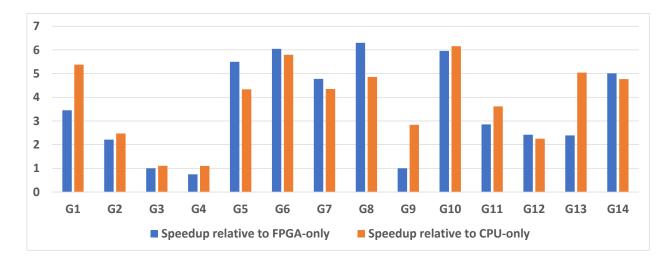

| 3.2 | GAHS's recommendation speedup relative to FPGA- and CPU-only execution.                                                                                                                                                     | 38         |

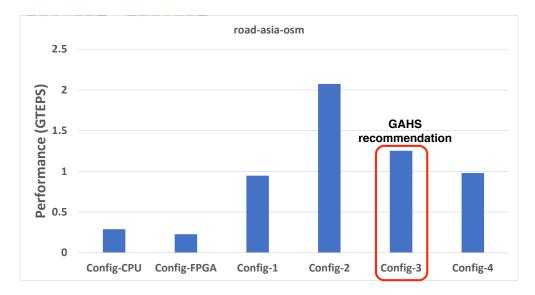

| 3.3 | Performance (GTEPS: Giga Traversed Edges Per Second) of road-asia-osm graph across all workload distribution configurations.                                                                                                | 39         |

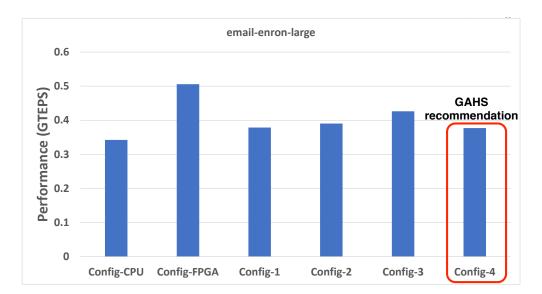

| 3.4 | Performance (GTEPS: Giga Traversed Edges Per Second) of email-enron-large graph across all workload distribution configurations.                                                                                            | <b>4</b> 0 |

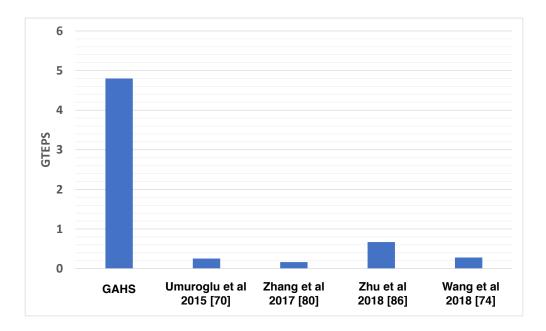

| 3.5 | Maximum performance achieved by GAHS compared to related work $\ . \ . \ .$                                                                                                                                                 | 41         |

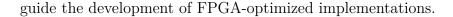

| 4.1 | Programmability vs. performance spectrum for FPGAs                                                                                                                                                                          | 46         |

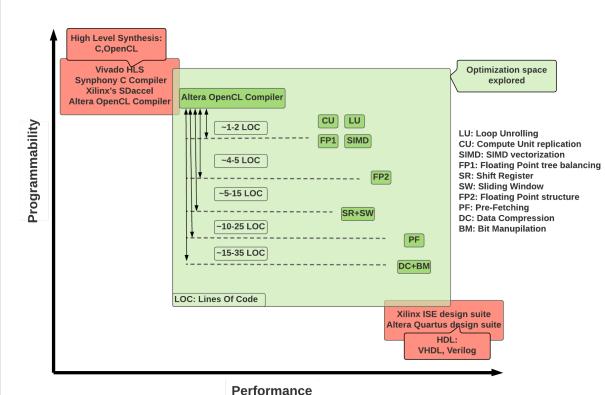

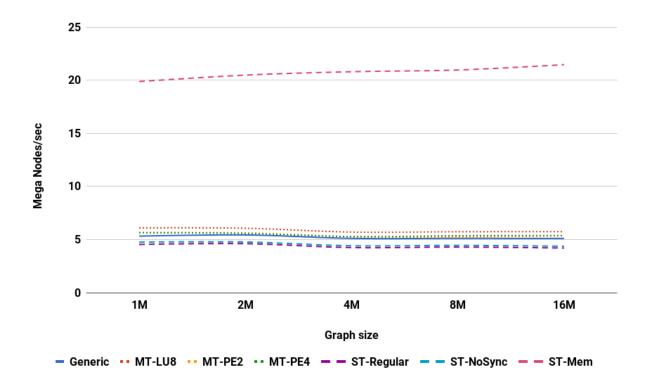

| 4.2 | The performance of irregular OpenCL kernels on CPU and FPGA architec-<br>tures. The optimized FPGA execution uses a deeply-pipelined, compute unit<br>running at 200-260 MHz, while the CPU platform consists of 16 compute |            |

|     | units running at 3.5 GHz.                                                                                                                                                                                                   | 47         |

| 4.3  | The performance of BFS (nodes processed per second) across different graph    |    |

|------|-------------------------------------------------------------------------------|----|

|      | sizes for multiple optimization techniques.                                   | 53 |

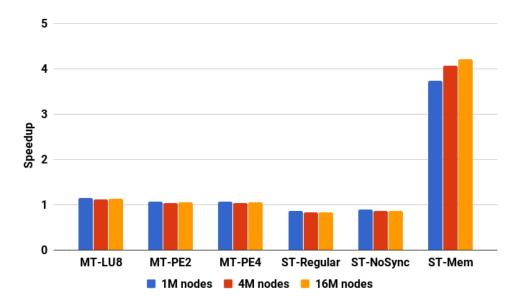

| 4.4  | BFS speedup across the different optimization techniques. The baseline is the |    |

|      | OpenDwarfs, architecture-agnostic OpenCL code                                 | 55 |

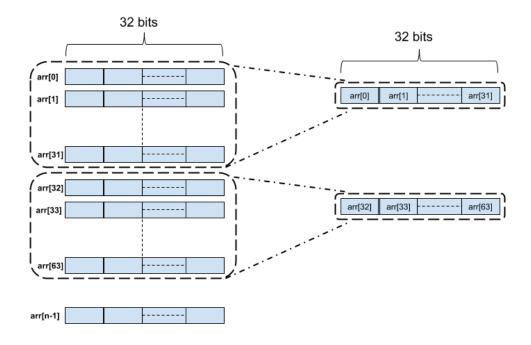

| 4.5  | Boolean array data compression.                                               | 55 |

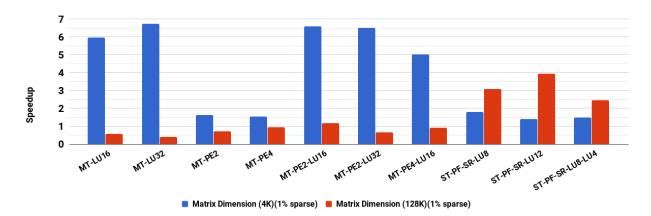

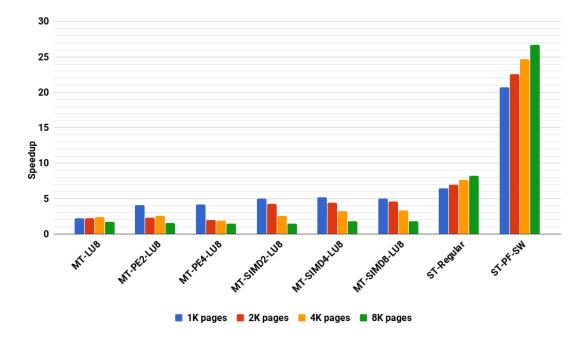

| 4.6  | SPMV speedup for small and large matrix sizes                                 | 57 |

| 4.7  | The performance of SPMV for the multi-threaded optimizations. The baseline    |    |

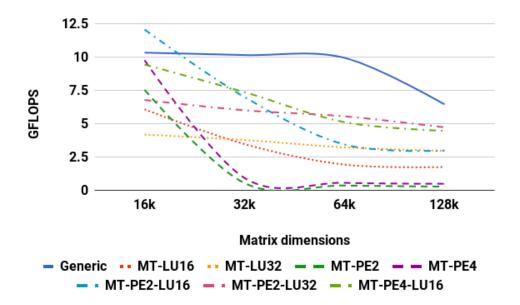

|      | is the OpenDwarfs, architecture-agnostic code                                 | 58 |

| 4.8  | The performance of the single-task optimizations for SPMV. The baseline is    |    |

|      | the OpenDwarfs, architecture-agnostic OpenCL code                             | 60 |

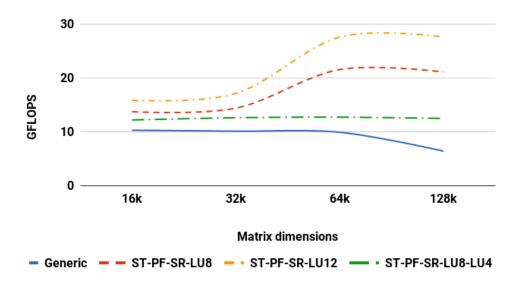

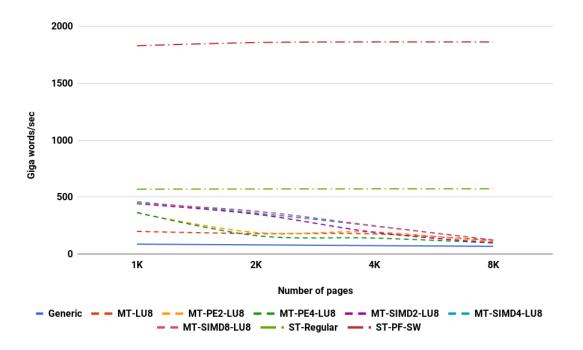

| 4.9  | CRC speedup across different optimization techniques. The baseline is the     |    |

|      | OpenDwarfs, architecture-agnostic OpenCL code.                                | 62 |

| 4.10 | The performance (words processed per second) of CRC across different opti-    |    |

|      | mization techniques.                                                          | 63 |

|      |                                                                               |    |

| 5.1  | Overview of the performance model framework. Information flowing from the     |    |

|      | user, through the framework, then back to the user                            | 75 |

| 5.2  | Speedup of the recommended optimization strategy compared to the single       |    |

|      | pipeline implementation.                                                      | 83 |

| 5.3  | Overall prediction accuracy of the performance model, The figure is shown in  |    |

|      | percentiles                                                                   | 84 |

| 5.4  | Average of prediction accuracy of each design across the whole data-set       | 85 |

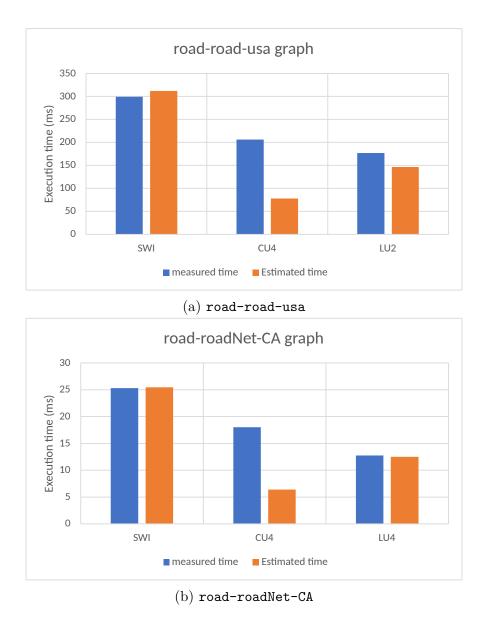

5.5 Measured and estimated time for three PR configurations, the baseline (SWI),framework's recommendation (CU), optimal configuration (LU). . . . . . . 87

# List of Tables

| 2.1 | Overview of graph processing frameworks.                                                                            | 14 |

|-----|---------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Kernels of the SPMV-based PageRank algorithm and the relevant kernel nam-<br>ing code used throughout this chapter. | 27 |

| 2.0 |                                                                                                                     |    |

| 3.2 | Sample of the data-set used for initializing GAHS                                                                   | 28 |

| 3.3 | The distribution of kernel computations over the hybrid system for the dif-                                         |    |

|     | ferent workload distribution configurations.                                                                        | 30 |

| 3.4 | Sample of the testing data-set used for evaluating GAHS framework                                                   | 37 |

| 4.1 | BFS optimizations and resource utilization. $[MT]$ : Multi-Threaded, $[ST]$ :                                       |    |

|     | Single Task.                                                                                                        | 52 |

| 4.2 | SPMV optimizations and resource utilization. $[MT]$ : Multi-Threaded, $[ST]$ :                                      |    |

|     | Single Task                                                                                                         | 57 |

| 4.3 | The CRC optimizations and their resource utilization. $[MT]$ : Multi-Threaded,                                      |    |

|     | [ST]: Single Task                                                                                                   | 61 |

| 5.1 | Data-set used for evaluating the performance model                                                                  | 74 |

| 5.2 | Performance model parameters, source, and description                                                               | 76 |

### Chapter 1

### Introduction

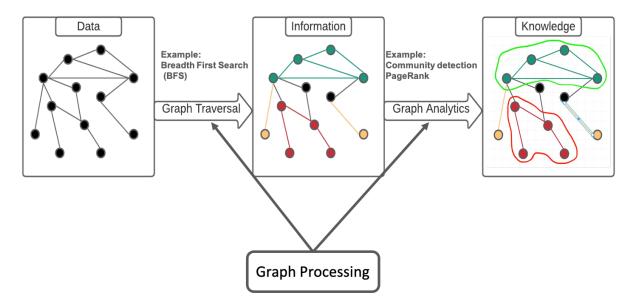

Many real-world problems can be presented as large-scale graphs with millions of vertices and billions of edges, such as social networks, biological interactions, and web graphs [37, 63]. Graph analytics is an area of study used to extract useful information from these huge datasets as depicted in Figure 1.1. For instance, in web graphs, web pages represent the graph vertices while hyper links between them represent the edges. Analyzing these types of graphs is used for web search engines, ranking websites, and network analysis among other uses [28]. The enormous size of these datasets compounded by the irregularity of the underlying problem exhibit substantial challenges to graph processing.

Figure 1.1: High level abstraction of the scope of graph processing

The importance of this application domain is highlighted by its usability to solve many problems but hampered by it underlying irregular nature. There is an abundance of research attempting to optimize graph processing via both, software optimizations [6, 20, 29, 44, 46, 48, 60, 63, 66, 67, 74] and hardware accelerators such as FPGAs [4, 5, 14, 15, 19, 21, 52, 53, 71, 75, 83]. However, efficiently utilizing such hardware accelerators with ease is still an open research problem especially when considering irregular applications like graph processing [4].

This dissertation aims to address and benefit two research areas, heterogeneous computing and graph processing. Heterogeneous computing, more specifically CPU-FPGA hybrid systems, are explored where the architectural strengths of each device are exploited. Moreover, FPGA design and optimization techniques are explored to optimize the usage of its underlying architecture. On the other hand, graph processing algorithms are analyzed to overcome some of its inherent challenges. Combining the improvements in these two research areas results in a significant overall enhancement in graph processing and CPU-FPGA hybrid systems efficiency as well.

#### **1.1 Research Problems**

Optimizing graph processing is a well-researched problem, whether it is using a generalized approach on CPUs and GPUs [22, 48, 68, 69, 74] or application specific using FPGAs [5, 57, 71, 75, 81, 84, 85]. While generalized approaches are programmable, they don't necessarily yield the best performance. On the other hand, application-specific solutions are restrictive to the targeted application only. Hence, with the rise of heterogeneous computing (more specifically, CPU-FPGA hybrid systems) and High Level Synthesis (HLS) tools, there is great potential to efficiently harness that growing computational power for irregular applications (such as graph processing). This section dissects the research challenges into two categories,

graph processing challenges, and hybrid-systems utilization challenges. Chapter 2 elaborates on the previous work and how to build on it to improve both the performance of graph applications and the efficiency of utilizing heterogeneous systems.

**Graph processing challenges** Graph algorithms are inherently difficult to process efficiently, especially when targeting large-scale real-world graphs. This application has a large memory footprint, coupled with poor locality, low compute to memory access ratio and irregular memory access pattern. As a result, system performance is usually bound by the throughput of the external DRAM bandwidth. Large scale graphs have exploded in size in recent years and extracting information from these graphs is increasingly challenging. The performance bottlenecks that hamper graph applications are diverse and variable, not only do they depend on the graph algorithm and the underlying hardware architecture, but the size and structure of the graph is also a critical variant. Graph processing challenges are summarized in the list below:

- Poor locality and irregular data access pattern

- Unstructured relationships between graph vertices lead to poor locality, which incurs frequent high latency global memory access.

- Lack of scalability

- Communication between partitions of large-scale graphs causes heavy traffic, which inhibits scalability.

- Heavy data conflicts

- Vertices from different partitions may read/write the same vertex simultaneously, leading to heavy conflicts.

Heterogeneous processing challenges There is a growing trend in high-performance computing towards heterogeneous platforms, where 25% of the top 100 supercomputers are designed using heterogeneous model employing either GPUs or FPGAs or both [18]. The use of heterogeneous systems in HPC to enhance performance is growing and proved effective for data parallel applications with regular memory access patterns [23, 56]. However, these powerful systems are still yet to be efficient in the irregular application domain such as graph applications [5, 21, 26, 71, 74, 75].

This dissertation focuses on CPU-FPGA hybrid systems. The research focuses on two aspects, exploiting the strengths of both CPU and FPGA platforms, and the process of synthesizing efficient designs on the FPGA. FPGAs offer a massively parallel configurable architecture that could be customized and optimized for a target problem and usually provide superior power efficiency, yet it has its limitations. Developing an efficient FPGA-based hardware design requires knowledge and expertise about the underlying configurable architecture. While the use of High-Level Synthesis (HLS) tools significantly reduced the level of effort to utilize FPGAs, it does not necessarily yield an efficient and performant hardware design [26, 88]. The FPGA's performance and scalability problems are aggravated when targeting irregular applications.

#### 1.2 Methodology

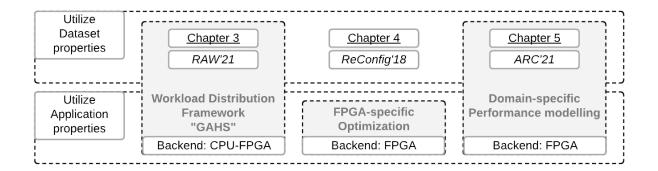

This research aims to expand the scope of graph processing frameworks to extract the best performance out of heterogeneous computing platforms when targeting graph applications domain. Hence, to tackle the challenges illustrated in Section 1.1, this dissertation lays out how to address some of the inherent challenges in graph processing in addition to exploiting the strengths of both CPUs and FPGAs. Figure 1.2 lays out the dissertation overview. First, a workload distribution framework is devised to partition the workload on devices in a CPU-FPGA hybrid system. Second, FPGA-specific optimizations are explored for irregular graph-like applications to improve the performance of the synthesized hardware. Third, an FPGA Domain-specific performance model framework is constructed to model the performance and automatically explore the optimization space for graph applications.

Figure 1.2: Dissertation overview.

The goal of this work is to optimize the performance of heterogeneous processing for graph applications. To harness the power of heterogeneous systems, one has to be able to exploit the architectural strengths of the available hardware devices. This dissertation focuses on CPU-FPGA hybrid systems, to optimize the performance of graph applications by exploiting knowledge of the graph-input dataset connectivity structure. However, exploiting the architectural strengths of FPGAs requires hardware skills, rendering it inaccessible to the masses. Hence the dissertation extends to explore how to efficiently utilize the FPGA's customizable architecture and optimize its performance, more specifically, when executing graph applications using HLS tools. Finally, research transitioned to performance model [88], we fashioned a custom performance model specifically for graph-like applications synthesized for FPGA using HLS tools. Consequently, we were able to devise a framework that explores the optimization space and recommends the best optimization strategy for a graph dataset. Testing and experimentation of the frameworks was conducted on Intel's Devcloud platform. Intel acquired Altera [9] in 2016 and in their pursuit to democratize the use of heterogeneous systems and make it accessible to the masses, they constructed the Devcloud platform. It is an experimental cluster including many nodes, where each node is constructed as a CPU-FPGA hybrid system or a CPU-GPU hybrid system. During my research I have been granted access to the Devcloud platform to run my experiments to verify my research, which also serves them as a way of advertising for their beta software/hardware system. This allowed me to join their community, Intel Innovators, which is tasked with providing feedback of user experience of their system as well as participating in conferences and workshops to promote their heterogeneous ecosystem.

#### **1.3** Contributions

This dissertation attempts to have a meaningful impact on both the graph analytics community and the heterogeneous/FPGA computing community. First, the graph processing community would benefit from improving the performance of graph analytics applications. Second, the FPGA community would benefit from research regarding FPGA specific optimization and domain-specific performance modelling which would ultimately serve the greater goal of including FPGAs into mainstream computing. The recent purchase of Xilinx by ARM [10], in addition to previous Altera acquisition by Intel [9], suggest trending towards tighter coupling of CPUs and FPGAs, perhaps on the same chip. The resulting collective impact of this research is well positioned to harness the computational power of a CPU-FPGA hybrid system, more specifically when targeting graph applications. To achieve the goal of high-performance scalable graph processing on heterogeneous platforms, multiple underlying steps have been taken. Hence, this study was conducted in four phases. In a first phase, graph datasets are evaluated on CPUs and FPGAs to capture the execution profile of such an irregular application. In a second phase, multiple aspects of irregular applications are analyzed such as memory access patterns, in addition to the execution profile, to formulate the basis of a workload distribution plan in order to exploit the strengths of each hardware device in a heterogeneous system. Up to  $6.5 \times$  speedup was achieved compared to CPU-only and FPGA-only implementations, by simply distributing the workload on a CPU-FPGA hybrid system. In a third phase, due to the inefficiency of irregular applications execution on FPGAs, architecture specific optimizations were explored to accelerate sub-optimal performance of graph applications on FPGAs. In a fourth phase, a custom performance model is built to project the execution profile of graph applications on FPGAs and explore the optimization space. Compared to the architecture agnostic implementations,  $3.4 \times$  speedup was achieved executing graph applications using the automated framework's optimization recommendations. The framework recommended the best optimization strategy in 90% of the test cases.

To that end, the contributions of this dissertation can be summarized as follows:

Augmenting graph input characteristics into a workload distribution framework (GAHS: Graph Analytics on Hybrid Systems), which is described in detail in chapter 3. Since graph applications follow a data-driven computation style, each graph input has its unique impact on the execution profile. Hence, generalizing an optimization approach for all graph datasets will not yield the best performance. Therefore, GAHS Utilizes the graph features to decide the best workload distribution over the resources of a CPU-FPGA hybrid system.

- Formalizing a method to optimize irregular applications such as graph processing when targeting hardware-based accelerators (HLS-based FPGA designs). Candidate code patterns for optimizations were identified and optimization recipes were created and applied as detailed in chapter 4.

- Addressing the irregular nature of graph applications that makes performance modeling erroneous, a domain-specific performance model has been devised for HLS-based FPGA designs. General purpose performance models are usually accurate for compute bound applications (i.e., regular applications), but fails to capture the execution profile of memory bound applications (i.e., graph applications). Exploiting knowledge of the graph structure aided the model to capture the execution profile of such a data-driven application domain, as depicted in chapter 5.

- Exploring the optimization space of graph kernels on FPGAs, an automated framework has been devised assisted by the domain-specific performance model. The framework guides the best optimization strategy for FPGA designs based on knowledge of the graph input properties and hardware design specifications. Chapter 5 details how such an automated framework relieves FPGA developers of the time-consuming burden of manually synthesizing and testing various optimization strategies attempting to maximize performance.

#### 1.4 Dissertation outline

The rest of this dissertation is organized as follows. Chapter 2 discusses background and related work. Chapter 3 describes a framework for workload partitioning and scheduling of graph analytics on CPU-FPGA hybrid systems exploiting the architectural strengths of both CPUs and FPGAs collectively. Chapter 4 addresses the efficiency and optimization of utilizing reconfigurable architectures to process irregular applications such as graph problems. Chapter 5 presents a domain-specific performance model and an automated framework to explore the optimization space for graph applications on FPGAs. Finally, Chapter 6 provides a summary of the contributions and outlines future research paths.

### Chapter 2

### **Background and Related Work**

While there are many ways computer scientists can attempt to accelerate the graph processing problem and scale it efficiently (such as optimizing software libraries, abstracting domain specific APIs, and using hardware accelerators), this work focuses on utilizing heterogeneous systems. This dissertation builds upon the work of graph processing, FPGA optimization, and heterogeneous computing domains. This research endeavor aims to enhance the performance and scalability of graph applications while exploiting the strengths of heterogeneous platforms, more specifically, CPU-FPGA hybrid systems.

This chapter first introduces background about graph processing in general in Section 2.1, later, chapters 3,4,5 elaborate in detail the background of each specific graph application used. Afterwards, Section 2.2 discusses previous research in the heterogeneous computing area concerning graph processing. Then, Section 2.3 presents previous work related to utilizing graph input properties to influence the runtime decision of graph processing. Later, Sections 2.4,2.5 detail previous efforts to optimize and model the performance of HLS based FPGA implementations. Finally, Section 2.6 summarizes the research attempts in each area and how it is built upon in this dissertation to achieve the overarching goal of enhancing graph processing on heterogeneous systems.

#### 2.1 Graph Processing Background

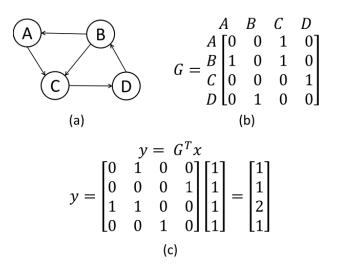

This section describes the algorithmic properties of graph algorithms and their impact on the underlying hardware architecture. Many graph applications depend on sparse matrix vector operations as shown in Figure 2.1, which like most graph algorithms are typically characterized by their workload imbalance, unpredictable control flow, and irregular memoryaccess patterns. Such an application domain usually executes data-driven computations dictated by the connectivity structure of the graph, while performing a relatively small amount of computation, which makes execution time governed by the memory access latency.

Figure 2.1: Graph (a) Logical representation (b) Adjacency matrix (c) In-degree calculation as SPMV (adopted from [69]).

Such pointer-based computation is unstructured and requires highly irregular fine-grained random memory accesses. This leads to poor temporal and spatial locality, which inhibits performance scalability on cache-based processors, especially when targeting real life largescale graphs. Properties of this application domain are listed below:

- *Data driven computation:* Most graph algorithms are iterative, where each iteration depends on the data processed (vertices and edges) in the previous iteration.

- *Irregular memory access:* Indirect, pointer-based memory references lead to random memory accesses with high latency.

- *Poor temporal and spatial locality:* Portions of a graph algorithm may be able to employ data reuse (high temporal locality), while other portions of the algorithm may have contiguous memory accesses (high spatial locality). Taking advantage of both locality types is challenging, while optimizing for one type and neglecting the other typically causes a performance hit.

- Low compute to memory access ratio: A significant amount of the graph workload is for traversing the graph while a much smaller amount is required for doing actual computation. This is the reason for characterizing this application domain as memory bound.

Graph applications are generally characterized by a low computation to communication ratio. A previous study by Ham et al. [22] showed that more than 90% of a graph algorithm's instruction (or execution time) is spent on traversing the graph, which translates to communication or global memory accesses. On the other hand, less than 10% of the instructions are for computation.

General-purpose processing (CPUs) is not ideal for such an execution profile. The fixed memory access granularity based on cache line sizes is rigid and wasteful in terms of memory bandwidth. This irregular application domain requires much finer granularity when accessing the global memory, where in the case of coarser grained CPU memory transaction,

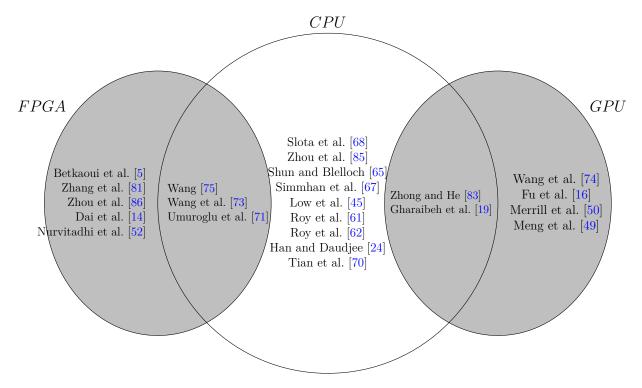

Figure 2.2: Overview of graph solvers: classification of hardware platforms

simply translates to wasted memory bandwidth. Hence, when executing such an irregular application, the little or no spatial and temporal locality of the application make it challenging to scale good performance on general-purpose CPUs. GPUs, on the other hand, offer massive parallelism for Single Program Multiple Data (SPMD) like applications. Graph applications with varying degrees of parallelism are a challenging target to harness the computational power of GPUs. While CPUs and GPUs are easier to program, FPGA designs are more flexible and power efficient. The data-driven execution profile of FPGAs saves a lot of the energy used by CPUs and GPUs to decode instructions and look up data in the cache, which usually consume the majority of power in instruction-based architectures. Table 2.1 shows an overview of the latest graph processing frameworks and their properties, while Figure 2.2 shows a visual representation of the hardware platform classification of graph solvers.

| Graph processing framework              | Year   | System architecture | Hardware platform |

|-----------------------------------------|--------|---------------------|-------------------|

| [68] Solta et al.                       | (2015) | Distributed         | CPU               |

| [85] Zhou et al.                        | (2017) | Distributed         | CPU               |

| [65] Ligra: Shun, et al.                | (2013) | Shared-memory       | CPU               |

| [67] GoFFish: Simmhan, et al.           | (2014) | Distributed         | CPU               |

| [45] GraphLab: Low, et al.              | (2010) | Shared-memory       | CPU               |

| [61] X-Stream: Roy, et al.              | (2013) | Shared-memory       | CPU               |

| [62] Chaos: Roy, et al.                 | (2015) | Distributed         | CPU               |

| [24] Giraph: Apache Software Foundation | (2012) | Distributed         | CPU               |

| [70] Giraph++: Tian, et al.             | (2013) | Hybrid              | CPU               |

| [73, 75] Wang, et al.                   | (2018) | Shared-memory       | FPGA+CPU          |

| [71] Umuroglu, et al.                   | (2015) | Shared-memory       | FPGA+CPU          |

| [5] Betkaoui, et al.                    | (2012) | Distributed         | FPGA              |

| [81] Zhang, et al.                      | (2017) | Shared-memory       | FPGA              |

| [86] Zhou, et al.                       | (2018) | Shared-memory       | FPGA              |

| [14] FPGP: Dai, et al.                  | (2016) | Shared-memory       | FPGA              |

| [83] Medusa: Zhong, et al.              | (2013) | Distributed         | GPU+CPU           |

| [19] TOTEM: Gharaibeh, et al.           | (2013) | Hybrid              | GPU+CPU           |

| [74] Gunrock: Wang et al.               | (2016) | Distributed         | GPU               |

| [16] MapGraph: Fu, et al.               | (2014) | Distributed         | GPU               |

| [50] Merrill, et al.                    | (2012) | Distributed         | GPU               |

| [48] Pregel: Malewicz, et al.           | (2010) | Distributed         | N/A               |

| [69] GraphMat: Sundaram, et al.         | (2015) | Shared-memory       | N/A               |

Table 2.1: Overview of graph processing frameworks.

### 2.2 Heterogeneous Computing &

#### Workload Partitioning

Various graph solvers make use of hardware accelerators to improve the performance of graph processing either using GPUs [16, 50, 74] or FPGAs [14, 25, 42, 52]. GPUs may appear poorly suited for graph processing, since massive parallelization with lack of adequate synchronization introduces load balancing and under-utilization problems. However, as stated by Merrill et al. [50], two key optimization techniques may alleviate these challenges, multi-threading and fine-grained synchronizations. Unlike the main GPU-based research, Zhong and He [83] and Gharaibeh et al. [19] leveraged the heterogeneity of CPU-GPU hybrid platform to

enhance the performance of graph processing. Zhong and He [83] introduced Medusa, a programming framework that exposes C/C++ APIs to make use of GPUs' massive parallel data structure. On the other hand, TOTEM, introduced by Gharaibeh et al. [19], distributes the workload on both GPUs and CPUs, where highly parallel workloads are assigned to GPUs, while small parallelism degree workloads are assigned to CPUs.

Many FPGA-based graph processing frameworks have been proposed, such as GraphGen [52], FPGP [14], GraphOps [53], ForeGraph [15], and others [5, 25, 42, 71, 75, 81]. However, the cooperative use of CPU-FPGA hybrid systems was not as extensively researched.

Research proposed by Umuroglu et al. [71] exploits a CPU-FPGA heterogeneous device to accelerate graph processing, specifically the Breadth-First Search (BFS) problem. They aim to maximize the memory bandwidth utilization and create a stall-free data path on the FPGA. The workload is partitioned to offload low parallelism iterations on the CPU while leaving the high parallelism iterations to the high-throughput FPGA. They achieve an average traversal speed of 172 million traversed edges per second (MTEPS).

Other work by Wang el al. in [75, 76] exploits the close coupling of CPU and FPGA in the shared memory architecture of the Heterogeneous Architecture Research Platform (HARP). The authors optimize data access by optimizing the on-chip data reuse. Moreover, they utilize the heterogeneity to implement Processor Assisted Scheduling (PAS) which offloads the scheduling tasks to the CPU and leaves the high-throughput data crunching to the FPGA. While employing hardware and pre-processing optimizations, they achieved a maximum performance of approximately 280 MTEPS for sparse graphs. While this work strives to optimize the custom FPGA design to maximize performance, it makes their design strictly application-specific.

#### 2.3 Graph-Input Aware Research

This section highlights the impact of the graph input on the execution profile of a graph processing framework. Programmable graph processing frameworks such as Gunrock [74] tend to integrate graph primitives to augment a general-purpose library. However, as stated by Meng et al. [49], these programmable approaches may fail to deliver optimized performance due to sensitivity to the input graph instance in addition to variations in the execution profile of different graph algorithms. For example, the best hand-tuned BFS implementation using Gunrock library achieves 47 GTEPS on a power-law graph, while executing a road-net graph performance drops to 44 MTEPS. The optimizations applied to graph traversal applications such as BFS, are not applicable to the denser workload of centrality measure applications such as PageRank.

GSWITCH, proposed in [49], is a pattern-based algorithmic auto-tuning system. It includes a set of algorithmic patterns that assemble variants of the algorithm and dynamically switches between optimization strategies with negligible overhead. This framework abstracts a graph algorithm as a set of algorithmic patterns characterized by quantitative parameters. Other work [79] proposes an input aware auto-tuning framework for parallel sparse matrix-matrix multiplication called IA-SpGEMM. This is strongly related to graph applications since the two application domains share many of characteristics. IA-SpGEMM automatically decides the best sparse format for arbitrary sparse matrices to enhance the performance based on sparse features from the input including statistics of the matrix sparsity, the ratio of nonzero elements and its variance. This work is limited to deciding the best sparse format to be used. While both [49, 79] work was tested on CPUs and GPUs, none took advantage of the heterogeneity of the system.

#### 2.4 HLS Design and Optimization on FPGAs

Czajkowski et al. [12] were the first to propose Altera's OpenCL compiler demonstrating four well-known applications: Monte Carlo Black-Scholes (MCBS), matrix multiplication (SGEMM), finite difference (FD), and particle simulation (Particles). To enhance the performance of dynamic programming on FPGAs, Settle [64] introduced OpenCL pipes [64], which improves the performance by  $1.5 \times$  and  $9.9 \times$  in comparison to the GPU and CPU implementations, respectively, while providing energy savings of up to 26-fold. Both endeavors achieved high utilization of FPGA resources with low clock frequency (less than 200 MHz). Moreover, the FPGA-specific implementations differed from their GPU-based counterparts. While the GPU implementation used SIMD-like parallelism, the FPGA implementation adopted a MIMD-like execution where each thread executed a distinct operation on a set of data items.

More recent research efforts proposed by Zohouri et al. [88] evaluated the performance of six regular benchmarks from the Rodinia suite using the Altera OpenCL SDK on a Stratix V FPGA. The original OpenCL implementations followed the bulk synchronous parallel (BSP) execution model, targeting GPU-like architectures with massive multi-threaded execution. Unfortunately, this approach can degrade FPGA performance due to barrier synchronization points that dictate flushing the pipeline, effectively halving the pipeline throughput. The authors in [88] reached the conclusion that FPGA-specific optimizations must be applied to the OpenCL kernels to yield efficient, high-performance hardware designs. In particular, they outlined five main FPGA-specific optimization techniques: compute unit replication, vectorization (or "SIMD-iztion"), loop unrolling, shift registers, and sliding windows. These optimizations improved the performance by up to two orders of magnitude compared to the BSP OpenCL kernels and achieved  $3.4 \times$  better power efficiency when compared to the

#### NVIDIA K20c GPU.

The work published by Zohouri et al. [88] was extended in [55] to evaluate the performance of three different design methodologies for FPGAs: general-purpose manycore system (30 Nios II soft-core processors), FSM-based architecture using LegUp HLS tool (MIMD architecture with focus on lower latency), and Intel's FPGA SDK for OpenCL (deeply-pipelined architectures with focus on higher throughput). The experiments showed that the FSM and soft-core implementations have scalability issues that are mainly related to cache conflicts and capacity misses. This issue was partially solved using a multi-banked cache design. However, the OpenCL implementations still outperformed both approaches across all the applications with up to two orders-of-magnitude speedup.

Other work [40, 72] used the OpenDwarfs benchmark suite to evaluate the performance of the OpenCL programming model on a Stratix V FPGA using the Altera OpenCL SDK. Kernels from regular application domains were tested, such as N-body methods, structured grids, unstructured grids, and dense linear algebra. Unlike Rodinia, the OpenDwarfs suite provides architecture-agnostic OpenCL kernels rather than GPU-specific (i.e., GPU-biased) implementations. These kernels were used as the baseline for comparison on the CPU, GPU, Intel MIC, and FPGA architectures. The authors explored FPGA-specific optimization techniques that exploit different parallelism levels as well as minimizing data movement across the memory hierarchy. It was also reported that the architecture-agnostic OpenCL kernels yielded inefficient hardware designs, which further suggests the need for FPGAspecific optimizations.

Finally, XSBench, a proxy application for Monte Carlo simulation, was used in [47] to evaluate the performance of OpenCL applications with irregular memory accesses on FPGAs on an Intel Arria 10 FPGA platform. The authors applied three different optimizations and evaluated their effect on performance. A fused multiply-add unit was integrated into the design. The BRAMs were used to implement a constant cache along with data pre-fetching and packing techniques. The final optimization technique used vector data types and stored them in private memory. Applying these optimizations delivered a 50% improvement in energy efficiency, while sacrificing 35% of the performance compared to an Intel Xeon CPU with eight cores.

## 2.5 HLS Performance Modelling and Design Space Exploration

As demonstrated in multiple publications [7, 17, 39, 55, 77], the expected performance for HLS design is highly unpredictable. Also, HLS tools require FPGA-specific optimizations more often than not in order to yield efficient hardware architectures [26, 40, 47]. One of the earliest works on modelling performance for HLS design was presented in [77]. Static and dynamic analyses were used to build an analytical performance model for the key architectural features of FPGAs under the OpenCL programming model. This tool can predict the performance of OpenCL kernels with different combinations of FPGA-specific optimizations. This greatly helps in guiding the code-tuning process for performance purposes. However, this approach depends on collecting information by performing static analysis of the LLVM code, dynamic profiling of the OpenCL application execution on GPUs, then feeding the information into the analytical model. This amount of information is not readily available for users and is not easily reproducible for new applications.

Zohouri et al. [88] presented one of the latest works in the performance of OpenCL kernels on a Stratix V FPGA. They proposed in this work an analytical performance model that captures the baseline performance of HLS designs. The approach presented is sound but will only be feasible in the case of compute bound applications. However, in the case of irregular memory access applications such as memory bound graph applications, the model fails to depict the execution profile accurately. Moreover, the exploration of optimization techniques was wildly off par. This is mainly due to the simplistic memory access model presented in their work.

Other interesting work proposed by Da Silva et al. [13], explores the idea of extending the roofline model [78] to the HLS design space. This work utilizes the resource consumption and the parameters used in the HLS tools, to maximize the performance and the resource utilization within the area of the FPGA. This work considers the resource utilization on the FPGA to maximize area usage by replicating the Processing Entities (PEs), and in turn maximize performance. However, in addition to the limited bandwidth of global memory access on FPGAs, complications may arise due to the irregular memory access patterns of graph applications. Moreover, this work only recognizes the peak performance attainable on the FPGA design, which is not realistic considering the irregularity of the graph applications domain.

Another effective design space exploration work was proposed in [82], where they recursively quantify the loop latency through an analysis on the LLVM-IR level. However, a major drawback that would make this work not well suited for graph applications, is that their analysis depends on having static loop bounds. This work is efficient in the case of regular memory access applications, where the loop bounds are usually static and global memory can be accessed through fixed stride accesses. However, unfortunately this is not the case for graph applications. Graph applications have an inner loop which is dynamically bound depending on the data input which makes this work an un-viable candidate for design space.

#### 2.6 Discussion

In summary, previous studies by Meng et al. [49], Xie et al. [79] showed the impact utilizing graph input properties to influence runtime decisions in graph processing and sparse matrix operations. Moreover, it has been established how powerful heterogeneous systems can be if its computational potential can be efficiently harnessed. Hence, this dissertation explores how to exploit the strength of each device in a CPU-FPGA hybrid system supported by the knowledge gained from graph input analysis, which facilitated the formulation of an automated framework for workload distribution and scheduling on both CPUs and FPGAs. Chapter 3 elaborates about this topic in detail.

Focusing on FPGA implementations, previous studies showed the need for applying FPGAspecific optimizations to OpenCL kernels to generate efficient custom hardware accelerators. However, the expected performance and efficiency is highly dependent on the characteristics of the target application as well as the graph input properties. Moreover, generic OpenCL kernels (following the BSP execution models), achieve high performance on GPUs, but generate extremely inefficient FPGA designs. While previous work generally focused on regular OpenCL kernels, this dissertation attacks the problem of optimizing the more challenging problem of *irregular* applications such as graph processing. The importance of this particular study is highlighted by the development of new benchmarks, such as CHO [51], developed for the sole purpose of providing unoptimized OpenCL kernels to test the FPGA capabilities using OpenCL compilers. Further details about the FPGA-specific optimization are examined in Chapter 4.

Modelling the performance of such FPGA designs is challenging especially in the case of irregular applications. Previous research relied on dynamic profiling [77], simplified memory access modelling [88], and oversimplified assumptions [82]. However, this dissertation tackles

the performance modelling for irregular graph applications by augmenting the innovative idea of using information from the dataset input. Building on the performance model proposed in [88] and augmenting it with knowledge from graph-input aware research, we were able to capture the execution profile of irregular memory accesses. This addressed the problem of simplified memory access modelling without the need for extra information gathering using dynamic profiling which is discussed in detail later in Chapter 5. This work extends the use of graph input properties which helped in formulating an automated framework for exploring the optimization space.

# Chapter 3

# Workload Distribution on CPU-FPGA Hybrid Systems

This chapter focuses on a high-level view of system design, in particular heterogeneous computing. The focus in this chapter is shifted towards a CPU-FPGA hybrid system, where the architectural properties of each device are exploited to enhance the performance of graph applications processing. This chapter examines two hypotheses. First, a variety of properties of a set of graph instances are extracted and examined to determine if they can be used to predict the analytical execution profile on different hardware devices. Second, can this information be used to partition the workload and properly schedule it on a hybrid CPU-FPGA system. This work is intended to enhance the performance and scalability of graph processing by exploiting the heterogeneity of CPU-FPGA hybrid systems [28].

This chapter details a framework called Graph Analytics on Hybrid Systems (GAHS) for workload partitioning and scheduling of graph analytics on hybrid systems. The decisionmaking process of the framework is configured to be guided by data input properties. The goal of this work is to expand the design space exploration to include both CPUs and FPGA. Moreover, GAHS not only depends on the characteristics of the application and the available hardware resources but also includes data input properties.

## 3.1 Motivation & Goal

Many real-world problems can be presented as large-scale graphs with millions of vertices and billions of edges, such as social networks, biological interactions, and web graphs [37, 63]. Graph analytics is an area of study used to extract useful information from these huge datasets. For instance, in web graphs, web pages represent the graph vertices while hyperlinks between them represent the edges. Analyzing these types of graphs (in this case, usually using the PageRank algorithm [54]) are used for web search engines, ranking websites, and network analysis among other uses. This emphasizes the motivation for enhancing the performance and scalability of graph applications.

### 3.1.1 Challenges

Performing graph analytics to extract useful information from these ever-growing graphs is a complex and challenging task. The sheer size of these graph data-sets combined with the irregular nature of the underlying problem pose a significant challenge for performance, scalability, and power efficiency [4, 26]. Large real-world graphs are challenging to process efficiently, not only due to their large memory footprint, but most graph algorithms entail irregular data-dependent memory access patterns with low compute to memory access ratio. To complicate matters further, these data-sets tend to be scale-free (following the powerlaw degree distribution), which makes load balancing and access locality harder to achieve. Analyzing and extracting useful information from this big data domain is challenging, which emphasizes the important role of high-performance scalable graph processing.

Previous research attempted to overcome the challenges of graph processing using the growing trend in heterogeneous high-performance computing. The use of hybrid systems to enhance the performance of applications is growing and proved effective for data-parallel applications with regular memory access patterns [23, 56]. However, these powerful systems are still yet to be efficient in the irregular applications domain such as graph applications [5, 21, 26, 71, 74, 75]. On the other hand, there is little prior work that explores optimizing the graph processing environment using the features of the input graph instance while targeting a hybrid ecosystem.

### 3.1.2 Approach

Observing a hybrid ecosystem of hardware including CPUs and FPGAs, each platform excels in a specific aspect. Generally, CPUs are easily programmable and can take advantage of instruction-level parallelism and sophisticated cache policies. On the other hand, FPGAs offer superior power efficiency and customizable hardware architecture to fit an application's needs. Hence, this chapter presents a graph analytics framework (GAHS) that exploits the strengths of each platform through efficient workload partitioning on a CPU-FPGA hybrid ecosystem. Moreover, GAHS auto-tunes the workload distribution based on graph input features (since it is a data-driven application). Not only that, but GAHS also learns as it goes. Augmenting GAHS's library with more execution profiles helps in fine-tuning the workload distribution decision making process.

### 3.1.3 Contributions

Using multiple workload distribution designs and graph input features, GAHS framework was able to achieve significant performance improvement compared to CPU-only, FPGAonly implementations, and state-of-the-art hybrid FPGA solvers. Results show that up to  $6.5 \times$  speedup can be attained over a CPU-only or FPGA-only implementations through proper distribution of the workload. Moreover, GAHS achieves an average of  $18 \times$  speedup compared to state-of-the-art hybrid CPU-FPGA solvers. The contributions of this work are listed below:

- Analyzing and profiling the execution of multiple graph types with a wide range of properties.

- Devising a novel framework that uses graph input features to decide the best workload distribution over the resources of a CPU-FPGA hybrid system.

- Constructing a self-learning technique, where the framework fine-tunes its decisionmaking process as it ingests more graphs via a feedback loop.

# 3.2 Background

This section explains the background of the PageRank application, the graph data-set, and the workload distribution configurations used. This is intended to introduce the problem scope and design space. PageRank application is used as a case study to showcase GAHS, so a detailed explanation of the algorithm and its kernel implementation is presented in Section 3.2.1. Then we elaborate on the graph data-set and the feature-set used to characterize graph properties. Finally, we demonstrate our workload distribution configurations.

### 3.2.1 PageRank Algorithm

PageRank (PR) is an algorithm used by the Google search engine to rank web pages [54]. Initially, PR assigns an equal PR value of the reciprocal of the number of vertices to all the vertices of the graph. Afterward, a series of *superstep* iterations are executed that terminate either after a user-defined iteration count or an automated convergence check condition. In each iteration, each vertex donates a share of its PR value to its neighbors along its outgoing edges. The number of outgoing edges of each vertex is used to divide the PR value equally among the recipient vertices. After the summation operation of each vertex calculating the total PR value donated to it, a damping factor is applied to the final PR value. The damping factor is a value set between 0 and 1, to which the default is 0.85. For this work, the default damping factor is used and the number of iterations of PageRank is set to 20 iterations.

The implementation in this chapter as in Chapter 4 is based on the SPMV-based PageRank algorithm from [8]. The kernels breakdown is shown in Table 3.1. The graph input is imported into a *compressed sparse row* (CSR) data structure and a CSR initialization kernel is invoked. The CSR initialization kernel is responsible for updating the sparse matrix that represents the graph to be compatible with SPMV calculations. Originally the sparse matrix included only the connectivity structure of the graph; however, after invoking the CSR initialization kernel, it is updated to consider the portion of PR value a vertex will receive from its neighbors. This allows a standard SPMV kernel to perform the PR value update, where the SPMV's dense vector represents the previous iteration's PR values for the vertices without the need for atomic addition (which is required in the original algorithm). The added overhead of including the CSR initialization kernel is insignificant relative to the overhead of the atomic addition operation required by the original PageRank algorithm [8].

| Kernel code-name | K1                     | K2                                      | K3                         | K4                                          |

|------------------|------------------------|-----------------------------------------|----------------------------|---------------------------------------------|

| Kernel name      | init_buffer()          | CSR_initialize()                        | SPMV()                     | PR_update()                                 |

| Description      | Initializes PR buffers | Constructs CSR matrix<br>from the graph | Performs SPMV calculations | Updates PR array with<br>the damping factor |

Table 3.1: Kernels of the SPMV-based PageRank algorithm and the relevant kernel naming code used throughout this chapter.

### **3.2.2** Graph Data-set and Features

The network data repository [59] is used as the source of real-world graphs used in this work. To ensure the generality of different types of graphs for the framework's learning process, we use a set of graphs with a wide range of properties as shown in Table 3.2. Although only a sample of the graphs is shown, 25 unweighted directed graphs were used spanning different types of graph data-sets including web graphs, social networks graphs, email graphs, citation networks, ecology networks, and road networks. This sample is used to evaluate the initial parameters of the framework's decision tree. Graph analytics applications (including PR application) follow a data-driven execution profile, which emphasizes its high sensitivity to the properties of the input graph. Since the goal is to capture a graph's sparsity and connectivity structure, we chose the features shown in Table 3.2, which are explained below.

- CC (Clustering Coefficient): is a measure of the tendency of graph vertices to cluster together.

- D (Diameter): is the greatest distance between any pair of vertices in the graph.

- DEG (average degree): is the average number of edges for graph vertices.

- SCC (Strongly Connected Component): is a maximal strongly connected subgraph.

This feature-set has been selected based on graph parameters used in [49, 79] for inputaware execution, augmented with additional parameters that capture the graph connectivity

| Туре                  | Graph              | Vertices | Edges    | $\mathbf{C}\mathbf{C}$ | D  | DEG | SCC      |

|-----------------------|--------------------|----------|----------|------------------------|----|-----|----------|

| Road network          | road-road-usa      | 23947347 | 28854313 | 0.0176                 | 10 | 2   | 0        |

| Collaboration network | ca-hollywood-2009  | 1069126  | 56306654 | 0.7664                 | 4  | 105 | 0.000001 |

| Web graph             | web-Stanford       | 281903   | 2312498  | 0.5976                 | 10 | 16  | 0.533985 |

| Social network        | socfb-Georgetown15 | 9414     | 425639   | 0.225                  | 3  | 90  | 0.000106 |

| Ecology network       | eco-foodweb-baydry | 128      | 2138     | 0.3346                 | 2  | 33  | 0.804688 |

Table 3.2: Sample of the data-set used for initializing GAHS.

structure. The workload per iteration in the PR application depends on the number of neighbors for each graph node, hence, the selected feature-set has a direct impact on the amount of computation and memory requests in each iteration.

The features and statistics of the data-set have been collected using SNAP library functions [43]. We use this feature-set to capture the structure of a graph instance. This structure directly affects the execution profile of the graph application in multiple ways. For instance, it affects the data parallelism granularity and memory transactions granularity. While CPUs take advantage of sophisticated cache policies, the fixed memory access granularity (which is based on the size of a cache line) is not well suited for graph processing. Graph applications may require much finer granularity when accessing the global memory, which in the case of coarser-grained CPU memory transactions simply translate to wasted memory bandwidth.

The graph structure also affects the pipeline parallelism efficiency, which is important for FPGA implementations. The data-driven execution model of FPGAs is well suited for the graph application domain. However, the graph structure may impose stalls in the data path pipeline (waiting for global memory access), significant performance degradation is observed. Hence, when executing such an irregular application with limited spatial and temporal locality, we aim to exploit the strengths of both general-purpose CPUs and application-specific FPGAs.

### 3.2.3 Workload Distribution Configurations

The execution of the PageRank algorithm was profiled for both CPU execution and FPGA execution to come up with reasonable partitioning of the workload over the available resources. The workload distributions chosen for this work are based on the execution profile of multiple graph inputs. Four design configurations were used to partition the workload between the CPU and FPGA in addition to CPU-only and FPGA-only configurations. In these cases (CPU-only and FPGA-only) the workload is not distributed over multiple devices, rather offloaded to one device only. Depicted in Table 3.3 are the different workload partitioning designs with the distribution of kernels among CPUs and FPGAs. Offloading kernels to the appropriate hardware resource in a hybrid system shows significant performance improvement as discussed later in Section 3.4.

| Configuration | Workload distribution |      |      |      |  |  |  |

|---------------|-----------------------|------|------|------|--|--|--|

| Comgutation   | K1                    | K2   | K3   | K4   |  |  |  |

| Config-CPU    | CPU                   | CPU  | CPU  | CPU  |  |  |  |

| Config-FPGA   | FPGA                  | FPGA | FPGA | FPGA |  |  |  |

| Config-1      | FPGA                  | CPU  | FPGA | FPGA |  |  |  |

| Config-2      | FPGA                  | CPU  | CPU  | FPGA |  |  |  |

| Config-3      | FPGA                  | CPU  | CPU  | CPU  |  |  |  |

| Config-4      | CPU                   | CPU  | FPGA | FPGA |  |  |  |

Table 3.3: The distribution of kernel computations over the hybrid system for the different workload distribution configurations.

During the initial stages of building the framework, it was observed that the "CSR\_initialize" kernel denoted as "K2" is significantly slower when executed on the FPGA compared to the CPU implementation. The reason is the many irregular global memory accesses required by that kernel that are not amortized over the very lightweight computation of the kernel. This influenced the decision when designing the workload distribution configurations to always offload that kernel to the CPU (except in the FPGA-only configuration). This emphasizes the importance of sharing the workload across the available hardware resources in the hybrid system.

# 3.3 Graph Processing on Hybrid Systems Using GAHS

The goal of GAHS framework is to make the best use of the available resources in a hybrid system. The general structure of GAHS is shown in Figure 3.1, which shows the breakdown of the components of the framework. GAHS is divided into two major parts, a back-end, and a front-end. The back-end constructs the analysis and learning process while the front-end recommends workload distributions for new incoming graph instances. GAHS is first initialized using the execution profile of a graph data-set with a wide range of properties. Then, it correlates relations between the execution profile of a graph and the different workload distribution configurations. After that initial start, GAHS can start recommending workload distribution configurations to new graphs. It also makes use of a feedback loop that uses the new graphs' execution profile to refine its analysis and recommendation process.

Figure 3.1: GAHS framework general structure and its associated components.

### 3.3.1 Execution Profile Library

The first module of GAHS's back-end is responsible for quantifying the execution profile of the application. This module is responsible for maintaining data structures and storing the initialization graphs' execution profiles in addition to execution profiles acquired from a learning feedback loop. A custom data structure was developed in this module to store all the relevant information of a graph's execution profile, including graph names, timing reports, and indexing pointers for easy information retrieval.

### 3.3.2 Analysis Engine

The analysis engine examines the properties of a graph instance along with its execution profile. This is a major component of the framework designed to find the best configuration for a graph instance with the objective of minimizing the execution time. This module is aware of the different design configurations identified earlier in Section 3.2.3. The information from the execution profile library is extracted and combined with the appropriate workload distribution design configuration. At this point, the analysis engine has the execution profile of each kernel along with information about the hardware resources used to execute each kernel. Next, the analysis subroutine is initiated to analyze the application's execution profile breakdown.

The execution profile is broken down into three major parts, host-device communication, kernel execution time, and workload distribution overhead. Although both the CPU and FPGA are considered computational devices, in this instance the 24-core CPU is referred to as the host while the FPGA is referred to as the device. The host-device communication pertains to loading initial data to the device and unloading the final result to the host. This is mainly affected by the memory bandwidth of a hardware resource. The kernel execution time is purely dependent on the efficiency of the hardware resource used when executing a specific kernel. For example, high data parallelism and fine-grained kernel computations are more suited to FPGA execution, while irregular cache-friendly kernels are better suited for CPU execution.

The workload distribution overhead pertains to the overhead incurred by moving data from one hardware device to the other. It is calculated as a ratio of the communication time relative to the performance gain of offloading computation to another device. This overhead is mitigated by parallel execution on more than one hardware device; however, its effect is not negligible. The analysis engine calculates the relative overhead coefficient that results from using a specific configuration with a specific graph input. This relative overhead coefficient is used later in the recommendation system.

### 3.3.3 Correlation Engine

The correlation engine starts by drawing relations between the analyzed information from the analysis engine and the graph input features. It is responsible for drawing links between graph input characteristics and hardware architecture abstractions for each kernel. The set of features identified previously in Section 3.2.2 are used to set the parameters that construct a scoring system. Thresholds for these parameters are set by the correlation engine using empirical evaluation of the initialization data-set. However, the more execution profiles learned by the framework, the more fine-tuned these thresholds are. The scoring system is explained later in Section 3.3.4, but the parameter thresholds are set at this stage. This module includes an iterative method that sets the parameter thresholds based on graph features linking it to the best workload distribution configuration. Absolute graph features identified in Section 3.2.2 are used in addition to a combined feature  $\left(\frac{V}{E}\right)$ , which is a measure of the sparsity of the graph.

- (V, E): The graph size is used to evaluate whether the graph fits in the cache memory of the CPU.

- (*CC*): Higher clustering coefficients translate to higher data reuse between different vertices. Properly designed hardware implementations can exploit data reuse to significantly enhance performance on FPGAs.

- (*DEG*): The degree of a vertex determines the number of its neighbours, which directly translates to the number of memory requests required to perform computation for that vertex. FPGAs offer flexible granularity for memory requests making use of burst coalescing memory access up to a maximum threshold (defined by the hardware specification). On the other hand, CPU cache has a fixed granularity, where if it doesn't match that of the graph instance may lead to many cache misses.

- $(\frac{V}{E})$ : Graph sparsity directly impacts the number of stall cycles required to resolve global memory requests.