## Defending Real-Time Systems through Timing-Aware Designs

Tanmaya Mishra

Dissertation submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

> Doctor of Philosophy in Computer Engineering

Thidapat Chantem, Chair Ryan Gerdes Ning Zhang Eli Tilevich Guoqiang Yu

April 22, 2022

Arlington, Virginia

Keywords: Real-time systems, Security, Trusted Execution, CAN, CFI, Mixed Criticality Copyright 2022, Tanmaya Mishra

## Defending Real-Time Systems through Timing-Aware Designs

Tanmaya Mishra

#### (ABSTRACT)

Real-time computing systems are those that are designed to achieve computing goals by certain deadlines. Real-time computing systems are present in everything from cars to airplanes, pacemakers to industrial-control systems, and other pieces of critical infrastructure. With the increasing interconnectivity of these systems, system security issues and the constant threat of manipulation by malicious external attackers that have plagued general computing systems, now threaten the integrity and safety of real-time systems. This dissertation discusses three different defense techniques that focuses on the role that real-time scheduling theory can play to reduce runtime cost, and guarantee correctness when applying these defense strategies to real-time systems. The first work introduces a novel timing aware defense strategy for the CAN bus that utilizes TrustZone on state-of-the-art ARMv8-M microcontrollers. The second reduces the runtime cost of control-flow integrity (CFI), a popular system security defense technique, by correctly modeling when a real-time system performs I/O, and exploiting the model to schedule CFI procedures efficiently. Finally, the third studies and provides a lightweight mitigation strategy for a recently discovered vulnerability within mixed criticality real-time systems.

### Defending Real-Time Systems through Timing-Aware Designs

#### Tanmaya Mishra

#### (GENERAL AUDIENCE ABSTRACT)

Real-time computing systems are those that are designed to achieve computing goals within certain timing constraints. Real-time computing systems are present in everything from cars to airplanes, pacemakers to industrial-control systems, and other pieces of critical infrastructure. With the increasing interconnectivity of these systems, system security issues and the constant threat of manipulation by malicious external attackers that have plagued general computing systems, now threaten the integrity and safety of real-time systems. This dissertation discusses three different defense techniques that focuses on the role that real-time scheduling theory can play to reduce runtime cost, and guarantee correctness when applying these defense strategies to real-time systems.

The first work introduces a novel timing aware defense strategy for the Controller Area Network (CAN). CAN is a popular communication system that is at the heart of every modern passenger vehicle and is indispensable for the safe operation of various components such as the engine and transmission systems, and due to its simplicity, may be vulnerable to a variety of attacks. We leverage security advancements in modern processor design to provide a lightweight and predictable (in terms of time taken to perform the operation) defense technique for some of these vulnerabilities.

The second work applies a technique called Control-Flow Integrity (CFI) to real-time systems. CFI is a general-purpose defense technique to prevent attackers from modifying software execution, and applying such techniques to real-time systems, particularly those with limited hardware capabilities, may be infeasible. By applying real-time scheduling theory, we propose a strategy to apply CFI to such systems, while reducing its overhead, or cost, without compromising the security guarantees CFI inherently provides.

Finally, safety-critical systems may consist of a mix of operations, each having a different level of importance (criticality) with respect to the safe operation of the system. However, due to the complexity of modeling such systems, the models themselves may be vulnerable to attacks. Through simulations we study one such vulnerability and propose a modification to mitigate it.

# Dedication

To my grandfather who taught me how to work hard and have fun

## Acknowledgments

This work was made possible through the concerted effort and guidance from many people, over the course of many years. I would first and foremost like to thank my advisor, Dr. Thidapat Chantem. Without her guidance, criticism, encouragement and invaluable advice, over more than half a decade, all of this work would have been impossible. I will forever be indebted to her for the countless lessons, technical and otherwise, that I have learned from her.

I would also like to thank my co-advisor, Dr. Ryan Gerdes, for his (many) criticisms and guidance during my Ph.D. journey, Dr. Ning Zhang for his technical comments and advice, and Dr. Guoqiang Yu and Dr. Eli Tilevich for their advice as part of my advisory committee.

There have been many others who have helped me in this journey, maybe even too many to list here. However, some of the most influential people, in both my growth as a person and this work, have been my lab mates and colleagues. Foremost of them has been Pratham, a person to bounce ideas off, and constant friend (and roommate) over the last five and a half years. Many of the ideas presented in this work are from late night conversations in the lab or over a session of chai, with others including Gaurang and Mahsa, at the Minerva Express Indian grocery store. The daily cups of chai at this store will always remain some of my brightest memories from my Ph.D. journey. Over the years, many have left and even more have joined these sessions, including Spandan, Rajarshi and Pragya. I am thankful for their support and glad that this tradition will pass on to them as they go through their respective academic journeys.

While those at the lab have been constant sources of support, it would be a remiss on my part if I do not thank my friends from my undergraduate days. These include Gaurang, Aniket, Prathamesh, Anurag, Niharika, Raj, Karan, Omkar, Amogh, Madhura, among others. The numerous trips we have had together, over the years, have been the bright moments of respite that were sorely needed to maintain the motivation and spirit required to complete this journey. For over a decade, these people have always remained a constant in my life and I will always be grateful for them. Special thanks to Gaurang and Raj for the time spent in Seattle during the summer of 2021. That time was a great breath of fresh air. I am grateful to Madhura for her constant support, encouragement and for being a source of happiness through out the years.

Finally, I would like to thank my parents, brother, and my cousins, Ankita and Ambika, for their constant support and motivation through the years, and Anushila (and, of course, Priyanka) for being my home away from home that I could always escape to when needed.

## Contents

| Li | List of Figures xi |                                                                                |    |  |  |

|----|--------------------|--------------------------------------------------------------------------------|----|--|--|

| Li | st of              | Tables                                                                         | xv |  |  |

| 1  | Intr               | troduction                                                                     |    |  |  |

|    | 1.1                | Motivation                                                                     | 2  |  |  |

|    | 1.2                | Limitations of embedded system hardware                                        | 6  |  |  |

|    | 1.3                | Predictability of real-time systems and its usefulness for system security     | 7  |  |  |

|    | 1.4                | Reviewing advancements in real-time system theory for security vulnerabilities | 8  |  |  |

|    | 1.5                | Organization and contributions                                                 | 9  |  |  |

| 2  | Pre                | eliminaries: TEE and ARM TrustZone for Cortex-M                                |    |  |  |

|    | 2.1                | ARM TrustZone for Cortex-M                                                     | 14 |  |  |

| 3  | Util               | Utilizing trusted execution to secure CAN bus communications                   |    |  |  |

|    | 3.1                | Introduction                                                                   | 18 |  |  |

|    | 3.2                | Related Work                                                                   | 22 |  |  |

|    | 3.3                | Preliminaries                                                                  | 24 |  |  |

|    |                    | 3.3.1 Controller Area Network (CAN)                                            | 24 |  |  |

| 3.4.1<br>3.4.2<br>3.4.3                                                             | Real-Time Task Model       Threat Model                                                                                                                | 26<br>27                   |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|                                                                                     | Threat Model                                                                                                                                           | 27                         |

| 3.4.3                                                                               |                                                                                                                                                        | 41                         |

|                                                                                     | Problem Statement                                                                                                                                      | 28                         |

| Syster                                                                              | n Design and Overview                                                                                                                                  | 29                         |

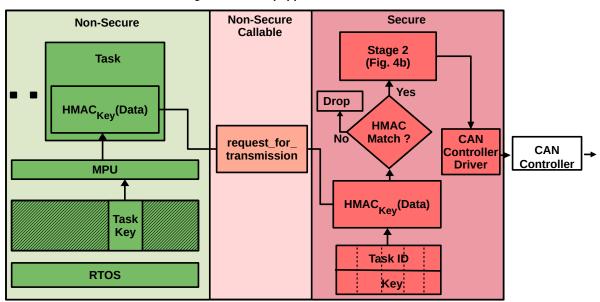

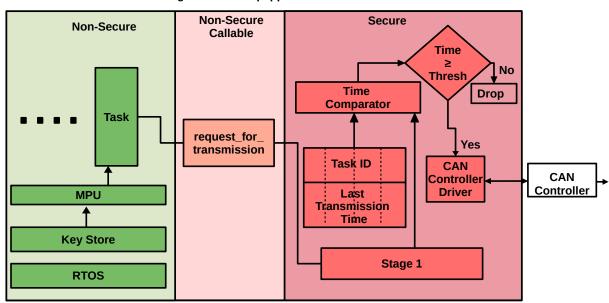

| TEEC                                                                                | Check : A TEE based CAN message checker                                                                                                                | 31                         |

| 3.6.1                                                                               | Transmission                                                                                                                                           | 32                         |

| 3.6.2                                                                               | Reception                                                                                                                                              | 38                         |

| Exper                                                                               | imentation                                                                                                                                             | 39                         |

| 3.7.1                                                                               | Experimental Setup                                                                                                                                     | 40                         |

| 3.7.2                                                                               | Results                                                                                                                                                | 41                         |

| Analy                                                                               | ses                                                                                                                                                    | 45                         |

| 3.8.1                                                                               | Real-Time Analysis                                                                                                                                     | 45                         |

| 3.8.2                                                                               | Security Analysis                                                                                                                                      | 46                         |

| Concl                                                                               | usion                                                                                                                                                  | 48                         |

| lizing                                                                              | hard real-time system predictability to implement control-flow                                                                                         | 7                          |

| 4 Utilizing hard real-time system predictability to implement control-<br>integrity |                                                                                                                                                        |                            |

| Introd                                                                              | luction                                                                                                                                                | 49                         |

| Relate                                                                              | ed Work                                                                                                                                                | 53                         |

| Prelin                                                                              | ninaries                                                                                                                                               | 55                         |

|                                                                                     | Syster<br>TEEC<br>3.6.1<br>3.6.2<br>Exper<br>3.7.1<br>3.7.2<br>Analy<br>3.8.1<br>3.8.2<br>Concl <sup>2</sup><br>lizing I<br>egrity<br>Introd<br>Relate | System Design and Overview |

|      | 4.3.1                             | Hardware model                                                       | 55 |

|------|-----------------------------------|----------------------------------------------------------------------|----|

|      | 4.3.2                             | Software Model                                                       | 56 |

|      | 4.3.3                             | Threat model                                                         | 57 |

| 4.4  | Overvi                            | ew of Procrastinating CFI                                            | 58 |

| 4.5  | Procas                            | tinating CFI Task model                                              | 59 |

|      | 4.5.1                             | Application task model                                               | 61 |

|      | 4.5.2                             | Security task model                                                  | 63 |

| 4.6  | Securit                           | y Task Deadline Relaxation                                           | 65 |

| 4.7  | Ensuri                            | ng Correctness and Schedulability                                    | 68 |

|      | 4.7.1                             | Race condition between output and security tasks                     | 68 |

|      | 4.7.2                             | Implicit data-dependency between output and security jobs $\ldots$ . | 70 |

|      | 4.7.3                             | Implications on scheduling                                           | 70 |

| 4.8  | 4.8 Procrastinating CFI mechanism |                                                                      |    |

|      | 4.8.1                             | SAU based function-block enforcement and shadow stack                | 73 |

|      | 4.8.2                             | RTOS modifications                                                   | 74 |

|      | 4.8.3                             | Design Alternatives                                                  | 75 |

|      | 4.8.4                             | Verification of Control Flow in Security Task                        | 76 |

| 4.9  | Securit                           | y analysis                                                           | 76 |

| 4.10 | Evalua                            | tion                                                                 | 78 |

|      | 4.10.1                            | Control flows in Cyber Physical System (CPS) Software                | 78 |

|   |      | 4.10.2  | Experimental setup                                                 | 79  |

|---|------|---------|--------------------------------------------------------------------|-----|

|   |      | 4.10.3  | Hardware Overhead                                                  | 79  |

|   |      | 4.10.4  | Simulation study                                                   | 81  |

|   | 4.11 | Conclu  | $\operatorname{usion}$                                             | 83  |

| 5 | Sim  | ulatior | n-based characterization and a priority degradation-based de-      |     |

|   | fens | e agaiı | nst the Mad Monk attack for mixed-criticality systems              | 84  |

|   | 5.1  | Introd  | uction                                                             | 84  |

|   | 5.2  | Relate  | d Work                                                             | 87  |

|   | 5.3  | Mixed   | Criticality Task Model                                             | 90  |

|   | 5.4  | The M   | lad Monk Attack                                                    | 92  |

|   |      | 5.4.1   | Threat Model                                                       | 93  |

|   |      | 5.4.2   | Mad Monk Attack mechanism                                          | 94  |

|   | 5.5  | Simula  | ting Mad Monk                                                      | 96  |

|   |      | 5.5.1   | Simulator setup                                                    | 96  |

|   |      | 5.5.2   | Determining basic conditions with realistic penalty                | 99  |

|   |      | 5.5.3   | Changing to harmonic periods                                       | 100 |

|   |      | 5.5.4   | Considering variations in penalty on a newly released intermediate |     |

|   |      |         | victim job                                                         | 101 |

|   |      | 5.5.5   | Converting the attacker task into a sporadic task                  | 103 |

|    |                  | 5.5.6                     | A note on dropping attacker jobs for single and multiple attacker tasks |     |

|----|------------------|---------------------------|-------------------------------------------------------------------------|-----|

|    |                  |                           | - suicide condition                                                     | 107 |

|    |                  | 5.5.7                     | Simulation summary                                                      | 109 |

|    | 5.6              | Critica                   | ality level-aware priority degradation to mitigate Mad Monk             | 110 |

|    |                  | 5.6.1                     | Response time analysis for degraded group for RM                        | 115 |

|    |                  | 5.6.2                     | Simulating effect on deadline misses for attacker tasks                 | 117 |

|    | 5.7              | Conclu                    | usion                                                                   | 117 |

| 6  | Con              | onclusion and Future Work |                                                                         |     |

|    | 6.1              | Summ                      | ary and Conclusion                                                      | 118 |

|    | 6.2              | Future                    | e Work - Vulnerability in real-time systems due to self-suspension      | 119 |

| Bi | Bibliography 121 |                           |                                                                         |     |

# List of Figures

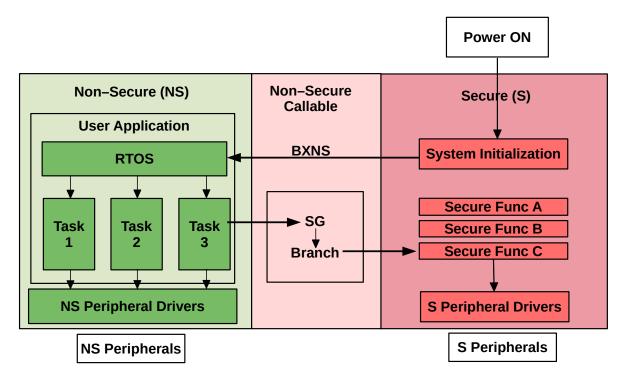

| 2.1 | ARMv8-M microcontroller power ON code flow                                                                                                                 | 14 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

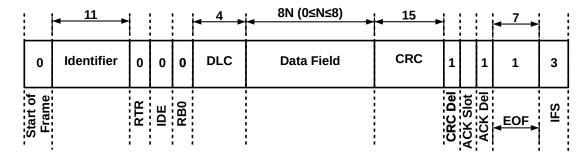

| 3.1 | CAN 2.0b standard frame format                                                                                                                             | 26 |

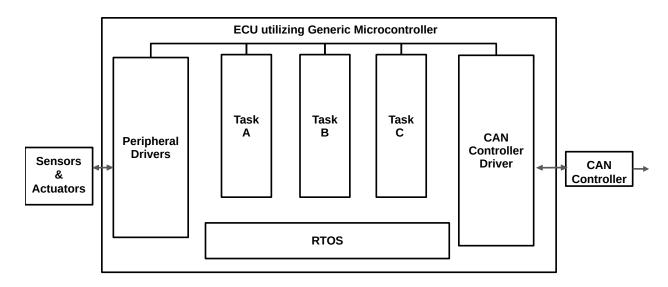

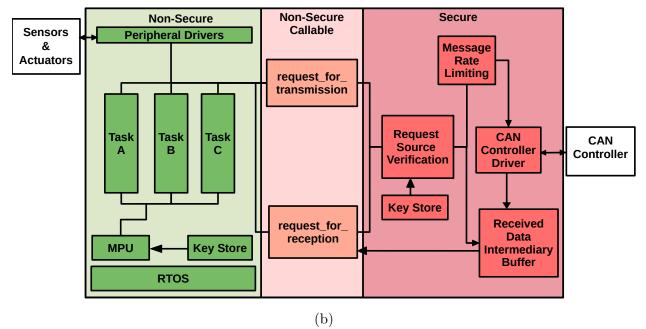

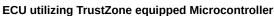

| 3.2 | (a) Regular ECU system and (b) ECU system utilized for TEECheck                                                                                            | 30 |

| 3.3 | (a) Source verification using HMAC (b) Rate limiting messages based on                                                                                     |    |

|     | per-task last transmission time                                                                                                                            | 33 |

| 3.4 | TEECheck Reception scheme                                                                                                                                  | 38 |

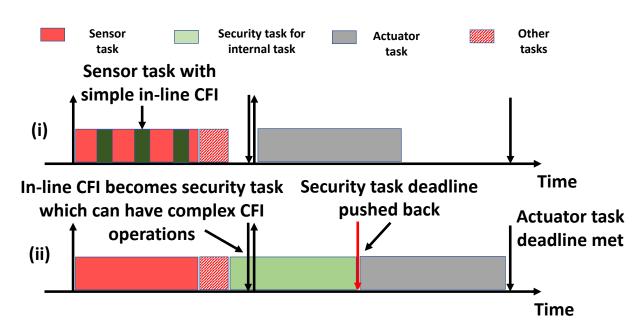

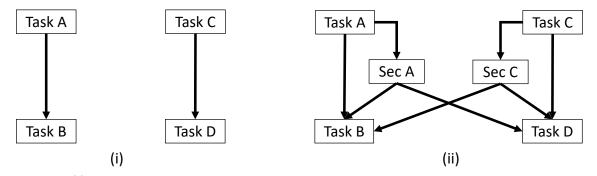

| 4.1 | (i) Task system where sensor task has simple in-line CFI, (ii) Proposed pro-<br>crastinating model where in-line CFI is bundled into a security task (Sec- |    |

|     | tion 4.5.2) which can implement complex CFI operations (accomodate greater WCET) but with pushed back deadlines to lower resource utilization              | 58 |

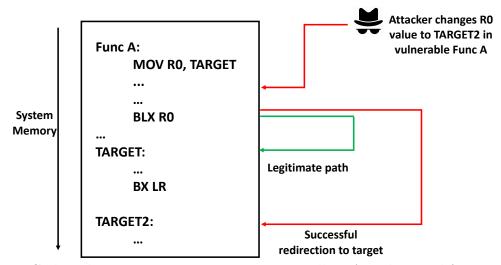

| 4.2 | Code redirection on a generic microcontroller. Attacker modifies contents of                                                                               |    |

|     | R0 to change branch target.                                                                                                                                | 60 |

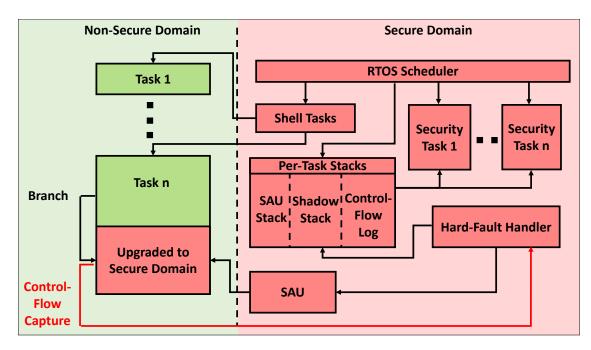

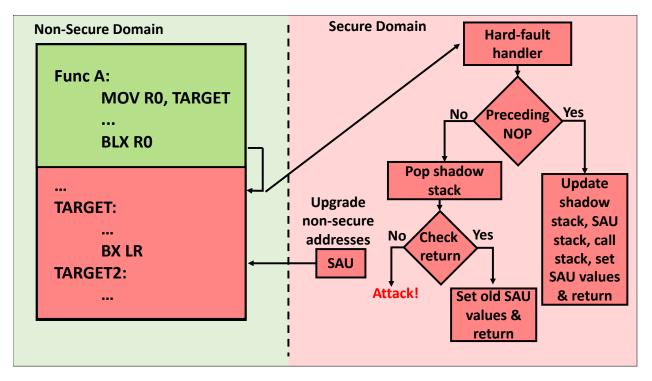

| 4.3 | Overview of Procrastinating CFI mechanism to capture forward-edge control-                                                                                 |    |

|     | flow logs (reading source and destination addresses of branch) and backward-                                                                               |    |

|     | edge verification. Branching into upgraded memory launches fault handler                                                                                   |    |

|     | that performs both operations - Section 4.8                                                                                                                | 62 |

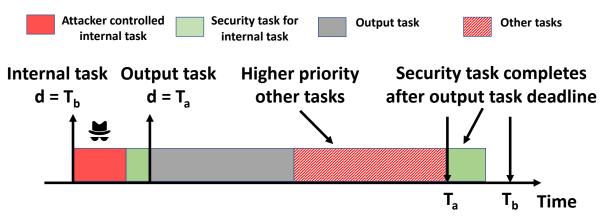

| 4.4 | Race condition: Attacker is able to execute and affect input of output task.                                                                               |    |

|     | In such a case, the output task's deadline (and output release time under                                                                                  |    |

|     | LET) is before the security task is able to complete execution                                                                                             | 67 |

| 4.5 | (i) Sample data dependency between internal tasks A and C with output tasks   |     |

|-----|-------------------------------------------------------------------------------|-----|

|     | B and D. (ii) Dependencies when security tasks are considered                 | 69  |

| 4.6 | SAU based function-call enforcement                                           | 72  |

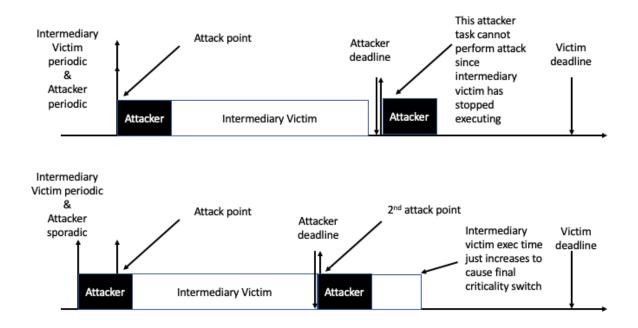

| 5.1 | Victim here is the intermediary victim job. Periodic jobs are harmonic syn-   |     |

|     | chronous. Sporadic attacker job "skips" a previous job, leading to an advan-  |     |

|     | tageous condition.                                                            | 107 |

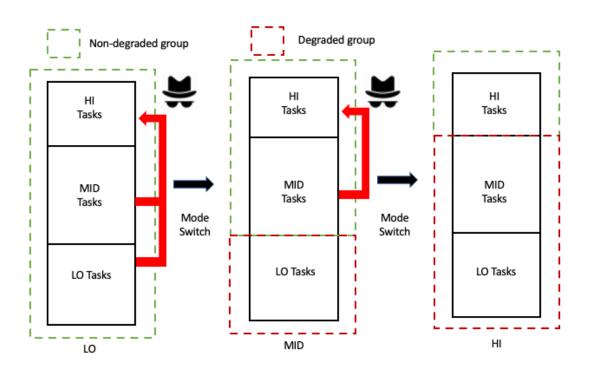

| 5.2 | Criticality based degradation strategy implemented on a 3 criticality level   |     |

|     | system. Each criticality change reduces the number of possible attackers that |     |

|     | can target a HI criticality intermediary victim task                          | 110 |

# List of Tables

| 3.1 | Single task running at highest frequency (RL - Rate Limiting, CAN - CAN controller transmission time)                                                                                                                                     | 40  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Single task running at highest frequency with reception. TEECheck call over-                                                                                                                                                              | 10  |

| 0.2 | head                                                                                                                                                                                                                                      | 42  |

| 3.3 | Transmitting different message sizes                                                                                                                                                                                                      | 44  |

| 3.4 | Automotive benchmark with increasing number of tasks with TEEC<br>heck $\ . \ .$                                                                                                                                                          | 46  |

| 4.1 | Control-flow transfers in popular real-time applications                                                                                                                                                                                  | 79  |

| 4.2 | Deadline relaxation of security tasks.                                                                                                                                                                                                    | 80  |

| 4.3 | Percentage of tasksets (/10,000) that are only schedulable under EDF+SRP<br>when push backs are accounted. Original task set utilization does not include<br>security tasks. WCET Ratio is ratio of WCET of security tasks to application |     |

|     | task                                                                                                                                                                                                                                      | 82  |

| 5.1 | Simulation where average execution time is 60% of worst-case for given crit-<br>icality level. Success % is the number of task sets (out of 100) that show<br>successful attack                                                           | 98  |

| 5.2 | Simulation where average execution time is 80% of worst-case for given crit-<br>icality level. Success % is the number of task sets (out of 100) that show<br>successful attack.                                                          | 100 |

5.3Changing to harmonic periods immediately increases the attack success ratio by 3 times. Success % is the number of task sets (out of 100) that show successful attack. 101 Success percentages when attacker cannot induce penalty on newly released 5.4 intermediary victim jobs. Success % is the number of task sets (out of 100) that show successful attack. 102Attacker can induce up to 10% of the penalty on the newly released interme-5.5diary victim job, that it can otherwise induce on a preempted job. Success %is the number of task sets (out of 100) that show successful attack. 103Attacker can induce up to 70% of the penalty on the newly released interme-5.6diary victim job, that it can otherwise induce on a preempted job. Success %is the number of task sets (out of 100) that show successful attack. 1045.7Comparing success rate of periodic and sporadic attacker for different number of tasks in task set. Success % is the number of task sets (out of 100) that show successful attack. Earliest Successful Attack % is where a task set shows strictly earlier successful attack occurrence under the specific type of attacker. 105 Success % where only the sporadic task was able to achieve successful attack 5.81065.9Simulating criticality aware priority degradation on LO criticality attacker all other tasks MID or HI criticality. Deadline Miss % is the number of task sets 116

## Chapter 1

## Introduction

Real-time computing systems are those that must maintain logical correctness while providing temporal guarantees. Specifically, these systems define a relation between when the system is provided an input and by when it must genenerate an output. The effect or consequence of violating this definition varies. For *soft* real-time systems the consequence of violating this pre-defined relation, also called *deadlines*, may simply degrade the quality of service (QoS) for the system user. An example of such a system is when a user streams a video from a remote server (such as YouTube or Netflix). If the user computer is unable to handle decrypting and rendering the video stream on screen in a timely manner, or if the network is overloaded, the user may have to wait time for the video to render and/or download and see frequent stutters while viewing the video stream. On the other hand, in the case of hard real-time systems, violating deadlines during system runtime could lead to catastrophic system failure and the consequences could include loss of human life. For example, the airbag in modern passenger vehicles must deploy within strict time bounds or else it would be too late to prevent injury to the occupants in the vehicle, rendering the airbag deployment system ineffective. Therefore, such systems have hard deadlines which must not be violated. While traditionally such computing systems have been isolated and work autonomously, due to the rise of system interconnectivity, such systems are becoming increasingly vulnerable to malicious external influence. This dissertation specifically looks at the increasingly relevant problem of security vulnerabilities in modern embedded

real-time system design and aims to motivate the larger real-time systems research community to consider security objectives and vulnerabilities alongside traditional real-time system guarantees. This dissertation shows that even in computationally limited systems, there is a possibility to include defenses against external attacks by judiciously utilizing real-time system concepts and techniques. Further, this dissertation showcases that, due to the predictability that is inherent in real-time systems, modern real-time system models need to be rethought and updated to mitigate vulnerabilities that they may inadvertently introduce, due to their design.

### 1.1 Motivation

This work is based on two pillars: real-time system scheduling theory and mechanisms, and system security. An interesting observation of *all* real-time systems is the *inherent predictability* of these systems which cannot be said of an arbitrary computing system. Since real-time systems have deadlines which are known apriori to deployment, it is but evident that such systems will perform useful work, that can be accurately measured, within these deadlines. Therefore, such a system's state can be accurately judged at any given time instant. This leads to an interesting relationship between temporal guarantees and security when such systems are judged by existing research and literature in the system security domain. However, before we discuss this relationship, the reader may question as to why is it necessary to consider the security of real-time systems in the first place? Why is this a relevant problem in the current state-of-the-art?

Consider, for instance, a vehicle from around 40 years ago. These were relatively simple machines and would have an internal combustion engine, a simple manual transmission, hydraulic brakes, and maybe a microprocessor-based fuel injection system [78] for improving

#### 1.1. MOTIVATION

engine fuel efficiency and engine output. Therefore, the computing systems within such vehicles were simple and robust to ensure occupant safety, and, more importantly, completely isolated from other computing systems. In fact, at that time, the internet was still being used primarily by scientific and military organizations for specialized work. With the proliferation of communication technologies over the last 3 decades and its application to computing environments ranging from massive data-centers to the personal smartphone, coupled with an ever increasing data bandwidth and transfer speeds, it is but natural that some of these technologies would trickle into critical systems such as vehicles. Modern vehicles are now far more complex machines. While the mechanics of the internal combustion engine may not have made major progress over the years, highly sophisticated add-on systems such as hybrid/electric drivetrains and advanced driver assistance systems (ADAS) have become increasingly popular in modern vehicles. ADAS mechanisms such as traction control, adaptive cruise control, automatic pedestrian-detection etc., utilize data captured by a vast array of sensors, computed in over a 100 distributed computing systems, also called electronic control units (ECU) spread throughout the vehicle that constantly communicate over intra-vehicular networks such as controller area network(CAN) [49]. Since the safety of the occupants as well as that of pedestrians on the road is dependent on the correct and timely operations of such systems, such ADAS systems have hard real-time requirements [25] to ensure occupant safety.

More recently, vehicles have been slowly opened up to external connections too. For example, in the last decade, it has become increasingly common to have wireless connectivity options such as Bluetooth, WiFi and cellular connectivity integrated into the vehicle's infotainment system for passenger convenience as well as for remote over-the-air (OTA) updates to vehicle software. In fact, manufacturers such as Tesla are capable of fine-tuning core vehicle performance such as top speed and efficiency via such OTA updates. While this has obvious advantages for those that are able to purchase such vehicles, the ability to perform such modifications to core vehicular functionality have already been successfully exploited. For example, researchers [85] were successfully able to send out malicious messages on a Tesla's CAN bus via a malicious OTA payload to perform potentially dangerous operations, such as disabling the vehicle's power steering and braking. While Tesla later sent out an OTA software patch after being notified, it can be argued that such attacks are only going to get more sophisticated with the passage of time.

Unfortunately, security vulnerabilities plague real-time systems in other domains too. For example, Iran's nuclear reactor program was severely undermined by the Stuxnet [48] computer worm which was able to modify plant operations. In fact, Stuxnet showcases an even more disturbing problem. Stuxnet was able to spread and maliciously take control even though the plant control computers were *air-gapped*. That is, they were physically isolated from external computing systems just like traditional real-time systems. However, the human operators were able to load the worm into the controllers by plugging in infected storage drives. Infected Stuxnet controllers could have caused catastrophic plant failure, and resulted in possibly Chernobyl-like consequences to human and animal life. Further, since these systems run legacy software which are rarely, if ever, updated since they control critical equipment, the possibility of such software having unpatched vulnerabilities is higher. As the sophistication of such attacks increase, legacy and connected modern real-time systems alike will become more vulnerable.

Therefore, there is an outstanding need to build security mechanisms into real-time systems. While taking reactionary measures, such as that performed by Tesla, to safeguard such systems is a possibility, it entirely depends on the benevolence of the attacker to inform real-time system vendors about such security vulnerabilities. However, Stuxnet shows that attackers exist who would try to exploit such systems for a myriad of reasons, from to economic to political, regardless of the consequences of such actions, and would only be detected by either forensic analysis of such systems or when the attack is executed in its entirety. The former, however inconvenient, is still more desirable to the latter which could have disastrous consequences.

To summarize this discussion, and determine the various facets this dissertation must consider in the domain of securing real-time systems, we can circle back to the example of a modern connected vehicle. The salient points are:

- 1. ECUs within modern connected vehicles have limited computational resources to manage size, weight and power consumption (SWaP) while also balancing the bill of materials (BoM) of the final product. Designing a system security solution must explicitly consider hardware constraints, especially in an embedded system scenario.

- 2. ECUs (and many other real-time systems that are deployed in critical environments) are increasingly vulnerable to advancements in system security attacks. Introducing general-purpose system security defenses in such hardware constrained systems may lead to insurmountable overheads, which may lead to system designers completely abandoning the use of any such security solution. Existing general-purpose designs must be judiciously modified to fit the specific needs of real-time systems to convince system designers to introduce these security solutions in real-time systems. In fact, it could be advantageous to utilize some of the assumptions of real-time systems to reduce the cost of existing security solutions.

- 3. Advancements in real-time systems research may inadvertently introduce more vulnerabilities. It is imperative, due to the increasing interconnectivity of modern real-time systems such as in the context of modern vehicles, to critically view recently introduced real-time systems models and determine if they allow malicious external manipulation,

and fix these problems as they arise.

We shall now discuss each of these salient points, and then conclude the introductory material with the specific contributions of this dissertation.

### 1.2 Limitations of embedded system hardware

While it is clear from current state of cyber-physical system security that there is a need to harden real-time systems to reduce the possibility of malicious manipulations, the type of hardware that is used in such systems must be explicitly considered.

Unlike desktop or server-grade computing environments that one usually encounters in domains such as cloud computing, high-performance computing, etc., many real-time systems utilize less complex hardware. For example, the ECUs used within vehicles typically use CPUs that share more similarities with microcontrollers with integrated RAM, Flash and typically run at much lower clock speeds of a few 100 MHz [72] as compared to state-of-theart CPUs which easily execute at least a magnitude higher clock speeds. This is done to consider size-weight-and-power (SWaP) constraints, especially for systems that are deployed in remote or inaccessible locations where dependability and power consumption are more important requirements than raw performance. In fact, the recently launched Perseverance rover for Mars exploration uses a radiation-hardened IBM RAD750 processor [21] which itself is 2 decades old and based on a processor design from the late 1990's. The performance of such systems that run critical real-time software is a far cry from what is available in modern processors. Further, many microcontrollers have much simpler architecture and lack modern features such as complex memory management units. Such systems also use simple operating systems called real-time operating systems (RTOS) such as FreeRTOS [11] that are built to be highly predictable and provide a small hardware-abstraction layer (HAL) to simplify application development while introducing the least possible additional software components.

Therefore, where appropriate, this dissertation strictly considers embedded systems which utilize low-performance microcontrollers for processing environments. Any technique presented, that specifically requires certain hardware capabilities, assumes that the technique will be deployed on modern variants of common low-performance microcontrollers that are currently available off-the-shelf. Such hardware introduce their own set of limitations which must be carefully considered while designing the real-time system software. It is assumed that the software running on such systems is either written to be bare-metal or, more commonly, divided into individual *tasks* that are scheduled via the RTOS.

# 1.3 Predictability of real-time systems and its usefulness for system security

As stated before, real-time systems are highly predictable. While this is necessary for correct and safe system operation, it makes it that much easier for attackers to exploit such systems. For example, real-time systems allow for timing inference attacks [36] where task timing characteristics are used to leak information regarding task behavior during runtime. In fact, a novel attack method has been developed for a modern real-time task model that depends on expected system behavior due to the model's design, and, within this thesis, a countermeasure is proposed to mitigate this vulnerability.

On the other hand, the very same predictability can be used to inform defense mechanisms to make them more performant and/or reduce their cost on the entire system. Since system behavior is predictable, for example, it is known apriori the number of messages sent out on the CAN bus by an ECU task in a modern vehicle, it is possible to inform defense mechanisms to consider typical system behavior to both a) harden the system against attacks, and b) lighten the load on the underlying hardware. In fact, it is even possible to perform increased security countermeasures on the same hardware while maintaining deadlines by exploiting the predictability of the system. However, care must be taken when exploiting predictability to reduce the cost of security countermeasures. Any assumption of predictability must be built upon the careful consideration of how the system would operate if the predictability assumption does not hold true due to malicious interference or if, within the scope of the attack, if the assumptions cannot be violated by the attacker.

Note that, in the theme of this dissertation, any designs and ideas for improving the integration of general-purpose system security defenses in real-time systems must consider the limitations of the underlying embedded hardware. Judiciously exploiting any architectural advantages afforded by modern variants of such types of hardware, alongside integrating traditional real-time system concepts, may help to make the final design tenable for typical embedded real-time systems.

# 1.4 Reviewing advancements in real-time system theory for security vulnerabilities

While the previous two sections deal with how modern embedded hardware constrains the ability of system designers to integrate system security solutions, and how existing real-time theory and techniques may counterbalance these constraints, it would be remiss to not discuss whether the advancements in real-time system theory introduce new system vulnerabilities. Traditionally, real-time systems research involves modelling such systems to improve resource utilization and efficiency, while strictly maintaining safety and predictability. However, due to the increasing interconnectivity of modern real-time systems, it is not feasible anymore to build these systems without considering malicious interference. There is currently a nascent trend in this domain of research that specifically looks at vulnerabilities within state-of-theart real-time task models. These vulnerabilities do not lie within system *implementations* but instead lie within the *modelling* of expected system behavior. It could be argued that such flaws are more dangerous than any single implementation flaw, since any correctly implemented systems, that closely match such flawed models, are automatically vulnerable. Therefore, it is imperative to look at prior work that aims to break the assumptions un-

derlying real-time system models, and/or utilizes the assumptions in these models to force the system to behave in an unintended manner. Such vulnerabilities must then be carefully addressed by fixing the assumptions within the model. This dissertation looks at one such vulnerability that has been discovered by prior work, and proposes a revised model to address this issue.

## 1.5 Organization and contributions

An overview of the rest of this dissertation is now presented. As discussed above, it is clear that there exists an avenue to apply the predictability of real-time systems to general system security concepts and that real-time system modeling may be flawed and open to attacker manipulation. Additionally, where applicable, the proposed defenses must recognize the constraints of the hardware on which it must operate.

Therefore, this dissertation is organized in a progressive manner. It starts by introducing a technique that is designed to co-depend on the underlying hardware architecture, and timing constraints of the system, to aid the defense mechanism. The second work reduces the cost (and improve the capabilities) of a well-known system security defense mechanism by carefully utilizing real-time modeling techniques. Here, certain underlying hardware capabilities are assumed only to provide an example implementation of a defense mechanism. Finally, the dissertation discusses a modification to a set of recently introduced real-time task models to harden them against a vulnerability discovered, by prior work, within these models. This is done by completely eschewing the requirement for specific hardware requirements, and by integrating the defense into the model's design itself.

The techniques are summarized here for the reader:

• Chapter 3 - This chapter focuses on utilizing modern embedded architecture to design a defense mechanism against a set of general security vulnerabilities, while being mindful of the system's timing requirements. Specifically, the CAN bus in vehicles is considered. Modern embedded hardware architectures, allow strong isolation between execution contexts through the introduction of architecture extensions such as ARM's TrustZone [12]. Such advancements are now available in the lowest powered micocontrollers and are built to introduce very low overheads and very *predictable* into system operation. The work presented in this chapter considers the temporal tightness of a typical hard real-time workload which would be found in a vehicle ECU. The work presented aims to showcase that it is possible to design defenses, even on low-end hardware, that defends against masquerade and denial-of-service attacks as well as prevents information leakage. The chapter presents experimental proof on real hardware that shows that such a technique can benefit ECU software without requiring large modifications to the original code base and does not introduce enough overhead to violate the temporal guarantees of pre-existing code.

#### **1.5. Organization and contributions**

- Chapter 4 While the previous chapter essentially presents a system design perspective to solve the hard real-time system security vulnerabilities utilizing predictability in hardware operation. This chapter, on the other hand, delves into a specific attack, collectively called *control-flow attacks* that are used to manipulate a computing system to perform attacker-controlled arbitrary computations, with a minimal set of requirements. While control-flow attacks and their defense mechanisms have been studied for over a decade, prior literature either does not validate the applicability of presented techniques to hard real-time systems, or does not consider the unique limitations of resource-constrained hardware commonly found in hard real-time systems. This chapter presents a novel approach to that utilizes real-time theory and, especially, assumptions regarding when a system receives input and by when it generates output. Such assumptions are made possible due to the *predictability* of the operation of the system, making it possible to temporally *spread* load by delaying control-flow transfer checks. This allows for not only improved utilization of system resources (that are already scarce in systems utilizing resource-constrained embedded hardware), but also opens an opportunity to integrate more complex defenses that are currently only available for systems with more capable hardware. Care is taken to ensure that the design does not violate the *correctness* of the defense mechanism and does not inadvertently introduce additional blindspots that could be exploited by an attacker.

- Chapter 5 This chapter delves into studying and defending against the recently proposed Mad Monk attack for mixed criticality systems. Mixed criticality task models have been proposed over the last decade to improve resource utilization in safety critical systems. Mixed criticality task models allow the system designer to explicitly configure the hierarchy of tasks by their *importance* to the safe and correct execution of the system. Importance, or *criticality*, of a task is a concept that may be orthogonal to

the traditional concept of *priority* in real-time systems since the priority of tasks may be determined with respect to other temporal parameters (such as deadline or frequency) depending on the scheduling algorithm, and may have no relation to how critical the task is to system operation. In mixed criticality systems, system criticality changes if a high criticality task requires greater execution time (suggesting non-average behavior), allowing the scheduler to assign greater execution budgets to higher criticality tasks while degrading lower criticality tasks. This re-shuffling of execution budgets allows the system to not only efficiently utilize system resources when system operates in the average condition, but also quickly re-prioritize system resources when the system enters non-average operating conditions. Mad Monk exploits this expected system behavior and can cause degradation of higher criticality tasks via a lower criticality task. In this chapter, by studying the conditions under which this attack can take place through extensive simulations, a new defense is proposed by modifying the degradation strategy.

## Chapter 2

# Preliminaries: TEE and ARM TrustZone for Cortex-M

Trusted Execution Environments (TEEs) are trusted execution context within an untrusted execution environment. TEEs are widely used for Digitial Rights Management (DRM) of copyrighted audio and video content in modern smartphones. For example, Google's Widevine DRM [107] is a popular framework that depends on the existence of a TEE to provide highest Quality-of-Service (QoS). For instance, streaming services could refuse to provide the highest quality of audio/video data if they do not detect a TEE or detect a compromised TEE. To ensure the integrity of TEEs and their constituent software, also called Trusted Applications (TA), there needs to mechanism to separate and enforce untrusted and trusted software components. TEEs are built to address a powerful threat model, i.e., an attacker that can take control over not only the application software but more privileged components such as the operating system itself. Therefore, TEEs must be supported by hardware extensions which constrain the attacker to the untrusted memory and execution space, and safely switch between untrusted and trusted spaces with manageable overheads. One such hardware mechanism is ARM's TrustZone.

Figure 2.1: ARMv8-M microcontroller power ON code flow

### 2.1 ARM TrustZone for Cortex-M

ARM TrustZone for Cortex-M [109] (based on ARMv8-M architecture) is a variant of the TrustZone technology first introduced in ARM's Cortex-A processors. ARM TrustZone is a set of processor architecture extensions which allow creating TEEs via software. It divides the processor execution into two domains, **secure** and **non-secure**. Code running in the secure domain has access to information from both domains while code running in the non-secure domain has access to information only from the non-secure domain. While TrustZone for Cortex-A is complex and has significant overheads [84], TrustZone for Cortex-M is designed to be very lightweight. To reduce the overhead for a low-powered microcontroller to switch between the two states, TrustZone for ARMv8-M utilizes a near static memory-mapped mechanism for delineating the domains. The TrustZone divides the memory space such that certain addresses are made available only to the secure domain. This is facilitated through

#### 2.1. ARM TRUSTZONE FOR CORTEX-M

a hard-wired controller logic called the implementation defined attribution unit (IDAU). The IDAU creates a striated memory partitioning scheme such that it is easy to identify to which domain an address belongs. Specifically, if the 29th bit of the memory address is 0, it is a secure domain address. Additionally, certain sections of the non-secure domain can be upgraded to the secure domain through software using the security attribution unit (SAU). Depending on the implementation, peripherals are memory-mapped into both secure and/or non-secure memory locations. The non-secure peripheral locations are enabled via a peripheral access controller (PAC) or security control unit (SCU). The SAU, PAC, and SCU are themselves mapped to secure locations by the IDAU, making it impossible for non-secure code to access or modify them, unless TrustZone is broken.

The secure code memory location is further divided into secure (S) and non-secure Callable (NSC) locations. While the former cannot be accessed by any code running in the non-secure domain (or it would cause the system to generate a hard fault likely requiring human intervention), the NSC locations provide an intermediary jump point where the secure gateway (SG) instruction is kept which switches the processor mode to secure when executed. All calls into the secure side have the interface function defined in the NSC. From an execution point of view, both domains have a *Thread* and *Handler* mode for regular and interrupt code executions, respectively. If an interrupt is generated from the non-secure side and the secure code is currently executing, all information is pushed to the secure stack and registers are cleared before the switch to the non-secure interrupt handler. The same set of steps happen when the situation is reversed. Based on our experiments (Section 3.7), the fact that both domains have the same execution flow and capabilities in ARMv8-M allows for consistently low interrupt latency regardless of the domain from which the interrupt originates (4 us overhead for switching in our case).

Figure 2.1 shows the flow of code execution once an ARMv8-M controller is powered on.

Code execution for ARMv8-M processors begins in the secure domain, which then branches into the non-secure domain. The bulk of the application code is written to run in the nonsecure domain, including a real-time operating system (RTOS), task code and peripheral drivers in our case<sup>1</sup>. When required, the application task code makes calls to the secure code via the intermediary functions present in the NSC.

It should be noted that the secure and non-secure domains are orthogonal to the regular processor privilege levels. Within each domain, the processor still executes under the traditional privilege model, where interrupts and the RTOS may run in privileged processor execution mode while task code may run under unprivileged processor execution mode. Further, there may be a shared or separate memory protection unit (MPU) for the secure and non-secure domains. An MPU is accessible from the privileged execution mode and enforces fine-grained access rights to certain memory locations for privileged and unprivileged code. Privileged code can access memory locations not specified in the MPU table, while access from unprivileged code would generate a fault. It must be noted the SAU has a very similar operation to that of the traditional microcontroller MPU but they are separate entities that can work together. Specifically, the SAU is used to augment the partitioning of the memory space into secure and non-secure domains over and above the fixed partitioning scheme provided by the IDAU while the MPU works within this partitioned memory space to provide different access right to different pieces of code. For example, an RTOS can load task-specific access rights before context switching to a task. This is possible because the SAU supports multiple regions depending on the implementation. Each region is a set of registers where secure domain code can programmatically upgrade a non-secure domain address space to secure domain. Switching between the domains has low overhead which is shown by the results in

<sup>&</sup>lt;sup>1</sup>While it is possible to run all the code inside the secure domain (within space limitations), it is notoriously difficult to produce bug-free code on a larger scale [96]. An attacker with knowledge of vulnerabilities in the secure code could compromise the entire system since the secure code has access to the entire memory space.

Chapter 3. Non-secure domain code cannot read/write contents of secure domain memory and can call only specially marked *non-secure callable* (NSC) secure domain code. Any other cross-domain memory access from the non-secure domain causes a high priority hard-fault. It should be noted that, traditionally, the hard-fault on ARM processors was utilized to handle critical system exceptions. As part of the ARMv8-M *mainline* architecture (implemented in the Cortex-M33 architecture), an illegal cross-domain memory access (TrustZone violation) is handled by a dedicated SecureFault exception handler. However, we aim to target even the ARMv8-M *baseline* architecture (implemented in the lower-powered Cortex-M23 variant) that bundles a TrustZone violation into a hard-fault, and calls the HardFault exception handler, to save on manufacturing costs. Throughout the rest of this thesis, we refer to either of the fault exceptions as a hard-fault exception for simplicity.

Our solution in Chapter 3 uses a combination of the MPU and careful partitioning of resources using the TrustZone. We utilize the SAU and the hard-fault for the procrastinating CFI defense mechanism in Chapter 4.

## Chapter 3

# Utilizing trusted execution to secure CAN bus communications

## 3.1 Introduction

Today's vehicles are complex machines. While they still have the same basic design of the internal combustion engine and transmission as vehicles from decades ago, they now have sophisticated, highly automated features such as advanced fuel injection systems, hybrid drivetrains, traction control, adaptive cruise control, and automatic lane-keeping, all of which are supported by sensor data and processing units. In addition, vehicles have become even more like regular computing systems, with (1) remote software updates that improve performance, or (2) having a certain degree of autonomy, allowing it to drive itself for short distances. To support these functionalities, vehicles must now generate, process and act upon a large amount of information to make driving safer, more comfortable, and more efficient.

Vehicular control systems are distributed throughout the vehicle, with some located physically close to the sensors and actuators with which they interact. While there have been proposals to consolidate the various components into a centralized system [10, 104] that controls every aspect of the vehicle, most vehicles still utilize separate electronic control units (ECUs) that are dedicated to specific functions. Modern vehicles have upwards of 100 different ECUs and this number is constantly increasing as vehicle manufacturers add func-

#### **3.1.** INTRODUCTION

tionality. While one ECU may control the engine, others may control the vehicle entertainment system, dashboard information, brakes, fuel system, etc. Advanced driver assistance mechanisms act upon information, in real-time, from many of these ECUs simultaneously. For example, certain luxury modern vehicles have crosswind stabilization which adjusts the vehicle braking characteristics under strong crosswinds. To do so, information from sensors measuring wind speed, steering position and characteristics (steering column ECU), and vehicle speed (engine control unit), among others, is processed in real-time to provide safe braking assistance.

To achieve timely sharing of vehicle runtime information between ECUs while reducing the size, weight, and power constraints (SWaP) and manufacturing cost, modern cars utilize a shared bus system for inter-ECU communications. In this chapter, we consider the CAN bus, an industry standard protocol for intra-vehicular networks. There is a large body of work in both academia and industry, along with the millions of cars that utilize it, which show that CAN is an efficient and robust communication network. While the older CAN protocol may not be sufficient for the autonomous vehicles of the near future, a newer variant (CAN-FD [60]) has been designed to increase the longevity of the protocol. However, with the increasing amount of data being shared over the bus, it becomes critical to develop techniques to not only maintain bandwidth availability but also the real-time nature of message transmission.

In addition to efficiency and timeliness, security has become an important consideration. As vehicles increasingly make decisions autonomously to ensure passenger comfort and safety, it becomes imperative that their operations are not disrupted. Due to the critical role of the CAN bus in facilitating and maintaining safe and reliable vehicle operation, CAN may draw heavy interest from malicious actors who wish to take control of a vehicle or change operational characteristics to make it unsafe for its riders. In fact, prior work [35, 69] has already shown various attacks that can take place on a vehicle, allowing malicious parties to perform actions such as applying brakes and causing a crash. For instance, newer vehicles have additional communication interfaces such as WiFi, Bluetooth and cellular connectivity to connect to external servers for software updates or for passenger convenience. These are usually provided by ECUs that are often directly connected to the vehicle's CAN bus. Such external interfaces may be vulnerable to exploitation and become a gateway to access the vehicle. For example, it has been shown that the Bluetooth stack in the car infotainment unit has vulnerabilities that when exploited, allow attackers to run arbitrary code on an ECU [35]. The attacker could then use this compromised ECU to perform masquerade attacks [19] where the attacker poses as a legitimate entity and sends out spoofed messages that could affect and/or control critical parts of the vehicle, e.g., sending messages to cut off fuel supply to the engine, or launch denial-of-service (DoS) attacks by flooding the bus with garbage messages. This is possible since CAN is a broadcast bus without message authentication. If such attacks are carried out in real-world scenarios, such as in high-speed traffic, it could have catastrophic consequences.

To maintain predictable and timely operation on the CAN bus, we believe that the best form of defense would be at the source itself. That is, an attacker that *fails to utilize* the bus is less effective than one which is given access to the bus and may have the ability to disrupt message transmissions. this chapter builds upon this core idea and proposes a lightweight technique to secure the CAN bus from attacks such that the compromised ECU cannot engage the bus more than the original (uncompromised) ECU.

To do so, we propose that ECUs utilize trusted execution environment (TEE)-capable processors which allow code compartmentalization, making it possible to verify CAN message source and destination within an ECU itself instead of at the receiver ECU. TEEs are isolated execution environments designed to run trusted software and are supported by processor ar-

#### **3.1.** INTRODUCTION

chitecture extensions which include strict access control policies to processor components, peripherals, data, and address buses. TEE implementations such as Intel SGX [40] and ARM TrustZone [12] can currently be found in commercially available hardware and have been used in a variety of security-critical applications, such as Samsung Pay [13]. In addition, TEE is a known entity, as there exists a large body of work [92] which studies the security benefits and pitfalls of TEEs. Although our approach requires changes to the critical hardware components inside a vehicle, we believe it to be an especially effective one, both in terms of performance and security. In fact, our approach incurs *no* increase in CAN bus bandwidth consumption and we observe substantial performance improvements over currently available approaches while running on much slower (12 MHz clock instead of 100+ MHz clock for typical ECUs) hardware. The shift towards using CAN-FD over CAN in recent vehicles [1] shows that the automotive industry is willing to utilize newer technologies when significant advantages are demonstrated. This chapter has the following major contributions:

- 1. We propose a TEE-based ECU system architecture to separate message generation and consumption from CAN transmission and reception.

- 2. Based on our new system architecture, we present **TEECheck**, an intermediary CAN bus interface which achieves efficient and trustworthy vetting of message origin and frequency before message transmission, and of request origin before received message data is disbursed. In particular, TEECheck:

- (a) Detects and prevents an attacker from *masquerading* as another legitimate message source such as other tasks on the same *or* different ECU.

- (b) Provides a *proactive* and *on-ECU* mechanism to mitigate DoS attacks on the CAN bus. Our technique is the first to utilize TEE to contain the aforementioned attacks to the compromised ECU and does *not* require a receiver ECU to validate

whether a message is from a legitimate party.

- (c) Provides an *on-device* mechanism to prevent an attacker from *any* access to messages not intended for it, i.e., prevents snooping. To the best of our knowledge, there are no other techniques designed for the CAN bus that prevents the attacker from accessing the CAN message frames meant for other endpoints.

- 3. We experimentally show that the overhead associated with our approach, which is incurred *only* when a task requires access to the CAN bus, is fairly negligible and quite predictable, making our approach suitable for resource-constrained devices running real-time applications. Specifically, the overhead typically takes 477 us from message generation to message transmission, and 480 us for message data reception, on a 12 MHz processor which would translate to 50 µs on a 100+ MHz processor.

While we consider CAN 2.0 as our target application in this chapter, our mechanism can be easily adapted to any broadcast communication mechanism, such as I2C or SPI, with minimal changes. In terms of TEE implementation, we selected the ARM TrustZone for Cortex-M (ARMv8-M architecture with Security Extensions) [109] which, although fairly recently introduced, has a number of commercial-off-the-shelf microcontroller implementations available that can be used in modern ECUs today as drop-in replacements.

We shall now look at relevant prior work.

## 3.2 Related Work

CAN bus security has become an important research area in the past several years. Considering the safety-critical nature of the systems where CAN is utilized, e.g., automobiles, this is not surprising. CAN bus hardening approaches are spread across the communication stack layers. At the physical layer, intrusion detection systems (IDS), have been introduced. These schemes are variants of clock-skew and voltage-based fingerprinting which help to detect and, in some cases, identify attacker ECUs. While such techniques can detect an attacker within a few frames [38, 39, 108] or single frame [50], they still, in general, require a specialized monitoring node for detection and are *reactive* in nature. That is, they only detect when the attacker has managed to engage the bus.

Network-level authentication techniques for CAN bus have also been widely studied. LeiA [91] and vatiCAN [87] are AUTOSAR [51] compliant authentication schemes which utilize some form of MAC based authentication at the receiver end. To compensate for the increased overhead, others such as CANAuth [102] and LiBrA-CAN [54] are based on variants of CAN+ [114], a backward-compatible variant of CAN capable of higher data rates, or CAN-FD-Sec [34] based on the CAN-FD [60]. Unlike CAN+, CAN-FD is expected to be the next-generation replacement for CAN 2.0. All these works require receiver-end authentication, which incurs unnecessary bus overhead since illegitimate messages must still be transmitted before they can be authenticated.

In addition, these work cannot prevent DoS attacks since receiver-end authentication cannot stop a transmitter from sending out a message. In contrast, we limit the frequency of message transmission of the compromised ECU. Further, we aim to be CAN variant agnostic. Our other goal is to propose a lightweight hardware based approach which requires minimal changes to the ECU software. In contrast, Berg et al. [20] considers separating the infotainment system from the rest of the vehicle by implementing secure gateways, which requires significant software addition and can incur large time overhead.

The concept of trust has been used to fortify CAN bus communication in prior work. Ve-Cure [106] uses the concept of trust groups where ECUs handling critical operations are kept in the higher trust group, authenticating each other using a MAC based scheme. The work by Gui et al. work [58] is more similar to ours in that it utilizes hardware trusted platform module (TPM) for establishing a root of trust. Perhaps the closest work, in spirit, to ours is VulCAN [100] where the authors utilize trusted execution. Their technique builds upon LeiA and vatiCAN by utilizing a trusted computing base (TCB, in their case, Sancus [86]) inside which they generate their MACs. VulCAN takes much longer, i.e, around 2ms for the entire authentication sequence. In addition, addressing DoS attacks are outside the scope of all of these techniques since they depend on the receiver for attack detection.

We shall now discuss some preliminary information regarding CAN bus before we begin discussion regarding the System Model.

## 3.3 Preliminaries

We now provide an overview of the underlying technologies of our system. Specifically, we consider the ARM TrustZone for ARMv8-M (Section 2.1) based microcontrollers and the CAN protocol. Due to the page limit, we only provide the details that are relevant to our work. For more details, readers are referred to existing publications [49, 109].

#### 3.3.1 Controller Area Network (CAN)

CAN is a protocol originally designed for communication between different vehicle components but has been applied to other areas such as industrial automation. It is a serial communication protocol designed to broadcast small messages over a shared bus. CAN uses a multi-master communication paradigm where nodes compete, on a per-message basis, to send messages on the bus and it is up to each node to accept or ignore the messages.

Currently, vehicles utilize the CAN 2.0 version which supports bitrates up to 1 Mbits/sec,

#### **3.3. Preliminaries**

25

although there has been ongoing effort to introduce the newer CAN-FD (CAN flexible data rate) [60] variant which allows larger message data (64 bytes instead of 8 bytes) and higher bitrates of up to 5 Mbits/sec. The CAN 2.0b standard frame format is shown in Figure 3.1. CAN supports different types of frame formats, including a DATA frame which contains the actual payload for communication between nodes, a REMOTE frame which is sent from a node requesting data from another node, an ERROR frame which is sent from a node when it detects an error on the bus, and an OVERLOAD frame to provide an additional delay between successive DATA or REMOTE frames. While we concern ourselves, in this work, with the DATA frame format since it contains the actual data being transmitted on the bus, our solution can be extended to consider REMOTE frames with minimal modifications.

Bus contention is resolved using the arbitration field. DATA frames may have different arbitration field lengths–11 bits for the *Standard Frame* (shown in Figure 3.1), and 29 bits for the *Extended Frame* formats (extended frame format is only valid for DATA or REMOTE frames). These arbitration bits constitute the message IDENTIFIER and is used by receiver nodes to identify if the message pertains to them. All nodes which wish to transmit sense the bus for any ongoing transmission and back off when they detect one. When the nodes sense that the bus is free to use, they send a start of frame (SOF). All contentions are resolved as the nodes send the arbitration bits. If a node senses a dominant bit (logic 0) being transmitted as it is transmitting a recessive bit (logic 1), it loses arbitration and stops transmission. Receiver CAN controllers utilize message identifier masks for filtering messages sent out on the bus. The bitmasks are applied to message identifiers as they are made available on the bus. If there is no match, the CAN controller stops listening on the bus until it detects a SOF on the bus. These bitmasks are programmed and kept in the CAN controller memory for comparison when a message IDENTIFIER is received.

Figure 3.1: CAN 2.0b standard frame format

## **3.4** System Model and Problem Statement

We now discuss the real-time task model, threat model, and formally define the problem in this section.

#### 3.4.1 Real-Time Task Model

We model all ECU tasks as periodic real-time tasks, each of which is described by a worstcase execution time (WCET) and a period. The period of these tasks can be lower-bounded based upon the time it takes to generate a message for transmission. Without a loss of generality, we assume that each task in the ECU is responsible for generating CAN messages with *non-overlapping* identifiers. That is, each task has a set of identifiers associated with it and only it. However, this is not a limitation of our approach and multiple tasks can share the same identifiers if so required. Further, certain ECUs may contain *emergency* tasks. For example, for airbag deployment, the airbag control module, arguably one of the most time-sensitive ECUs in a vehicle, may generate an emergency hard sporadic task to send a message to cut-off fuel to the engine to prevent a fire in the event of a crash. We consider such a task as having a very high priority, and which would be able to preempt any currently running periodic ECU task. We assume that tasks are scheduled using a priority-based round-robin scheduling algorithm where a higher-priority task always preempts a lowerpriority task and processor time is equally divided between tasks of equal priority. Such a policy is selected for ease of implementation and predictability. In fact, ARM's commercial RTOS, Keil RTX5 [77], which we utilize in our experiments, uses this policy.

#### 3.4.2 Threat Model

We consider a threat model where the attacker has *remote* access to a vehicle ECU. For detecting physical intrusions, such as an attacker attaching a malicious ECU to the bus, authentication must be done at the network level or at the receiver, which has already has been addressed by prior work [34, 54, 87, 91, 106] and is beyond the scope of this work. We consider that the attacker has taken advantage of external network interfaces made available by certain ECUs on the vehicle (such as WiFi and Bluetooth network interfaces created by a vehicle's infotainment unit) and has managed to compromise task(s) on the ECU. We also assume that the attacker operates *only* within the non-secure domain, and an attacker-controlled task can still make calls to the API made available in the NSC region. We assume two attacker privilege cases: