### Real-Time Software Transactional Memory: Contention Managers, Time Bounds, and Implementations

Mohammed El-Shambakey

Dissertation Submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

> Doctor of Philosophy in Computer Engineering

Binoy Ravindran, Chair Robert P. Broadwater Cameron D. Patterson Mohamed Rizk Mohamed. Rizk Anil Kumar S. Vullikanti

> September 13, 2013 Blacksburg, Virginia

Keywords: Software Transactional Memory, Embedded Systems, Contention Managers Copyright 2013, Mohammed El-Shambakey Real-Time Software Transactional Memory: Contention Managers, Time Bounds, and Implementations

Mohammed El-Shambakey

(ABSTRACT)

Lock-based concurrency control suffers from programmability, scalability, and composability challenges. These challenges are exacerbated in emerging multicore architectures, on which improved software performance must be achieved by exposing greater concurrency. Transactional memory (TM) is an emerging alternative synchronization model for shared memory objects that promises to alleviate these difficulties.

In this dissertation, we consider software transactional memory (STM) for concurrency control in multicore real-time software, and present a suite of real-time STM contention managers for resolving transactional conflicts. The contention managers are called ECM, RCM, LCM, PNF, and FBLT. RCM and ECM resolve conflicts using fixed and dynamic priorities of real-time tasks, respectively, and are naturally intended to be used with the fixed priority (e.g., G-RMA) and dynamic priority (e.g., G-EDF) multicore real-time schedulers, respectively. LCM resolves conflicts based on task priorities as well as atomic section lengths, and can be used with G-EDF or G-RMA schedulers. Transactions under ECM, RCM, and LCM may retry due to conflicts with higher priority tasks even when there are no shared objects, i.e., transitive retry. PNF avoids transitive retry and optimizes processor usage by lowering the priority of retrying transactions, thereby enabling other non-conflicting transactions to proceed. PNF, however, requires a priori knowledge of all requested objects for each atomic section, which is inconsistent with the semantics of dynamic STM. Moreover, its centralized design increases overhead. FBLT avoids transitive retry, do not require a priori knowledge of requested objects, and has a decentralized design.

We establish upper bounds on transactional retry costs and task response times under the contention managers through schedulability analysis. Since ECM and RCM preserve the semantics of the underlying real-time scheduler, their maximum transactional retry cost is double the maximum atomic section length. This is improved in the design of LCM, which achieves shorter retry costs and tighter upper bounds. As PNF avoids transitive retry and improves processor usage, it yields shorter retry costs and tighter upper bounds than ECM, RCM, and LCM. FBLT's upper bounds are similarly tight because it combines the advantages of PNF and LCM.

We formally compare the proposed contention managers with each other, with lock-free synchronization, and with multiprocessor real-time locking protocols. Our analysis reveals that, for most cases, ECM, RCM, and LCM achieve higher schedulability than lock-free synchronization only when the atomic section length does not exceed half of lock-free synchronization's retry loop length. With equal periods and greater access times for shared objects, atomic section length under ECM, RCM, and LCM can be much larger than the retry loop length while still achieving better schedulability. With proper values for LCM's design parameters, atomic section length can be larger than the retry loop length for better schedulability. Under PNF, atomic section length can exceed lock-free's retry loop length and still achieve better schedulability in certain cases. FBLT achieves equal or better schedulability advantage of the contention managers over multiprocessor real-time locking protocols such as Global OMLP and RNLP depends upon the value of  $s_{max}/L_{max}$ , the ratio of the max-

imum transaction length to the maximum critical section length. FBLT's schedulability is equal or better than Global OMLP and RNLP if  $s_{max}/L_{max} \leq 2$ .

Checkpointing enables partial roll-back of transactions by recording transaction execution states (i.e., checkpoints) during execution, allowing roll-back to a previous checkpoint instead of transaction start, improving task response time. We extend FBLT with checkpointing and develop CP-FBLT, and identify the conditions under which CP-FBLT achieves equal or better schedulability than FBLT.

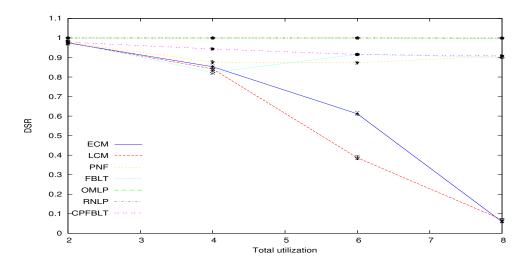

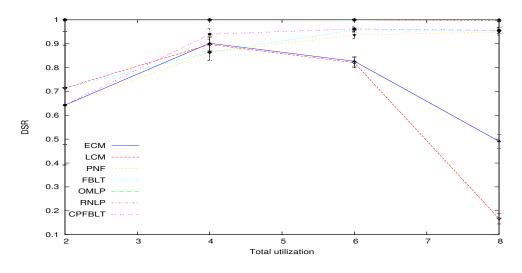

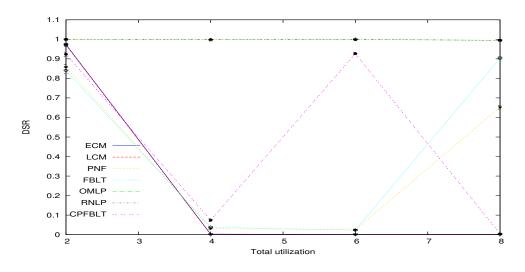

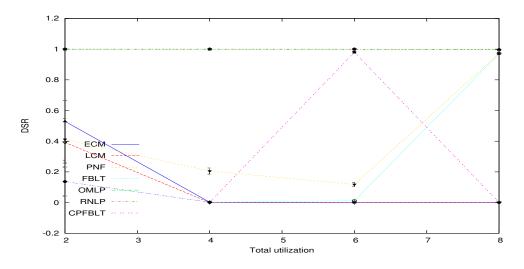

We implement the contention managers in the Rochester STM framework and conduct experimental studies using a multicore real-time Linux kernel. Our studies reveal that among the contention managers, CP-FBLT has the best average-case performance. CP-FBLT's higher performance is due to the fact that PNF's and LCM's advantages are combined into the design of FBLT, which is the base of CP-FBLT. Moreover, checkpointing improves task response time. The contention managers were also found to have equal or better average-case performance than lock-free synchronization: more jobs meet their deadlines using CP-FBLT, FBLT, and PNF than lock-free synchronization by 34.6%, 28.5%, and 32.4% (on average), respectively. The superiority of the contention managers is directly due to their better conflict resolution policies.

Locking protocols such as OMLP and RNLP were found to perform better: more jobs meet their deadlines under OMLP and RNLP than any contention manager by 12.4% and 13.7% (on average), respectively. However, the proposed contention managers have numerous qualitative advantages over locking protocols. Locks do not compose, whereas STM transactions do. To allow multiple objects to be accessed in a critical section, OMLP assigns objects to non-conflicting groups, where each group is protected by a distinct lock. RNLP assumes that objects are accessed in a specific order to prevent deadlocks. In contrast, STM allows multiple objects to be accessed in a transaction in any order, while guaranteeing deadlock-freedom, which significantly increases programmability. Moreover, STM offers platform independence: the proposed contention managers can be entirely implemented in the user-space as a library. In contrast, real-time locking protocols such as OMLP and RNLP must be supported by the underlying platform (i.e., operating system or virtual machine).

## Dedication

To my parents, my wife, my daughter, and all my family

## Acknowledgments

I would like to gratefully acknowledge the supervision of my advisor, Dr. Binoy Ravindran during my Ph.D. study, for his enthusiasm, and his great efforts to guide my research from the start.

Many thanks to the rest of my committee: Dr. Robert P. Broadwater, Dr. Cameron D. Patterson, Dr. Mohamed R. Rizk, and Dr. Anil Vullikanti for their invaluable advice and comments during my preliminary and defence exams. It is a great honour to have them serving in my committee.

In addition, I would like to thank all my previous and current colleagues in Systems Software Research Group, who provided my great environment for collaboration and discussion. Their warm suggestions and help made me never feel alone in this long journey.

Last but not least, thank all my family members for their love and support. I am grateful to my parents, who always did their best in supporting my education from the childhood, and suggested me the correct direction to make my dream come true. Also, I thank my dear wife who devoted her love and support to me through the ups and downs over the past years. It is difficult to overstate my gratitude to her for being such a wonderful wife.

This dissertation is dedicated to all the people who helped me and are helping me all the way.

This work is supported in part by US National Science Foundation under grants CNS 0915895, CNS 1116190, CNS 1130180, and CNS 1217385. Any opinions, findings, and conclusions or recommendations expressed in this site are those of the author(s) and do not necessarily reflect the views of the National Science Foundation.

## Contents

| 1        | Intr | roduction                                         | 1  |

|----------|------|---------------------------------------------------|----|

|          | 1.1  | Transactional Memory                              | 2  |

|          | 1.2  | STM for Real-Time Software                        | 3  |

|          | 1.3  | Research Contributions                            | 4  |

|          | 1.4  | Organization                                      | 8  |

| <b>2</b> | Pas  | t and Related Work                                | 9  |

|          | 2.1  | Real-Time Locking Protocols                       | 10 |

|          | 2.2  | Real-Time Lock-Free and Wait-Free Synchronization | 14 |

|          | 2.3  | Real-Time Database Concurrency Control            | 16 |

|          | 2.4  | Real-Time TM Concurrency Control                  | 19 |

| 3        | Mo   | dels and Assumptions                              | 25 |

| 4        | The  | e ECM and RCM Contention Managers                 | 30 |

|          | 4.1  | ECM                                               | 30 |

|          |      | 4.1.1 Illustrative Example                        | 31 |

|          |      | 4.1.2 Transitive Retry                            | 31 |

|          |      | 4.1.3 G-EDF Interference                          | 32 |

|          |      | 4.1.4 Retry Cost of Atomic Sections               | 34 |

|          |      | 4.1.5 Upper Bound on Response Time                | 38 |

|          | 4.2  | RCM                                               | 40 |

|          |     | 4.2.1  | Maximum Task Interference           | 41 |

|----------|-----|--------|-------------------------------------|----|

|          |     | 4.2.2  | Retry Cost of Atomic Sections       | 41 |

|          |     | 4.2.3  | Upper Bound on Response Time        | 42 |

|          | 4.3 | Analy  | tical Performance Comparison        | 43 |

|          | 4.4 | STM ·  | versus Lock-Free                    | 43 |

|          |     | 4.4.1  | ECM versus Lock-Free                | 44 |

|          |     | 4.4.2  | RCM versus Lock-Free                | 46 |

|          | 4.5 | STM ·  | versus Locking protocols            | 48 |

|          |     | 4.5.1  | Priority Inversion under OMLP       | 48 |

|          |     | 4.5.2  | ECM versus OMLP                     | 49 |

|          |     | 4.5.3  | RCM versus OMLP                     | 50 |

|          |     | 4.5.4  | Priority Inversion under RNLP       | 50 |

|          |     | 4.5.5  | ECM versus RNLP                     | 51 |

|          |     | 4.5.6  | RCM versus RNLP                     | 51 |

|          | 4.6 | Conclu | usions                              | 52 |

| <b>5</b> | The | LCM    | Contention Manager                  | 53 |

|          | 5.1 | Lengt  | h-based CM                          | 53 |

|          |     | 5.1.1  | Design and Rationale                | 54 |

|          |     | 5.1.2  | LCM Illustrative Example            | 56 |

|          | 5.2 | Prope  | rties                               | 57 |

|          | 5.3 | Retry  | Cost and Response Time of LCM/G-EDF | 59 |

|          | 5.4 | Total  | utilization of LCM/G-EDF            | 60 |

|          |     | 5.4.1  | LCM/G-EDF versus ECM                | 60 |

|          |     | 5.4.2  | LCM/G-EDF versus Lock-free          | 61 |

|          |     | 5.4.3  | LCM/G-EDF versus OMLP               | 62 |

|          |     | 5.4.4  | LCM/G-EDF versus RNLP               | 62 |

|          | 5.5 | Retry  | Cost and Response Time of LCM/G-RMA | 62 |

|          |     |        |                                     |    |

|          | 5.6 | Total  | utilization of LCM/G-RMA            |    |

|   |     | 5.6.1 LCM/G-RMA versus RCM $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 64 |

|---|-----|-----------------------------------------------------------------------------------------------------------|----|

|   |     | 5.6.2 LCM/G-RMA versus Lock-free                                                                          | 64 |

|   |     | 5.6.3 LCM/G-RMA versus OMLP                                                                               | 67 |

|   |     | 5.6.4 LCM/G-RMA versus RNLP                                                                               | 68 |

|   | 5.7 | Conclusions                                                                                               | 68 |

| 6 | The | e PNF Contention Manager                                                                                  | 70 |

|   | 6.1 | Limitations of ECM, RCM, and LCM                                                                          | 70 |

|   | 6.2 | The PNF Contention Manager                                                                                | 71 |

|   |     | 6.2.1 Illustrative Example                                                                                | 73 |

|   | 6.3 | Properties                                                                                                | 74 |

|   | 6.4 | Retry Cost and Response Time Under PNF                                                                    | 76 |

|   | 6.5 | PNF versus Competitors                                                                                    | 79 |

|   |     | 6.5.1 PNF versus ECM                                                                                      | 79 |

|   |     | 6.5.2 PNF versus RCM                                                                                      | 80 |

|   |     | 6.5.3 PNF versus LCM/G-EDF                                                                                | 81 |

|   |     | 6.5.4 PNF versus LCM/G-RMA                                                                                | 82 |

|   |     | 6.5.5 PNF versus Lock-free Synchronization                                                                | 83 |

|   |     | 6.5.6 PNF versus Locking Protocols                                                                        | 85 |

|   | 6.6 | Conclusions                                                                                               | 86 |

| 7 | The | e FBLT Contention Manager                                                                                 | 88 |

|   | 7.1 | Motivation                                                                                                | 88 |

|   | 7.2 | The FBLT Contention Manager                                                                               | 89 |

|   |     | 7.2.1 Illustrative Example                                                                                | 89 |

|   | 7.3 | Retry Cost and Response Time Bounds                                                                       | 91 |

|   | 7.4 | Total utilization Comparison                                                                              | 92 |

|   |     | 7.4.1 FBLT versus ECM                                                                                     | 93 |

|   |     | 7.4.2 FBLT versus RCM                                                                                     | 94 |

|    |      | 7.4.3 FBLT versus LCM/G-EDF $\dots \dots \dots$   |

|----|------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|    |      | 7.4.4 FBLT versus G-RMA/LCM                                                                                                                       |

|    |      | 7.4.5 FBLT versus PNF/G-EDF                                                                                                                       |

|    |      | 7.4.6 FBLT versus PNF/G-RMA                                                                                                                       |

|    |      | 7.4.7 FBLT versus Lock-free                                                                                                                       |

|    |      | 7.4.8 FBLT versus Locking Protocols                                                                                                               |

|    | 7.5  | Conclusions                                                                                                                                       |

| 8  | FBI  | Contention Manager with Checkpointing 100                                                                                                         |

|    | 8.1  | Motivation $\ldots \ldots \ldots$ |

|    | 8.2  | Checkpointing FBLT (CP-FBLT)                                                                                                                      |

|    |      | 8.2.1 Checkpointing LCM (CPLCM) 102                                                                                                               |

|    |      | 8.2.2 CP-FBLT                                                                                                                                     |

|    | 8.3  | CP-FBLT Retry Cost                                                                                                                                |

|    | 8.4  | CP-FBLT versus FBLT                                                                                                                               |

|    | 8.5  | Conclusion                                                                                                                                        |

| 9  | Imp  | ementation and Experimental Evaluations 110                                                                                                       |

|    | 9.1  | $Methodology \dots \dots$                   |

|    | 9.2  | Fasksets                                                                                                                                          |

|    | 9.3  | Performance Measurements                                                                                                                          |

|    | 9.4  | Results                                                                                                                                           |

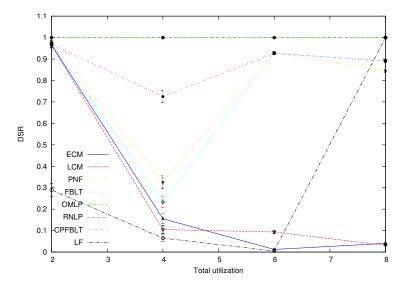

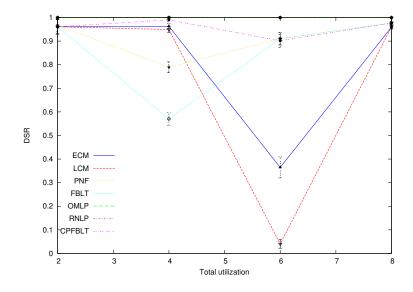

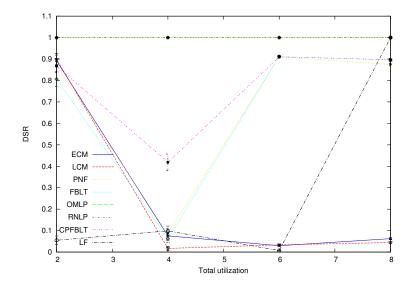

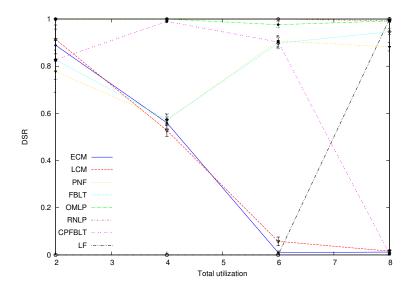

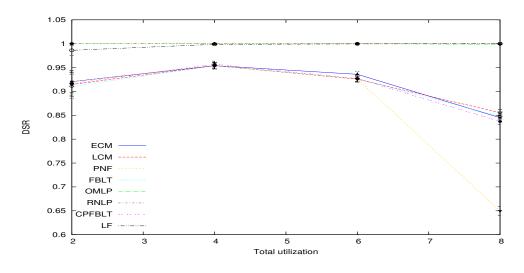

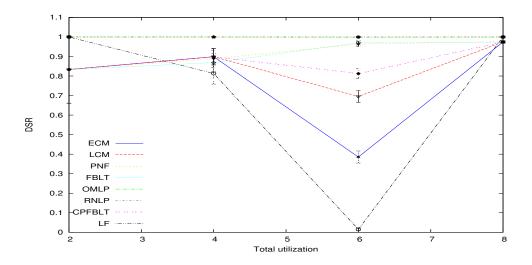

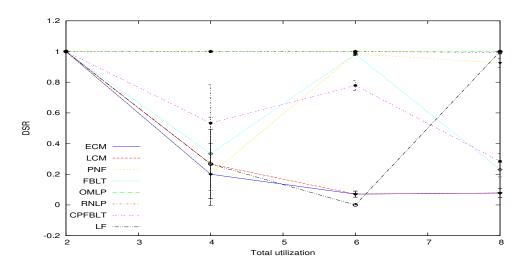

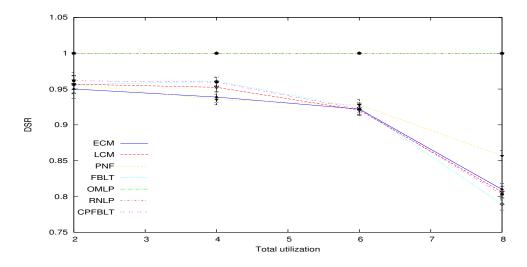

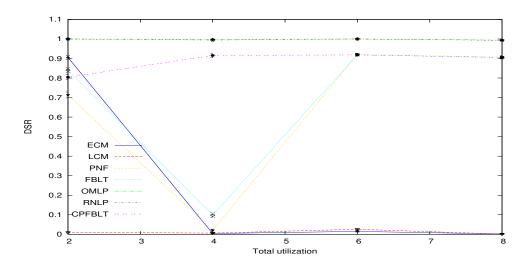

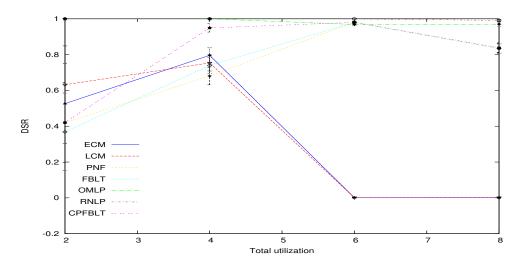

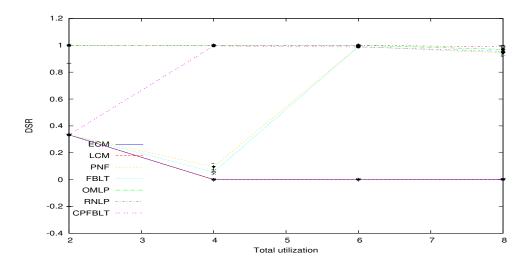

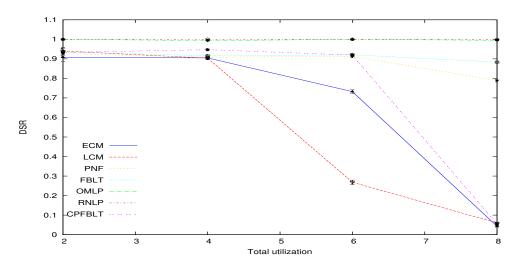

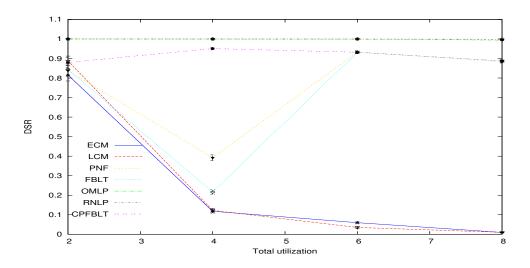

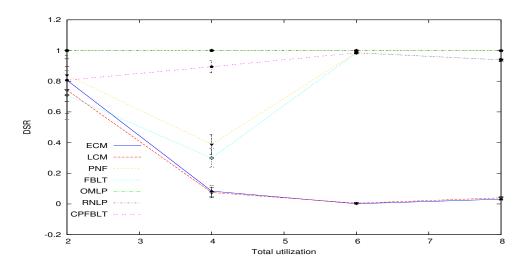

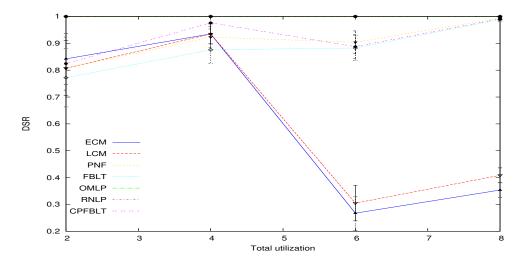

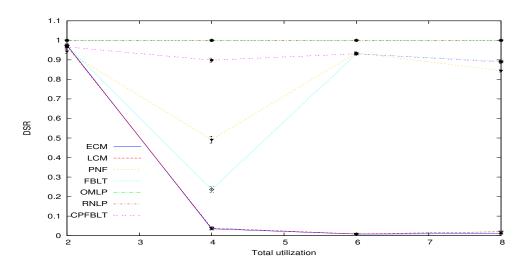

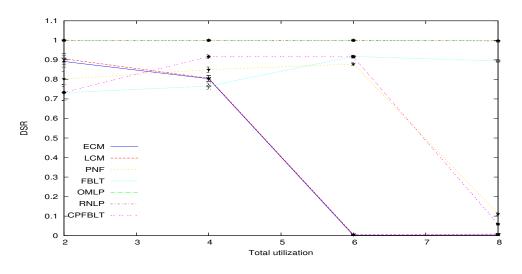

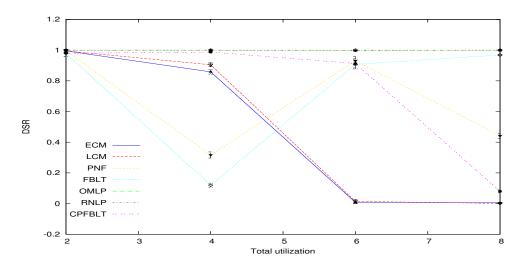

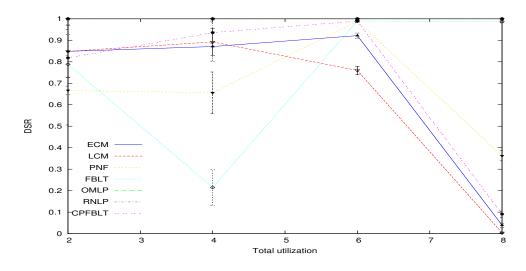

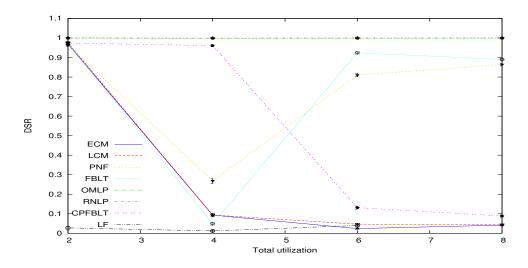

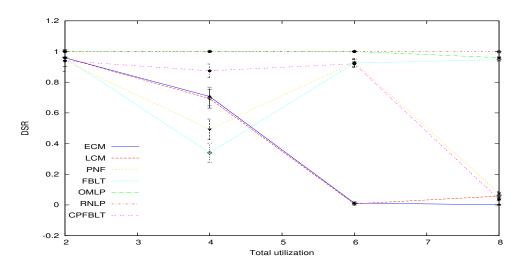

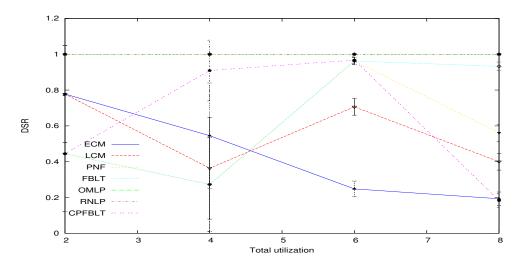

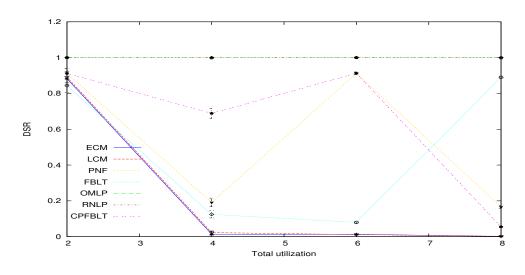

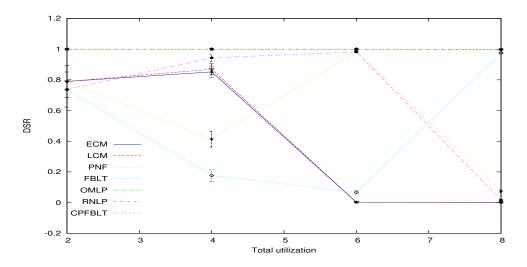

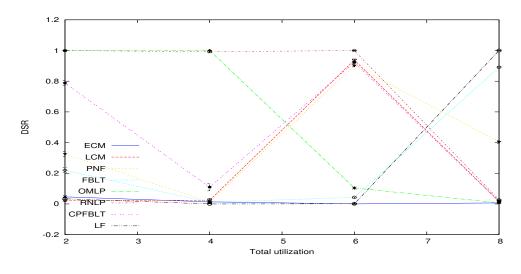

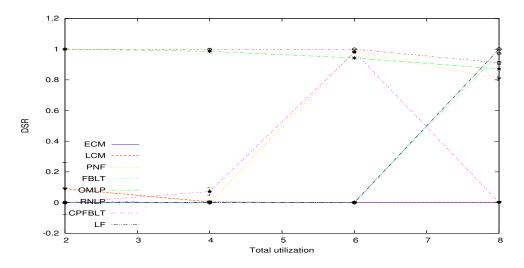

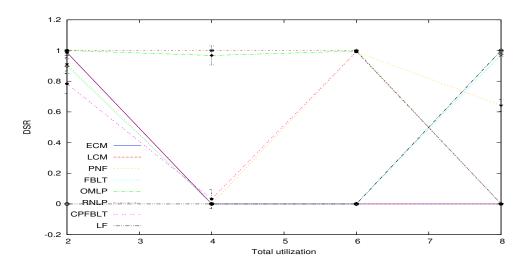

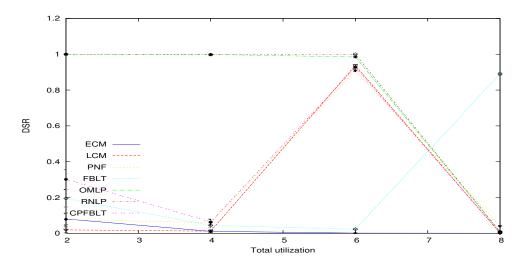

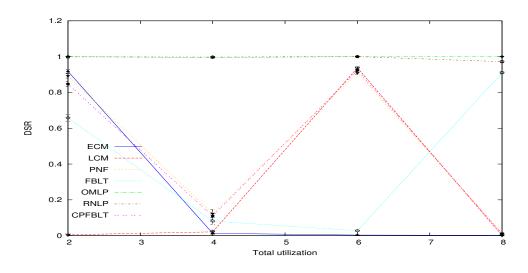

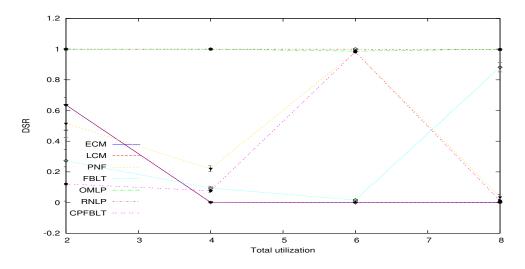

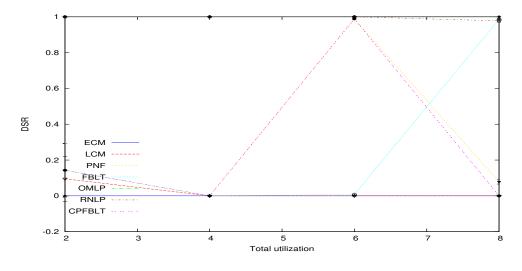

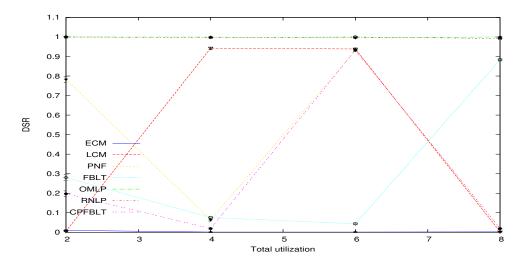

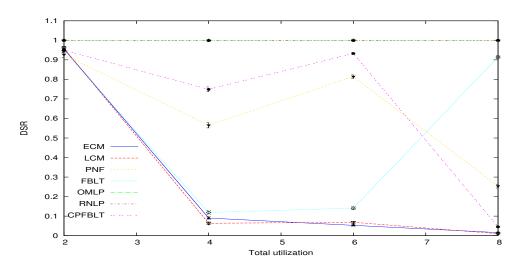

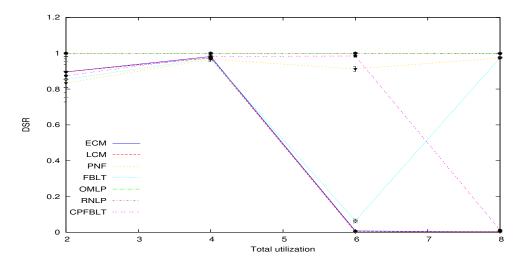

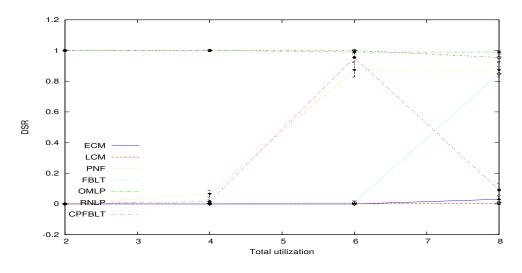

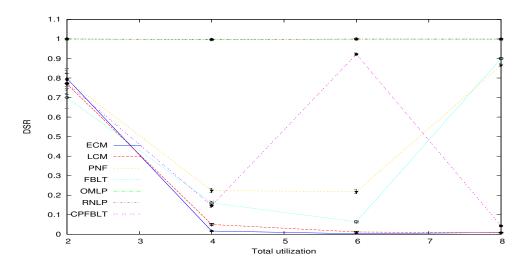

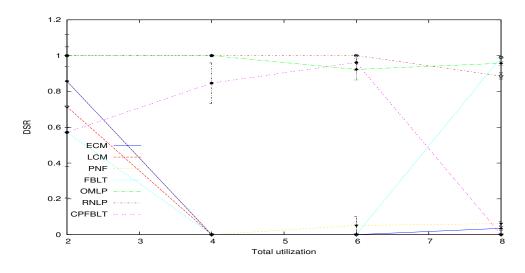

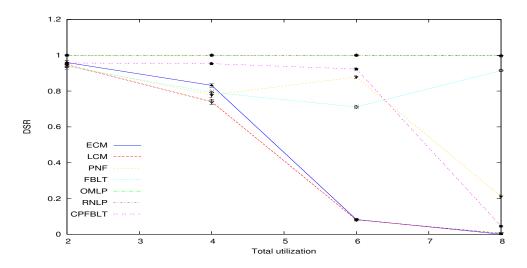

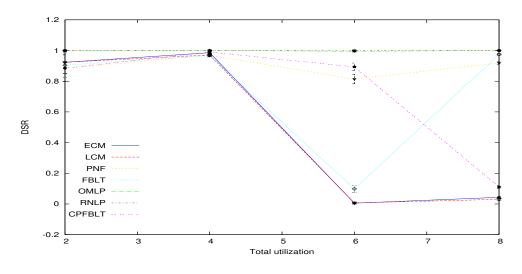

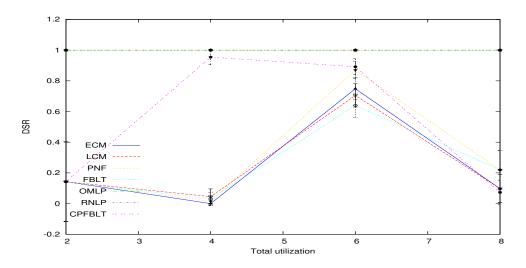

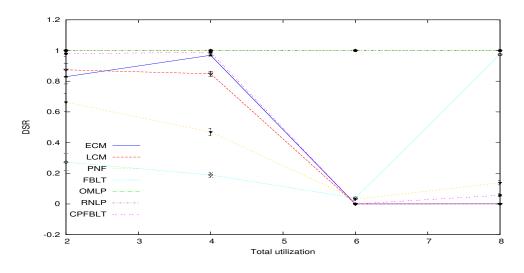

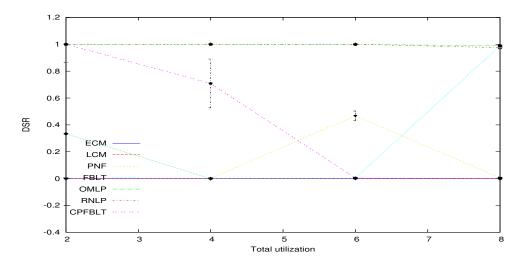

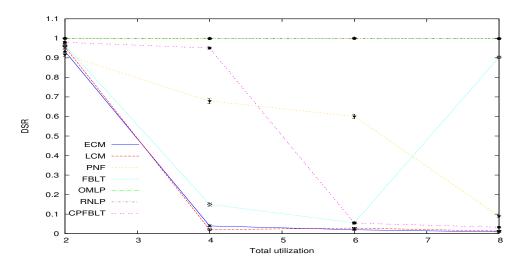

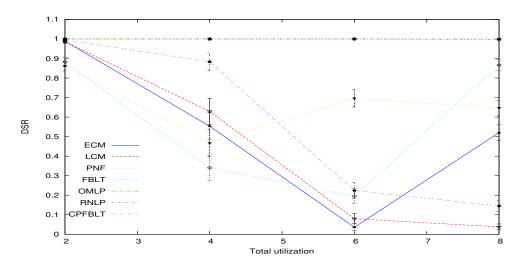

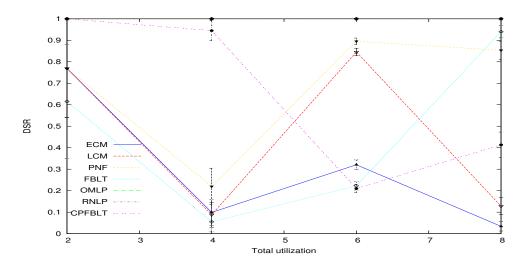

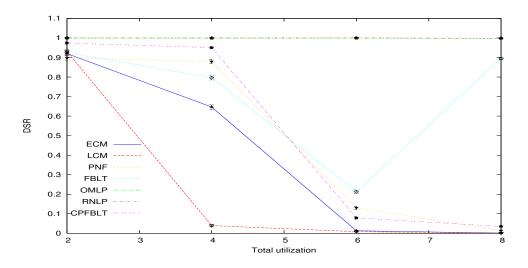

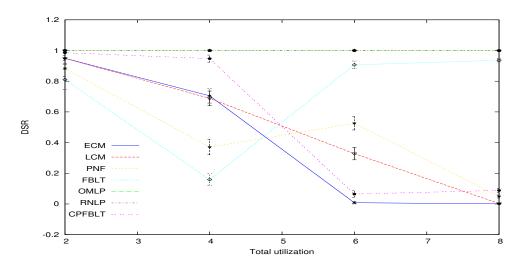

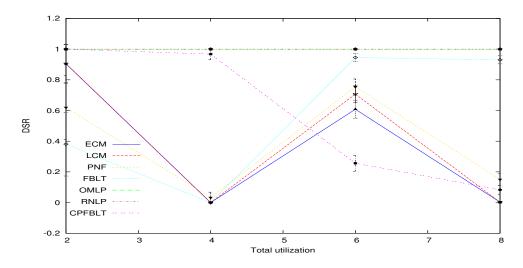

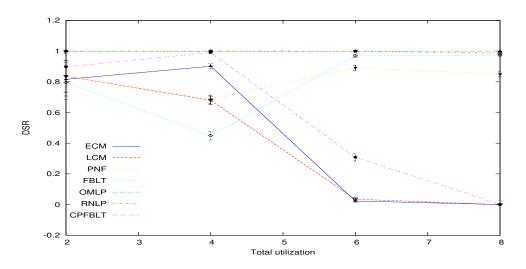

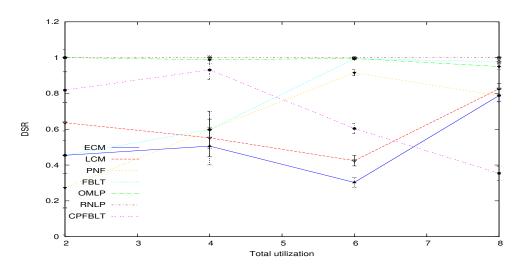

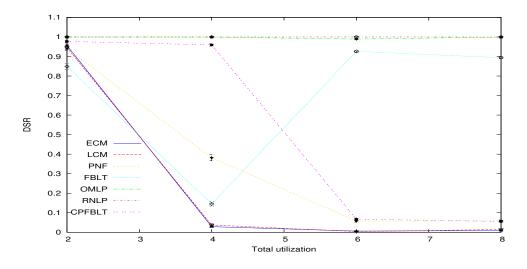

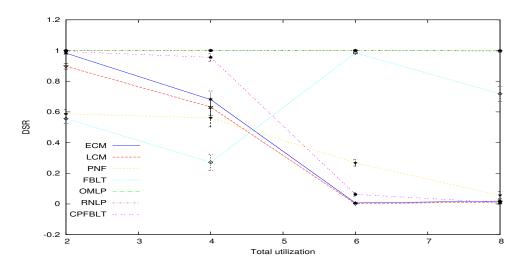

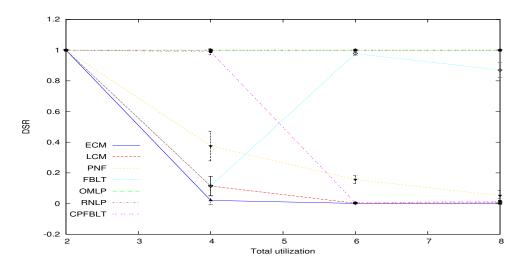

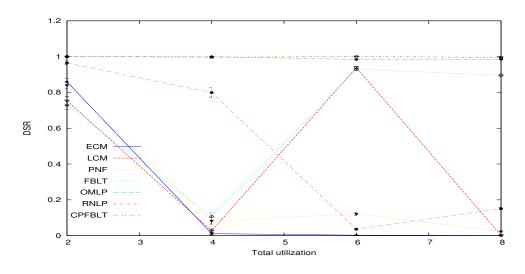

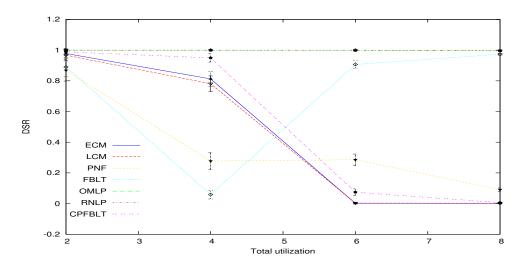

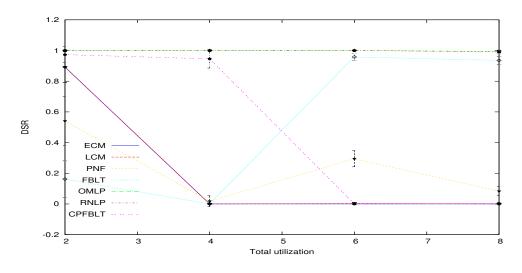

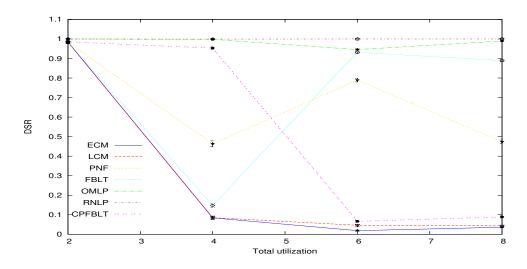

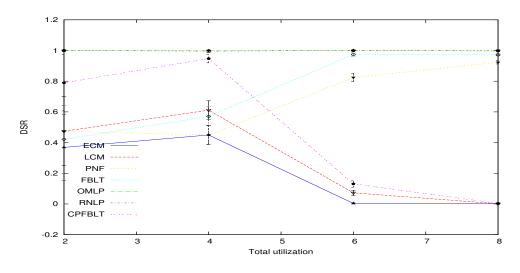

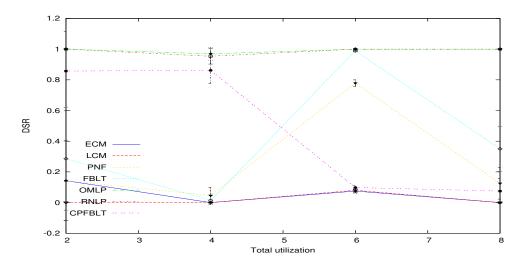

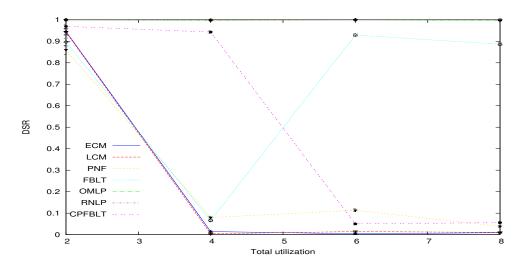

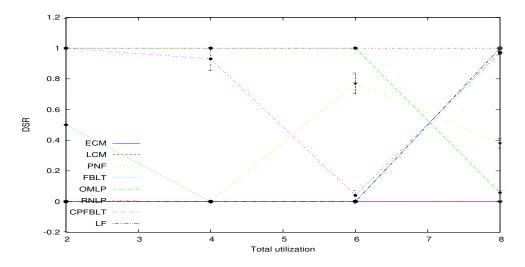

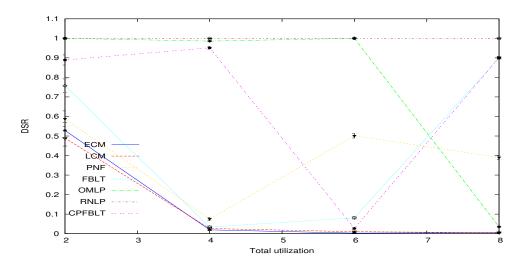

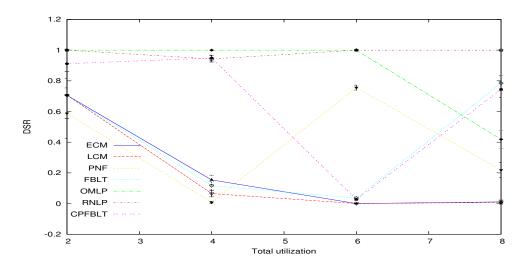

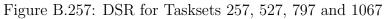

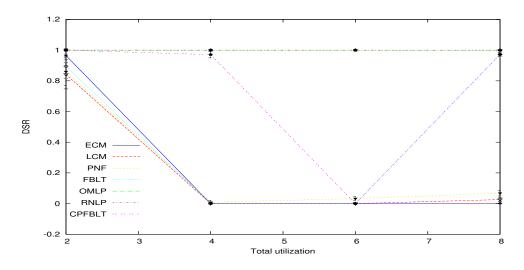

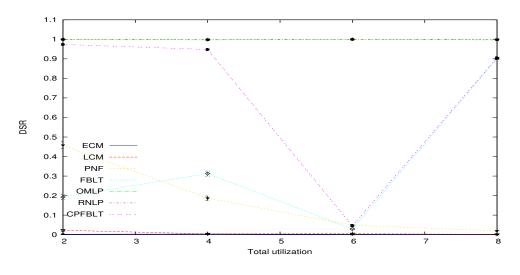

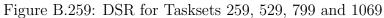

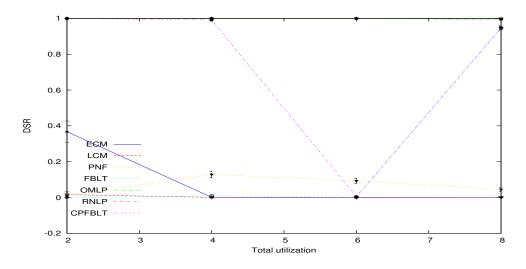

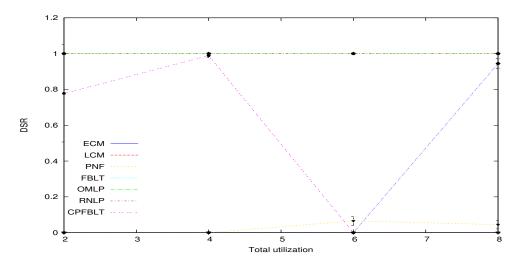

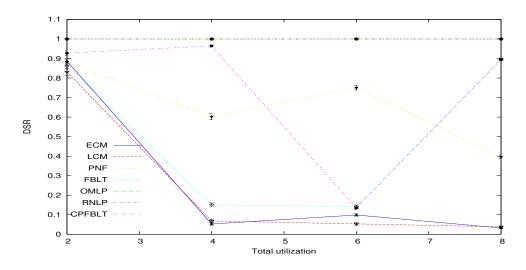

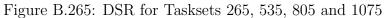

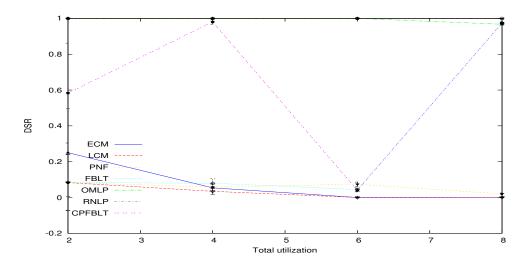

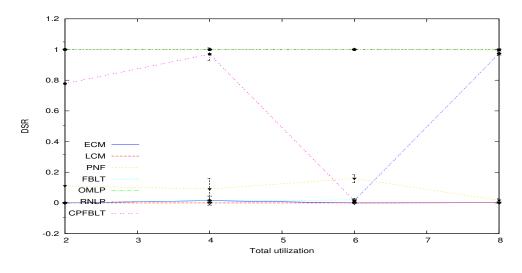

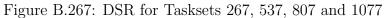

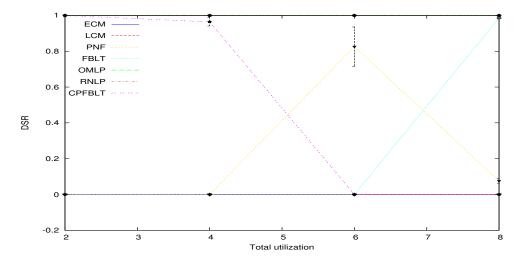

|    |      | 9.4.1 General results for DSR 113                                                                                                                 |

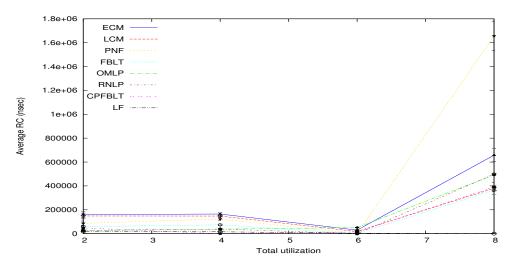

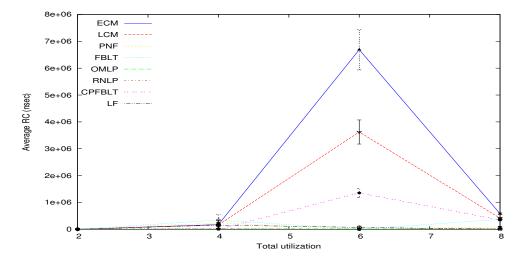

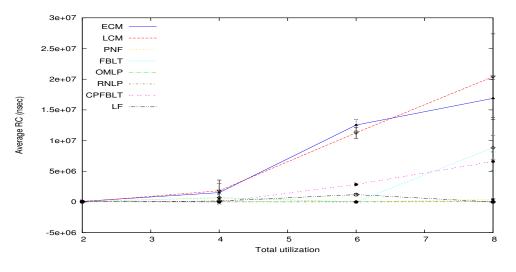

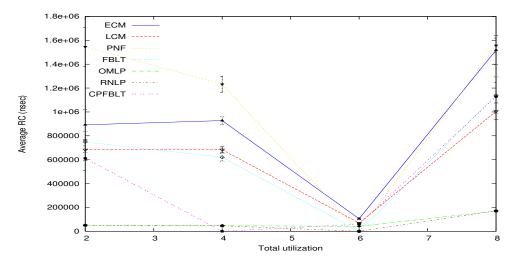

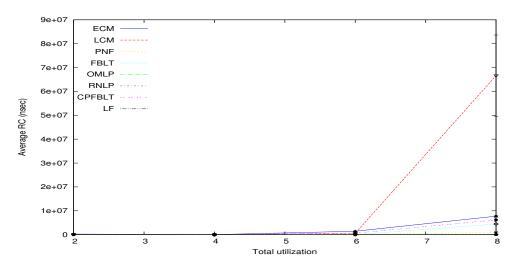

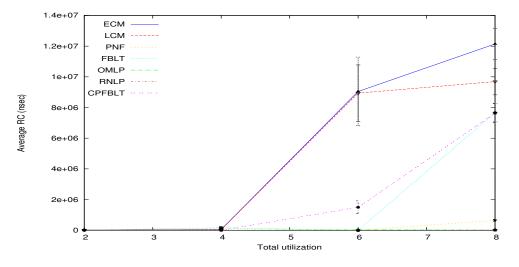

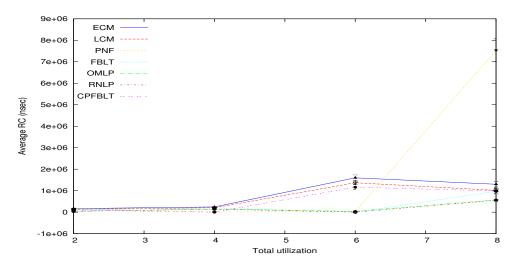

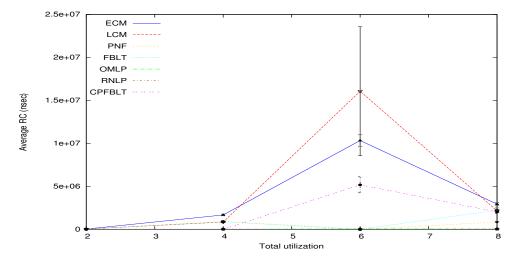

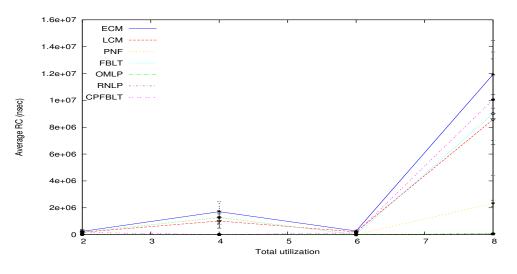

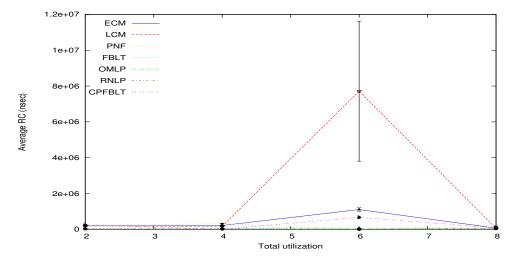

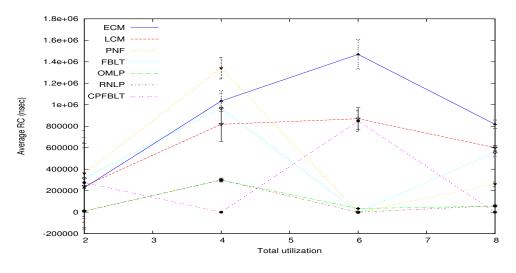

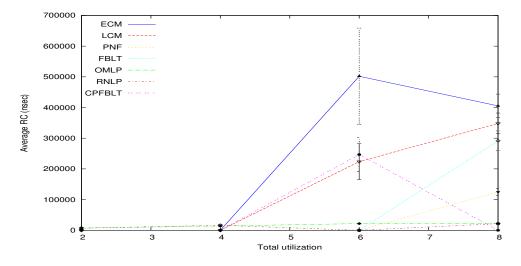

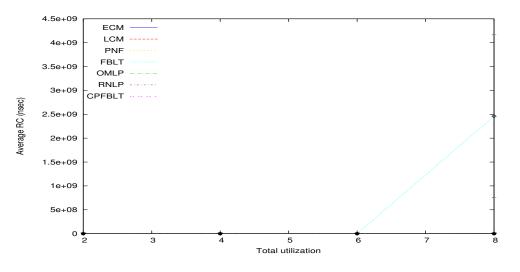

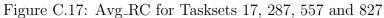

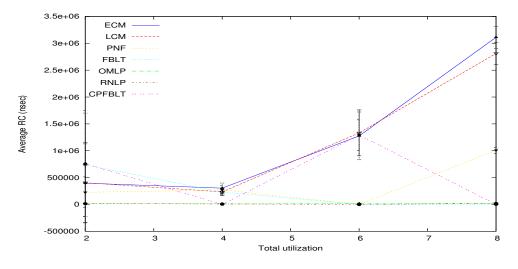

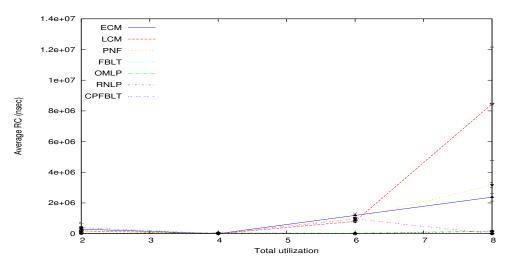

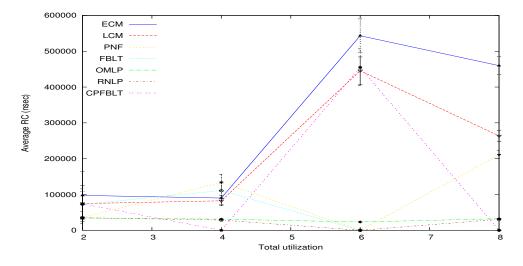

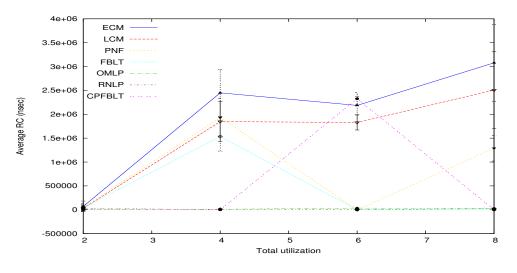

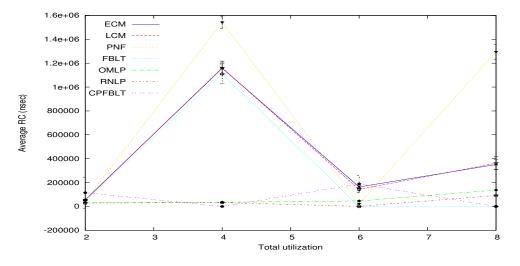

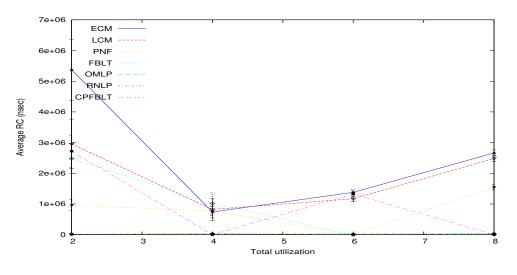

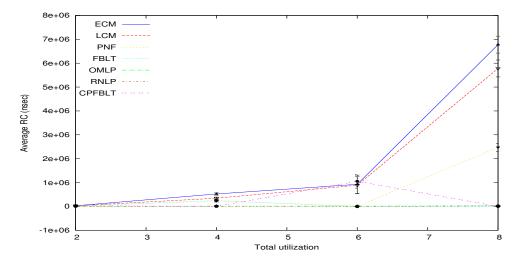

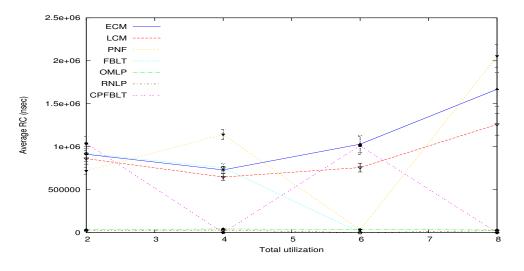

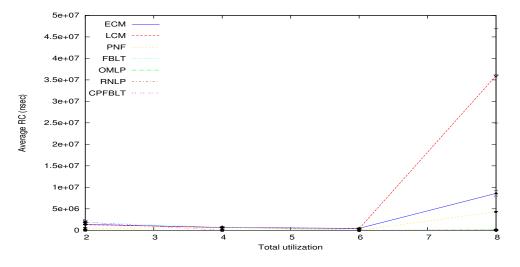

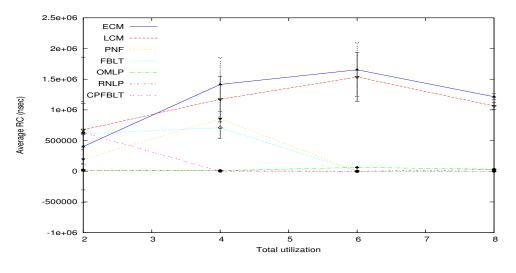

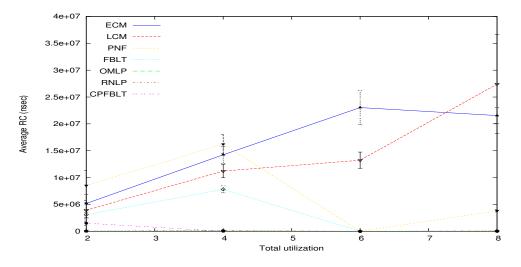

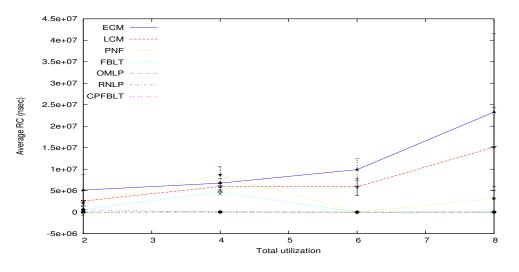

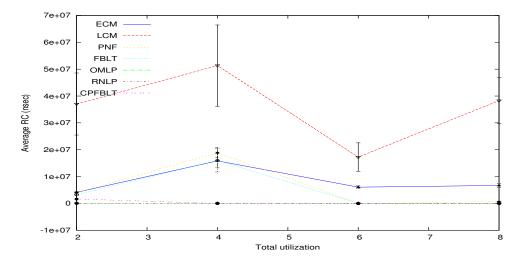

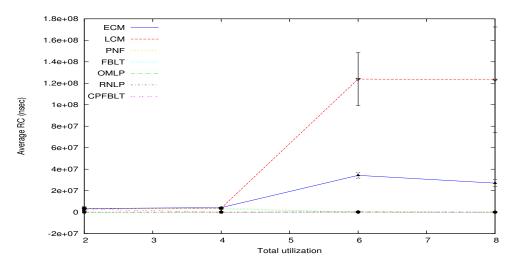

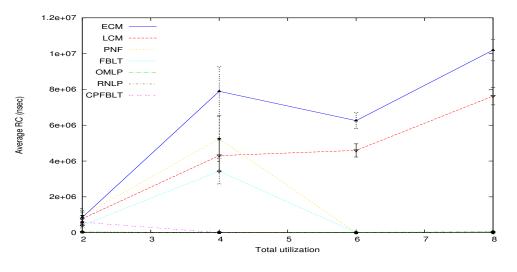

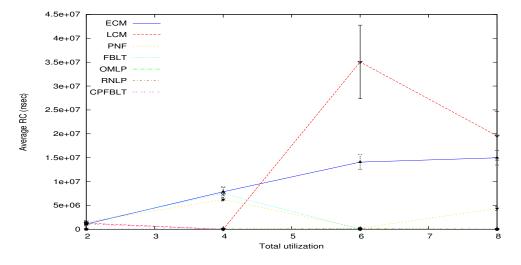

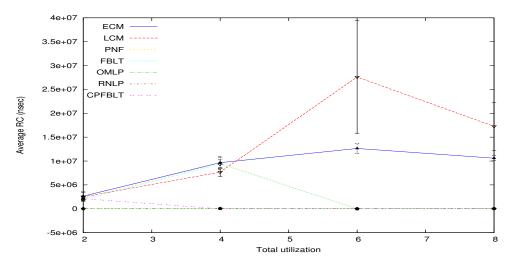

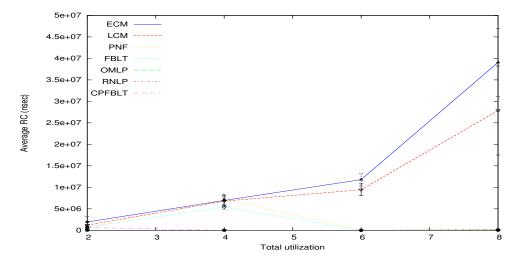

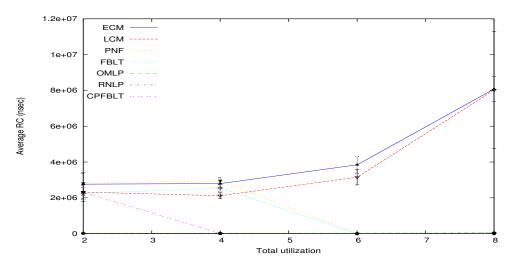

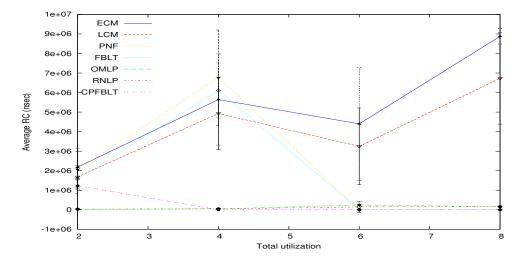

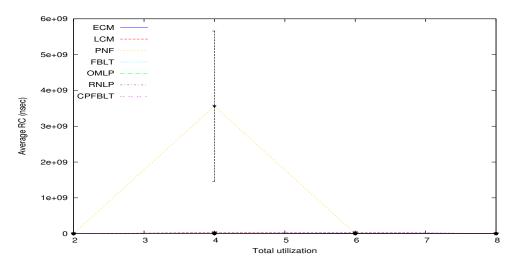

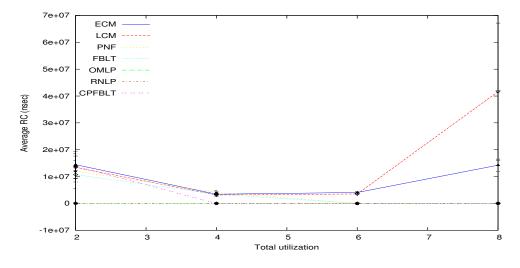

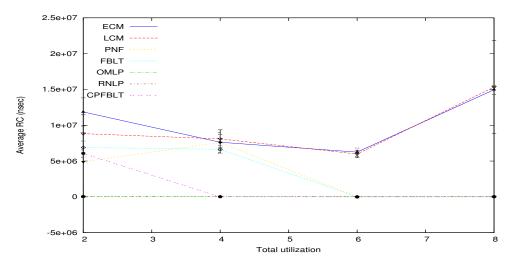

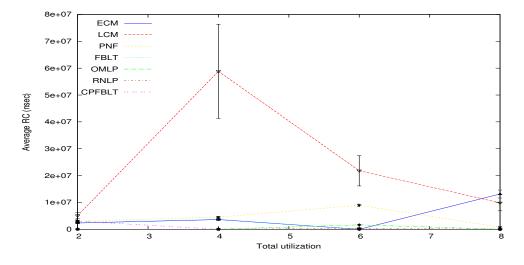

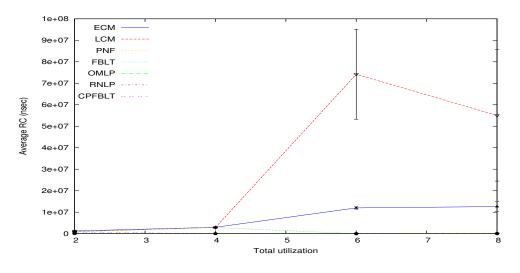

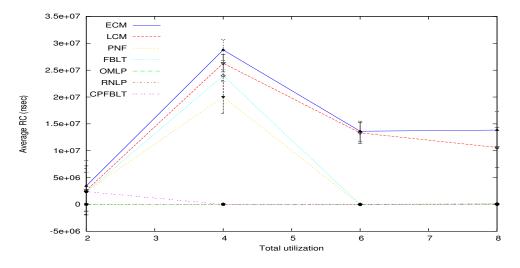

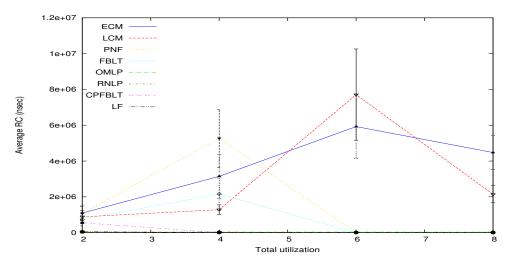

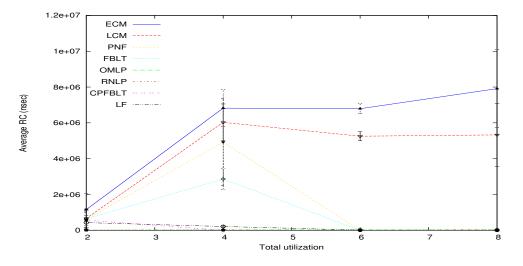

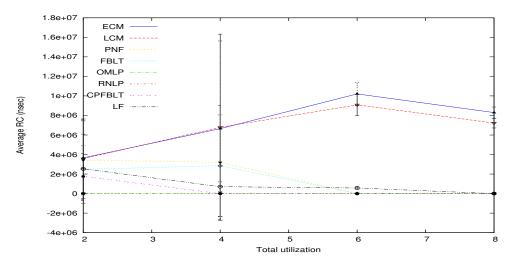

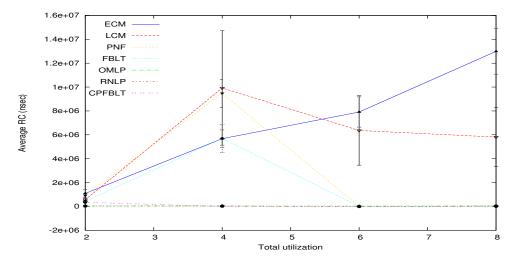

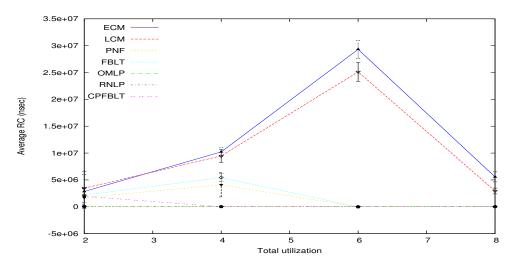

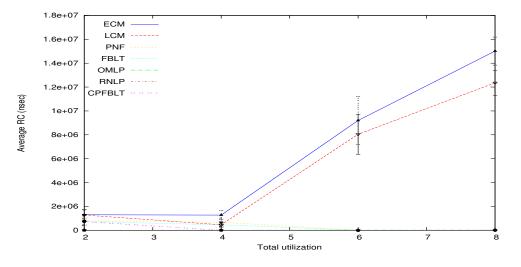

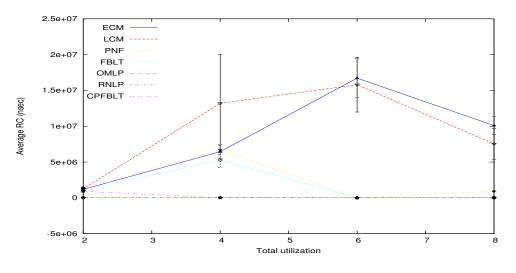

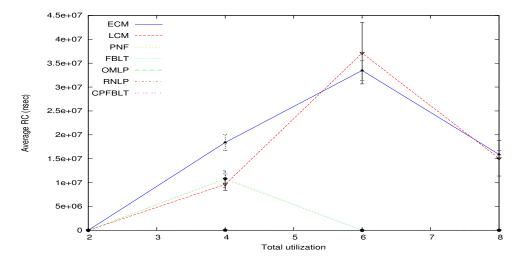

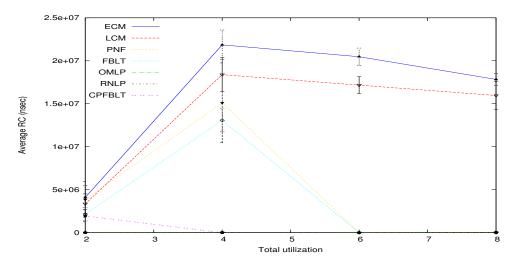

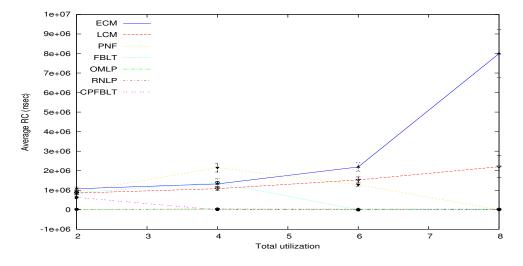

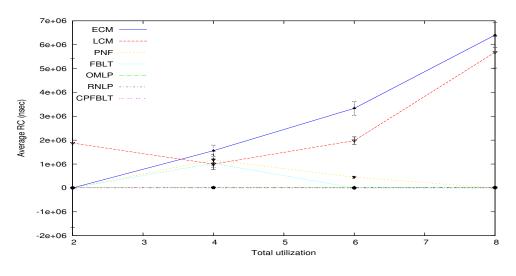

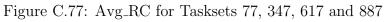

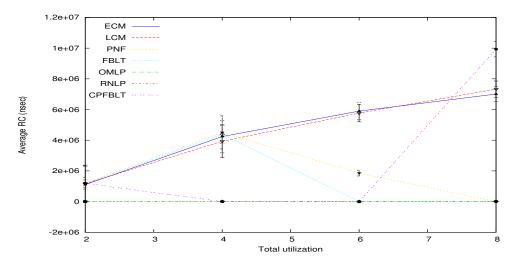

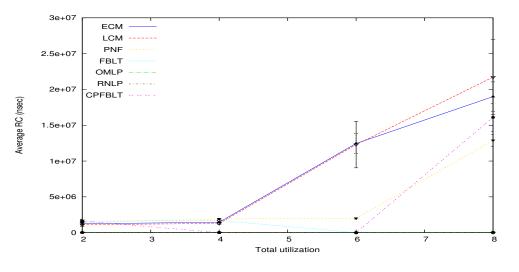

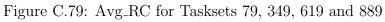

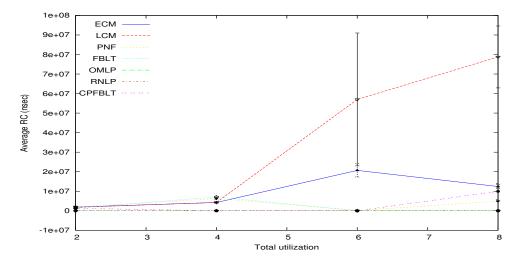

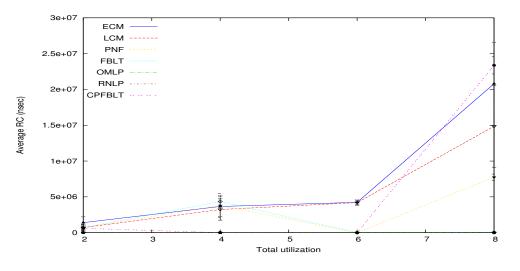

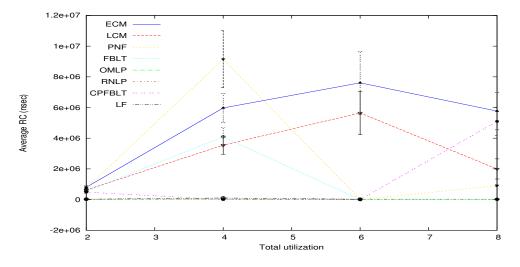

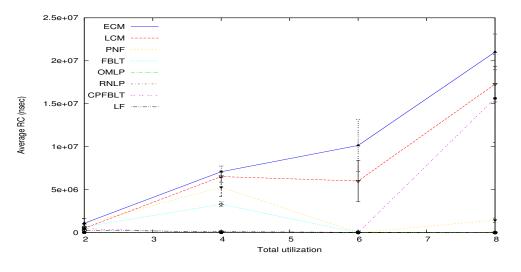

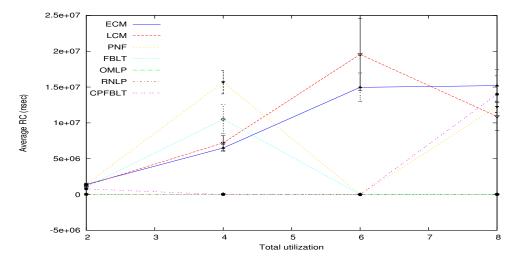

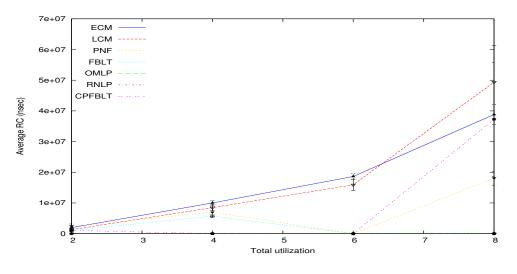

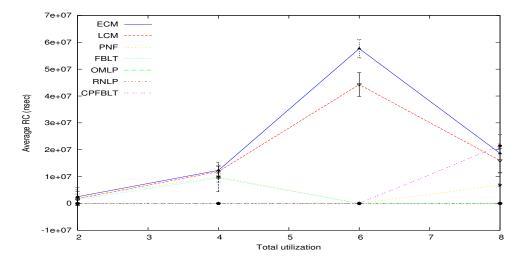

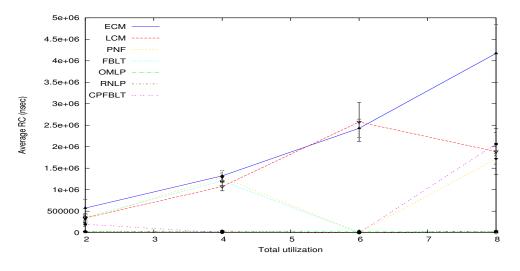

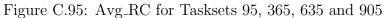

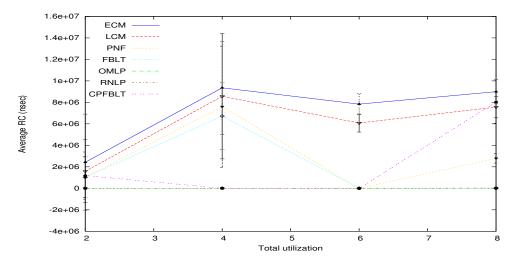

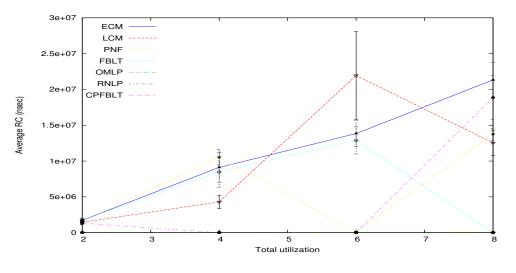

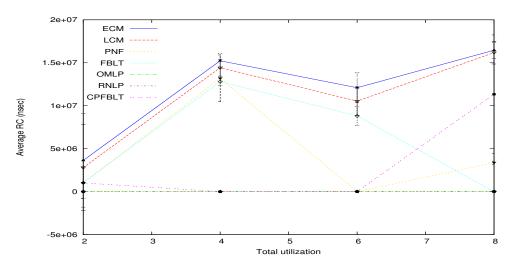

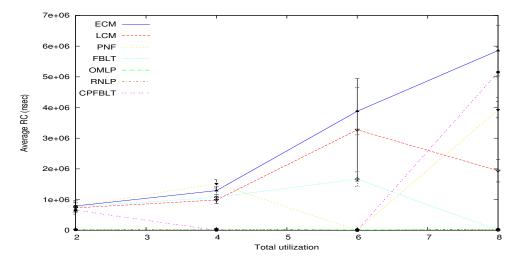

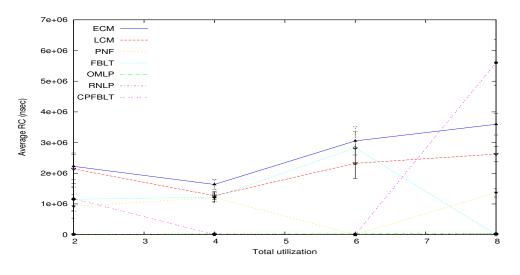

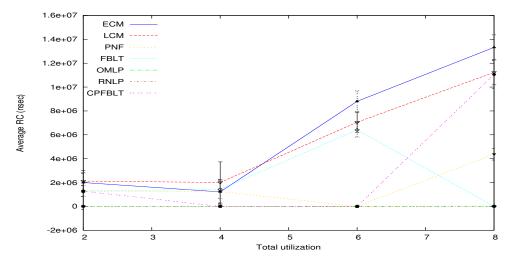

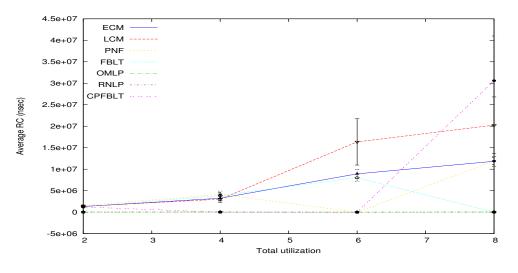

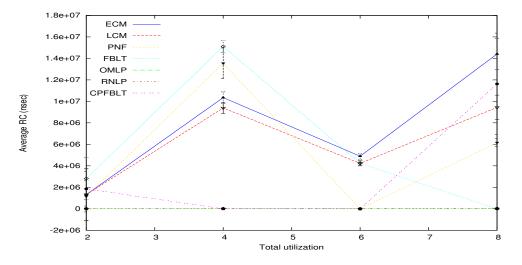

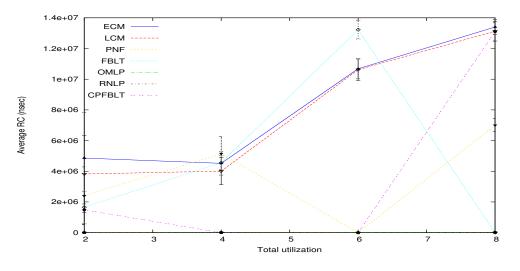

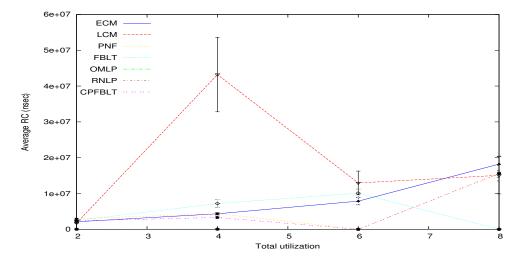

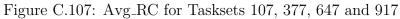

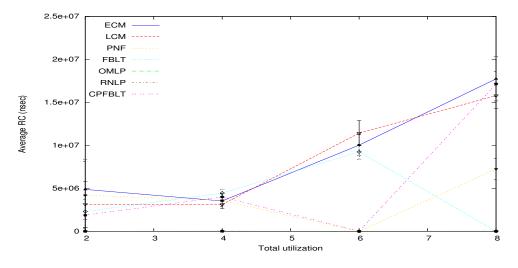

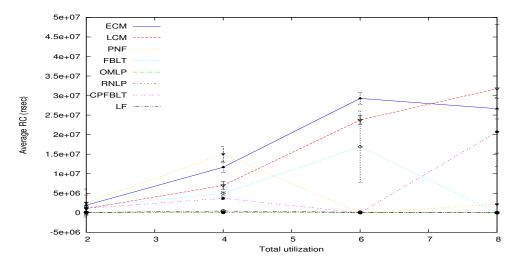

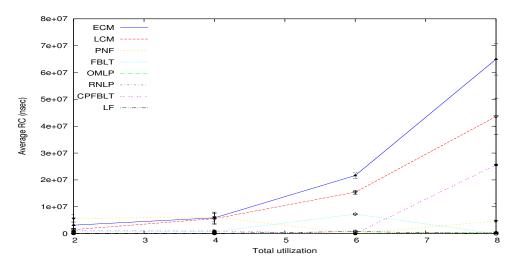

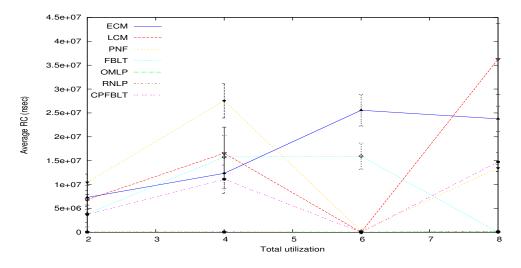

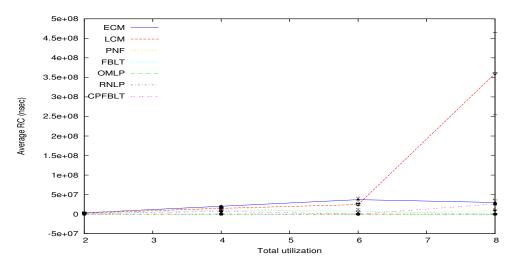

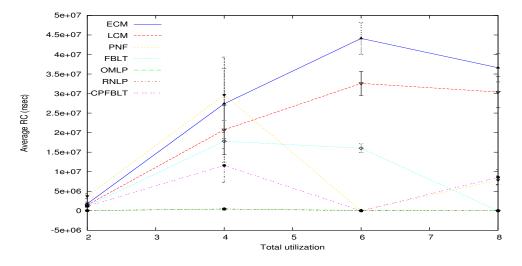

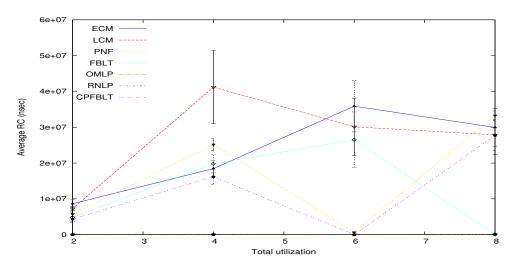

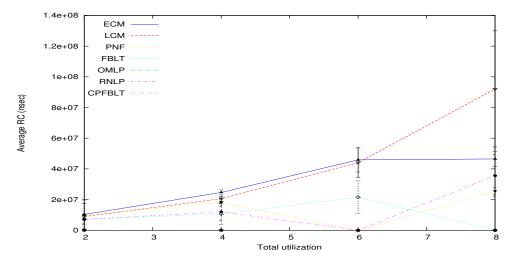

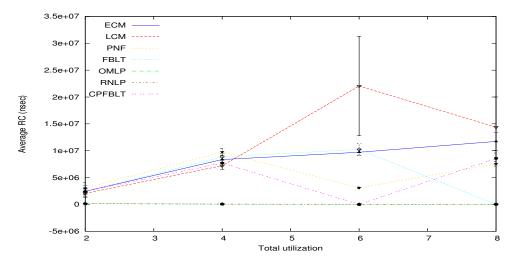

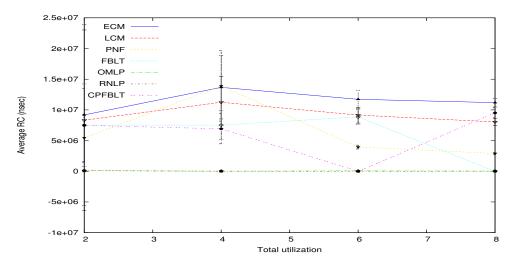

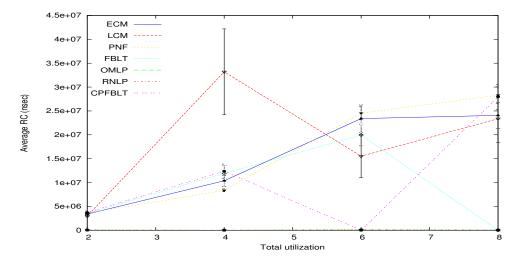

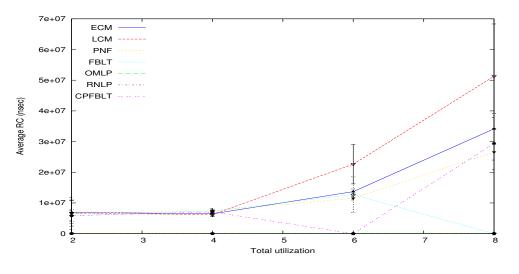

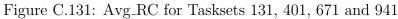

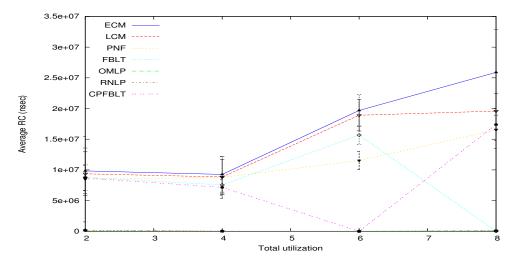

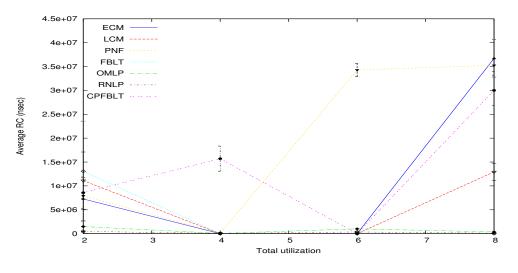

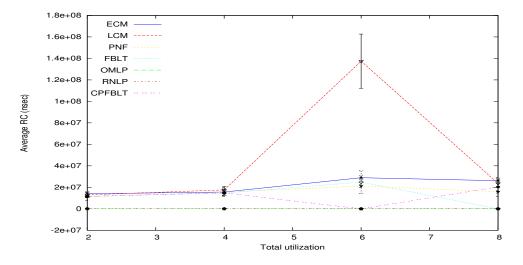

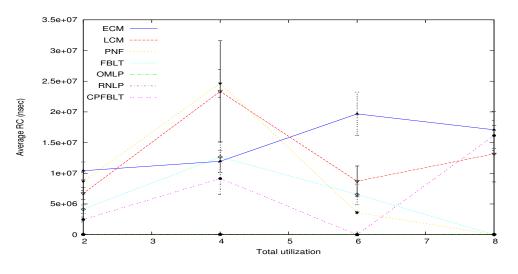

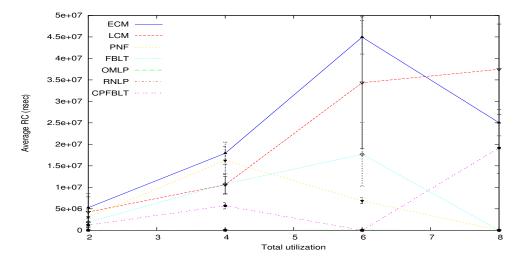

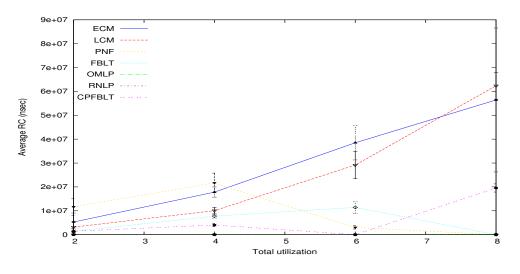

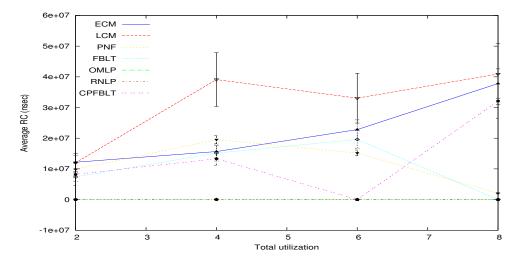

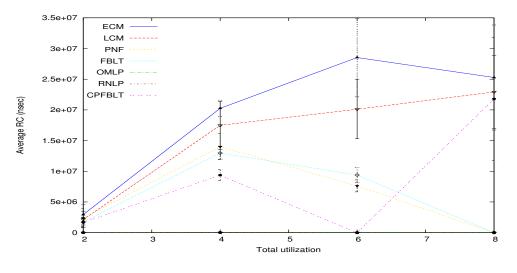

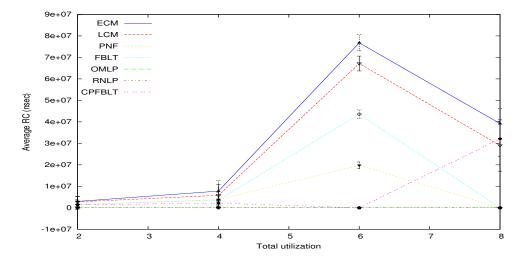

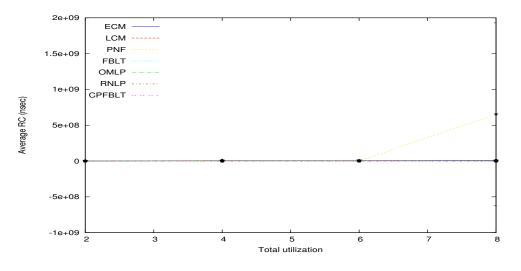

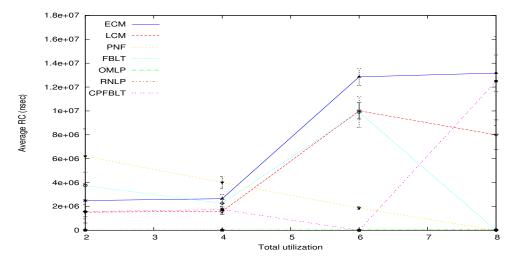

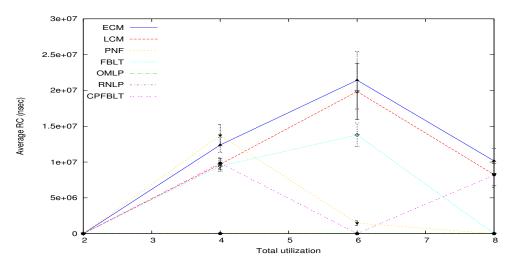

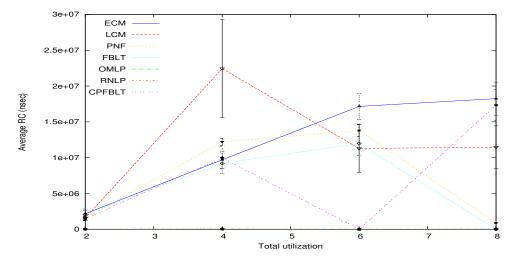

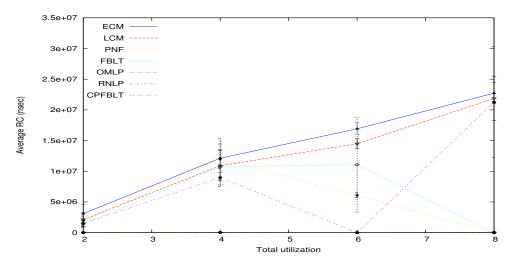

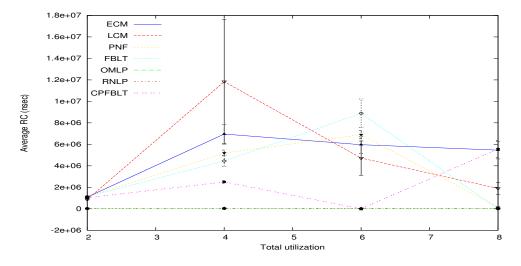

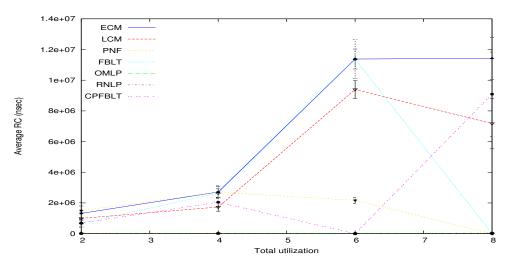

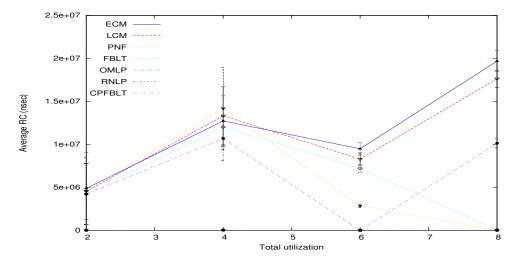

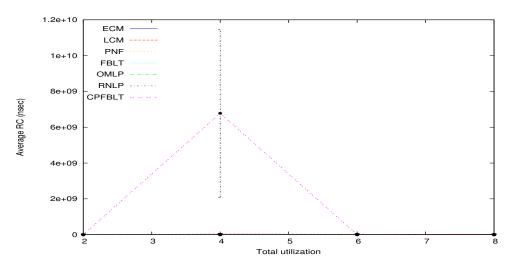

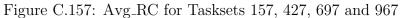

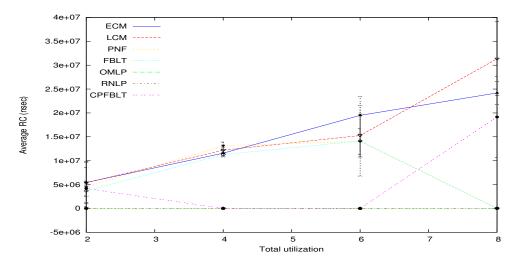

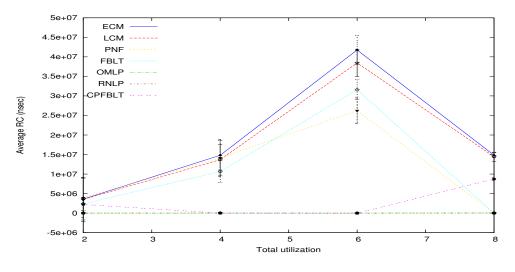

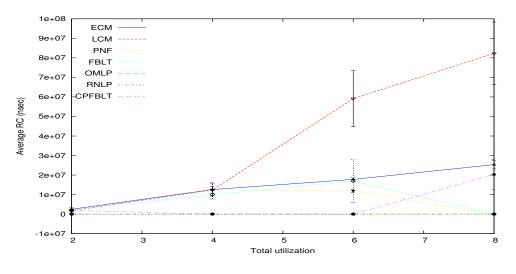

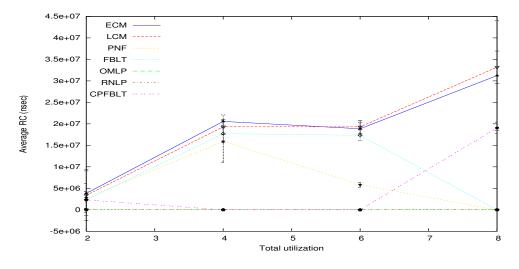

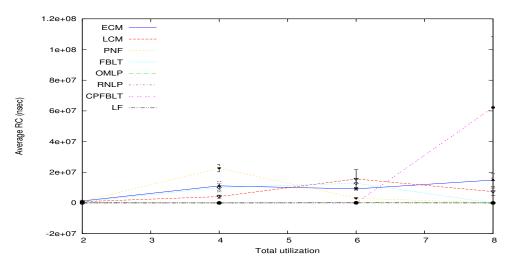

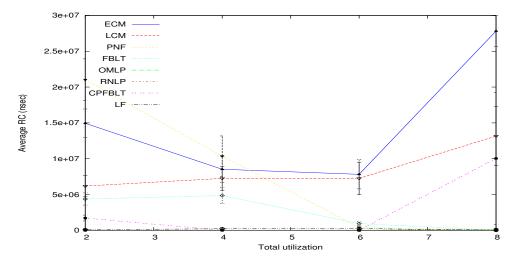

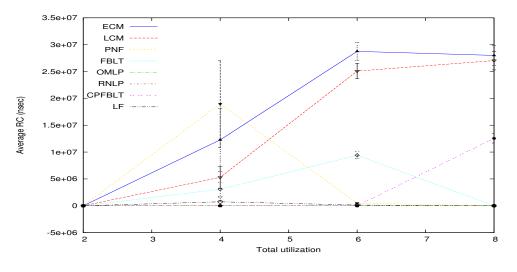

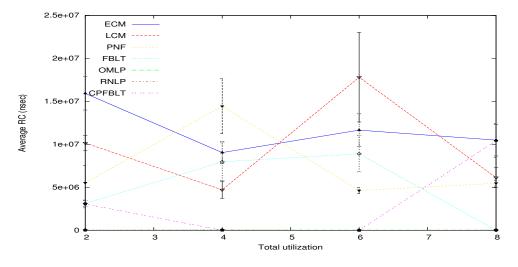

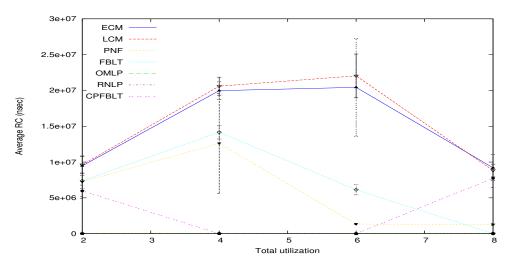

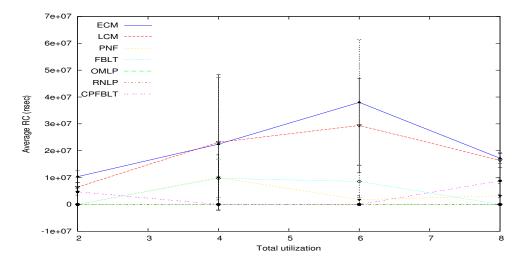

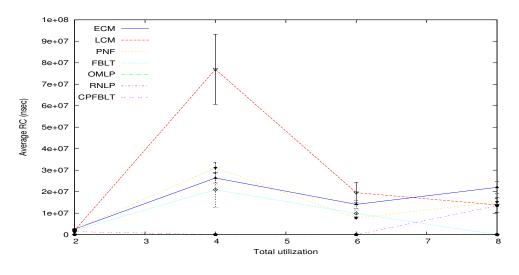

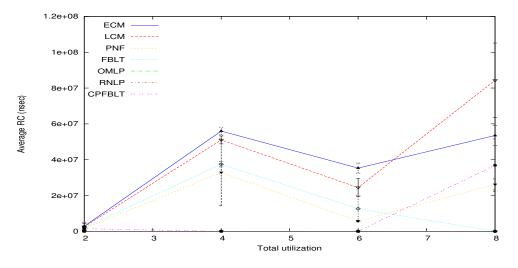

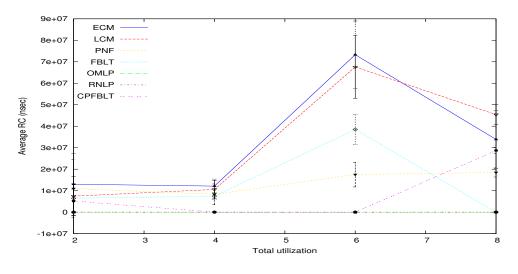

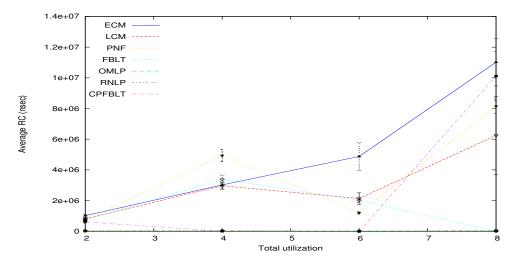

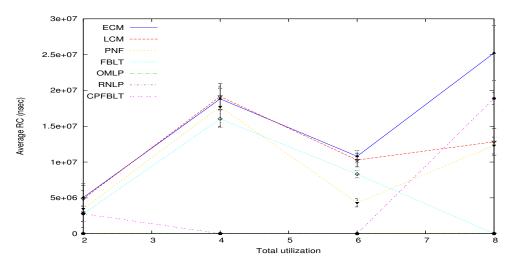

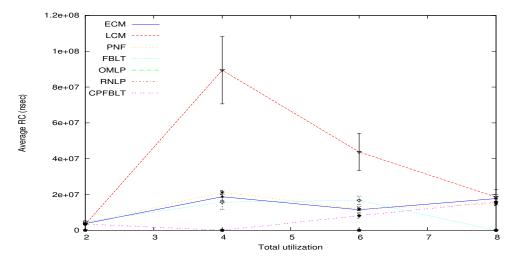

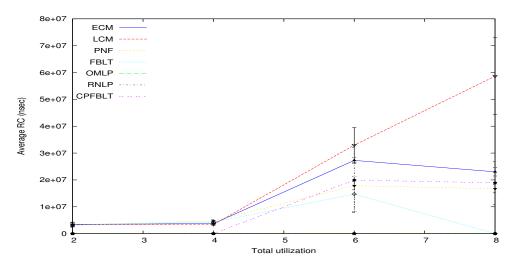

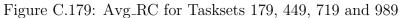

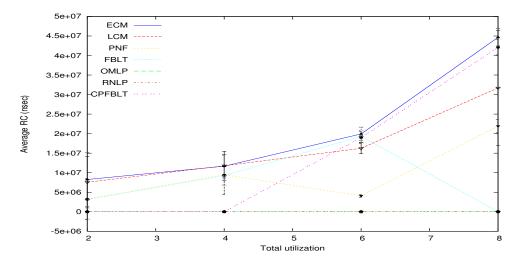

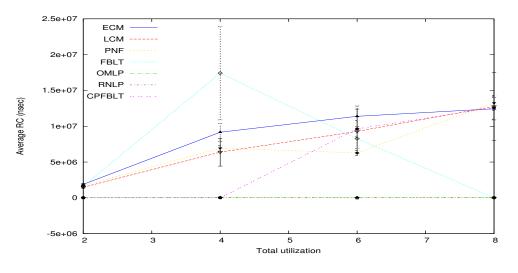

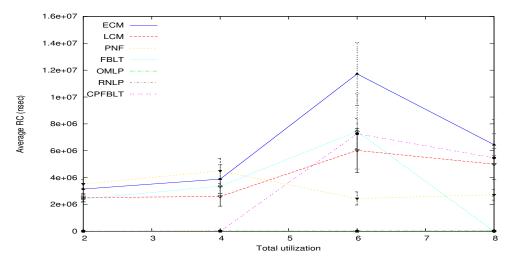

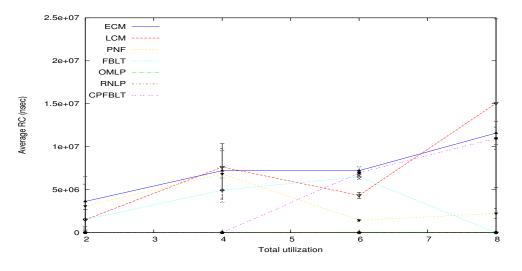

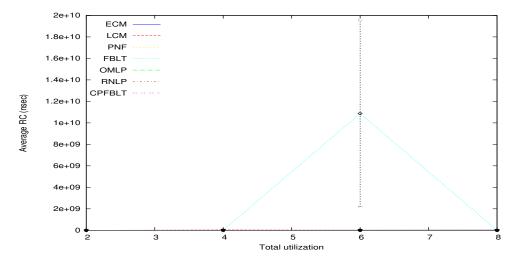

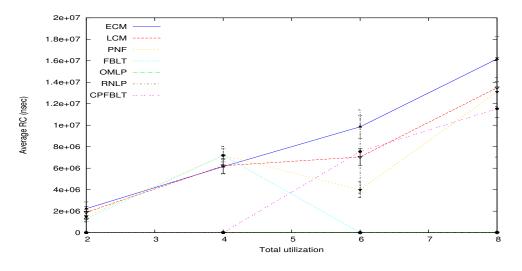

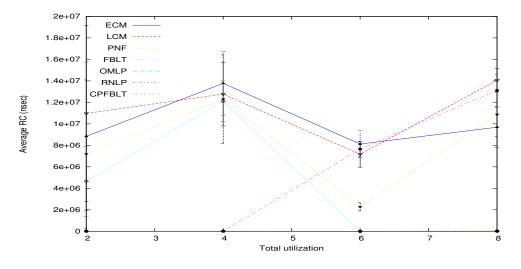

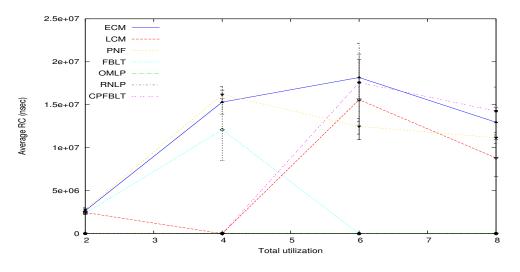

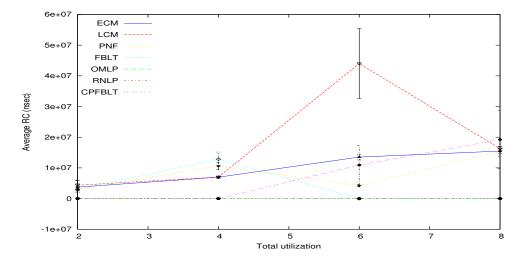

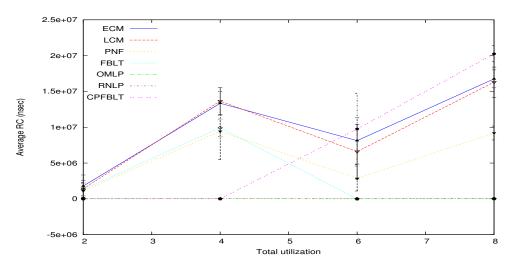

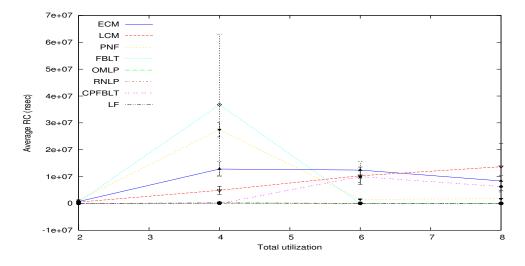

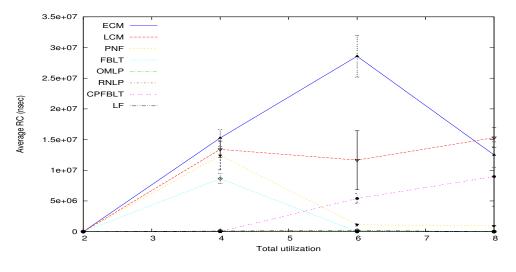

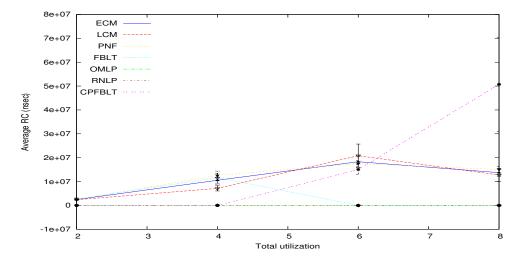

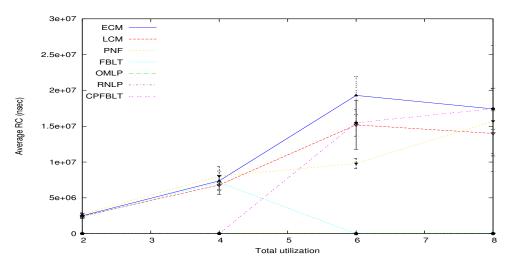

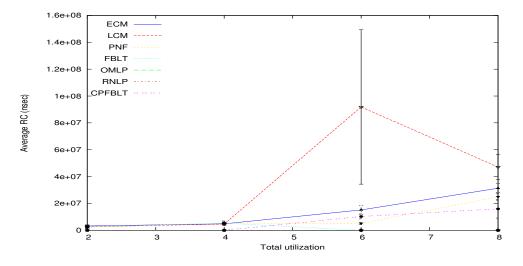

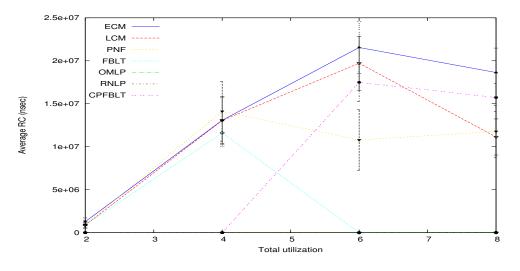

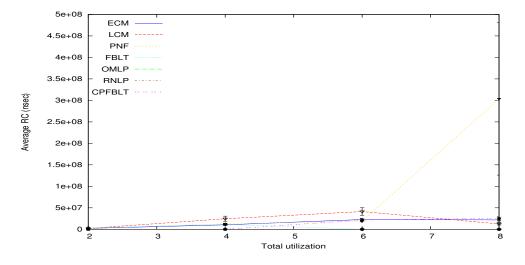

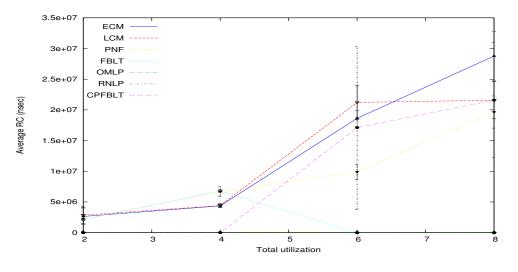

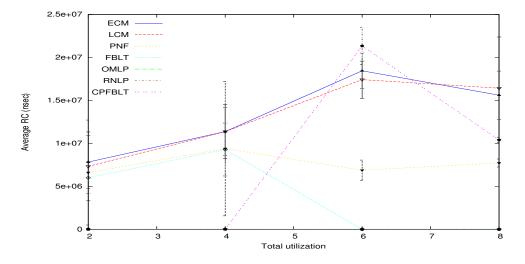

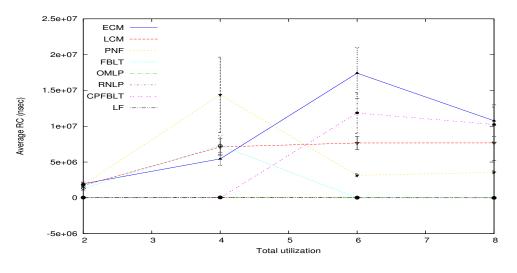

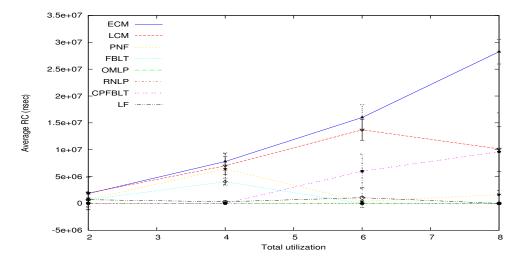

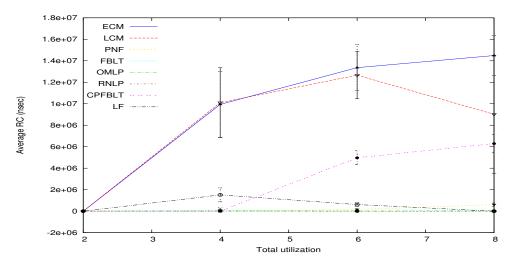

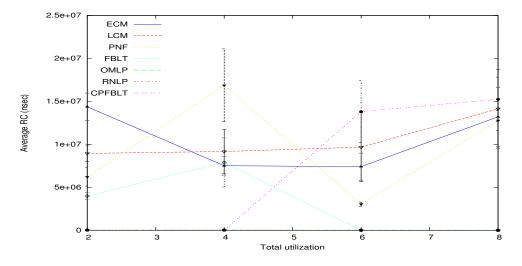

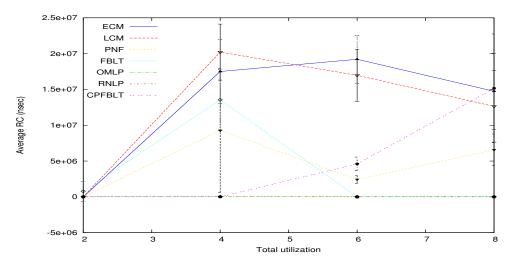

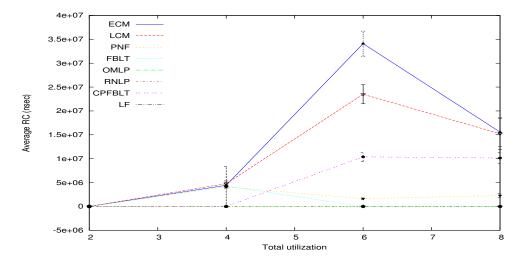

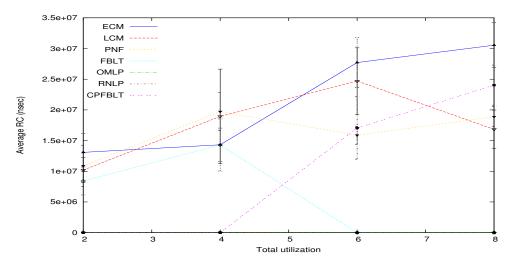

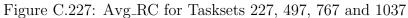

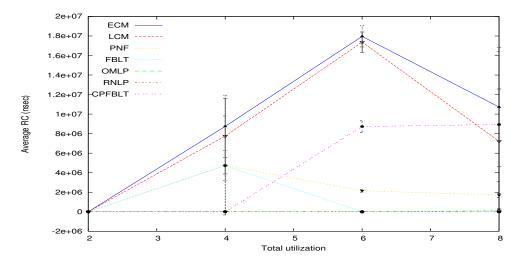

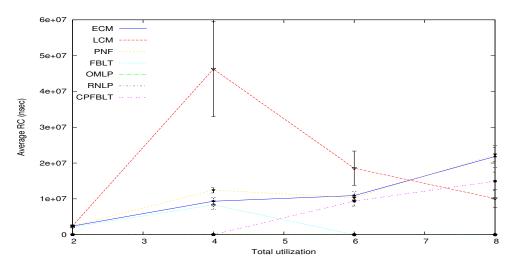

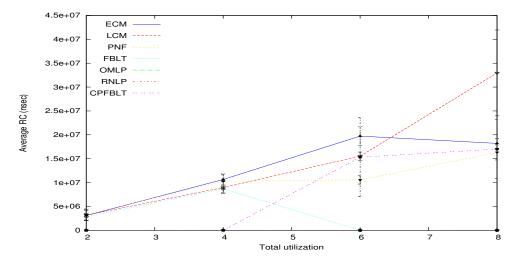

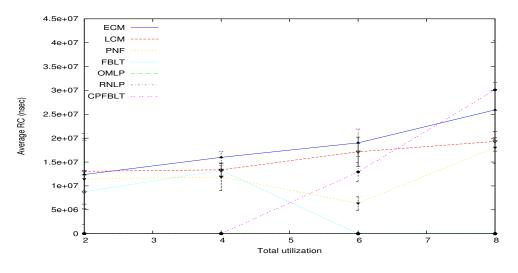

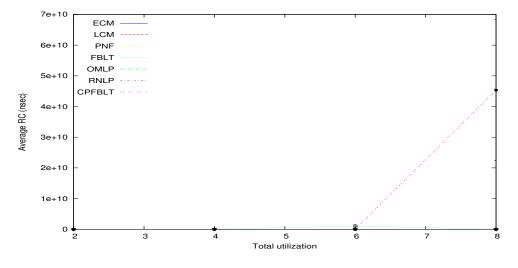

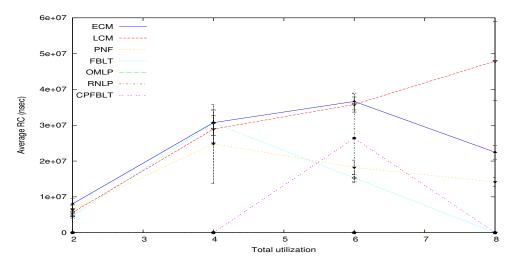

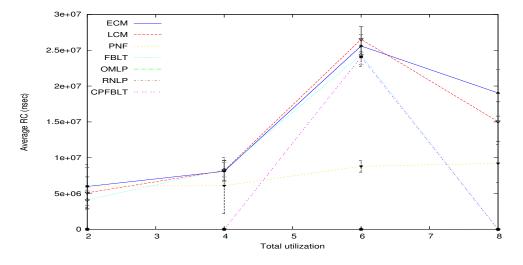

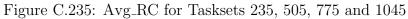

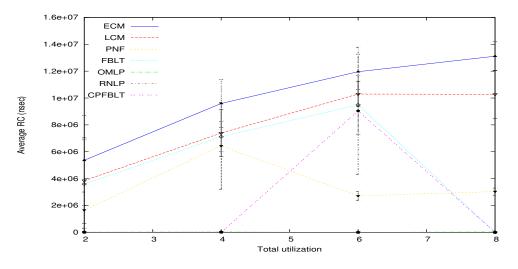

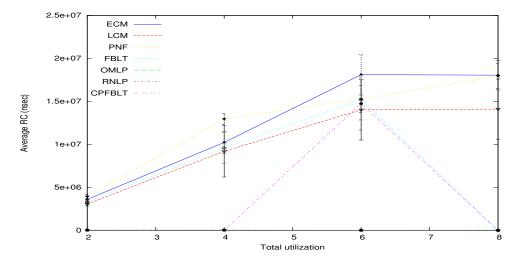

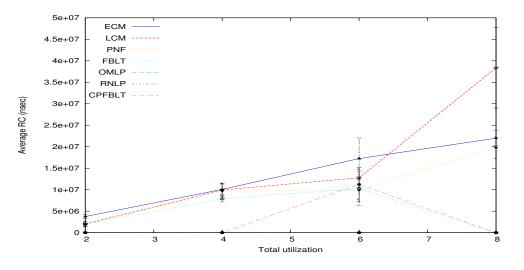

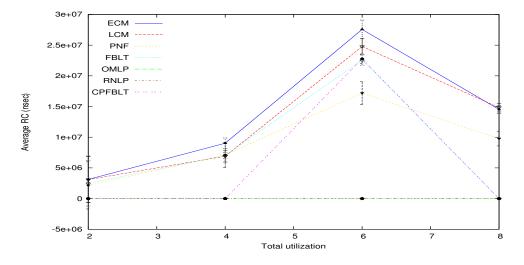

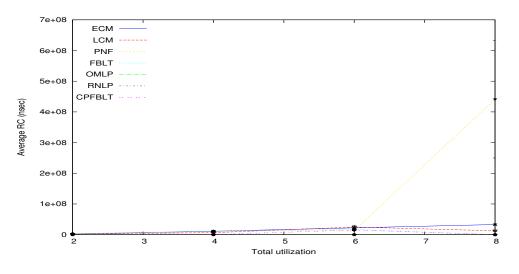

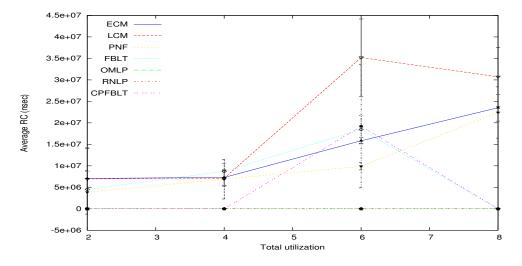

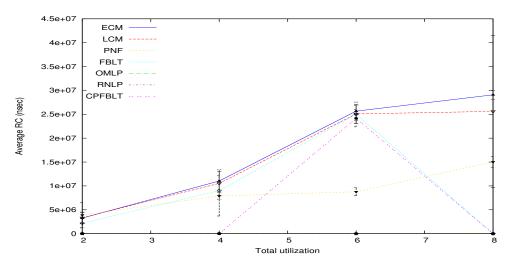

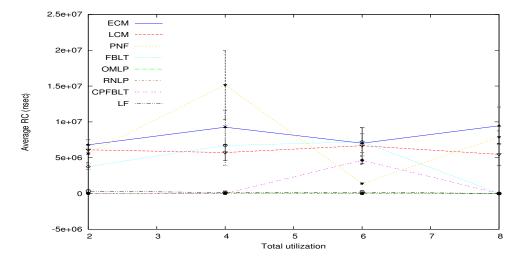

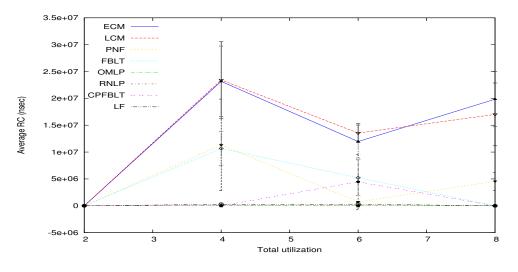

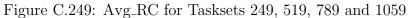

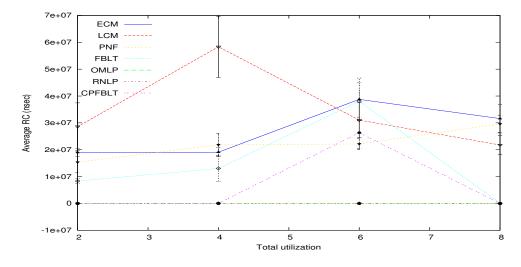

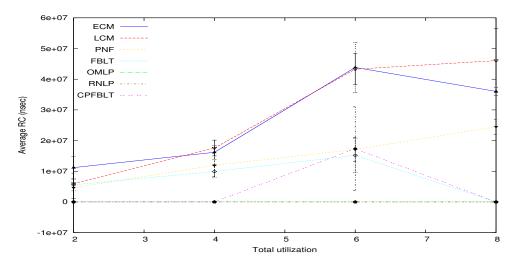

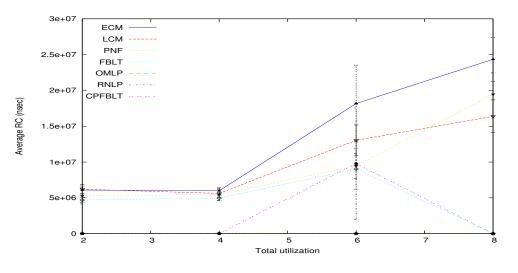

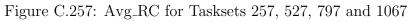

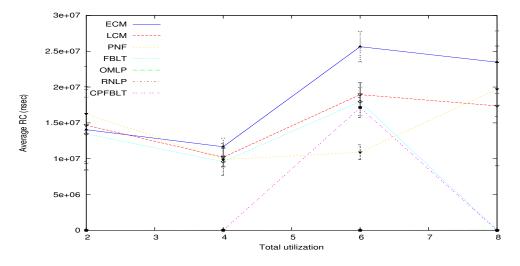

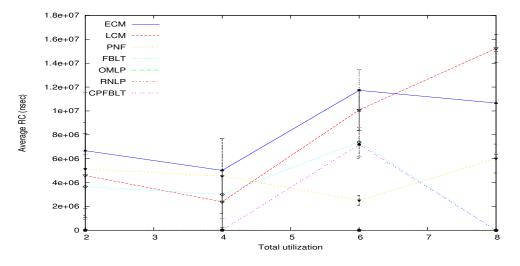

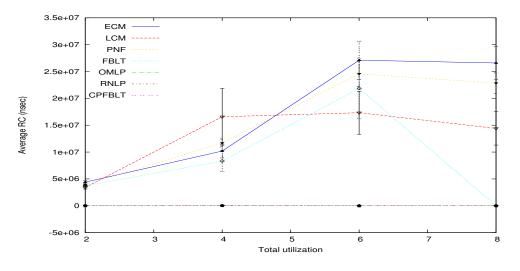

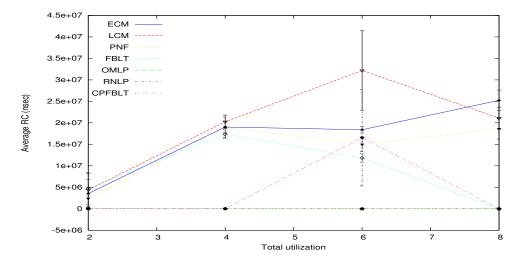

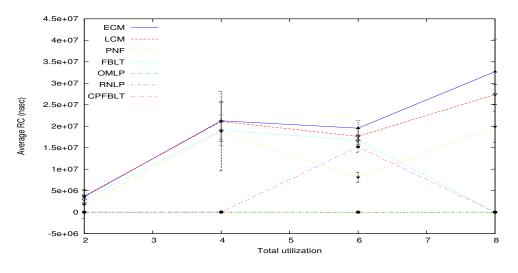

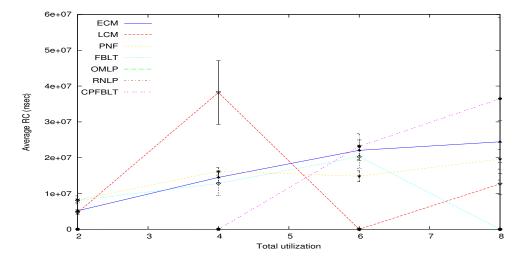

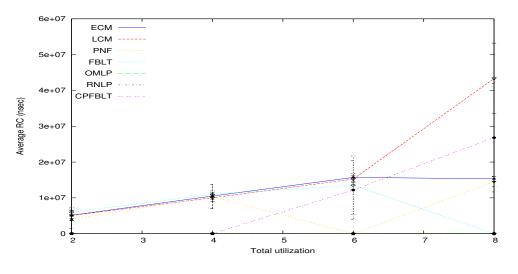

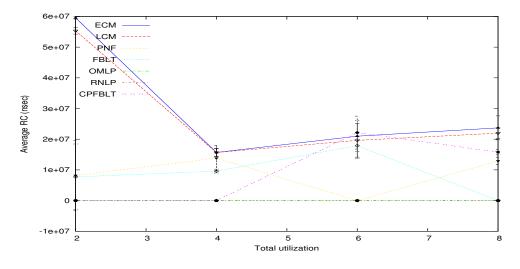

|    |      | 9.4.2 General results for Avg_RC                                                                                                                  |

|    | 9.5  | Results Summary                                                                                                                                   |

| 10 | Qua  | tative Comparison Between STM, Locking Protocols and Lock-Free138                                                                                 |

|    | 10.1 | Compositionality                                                                                                                                  |

|    | 10.2 | Priority Inversion                                                                                                                                |

|    | 10.3 | Nesting                                                                                                                                           |

|    | 10.4 Convoying                                         | 140 |

|----|--------------------------------------------------------|-----|

|    | 10.5 Deadlock and Livelock                             | 141 |

|    | 10.6 Platform Dependence and Implementation Complexity | 142 |

|    | 10.7 Transparency                                      | 142 |

|    | 10.8 Upper Bounds Complexity                           | 143 |

|    | 10.9 Memory                                            | 144 |

|    | 10.10Conclusion                                        | 146 |

| 11 | Conclusions and Future Work                            | 147 |

|    | 11.1 Conclusions                                       | 147 |

|    | 11.2 Future Work                                       | 151 |

| Bi | bliography                                             | 152 |

| Α  | Tasksets' Properties                                   | 166 |

| в  | Complete Deadline Satisfaction Results                 | 194 |

| С  | Complete Average Retry Cost Results                    | 330 |

# List of Figures

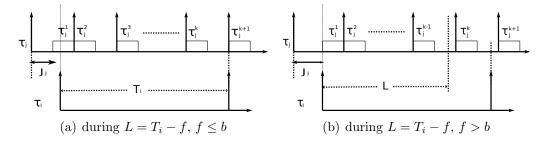

| 4.1  | Maximum interference of jobs of $\tau_j$ to $\tau_i^x$ running on different processors, under G-EDF. $T_i = aT_j + b$ | 34  |

|------|-----------------------------------------------------------------------------------------------------------------------|-----|

| 4.9  |                                                                                                                       |     |

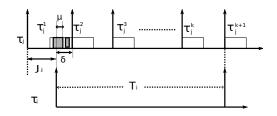

| 4.2  | Effect of carried_in job of $\tau_j$ to retry cost of transactions in $\tau_i$                                        | 37  |

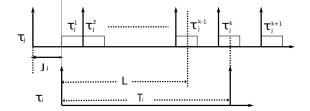

| 4.3  | Max interference of $\tau_j$ to $\tau_i$ in G-RMA                                                                     | 41  |

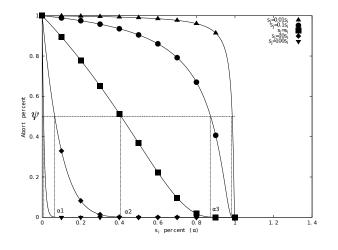

| 5.1  | Interference of $s_i^k$ by various lengths of $s_j^l$                                                                 | 55  |

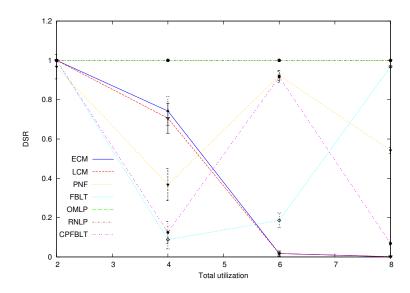

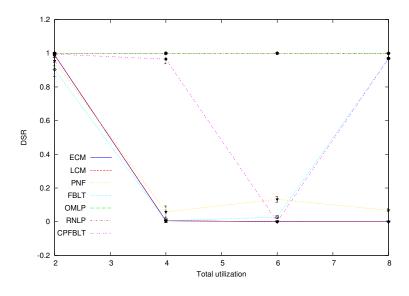

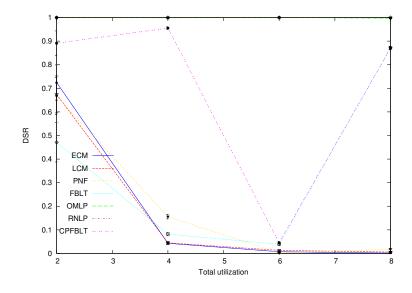

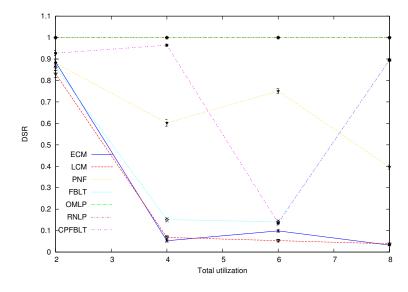

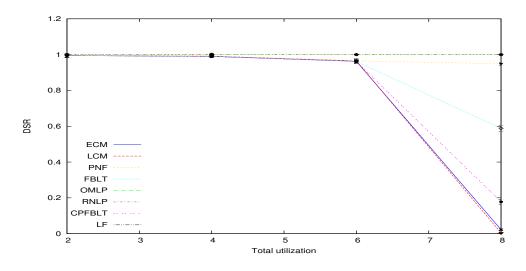

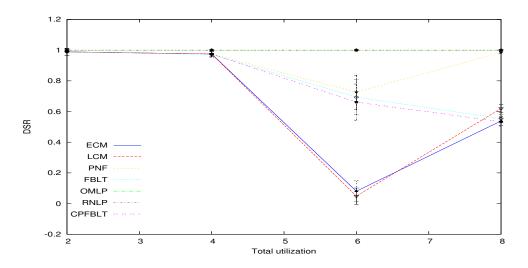

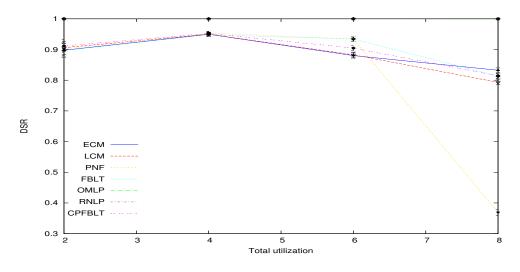

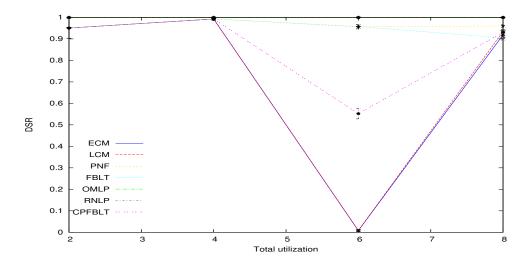

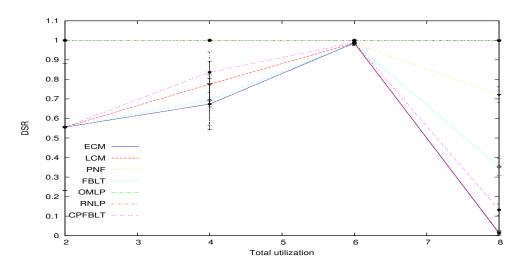

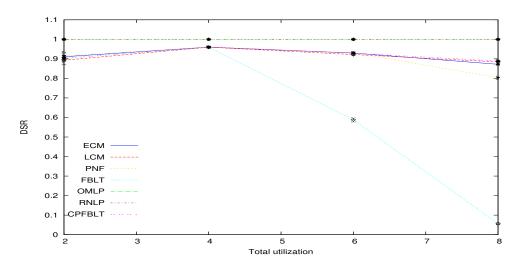

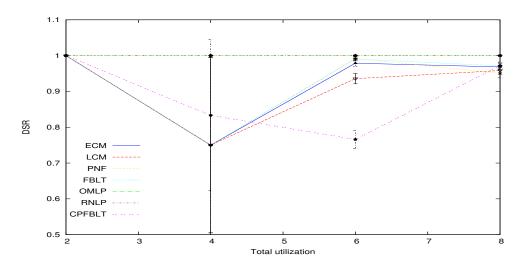

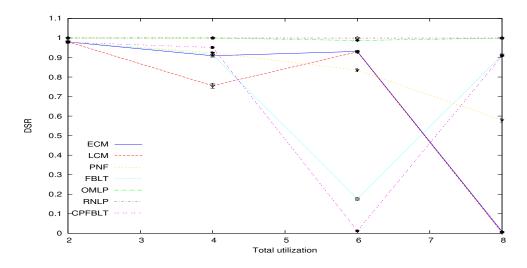

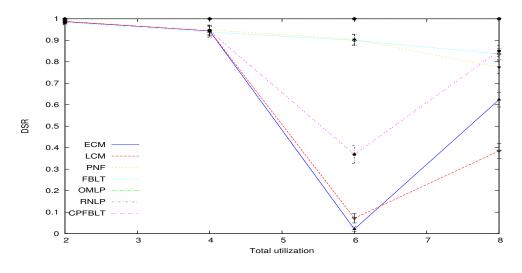

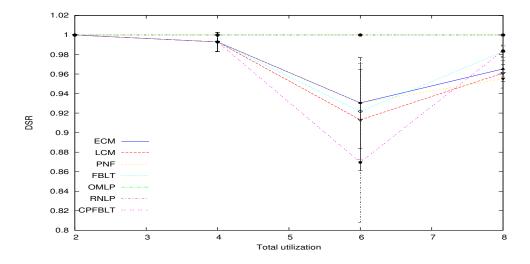

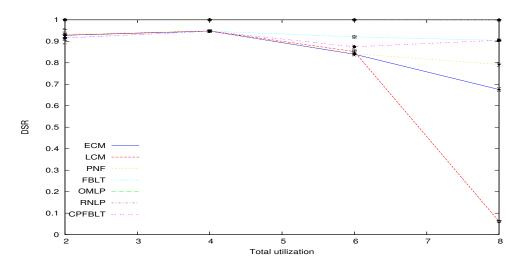

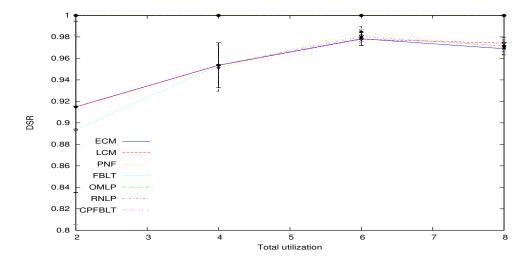

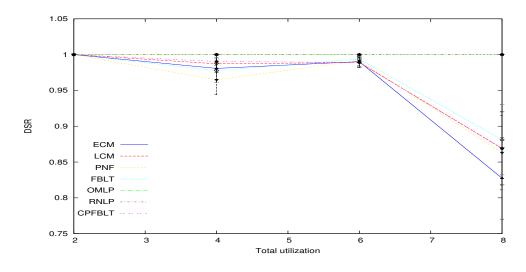

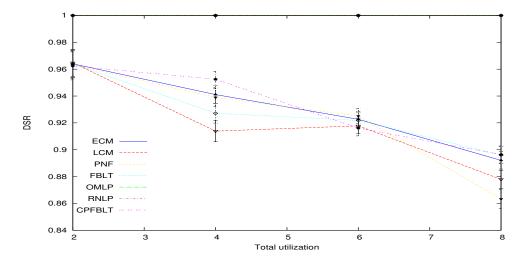

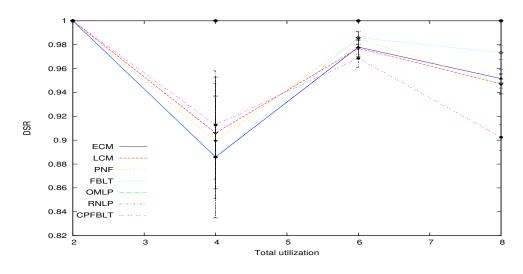

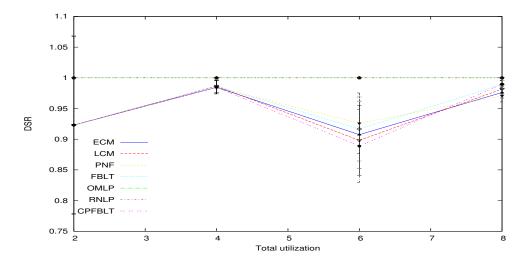

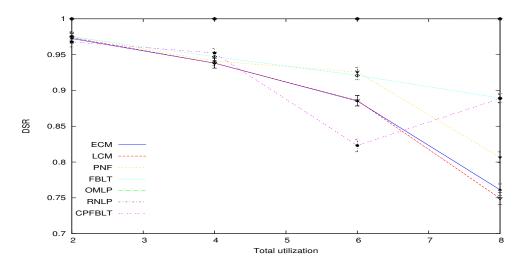

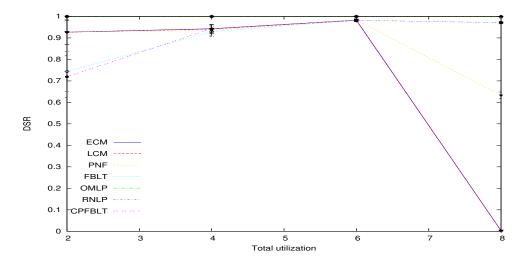

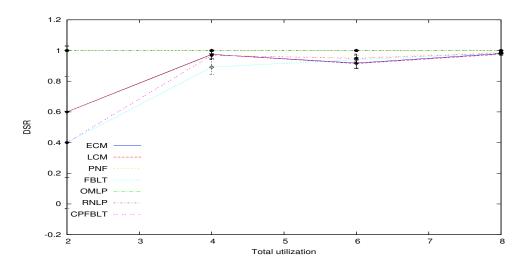

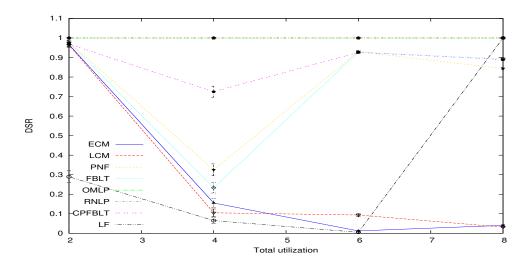

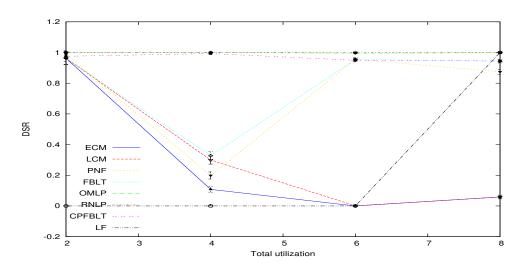

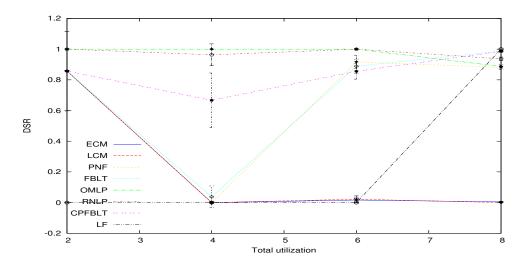

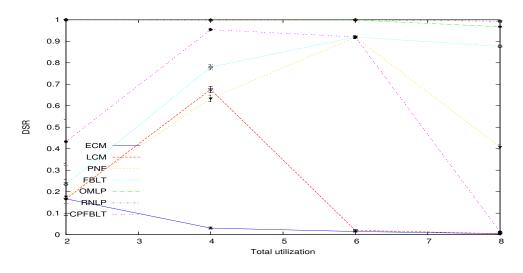

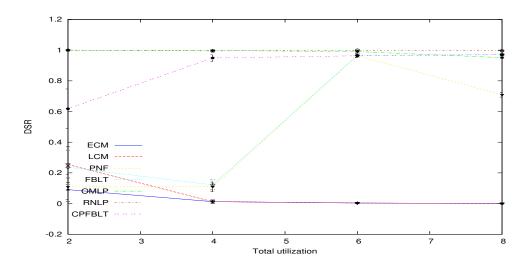

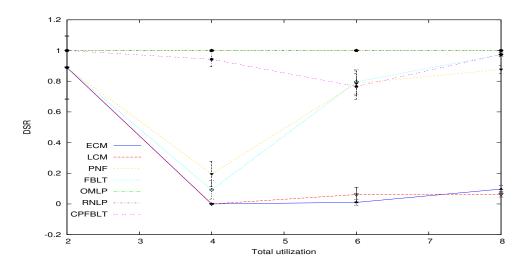

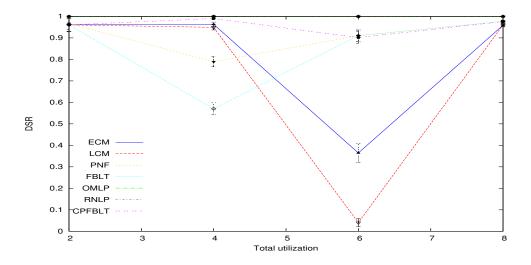

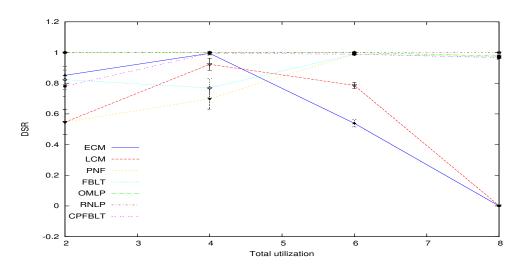

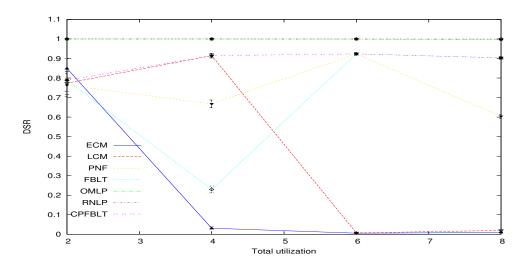

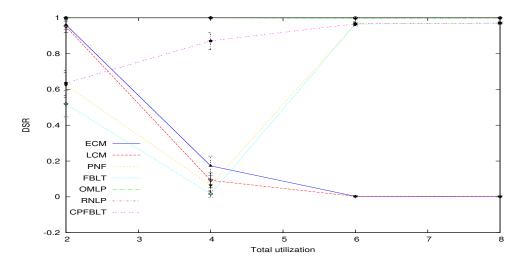

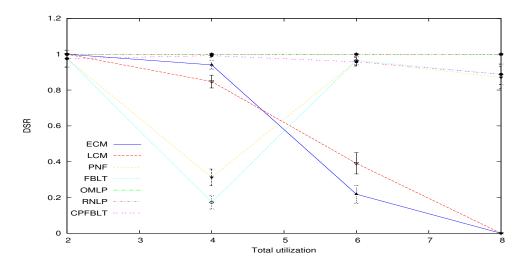

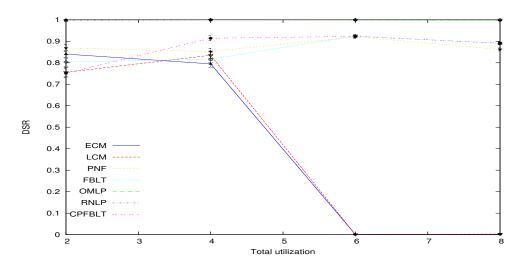

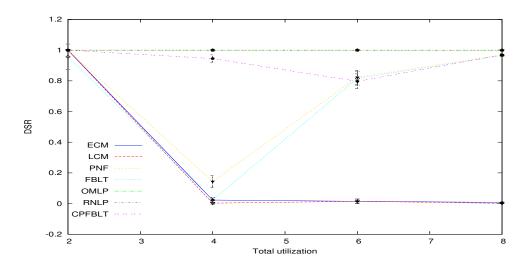

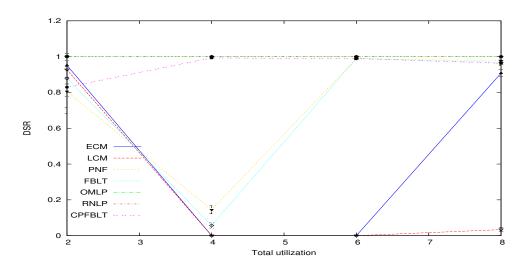

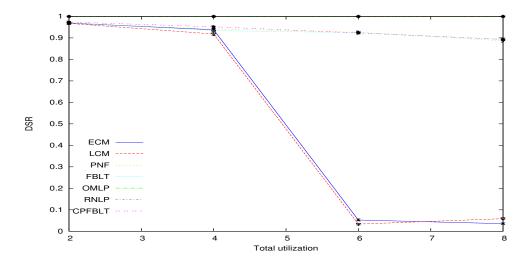

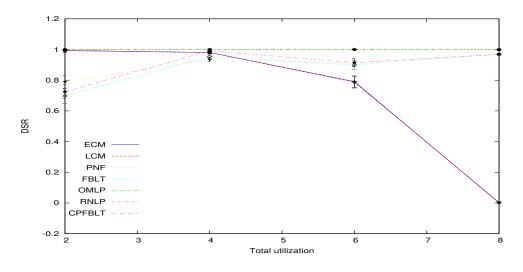

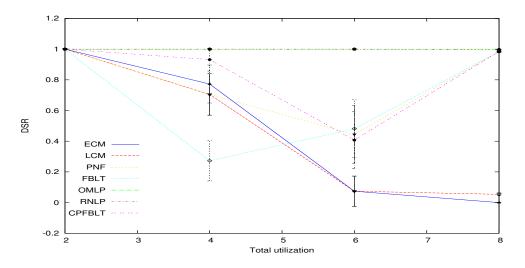

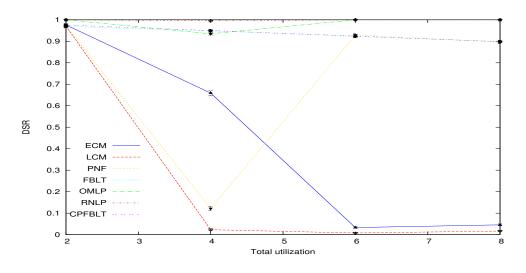

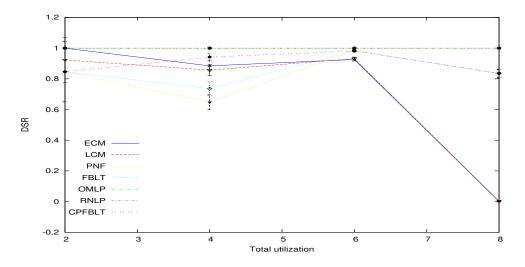

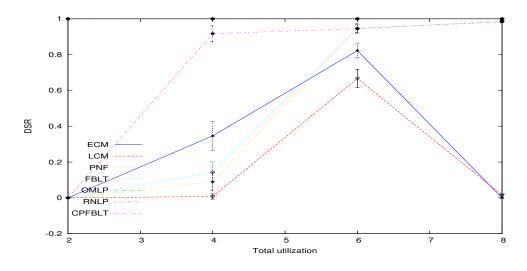

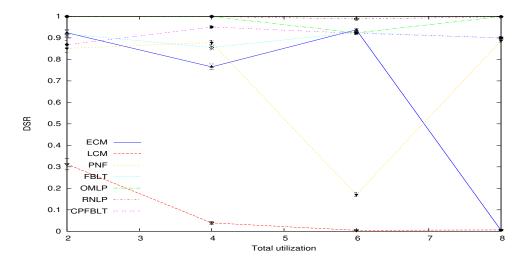

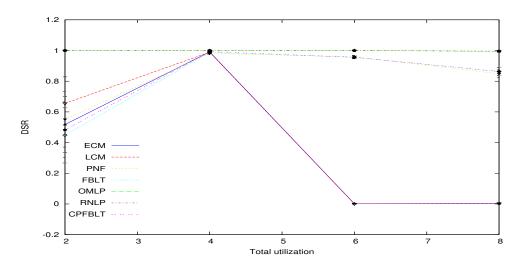

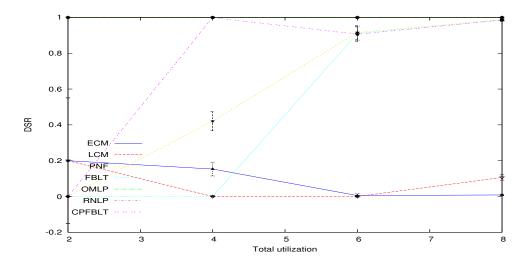

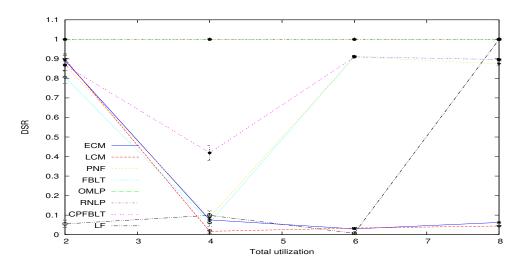

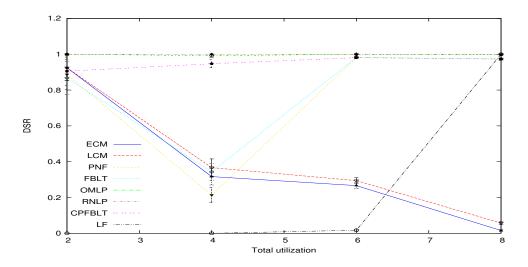

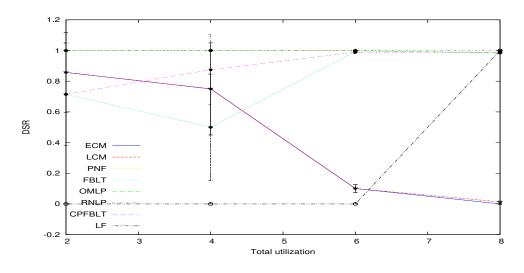

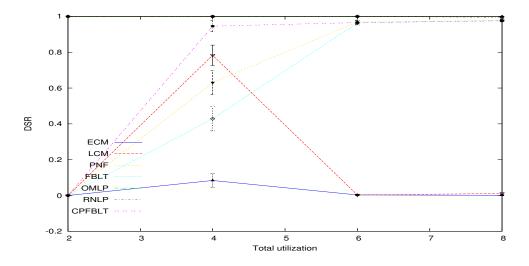

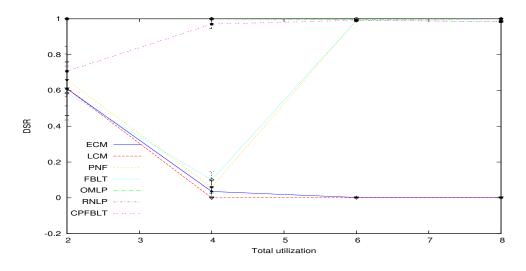

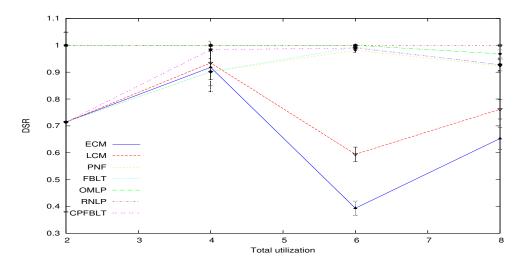

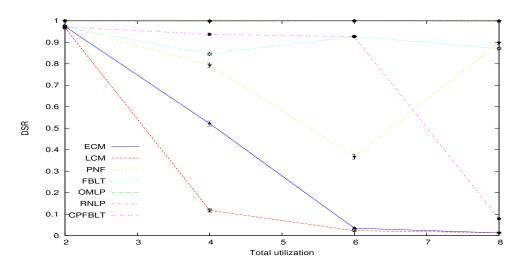

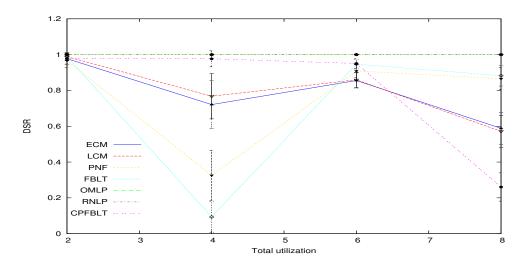

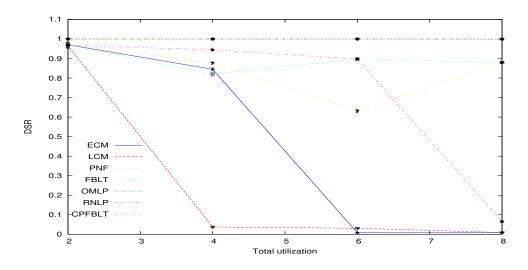

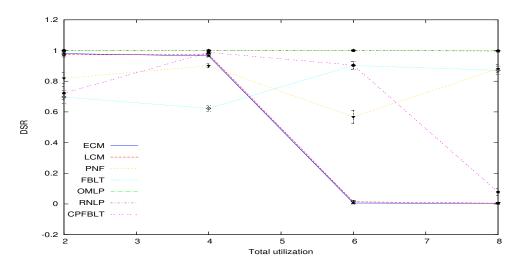

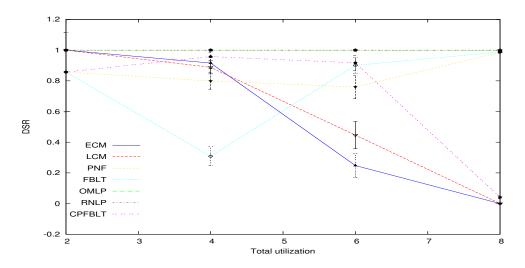

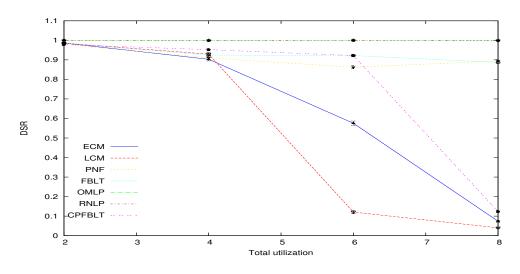

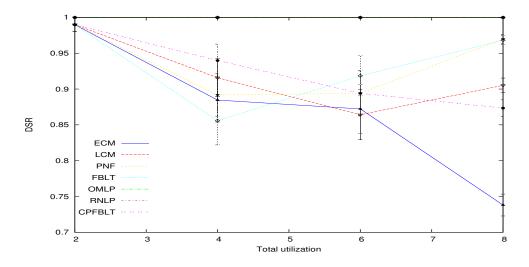

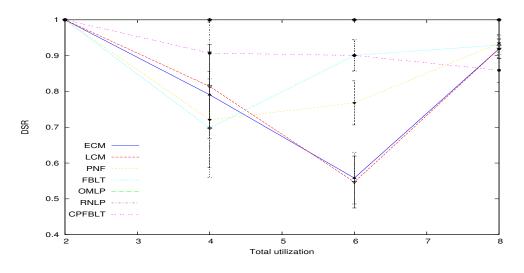

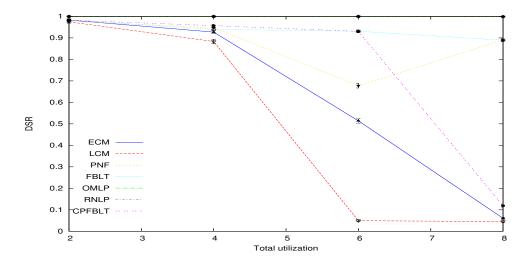

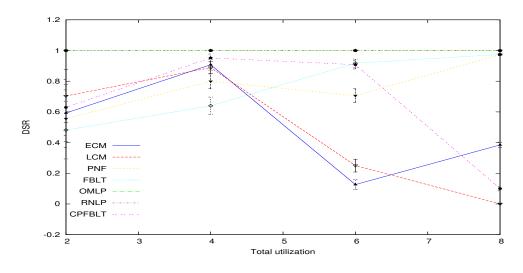

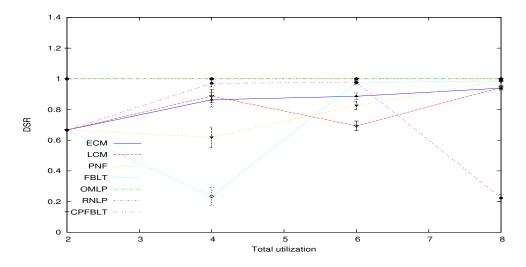

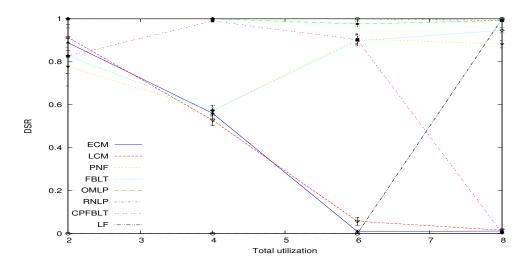

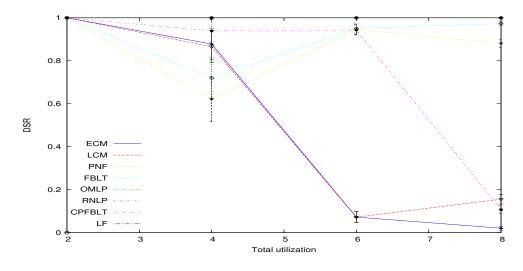

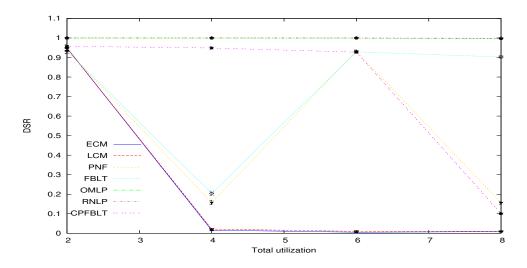

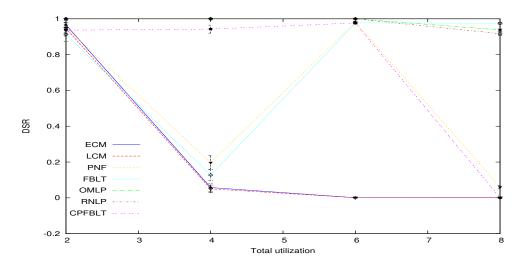

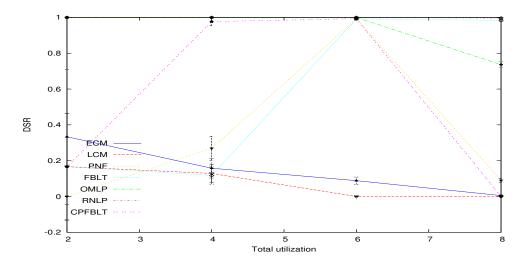

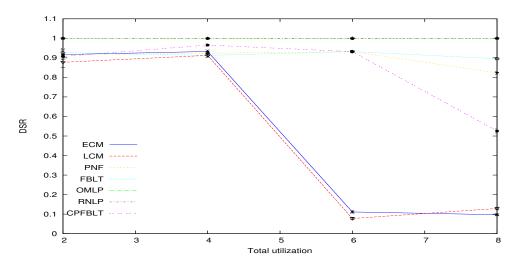

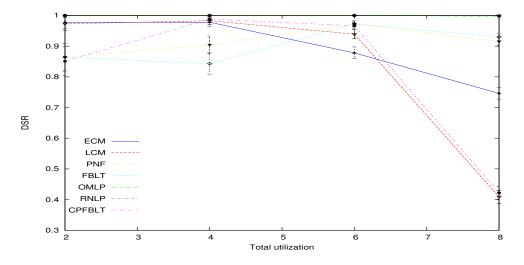

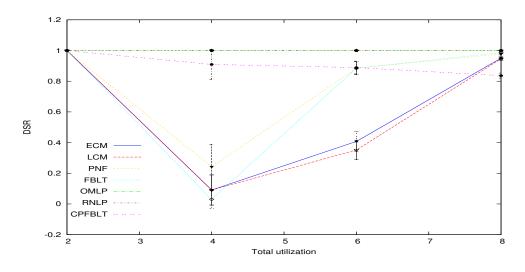

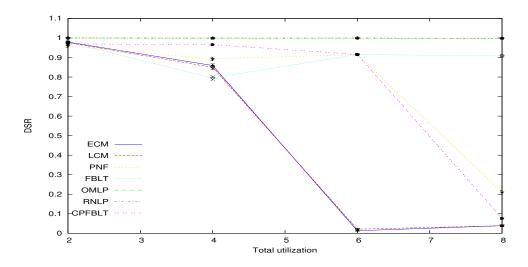

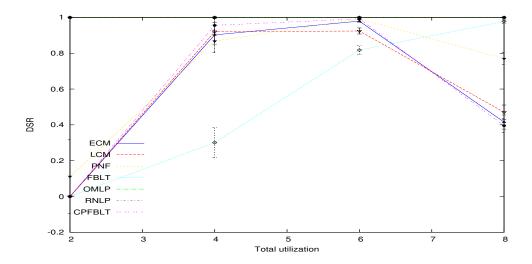

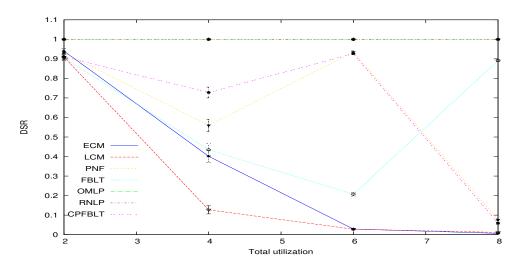

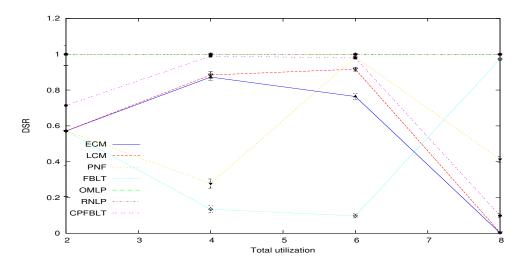

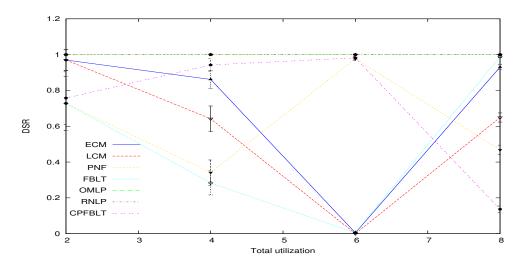

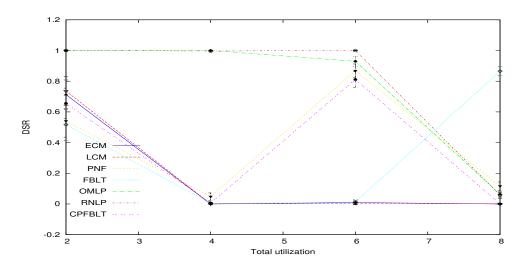

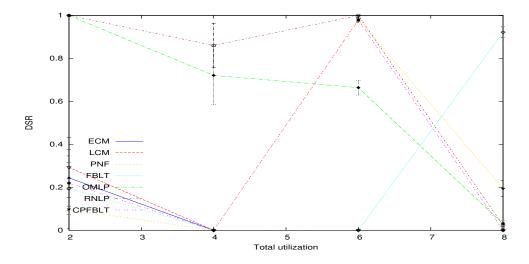

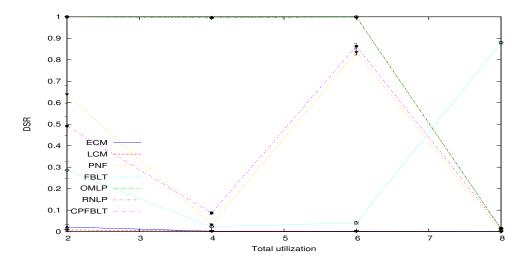

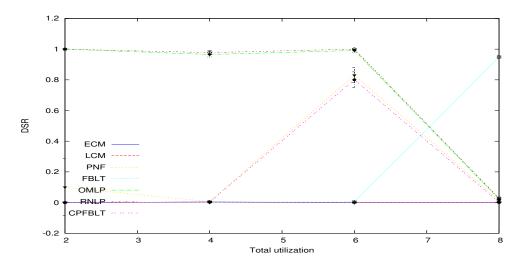

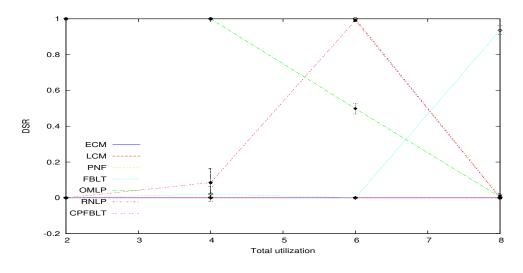

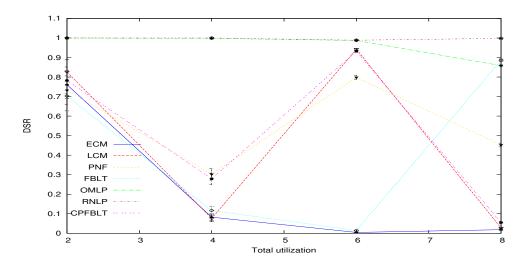

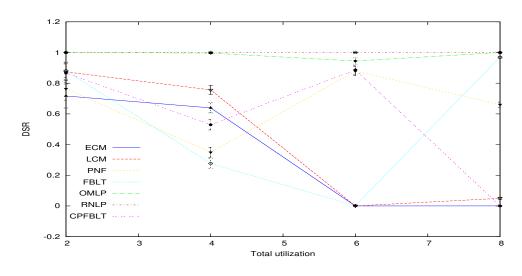

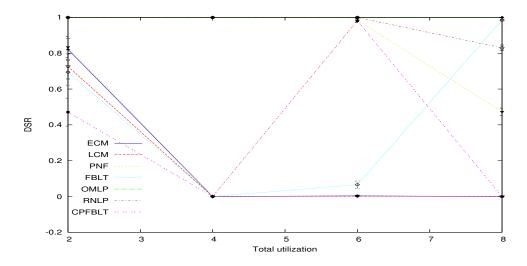

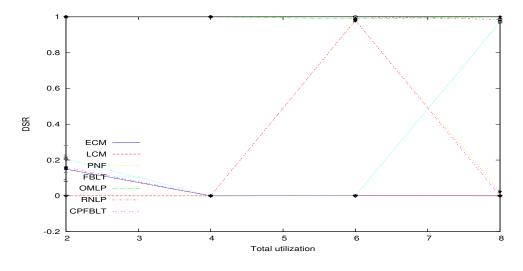

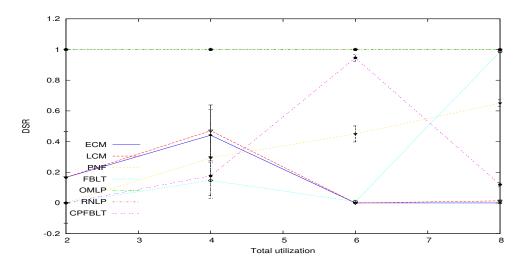

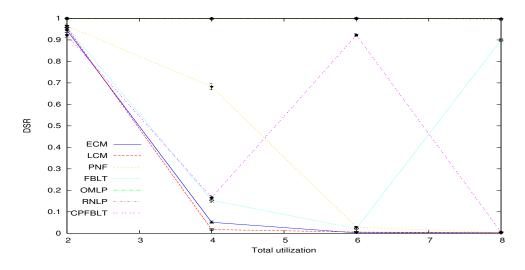

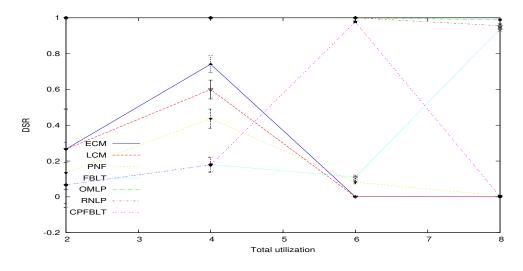

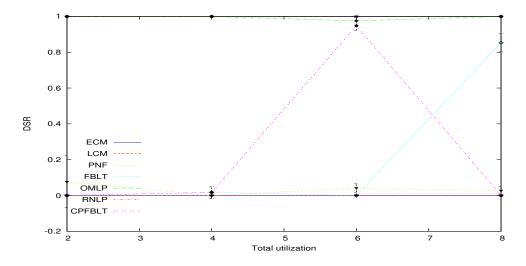

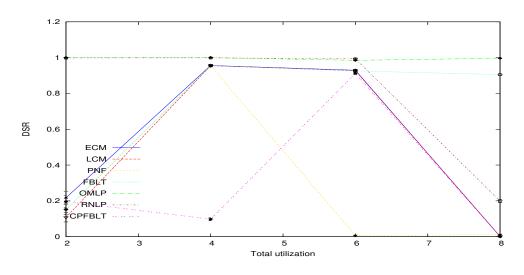

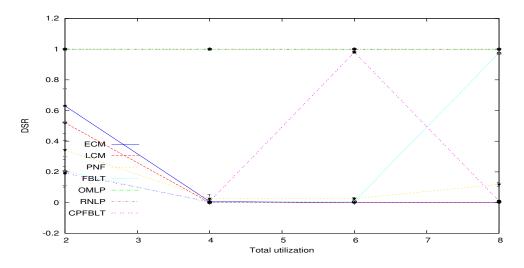

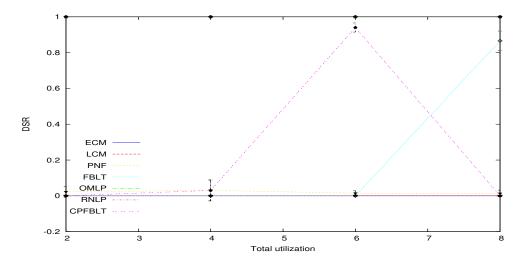

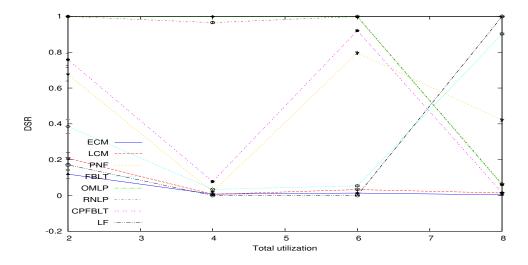

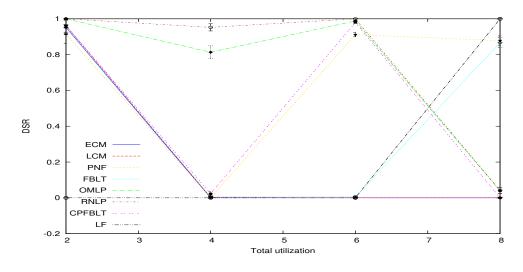

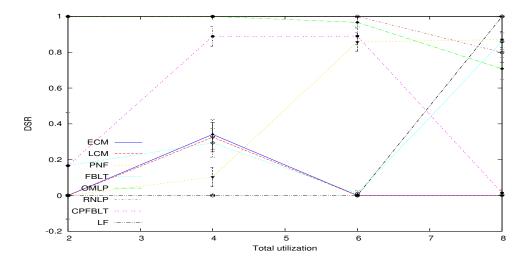

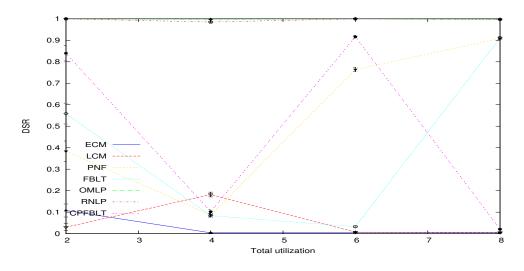

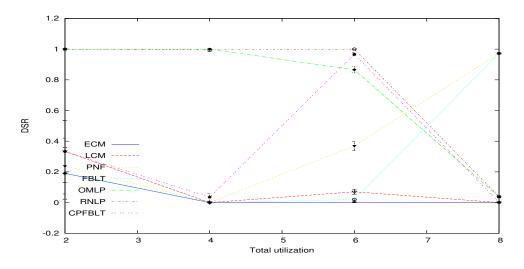

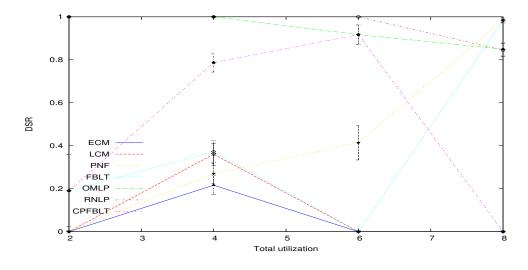

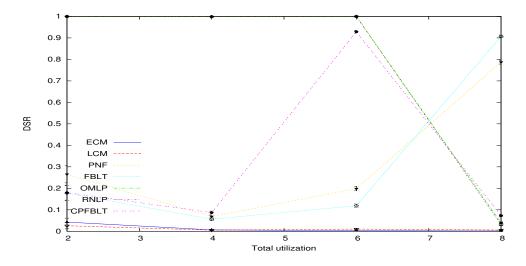

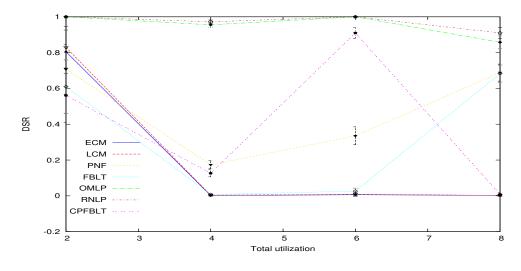

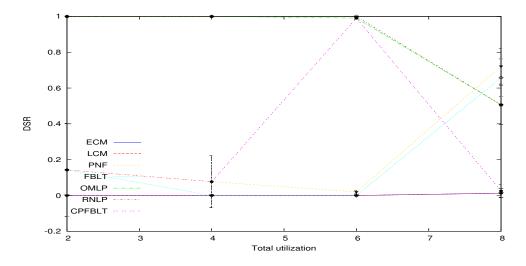

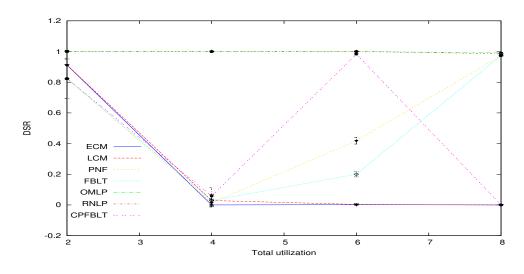

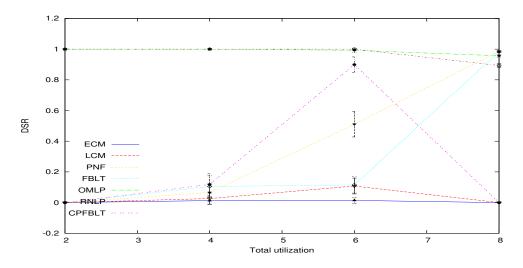

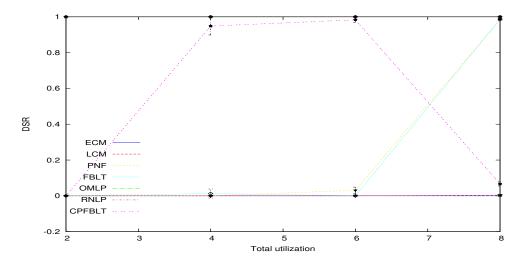

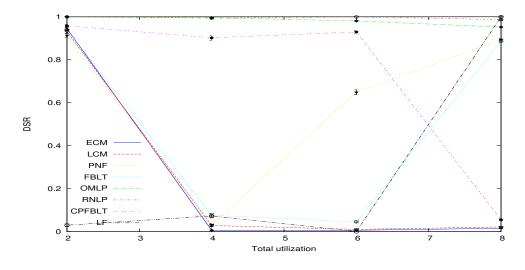

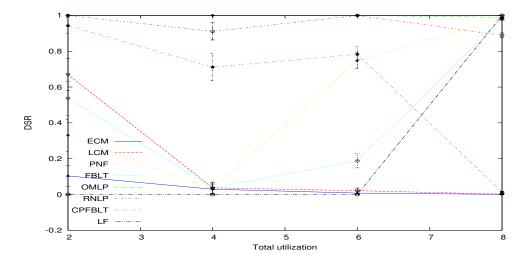

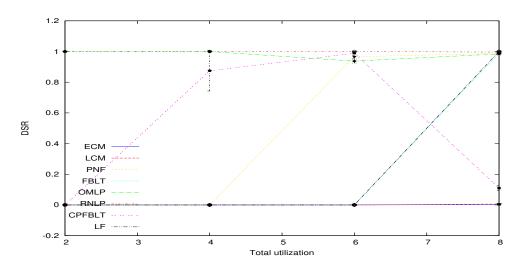

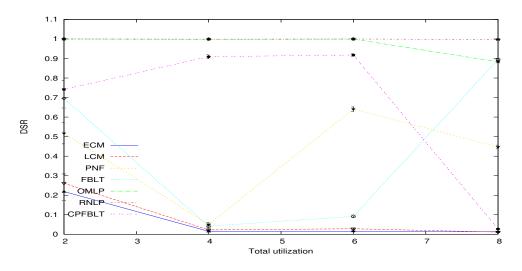

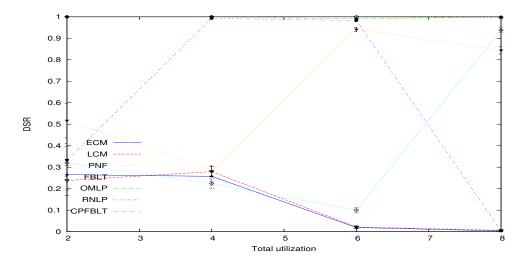

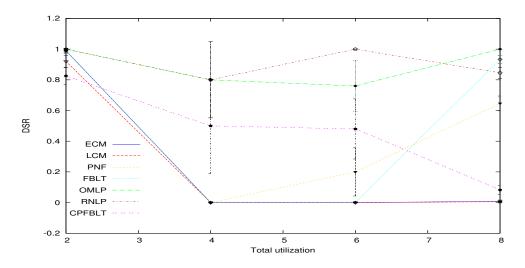

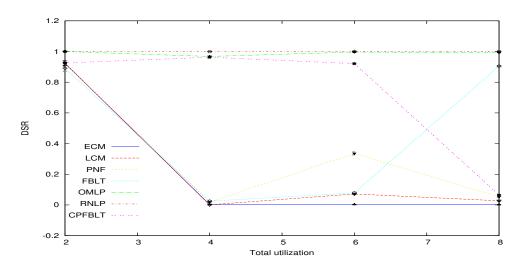

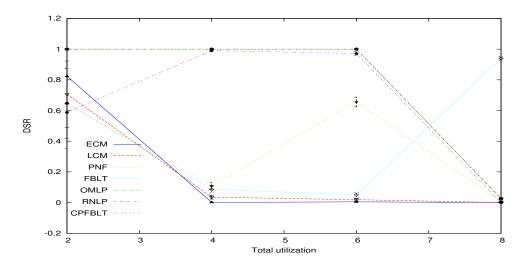

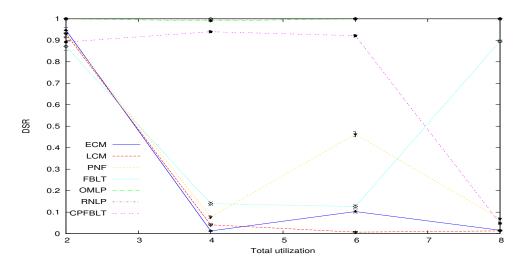

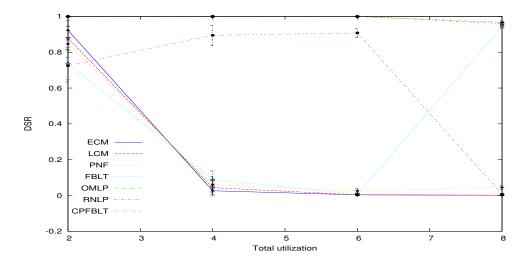

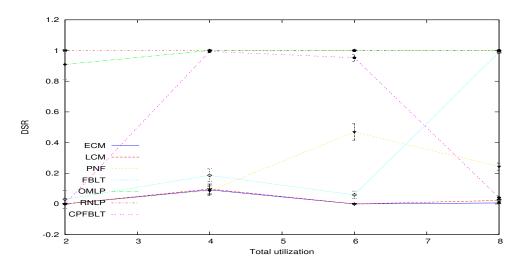

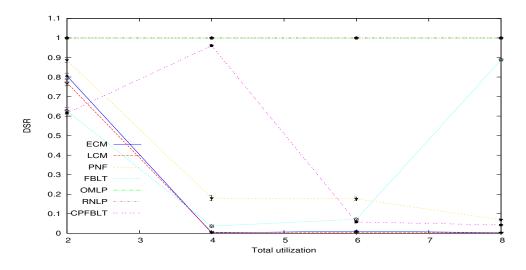

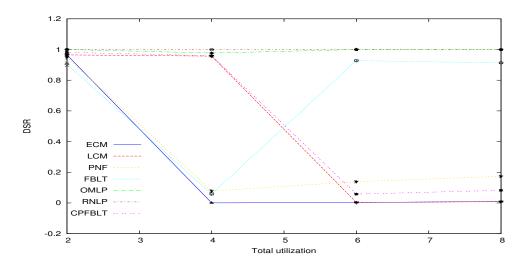

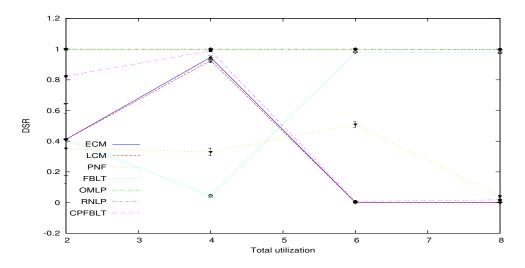

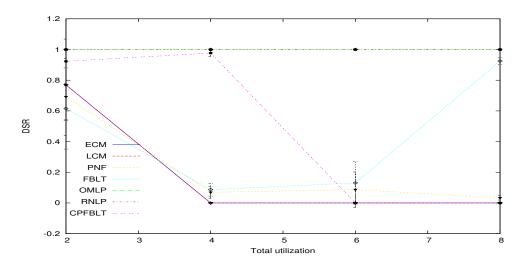

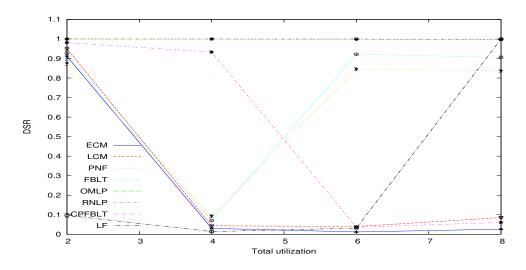

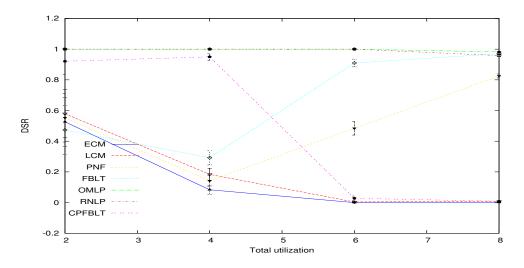

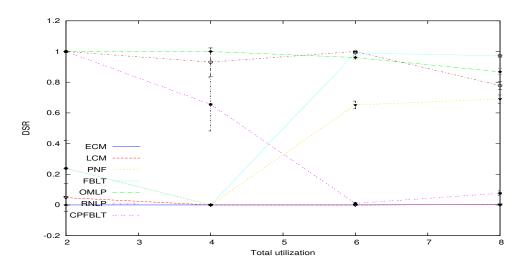

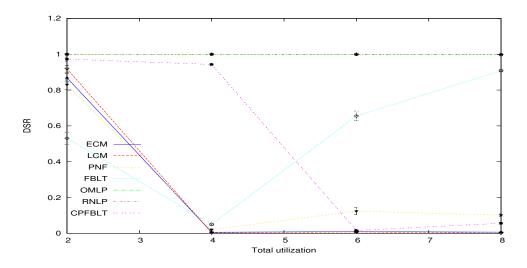

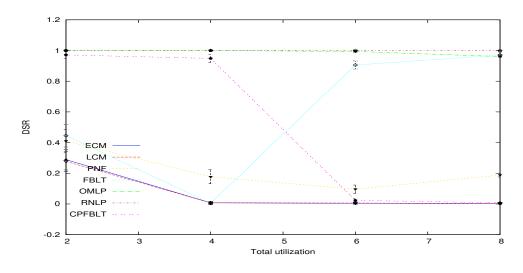

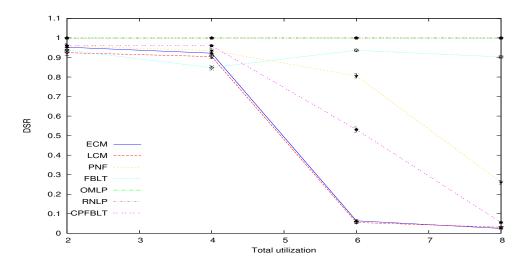

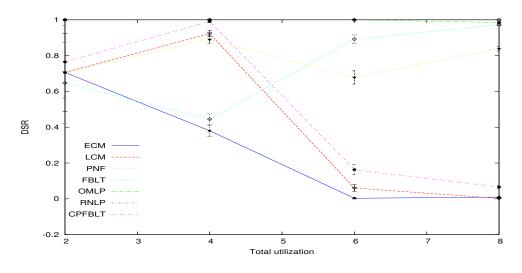

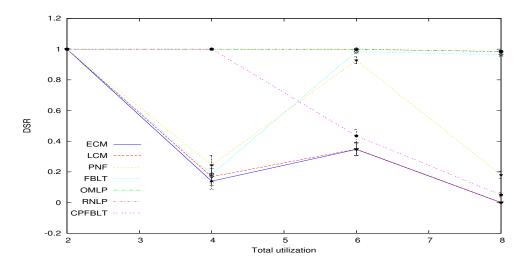

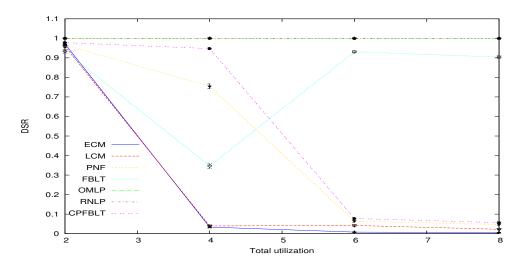

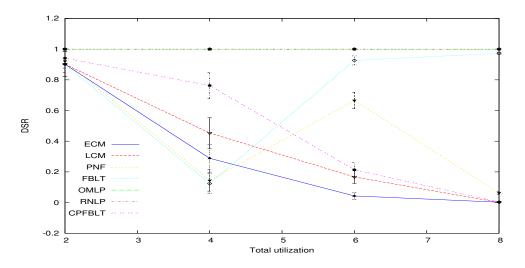

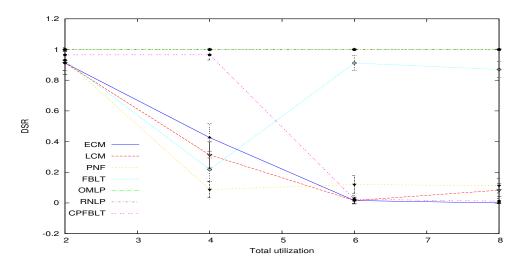

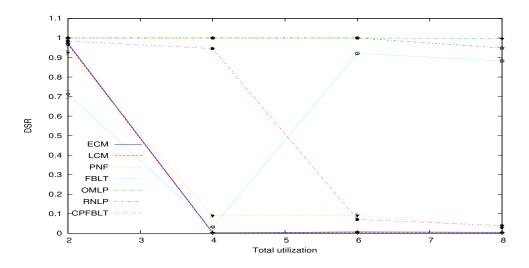

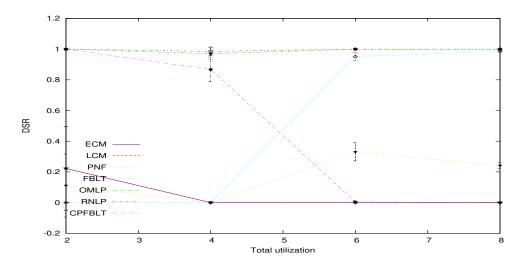

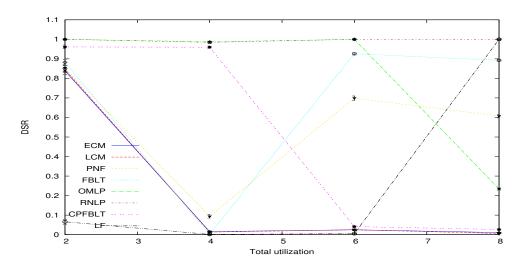

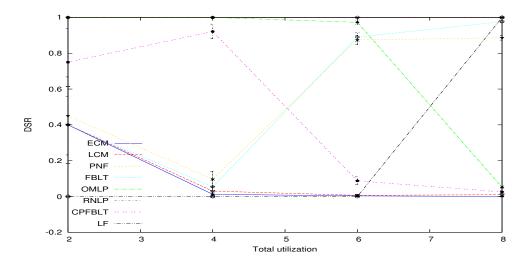

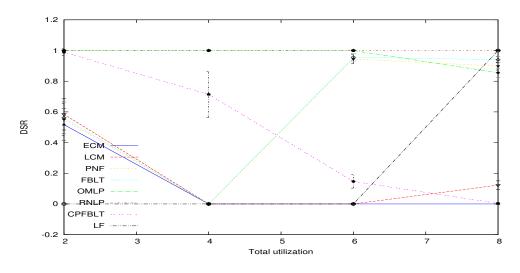

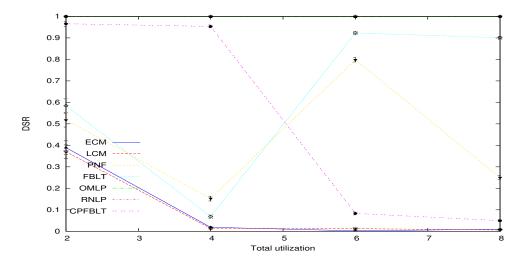

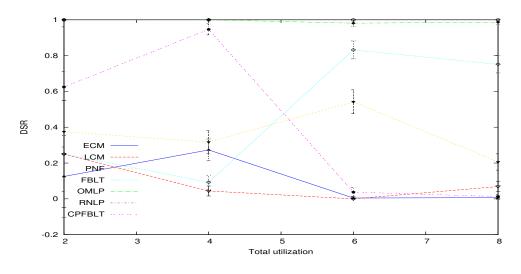

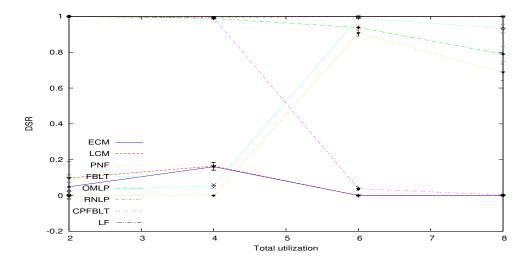

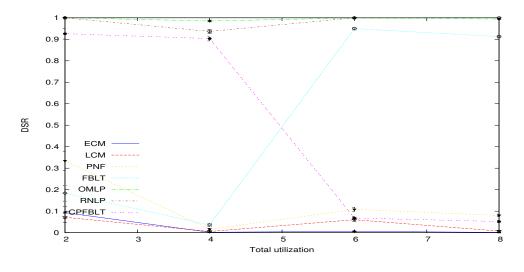

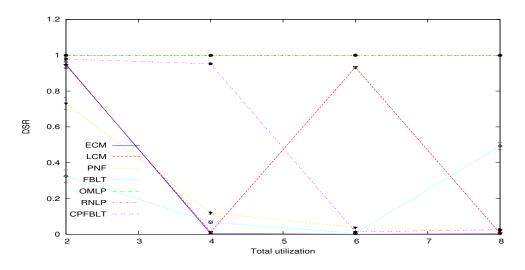

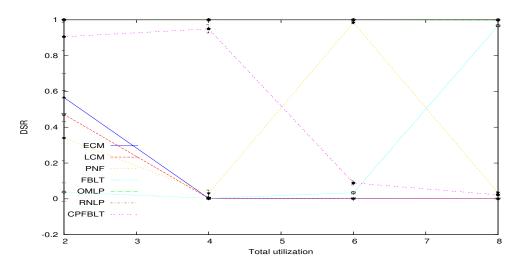

| 9.1  | DSR for Tasksets 2, 542, 1082 and 1622                                                                                | 115 |

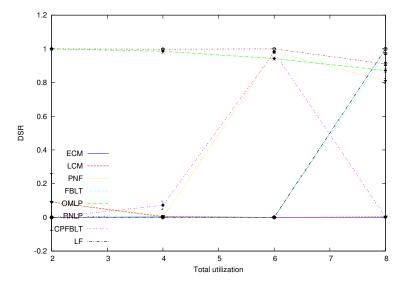

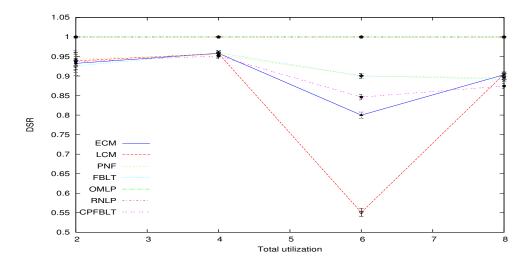

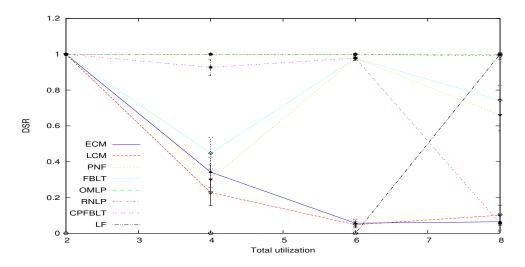

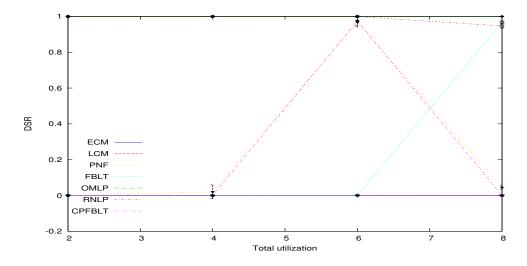

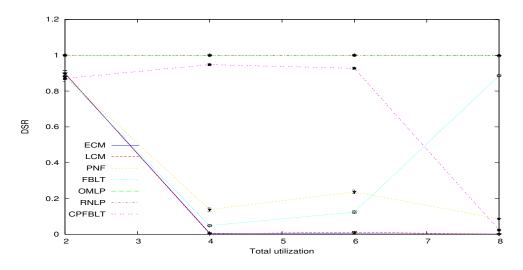

| 9.2  | DSR for Tasksets 28, 568, 1108 and 1648                                                                               | 116 |

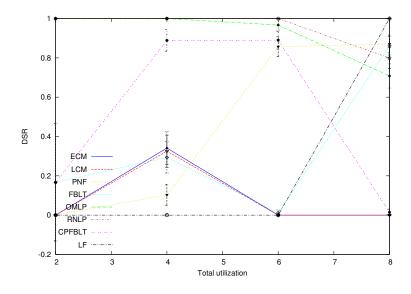

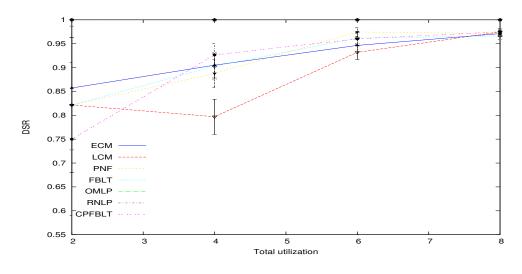

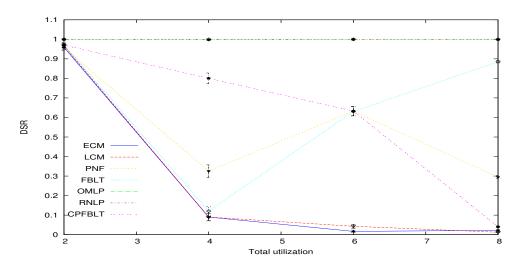

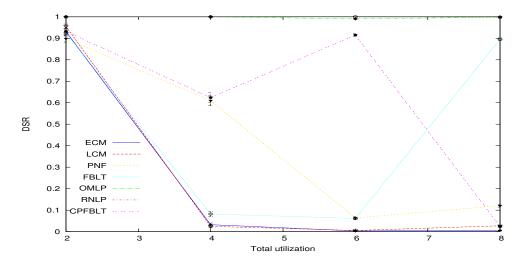

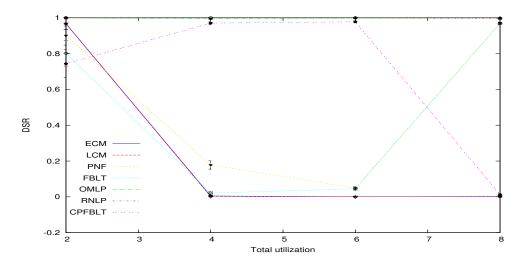

| 9.3  | DSR for Tasksets 38, 578, 1118 and 1658                                                                               | 116 |

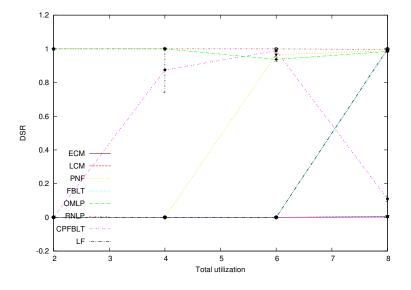

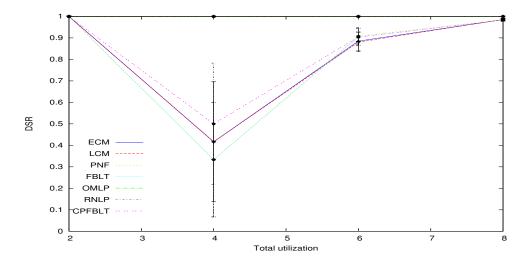

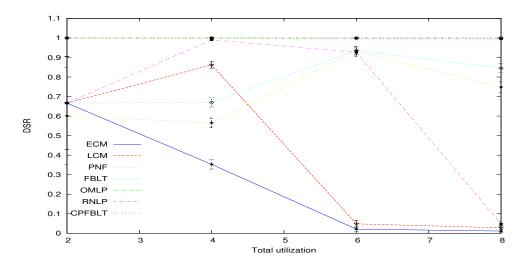

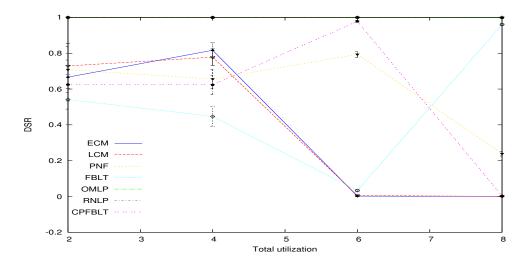

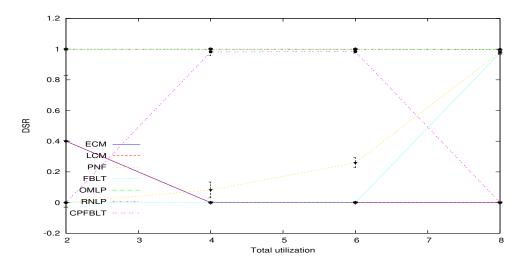

| 9.4  | DSR for Tasksets 55, 595, 1135 and 1675                                                                               | 117 |

| 9.5  | DSR for Tasksets 83, 623, 1163 and 1703                                                                               | 117 |

| 9.6  | DSR for Tasksets 107, 647, 1187 and 1727                                                                              | 118 |

| 9.7  | DSR for Tasksets 110, 650, 1190 and 1730                                                                              | 119 |

| 9.8  | DSR for Tasksets 138, 678, 1218 and 1758                                                                              | 119 |

| 9.9  | DSR for Tasksets 165, 705, 1245 and 1785                                                                              | 120 |

| 9.10 | DSR for Tasksets 233, 773, 1313 and 1853                                                                              | 120 |

| 9.11 | DSR for Tasksets 244, 784, 1324 and 1864                                                                              | 121 |

| 9.12 | DSR for Tasksets 256, 796, 1336 and 1876                                                                              | 121 |

| 9.13 | DSR for Tasksets 262, 802, 1342 and 1882                                                                              | 122 |

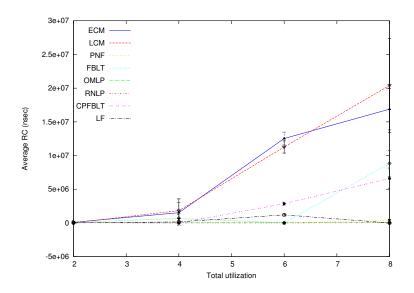

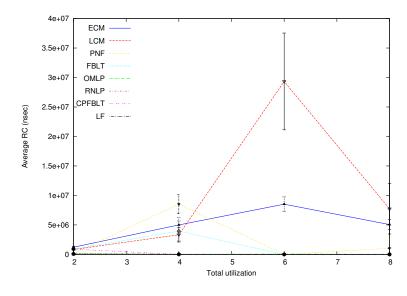

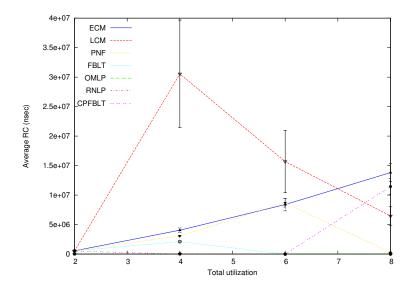

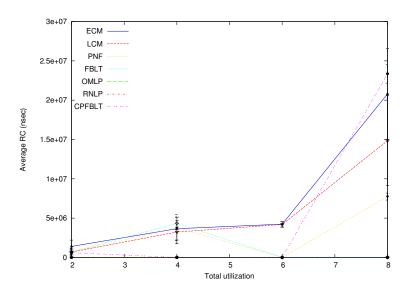

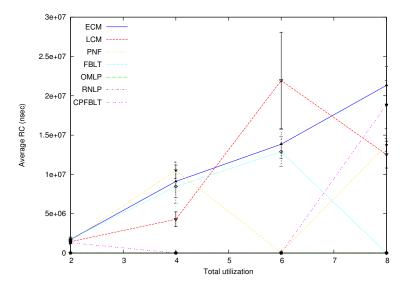

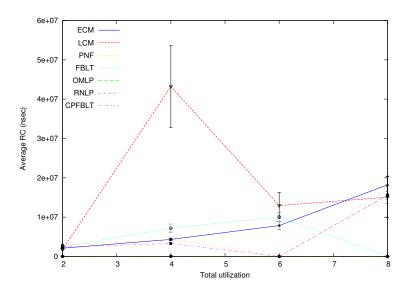

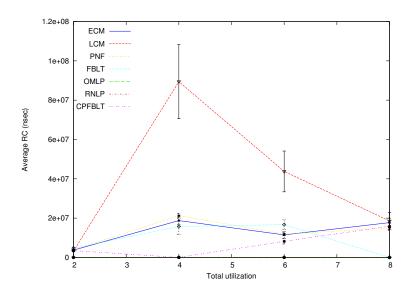

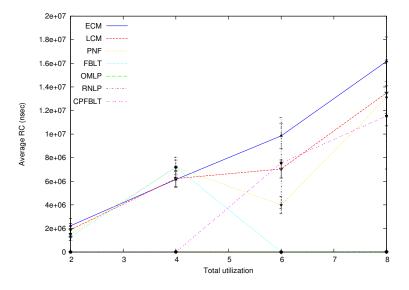

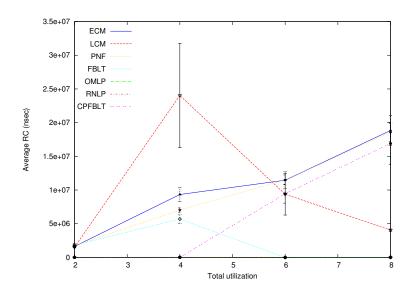

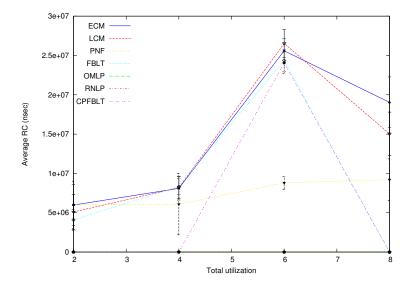

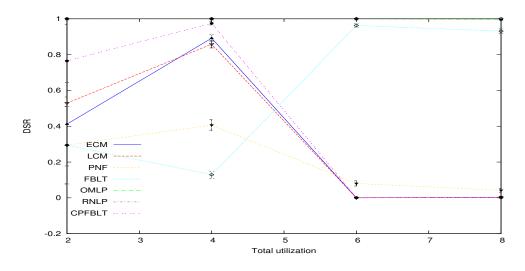

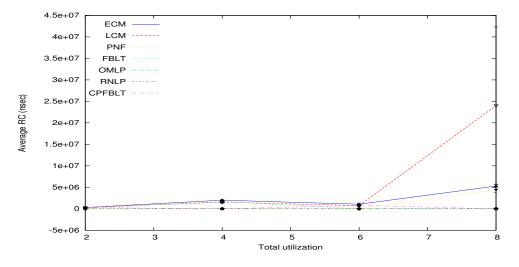

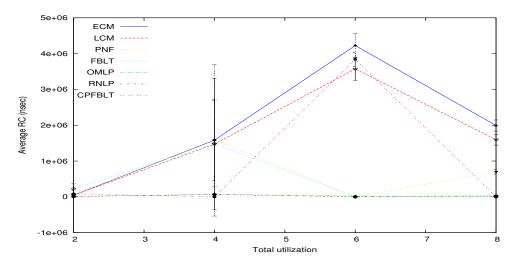

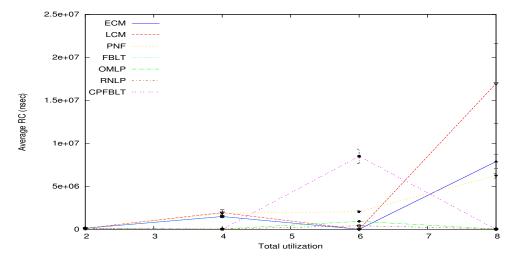

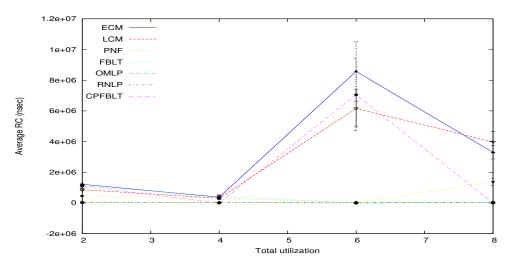

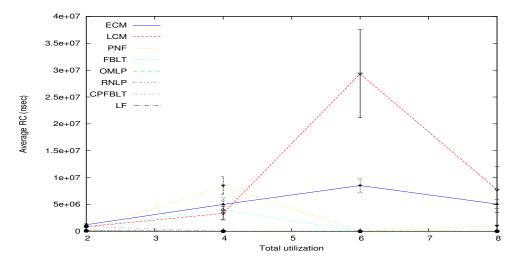

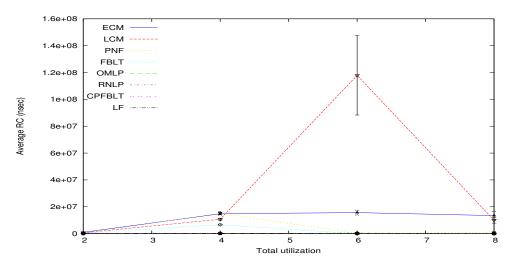

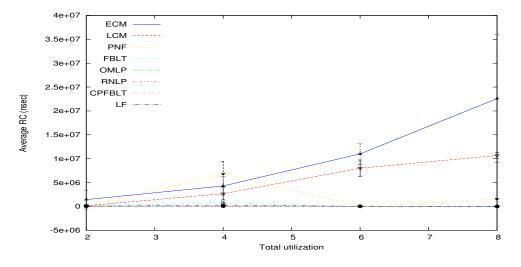

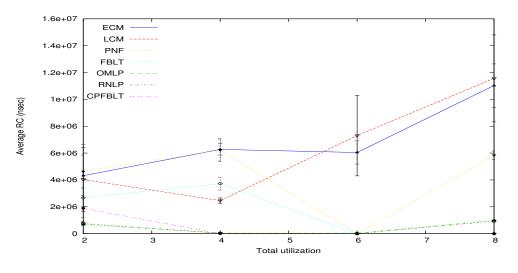

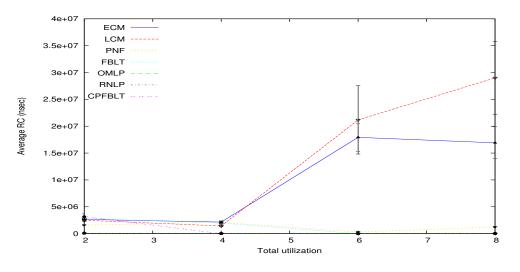

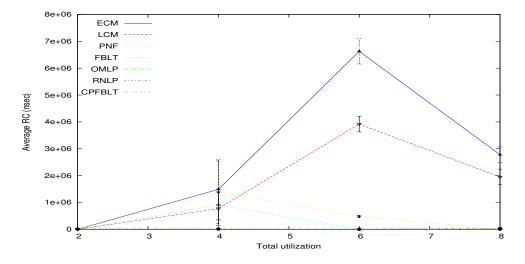

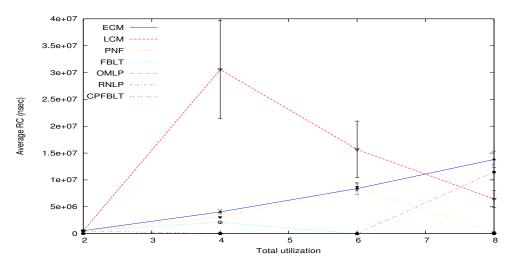

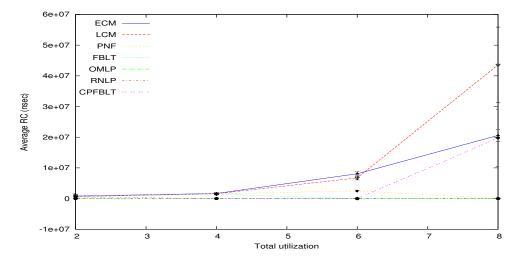

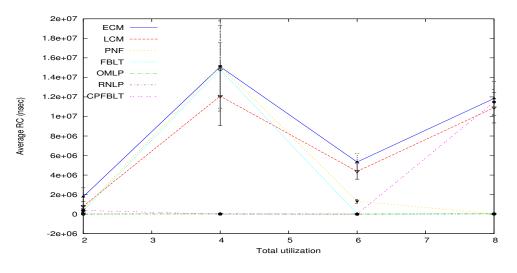

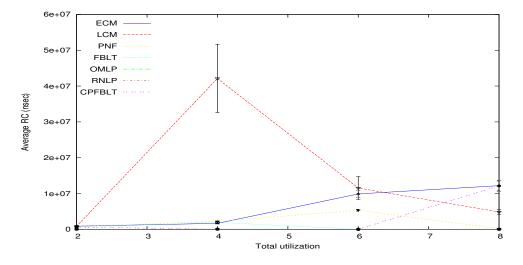

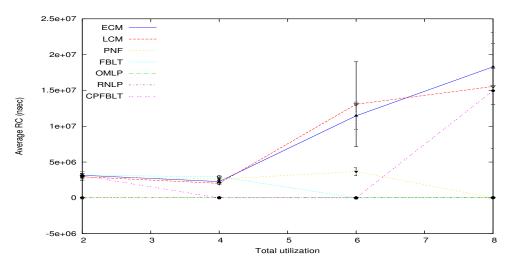

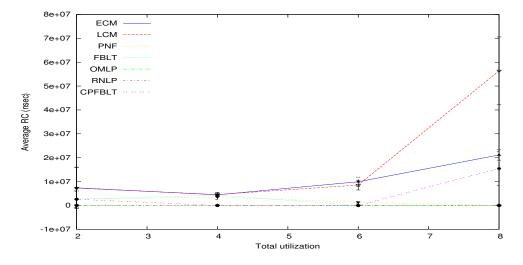

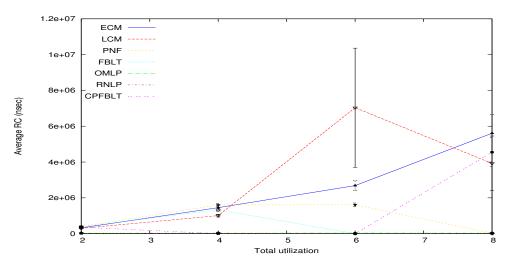

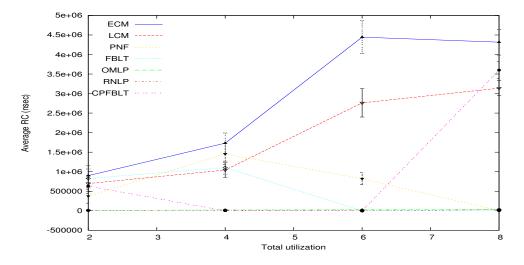

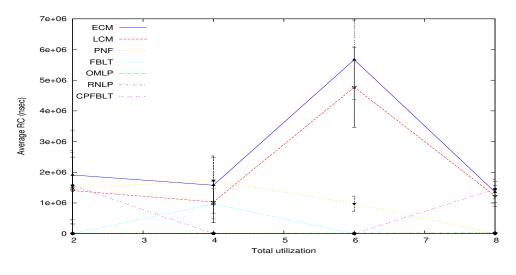

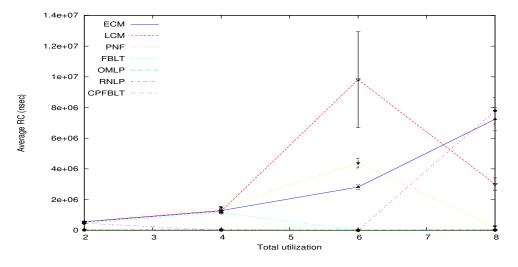

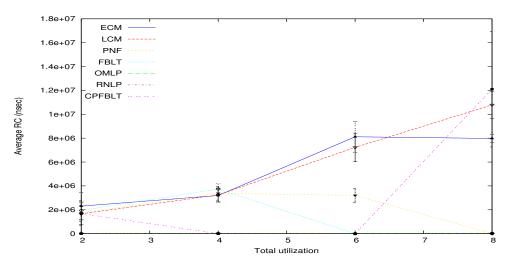

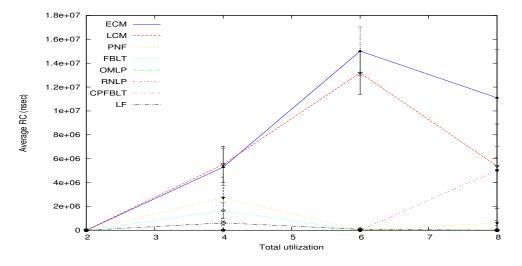

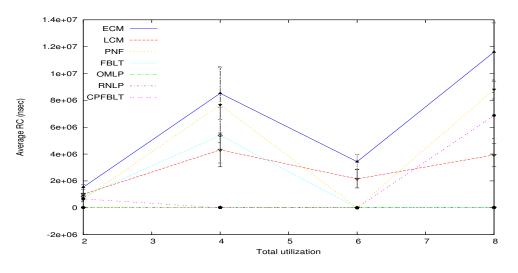

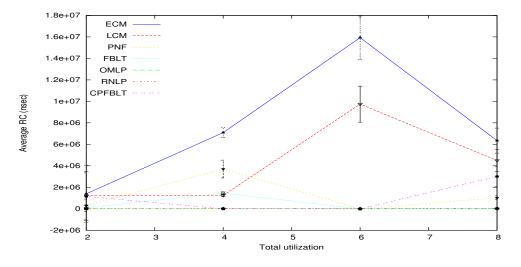

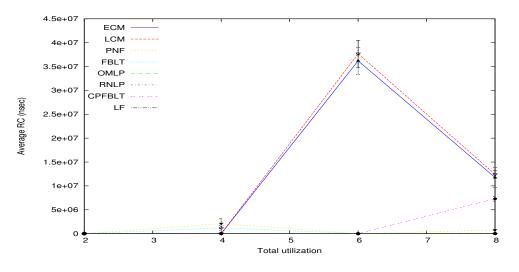

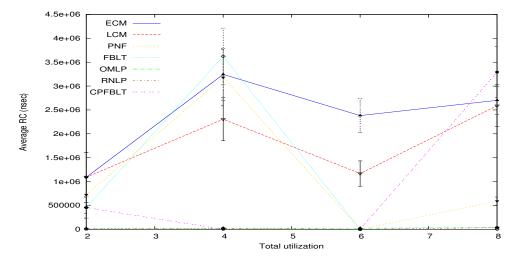

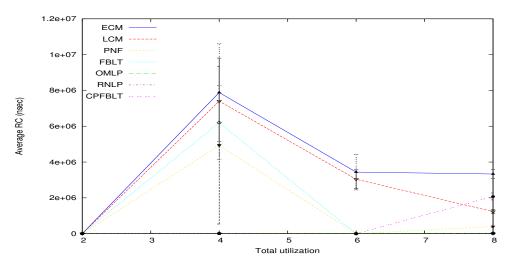

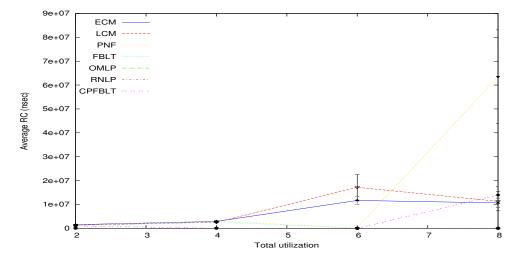

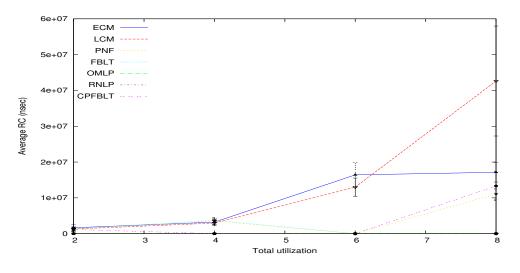

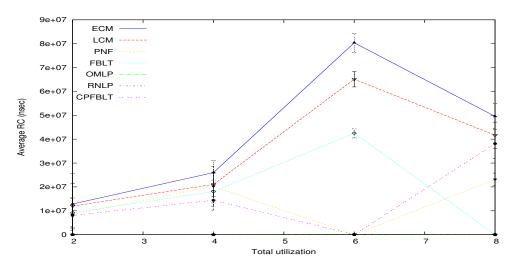

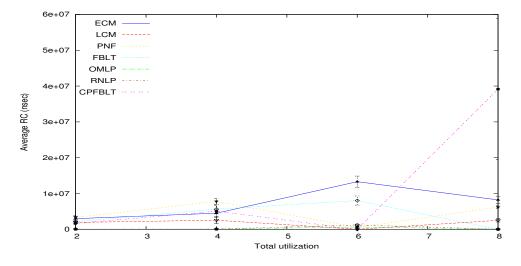

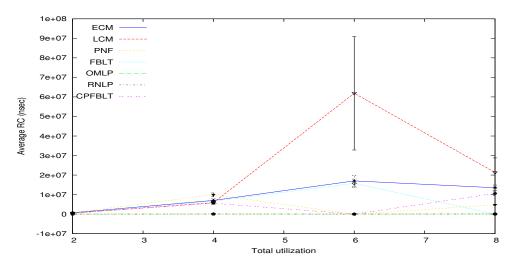

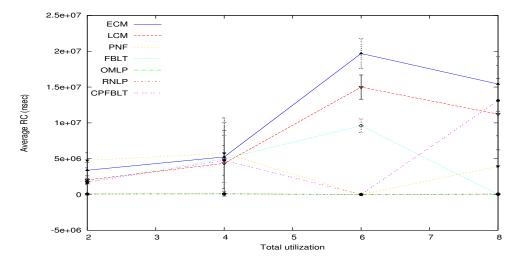

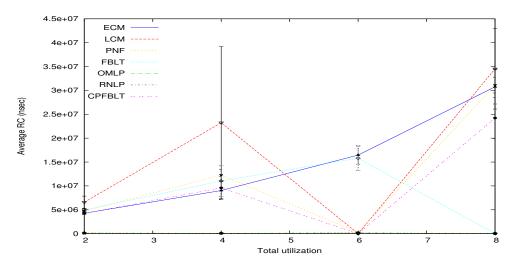

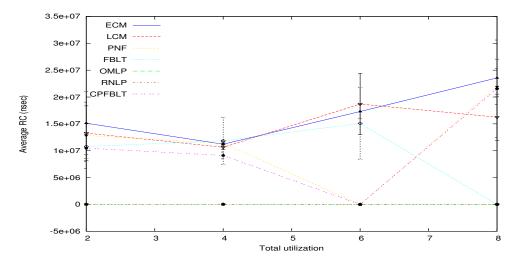

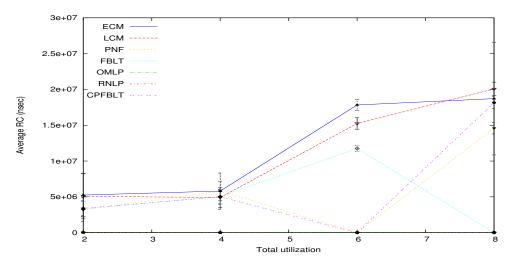

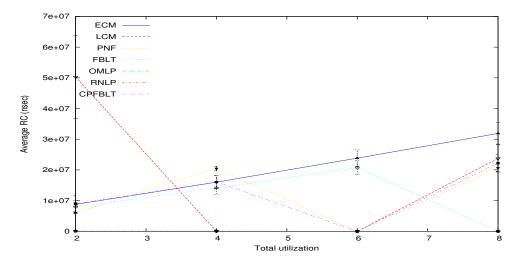

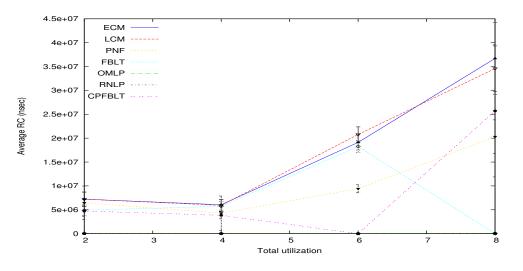

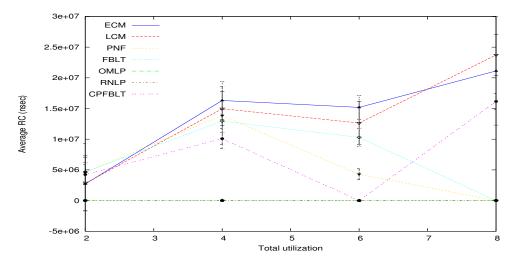

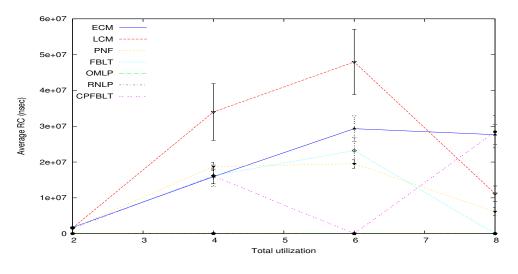

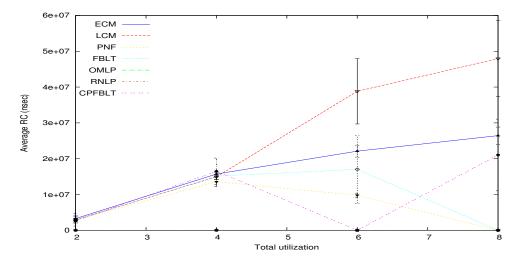

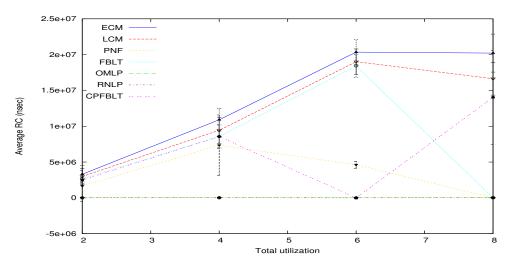

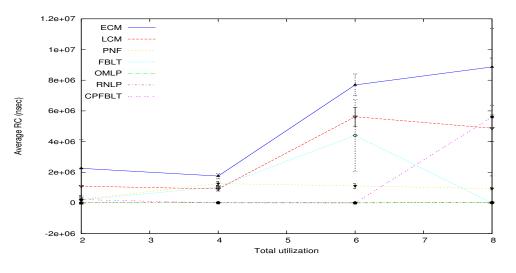

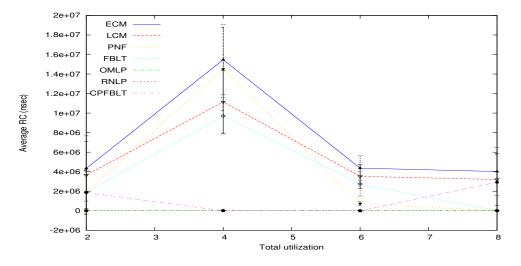

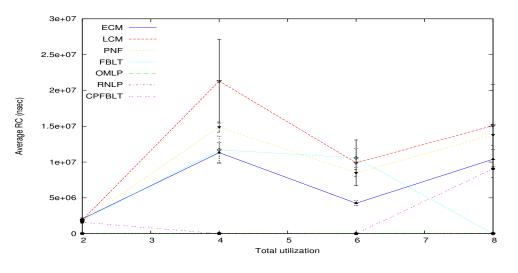

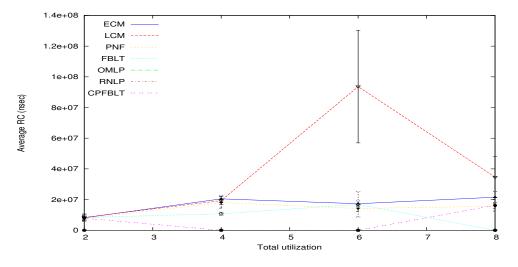

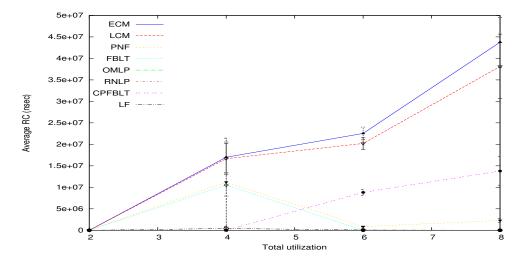

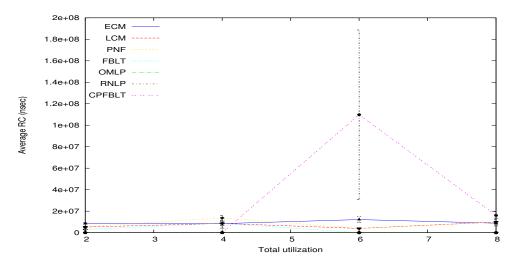

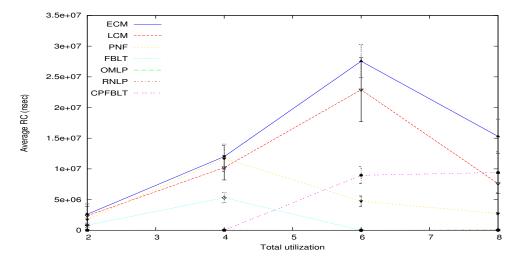

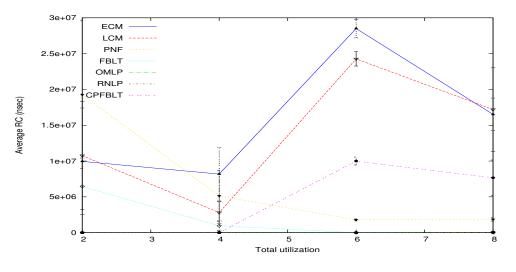

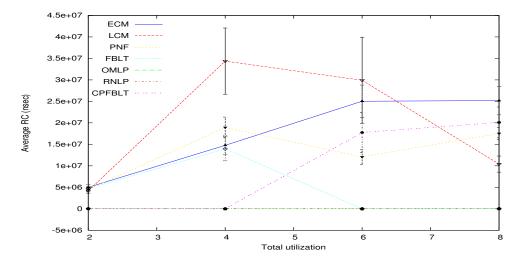

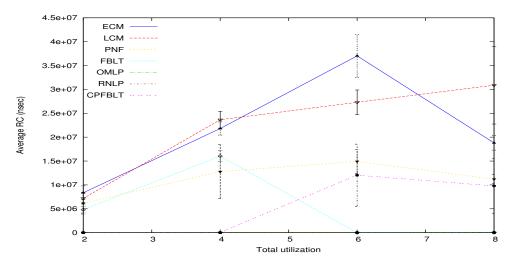

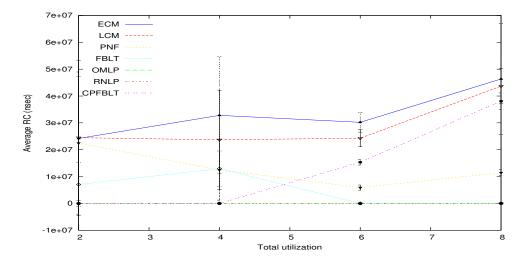

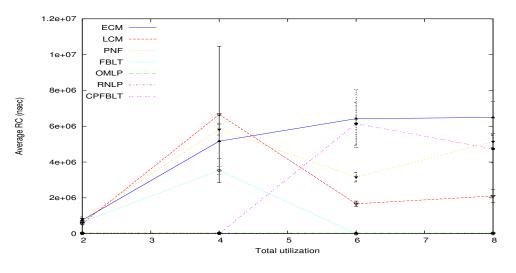

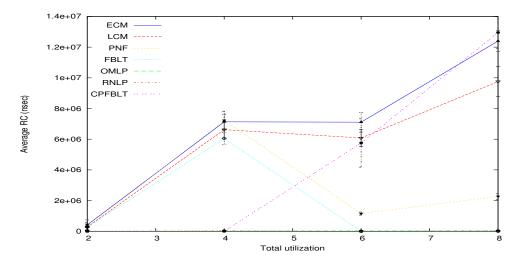

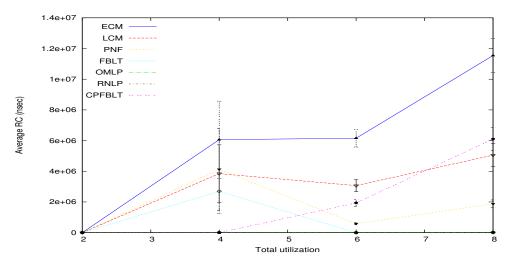

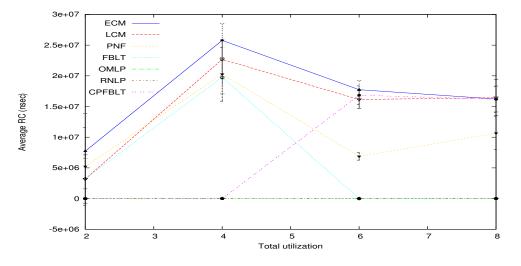

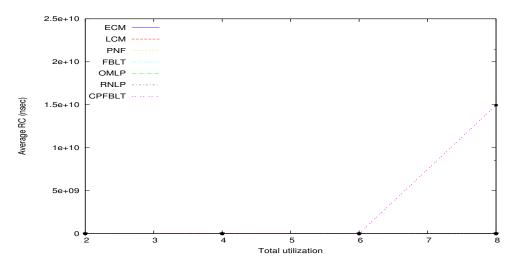

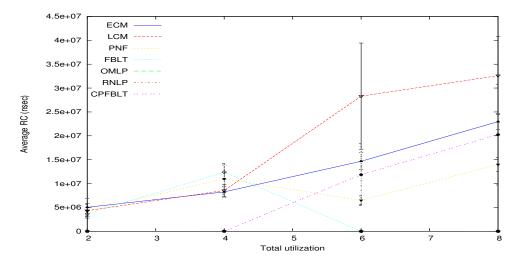

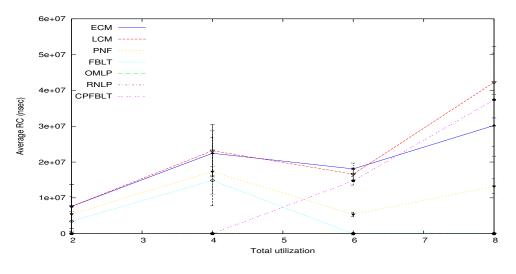

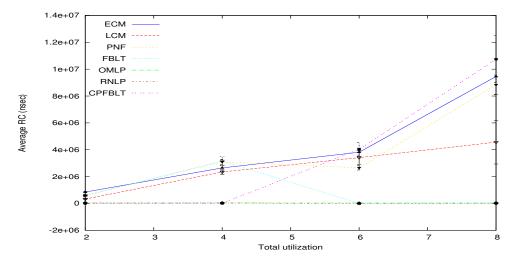

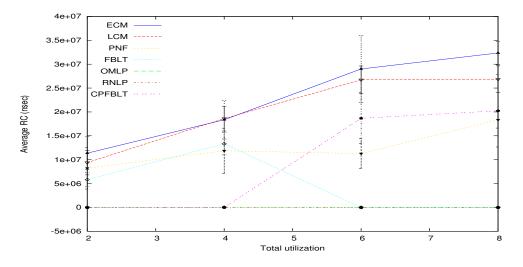

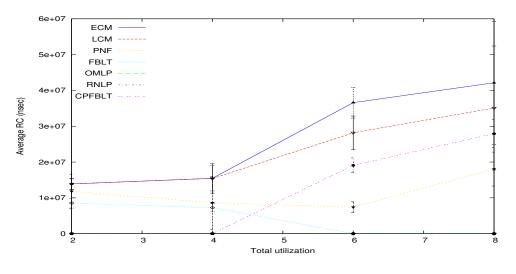

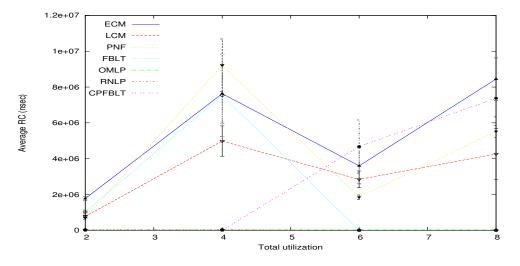

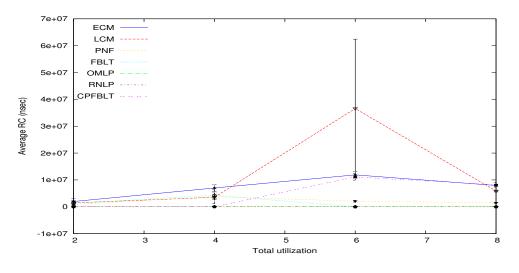

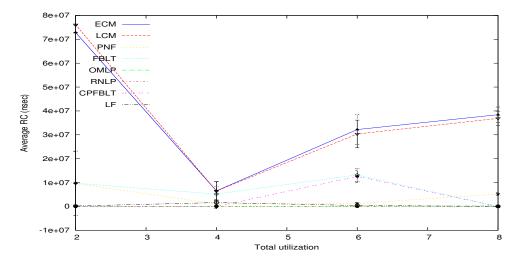

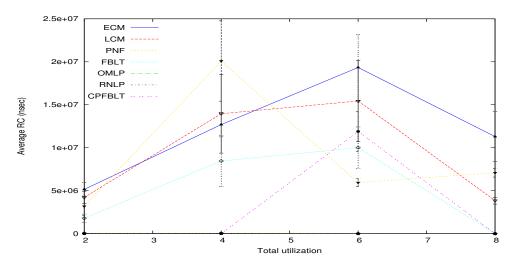

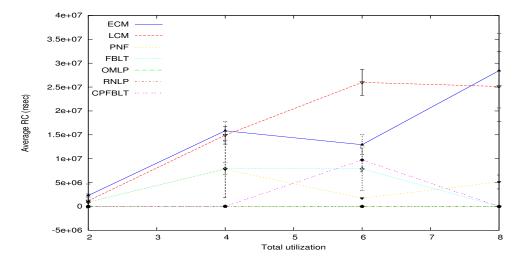

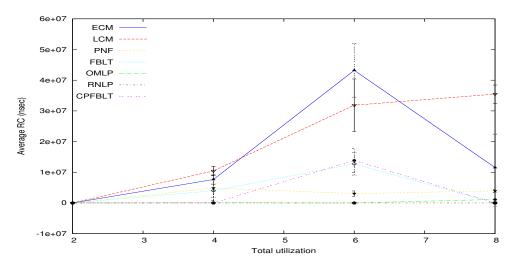

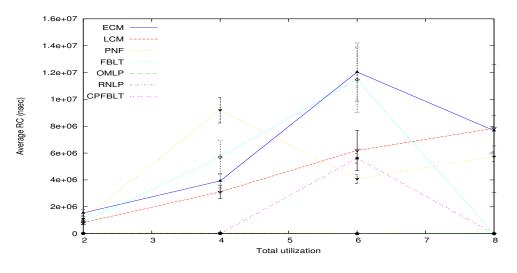

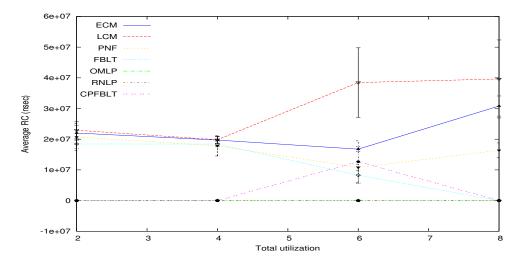

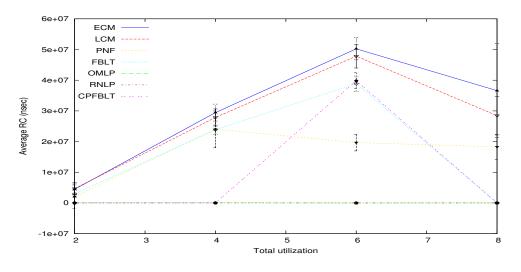

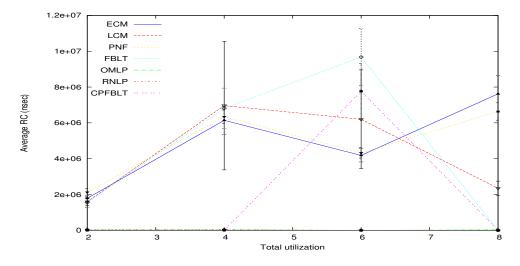

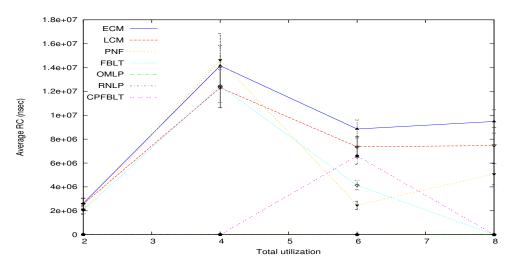

| 9.14 | Average RC for Tasksets 3, 543, 1083 and 1623                                                                         | 127 |

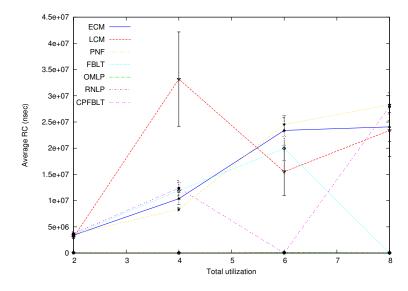

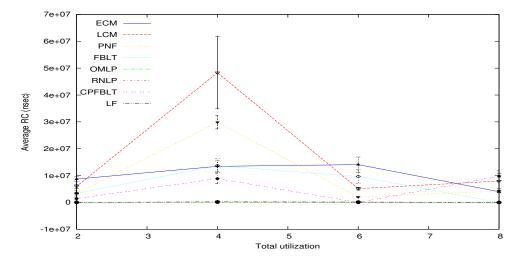

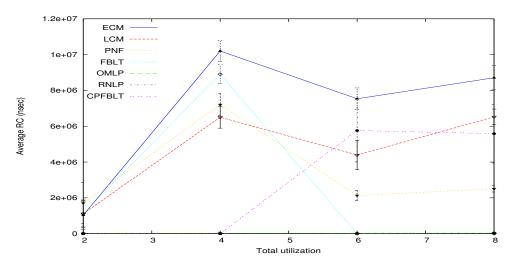

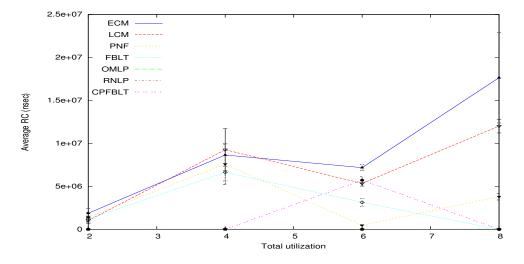

| 9.15 | Average RC for Tasksets 28, 568, 1108 and 1648                                                                        | 128 |

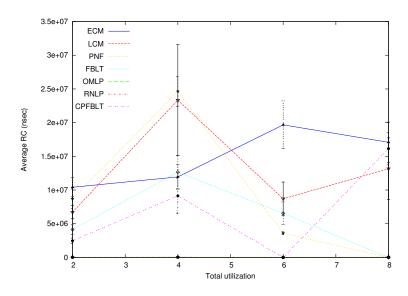

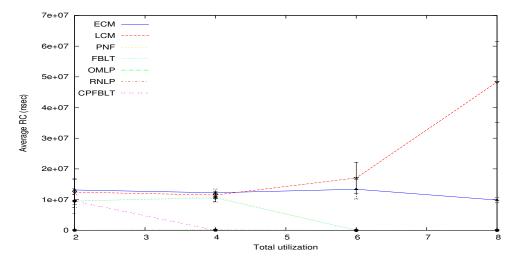

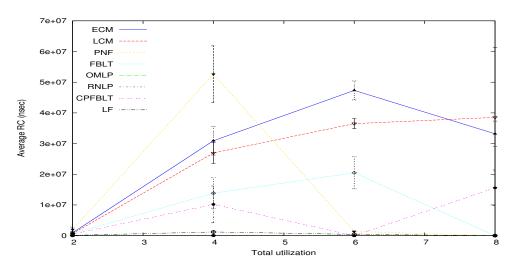

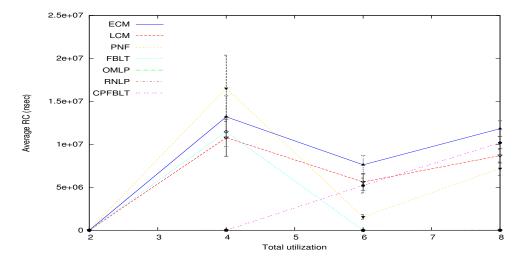

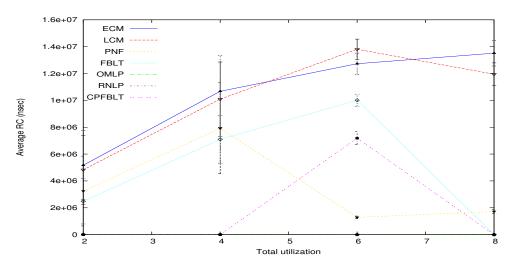

| 9.16 | Average RC for Tasksets 67, 607, 1147 and 1687 $\ldots$ $\ldots$ $\ldots$ $\ldots$                                    | 129 |

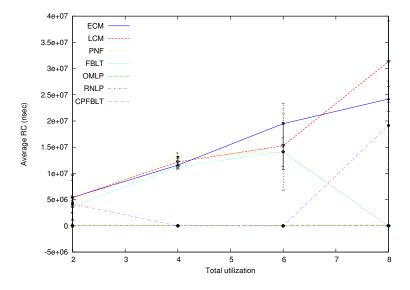

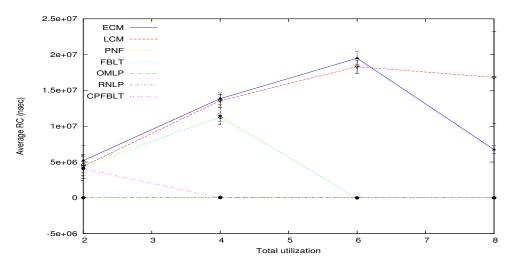

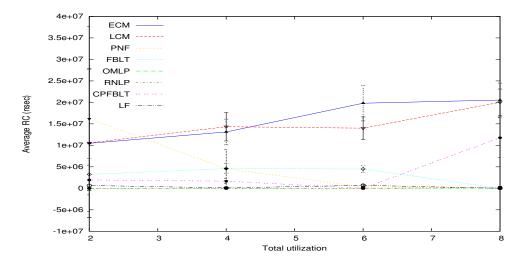

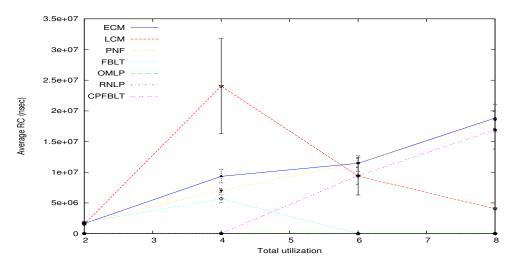

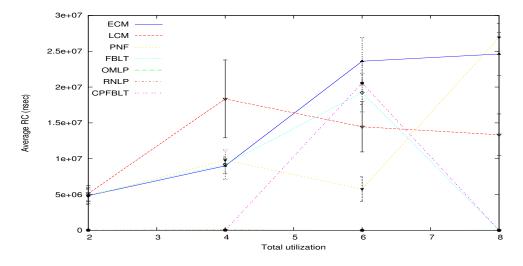

| 9.17 | Average RC for Tasksets 81, 621, 1161 and 1701                            | 129        |

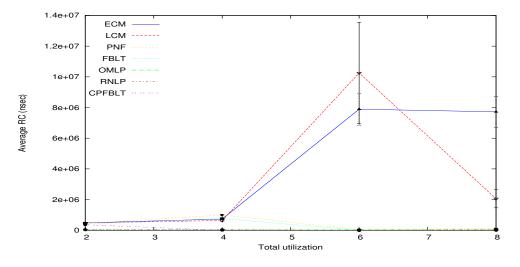

|------|---------------------------------------------------------------------------|------------|

| 9.18 | Average RC for Tasksets 97, 637, 1177 and 1717                            | 130        |

| 9.19 | Average RC for Tasksets 106, 646, 1186 and 1726                           | 130        |

| 9.20 | Average RC for Tasksets 130, 670, 1210 and 1750                           | 131        |

| 9.21 | Average RC for Tasksets 139, 679, 1219 and 1759                           | 131        |

| 9.22 | Average RC for Tasksets 158, 698, 1238 and 1778                           | 132        |

| 9.23 | Average RC for Tasksets 178, 718, 1258 and 1798                           | 132        |

| 9.24 | Average RC for Tasksets 185, 725, 1265 and 1805                           | 133        |

| 9.25 | Average RC for Tasksets 211, 751, 1291 and 1831                           | 133        |

| 9.26 | Average RC for Tasksets 234, 774, 1314 and 1854                           | 134        |

| B.1  | DSR for Tasksets 1, 271, 541 and 811                                      | 195        |

| B.2  |                                                                           | 195<br>195 |

| В.3  |                                                                           | 195<br>196 |

| В.4  |                                                                           | 190<br>196 |

| B.5  |                                                                           | 190        |

| В.6  |                                                                           | 197        |

| В.7  |                                                                           | 197        |

| B.8  |                                                                           | 198<br>198 |

| В.9  |                                                                           | 190<br>199 |

|      |                                                                           | 199<br>199 |

|      |                                                                           | 200        |

|      |                                                                           |            |

|      |                                                                           | 200        |

|      |                                                                           | 201        |

|      |                                                                           | 201        |

|      |                                                                           | 202        |

|      |                                                                           | 202        |

|      |                                                                           | 203        |

| B.18 | DSR for Tasksets 18, 288, 558 and 828 $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 203        |

| B.19 DSR for Tasksets 19, 289, 559 and 829 204 |

|------------------------------------------------|

| B.20 DSR for Tasksets 20, 290, 560 and 830     |

| B.21 DSR for Tasksets 21, 291, 561 and 831 205 |

| B.22 DSR for Tasksets 22, 292, 562 and 832 205 |

| B.23 DSR for Tasksets 23, 293, 563 and 833 206 |

| B.24 DSR for Tasksets 24, 294, 564 and 834     |

| B.25 DSR for Tasksets 25, 295, 565 and 835     |

| B.26 DSR for Tasksets 26, 296, 566 and 836 207 |

| B.27 DSR for Tasksets 27, 297, 567 and 837 208 |

| B.28 DSR for Tasksets 28, 298, 568 and 838 208 |

| B.29 DSR for Tasksets 29, 299, 569 and 839 209 |

| B.30 DSR for Tasksets 30, 300, 570 and 840     |

| B.31 DSR for Tasksets 31, 301, 571 and 841     |

| B.32 DSR for Tasksets 32, 302, 572 and 842 210 |

| B.33 DSR for Tasksets 33, 303, 573 and 843 211 |

| B.34 DSR for Tasksets 34, 304, 574 and 844 211 |

| B.35 DSR for Tasksets 35, 305, 575 and 845 212 |

| B.36 DSR for Tasksets 36, 306, 576 and 846 212 |

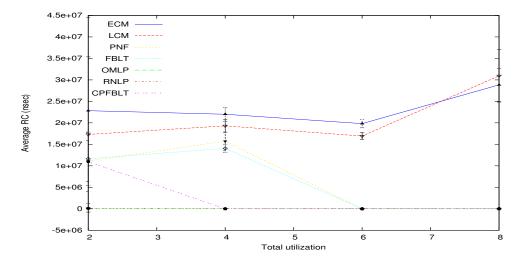

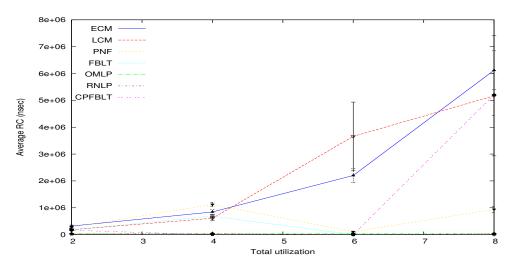

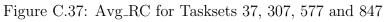

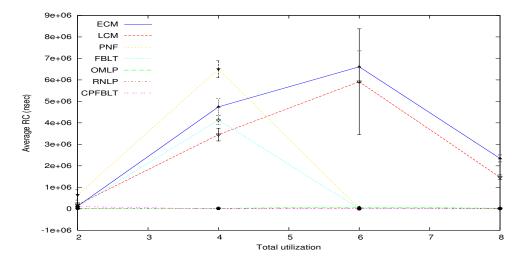

| B.37 DSR for Tasksets 37, 307, 577 and 847 213 |

| B.38 DSR for Tasksets 38, 308, 578 and 848 213 |

| B.39 DSR for Tasksets 39, 309, 579 and 849 214 |

| B.40 DSR for Tasksets 40, 310, 580 and 850 214 |

| B.41 DSR for Tasksets 41, 311, 581 and 851 215 |

| B.42 DSR for Tasksets 42, 312, 582 and 852 215 |

| B.43 DSR for Tasksets 43, 313, 583 and 853 216 |

| B.44 DSR for Tasksets 44, 314, 584 and 854 216 |

| B.45 DSR for Tasksets 45, 315, 585 and 855 217 |

| B.46 DSR for Tasksets 46, 316, 586 and 856 217 |

|                                                |

| B.47 DSR for Tasksets 47, 317, 587 and 857 218                     |

|--------------------------------------------------------------------|

| B.48 DSR for Tasksets 48, 318, 588 and 858                         |

| B.49 DSR for Tasksets 49, 319, 589 and 859                         |

| B.50 DSR for Tasksets 50, 320, 590 and 860                         |

| B.51 DSR for Tasksets 51, 321, 591 and 861                         |

| B.52 DSR for Tasksets 52, 322, 592 and 862         200         220 |

| B.53 DSR for Tasksets 53, 323, 593 and 863       221               |

| B.54 DSR for Tasksets 54, 324, 594 and 864                         |

| B.55 DSR for Tasksets 55, 325, 595 and 865         222             |

| B.56 DSR for Tasksets 56, 326, 596 and 866                         |

| B.57 DSR for Tasksets 57, 327, 597 and 867         223             |

| B.58 DSR for Tasksets 58, 328, 598 and 868         223             |

| B.59 DSR for Tasksets 59, 329, 599 and 869                         |

| B.60 DSR for Tasksets 60, 330, 600 and 870       224               |

| B.61 DSR for Tasksets 61, 331, 601 and 871         225             |

| B.61 DSR for Tasksets 62, 332, 602 and 872       225               |

|                                                                    |

| B.63 DSR for Tasksets 63, 333, 603 and 873                         |

| B.64 DSR for Tasksets 64, 334, 604 and 874                         |

| B.65 DSR for Tasksets 65, 335, 605 and 875                         |

| B.66 DSR for Tasksets 66, 336, 606 and 876                         |

| B.67 DSR for Tasksets 67, 337, 607 and 877                         |

| B.68 DSR for Tasksets 68, 338, 608 and 878                         |

| B.69 DSR for Tasksets 69, 339, 609 and 879                         |

| B.70 DSR for Tasksets 70, 340, 610 and 880                         |

| B.71 DSR for Tasksets 71, 341, 611 and 881                         |

| B.72 DSR for Tasksets 72, 342, 612 and 882                         |

| B.73 DSR for Tasksets 73, 343, 613 and 883 231                     |

| B.74 DSR for Tasksets 74, 344, 614 and 884                         |

| B.75 DSR for Tasksets 75, 345, 615 and 885 232 |

|------------------------------------------------|

| B.76 DSR for Tasksets 76, 346, 616 and 886 232 |

| B.77 DSR for Tasksets 77, 347, 617 and 887 233 |

| B.78 DSR for Tasksets 78, 348, 618 and 888 233 |

| B.79 DSR for Tasksets 79, 349, 619 and 889 234 |

| B.80 DSR for Tasksets 80, 350, 620 and 890 234 |

| B.81 DSR for Tasksets 81, 351, 621 and 891 235 |

| B.82 DSR for Tasksets 82, 352, 622 and 892 235 |

| B.83 DSR for Tasksets 83, 353, 623 and 893 236 |

| B.84 DSR for Tasksets 84, 354, 624 and 894 236 |

| B.85 DSR for Tasksets 85, 355, 625 and 895 237 |

| B.86 DSR for Tasksets 86, 356, 626 and 896 237 |

| B.87 DSR for Tasksets 87, 357, 627 and 897 238 |

| B.88 DSR for Tasksets 88, 358, 628 and 898 238 |

| B.89 DSR for Tasksets 89, 359, 629 and 899 239 |

| B.90 DSR for Tasksets 90, 360, 630 and 900 239 |

| B.91 DSR for Tasksets 91, 361, 631 and 901 240 |

| B.92 DSR for Tasksets 92, 362, 632 and 902 240 |

| B.93 DSR for Tasksets 93, 363, 633 and 903 241 |

| B.94 DSR for Tasksets 94, 364, 634 and 904 241 |

| B.95 DSR for Tasksets 95, 365, 635 and 905 242 |

| B.96 DSR for Tasksets 96, 366, 636 and 906 242 |

| B.97 DSR for Tasksets 97, 367, 637 and 907 243 |

| B.98 DSR for Tasksets 98, 368, 638 and 908 243 |

| B.99 DSR for Tasksets 99, 369, 639 and 909 244 |

| B.100DSR for Tasksets 100, 370, 640 and 910    |

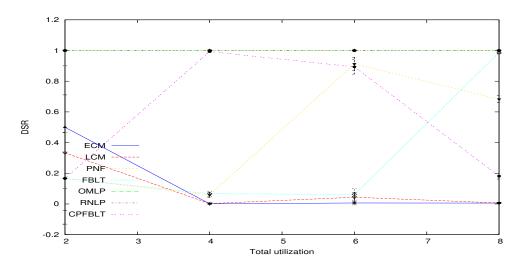

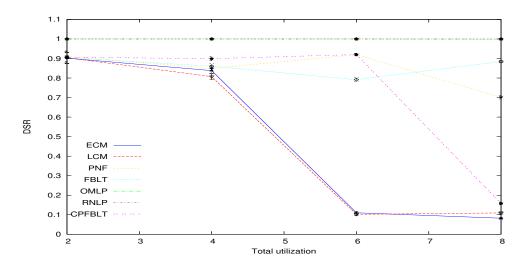

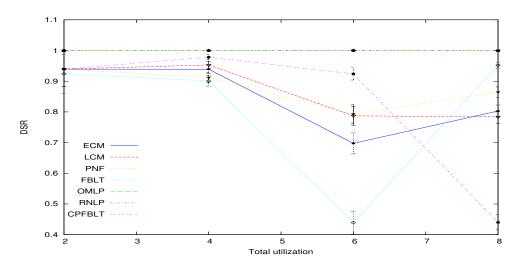

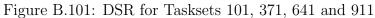

| B.101DSR for Tasksets 101, 371, 641 and 911    |

| B.102DSR for Tasksets 102, 372, 642 and 912    |

| B.103DSR for Tasksets 103, 373, 643 and 913     |

|-------------------------------------------------|

| B.104DSR for Tasksets 104, 374, 644 and 914     |

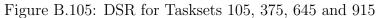

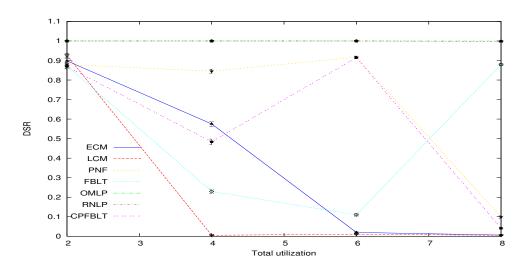

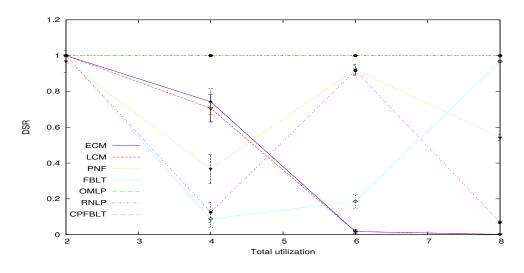

| B.105DSR for Tasksets 105, 375, 645 and 915     |

| B.106DSR for Tasksets 106, 376, 646 and 916     |

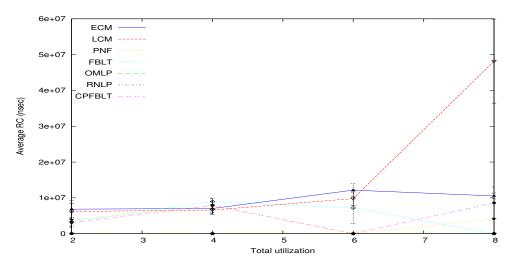

| B.107DSR for Tasksets 107, 377, 647 and 917     |

| B.108DSR for Tasksets 108, 378, 648 and 918 248 |

| B.109DSR for Tasksets 109, 379, 649 and 919     |

| B.110DSR for Tasksets 110, 380, 650 and 920     |

| B.111DSR for Tasksets 111, 381, 651 and 921     |

| B.112DSR for Tasksets 112, 382, 652 and 922     |

| B.113DSR for Tasksets 113, 383, 653 and 923     |

| B.114DSR for Tasksets 114, 384, 654 and 924     |

| B.115DSR for Tasksets 115, 385, 655 and 925     |

| B.116DSR for Tasksets 116, 386, 656 and 926     |

| B.117DSR for Tasksets 117, 387, 657 and 927     |

| B.11&DSR for Tasksets 118, 388, 658 and 928 253 |

| B.119DSR for Tasksets 119, 389, 659 and 929     |

| B.120DSR for Tasksets 120, 390, 660 and 930     |

| B.121DSR for Tasksets 121, 391, 661 and 931     |

| B.122DSR for Tasksets 122, 392, 662 and 932     |

| B.123DSR for Tasksets 123, 393, 663 and 933     |

| B.124DSR for Tasksets 124, 394, 664 and 934     |

| B.125DSR for Tasksets 125, 395, 665 and 935     |

| B.126DSR for Tasksets 126, 396, 666 and 936     |

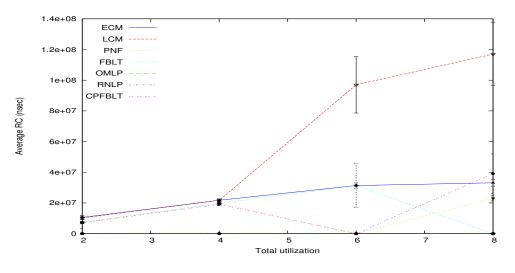

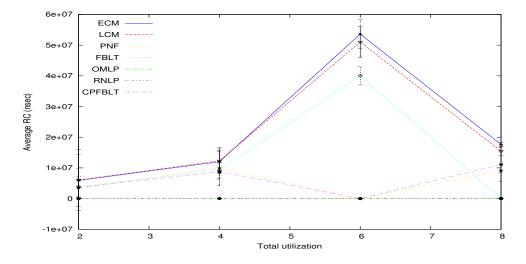

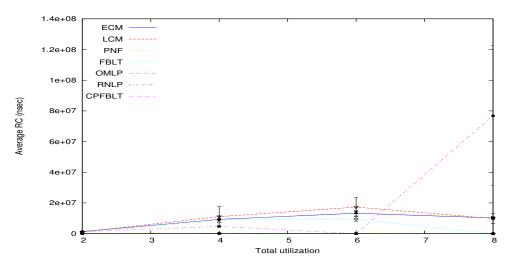

| B.127DSR for Tasksets 127, 397, 667 and 937     |

| B.12&DSR for Tasksets 128, 398, 668 and 938 258 |

| B.129DSR for Tasksets 129, 399, 669 and 939 259 |

| B.130DSR for Tasksets 130, 400, 670 and 940     |

| B.131DSR for Tasksets 131, 401, 671 and 941 |

|---------------------------------------------|

| B.132DSR for Tasksets 132, 402, 672 and 942 |

| B.133DSR for Tasksets 133, 403, 673 and 943 |

| B.134DSR for Tasksets 134, 404, 674 and 944 |

| B.135DSR for Tasksets 135, 405, 675 and 945 |

| B.136DSR for Tasksets 136, 406, 676 and 946 |

| B.137DSR for Tasksets 137, 407, 677 and 947 |

| B.13&DSR for Tasksets 138, 408, 678 and 948 |

| B.139DSR for Tasksets 139, 409, 679 and 949 |

| B.140DSR for Tasksets 140, 410, 680 and 950 |

| B.141DSR for Tasksets 141, 411, 681 and 951 |

| B.142DSR for Tasksets 142, 412, 682 and 952 |

| B.143DSR for Tasksets 143, 413, 683 and 953 |

| B.144DSR for Tasksets 144, 414, 684 and 954 |

| B.145DSR for Tasksets 145, 415, 685 and 955 |

| B.146DSR for Tasksets 146, 416, 686 and 956 |

| B.147DSR for Tasksets 147, 417, 687 and 957 |

| B.148DSR for Tasksets 148, 418, 688 and 958 |

| B.149DSR for Tasksets 149, 419, 689 and 959 |

| B.150DSR for Tasksets 150, 420, 690 and 960 |

| B.151DSR for Tasksets 151, 421, 691 and 961 |

| B.152DSR for Tasksets 152, 422, 692 and 962 |

| B.153DSR for Tasksets 153, 423, 693 and 963 |

| B.154DSR for Tasksets 154, 424, 694 and 964 |

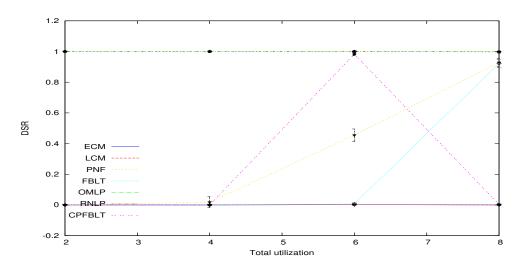

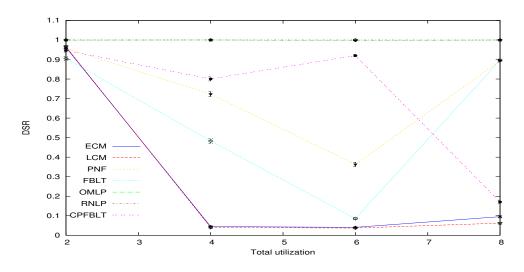

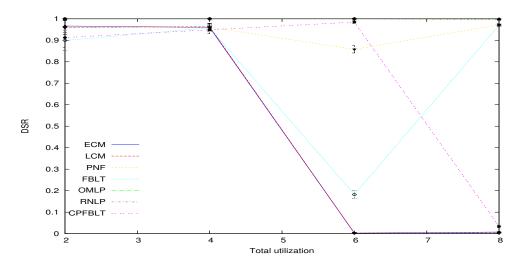

| B.155DSR for Tasksets 155, 425, 695 and 965 |

| B.156DSR for Tasksets 156, 426, 696 and 966 |

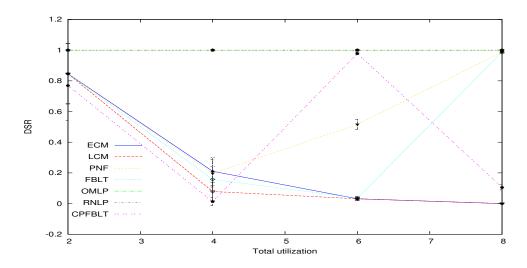

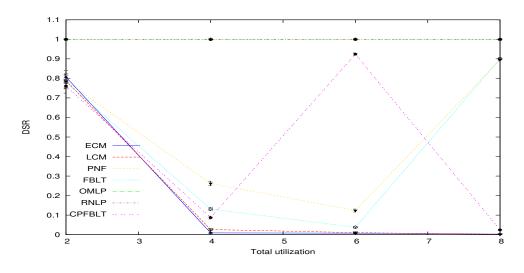

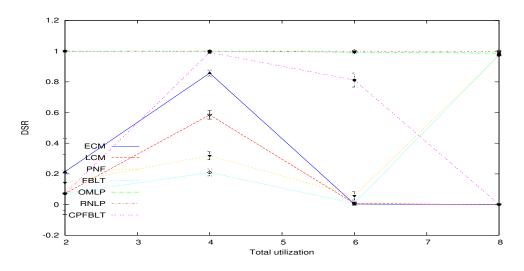

| B.157DSR for Tasksets 157, 427, 697 and 967 |

| B.15&DSR for Tasksets 158, 428, 698 and 968 |

| B.160DSR for Tasksets 160, 430, 700 and 970.       274         B.161DSR for Tasksets 161, 431, 701 and 971.       275         B.162DSR for Tasksets 162, 432, 702 and 972.       275         B.163DSR for Tasksets 163, 433, 703 and 973.       276         B.164DSR for Tasksets 164, 434, 704 and 974.       276         B.164DSR for Tasksets 165, 435, 705 and 975.       277         B.164DSR for Tasksets 165, 435, 705 and 976.       277         B.164DSR for Tasksets 166, 436, 706 and 976.       277         B.164DSR for Tasksets 167, 437, 707 and 977.       278         B.164DSR for Tasksets 164, 438, 708 and 978.       278         B.164DSR for Tasksets 169, 439, 709 and 979.       279         B.170DSR for Tasksets 170, 440, 710 and 980.       279         B.172DSR for Tasksets 171, 441, 711 and 981.       280         B.172DSR for Tasksets 173, 443, 713 and 983.       281         B.174DSR for Tasksets 174, 444, 714 and 984.       281         B.174DSR for Tasksets 175, 445, 715 and 985.       282         B.174DSR for Tasksets 174, 444, 714 and 984.       281         B.174DSR for Tasksets 174, 444, 714 and 984.       281         B.174DSR for Tasksets 174, 445, 716 and 986.       282         B.174DSR for Tasksets 174, 444, 714 and 984.       281         B.174DSR for Tasksets 180, 450, 720 and 990.   | B.159DSR for Tasksets 159, 429, 699 and 969     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| B.162DSR for Tasksets 162, 432, 702 and 972.       275         B.164DSR for Tasksets 163, 433, 703 and 973.       276         B.164DSR for Tasksets 164, 434, 704 and 974.       276         B.164DSR for Tasksets 164, 434, 704 and 974.       277         B.164DSR for Tasksets 165, 435, 705 and 975.       277         B.166DSR for Tasksets 166, 436, 706 and 976.       277         B.164DSR for Tasksets 167, 437, 707 and 977.       278         B.164DSR for Tasksets 169, 439, 709 and 979.       278         B.164DSR for Tasksets 169, 439, 709 and 979.       279         B.170DSR for Tasksets 170, 440, 710 and 980.       279         B.170DSR for Tasksets 171, 441, 711 and 981.       280         B.173DSR for Tasksets 173, 443, 713 and 983.       281         B.174DSR for Tasksets 174, 444, 714 and 984.       281         B.174DSR for Tasksets 175, 445, 715 and 985.       282         B.174DSR for Tasksets 176, 446, 716 and 986.       282         B.174DSR for Tasksets 174, 444, 714 and 984.       281         B.174DSR for Tasksets 174, 444, 714 and 984.       281         B.174DSR for Tasksets 175, 445, 715 and 985.       282         B.174DSR for Tasksets 176, 446, 716 and 986.       282         B.174DSR for Tasksets 179, 449, 719 and 989.       284         B.184DSR for Tasksets 180, 450, 720 and 990.   | B.160DSR for Tasksets 160, 430, 700 and 970     |

| B.16DSR for Tasksets 163, 433, 703 and 973.       276         B.16DSR for Tasksets 164, 434, 704 and 974.       276         B.16DSR for Tasksets 165, 435, 705 and 975.       277         B.16DSR for Tasksets 166, 436, 706 and 976.       277         B.16DSR for Tasksets 167, 437, 707 and 977.       278         B.16DSR for Tasksets 168, 438, 708 and 978.       278         B.16DSR for Tasksets 169, 439, 709 and 979.       279         B.170DSR for Tasksets 170, 440, 710 and 980.       279         B.171DSR for Tasksets 171, 441, 711 and 981.       280         B.172DSR for Tasksets 172, 442, 712 and 982.       280         B.174DSR for Tasksets 173, 443, 713 and 983.       281         B.174DSR for Tasksets 174, 444, 714 and 984.       281         B.175DSR for Tasksets 175, 445, 715 and 985.       282         B.170DSR for Tasksets 176, 446, 716 and 986.       283         B.175DSR for Tasksets 177, 447, 717 and 987.       283         B.175DSR for Tasksets 179, 449, 719 and 989.       284         B.180DSR for Tasksets 180, 450, 720 and 990.       284         B.180DSR for Tasksets 181, 451, 721 and 991.       285         B.182DSR for Tasksets 183, 453, 723 and 993.       286         B.184DSR for Tasksets 184, 454, 724 and 994.       286         B.184DSR for Tasksets 184, 454, 724 and 994.       28 | B.161DSR for Tasksets 161, 431, 701 and 971     |

| B.164DSR for Tasksets 164, 434, 704 and 974                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B.162DSR for Tasksets 162, 432, 702 and 972     |

| B.16DSR for Tasksets 165, 435, 705 and 975                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | B.163DSR for Tasksets 163, 433, 703 and 973     |

| B.166DSR for Tasksets 166, 436, 706 and 976                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B.164DSR for Tasksets 164, 434, 704 and 974     |

| B.167DSR for Tasksets 167, 437, 707 and 977                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B.165DSR for Tasksets 165, 435, 705 and 975     |

| B.168DSR for Tasksets 168, 438, 708 and 978       278         B.169DSR for Tasksets 169, 439, 709 and 979       279         B.170DSR for Tasksets 170, 440, 710 and 980       279         B.171DSR for Tasksets 171, 441, 711 and 981       280         B.172DSR for Tasksets 172, 442, 712 and 982       280         B.173DSR for Tasksets 173, 443, 713 and 983       281         B.174DSR for Tasksets 173, 443, 714 and 984       281         B.174DSR for Tasksets 174, 444, 714 and 984       281         B.174DSR for Tasksets 175, 445, 715 and 985       282         B.174DSR for Tasksets 176, 446, 716 and 986       282         B.174DSR for Tasksets 177, 447, 717 and 987       283         B.178DSR for Tasksets 179, 449, 719 and 989       283         B.179DSR for Tasksets 180, 450, 720 and 990       284         B.180DSR for Tasksets 181, 451, 721 and 991       285         B.182DSR for Tasksets 183, 453, 723 and 993       286         B.184DSR for Tasksets 184, 454, 724 and 994       286         B.184DSR for Tasksets 185, 455, 725 and 995       286                                                                                                                                                                                                                                                                      | B.166DSR for Tasksets 166, 436, 706 and 976     |

| B.169DSR for Tasksets 169, 439, 709 and 979                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B.167DSR for Tasksets 167, 437, 707 and 977     |

| B.170DSR for Tasksets 170, 440, 710 and 980                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B.168DSR for Tasksets 168, 438, 708 and 978 278 |

| B.171DSR for Tasksets 171, 441, 711 and 981.       280         B.172DSR for Tasksets 172, 442, 712 and 982.       280         B.173DSR for Tasksets 172, 442, 712 and 983.       281         B.173DSR for Tasksets 173, 443, 713 and 983.       281         B.174DSR for Tasksets 174, 444, 714 and 984.       281         B.175DSR for Tasksets 174, 444, 714 and 984.       281         B.175DSR for Tasksets 175, 445, 715 and 985.       282         B.176DSR for Tasksets 176, 446, 716 and 986.       282         B.177DSR for Tasksets 177, 447, 717 and 987.       283         B.178DSR for Tasksets 179, 449, 719 and 989.       283         B.179DSR for Tasksets 179, 449, 719 and 989.       284         B.180DSR for Tasksets 180, 450, 720 and 990.       284         B.181DSR for Tasksets 181, 451, 721 and 991.       285         B.182DSR for Tasksets 182, 452, 722 and 992.       285         B.184DSR for Tasksets 183, 453, 723 and 993.       286         B.184DSR for Tasksets 184, 454, 724 and 994.       286         B.185DSR for Tasksets 184, 454, 725 and 995.       286                                                                                                                                                                                                                                                     | B.169DSR for Tasksets 169, 439, 709 and 979     |

| B.172DSR for Tasksets 172, 442, 712 and 982       281         B.173DSR for Tasksets 173, 443, 713 and 983       281         B.174DSR for Tasksets 174, 444, 714 and 984       281         B.175DSR for Tasksets 175, 445, 715 and 985       282         B.176DSR for Tasksets 176, 446, 716 and 986       282         B.177DSR for Tasksets 177, 447, 717 and 987       283         B.179DSR for Tasksets 178, 448, 718 and 988       283         B.179DSR for Tasksets 179, 449, 719 and 989       284         B.180DSR for Tasksets 180, 450, 720 and 990       284         B.182DSR for Tasksets 181, 451, 721 and 991       285         B.183DSR for Tasksets 182, 452, 722 and 992       285         B.184DSR for Tasksets 183, 453, 723 and 993       286         B.184DSR for Tasksets 184, 454, 724 and 994       286         B.184DSR for Tasksets 184, 454, 724 and 994       286         B.184DSR for Tasksets 185, 455, 725 and 995       287                                                                                                                                                                                                                                                                                                                                                                                                  | B.170DSR for Tasksets 170, 440, 710 and 980     |

| B.173DSR for Tasksets 173, 443, 713 and 983       281         B.174DSR for Tasksets 174, 444, 714 and 984       281         B.174DSR for Tasksets 175, 445, 715 and 985       282         B.176DSR for Tasksets 176, 446, 716 and 986       282         B.177DSR for Tasksets 177, 447, 717 and 987       283         B.179DSR for Tasksets 178, 448, 718 and 988       283         B.179DSR for Tasksets 179, 449, 719 and 989       283         B.180DSR for Tasksets 180, 450, 720 and 990       284         B.182DSR for Tasksets 181, 451, 721 and 991       285         B.183DSR for Tasksets 183, 453, 723 and 993       285         B.184DSR for Tasksets 184, 454, 724 and 994       286         B.185DSR for Tasksets 184, 455, 725 and 995       287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | B.171DSR for Tasksets 171, 441, 711 and 981     |

| B.174DSR for Tasksets 174, 444, 714 and 984                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B.172DSR for Tasksets 172, 442, 712 and 982     |

| B.175DSR for Tasksets 175, 445, 715 and 985       282         B.176DSR for Tasksets 176, 446, 716 and 986       282         B.177DSR for Tasksets 177, 447, 717 and 987       283         B.178DSR for Tasksets 179, 449, 719 and 988       283         B.179DSR for Tasksets 179, 449, 719 and 989       284         B.180DSR for Tasksets 180, 450, 720 and 990       284         B.181DSR for Tasksets 181, 451, 721 and 991       285         B.182DSR for Tasksets 182, 452, 722 and 992       285         B.183DSR for Tasksets 183, 453, 723 and 993       286         B.184DSR for Tasksets 184, 454, 724 and 994       286         B.185DSR for Tasksets 185, 455, 725 and 995       287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | B.173DSR for Tasksets 173, 443, 713 and 983     |

| B.176DSR for Tasksets 176, 446, 716 and 986       282         B.177DSR for Tasksets 177, 447, 717 and 987       283         B.178DSR for Tasksets 178, 448, 718 and 988       283         B.179DSR for Tasksets 179, 449, 719 and 989       283         B.180DSR for Tasksets 180, 450, 720 and 990       284         B.181DSR for Tasksets 181, 451, 721 and 991       285         B.182DSR for Tasksets 182, 452, 722 and 992       284         B.183DSR for Tasksets 183, 453, 723 and 993       285         B.184DSR for Tasksets 184, 454, 724 and 994       286         B.185DSR for Tasksets 185, 455, 725 and 995       287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | B.174DSR for Tasksets 174, 444, 714 and 984     |

| B.177DSR for Tasksets 177, 447, 717 and 987       283         B.178DSR for Tasksets 178, 448, 718 and 988       283         B.179DSR for Tasksets 179, 449, 719 and 989       284         B.180DSR for Tasksets 180, 450, 720 and 990       284         B.181DSR for Tasksets 181, 451, 721 and 991       285         B.182DSR for Tasksets 182, 452, 722 and 992       285         B.183DSR for Tasksets 183, 453, 723 and 993       286         B.184DSR for Tasksets 184, 454, 724 and 994       286         B.185DSR for Tasksets 185, 455, 725 and 995       287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | B.175DSR for Tasksets 175, 445, 715 and 985     |

| B.178DSR for Tasksets 178, 448, 718 and 988                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B.176DSR for Tasksets 176, 446, 716 and 986     |

| B.179DSR for Tasksets 179, 449, 719 and 989                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B.177DSR for Tasksets 177, 447, 717 and 987     |

| B.180DSR for Tasksets 180, 450, 720 and 990       284         B.181DSR for Tasksets 181, 451, 721 and 991       285         B.182DSR for Tasksets 182, 452, 722 and 992       285         B.183DSR for Tasksets 183, 453, 723 and 993       285         B.184DSR for Tasksets 184, 454, 724 and 994       285         B.185DSR for Tasksets 185, 455, 725 and 995       285                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B.178DSR for Tasksets 178, 448, 718 and 988 283 |

| B.181DSR for Tasksets 181, 451, 721 and 991                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B.179DSR for Tasksets 179, 449, 719 and 989 284 |

| B.182DSR for Tasksets 182, 452, 722 and 992       285         B.183DSR for Tasksets 183, 453, 723 and 993       286         B.184DSR for Tasksets 184, 454, 724 and 994       286         B.185DSR for Tasksets 185, 455, 725 and 995       287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | B.180DSR for Tasksets 180, 450, 720 and 990     |

| B.183DSR for Tasksets 183, 453, 723 and 993       286         B.184DSR for Tasksets 184, 454, 724 and 994       286         B.185DSR for Tasksets 185, 455, 725 and 995       287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | B.181DSR for Tasksets 181, 451, 721 and 991     |

| B.184DSR for Tasksets 184, 454, 724 and 994                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B.182DSR for Tasksets 182, 452, 722 and 992     |

| B.185DSR for Tasksets 185, 455, 725 and 995                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B.183DSR for Tasksets 183, 453, 723 and 993     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | B.184DSR for Tasksets 184, 454, 724 and 994     |

| B.186DSR for Tasksets 186, 456, 726 and 996                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B.185DSR for Tasksets 185, 455, 725 and 995     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | B.186DSR for Tasksets 186, 456, 726 and 996     |

| B.187DSR for Tasksets 187, 457, 727 and 997  |

|----------------------------------------------|

| B.188DSR for Tasksets 188, 458, 728 and 998  |

| B.189DSR for Tasksets 189, 459, 729 and 999  |

| B.190DSR for Tasksets 190, 460, 730 and 1000 |

| B.191DSR for Tasksets 191, 461, 731 and 1001 |

| B.192DSR for Tasksets 192, 462, 732 and 1002 |

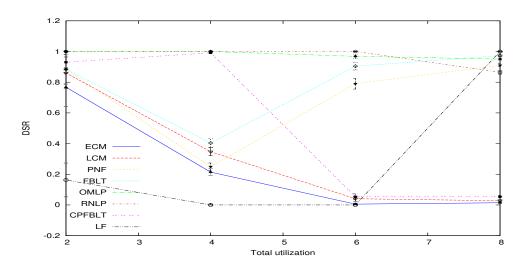

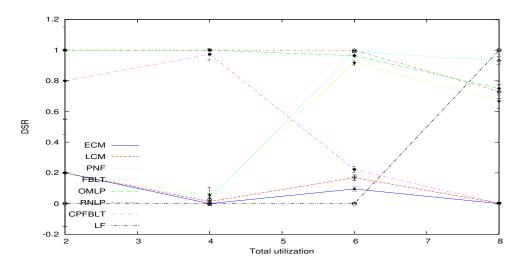

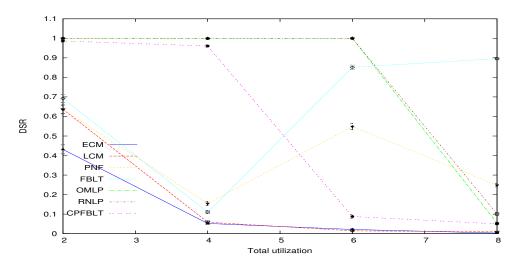

| B.193DSR for Tasksets 193, 463, 733 and 1003 |

| B.194DSR for Tasksets 194, 464, 734 and 1004 |

| B.195DSR for Tasksets 195, 465, 735 and 1005 |

| B.196DSR for Tasksets 196, 466, 736 and 1006 |

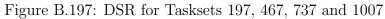

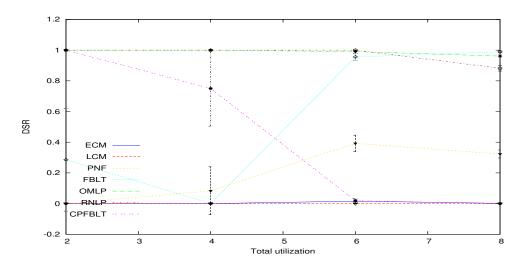

| B.197DSR for Tasksets 197, 467, 737 and 1007 |

| B.198DSR for Tasksets 198, 468, 738 and 1008 |

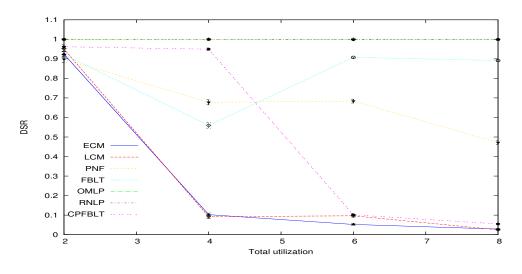

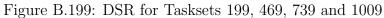

| B.199DSR for Tasksets 199, 469, 739 and 1009 |

| B.200DSR for Tasksets 200, 470, 740 and 1010 |

| B.201DSR for Tasksets 201, 471, 741 and 1011 |

| B.202DSR for Tasksets 202, 472, 742 and 1012 |

| B.203DSR for Tasksets 203, 473, 743 and 1013 |

| B.204DSR for Tasksets 204, 474, 744 and 1014 |

| B.205DSR for Tasksets 205, 475, 745 and 1015 |

| B.206DSR for Tasksets 206, 476, 746 and 1016 |

| B.207DSR for Tasksets 207, 477, 747 and 1017 |

| B.208DSR for Tasksets 208, 478, 748 and 1018 |

| B.209DSR for Tasksets 209, 479, 749 and 1019 |

| B.210DSR for Tasksets 210, 480, 750 and 1020 |

| B.211DSR for Tasksets 211, 481, 751 and 1021 |

| B.212DSR for Tasksets 212, 482, 752 and 1022 |

| B.213DSR for Tasksets 213, 483, 753 and 1023 |

| B.214DSR for Tasksets 214, 484, 754 and 1024 |

| B.215DSR for Tasksets 215, 485, 755 and 1025     |

|--------------------------------------------------|

| B.216DSR for Tasksets 216, 486, 756 and 1026     |

| B.217DSR for Tasksets 217, 487, 757 and 1027     |

| B.21&DSR for Tasksets 218, 488, 758 and 1028     |

| B.219DSR for Tasksets 219, 489, 759 and 1029 304 |

| B.220DSR for Tasksets 220, 490, 760 and 1030     |

| B.221DSR for Tasksets 221, 491, 761 and 1031     |

| B.222DSR for Tasksets 222, 492, 762 and 1032     |

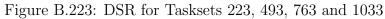

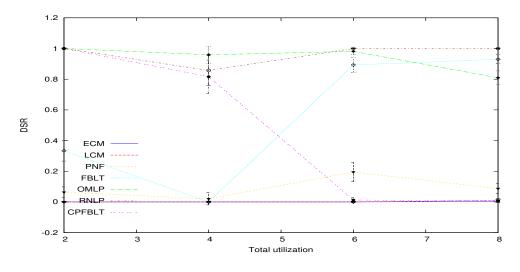

| B.223DSR for Tasksets 223, 493, 763 and 1033 306 |

| B.224DSR for Tasksets 224, 494, 764 and 1034     |

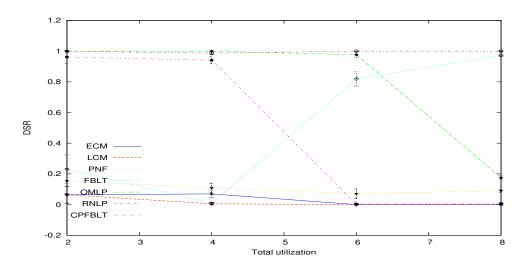

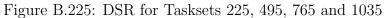

| B.225DSR for Tasksets 225, 495, 765 and 1035     |

| B.226DSR for Tasksets 226, 496, 766 and 1036 307 |

| B.227DSR for Tasksets 227, 497, 767 and 1037 308 |

| B.22&DSR for Tasksets 228, 498, 768 and 1038 308 |

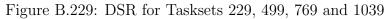

| B.229DSR for Tasksets 229, 499, 769 and 1039     |

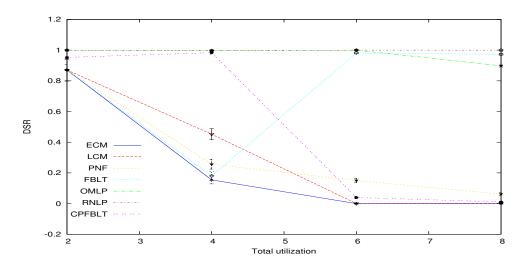

| B.230DSR for Tasksets 230, 500, 770 and 1040     |

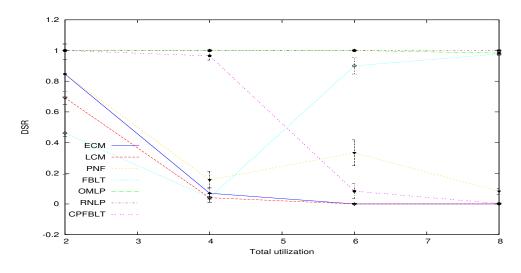

| B.231DSR for Tasksets 231, 501, 771 and 1041     |

| B.232DSR for Tasksets 232, 502, 772 and 1042 310 |

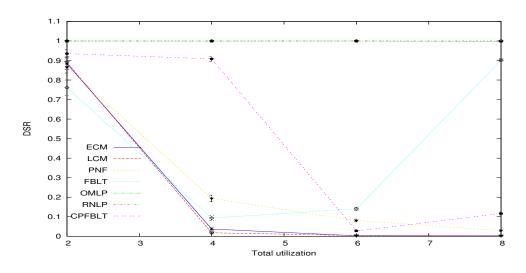

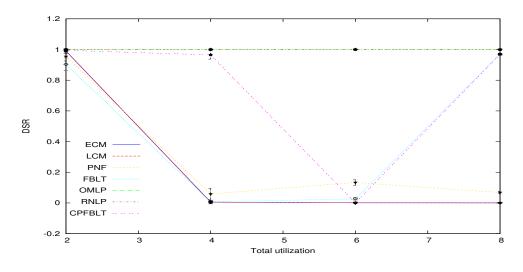

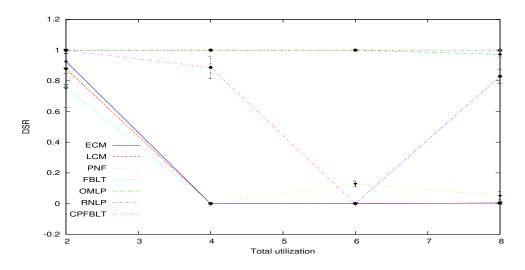

| B.233DSR for Tasksets 233, 503, 773 and 1043 311 |

| B.234DSR for Tasksets 234, 504, 774 and 1044     |

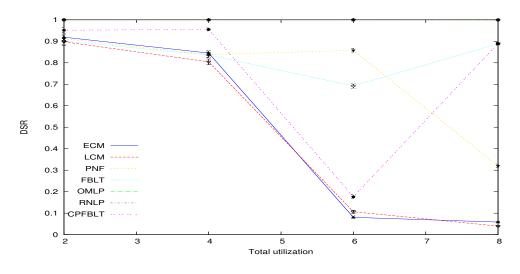

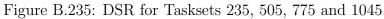

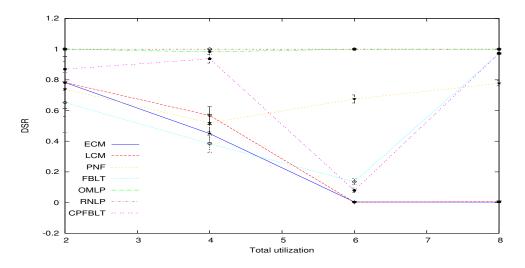

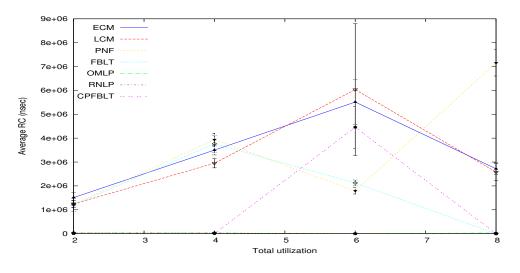

| B.235DSR for Tasksets 235, 505, 775 and 1045 312 |

| B.236DSR for Tasksets 236, 506, 776 and 1046 312 |

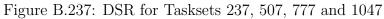

| B.237DSR for Tasksets 237, 507, 777 and 1047 313 |

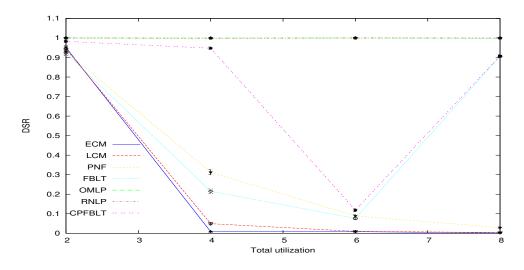

| B.23&DSR for Tasksets 238, 508, 778 and 1048 313 |

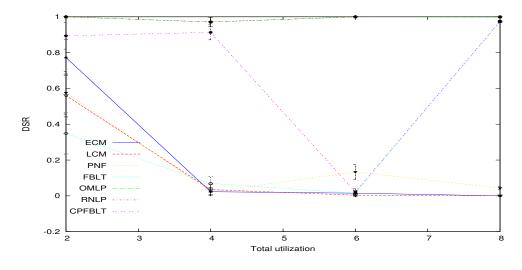

| B.239DSR for Tasksets 239, 509, 779 and 1049 314 |

| B.240DSR for Tasksets 240, 510, 780 and 1050     |

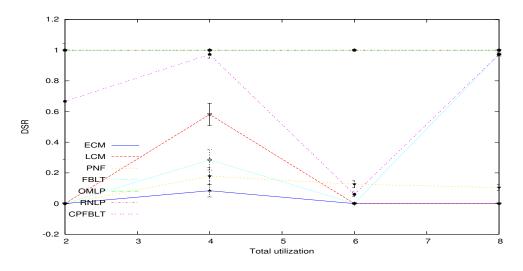

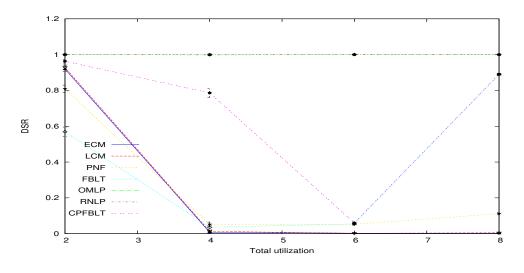

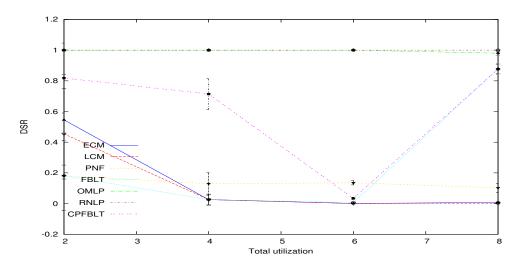

| B.241DSR for Tasksets 241, 511, 781 and 1051     |

| B.242DSR for Tasksets 242, 512, 782 and 1052     |

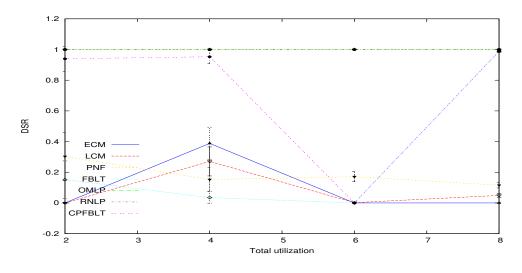

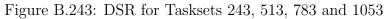

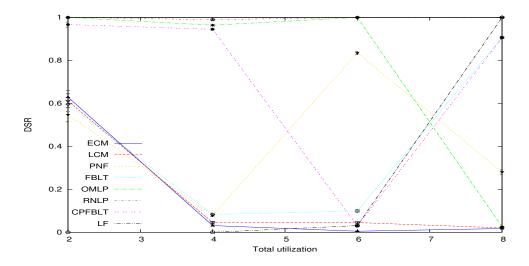

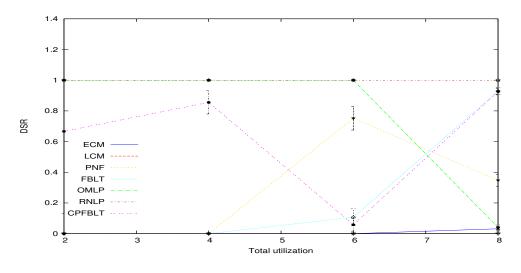

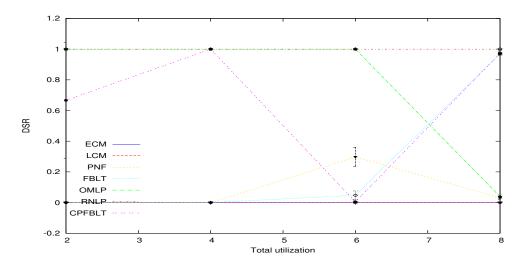

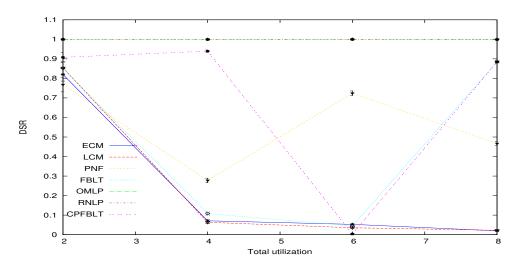

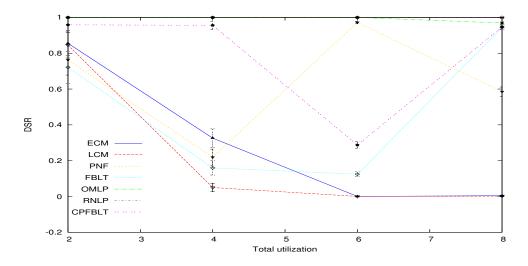

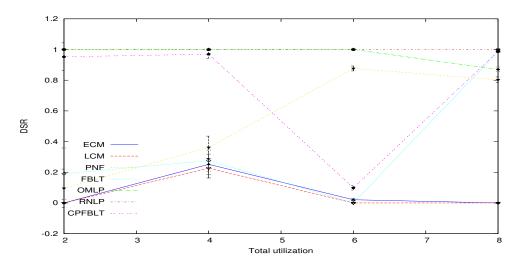

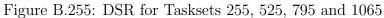

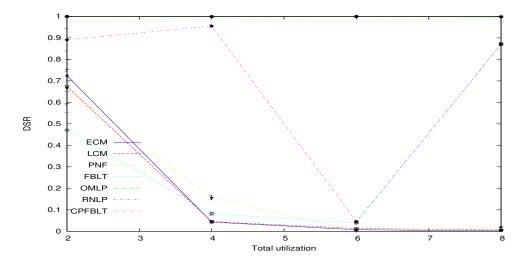

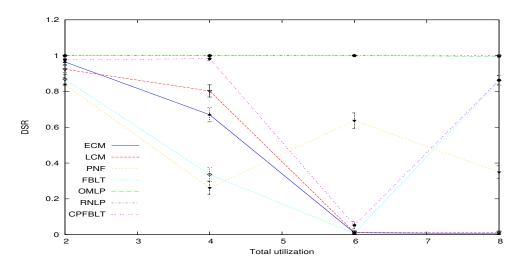

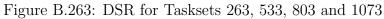

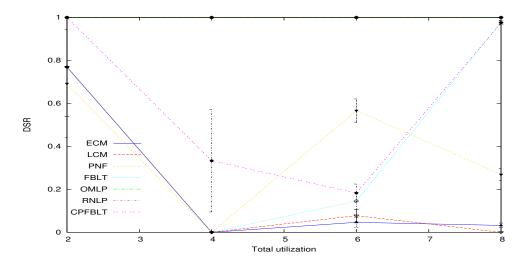

| $D_{2}^{0} = 0.000 f_{em} = 0.000 f_{em} = 0.000 f_{em} = 0.0000 f_{em} = 0.0$ |