## High Frequency, High Power Density Integrated Point of Load and Bus Converters

**David Clayton Reusch**

Dissertation submitted to the faculty of the

Virginia Polytechnic Institute and State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in

Electrical Engineering

Fred C. Lee, Chairman Jaime De La Ree Guo-Quan Lu Khai D. T. Ngo Mayuresh J Patil

April 16th, 2012 Blacksburg, Virginia

Keywords: High power density, high frequency, point-of-load converter, bus converter, gallium nitride, magnetic integration

© 2012, David Clayton Reusch

# High Frequency, High Power Density Integrated Point of Load and Bus Converters

#### David Clayton Reusch

#### **Abstract**

The increased power consumption and power density demands of modern technologies combined with the focus on global energy savings have increased the demands on DC/DC power supplies. DC/DC converters are ubiquitous in everyday life, found in products ranging from small handheld electronics requiring a few watts to warehouse sized server farms demanding over 50 megawatts. To improve efficiency and power density while reducing complexity and cost the modular building block approach is gaining popularity. These modular building blocks replace individually designed specialty power supplies, providing instead an optimized complete solution. To meet the demands for lower loss and higher power density, higher efficiency and higher frequency must be targeted in future designs. The objective of this dissertation is to explore and propose methods to improve the power density and performance of point of load modules ranging from 10 to 600W.

For non-isolated, low current point of load applications targeting outputs ranging from one to ten ampere, the use of a three level converter is proposed to improve efficiency and power density. The three level converter can reduce the voltage stress across the devices by a factor of two compared to the traditional buck; reducing switching losses, and allowing for the use of improved low voltage lateral and lateral trench devices. The three level can also significantly reduce the size of the inductor, facilitating 3D converter integration with a low profile magnetic by doubling the effective switching frequency and reducing the volt-second across the inductor.

This work also proposes solutions for the drive circuit, startup, and flying capacitor balancing issues introduced by moving to the three level topology.

The emerging technology of gallium nitride can offer the ability to push the frequency of traditional buck converters to new levels. Silicon based semiconductors are a mature technology and the potential to further push frequency for improved power density is limited. GaN transistors are high electron mobility transistors offering a higher band gap, electron mobility, and electron velocity than Si devices. These material characteristics make the GaN device more suitable for higher frequency and voltage operation. This work will discuss the fundamentals of utilizing the GaN transistor in high frequency buck converter design; addressing the packaging of the GaN transistor, fundamental operating differences between GaN and Si devices, driving of GaN devices, and the impact of dead time on loss in the GaN buck converter. An analytical loss model for the GaN buck converter is also introduced.

With significant improvements in device technology and packaging, the circuit layout parasitics begins to limit the switching frequency and performance. This work will explore the design of a high frequency, high density 12V integrated buck converter, identifying the impact of parasitics on converter performance, propose design improvements to reduce critical parasitics, and assess the impact of frequency on passive integration. The final part of this research considers the thermal design of a high density 3D integrated module; this addresses the thermal limitations of standard PCB substrates for high power density designs and proposes the use of a direct bond copper (DBC) substrate to improve thermal performance in the module.

For 48V isolated applications, the current solutions are limited in frequency by high loss generated from the use of traditional topologies, devices, packaging, and transformer design.

This dissertation considers the high frequency design of a highly efficient unregulated bus converter targeting intermediate bus architectures for use in telecom, networking, and high end computing applications. This work will explore the impact of switching frequency on transformer core volume, leakage inductance, and winding resistance. The use of distributed matrix transformers to reduce leakage inductance and winding resistance, improving high frequency transformer performance will be considered. A novel integrated matrix transformer structure is proposed to reduce core loss and core volume while maintaining low leakage inductance and winding resistance. Lastly, this work will push for higher frequency, higher efficiency, and higher power density with the use of low loss GaN devices.

# To my family:

My parents: George III and Janet Reusch My wife: Katelyn Reusch

My daughter: Paige Reusch

My sister: Jennifer Reusch

#### **ACKNOWLEDGEMENTS**

First and foremost I would like to thank my advisor, Dr. Fred C. Lee for his guidance in my studies. His depths of knowledge and experience, along with his leadership skills have motivated me to become a better engineer and researcher. His invaluable insight and advice will remain with me for all my years. To have the opportunity to pursue my graduate studies at the Center for Power Electronics Systems has been an honor.

I am grateful to my committee members: Dr. Jaime De La Ree, Dr. Guo-Quan Lu, Dr. Khai D.T. Ngo, and Dr. Mayuresh J Patil. Their advice, experience, and encouragement have contributed significantly to my research and understanding of engineering and power electronics fundamentals.

I would like to thank my colleagues in the power management group over the years. The PMC team is a very motivated group in which all members work hard to contribute and improve the field of power electronics. Many thanks go to: Dr. Ming Xu, Dr. Q. Li, Y. Su, D. Gilham, A. Ji, M. Mu, F. Yu, Dr D. Fu, Dr. Y. Qiu, Dr. J.L. Sun, Dr. J.J. Sun, Dr. C. Wang, Dr. Y. Dong, Dr. J. Li, D. Sterk, C. Person, Dr. A. Ball, Dr. B. Lu, Dr. M. Lim, Dr. K. Lee, Y. Meng, Y. Yang, Y. Ying, D. Huang, Dr. J Zhou, Dr. Y. Ren, and Y. Sun.

I came to CPES eight years ago in the middle of my undergraduate studies and my stay at CPES has been a pleasure. The excellent faculty and staff has facilitated my research and provided the best resources available. I would like to thank Dr. Dushan Boroyevich, Dr. Paolo Mattavelli, Linda Gallagher, Teresa Shaw, David Gilham, Trish Rose, Doug Sterk, Marianne Hawthorne, Linda Long, Beth Tranter, Wenli Zhang, Dan Huff, Bob Martin, Jamie Evans, and Cindy Hopkins in the Graduate Advising office.

My family has been very important to my studies throughout my life. Their dedication and encouragement has allowed me to continue my education to the graduate level. I would like to thank my parents Janet and George III Reusch especially; there unwavering support throughout my life has meant more than can be put into words. I would also like to thank Jennifer Reusch, George II and Floretta Reusch, Otto Smith, Walter Reusch, Larry Smith, Chloe

Reusch, Ingrid Reusch, Bo Sperry, Loki Reusch, and Lilly Reusch. Without these people I would not have made it this far.

I would like to thank my loving wife, Katelyn Reusch, for all of her support through the years. She has always been there to support me through the good times and the bad. With her support and friendship, my years at Virginia Tech have been full of joy. I would also like to thank Paige Reusch; she has helped me understand a balance in life, always putting a smile on my face through the completion of my dissertation.

My friends have helped make my years at Virginia Tech very enjoyable. The people at CPES outside of my research group I would like to thank for their academic support as well as their friendship are: Clark Person, Tim Thacker, Arman Roshan, Anish Prasai, Andy Schmitt, David Lugo, Carson Baisden, Callaway Cass, Milisav Danilovic, Igor Cvetkovic, Hemant Bishnoi, and Jerry Francis. Outside of CPES I would like to thank my friends for all of their support: Sean Shealy, Tony Gentile, and Patrick McQuire.

Special thanks goes out to the CPES consortium members for the funding of my research: National Semiconductor, Crane Aerospace & Electronics, Chicony Power Technology Co., Ltd., Delta Electronics, Emerson Network Power, Huawei Technologies, International Rectifier, Intersil Corporation, Linear Technology, LiteOn Technology, NEC/TOKIN Corporation, NXP Semiconductors, Osram Sylvania, Power Integrations, Richtek Technology, Texas Instruments, Infineon, and the ZTE Corporation. I would also like to thank the National Science Foundation who generously endowed me as an NSF fellow to be able to pursue this research, as well as the Bradley Department of Electrical and Computer Engineering for awarding me the Bradley Fellowship. I would also like to thank ARPA-E for their funding on the project "Power Supplies on a Chip". Lastly, I would like to thank Jeff Nilles, Bijoy Chatterjee, and David Anderson of National Semiconductor/Texas Instruments for their industry collaboration and being my primary industry sponsor during my masters and PhD studies.

| Chapter 1: Introduction                                                         | 1  |

|---------------------------------------------------------------------------------|----|

| 1.1 Background of Point of Load (POL) Converters                                | 1  |

| 1.2 State of the Art POL Modules                                                | 3  |

| 1.2.1 Discrete POL Module                                                       | 3  |

| 1.2.2 Co-Packaged POL Module                                                    | 4  |

| 1.2.3 Integrated POL Module                                                     | 6  |

| 1.3 History of Integration in POL Modules                                       | 9  |

| 1.3.1 Active Layer Integration Techniques                                       | 9  |

| 1.3.2 Passive Layer Integration Techniques                                      | 14 |

| 1.4 Advanced Semiconductors for High Frequency Applications                     | 18 |

| 1.4.1 Evolution of Power Semiconductors                                         | 18 |

| 1.4.2 Evolution of Power Semiconductor Packaging                                | 21 |

| 1.5 Background of Isolate Bus Converters                                        | 23 |

| 1.5.1 Distributed Power Architecture History                                    | 23 |

| 1.5.2 State of Art Isolated Bus Converters                                      | 26 |

| 1.5.3 Distributed Matrix Transformers for High Frequency Applications           | 28 |

| 1.6 Challenges to High Density Integration                                      | 29 |

| 1.7Dissertation Outline                                                         | 31 |

| Chapter 2: Three Level Buck Converter for High Frequency, Low (POL Applications |    |

| 2.1 Introduction                                                                | 34 |

| 2.2 12V Three Level Buck Converter                                              | 39 |

| 2.2.1 Three Level Buck Converter Operating Principles                                                          | 40       |

|----------------------------------------------------------------------------------------------------------------|----------|

| 2.2.2 Passive Size Reduction of Three Level Buck Converter                                                     | 42       |

| 2.2.3 Flying Capacitor Selection                                                                               | 44       |

| 2.2.4 Advantages of Low Voltage Devices                                                                        | 47       |

| 2.2.5 Experimental Results                                                                                     | 49       |

| 2.2.6 Gate Drive Design for Three Level Converter                                                              | 53       |

| 2.2.7 3D Integration with Low Profile LTCC Inductor                                                            | 54       |

| 2.3 Flying Capacitor Balancing Methods                                                                         | 57       |

| 2.3.1 Novel Flying Capacitor Balancing with Current Control                                                    | 58       |

| 2.3.2 Simulation Verification of Control Method                                                                | 61       |

| 2.3.3 Soft Startup for Flying Capacitor                                                                        | 63       |

| 2.4 Conclusions                                                                                                | 64       |

| Chapter 3: Gallium Nitride Based Transistors for High Frequency, High Current POL Applications                 | _        |

| 3.1 Emergence of Gallium Nitride Transistors                                                                   | 66       |

| 3.1.1 Introduction of Gallium Nitride Technology                                                               | 66       |

| 3.1.2 Gallium Nitride Transistor Characteristics                                                               | 69       |

|                                                                                                                | 72       |

| 3.2 Driving Gallium Nitride Transistors                                                                        | 72       |

| 3.2 Driving Gallium Nitride Transistors                                                                        |          |

|                                                                                                                |          |

| 3.2.1 Gate Drive Considerations for Gallium Nitride Transistors                                                | 73       |

| 3.2.1 Gate Drive Considerations for Gallium Nitride Transistors                                                | 73<br>76 |

| 3.2.1 Gate Drive Considerations for Gallium Nitride Transistors  3.2.2 Over Voltage Issues for Enhancement GaN | 73<br>76 |

| 3.3.2 Parasitic Inductance and Resistance Modeling                                | 88  |

|-----------------------------------------------------------------------------------|-----|

| 3.3.3 Model Verification                                                          | 89  |

| 3.3.4 Evaluation of Device Package Parasitic Influence on Switching Loss          | 90  |

| 3.3.5 Mounting of GaN LGA Package                                                 | 93  |

| 3.4 Conclusions                                                                   | 96  |

| Chapter 4: Optimization of High Density 3D Non-Isolated Point of L<br>Module      |     |

| 4.1 Introduction                                                                  | 98  |

| 4.2 Evaluating Impact of Parasitics on Loss in GaN Synchronous Buck               | 99  |

| 4.2.1 Generation 2 Design Comparisons                                             | 103 |

| 4.2.2 High Density Generation 3 Design                                            | 104 |

| 4.2.3 Low Profile Inductor Integration                                            | 108 |

| 4.3 Thermal Analysis of High Density POL Module                                   | 111 |

| 4.4 High Density DBC Module Electrical Improvements                               | 114 |

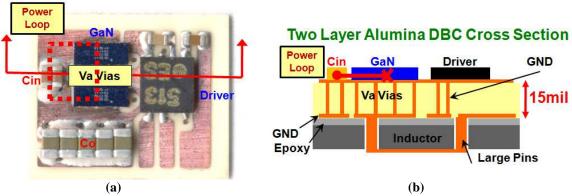

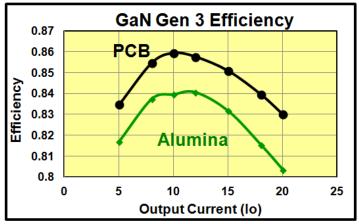

| 4.4.1 Generation 3 PCB and DBC Electrical Performance Comparison                  | 114 |

| 4.4.2 Shield Layer Impact on Performance                                          | 116 |

| 4.4.3 Generations 3 DBC and PCB Shield Layer Comparisons                          | 121 |

| 4.4.4 Generation 4 Shield Less DBC Module                                         | 126 |

| 4.5 Conclusions                                                                   | 135 |

| Chapter 5: High Density Isolated Bus Converter with Integrated Ma<br>Transformers |     |

| 5.1 Introduction                                                                  | 137 |

| 5.2 High Frequency Transformer Design                                             | 140 |

| 5.2.1 Impact of High Frequency on Transformer Size                                | 140 |

| 5.2.2 Limitations of Traditional Transformer at High Frequency       | 144 |

|----------------------------------------------------------------------|-----|

| 5.3 Matrix Transformers in High Frequency Designs                    | 152 |

| 5.3.1 Basic Principles of Matrix Transformers                        | 152 |

| 5.3.2 Matrix Transformer Modeling                                    | 156 |

| 5.3.3 Matrix Transformers in State of Art Designs                    | 158 |

| 5.4 Matrix Transformer Design                                        | 159 |

| 5.4.1 Integrated Matrix Transformer Structure with Flux Cancellation | 162 |

| 5.4.2 800kHz Silicon Experimental Verification                       | 166 |

| 5.4.3 Improved Integrated Transformer Structure                      | 169 |

| 5.5 High Frequency GaN DCX Bus Converter                             | 170 |

| 5.5.1 Benefits of GaN for High Frequency 48V Applications            | 170 |

| 5.5.2 Impact of Soft Switching on GaN Performance                    | 172 |

| 5.5.3 1.6MHz Transformer Structures                                  | 174 |

| 5.5.4 1.6MHz GaN Experimental Verification                           | 182 |

| 5.6 Conclusions                                                      | 186 |

| Chapter 6: Conclusions and Future Work                               | 187 |

| 6.1 Conclusions                                                      | 187 |

| 6.2 Future Work                                                      | 189 |

| Appendix A: GaN Analytical Loss Model                                | 190 |

| References                                                           | 199 |

### **List of Figures**

| Figure 1.1. Server motherboard and POL converters on board2                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2: Wide ranging applications for point of load converters3                                                                                                                                                                                                                    |

| Figure 1.3: Typical 12V Discrete POL Module4                                                                                                                                                                                                                                           |

| Figure 1.4: Linear Technology's co-pacakaged Vin=12V Fs=1MHz Io=12A POL converter LTM4601 (a) Top View (b) Side View5                                                                                                                                                                  |

| Figure 1.5: Enpirion's co-pacakaged Vin=5V Fs=5MHz Io=9A POL converter 5396QI (a) Top View (b) Side View                                                                                                                                                                               |

| Figure 1.6: Integrated Vin=5V Fs=2MHz Io=1A POL converter                                                                                                                                                                                                                              |

| Figure 1.7: POL Power Density Roadmap8                                                                                                                                                                                                                                                 |

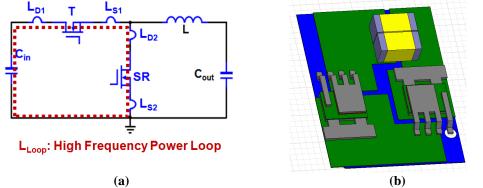

| Figure 1.8: (a) Buck Converter Schematic (b) 3D Integrated Converter9                                                                                                                                                                                                                  |

| Figure 1.9: (a) 3D Integrated POL on LTCC Inductor Substrate (b) Hardware Design10                                                                                                                                                                                                     |

| Figure 1.10: (a) 3D Integrated POL on Pyralux Substrate (b) Hardware Design11                                                                                                                                                                                                          |

| Figure 1.11: Voltage Ringing Waveforms for Design Without and With shield11                                                                                                                                                                                                            |

| Figure 1.12: Converter Efficiency With and Without Shield for Vin=5V Vo=1.1V Fs=1.3MHz                                                                                                                                                                                                 |

| Figure 1.13: (a) Power Loop Design of 3D Integrated Module with Bare Die (b) Stacked Power Hardware for Vin=5V Vo=1.2V Io=20A Fs=1.3MHz13                                                                                                                                              |

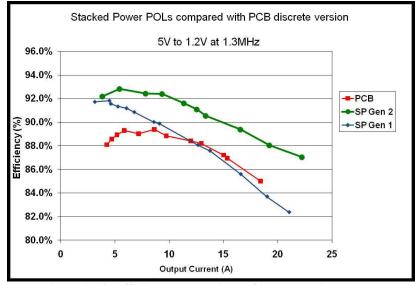

| Figure 1.14: Efficiency comparison of improved 3D module                                                                                                                                                                                                                               |

| Figure 1.15: Conventional Cooling Method for PCB design and Improved Double Sided Cooling using AlN Heat Spreading Substrate14                                                                                                                                                         |

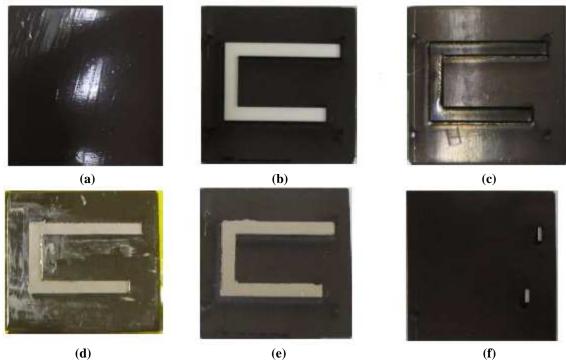

| Figure 1.16: LTCC Inductor Fabrication Procedure: (a) Bottom inductor layer (b) middle winding layer (c) Result of laminating bottom layer and middle layer with winding (d) Conductor paste (e) Bottom and middle layer with winding after conductive paste drying (f) Final inductor |

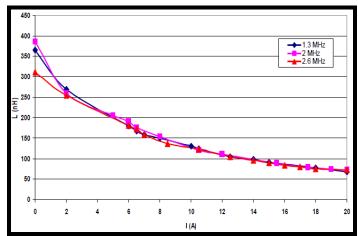

| Figure 1.17: Inductance vs Load Current for LTCC Inductor16                                                                                                                                                                                                                            |

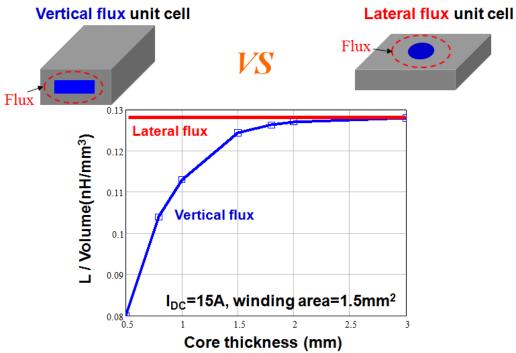

| Figure 1.18: Inductance vs Core Thickness for Vertical and Lateral Flux LTCC Inductors                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.19: (a) Hardware Designs of Vertical and Lateral Flux Inductors (b) Inductance vs Bias Current for Vertical and Lateral Flux Inductor Designs18                                         |

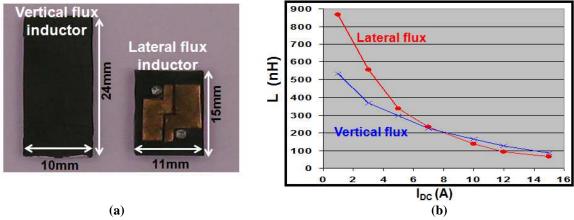

| Figure 1.20: Figure of merit comparison between Si based devices vs breakdown voltages                                                                                                           |

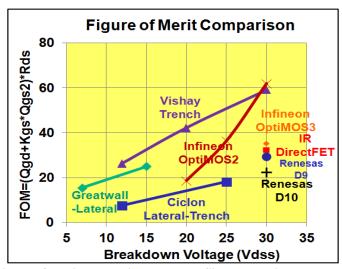

| Figure 1.21: (a) FOM vs year for SI and GaN devices (b) FOM vs breakdown voltage for current Si and GaN devices                                                                                  |

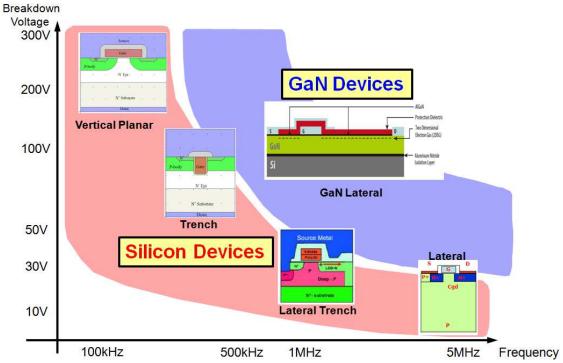

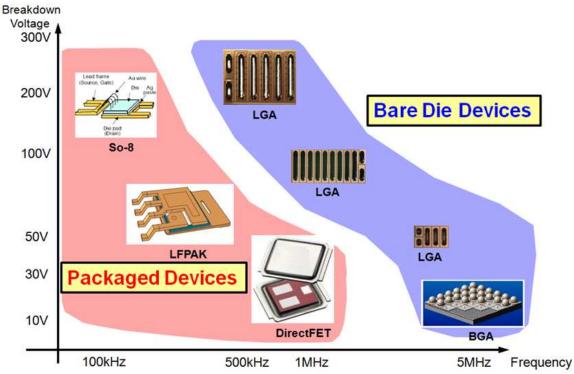

| Figure 1.22: Map for Frequency vs Breakdown Voltage for Different Device Technologies                                                                                                            |

| Figure 1.23: Different Commercial Trench Packaging Technologies (a) So-8 (b) LFPAK (c) DirectFET                                                                                                 |

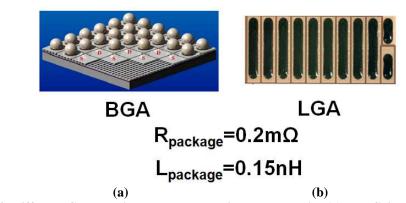

| Figure 1.24: Different Commercial Lateral Packaging Technologies (a) Ball Grid Array (b) Linear Grid Array                                                                                       |

| Figure 1.25: Map for Frequency vs Breakdown Voltage for Different Device Packaging Technologies                                                                                                  |

| Figure 1.26: Traditional Distributed Power Architecture for Telecom and High End Servers                                                                                                         |

| Figure 1.27: Intermediate Bus Architecture for Telecom and High End Servers                                                                                                                      |

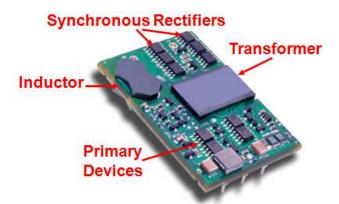

| Figure 1.28: Typical industry discrete unregulated bus converter27                                                                                                                               |

| Figure 1.29: Unregulated Bus Converter Power Density Roadmap28                                                                                                                                   |

| Figure 1.30: Vicor's B048F120T30 Vin=48V Vo=12V Io=25A Fs=1.7MHz Co-Packaged Resonant Unregulated Bus Converter                                                                                  |

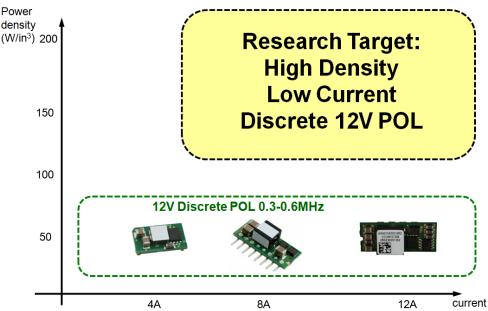

| Figure 2.1: (a) Possible applications for point of load converters (b) Discrete point of load module                                                                                             |

| Figure 2.2: Power density comparison of current discrete 12V point of load modules35                                                                                                             |

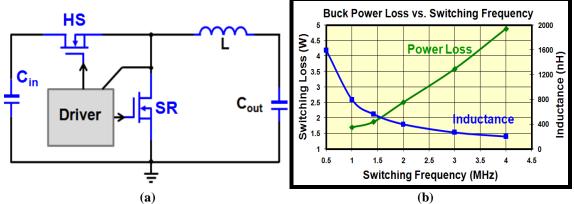

| Figure 2.3: Traditional buck converter (a) schematic (b) Power loss and required inductance (40% ripple) for Vin=12V Vo=3.3V Io=7.5A, Top switch:RJK0305, Bottom Switch:RJK0302, Driver:LM27222) |

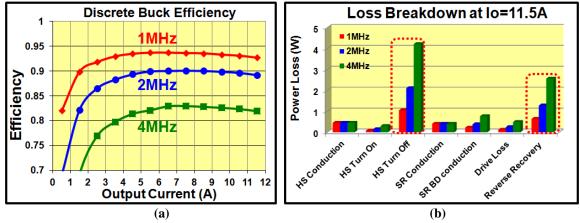

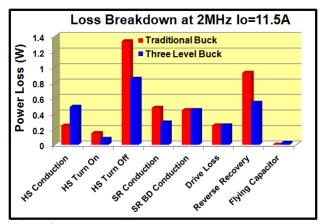

| Figure 2.4: (a) Traditional buck converter efficiency and (b) Loss breakdown for Vin=12V Vo=3.3V Io=11.5A, Top switch:RJK0305, Bottom Switch:RJK0302, Driver:LM27222)38                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

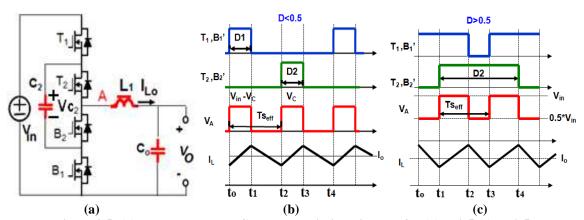

| Figure 2.5: (a) Three level Buck Converter. Timing diagram for (b)D<0.5 (c) D>0.540                                                                                                          |

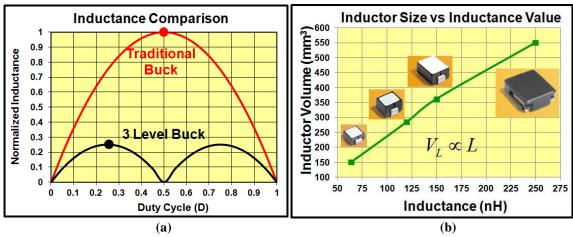

| Figure 2.6: (a) Inductance comparison with same switching frequency and inductor ripple current (b) Inductor volume vs value for commercial discrete inductors43                             |

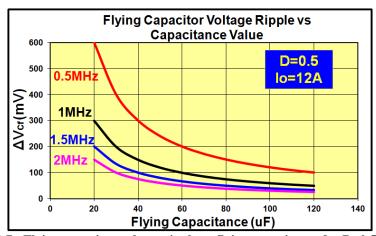

| Figure 2.7: Flying capacitor voltage ripple vs flying capacitance for D=0.5, Io=12A45                                                                                                        |

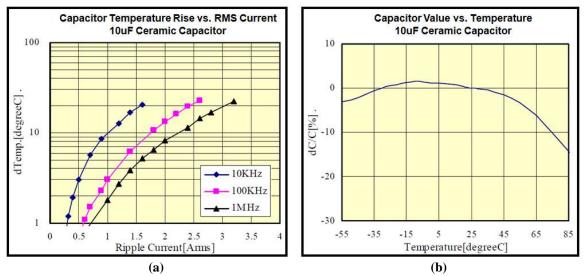

| Figure 2.8: (a) Capacitor temperature rise vs. ripple current (b) Capacitance value vs. temperature                                                                                          |

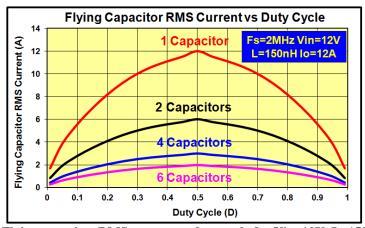

| Figure 2.9: Flying capacitor RMS current vs duty cycle for Fs=2MHz, Vin=12V, L=150nH, Io=12A                                                                                                 |

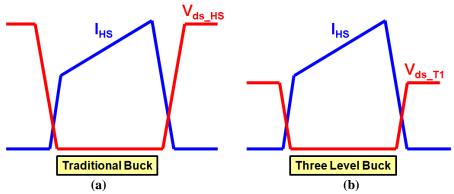

| Figure 2.10: Current and voltage waveforms of top switch in (a) Traditional buck converter (b) Three level buck converter                                                                    |

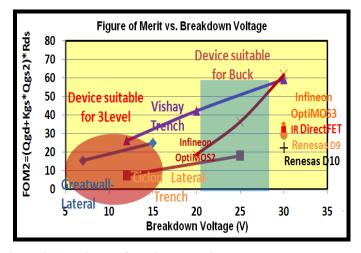

| Figure 2.11: Figure of merit comparison vs. breakdown voltage48                                                                                                                              |

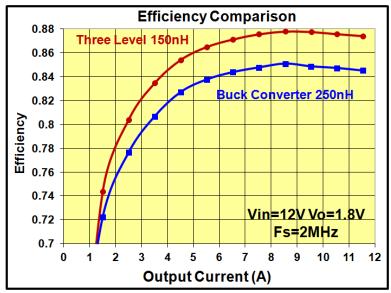

| Figure 2.12: Efficiency comparison Vin=12V, Vo=1.8V, Fs effective= 2MHz50                                                                                                                    |

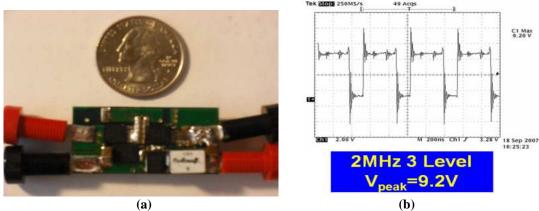

| Figure 2.13: (a) Experimental hardware (b) Three Level Buck Peak MOSFET Voltage                                                                                                              |

| Figure 2.14: (a) Synchronous buck converter parasitic loop (b) FEA model for traditional buck converter                                                                                      |

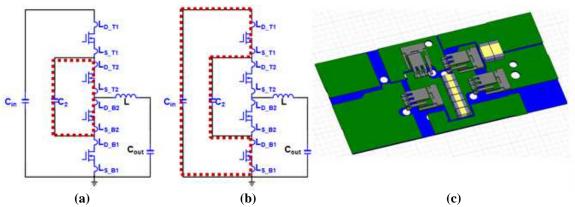

| Figure 2.15: Three level buck converter parasitic loop (a) Loop 1 for $t_2$ - $t_3$ (b) Loop 2 for $t_0$ - $t_1$ (c) FEA model of experimental hardware                                      |

| Figure 2.16: Comparison of 2MHz traditional buck and three level converter loss breakdowns                                                                                                   |

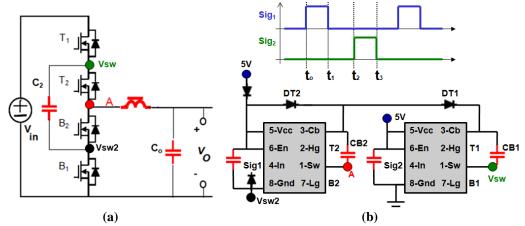

| Figure 2.17: (a) Three level buck converter schematic (b) Driver scheme and timing diagram54                                                                                                 |

| Figure 2.18: (a) 3D integrated point of load module (b) 2D point of load module                                                                                                              |

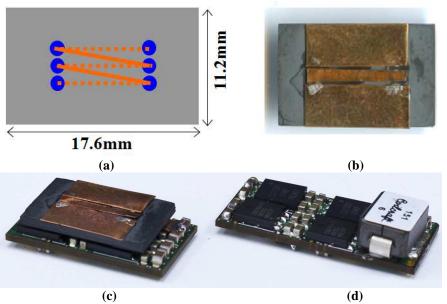

| Figure 2.19: Low profile LTCC inductor (a) Conceptual view (b) Experimental prototype. Hardware designs: (c) 3D integrated converter with LTCC inductor (d) 2D design with discrete inductor |

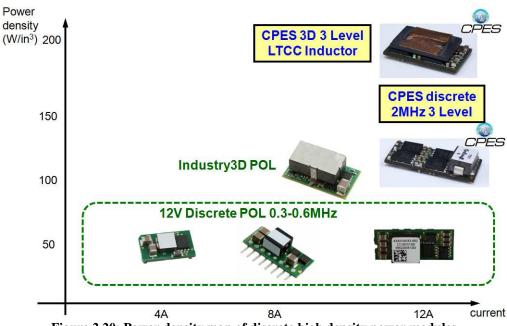

| Figure 2.20: Power density map of discrete high density power modules56                                                                                                                      |

| Figure 2.21: Circuit operation with capacitor unbalance                                                                    |

|----------------------------------------------------------------------------------------------------------------------------|

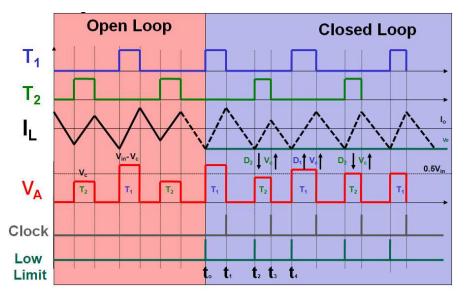

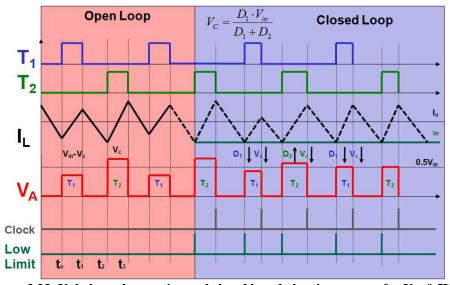

| Figure 2.22: Unbalanced operation and closed loop balancing process for Vc<0.5Vin59                                        |

| Figure 2.23: Unbalanced operation and closed loop balancing process for Vc>0.5Vin60                                        |

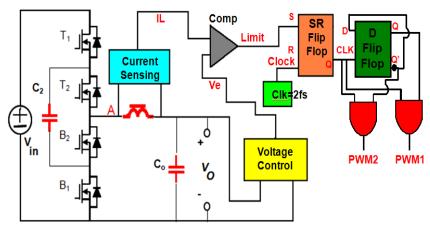

| Figure 2.24: Proposed leading edge current control scheme applied to three level buck61                                    |

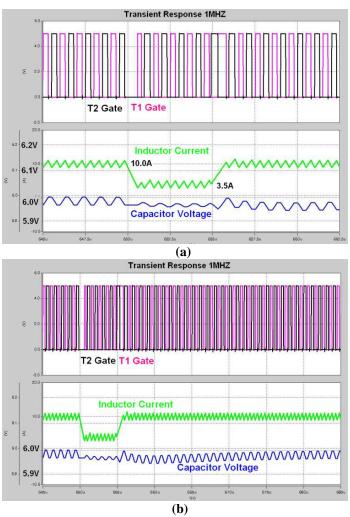

| Figure 2.25: (a) Transient Response Zoomed to Load Transient (b) Transient Response with Capacitor Rebalancing Period      |

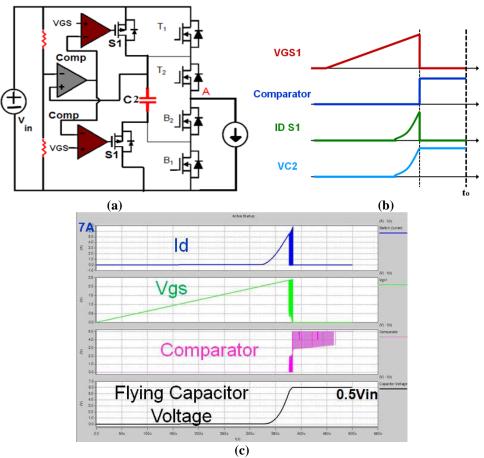

| Figure 2.26: (a) Startup Circuit (b) Conceptual Startup Waveforms (c) Simulated Startup in Saber                           |

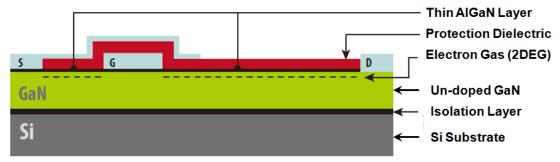

| Figure 3.1: Typical GaN lateral power transistor structure67                                                               |

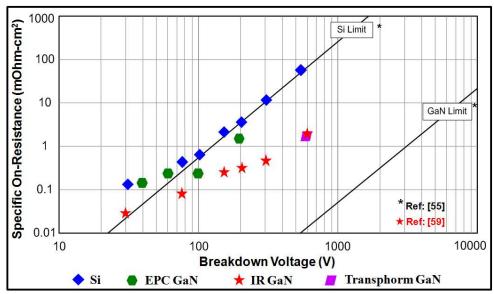

| Figure 3.2: Comparison of specific on resistance for Si and GaN68                                                          |

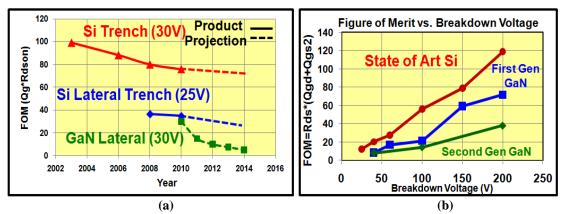

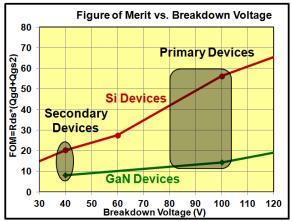

| Figure 3.3: FOM vs breakdown voltage for current Si and GaN power devices69                                                |

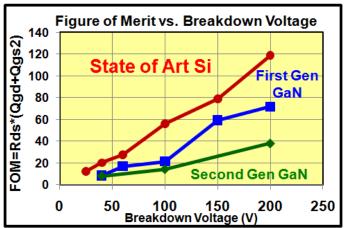

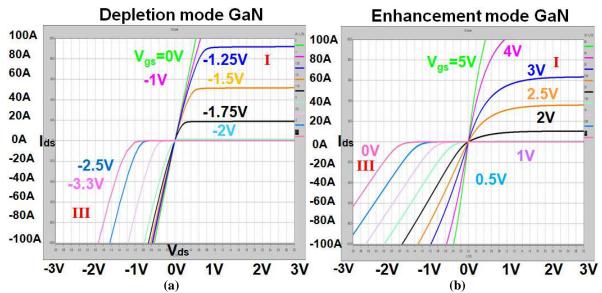

| Figure 3.4: (a) Discrete enhancement mode transistors (b) Integrated depletion mode power module70                         |

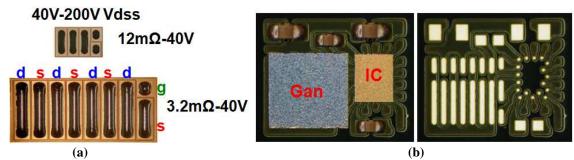

| Figure 3.5: IV curve for (a) Depletion mode GaN (b) Enhancement mode GaN72                                                 |

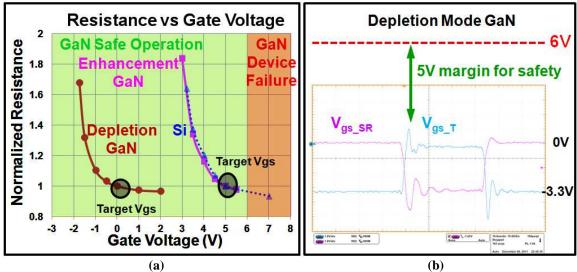

| Figure 3.6: (a) Gate drive characteristics of GaN and Si transistors (b) Gate drive signals for depletion mode GaN devices |

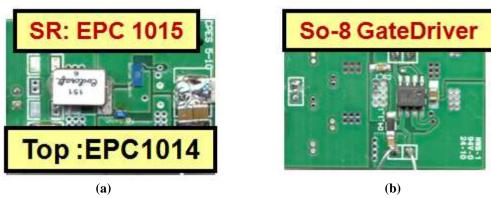

| Figure 3.7: Generation 1 enhancement GaN design (a) top view (b) bottom view74                                             |

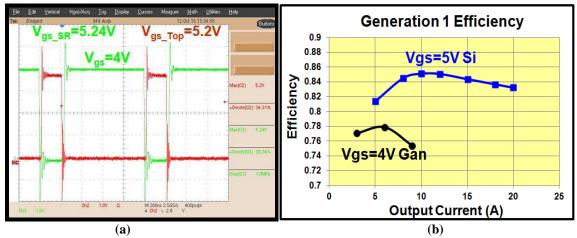

| Figure 3.8: (a) Generation 1 GaN Gate Signals at 1MHz (b) Generation 1 GaN efficiency at Vin=12V, Vo=1.2V,L=150nH74        |

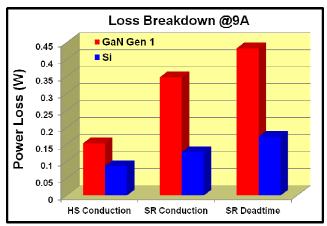

| Figure 3.9: Loss breakdown of Generation 1 GaN and Si benchmark at Vin=12V, Vo=1.2V, Io=9A,L=150nH76                       |

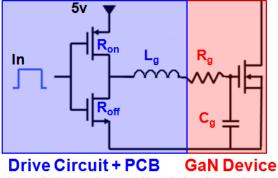

| Figure 3.10: Equivalent Circuit for Gate Ringing77                                                                         |

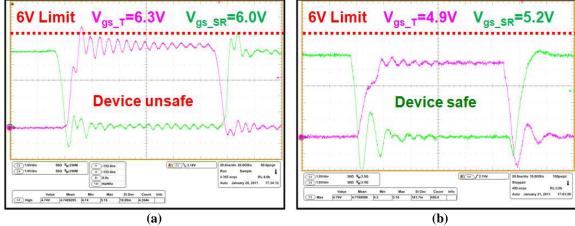

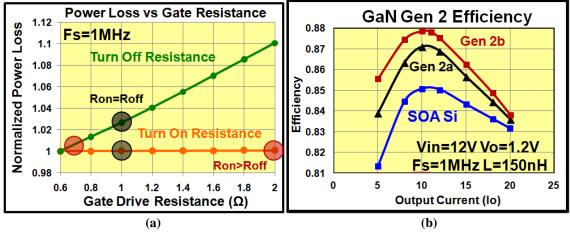

| Figure 3.11: Gate waveforms for (a) Generation 2a (b) Generation 2b79                                                      |

| Figure 3.12: (a) Gate drive resistance vs power loss (b) Efficiency for generation 2 designs80                             |

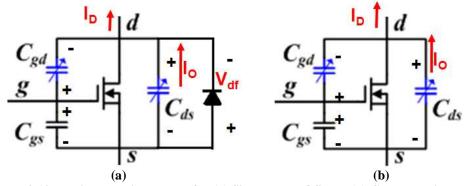

| Figure 3.13: Device electrical model for (a) Si Trench MOSFET (b) GaN Transistor81                                         |

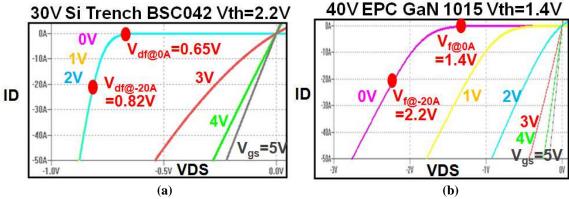

| Figure 3.14: Third quadrant I-V curve for (a) Si Trench MOSFET (b) GaN Transistor                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

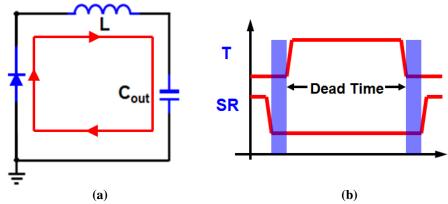

| Figure 3.15: (a) Equivalent circuit for buck converter operating during dead time (b) Timing diagram of buck converter with built in dead time83                                                                                                                      |

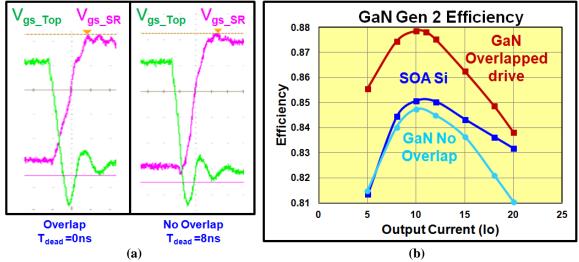

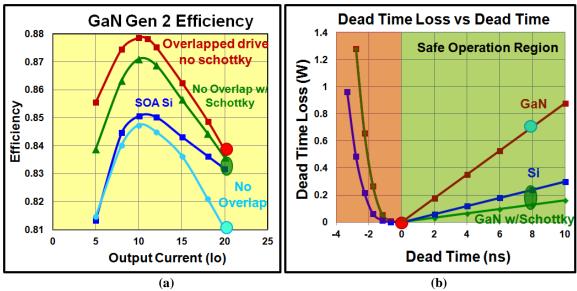

| Figure 3.16: (a) Gate drive signals for dead time efficiency comparison (b) Impact of different gating signals on efficiency (Vin=12V, Vo=1.2V, Fs=1MHz, L=150nH)84                                                                                                   |

| Figure 3.17: (a) Impact of different gating signals on efficiency (Vin=12V, Vo=1.2V, Fs=1MHz, L=150nH) (b) Dead time loss vs dead time for 1MHz designs85                                                                                                             |

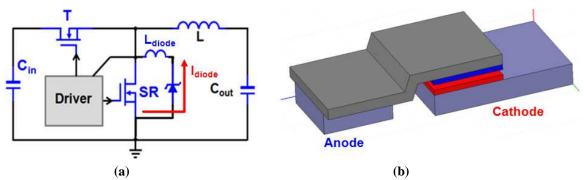

| Figure 3.18: (a) Buck converter schematic with external schottky diode (b) Maxwell Q3D model of micoSMP package86                                                                                                                                                     |

| Figure 3.19: Accurate loss model process chart87                                                                                                                                                                                                                      |

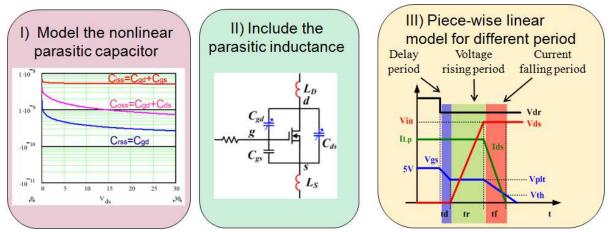

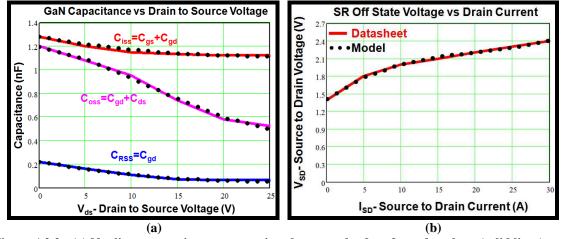

| Figure 3.20: (a) Nonlinear capacitance comparison between the data from datasheet (solid lines) and data obtained from GaN model (dotted lines) (b) Reverse drain source characteristics from datasheet (solid lines) and data obtained from GaN model (dotted lines) |

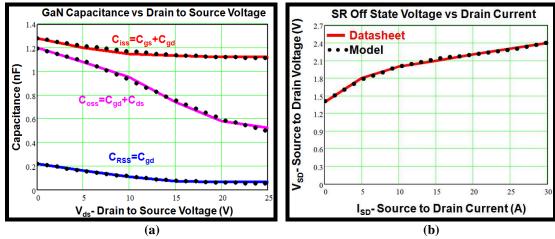

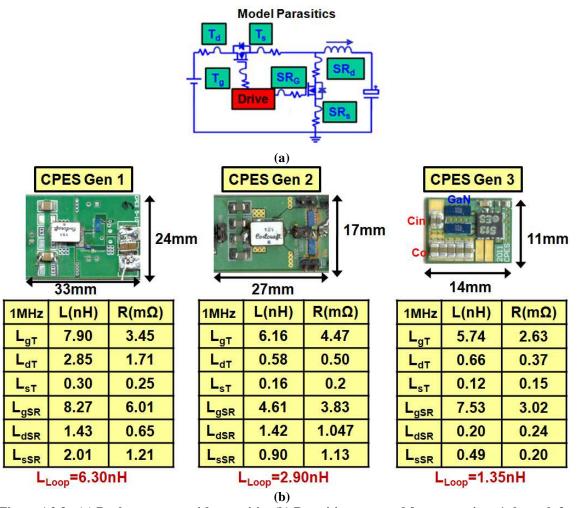

| Figure 3.21: Generation 2 (a) FEA model (b) Hardware top view (c) hardware bottom view (d) circuit model with parasitics                                                                                                                                              |

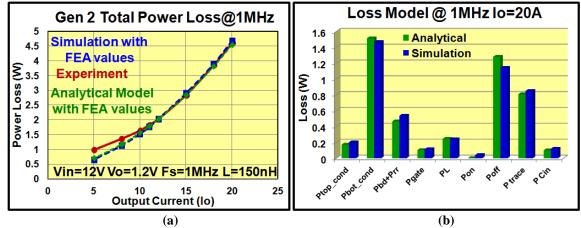

| Figure 3.22. Generation 2 GaN design with Vin=12V, Vo=1.2V, Fs=1MHz, Top switch:EPC1015, SR:EPC1015 (a) Loss comparison of simulation, experiment, and analytical model (b) loss breakdown comparison of analytical and simulated model90                             |

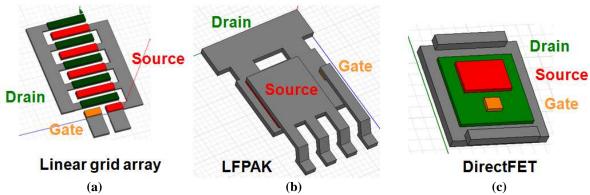

| Figure 3.23: FEA package models for (a) Linear Grid Array (b) LFPACK (c) Si DirectFET                                                                                                                                                                                 |

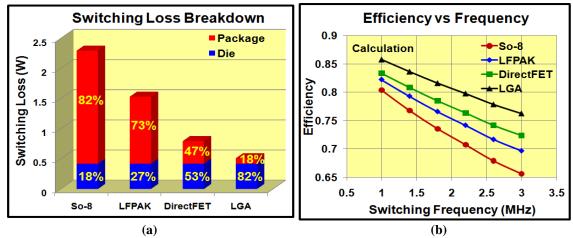

| Figure 3.24: (a) Loss breakdown for different packages (Fs=1MHz, Vin=12V, Vo=1.2V,Io=20A,L=150nH) (b) Package impact on efficiency for various frequencies (Fs=1MHz, Vin=12V, Vo=1.2V,Io=20A, $\Delta$ IL=40%Io)92                                                    |

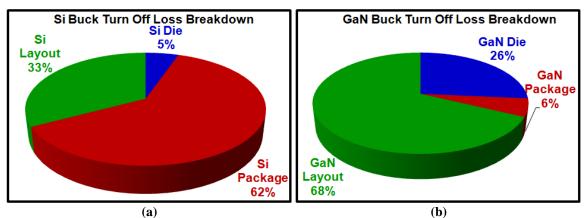

| Figure 3.25: Turn off loss breakdown of PCB layout, die, and package of (a) Si benchmark using LFPAK devices (b) GaN generation 2 design93                                                                                                                            |

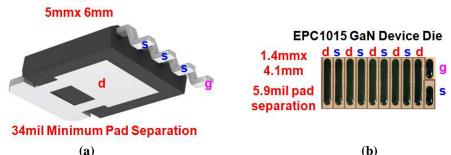

| Figure 3.26: Mounting pads for (a) 5x6mm LFPAK (b) 1.4x4.1mm GaN LGA94                                                                                                                                                                                                |

| Figure 3.27: Cross-sectional view of a die placed on a PCB with (a) stencil-printed solder paste (b) Kester TSF6502 tacky flux94                                                                                                                                      |

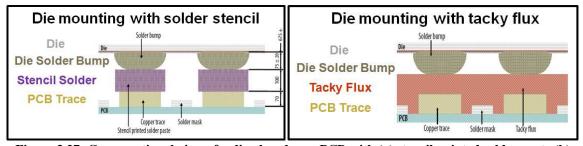

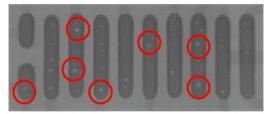

| Figure 3.28: X-Ray of GaN device with solder voiding95                                                                                                                                                                                                                |

| Figure 3.29: (a) Pick and place machine setup (b) Solder reflow station with 90° heat source95                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

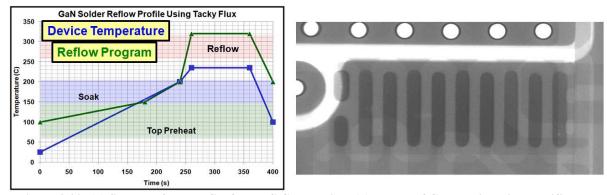

| Figure 3.30: (a) Solder reflow profile for EPC GaN devices (b) X-Ray of GaN device with modified mounting procedure without solder voiding96                                                                                                                                               |

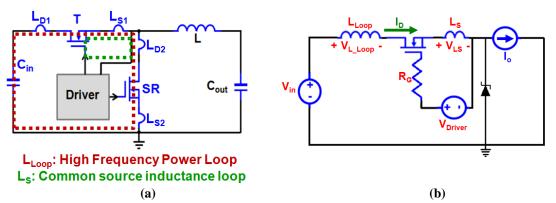

| Figure 4.1: (a) Synchronous buck converter parasitic loops (b) Equivalent circuit for top switch99                                                                                                                                                                                         |

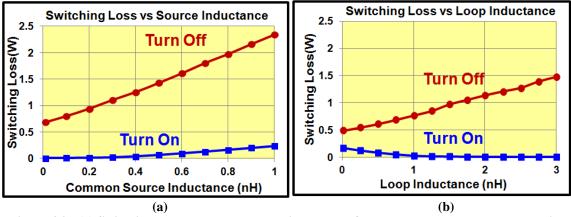

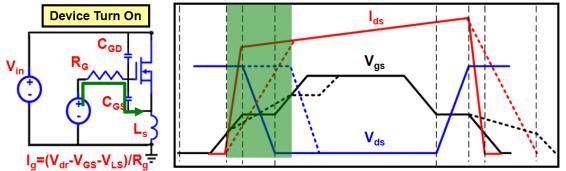

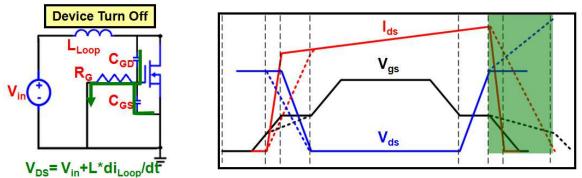

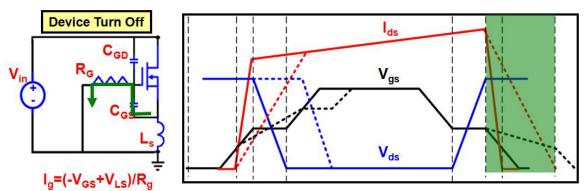

| Figure 4.2: Impact of common source inductance during device (a) turn on (b) turn off                                                                                                                                                                                                      |

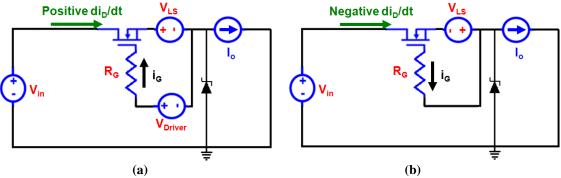

| Figure 4.3: (a) Switching loss vs common source inductance for synchronous buck converter with Vin=12V,Vo=1.2V,Io=20A, $L_{Loop}$ =1.35nH, Device:EPC1015 (b) Switching loss vs loop inductance for synchronous buck converter with Vin=12V,Vo=1.2V,Io=20A, $L_{S}$ =0.16nH Device:EPC1015 |

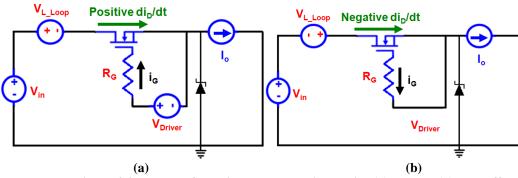

| Figure 4.4: Impact of loop inductance during device (a) turn on (b) turn off102                                                                                                                                                                                                            |

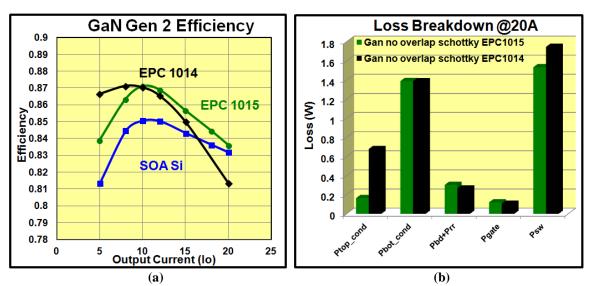

| Figure 4.5: (a) Generation 2 efficiency comparison (Vin=12V, Vo=1.2V, Fs=1MHz, L=150nH Top device=EPC1014/5 SR=EPC1015) (b) Loss breakdown103                                                                                                                                              |

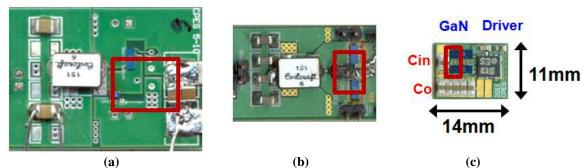

| Figure 4.6: Vin=12V, Vo=1.2V, Fs=1MHz, L=150nH GaN designs (a) Generation 1 (b) Generation 2 (c) Generation 3                                                                                                                                                                              |

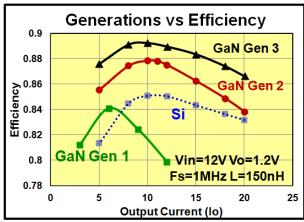

| Figure 4.7: Efficiency comparison between generations. Vin=12V, Vo=1.2V, Fs=1MHz, L=150nH Gen1 T:EPC1014, SR:EPC1015, Gen2&3 T:EPC1015, SR:EPC1015105                                                                                                                                      |

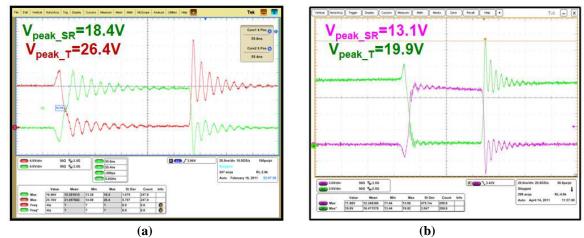

| Figure 4.8: (a) Generation 2 voltage waveforms (b) Generation 3 voltage waveforms106                                                                                                                                                                                                       |

| Figure 4.9: (a) Parasitic inductance impact on power loss (Vin=12V, Vo=1.2V, Fs=1MHz, L=150nH) (b) Loss breakdown for generations 2 and 3107                                                                                                                                               |

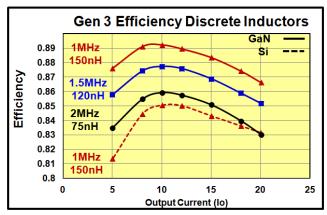

| Figure 4.10: Efficiency of GaN generation 3 at 1, 1.5, 2MHz vs Si Buck at1MHz. Vin=12V, Vo=1.2V, Si Buck: Top Device: CSD16410 SR:CSD16325 Driver:LM27222 GaN Gen 3 Devices:2xEPC1015, Driver:LM5113                                                                                       |

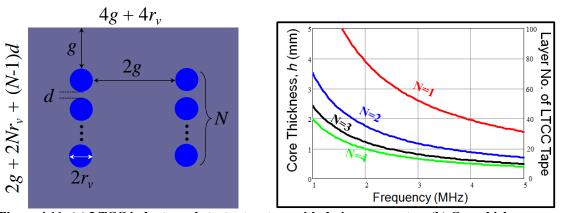

| Figure 4.11: (a) LTCC inductor substrate structure with design parameters (b) Core thickness as a function of frequency for different number of turns                                                                                                                                      |

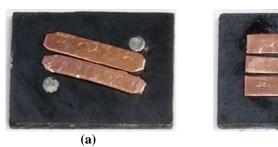

| Figure 4.12: Three turn LTCC inductor with surface winding (a) Top view (b) Bottom view109                                                                                                                                                                                                 |

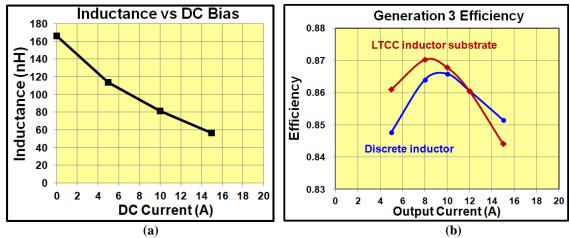

| Figure 4.13: (a) Inductance vs. DC bias current for LTCC 50 inductor (b) Efficiency for generation 3 design with discrete and LTCC inductors                                                                                                                                               |

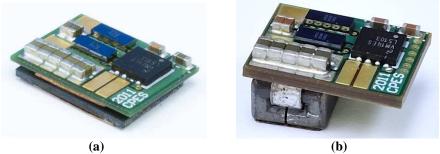

| Figure 4.14: Experimental hardware for generation 3 with (a) LTCC inductor (b) Discrete inductor                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

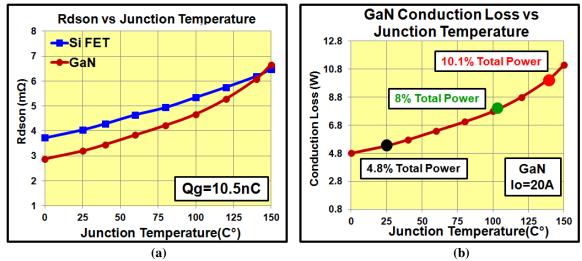

| Figure 4.15: (a) On resistance vs junction temperature for GaN and Si devices (b) Conduction loss for GaN buck converter at 20A vs junction temperature111                                                                                            |

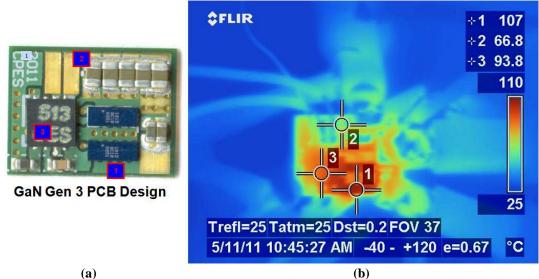

| Figure 4.16: (a) Generation 3 PCB design with corresponding temperature measurement points (b) Thermal image of generation 3 @Ta=25C Fs=2MHz Ploss=4W under natural convection                                                                        |

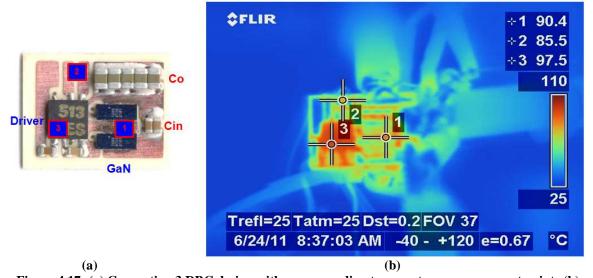

| Figure 4.17: (a) Generation 3 DBC design with corresponding temperature measurement points (b) Thermal image of generation 3 @Ta=25C Fs=2MHz Ploss=5.4W under natural convection                                                                      |

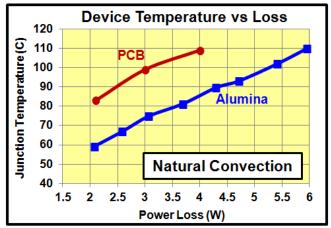

| Figure 4.18. Device Temperature vs Power Loss for generation 3 PCB and DBC designs                                                                                                                                                                    |

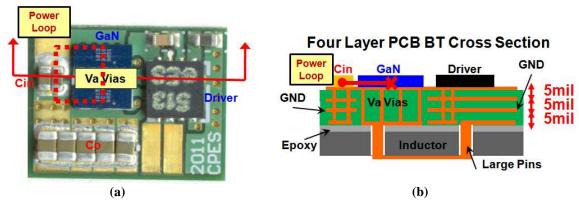

| Figure 4.19: Generation 3 PCB design (a) top view with cross cut shown in solid red (b) cross section view of 4 layer structure                                                                                                                       |

| Figure 4.20: Generation 3 DBC design (a) top view with cross cut shown in solid red (b) cross section view of 2 layer structure                                                                                                                       |

| Figure 4.21: Generation 3 PCB and DBC efficiency comparison116                                                                                                                                                                                        |

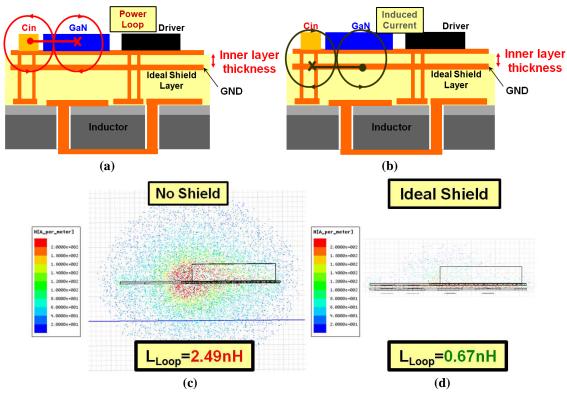

| Figure 4.22: Cross sectional view of generation 3 design (a) Flux induced by power loop (b) Induced flux and current in shield layer (c) Magnetic field intensity plot without shield layer (d) Magnetic field intensity plot with ideal shield layer |

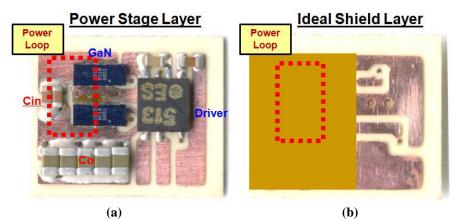

| Figure 4.23: (a) Power stage plane with high frequency power loop (b) Ideal shield layer with high frequency power loop superimposed119                                                                                                               |

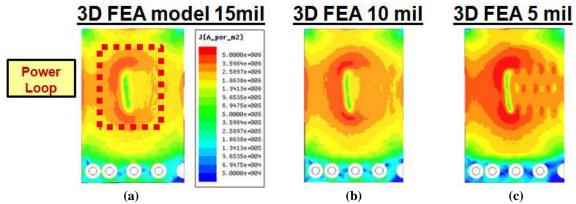

| Figure 4.24: Shield plane current density for (a) 15mil distance from power plane to shield plane (b) 10mil distance from power plane to shield plane (c) 5mil distance from power plane to shield plane                                              |

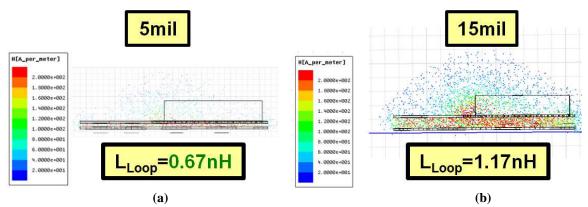

| Figure 4.25: Generation 3 DBC with ideal shield magnetic field intensity for (a) 5 mil shield separation distance from power loop (b) 15 mil shield separation distance from power loop                                                               |

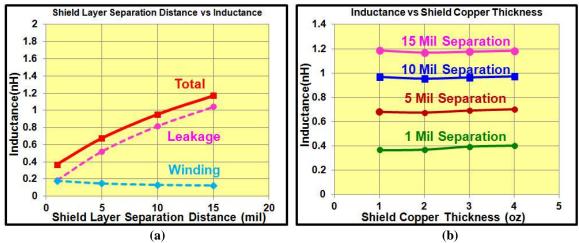

| Figure 4.26: (a) Inductance breakdown for inductance vs distance between shield layer and power plane (b) Inductance vs shield thickness for 1-15mil shield separation distances                                                                      |

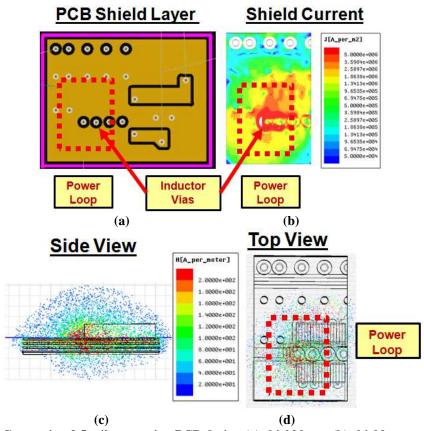

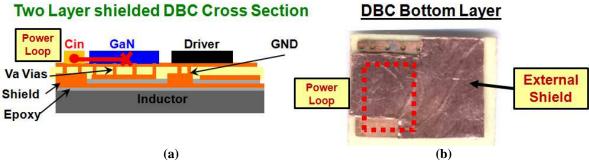

| Figure 4.27: Generation 3 5 mil separation PCB design (a) shield layer (b) shield current density (c) side view of magnetic field (d) top view of magnetic field122                                                                                   |

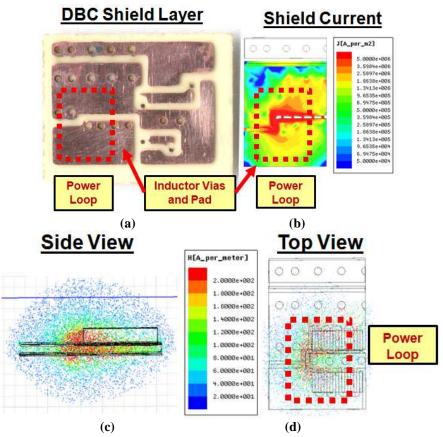

| Figure 4.28: Generation 3 15 mil separation distance DBC design (a) shield layer (b) shield current density (c) side view of magnetic field (d) top view of magnetic field123                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

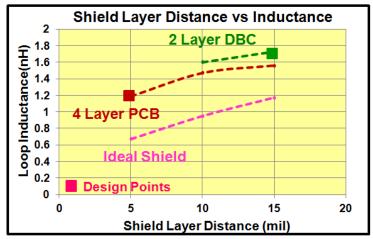

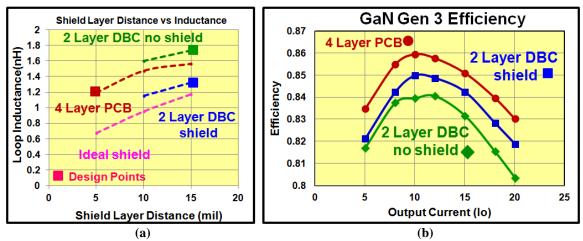

| Figure 4.29: Inductance vs distance between shield layer and power plane for different designs                                                                                                        |

| Figure 4.30: (a) Cross section view of generation 3 DBC with shield layer (b) Bottom view of DBC module with shield layer                                                                             |

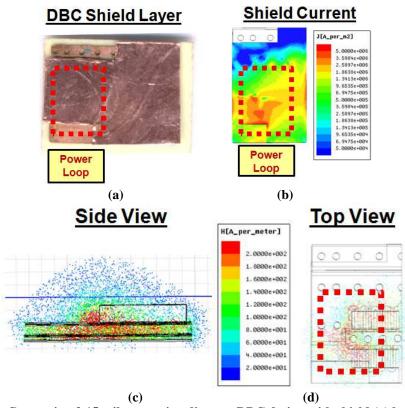

| Figure 4.31: Generation 3 15 mil separation distance DBC design with shield (a) bottom view of shield layer (b) shield current density (c) side view of magnetic field (d) top view of magnetic field |

| Figure 4.32: (a) Inductance vs distance between shield layer and power plane for different designs (b) Generation 3 PCB and DBC efficiency comparison126                                              |

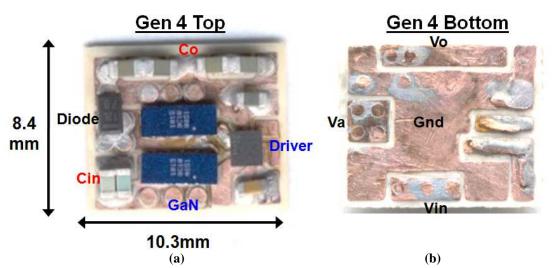

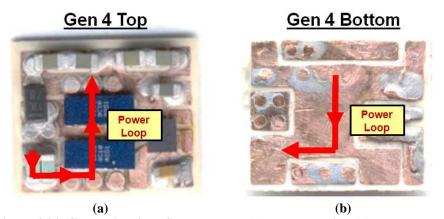

| Figure 4.33: Generation 4 DBC hardware (a) Top layer view (b) Bottom layer127                                                                                                                         |

| Figure 4.34: Generation 4 DBC power loop (a) Top layer view (b) Bottom layer128                                                                                                                       |

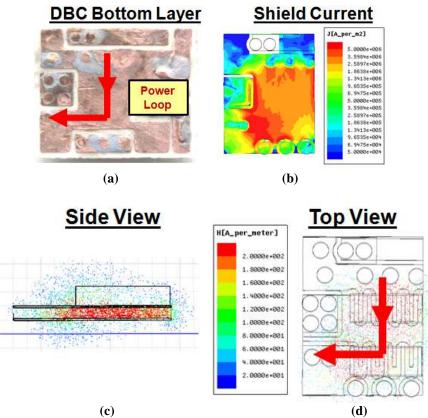

| Figure 4.35: Generation 4 15 mil separation distance DBC design (a) bottom layer (b) bottom layer current density (c) side view of magnetic field (d) top view of magnetic field                      |

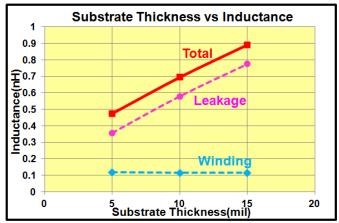

| Figure 4.36: Inductance breakdown for generation 4 inductance vs substrate thickness                                                                                                                  |

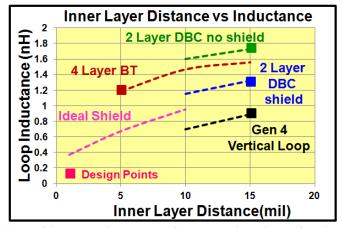

| Figure 4.37: Loop inductance for generations 3 and 4 designs130                                                                                                                                       |

| Figure 4.38: DBC module efficiency comparison (Top device:EPC1015 SR:EPC1015 Driver:LM5113)                                                                                                           |

| Figure 4.39: Synchronous rectifier conduction loop (a) Electrical diagram (b) Generation 3 (c) Generation 4                                                                                           |

| Figure 4.40: inductor connection via current distribution for (a) Generation 3 (b) Generation 4                                                                                                       |

| Figure 4.41: Device temperature vs power loss for generation 3 and 4 DBC designs at natural convection Vin=12V, Vo=1.2V, Fs=2MHz134                                                                   |

| Figure 4.42: Power density comparison of state of the art power modules136                                                                                                                            |

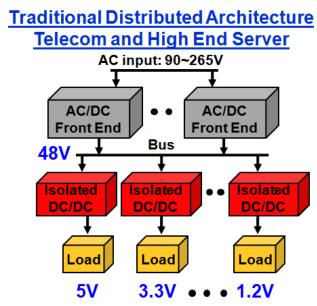

| Figure 5.1: (a) Traditional Distributed Power Architecture (b) Intermediate Bus Distributed Power Architecture                                                                                        |

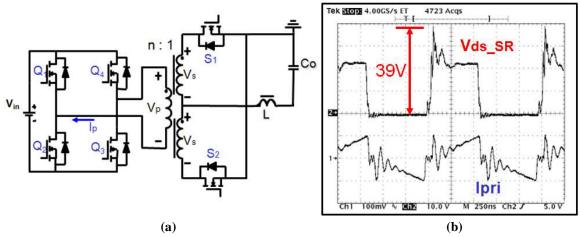

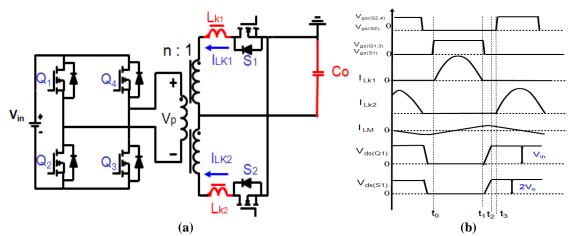

| Figure 5.2: (a) Conventional full bridge converter with center tapped rectifier (b) Operational waveforms for synchronous rectifier voltage and primary current138       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

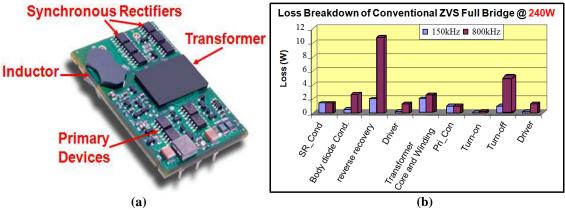

| Figure 5.3: (a) Typical Low frequency unregulated bus converter module (b) Loss breakdown for ZVS full bridge at Vin=48V, Vo=12V, Io=20 for frequencies 150 and 800kHz   |

| Figure 5.4: (a) Inductor Less Full Bridge Converter (b) Operating Waveforms139                                                                                           |

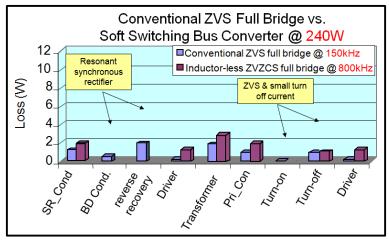

| Figure 5.5: Loss breakdown of 150kHz ZVS full bridge and 800kHz soft switching bus converter                                                                             |

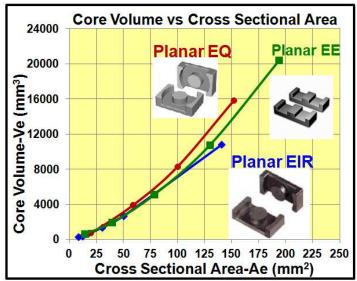

| Figure 5.6: Core volume vs cross sectional area for EQ, EE, and EIR planar transformer cores                                                                             |

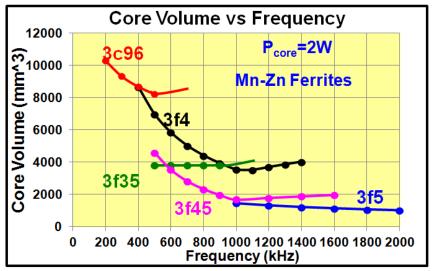

| Figure 5.7: Core volume vs frequency for EIR planar transformer for $P_{core}$ =2W, $V_{in}$ =48V, $V_{o}$ =12V, and D=0.5                                               |

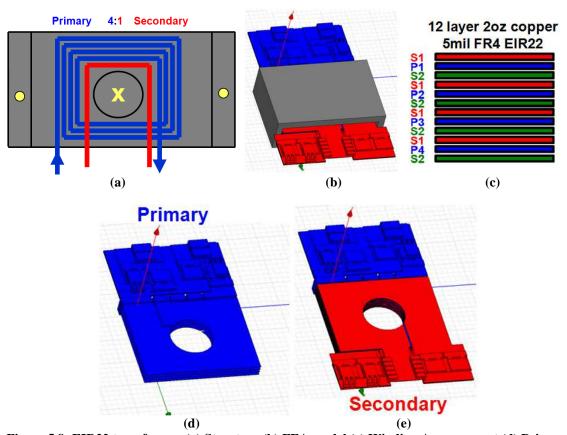

| Figure 5.8: EIR22 transformer (a) Structure (b) FEA model (c) Winding Arrangement (d) Primary winding and termination loop (e) Secondary winding and termination loop145 |

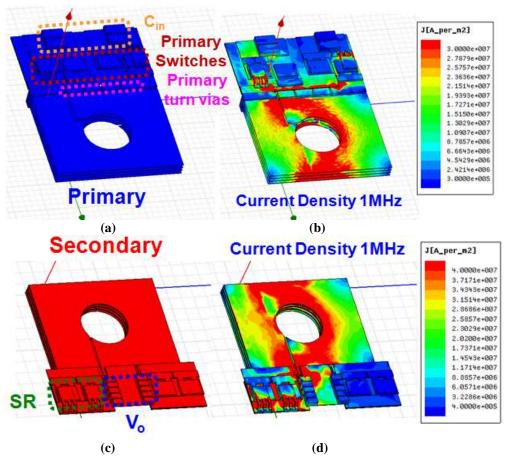

| Figure 5.9: EIR22 transformer (a) Primary winding (b) Primary winding current density at 1MHz (c) Secondary winding (d) Secondary winding current density at 1MHz146     |

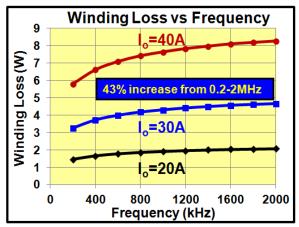

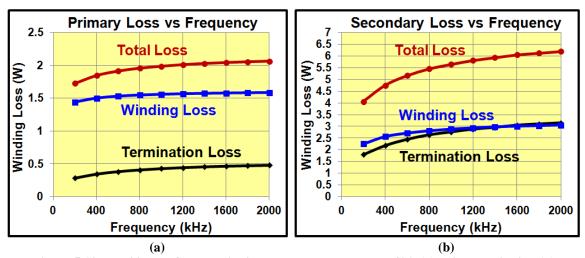

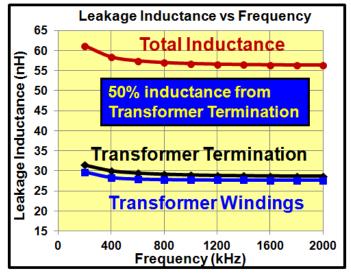

| Figure 5.10: EIR22 transformer Winding loss from 200kHz to 2MHz for Io=20A, 30A, 40A                                                                                     |

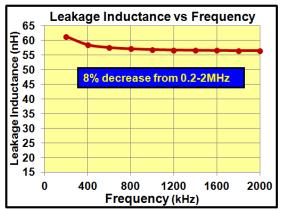

| Figure 5.11: EIR22 transformer Leakage inductance from 200kHz to 2MHz149                                                                                                 |

| Figure 5.12: EIR22 transformer field intensity plot (a) with complete design termination (b) Simplified termination                                                      |

| Figure 5.13: EIR22 transformer winding loss breakdown at Io=40A (a) Primary winding (b) Secondary winding                                                                |

| Figure 5.14: EIR22 transformer leakage inductance breakdown151                                                                                                           |

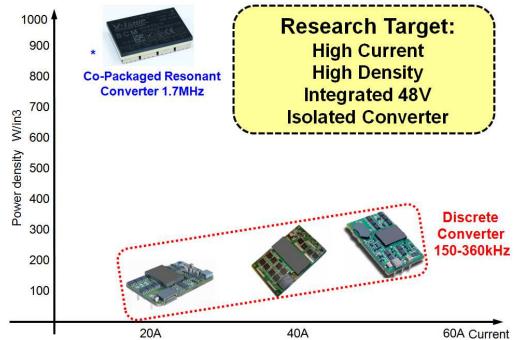

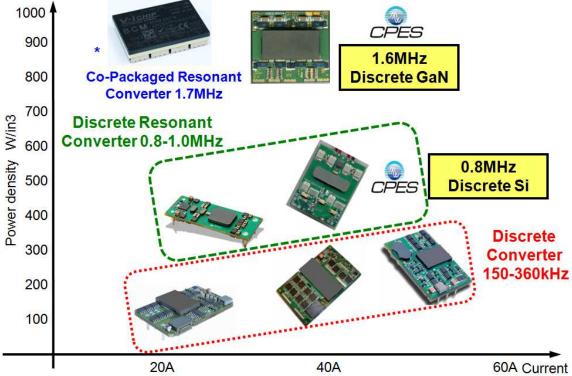

| Figure 5.15: Power density comparison of Vin=48V, Vo=12V discrete isolated bus converters                                                                                |

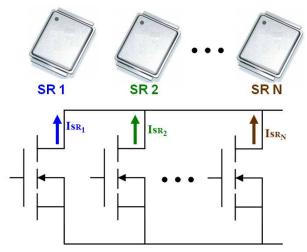

| Figure 5.16: Multiple MOSFET devices in parallel configuration153                                                                                                        |

| Figure 5.17: Matrix transformer element structure and electrical configuration154                                                                                        |

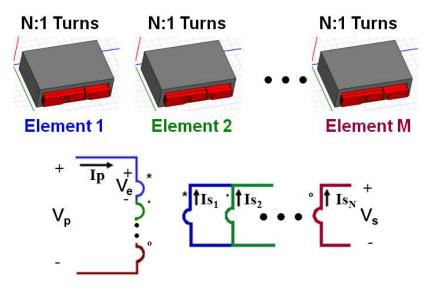

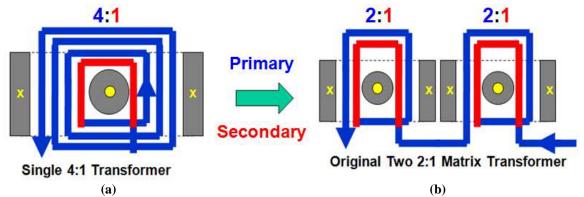

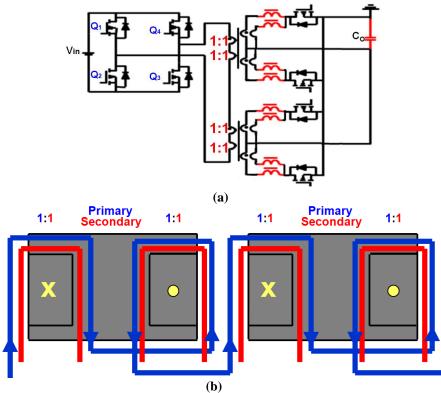

| Figure 5.18: (a) Single 4:1 transformer (b) Two 2:1 matrix Transformer (c) Four 1:1 matrix transformer (d) Equivalent transformer model                                  |

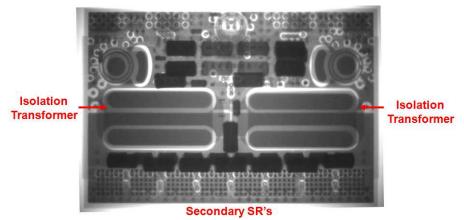

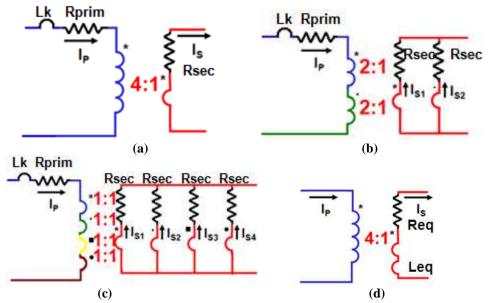

| Figure 5.19: Co-packaged module Vin=48V, Vo=12V, Fs=1.7MHz, Io=25A internal view (a) top view (b) side vide of BGA SR output for each transformer158                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

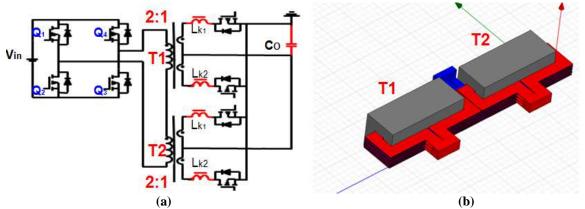

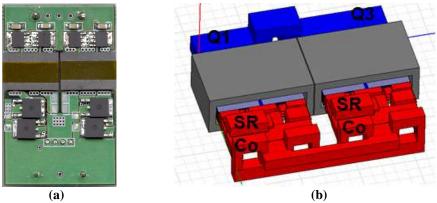

| Figure 5.20: (a) Circuit diagram for DCX with matrix transformer (b) FEA model of copackaged module Vin=48V, Vo=12V, Fs=1.7MHz, Io=25A matrix transformer structure              |

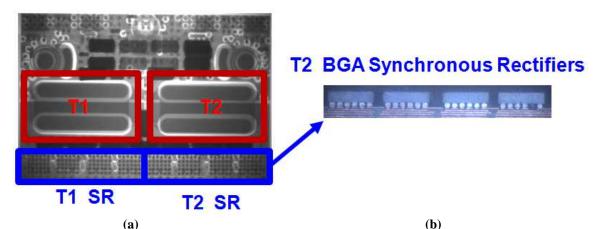

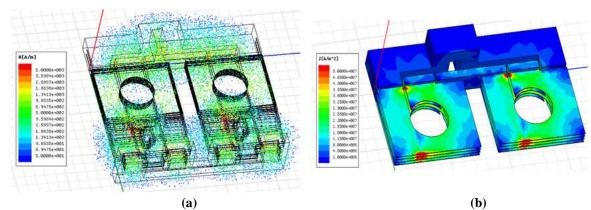

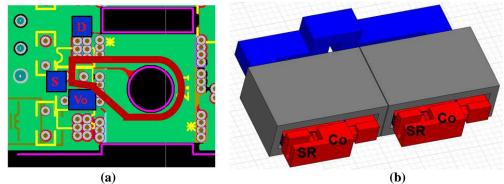

| Figure 5.21: (a) Experimental hardware for 800kHz DCX with matrix transformer (b) FEA model of Vin=48V, Vo=12V, Fs=800kHz, Io=40A matrix transformer structure160                |

| Figure 5.22: 800kHz DCX with matrix transformer (a) Field intensity plot (b) Current density plot                                                                                |

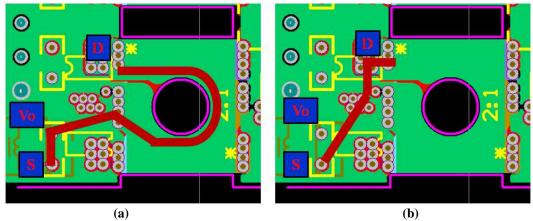

| Figure 5.23: 800kHz DCX matrix transformer element (a) Secondary current path in red through winding into output capacitor (b) Return path from capacitor to device161           |

| Figure 5.24: 800kHz DCX matrix transformer element (a) layout with improved secondary termination (b) FEA model                                                                  |

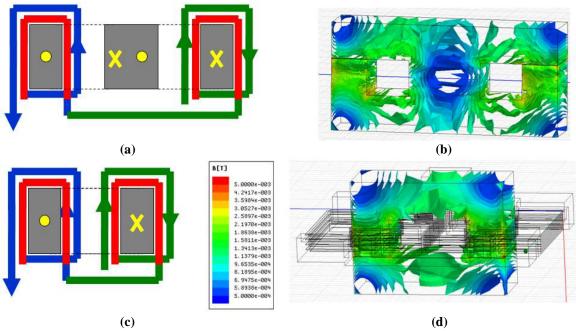

| Figure 5.25: 48V bus converter transformer structure cross sectional top view (a) Traditional single core 4:1 design (b) Two core 2x2:1 matrix transformer design163             |

| Figure 5.26: 48V bus converter transformer structure (a) Single core 2x2:1 design without flux cancellation (b) Single core 2x2:1 design with flux cancellation164               |

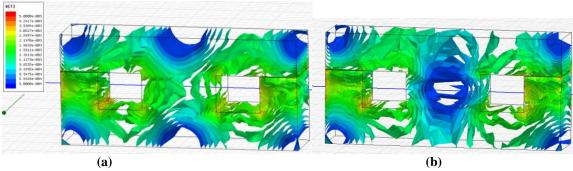

| Figure 5.27: 48V bus converter transformer core flux simulation (a) Single core 2x2:1 design without flux cancellation (b) Single core 2x2:1 design with flux cancellation165    |

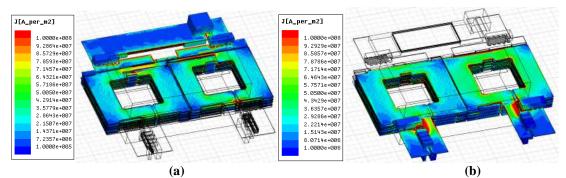

| Figure 5.28: (a) AC flux cancellation matrix transformer design (b) FEA simulation of current distribution in primary windings                                                   |

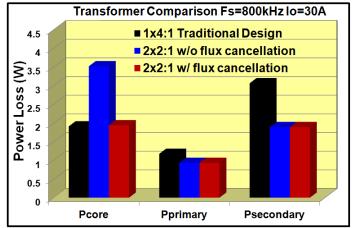

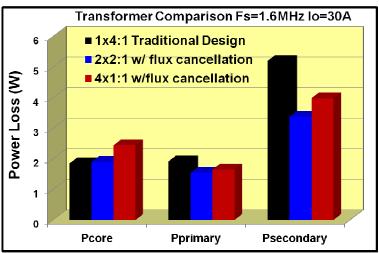

| Figure 5.29: Transformer Loss Comparison166                                                                                                                                      |

| Figure 5.30: Experimental hardware Vin=48V Vo=12V Fs=800kHz167                                                                                                                   |

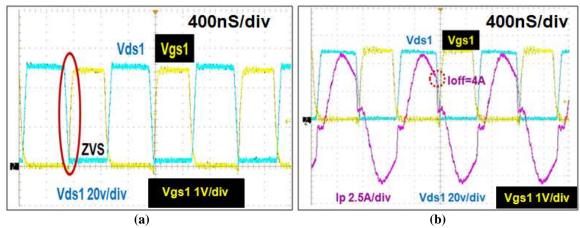

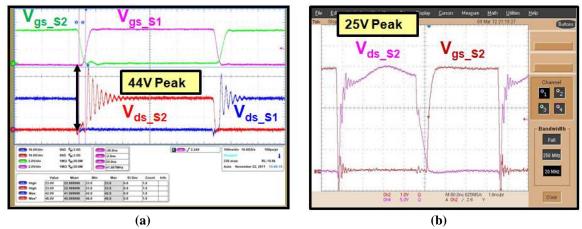

| Figure 5.31: Experimental waveforms for Fs=800kHz, Vin=48V, Vo=48V (a) Primary side device Vgs and Vds showing ZVS (b) Primary current waveform showing reduced turn off current |

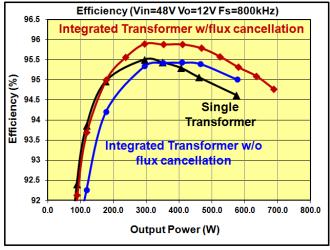

| Figure 5.32 Efficiency at Vin=48V,Vo=12V, Fs=800kHz integrated matrix transformer structures with and without flux cancellation                                                  |

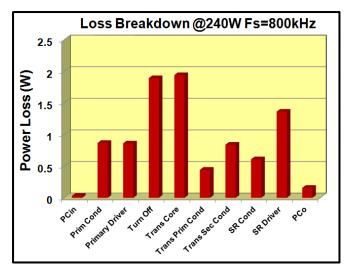

| Figure 5.33 Loss breakdown of Vin=48V,Vo=12V, Fs=800kHz, Io=20A integrated matrix transformer structures with flux cancellation169                                               |

| Figure 5.34: Integrated single core matrix structure with flux cancellation in center leg (a) Winding structure (b) Flux density distribution. Proposed integrated matrix structure without center leg (c) Winding structure (d) Flux density distribution |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.35 Figure of merit comparison for primary and secondary GaN devices for use in 48V GaN DCX bus converter                                                                                                                                          |

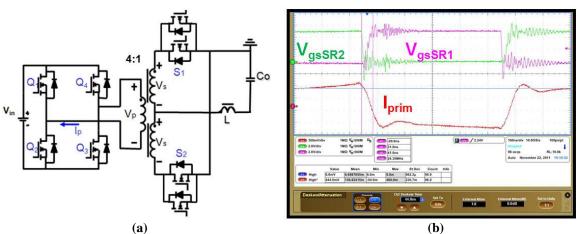

| Figure 5.36: (a) GaN hard switching FB schematic Vin=48V, Vo=12V, Primary: 4xEPC2001, SR: 4xEPC2015, L=150nH, Co=88uF (b) Primary current waveform and secondary drive voltages                                                                            |

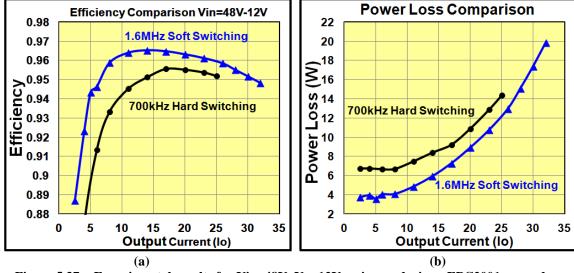

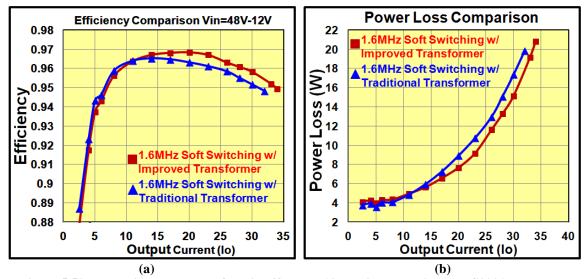

| Figure 5.37: Experimental results for Vin=48V, Vo=12V, primary devices: EPC2001, secondary devices: EPC2015, driver:LM5113(a) Efficiency comparison between 700kHz hard switching and 1.6MHz soft switching (b) Power loss comparison                      |

| Figure 5.38: Experimental waveforms for Vin=48V, Vo=12V, primary devices: EPC2001, secondary devices: EPC2015, driver:LM5113 (a) GaN hard switching secondary voltage waveforms (b) GaN soft switching secondary voltage waveforms                         |

| Figure 5.39: (a) Circuit diagram with secondary loop (b) Transformer structure of 4:1 EE transformer                                                                                                                                                       |

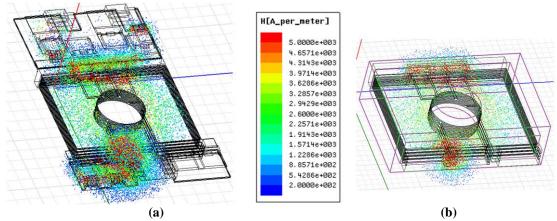

| Figure 5.40: (a) FEA model of 4:1 EE transformer (b) winding interleaving arrangement of transformer                                                                                                                                                       |

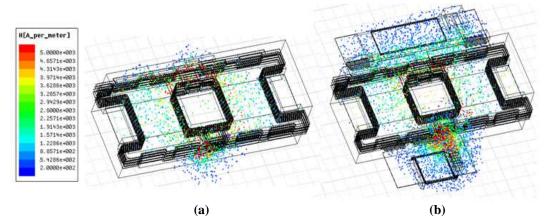

| Figure 5.41: (a) Magnetic field intensity plot of shorted transformer at 2MHz (b) Magnetic field intensity plot of design case at 2MHz177                                                                                                                  |

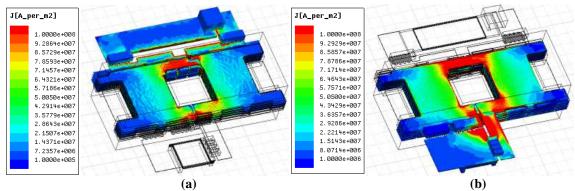

| Figure 5.42: (a) Primary winding current density at 2MHz (b) Secondary winding current density at 2MHz                                                                                                                                                     |

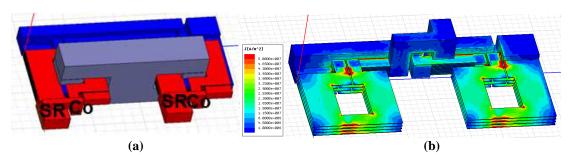

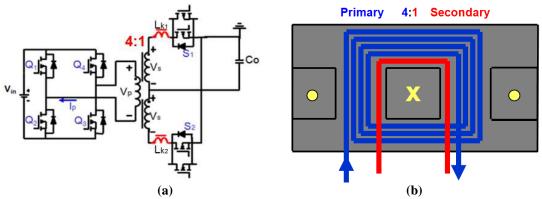

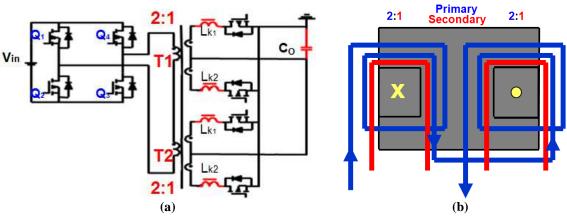

| Figure 5.43: (a) Circuit diagram with 2x2:1 distributed secondary loop (b) Transformer structure of 2x2:1 proposed integrated design                                                                                                                       |

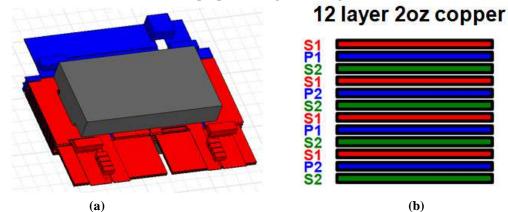

| Figure 5.44: (a) FEA model of proposed 2x2:1 integrated transformer (b) winding interleaving arrangement of transformer                                                                                                                                    |

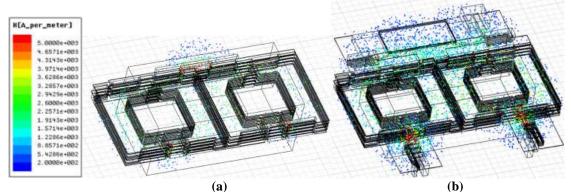

| Figure 5.45: (a) Magnetic field intensity plot of shorted transformer at 2MHz (b) Magnetic field intensity plot of design case at 2MHz180                                                                                                                  |

| Figure 5.46: (a) Primary winding current density at 2MHz (b) Secondary winding current density at 2MHz                                                                                                                                                     |

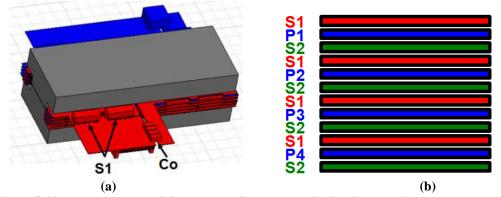

| Figure 5.47: (a) Circuit diagram with 4x1:1 transformer (b) Transformer structure of 4x1:1 using two proposed integrated structures                                                                                                                        |

| Figure 5.48: Transf                          | former Loss Comparison at 1.6MHz, Io=30A182                                                                                                                                                        |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

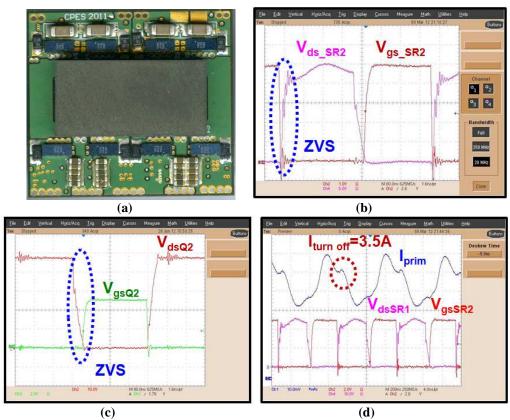

| rectifier gate and dr                        | perimental hardware Vin=48V, Vo=12V, Fs=1.6MHz (b) Synchronous ain voltages achieving ZVS (c) Primary device gate and drain voltages rimary side current waveform183                               |

| secondary devices : E<br>between traditional | imental results for Vin=48V, Vo=12V, primary devices: EPC2001, EPC2015, driver:LM5113, fs=1.6MHz (a) Efficiency comparison and improved transformer structures (b) Power loss comparison           |

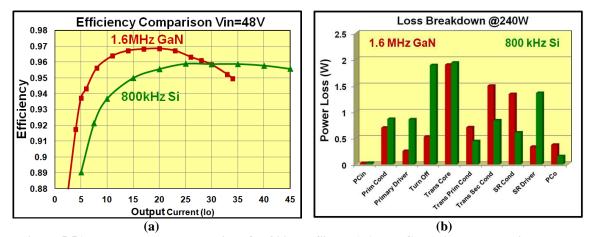

| _                                            | nverter comparison for 800kHz Si and 1.6MHz GaN with proposed nsformers (a) Efficiency curves (b) Loss breakdowns185                                                                               |

| Figure 5.52: Power of                        | lensity comparison of bus converters185                                                                                                                                                            |

| Figure A1.1: Accura                          | ate loss model process chart from [37][38]190                                                                                                                                                      |

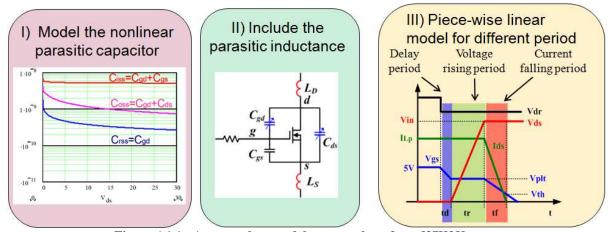

| lines) and data obtain characteristics from  | nlinear capacitance comparison between the data from datasheet (solid ined from GaN model (dotted lines) (b) Reverse drain source datasheet (solid lines) and data obtained from GaN model (dotted |

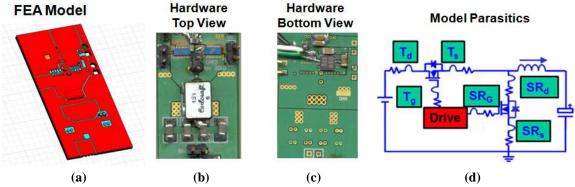

| •                                            | ck converter with parasitics (b) Parasitics extracted for generations 1                                                                                                                            |

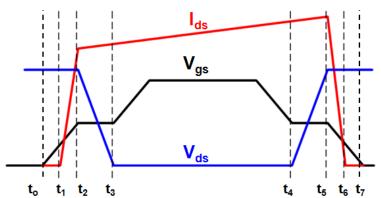

| Figure A2.4: Timing                          | diagram for ideal switching waveforms193                                                                                                                                                           |

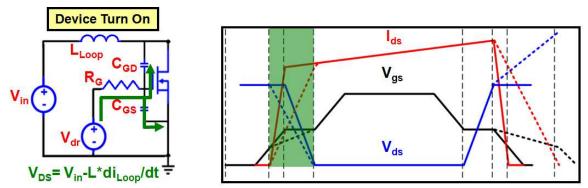

| -                                            | of high frequency loop inductance, $L_{\text{Loop}}$ , on turn on. Ideal ne, Waveforms with parasitic influence: Dashed line195                                                                    |

| _                                            | of common source inductance, $L_{\rm S}$ , on turn on. Ideal waveforms: Solid h parasitic influence: Dashed line195                                                                                |

| _                                            | of high frequency loop inductance, $L_{\text{Loop}}$ , on turn off. Ideal ne, Waveforms with parasitic influence: Dashed line197                                                                   |

|                                              | of common source inductance, $L_{\rm S}$ , on turn off. Ideal waveforms: Solid h parasitic influence: Dashed line198                                                                               |

### **List of Tables**

| Table 1.1: Material Characteristics of Si, SiC, and GaN semiconductors                   | 20        |

|------------------------------------------------------------------------------------------|-----------|

| Table 2.1: Device comparison for traditional two level and three level buck converter4   | 49        |

| Table 2.2: Parasitic comparison for traditional two level and three level buck converter | 52        |

| Table 2.3: Comparison between discrete and low profile inductor                          |           |

| Table 3.1: Material characteristics of Si, SiC, and GaN semiconductors                   | 67        |

| Table 3.2: Device parameter comparison between 40V GaN and Si enhancement power devices  | 71        |

| Table 3.3: Gate Drive Parameters for Generations 1 and 2                                 | <b>78</b> |

| Table 3.4: Turn on and turn off times for Generation 2 designs                           | <b>79</b> |

| Table 3.5: Parasitic inductances and resistances for generation 2 GaN design             | 89        |

| Table 3.6: Package inductances and resistances at 1MHz                                   | 91        |

| Table 4.1: Device characteristics of EPC1014 and EPC101510                               | )4        |

| Table 4.2: Parasitic loop inductances for generations 1,2 and 3 designs10                | 05        |

| Table 4.3: Peak device voltages for generations 2 and 3 designs10                        | 06        |

| Table 4.4: Comparison between discrete and LTCC inductor for 2MHz10                      | 09        |

| Table 4.5: Direct bond copper substrate material characteristics11                       | 13        |

| Table 4.6: Parasitic loop inductances for generations 1, 2, 3, and 4 designs13           | 31        |

| Table 4.7: Synchronous rectifier conduction loop resistances                             | 34        |

| Table 5.1: Core loss Steinmetz constants14                                               | 42        |

| Table 5.2: Core volume to cross-sectional area constants14                               | 43        |

| Table 5.3: Matrix transformer simulated leakage inductance and winding resistance — 15   | 59        |

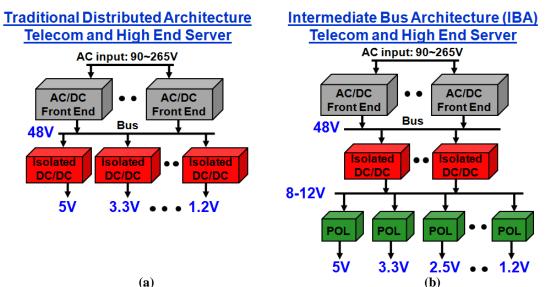

### Chapter 1

### Introduction

#### 1.1 Background of Point of Load (POL) Converters

Point of load converters are found in a variety of technologies used in everyday life, ranging from small handheld electronics to warehouse sized systems used to power server farms. As technologies have advanced over the years, so have the methods to power these complex systems. In 1965, Intel co-founder Gordon Moore established Moore's law by predicting that the number of transistors on an integrated circuit would double every two years [1]. This prediction has proved accurate and the number of transistors in the current Intel processor approaches 1 billion compared to 7.5 million ten years ago [2].

With growing processor speeds and transistor counts the power demands have also increased significantly [3][4]. In 1997, the Intel Pentium Pro processor used a single power supply to provide a maximum load current of 13.2 amperes. As the power demands of future processors grew, so did the power demands and transient response requirements of the voltage regulator (VR). The multi-phase VR was proposed by CPES to improve efficiency, transient performance, and power density [5]-[7]. As of 2011, every computer employs the multi-phase VR concept and the current multi-core server microprocessor can demand up to 180A which is supplied by as many as 8 multi-phase buck converters. The current multi-phase converters operate at lower switching frequencies, ranging from 200-600 kHz to maintain high efficiency. With lower switching frequencies, the passive components including the inductors and capacitors

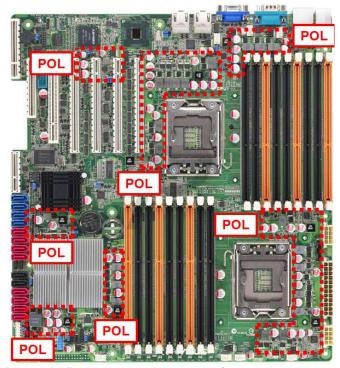

become bulky and occupy a large amount of motherboard real estate. Shown in figure 1.1 is a current server mother board, the space occupied on the mother board by power supplies is up to 30% of the overall real estate [8]. With future demands calling for higher output currents and smaller sizes, power supplies must improve power density while maintaining high efficiency.

Figure 1.1. Server motherboard and POL converters on board

The current computer and telecom applications require a large number of POL converters to power the various loads which have a wide range of currents and voltages. To simplify the design of the power management, industry leaders are migrating to a solution that does not require the power management being embedded into the PCB. The proposed shift is to a modular power management solution built from individual power blocks designed by power supply manufacturers. The power block concept allows the designers to save board space by selecting from the optimized power blocks to meet their

power requirements. To achieve higher power levels the manufacturer can use multiple point of load (POL) modules in a multi-phase configuration, providing design flexibility.

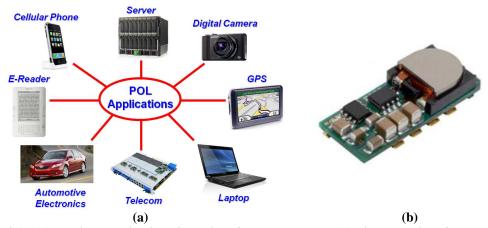

The increase in power demands is not limited just to the microprocessor. Many everyday technologies such as cellular phones, mp3 players, etc. require low current switching power supplies to efficiently convert power to the processors, graphics units, and memory of these small handheld devices. In these applications small size is paramount and high density solutions are required.

Figure 1.2: Wide ranging applications for point of load converters

#### 1.2 State of the Art POL Modules

#### 1.2.1 Discrete POL Module

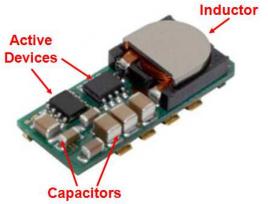

There are three different types of POL modules considered in this research. The first and most common POL available today is a discrete module. The discrete module generally contains two discrete semiconductors, a discrete driver, a discrete inductor, and

discrete output capacitors [9]. These components are connected electrically on a pcb board and connected to the mother board with external leads. These modules are available from currents as low as 3A to as high as 40A. The discrete solution operates at the lowest frequencies ranging from 200-600kHz, has the largest passive size, and offers the lowest power density in the 50-200W/in<sup>3</sup> range. The limitations in switching frequency for the discrete converter are a result of the large parasitics introduced to the converter from the discrete packaged components. At lower switching frequencies, the size of the converter is dominated by the size of the passive components, with the output inductor being the largest component.

Figure 1.3: Typical 12V Discrete POL Module

#### 1.2.2 Co-Packaged POL Module

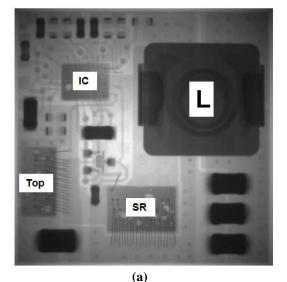

The second type of POL module is a co-packaged solution. The co-packaged solution utilizes bare die for the power devices, driver, and control circuit to reduce parasitics compared to the discrete case. For the 12V input case, the active bare dies are generally trench based devices that are connected to the PCB substrate by direct die attachment and wire bonding. The passives remain discrete components and are connected to the active layers through the PCB substrate. Shown in figure 1.4 is a top and side view of a state of the art 12V/12A co-packaged module [10]. The drain of the

top device and synchronous rectifier (SR) are connected to the PCB substrate with a direct solder connection to the die. The gate and source pads of the two sided trench power devices are connected to the PCB substrate via wire bonding with multiple bonds used for the source to decrease parasitics. The 12V co-packaged solution offers lower parasitics than the discrete case and switching frequencies are increased to the range of 0.5MHz-1MHz allowing for smaller magnetic size leading to improved power density. From the top and side view of the converter it can be seen that the inductor's volume is still substantially larger than the other components and is the major bottleneck to higher power density.

Figure 1.4: Linear Technology's co-pacakaged Vin=12V Fs=1MHz Io=12A POL converter LTM4601 (a) Top View (b) Side View. Images by author.

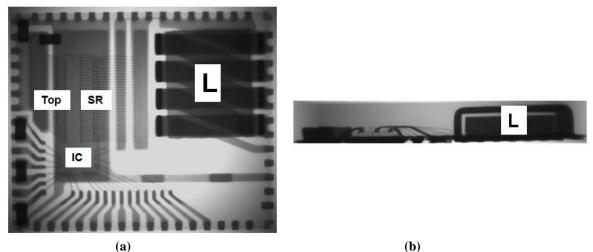

For lower voltage applications, i.e. portable electronics, a bus voltage of 5V or under is common, resulting in a large market for 3.3-5V power modules. For a copackaged POL module with a 5V input, the design of the active stage changes to a monolithic solution for the active components. For the 12V case, the driver and control chips are lateral devices and the power devices are double sided trench devices. Since the

top and SR devices in a buck converter connect the source of the top switch to the drain to the SR a monolithic die cannot be used for a trench based module.

In the 5V case, the IC and power devices both use a low voltage lateral process allowing for monolithic integration of the driver and control with the power devices. Also, in a lateral semiconductor the device connections are all on a single side of the device, this allows for monolithic integration of the power devices as a result of the source of the top device and drain of the SR being contained on the same plane. Combining reduced parasitics of monolithic integration of the active stage, a lower input voltage, and better performing low voltage lateral transistors the switching frequency can be pushed to 5MHz with current levels up to 9A [11]. For the high frequency 5V copackaged modules, the inductor size is greatly reduced, but at high currents remains a discrete component connected to the active layer through the pcb substrate. The inductor size still dominates module volume, limiting power density.

Figure 1.5: Enpirion's co-pacakaged Vin=5V Fs=5MHz Io=9A POL converter 5396QI (a) Top View (b) Side View. Images by author.

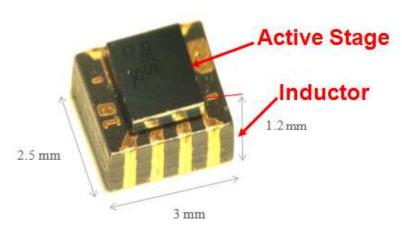

#### 1.2.3 Integrated POL Module

The third type of POL module available today is a fully integrated solution. An integrated solution uses 3D integration to mount the inductor directly to the active stage, minimizing solution footprint and improving power density. The current 3D integrated products are confined to lower input voltages (3.3V,5V) and smaller output currents (Io<1A) to allow for monolithic active stage integration, yielding higher switching frequencies and smaller output inductors [12][13]. To minimize the inductor size a multiturn inductor is used which reduces magnetic size but suffers from high winding resistance. Integrated converters operate with the highest switching frequencies ranging from 2-5MHz and offer the highest power density of all the POL modules. It should be noted however that the current integrated solutions do not integrate the input and output capacitors, which are co-packaged on the application motherboard with the module for a complete solution.

Figure 1.6: Integrated Vin=5V Fs=2MHz Io=1A POL converter

Having looked at the state of the art discrete, co-packaged, and integrated POL modules available today a trend emerges, increasing the level of integration can significantly increase converter performance and power density. To increase the level of integration, the switching frequency of the converter must be increased from the range of a couple hundred kHz to the range of multi-MHz to reduce the required passive size to a

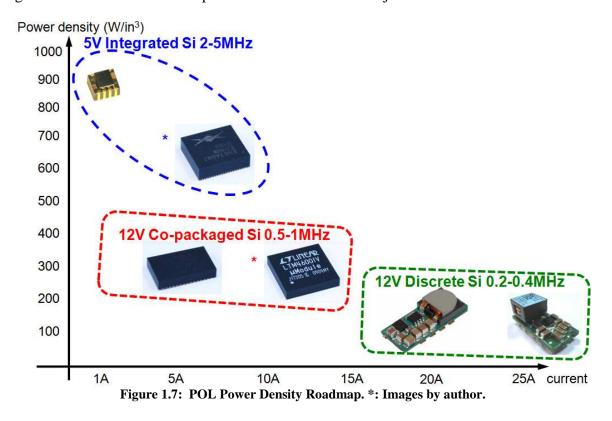

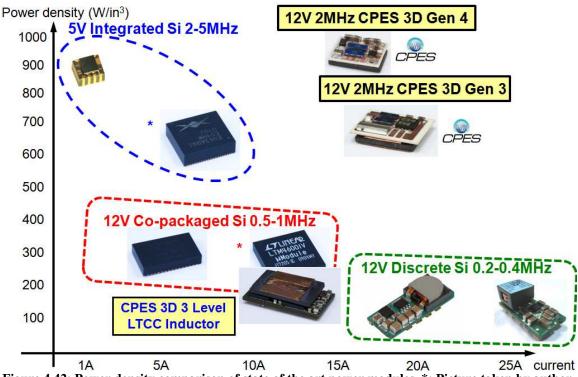

level suitable for integration. The ability to increase switching frequencies requires the use of improved semiconductors, device packaging, converter layout, and inductor design. Figure 1.7 shows the power density map of today's POL converters. For the trench based 12V POL modules, there are no integrated and few co-packaged solutions currently available, limiting the frequency and power density. For the converters with a lower 5V input voltage, higher levels of integration can be achieved through the use of monolithic lateral solutions, resulting in high power density. From the roadmap it can also be noted that the level of integration reduces significantly at higher current levels, with no product integrating the inductor above 6A of output current and co-packaged solutions being limited to under 12A.

The objective of this dissertation is to explore methods to improve high frequency performance and power density for point of load applications. The following section will give an overview of relevant previous research on the subject matter.

#### 1.3 History of Integration in POL Modules

#### 1.3.1 Active Layer Integration Techniques

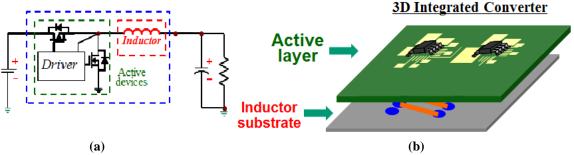

The push for integration in the POL module has been pursued very aggressively in previous research. This section will outline the previous work done to integrate the POL module for low voltage, high current applications. A major barrier to higher power density can be seen by looking at the state of the art capsulated modules in figures 1.4b & 1.5b. The inductor footprint and height make up the majority of module volume. To minimize footprint and maximize power density a 3D integration approach should be considered [14][15]. The concept of 3D integration proposes integrating a low profile inductor substrate to the active layer substrate to produce a low footprint, low profile solution. 3D integration can offer high power density and the concept is illustrated in figure 1.8.

Figure 1.8: (a) Buck Converter Schematic (b) 3D Integrated Converter

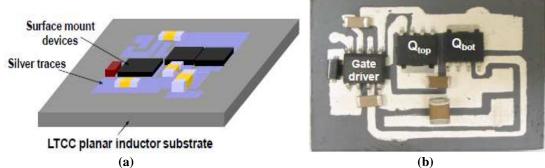

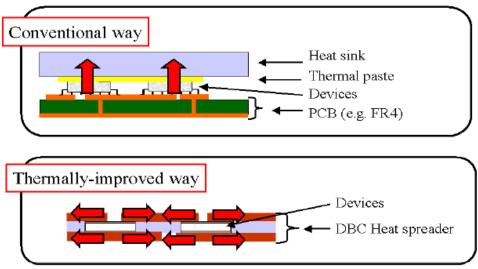

The first CPES designed 3D integrated POL, shown in figure 1.9, employed the concept of integrating the active and passive layers by building the active layer directly onto a low temperature co-fired ceramic (LTCC) based inductor substrate [15]. A proposed benefit of using the LTCC inductor as the circuit substrate was that LTCC has 10x higher thermal conductivity than traditional PCB substrates which would help distribute heat, reducing thermal design concerns. Another proposed benefit of this

approach is that the coefficient of thermal expansion (CTE) of LTCC matches more closely to Si than the PCB substrate, limiting mechanical stress of the active stage.

Figure 1.9: (a) 3D Integrated POL on LTCC Inductor Substrate (b) Hardware Design

The prototype of the 3D integrated converter built on a LTCC inductor substrate is shown in figure 1.9b. This converter was designed to run at an input voltage of 5V, output voltage of 1.1V, switching frequency of 1.3MHz, and an output current of 20A. The original experimental prototype for this design experienced low efficiency when compared to the performance of a buck converter built on a traditional PCB substrate. The cause of the low efficiency in this design was identified as interference between the inductor and the active power stage increasing the active stage parasitics. The results of increased parasitics were higher switching related losses and higher voltage ringing, increasing the voltage stress seen by the power devices.

To minimize parasitics and improve converter performance, isolation of the active and passive substrates was proposed. The isolation was achieved by using a Pyralux flex substrate to build the active layer, using an isolating copper shield layer in between the inductor and the active power stage to eliminate inductor interference on the power stage; the conceptual drawing is shown in figure 1.10a and the hardware design is shown in figure 1.10b.

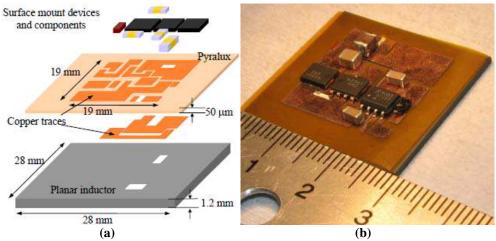

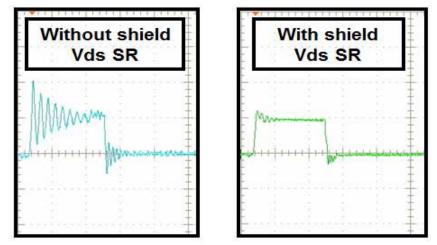

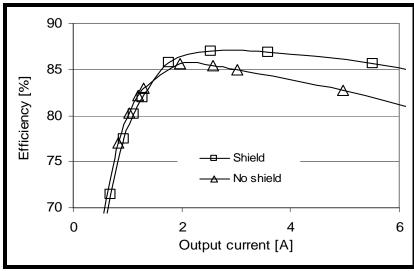

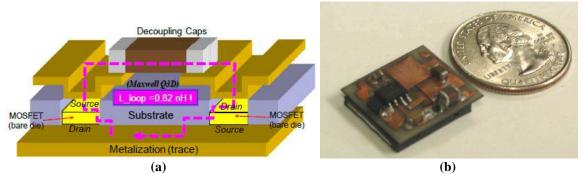

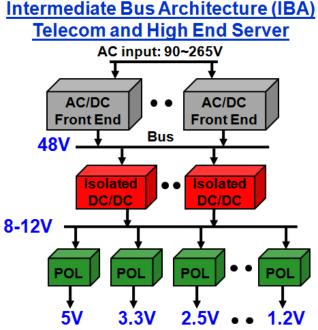

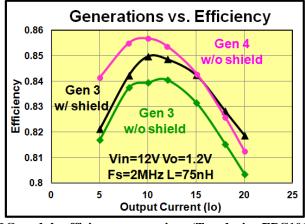

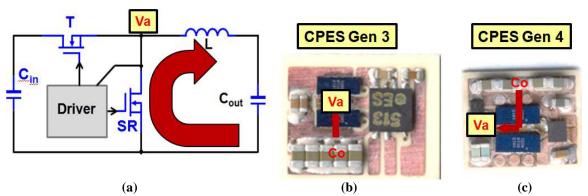

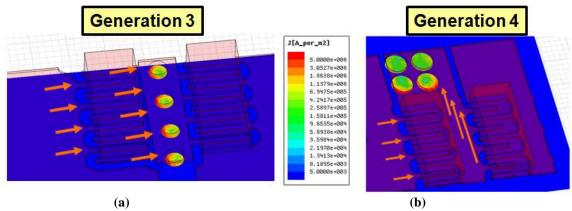

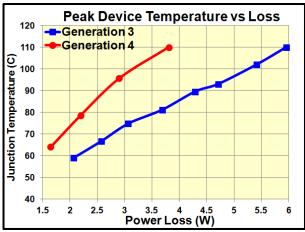

Figure 1.10: (a) 3D Integrated POL on Pyralux Substrate (b) Hardware Design