# **High Accuracy Real-time GPS Synchronized Frequency Measurement Device for Wide-area Power Grid Monitoring**

#### Chunchun Xu

Dissertation submitted to the faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

Doctor of Philosophy In Electrical and Computer Engineering

Dr. Yilu Liu (Chair)

Dr. Virgilio Centeno (Co-Chair)

Dr. Richard W. Conners

Dr. Michael S. Hsiao

Dr. Yao Liang

Dr. Tao Lin

February 20<sup>th</sup> 2006 Blacksburg, Virginia

Keywords: Power System Frequency Tracking, Frequency Disturbance Recorder, FDR, Frequency Monitoring Network, FNET, Real-time Embedded System Design, GPS, Wide-area Measurement System

Copyright © 2006, Virginia Tech

# **High Accuracy Real-time GPS Synchronized Frequency Measurement Device for Wide-area Power Grid Monitoring**

#### Chunchun Xu

#### **Abstract**

Frequency dynamics is one of the most important signals of a power system, and it is an indicator of imbalance between generation and load in the system. The Internet-based real-time GPS-synchronized wide-area Frequency Monitoring Network (FNET) was proposed to provide imperative frequency dynamics information for a variety of system-wide monitoring, analysis and control applications. The implementation of FNET has for the first time made the synchronized observation of the entire U.S. power network possible with very little cost.

The FNET is comprised of many Frequency Disturbance Recorders (FDR) geographically dispersed throughout the U.S. and an Information Management System (IMS), currently located at Virginia Tech. The FDR works as a sensor, which performs local measurements and transmits calculations of frequency, voltage magnitude and voltage angle to the remote servers via the Internet. Compared with its commercial counterpart Phasor Measurement Unit (PMU), FDR provides less expensive version for networked high-resolution real-time synchronized. The improved single phase algorithm in the FDRs made it possible to measure at 110V level which is much more challenging than PMUs due to the noise involved at this level.

This research work presents the challenges and issues of both software and hardware design for the novel measurement device FDR, which is one of the devices with the highest dynamic precision for power system frequency measurement. The DFT-based Phasor Angle Analysis algorithm has been improved to make sure the high-resolution measuring FDRs are installed at residential voltage outlets, instead of substation high-voltage inputs. An embedded 12-channel timing GPS receiver has been integrated to

provide an accurate timing synchronization signal, UTC time stamp, and unit location. This research work also addresses the harmonics, voltage swing and other noise components' impacts on the measurement results, and the optimized design of filters and a coherent sampling scheme to reduce or eliminate those impacts. The verification test results show that the frequency measurement accuracy of the FDR is within +/-0.0005Hz, and the time synchronization error is within +/-500ns with suitable GPS antenna installation. The preliminary research results show the measurement accuracy and real-time performance of the FDR are satisfactory for a variety of FNET applications, such as disturbance identification and event location triangulation.

Chunchun Xu Acknowledgement

#### Acknowledgement

I would like to express my sincere appreciations to my advisor, Dr. Yilu Liu, for her consistent guidance, encouragement and support throughout my study and life here at Virginia Tech. She is not only a successful researcher with profound knowledge and acute foresight, but also a great person with a warm heart and amazing personalities. I feel so honored to be one of her students, and I enjoy my experience working with her very much.

My sincere appreciation goes to Dr. Richard W. Conners for his invaluable guidance and leadership on the implementation of frequency disturbance recorder, and to my coadvisor Dr. Virgilio Centeno for his selfless sharing and guidance throughout my research activities. I also would like to express sincere appreciation to Dr. Michael S. Hsiao, Dr. Tao Lin, and Dr. Yao Liang for their support and serving as my committee members. The research work would not have been possible without their guidance and assistance.

Special thanks go to Dr. Fred Wang, Dr. Mark Shepard, Rajarshi Sen, and William Collard for their strong recommendation and invaluable guidance during my Co-op with General Electric, which enriched my study and professionally provided me the valuable industrial experience that I cannot get at a university. Many thanks also go to Dr. A.G. Phadke for his invaluable guidance on frequency estimation algorithm development.

It has been a great pleasure to work with the talented, creative, helpful and dedicated colleagues. I would like to express my gratitude and appreciation to all fellow students in my team: Dr. Kevin Zhong, Ryan Zuo, Dr. Henry Zhang, Dr. Steven Tsai, Lei Wang, Dr. Ling Chen, Bruce Billian, Vivian Liang, Matt Gardner, Dr. Li Zhang, Dawei Fan, Will Kook, Mark Baldwin, Jon Burgett, Kevin Khan, Keith McKenzie, Jason Bank, Jingyuan Dong, Il-Yop Chung. Also thanks to Glenda Caldwell for her administrative support.

Chunchun Xu Acknowledgement

Many thanks also go to my dear friends for all their understandings and being supportive all the time. They are Yunjun Xu, Yanli Xia, Lingyin Zhao, Ming Xu, Ping Yan, Yu Zheng, Wenduo Liu, Fenghua Chen, Asma Waqar, Kevin Yang, Xiaodan Crouch, Jian Liu, Guiqing Wang, Fei Liu, Xiangfei Ma, Tiger Zhou, Ming Leng, Jinghong Guo, Jia Wei, Jian Yin, Yang Qiu, Juanjuan Sun, Bing Lu, Gary Yao, Rao Shen, Yan Jiang, Jing Xu, Xi Xiong, Ning Zhu, Wei Dong, Dianbo Fu, Julu Sun, Yuancheng Ren, Qian Liu, Chingshan Lev.

Finally, with the deepest love, I would like to express my heartfelt appreciation to my mother Zhongfang Shi, my boy friend Chuanyun Wang, my cousins Feng Xu, Xiaoyong Gu, Xuehua Zhu, and other families for their unconditional love and providing me guidance and discipline needed for achievements. Last year, my dearest father passed away, which leaves me indescribable grief and prevents me picturing this special moment and the promising future with him. He was a great father, and there is nothing in the world could bear comparison with his kindness and love. Without him, it was impossible for me to achieve this accomplishment. Wherever he is, I know I will miss and love him forever.

Chunchun Xu Table of Contents

## **Table of Contents**

| Abstracti                                          | i |

|----------------------------------------------------|---|

| Acknowledgementiv                                  | 7 |

| Table of Contentsvi                                | i |

| List of Figures                                    | K |

| List of Tablesxii                                  | i |

| Chapter 1 Introduction                             | ĺ |

| 1.1 Scope and Background of Research Interest      | ĺ |

| 1.2 Challenges                                     | 2 |

| 1.3 Frequency Monitoring Network (FNET)            | 3 |

| 1.4 Frequency Estimation Algorithm                 | 1 |

| 1.5 Frequency Disturbance Recorder5                | 5 |

| 1.6 Dissertation Outline                           | 5 |

| Chapter 2 Frequency Estimation Algorithms Review   | 7 |

| 2.1 Frequency Estimation Algorithm                 | 7 |

| 2.2 Zero Crossing Techniques                       | 3 |

| 2.3 Leakage Effect of Fourier Transform            | ) |

| 2.4 Phasor angle analysis                          | ) |

| 2.5 Least Error Square Technique                   | 3 |

| 2.6 Kalman Filter Techniques                       | 5 |

| 2.7 Smart Discrete Fourier Transforms              | 3 |

| 2.8 Wavelet Approach                               | ) |

| 2.9 Adaptive Neural Network approach               | ĺ |

| 2.10 Summary                                       | 3 |

| Chapter 3 FDR Conceptual Design24                  | 1 |

| 3.1 Frequency Monitoring Network Architecture24    | 1 |

| 3.2 Frequency Disturbance Recorder Design Overview | 5 |

| 3.3 Phasor Angle Analysis Algorithm Implementation | ) |

| 3.4 Hardware Architecture                          | 3 |

| 3.4.1 Microcontroller                              | 2 |

| 3.4.2 Analog to Digital Converter         | 38  |

|-------------------------------------------|-----|

| 3.4.3 GPS receiver                        | 42  |

| 3.4.4 Signal Conditioning System          | 47  |

| 3.4.5 Serial to Ethernet Converter        | 50  |

| 3.5 Software Architecture                 | 56  |

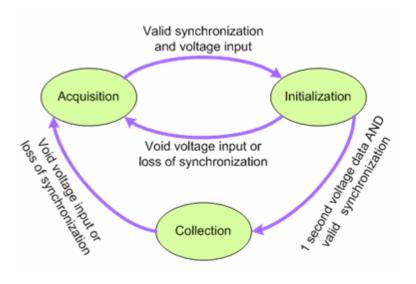

| 3.5.1 States of operation                 | 56  |

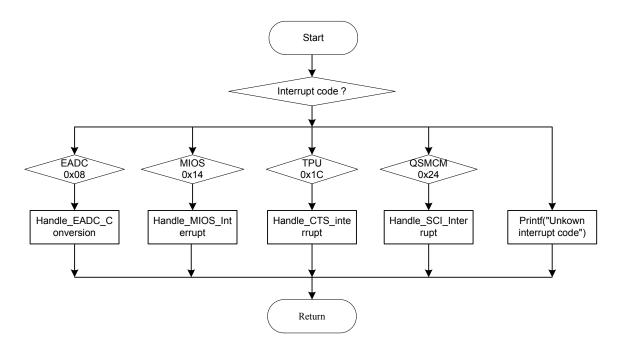

| 3.5.2 Interrupt Handling                  | 59  |

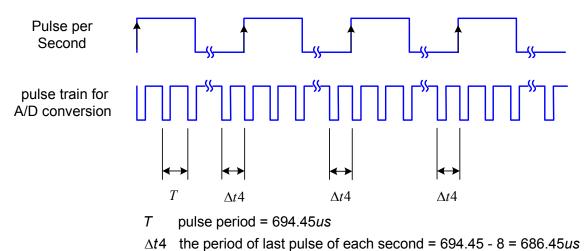

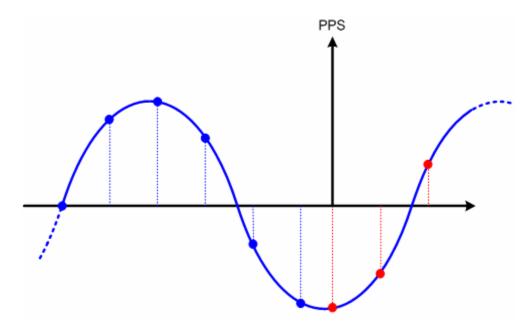

| 3.5.3 External A/D Conversion             | 61  |

| 3.5.4 MIOS                                | 63  |

| 3.5.5 QSMCM                               | 64  |

| 3.6 TPU Timing processing unit            | 65  |

| 3.6.1 GPS timing synchronization          | 67  |

| Chapter 4 Practical Implementation Issues | 71  |

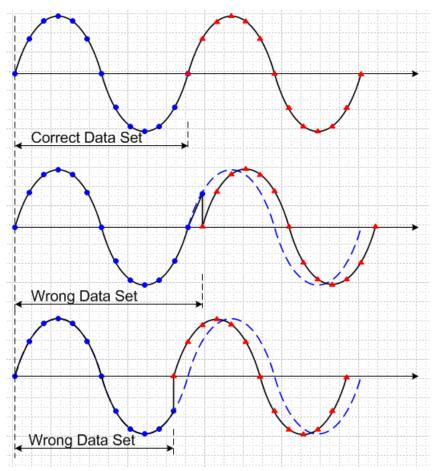

| 4.1 Coherent Sampling Issue               | 71  |

| 4.1.1 Coherent Sampling                   | 71  |

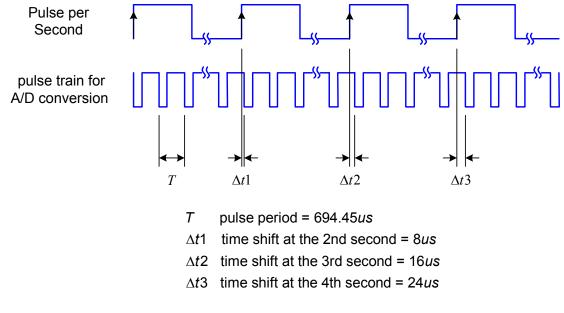

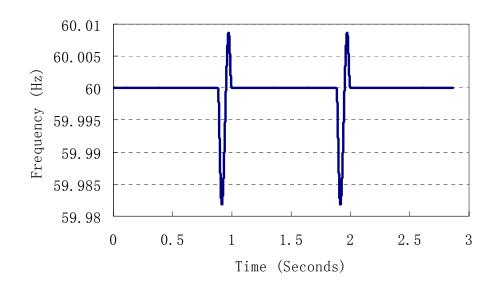

| 4.1.2 PWM Precision                       | 74  |

| 4.1.3 External oscillator                 | 77  |

| 4.1.4 Alternating over-sampling           | 80  |

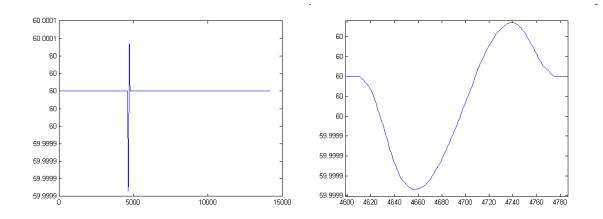

| 4.1.5 Proportional reconstruction         | 81  |

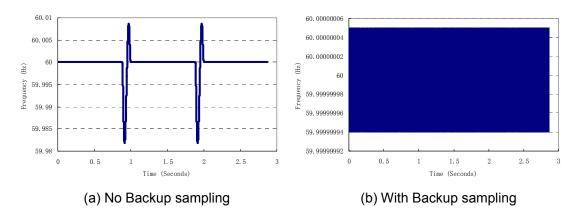

| 4.1.6 Backup sampling                     | 85  |

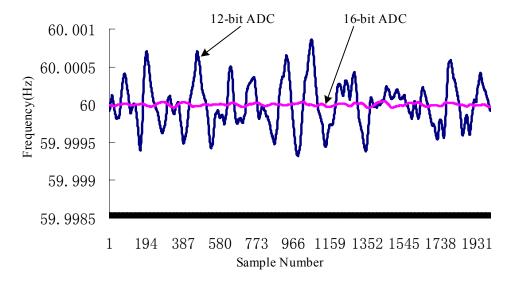

| 4.2 A/D Converter Quantization errors     | 88  |

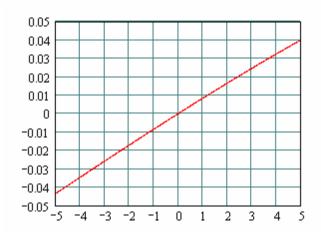

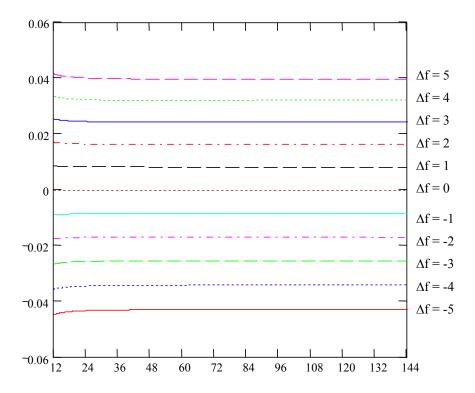

| 4.3 Off-nominal frequency component       | 91  |

| 4.4 Noise Analysis                        | 99  |

| 4.4.1 Amplitude swing effects             | 100 |

| 4.4.2 Harmonics effects                   | 101 |

| 4.4.3 Digital filter                      | 102 |

| 4.4.4 FIR moving average filter           | 104 |

| 4.4.5 IIR bandpass Butterworth filter     | 106 |

| 4.5 FDR Placement and Communication       | 106 |

| 4.6 Unit Testing and Verification Results | 110 |

| 4.7 Missing Point                         | 115 |

Chunchun Xu Table of Contents

| Chapter 5 FNET Implementation and Applications | 118 |

|------------------------------------------------|-----|

| 5.1 FNET Implementation                        | 118 |

| 5.2 FNET Applications Overview                 | 121 |

| Chapter 6 Conclusion                           | 124 |

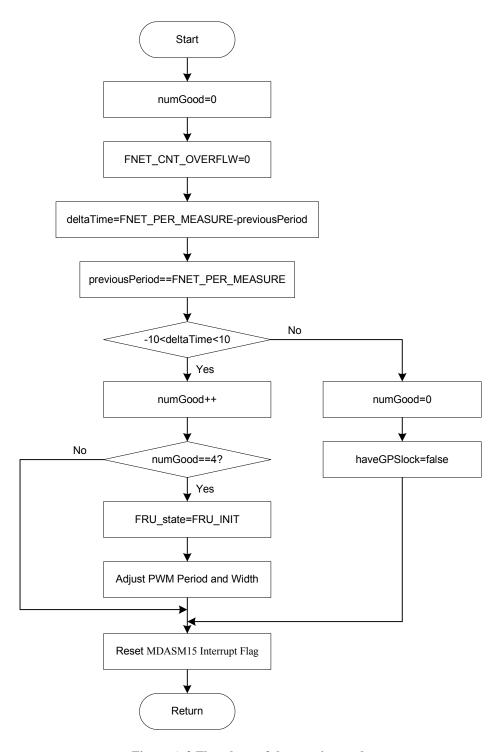

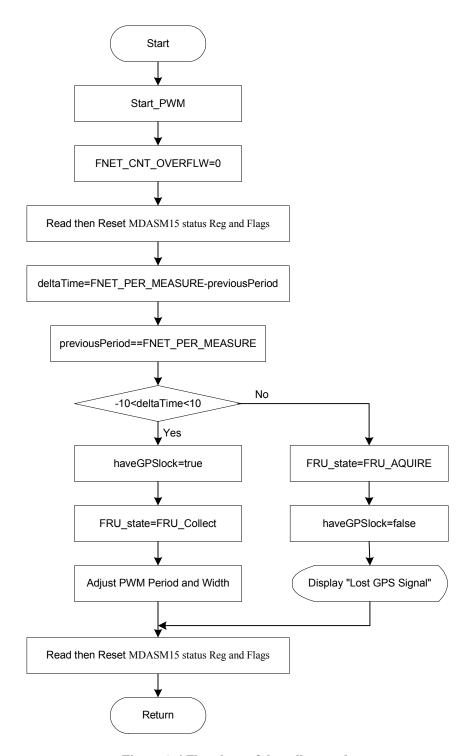

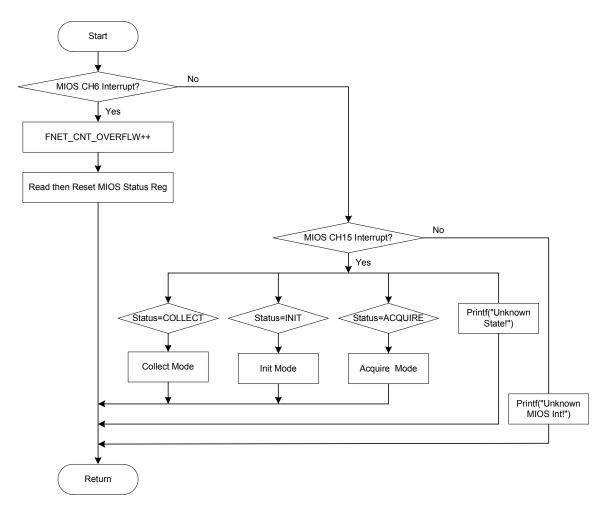

| Appendix A. Flowcharts of the FDR Firmware     | 126 |

| Reference                                      | 131 |

| Vita                                           | 136 |

Chunchun Xu List of Figures

# **List of Figures**

| Figure 2.1 Block diagram of ADALINE                                         | 22  |

|-----------------------------------------------------------------------------|-----|

| Figure 3.1 Frequency Monitoring Network (FNET) Architecture                 | 24  |

| Figure 3.2 System Block Diagram                                             | 28  |

| Figure 3.3 Appearance of Frequency Disturbance Recorder                     | 29  |

| Figure 3.4 LCD panel display                                                | 29  |

| Figure 3.5 Flow chart of frequency estimation algorithm                     | 32  |

| Figure 3.6 MPC555 block diagram                                             | 37  |

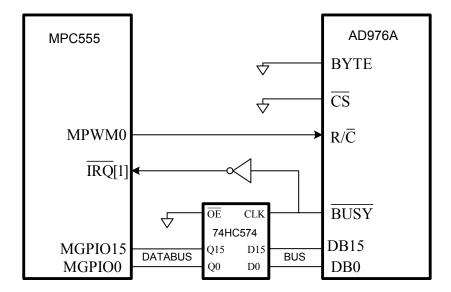

| Figure 3.7 AD976A and MPC555 interface                                      | 41  |

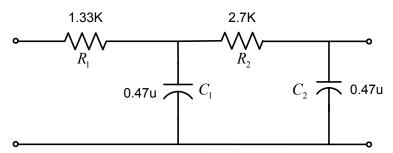

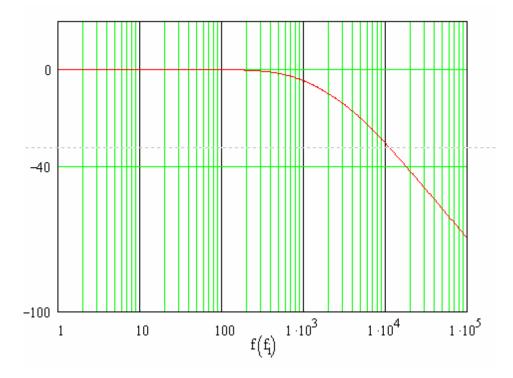

| Figure 3.8 Anti-aliasing filter                                             | 48  |

| Figure 3.9 Frequency response                                               | 49  |

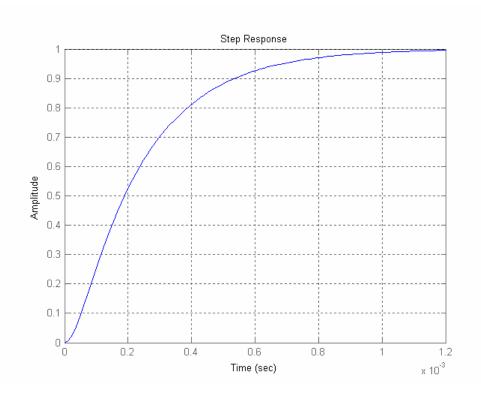

| Figure 3.10 Step response                                                   | 50  |

| Figure 3.11 Device server connection                                        | 52  |

| Figure 3.12 Top level state machine of the FDR                              | 57  |

| Figure 4.1 Sample Set with Leakage                                          | 72  |

| Figure 4.2 Method One: continuous pulses from PWM                           | 76  |

| Figure 4.3 Method Two: reset PWM each second                                | 76  |

| Figure 4.4 Phase shift phenomena                                            | 77  |

| Figure 4.5 Phase shift introduce errors in frequency measurement            | 77  |

| Figure 4.6 Step phase shift                                                 | 78  |

| Figure 4.7 Accumulated phase shift                                          | 78  |

| Figure 4.8 Estimation with Phase Shift of 0.001-degree lead                 | 79  |

| Figure 4.9 Estimation with Accumulated Phase Shift of 0.001-degree lead     | per |

| sample                                                                      | 79  |

| Figure 4.10 Improve over-sampling mechanism                                 | 80  |

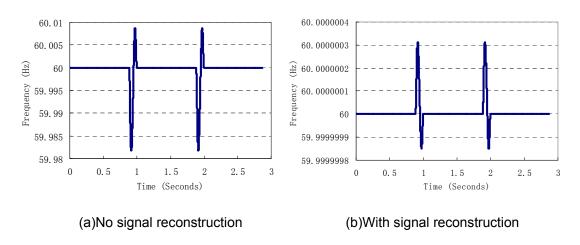

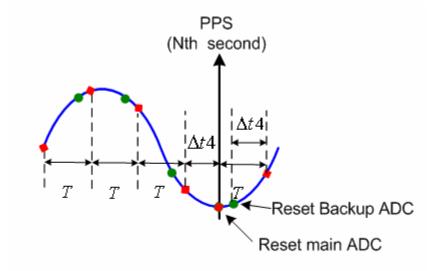

| Figure 4.11 Signal reconstruction                                           | 81  |

| Figure 4.12 Proportional reconstruction algorithm                           | 82  |

| Figure 4.13 Computation window before and after signal reconstruction       | 83  |

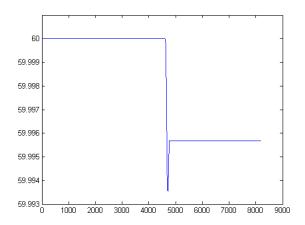

| Figure 4.14 Frequency measurement results for a 60 pure sinusoidal waveform | 83  |

Chunchun Xu List of Figures

| Figure 4.15 Frequency measurement results for a 60 sinusoidal waveform with 59   | <b>%</b> |

|----------------------------------------------------------------------------------|----------|

| 5 <sup>th</sup> harmonics                                                        | 4        |

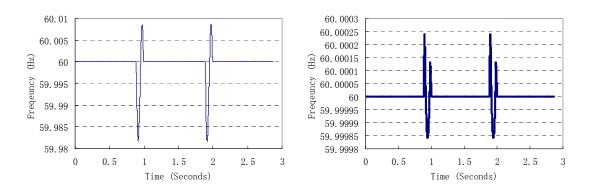

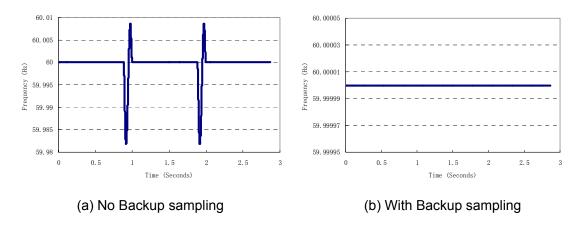

| Figure 4.16 Alternating sampling                                                 | 6        |

| Figure 4.17 Frequency measurement results for a 60 pure sinusoidal waveform 8    | 7        |

| Figure 4.18 Frequency measurement results for a 60 sinusoidal waveform with 59   | %        |

| 5 <sup>th</sup> harmonics                                                        | 8        |

| Figure 4.19Frequency estimation results of a 12-bit ADC and a 16-bit ADC 8       | 9        |

| Figure 4.20 Y term versus Δf                                                     | 1        |

| Figure 4.21 Y term effects cause by various sampling rates various Δf            | 3        |

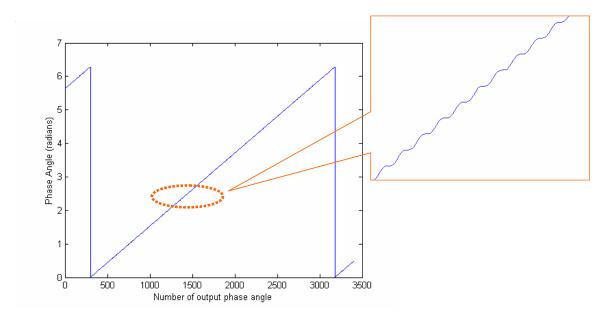

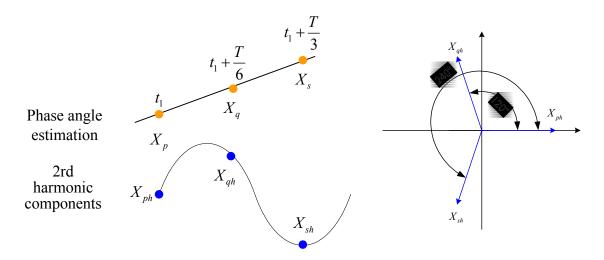

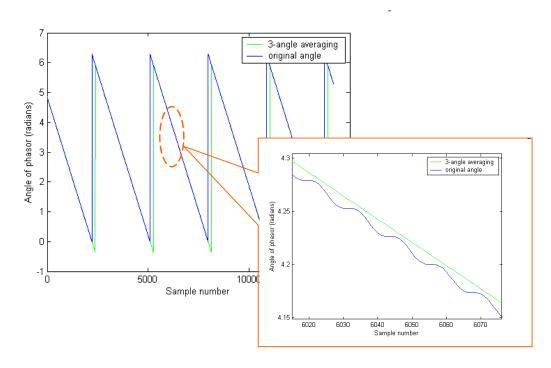

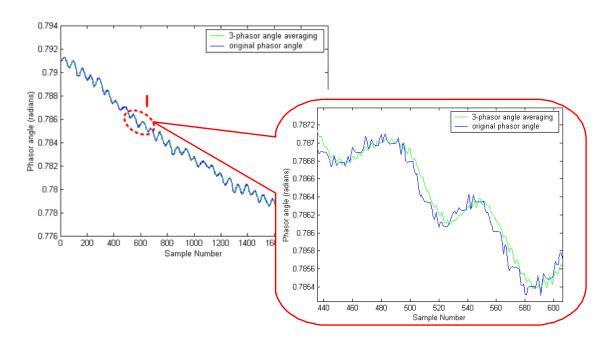

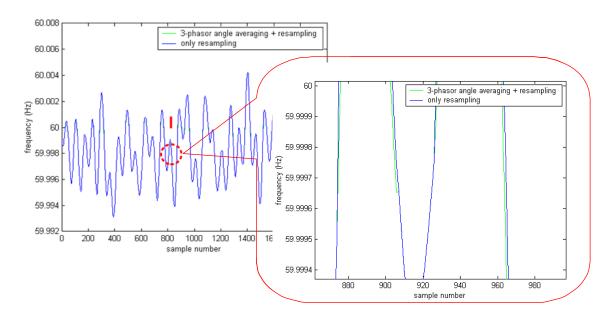

| Figure 4.22 Frequency Estimation with Small Ripples                              | 4        |

| Figure 4.23 3-point Phasor Angle Averaging 9                                     | 5        |

| Figure 4.24 Frequency Estimation with 3-point Averaging Filter                   | 5        |

| Figure 4.25 Phase Angle of unfiltered raw data from real power system            | 8        |

| Figure 4.26 Frequency estimation of unfiltered raw data from real power system 9 | 9        |

| Figure 4.27 Frequency estimation comparison                                      | 0        |

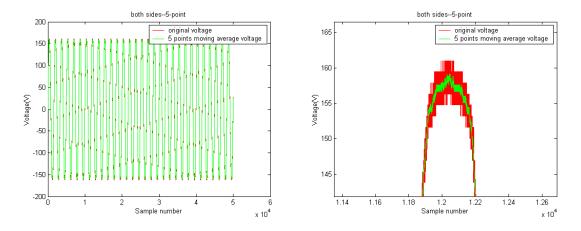

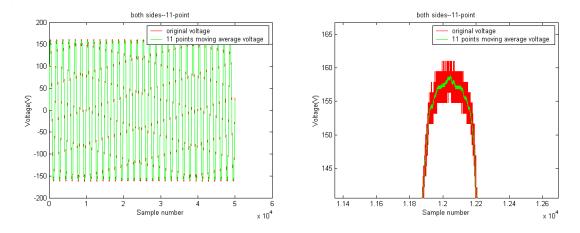

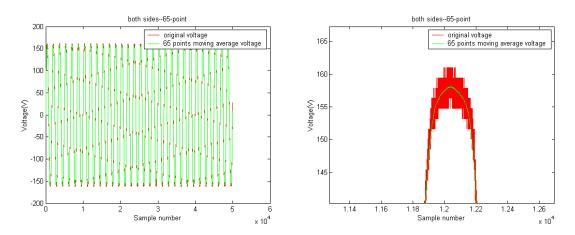

| Figure 4.28 Voltage Waveform w/o 5-point Moving Average Filter 10                | 4        |

| Figure 4.29 Voltage Waveform w/o 11-point Moving Average                         | 5        |

| Figure 4.30 Voltage Waveform w/o 65-point Moving Average                         | 5        |

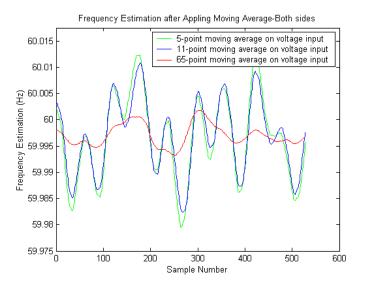

| Figure 4.31 Frequency Estimation with Moving Average Filters                     | 5        |

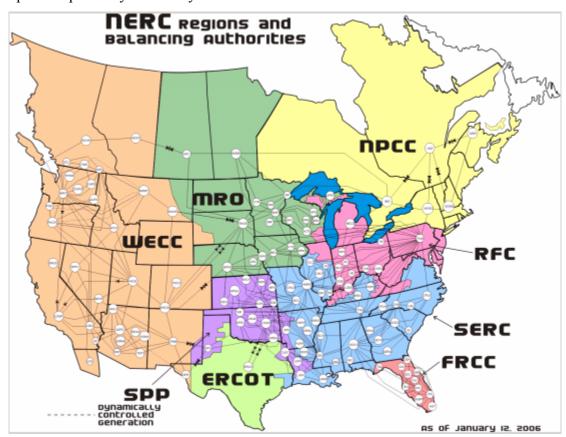

| Figure 4.32 NERC regions and balancing authorities                               | 7        |

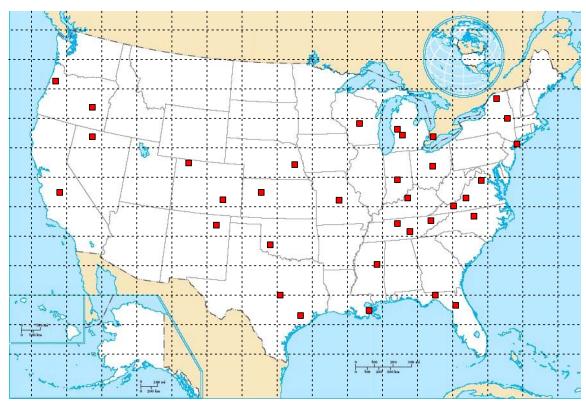

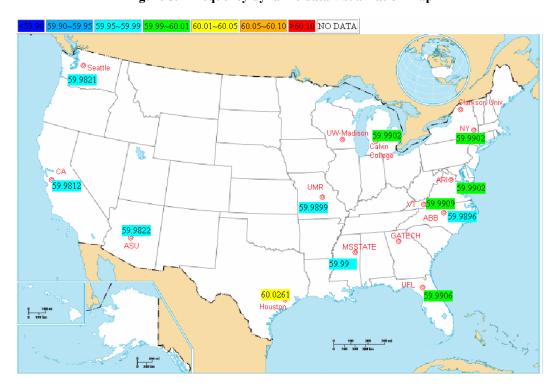

| Figure 4.33 FDR placement map                                                    | 9        |

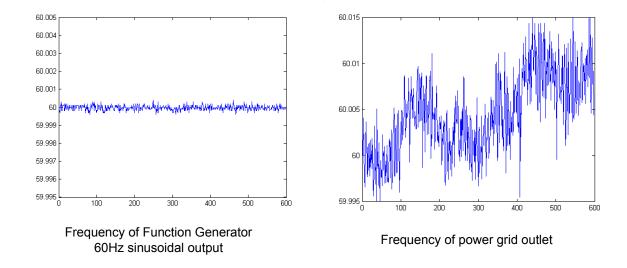

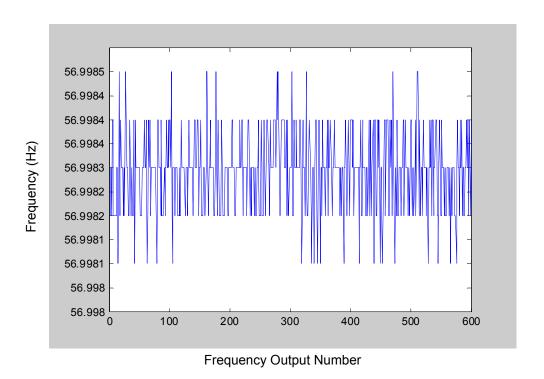

| Figure 4.34 FDR frequency estimation with 57 Hz sinusoidal input                 | 0        |

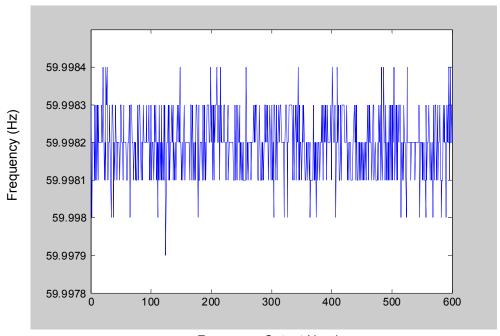

| Figure 4.35 FDR frequency estimation with 60 Hz sinusoidal input                 | 1        |

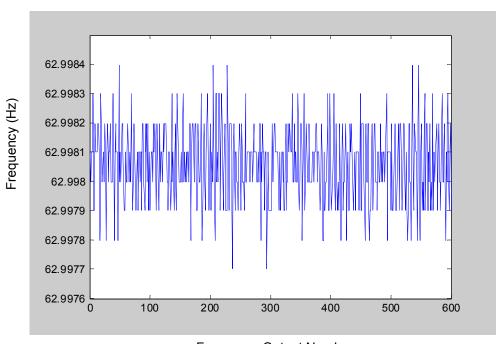

| Figure 4.36 FDR frequency estimation with 63 Hz sinusoidal input                 | 1        |

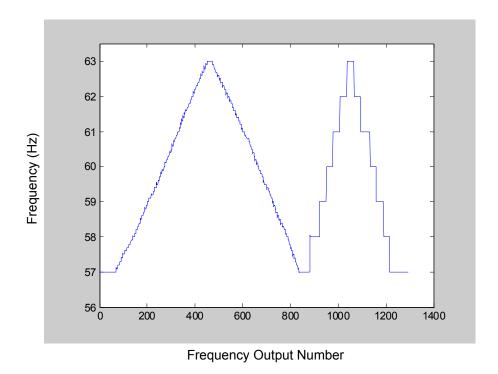

| Figure 4.37 FDR frequency estimation with dynamic sinusoidal waveform input 11   | 2        |

| Figure 4.38 Frequency estimation comparison of 2 FDRs with voltage input from    | m        |

| the same wall outlet                                                             | 2        |

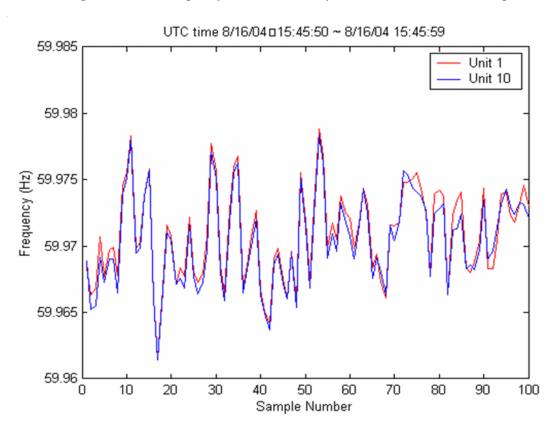

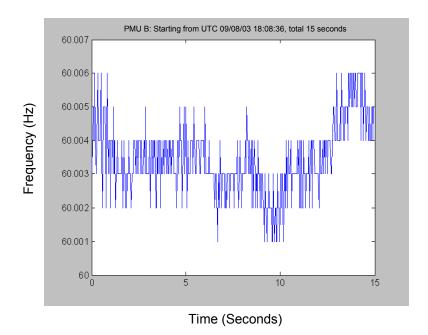

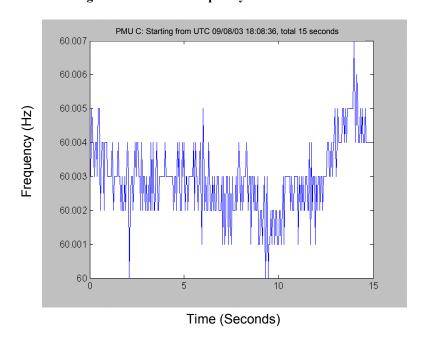

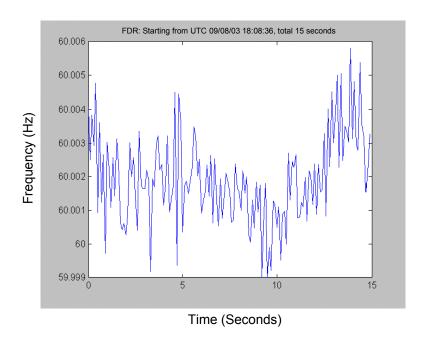

| Figure 4.39 PMU A frequency estimation results                                   | 3        |

| Figure 4.40 PMU B frequency estimation results                                   | 4        |

| Figure 4.41 PMU C frequency estimation results                                   | 4        |

| Figure 4.42 FDR frequency estimation results                                     | 5        |

Chunchun Xu List of Figures

| Figure 4.43 Voltage samples and voltage angles in a missing point case |

|------------------------------------------------------------------------|

| Figure 4.44 Frequency and voltage angles in a missing point case       |

| Figure 4.45 Frequency and voltage samples in a missing point case      |

| Figure 5.1 Multi-tier Information Management System Structure          |

| Figure 5.2 Frequency dynamic data visualization map                    |

| Figure 5.3 FNET data display                                           |

| Figure 5.4 FNET Data stream of 5-second average                        |

| Figure A.1 Flowchart of the FDR interrupt handling                     |

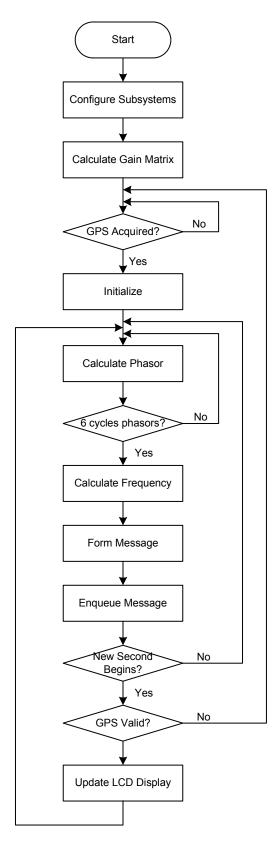

| Figure A.2 Flowchart of the main function                              |

| Figure A.3 Flowchart of the acquire mode                               |

| Figure A.4 Flowchart of the collect mode                               |

| Figure A.5 Flowchart of the MIOS interrupt                             |

Chunchun Xu List of Tables

# **List of Tables**

| Table 1 Format of character array from FDR                   | 52  |

|--------------------------------------------------------------|-----|

| Table 2 FDR interrupt priority and codes                     | 61  |

| Table 3 Frequency estimation error range                     | 96  |

| Table 4 Errors introduced by amplitude swing                 | 101 |

| Table 5 Maximum Measurement errors due to harmonics presence | 102 |

| Table 6 FDR Unit Location and RELATIVE SYSTEM Area           | 107 |

# **Chapter 1** Introduction

#### 1.1 Scope and Background of Research Interest

The electric power network is one of the largest and most important networks in the world, since it affects all aspects of our lives every moment. However, recent large-scale blackouts throughout the world warn us that most of the power grids are heavily loaded and operate at their maximum capacity, and the power grids are very vulnerable to system-wide disturbance and cascade failures. US deregulation, competition and the increase of complexity of today's power networks have only further exacerbated power system stability issues.

In order to ensure system stability in a heavily loaded system, all or most installed components should remain in service, and the right actions must be taken quickly if the system does not recover after a serious event. To cater to those requirements, one of the best solutions is to have wide-area real-time monitoring systems, which could provide critical information for a variety of operation, protection, control and analysis applications.

In recent years, more and more wide-area monitoring systems have been built around the world to meet the growing needs for all kinds of system-stability-related applications. Most of the current wide-area monitoring systems are based on Phasor Measurement Units (PMU). PMU is a measurement device developed and commercialized in the late 1980s. It is capable of recording long-term phasor representations of voltage and current, which could define the status of a power network in phasor format and help improve the power grid's performance. However, in order to obtain the valuable measurement information for observing a power system's dynamics, a number of PMUs are required to be installed in facilities with high-voltage three-phase inputs, which make PMUs costly to manufacture, install and maintain.

1

In terms of global energy balance, as long as power generation is equal to power consumption and loss of loads, the frequency of the entire power network remains constant. However, in the real world, the balance between the generation and load constantly suffers perturbation due to fluctuations or outage of loads, generations and interconnections. Frequency is a good indicator of imbalance between power generations and loads, and it is one of the most important signals for disturbance identification. GPS timing synchronization techniques, coupled with fast-growing information technology, provides a great opportunity to measure and monitor the frequency wide area in real time. An Internet-based Frequency Monitoring Network (FNET) was proposed in 2001 [1], and has since been implemented.

The FNET consists of two major parts, the Frequency Disturbance Recorder (FDR) and the Information Management System (IMS). The FDR works as a sensor, which performs local frequency data measurements and transmits the data to remote servers through the Internet. IMS works as a central server, which provides data collection, storage, web service, post-disturbance analysis and other information management functions. FNET provides continuous, real-time, wide-area collection of GPS time-stamped frequency data for monitoring purposes; it made the synchronized observation of the entire US power network possible with reasonable cost for the first time. Based on the valuable information provided by FNET, a variety of protection and control applications could be studied in order to access and improve the performance of power systems during steady-state and transient conditions.

#### 1.2 Challenges

Many studies and investigations show that the lack of effective sensing and monitoring information for system reliability, operation, protection, control process and other applications is one of the major causes of 2003 North American and Italian blackouts [2, 3]. The frequency of a power system remains constant regardless of voltage level; however, when a disturbance occurs in the power grids, the frequency varies. Therefore

the proposed FNET should be able to provide a coherent picture of how the entire power grid behaves during both the steady state and disturbances, and help prevent cascade blackouts like the one in the summer of 2003. In order to provide critical support for system monitoring, measurement, protection, operation, control, and reliability assessment, the measurement of FNET should be networked, occur in real-time, be synchronized, and be done with satisfactory accuracy. Those challenges have been the keys to implementation of FNET.

#### 1.3 Frequency Monitoring Network (FNET)

Frequency is one of the most important parameters for accessing and controlling the power system dynamic performance. In other words, frequency information can be used in many applications of power system operation, monitoring, analysis and control [1]. Traditionally, only local frequency measurement with the assumption of a steady state can achieve acceptable estimation accuracy. However, system frequency varies with respect to time and location, and the frequency information during disturbance or faults is much more valuable. Accurate, continuous, time-synchronized, quasi-real-time wide-area dynamic frequency information is the key for accurate monitoring, control and protection applications of a power system, including: disturbance and events analysis, system monitoring and tests, power system models and theories validation, and method development for grid reliability management

In the past several decades, there have been many attempts to develop frequency estimation algorithms and measurement device, in which the Phasor Measurement Unit (PMU) has been a big success. However, due to some issues discussed in the previous section, PMUs have not been widely used for many research and academic purposes.

The Frequency Monitoring Network (FNET) provides a cost-effective way for accurate dynamic frequency monitoring. The FNET implementation includes, but is not limited to the following:

Development and implementation of highly accurate frequency estimation algorithms and techniques;

- Design and development of measurement device hardware and software;

- Development of an Internet-based information management system;

- Development of real-time and offline post data processing algorithms for a variety of power system analysis and control applications;

- Development of data compression or aggregation methods for data transmission, storage and processing.

### 1.4 Frequency Estimation Algorithm

In real world power systems, there are a growing number of power electronics devices, arc furnaces and other equipment, which bring harmonics, flickers and noise [4] to the modern power network. It is always a challenge to discover and develop reliable algorithms for precise frequency estimation in presence of harmonics and noise. During the past several decades, a variety of synchronous frequency estimation algorithms have been proposed. These include, but are not necessarily limited to: Zero-crossing Techniques, Least Error Square Approximation, Fast Fourier Transform, leakage effect of DFT, Phasor Angle Analysis, and Kaman Filtering Techniques.

In the zero-crossing technique, a very simple circuit is required, which could minimize the design efforts and computation burden. However, the technique is vulnerable in the presence of noise, and the measurement accuracy heavily depends on the accuracy of the oscillator. It's not suitable for applications requiring heavy measurement data, since only one new frequency measurement result at most could be obtained every cycle.

The Leakage Effect of the Fourier Transform can be easy implemented, but accuracy of this algorithm suffers a great deal from the non-fundamental components of a real power system. Since it only works for sinusoidal waveform, a zero-crossing detector is required for the algorithm implementation, which could bring additional noise issues. The Least

Error Square Technique can adjust the coefficients of pseudo-inverse matrix to improve the noise suppression. However, this technique will introduce a larger error for large frequency deviation. Phasor Angle Analysis provides fast recursive estimation of phasor and frequency by calculating the DFT fundamental frequency component of an input signal. The phasor angle analysis is capable of self-filtering in presence of noise and can provide a highly precise estimation of frequency. It is therefore the best fit for FNET implementation.

#### 1.5 Frequency Disturbance Recorder

The Frequency Disturbance Recorder (FDR) is the key component of FNET. It takes the single phasor voltage input from a 110V residential wall outlet, estimates the synchronous frequency, voltage, and other power system parameters in real time, and transmits the measurement results to a central server via Internet.

The FDR consists of 4 major parts; the computation unit, GPS, the device server, and signal digitizing and conditioning. The computation unit is the place where the frequency estimation algorithm, process scheduler, and data processing are running. In the first generation, the computation unit is a microcontroller, and in the second generation it could be an MCU, DSP or PC depending on different installation scenarios.

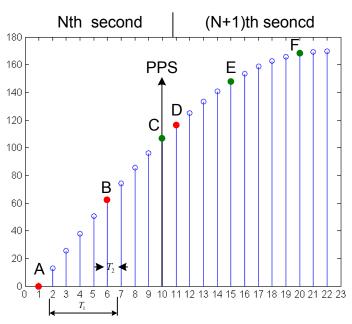

The GPS receiver provides the pulse per second (PPS) signal and UTC time stamp. The PPS is the trigger to synchronized pulse train of voltage sampling, and the UTC time stamp provides the common timing tag for the sampling at a certain instant.

A device server is capable of converting serial communication to the Ethernet, which make all the measurement results networked and accessible in real-time. The signal digitizing and conditioning system processes the input voltage signal in order to provide a clean and reasonable measurement signal to algorithm.

Compared with its commercial counterpart, even though the FDR gives up line voltage angles and flow, it is portable, compact in size, cost effective, and accurate, all of which make it a practical and effective way to deploy the wide-area, real-time synchronized frequency measurement and monitoring system. So far, there are around 30 FDRs in place at universities, research institutes, and offices all across the country providing continuous, GPS-synchronized, real-time collection of power system frequency measurement data.

#### 1.6 Dissertation Outline

This dissertation is organized as follows: The first chapter will give some introduction and background of the research work of this dissertation. The second chapter will address investigation and research work on the frequency estimation algorithm and makes a safe conclusion that the DFT-based Phasor Angle Analysis is the best solution so far for FDR and FNET implementation. In the third chapter, the conceptual design of a portable FDR will be proposed, and the software and hardware architecture of the FDR will be discussed fully. The fourth chapter presents some research work on the issues affecting frequency measurement accuracy and reliability. Some preliminary research work of FNET applications will be presented in the fifth chapter, and the last chapter will summarize the dissertation.

# Chapter 2 Frequency Estimation Algorithms Review

#### 2.1 Frequency Estimation Algorithm

The phasor representation can be used to consider the ideal voltage and current signal in power system as a rotation vector:

$$v(t) = X(t)e^{i\theta(t)}. (2.1.1)$$

X(t) and  $\theta(t)$  are the instantaneous magnitude and phasor angle respectively, and both of them can be considered as functions of time. Whenever the change of  $\theta(t)$  is constant or small enough with respect to the synchronous frequency, i.e.  $\omega_0$ , the frequency is defined as the inverse of the shortest time interval between two instants with the same value for all times [5].

$$(\forall t) \left( v(t) = v(t - T) = v(t - f^{-1}) \right) \tag{2.1.2}$$

The instantaneous frequency deviation is defined as

$$\Delta f = \frac{\Delta \omega}{2\pi} = \frac{1}{2\pi} \frac{d\theta}{dt}.$$

(2.1.3)

Frequency is one of the most important parameters and is the quality index of the power system. Deregulation, expansion of the transmission and distribution network, and the increased application of power electronics make the power system more complex and make the determination of accurate frequency more difficult.

In the past several decades, a variety of synchronous frequency estimation algorithms have been proposed. These include, but are not limited to:

- Zero Crossing Techniques [6-8],

- Leakage Effect of Fourier Transform [9],

- Phasor Angle Analysis [10-14],

- Least Error Square Techniques [15-17],

- Kalman Filter Techniques [18],

- Smart Discrete Fourier Transforms [19-22],

- Wavelet Approach [23], and

- Adaptive Neural Network Approach [24, 25].

In the following sections, some analysis and comparison results of these algorithms will be discussed, based on which we make a safe conclusion that Phasor Angle Analysis is the ideal solution for FNET and FDR implementation.

#### 2.2 Zero Crossing Techniques

The zero crossing technique is the most intuitive method for frequency measurement. It uses a counter to record the time between two successive zero crossing points (where the signal goes from positive to zero) of a voltage waveform. The relationship between the counts and the period of the voltage is as follows:

$$\frac{1}{2}T = \frac{C_m}{C_{f_0}} \frac{1}{f_0} \tag{2.2.1}$$

Where T is the period of the voltage signal,

$C_m$  is the counter number recorded for the voltage signal been measured,

$C_{\it f_0}$  is the counter number recorded for the signal operating at nominal frequency, and

$f_{\alpha}$  is the nominal frequency.

Besides the technique of measuring the frequency at only the zero-crossing points of a signal, many other variations have been developed. Using the slope of linearly interpolated samples, the Level Crossing Technique measures frequency at every incoming sample. Some other variations extend the measurement window more than two cycles to minimize the noise effects.

When the zero crossing technique is used, a very simple circuit is needed, and the minimum computation burden will be applied to microcontrollers. However, this technique is vulnerable in the presence of noise, and at most one new frequency

measurement result can be obtained every cycle. Additionally, for high accuracy, the very expensive oscillator and peripheral circuit are necessary for precise timing.

#### 2.3 Leakage Effect of Fourier Transform

The leakage effect is the discrepancy between the Fourier Transform and the function's Fourier series of a signal with only part of a cycle. The leakage coefficient  $\eta$  could be written:

$$\eta = \frac{\sum_{k=0}^{N-1} |X(k)| - |X(1)|}{|X(1)|}$$

(2.3.1)

where

X(k) are the Discrete Fourier Transform terms and

X(1) corresponds to the fundamental component.

Assuming a sinusoidal waveform with a small frequency deviation  $(\pm 5Hz)$ , the relationship between the leakage coefficient  $\eta$  and the frequency deviation  $\Delta f$  is linear [9]. The governing equation of the relationship is:

$$|\Delta f| = \frac{\eta}{0.095584345} \,. \tag{2.3.2}$$

For a cosinusoidal waveform, this relation will not hold. In this case, a zero-crossing detector must be applied to detect the zero-crossing point (positive going to zero in this case) to obtain a sinusoidal waveform. However, there's no perfect zero-crossing detector in the real world, so a time error will always be introduced. This implies that the sinusoidal waveform poses a phase delay, which will definitely introduce an error in the frequency estimation.

Another thing that must be noted here is that the leakage coefficient defined above is for only the fundamental component. However, a real power voltage waveform contains a lot of waveforms or noise in addition to the fundamental component. Those non-fundamental components will definitely impair the estimation accuracy using this technique.

#### 2.4 Phasor angle analysis

This DFT-based frequency measurement technique is the most widely used algorithm in the commercial Phasor Measurement Units (PMU).

Consider a pure sinusoidal input signal

$$X(t) = \sqrt{2}X\sin(2\pi ft + \theta). \tag{2.4.1}$$

The phasor of the signal  $\overline{X}$  can be expressed as

$$\overline{X} = Xe^{j\theta} = X\cos\theta + X\sin\theta. \tag{2.4.2}$$

Assuming that X(t) is sampled N times per cycle at 60 Hz to produce a sample data sequence  $\{x_k\}$ ,

$$x_{k} = \sqrt{2}X \sin\left(\frac{2\pi k}{N} + \theta\right) = \sqrt{2}X \left(\frac{e^{j\left(\frac{2\pi k}{N} + \theta\right)} - e^{-j\left(\frac{2\pi k}{N} + \theta\right)}}{2j}\right). \tag{2.4.3}$$

Take the N-point Discrete Fourier Transform of  $\{x_k\}$ , and evaluating the fundamental frequency component,

$$\overline{X_1} = \frac{2}{N} \sum_{k=0}^{N-1} x_k e^{-j\frac{2\pi}{N}k} = \frac{2}{N} \sum_{k=0}^{N-1} x_k \cos\left(\frac{2\pi}{N}k\right) - j\frac{2}{N} \sum_{k=0}^{N-1} x_k \sin\left(\frac{2\pi}{N}k\right). \tag{2.4.4}$$

Substituting for  $x_k$  from (2.4.3),

$$\overline{X_1} = X_c - jX_s \tag{2.4.5}$$

$$X_{c} = \frac{2}{N} \sum_{k=0}^{N-1} \sqrt{2} X \sin\left(\frac{2\pi k}{N} + \theta\right) \cos\left(\frac{2\pi}{N} k\right) = \frac{2}{N} \sum_{k=0}^{N-1} \sqrt{2} X \left[ \frac{e^{j\left(\frac{2\pi k}{N} + \theta\right)} - e^{-j\left(\frac{2\pi k}{N} + \theta\right)}}{2j} \right] \left[ \frac{e^{j\left(\frac{2\pi k}{N} + \theta\right)} - e^{-j\left(\frac{2\pi k}{N} + \theta\right)}}{2j} \right]. \tag{2.4.6}$$

Using a geometric series,

$$\sum_{n=0}^{N-1} r^n = \frac{r^p - r^N}{1 - r} \tag{2.4.7}$$

$$X_c = \sqrt{2}X\sin\theta \tag{2.4.8}$$

while

$$X_{s} = \sqrt{2}X\cos\theta \,. \tag{2.4.9}$$

So in general, the phasor of signal (2.4.1) is:

$$\overline{X} = \frac{1}{\sqrt{2}} j \overline{X_1}. \tag{2.4.10}$$

Consider the phasor of X(t) at the rth sampling interval [10],

$$\overline{X}^{(r)} = \frac{1}{\sqrt{2}} j \overline{X_1}^{(r)} = \frac{1}{\sqrt{2}} j \frac{2}{N} \sum_{k=0}^{N-1} x_{r+k} e^{-j\frac{2\pi}{N}k}.$$

(2.4.11)

Substituting for  $x_{r+k}$  from (2.4.3) results in [26]

$$\overline{X}^{(r)} = \frac{X}{N} \sum_{k=0}^{N-1} \left( e^{jA} - e^{-jB} \right)$$

(2.4.12)

with

$$A = \frac{2\pi (r+k)}{N} + \theta - \frac{2\pi k}{N} = \frac{2\pi r}{N} + \theta$$

(2.4.13)

$$B = \frac{2\pi (r+k)}{N} + \theta + \frac{2\pi k}{N} = \frac{2\pi}{N} (r+2k) + \theta.$$

(2.4.14)

Then the phasor is

$$\overline{X}^{(r)} = \frac{X}{N} \sum_{k=0}^{N-1} \left( e^{j\frac{2\pi}{N}r} e^{j\theta} - e^{-j\frac{2\pi}{N}r} e^{-j\frac{2\pi}{N}2k} e^{-j\theta} \right).$$

(2.4.15)

Applying the identity

$$\sum_{n=0}^{N-1} \left( e^{j\theta} \right)^n = \frac{\sin\left(\frac{N\theta}{2}\right)}{\sin\left(\frac{\theta}{2}\right)} e^{j(N-1)\frac{\theta}{2}}$$

(2.4.16)

leads to

$$\sum_{k=0}^{N-1} e^{-j\frac{2\pi}{N}2k} = 0 {(2.4.17)}$$

so

$$\overline{X}^{(r)} = \frac{X}{N} \sum_{k=0}^{N-1} \left( e^{j\frac{2\pi}{N}r} e^{j\theta} \right) = X e^{j\theta} e^{j\frac{2\pi}{N}r}.$$

(2.4.18)

Now assuming a signal with the off nominal frequency  $f + \Delta f$ ,

$$X(t) = \sqrt{2}X\sin\left(2\pi\left(f + \Delta f\right)t + \theta\right). \tag{2.4.19}$$

The new phasor at the rth sampling is

$$\overline{X}_{f+\Delta f}^{(r)} = \frac{X}{N} \sum_{k=0}^{N-1} \left( e^{jC} - e^{-jD} \right)$$

(2.4.20)

with

$$C = \frac{2\pi}{N}r + \frac{2\pi\Delta f}{N60}r + \theta + \frac{2\pi\Delta f}{N60}k$$

(2.4.21)

$$D = \frac{2\pi}{N}r + \frac{2\pi\Delta f}{N60}r + \theta + \left(\frac{4\pi}{N} + \frac{2\pi\Delta f}{N60}\right)k. \qquad (2.4.22)$$

Then

$$\overline{X}_{f+\Delta f}^{(r)} = \frac{X}{N} \left( e^{j\frac{2\pi}{N}r} e^{j\frac{2\pi\Delta f}{N60}r} e^{j\theta} \sum_{k=0}^{N-1} e^{j\frac{2\pi\Delta f}{N60}k} - e^{-j\frac{2\pi}{N}r} e^{-j\frac{2\pi\Delta f}{N60}r} e^{-j\theta} \sum_{k=0}^{N-1} e^{-j\left(\frac{4\pi}{N} + \frac{2\pi\Delta f}{N60}\right)k} \right)$$

(2.4.23)

for rth data window, the phasor of (2.4.1) is expressed by

$$\overline{X}_{f}^{(r)} = Xe^{j\theta}e^{j\frac{2\pi}{N}r}.$$

(2.4.24)

To make the phasor be stationary in the complex plane, a time delay was used to compensate the angular:

$$\overline{Y}^{(r)} = \overline{X}^{(r)} e^{-j\frac{2\pi}{N}r} = Xe^{j\theta}$$

(2.4.25)

Applying the identity (2.4.16) and introducing the phasor expression in (2.4.25) leads to

$$\overline{X}_{f+\Delta f}^{(r)} = \overline{X}_{f}^{(r)} e^{j\frac{2\pi\Delta f}{N60}r} e^{j(N-1)\frac{\pi\Delta f}{N60}} \frac{\sin\frac{\pi\Delta f}{60}}{\sin\frac{2\pi\Delta f}{N60}} - \overline{X}_{00}^{*(r)} e^{-j\frac{2\pi\Delta f}{N60}r} e^{j(N-1)\left(\frac{2\pi}{N} + \frac{\pi\Delta f}{N60}\right)} \frac{\sin\frac{\pi\Delta f}{N60}}{\sin\frac{2\pi}{N} + \frac{\pi\Delta f}{N60}}.(2.4.26)$$

For a small value of  $\Delta f$ , the following simplifications hold:

$$\frac{\sin\frac{\pi\Delta f}{60}}{\sin\frac{2\pi\Delta f}{N60}} = 1 \tag{2.4.27}$$

$$\frac{\sin\frac{\pi\Delta f}{N60}}{\sin\frac{2\pi}{N} + \frac{\pi\Delta f}{N60}} = 0. \tag{2.4.28}$$

So (2.4.26) can be reduced to

$$\overline{X}_{f+\Delta f}^{(r)} = \overline{X}_{f}^{(r)} e^{j\frac{2\pi\Delta f}{N60}r} e^{j(N-1)\frac{\pi\Delta f}{N60}}.$$

(2.4.29)

The computed phasor is broken down into its magnitude and angle parts.

By denoting the angle of the new phasor as  $\psi_r$  and the angle of the previous phasor as  $\psi_{r-1}$ , one can approximate the new phasor as:

$$\psi_r = \frac{\Delta f}{f_0} \frac{2\pi}{N} + \psi_{r-1} \tag{2.4.30}$$

$$\frac{d\psi}{dt} = \lim_{t \to 0} \frac{\psi_r - \psi_{r-1}}{t} \approx \frac{\psi_r - \psi_{r-1}}{1/Nf_0} = 2\pi\Delta f.$$

(2.4.31)

The system frequency can now be computed with:

$$f = f_0 + \Delta f = f_0 + \frac{1}{2\pi} \frac{d\psi}{dt} \quad , \tag{2.4.32}$$

and the rate of change of frequency is

$$\frac{df}{dt} = \frac{1}{2\pi} \frac{d^2 \psi}{dt^2} \,. \tag{2.4.33}$$

The Phasor Analysis Technique is simple in terms of computation burden. Under the assumption that the system frequency is very close to 60Hz in normal operation, the leakage error of DFT is very small. So phasor angle analysis can provide highly accurate frequency estimation with minimum computation complexity and time.

#### 2.5 Least Error Square Technique

The Taylor Series Expansion is the underlying principle of the Least Error Square Technique. A single frequency sinusoidal waveform can be represented as

$$v(t) = A_{v} \sin(2\pi f t + \theta)$$

$$= A_{v} \cos\theta \sin(2\pi f t) + A_{v} \sin\theta \cos(2\pi f t)$$

(2.5.1)

Expanding the Taylor series of  $\sin(2\pi ft)$  and  $\cos(2\pi ft)$  centered on the nominal frequency  $f_0$ , the first three terms are taken,

$$v(t_{1}) \approx a_{11}x_{1} + a_{12}x_{2} + a_{13}x_{3} + a_{14}x_{4} + a_{15}x_{5} + a_{16}x_{6}$$

$$v(t_{2}) \approx a_{21}x_{1} + a_{22}x_{2} + a_{23}x_{3} + a_{24}x_{4} + a_{25}x_{5} + a_{26}x_{6}$$

$$\vdots$$

$$v(t_{m}) \approx a_{m1}x_{1} + a_{m2}x_{2} + a_{m3}x_{3} + a_{m4}x_{4} + a_{m5}x_{5} + a_{m6}x_{6}$$

$$x_{1} = A_{v}\cos\theta, x_{2} = (f - f_{0})A_{v}\cos\theta$$

$$x_{3} = A_{v}\sin\theta, x_{4} = (f - f_{0})A_{v}\sin\theta$$

$$x_{5} = \left(-\frac{(2\pi)^{2}}{2}f^{2} + (2\pi)^{2}ff_{0} - \frac{(2\pi)^{2}}{2}f_{0}^{2}\right)A_{v}\cos\theta$$

$$x_{6} = \left(-\frac{(2\pi)^{2}}{2}f^{2} + (2\pi)^{2}ff_{0} - \frac{(2\pi)^{2}}{2}f_{0}^{2}\right)A_{v}\sin\theta$$

where

and

$a_{i4} = 2\pi t_i \sin(2\pi f_0 t_i), a_{i5} = t_i^2 \sin(2\pi f_0 t_i), a_{i6} = t_i^2 \cos(2\pi f_0 t_i)$   $v(t_1)...v(t_m) \text{ are measured inputs, and all } as \text{ can be calculated if the nominal frequency}$

$f_0$  and sampling instant t are known. The only unknowns are values of xs.

$a_{i1} = \sin(2\pi f_0 t_i), a_{i2} = 2\pi t_i \cos(2\pi f_0 t_i), a_{i3} = \cos(2\pi f_0 t_i)$

We can rewrite (2.5.2) as

$$\mathbf{AX} = \mathbf{V} \tag{2.5.3}$$

where **A** is a  $m \times 6$  matrix, and m ought to be greater or equal to 6 to obtain a solution of X. When  $m \ge 6$ , the least error square estimation of X is:

$$\mathbf{X} = \left[ \left[ \mathbf{A}^{\mathrm{T}} \mathbf{A} \right]^{-1} \mathbf{A}^{\mathrm{T}} \right] \mathbf{V} . \tag{2.5.4}$$

With the solution of X, the frequency deviation  $\Delta f$  can be found according to equations (2.5.5) and(2.5.6):

$$\frac{x_2}{x_1} = \frac{(f - f_0) A_v \cos \theta}{A_v \cos \theta} = f - f_0$$

(2.5.5)

$$\frac{x_4}{x_3} = \frac{(f - f_0) A_v \sin \theta}{A_v \sin \theta} = f - f_0.$$

(2.5.6)

Another alternative is the combination of (2.5.5) and (2.5.6):

$$(f - f_0)^2 = \frac{{x_2}^2 + {x_4}^2}{{x_1}^2 + {x_3}^2}.$$

(2.5.7)

The pseudo-inverse matrix  $\left[\left[\mathbf{A}^T\mathbf{A}\right]^1\mathbf{A}^T\right]$  can be considered a filter, which will amplify or suppress noise depending on its coefficients. Both the sampling rate and the window size play rather important roles in determining the pseudo-inverse matrix. Experimental data shows that increasing the sampling rate improves the noise immunity characteristics of the pseudo-inverse matrix [15]. However, only extending the data window will not reduce the noise effects on the output. The underlying principle of the least error square is the approximation of the voltage waveform using the Taylor Series instead of the least error square. So, for a more accurate result, one needs to increase both the window size and the terms of Taylor Series. However, more Taylor Series terms imply more unknowns, and then a bigger pseudo-inverse matrix, all of which will add up to more of a computational burden. Also, if the waveform frequency is not constant within the longer window, then additional errors will be introduced. Giray and Sachdev found that for large frequency deviation, the error introduced will also be larger. To obtain better accuracy and to meet the speed requirements of relay systems, they proposed a lookup table to compensate the errors [16].

### 2.6 Kalman Filter Techniques

Girgis and Huang were first to propose the Kalman Filtering Technique for frequency estimation in detail [18]. The Kalman filter addresses the general problem of trying to estimate the state of a discrete-time-controlled process that is governed by the linear stochastic difference equation

$$\mathbf{x}_{k+1} = \phi_k \mathbf{x}_k + \mathbf{w}_k \tag{2.5.8}$$

where

$\mathbf{x}_k$  is the state vector at step k,

$\phi_k$  is the state transition matrix, and

$\mathbf{w}_k$  is the process noise vector with a covariance matrix  $\mathbf{E}\left[\mathbf{w}_k\mathbf{w}_j^T\right] = \mathbf{Q}_k$ , in which  $\mathbf{Q}_k = 0$  if  $k \neq j$ .

The measurement equation is

$$\mathbf{z}_{k} = \mathbf{H}_{k} \mathbf{x}_{k} + \mathbf{v}_{k} \tag{2.5.9}$$

where

$\mathbf{z}_k$  is the measurement vector at step k,

$\mathbf{H}_k$  is the measurement matrix,

$\mathbf{v}_k$  is the random measurement error vector with covariance

$$E[\mathbf{v}_k \mathbf{v}_j^T] = \mathbf{R}_k$$

in which  $\mathbf{R}_k = 0$  if  $k \neq j$ .

The random variables  $\mathbf{w}_k$  and  $\mathbf{v}_k$  represent the process and measurement noise respectively. And they are assumed to be independent, white, and with normal probability distributions.

Defining the estimate error covariance  $P_k$  and the Kalman gain matrix  $K_k$ , the Kalman filter time update equations can be represented as:

$$\hat{\mathbf{x}}_{k+1/k} = \phi_k \hat{\mathbf{x}}_k

\mathbf{P}_{k+1/k} = \phi_k \mathbf{P}_k \phi_k^T + \mathbf{Q}_k$$

(2.5.10)

and the Discrete Kalman filter measurement updates equations are:

$$\mathbf{K}_{k} = \mathbf{P}_{k/k-1} \mathbf{H}_{k}^{T} \left( \mathbf{H}_{k} \mathbf{P}_{k/k-1} \mathbf{H}_{k}^{T} + \mathbf{R}_{k} \right)^{-1}$$

$$\hat{\mathbf{x}}_{k} = \hat{\mathbf{x}}_{k/k-1} + \mathbf{K}_{k} \left( \mathbf{z}_{k} - \mathbf{H}_{k} \hat{\mathbf{x}}_{k/k-1} \right) . \tag{2.5.11}$$

$$\mathbf{P}_{k} = \mathbf{E} \left[ \left( \mathbf{x}_{k} - \hat{\mathbf{x}}_{k} \right) \left( \mathbf{x}_{k} - \hat{\mathbf{x}}_{k} \right)^{T} \right]$$

A two-state model and a three-state model can be used in the Kalman Filter Technique. The two-state Kalman filter technique calculates the voltage phasor first, and then computes the frequency using  $\frac{d\phi}{dt} \approx 2\pi\Delta f$ . In this technique, the equation of a waveform can be represented as:

$$v(t) = A_v \exp(j\omega t + \phi) = x_1 \cos \omega_0 t - x_2 \sin \omega_0 t \qquad (2.5.12)$$

where  $x_1$  and  $x_2$  are real and imaginary parts of phasor respectively.

The state vector is:

$$\mathbf{x}_{k} = \begin{bmatrix} x_{1_{k}} \\ x_{2_{k}} \end{bmatrix} \tag{2.5.13}$$

and the transition matrix can be defined as:

$$\phi_k = \begin{bmatrix} 1.0 & 0.0 \\ 0.0 & 1.0 \end{bmatrix}. \tag{2.5.14}$$

The measurement equation can be defined as:

$$\mathbf{z}_{k} = \left[\cos\left(\omega_{0}k\Delta t\right) - \sin\left(\omega_{0}k\Delta t\right)\right] \begin{bmatrix} x_{1} \\ x_{2} \end{bmatrix} + \mathbf{v}_{k}. \tag{2.5.15}$$

After knowing the initial estimation of  $\mathbf{P}_0$  and  $\hat{\mathbf{x}}_0$ , (2.5.10) and (2.5.11) can be used to solve the real-time phasor angles recursively. One thing needs to be noted: by using this two-state Kalman Filter technique, a small error in phasor angles computation will introduce a large error in the later frequency estimation.

A three-state Kalman filter model can compute frequency deviation directly. The equation of the waveform can be represented as:

$$v(t) = A_v e^{i[(\omega + \Delta\omega)t + \phi]} = x_1 \cos(\omega_0 t + 2\pi x_3 t) - x_2 \sin(\omega_0 t + 2\pi x_3 t)$$

(2.5.16)

where  $x_1$  and  $x_2$  still represent the real and imaginary components of the phasor respectively, and  $x_3$  represents the frequency deviation.

The state vector is

$$\mathbf{x}_{k} = \begin{bmatrix} x_{1_{k}} \\ x_{2_{k}} \\ x_{3_{k}} \end{bmatrix}. \tag{2.5.17}$$

The transition matrix can be a  $3\times3$  Identity Matrix, and the measurement equation can be

$$\mathbf{z}_k = h_k(x) + \mathbf{v}_k \tag{2.5.18}$$

where

$$h_k(x) = x_{1_k} \cos(\omega_0 k \Delta t + 2\pi x_{3_k} \Delta t) - x_{2_k} \sin(\omega_0 k \Delta t + 2\pi x_{3_k} \Delta t)$$

.

Similarly, (2.5.10) and (2.5.11) can be used to solve  $x_{3k}$ , if the initial estimation of  $\mathbf{P}_0$  and  $\hat{\mathbf{x}}_0$  is known.

The accuracy of the result obtained by the three-state model is much better than the accuracy of the result obtained by the two-state model. Kalman has the ability to filter out variable covariance noise, so the Kalman filter is a very accurate technique for frequency measurement, especially in the presence of noise. Also, the Kalman filter technique

allows different model representations for frequency deviation, such as random constant, random walk, or a combination of both.

However, the Kalman filter technique is built based on the assumption that the probability density functions of the state vectors are known, which is not always true. High values for the variance of the measurement noise need to be used in order to minimize the noise effects on the measurement result. The high variance will introduce unnecessary delay, which causes a longer response delay in estimation calculation. The three-state Kalman filter requires on-line calculation of the Kalman gain, which implies that fast microprocessor or Digital Signal Processor is needed for algorithm implementation.

#### 2.7 Smart Discrete Fourier Transforms

In 2000, Yang and Liu [19] proposed a series of DFT-based algorithms to calculate frequency in real time. The fundamental component of a waveform is considered to be:

$$x(t) = X_l \cos(\omega t + \phi_1). \tag{2.6.1}$$

This also can be presented as:

$$x(t) = \frac{\hat{x}_{i}e^{j\omega t} + \hat{x}_{i}^{*}e^{-j\omega t}}{2}$$

(2.6.2)

where  $\hat{x}_{i}^{*}$  is the complex conjugate of  $\hat{x}_{i}$ .

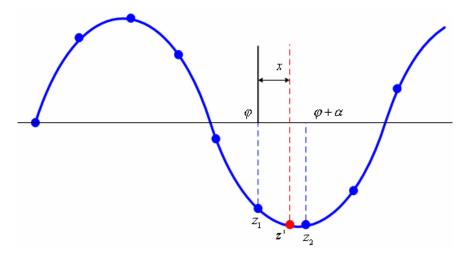

Defining  $z_1 = real(a) = \cos\left(\frac{2\pi}{60N}(60 + \Delta f)\right)$ , and (60\*N) as the sampling rate to generate

voltage sample set  $\{x(k)\}$ , the following expression could be obtained after some algebraic manipulations.

$$2 \times x(r+1) \times z_1$$

$$-1 \times (x(r) + x(r+2)) = 0$$

(2.6.3)

$z_1$  is the only unknown in (2.6.3), so the frequency could be obtained as

$$f = 60 + \Delta f = \cos^{-1}(real(z_1)) \times \frac{60N}{2\pi}$$

(2.6.4)

If considering an input signal with integral harmonic, non-integral harmonic and DC offset at the same time,

$$x(t) = X_1 \cos(\omega t + \phi_1) + X_m \cos(m\omega t + \phi_m) + X_n \cos(\omega_n t + \phi_n) + X_d e^{-\alpha t}$$

(2.6.5)

where

$X_t \cos(\omega t + \phi_1)$  is the fundamental component,

$X_m \cos(m\omega t + \phi_m)$  is the integral harmonics,

$X_n \cos(\omega_n t + \phi_n)$  is non-integral harmonic component,

$X_d e^{-\alpha t}$  is DC offset,

$\frac{1}{\alpha} = \tau$  is the time constant of the signal,

and the fundamental frequency component of DFT of  $\{x(k)\}$  is

$$\overline{x}_r = \frac{2}{M} \sum_{k=0}^{M-1} x(k+r) e^{-j\frac{2\pi k}{N}}.$$

(2.6.6)

After algebraic operations an expression similar to (2.6.3) can be obtained, which provides the solution of  $z_n$  and  $a_d$ . So  $f_n$  and  $\tau$  can also be calculated by:

$$f_n = 60 + \Delta f_n = \cos^{-1}(real(z_n))\frac{60N}{2\pi}$$

(2.6.7)

$$\tau = \frac{1}{60N \log a_d} \,. \tag{2.6.8}$$

There's no leakage error in this technique, which means it could estimate the frequency from 0 to half of the sampling frequency. So the smart Discrete Fourier Transforms provide a good way to estimation frequency over a wide range in the presence of harmonics and DC offset.

However, this technique needs tradeoffs between estimation accuracy, computation complexity and time, and observation window length, and this technique is not suitable for real-time processing due to the increased computation complexity.

#### 2.8 Wavelet Approach

Wavelets are mathematical functions that provide representation of a signal corresponding to different frequency components, and then study each component with a resolution matched to its scale. Compared with Fourier methods, wavelets have an advantage for analyzing of signals that contain discontinuities and spikes.

The analyzing wavelet function  $\psi(t)$  satisfies the "admissibility condition"

$$C_{\psi} = \int_{-\infty}^{+\infty} \frac{\|\psi(\omega)\|}{|\omega|} d\omega < \infty.$$

(2.6.9)

This presents the band pass filtering property of  $\psi(t)$ , and  $\psi(\omega)$  is the frequency response of  $\psi(t)$ . Then a series of wavelet can be derived from  $\psi(t)$ :

$$\psi_{a,b}(t) = \frac{1}{a}\psi\left(\frac{t-b}{a}\right) \tag{2.6.10}$$

where a is the scaling (dilation) factor, and b is the time shifting (of translation) factor.

Similar to the Fourier Transform, the Continuous Wavelet Transform (CWT) measures the difference between the analyzed real signal s(t) and sample wavelet function  $\psi_{a,b}(t)$ , and it is defined as the inner product of  $\psi_{a,b}(t)$  and s(t):

$$W_{\psi}(a,b) = \langle s(t), \psi_{a,b}(t) \rangle = \int_{-\infty}^{+\infty} s(t) \overline{\psi}_{a,b}(t) dt = \int_{-\infty}^{+\infty} s(t) \overline{\psi}_{1,a}(b-t) dt = s(t) * \psi_{1,a}(t) (2.6.11)$$

of which  $\psi_1(t)$  is the mother filter function and satisfies  $\psi_1(t) = \overline{\psi(t)}$  or frequency response  $\psi_1(\omega) = \overline{\psi(\omega)}$ ; and sample filter function  $\psi_{1,a}(t)$  is derived from mother filter function  $\psi_1(t)$  and satisfies  $\psi_{1,a}(t) = \frac{1}{\sqrt{a}} \psi_1(\frac{t}{a})$  or frequency response  $\psi_{1,a}(\omega) = \sqrt{a} \psi_1(a\omega) = \sqrt{a} \psi_1(a\omega)$ . The frequency response of  $W_{\psi}(a,b)$  can be derived as  $W_{\psi}(a,\omega) = S(\omega) \psi_{1,a}(\omega) = \sqrt{a} S(\omega) \psi_1(a\omega) = \sqrt{a} S(\omega) \overline{\psi}(a\omega)$  (2.6.12) in which  $S(\omega)$  is the frequency response of  $s(t)$ .

Similar to the orthogonal filters of the Fourier algorithm, the CWT acts as complex band pass filter, and can used to estimate rotation vector from original current or voltage signal. Assuming  $W_R(t)$  and  $W_I(t)$  are the real part and imaginary part of CWT, the instantaneous frequency can be derived.

$$W_{R}(\tau) = \operatorname{Re}(W_{\psi}(a,\tau)) = s(t) * \left[\operatorname{Re}(\psi_{1,a}(\tau))\right]$$

$$W_{I}(\tau) = \operatorname{Im}(W_{\psi}(a,\tau)) = s(t) * \left[\operatorname{Im}(\psi_{1,a}(\tau))\right]$$

$$\theta(\tau) = \tan^{-1}(W_{I}(\tau)/W_{R}(\tau))$$

$$f(\tau) = \frac{1}{2\pi} \frac{d\theta(\tau)}{d\tau}$$

(2.6.13)

By defining a proper polynomial-type mother wavelet, the recursive CWT can also be implemented to save significant computation time and resources.

The wavelet approach can track the frequency over a wide range under dynamic conditions, and it is immune to harmonics and DC components. However, compared with the Fourier Algorithm, the estimation accuracy of CWT is limited even within the small range around the nominal frequency. Due to its complexity, the CWT could not be easily implemented and requires more computation time and resources than the Fourier algorithm.

## 2.9 Adaptive Neural Network approach

The Adaptive Neural Network approach uses a single-layer adaptive neural network consisting of adaptive neurons called an adaline. The voltage signal of a power system is modeled as a difference equation, where coefficients are identified using an adaline. The weight vector of the adaline is adaptively changed by using a discrete error equation rather than the conventional back propagation technique.

Considering an input signal containing a decaying DC component and harmonics:

$$y_t = \sum_{m=1}^{M} A_m \sin(m\omega_0 t + \phi_m) + a_{dc} \exp(-\alpha_{dc} t) + \varepsilon(t)$$

(2.7.1)

where M is the highest frequency component in the signal,

$a_{dc} \exp(-\alpha_{dc}t)$ : is the decaying DC component,

$\varepsilon(t)$ : is additive noise,

the relationship between three consecutive samples can be represented as follows

$$y_{t} = \cos \omega_{0} T_{s} y_{t-1} - y_{t-2} + \sum_{m=1}^{M} \left\{ A_{m} \left( 2 \cos m \omega_{0} T_{s} - 2 \cos \omega_{0} T_{s} \right) \cdot \left[ \sin m \omega_{0} \left( t - T_{s} \right) + \phi_{m} \right] \right\} . (2.7.2)$$

$$-2 \cos m \omega_{0} T_{s} a_{dc} - 2 \left( 1 - \cos \omega_{0} T_{s} \right) k T_{s} a_{dc} \alpha_{dc}$$

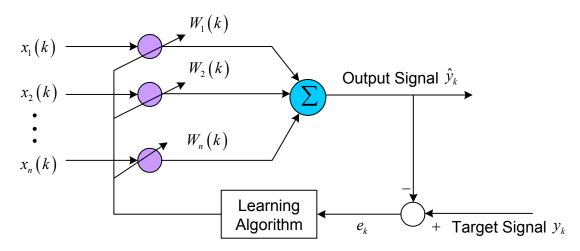

Figure 2.1 Block diagram of ADALINE

Figure 2.1 is the block diagram of an Adaline, and the learning algorithm can be developed as

$$W_{k+1} = W_k + \frac{\alpha e(k)\theta(X)}{X^T \theta(X)}$$

(2.7.3)

Where

k is the time index,

$$W_k = [W_1(k), W_2(k), \dots, W_n(k)]^T$$

: is the weight vector at time  $k$ ,

$$X = [x_1, x_2, \dots, x_n]^T$$

: is the input vector,

$\alpha$ : is the reduction factor;

$$\theta(X) = \begin{bmatrix} SGN(x_1) \\ SGN(x_2) \\ \vdots \\ SGN(x_n) \end{bmatrix} \text{ with } SGN(x) = \begin{cases} +1 & \text{if } x > 0 \\ -1 & \text{if } x < 0 \end{cases}.$$

Therefore, if the pure sinusoidal input is considered, the weight vector of the adaline converges to

$$W = \begin{bmatrix} 2\cos\omega_0 T_s \\ -1 \end{bmatrix} \tag{2.7.4}$$

and the frequency estimation can be derived as

$$f_0 = \left[\cos^{-1}(W(1)/2)\right]/(2\pi T_s). \tag{2.7.5}$$

If an input signal containing the DC component and harmonics is taken into consideration, the frequency is updated as each iteration as

$$\omega_0(k) = \cos^{-1}(0.5W_{1,k})/(2\pi T_s).$$

(2.7.6)

The Adaptive Neural Network approach is a straightforward method, and easily implemented. However in a practical environment in the presence of harmonics, noise and a DC component, the estimation accuracy will be severely jeopardized, from 0.001Hz for a pure sinusoidal input to 0.05Hz for a real world input.

#### 2.10 Summary

After exploring different kinds of frequency estimation algorithms, we find that each algorithm has its unique advantages and disadvantages. Precise frequency estimation is not only a choice of a certain algorithm, but also should be considered as an unconstrained optimization problem. Phasor angle analysis provides fast and accurate frequency estimation over a wide range of interested frequency, and the computation requirement is modest for online implementation. From a practical point of view, we consider Phasor Angle Analysis as the best choice for FDR implementation.

# **Chapter 3 FDR Conceptual Design**

# 3.1 Frequency Monitoring Network Architecture

The Frequency Monitoring Network (FNET) was first proposed in 2001 to meet the fast-growing demands of wide area monitoring [1]. The underlying concept of FNET is that in steady states the power system frequency remains constant regardless of voltage level; however, when a significant disturbance occurs, the frequency varies with respect to time and location. According to this proposal, the FNET should provide continuous real-time wide-area time-synchronized measurement and analysis of power grids' frequency, and feed those values to a variety of power system control and operation applications.

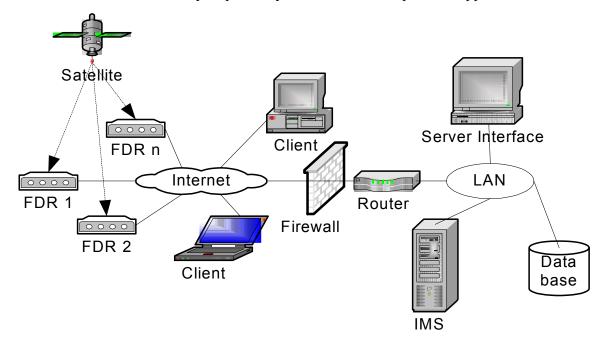

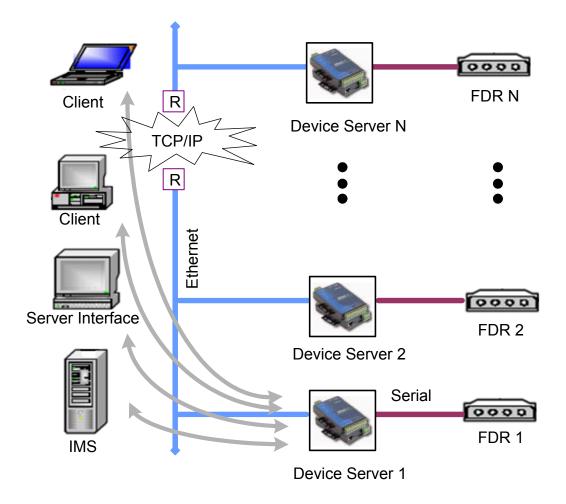

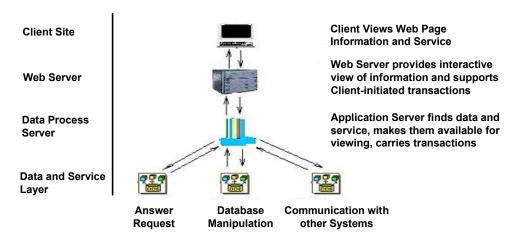

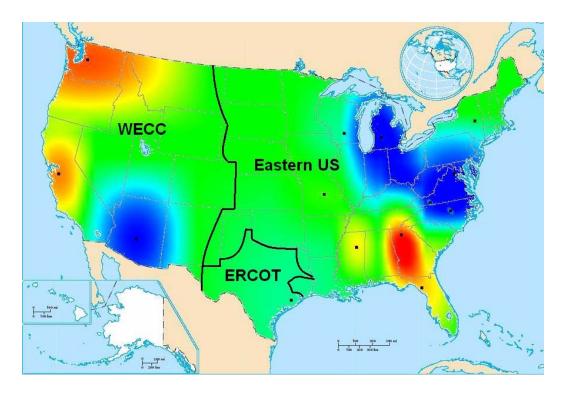

Figure 3.1 Frequency Monitoring Network (FNET) Architecture

Figure 3.1 shows the FNET architecture. The whole FNET system consists of three major components: Frequency Disturbance Recorders (FDR), the Information Management Server (IMS), and the Internet. Frequency Disturbance Recorders or FDRs perform as sensors, which are geographically dispersed at different locations in the US power grid. They take the 110V single-phase voltage input of residential wall outlets, calculate and

analyze the local frequency changing, and communicate with remote central servers via the Internet for data transmission and system configuration.

The Information Management Server (IMS) provides data collection, storage, communication, database operations, and web service. The IMS design is based on the multi-tier client/server architecture, which coordinates, integrates and models the data collection, processing, display and other functions. The IMS performs four major functions:

- Communication with FDRs

- Database operation and management

- GUI and display

- Provides web service

The communication between FDRs and the IMS server is based on the TCP/IP protocol, which ensures a reliable connection and data transmission. The ongoing and future research of IMS functions includes historical data retrieval, automatic event trigger and reconstruction, and event prediction.

One of the most crucial innovations of FNET is that the FDR can perform the frequency measurement based on the 110V voltage input from 110V wall outlets; thus the overall cost of FNET can be significantly reduced, which enables the build up, expansion and reinforcement of FNET within a short period of time. With the efforts of the research team at Virginia Tech and associate members in different universities and industrial facilities, the FNET system started operation in summer of 2004, and there are almost 30 FDR units installed in critical locations as of January 2006. The FNET has made observations of the entire power grid of US possible for the first time.

# 3.2 Frequency Disturbance Recorder Design Overview

The Frequency Disturbance Recorder (FDR) is a measurement device that is capable of taking the single phase voltage from a wall plug, calculating and analyzing the frequency

dynamics, and sending measurement results to central servers. In FNET, FDRs perform as remote sensors, and are distributed at many critical observation locations all over the US. The measurement accuracy is one of the most important concerns for FDR design, as all FNET applications are based on the measurement data. In other words, the more accurate the measurements are the more reliable and valuable the FNET applications are. According to the review and comparison results of the frequency estimation algorithms discussed in Section 2, the Phasor Angle Analysis technique can provide acceptable frequency estimation accuracy as well as many other advantages for algorithm implementation.

In order to capture the whole picture of power grid performance throughout the US at any given instant, all the measurement data should have a common time reference for synchronization, which is the most important feature for wide-area monitoring. The use of different time references in monitoring systems of different companies is partially responsible for the delay in determining the causes of the 2003 North America Blackout. In the past several years, recognizing the importance of frequency at different locations for system performance monitoring and analysis, many attempts have been made to synchronize the frequency measurement. However, none of these attempts could be called a success, as those technologies put severe limitations on the achievable accuracy of synchronization. It is only in recent years, as GPS has become more available and economical for civil applications, that we can synchronize the measurement in a practical and affordable way with a synchronization error of less than 1 microsecond.

According to an EPRI study, the noise of a real world power system is a combination of harmonic noise, white noise and random noise[27]. Harmonic noise comes from the harmonic components in the input signal. White noise is the frequency spectrum over a wide range of frequencies, and all frequency components in equal amounts. A random spike is generated by external random changes, such as sudden load change, lighting, and capacitor switching. The noise in the power system has severe impacts on the accuracy of frequency measurement, so analog and digital filter design is an important part of FDR implementation. In recent years, significant improvement has been made on MATLAB

Signal Processing Toolbox, which provides a convenient and effective Filter Design and Analysis Tool (FDA Tool). With the FDA Tool, it is easy to make a primary design, analyze and adjust digital filters to meet system requirements. Coupled with advanced digital processing techniques of a Microcontroller DSP or FPGA, digital filters can be effectively implemented with expected performance.

Traditionally, most power system measurements are performed locally, so geographic distance and time delay prevent those measurements from being easily employed for different power system monitoring, protection and control purposes. In recent years, with information technologies that have developed so quickly, the internet has become a safe and reliable media for data transmission, which makes wide-area synchronized measurement more realistic and desirable.

Taking full advantage of the state-of-the-art technologies and concepts in different areas, the compact portable frequency disturbance recorder provides the GPS synchronized, close to real-time frequency measurement and analysis data from flexible locations in US to one or multiple central servers.

Conceptually, the FDR comprises four main functional components:

- Main computation unit: it can be a microcontroller, DSP, FPGA or a PC,

- GPS receiver,

- Digital signal conditioning part,

- Serial to Ethernet converter.

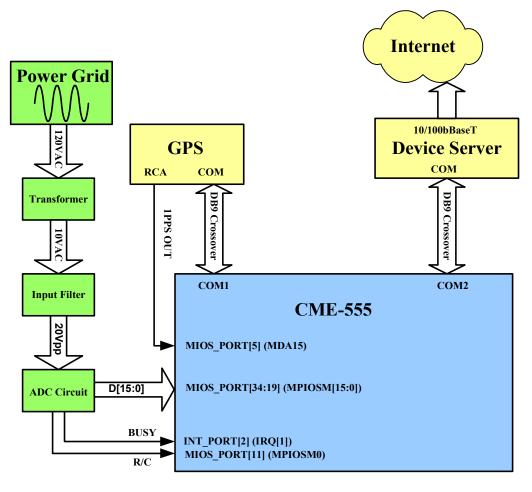

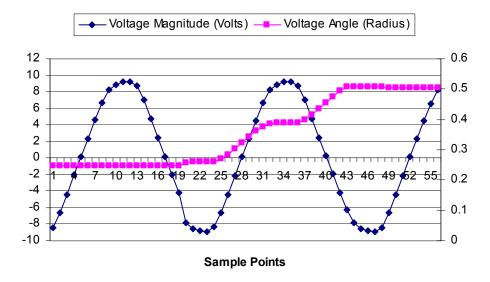

Figure 3.2 is the system block diagram of the second generation MCU-based FDR.

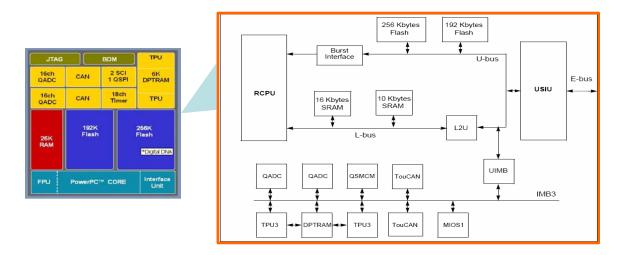

As shown in Figure 3.2, the main computation unit is based on MPC555 from Freescale, and CME-555 is the off-the-shelf evaluation board of MPC555 from Axiom Manufacturers. The CME 555 performs voltage input digitizing and filtering, and it also provides precise and clean voltage data for frequency estimation. The CME 555 is where the frequency estimation algorithm is located, and it also performs the GPS time synchronization, data communication, signal conditioning, interrupt handling, process scheduling and other functions.

Figure 3.2 System Block Diagram

In the second generation of the FDR, the M12+ timing GPS receiver from Motorola is adopted (On June 2<sup>nd</sup>, 2005, SiRF Technology Acquires Motorola's GPS Chip Set Product Lines), which provides precise Pulse Per Second signal, and the common timing stamp for different units dispersed in different locations. The timing accuracy of M12+ timing GPS receiver is less than 500ns with SA on, and the Motorola binary I/O commands can be used to initialize, configure, control, and monitor the GPS receiver. With GPS, the frequency estimation of different units is on a common reference if they are sampled at precisely the same instant.

The serial-to-Ethernet converter, the Device Server, makes the device networked. Compared with serial communication, Ethernet communication needs tremendous time and cost to make it reliable. The Device Server saves those efforts, and provides an easy and practical way to make serial communication data be Ethernet data, which can be

transmitted to remote access points via TCP/IP. The Device Server can be configured remotely online; therefore it gives great flexibility for different data collection relocation and analysis applications interface updates.

Figure 3.3 Appearance of Frequency Disturbance Recorder

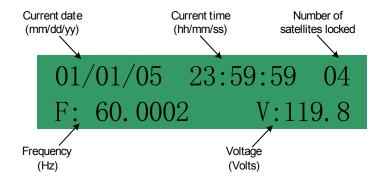

Figure 3.4 LCD panel display

The FDR is lightweight, has a compact size and is free-standing, and Figure 3.3 shows the first commercial FDR. In addition to the data transmitted via internet, on the front of FDR an 20×2 LCD provides the current frequency measurement result updated at a rate of 10 times per second. Figure 3.4 is a demo of the LCD message, which includes current time, frequency, RMS voltage, and the number of satellites locked by GPS. The frequency estimation precision of the second generation FDR is 0.0005 Hz in a lab environment, which can meet most needs of power system monitoring, control and protection applications.

# 3.3 Phasor Angle Analysis Algorithm Implementation

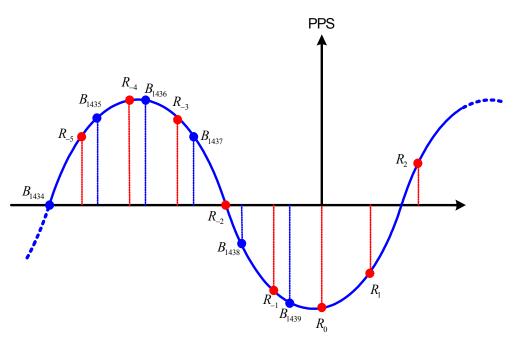

From (2.4.4) and (2.4.5), one can derive the successive phasor expression:

$$X_{c}^{(k+1)} = X_{c}^{(k)} + \frac{2}{N} (x_{k+1} - x_{k+1-N}) \cos\left(\frac{2\pi}{N}k\right)$$

$$X_{s}^{(k+1)} = X_{s}^{(k)} - \frac{2}{N} (x_{k+1} - x_{k+1-N}) \sin\left(\frac{2\pi}{N}k\right)$$

(3.3.1)

$$k = N f_0 t \tag{3.3.2}$$

where

N is the number of phasor angles per cycle and

$f_0$  is the nominal frequency.

The angle of the kth phasor is given by:

$$\psi(k) = \tan^{-1} \frac{-X_s^{(k)}}{X_c^{(k)}}.$$

(3.3.3)

Assuming a quadratic function could express the variation of phasor angles with respect to the sample numbers:

$$\psi(k) = a_0 + a_1 k + a_2 k^2, \qquad (3.3.4)$$

a computation window with M phasor angles are used to estimate the value of coefficients  $a_0$ ,  $a_1$  and  $a_2$ .

$$\psi(1) = a_0 + a_1 1 + a_2 1^2$$

$$\psi(2) = a_0 + a_1 2 + a_2 2^2$$

$$\vdots \qquad \vdots \qquad \vdots$$

$$\psi(M) = a_0 + a_1 M + a_2 M^2$$

(3.3.5)

Rewriting equation (3.3.5) in matrix format yields:

$$\begin{bmatrix} \psi_1 \\ \psi_2 \\ \vdots \\ \psi_M \end{bmatrix} = \begin{bmatrix} 1 & 1 & 1 \\ 1 & 2 & 2^2 \\ \vdots & \vdots & \vdots \\ 1 & M & M^2 \end{bmatrix} \begin{bmatrix} a_0 \\ a_1 \\ a_2 \end{bmatrix} \quad \text{or} \quad \psi = Xa . \tag{3.3.6}$$

Using the least error square solution the matrix a can be solved:

$$\mathbf{a} = \left[ \mathbf{X}^T \mathbf{X} \right]^{-1} \mathbf{X}^T \phi . \tag{3.3.7}$$

Taking the derivate of (3.3.4) with respect to k,

$$\frac{d\psi}{dk} = a_1 + 2a_2k \ . \tag{3.3.8}$$

Taking the derivate of (3.3.2) with respect to t,

$$\frac{dk}{dt} = Nf_0. ag{3.3.9}$$

So

$$\frac{d\psi}{dt} = \frac{d\psi}{dk}\frac{dk}{dt} = Nf_0 \frac{d\psi}{dk} = Nf_0 \left(a_1 + 2a_2k\right) = Nf_0 \left(a_1 + 2a_2Nf_0t\right)$$

(3.3.10)

with (2.4.31) and (2.4.33)

$$\Delta f \approx \frac{1}{2\pi} N f_0 \left( a_1 + 2a_2 N f_0 t \right)$$

(3.3.11)

$$\frac{df}{dt} \approx \frac{1}{2\pi} 2\left(Nf_0\right)^2 a_2. \tag{3.3.12}$$

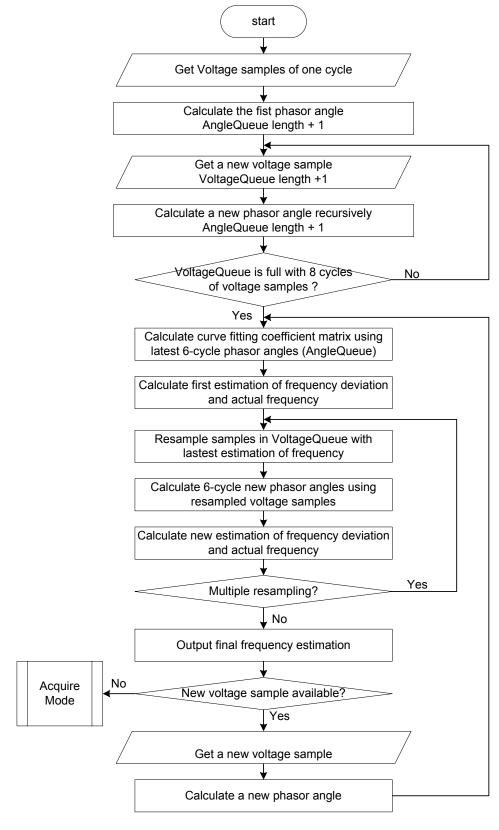

The actual power system frequency varies from the DFT fundamental frequency by an amount of  $\Delta f$ . Equations (3.3.11) and (3.3.12) are the main formulas used for frequency estimation in FDRs. It must be remembered that the frequency estimation obtained at the end of the computation window is actually the frequency at the half cycle point before the end of the window. This is because the phasor computed at the end of one cycle actually represents the phasor at the center. Figure 3.5 shows the flow chart of algorithm initialization and the flow chart of main function body.

Figure 3.5 Flow chart of frequency estimation algorithm

### 3.4 Hardware Architecture

As shown in Figure 3.2, the second generation of FDR consists of six major hardware subsystems: a microcontroller system (single board computer), an A/D Converter, a GPS receiver, a serial-to-Ethernet converter (device server), an analog filter, and a power supply. In order to meet the performance goals for the whole system, the selection and integration of these subsystems have consistently been a huge challenge.

### 3.4.1 Microcontroller

Do we need fixed- or floating-point-based microcontroller (or DSP for 3<sup>rd</sup> generation) for this system? This is the first question we came up with when we selected the microcontroller. As the terms fixed-point and floating-point indicate, the fundamental difference between the two types of computation is in their respective numeric representations of data. While fixed-point hardware performs strictly integer arithmetic, floating-point hardware supports either integer or real arithmetic. Therefore the fixed-point data has less bit-width, so it is more hardware efficient than the floating-point hardware. In addition, real arithmetic could be coded directly into hardware operations with the floating-point format, while fixed-point devices must implement real arithmetic indirectly through software routines, which adds development time and extra instructions to the algorithm.

The much greater computational power offered by the floating-point unit is normally the critical element in the fixed- or floating-point design decision. However, the floating-point representation has longer bit-width, and thus requires more internal circuitry and more hardware resources. These factors, in addition to the greater number of pins required by the wider data bus, meant a larger die and larger package that resulted in a significant cost premium for the new floating-point devices. Offsetting the cost issue is the fact that the floating-point microcontroller is easier to program; usually they have been adopted for low-volume applications where the time and cost of software development were of greater concern than unit manufacturing costs. A fixed-point

microcontroller is therefore favored for high-volume applications like digitized voice and telecom concentration cards, where unit manufacturing costs have to be kept low.

Microcontroller performance is another important concern for microcontroller selection. It is a common trap to compare microcontroller performance only by crystal frequency. The fact of the matter is that many microcontroller vendors have included bonus architectural features to the microcontroller. Those features enable micros and peripherals run directly off the crystal oscillatory circuitry, which make designs easily meet RT and EMI specifications when the crystal speed is ideally matched to performance.

There are a variety of benchmarks to evaluate microcontroller performance. The Embedded Microprocessor Benchmark Consortium (EEMBC) is one of the most widely used benchmarks to help the designer to decide the best for their application. EEMBC provides an easy way to objectively evaluate both microcontroller performance and compiler efficiency, and offers system designers a valuable tool for selecting the right embedded processors for their systems. EEMBC was founded by a group of semiconductor vendors seeking a method for determining relative levels of processor performance with more representative workloads than Dhrystones. Today EEMBC's members include over fifty of the world's leading microcontroller and microprocessor vendors, such as Freescale, NEC, and AMD.

There are two common classifications for defining the kind of instruction set the processor has: CISC (Complex Instruction Set Computer) means that the processor has a large set of instructions that perform complex tasks, and RISC (Reduced Instruction Set Computer) means that that the processor has quite a small set of instructions so that they do less per command (complicated operations are done by combining many simple instructions to perform a complicated task). Some processors are CISC-based (like x86, Z80etc.), while others are RISC-based (like ARM, MIPS, PowerPC).

In today's embedded microcontroller market, ARM, MIPS and PowerPC are the three most popular RISC computer architectures. The ARM architecture, originally the Acorn

RISC Machine, was started in 1983 as a development project at Acorn Computer Ltd. Due to its power-saving features, ARM variants are in a variety of embedded and low-power applications; ARM7TDMI has been the most successful implementation with hundreds of millions sold in mobile phones and handheld video game systems. ARM's main business has always been to sell IP cores, and many licensees, such as Freescale, IBM, TI, and Intel, have licensed the basic ARM core for various uses.

MIPS (Microprocessor without interlocked pipeline stages), is another popular RICS computer architecture developed by MIPS Computer Systems Inc. The latest of these, MIPS 32/64 Release 2, defines a control register set as well as the instruction set. Several "add-on" extensions are also available, including MIPS-3D, which is a simple set of floating-point SIMD instructions dedicated to common 3D tasks; MDMX, which is a more extensive integer SIMD instruction set using the 64-bit floating-point registers; and MIPS16, which adds compression to the instruction stream to make programs smaller. The use of MIPS designs is widespread in SGI's computer product line, Windows CE devices, and Cisco routers.

PowerPC is a RISC microprocessor architecture created by the 1991 Apple-IBM-Motorola alliance, known as AIM. PowerPC processors bring the processor's local bus to the chip's surface, and connect to a bridge chip that translate this into other on-board device buses that attach to RAM, PCI, and other devices. Thirty-two-bit PowerPC processors have been a favorite of embedded computer designers. Originally intended for personal computers, PowerPC CPUs have since become popular embedded and high-performance processors as well. Besides Apple's Macintosh lines from 1994-2005, the greatest success of PowerPC architecture, PowerPC processors have been used in many embedded products and will be contained in the sixth-generation consoles of the three most popular game consoles: Sony's PlayStation 3, Microsoft's Xbox 360, and the Nintendo Revolution console.

The MPC555 is a high-speed 32-bit central processing unit that contains a floating-point unit designed to accelerate the advanced algorithms necessary to support complex