# Planar Metallization Failure Modes in Integrated Power Electronics Modules

By

# Ning Zhu

Dissertation submitted to the faculty of the Virginia Polytechnic Institute and State

University in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

In

#### **ELECTRICAL ENGINEERING**

Dr. J.D. van Wyk

Dr. Z.X. Liang

Dr. W.G. Odendaal

Dr. G.Q. Lu

Dr. Carlos T A Suchicital

Dr. Michael C. Shaw

April 14, 2006

Blacksburg, Virginia

Keywords: Planar Metallization, Failure Mode, Integrated Power Electronics Modules, Intrinsic Residual Stress, Thermo-mechanical Stress, Peel Stress, In-plane Stress, Power Cycling Test, Temperature Cycling Test

Copyright@2006, Ning Zhu

#### Planar Metallization Failure Modes in Integrated Power Electronics Modules

By

Ning Zhu

J.D. van Wyk, Chairman

Electrical Engineering

### **Abstract**

Miniaturizing circuit size and increasing power density are the latest trends in modern power electronics development. In order to meet the requirements of higher frequency and higher power density in power electronics applications, planar interconnections are utilized to achieve a higher integration level. Power switching devices, passive power components, and EMI (Electromagnetic Interference) filters can all be integrated into planar power modules by using planar metallization, which is a technology involving electrical, mechanical, material, and thermal issues. By processing high dielectric materials, magnetic materials, or silicon chips using compatible manufacturing procedures, and by carefully designing structures and interconnections, we can realize the conventional discrete inductors, capacitors, and switch circuits with planar modules. Compared with conventional discrete components, the integrated planar modules have several advantages including lower profiles, better form factors, and less labor-intensive processing steps. In addition, planar interconnections reduce the wire bond inductive and resistive parasitic parameters, especially for high frequency applications.

However, planar integration technology is a packaging approach with a large contact area between different materials. This may result in unknown failure mechanisms in power applications. Extensive research has already been done to study the performance, processing, and reliability of the planar interconnects in thin film structures. The thickness of the thin films used in integrated circuits (IC) or microelectronics applications ranges from the magnitude of nanometers to that of micrometers. In this work, we are

interested in adopting planar interconnections to Integrated Power Electronics Modules (IPEM). In Integrated Power Electronics Modules (IPEMs), copper traces, especially bus traces, need to conduct current ranging from a few amps to tens of amps. One of the major differences between IC and IPEM is that the metal layer in IPEMs (normally >75μm) is much thicker than that of the thin films in IC (normally <1μm). The other major difference, which is also a feature of IPEM, is that the planar metallization is deposited on different brittle substrates. In active IPEM, switching devices are in a bare die form with no encapsulation. The copper deposition is on top of the silicon chips and the insulation polyimide layer. One of the key elements for passive IPEM and the EMI IPEM is the integrated inductor-capacitor (LC) module, which realizes equivalent inductors and capacitors in one single module. The deposition processes for silicon substrates and ceramic substrates are compatible and both the silicon and ceramic materials are brittle. Under high current and high temperature conditions, these copper depositions on brittle materials will cause detrimental failure spots.

Over the last few years, the design, manufacture, optimization, and testing of the IPEMs has been developed and well documented. Up to this time, the research on failure mechanisms of conventional integrated power modules has led to the understanding of failures centered on wire bond or solder layer. However, investigation on the reliability and failure modes of IPEM is lacking, particularly that which uses metallization on brittle substrates for high current operations. In this study, we conduct experiments to measure and calculate the residual stresses induced during the process. We also, theoretically model and simulate the thermo-mechanical stresses caused by the mismatch of thermal expansion coefficients between different materials in the integrated power modules. In order to verify the simulation results, the integrated power modules are manufactured and subjected to the lifetime tests, in which both power cycling and temperature cycling tests are carried out. The failure mode analysis indicates that there are different failure modes for copper films under tensile or compressive stresses. The failure detection process verifies that delamination and silicon cracks happen to copper films due to compressive and tensile stresses respectively.

This study confirms that the high stresses between the metallization and the silicon are the failure drivers in integrated power electronics modules.. We also discuss the driving forces behind several different failure modes. Further understanding of thesefailure mechanisms enables the failure modes to be engineered for safer electrical operation of IPEM modules and helps to enhance the reliability of system-level operation. It is also the basis to improve the design and to optimize the process parameters so that IPEM modules can have a high resistance to recognized failures.

**Acknowledgements**

I would like to give my deepest appreciation to my advisor, Dr. J.D. van Wyk, for

embarking with this project and unconditionally supporting me to complete this study.

With his greatest patience, he leads me to this very interesting area, about which I have

great passion finally, although knew nothing from the beginning. It is such a great

experience to be his student for these years. Without him, I cannot get so far. The spirit

and methodology he passed on us will benefit me in my whole life.

Thank you, Dr. Z. X .Liang, for giving me hands on helps almost anytime I need and

anywhere I can find you. Thank you for your smart ideas and encouragements throughout

my research. I also want to thank Dr. Michael C. Shaw, Dr. G.Q. Lu, Dr. Carlos T A

Suchicital, and Dr. W.G. Odendaal to share their research results with me, provide

important technical inputs and resources, and to spend time with me for further

improvements.

I would like to thank all the stuff and faculties in CPES for providing us this good

research and education environment. Thank you for my colleagues in CPES. You always

let me feel at home.

Very special thanks to Prof. Liu Dichen, who is my advisor of my master's degree.

He is the one introduce me into power electronics area and encourage me to pursue

further educations.

Finally, I need to thank my family. That is where I came from and who I am. My

parents taught me to be gentle, yet be strong, to be smart, but not aggressive. Always be

prepared and look forward for better future especially in hard times. I am proud to be

their daughter.

To all the friends, thank you!

Ning Zhu

April 2006

Blacksburg, VA

V

# **Table of Contents**

| Abstract    |                                                                 | ii   |

|-------------|-----------------------------------------------------------------|------|

| Acknowle    | dgements                                                        | v    |

| List of Fig | gures                                                           | X    |

| List of Ta  | bles                                                            | xvii |

| Chapter 1   | Introduction                                                    | 1    |

| 1.1 Hi      | gh density integration trends in power electronics applications | 1    |

| 1.2 Cu      | nrrent interconnection technologies                             | 4    |

| 1.2.1       | Wire bonding                                                    | 4    |

| 1.2.2       | Ball grid array                                                 | 6    |

| 1.2.3       | Planar metallization interconnection                            | 7    |

| 1.3 Ap      | oplications of the planar interconnect technology               | 9    |

| 1.3.1       | Embedded Power modules                                          | 9    |

| 1.3.2       | Integrated power passive modules                                | 11   |

| 1.3.3       | Integrated EMI filters                                          | 16   |

| 1.4 Ai      | m of this study                                                 | 18   |

| 1.4.1       | Summary of related research                                     | 18   |

| 1.4.2       | Research work covered in this study                             | 20   |

| Chapter 2   | : Metal Films on Brittle Substrates in IPEMs                    | 22   |

| 2.1 Fa      | brication processes of integrated modules                       | 22   |

| 2.1.1       | Integrated active modules (Embedded Power)                      | 22   |

| 2.1.2       | Integrated passive modules                                      | 25   |

| 2.1.3       | Integrated EMI filters                                          | 27   |

| 2.2    | Met   | tal Films on Brittle Substrates in IPEMs                        | 28 |

|--------|-------|-----------------------------------------------------------------|----|

| 2.3    | Inte  | rfaces properties                                               | 30 |

| 2.3    | .1    | DBC Cu-Alumina interface                                        | 32 |

| 2.3    | .2    | Inter-metallic interfaces                                       | 32 |

| 2.3    | .3    | Surface roughness of different substrates                       | 35 |

| 2.4    | Med   | chanical properties of electroplated Cu film                    | 37 |

| 2.5    | Effe  | ect of film intrinsic residual stress                           | 41 |

| Chapte | er 3: | Intrinsic Residual Stress                                       | 43 |

| 3.1    | Intr  | oduction and Literature Review                                  | 43 |

| 3.2    | Mea   | asurement of Intrinsic Residual Stress in Glass-metal Structure | 45 |

| 3.2    | .1    | Sample preparation                                              | 45 |

| 3.2    | .2    | Measuring the bending of glass-copper structure                 | 49 |

| 3.2    | .3    | Calculation of the intrinsic residual stress                    | 51 |

| 3.3    | Pos   | sible methods to minimize the residual stress                   | 53 |

| 3.3    | .1    | Optimize electroplating parameters                              | 53 |

| 3.3    | .2    | Annealing of the residual stress                                | 54 |

| 3.4    | Cha   | pter review                                                     | 55 |

| Chapte | er 4: | Thermo-mechanical Stresses in IPEMs                             | 56 |

| 4.1    | Ten   | nperature Distribution in Embedded Power Module                 | 56 |

| 4.1    | .1    | Simulation and experimental results                             | 56 |

| 4.1    | .2    | Time constant of simplified structure                           | 58 |

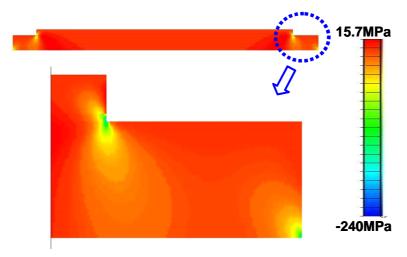

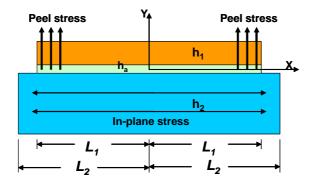

| 4.2    | The   | rmo-mechanical Stress in Simplified Structure                   | 61 |

| 4.2    | 1     | Von Mises stress                                                | 61 |

| 4.2   | 2.2    | In-plane stress                                                   | 64     |

|-------|--------|-------------------------------------------------------------------|--------|

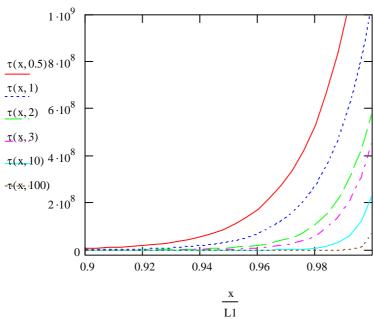

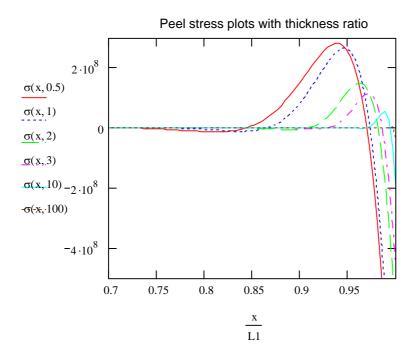

| 4.2   | 2.3    | Peel stress                                                       | 70     |

| 4.2   | 2.4    | Shear stress                                                      | 76     |

| 4.3   | FEI    | M modeling and simulation in Embedded Power multi-layer structure | 77     |

| 4.4   | The    | ermo-mechanical stress investigation in passive modules           | 80     |

| 4.5   | Cha    | apter Review                                                      | 86     |

| Chapt | ter 5: | Power Cycling and Temperature Cycling Test                        | 88     |

| 5.1   | Em     | bedded Power modules power cycling test                           | 88     |

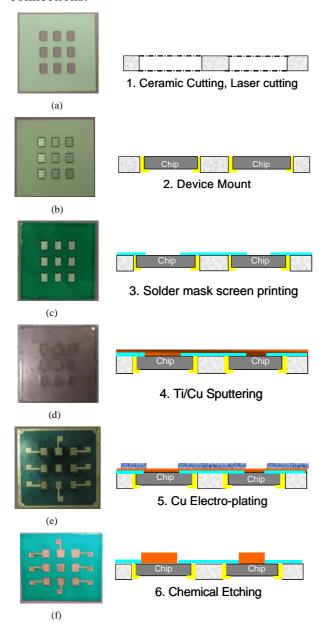

| 5.1   | 1.1    | Sample preparation                                                | 88     |

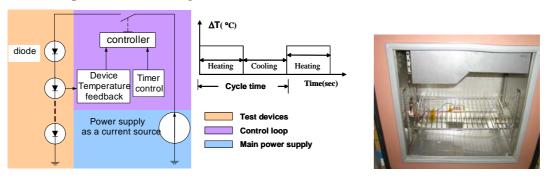

| 5.1   | 1.2    | Power cycling test setup and test results                         | 90     |

| 5.1   | 1.3    | Failure mode analysis for Embedded Power module after power cy    | cling  |

| tes   | st     | 92                                                                |        |

| 5.2   | Em     | bedded Power modules temperature cycling test                     | 94     |

| 5.2   | 2.1    | Temperature cycling test setup and test results                   | 94     |

| 5.3   | Eff    | ect of contact pattern on Embedded Power maximum working temper   | rature |

|       | 96     |                                                                   |        |

| 5.4   | Inte   | egrated power passive modules power cycling test                  | 103    |

| 5.4   | 4.1    | Sample preparation                                                | 103    |

| 5.4   | 4.2    | Test setup and test results                                       | 104    |

| 5.4   | 4.3    | Failure mode analysis for integrated passive modules              | 106    |

| 5.5   | Cha    | apter review                                                      | 107    |

| Chapt | ter 6: | Optimization Design in Simplified Structures                      | .109   |

| 6.1   | Des    | sign guidelines for optimized peel stress and in-plane stress     | 109    |

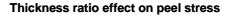

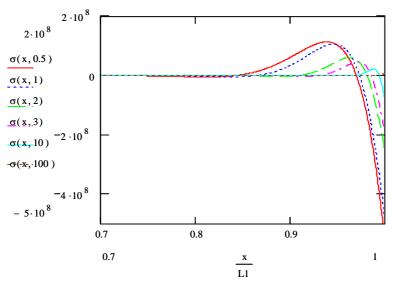

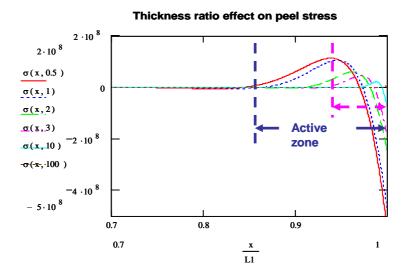

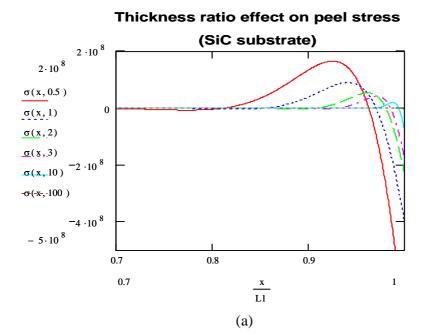

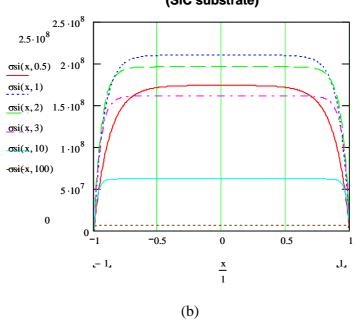

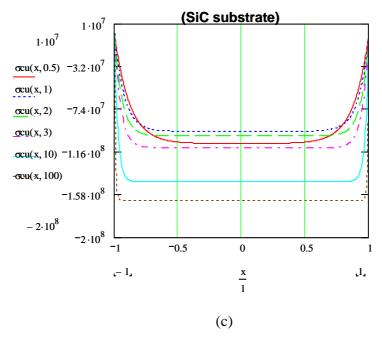

| 6     | 5.1.1   | Thickness ratio                   | 110 |

|-------|---------|-----------------------------------|-----|

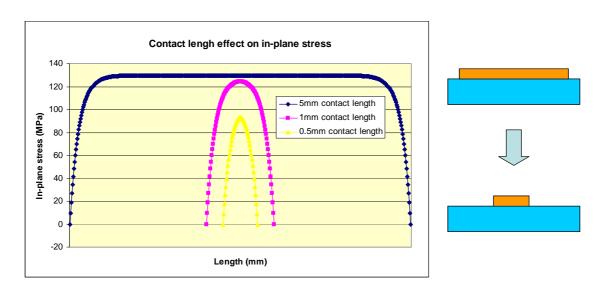

| 6     | 5.1.2   | Critical size of contact pattern  | 114 |

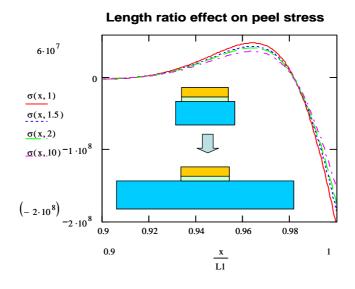

| 6     | 5.1.3   | Length ratio                      | 115 |

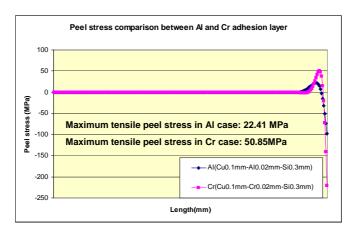

| 6     | 5.1.4   | Adhesion layer material selection | 117 |

| 6     | 5.1.5   | SiC and Si                        | 118 |

| 6.2   | Cha     | pter review                       | 121 |

| Chap  | oter 7: | Summary and future work           | 123 |

| 7.1   | Sun     | nmary                             | 123 |

| 7.2   | Futı    | ure work                          | 125 |

| Refe  | rences  |                                   | 127 |

| Appe  | endix A | A: E. Suhir's stress model        | 134 |

| Арре  | endix I | 3: Wang's stress model            | 137 |

| Appe  | endix ( | C: Related publications           | 140 |

| Vita. |         |                                   | 142 |

# **List of Figures**

| Figure 1.2.1 Power modules using wire bonding interconnection                                 |

|-----------------------------------------------------------------------------------------------|

| Figure 1.2.2 Schematic of a BGA module 6                                                      |

| Figure 1.2.3 Cross section schematic of a 3-D integration module                              |

| Figure 1.3.1Structural schematic of the Embedded Power module                                 |

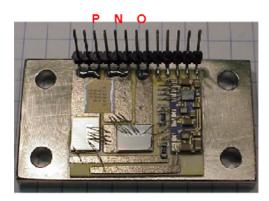

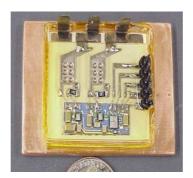

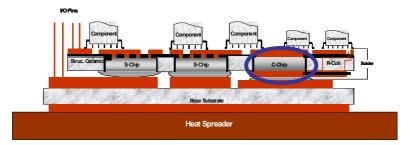

| Figure 1.3.2 Integrated power electronics module realized by Embedded Power                   |

| technique                                                                                     |

| Figure 1.3.3 Exploded view of the Embedded Power module                                       |

| Figure 1.3.4 1kW integrated DC/DC converter; (a)Embedded Power module;(b) circuit             |

| diagram                                                                                       |

| Figure 1.3.5 Embedded decoupling capacitor to decrease the current loop (a) Decoupling        |

| cap soldering on top of module (b) Embedded cap                                               |

| Figure 1.3.6 Embed MOSFET and capacitor into same alumina substrate                           |

| Figure 1.3.7 Cross-section view of embedded capacitor schematic structure                     |

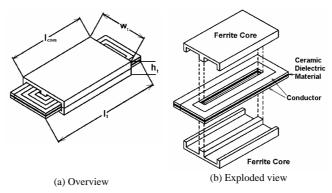

| Figure 1.3.8 Typical structure of a planar LC integrated passive resonant module 13           |

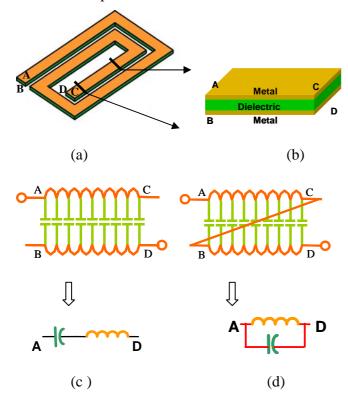

| Figure 1.3.9 Classification of typical resonators. (a) Spiral winding structure; (b) Physical |

| structure; (c) Series LC module used for integrated resonators in power electronics;          |

| (d) Parallel LC module used for integrated resonators in power electronics 14                 |

| Figure 1.3.10 Integrated parallel resonant transformer. (a) Explored view of integrated       |

| planar transformer; (b) Series Resonator-Transformer; (c) Parallel Resonator-                 |

| Transformer                                                                                   |

| Figure 1.3.11 1kW integrated parallel resonant converter transformer passives                 |

| Figure 1.3.12 The comparison of integrated EMI filter and discrete EMI filter. (a)            |

|-----------------------------------------------------------------------------------------------|

| Integrated EMI filter; (b) Discrete EMI filter; (c) Physical structure of integrated          |

| EMI filter                                                                                    |

| Figure 2.1.1 Cross-section schematic of Embedded Power Module                                 |

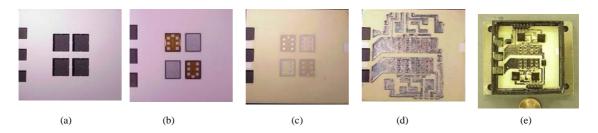

| Figure 2.1.2 Manufacturing process of test sample (a) laser cut substrate; (b) chip           |

| mounting; (c)solder mask screening; (d) electroplated copper with designed patterns;          |

| (e) final sample with encapsulation;                                                          |

| Figure 2.1.3 ceramic samples pictures                                                         |

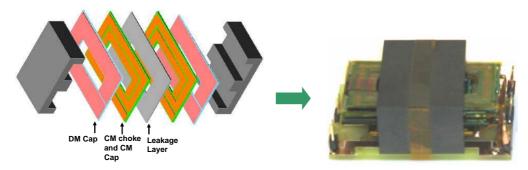

| Figure 2.1.4 Integrated power passive module                                                  |

| Figure 2.1.5 Integrated EMI filter                                                            |

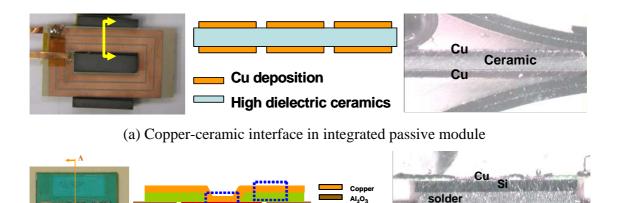

| Figure 2.2.1 Copper deposition on brittle substrates in IPEMs. (a) Copper-ceramic             |

| interface in Passive IPEMs; (b) Copper-Silicon interface in Active IPEMs 30                   |

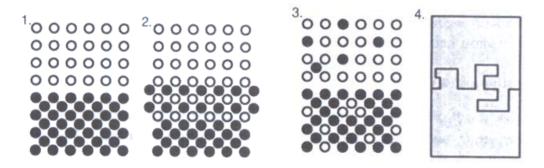

| Figure 2.3.1 Interfacial layers formed between film and substrate: (1) abrupt interface; (2)  |

| compound interface; (3) diffusion interface; (4) mechanical anchoring at interface 31         |

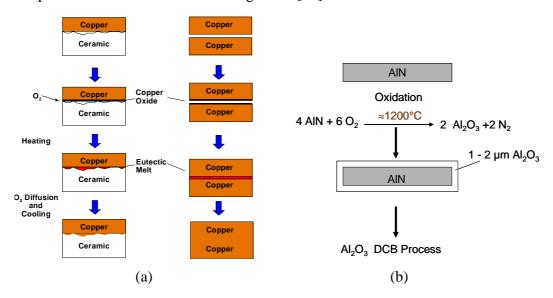

| Figure 2.3.2 DBC copper-ceramic bonding process (a) Alumina DBC; (b) AlN DBC                  |

| process reaction                                                                              |

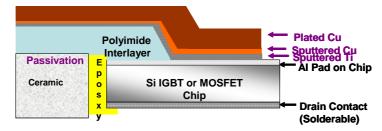

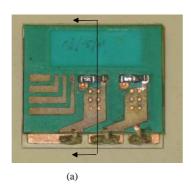

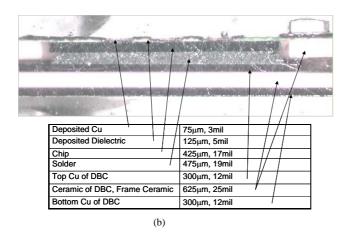

| Figure 2.3.3 Cross-section view of metallized substrates. (a) Inter-metallic interfaces of    |

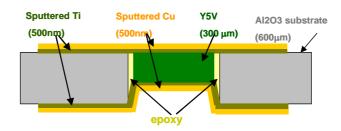

| Embedded Power modules. (b) Material layers in Passive IPEMs                                  |

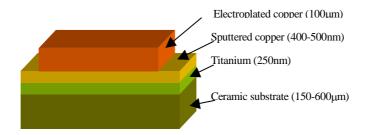

| Figure 2.3.4 Surface profiles of different substrates. (a) $Al_2O_{3}$ ; (b) Polymer; (c) Y5V |

| ceramics; (d)glass                                                                            |

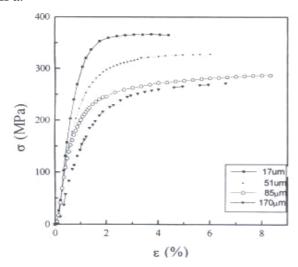

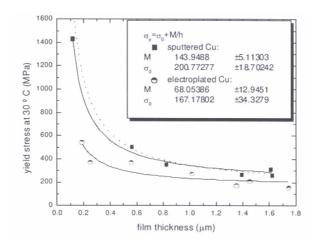

| Figure 2.4.1 The uniaxial stress-strain curves of Cu films of various thicknesses 39          |

| Figure 2.4.2 Tensile yield stress at 30°C as a function of film thickness for electroplated   |

| and sputtered Cu40                                                                            |

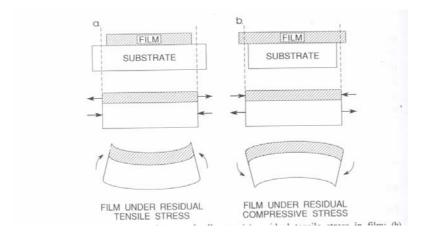

| Figure 3.1.1 residual tensile and compressive stress in the film                           |

|--------------------------------------------------------------------------------------------|

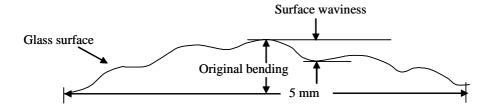

| Figure 3.2.1Schematic of original bending and surface waviness of glass                    |

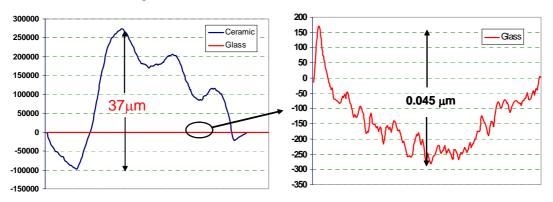

| Figure 3.2.2 The surface waviness comparison of ceramic substrate and glass substrate. (a  |

| two surface waviness curves listed in a same Y axis as comparison; (b) the enlarged        |

| glass surface waviness                                                                     |

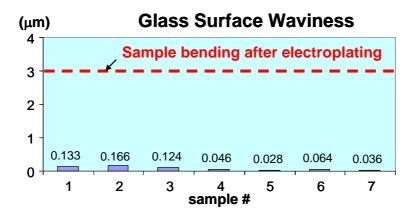

| Figure 3.2.3 Glass surface waviness is small enough to be neglected                        |

| Figure 3.2.4 Dektak measured Glass original bending. (a) the original bending varies a lot |

| (b) example bending curves of sample #1, #2, #7                                            |

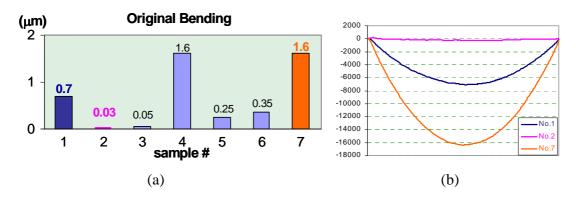

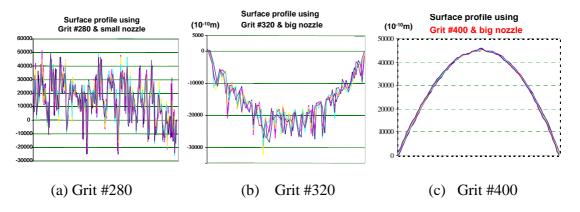

| Figure 3.2.5 Surface profiles of roughened glass surface                                   |

| Figure 3.2.6 Electroplating settings (a) frame to fix the sample; (b) electroplating tank  |

| settings                                                                                   |

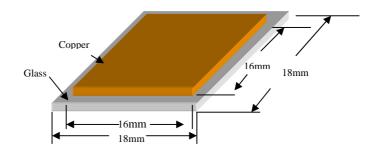

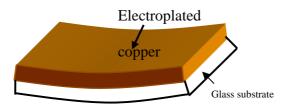

| Figure 3.2.7 Test sample for residual stress measurement                                   |

| Figure 3.2.8 Sample bending after electroplating. 49                                       |

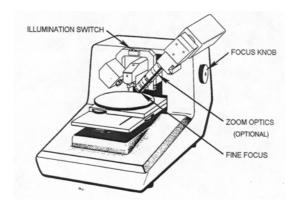

| Figure 3.2.9 Dektak surface profile measuring system                                       |

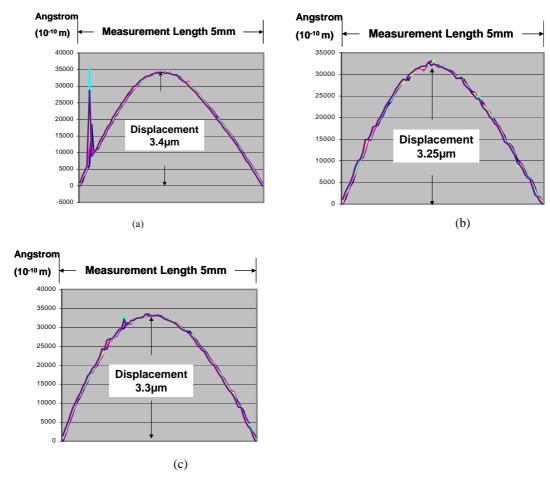

| Figure 3.2.10 Curvature Measurement results                                                |

| Figure 3.2.11 Mathematical model of the sample                                             |

| Figure 3.2.12 Glass substrate was electroplated in the same solution as the integrated     |

| active modules                                                                             |

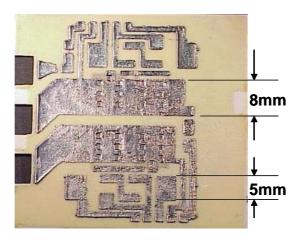

| Figure 4.1.1 PFC IPEM picture                                                              |

| Figure 4.1.2 Electrical terminals for PFC IPEM                                             |

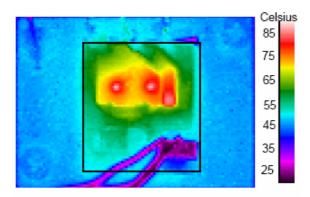

| Figure 4.1.3 Thermal image of PFC IPEM                                                     |

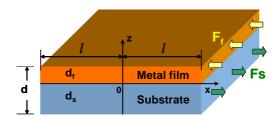

| Figure 4.1.4 Simplified Bi-material structure                                              |

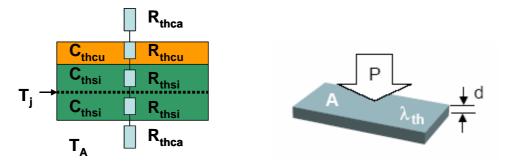

| Figure 4.1.5 Thermal model for the bi-material structure 59                                |

| Figure 4.1.6 Saber simulation model and time constant. (a) Saber thermal simulation      |

|------------------------------------------------------------------------------------------|

| model. (b) Time constant of copper-silicon structure                                     |

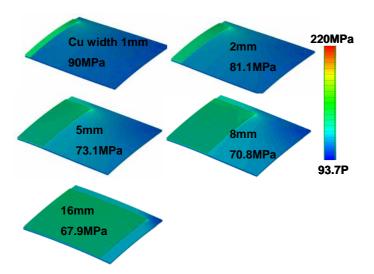

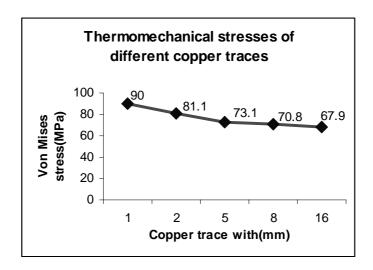

| Figure 4.2.1 Metallization pattern in Embedded Power modules                             |

| Figure 4.2.2 Thermo-mechanical stresses comparison between copper traces of different    |

| widths64                                                                                 |

| Figure 4.2.3 Von Mises thermal stresses under a temperature change from 20°C to 100°C    |

| 64                                                                                       |

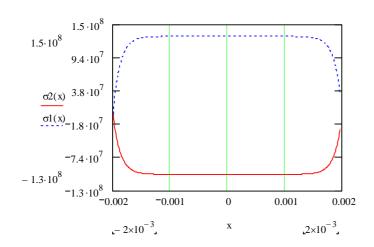

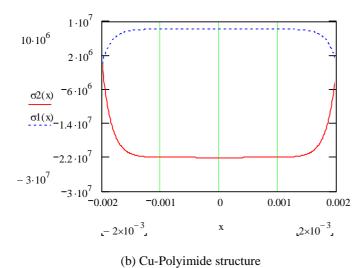

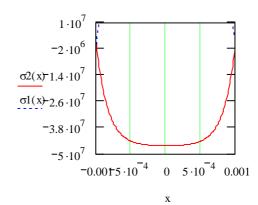

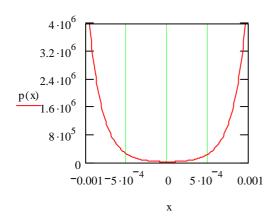

| Figure 4.2.4 Calculated in-plane stresses (a) Cu-Silicon structure; (b) Cu-Polyimide     |

| structure (#1 represents substrate; #2 represents film)                                  |

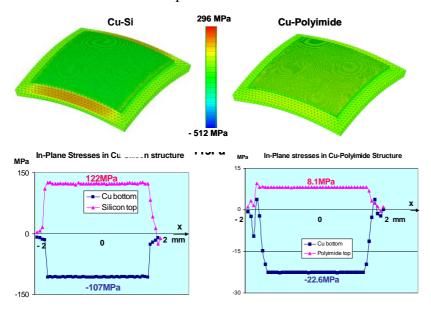

| Figure 4.2.5 Simulated in-plane stresses under a temperature change from 20°C to 100°C.  |

| (a) Von Mises stress distributions for Cu-Si case and Cu-polyimide case. (b)             |

| Interface in-plane stresses of each layer for both cases                                 |

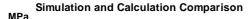

| Figure 4.2.6 Simulated stresses and calculated stresses comparison under temperature     |

| change from 20°C to 100°C70                                                              |

| Figure 4.2.7 Schematic of a bi-layer assembly with adhesion layer                        |

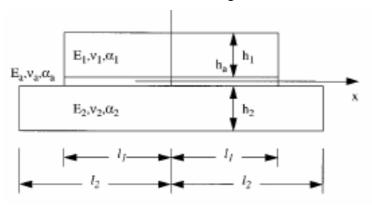

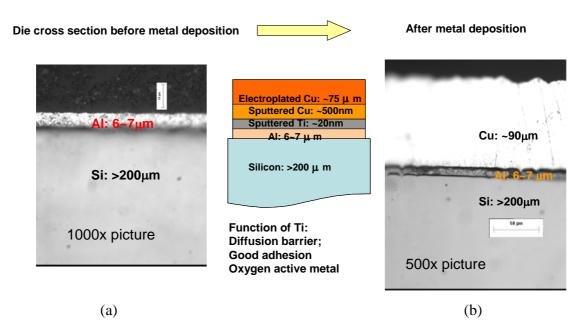

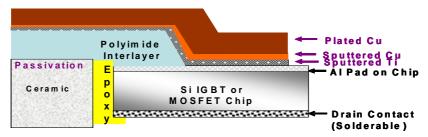

| Figure 4.2.8 Cross section of silicon chips before and after metal deposition process 73 |

| Figure 4.2.9 Peel stress plot Cu-Al-Si having thickness as 0.1mm, 0.006mm, and 0.3mm     |

| 74                                                                                       |

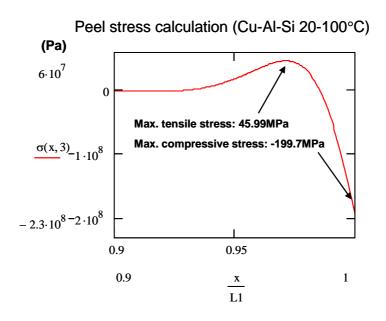

| Figure 4.2.10 Peel stress simulation results (thickness as Cu:0.1mm; Al:0.02mm;          |

| Si:0.3mm)                                                                                |

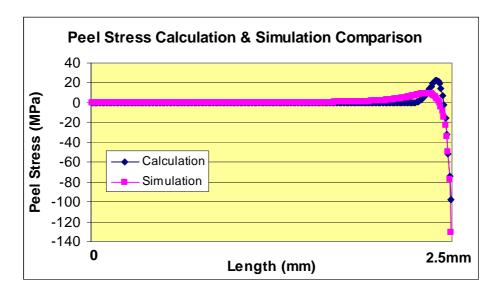

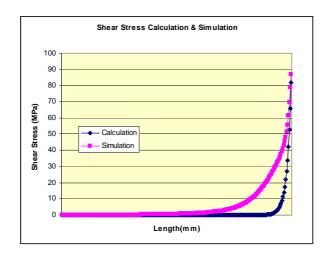

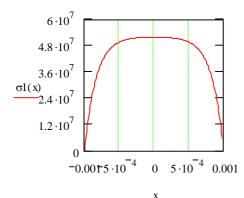

| Figure 4.2.11 Peel stress simulation and calculation results comparison                  |

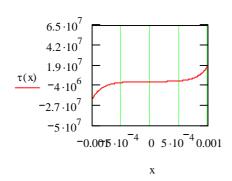

| Figure 4.2.12 Calculated and simulated shear stress                                      |

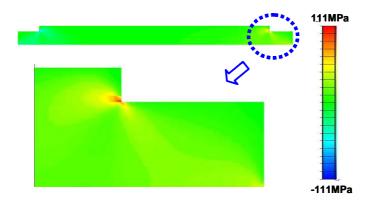

| Figure 4.2.13 Simulation of shear stress                                                 |

| Figure 4.3.1 Cross section view of Embedded Power Chip Stage                              |

|-------------------------------------------------------------------------------------------|

| Figure 4.3.2 The cross-section of Embedded Power Module Segment including MOSFET          |

| and surrounding parts (a) top view; (b) cross section view                                |

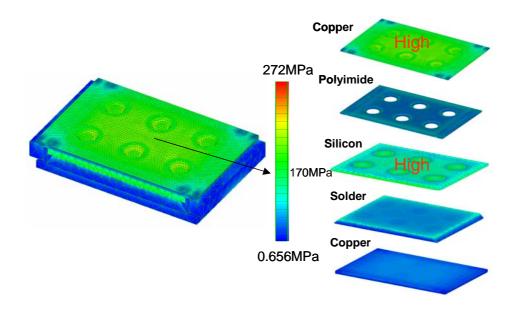

| Figure 4.3.3 Thermal-mechanical stress of different layers in the Embedded Powe           |

| Module (MOSFET segment)                                                                   |

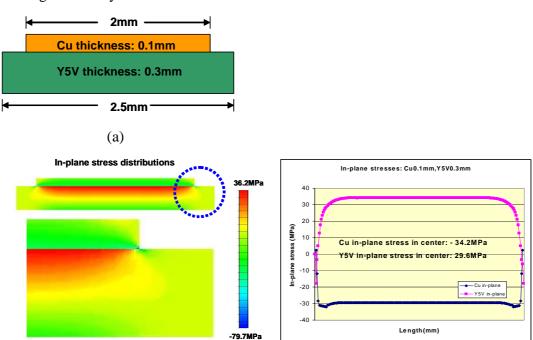

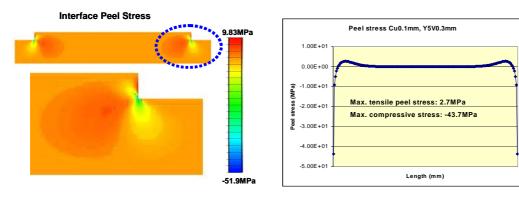

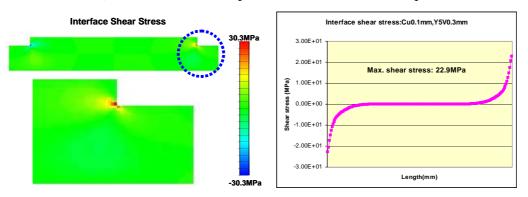

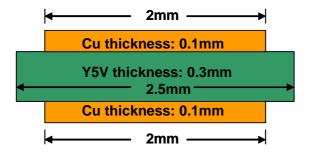

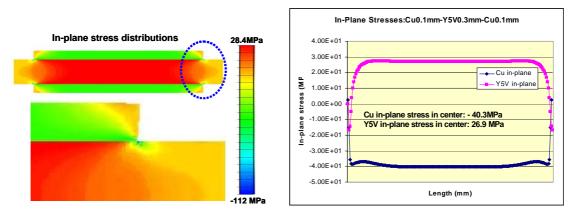

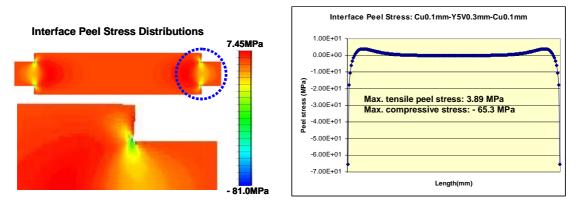

| Figure 4.4.1 Simulated stress distributions and plots in bi-material structure            |

| Figure 4.4.2 Simulated stress distributions and plots in tri-material structure           |

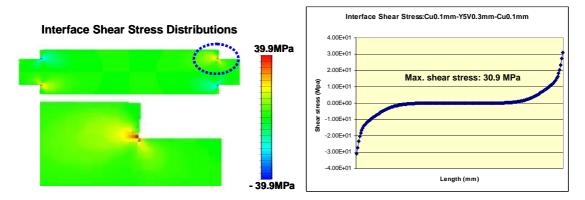

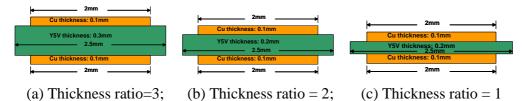

| Figure 4.4.3 Tri-material structures with different thickness ratios                      |

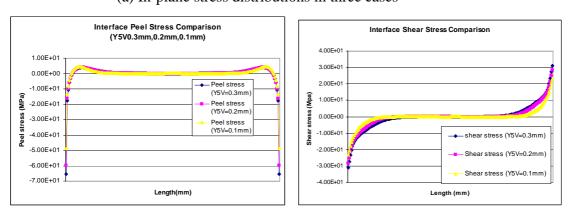

| Figure 4.4.4 In-plane stress, peel stress and shear stress comparison in three cases with |

| Y5V thickness 0.3mm, 0.2mm and 0.1mm.                                                     |

| Figure 5.1.1 Manufacturing process of test sample (a) laser cut substrate; (b) chip       |

| mounting; (c)solder mask screening; (d) sputtering copper; (e) photo resist; (f) fina     |

| sample;                                                                                   |

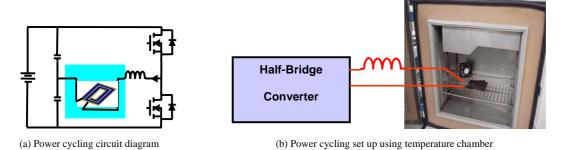

| Figure 5.1.2 Power cycling test circuit schematic and setup                               |

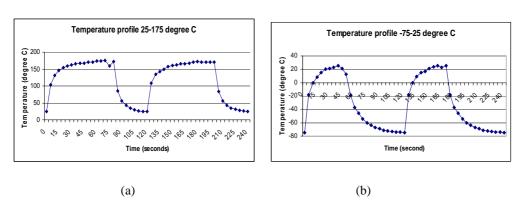

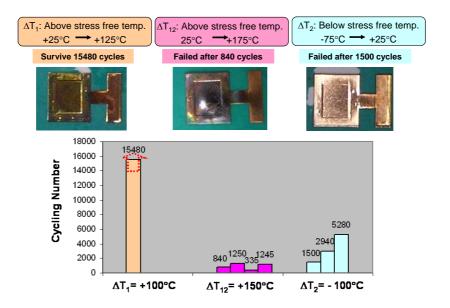

| Figure 5.1.3 Power cycling temperature profiles. (a) 25°C~175°C. (b) -75°C~25°C 92        |

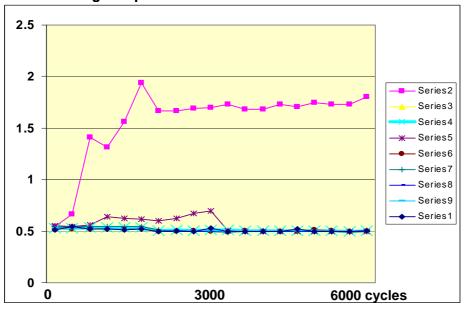

| Figure 5.1.4 Power cycling test results                                                   |

| Figure 5.1.5 Scanning Acoustic Microscopy                                                 |

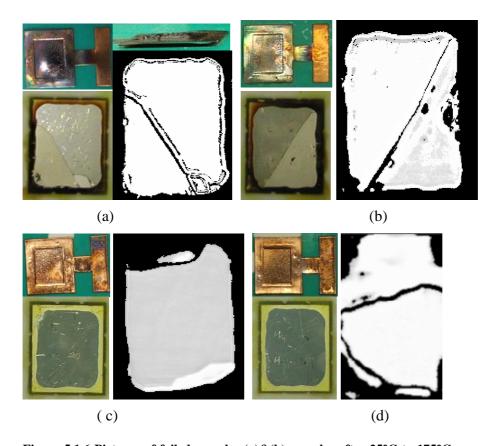

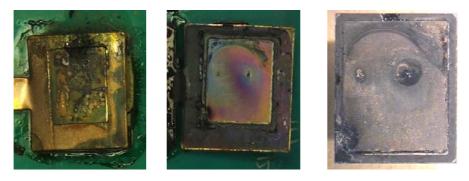

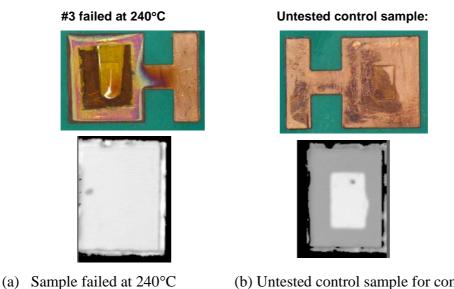

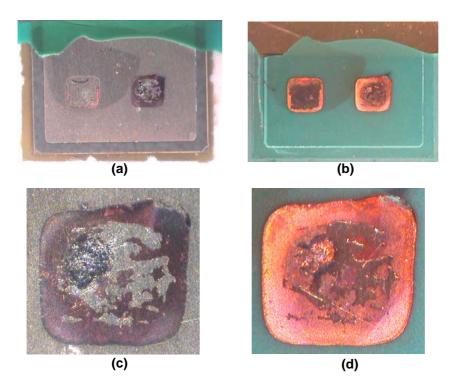

| Figure 5.1.6 Pictures of failed samples (a)&(b) samples after 25°C to 175°C power         |

| cycling; (c)&(d) samples after -75°C to 25°C power cycling                                |

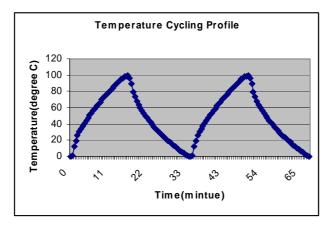

| Figure 5.2.1 Temperature cycling profile                                                  |

| Figure 5.2.2 Voltage drop through the source and drain                                    |

| Figure 5.3.1 An example of Embedded Power module                                          |

| Figure 5.3.2 Samples with different contact patterns                                      |

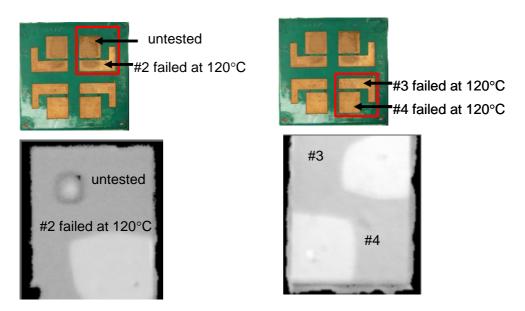

| Figure 5.3.3 Schematic of test circuit and temperature profile                      | 98      |

|-------------------------------------------------------------------------------------|---------|

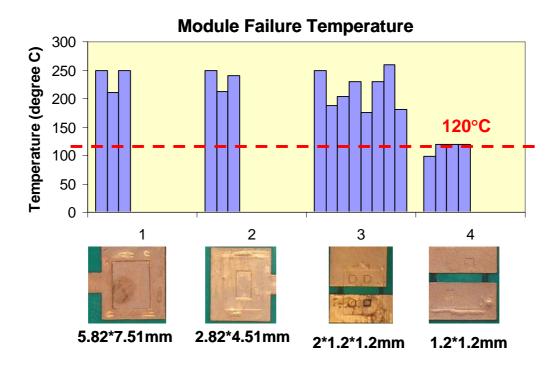

| Figure 5.3.4 Device failure temperatures                                            | 99      |

| Figure 5.3.5. An example of failed sample in Group 1                                | 99      |

| Figure 5.3.6 SAM pictures of failed samples.                                        | 100     |

| Figure 5.3.7 Failed samples in Group 3. (a) Silicon surface; (b) copper surface; (c | ) burn  |

| of silicon surface; (d) burn of copper surface.                                     | 101     |

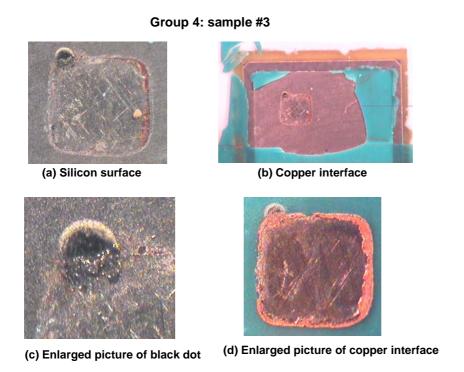

| Figure 5.3.8 SAM pictures of failed samples in Group 4.                             | 102     |

| Figure 5.3.9 Silicon and copper interface of failed sample #3.                      | 102     |

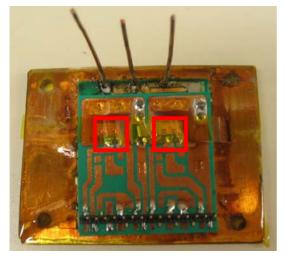

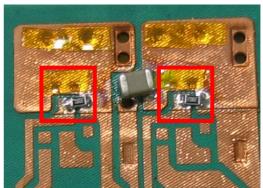

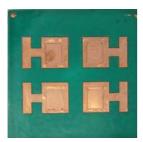

| Figure 5.4.1 Integrated LC series resonant passive modules used for power cyclin    | g test  |

|                                                                                     | 103     |

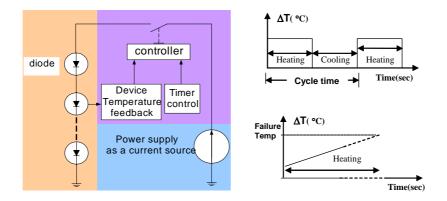

| Figure 5.4.2 Experimental test set up for power cycling test                        | 104     |

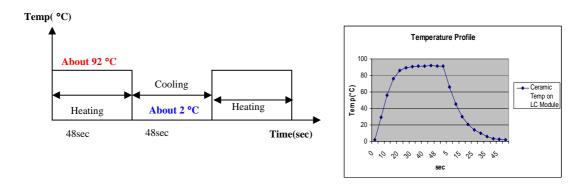

| Figure 5.4.3 Power cycling by the timer and the temperature profile in one cycle    | 105     |

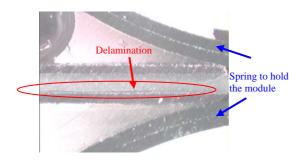

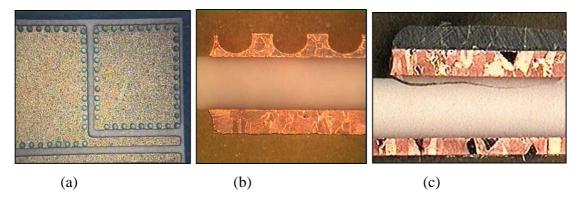

| Figure 5.4.4 Optical image at cross section of integrated passive module            | 107     |

| Figure 6.1.1 Bi-material structure with adhesive layer                              | 109     |

| Figure 6.1.2 Thickness ratio effect on peel stress and in-plane stresses            | 112     |

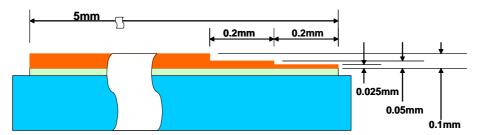

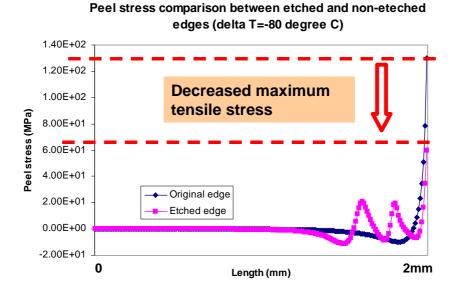

| Figure 6.1.3 Etched film has lower maximum peel stress. (a) Schematic of Cu         | -Al-Si  |

| structure with etched copper edge; (b) Peel stress FEM simulation                   | 113     |

| Figure 6.1.4 Curamik experiences on etching copper film thickness for better reli   | ability |

|                                                                                     | 114     |

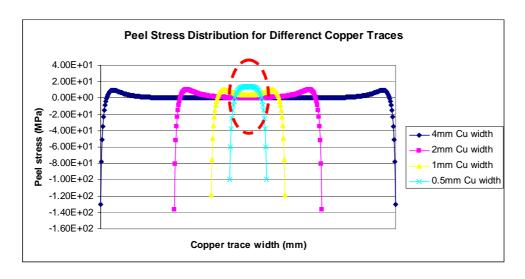

| Figure 6.1.5 FEM simulated peel stress for cases with different contact sizes       | 115     |

| Figure 6.1.6 Thicker copper films should have bigger contacts                       | 115     |

| Figure 6.1.7 Length ratio effect on peel stress                                     | 116     |

| Figure 6.1.8 Contact length effect on substrate in-plane stress                     | 117     |

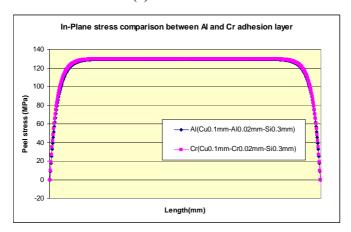

| Figure 6.1.9 Adhesion material effect on peel stress and in-plane stress | 118 |

|--------------------------------------------------------------------------|-----|

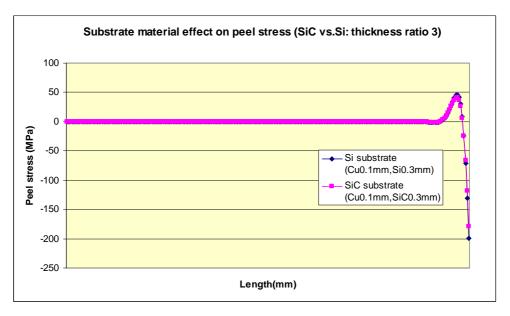

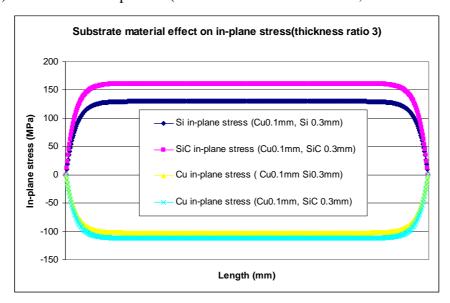

| Figure 6.1.10 SiC substrate effect on peel stress and in-plane stress    | 120 |

| Figure 6.1.11 Substrate effect on peel stress and in-plane stresses.     | 121 |

# **List of Tables**

| Table 1.1 Comparison of the power module parameters of two generations                | 2    |

|---------------------------------------------------------------------------------------|------|

| Table 1.2. The 1kW integrated transformer parameters                                  | . 16 |

| Table 2.1 Embedded power module assembling materials, parts and vendors               | . 24 |

| Table 2.2 Temperature range data meanings                                             | . 25 |

| Table 2.3 Material properties of ceramic substrates used in integrated power passives | . 26 |

| Table 2.4 Composition of Cu electroplating solutions and yield strength of Cu films   | . 38 |

| Table 2.5 Research summary for electroplated copper film yield stress                 | . 40 |

| Table 3.1 Material properties of glass and copper.                                    | . 52 |

| Table 3.2 Calculation results of curvature and residual stress                        | . 52 |

| Table 4.1 Material properties of silicon and copper                                   | . 59 |

| Table 4.2 Equivalences between thermal and electrical variables                       | . 60 |

| Table 4.3 Substrate and metallization material properties                             | . 68 |

| Table 4.4 Calculated interface in-plane stressesS                                     | . 68 |

| Table 4.5 Simulated in-plane stresses                                                 | . 70 |

| Table 4.6 Material properties for peel stress modeling                                | . 74 |

| Table 4.7 Comparison of peel stress simulation and calculation results                | . 76 |

| Table 4.8 Comparison of shear stress simulation and calculation results               | . 77 |

| Table 4.9 Material Properties                                                         | . 79 |

| Table 4.10 Y5V Material properties                                                    | . 81 |

| Table 5.1 Voltage drop through source and drain (Unit: Volt)                          | . 95 |

| Table 5.2 Samples failed temperatures                                                 | . 98 |

| Table 5.3 Electrical characteristics of the passive modules without the ferrit | e core before |

|--------------------------------------------------------------------------------|---------------|

| power cycling test                                                             | 103           |

| Table 5.4 Electrical characteristics of the integrated LC series resonant pa   | ssive module  |

| (2-turn)                                                                       | 105           |

| Table 5.5 Electrical characteristics of the integrated LC series resonant pa   | ssive module  |

| (3-turn)                                                                       | 106           |

| Table 6.1 Material properties and geometry parameters of layers                | 111           |

| Table 6.2 Material properties and geometry parameters of layers                | 116           |

| Table 6.3. Material properties and geometry parameters of layers               | 118           |

| Table 6.4 Material properties and geometry parameters of layers                | 119           |

# **Chapter 1 Introduction**

Global economic growth drives increases in energy consumption. The world's net electricity consumption was estimated as 13,290 billion kilowatt-hours in 2001. It was predicted that in the year 2025, the world's consumption would reach 23,072 billion kilowatt-hours [1]. In practice, most of power is not consumed in the same form as it was originally produced. It has to be reprocessed to meet certain requirements depending on the applications. Power electronics is the technology associated with the efficient conversion, control, and conditioning of electric power from its input form to the desired output form. This conversion is performed by semiconductor switching devices. According to an EPRI survey [2], more than 40 percent of the electric power being processed is passed through some power electronics equipments. By the year 2010, close to 80 percent of electrical power is expected to be processed by power electronics equipments and systems. By simply employing power electronics technologies, total energy consumption can be reduced by more than 35 percent.

Tremendous efforts have been made over the last twenty years to develop more powerful and cost-effective power electronics technologies. Power densities of power electronic products have been pushed to a higher level in order to meet the customer's requirements for smaller and lighter solutions. This has caused a trend towards high density integration in power electronic applications.

# 1.1 High density integration trends in power electronics applications

Two major enablers for increased power density are increasing the frequency and implementing integration technology. New semiconductor device technologies result in a switching time reduction which tests the limits of the structural inductances associated with packaging, as well as the thermal handling capability [3]. It has been argued for some time that it is packaging, control, thermal management, and system integration issues that are the dominant technology barriers currently limiting the rapid growth of

power conversion applications [4-7]. As of this time, most power electronics equipments are custom-designed and require a labor-intensive manufacturing process. The design goals are to achieve minimum thermal resistances, minimum on-state resistances, minimum parasitic inductances and capacitances with an overall standard foot-print, and maximum functionality integration. Table 1.1 lists important parameters of the very first power module, the SEMIPACK, introduced in 1975, to one of the latest power modules, SEMITOP, in 1998. Both modules have the same power rating [8].

Table 1.1 Comparison of the power module parameters of two generations

|                         | SEMIPACK 1 | SEMITOP |

|-------------------------|------------|---------|

|                         | (1975)     | (1998)  |

| Module weight (g)       | 160        | 19      |

| Weight efficiency (%)   | 0.15       | 1.3     |

| Package footprint (cm²) | 18.6       | 11.3    |

| Area efficiency (%)     | 16.6       | 27.4    |

| R <sub>th</sub> (K/W)   | 0.3        | 0.225   |

| # of assembly parts     | 22         | 5       |

| # of solder layers      | 5          | 1       |

In order to achieve higher thermal conductivity and smaller electrical resistance, new materials and novel structures are employed in high-density power modules. For example, instead of discrete switching devices, power semiconductors in a bare die form are directly mounted on a common substrate. Traditional Alumina DBC substrates can be replaced with AlN substrates for about 9 time's higher thermal conductivity (180 W/m-K). Buffer materials, such as Mo or Tri-metal (Cu-Fe/Ni-Cu), are used for matching CET between layers [8].

Beyond individual component integration, system-level integration involved with passive components, switching devices, associated drivers, protections, and sensors can optimize the structure parameters and maximize the improvement of electrical performances. One example is the realization of inductor-capacitor integration in a single

module. As mentioned previously, the improvement of the power semiconductor devices results in an increase of the circuit working frequency to megahertz or higher. As the frequency increases, the structural effect of passive components becomes more and more significant. The parasitic inductance of a capacitor in a low frequency can be ignored. However, in a high frequency range, the capacitor may behave as an inductor due to this Although there have been many efforts to decreasing parasitic parasitic effect. components, the limitation of discrete passive components cannot be overcome. The integration of discrete capacitive and inductive components into one electromagnetic component has become a research topic in recent years. The study of generalized inductor-capacitor (LC) components and the integrated inductor-capacitor-transformer (LCT) modules used in converter systems are presented in [9-11]. As an alternative to a discrete inductor and capacitor LC resonant circuit, the planar LC resonant module demonstrates promising merits for power electronic applications, such as less parasitics, compatible mass manufacturing process, and potentially smaller size. The details will be discussed later.

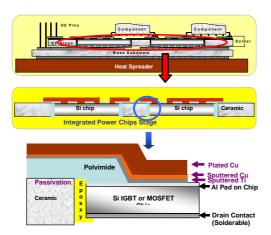

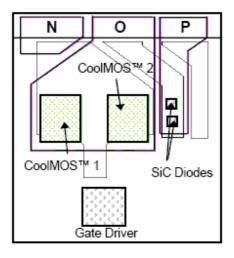

An Embedded Power module is another example of system level integration involved with switching devices, associated drivers, and protection circuits. The Embedded Power module is built by mounting silicon chips in the openings of a ceramic substrate followed by printing a polymer dielectric isolation layer and vapor-depositing multilayer metallic thin films for the construction of a three-dimensional package. There are three major parts in the structure: embedded power chip stage, electronics circuits, and base substrate. The electronic circuits consist of gate drive, control, and protection components. The base substrate provides electrical interconnection and the major thermal path for power chips. It will be introduced in the next chapter.

Although most power electronics modules are essentially custom-designed nowadays, system-level integration and novel functionality packaging technologies provide the possibility of manufacturing the standardized highly integrated Power Electronics Building Blocks (PEBBs) [12]. In low power applications, the very-large-scale-integration (VLSI) technology has shown tremendous advantages on standardization, volume reduction, manufacturability, and cost reduction. In high power applications, the monolithic integration in power IC forms is not suitable. The PEBB

approach integrates switching devices, circuits, controls, sensors, and actuators into standardized manufactured subassemblies and modules. By employing different PEBBs as power electronics modules with different functions to form a particular system, it is expected that the PEBB approach will have the same advantages for high power systems. However, developing PEBB is more complicated than low power VLSI circuits. Issues include high current carrying capability, monolithic integration of associated control, protection and sensor circuits, interconnection technology, thermal management, and passives integration. All these are multi-disciplinary issues involving electrical, material, and mechanical knowledge.

The renovation of interconnection technology in high density power technology is associated with the material, structure change, and higher system level integration trends. Wire bond technology is still widely used as the electrical contact from semiconductor die chips to terminals. There are alternative interconnection technologies such as BGA (Ball Grid Array), pressure contact, and planar interconnection, etc., depending on the applications. The details about interconnection technologies will be covered in the next section.

# 1.2 Current interconnection technologies

In integrated power modules, interconnections not only need to provide good electrical contact, but also need to provide a good thermal path and a good mechanical performance. The requirements for interconnecting materials include high electrical conductivity, high resistance to electro-migration, high thermal conductivity, low thermal coefficient of expansion, high strength and ductility, less fatigue problem, and ease of processing. The most widely used metal interconnections for power devices include wire bonds, solder balls, and planar metallization. The features of each technology are introduced as follows.

# 1.2.1 Wire bonding

Wire bonding is a chip-to-package interconnection technique where a fine metal wire is attached between the I/O pads on a chip and its associated package pin. This technology originated from AT&T's bean lead bonding in the 1950s. In this technology,

a fine wire, typically a gold wire with 25µm thickness, is bonded using ultrasonic bonding between the IC bond pad and the matching package or the substrate bond pad. Wire bonding accounted for over 90% of all the chip-to package interconnections formed in 1999 [13]. Fig. 1.2.1 shows a picture of wire bonded power modules [8].

Figure 1.2.1 Power modules using wire bonding interconnection

The advantages of wire bonding include the highly flexible chip-to-package interconnection process, the high yield interconnection processing (40-1000ppm), the easily programmed boning cycles, the very large industry infrastructure supporting the technology, and the rapid advances in equipment, tools, and material technology. While it is the most common method in use, it is perhaps the most limited for the future development of high density, high-performance multi-chip modules [14]. The disadvantages of the wire bonding interconnection include the slower interconnection rates due to point-to-point processing of each wire bond, long chip-to package interconnection lengths, degraded electrical performance, larger footprint required for chip to package interconnection, and potential for wire sweep during encapsulation over molding. A common failure in wire bonding plastic packages tends to occur due to delamination of the encapsulant molding compound or die attach. It is followed by a highly localized stress concentration in the wire bonds, causing fatigue failures in the wires. A number of other failures are chip fracture, chip passivation cracking, chip metallization corrosion, wire sweep, bond fracture and lift-off, interfacial delamination, and package cracking.

# 1.2.2 Ball grid array

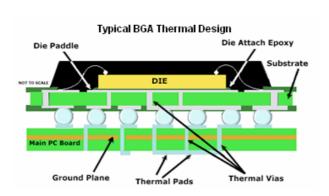

Current wire-bonding technology limits today's smaller package sizes to pin counts of 256 or less. With the ever-increasing demand for high density and high I/O count packaging, area array packaging is rapidly becoming very popular in the industry. The most common area array component is the ball grid array (BGA), which is shown in Fig. 1.2.2. The bottom side interconnection area can be extended over the size of the silicon chip perimeter. The increased interconnection area enables an increase in the lead pitch, which results in a more robust screen-printing process and causes less risk of short circuit between leads. The solder balls used in the interconnection between the component and the board provide a shorter electrical path, which therefore, has less parasitic inductance and causes less degradation of the signal.

Figure 1.2.2 Schematic of a BGA module

The advantages of BGA over traditional packaging include higher interconnect densities, better electrical performance due to a shorter distance between chip and solder balls, better thermal performance by using thermal vias, reduced placement problems, and reduced handling issues [15]. Hopefully, the many advantages of this interconnection technology will also benefit power electronics. Currently, most of the commercial power devices packaged by flip chip solder bumping are in the low to medium power ranges. Requirements for the adoption of flip chip area array solder bumping in power electronics packaging include high current handling capability, better thermal management, process

compatibility, and good insulation and understanding of the reliability of the solder bumping interconnection.

One big drawback with a BGA component is the difficulty to inspect the formed solder joints after assembly. X-ray method can inspect BGA components. However, it is very difficult to judge the appearance of the solder joint. The inspection is very time-consuming, as compared to using a microscope for standard surface mounted components. Furthermore, the BGA technology is not compatible with the integrated power technology used for further integration of power passives and power active devices.

#### 1.2.3 Planar metallization interconnection

The fundamental approach to electronics power conversion has steadily moved toward "high-frequency synthesis", resulting in huge improvements in converter performance, size, weight, and cost. However, as with many high-frequency power conversion technologies, fundamental limits are being reached that will not be overcome without a radical change in the power conversion strategy [16]. Integration technology is essential to further decrease module size and increase power density. There are two main categories for integration technology: structural integration and function integration.

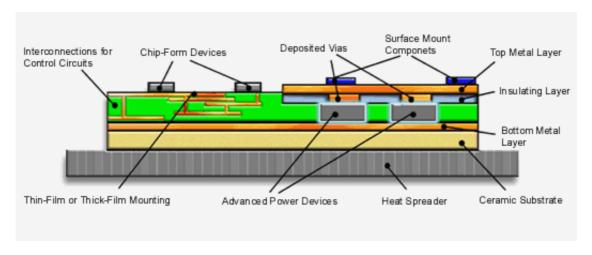

Structural integration is used to make discrete devices and components in an integrated process or in an integrated structure. Examples of such technologies are 3-D integration modules, low temperature co-fired ceramics (LTCC), and embedded passives for PCBs. In the power IC industry, the vertical interconnections are standardized and commercially available for 3-D integration. It offers short interconnection paths and makes mass production a possibility. As shown in Fig.1.2.3, the same concept can be used for power module packaging technology. Instead of using wire bonds, the switching devices can be interconnected by a planar metallization layer. The Embedded Power, to be introduced later, is a good structural integration example of utilizing the planar metallization to replace the wire bond and embedding passive components with compatible processes.

Figure 1.2.3 Cross section schematic of a 3-D integration module

The use of embedded passive components for Printed Circuit Boards (PCB) is a very promising integration technology. To integrate capacitors into a PCB, capacitive materials can replace the insulation layers. The conductors on top and bottom of this layer form the electrodes of the integrated capacitors. The capacitive layers can be used to replace resonant capacitors, filters, decoupling and snubber capacitors, and timing capacitors for controllers. Most of the layers exhibit a high breakdown voltage (1000V or higher). At least two materials (Isola C-Lam, Roger RO3210) and their manufacturing process for PCB are already commercially available. The cost can be moderate. The integration of capacitors into PCB will become state of the art soon; however, very high capacitive materials to replace electrolytic capacitors are far from being realized [17].

Functional integration manufactures an integrated device, which can present combined electrical functions. Examples are integrated filters and inductor-capacitor-transformer modules used in converter system. The integrated modules present the desired function combinations of capacitors, inductors, and even transformers in certain frequency ranges. The integration of passive components is a technology for highly integrated electronic circuits, because they typically need more than 2/3 of the space of a conventional circuit. This is especially necessary for applications that need an ultra-thin building height such as thin, flat displays [17].

The combination of structural integration and functional integration has the following advantages: a much more compact and thinner circuit, a compatible

manufacturing process for different kind of modules and circuits, a large potential for cost reduction, a better reproducibility, a better reliability because the interconnections are no longer mechanical fixings, a better EMI performances, better recyclables because less materials are used, and a standardized layered structure.

The main feature of the structural and functional integration is the planar structure, which therefore makes the interconnection layers planar. Unlike wire bonding or BGA interconnections, which have to be processed individually for each terminal, planar metallization enables a massive parallel processing for all modules. The planar metallization process is also compatible with either active switching device connections, which have silicon as the substrate, or passive device connections, which have ceramic as the substrate. To evaluate the planar metallization interconnection, we need to consider electrical performance, mechanical performance, and thermal performance. Compared with wire bond, planar interconnections have shortened electrical paths and smaller parasitic inductance, which is suitable for high frequency applications. As shown by the comparison of the packages depicted in Fig. 1.2.1, Fig. 1.2.2 and Fig.1.2.3, the heat generated by switching devices can be removed mainly from the bottom side of the package for the wire bonding technology or the BGA package, while the planar top surfaces enable the double-side cooling for better thermal management. Due to the large area of contact between different material layers in planar metallization, the mismatch of coefficient thermal expansion (CTE) will be an issue in 3-D packaging. The mechanical behavior and performances of planar metallization in power electronics modules needs to be investigated.

# 1.3 Applications of the planar interconnect technology

#### 1.3.1 Embedded Power modules

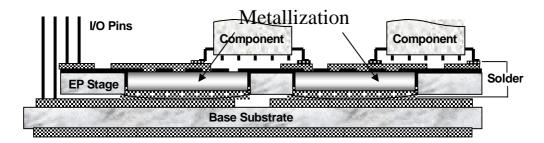

In today's power electronics modules, power semiconductor devices such as MOSFETs and IGBTs are interconnected via wire bonds. These bonds are susceptible to ringing due to the long interconnection path, which will cause higher stresses for switching devices and larger EMI noise. Over the last few years, a planar interconnection technique has been developed to enable the construction of 3-D integrated power

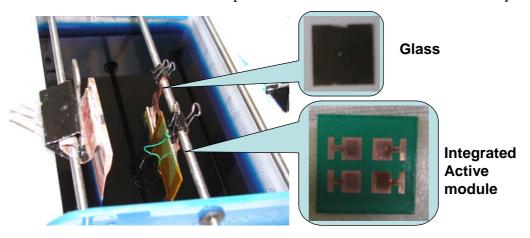

electronics modules. This technique is called Embedded Power. The schematic cross-section for this technique is shown in Fig.1.3.1. This integrated power electronics modules integrates power switching devices, control, drive, and protection circuits together, as shown in Fig.1.3.2.

Figure 1.3.1Structural schematic of the Embedded Power module

Figure 1.3.2 Integrated power electronics module realized by Embedded Power technique.

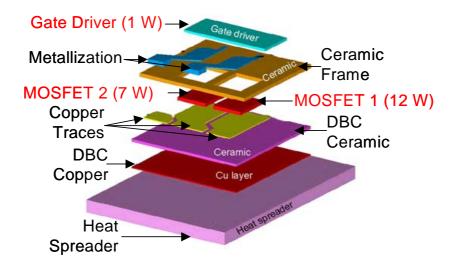

The Embedded Power module is built by mounting power devices in the openings of a ceramic substrate followed by printing a polymer dielectric isolation layer and vapor-depositing multilayer metallic thin films for the construction of a three-dimensional package. The structural schema and the exploded view of the Embedded Power module are shown in Fig.1.3.1 and Fig.1.3.3, respectively. The core element in this structure is the embedded power stage that consists of ceramic carriers, power chips, isolation dielectrics, and metallization circuits.

Figure 1.3.3 Exploded view of the Embedded Power module

# 1.3.2 Integrated power passive modules

Power passive integration includes structural integration and functional integration. Examples of each kind are listed below. Embedded decoupling capacitor is a typical case of structural integration. The integrated LC module and integrated resonator-transformer are examples for functional integration.

#### A. Embedded decoupling capacitor

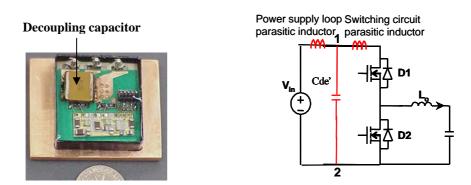

The module shown in Fig. 1.3.4 is a 1kW half-bridge switching module with input voltage as 400V. This front-end DC/DC converter is designed to operate at 200 kHz switching frequency. The switching devices are two MOSFETs with 500V voltage rating and 24A current rating.

During a switching activity, voltage spikes will appear at the terminals of MOSFET because of the parasitic inductor of a power supply loop. The voltage spikes on the MOSFET are proportional to the current slew rate of the circuit and the parasitic inductance of the power loop. The current slew rate can be decreased by reducing the switching frequency, but it will also reduce the circuit performance. Therefore, the reduction of the effective parasitic inductance is a more effective way to reduce the voltage stress on the switching devices. If a large enough capacitor is connected between point 1 and 2 as shown in the Fig. 1.3.4 (b), the energy stored in the parasitic inductor can pass through the capacitor branch instead of passing through the switching devices which

can cause voltage spikes on devices. Simulation results show that the switching device voltage spikes without and with decoupling capacitor is 514V and 414V, respectively. Since the voltage rating of the MOSFET is 500V, this decoupling capacitor is necessary for the circuit operating and decreases the device voltage stress tremendously.

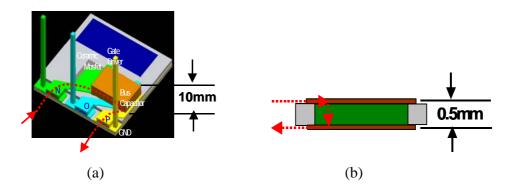

Figure 1.3.4 1kW integrated DC/DC converter; (a)Embedded Power module;(b) circuit diagram

As shown in Fig. 1.3.5, the Embedded Power modules use planar interconnection technology, which shortens the current loop. It can decrease the interconnection parasitic inductors from 5-15nH in discrete circuit to 1.0-3.4nH in the Embedded module. Hence, instead of soldering decoupling capacitors on top of the module, it is embedded into the module using compatible Embedded Power manufacturing steps. The current loop can decrease from 10mm to 0.5mm as shown in Fig.1.3.5.

Figure 1.3.5 Embedded decoupling capacitor to decrease the current loop (a) Decoupling cap soldering on top of module (b) Embedded cap

The embedded capacitor is a piece of thin high permittivity material mounted into the alumina substrate using the compatible manufacturing steps used in EP module shown in Fig. 1.3.6. Capacitance is proportional to the relative permittivity of material, area, and inverse of the thickness, as shown in Fig. 1.3.7.

Figure 1.3.6 Embed MOSFET and capacitor into same alumina substrate

Figure 1.3.7 Cross-section view of embedded capacitor schematic structure

# B. Integrated LC module

In most power electronics converters, the total size and the profile of a system are mostly determined by the physical size and the profile of the passive components. The integration technology for power passives integrates inductor and capacitor by placing a LC module inside of a planar ferrite core as shown in Fig.1.3.8.

Figure 1.3.8 Typical structure of a planar LC integrated passive resonant module.

The LC module consists of a dielectric material layer with deposited copper windings on both sides. This structure has distributed inductance and capacitance and is an electromagnetically integrated LC-resonant structure for which equivalent circuit characteristics depend on the external connections as shown in Fig. 1.3.9 [18].

Figure 1.3.9 Classification of typical resonators. (a) Spiral winding structure; (b) Physical structure; (c) Series LC module used for integrated resonators in power electronics; (d) Parallel LC module used for integrated resonators in power electronics.

#### C. Integrated resonator-transformer

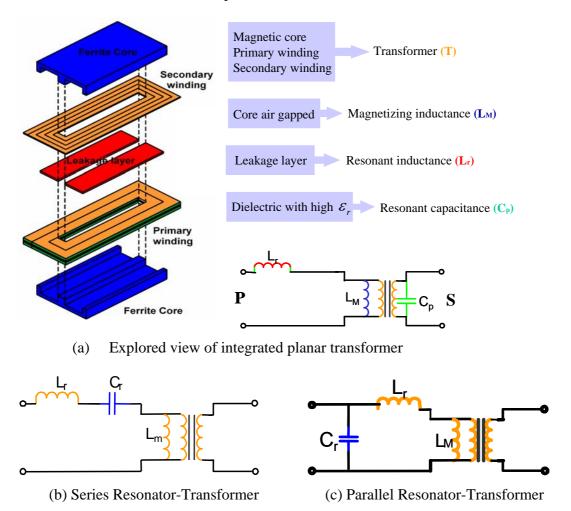

Based on the principle of the integrated LC module, more complex integrated structures can be realized by adding more winding layers. This has been demonstrated by an integrated resonant transformer structure, which is shown in Fig. 1.3.10 (a). The transformer's primary and secondary sides are formed by planar spiral winding layers which are separated by a leakage layer. This leakage layer is a low permittivity magnetic layer to realize the resonant inductor. The magnetizing inductor is realized by putting the planar spiral windings into the planar ferrite core. Those spiral windings are the main parts of the modules. A spiral winding consists of a dielectric substrate with conductor

windings directly deposited on both sides. The resonant converters include series and parallel resonant converters. Both converters can be realized by a special interconnection between the layers. The equivalent circuits are shown in Fig. 1.3.10 (b) and (c).  $L_r$  and  $C_r$  represent the resonant inductor and capacitor.  $L_M$  is the magnetizing inductor. Fig. 1.3.11 gives a practical example of a 1kW integrated parallel resonant transformer passives module with resonant capacitance about 12nF, resonant inductor of 1 $\mu$ H, and transformer turns ration of 2:12. The module parameters are listed in Table 1.2.

Figure 1.3.10 Integrated parallel resonant transformer. (a) Explored view of integrated planar transformer; (b) Series Resonator-Transformer; (c) Parallel Resonator-Transformer.

Figure 1.3.11 1kW integrated parallel resonant converter transformer passives

Table 1.2. The 1kW integrated transformer parameters

| Input volatge Vin                             | 60V                 |

|-----------------------------------------------|---------------------|

| Output voltage Vout                           | 537V                |

| Primary current                               | 54.7A               |

| Current density                               | 20A/mm <sup>2</sup> |

| Resonant frequency                            | 250kHz              |

| Transformer turns ratio                       | 2:12                |

| Number of turns per layer of primary          | 1                   |

| Number of turns per layer of secondary        | 3                   |

| Winding conductor thickness                   | 0.15mm              |

| Relative permittivity of insulatoin material  | 3.4                 |

| Dielectric material thickness                 | 0.35mm              |

| Relative permittivity of the dielectric layer | 2200                |

| Leakage layer thickness                       | 1.65mm              |

| Relative permittivity of the leakage layer    | 9                   |

| Mean length per turn                          | 216mm               |

| Width of the core window                      | 21mm                |

| Distance between winding and core             | 3mm                 |

# 1.3.3 Integrated EMI filters

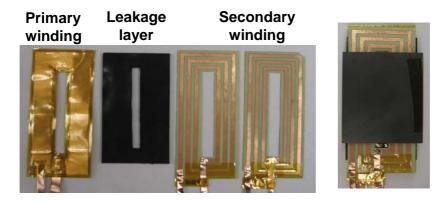

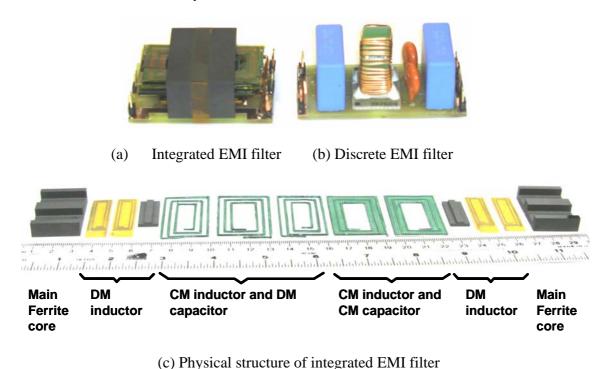

Power electronics converters are potentially large EMI noise sources to nearby electrical and electronic equipments because of the switching function. EMI filters are necessary to insure the electromagnetic compatibility. Conventional discrete EMI filters consist of a fairly large number of components, with different shapes, sizes, and form factors, and they are manufactured by different processing and packaging technologies, which may include labor-intensive processing steps. As a result, discrete EMI filters are usually bulky, high-profile, and have poor space and material utilization factors, as

Fig.1.3.12 shows [19]. In addition, because of the parasitic parameters of the discrete components and the interconnection board layout, the high frequency attenuation of discrete EMI filters is reduced. Hence the effective filter frequency range is limited. Aiming at these issues, our goal is to accomplish integrated EMI filters with structural, functional, and processing integration to achieved smaller size, lower profile, better performance, and reduced fabrication time and cost.

The materials used in EMI filters include conductor materials (Cu), magnetic materials (ferrite), and dielectric materials for capacitors and insulation. The diagram and the physical structure of EMI filters are shown in Fig. 1.3.12 (c). The integrated EMI filters are composed of a set of integrated LC modules. Studying the failure modes of the basic LC modules is necessary to understand the failure modes of the EMI filter modules.

Figure 1.3.12 The comparison of integrated EMI filter and discrete EMI filter. (a) Integrated EMI filter; (b) Discrete EMI filter; (c) Physical structure of integrated EMI filter.

# 1.4 Aim of this study

Over the past several decades, extensive research into the drivers of failure mechanisms in integrated power modules has led to an understanding of failure mechanisms, chiefly centered on wire bond and solder layer failures. The lifetime estimation in planar metallization power package is different from ball grid array or chipscale packages because of the different physical interconnection dimensions and different failure modes. For example, for the case of solder-joint fatigue in packages with tens of hundreds of I/O connections, the failure of a single I/O may constitute the failure of the package. Furthermore, since the physical dimensions of each connection are tens of micrometers, the estimation of failure initiation often corresponds closely to the end of life, owing to the immediate impact of failure initiation on joint integrity. In contrast, since power connections are often orders of magnitude larger (tens of millimeters), there is a greater tolerance to such defects. Instead, the major effects are manifested as a lowered thermal resistance, which directly affects the electrical performance of the device systems [20].

As to the novel planar integrated technology used in power electronics, new material combination and new structures are used. The failure modes for the integrated power modules based on the thick copper deposition on brittle materials and high current working conditions of the power modules are not fully understood.

# 1.4.1 Summary of related research

As introduced previously, the planar interconnection is widely used in the IC industry. By adopting this technology in power applications, unique features are introduced: (1) the thickness of metal deposition is in the range of 100µm to conduct high current in power circuits, which is much thicker than the IC application; (2) the copper deposition on brittle materials is critical for circuit operation. It is also the most probable failure spots. The design, manufacture, optimization, and testing of the IPEMs has been developed and well documented over the last few years. Up to this date, the failure mechanism research of conventional integrated power modules has led to the understanding of failures centered on wire bond or solder layer. However, the IPEM

reliability and failure modes investigation based on the metallization on brittle substrates for high current operations is still lacking.

Some research on the DBC copper-ceramic interface failure of power electronics modules has been done by Johannes Juul Mikkelsen and his group [21]. The DBC substrates used in the experiments are production samples for a 2kW integrated power converter. The substrates are standard-grade 96% Al<sub>2</sub>O<sub>3</sub> ceramic, 0.635mm thick. The copper layers are 0.3mm thick. Half of the samples are soldered to a 4mm copper base. The other half of the substrates are left free. The results show that soldering conditions will significantly change the failure development. The failure mode is the same. In both cases fracture goes down from the edge of the DBC copper layer. However, in the mounted condition, the failure only occurs near the edge of the DBC and the cracked area is significantly smaller than that in the free condition.

The research group led by Prof. Mike Shaw studied the strength distribution of the ceramic materials properties and measured the fracture toughness of the metal-ceramic interfaces [22]. Five types of brittle ceramic materials used in integrated passives and integrated EMI filters are experimentally characterized for their strength distributions and fracture toughness. The failure and reliability criteria for brittle materials are governed by both the applied stress and a length-scale parameter, such as the defect size or the layer thickness. These dual requirements represent a fundamental distinction compared to most ductile materials, where only a stress or strain-based parameter is required to reliably predict failure. The interfacial delamination or peeling often occurs at levels of stress or temperature well below those needed to induce fracture or yield of the materials on either side of the interface. This can result either from an adhesive joint with insufficient fracture toughness or the presence of a defect population with unacceptably large dimensions. The strength distributions of the brittle constituents were measured in biaxial loading. The controlled cracks produced by the Vicers technique have been applied to previous investigations to explore the fracture toughness of the interface in ceramic/metal multilayer. Delamination along the interface is visible, indicating a lower critical strain energy release rate than that of the ceramic. Although preliminary, this technique is invaluable in rapid assessment of the adhesion of such interfaces.

## 1.4.2 Research work covered in this study

In this study, the integrated power modules are manufactured and their lifetime is tested. It is expected that most of the mechanical failures are caused by the delamination of the metal layer from the substrate. Poor interface adhesion, intrinsic residual stress, and thermally induced mechanical stresses are possible contributing factors causing failure of these modules. These factors are studied respectively in embedded power modules and integrated passive modules.

In Chapter 2, the manufacturing processes of different kinds of integrated power modules are introduced first. Metallization on brittle materials is one of the major features of integrated power modules. The interface conditions for different structures are reviewed from the material science point of view and the research is the results of extensive thin film studies.

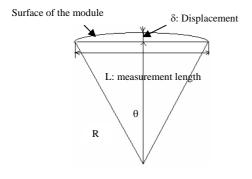

Residual stress and thermal mechanical stress are two major stresses in the system which can cause failures. Chapter 3 covers the residual stress background knowledge and introduces an experimental method to measure and calculate the residual stress introduced by the planar integration process. Since directly measuring the residual stress in a complicated structure is a very difficult task, a simplified copper-glass structure is chosen as the experiment samples. The deposition processes are the same as those in the integrated modules. The curvature of the glass slide is measured by a surface profile system and the stress is calculated based on this curvature.

Chapter 4 investigates the thermo-mechanical stresses in the integrated power modules. There are two approaches to analyze the thermal stresses in a layered structure. The layered structure can be modeled as beams. The thermal stress can be calculated using the force equilibrium equations. With simplified assumptions, the model can predict the thermal stresses in layered structures. This approach can provide easy-to-use expressions. The second approach is to use the finite element analysis to analyze the stresses. Although it cannot provide a simple expression, like the previous method does, finite element analysis is the more effective tool for complicated structures, where the simplified assumptions that are necessary to make the expressions manageable may lead to large errors. In chapter 4, both theoretical analysis and software simulation are used to study the thermal stress in a simplified bi-layer structure and the results are compared.

The matching results verify that finite element analysis is an effective tool to study the thermal stress in a complicated structure. A multi-layered module is then simulated and the stress distribution is presented.

In order to verify the stress analysis results, lifetime tests of the integrated modules are designed and carried out in chapter 5. The manufacturing process used to prepare the test samples is identical to that of the Embedded Power modules. According to literature, the thin films under tensile and compressive stresses have different failure modes. In order to separate the driving forces for different failure modes, two temperature profiles are used. Failed sample investigation indicates the major failure modes for different stress conditions. Further understanding of those failure mechanisms enables the engineering of the failure modes for safe electrical operations of IPEM modules and helps to enhance the reliability of system-level operations. It is the basis for improving the design and for optimizing the process parameters to achieve a high resistance to the failure. It is also helpful to establish the methodology for failure prediction based on the understanding of the recognized failure modes.

Chapter 6 covers the optimization design in simplified structure. Optimization of geometry and material parameters such as thickness ratio, length ratio, critical size, adhesion material and substrate materials are discussed based on the modeling results. This provides the guidelines for practical IPEM design.

Chapter 7 is the summary and discussion of future work.

# Chapter 2: Metal Films on Brittle Substrates in IPEMs

# 2.1 Fabrication processes of integrated modules

## 2.1.1 Integrated active modules (Embedded Power)

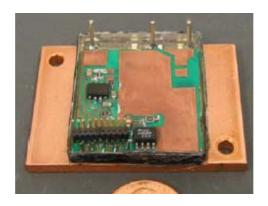

As shown in Fig. 2.1.1, a fully integrated power module includes three main layers: base substrate, Embedded Power stage, and necessary components soldered on top of the power stage. The base plate usually employs a direct-bonded-copper (DBC) ceramic substrate. It is composed of a 500-625 µm-thick Alumina ceramic and two 200-250 µm-thick copper on both sides. The vender is Curamik. The top copper layer of the DBC is etched into certain patterns and is soldered into MOSFET chip drain electrodes. The bottom copper layer of DBC is in direct contact with a heat spreader for thermal management. The components soldered on top of the power stage are capacitors, resistors, and driver chips. They are all surface mounted components. The solder paste used for the base plate and components soldering is the no clean low residue Sn63Pb37 from SolderPlus<sup>TM</sup>. The embedded power stage is the most important part. The fabrication processes are shown in Fig.2.1.2. The typical packaging materials, structure parameters, and vendor information are all listed in Table 2.1.

The power stage fabrication starts with an alumina ceramic working as a holding frame. The ceramic is 96% alumina as-fired ceramic with a thickness of 500-625µm and a size of 2 inches square (or 3 inches square depending on applications). The vender is Valley Design<sup>®</sup>. The openings that hold the MOSFET chips are cut on the ceramic frame by the laser cutting machine, which is shown in Fig. 2.1.2 (a).

The MOSFET chips are mounted in these openings with an adhesive epoxy surrounding the edges. The epoxy is Master Bond's EP3HT. After curing at 150°C for about 7 minutes, the epoxy is hardened and provides good mechanical support for silicon chips. A liquid photoimageable solder mask system ENTHONE®DSR-3241 A&B is then spin coated on the top. After exposing it under UV light for about 8-10 minutes, the sample is washed by the liquid developer concentrate D-4000 from DUPOND Electronic Chemicals. The dielectric layer has the opening holes where the Al pad pattern of the

MOSFET chips can contact the planar metal deposition for circuit interconnection. The metal deposition begins with sputtering a very thin layer of Titanium. The Titanium layer helps the adhesion between the silicon and the copper deposition. The sputtering time of Titanium is about 15 minutes to get a deposition layer of about 20 nm thickness. Then, a layer of copper is sputtered for 30 minutes to get a thickness of 500nm. To carry high current, the cooper metallization layer needs to be thickened by an electroplating process. In order to thicken the copper in only the patterned areas, a photo resist layer is applied on top of the sputtered layers. The photo resist is the Photoimageable Etch Resist PHOTRAK ETP 240/1694. After being exposed under UV light for 10 minutes, it is washed by the same developer used for dielectric developing (mentioned before). The sample can now be electroplated. The electroplating solution is the copper plating solution from CuTech. The plating temperature is about the room temperature. The current density is 200A/m<sup>2</sup> and the plating speed is about 25µm/hour. In order to get the copper thickness of 100µm, the total plating time is 4 hours. After electroplating, the photo resist layer is washed with acetone. The sputtered copper layer can be washed with the sodium persulfate-oxidizer Etchant-SP and the sputtered titanium layer can be washed with the micro etching solution Etchant TFT, the main contents of which are Hydrofluoric acid. Now the process of the power stage is finished and it is ready to be soldered into the DBC base plate. Finally, a silicone gel is used to encapsulate the whole module. The picture of an Embedded Power module is shown in Fig. 1.3.2.

Figure 2.1.1 Cross-section schematic of Embedded Power Module

Figure 2.1.2 Manufacturing process of test sample (a) laser cut substrate; (b) chip mounting; (c)solder mask screening; (d) electroplated copper with designed patterns; (e) final sample with encapsulation;

Table 2.1 Embedded power module assembling materials, parts and vendors

| Name            | Part number | Purpose                  | description           | Vendor                     |

|-----------------|-------------|--------------------------|-----------------------|----------------------------|

| DBC             |             | Base plate               | Alumina DBC           | Curamik <sup>®</sup>       |

| Solder paste    |             | Solder power stage to    | no clean low residue  | SolderPlus <sup>®</sup>    |

|                 |             | base plate               | Sn63Pb37              |                            |

| Ceramic carrier |             | Frame to hold chips      | 96% 2" by 2" as-fired | Valley Design <sup>®</sup> |

|                 |             |                          | Alumina               |                            |

| Epoxy           | EP3HT       | Fill gap between chips   | Curing at 150°C       | Master Bond                |

|                 |             | and frame                |                       |                            |

| Polyimide       | DSR-3241    | Insulation and           | liquid photoimageable | ENTHONE <sup>®</sup>       |

|                 | A&B         | mechanical support       | solder mask system    |                            |

| Photo resist    | ETP         | Define electroplating    | Photoimageable Etch   | PHOTRAK                    |

|                 | 240/1694    | pattern                  | Resist                |                            |

| Developer       | D-4000      | Wash the polyimide or    | Concentrate solutions | DUPOND                     |

|                 |             | photo resist away after  | (1:20)                | Electronic                 |

|                 |             | UV light                 |                       | Chemicals                  |

| Cu Plating      |             | Electroplating copper    | brightener added      | Cutech                     |

| solution        |             |                          |                       |                            |

| Cu etching      | ETCHANT     | Micro etch the sputtered | Sodium persulfate     | INJECTORALL                |

| solution        | -SP         | Copper                   |                       | ELECTRONIC                 |

|                 |             |                          |                       | S CORP.                    |

| Ti etching      |             | Etch the sputtered Ti    | Titanium etchant TFT  | TRANSENE                   |

| solution        |             |                          |                       | Company Inc.               |

#### 2.1.2 Integrated passive modules

One big difference between integrated passive modules and integrated active modules is that the substrates used in passive modules are ceramics instead of silicon. These ceramics are manufactured by an Italian company Via F. Ili Philips. There are 6 different kinds of ceramics available in the lab. They are K14000-Y5V (available with 3 thicknesses: 150um, 200um, 300um), K186-N1250, K85-NP0, K2400-X5S (available with 2 thicknesses: 190um, 350um), K4400-X5U, and K2200-X7R. The temperature ranges of different types are shown in Table 2.2. The material properties are shown in Table 2.3. The pictures and ingredients of ceramics samples are shown in Fig.2.1.3.

Figure 2.1.3 ceramic samples pictures

Table 2.2 Temperature range data meanings

| Low Temp | High Temp | % variation |

|----------|-----------|-------------|

| X -55C   | 5 +85C    | F +/- 7.5   |

| Y -30C   | 6 +105C   | P +/-10     |

| Z +10C   | 7 +125C   | R +/- 15    |

|          | 8 +150C   | S +/- 22    |

|          | 9 +200C   | T -33 +22   |

|          |           | U -56 +22   |

|          |           | V -82 +22   |

Table 2.3 Material properties of ceramic substrates used in integrated power passives

| Material   | Relative     | Thickness | Breakdown | Young's | Thermal      | CTE(mpp/K) |

|------------|--------------|-----------|-----------|---------|--------------|------------|