## Low-Temperature Sintering of Nanoscale Silver Paste for Semiconductor Device Interconnection

by

### **Guofeng Bai**

Dissertation submitted to the faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirement for the degree of Doctor of Philosophy

in Materials Science and Engineering

Dr. Guo-Quan Lu, Chair Dr. Dushan Boroyevich Dr. Sean G. Corcoran Dr. William T. Reynolds, Jr. Dr. J. Daan van Wyk

> October 2005 Blacksburg, Virginia

Keywords: Electronic packaging, Nanoscale silver paste, Low-temperature sintering, Semiconductor device interconnection, Silver joint, Lead-free solution, Reliability

Copyright 2005, Guofeng Bai

### Low-Temperature Sintering of Nanoscale Silver Paste for Semiconductor Interconnection

Guofeng Bai

Center for Power Electronics Systems & Center for Microelectronics, Optoelectronics, and Nanotechology & Department of Materials Science and Engineering Virginia Polytechnic Institute and State University

### ABSTRACT

This research has developed a lead-free semiconductor device interconnect technology by studying the processing-microstructure-property relationships of low-temperature sintering of nanoscale silver pastes.

The nanoscale silver pastes have been formulated by adding organic components (dispersant, binder and thinner) into nano-silver particles. The selected organic components have the nano-particle polymeric stabilization, paste processing quality adjustment, and non-densifying diffusion retarding functions and thus help the pastes sinter to  $\sim 80\%$  bulk density at temperatures no more than 300°C. It has been found that the low-temperature sintered silver has better electrical, thermal and overall thermomechanical properties compared with the existing semiconductor device interconnecting materials such as solder alloys and conductive epoxies. After solving the organic burnout problems associated with the covered sintering, a lead-free semiconductor device interconnect technology has been designed to be compatible with the existing surface-mounting techniques with potentially low-cost. It has been found that the low-temperature sintered silver joints have high electrical, thermal, and mechanical performance. The reliability of the silver joints has also been studied by the 50-250°C thermal cycling experiment. Finally, the bonging strength drop of the silver joints has been suggested to be ductile fracture in the silver joints as micro-voids nucleated at microscale grain boundaries during the temperature cycling.

The low-temperature silver sintering technology has enabled some benchmark packaging concepts and substantial advantages in future applications.

To my wife, Qing

### ACKNOWLEDGMENTS

I would like to express my sincere thanks to my advisor, Dr. Guo-Quan Lu. With his guidance and support, I was able to engage in a broad range of research activities. His methods of conducting research and ways of tackling problems spurred me to think out of the box in order to solve various technical issues. He has been a constant source of encouragement and extremely understanding at all times.

I am indebted to my other committee members, Dr. Dushan Boroyevich, Dr. Sean G. Corcoran, Dr. William T. Reynolds, Jr., and Dr. J. Daan van Wyk, for agreeing to serve on my committee and offering me thoughtful advice and guidance.

I am grateful to all my research group fellows, Jesus N. Calata, Sihua Wen, Xingsheng Liu, Zhiye Zhang, Guangyin Lei, Chendong Bai, Gustina Collins, Anders DiBiccari, Robert Fielder, Xingdan Li, Kelly Stinson-Bagby, and Robert Mitchell, for their useful discussion, great friendship and help.

I am also grateful to Dr. Zhenxian Liang in CPES; Dr. Carlos Suchicital, Dr. Louis Guido, Dr. Dwight Viehland, Dr. Shuxiang Dong, Dr. Alex Aning, and Dr. Brain Love in MSE department; Dr. Elaine Scott and Dr. Scott Huxtable in ME department; Dr. Tao Lin in Mathematics; Mr. Mac McCord and Mr. Bob Simonds in ESM department; Mr. Steve McCartney at the SEM lab; Mr. Frank Kromer at the surface analysis lab and Dr. Kathleen Meehan and Sanjay Raman in MicrON center for generous help, great collaboration or useful discussions.

Special thanks to our lab managers Dan Huff, Steve Chen, Bob Martin and Jamie Evans at CPES and David Berry in MSE department for their continuous supports throughout my research projects.

I would like to mention and thank my other CPES friends Yingfeng Pang, Manu Mital, Yuming Bai, Joseph Witcher, Bin Lu, Jian Yin, Rengang Chen, Lingyin Zhao, Huiyu Zhu, Zhou Chen, Johan Strydom, Jing Xu, Chucheng Xiao, Yan Liang, Ning Zhu, Dianbo Fu, and MSE friends Feiming Bai, Naigang Wang, Hu Cao, Li Yan, Zhenping Xing, Junyi Zhai, and Bryan Dickerson for their friendship and help. I also shared pleasant experience with Yang Xu, Ali Hajjiah, Charlie French, Chris Maxey, Bill Houck, and David Gray in MicrON labs and I appreciate for their friendship and help. I would like to thank Trish Rose, Elizabeth Tranter, Marianne Hawthorne, Teresa Shaw and Ann Craig at CPES and Amy Hill, Catherine Fisher, Tracey Keister, Susette Sowers, and Jan Doran in MSE their administrative and secretarial help over the years.

I also would like to thank my friends Jinggang Wang, Xiaofeng Bao, Zuo Sun and Honghui Tan. Many thanks to all the people I have come to know in Virginia Tech and Blacksburg, whose friendship and companionship I will always enjoy.

I owe my sincere appreciation to my family and relatives who have supported and encouraged me over the years. I thank my elder brother and sister for their love and supports. I especially want to thank my wife Qing Li for her constant love, indulgence, and inspiration during my studies. Her company has made my stay in Blacksburg an enjoyable and pleasant experience. Finally, I want to extend my profound appreciation to my beloved parents for their love, affection, and invaluable support during my life and studies.

During my several research projects, Burhan Ozmat in General Electric, Inc., Paul Duncan and Sean Christian in Airak, Inc., Yanjing Liu in Luna, Inc., and Christopher Luechinger in Orthodyne Electronics, Inc. have supported me either technically or financially or both.

I also extend my sincere thanks to Infineon Technologies (Kanata, Ontario) and CREE Power Inc. (Durham, NC) for providing me a considerable mount of free SiC diodes for using in this dissertation research, without their support this research could be impossible.

This dissertation work was mainly supported by the National Science Foundation under Award Number EEC-9731677.

# TABLE OF CONTENTS

| Abstr  | act     |                                                        |                                                          | ii  |

|--------|---------|--------------------------------------------------------|----------------------------------------------------------|-----|

| Ackn   | owled   | gements                                                | 5                                                        | iv  |

| Table  | of Co   | ontents                                                |                                                          | vi  |

| Nome   | enclati | ıre                                                    |                                                          | ix  |

| Acror  | nyms    |                                                        |                                                          | X   |

| List o | f Figu  | res                                                    |                                                          | xi  |

| List o | f Tabl  | es                                                     |                                                          | xix |

| 1      | Intro   | Introduction                                           |                                                          |     |

|        | 1.1     | Overv                                                  | iew of Power Electronics Packaging                       | 2   |

|        |         | 1.1.1                                                  | Current Chip-Level Interconnect Technologies             | 3   |

|        |         | 1.1.2                                                  | Summary of Current Chip-Level Interconnect Technologies  | 13  |

|        | 1.2     | Overv                                                  | iew of Sintering Theory                                  | 15  |

|        |         | 1.2.1                                                  | Sintering Mechanisms                                     | 16  |

|        |         | 1.2.2                                                  | Theoretical Analysis of Sintering                        | 17  |

|        |         | 1.2.3                                                  | Driving Force for Sintering                              | 20  |

|        |         | 1.2.4                                                  | Challenges Associated with Nanomaterial Sintering        | 22  |

|        |         | 1.2.5                                                  | Summary                                                  | 26  |

|        | 1.3     | Motiv                                                  | ation of Research                                        | 27  |

|        |         | 1.3.1                                                  | Issues Associated with Current Interconnect Technologies | 27  |

|        |         | 1.3.2                                                  | Advantages of Low-Temperature Nanoscale Silver Sintering | 32  |

|        | 1.4     | Objectives and Significance of Study                   |                                                          | 35  |

|        | 1.5     | Organization of Dissertation                           |                                                          | 37  |

|        | Refe    | erences.                                               |                                                          | 38  |

| 2      | Exp     | Experimental Procedure                                 |                                                          |     |

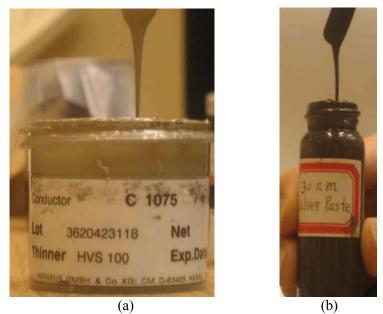

|        | 2.1     | Formu                                                  | ilation of Nanoscale Silver Pastes                       | 43  |

|        |         | 2.1.1                                                  | Preparation of Nanoscale Silver Particles                | 44  |

|        |         | 2.1.2                                                  | Selection of Organic Dispersant, Binder, and Thinner     | 45  |

|        |         | 2.1.3                                                  | Preparation of Nanoscale Silver Pastes                   | 48  |

|        | 2.2     | 2 Low-Temperature Sintering of Nanoscale Silver Pastes |                                                          | 50  |

|        | 2.3     | Chara                                                  | cterization of Sintered Silver                           | 51  |

|   |             | 2.3.1                                  | Determination of Electrical Resistivity                       | 51  |

|---|-------------|----------------------------------------|---------------------------------------------------------------|-----|

|   |             | 2.3.2                                  | Determination of Thermal Conductivity                         | 52  |

|   |             | 2.3.3                                  | Determination of Elastic Modulus, Yield and Tensile Strengths | 54  |

|   |             | 2.3.4                                  | Determination of Coefficient of Thermal Expansion             | 56  |

|   |             | 2.3.5                                  | Determination of Thermal Stress in Silver Sintered on Silicon | 57  |

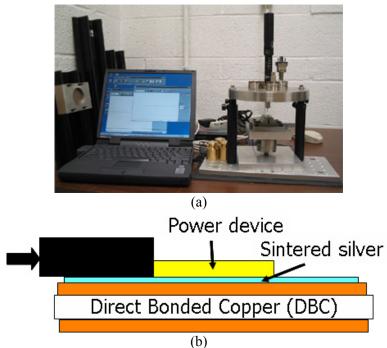

|   | 2.4         | Devic                                  | e Attachment to Form Silver Joints                            | 60  |

|   | 2.5         | Evalua                                 | ation of Sintered Silver Joints                               | 64  |

|   | 2.6         | Silver                                 | Joint Reliability Assessment                                  | 67  |

|   | Refe        | erences.                               |                                                               | 71  |

| 3 | Res         | ults and                               | Discussion                                                    | 73  |

|   | 3.1         | Proper                                 | rties of Silver Paste and Low-Temperature Sintered Silver     | 73  |

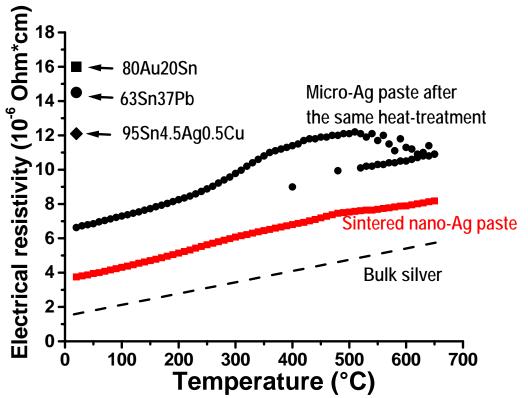

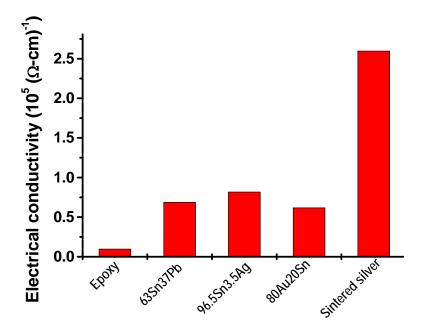

|   |             | 3.1.1                                  | Electrical Properties                                         | 82  |

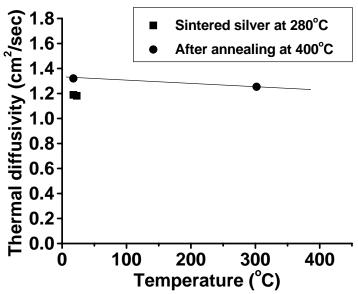

|   |             | 3.1.2                                  | Thermal Properties                                            | 85  |

|   |             | 3.1.3                                  | Mechanical Properties                                         | 88  |

|   |             | 3.1.4                                  | Summary                                                       | 93  |

|   | 3.2         | Perfor                                 | mance of Sintered Silver Joints                               | 94  |

|   |             | 3.2.1                                  | Electrical Performance                                        | 99  |

|   |             | 3.2.2                                  | Thermal Performance                                           | 101 |

|   |             | 3.2.3                                  | Mechanical Performance                                        | 102 |

|   |             | 3.2.4                                  | Summary                                                       | 107 |

|   | 3.3         | Reliab                                 | vility of Sintered Silver Joints                              | 108 |

|   |             | 3.3.1                                  | Temperature Cycling Experimental Results                      | 110 |

|   |             | 3.3.2                                  | Discussion on Reliability and Failure Mechanisms              | 116 |

|   |             | 3.3.3                                  | Summary                                                       | 119 |

|   | Refe        | erences.                               |                                                               | 119 |

| 4 | Арр         | Applications of Sintered Silver Joints |                                                               |     |

|   | 4.1         | Applic                                 | cations in Single-Chip Power Packages                         | 121 |

|   | 4.2         | Applic                                 | cations in Multi-Chip Power Modules                           | 129 |

|   | 4.3         | Other                                  | Applications                                                  | 129 |

|   | 4.4         | Summ                                   | ary                                                           | 132 |

|   | References1 |                                        |                                                               | 132 |

| 5      | Sum         | nary and Conclusions                                              | 133 |

|--------|-------------|-------------------------------------------------------------------|-----|

| Append | 5.1         | 1 Low-Temperature Silver Sintering Technology                     |     |

|        | 5.2         | Applications of Sintered Silver Joints                            |     |

|        | 5.3         | Recommendations on Future Work                                    | 135 |

|        |             | 5.3.1 Formulation of Nano-Pastes for Larger Joints                | 135 |

|        |             | 5.3.2 Formulation of Nano-Pastes Sinterable at Lower Temperatures | 135 |

|        |             | 5.3.3 Solutions for Silver Migration                              | 136 |

|        |             | 5.3.4 Implementation of Sintered Silver Joints                    | 137 |

|        | Refe        | rences                                                            | 137 |

| Appen  | dix A       | Processing of DBC or Cu Substrates for Silver Joints              | 139 |

|        | A.1         | Introduction to Direct Bond Copper Substrates                     | 139 |

|        | A.2         | Etching of Direct Bond Copper Substrates                          | 141 |

|        | A.3         | Metallization of DBC or Cu Substrates for Silver Joints           | 143 |

|        |             | A.3.1 Nickel Deposition                                           | 144 |

|        |             | A.3.2 Gold Deposition                                             | 145 |

|        |             | A.3.3 Silver Deposition                                           | 146 |

|        | Refe        | rences                                                            | 147 |

| Appen  | dix B       | Datasheets of Power Devices Used in This Research                 | 148 |

|        | <b>B</b> .1 | Infineon SIDC24D30SIC3 Silicon Carbide Schottky Diodes            | 148 |

|        | B.2         | CREE CPWR-0600S010 Silicon Carbide Schottky Diodes                | 152 |

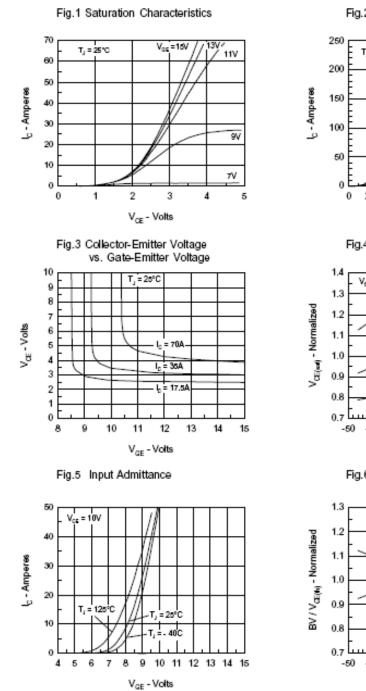

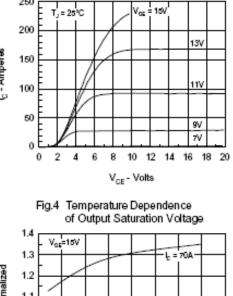

|        | B.3         | IXYS Corporation IXSH35N120A Single-Chip Packaged IGBT            | 155 |

| Appen  | dix C       | Material Properties Involved in Power Packaging                   | 159 |

| Appen  | dix D       | Related Research Work by the Author                               | 161 |

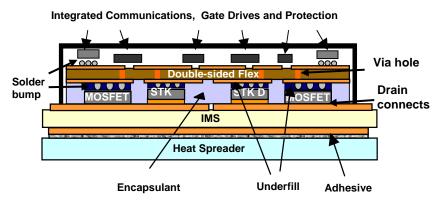

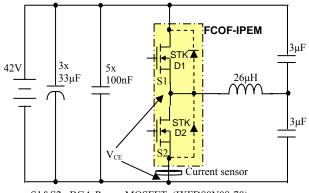

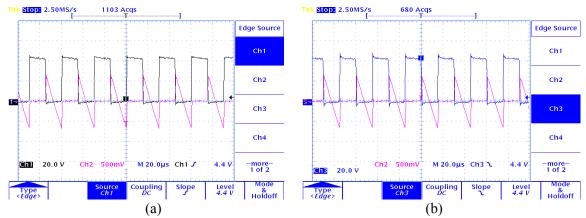

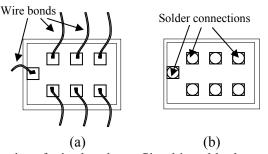

|        | D.1         | Flip-Chip on Flex Integrated Power Electronics Modules            | 161 |

|        | D.2         | Reliability Discussion on Solder-Bump and Direct-Solder Packages  | 174 |

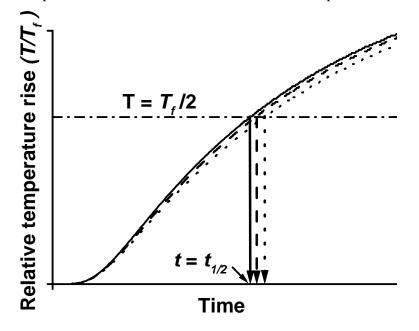

|        | D.3         | Characterization of Solder/Copper Interfacial Thermal Resistance  | 188 |

| Vita   |             |                                                                   | 196 |

## NOMENCLATURE

- *c* Heat capacity, J/Kg-K

- d Thickness, m

- *E* Elastic Modulus, GPa

- I Current, A

- *K* Thermal Conductivity, W/m-K

- *L*, *l* Length, m

- *m* Mass, Kg

- *R* Electrical Resistance,  $\Omega$

- $R_{th}$  Thermal Resistance, K/W

- 1/R Curvature, m<sup>-1</sup>

- S Area,  $m^2$

- *T* Temperature, °C

- t Time, s

- V Voltage, Volt

- $\alpha$  Thermal diffusivity, m<sup>2</sup>/s

- v Poisson's ratio

- $\rho$  Density, Kg/m<sup>3</sup>

- $\rho_e$  Electrical Resistivity,  $(\Omega \cdot m)^{-1}$

- $\sigma$  Stresses, MPa

## ACRONYMS

| AC     | Alternative Current                               |

|--------|---------------------------------------------------|

| BGA    | Ball Grid Array                                   |

| CPES   | Center for Power Electronic Systems               |

| CSP    | Chip-Scale Package                                |

| CTE    | Coefficient of Thermal Expansion                  |

| DBC    | Direct Bond Copper or Direct Copper Bonding       |

| DC     | Direct Current                                    |

| DSC    | Differential Scanning Calorimetry                 |

| EDS    | Energy Dispersive Spectrometry                    |

| FAST   | Field-Activated Sintering Technique               |

| FEA    | Finite Element Analysis                           |

| IC     | Integrated Circuit                                |

| IGBT   | Insulated Gate Bipolar Transistor                 |

| IPEM   | Integrated Power Electronic Module                |

| LED    | Light Emitting Diode                              |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| PCB    | Printed Circuit Board                             |

| POL    | Power OverLay                                     |

| PZT    | Lead Zirconate Titanate                           |

| SAM    | Scanning Acoustic Microscopy                      |

| SEM    | Scanning Electron Microscopy                      |

| TGA    | Thermogravimetric Analysis                        |

| UBM    | Under Bump Metallization                          |

| XPS    | X-ray Photoelectron Spectroscopy                  |

## **LIST OF FIGURES**

| Figure 1.1. Top views of the wirebond TO-247 (a) and SO-8 (b) MOSFET packages                     | 3    |

|---------------------------------------------------------------------------------------------------|------|

| Figure 1.2. Top view of a wirebond multichip power module                                         | 4    |

| Figure 1.3. Cross-sectional schematic of power overlay module                                     | 5    |

| Figure 1.4. A prototype of power module packaged using POL interconnect technology                | 6    |

| Figure 1.5. Cross-sectional schematic of embedded power module                                    | 6    |

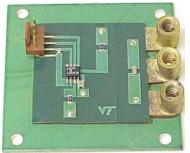

| Figure 1.6. An IPEM packaged by the embedded power technology                                     | 6    |

| Figure 1.7. Cross-sectional schematic of a PowerConnect chip-level power package                  | 8    |

| Figure 1.8. Cross-sectional view of a SO-8 Wireless chip-level power package                      | 8    |

| Figure 1.9. Chip-level power packages interconnected by SO-8 Bottomless technology                | 9    |

| Figure 1.10. Schematic of Fairchild Semiconductor's BGA MOSFET                                    | 9    |

| Figure 1.11. IR's FlipFET power MOSFET                                                            | 10   |

| Figure 1.12. Die-dimensional BGA power packages developed in CPES                                 | 10   |

| Figure 1.13. A Flip-chip on flex integrated power electronics module (a) and its schematic        |      |

| structure (b)                                                                                     | 10   |

| Figure 1.14. A chip-level CopperStrap power package                                               | 11   |

| Figure 1.15. IR's DirectFET power package (a) and its cross-sectional schematic (b)               | 11   |

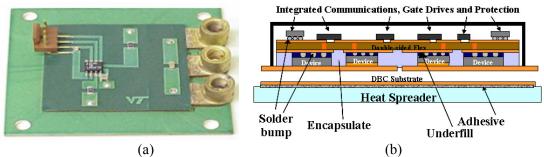

| Figure 1.16. Gate turnoff high power devices packaged using the press pack technology             | 12   |

| Figure 1.17. Schematic of a pressure-assisted silver paste sintering setup                        | 13   |

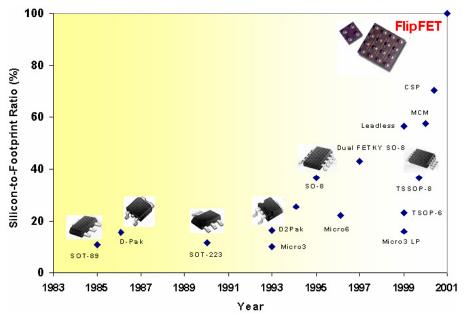

| Figure 1.18. Technology roadmap of IR's chip-level discrete power packages                        | 14   |

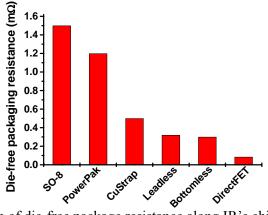

| Figure 1.19. Reduction of die-free package resistance along IR's chip-level discrete power        |      |

| package developing roadmap                                                                        | 14   |

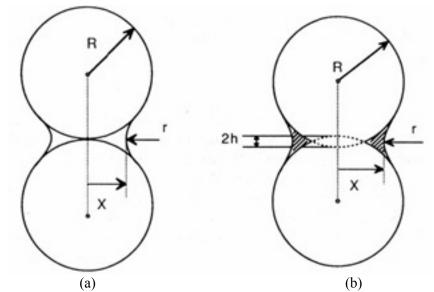

| Figure 1.20. Two-particle geometric model for the initial stage of sintering                      | 18   |

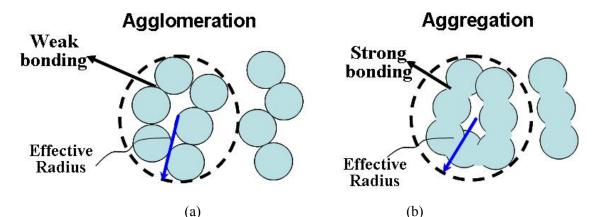

| Figure 1.21. Illustration of agglomeration and aggregation and their effective particle sizes     | 23   |

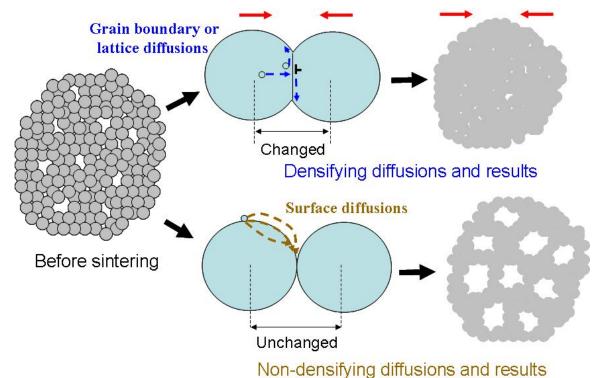

| Figure 1.22. Illustration of densifying and non-densifying diffusions and their sintering results | s.24 |

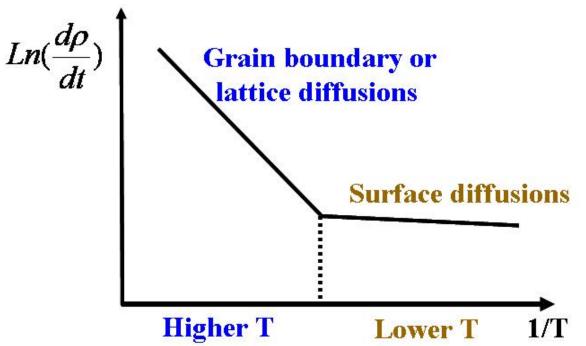

| Figure 1.23. Schematic diagram of change in densification rate with temperature. According to     | 0    |

| rapid rate sintering theory, the two regimes should corresponding to poor or no densification     | on   |

| (surface) at low temperatures and much more efficient densification (via grain boundary or        | r    |

| lattice diffusion) at high temperature                                                            | 25   |

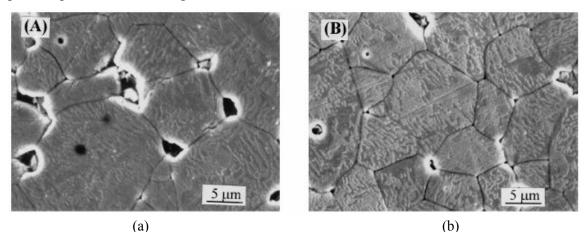

| Figure 1.24. The SEM micrographs of PZT sintered at 1150°C for 2 hours in air: (a) with the       |      |

| heating rates of 0.5°C/min and (b) 100°C/min                                                      | 26   |

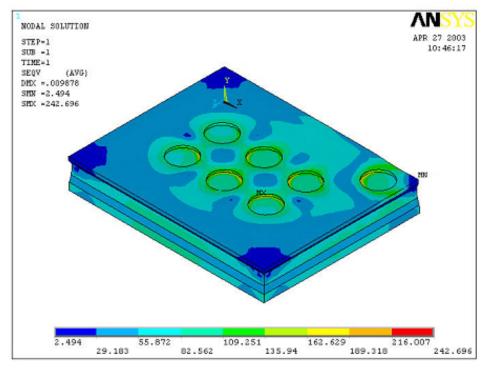

| Figure 1.25. Thermal stress distribution in the local position when the MOSFET operating at       |      |

| 94°C in an embedded power module                                                                  | 29   |

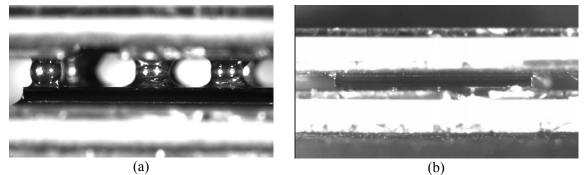

| Figure 1.26. The initial void problems in the reflowed die-attaching solder layers in (a) lead-tin     |

|--------------------------------------------------------------------------------------------------------|

| solder and (b) lead-free solder                                                                        |

| Figure 1.27. The solder bump failure after thermal cycling. (a) Barrel-shaped solder joints and (b)    |

| hourglass-shaped solder joints                                                                         |

|                                                                                                        |

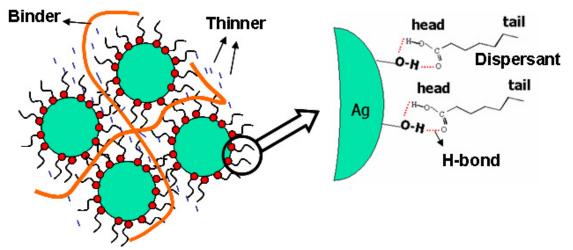

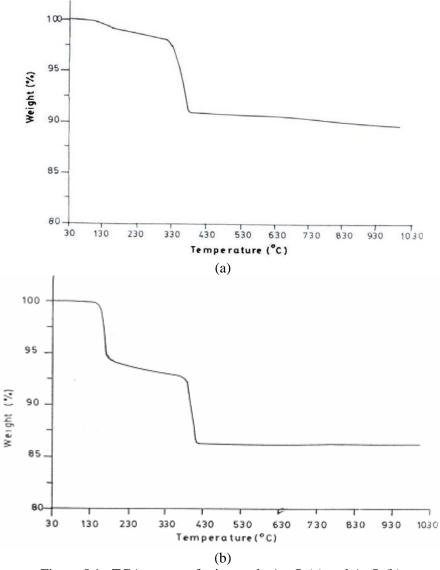

| Figure 2.1. Functions of the dispersant, binder and thinner in the formulation of nanoscale silver     |

| pastes                                                                                                 |

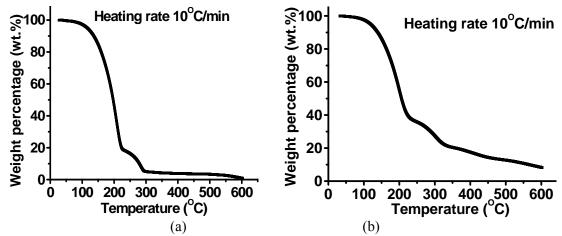

| Figure 2.2. Thermogravimetric analysis (TGA) curves of the thinner (a) and binder (b) selected         |

| for the silver paste formulation. Heat treatment condition is 10°C/min in air. Note the quick          |

| weight percentage drops at temperatures below 300°C                                                    |

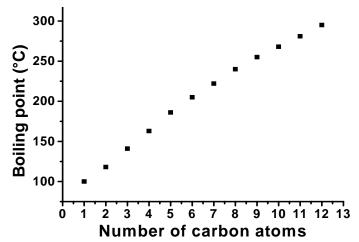

| Figure 2.3. The relationship of the boiling point of fatty acid versus their number of carbon          |

| atoms                                                                                                  |

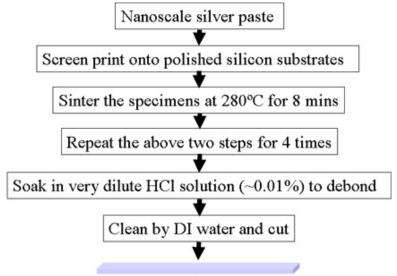

| Figure 2.4. Preparation procedure of nanoscale silver pastes                                           |

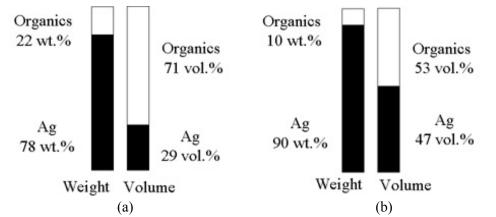

| Figure 2.5. The weight and volume percentages of the 78 wt.% silver paste (a) and those of the         |

| 90 wt.% silver paste (b)                                                                               |

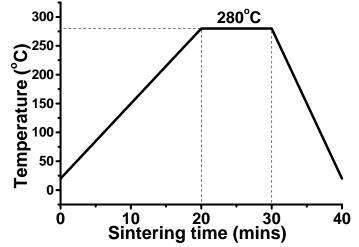

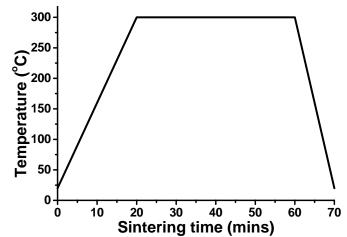

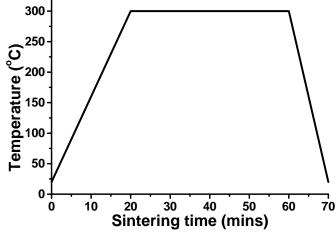

| Figure 2.6. Typical temperature profile for sintering nanoscale silver pastes                          |

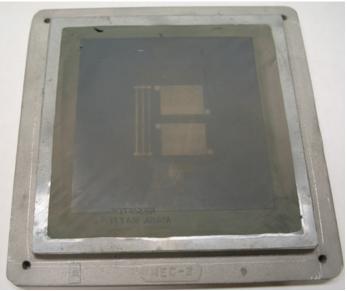

| Figure 2.7. Screen was used for printing resistor patterns                                             |

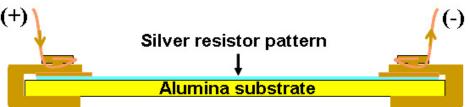

| Figure 2.8. Two electrodes used for the measurement of electrical resistance                           |

| Figure 2.9. Illustration of electrical resistivity determination from printed resistor patterns        |

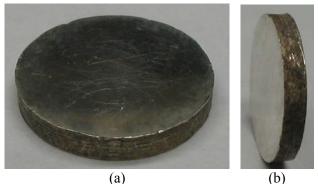

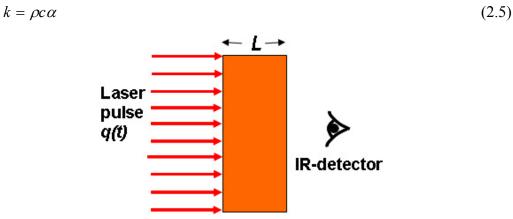

| Figure 2.10. The disc-shaped silver specimens prepared by molding and low-temperature                  |

| sintering                                                                                              |

| Figure 2.11. Illustration of the laser-flash experiment                                                |

| Figure 2.12. Preparation steps of the sintered sliver band-shaped samples for the tensile tests55      |

| Figure 2.13. Setup of ComTen tensile test machine                                                      |

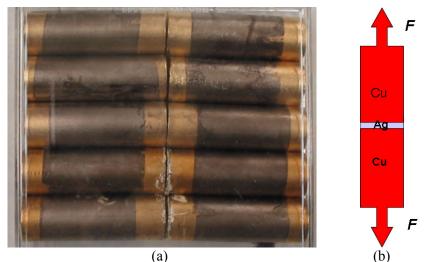

| Figure 2.14. Nickel/gold plated copper rods for the preparation of sintered silver joints (a) and      |

| their debonding illustration                                                                           |

| Figure 2.15. The quartz dilatometer used for the CTE measurement                                       |

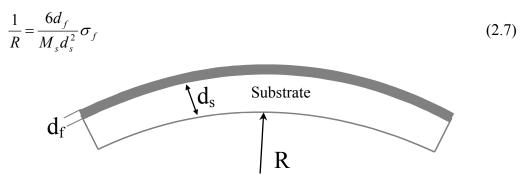

| Figure 2.16. Deformation of a film–substrate bilayer composite                                         |

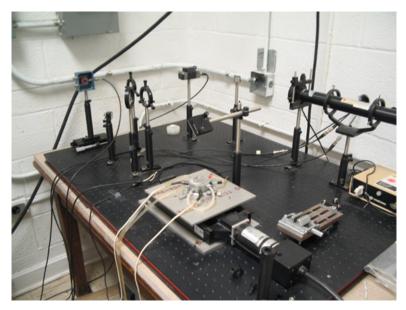

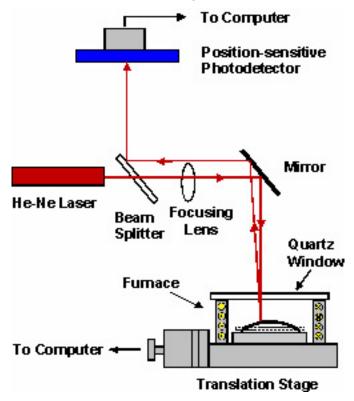

| Figure 2.17. The optical setup for measuring the curvature of bi-layer composite during thermal        |

| heating                                                                                                |

| Figure 2.18. The schematic of optical setup for measuring the curvature of bi-layer composite          |

| during thermal heating                                                                                 |

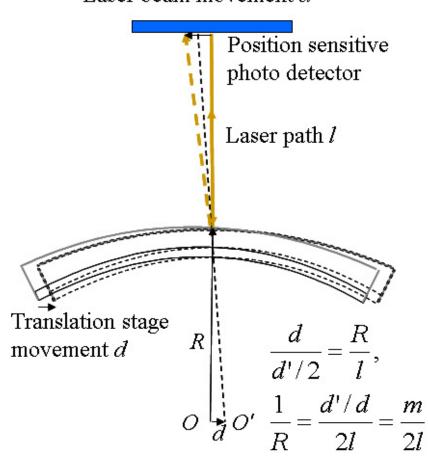

| Figure 2.19. The illustration of the translate relationships in the optical setup during the curvature |

| measurement                                                                                            |

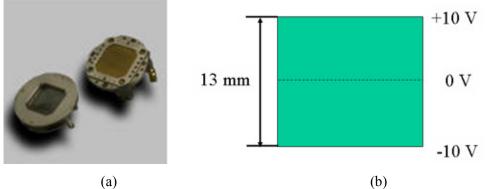

| Figure 2.20.                     | The position sensitive photodetectors used in the curvature determination optical                   |

|----------------------------------|-----------------------------------------------------------------------------------------------------|

| setup (a)                        | ) and their position-sensing mechanism (b)                                                          |

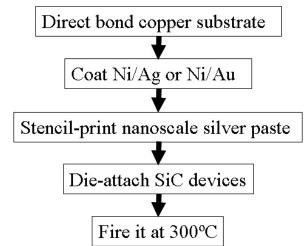

| Figure 2.21.                     | Preparation steps of the sintered sliver joint samples                                              |

| Figure 2.22.                     | Nickel/gold (a) and nickel/silver (b) coated AlN DBC and the nickel/silver and                      |

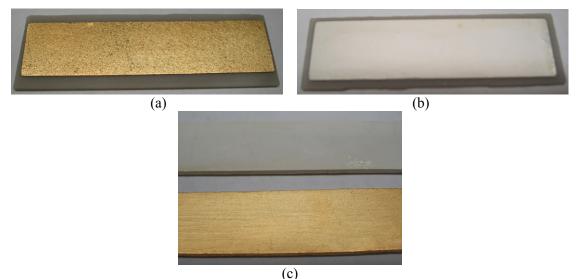

| nickel/g                         | old coated copper substrates (c)                                                                    |

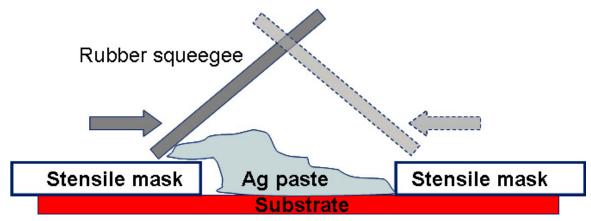

| Figure 2.23.                     | Illustration for the stencil printing process                                                       |

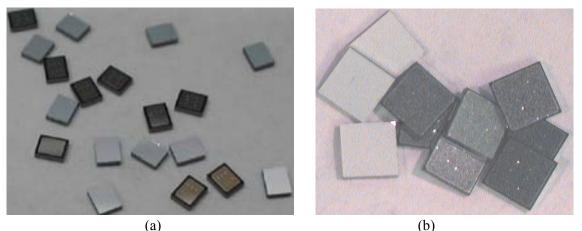

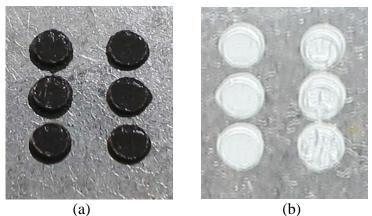

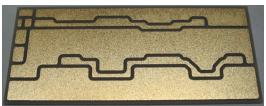

| Figure 2.24.                     | Infineon (a) and CREE (b) SiC devices used to form sintered silver joints62                         |

| Figure 2.25.                     | The sintering profile for achieve high bonding strength in the silver joints                        |

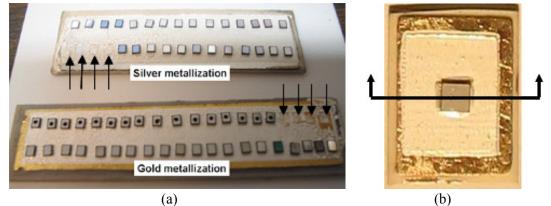

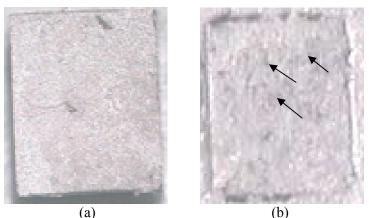

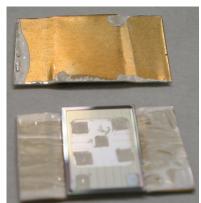

| Figure 2.26.                     | (a) Die-attached Infineon SiC devices on silver or gold-coated DBC substrates for                   |

| the die-s                        | shear tests. Arrows indicate the die-attaching cavities where the devices have been                 |

| sheared-                         | off. (b) A die-attached CREE device for the cross-sectional inspections                             |

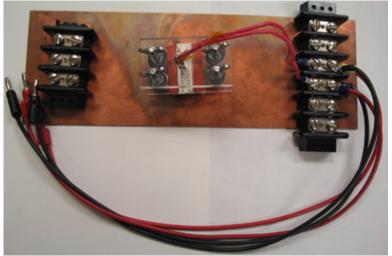

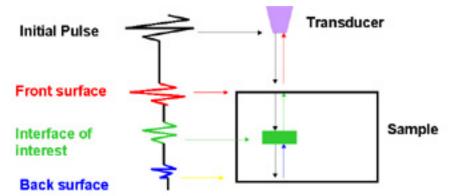

| Figure 2.27.                     | Fixture for the high-power curve tracer tests                                                       |

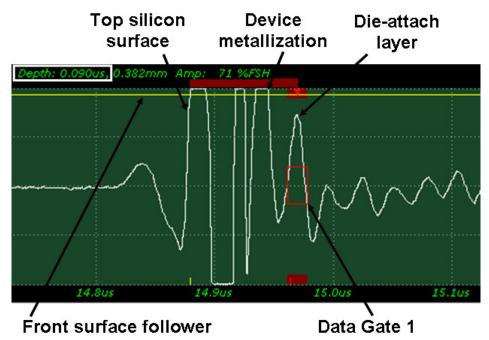

| Figure 2.28.                     | The pulse-echo mode illustration in scanning acoustic microscopy                                    |

| Figure 2.29.                     | A typical scan SAM image of an Infineon SiC device die-attached silver joint66                      |

| Figure 2.30.                     | The die-shear tester for die-shear-off test (a) and illustration for die shear-off (b)66            |

| Figure 2.31.                     | A silver joint specimen molded in cured epoxy for polishing and inspection67                        |

| Figure 2.32.                     | The die-attached Infineon SiC devices used for the 50-250°C thermal cycling                         |

| experim                          | ent. From top to bottom: Ag-coated Al <sub>2</sub> O <sub>3</sub> DBC, Ag-coated AlN DBC, Au-coated |

| Al <sub>2</sub> O <sub>3</sub> D | BC, Ag-coated AlN DBC, and Ag-coated copper substrates                                              |

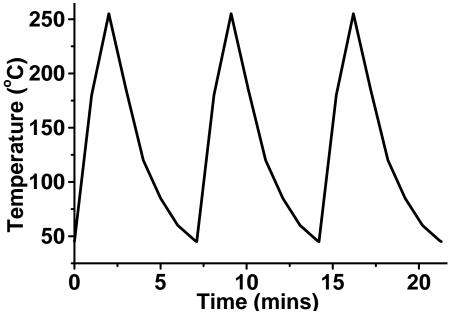

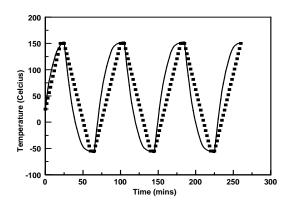

| Figure 2.33.                     | The Sikama belt reflow oven adapted for the 50-250°C thermal cycling experiment.                    |

| The four                         | r perpendicular arrows in the middle show the four of the total five slots were set to              |

| be 280°                          | C. The fifth is left for cooling and the last window is for setting the cycling speed.              |

| The two                          | arrows in the lower left corner indicate the two blowing fans for cooling down69                    |

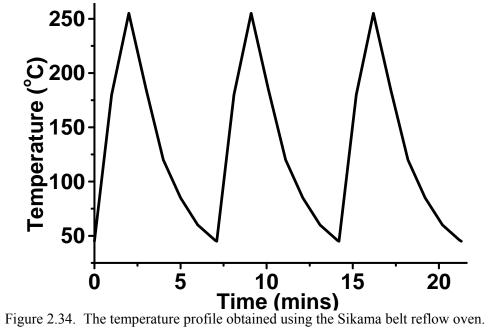

| Figure 2.34.                     | The temperature profile obtained using the Sikama belt reflow oven70                                |

| Figure 2.35.                     | The fixture and samples used for the 50-250°C thermal cycling70                                     |

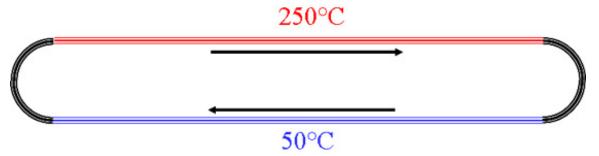

| Figure 2.36.                     | Realization of 50-250°C temperature profile using the Sikama belt reflow oven70                     |

| Figure 2.37.                     | The loaded sample holders installed in the belt oven during the 50-250°C thermal                    |

| cycling.                         | The covering lid was removed for clarity71                                                          |

|                                  |                                                                                                     |

| Figure 3.1.                      | The 78 wt.% (a), 84 wt.% (c), and 90 wt.%(d) silver-loading nano- pastes stored in                  |

| containe                         | ers. (b) 78 wt.% silver paste stored in a plastic syringe74                                         |

| Figure 3.2.                      | Good flowability of the commercial microscale silver paste (a) and that of 78 wt.%                  |

| nanosca                          | le silver paste74                                                                                   |

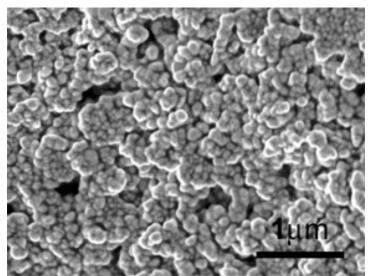

| Figure 3.3.                      | Scanning electron microscopy of as-prepared 78 wt.% nanoscale silver paste75                        |

| Figure 3.4. The stencil-printed nanoscale silver pattern on alumina (a) and that on glass (b)                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| before sintering                                                                                                                                                                 |

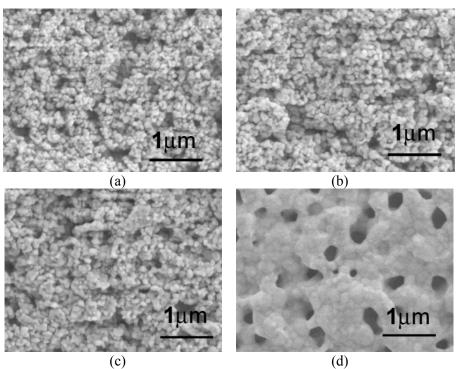

| Figure 3.5. The microstructure changes of nanoscale silver heated up to 200°C (a), 225°C (b),                                                                                    |

| 250°C (c) and 275°C, respectively, during the low-temperature sintering                                                                                                          |

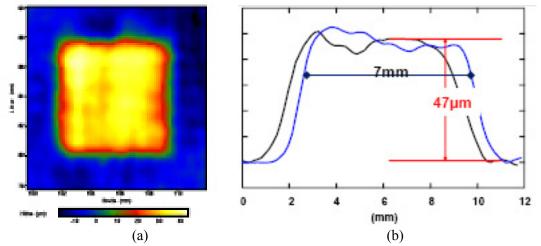

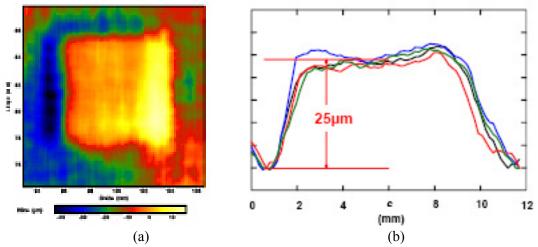

| Figure 3.6. Topological image (a) and its two topological profiles (b) of the printed nanoscale                                                                                  |

| silver paste before sintering                                                                                                                                                    |

| Figure 3.7. Topological image (a) and its two topological profiles (b) of the printed nanoscale                                                                                  |

| silver paste after sintering                                                                                                                                                     |

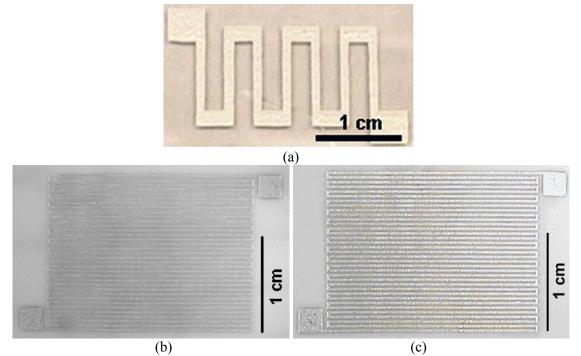

| Figure 3.8. Screen-printed and low-temperature sintered silver patterns on alumina substrates78                                                                                  |

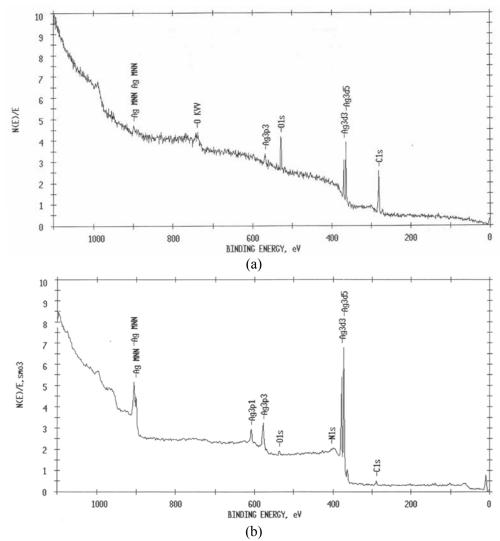

| Figure 3.9. XPS analysis of the as-prepared 78 wt.% silver paste (a) and that of after the low-                                                                                  |

| temperature sintering (b). Compared (b) to (a), it was found that the carbon and oxygen were                                                                                     |

| reduced more than 90% during the low-temperature sintering79                                                                                                                     |

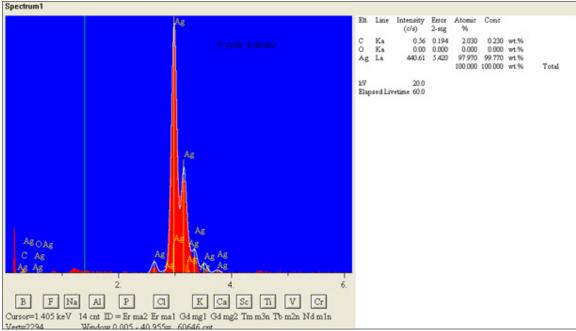

| Figure 3.10. EDS analysis of the 78 wt.% silver paste after the low-temperature sintering. Silver                                                                                |

| is about 99.77 wt.% after the low-temperature sintering and the rest of the sintered silver is                                                                                   |

| carbon (~0.23 wt.%). There is no detectable oxygen left                                                                                                                          |

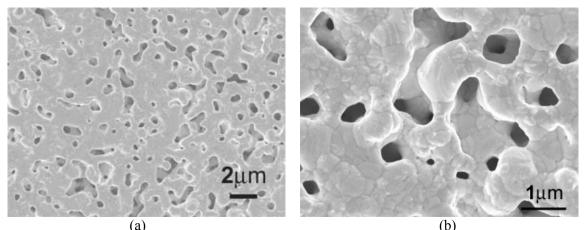

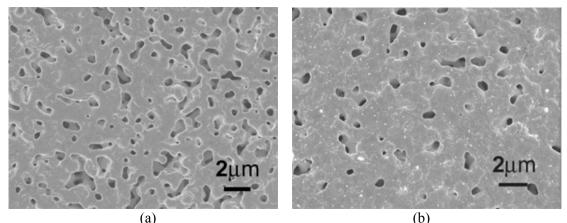

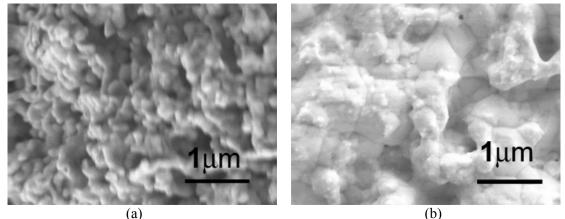

| Figure 3.11. Microstructure of the low-temperature sintered nanoscale silver on an alumina                                                                                       |

| substrate (top surface of a sintered film with thickness about 1 mil). (a) at 10 Kx and (b) 50                                                                                   |

|                                                                                                                                                                                  |

| Kx                                                                                                                                                                               |

| Kx                                                                                                                                                                               |

|                                                                                                                                                                                  |

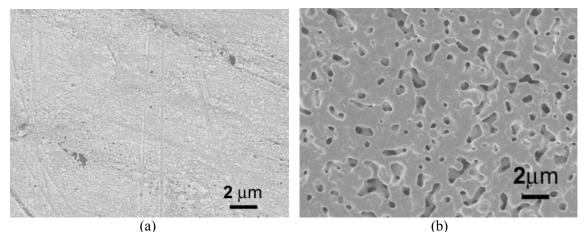

| Figure 3.12. Microstructures of the low-temperature sintered nanoscale silver (a) by follows the                                                                                 |

| Figure 3.12. Microstructures of the low-temperature sintered nanoscale silver (a) by follows the profile in Figure 2.6 and (b) abrupt sintering, respectively                    |

| <ul><li>Figure 3.12. Microstructures of the low-temperature sintered nanoscale silver (a) by follows the profile in Figure 2.6 and (b) abrupt sintering, respectively</li></ul>  |

| <ul> <li>Figure 3.12. Microstructures of the low-temperature sintered nanoscale silver (a) by follows the profile in Figure 2.6 and (b) abrupt sintering, respectively</li></ul> |

| <ul> <li>Figure 3.12. Microstructures of the low-temperature sintered nanoscale silver (a) by follows the profile in Figure 2.6 and (b) abrupt sintering, respectively</li></ul> |

| <ul> <li>Figure 3.12. Microstructures of the low-temperature sintered nanoscale silver (a) by follows the profile in Figure 2.6 and (b) abrupt sintering, respectively</li></ul> |

| <ul> <li>Figure 3.12. Microstructures of the low-temperature sintered nanoscale silver (a) by follows the profile in Figure 2.6 and (b) abrupt sintering, respectively</li></ul> |

| <ul> <li>Figure 3.12. Microstructures of the low-temperature sintered nanoscale silver (a) by follows the profile in Figure 2.6 and (b) abrupt sintering, respectively</li></ul> |

| <ul> <li>Figure 3.12. Microstructures of the low-temperature sintered nanoscale silver (a) by follows the profile in Figure 2.6 and (b) abrupt sintering, respectively</li></ul> |

| <ul> <li>Figure 3.12. Microstructures of the low-temperature sintered nanoscale silver (a) by follows the profile in Figure 2.6 and (b) abrupt sintering, respectively</li></ul> |

| <ul> <li>Figure 3.12. Microstructures of the low-temperature sintered nanoscale silver (a) by follows the profile in Figure 2.6 and (b) abrupt sintering, respectively</li></ul> |

| <ul> <li>Figure 3.12. Microstructures of the low-temperature sintered nanoscale silver (a) by follows the profile in Figure 2.6 and (b) abrupt sintering, respectively</li></ul> |

| <ul> <li>Figure 3.12. Microstructures of the low-temperature sintered nanoscale silver (a) by follows the profile in Figure 2.6 and (b) abrupt sintering, respectively</li></ul> |

| Figure 3.19. | Comparison of thermal conductivity values of the common-used interconnecting                          |

|--------------|-------------------------------------------------------------------------------------------------------|

| material     | s with that of the sintered silver                                                                    |

| Figure 3.20. | Comparison of surface microstructures of the polished samples for the thermal                         |

| conducti     | vity measurement (a) and those for the electrical conductivity measurement (b)88                      |

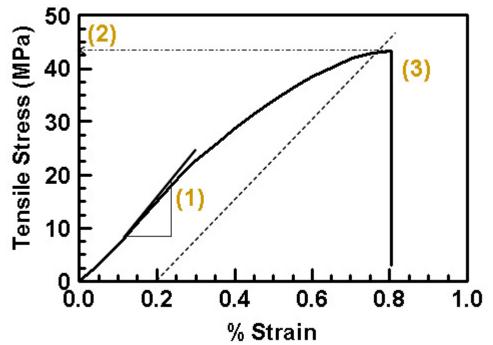

| Figure 3.21. | A typical stress-strain curve of the sintered silver in the tensile test                              |

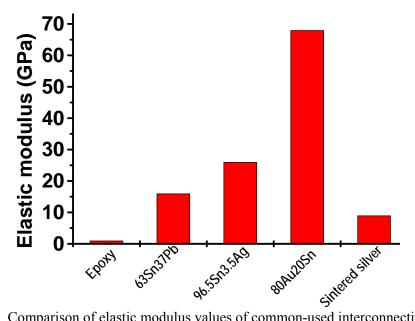

| Figure 3.22. | Comparison of elastic modulus values of common-used interconnecting materials                         |

| with that    | t of the sintered silver                                                                              |

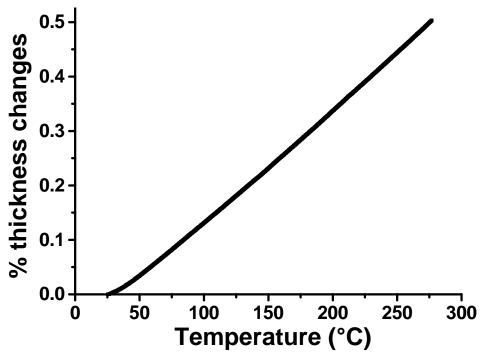

| Figure 3.23. | A typical thickness change-temperature curve of the quartz dilatometry test90                         |

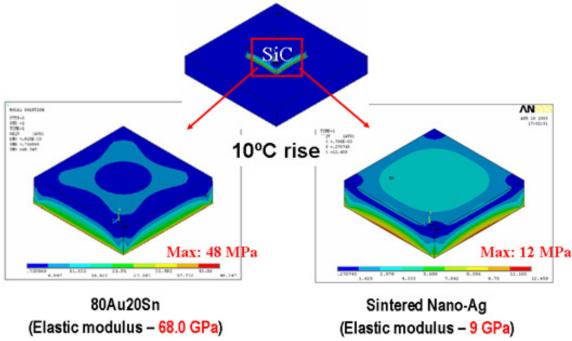

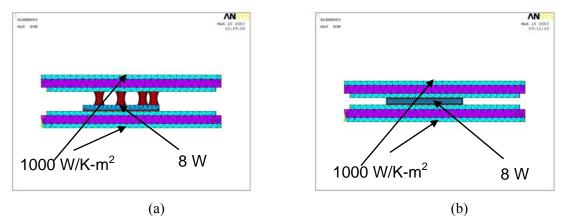

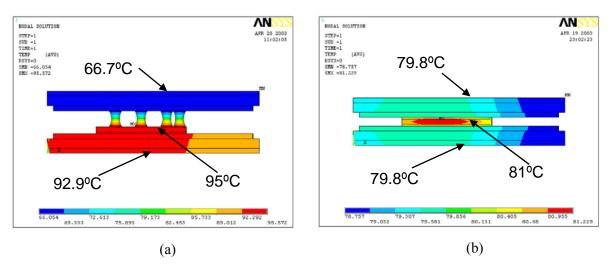

| Figure 3.24. | A finite element analysis shows that the sintered silver induces less thermal stresses                |

| than those   | se of gold-tin solder                                                                                 |

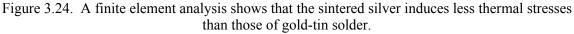

| Figure 3.25. | The date plot of the position changes in the photodetector versus the scanning                        |

| distance     | from the curvature experiment                                                                         |

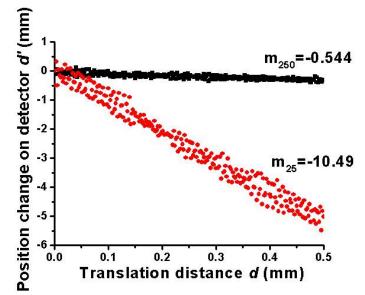

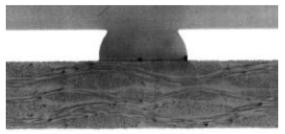

| Figure 3.26. | The organic components are more difficult to burn out in covering case (b) than in                    |

| the open     | -air case (a)                                                                                         |

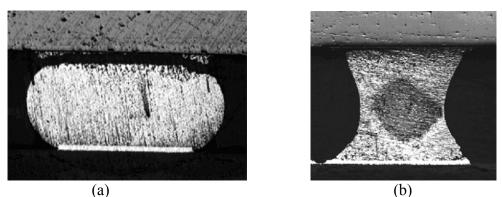

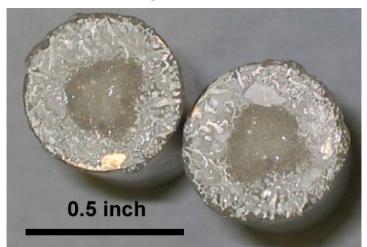

| Figure 3.27. | Low-temperature sintered silver at half-inch thick rod surfaces after debonding95                     |

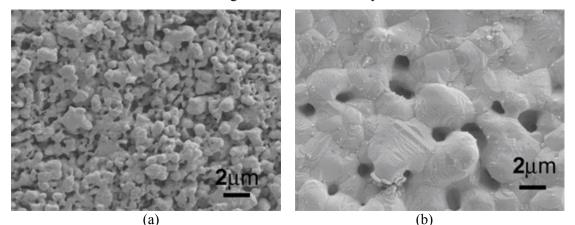

| Figure 3.28. | The comparison of the microstructures of unsintered silver (a) with those of sintered                 |

| silver (b)   | )                                                                                                     |

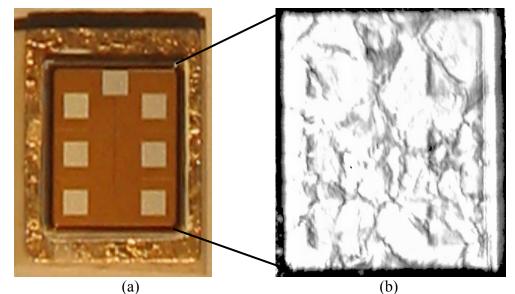

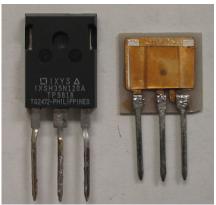

| Figure 3.29. | The silver sintering die-attached power IGBT with a size of $8.91 \times 7.22 \text{ mm}^2$ (a) and   |

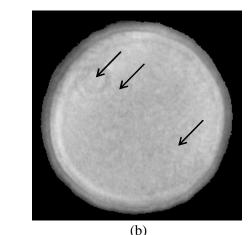

| its SAM      | image (b)96                                                                                           |

| Figure 3.30. | The 78 wt.% (a) and 84 wt.% (b) silver paste sintering under the $4 \times 4 \text{ mm}^2$ glass      |

| slide cov    | verage after 10-min dwell sintering at 300°C                                                          |

| Figure 3.31. | The 84 wt.% silver paste sintering under a $6 \times 6 \text{ mm}^2$ glass slide (a) and that under a |

| a 3×3 m      | m <sup>2</sup> glass slide coverage after 5-min dwell at 300°C                                        |

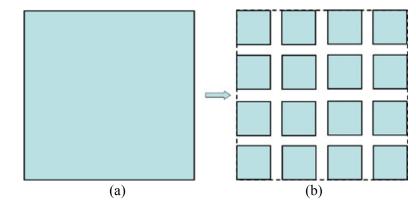

| Figure 3.32. | Illustration of using small patterns for the enhancement of organic burnout and paste                 |

| sintering    | for large area silver bonding                                                                         |

| Figure 3.33. | The sintering profile for achieving enhanced sintering and high bonding strength for                  |

| the silve    | r joints with size 4×4 mm <sup>2</sup> or under                                                       |

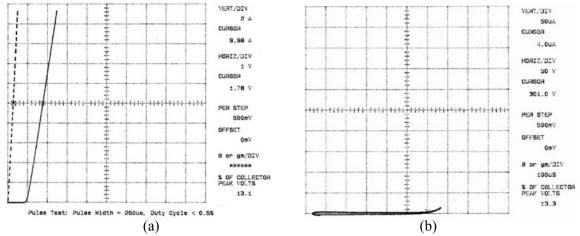

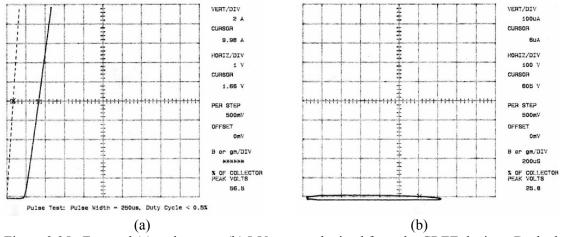

| -            | Forward (a) and reverse (b) I-V curves obtained from the Infineon devices. Dashed                     |

| curve in     | (a) is due to the test fixture                                                                        |

| Figure 3.35. | Forward (a) and reverse (b) I-V curves obtained from the CREE devices. Dashed                         |

| curve in     | (a) is due to the test fixture                                                                        |

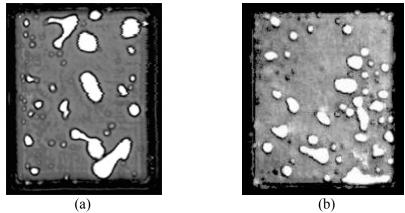

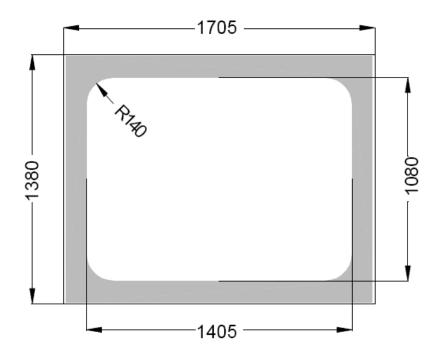

| Figure 3.36. | SAM images of the sintered silver joints between the SiC devices and the gold-                        |

|              | DBC substrate. (a) from the Infineon devices measured of $1.706 \times 1.38 \text{ mm}^2$ and (b)     |

| from the     | CREE devices measured of $2.26 \times 2.26 \text{ mm}^2$                                              |

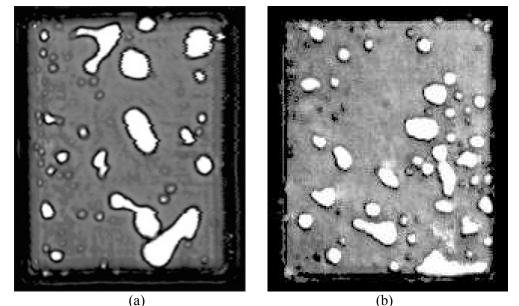

| Figure 3.37. The initial void problems in the reflowed die-attaching solder layers (a) lead-tin   |

|---------------------------------------------------------------------------------------------------|

| solder and (b) lead-free solder                                                                   |

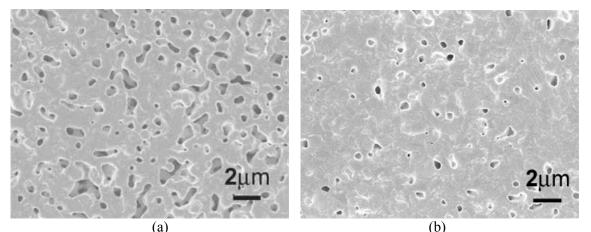

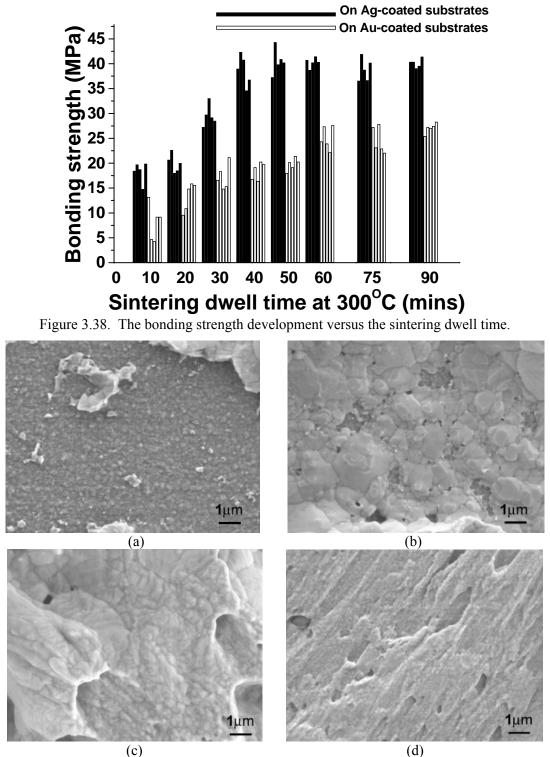

| Figure 3.38. The bonding strength development versus the sintering dwell time103                  |

| Figure 3.39. Microstructures of the debonded sintered silver joints on the silver-coated SiC      |

| devices after dwelling sintering at 300°C for (a) 10 mins, (b) 20mins, (c) 40mins, and (d) 60     |

| mins103                                                                                           |

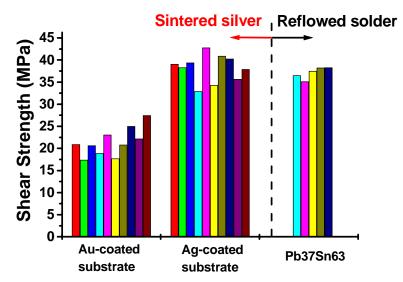

| Figure 3.40. The comparison of the shear strength of the low-temperature sintered silver with     |

| that of the reflowed solder104                                                                    |

| Figure 3.41. Optical microscopy pictures of one of the sheared-off Infineon SiC device (a) and    |

| the corresponding die-attach cavity on the gold-coated DBC substrate (b). The arrows in (b)       |

| indicate the debonding areas from the gold-silver interface104                                    |

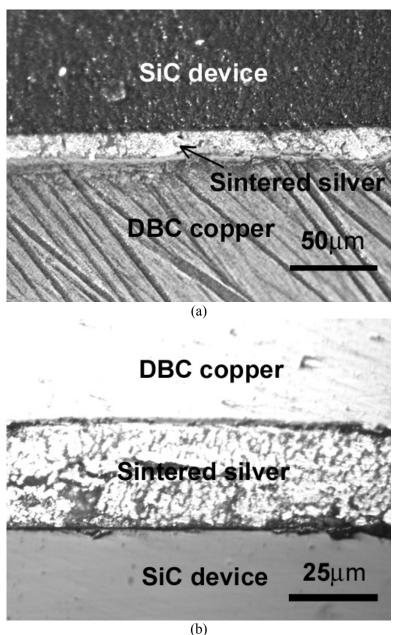

| Figure 3.42. Optical microscope pictures of the cross-section of the sintered silver joints105    |

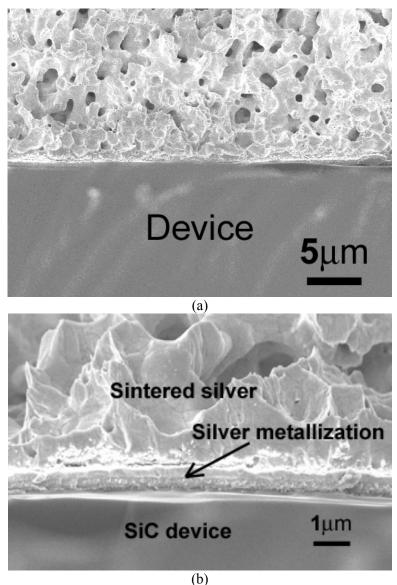

| Figure 3.43. Scanning electron microscope pictures of the cross-section of the sintered silver    |

| joints106                                                                                         |

| Figure 3.44. An alumina DBC substrate broken from the alumina layer between 100-200 cycles        |

| switching from 50°C to 300°C108                                                                   |

| Figure 3.45. Another alumina DBC substrate broken from the alumina layer between 500 to 1000      |

| cycles switching from 50°C to 250°C                                                               |

| Figure 3.46. The temperature profile obtained using the Sikama belt reflow oven109                |

| Figure 3.47. The SAM images of the sintered silver joints on nickel/silver-coated AlN DBC after   |

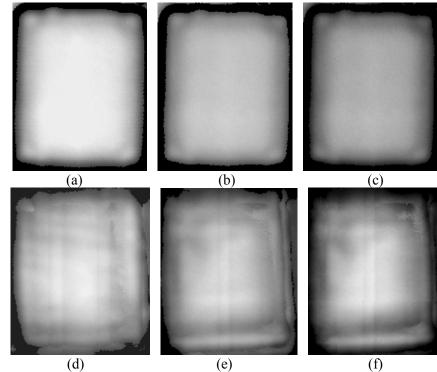

| 0 (a), 1000 (b), 2000 (c), 4000 (d), 6000 (e), and 8000 (f) thermal cycles, respectively110       |

| Figure 3.48. SAM images of the sintered silver joints on nickel/gold-coated $Al_2O_3$ DBC after 0 |

| (a), 1000 (b), 2000 (c), 4000 (d), 6000 (e), and 8000 (f) thermal cycles, respectively111         |

| Figure 3.49. The debonding of the eutectic lead-tin solder joints after 875 temperature cycles    |

| between -55—150°C. The enclosed area indicates the initial extent of the solder joints111         |

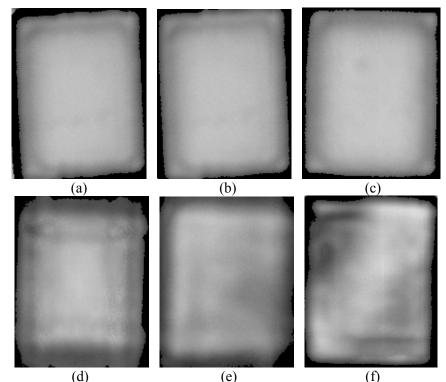

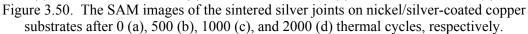

| Figure 3.50. The SAM images of the sintered silver joints on nickel/silver-coated copper          |

| substrates after 0 (a), 500 (b), 1000 (c), and 2000 (d) thermal cycles, respectively112           |

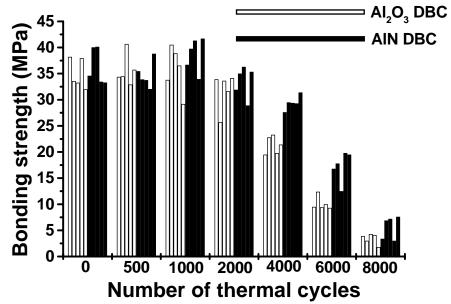

| Figure 3.51. Changes of shear strength of the low-temperature sintered silver joints on           |

| nickel/silver-coated DBC substrates during the temperature cycling experiment112                  |

| Figure 3.52. Changes of shear strength of the low-temperature sintered silver joints on           |

| nickel/gold-coated DBC substrates during the temperature cycling experiment113                    |

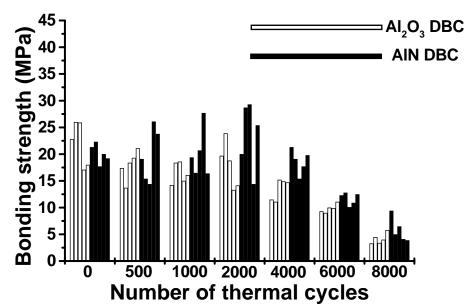

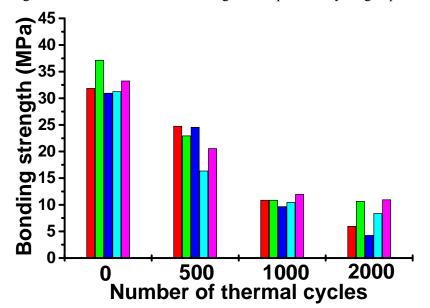

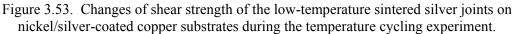

| Figure 3.53. Changes of shear strength of the low-temperature sintered silver joints on           |

| nickel/silver-coated copper substrates during the temperature cycling experiment113               |

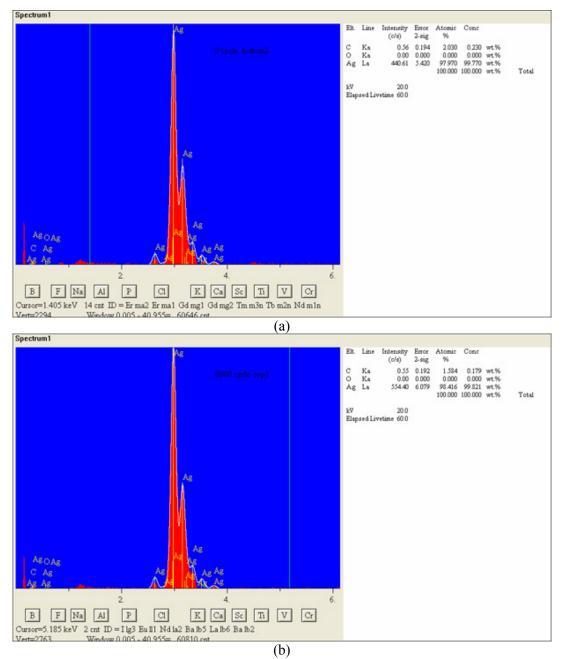

| Figure 3.54. EDS analysis of the silver joints before (a) after (b) the 8000 50-250°C thermal                        |

|----------------------------------------------------------------------------------------------------------------------|

| cycles. Silver is about 99.8 wt.% and the rest component is carbon. There is no detectable                           |

| oxygen element before and after thermal cycles                                                                       |

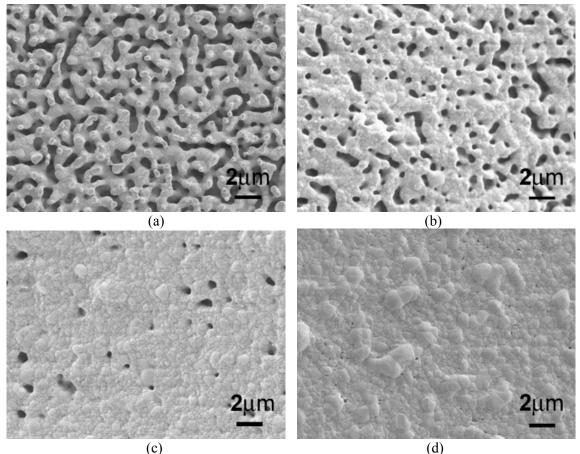

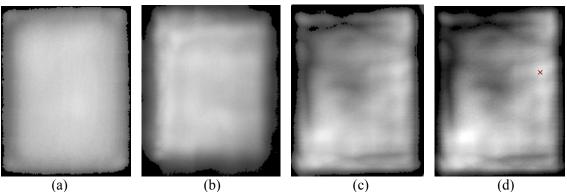

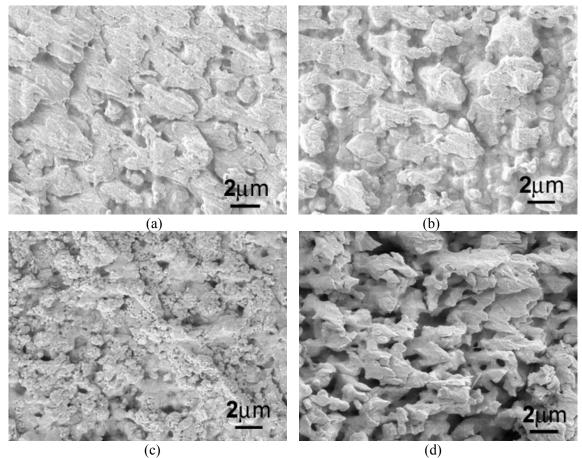

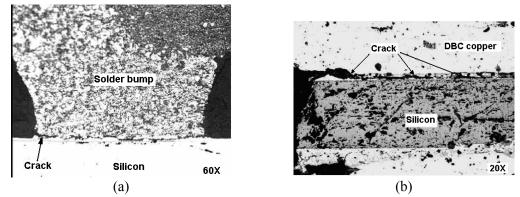

| Figure 3.55. Microstructures of the debonded sintered silver joints on the silver-coated SiC                         |

| devices after (a) 0, (b) 2000, (c) 4000, and (d) 6000 cycles. The silver joints were debonded                        |

| from the nickel/silver aluminum-nitride DBC substrates                                                               |

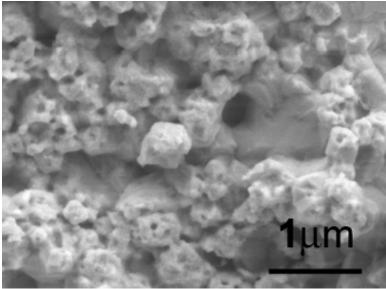

| Figure 3.56. Microstructure changes of the debonded sintered silver joint surfaces after 4000                        |

| thermal cycles. The silver joints were debonded from the nickel/silver aluminum-oxide DBC                            |

| substrates                                                                                                           |

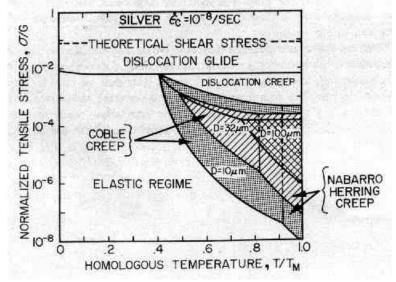

| Figure 3.57. The deformation-mechanism map for pure silver, established for a critical strain rate                   |

| of 10 <sup>-8</sup> s <sup>-1</sup>                                                                                  |

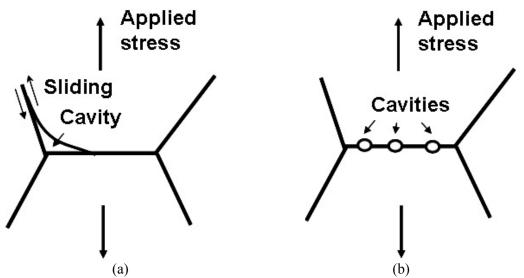

| Figure 3.58. <i>w</i> -type cavitation at a grain-boundary triple point (a) and <i>r</i> -type cavitation at a grain |

| boundary normal to the stress axis                                                                                   |

|                                                                                                                      |

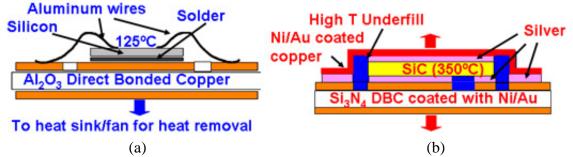

| Figure 4.1. The solder die-attaching and wire-bonding technology (a) versus the low-temperature                      |

| silver sintering technology (b)                                                                                      |

| Figure 4.2. The IXYS bare dies used for single-chip power packaging demonstration. (a) Bare                          |

| power IGBTs with type # of IXSD35N120A; (b) Bare power IGBTs with type # of                                          |

| IXSD1765                                                                                                             |

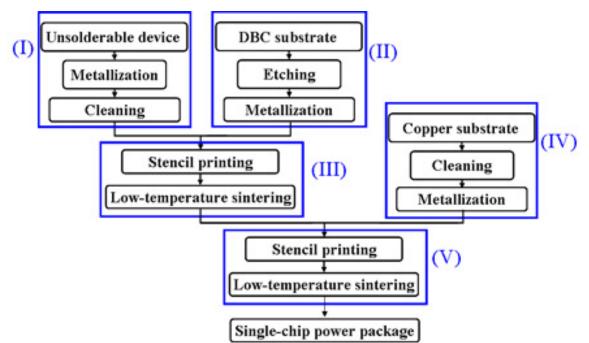

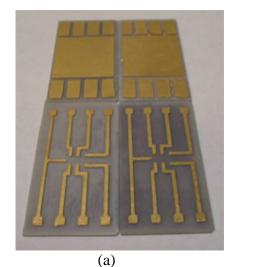

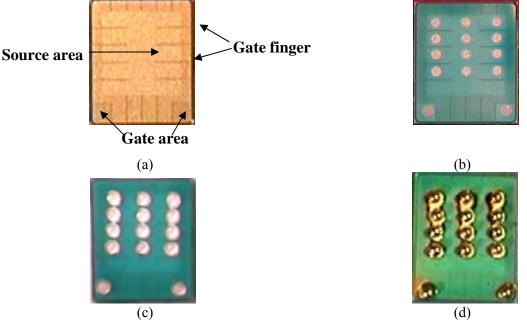

| Figure 4.3. The fabrication steps for the silver jointed single-chip power packages124                               |

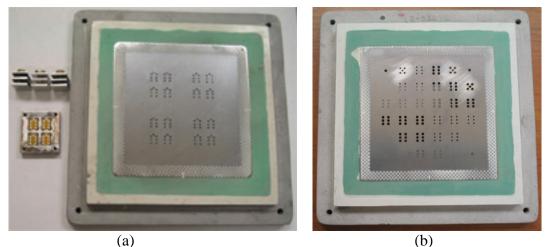

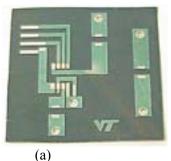

| Figure 4.4. The stencil masks and fixtures used for stencil-printing silver paste. (a) The stencil                   |

| pattern designed for the IXSD35N120A bare dies, and (b) the pattern for the drain terminals                          |

| of the silver joints                                                                                                 |

| Figure 4.5. The IXSD35N120A bare dies after the sputtering metallization and low-temperature                         |

| sintering of stencil-printed silver paste on the gate and source terminals. The top middle                           |

| square is for gate and other six are for the source                                                                  |

| Figure 4.6. The IXSD1765 bare dies after the solder mask deposition to protect the exposed gate                      |

| fingers. Note that the IXSD1765 dies are already metallized nickel/silver at the open                                |

| windows for the gate and source terminals                                                                            |

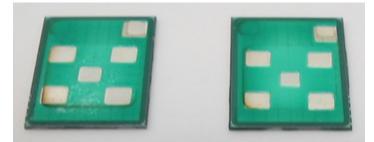

| Figure 4.7. The etched and nickel/gold coated DBC substrates for the IXSD35N120A dies (a)                            |

| and those for the IXSD1765 dies (b)                                                                                  |

| Figure 4.8. Flip die-attached IXSD1765 on the nickel/gold coated DBC substrate126                                    |

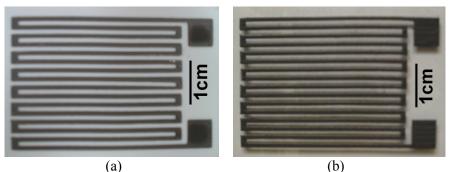

| Figure 4.9. The stencil-printed silver paste patterns on nickel/silver coated DBC substrates (a)                     |

| and those after the low-temperature sintering (b)                                                                    |

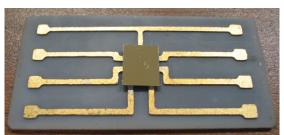

| Figure 4.10. | The finished single-chip power packages for the IXSD35N120A devices (a) using       |    |

|--------------|-------------------------------------------------------------------------------------|----|

| the nicke    | el-gold plated DBC substrates and (b) the nickel-silver plated DBC substrates12     | 27 |

| Figure 4.11. | The IXSD1765 dies with the drain terminals interconnected to nickel-gold coated     |    |

| copper ca    | avities12                                                                           | 28 |

| Figure 4.12. | Comparison of the commercial wire-bonded single-chip power package (left, TO-       |    |

| 247 pow      | er package) with the low-temperature sintered silver joint power package (right)12  | 28 |

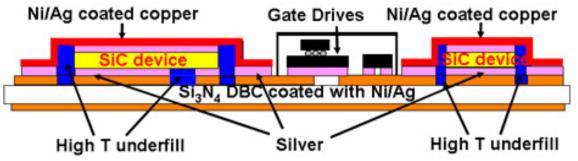

| Figure 4.13. | Illustration of a high-temperature integrated power electronics module bonded usin  | ıg |

| low-temp     | perature sintered silver                                                            | 29 |

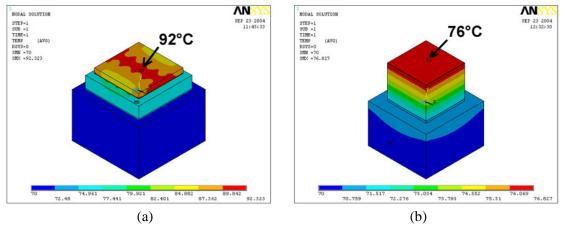

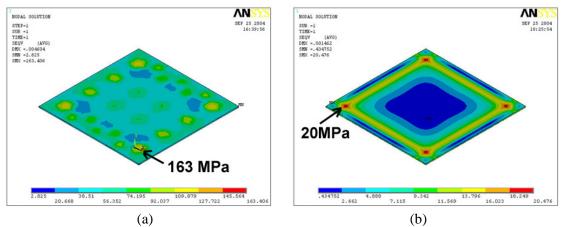

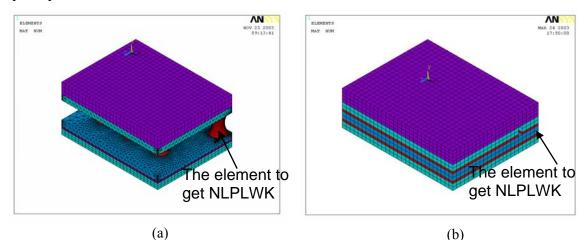

| Figure 4.14. | FEM thermal modeling of the temperature distributions in our proposed LED           |    |

| package      | versus the flip-chip LED package12                                                  | 30 |

| Figure 4.15. | FEM modeling of thermomechanical stress distributions in the packaged LED           |    |

| devices v    | versus that in the flip-chip LED device during operation (the stress-free state was |    |

| assumed      | to be at the respective die-attach temperatures)12                                  | 31 |

| Figure 4.16. | Low-temperature sintered silver die-attached LEDs. The two white parts are          |    |

| dispense     | d-silver after low-temperature sintering and the two blacks squares are two die-    |    |

| attached     | LEDs                                                                                | 31 |

|              |                                                                                     |    |

|              |                                                                                     |    |

| Figure 5.1. | TGA curves of microscal | e Ag <sub>2</sub> O (a) and AgO (b) |  |

|-------------|-------------------------|-------------------------------------|--|

|-------------|-------------------------|-------------------------------------|--|

## LIST OF TABLES

| Table 1.1. | Pros and cons of various chip-level interconnect technologies  | 13 |

|------------|----------------------------------------------------------------|----|

| Table 1.2. | Sintering mechanisms in polycrystalline and amorphous solids   | 17 |

| Table 1.3. | Values for the constants <i>m</i> and <i>n</i> in Equation 1.1 | 19 |

| Table 1.4. | Pros and cons of various chip-level interconnect technologies  | 27 |

Table 2.1. The properties of two types of SiC Schottky rectifiers obtained from industry. Data from Infineon and CREE datasheets, respectively (under the condition of  $T_J = 25^{\circ}C$ ) ......63

| Table 3.1. | The values of specific heat of the sintered nanoscale silver paste at different      |

|------------|--------------------------------------------------------------------------------------|

| temper     | ratures. Tabulated data has been compared to reference data for sapphire             |

| Table 3.2. | Thermal properties of the sintered nanoscale silver paste and those of bulk silver87 |

| Table 3.3. | The determined curvature and stress values from the curvature experiment92           |

| Table 3.4. | The mechanical property values of the sintered silver films and silicon substrates93 |

| Table 3.5. | Property comparison of some commonly used solder alloys with our low-temperature     |

| sintere    | d silver pastes                                                                      |

| Table 3.6. | The static curve tracer test results of the two types of SiC devices101              |

# Chapter 1 Introduction

Electronic packaging provides electrical connection or isolation, thermal cooling, mechanical support, and physical protection for power electronic components that make up the circuits. Therefore, the overall performance of a single-chip power package, a multichip power module as well as a whole power system is not only determined by the electrical components and the circuit layouts, but also affected by their packaging technology. Over last twenty years, industrial and academic research efforts on electronic power conversion are making the move toward high-frequency synthesis, which results in great improvement in converter performance, miniaturization in physical size and reduction of mass weight and loss. It is pushing the limits of existing power packaging and thermal management technology. On the other hand, wide-bandgap semiconductors such as silicon carbide (SiC) based electronic devices and circuits are presently being developed for advantageous use in high-temperature, high-power, and/or high-radiation conditions. The applications of SiC pose another significant challenge for packaging of these electronic devices. The conventional technology for interconnecting power devices typically involves die-attaching one terminal of the semiconductor die to a heat-sinking substrate with solder alloys or conductive epoxies and wirebonding fine aluminum or gold wires to the other terminal(s). Such an interconnect technology is not able to meet the high-temperature operating requirement of the wide-bandgap devices. It is device interconnecting and packaging technology the dominant technical barrier that currently limits the rapid growth of power electronics. New interconnecting materials and technologies are needed before high-temperature devices and circuits can be scaled-up and reliably incorporated into power electronic systems.

The sintering of powder compacts has been widely applied in microelectronics for making hybrid circuits, cofired multilayer metal/ceramic interconnecting substrates, multilayer ceramic capacitors, magnetic components, and etc. Since the conventional sintering normally requires a temperature that may be substantially higher than the maximum temperature a semiconductor device can tolerate, any means of lowing the sintering temperature is desirable and necessary for the successful implementation.

This research presents a new semiconductor device interconnect technology using low-temperature sinterable nanoscale silver pastes for electronic packaging applications. First, the silver pastes were formulated through a metal colloidal/paste process with the aid of cutting-edge nanotechnology. Then a new power device interconnect technology was developed and the reliability of the low-temperature sintered silver joints was evaluated and their failure mechanisms were discussed. Finally, the potential applications of the technology were demonstrated at conceptual levels.

#### 1.1 Overview of Power Electronic Packaging

Hierarchically, electronic packaging begins from the interface of a semiconductor chip itself--which is considered as the first-level or chip-level packaging--to higher levels of packaging such as board-level and system-level packaging. Chip-level packaging deals with the attachment of one or more bare chips to a substrate, the interconnection from these chips to package leads, and encapsulation. In power electronic systems, the firstlevel chip interconnection plays a vital role because it directly interfaces with the power chips that contain millions of transistor circuits not only electrically but also thermally and mechanically. It has to fulfill very different requirements compared with those for microelectronic integrated circuit (IC) chips. Firstly, since power devices typically operate at high switching frequencies, parasitic noises must be reduced in order to maintain a high level of circuit performance and efficiency. Secondly, compared with IC interconnections, larger cross-sectional areas and current-handling capabilities are needed in power interconnections because the flowing current increases by several orders of magnitude. Furthermore, the increased power density drives the first-level packaging to improve its roles in heat dissipation and thermal management. At last, the reliability of the first-level power interconnections is essential to ensure the electronic systems to have an extended lifetime.

#### 1.1.1 Current Chip-Level Interconnect Technologies

#### A. Wirebond

The traditional chip-level interconnect technology in power electronics is wirebond. This is primarily due to the fact that the technology can easily accommodate changes in package design with the minimum modification of facilities and lowest cost per interconnection. The flexibility and the low cost combined with a continuous effort in reliability improvement indicate that wirebond will continue to be the prominent method for chip-level interconnections [1].

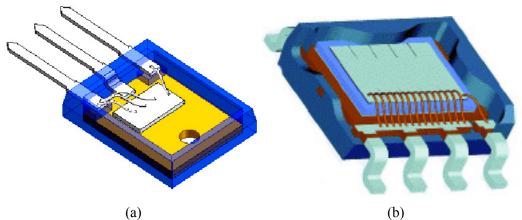

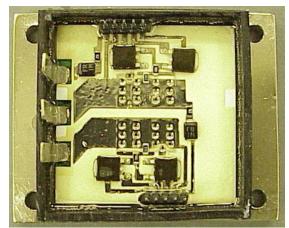

In a typical single-chip package, the source and gate terminals are connected from the aluminum chip bonding pads to nickel-plated copper leads. The chip and wirebonds are encapsulated with molding compound for insulation, mechanical support and protection. Figure 1.1(a) shows a wirebond transistor-outline package (TO-247) and (b) shows the famous small outline package (SO-8) with the top molding hidden for clarity. The die-attachment of the devices is connected by solder reflow.

Figure 1.1. Top views of the wirebond TO-247 (a) and SO-8 (b) MOSFET packages.

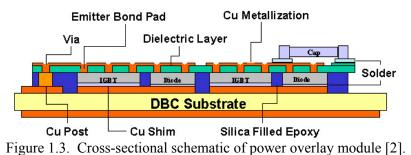

In a wirebond multichip power module, a direct bond copper (DBC) substrate (see Appendix A) is usually used for attaching the switching devices. The die-attach material is usually solder. Aluminum wires ranging from 5 to 20-mil (125-500  $\mu$ m) thick are used to connect power chips and conductor leads (or traces) at the periphery of the power module. In order to achieve high current capability, several power chips may be used in parallel and connected by tens or even hundreds of aluminum bonding wires, as shown in Figure 1.2.

The ultrasonic bonding is the most common method for wirebond process. The aluminum wires are bonded to aluminum metallization on chip pads without use of a heat source. During the process, an aluminum wire is first passed through a hole in a capillary. By applying a continuous downward force and ultrasonic horizontal rubbing (60 to 120 kHz) of the wire to the bonding surfaces, the aluminum wire plastically deforms and breaks the aluminum oxide layers to allow a pure aluminum-to-aluminum contact. After the first bond, the bonding machine forms a second bond between the wire and the nickel-plated copper substrate to finish a bond cycle.

Figure 1.2. Top view of a wirebond multichip power module.

In a wirebond power package, the wirebond and the top-metal-sheet resistances contribute about 90% of the packaging resistance. They are the primary contributors to electrical and thermal losses from packaging. The wirebonds also have significant parasitic inductance at high frequencies and they are one of the causes of failure. Therefore, several alternative chip-level interconnect technologies have been developed to eliminate the bonding wires.

#### B. Deposited metallization

One of the wirebond-free interconnect technologies is the metal deposition method. In this method, device interconnections are constructed with metals (usually copper) that are deposited directly on the device electrodes. The deposited metals form power and signal linkages from power chips to the rest of the circuit. The metal deposition covers both physical (sputter and e-beam) and chemical (electroplating and electroless-plating) ways. Since metal deposition could be processed in parallel, the technology has advantages in making multichip power modules. Representative packaging schemes using deposited metallization include General Electric's (GE's) power overlay (POL) [2] and the embedded power developed in the Center for Power Electronics Systems (CPES) [3].

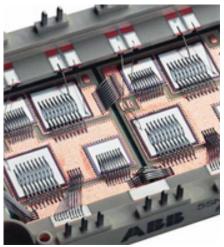

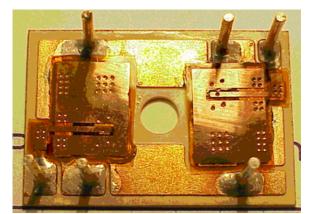

The POL technology proposed by GE eliminated wirebonds through the use of metallized copper via holes in a polyimide film. As shown in Figure 1.3, POL has a multilayer structure, which includes power semiconductor devices soldered to a DBC substrate from the backside, the polyimide dielectric layer, and the deposited copper on the topside. Differences in device thickness are compensated by copper-tungsten or molybdenum shims.

The fabrication process of GE's POL power module starts with laser-drilling or mechanical punching of via-holes in a polyimide film. Power devices are then attached to the bottom side of the polyimide film using a special adhesive with the device electrodes accurately aligned with the via-holes. Next, topside of the whole assembly is metallized with titanium, nickel and copper using sputtering and electroplating process. The sputtering of titanium, nickel and copper is similar to the under bump metallization (UBM) schemes used in the IC packaging. Proper circuit patterns are then formed through wet-etching of the deposited metal layers. After cleaning, the devices along with the left copper/polyimide layers are solder-attached to an etched DBC substrate. A final step of silicone gel-filling is needed to protect devices from moisture. Figure 1.4 is a top view of a prototype POL converter module fabricated in CPES at Virginia Tech. Because the process can be realized by fine resolution photolithography, the POL interconnect technology is capable of achieving high density interconnections with via-hole diameter down to 0.25 mm (10 mil).

Figure 1.4. A prototype of power module packaged using power overlay interconnect technology.

Another interconnect strategy using the metal deposition method is called embedded power [3]. Different from the POL, which uses the polyimide films, the embedded power applies ceramic substrates and screen-printed dielectric materials. Figure 1.5 shows a cross-sectional schematic of an embedded power module. There are three major parts in the structure: the control circuit on the top, the embedded power stage in the middle, and the base substrates at the bottom. The core element in the structure is the embedded power stage constructed by the laser-cut ceramic frames, the inserted power chips, the dielectric fillings and the deposited metallization layers.

Figure 1.5. Cross-sectional schematic of embedded power module [3].

Figure 1.6. An IPEM packaged by the embedded power technology [3].

The metal deposition process in embedded power is similar to GE's POL. Figure 1.6 shows an integrated power electronics module (IPEM) packaged by the embedded power interconnect technology.

Generally speaking, the electrical performance and efficiency of a deposited metallization power module are significantly improved compared to a wirebond power module mainly due to the reduction of packaging inductance.

#### C. Solder interconnections

Solder interconnection is another effective strategy to get rid of wirebonds. Actually either in a wirebond or in a deposited metallization (both POL and embedded power) power package, solder reflow is already used for attaching power chips onto metallized substrates. In some other power packages, solder is not only used for the dieattachment, but also used for the interconnections of the top electrodes (gate and source) of the power chips. These technologies are usually referred to solder interconnections. The origin of solder interconnections dates back to the early 1960s, which is known as the IBM's controlled collapse chip connection (C4) technology [4]. In recent years, there was a continuous progress to apply more solder interconnections in power electronics. Follows we introduce several power packaging concepts that utilize solder interconnections.

Vishay Siliconix has developed a PowerConnect technology to replace the traditional wirebonds with direct interconnections between the die and the copper leadframe, as shown in Figure 1.7 [5]. To accomplish the solder interconnections, the top surface of the power MOSFET was made solderable by developing a nickel-based metallization on top of the aluminum pads. The leadframe can be attached to both the bottom and top surfaces of the die. It is reported that the resistance contribution by the interconnections has been cut down to less than 1 m $\Omega$ , thereby doubling the current capability of the low-voltage MOSFET in an SO-8 package. The power dissipation has also been enhanced. However, reliability is a big concern in the PowerConnect structure because of the coefficient of thermal expansion (CTE) mismatch between the large-area copper leadframe and the silicon die.

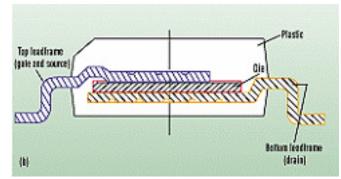

To mitigate the reliability concerns due to the large-area interconnections between CTE mismatched copper and silicon, Fairchild Semiconductor developed a SO-8 wireless package [6] use solder bumps to reduce the interconnect resistance and improve heat transfer. The package outline is the same as the conventional SO-8 package as shown in Figure 1.8. The majority of heat is still conducted through the bottom drain leadframe while the solder bumps can also be served a heat path.

Figure 1.7. Cross-sectional schematic of a PowerConnect chip-level power package [5].

Figure 1.8. Cross-sectional view of a SO-8 Wireless chip-level power package [6].

Wireless versions of the SO packages reduce the package resistance but do not significantly improve the thermal performance. Fairchild Semiconductor's Bottomless package as shown in Figure 1.9 [7] accomplishes both goals simultaneously by eliminating the bottom drain leadframe and allowing the solderable backsides of the MOSFET die to directly contact printed circuit board (PCB) substrates by solder reflow. The top source leadframe keeps the same as in the Wireless and still uses solder bumps for interconnection. As a result, package resistance is further reduced and it can handle 60% more current than the same die in a conventional SO-8 package. It is also reported that the Bottomless reduces the junction-to-case thermal resistance below 1°C/W, which is a dramatic improvement from 25°C/W in a conventional SO-8 package.

Figure 1.9. Chip-level power packages interconnected by SO-8 Bottomless technology [7].

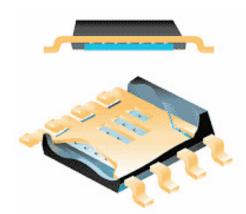

In 1999, Fairchild Semiconductor introduced new low-*R<sub>DS(on)</sub>* power MOSFETs in the form of solder ball grid array (BGA) chip-scale package (CSP) [8]. To overcome the drawbacks in a traditional package, Fairchild Semiconductor encased the low-voltage MOSFET in a fine-pitch BGA for flip-attachment of the CSP onto a PCB substrate using the surface mount technology. Figure 1.10 shows the structure of a BGA power MOSFET package. By allowing direct connection using solder balls, BGA MOSFET eliminates the undesired parasitic contribution from wirebonds or leadframes. Furthermore, BGA MOSFET is only 0.7-mm high and it consumes less than 50% the PCB area for a conventional package. Its unique design and construction allow heat to dissipate directly from the die to the PCB board through the solder balls. As a result, BGA MOSFET offers a 35% reduction in on-resistance over the Wireless SO-8 package and improves heat dissipation over 175% compared with the Wireless SO-8 package.

Figure 1.10. Schematic of Fairchild Semiconductor's BGA MOSFET [8].

In 2000, International Rectifier Corporation (IR) introduced a true CSP called FlipFET, in which all of the terminals are on a single side of the die in the form of solder bumps [9]. Figure 1.11 shows a FlipFET power MOSFET package. FlipFET combines the latest die design and wafer level packaging technology to make 100% silicon-to-

footprint ratio possible. Thus, FlipFET is advantageous for advanced portable power application such as digital cameras, MP3 players and cell phones.

Researchers in CPES have also developed a CSP structure termed as the Die-Dimensional BGA ( $D^2BGA$ ) [10]. Figure 1.12 shows a power MOSFET constructed using the  $D^2BGA$  interconnect technology. The  $D^2BGA$  power devices have been successfully applied in the Flip-Chip on Flex IPEMs as shown in Figure 1.13 and better electrical performance has been achieved than the conventional wirebond power modules[11].

Figure 1.11. IR's FlipFET power MOSFET [9].

Figure 1.12. Die-dimensional BGA power packages developed in CPES [10].

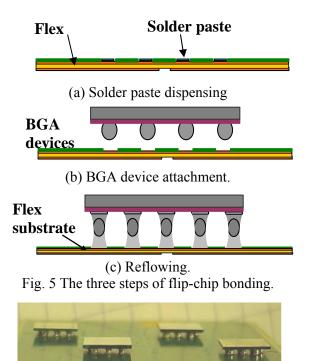

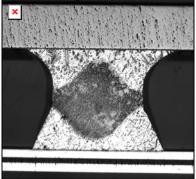

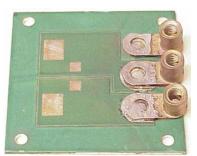

Figure 1.13. A Flip-chip on flex integrated power electronics module (a) and its schematic structure (b) [11].

Other power packaging structures making use of the solder interconnections with some modifications include Harris Semiconductor's ThinPack [12] and CPES' Metal Post Interconnect Parallel Plate Structures (MPIPPS) [13].

#### D. Conductive epoxy interconnections

IR's CopperStrap as shown in Figure 1.14 [14] replaces the wirebonds that connect the source to the leadframe with a solid strap that covers the surface of the die. Different from Vishay Siliconix's PowerConnect, silver-filled conductive epoxy is used to attach the copper straps to aluminum pad surfaces of the power dies. Because the conductive epoxy has a much lower elastic modulus than solder and it serves as a stress buffer layer, thermal stresses caused by the CTE mismatch of the copper strap and silicon is reduced dramatically. However, there is a payment for higher packaging resistance.

Figure 1.14. A chip-level CopperStrap power package [14].

Figure 1.15. IR's DirectFET power package (a) and its cross-sectional schematic (b) [15].

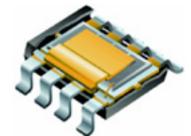

Aiming at reducing footprint size and increasing performance, IR released another interconnect technology called DirectFET [15]. Same as that in the CopperStrap, DirectFET uses conductive epoxy that directly mounts a power device into a copper "can" and applies patterned solderable areas for flip-mounting as shown in Figure 1.15. Combining a proper passivation system, a surface mountable package with ultra-low profile is realized. It has only 1/20 junction-to-case thermal resistance compared with the wirebond SO-8 package. DirectFET is among the first commercial packaging technologies which has the double-sided cooling capability.

#### E. Press pack

Another interesting wirebond-free interconnect technology is the press pack interconnections that was originally developed by Fuji, Toshiba and ABB [16]. The structure has been applied to high power devices such as diodes and gate turnoff

thyristors as shown in Figure 1.16 with proven reliability. Molybdenum is usually applied for less CTE mismatch.

Figure 1.16. Gate turnoff high power devices packaged using the press pack technology [16].

SemiKron International's SkiiPPack [17] is another example using the press pack technology. One of the disadvantages of the interconnect technology is its expensive manufacturing cost involved with precise machining and planarization. Therefore, the press pack technology is only proposed for extremely high power packages so far.

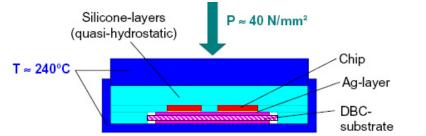

#### F. Pressure-assisted silver sintering

Silver paste sintering has been widely used in microelectronic packages due to the high electrical and thermal performance of silver [18-20]. However, the paste containing microscale silver powders requires high sintering temperatures (>500°C) that are beyond what semiconductor devices can withstand. Studies [21 - 24] showed that the application of external pressure can lower the sintering temperature of silver pastes. Figure 1.17 shows schematically one of the setups for low-temperature sintering of microscale silver paste with the assistance of external pressures. Compared with the solder reflow interconnection, pressure-assisted silver sintering has the advantages such as more environmental friendly due to the lead (Pb)-free materials, more uniform interconnecting layers, better electrical and thermal performance, and higher reliability. However, similar to the press pack, the application of external pressure tends to complicate the manufacturing process and thus increases the cost.

Other technologies are also being tried to lower the processing temperatures of the silver joints but they are still not fully developed [25].

Figure 1.17. Schematic of a pressure-assisted silver paste sintering setup [26].

#### 1.1.2 Summary of Current Chip-Level Interconnect Technologies

In power electronic packaging, it is unlikely to come out a universal chip-level interconnect technology that can cover all the applications from the low-power levels to the extremely high-power levels. Each interconnect technology has pros and cons as summarized in Table 1.1. Therefore, various types of power packages are found in nowadays power electronic market.

| Interconnect                              | Interconnect                                                   | Advantages                                                                                              | Disadvantages                                                                                                        | Application                                                                          |

|-------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| technologies                              | materials                                                      |                                                                                                         |                                                                                                                      | examples                                                                             |

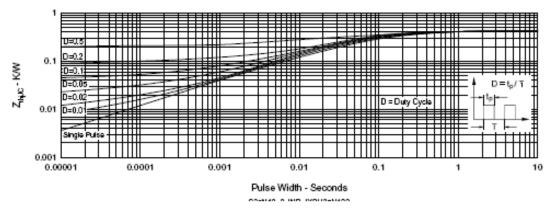

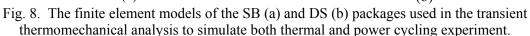

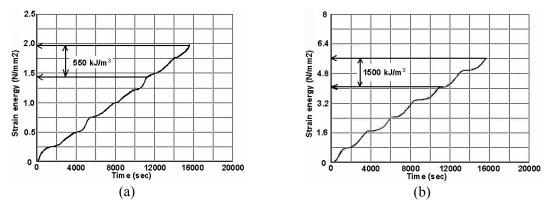

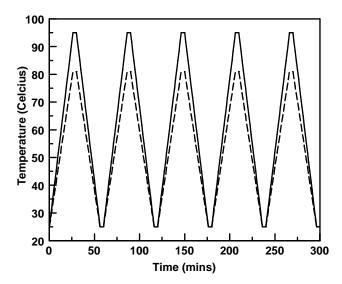

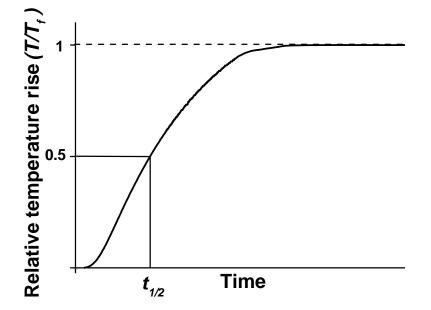

| Wirebond                                  | Pure Al wire<br>or Al wire with<br>1% silicon or<br>Au wire    | High flexibility;<br>Low cost;<br>Improved reliability                                                  | Large packaging<br>parasitics;<br>Poor thermal<br>management;<br>Hard for integration                                | Still dominant power<br>packaging<br>technology                                      |