# DOUBLE-SIDED LIQUID COOLING FOR POWER SEMICONDUCTOR DEVICES USING EMBEDDED POWER TECHNOLOGY

Bryan Charles Charboneau

Thesis submitted to the faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirement for the degree of

# MASTER OF SCIENCE

In Electrical Engineering

APPROVED:

Dushan Boroyevich, Chairman

Fred Wang

Daan van Wyk

Elaine P. Scott

July 22, 2005

Blacksburg, Virginia

Keywords: Double-sided cooling, semiconductor packaging, liquid convection

Copyright 2005, Bryan C. Charboneau

# DOUBLE-SIDED LIQUID COOLING FOR POWER SEMICONDUCTOR DEVICES USING EMBEDDED POWER TECHNOLOGY

Bryan Charles Charboneau

#### **ABSTRACT**

Power electronics is a constantly growing and demanding technical field. Consumer demand and developing technologies have made the improvement of power density a primary emphasis of research for this area. Power semiconductors present some of the major challenges for increasing system level power density due to high loss density and interconnection requirements. Advanced cooling schemes, such as double-sided, forced liquid convection or multi-phase flow, can be implemented with non-wire bond packaging to improve thermal management while maintaining proper electrical performance. Embedded power is one such packaging technology, which provides a compact structure for interface of power semiconductor to fluid flow.

The objective of this work was to identify the potential of implementing embedded power packaging with double-sided forced liquid convection. Physics based, electro-thermal models were first used to predict the improvement in heat transfer of double-sided, forced liquid convection with embedded power packaging over single-sided liquid cooled wire bond based packaging. A liquid module test bed was designed and constructed based on the electro-thermal models, which could be interfaced with high power MOSFET based samples implementing various packaging technologies. Experiments were used to verify the model predictions and identify practical limitations of high flow rate, double-sided liquid cooling with embedded power. An improvement of 45% to 60% in total junction to case thermal resistance is shown for embedded power packaging with double-sided liquid cooling for water flow rates between 0.25 and 4.5 gal/min.

#### **ACKNOWLEDGEMENTS**

I would like to express my appreciation for my advisor, Dr. Dushan Boroyevich. Dr. Boroyevich introduced me to the exciting and challenging field of power electronics, which has been stimulating and extremely rewarding for me to research. I would like thank him for giving me the opportunity to perform research as a member of CPES and allowing me to aggressively explore the multidisciplinary aspects of power electronics. Dr. Boroyevich has allowed me to gain invaluable experience in electronics and research techniques, while helping me find areas where I may improve upon myself.

I would like to thank my other committee members, Dr. Fred Wang, Dr. Daan van Wyk, and Dr. Elaine P. Scott. Dr. Wang has provided me with essential guidance for my research while challenging me to find my limits of thought and the limits of the technology I studied. I would also like to thank Dr. Wang for his willingness to discuss project/thesis related issues on a moments notice. I wish to thank Dr. van Wyk for his support in the development and execution of my thesis topic. Dr. van Wyk has provided me strong technical advice while challenging me to look at the fundamentals of my research. I would like to thank Dr. Scott for her guidance in mechanical design and thermal modeling for my research topic. Dr. Scott also provided essential advice for writing and editing this thesis.

I extremely grateful for the advice and assistance provided by Dr. Dushan Boroyevich, Dr. Fred Wang, Dr. Elaine P. Scott, Dr. Daan van Wyk, and Dr. Fred C. Lee, which has helped me choose a place to continue research and my education, University of Maryland, College Park.

I would like to thank Dr. Zhenxian Liang for his guidance, which helped me understand various packaging techniques and perform proper lab procedures. I would also like to thank Dr. Xu Yang, who helped motivate me in the final stages of my research and provide me with the confidence to do so. Dr. Xu Yang has provided essential support while being a close colleague.

I would like to express my appreciation to Bob Martin, Dan Huff, Trish Rose, Teresa Shaw, Elizabeth Tranter, Marianne Hawthorne, Linda Gallagher, and all of the other CPES staff for the assistance on a daily basis.

I am very lucky and grateful to have worked on the Army Research Laboratory (ARL) team. I would like to thank the student members Wei Shen, Xigen Zhou, Dianbo Fu, Qian Liu, Hongfang Wang, Yonghan Kang, Ning Zhu, and Lingyin Zhao. Each team member has provided assistance and guidance to me during my study in CPES and has become a good friend to me. I would like to thank the ARL managers/advisors Wesley C. Tipton, Damian Urciuoli, and Bruce Geil for their guidance and support. I also thank Jonathan Dodge of Advanced Power Technology, Inc. and Tony Mendoza of Accumet Engineering Corporation for their input in relation to my research.

I would like to thank my friends and colleagues at CPES, Jian Yin, Rengang Chen, Ying-Feng Pang, Arthur Ball, Andy Schmit, Luis Arnedo, Callaway Cass, Jerry Francis, Bing Lu, Brooks Mann, Anish Prasai, Bass Sock and Doug Sterk for their friendship and assistance while in CPES. I would like express great appreciation to my close friends in CPES, Daniel Ghizoni and Tim Thacker.

Most importantly, I would like to thank my parents for everything they have done for me. They have provided me with constant and loving support, which is at the root of all of my decisions. I would like to thank my roommates, Andrew C. Baisden and Chad D. Hudson, for their friendship and support throughout my graduate study.

This work was made possible by Army Research Laboratory grant DAAD19-03-2-0008 and the National Science Foundation.

"This work made use of Engineering Research Center Shared Facilities supported by the National Science Foundation under NSF Award Number EEC-9731677." "Any opinions, findings, and conclusions or recommendations expressed in this material are those of the author(s) and do not necessarily reflect those of the National Science Foundation."

# TABLE OF CONTENTS

| ABSTRACT                                                           | ii   |

|--------------------------------------------------------------------|------|

| ACKNOWLEDGEMENTS                                                   | iii  |

| TABLE OF CONTENTS                                                  | v    |

| LIST OF FIGURES                                                    | viii |

| LIST OF TABLES                                                     | xii  |

| 1 INTRODUCTION                                                     | 1    |

| 1.1 Motivation for Improved Power Semiconductor Thermal Management | t 1  |

| 1.2 Cooling Schemes Review                                         | 1    |

| 1.3 Power Semiconductor Thermal Management Survey                  | 3    |

| 1.3.1 Wire Bond Packaging and Cooling                              | 3    |

| 1.3.2 Non-Wire Bond Packaging and Cooling                          | 7    |

| 1.4 Embedded Power Technology with Forced Liquid Convection        | 13   |

| 1.5 Objectives                                                     | 14   |

| 2 THERMAL MODELING                                                 | 15   |

| 2.1 Physics Based Electro-Thermal Modeling Background              | 15   |

| 2.1.1 Conduction Heat Transfer Modeling                            | 16   |

| 2.1.2 Convection Heat Transfer Modeling                            | 17   |

| 2.2 Package Structure and Thermal Models                           | 18   |

| 2.2.1 Embedded Power Package                                       | 18   |

| 2.2.2 Wire Bond Package                                            | 24   |

| 2.3 Thermal Modeling Results                                       | 26   |

| 2.4 Thermal Modeling Summary                                       | 28   |

| 3 | EXI    | PERIMENTAL VERIFICATION                                              | . 29 |

|---|--------|----------------------------------------------------------------------|------|

|   | 3.1    | Liquid Module Test Bed                                               | . 29 |

|   | 3.2    | MOSFET for Experimental Verification                                 | . 31 |

|   | 3.3    | Embedded Power Package                                               | . 33 |

|   | 3.3.   | I Embedded Power Package Design                                      | . 33 |

|   | 3.3    | 2 Embedded Power Package Construction                                | . 33 |

|   | 3.4    | Wire Bond Package                                                    | . 47 |

|   | 3.4.   | 1 Wire Bond Package Design                                           | . 47 |

|   | 3.4.   | 2 Wire Bond Package Construction                                     | . 47 |

|   | 3.5    | Experimental Setup.                                                  | . 49 |

|   | 3.6    | Liquid Module and Sample Design Test                                 | . 52 |

|   | 3.7    | Experimental Results                                                 | . 54 |

|   | 3.7.   | I Experimental Results and Analysis                                  | . 54 |

|   | 3.7    | 2 Comparison of Thermal Modeling Predictions to Experimental Results | . 58 |

| 4 | CO     | NCLUSIONS AND FUTURE RESEARCH                                        | . 70 |

|   | 4.1    | Conclusions                                                          | . 70 |

|   | 4.2    | Direction of Future Research                                         | . 71 |

| A | ppendi | ix A Liquid Module Autocad Drawings                                  | . 73 |

| A | ppendi | ix B Embedded Power Package Autocad Drawings                         | . 75 |

| A | ppendi | ix C Embedded Power Package Construction Outline                     | . 77 |

| A | ppendi | ix D Wire Bond Package Autocad Drawings                              | . 80 |

| A | ppendi | ix E Wire Bond Package Construction Outline                          | . 81 |

| R | EFERI  | ENCES                                                                | . 82 |

| Bryan Charboneau | TABLE OF CONTENTS |

|------------------|-------------------|

|                  |                   |

|                  | o-                |

| VITA             | 85                |

Bryan Charboneau LIST OF FIGURES

# LIST OF FIGURES

| Figure 1.1  | Heat transfer coefficient for various heat transfer methods and cooling fluids              | . 2 |

|-------------|---------------------------------------------------------------------------------------------|-----|

| Figure 1.2  | Cross section of typical wire bond package                                                  | . 4 |

| Figure 1.3  | Conceptual drawing of an integrated liquid cooling in a high power MOSFET module            | . 5 |

| Figure 1.4  | Conceptual drawing of an IGBT and integrated micro structure for single- and two-phase      |     |

| cooli       | ing                                                                                         | . 6 |

| Figure 1.5  | Structure of an air micro jet array for a power MOSFET                                      | . 7 |

| Figure 1.6  | Cross section of power semiconductors connected to DBC using low temperature joining        |     |

| techr       | niques (microstructures were formed between DBC pieces to create cooling fluid channels)    | . 8 |

| Figure 1.7  | Cross section of a double-sided micro channel package for IGBTs using flip chip             |     |

| inter       | connection                                                                                  | . 9 |

| Figure 1.8  | Cross section of a DirectFET <sup>TM</sup> device                                           | 10  |

| Figure 1.9  | Cross section of a press pack semiconductor package with double-sided multiphase cooling    |     |

| chan        | nels                                                                                        | 10  |

| Figure 1.10 | O Cross section of embedded power with double-sided air cooling                             | 11  |

| Figure 1.1  | 1. Power factor correction (PFC) integrated power electronics module using embedded power   |     |

| techr       | nology with a CoolMos <sup>TM</sup> and SiC schottky diodes                                 | 13  |

| Figure 1.12 | 2 Cross section of typical embedded power technology structure with proposed double-sided   |     |

| liqui       | d cooling                                                                                   | 14  |

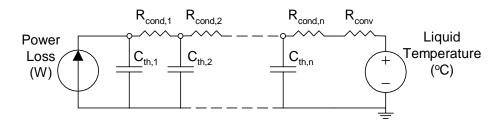

| Figure 2.1  | Cauer RC electro-thermal simulation circuit example                                         | 16  |

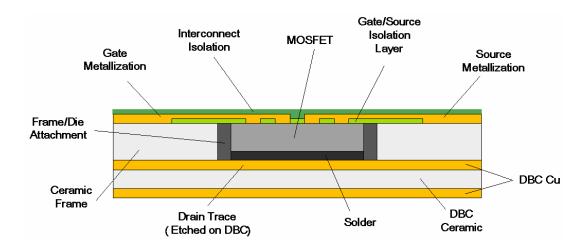

| Figure 2.2  | Cross section of embedded power technology with DBC base                                    | 19  |

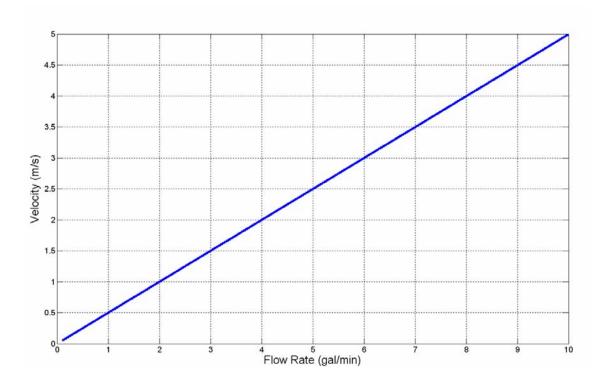

| Figure 2.3  | Fluid velocity, $u_m$ versus flow rate, $F$                                                 | 21  |

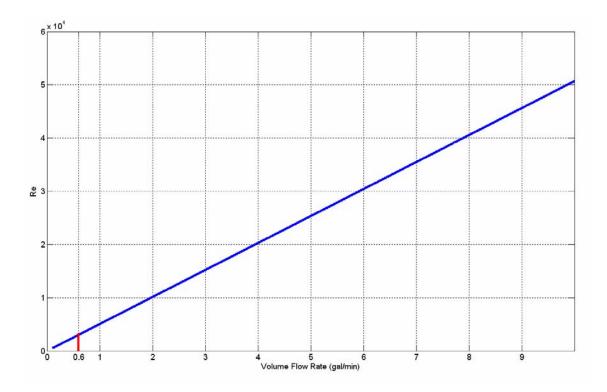

| Figure 2.4  | Reynolds number, Re <sub>D</sub> versus flow rate, F                                        | 21  |

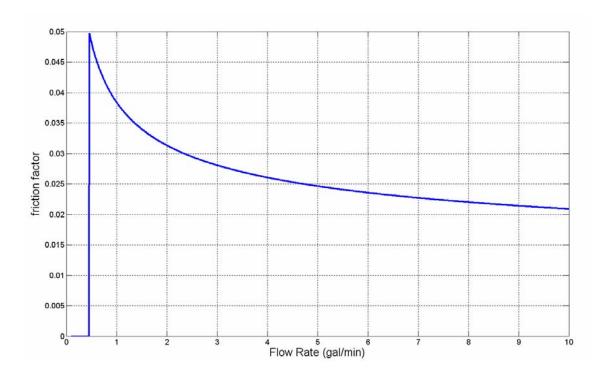

| Figure 2.5  | Friction factor, f versus flow rate, F                                                      | 22  |

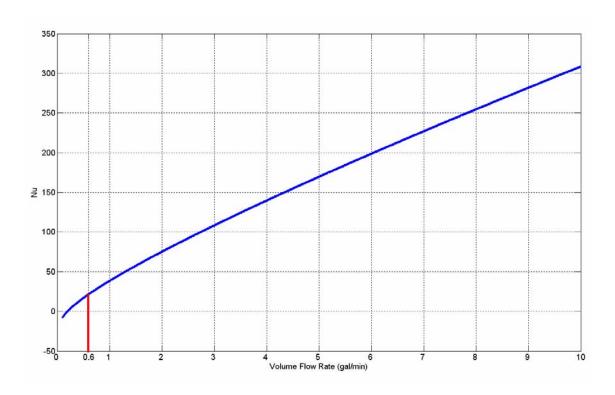

| Figure 2.6  | Nusselt number, Nu <sub>D</sub> versus flow rate, F                                         | 22  |

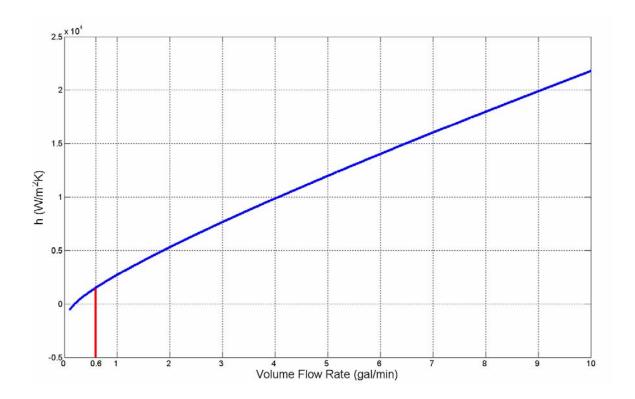

| Figure 2.7  | Convection heat transfer coefficient, h versus flow rate, F                                 | 23  |

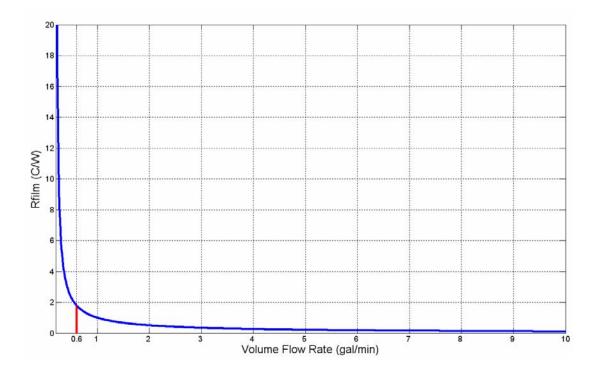

| Figure 2.8  | Convection thermal resistance, $R_{convection}$ versus flow rate, $F$                       | 23  |

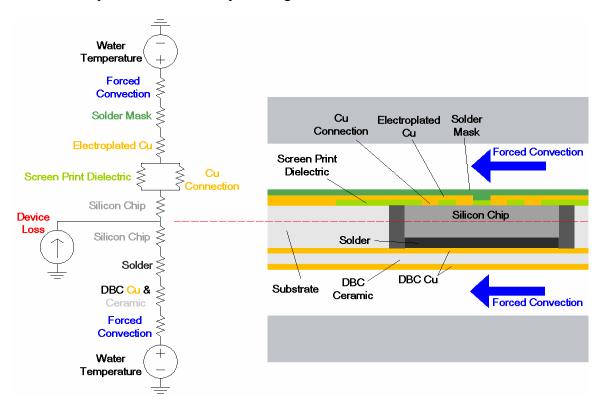

| Figure 2.9. | Thermal model for embedded power with double-sided forced liquid convection                 | 24  |

| Figure 2.10 | O Cross section of wire bond package with single-sided liquid cooling                       | 25  |

| Figure 2.1  | 1 Thermal model for a wire bond package with single-sided forced liquid convection          | 26  |

| Figure 2.12 | 2 Comparison of conduction and convection thermal resistances found from thermal modeling   | 27  |

| Figure 2.13 | 3 Predicted total junction to case thermal resistance comparison for double-side cooled     |     |

| embe        | edded power packaging and single-side cooled wire bond packaging versus flow rate           | 27  |

| Figure 2.14 | 4 Predicted percentage improvement provided by double-sided cooling over single-sided cooli | ng  |

|             |                                                                                             | 28  |

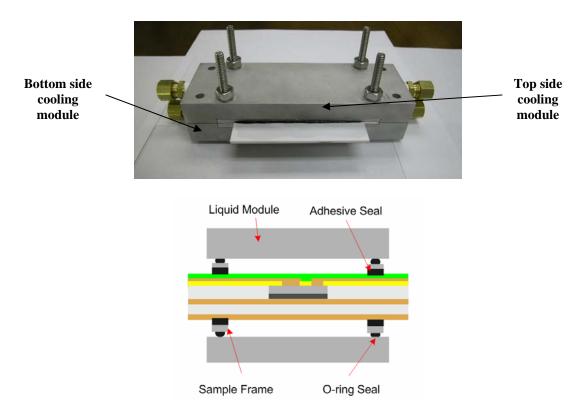

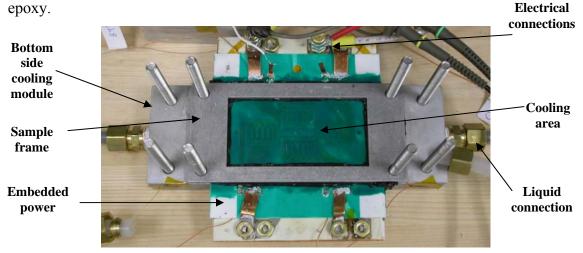

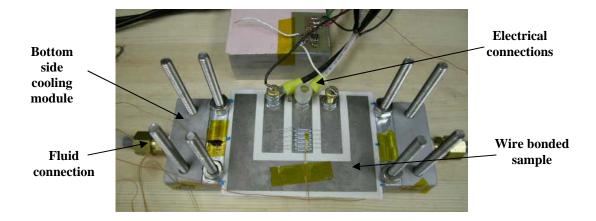

| Figure 3.1  | Liquid module test hed and sample frame                                                     | 30  |

Bryan Charboneau LIST OF FIGURES

| Figure 3.2  | Liquid module in single-side cooling test configuration                                       | . 31 |

|-------------|-----------------------------------------------------------------------------------------------|------|

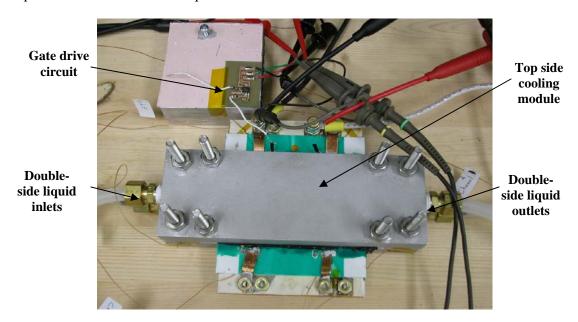

| Figure 3.3  | Picture and cross section of liquid module test bed in double-side cooling test configuration | . 31 |

| Figure 3.4  | APT APT60M75DFLL FREDFET device                                                               | . 32 |

| Figure 3.5  | Uncut and laser cut alumina substrate for semiconductor die placement                         | . 34 |

| Figure 3.6  | Top and bottom views of die attachment to alumina substrate carrier                           | . 35 |

| Figure 3.7  | Screen printed dielectric layer over top of MOSFET chips                                      | . 36 |

| Figure 3.8  | Solder mask layer for sputtering and photolithography transparency                            | . 36 |

| Figure 3.9  | Physical vapor deposited (PVD) thin film titanium and copper for electrical interconnects     | . 37 |

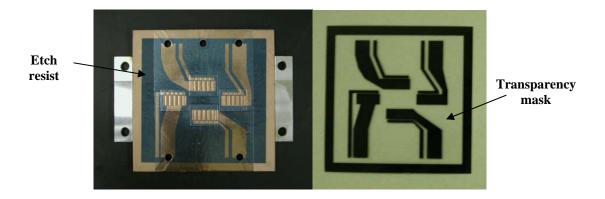

| Figure 3.10 | Photo mask for copper electroplating and photolithography transparency                        | . 38 |

| Figure 3.11 | Copper electroplate frame, top and bottom views of sample in electroplate frame, and          |      |

| electro     | oplating station                                                                              | . 39 |

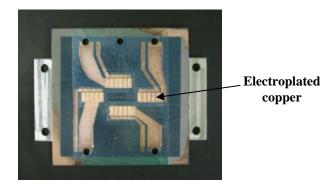

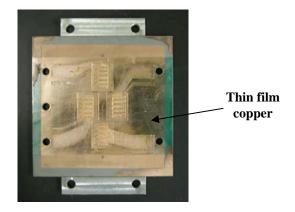

| Figure 3.12 | Embedded power sample after copper electroplating                                             | . 39 |

| Figure 3.13 | Embedded power sample before PVD thin film copper etch                                        | . 40 |

| Figure 3.14 | Embedded power sample after PVD thin film copper etch                                         | . 40 |

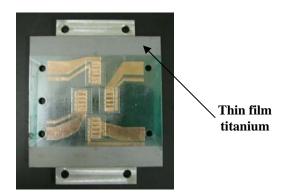

| Figure 3.15 | Embedded power structure after PVD thin film titanium etch                                    | . 41 |

| Figure 3.16 | DBC and photo masked pattern on DBC                                                           | . 42 |

| Figure 3.17 | Drain pattern on DBC and DBC base with thermocouples                                          | . 42 |

| Figure 3.18 | Bottom side of chips showing MOSFET drain, solder paste, and copper shim; Solder paste of     | on   |

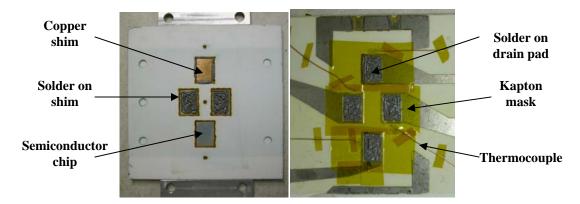

| DBC         | drain pads                                                                                    | . 43 |

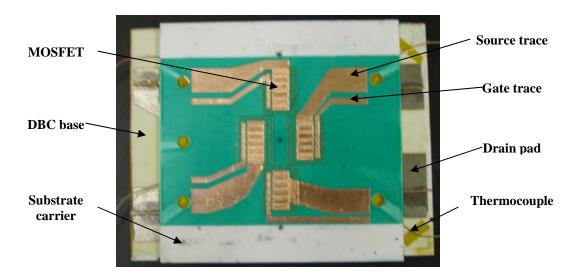

| Figure 3.19 | DBC based embedded power package with thermocouples                                           | . 43 |

| Figure 3.20 | Attachment of electrical connectors via solder paste and hot plate                            | . 44 |

| Figure 3.21 | Solder mask insulation for top side of embedded power sample                                  | . 44 |

| Figure 3.22 | Completed embedded power sample attached to sample frames via silicone adhesive               | . 45 |

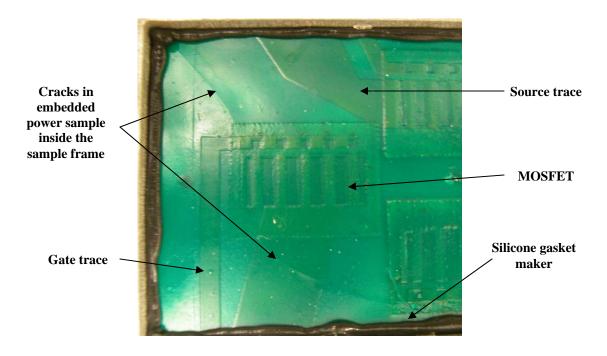

| Figure 3.23 | Cracked embedded power sample from a lack of support under the sample frames                  | . 46 |

| Figure 3.24 | Embedded power sample connected to liquid module for double-sided cooling test                | . 46 |

| Figure 3.25 | MOSFET based wire bond package with thermocouples attached to sample frame via silicon        | ne   |

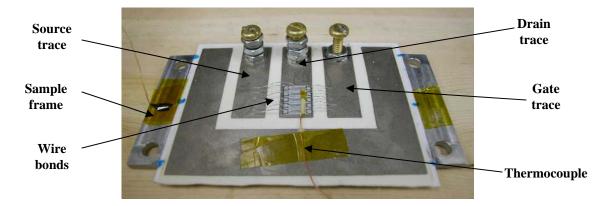

| adhes       | ive                                                                                           | . 48 |

| Figure 3.26 | Wire bond package connected to liquid module for single-sided testing                         | . 48 |

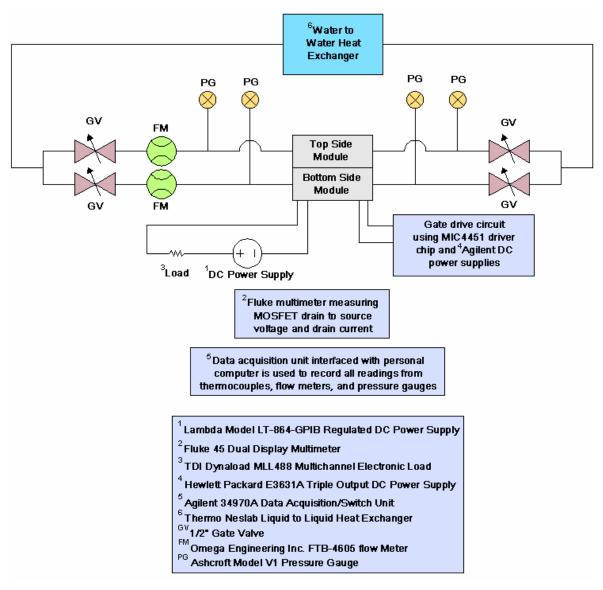

| Figure 3.27 | Test configuration schematic                                                                  | . 49 |

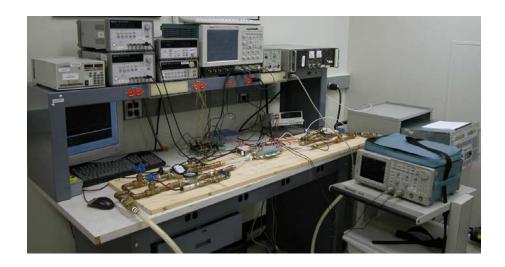

| Figure 3.28 | Picture of test bench                                                                         | . 50 |

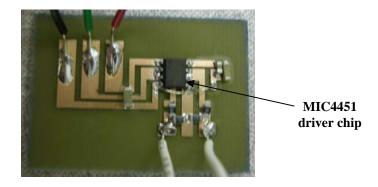

| Figure 3.29 | Picture of MIC4452 MOSFET driver circuit                                                      | . 51 |

| Figure 3.30 | Fluid measurement and control system                                                          | . 51 |

| Figure 3.31 | O-ring test configuration via clear lexan plastic.                                            | . 52 |

| Figure 3.32 | Sample frame adhesive test configuration using Master Bond EP3AOHT                            | . 53 |

| Figure 3.33 | Failed frame adhesion with Master Bond EP3AOHT after initial pressure test                    | . 53 |

| Figure 3.34 | Mega Black O.E.M. high temperature silicone gasket maker test sample                          | . 53 |

| Figure 3.35 | Pressure drop analysis for the liquid module test bed: pressure versus fluid flow rate        | . 54 |

Bryan Charboneau LIST OF FIGURES

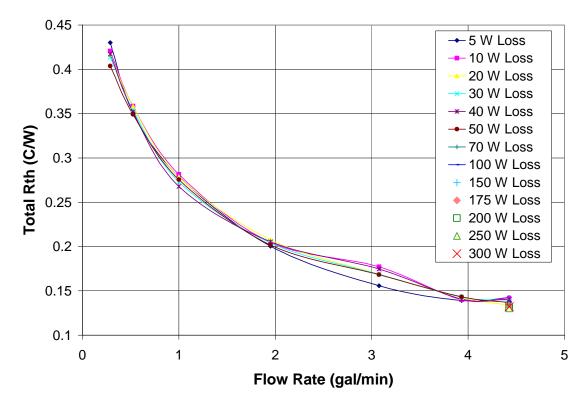

| Figure 3.36 Junction to case (total) thermal resistance versus flow rate for the wire bond pack      | kage with       |

|------------------------------------------------------------------------------------------------------|-----------------|

| single-side forced liquid convection and various device power loss                                   | •               |

| Figure 3.37 Junction to case (total) thermal resistance versus flow rate for the embedded pow        |                 |

| with double-side forced liquid convection and various device power loss                              |                 |

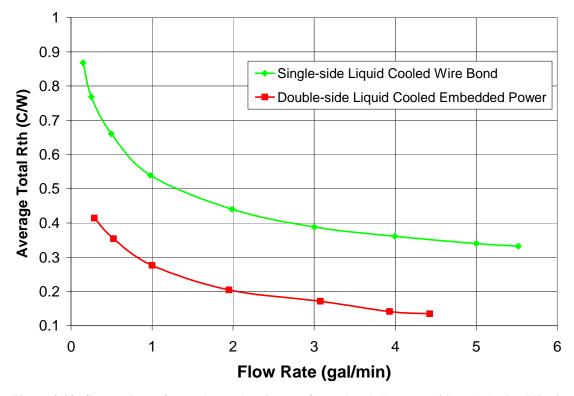

| Figure 3.38 Comparison of total thermal resistance for embedded power with double-sided li           | quid cooling    |

| and a wire bond package with single-sided liquid cooling ( $R_{thavg}$ from average of $R_{th}$ from | om different    |

| loss)                                                                                                |                 |

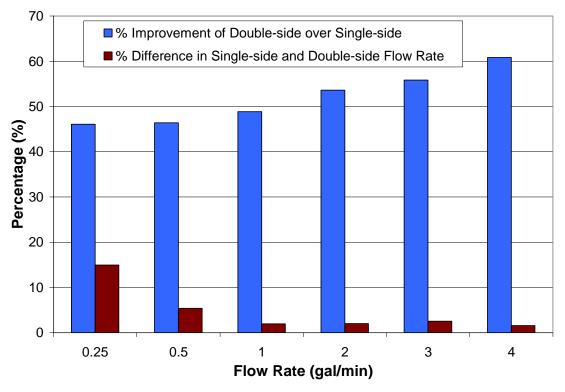

| Figure 3.39 Percentage improvement in thermal resistance from double-side cooled embedde             | ed power over   |

| single-side cooling and percentage difference of measured flow rates                                 | 57              |

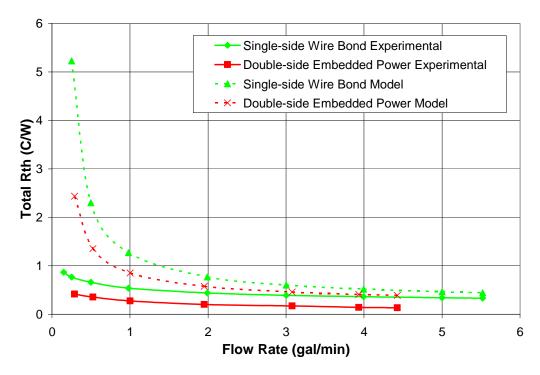

| Figure 3.40 Junction to case (total) thermal resistance comparison of electro-thermal models         | to average      |

| experimental results                                                                                 | 58              |

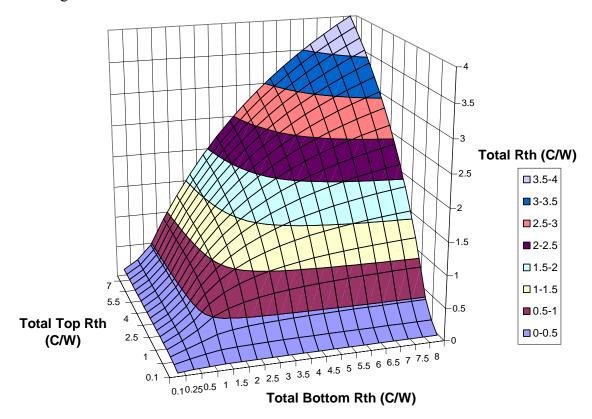

| Figure 3.41 Total package thermal resistance vs. total top thermal resistance vs. total bottom       | thermal         |

| resistance                                                                                           | 59              |

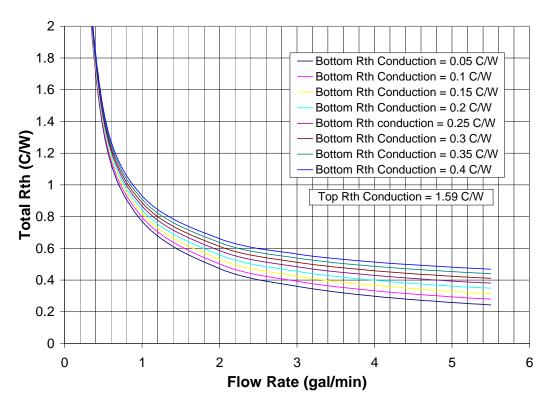

| Figure 3.42 Total package thermal resistance vs. flow rate for various bottom side conduction        | n thermal       |

| resistance values.                                                                                   | 60              |

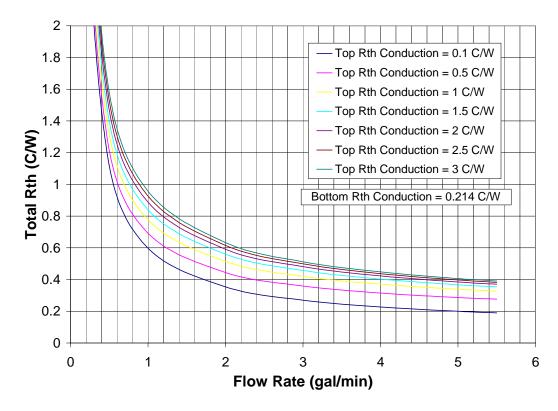

| Figure 3.43 Total package thermal resistance vs. flow rate for various top side conduction the       | ermal           |

| resistance values                                                                                    | 61              |

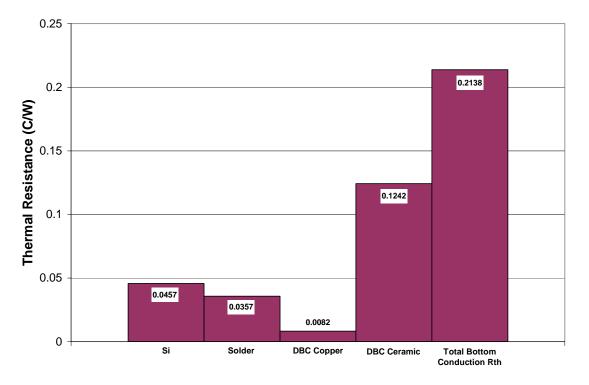

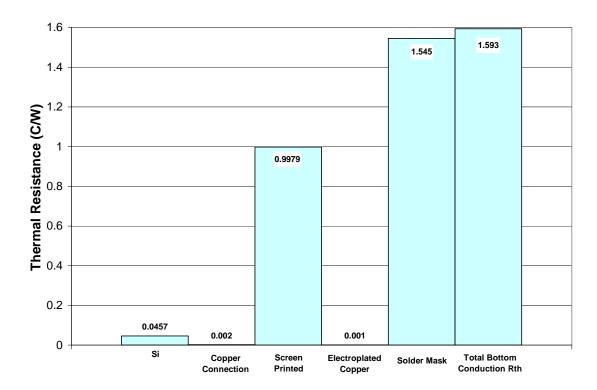

| Figure 3.44 Comparison of bottom side conduction thermal resistance components                       | 61              |

| Figure 3.45 Comparison of top side conduction thermal resistance components                          | 62              |

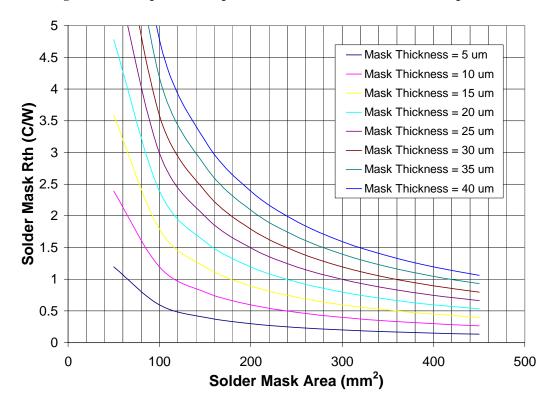

| Figure 3.46 Solder mask thermal resistance vs. solder mask area for various solder mask thic         | knesses 62      |

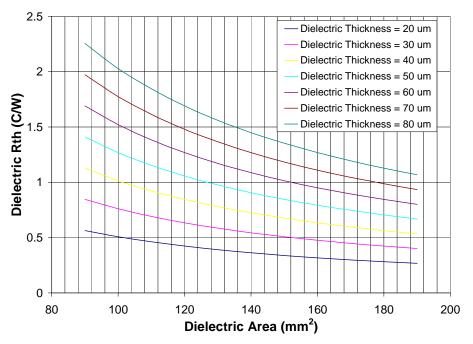

| Figure 3.47 Screen printed dielectric thermal resistance vs. dielectric area for various dielectric  | ric thicknesses |

|                                                                                                      | 63              |

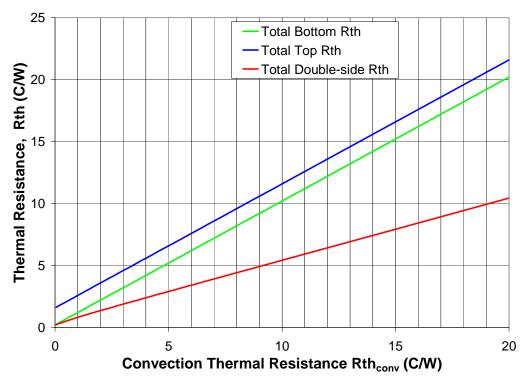

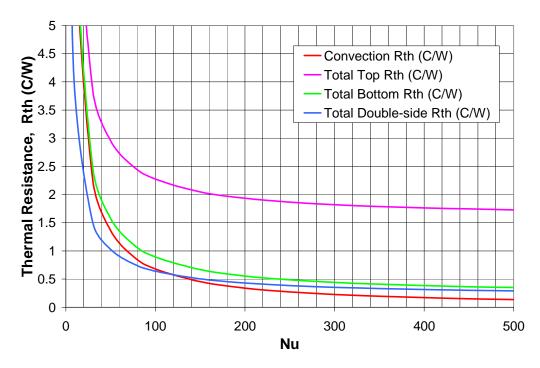

| Figure 3.48 Total top, bottom, and double-side thermal resistance vs. convection thermal resistance  | istance 65      |

| Figure 3.49 Convection, total top, total bottom, and total double-side thermal resistance vs. N      | Jusselt         |

| number, Nu                                                                                           | 65              |

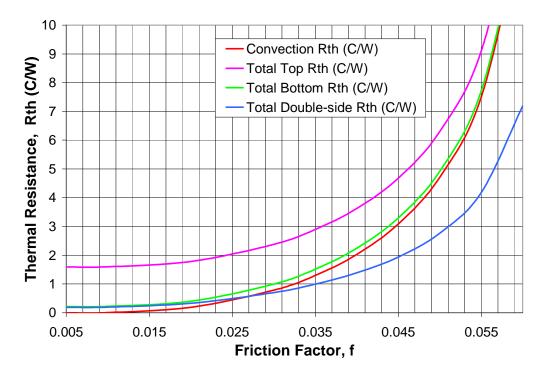

| Figure 3.50 Convection, total top, total bottom, and total double-side thermal resistance vs. fi     | riction factor, |

| f                                                                                                    | 66              |

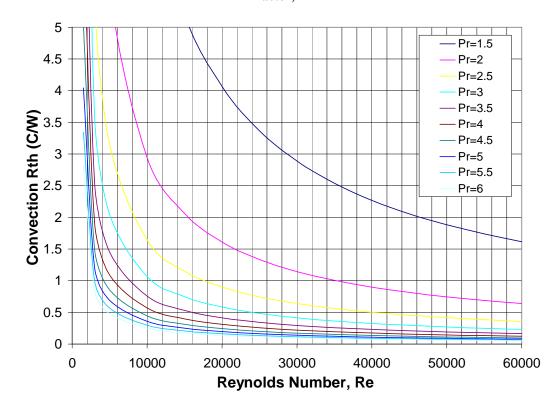

| Figure 3.51 Convection thermal resistance vs. Reynolds number, Re, for various Prandtl num           | nbers, Pr 66    |

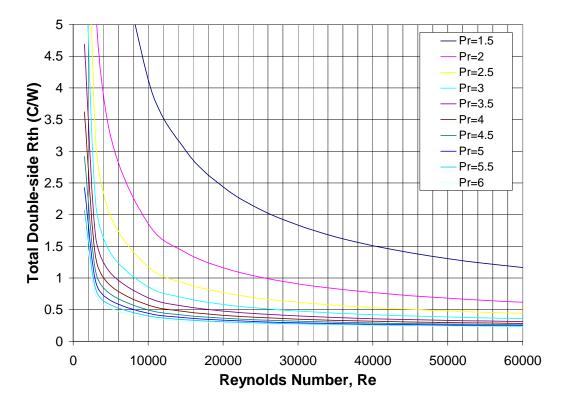

| Figure 3.52 Total package thermal resistance vs. Reynolds number, Re, for various Prandtl n          | umbers, Pr 67   |

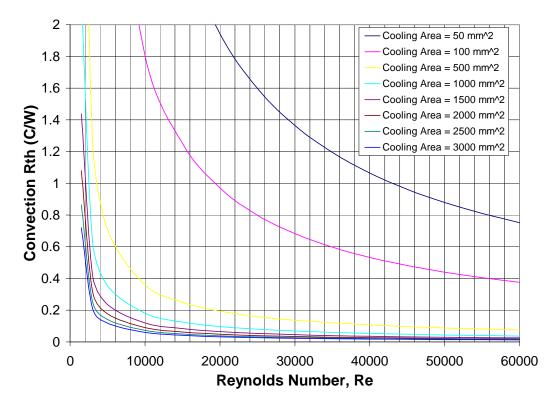

| Figure 3.53 Convection thermal resistance vs. Reynolds number, Re, for various cooling area          | as 68           |

| Figure 3.54 Total package thermal resistance vs. Reynolds number, Re, for various cooling a          | reas 68         |

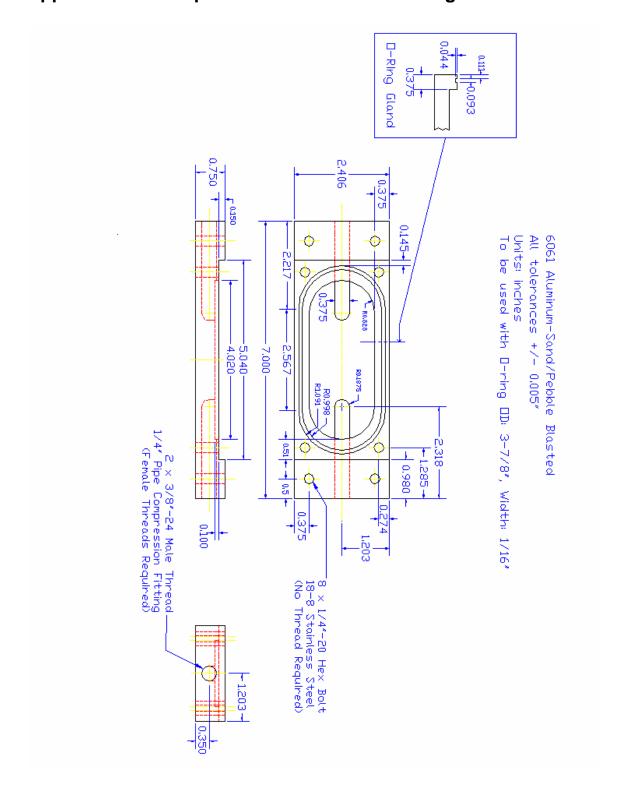

| Figure A.1 Liquid module test bed design                                                             | 73              |

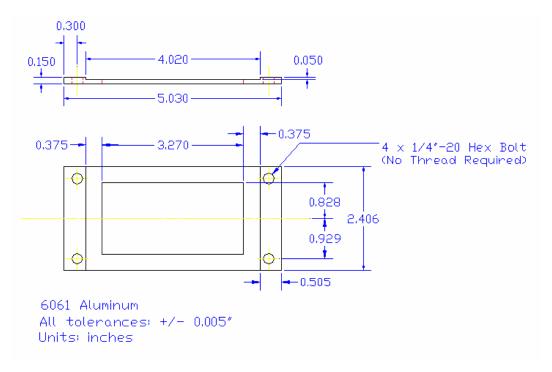

| Figure A.2 Sample frame design                                                                       | 74              |

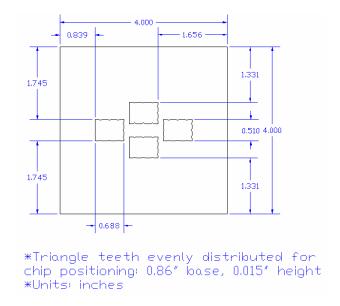

| Figure B.1 Substrate carrier laser cut out pattern for the embedded power package                    | 75              |

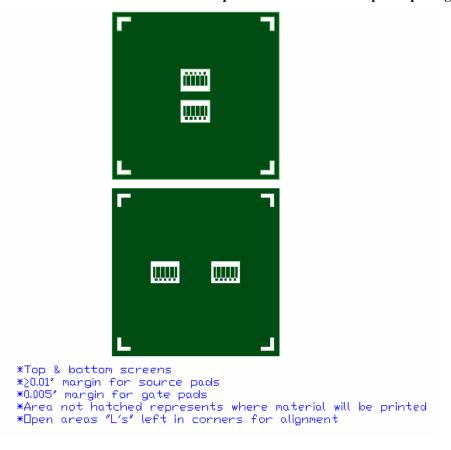

| Figure B.2 Drawing of screen printing dielectric layer design for the embedded power package         | ge 75           |

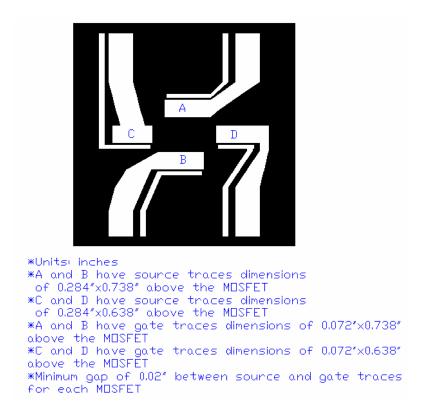

| Figure B.3 Drawing of trace layout design for the embedded power package                             | 76              |

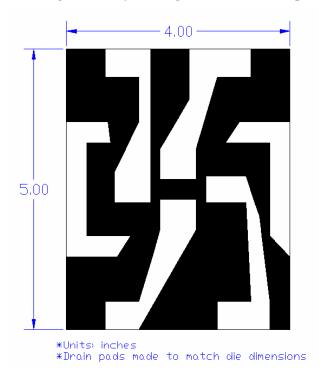

| Figure B.4 DBC drain trace design for the embedded power package                                     | 76              |

| Bryan Charboneau                                  | LIST OF FIGURES |

|---------------------------------------------------|-----------------|

|                                                   |                 |

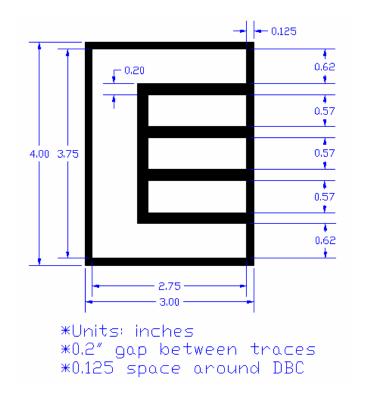

| Figure D.1 DBC trace design for wire bond package | 80              |

Bryan Charboneau LIST OF TABLES

# LIST OF TABLES

| Table 1.1  | Summary of cooling and packaging technologies explored for power semiconductor components | ents |

|------------|-------------------------------------------------------------------------------------------|------|

| and        | systems                                                                                   | 12   |

| Table 2.1  | Thermal resistance values for embedded power technology                                   | 20   |

| Table 2.2. | Thermal and flow properties of water at 25°C.                                             | 20   |

| Table 2.3  | Thermal resistance values for wire bond packaging.                                        | 25   |

| Table 3.1  | APT APT60M75DFLL FREDFET key parameters                                                   | 32   |

# 1 INTRODUCTION

## 1.1 Motivation for Improved Power Semiconductor Thermal Management

Semiconductor based power converters are essential for efficient power delivery and use for countless applications in the world. Technology, specifically related to electronics, has advanced rapidly in recent decades and consumer requirements for electronic systems have become more and more demanding. These developments have sparked the need for higher efficiency and higher power density power converters. As the power density requirements grow for power conversion system, effective thermal management design for power electronic components becomes more critical [1].

High power density packaging of power semiconductor devices presents some of the greatest thermal design challenges. Power semiconductor devices typically have the greatest quantity of power loss in a power conversion system [1]. This issue is made even more complicated since semiconductors have a limited amount of surface area to interface with heat removal systems. Electrical interconnection requirements complicate this matter twofold. Advanced cooling techniques involving forced liquid convection or phase change can help meet loss density requirements for current and future semiconductor devices [2]. These advanced cooling techniques can improve power density greatly if they can be interfaced properly with the semiconductor device packaging technology.

# 1.2 Cooling Schemes Review

There are many examples of cooling schemes for semiconductor based systems and individual semiconductor device. These cooling schemes can be placed into four areas of heat transfer including conduction, convection, phase change, and radiation heat transfer [3]. It is important to understand the potential of each heat transfer method and also identify the effectiveness for each in a particular electronics application.

Conduction heat transfer is present in all semiconductor cooling schemes due to electrical and mechanical interconnection requirements for semiconductor chips. Conduction is also considered in thermal management design for heat spreading and

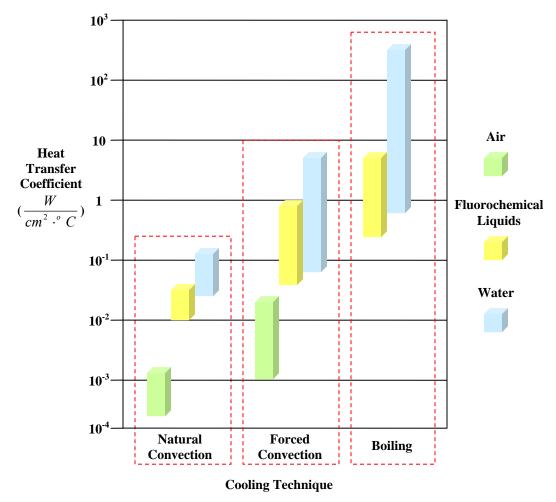

thermal energy storage. Heat transfer via conduction can not be considered alone since thermal energy from power loss is normally exchanged or removed to the environment. This heat removal requires convection, radiation or a combination of these heat transfer methods. Phase change can also be implemented with convection to remove a greater amount of heat. These heat transfer methods are compared approximately in Figure 1.1, which shows the heat transfer coefficient range for various cooling media and schemes [2-3].

Figure 1.1 Heat transfer coefficient for various heat transfer methods and cooling fluids

Figure 1.1 shows the potential of forced liquid convection and phase change heat transfer methods for combating the high loss density of power semiconductor devices. These cooling techniques will provide the lowest temperature rise for high surface heat flux. The interface of these advanced electronics cooling schemes to power

semiconductors should be considered to effectively cool while providing high power density.

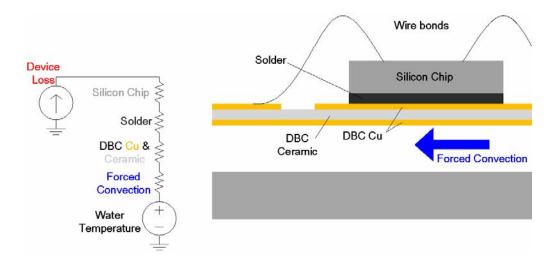

# 1.3 Power Semiconductor Thermal Management Survey

There has been a considerable amount of research on thermal management of power semiconductors. This research includes investigations on advanced cooling for typical power device packaging technology, which uses wire bonds. Most of these studies cover cooling schemes for the non-wire bond side of the device, while a few cover cooling of the top side of the device. Few, if any, sources mention double-sided cooling with wire bond packaging, but this is not impossible. Some research effort has been placed on improved thermal management using non-wire bond packaging technologies. These packaging technologies use flip chip technology or other alternate interconnection methods to replace wire bonds. This allows for easier interface to advanced cooling schemes. This section presents a survey of state of the art advanced cooling schemes and power semiconductor packaging.

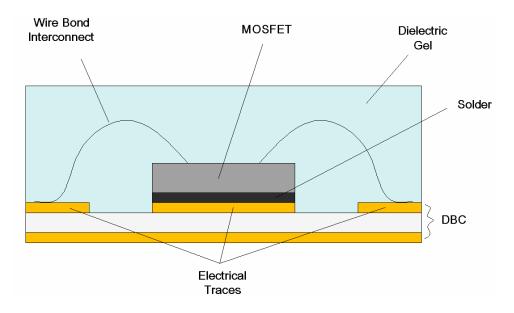

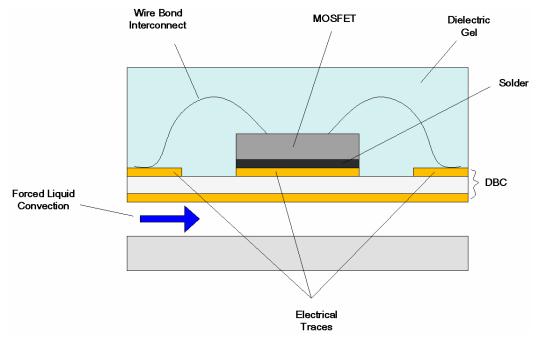

#### 1.3.1 Wire Bond Packaging and Cooling

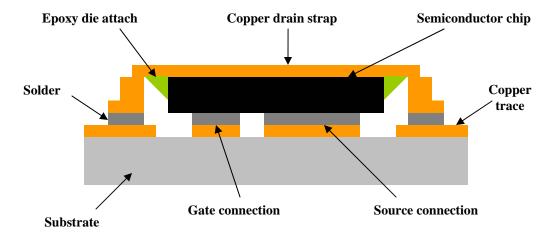

Previous efforts to interface advanced cooling schemes with power semiconductor devices are primarily driven by device packaging containing wire bond interconnects [1]. A cross section of a typical wire bond package is shown in Figure 1.2. In these schemes, semiconductors are usually interfaced with cooling mechanisms on the non-wire bond side of the package. The wire bond side is normally avoided for electrical isolation and wire bond reliability concerns. Some efforts have been made to improve the removal of heat through the wire bond side of MOSFET and IGBT packages by using advanced cooling techniques such as spray cooling.

Figure 1.2 Cross section of typical wire bond package

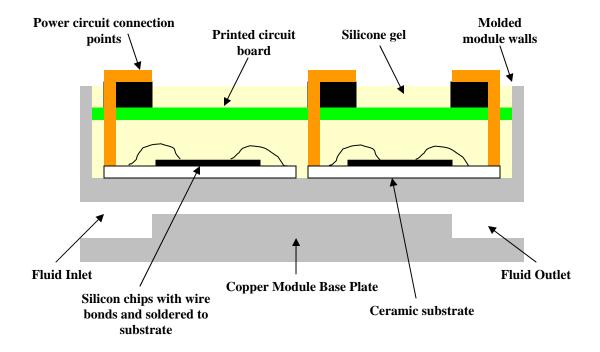

One effort to improve heat transfer for wire bonded MOSFETs is to integrate liquid cooling under the semiconductor device in a power electronics module package [4]. This MOSFET based module uses an integrated fluid channel under the copper base plate, which the semiconductor die are directly soldered to. The devices in this package are therefore not electrically isolated from the coolant, so de-ionized water is used as the cooling media in the module. Figure 1.3 shows a simple representation for this cooling package. This structure improves thermal management of the semiconductor device by reducing the thermal resistance between the chip and fluid compared to a system with a module on a liquid cold plate. Thermal resistance was calculated based on experimental results to be between 0.02 to 0.01 °C/W for a flow rate range of 0.4 to 1.8 gal/min with a 1300 W loss from a dual switch MOSFET module. A maximum pressure drop was found to be approximately 200 mbar.

Figure 1.3 Conceptual drawing of an integrated liquid cooling in a high power MOSFET module

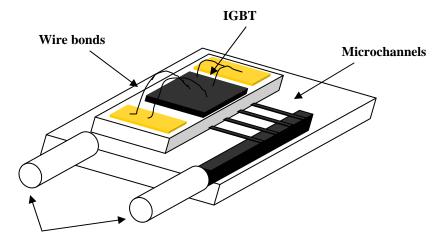

An improved thermal management scheme was demonstrated for an insulated gate bipolar transistor (IGBT) by using integrated single- and two- phase micro heat sinks [5]. It was mentioned that the micro scale cooling system could actually be implemented in the semiconductor itself, but this is not demonstrated since metallization is applied on the wafer for chip connections. As an alternative, micro heat sinks were place directly under the power semiconductor die. This micro structure can be used with single phase fluid flow to greatly reduce thermal resistance between the device and fluid. Thermal resistance was found to be approximately 0.1 °C/W for single phase water flow of 0.4 gal/min, 31 mbar pressure drop and 300 W device loss. A similar thermal resistance was found for multiphase flow, but with a flow rate of 0.007 gal/min and 2.7 mbar pressure drop. Figure 1.4 shows a conceptual drawing of the micro cooling structure for an IGBT device. A similar study with micro channels was performed for a group of IGBTs [6]. Single phase flow provides improved cooling performance due to a reduction in thermal resistance and can be implemented on the system level while remaining compact.

Fluid inlet & outlet

Figure 1.4 Conceptual drawing of an IGBT and integrated micro structure for single- and two-phase cooling

An advanced liquid cooled base plate can also improve thermal performance for IGBTs [7]. Multiple IGBTs are placed on a metal matrix composite (MMC) base plate. This base plate has been enhanced by using a pin pattern to increase surface area and promote turbulent flow. This structure reduces junction to fluid thermal resistance and provided a more uniform temperature across all of the devices. This package design gave a thermal resistance of 0.047 °C/W for a flow rate range of 0.8 to 4.2 gal/min, a 39 mbar pressure drop, and 800 W device loss.

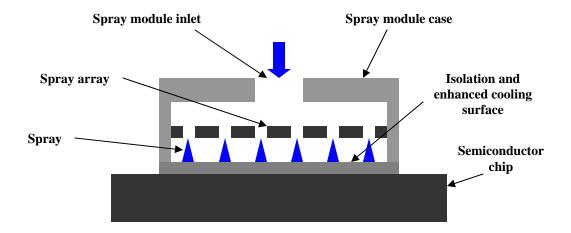

A micro jet array was also demonstrated to cool a power MOSFET device [8]. This cooling structure is applied to the bottom side of the MOSFET and utilizes air rather than a liquid. The cooling structure was created by assembling 4 etched layers of silicon using epoxy. A micro structure is included to enhance the heat transfer at the stagnation region for each jet plume in a jet array. A detailed analysis of heat transfer for a micro jet array reported heat flux capability greater than 15 W/m² [9]. A conceptual drawing of the jet array cooling structure is shown in Figure 1.5.

Figure 1.5 Structure of an air micro jet array for a power MOSFET

A more aggressive effort was made for wire bond packaging by implementing spray cooling [10]. Water spray was applied directly over an entire three phase motor drive system. Parylene was used to insulate the wire bonds and the chips themselves. This cooling method greatly improved thermal management for the semiconductors. A thermal resistance for the IGBTs in this system is estimated to be 0.05 °C/W for spray flow rates range of 0.05 to 0.34 gal/min and a system power loss of 670 W.

# 1.3.2 Non-Wire Bond Packaging and Cooling

Alternative non-wire bond power device packaging can provide a better opportunity to interface both sides of the semiconductor device with advanced cooling schemes. These non-wire bond packaging techniques include low temperature joining, flip chip solder balls interconnection technology, power overlay technology, DirectFET<sup>TM</sup>, press pack technology, and embedded power technology [11-18]. Design complexity, cooling efficiency, electrical isolation and power density must be considered for each case when interfacing the device package with advanced double-sided cooling schemes.

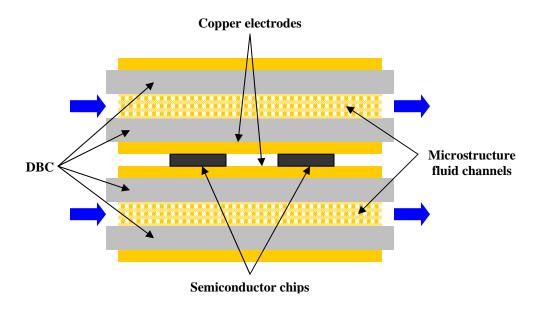

Low temperature joining techniques have been used to connect IGBT devices to Direct Bond Copper (DBC) in order to achieve double-sided liquid cooling [9]. This technique increases cooling performance, but electrical isolation via DBC adds thermal resistance [11]. Figure 1.6 shows a cross section of the double-sided cooling structure

with power semiconductors. This package design gave a thermal resistance of 0.087  $^{\circ}$ C/W for a flow rate of 1.6 gal/min.

Figure 1.6 Cross section of power semiconductors connected to DBC using low temperature joining techniques (microstructures were formed between DBC pieces to create cooling fluid channels)

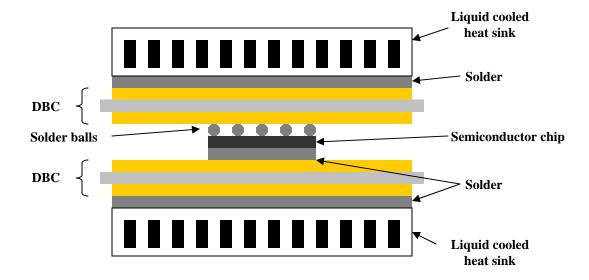

Flip chip solder ball interconnection technology can be used to eliminate cooling interface issues related to wire bonds, but electrical isolation requirements also limit the efficiency of the cooling system [12]. Micro channels are integrated directly in the package to provide double-sided cooling. The interface between the device and DBC via solder balls as well as the use of DBC as isolation between the device and heat sinks greatly reduces the heat transfer from the chip. This cooling and package configuration provides a thermal resistance of 0.09 to 0.12 °C/W for a flow rate range of 0.2 to 2 gal/min. Figure 1.7 shows a cross section of the structure.

Figure 1.7 Cross section of a double-sided micro channel package for IGBTs using flip chip interconnection

Various other interconnection methods eliminate wire bonds and can interface with double-sided cooling. Most have been demonstrated with conduction and air cooling schemes, while most have not been implemented with advanced cooling schemes such as forced liquid convection or phase change. Power overlay technology is one such technology that could possibly be implemented in an advanced double-side cooling configuration [13]. Electrical isolation and mechanical structure would have to be considered when implementing this technology with liquid systems.

DirectFET<sup>TM</sup> by International Rectifier is a very promising packaging technology for low power devices on a single chip scale [14]. DirectFET<sup>TM</sup> boast double-sided cooling as a primary benefit of the package. Underfill is helpful in the implementation of this device and could be necessary to prevent non-dielectric fluid flow under the chip for some advanced cooling schemes cooling. As higher power devices are produced with this technology more advanced cooling schemes will most certainly be explored. A cross section of a DirectFET<sup>TM</sup> is shown in Figure 1.8.

Figure 1.8 Cross section of a DirectFET<sup>TM</sup> device

Press-pack semiconductor packaging technology can also allow advanced double-side cooling schemes [15]. This example uses evaporators on both sides of the semiconductors. This method is promising for applications that use press-pack technology. Figure 1.9 shows the cross section of the press-pack and double-sided multiphase cooling structure.

Figure 1.9 Cross section of a press pack semiconductor package with double-sided multiphase cooling channels

Double-sided cooling for embedded power has been explored for standard cooling techniques including conduction and forced air convection [16-18]. Planar metallization with a copper strap rather than wire bonds were used for electrical connection and heat

transfer through the top side of a MOSFET [17]. The copper strap does not provide a major improvement since the conduction path from the top of the semiconductor chip through the strap is long. This structure has some similarity to the DirectFET<sup>TM</sup> design.

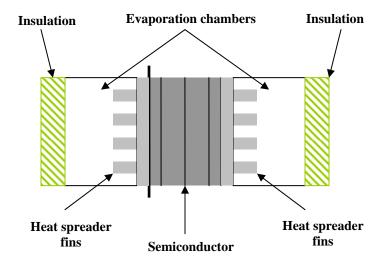

A more direct cooling approach is shown by using DBC and heat sinks attached to the top side metallization of an embedded power package [18]. This scheme reduced thermal resistance between the device and cooling media, but a more advanced cooling scheme could improve heat transfer even greater. Figure 1.10 shows a cross section of embedded power configured for double-sided air cooling.

Figure 1.10 Cross section of embedded power with double-sided air cooling

A summary of cooling and packaging technologies previously explored can be seen in Table 1.1. Some packaging technologies, such as DirectFET<sup>TM</sup>, press pack, and power overlay, are not included in Table 1.1 since advanced cooling schemes have not been reported with these technologies. From the survey it is easy to notice many research avenues for advanced cooling and packaging for power semiconductor devices. Both single- and multi-phase forced liquid cooling techniques have been explored for wire bond packaging. Non-wire bond packaging has been used to implement double-sided air and liquid cooling. Micro channels or micro structures are often utilized with liquid or air cooling for wire bond and non-wire bond packaging. High flow rate liquid convection has been used with several packaging technologies, but not embedded power. Higher velocity, forced liquid convection close to or directly on both sides of a power semiconductor in embedded power technology is new and reasonable area of study.

Table 1.1 Summary of cooling and packaging technologies explored for power semiconductor components and systems

| Interconnect<br>and packaging<br>technology<br>[Reference]         | Type of cooling                    | Number<br>of<br>cooling<br>sides | Total<br>package<br>thermal<br>resistance<br>(C/W) | Flow rate              | Device & Cooling<br>Area                            | Device<br>Loss<br>(W) |

|--------------------------------------------------------------------|------------------------------------|----------------------------------|----------------------------------------------------|------------------------|-----------------------------------------------------|-----------------------|

| Wire bond<br>module with liquid<br>cooled base plate<br>[4]        | Forced liquid convection           | 1                                | 0.02-0.01                                          | 0.4-1.8<br>gal/min     | 12 APT 20M38DVR<br>200V MOSFETS                     | 1300                  |

| Wire bond<br>module with<br>microchannels [5]                      | Forced liquid convection           | 1                                | 0.1                                                | 0.4 gal/min            | 1 SIEMENS 1600<br>V, 50 A IGBT<br>(14x14 mm)        | 300                   |

| Wire bond<br>module with<br>microchannels [5]                      | Multiphase<br>forced<br>convection | 1                                | 0.1                                                | 0.007<br>gal/min       | 1 SIEMENS 1600<br>V, 50 A IGBT<br>(14x14 mm)        | 300                   |

| Wire bond<br>module with<br>microchannels [6]                      | Forced liquid convection           | 1                                | 0.09-0.11                                          | 1.9-4.4<br>gal/min     | 2 IGBT on Cu heat<br>spreader (51x19<br>mm)         | 300                   |

| Wire bond<br>module with liquid<br>cooled MCM<br>base plate [7]    | Forced liquid convection           | 1                                | 0.047                                              | 0.8-4.2<br>gal/min     | 12 IGBT (9.5x9.5<br>mm) and 12 diodes<br>(7x7mm)    | 800                   |

| Wire bond system [10]                                              | Water<br>spray<br>convection       | 1                                | 0.05                                               | 0.05-0.34<br>gal/min   | 3-phase IGBT<br>module (Eupec<br>BSM50GD120DN2)     | 670                   |

| Low temperature joining of DBC with microchannels [11]             | Forced liquid convection           | 2                                | 0.087                                              | 1.6 gal/min            | 1 IGBT (12x12mm)                                    | 900                   |

| Flip chip solder<br>ball module [12]                               | Forced liquid convection           | 2                                | 0.12-0.09                                          | 0.2-2<br>gal/min       | 1 IGBT<br>(11.8x11.8mm)                             | 300                   |

| Embedded power [16]                                                | Forced air convection              | 1                                | 2-3                                                | 0.0094<br>m³/s         | 2 MOSFET<br>(8.8x7.1mm) on Cu<br>spreader (2x3.5cm) | 6-9                   |

| Embedded power with copper strap [17]                              | Thermo-<br>electric<br>cooler      | 2                                | 0.55                                               |                        | 1 MOSFET                                            | 19                    |

| Embedded power [18]                                                | Forced air convection              | 2                                | 14.07                                              | 0.05 m <sup>3</sup> /s | 1 MOSFET<br>(8.8x7.1mm)                             | 1.4                   |

| Embedded power with double-side DBC[18]                            | Forced air convection              | 2                                | 11.29                                              | 0.05 m <sup>3</sup> /s | 1 MOSFET<br>(8.8x7.1mm)                             | 1.86                  |

| Embedded power<br>with double-side<br>DBCand heat<br>spreaders[18] | Forced air convection              | 2                                | 5.38                                               | 0.05 m <sup>3</sup> /s | 1 MOSFET<br>(8.8x7.1mm)                             | 1.8                   |

# 1.4 Embedded Power Technology with Forced Liquid Convection

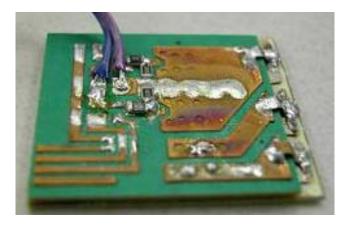

Embedded power technology is an advanced packaging technology with a structure favorable for interface to advanced cooling schemes. The basic structure and construction details for embedded power are defined by Liang [16]. Figure 1.11 shows an example of a power factor correction (PFC) integrated power electronics module using embedded power technology with a CoolMos<sup>TM</sup> and SiC Schottky diodes. This module shows the possible improvement to power density of an active power stage for a power converter. Embedded power technology may provide other benefits, including improved electrical performance and system manufacturing ability.

Figure 1.11. Power factor correction (PFC) integrated power electronics module using embedded power technology with a CoolMos<sup>TM</sup> and SiC schottky diodes

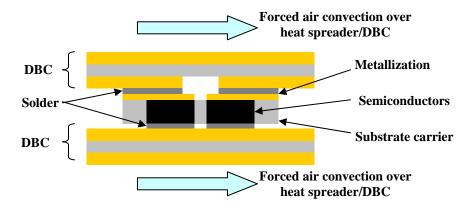

This device packaging technology can easily envisage single or double-sided conductive cooling since wire bonds are eliminated [16-18]. Table 1.1 gives expected thermal resistances for different cooling configurations. An alternate and more advanced cooling method, such as forced liquid convection, can be applied in a similar manner by interfacing the device package with a module or larger package to contain and control fluid flow directly across top and bottom side interconnects. Figure 1.12 shows a cross section of this proposed interface of the embedded power package with a forced liquid cooling system.

Figure 1.12 Cross section of typical embedded power technology structure with proposed doublesided liquid cooling

# 1.5 Objectives

A state of the art survey of thermal management and packaging schemes for power semiconductor devices quickly shows that a double-sided, high flow rate cooled embedded power package is a value topic to explore. Wire bond packaging and advanced cooling schemes have been explored thoroughly, but cooling potential is usually limited by single-side cooling. Non-wire bond packaging provides the opportunity for advanced double-sided cooling. Micro channels and micro structures have been implemented with both types of packaging and show promise when higher flow rates can be achieved. The goal of this thesis is to identify the potential of embedded power with double-sided, high flow rate forced liquid convection using a liquid cooling test bed.

Chapter 2 will present the development of a physics based electro-thermal model, which is used to predict the improvements provided by embedded power technology with double-sided forced liquid convection. Chapter 3 will discuss the design, development, and results of an experimental study used to verify thermal modeling predictions as well as explore practical issues of implementing double-sided liquid cooling with embedded power packaging. Finally, chapter 4 gives some conclusions and topics for future work.

# 2 THERMAL MODELING

Thermal modeling was considered as the next research tool after reviewing the state of art technology related to advance cooling schemes for power semiconductors. Several thermal modeling techniques were available, including finite difference techniques using Mathematica or Matlab, finite element software such as ANSYS, IDEAS or Flotherm, and physics based electro-thermal modeling using Saber or other electrical simulation software. A quick simulation method was preferred and electro-thermal modeling would provide this while being accurate. Physics based electro-thermal models were used to help predict the improvement provided by double-sided forced liquid convection with embedded power technology in comparison to single-sided forced liquid convection. The remainder of this chapter gives a description of the physics based electro-thermal modeling technique used, an example of electro-thermal modeling applied to embedded power, and a comparison of embedded power with double-sided forced liquid convection to a wire bond package with single-sided forced liquid convection.

# 2.1 Physics Based Electro-Thermal Modeling Background

Physics based electro-thermal models can be constructed simply and then simulated in electrical simulation software such as Saber. The construction of an electro-thermal model for a power semiconductor package with forced liquid cooling requires several elements to represent the forms of heat transfer. These elements include the thermal resistance of solid materials, the thermal capacitance of solid materials, and the thermal resistance of heat transfer via forced liquid convection. These elements are placed in a Cauer RC electrical circuit similar to the circuit example shown in Figure 2.1 [19-20]. Current sources represent heat flux boundary conditions while voltage sources represent temperature boundary conditions. Voltage and current values therefore represent temperature and heat flux values.

Figure 2.1 Cauer RC electro-thermal simulation circuit example

To simplify the development of each of these electro-thermal components, several key assumptions were made. One dimensional heat transfer is assumed to greatly reduce the complexity of the model. This assumption is reasonable since a semiconductor device has a considerably greater area versus height. Thermal capacitances can be eliminated in the model when only studying steady state thermal conditions. Interfacial thermal resistance between solid materials is also neglected. This assumption is necessary since interfaces are difficult to characterize and control. Solid material properties and fluid properties were considered to be constant since these properties change very little over the temperature range expected, 25 °C to 150 °C. Heat transfer through forced liquid convection is also assumed to be the only form of heat removal from the semiconductor device. This is hard to control in most experimental cases, but heat transfer through high velocity fluid convection is considered to dominate most other forms of heat transfer encountered. This can be confirmed easily for the most likely case by comparing the range of forced water convection thermal resistance to the thermal resistance range of natural air convection from Figure 1.1. Fluid flow is considered to be fully developed and in the turbulent flow regime with 3000<Re<sub>D</sub><5x10<sup>6</sup>. assumption is reasonable for high velocity fluid flow and can be checked by calculating the Reynolds number. The following two sections describe the construction of conduction based thermal resistance and convection thermal resistance.

#### 2.1.1 Conduction Heat Transfer Modeling

Electro-thermal model components for conduction heat transfer are simple to create in comparison to convection based thermal resistance. Conduction based thermal resistance can be calculated based on equation 1.1 [21].

$$R_{conduction} = \frac{L}{kA_s} \tag{1.1}$$

$A_s$  is the area of the device, while L is the thickness of each layer of material under the device. Solid material thermal conductivity is defined by k.

#### 2.1.2 Convection Heat Transfer Modeling

Convection thermal resistance can be extremely complicated to formulate. This is due to combining fluid mechanics and heat transfer, which are both complex subjects. The assumptions mentioned previously help to reduce the formulation and simulation difficulties for convection heat transfer. A convection thermal resistance can be found from equations 1.2 through 1.4 [21].

$$R_{convection} = \frac{1}{hA_s} \tag{1.2}$$

$$h = \frac{Nu_D D_h}{k_f} \tag{1.3}$$

$$D_h = \frac{4A_c}{P} \tag{1.4}$$

$D_h$  is the hydraulic diameter in the cooling chamber,  $A_c$  is the cross sectional area of fluid flow, and P is the perimeter of rectangular flow area. Fluid thermal conductivity is defined by  $k_f$ . The Nusselt number,  $Nu_D$ , is a function of the Reynolds number, which is defined by equation 1.5 [21].

$$Re_D = \frac{\rho u_m D_h}{\mu} \tag{1.5}$$

Fluid density and viscosity are defined by  $\rho$  and  $\mu$ , respectively. An average Reynolds number can be calculated by finding a mean velocity,  $u_m$ , in the cooling region. The mean velocity in the cooling region is calculated from using equation 1.6 assuming a fluid flow rate, F is known.

$$u_m = \frac{F}{A_c} \tag{1.6}$$

It was assumed that the flow in the cooling region is in the turbulent regime with  $3000 < \text{Re}_D < 5 \times 10^6$ . Based on this assumption,  $Nu_D$  can be found for fully developed turbulent flow through a rectangular duct from the correlation proposed by Gnielinski, which is given by equations 1.7 and 1.8 [21].

$$Nu_D = \frac{(f/8)(\text{Re}_D - 1000)\text{Pr}}{1 + 12.7(f/8)^{1/2}(\text{Pr}^{2/3} - 1)}$$

(1.7)

$$f = (0.79 \ln \text{Re}_D - 1.64)^{-2} \tag{1.8}$$

These equations are valid for fluid properties and flow conditions such that  $3000 < \text{Re}_D < 5 \times 10^6$  and 0.5 < Pr < 2000. The Prandtl number, Pr, can be calculated based on equation 1.9, where  $c_p$  is specific heat of the fluid [21].

$$\Pr = \frac{c_p \mu}{k_f} \tag{1.9}$$

## 2.2 Package Structure and Thermal Models

The following sections describe the packaging structures under study and their thermal models.

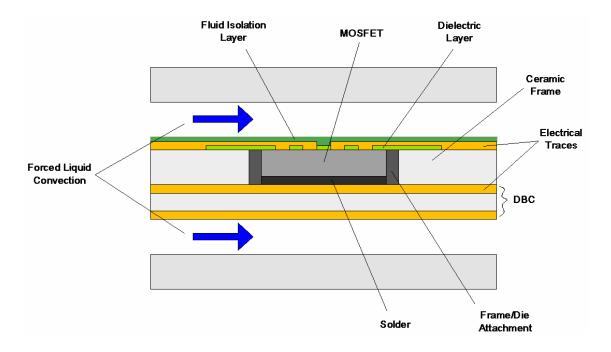

#### 2.2.1 Embedded Power Package

A completed example of embedded power with CoolMOS<sup>TM</sup> and SiC schottky diodes for power factor correction applications was shown in Figure 1.11. A detailed cross section of a similar package with a single MOSFET is shown in Figure 2.2. Design and construction details are described by Liang [16]. As described in a previous section, this package can be interfaced with forced liquid convection using a liquid module to contain and control fluid flow over the top and bottom side of the embedded power package. Direct fluid flow requires a thin insulation layer to be applied to the gate/source

side of the MOSFET for electrical insulation and to prevent degradation of the chip interconnections by mechanical abrasion. Enthone<sup>®</sup> DSR-3241 liquid photoimageable solder mask is a reasonable material to use for this purpose, but other materials including sputtered silicon nitride, sputtered aluminum nitride, or chemical vapor deposited parylene may be better candidates for even greater heat transfer [22]. This insulation layer could also be eliminated if a dielectric fluid was used, but mechanical abrasion of the copper traces and the semiconductor chip would still need to be considered. DBC and solder are used as a drain interconnection. This DBC/solder interconnect also acts as isolation and mechanical support, but could be replaced by a planar metallization interconnection similar to the top side to further improve heat transfer.

Figure 2.2 Cross section of embedded power technology with DBC base

A one dimensional, physics based electro-thermal model can be constructed for an embedded power package by first identifying the loss or heat source, which in this case is a single MOSFET device, Advanced Power Technology (APT) APT60M75DFLL, with dimensions of 11.9 mm x 16.5 mm x 0.254 mm [23]. Next, all solid material layers should be identified and their thicknesses and material properties recorded. This information can be used to calculate thermal resistance using equation 1.1. The material properties and thermal resistances of all solid layers in the embedded power package are shown in Table 2.1.

|                             | L         | k              | $A_s$                  | $R_{th}$      |

|-----------------------------|-----------|----------------|------------------------|---------------|

|                             | m         | $\frac{W}{mK}$ | m <sup>2</sup>         | $\frac{W}{C}$ |

| Bottom half of silicon chip | 0.000127  | 118            | 0.000196               | 0.0457        |

| Solder                      | 0.0004    | 57             | 0.000196               | 0.0357        |

| DBC copper                  | 0.0006096 | 380            | 0.000196               | 0.0082        |

| DBC ceramic                 | 0.000635  | 26             | 0.000196               | 0.1242        |

| Top half of silicon chip    | 0.000127  | 118            | 0.000196               | 0.0457        |

| Copper connections          | 0.0000508 | 380            | 6.735x10 <sup>-5</sup> | 0.002         |

| Screen printed dielectric   | 0.0000508 | 0.3942         | 1.291x10 <sup>-4</sup> | 0.9979        |

| Electroplated copper        | 0.0000762 | 380            | 0.000196               | 0.001         |

| Solder mask insulation      | 0.00002   | 0.08368        | 0.000196               | 1.5448        |

Table 2.1 Thermal resistance values for embedded power technology

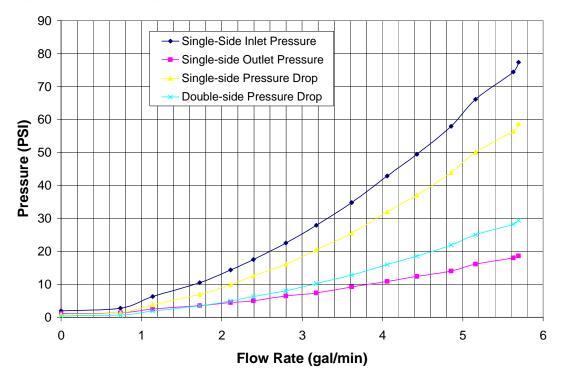

Convection thermal resistance can be calculated based on equations 1.3 through 1.10. A fluid flow range between 0 and 10 gal/min with water in a rectangular duct with flow cross section dimensions 42 mm x 5 mm was assumed. Fluid properties are summarized in Table 2.1 and fluid velocity versus flow rate for this cross sectional area is shown in Figure 2.3. The Reynolds number versus flow rate is shown in Figure 2.4. A red line was added at F≈0.6 gal/min, which gives a Reynolds around 3000, the lower limit of the turbulent convection correlation given in equation 1.7. Figure 2.5 through Figure 2.7 show the friction factor, the Nusselt number, and the convection heat transfer coefficient versus flow rate. Figure 2.8 gives the convection thermal resistance for a single side of a chip. The lower limit of the convection model is depicted with a red line in appropriate graphs.

Table 2.2. Thermal and flow properties of water at 25°C

|       | ρ                     | μ                                          | $k_f$                          | $c_p$                         | Pr   |

|-------|-----------------------|--------------------------------------------|--------------------------------|-------------------------------|------|

| Water | $1000 \frac{kg}{m^3}$ | $855 \times 10^{-6} \frac{N \cdot s}{m^2}$ | $613\times10^{-3}\frac{W}{mK}$ | $4.179 \frac{kJ}{kg \cdot K}$ | 5.83 |

Figure 2.3 Fluid velocity,  $u_m$  versus flow rate, F

Figure 2.4 Reynolds number,  $Re_D$  versus flow rate, F

Figure 2.5 Friction factor, f versus flow rate, F

Figure 2.6 Nusselt number,  $Nu_D$  versus flow rate, F

Figure 2.7 Convection heat transfer coefficient, h versus flow rate, F

Figure 2.8 Convection thermal resistance,  $R_{convection}$  versus flow rate, F

A thermal model for embedded power with a single APT APT60M75DFLL MOSFET and a water flow rate between 0 and 10 gal/min can now be constructed as shown in Figure 2.9. The MOSFET power loss can be defined as a single current source and fluid temperature can be set by a voltage source.

Figure 2.9. Thermal model for embedded power with double-sided forced liquid convection

#### 2.2.2 Wire Bond Package

A wire bond based package with single-side forced liquid convection was chosen to compare to the high fluid flow rate cooled embedded power package. A cross section of a wire bond based package with single-sided liquid cooling is shown in Figure 2.10. A protective silicone based, dielectric gel is typically placed on the top side of a wire bond device. This gel is considered as an electrical and thermal insulator, so heat can only pass through the bottom side of the device through the DBC. This heat transfer path is assumed to be the same as the bottom side of the embedded power case. The wire bond package solid layers and their respective properties and thermal components are shown in

Table 2.3. The convection thermal resistance found previously for the embedded power case with a water flow rate of 0 to 10 gal/min is used with the wire bond package.

Figure 2.10 Cross section of wire bond package with single-sided liquid cooling

L k  $A_s$  $R_{th}$ WW $m^2$ m CmKBottom half of silicon chip 0.000127 118 0.000196 0.0457 **Solder** 0.0004 57 0.000196 0.0357 **DBC** copper 0.0006096 380 0.000196 0.0082**DBC** ceramic 0.000635 26 0.000196 0.1242

Table 2.3 Thermal resistance values for wire bond packaging

A thermal model for a wire bond package with a single APT APT60M75DFLL MOSFET and a water flow rate between 0 and 10 gal/min can now be constructed as shown in Figure 2.11.

Figure 2.11 Thermal model for a wire bond package with single-sided forced liquid convection

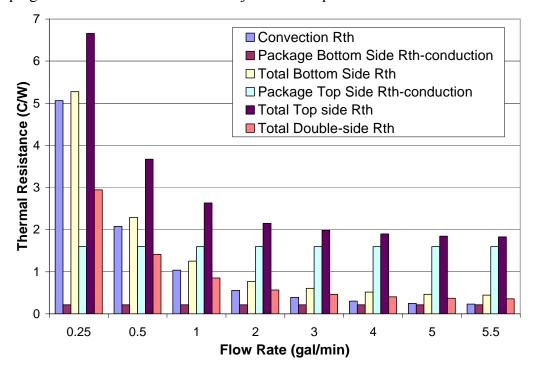

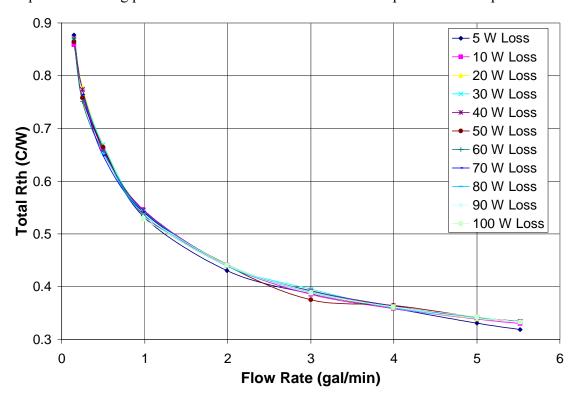

## 2.3 Thermal Modeling Results

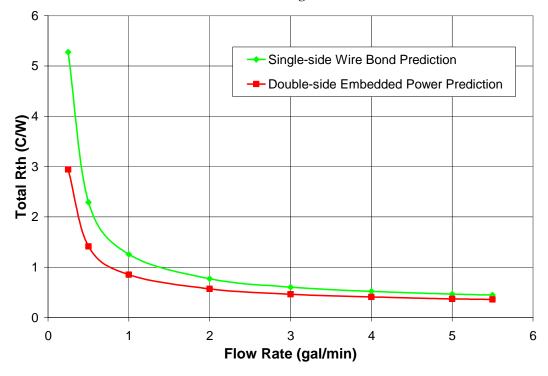

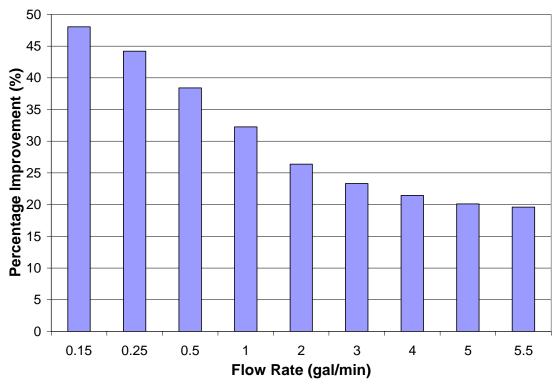

The thermal models for the embedded power and wire bond packages were compared to predict the improvements of high velocity double-side forced liquid convection. Total junction to case thermal resistance can be found by adding conduction thermal resistance to convection thermal resistance. These resistances are shown versus flow rate in Figure 2.12. The total junction to case thermal resistance versus flow rate is shown in Figure 2.13. The percentage improvement provided by double-sided cooling over single-sided cooling is shown in Figure 2.14. This plot shows approximately 48% improvement at low flow rates and 20% improvement at high flow rates for double-side cooled embedded power packaging versus single-side cooled wire bond packaging.

This improvement is due to the additional heat removal path of the embedded power package. The improvement decreases with flow rate because the bottom side total thermal resistance of the embedded power is used for the wire bond thermal model. Therefore the wire bond total package thermal resistance approaches that of the embedded power package at high flow rates. The top side and bottom side of the device contribute differently to the overall efficiency of double-sided cooling due to different solid layers above and below the device in embedded power technology. This can be seen clearly in Figure 2.12. Alternate insulation materials may make the top-side cooling more effective. It can be predicted that a 300 W semiconductor device loss can be

achieved with this MOSFET in embedded power with high flow rate cooling while keeping the device below its maximum junction temperature of 150 °C.

Figure 2.12 Comparison of conduction and convection thermal resistances found from thermal modeling

Figure 2.13 Predicted total junction to case thermal resistance comparison for double-side cooled embedded power packaging and single-side cooled wire bond packaging versus flow rate

Figure 2.14 Predicted percentage improvement provided by double-sided cooling over single-sided cooling

# 2.4 Thermal Modeling Summary

Thermal modeling helps show the potential of double-sided forced liquid convection with embedded power versus a wire bond package with single-sided forced liquid convection. One dimensional, physics based electro-thermal models provide a quick and accurate modeling method. An improvement of approximately 48% for low flow rates and 20% for high flow rates is predicted for thermal resistance of the double-side cooled embedded power package compared to the single-side cooled wire bond package for planar water flow rate between 0 and 5.5 gal/min. Maximum temperature rise for a power semiconductor can be significantly reduced due to this reduction in overall thermal resistance. The cooling potential for high flow rates in conjunction to double-sided heat transfer is clearly shown.

## 3 EXPERIMENTAL VERIFICATION

Experimental verification can verify the potential predicted in thermal modeling for double-sided, high velocity, forced convection with embedded power technology. Experimenting with embedded power and liquid cooling also helps identify design issues and future work for the implementation of a similar system in a commercial or military application. A test bed for liquid cooling of power semiconductors is also developed from this experimentation and can be applied to future semiconductor package designs.

This chapter presents the design and construction details for experimental analysis of high velocity, liquid-cooled power semiconductor packaging. A liquid module test bed was created to interface power semiconductor packaging technologies to high velocity fluid flow. A MOSFET based embedded power package and a wire bond package were designed and constructed to mimic the package cases reviewed in thermal modeling and allow attachment to the liquid module test bed. Design challenges are reviewed and experimental results are given. Thermal modeling results are also compared to experimental results to analyze the overall prediction quality.

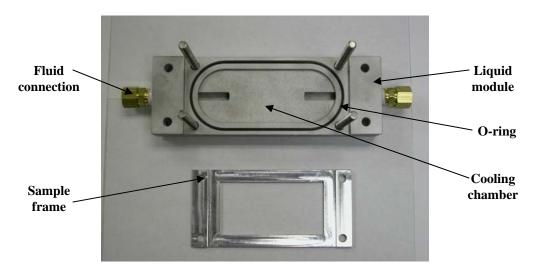

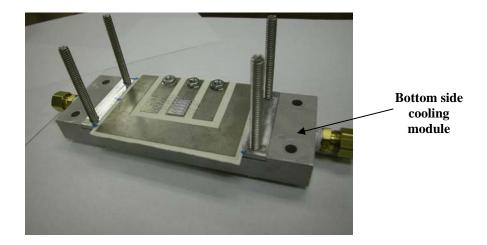

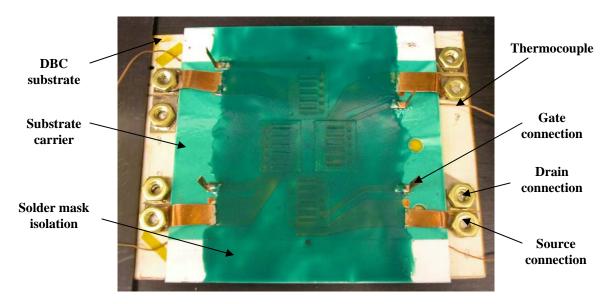

#### 3.1 Liquid Module Test Bed

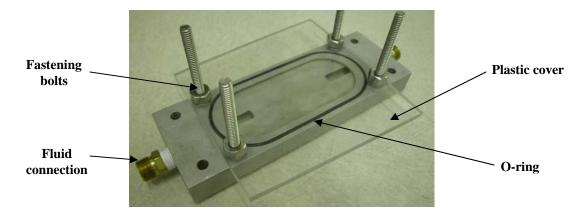

A packaging structure is required to interface cooling fluid to the power semiconductor packaging. This packaging structure contains the fluid while controlling its direction over the semiconductor devices. A liquid module test bed was designed to handle a fluid range of 0 to 6 gal/min and provide planar flow over the packaging structures studied with thermal modeling. Future liquid module designs could incorporate perpendicular flow types, such as spray cooling or jet impingement, by adding connections and fluid distribution channels through the bottom of the modules in the cooling region. The cross sectional flow region was designed with dimensions similar to those assumed in thermal modeling while the length of the cooling region was chosen to allow reasonable sample cooling area. It was desired to create a module, which would allow for quick and easy change of samples without destroying the module or semiconductor package. This is achieved by employing a substrate frame, which can be permanently attached to the semiconductor package via a sealing adhesive, and a viton o-

ring seal to attach this frame to the liquid module. O-ring material choice and gland design details can be found in from Erik's technical documentation on o-rings [24]. The liquid module and sample frame were drawn in Autocad as shown in Figure A.1.

The final pieces were manufactured in multipurpose 6061 alloy Aluminum by Metal Processing Inc. in Radford, Virginia and are shown in Figure 3.1. Aluminum was chosen due to its excellent machining qualities, strength and light weight. The sample frame design causes some bowing to appear after machining. This was ignored assuming pressure applied by the liquid module would flatten the frame and provide a good seal. Future designs should consider this by choosing an alternate material or defining a specific machining method. The liquid module has a powdered finish and the substrate frame has a polished finish to improve the seal between these pieces around the o-ring. Brass pipe compression fittings are used to attach round pipe to the module ends allowing connection to a fluid system. Bolts are used to connect the pieces of the package and apply pressure. These bolts can also be used to connect the package to a testing bench or converter case. Figure 3.2 and Figure 3.3 show the liquid module test bed in single-side and double-side test configuration, respectively.

Figure 3.1 Liquid module test bed and sample frame

Figure 3.2 Liquid module in single-side cooling test configuration

Figure 3.3 Picture and cross section of liquid module test bed in double-side cooling test configuration

## 3.2 MOSFET for Experimental Verification

A MOSFET based package was chosen for experimental verification to more closely represent a power converter semiconductor package. Other components like diodes and resistors could also be used to explore the potential of double-side cooled

embedded power packaging, but each have advantages and disadvantages for research, which must be considered. High power chip resistors that have similar thickness and footprint to high power, power semiconductors are not available as standard commercial products. Power diodes could have been implemented rather than MOSFETs, but a working power MOSFET sample could eventually be placed directly in a switching power converter system. Using a MOSFET rather than other components is much more useful in order to explore practical design and manufacturing issues for a switching power semiconductor in an embedded power package with high velocity fluid flow.

The MOSFET chosen for experimental verification is APT60M75DFLL by Advanced Power Technology and was previously used for the thermal modeling example in section 2.2 [23]. A picture of the bare FREDFET is shown in Figure 3.4. The die dimensions, gate structure, and source structure are available from Advanced Power Technology [25]. The die has titanium-nickel-silver (Ti-Ni-Ag) metallization on the backside or drain, which can handle most solders [25]. Key characteristics can be taken from the datasheet for its discrete counterpart and are listed in Table 3.1 [23]. Low voltage forward characteristics for this FREDFET can also be obtained from the device datasheet and are used to determine the device power loss range possible with different gate to source voltage  $V_{GS}$ , drain current  $I_D$ , and drain-to-source voltage  $V_{DS}$ .

Figure 3.4 APT APT60M75DFLL FREDFET device

Table 3.1 APT APT60M75DFLL FREDFET key parameters

|              | $V_{DS}$ | $I_D$        | $V_{GS(th)}$ | $\mathbf{R}_{\mathrm{DS(on)}}$ | $T_{J(max)} \\$ |

|--------------|----------|--------------|--------------|--------------------------------|-----------------|

| APT60M75DFLL | 600V     | 73A          | 3V to 5V     | 0.0750                         | 150°C           |

| FREDFET      | 000 V    | / <i>3</i> A | 3 1 10 3 1   | 0.07322                        | 130 C           |

## 3.3 Embedded Power Package

### 3.3.1 Embedded Power Package Design

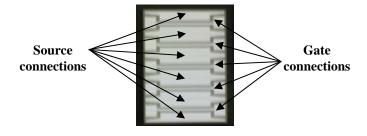

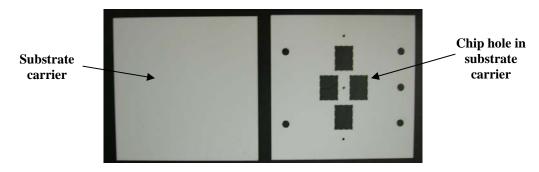

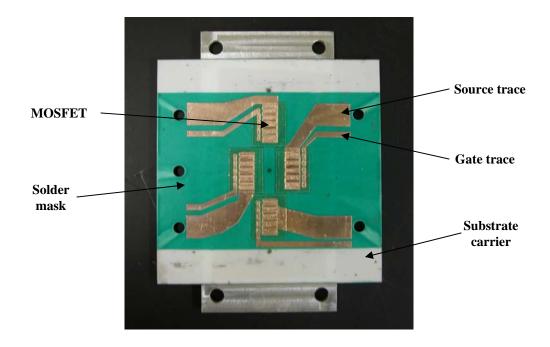

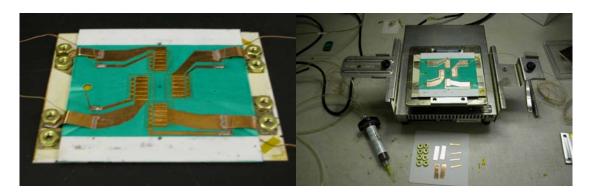

An embedded power package using APT60M75DFLL by Advanced Power Technology was designed for liquid cooling testing. The cooling area of the liquid module defines the area allowed for power semiconductor devices to be mounted. It was chosen to use four FREDFETs by APT to improve yield in case any of the semiconductor die are damaged during manufacturing steps. These chips are placed in a diamond formation to make electrical connection simpler and to ensure the chips are close to the center of the cooling region. Each chip can be connected to external circuitry separately through electrical connectors outside the cooling region. This requires that the substrate be wider than the cooling region. Future connection could be half bridge, full bridge, or multiple levels. A solder joint to a DBC substrate is used for the drain connection. DBC provides insulation from non-dielectric fluid and protection against abrasion caused by fluid flow. The DBC also acts as mechanical support for the high pressure flow. Type k thermocouples from Omega Engineering Inc. are attached next to each drain pad to monitor chip temperature [26]. Solder mask is used to insulate the top side gate and source traces. This layer also helps prevent mechanical degradation of electrical traces and the semiconductor chips. Silicone based gel is used between the DBC and substrate carrier to provide mechanical support for the sample frame. The dielectric layer design and trace layout design are shown in Figure B.2 and Figure B.3.

#### 3.3.2 Embedded Power Package Construction

This section describes the steps to construct the MOSFET based embedded power package for double-sided liquid cooling. The basic process is described by Liang [16]. All major steps are discussed while some minor steps, such as equipment use and sample cleaning, are not. An outline of the complete process is given in Appendix C.

After first creating a conceptual design via hand drawings, a finalized design should be created in Autocad. Key information to finalize completely are the substrate laser cutting pattern, dielectric screen print pattern, metallization electrical trace pattern, and DBC electrical trace pattern. These patterns are shown in Figure B.1 through Figure

B.4. The first step after completing the design phase is to laser cut the substrate carrier. 99.6% alumina, Al<sub>2</sub>O<sub>3</sub>, with the dimensions 101.6 mm x 101.6 mm x 0.635 mm, from Accumet Engineering Corporation was used in this sample [27]. The laser cut pattern in Figure B.1 is then used to cut the substrate. Care was taken by using a low laser power settings and multiple runs to reduce heating and therefore avoid breaking substrates. Figure 3.5 shows an uncut substrate and cut substrate. Extra holes were cut for pressure relief and screw connectors, but weren't used in this version. After cutting, the sample was mechanical cleaned using a diamond file, then wet cleaned using acetone, isopropyl alcohol, and de-ionized water, and allowed to dry completely.

Figure 3.5 Uncut and laser cut alumina substrate for semiconductor die placement

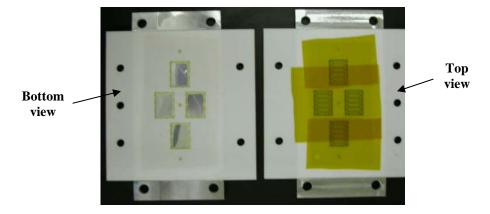

The semiconductor die were placed in the substrate carrier. This steps requires extreme care to not damage the semiconductor via static charge or mechanical abuse. Kapton tape is first placed on the top side of the substrate over the hole where chips and/or epoxy will be placed. The chips are then carefully placed in their respective holes with their gate and source patterns touching the Kapton tape. This is done using a suction cup system. The chip drains and top side are then pressed using the suction cup system to remove air bubbles seen through the Kapton. This is important to prevent epoxy flow onto the top of the chip. Die attach epoxy, EP3AOHT from Master Bond Inc., is then applied around the chip via a syringe [28]. This epoxy can be heated slightly to improve its viscosity for uniform application. Voids are stamped out of the epoxy by using a tweezers or needle point to ensure good adhesion between the chip and substrate and more epoxy is added if needed. The voids can be viewed by holding the sample up to a light and looking though the epoxy. After epoxy application is complete, the epoxy

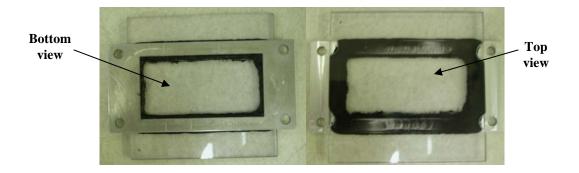

should be baked and the allowed to cool. Figure 3.6 shows bottom and top views of the chips in the substrate carrier post epoxy bake.

Figure 3.6 Top and bottom views of die attachment to alumina substrate carrier

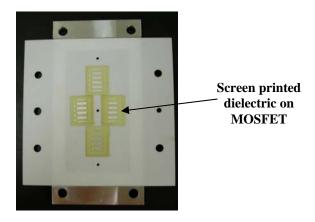

Top side dielectric application is required to isolate gate and source pads. This dielectric can be applied using screen printing or photolithography methods depending on the isolation requirement between the gate and source, source and drain, and gate and drain. Screen printing was chosen for this case due to previous experience and higher dielectric strength. The screen print material used is EPO-TEK 600 from Epoxy Technology and the dielectric screen print pattern is shown in Figure B.2 [29]. The screens were constructed by Sefar Printing Solutions, Inc. The Kapton tape is removed from the previous step and a wet clean with acetone, isopropyl alcohol, and de-ionized water is then performed to remove residue left by the tape. Screen printing is then performed on the substrate after firmly securing the substrate and checking alignment. EPO-TEK 600 can be heated slightly to improve viscosity for application. The screen printed sample is then baked. Figure 3.7 shows the sample after screen printing and baking.

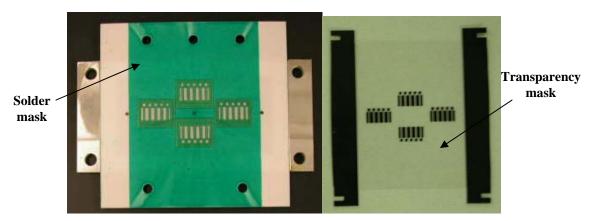

Figure 3.7 Screen printed dielectric layer over top of MOSFET chips

A smooth solid layer is then applied over the screen printed pattern to help with adhesion of thin film metals in future steps. Enthone<sup>®</sup> DSR-3241 liquid photoimageable solder mask is used for this and will also add to the dielectric strength of the system between MOSFET connection points [30]. The solder mask is mixed and applied by spin coating. The material is then pre-cured and developed using photolithography steps. The solder mask is put through a final bake after developing. The photolithography pattern is identical to the pattern used for screen printing in Figure B.2. A sample after solder mask application and the photolithography transparency used for this step is shown in Figure 3.8.

Figure 3.8 Solder mask layer for sputtering and photolithography transparency

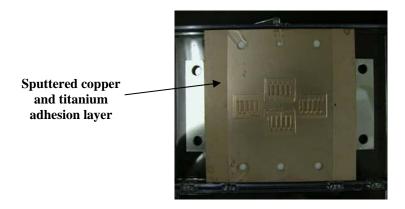

Proper application of thin film metal interconnects is critical for the success of an embedded power sample. Physical vapor deposition (PVD) or sputtering is used to apply titanium and copper thin films on the gate and source side of the sample. A complete and

thorough description of PVD and related issues such as sample preparation and plasma cleaning can be found in the Handbook of Physical Vapor Deposition (PVD) Processing [31]. The sample is first put through a wet clean process using acetone, isopropyl alcohol, and de-ionized water and then put through an ex-situ plasma clean process. In-situ plasma cleaning should be implemented in the future to improve deposition quality. The embedded power structure is then put in a PVD chamber where thin film metals are applied. Titanium is used as an adhesion layer for copper, which provides electrical connection. Figure 3.9 shows the sample after titanium and copper were deposited.

Figure 3.9 Physical vapor deposited (PVD) thin film titanium and copper for electrical interconnects