## Designing a Software Defined Radio to Run on a Heterogeneous Processor

Almohanad S. Fayez

Thesis submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

> Master of Science in Electrical Engineering

Charles W. Bostian, Chair Scott F. Midkiff Cameron D. Patterson

> April 25, 2011 Blacksburg, Virginia

Keywords: Software Defined Radio, Heterogeneous Processors, OMAP, Cognitive Radio, DSP Copyright 2011, Almohanad S. Fayez

#### Designing a Software Defined Radio to Run on a Heterogeneous Processor

Almohanad S. Fayez

#### (ABSTRACT)

Software Defined Radios (SDRs) are radio implementations in software versus the classic method of using discrete electronics. Considering the various classes of radio applications ranging from mobile-handsets to cellular base-stations, SDRs cover a wide range of power and computational needs. As a result, computing heterogeneity, in terms of Field-Programmable Gate Arrays (FPGAs), Digital Signal Processors (DSPs), and General Purpose Processors (GPPs), is needed to balance the computing and power needs of such radios. Whereas SDR represents radio implementation, Cognitive Radio (CR) represents a layer of intelligence and reasoning that derives reconfiguration of an SDR to suit an application's need. Realizing CR requires a new dimension for radios, dynamically creating new radio implementations during runtime so they can respond to changing channel and/or application needs.

This thesis explores the use of integrated GPP and DSP based processors for realizing SDR and CR applications. With such processors a GPP realizes the mechanism driving radio reconfiguration, and a DSP is used to implement the SDR by performing the signal processing necessary. This thesis discusses issues related to implementing radios in this computing environment and presents a sample solution for integrating both processors to create SDR-based applications.

The thesis presents a sample application running on a Texas Instrument (TI) OMAP3530 processor, utilizing its GPP and DSP cores, on a platform called the Beagleboard. For the application, the Center for Wireless Telecommunications' (CWT) Public Safety Cognitive Radio (PSCR) is ported, and an Android based touch screen interface is used for user interaction. In porting the PSCR to the Beagleboard USB bandwidth and memory access latency issues were the main system bottlenecks. Latency measurements of these interfaces are presented in the thesis to highlight those bottlenecks and can be used to drive GPP/DSP based system design using the Beagleboard.

# **Grant Information**

This project is supported by Award No. 2009-SQ-B9-K011 awarded by the National Institute of Justice, Office of Justice Programs, US Department of Justice. The opinions, findings, and conclusions or recommendations expressed are those of the author and do not necessarily reflect the views of the Department of Justice.

I would also like to acknowledge the Saudi Arabian Cultural Mission (SACM) for providing me with a graduate fellowship during the course of my studies.

# Dedication

To my parents, wife, brothers, sisters, friends, and my yet to be born child.

# Acknowledgments

I would like to thank all of my family for their patience and support throughout my studies and graduate education. Especially my parents and wife who have endured being neglected in the weeks leading to my thesis defense.

I would like to thank Dr. Bostian for his support, understanding, and encouragement during my undergraduate and graduate careers. I would like to thank Ms. Judy Hood for all her help, guidance, and magic.

I would also like to thank my committee members - Dr. Cameron Patterson and Dr. Scott Midkiff for their valuable advice and insight.

I would like to thank my friend and colleague Shereef Sayed for all the guidance he gave me throughout my graduate career and all the long discussions we had.

I would like to thank all CWT family for helping me whenever I needed it the most. I have enjoyed all the long work days, cookouts, and the occasional testing of the lab's big screen TV with movies.

I would like to thank all of my friends; I really appreciate you still talking to me even after disappearing in my lab for weeks at end.

All photographs in the thesis have been taken by the author or other members of our laboratory and all illustrations have also been created by the author, except for Figure 2.6 with the publication permission included in Appendix D. Some of the reamining illustrations are based on information available in literature, which is appropriately cited, and the illustrations themselves are generated by the author to further clarify the information.

# Contents

| G            | Grant Information |                                       |   |  |

|--------------|-------------------|---------------------------------------|---|--|

| D            | edica             | ition                                 | v |  |

| $\mathbf{A}$ | cknov             | wledgments                            | v |  |

| $\mathbf{A}$ | crony             | yms xiv                               | v |  |

| 1            | Ove               | erview                                | 1 |  |

|              | 1.1               | Introduction                          | 1 |  |

|              | 1.2               | Motivation                            | 2 |  |

|              | 1.3               | Literature Review                     | 2 |  |

|              | 1.4               | Goals                                 | 3 |  |

|              | 1.5               | Outline                               | 4 |  |

|              | 1.6               | Publications                          | 4 |  |

| <b>2</b>     | SDI               | R System Implementation               | 5 |  |

|              | 2.1               | SDR System HW/SW                      | 5 |  |

|              | 2.2               | Computational Device Considerations   | 7 |  |

|              |                   | 2.2.1 Memory Architecture             | 7 |  |

|              |                   | 2.2.2 Addressing                      | 9 |  |

|              |                   | 2.2.3 Signal Processing Functionality | 9 |  |

|              | 2.3               | Platforms                             | 0 |  |

|          |                | 2.3.1  | Programmable Radio Front-End                                                                      | 10 |  |

|----------|----------------|--------|---------------------------------------------------------------------------------------------------|----|--|

|          |                | 2.3.2  | Computational Platforms                                                                           | 12 |  |

|          |                | 2.3.3  | Integrated SDR Systems                                                                            | 14 |  |

|          | 2.4            | SDR I  | Platform Choice                                                                                   | 15 |  |

|          |                | 2.4.1  | Integrated GPP and DSP core                                                                       | 15 |  |

|          |                | 2.4.2  | Allows the installation of Linux                                                                  | 15 |  |

|          |                | 2.4.3  | Functional USB/Ethernet drivers                                                                   | 15 |  |

| 3        | Software Tools |        |                                                                                                   |    |  |

|          | 3.1            | Embe   | dded Development Framework                                                                        | 18 |  |

|          | 3.2            |        | al Purpose Processor (GPP)/Digital Signal Processor (DSP) Develop-<br>Tools and Interface Toolkit | 19 |  |

|          | 3.3            | SDR S  | Software Toolkit                                                                                  | 21 |  |

|          | 3.4            | Softwa | are Selection and Integration                                                                     | 22 |  |

| 4        | DSI            | P Man  | agement and Platform Support                                                                      | 23 |  |

|          | 4.1            | Work   | Flow                                                                                              | 23 |  |

|          | 4.2            | Platfo | rm Setup                                                                                          | 24 |  |

|          |                | 4.2.1  | GNU Radio                                                                                         | 25 |  |

|          |                | 4.2.2  | TI Software                                                                                       | 25 |  |

|          | 4.3            | Comp   | onents to Set Up GPP/DSP Based Applications                                                       | 26 |  |

|          |                | 4.3.1  | GPP Side Library                                                                                  | 27 |  |

|          |                | 4.3.2  | DSP-Side Executable                                                                               | 29 |  |

|          |                | 4.3.3  | Writing GNU Radio DSP-Based Blocks                                                                | 32 |  |

|          | 4.4            | GPP/   | DSP Communication Overhead Measurements                                                           | 34 |  |

| <b>5</b> | Exa            | mple . | Application Use                                                                                   | 38 |  |

|          | 5.1            | Consid | derations for OMAP Processor Based SDR Application                                                | 38 |  |

|          | 5.2            | PSCR   | Introduction                                                                                      | 39 |  |

|          | 5.3            | Embe   | dded PSCR                                                                                         | 39 |  |

|              | 5.4   | Beagle | eboard-Specific Issues                 | . 41 |

|--------------|-------|--------|----------------------------------------|------|

|              | 5.5   | Embe   | dded PSCR Implementation               | . 42 |

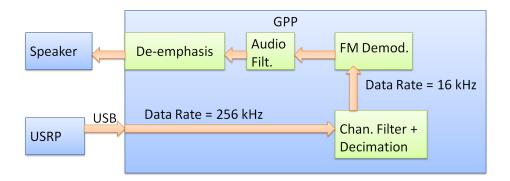

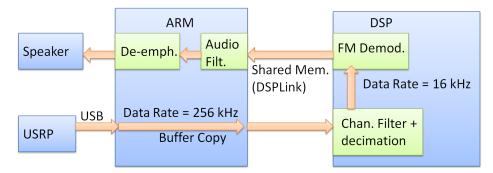

|              |       | 5.5.1  | Receive Flowgraph                      | . 43 |

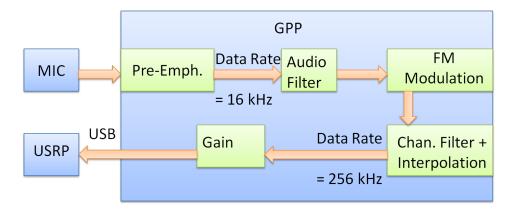

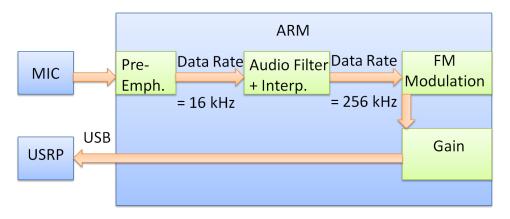

|              |       | 5.5.2  | Transmit Flowgraph:                    | . 44 |

|              |       | 5.5.3  | Gateway Flowgraph                      | . 47 |

|              | 5.6   | Embe   | dded PSCR Demonstration                | . 49 |

|              | 5.7   | Conclu | usions Regarding Overall System Design | . 50 |

| 6            | Con   | clusio | n and Recommendations for Future Work  | 52   |

|              | 6.1   | Summ   | nary                                   | 52   |

|              | 6.2   | Conclu | usion                                  | . 53 |

|              | 6.3   | Contri | ibutions                               | . 53 |

|              | 6.4   | Recon  | amendations for Future Work            | . 54 |

| $\mathbf{A}$ | Ope   | enEmb  | edded Setup Scripts                    | 55   |

|              | A.1   | Config | guration Script                        | 55   |

|              | A.2   | Config | guration Settings                      | 55   |

| в            | Ope   | enEmb  | edded Recipes                          | 57   |

|              | B.1   | Custo  | m Console Image Recipe                 | 57   |

|              | B.2   | GPP-   | Lib Shared Library Recipe              | 58   |

|              | B.3   | gr-dsp | O Class Recipe                         | 59   |

| С            | GP]   | P/DSI  | P Benchmark Code                       | 61   |

| D            | Per   | missio | n from Matt Ettus                      | 62   |

| Bi           | bliog | graphy |                                        | 63   |

# List of Figures

| 2.1 | Description of an SDR System Implementation.                                                             | 6  |

|-----|----------------------------------------------------------------------------------------------------------|----|

| 2.2 | Von Neumann Architecture                                                                                 | 8  |

| 2.3 | Harvard Architecture                                                                                     | 8  |

| 2.4 | Memory hierarchy and the associated relative cost and speed. $\ldots$                                    | 9  |

| 2.5 | How USRP can be Used in SDR Applications                                                                 | 11 |

| 2.6 | USRP Hardware Illustration, ©Matt Ettus. Used With Permission. See Appendix D Permission from Matt Ettus | 12 |

| 3.1 | OpenEmbedded Framework                                                                                   | 19 |

| 3.2 | DSPLink GPP/DSP Programming Approach.                                                                    | 20 |

| 3.3 | Codec Engine GPP/DSP Programming Approach                                                                | 21 |

| 4.1 | Development Workflow                                                                                     | 24 |

| 4.2 | TSK Based DSPLink                                                                                        | 28 |

| 4.3 | SWI Based DSPLink                                                                                        | 29 |

| 4.4 | GPP/DSP Message Format                                                                                   | 30 |

| 4.5 | The Programming Flow Between GNU Radio, GPP library, and DSP Executable                                  | 33 |

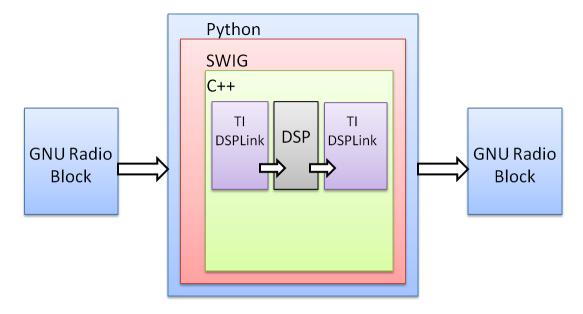

| 4.6 | DSP Based GNU Radio Block Abstraction                                                                    | 34 |

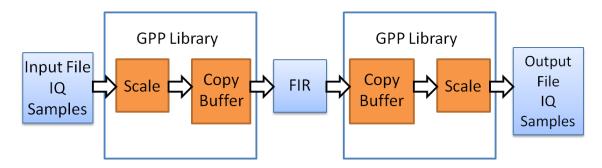

| 4.7 | GPP Timing Flowgraph                                                                                     | 35 |

| 4.8 | DSP Timing Flowgraph                                                                                     | 36 |

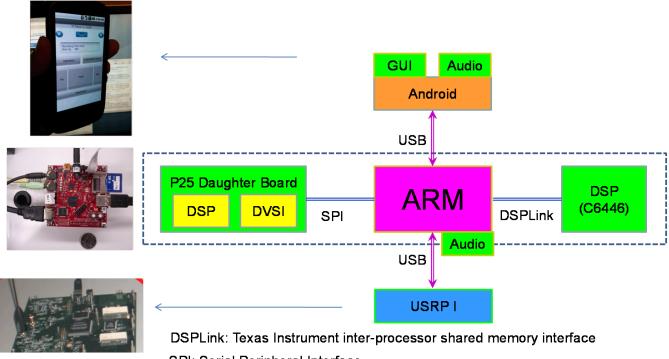

| 5.1 | PSCR Hardware Architecture                                                                               | 40 |

| 5.2 | Original PSCR GNU Radio Receive Flowgraph                                                                | 44 |

| 5.3  | Beagleboard Based GPP/DSP GNU Radio Receive Flowgraph                                                            | 44 |

|------|------------------------------------------------------------------------------------------------------------------|----|

| 5.4  | Original PSCR GNU Radio Transmitter Flowgraph                                                                    | 45 |

| 5.5  | Beagleboard Based Transmitter Flowgraph.                                                                         | 47 |

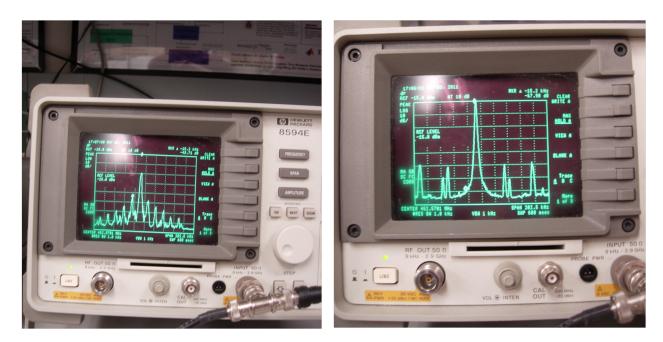

| 5.6  | Beagleboard-Based Transmitter Spectrum                                                                           | 48 |

| 5.7  | FRS-Based Transmitter Spectrum.                                                                                  | 48 |

| 5.8  | Beagleboard Based Transmitter FM Deviation and Spectrum                                                          | 49 |

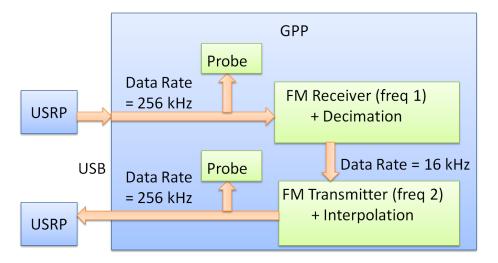

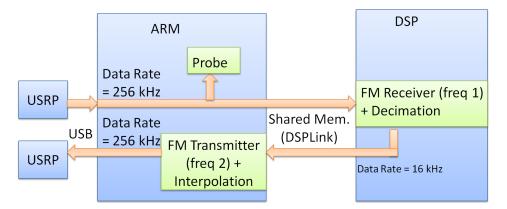

| 5.9  | Original GPP Based Gateway                                                                                       | 50 |

| 5.10 | Beagleboard Based Gateway                                                                                        | 50 |

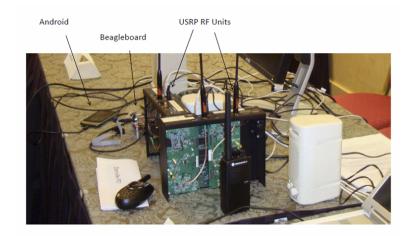

| 5.11 | $\operatorname{PSCR}$ setup at November 15-17, 2010, demonstrations on the Beagleboard $% \operatorname{PSCR}$ . | 51 |

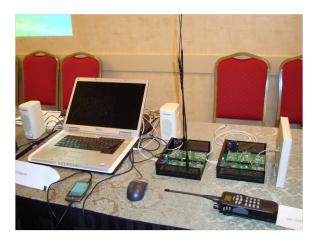

| 5.12 | The PSCR Gateway Function as Implemented on a Laptop Computer                                                    | 51 |

# List of Tables

| 4.1 | Summary of GPP/DSP based FIR filter execution times and DSP implemen-<br>tation speedup factor.               | 36 |

|-----|---------------------------------------------------------------------------------------------------------------|----|

| 4.2 | Summary of IQ data overhead in the flow graphs and DSP overhead for buffer copies and data format conversion. | 37 |

| 4.3 | GPP/DSP Interface Latency.                                                                                    | 37 |

## Acronyms

ADC Analog-to-Digital Converter  ${\bf ALU}\,$  Arithmetic Logic Unit **API** Application Programming Interface **ALSA** Advanced Linux Sound Architecture **CCS** Code Composer Studio **CE** Cognitive Engine CHNL DSPLink Channel Component **CORBA** Common Object Request Broker Architecture **CPU** Central Processing Unit **CR** Cognitive Radio **CWT** Center for Wireless Telecommunications **DAC** Digital-to-Analog Converter **DSP** Digital Signal Processor **DVSDK** Digital Video Software Development Kit EDK Embedded Development Kit EHCI Enhanced Host Controller Interface **EVM** Evaluation Module FCC Federal Communications Commission **FFT** Fast Fourier Transform

**FIR** Finite Impulse Response

FPGA Field-Programmable Gate Array

**FRS** Family Radio Service

**FSM** Finite State Machine

**GPMC** General-Purpose Memory Controller

GPP General Purpose Processor

${\bf GUI}$  Graphical User Interface

**IDE** Integrated Development Environment

**IIR** Infinite Impulse Response

**IQ** In-Phase and Quadrature

**ISE** Integrated Software Environment

**ITAR** International Traffic in Arms Regulation

JTAG Joint Test Action Group

**JTRS** Joint-Tactical Radio System Program

LPM Local Power Manager

MHAL Modem Hardware Abstraction Layer

**MMU** Memory Management Unit

**OE** OpenEmbedded

**OS** Operating System

**P25** Project 25

**POOL** DSPLink Pool Component

**PROC** DSPLink Proceessor Component

**PSCR** Public Safety Cognitive Radio

$\mathbf{PTT}\,$  Push to Talk

**RTW** Mathwork's Real-Time Workshop

| <b>SCA</b> Software Communications Architecture              |

|--------------------------------------------------------------|

| SCP Secure Copy                                              |

| $\mathbf{SDR}$ Software Defined Radio                        |

| $\mathbf{SFF}$ Small Form Factor                             |

| SoC System on a Chip                                         |

| <b>SPI</b> Serial Peripheral Interface                       |

| <b>SSH</b> Secure Shell                                      |

| <b>SWI</b> Software Interrupt                                |

| ${\bf SWIG}$ Simplified Wrapper and Interface Generator      |

| <b>TI</b> Texas Instrument                                   |

| TSK Task                                                     |

| ${\bf USRP}$ Universal Software Radio Peripheral             |

| <b>VLIW</b> Very Large Instruction Word                      |

| <b>XDAIS</b> eXpress DSP Algorithm Interoperability Standard |

## Chapter 1

## Overview

## 1.1 Introduction

Radios provide a means of basic wireless communication between individuals. While classic radios depend on the use of analog electronics, the introduction of software-based technologies in radios adds flexibility and allows the developers to integrate radios into various softwarebased systems. However, with the use of software in a system classically understood to be purely based on electronics, new challenges and issues are introduced related to the software, computational platforms, and interfaces used in realizing such system. For example, issues such as algorithm implementation, processor cache performance, and thread scheduling are important for software-based radios. A Software Defined Radio (SDR) is defined as a radio that "accommodates a significant range of RF bands and air interface modes through software" [1]. Basically, an SDR is able to realize significant portions of its radio functionality in software instead of hardware. By introducing software radio pieces in the critical radio transceiver path, the characterization of such radios involves the computational devices used, and the software implementation of the various radio pieces. Looking even beyond SDR, SDR technology is an enabler for Cognitive Radio (CR) technology where a CR is defined as "the integration of model-based reasoning with software radio" [1]. Whereas an SDR represents the implementation of a radio in software, CR represents a model-based representation for a radio, one which allows a radio to further configure itself to meet application needs and demands by observing its various *meters* which describe a radio's immediate performance and adjusting the radio's knobs through a cognitive cycle which utilizes artificial intelligence algorithms. The software that drives the cognitive cycle is identified as a Cognitive Engine (CE) [2].

Looking at the diverse applications for SDR, which range from mobile handsets to base station level radios, it is evident that various classes of power utilization and computational density are needed to cover the wide spectrum of SDR needs. For such applications, three main computing devices are available: GPP, DSP, and Field-Programmable Gate Array (FPGA). Therefore, planning for radio hardware from a computational perspective needs to account for the end goal application and ultimate usage scenario.

### 1.2 Motivation

By including computational devices other than GPPs in SDR system design, designers are able to create heterogeneous computing systems that address the application space more widely at various degrees of bandwidth, complexity, and power consumption, among other parameters. Heterogeneous computing systems can have a static configuration where the system of interest is known *a priori*. In such systems, the radio would need to monitor and tweak some of its parameters according to channel conditions and user demands while CR-based applications can also modify the underlying radio structure more drastically by creating new radio system configurations during runtime. As we can see in the first scenario, the radio would need to move data streams between the computational devices to implement the radio functionality and it also needs to read/write data for monitoring and tweaking radio activity during runtime. However, in the CR cases a radio might create and destroy functional blocks running on the various computational devices which can impose the need for the computational devices to reconfigure themselves completely during runtime. One of the primary motivations of this thesis is to provide a framework in which CRs can reconfigure their functional blocks within runtime for heterogeneous GPP/DSP processors.

### **1.3** Literature Review

In the scope of the research presented here, my purpose is to explore SDR application space in small form factor embedded platforms. The work is based on Texas Instrument processors intended for mobile applications which couple GPP/DSP cores on the same chip, *i.e.* the OMAP and DaVinci family of System on a Chip (SoC) processors. There are two main publicly available software suites for SDR development, OSSIE and GNU Radio. OSSIE is based on the Joint-Tactical Radio System Program (JTRS) Software Communications Architecture (SCA) specification which is intended to allow the reuse of radio applications for military radios [3] while GNU Radio is an open source SDR development tool [4]. These two development tools do not provide a readily available mechanism for integrating and developing SDR components to run on computing devices other than GPPs. JTRS attempted to extend the Common Object Request Broker Architecture (CORBA) specification (the standard used to address software component communication) to include DSPs and FPGAs by defining a Modem Hardware Abstraction Layer (MHAL) layer to allow compatibility and reuse of components. However, the specification is International Traffic in Arms Regulation (ITAR) restricted which prevents it from being publicly accessible [5]. In addition, [6]

3

explored the use of CORBA for FPGAs and discussed the overhead associated with it and how it can hinder the development of SDR systems on FPGAs. There are also some commercial applications that allow control and data exchange between GPP, DSP, and FPGA devices such as *ORBExpress* from OIS [7]. GNU Radio is primarily intended to run on desktop grade computers and does not lend itself to integrated FPGA and/or DSP designs. Some vendors provide proprietary FPGA/DSP interfaces and libraries for device communication such as the Lyrtech's Lyrio interface [8]. However, such proprietary interfaces and libraries can be a hurdle for porting and developing applications outside the realm of the vendor's platforms and development environment.

In terms of supporting radio reconfiguration for FPGAs, there is work which explores FPGA partial reconfiguration [9], [10], and [11] which supports the modification of parts of FPGA without disrupting the overall application running on the FPGA. In terms of FPGA partial reconfiguration, the work looks at how to modify the underlying FPGA fabric to allow the addition and modification of radio components. However, the work in this thesis explores modifying radio component on a softer level in DSPs, where it develops a token-based protocol which allows a GPP to pass configuration instructions to a connected DSP. The configuration instructions would not necessarily be able to add new functions that are not already available on the DSP. Instead, the idea is that the DSP would contain the necessary functions but lacks the associated parameters, e.q., filter coefficients, and it would also lack the radio component assembly configurations. Basically, the configuration instructions would allow a controlling program on a GPP to request radio configurations from the DSP and supply the necessary configuration parameters. There is also some work which proposes programmable architectures which cater to the power and performance needs of wireless protocols, e.g., SODA [12] and DPP core[13]. Such work explores processor architecture which might be more suited for wireless and communication applications than off-the-shelf processors, e.g., DSPs. In this thesis, my interest is how to allow soft radio reconfiguration in GPP/DSP based processors via software and not fundamental hardware alternatives and/or modifications to modern processors.

## 1.4 Goals

The work presented in this thesis is motivated by enabling SDRs to run on embedded platforms. The hardware selection is a Beagleboard connected to a first generation Universal Software Radio Peripheral (USRP) over USB. In order to realize radios on the Beagleboard, it is beneficial to incorporate the DSP in the data path for acceleration. The thesis explores a sample implementation of heterogeneous GPP/DSP based processors in realizing software radio implementations using the Texas Instrument (TI) OMAP processor. This work also involved incorporating this infrastructure with GNU Radio to make the DSP more readily available by being part of a well acclaimed SDR tool.

The goal of the thesis is to provide and characterize a mechanism to setup, configure, and

utilize a DSP to accelerate SDR application performance on GPP/DSP based processors. The interface would need to allow both processors to dynamically exchange both control messages and data streams for processing.

## 1.5 Outline

The thesis is organized as follows:

- SDR System Implementation: Discussion of the SDR system implementation, the various components needed, and focus on the computational devices involved in realizing SDR systems.

- **Software Tools:** A summary of the software tools used in the presented work and the development flow used.

- **DSP Management and Platform Support:** A discussion of how the elements in the contribution listing were developed.

- Example Application Use: A discussion of the process used to port the Public Safety Cognitive Radio (PSCR) to a TI OMAP based processor and the issues and challenges faced in the process.

- Conclusion and Recommendations for Future Work.

## 1.6 Publications

My work is described in the following publications:

- Almohanad S. Fayez, Qinqin Chen, Jeannette Nounagnon, and Charles Bostian, "Leveraging Embedded Heterogeneous Processors for Software Defined Radio Applications," *Wireless Innovation Forum Conference and Product Exposition*, December 2010.

- Rohit Rangnekar, Feng (Andrew) Ge, Alex Young, Mark D. Silvius, Almohanad Fayez, Charles Bostian, "A Remote Control and Service Access Scheme for a Vehicular Public Safety Cognitive Radio," in Vehicular Technology Conference Fall (VTC 2009-Fall), 2009 IEEE 70th, 2009, pp. 1-5.

- Feng Ge, Rohit Rangnekar, Aravind Radhakrishnan, Sujit Nair, Qinqin Chen, Almohanad Fayez, Ying Wang, and Charles W. Bostian, "A Cooperative Sensing Based Spectrum Broker for Dynamic Spectrum Access", in IEEE *Military Communications Conference, 2009. MILCOM 2009.*, pp. 1-7.

## Chapter 2

## **SDR System Implementation**

## 2.1 SDR System HW/SW

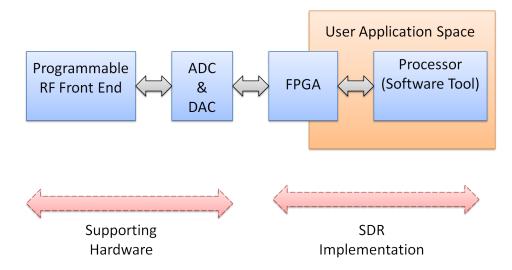

While SDR systems depend on software for radio implementation they also rely on some supporting hardware, as shown in Figure 2.1:

- **Supporting Hardware:** Includes the necessary hardware for transmitting and receiving the radio signal.

- The programmable RF front end that has user-tunable RF parameters.

- An Analog-to-Digital Converter (ADC) to digitize the analog RF signal and a Digital-to-Analog Converter (DAC) to generate an RF signal from a digital data feed.

- A device which performs decimation and downconversion for a receiver, to a manageable data rate where the stream can be processed. Also for a transmitter, the device performs interpolation and upconversion to RF. Usually an FPGA is used in managing the programmable radio front end, the ADC, and DAC.

- SDR Implementation Software: This is user written software which realizes the radio functionality; users typically have the choice of using FPGAs, DSPs, and/or GPPs. Please note that the FPGA can also include and run user applications in addition to managing the supporting SDR hardware. For GPPs, programmers have the option of using high-end desktop grade processors, *e.g.*, high-end Intel processors, or embedded-grade processors, *e.g.*, ARM processors. When programmers develop their software they have the option of writing a complete implementation from scratch or they can use software development frameworks. Available software development frameworks include: GNU Radio [4] and OSSIE [14]. Such frameworks allow programmers

Figure 2.1: Description of an SDR System Implementation.

to develop SDR applications by leveraging existing communication function libraries and to run those applications with supported programmable radio front-ends.

In terms of SDR implementation, there are three main computational devices available: FPGAs, DSPs, and GPPs. The work presented in this thesis focuses on GPP and DSP usages, so FPGAs usage will not be discussed. There are two main approaches for developing SDR applications: a classic method and the model-based design method.

- 1. Classic Approach: Developers would use individual chip maker's tools for each computational device. For GPP development developers can use the GNU tools available at no cost and are not restricted by manufacturer specific tools. For TI manufactored DSPs, the software tool available is Code Composer Studio (CCS) Integrated Development Environment (IDE). For Xilinx manufactured FPGAs, Integrated Software Environment (ISE) and Embedded Development Kit (EDK) are the main tools to target the FPGA. This method is supported by all SDR platforms.

- 2. Model-Based Design Approach: This approach allows developers to leverage the Mathworks Simulink tool to simulate and generate a system model for SDR applications. Simulink hides details related to running all the vendor specific tools discussed in the classic method. For Xilinx manufactured FPGAs, programmers are able to use FPGA cores provided by Xilinx or write their own custom cores; the FPGA bitstream is ultimately generated and synthesized through Xilinx's ISE software [15]. DSPs can be programmed through Mathwork's Mathwork's Real-Time Workshop (RTW) which is able to generate a C-based code and ultimately compile the C-code through CCS for TI manufactured DSPs.

## 2.2 Computational Device Considerations

In terms of computational devices, the discussion will evolve around computer architecture concepts of interest to processor performance for streaming SDR applications. The two types of processors discussed here are GPPs and DSPs where a DSP is a "special-purpose processor optimized for executing digital signal processing algorithms" [16] and a GPP is designed to address general-case computing and not a specific application. The following aspects will be discussed: memory architecture, addressing, and signal processing functionality.

#### 2.2.1 Memory Architecture

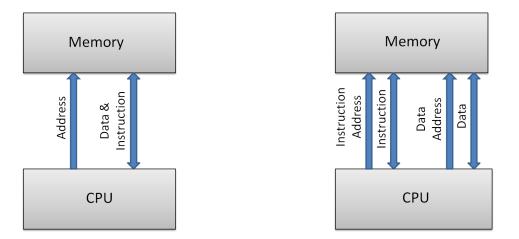

There are two main memory architectures: the Von Neumann (or Princeton) architecture and the Harvard architecture [17]. In the Von Neumann architecture, a Central Processing Unit (CPU) has two separate pathways to memory: one for specifying read/write memory addresses and another for reading/writing instruction and data to the specified memory addresses. If a program needs to add two numbers and write the result back to memory it would use:

- 1. A memory access cycle to retrieve the addition operator, by specifying instruction address.

- 2. Another cycle to retrieve the first operand, by specifying data address.

- 3. Another cycle to retrieve the second operand.

- 4. Another cycle to write the result back to memory.

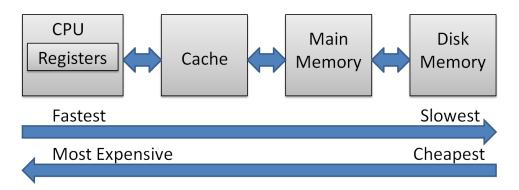

Please refer to Figure 2.2. With the Harvard architecture, there are two independent address pathways; one for data and another for instructions; and two more pathways, one for data read/writes and another for instruction reads. If a program needs to add two numbers and write the result back to memory, it would spend:

- 1. A memory access cycle to retrieve the addition operator, by specifying instruction address on the instruction bus. In the same cycle the processor can retrieve the first operand, by specifying the data address on the data bus.

- 2. Another cycle to retrieve the second operand.

- 3. Another cycle to write the result back to memory.

Please refer to Figure 2.3. In the Von Neumann architecture we can see that the pathways can only fetch data or instructions one at a time from memory. Memory access is essentially a bottleneck because of the shared pathways. Within the Harvard architecture it is possible to fetch both data and instructions in parallel since they travel on different pathways; the Harvard architecture is able to mitigate the inherent bottleneck in the Von Neumann architecture by physically separating data and instruction pathways.

Figure 2.2: Von Neumann Architecture

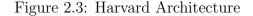

Memory accessibility is important in computing since it provides the means of retrieving instructions and reading/writing data as needed by programs. However, memory can be a scarce commodity; the faster the memory the more expensive it is and the slower the memory, the less expensive it is. Therefore it is important to balance memory speed and cost to provide running applications with acceptable memory performance at an acceptable cost. Memory hierarchy is used to reduce the memory access bottleneck and to balance memory speed and cost factors by placing the fastest memory closest to the CPU, this memory also corresponds to the smallest memory capacity footprint to save on cost. The slowest memory is kept farther away from the CPU though it would correspond to the largest amount of memory available because it is the cheapest. Figure 2.4 illustrates the discussed memory hierarchy. Data and instructions in programs demonstrate elements of *spatial* and *temporal* locality. Spatial locality means that if the CPU requests a few data elements, e.g., from a matrix, then it will probably need to access the subsequent matrix elements; by pre-fetching those elements and saving them in cache, the CPU will have the data readily available when it requests them in the future and it will not need to access main or external memory to retrieve them. Temporal locality means that if the CPU just fetched data elements, then the data should be kept close by because the CPU might need the same data again soon, e.q., for matrix multiplication. Exploiting locality of instructions and data, both temporal and spatial, together with the concept of memory hierarchy are important elements in mitigating memory latency issues in computing. The basic idea is to keep data and instruction being currently used on the fastest memory available, which means the memory closest to the

processor. This way when the data is needed the processor will not have to wait and retrieve it from slower memory thus mitigating memory latency. There are many other important aspects associated with memory hierarchy, such as how to determine what data should be put in cache, when should data be moved from one hierarchical level to the next, and how the physical data movement should be performed (which will not be discussed but the interested reader can refer to [16]).

Figure 2.4: Memory hierarchy and the associated relative cost and speed.

Memory architecture will not be used to distinguish GPPs and DSPs from each other because in modern times both processors leverage memory hierarchy to mitigate memory latency. However, in writing applications for both processors, it is important to be aware that memory access can be a system bottleneck regardless of what type of processor is used. Concepts related to memory architecture and hierarchy are of interest in this thesis because data processing has a dependency on memory accesses, since that is where data is saved, and also because shared memory is a common method to interface between processors.

#### 2.2.2 Addressing

DSPs provide addressing schemes that might not be found in GPPs - for example modulo addressing and bit-reversed addressing [18], which are useful for data processing applications. Modulo addressing provides the ability to create circular buffers where buffer indices will wrap around when the end of a buffer is reached instead of overstepping the buffer boundary or requiring the index to be reset manually. Bit-reversed addressing provides a memory addressing scheme aimed at speeding Fast Fourier Transform (FFT) calculations by providing direct mapping between input and output buffer indices.

#### 2.2.3 Signal Processing Functionality

The basic structure of many digital signal processing algorithms consists of multiplication and accumulation operations. Therefore, DSPs contain hardware multipliers in addition to accumulators as part of their architecture. Many DSPs are fixed point based and contain shifter circuits which help in scaling values and limiter circuits which set register values to all 1's when an overflow occurs [18]. Basically DSPs contain specialized circuitry to accelerate and support digital signal processing algorithms.

Even though GPPs are becoming more sophisticated in terms of signal processing performance they are designed to address general computational needs while DSPs are designed specifically to address the computational needs for signal processing.

## 2.3 Platforms

A platform is defined as "A common hardware denominator that could be shared across multiple applications" [19]. For the purpose of our discussion, an SDR platform strictly refers to the underlying hardware on which the SDR code runs. Three main type of devices will be discussed:

- 1. **Programmable Radio Front-End:** These devices only include the supporting hardware necessary for an SDR. They still need to be coupled with a computational platform to allow the realization of an SDR system.

- 2. Computational Platforms: These devices are just raw computational platforms; they still need to be coupled with a programmable radio front-end.

- 3. Integrated SDR Systems: These devices include an integrated radio front-end with a computational platform and do not require an external supporting hardware.

The following is a summary of the devices considered during the course of my thesis work.

#### 2.3.1 Programmable Radio Front-End

#### Universal Software Radio Peripheral

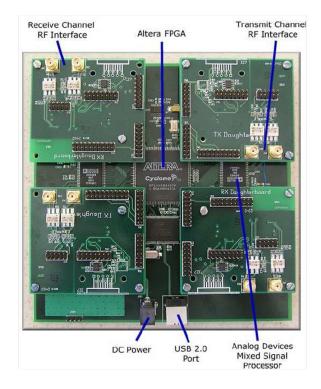

The USRP [20] contains an Altera Cyclone FPGA and uses a USB 2.0 link to transfer digitized RF data for processing. The USRP acts as the digital baseband and IF receiver of a radio. Essentially a USRP either:

• Receives an analog RF signal at a user specified frequency, decimates and downconverts the data using the FPGA to a manageable rate where it can transmit it to a computer over USB 2.0 for processing.

• Transmits an analog RF signal at a user specified frequency after interpolating and upconverting the digital user signal supplied by the computer over USB 2.0.

Figure 2.5 illustrates how the USRP can be used in implementing an SDR. There are many RF daughterboards that operate at different frequencies from which users may choose. The USRP's FPGA is intended to act as part of the radio front-end and the base USRP FPGA firmware occupies most of the FPGA, leaving little extra space for users to add user defined circuits. The base FPGA image performs decimation and interpolation necessary to move In-Phase and Quadrature (IQ) data to a host computer and have the computer implement the radio functionalities [21].

The USRP can be used in developing SDR systems using either the GNU Radio or OSSIE framework or with custom code. Developers just need to decide on a computational platform to use in conjunction with the USRP, whether it be a desktop/laptop computer or an embedded platform connected over USB. [22] discusses in greater detail the use of USRPs for SDR applications.

Figure 2.5: How USRP can be Used in SDR Applications.

#### Universal Serial Radio Peripheral 2

The USRP2 contains a Xilinx Spartan 3 2000 FPGA and uses a 1000T Ethernet interface to transfer RF data for processing [23]. In essence it is similar to the USRP but has a

Figure 2.6: USRP Hardware Illustration, ©Matt Ettus. Used With Permission. See Appendix D Permission from Matt Ettus

different FPGA and a faster interface to the computational platform, 1000T versus USB 2.0. This version of the USRP contains a large enough FPGA to accommodate user defined logic in addition to the base FPGA image; the intention is to allow users to embed some SDR functionalities in the USRP itself. However, for the most part users still need to supplement the USRP 2 with an external computational platform.

#### 2.3.2 Computational Platforms

In selecting computational platforms for SDR system implementations there are a number of processors available with many platform variations. An obvious choice would be using a laptop or desktop computer; however, the scope of this thesis focuses on the usage of embedded processors so there will be no discussion about using desktop/laptop computers. In terms of narrowing down the processor choice, the discussion will be limited to the TI family of DaVinci and OMAP processors because they contain integrated GPP and DSP cores on the processor with a shared memory region that allows inter processor communication and data exchange.

#### DaVinci (DM6446) Evaluation Module

This evaluation module is provided by Spectrum Digital [24] contains the TI TMS320DM6446 processor, from the DaVinci processor family. The DM6446 is an SoC containing [25]:

- ARM9 GPP(ARM926EJ-S), which includes:

- Supports for 32-Bit and 16-Bit (Thumb Mode) instruction sets.

- DSP Instruction extension and single cycle MAC.

- ARM Jezelle Technology

- C64x+ Fixed-Point Very Large Instruction Word (VLIW) DSP

- Six Arithmetic Logic Units (ALUs) each supporting a single 32-bit, dual 16-bit, or quad 8-bit arithmetic per clock cycle.

- Two multipliers which support dual 16-bit x 16-bit multiplies of eight 8-bit x 8-bit multiplies per clock cycle .

- Video Imaging Co-Processors (VICP).

The ARM processor can operate up to 300 MHz and the C64x+DSP can operate up to 600 MHz, 256 DDR2 DRAM, 16 Mbytes of flash memory, 64 MBytes NAND flash, 4 MBytes SRAM, USB2 interface, 10/100 MBS Ethernet, IR remote interface, ATA interface, AIC33 stereo codec. The C64+ DSP is considered a VLIW processor because it contains multiple functional units, multipliers and ALUs, and the processor's instruction set "allows the specification of multiple operations per instruction" [26].

#### Beagleboard

The Beagleboard is intended as a low cost (<\$150) platform manufactured by Circuitco Electronics LLC that makes the TI OMAP3530 processor accessible to the open source community [27]. The TI OMAP3530 is intended for mobile graphic applications [28]; it is an integrated GPP/DSP processor combining an ARM Cortex-A8 GPP and a C64x+ DSP core. The Cortex-A8 is composed of an ARMv7 GPP with a NEON core and a multimedia acceleration SIMD coprocessor [29]. The C64x+ DSP is a 16-bit fixed-point VLIW DSP. The DSP contains eight independent functional units: six ALUs and two multipliers that support either four 16 x 16 bit multiplies or eight 8 x 8 bit multiplies [28]. The Beagleboard revision used in this work supports a host-side Enhanced Host Controller Interface (EHCI) USB driver which is needed to interface with first generation USRPs [30].

#### 2.3.3 Integrated SDR Systems

#### Lyrtech Small Form Factor (SFF) SDR Evaluation Module (EVM)

The Lyrtech SFF SDR EVM [8] contains two Xilinx Virtex-4 SX-35 FPGAs; one is dedicated for signal down conversion and another is reserved for application development. The Lyrtech SFF SDR contains a TI DM6446 processor composed of an ARM9 GPP core and a C64x+DSP core. A more detailed discussion of the processor will follow in a subsequent section.

While working on the Lyrtech to implement a coarse radio signal classifier, as discussed in [31], in collaborating with the author of [31], we were successful in using Simulink in simulating and synthesizing FPGA bitstreams. However, we were not successful in using the RTW to generate, compile, and load C-code (for the DSP) which would behave consistently with the simulation. The issue might have been that Lyrtech requires the usage of old versions of the Mathworks software for compatibility issues. In working with the Lyrtech SFF SDR we determined that generating the FPGA image in Simulink and writing the DSP code manually in CCS was the best approach for our application needs. We were able to exchange data between the FPGA and DSP by reading/writing to the buffers made available by the Lyrtech Application Programming Interface (API).

#### USRP E100

The USRP E100 [20] contains a Xilinx Spartan 3A-DSP1800 FPGA which is large enough to accommodate the base USRP FPGA image while leaving some free space for user defined circuits. The E100 also allows users to connect a Gumstix Overo, which basically contains the same OMAP3530 processor as the Beagleboard, to be used instead of a laptop or desktop computer as was the case with previous generation USRPs. In the E100, the Overo board is actually connected directly to the FPGA over the processor bus using the General-Purpose Memory Controller (GPMC) controller which mitigates the latency and overhead issues associated with the USB and Ethernet interfaces as seen in other USRP varieties. While the current E100 only supports the transfer of IQ data with the GPP, the driver can be rewritten to support data exchange with the DSP. Transferring IQ data directly with the DSP reduces the overhead of transferring the data from the GPP to the DSP.

The E100, which was released more recently, is a better suited platform for SDR applications than the Beagleboard and USRP combination. Unfortunately it was just recently released. The E100 is better suited because the processor is able to transfer IQ directly over the GPMC bus, an interface dedicated to external memory access which also allows data to be transferred directly to the DSP. The drawback of the E100 is that it only has space for one RF daughterboard instead of two as is found in the other USRP products.

## 2.4 SDR Platform Choice

In selecting an SDR platform, there are three selection criteria of interest.

- 1. **Integrated GPP and DSP core:** The interest in this thesis is to explore developing SDR applications in mixed GPP/DSP environments.

- 2. Allows the installation of Linux: Since the work will explore leveraging GNU Radio, an existing SDR framework, and coupling it with a GPP/DSP integrated processor being able to install a Linux operating system is important.

- 3. Functional USB/Ethernet drivers: Allows the integration of various peripherals to the SDR platform.

### 2.4.1 Integrated GPP and DSP core

All of the discussed integrated SDR and computational platforms have either DaVinci or OMAP TI processors. In terms of computational platforms, they must be coupled with a programmable radio front-end, such as the USRP and USRP2.

### 2.4.2 Allows the installation of Linux

The DaVinci and Beagleboard computational platforms allow Linux support. There are open source tools which are readily available to load Linux on both platforms and there is existing community support for them. The Lyrtech SFF SDR platform allows Linux installation but configuring the integrated radio front-end is not fully supported since the Linux installation is not officially supported by the manufacturer. Also the Lyrtech interface between the FPGA/DSP/GPP is proprietary, which can hinder the development of SDR applications outside the scope and work environment of the manufacturer. The USRP E100 provides Linux support and there exists community support; however, since the platform was not available during the selection process it was not considered during the SDR platform selection process.

At this point the SDR platform contenders are a combination of Beagleboard/DM6446 platforms with either a first or second generation USRP.

### 2.4.3 Functional USB/Ethernet drivers

While I was successful in running Angstrom Linux distribution, TI's GPP/DSP communication interface, and GNU Radio on the DM6446, there was a problem in the USB host

side driver implementation, which is necessary for the DM6446 to communicate with a first generation USRP. The board is not able to connect readily to a USRP2 because it lacks a Gigabit Ethernet interface and it is not able to communicate with a first generation USRP due to a bug in the host side USB driver implementation. The DM6446 board supports the VLYNQ interface, a TI proprietary high speed serial interface which can be used to communicate directly with the FPGA in the USRP2. However, in this work I am more focused on the programming SDR applications across the GPP and DSP so I elected not to use this platform.

With the Beagleboard I was successful with installing Linux, TI GPP/DSP communication interface, and GNU Radio. Also the USB host side driver for the Beagleboard is functional and is able to communicate with a first generation USRP. The Beagleboard does not have an integrated Ethernet interface but there are expansion boards, the *Zippy* and *Zippy2* boards, manufactured by Tin Can Tools [32] which add 10T or 100T ethernet support respectively. I was able to connect a first generation Zippy board and install all the necessary drivers to have a fully functional Ethernet interface. Since the Beagleboard does not have 1000T Ethernet support it cannot be used in conjunction with a USRP2 which leaves a first generation USRP as the only available programmable front-end.

In selecting an SDR platform, developers need to have an idea of what type of systems they are interested in creating and what system and platform criteria are important. In terms of criteria discussed for selecting an SDR platform, the hardware platform of choice was a Beagleboard connected over USB to a USRP for the reasons listed above.

## Chapter 3

## Software Tools

To implement SDR applications, developers can write a customized system implementation from scratch. However, it is possible to leverage an existing toolkit, *e.g.*, GNU Radio or OSSIE. A toolkit provides a set of functionalities and tools needed to build applications for a specified application. In terms of SDR, a toolkit would include the necessary communication, signal processing, networking, and other supporting functionalities.

Since the SDR development will be on an embedded platform (the Beagleboard in this case) a desktop or laptop computer is still needed to build the operating system, the filesystem, and the device drivers for the embedded platform. Basically, an embedded platform development framework is needed where a framework constitutes an integrated environment for setting up, generating, and developing software for a particular task. The framework would also allow the compilation of various software for the embedded platform, where the process would be identified as *cross compilation* versus *compilation* since a desktop and/or laptop, employing an x86 based processor, is used to compile code which runs on a different *target*, or platform.

The Beagleboard is the embedded target; it has an OMAP processor which includes a GPP and DSP core. Both cores contain a shared memory region that enables inter-processor communication which occurs by reading and writing to the shared memory region. While developers can create their own protocols, some vendors provide a toolkit which handles such details and developers can incorporate the toolkits in their applications.

The software used in building SDR applications on the Beagleboard can be divided into three main categories:

- Embedded Development Framework.

- GPP/DSP Development Tools and Interface Toolkit.

- SDR Software Toolkit.

The embedded framework would include the GPP/DSP development tools and interface toolkit in addition to the SDR software tool. Basically the framework would set up an environment that makes it seem as if code intended for the Beagleboard is being compiled and generated on the Beagleboard itself instead of being done on a separate computer. The compilation tools themselves are downloaded and installed from separate sources but the framework makes them work in cohesion. The same is also true for the SDR software toolkit. It is separate from the embedded framework, it is just that the framework allows the software to be compiled and linked against the target platform.

## 3.1 Embedded Development Framework

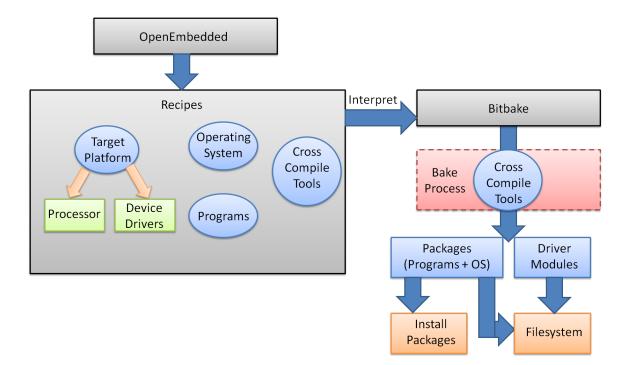

The framework allows an integrated environment allowing the cross compile tools to compile programs, compile drivers, compile the operating system, generate packages, and generate a filesystem for an embedded target, or platform, from a host development computer- the developer's laptop/desktop. The embedded development framework used is OpenEmbedded (OE) [33]. Figure 3.1 provides a general overview of how the framework works and how it can be employed by developers. Where OE provides a set of instruction, or *recipes*, which are read and executed via *Bitbake* and the necessary compilation tools to generate the final package binaries and filesystem. OE provides information about supported embedded platforms and the various environments which can be set for them. A developer is able to identify the following:

- Embedded platform, or *machine*: In this case the machine is the Beagleboard. The machine definition implies two things.

- 1. The processor used; the OMAP3530 processor in the Beagleboard case.

- 2. The devices used; such as the network devices, external memory chip, USB chip, sound chip, ... etc. The device definition allows the framework to select and compile the appropriate device drivers for the platform.

- **Operating system:** In this case the Operating System (OS) used is Angstrom, a Linux based distribution.

- **Compiler:** The OE framework uses the GNU toolchain for cross compilation and the user is able to specify specific versions of the GNU toolchain for OE to download.

OE contains a set of *recipes*, basically directions, for the framework. Recipes would include information such as:

• The Internet address from which application source code can be downloaded.

Figure 3.1: OpenEmbedded Framework.

- Directions on how to cross compile source code.

- Directions on how to put compiled source code into packages so developers can install them on their embedded platforms.

The application which ultimately reads the recipes is *Bitbake*. Bitbake essentially parses the recipe and implements the various commands and instructions identified in it, also known as *baking* the recipe. Bitbake would employ the cross compilation tools for the embedded platform's processor.

Developers are able to identify individual packages for *baking* or images. An image essentially identifies things such as: should the OS be Graphical User Interface (GUI) based or non-GUI based, or console-only, and what type of programs should be pre-installed for the user. The image would ultimately provide a compiled OS, device drivers, and a filesystem. Any packages *baked* but not identified in the image recipe must be installed manually by the developer on the embedded target.

## 3.2 GPP/DSP Development Tools and Interface Toolkit

The OE framework previously discussed is an integrated framework for GPP based embedded development. Therefore, compiling and managing any DSP and/or GPP/DSP interface code

should be handled separately, in a different directory, from OE. The following is a list of the DSP and inter-processor communication tools which are needed by developers to maintain separately from OE write DSP/GPP-based applications:

- The DSP Compiler: It is downloaded as part of TI's *C6000 Code Generation Tools*. The compiler can be downloaded at no cost from TI's website [34].

- The OS: The OS used is DSP BIOS which is a lightweight real-time library that provides basic run-time functionalities. Examples of such functionalities include scheduling threads, handling I/O, and capturing information in real-time [35].

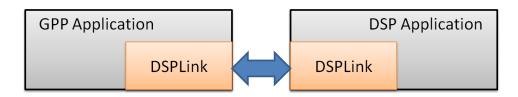

- DSPLink and the Codec Engine: The GPP and DSP communication is performed over their shared memory region. For this work, DSPLink is used, a TI provided open source toolkit [36]. The toolkit provides a mechanism for basic processor control, data transfer, memory sharing/synchronization, and messaging, among other inter-process functionalities. Figure 3.2 illustrates how the communication between the processors occurs. DSPLink allows programmers to compile either a running executable or a static library. To install the TI toolkit and build the necessary DSPLink drivers, the instructions available on [37] were followed.

Figure 3.2: DSPLink GPP/DSP Programming Approach.

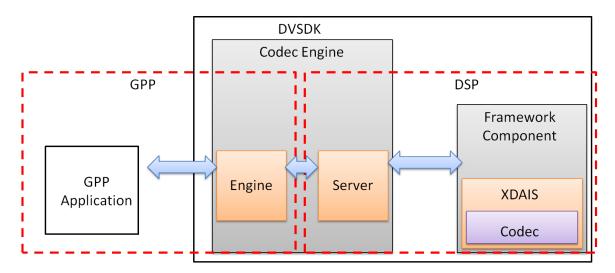

In terms of GPP and DSP communication, there is another mechanism provided by TI called the Codec Engine [38] [39], as shown in Figure 3.3. Using this method, a GPP application would utilize a Digital Video Software Development Kit (DVSDK) which integrates Codec Engine with other components needed to support DSP/GPP integration. The Codec Engine represents the core component of the DVSDK. There are two components of the Codec Engine, an *engine* component representing the GPP side of the system and a *server* component representing the DSP side of the system. The *framework component* is used to initialize and allocate resources associated with a DSP codec. The application developer is able to run various DSP based functions which adhere to TI specified standard interfaces such as eXpress DSP Algorithm Interoperability Standard (XDAIS). DSP codecs are able to allocate DSP resources by using the *framework component*.

Both GPP/DSP communication mechanisms allow the realization of SDR applications utilizing the DSP; however, the DSPLink interface is used because it is simpler and provides a more direct connection between the GPP and DSP cores. The Codec Engine approach can be more beneficial in a scenario where developers purchase commercial DSP implementation of signal processing algorithms where vendors would not make their source code available. In that scenario an application developer is able to utilize the Codec Engine to invoke the algorithms where with the DSPLink approach it is necessary to have the source code of the algorithms being invoked.

Figure 3.3: Codec Engine GPP/DSP Programming Approach.

TI also provides tools which are installed and used on top of the DSPLink and Codec Engine to further enhance the user experience, for example: C6Flo [40], C6Run [41], and C6Accel [42]. C6Flo is a graphical tool intended to configure the DSP graphically by loading drivers, configuring DSP peripherals, and connecting DSP blocks, or functions. The GUI tool ultimately generates C-code which is then fed to the DSP compiler. The motivation here is to make programming the DSP easier by using a GUI rather than manually setting it up by writing C-code. C6Run is intended to generate code for the DSP using portable C-code with the motivation to enable developers not familiar with DSP programming to generate and run DSP programs with C6Run taking care of the compiling the code and setting up the DSP. C6Accel allows developers to call functions which are part of the TI signal processing libraries using the Codec engine interface. Again, the user does not need to worry about the specifics of setting up the DSP or how to use the Codec engine APIs.

## 3.3 SDR Software Toolkit

GNU Radio is a software toolkit which allows developers to transmit and receive radio signals, when coupled with appropriate programmable radio front-ends, using software based radio implementations. Radios are implemented as *flowgraphs*; Python-language based files that instantiate individual functions, or *blocks*. The blocks are then connected through their

input/output ports, generating and feeding data streams between each other. When the flowgraph is first started, a scheduler which parses through the individual blocks is called. Each block is executed in a separate thread; the scheduler allocates the I/O buffers associated with each block, and determines a *firing* schedule for each block along with the number of data samples to move between the blocks.

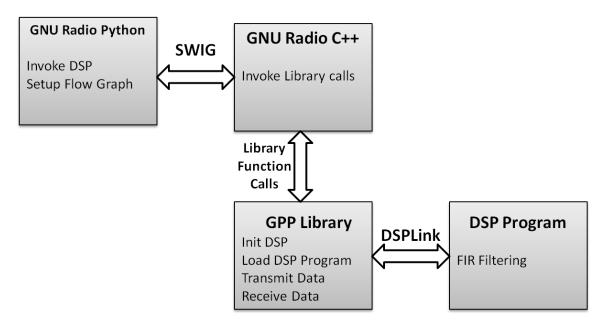

Please note that Python is used to set up and instantiate the radio flowgraphs; once a flowgraph starts, the actual implementation occurs in C++. GNU Radio utilizes the Simplified Wrapper and Interface Generator (SWIG) to allow communication and data exchange between Python and C++.

In order to make the DSP in the OMAP processor readily available for SDR applications, I elected to integrate the DSP into the GNU Radio framework [4]. The basic idea is to add new functional blocks to GNU Radio which are DSP based so GNU Radio applications utilizing TI OMAP processors are able to make use of the onboard C64x+ DSP by electing to use the DSP functions instead of the ARM GPP based ones.

## 3.4 Software Selection and Integration

There are many different software frameworks and toolkits involved in using and setting up an embedded platform; communicating between multi-core processors, GPP, and for creating SDR applications. In designing applications on embedded multi-core platforms it is important for developers to account for both the hardware and software needed to assure compatibility and consistency throughout the application development cycle. By using frameworks such as OE, developers are able to port and leverage existing GPP applications for embedded development. However, users should be aware that such applications might need to be tuned to run on embedded processors which are more resource constrained than desktop-grade processors. Considering that vendors may provide processor communication tools, SDR application developers need to justify increased overhead if they want to implement standards such as CORBA on top of what is already available.

The next chapters will explore how the described tools can be used to develop means of abstracting, or simplify, the cross GPP/DSP processing and communication which is needed for application development. Also an example SDR application will be constructed using the provided abstraction.

## Chapter 4

# DSP Management and Platform Support

This chapter discusses how an embedded platform can be used for creating SDR applications using heterogeneous multi-core GPP and DSP based processors. Embedded GPPs are not as computationally powerful as desktop-grade GPPs; therefore, in embedded SDR applications it is important to utilize heterogeneous computing platforms, a GPP coupled with a computing device intended for signal processing, for example, a DSP or FPGA. The chapter discusses the development environment of such embedded platforms and provides a sample example of an approach which integrates the GPP/DSP development and allows data and command communication between both processors.

### 4.1 Work Flow

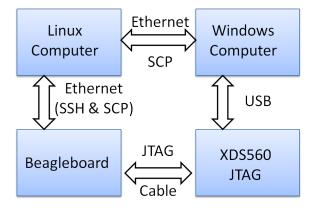

It is worth noting the work flow environment followed in the course of this project. A Linux computer is used for OpenEmbedded (OE) and for building the images, packages ,and drivers necessary for the Beagleboard. For loading the Angstrom image, an embedded Linux distribution, on the Beagleboard, an SD card was formatted to include two partitions. Formatting steps can be found at [43]. The first is the boot partition, which includes the bootloader, u-boot, the kernel, and OMAP3530 initialization files. The second partition includes the file system and the Beagleboard drivers; this is the partition used while running and developing applications on the Beagleboard.

After successfully running an Angstrom image on the Beagleboard, I use the Linux application Secure Shell (SSH) to remote log into the Beagleboard over Ethernet and interact with it, and I use Secure Copy (SCP) to transfer files and packages to and from the Beagleboard. In order to add Ethernet capability to the Beagleboard, I added the Zippy expansion board manufactured by Tin Can Tools [32]. A Linux computer is used for compiling the DSPLink code, GNU Radio, and the developed DSP based GNU Radio blocks, which are created as part of the *gr-dsp* class. However, to debug DSP applications, it is necessary to use a Joint Test Action Group (JTAG) and in order to use JTAG, TI's Code Composer Studio (CCS) development environment has to be used. However, CCS only runs on a Windows based computer. Another Windows based computer is used with parallel installation of all the TI software needed for development. The CCS used is version 3.3 with service package 12 installed. When DSP debugging is necessary, the DSP program source code is synched to the Windows machine so CCS and the JTAG can be used.

Figure 4.1: Development Workflow

## 4.2 Platform Setup

OpenEmbedded (OE) is the framework used in cross compiling the operating system, software packages, drivers, and generating the file system. In order to set up OE, users need to write a script to set up the OE environment defining the base OE directory. The user also needs to define a configuration file to specify the embedded target which will be used, the desired operating system for the target, and any optional preferences which include parameters such as the preferred Linux kernel or particular versions of packages which will be cross compiled. The configuration file and script are included in Appendix A.

The OS of choice was Angstrom, mainly because there is existing support for GNU Radio and the USRP on it. The Angstrom image used a console based image versus a GUI enabled image because I wanted to reduce the install image to the bare necessities for running GNU Radio and to utilize the DSP. This way we ensure that the processor will be mostly used for radio processing and not for miscellaneous unnecessary tasks; also that the image size footprint is as small as possible.

If developers need any more packages added to the console-only installation of Angstrom, *e.g.*, GNU Radio, they would need to cross-compile the packages using OE, download the

generated packages on the Beagleboard, and install them individually, along with all dependent packages, e.g., GNU Radio needs Python. The process of installing individual packages to the Beagleboard along with all of the dependent packages can be very cumbersome. This is particularly true in this case because console-image is minimalist, meaning it is missing a lot of packages which are typically found in a desktop installation of Linux. So in order to install GNU Radio on the Beagleboard, users would have to install all the packages that GNU Radio depends on before installing GNU Radio itself. Ultimately, I wrote a recipe based on the OE console recipe which includes the package dependencies needed to run GNU Radio and the necessary TI support drivers. The benefit of developing a custom image recipe is that it allows OE to generate an image that contains all the packages of interest. In this case the image will have GNU Radio installed and the TI toolkits with all their dependent packages pre-installed; the developed image is named *console-image-cwt-image*. The OE recipe developed for the *console-image-cwt-image* is included in Appendix B and can be used to replicate the Angstrom installation used in this thesis. To generate the image, users can run bitbake followed by the image name, bitbake console-image-cwt-image and the generated kernel, filesystem, and device drivers can be found in the OE tree under the *deploy* directory.

When using OE, users would select either the OE stable or the unstable branch. The unstable branch corresponds to recipes of the latest software releases, *e.g.*, compile tools, operating systems, drivers, and other programs. The latest releases would fall under the unstable branch because they have not been released as long as some of their other older more *stable* releases. The stable branch would contain older releases of the same software; they fall under the stable branch because the assumption is that since they have been available for a longer period of time they would have fewer bugs and be more *stable*.

### 4.2.1 GNU Radio

The GNU Radio recipe used is from the stable OE branch, which uses an older GNU Radio 3.2.1 versus the current 3.4 version. While an install from GNU Radio using the unstable OE branch was successful, there were some issues associated with the USRP.

### 4.2.2 TI Software

To install the TI DSPLink software, the directions from [37] are used. In order to run cross GPP/DSP applications the following software packages are needed: DSPLink, Codec Engine, Local Power Manager (LPM), C6000 Code Generation Tools, XDC Tools, and DSP BIOS. The Codec Engine and XDC tools are not used but they have to be installed to fulfill package dependency requirements. The LPM tool is needed mainly to power up/down the DSP, a necessary step because the DSP has to be reset between program loads due to a bug in the OMAP3530 processor [44]. It is possible to use the TI software in the OE build directory to write applications, but I consider it wise to make duplicate installations outside

of the OE install tree so user code would not be lost in case of a rebuild of the OE tree which is necessary at times when major updates are made to the OE repository.

DSPLink is essentially an open source library containing functions and constructs that enable communication between the GPP and DSP over the shared memory region. After installing the package, users need to deallocate memory from Angstrom; the freed memory can be used by DSPLink. Basically, the Beagleboard has 128MB of RAM and the default bootloader setting is to reserve all 128MB of RAM for the operating system but in this case DSPLink needs some of the RAM for the GPP/DSP communication interface. Using this memory region, DSPLink is able to manage data structure and resource allocation, allowing communication and data exchanges between both processors. The memory mapping needs to be modified from the u-boot, the bootloader, by changing the *bootargs* variable. The *mem=* variable is passed to determine the amount of RAM specified for the kernel. The memory mapping suggested by [37] is mem=80M which allocates 80MB for Angstrom. Since the Beagleboard has 128MB of RAM this leaves 48MB of unallocated memory to be used by DSPLink. It is important to specify this parameter or DSPLink will fail when attempting to allocate memory.

## 4.3 Components to Set Up GPP/DSP Based Applications

Three main components are required to allow GPP/DSP based SDR applications to run on the Beagleboard:

- 1. **GPP Side Library:** The GPP side library is responsible for abstracting the DSPLink function calls. For example, it would provide a function call to initialize the DSP without exposing the initialization details to the user. This library also provides function calls which allow data and messages to be exchanged between the GPP and DSP without exposing the details of the interface.

- 2. **DSP Side Executable:** The executable is a DSP program which can receive requests from the GPP to execute particular signal processing functions and is able to handle receive a stream of data for processing and send the processed data back to the GPP.

- 3. GNU Radio DSP-Based Blocks: To allow DSP-based blocks to be integrated with GNU Radio, new GNU Radio blocks are developed which through the discussed GPP side library are able to transmit requests for particular signal processing functions, send data streams to the DSP for processing, and receive the processed data from the DSP.

### 4.3.1 GPP Side Library

The GPP library currently uses three components from DSPLink:

- (a) **PROC**: the processor component.

- (b) **POOL**: the shared memory configuration and management component.

- (c) **CHNL**: the channel component.

The PROC component is used to initialize the DSP processor, load DSP executables, and stop DSP execution; basically it allows users to setup and load the DSP. The POOL component configures and synchronizes the shared memory regions between the GPP and DSP necessary for inner-processor data transfers. The CHNL component instantiates a logical data transfer link, or channel, between the GPP and DSP. While the CHNL component manages the logical data link between the DSP and GPP, the POOL component manages the physical memory used for the CHNL component including all the necessary memory allocation, synchronization, and address translation between the GPP and DSP. The GPP library essentially abstracts the DSPLink function calls necessary to initialize the DSP, instantiate the shared memory region, create the channel constructs, and the physical exchange of data back and forth with the DSP.

The GPP library abstracting the DSPLink interface performs five main functions:

- (a) **Initialize DSP**: Initialize the DSP.

- (b) **Transmit Data (Complex)**: Send complex IQ data to the DSP.

- (c) **Receive Data (Complex)**: Receive complex IQ data from the DSP.

- (d) **Transmit Data (Real)**: Transmit real data to the DSP.

- (e) **Receive Data (Real)**: Receive real data from the DSP.

- (f) **Clear DSP**: Called when the user application does not need the DSP anymore. It deallocates DSP specific resources and buffers that were allocated by the DSP initialization function.

It is necessary to support functions for moving complex IQ and real data because radio transmitters and receivers can have a complex IQ and/or real data paths. When developers use any of the above functions they need to specify a pointer to the transmit or receive buffers, buffer size, interpolation factor, decimation factor, a scaling factor, and a block ID tag. The scaling factor is used to identify the fixed point representation, or Q-Format. Since the DSP is fixed point, data needs to be converted from floating point to fixed point format before transmitting it to the DSP. The GPP library takes care of the data type conversion by taking the scaling factor and multiplying values by  $2^{scale}$  before sending the data to the DSP, and it also converts received data from the DSP back to floating point format by dividing by  $2^{scale}$ . The GPP/DSP interface is able to handle transmitting/receiving 8192 16-bit real data points or 4096 16-bit complex data points at a time because of a DSPLink buffer size restriction. Therefore in case buffers sizes exceed the limit they are fragmented.

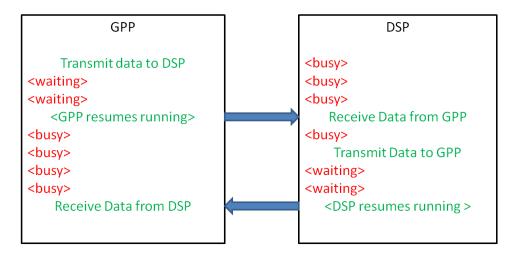

DSPLink allows programs to be either Task (TSK) based or Software Interrupt (SWI) based. TSK based programs are synchronous, meaning that processors will make *blocking* function calls to each other. As shown in Figure 4.2, when the GPP wants to communicate data to DSP, it will *block*, or wait, until the DSP is ready. Also when the DSP wants to send data to the GPP it will block until the GPP is ready to receive the data from the DSP. As the figure shows, when a processor is in the middle of a blocking transmit or receive function, it is wasting time that can be used to compute instead of waiting.

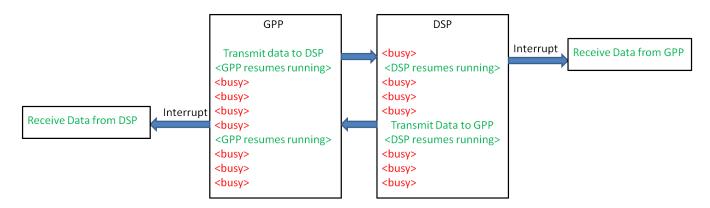

Figure 4.2: TSK Based DSPLink

In the SWI mode, the GPP transmit function actually causes a software interrupt in the DSP. The interrupt allows the DSP to receive data without the GPP having to block. When the DSP wants to transmit data to the GPP it causes a software interrupt on the GPP and the GPP receives the data without having the DSP block. While the current design is TSK-based, part of the future work is to make it SWI-based.