### On Best-Effort Utility Accrual Real-Time Scheduling on Multiprocessors

Piyush Garyali

Thesis submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

> Master of Science in Computer Engineering

Binoy Ravindran, Chair Paul E. Plassmann Robert P. Broadwater

July 16, 2010 Blacksburg, Virginia

Keywords: Multiprocessor Real-Time Scheduling, Utility Accrual Scheduling, Time/Utility

Functions, Real-Time Linux

Copyright 2010, Piyush Garyali

We consider the problem of scheduling real-time tasks on a multiprocessor system. Our primary focus is scheduling on multiprocessor systems where the total task utilization demand, U, is greater than m, the number of processors on a multiprocessor system—i.e., the total available processing capacity of the system. When U > m, the system is said to be overloaded; otherwise, the system is said to be underloaded.

While significant literature exists on multiprocessor real-time scheduling during underloads, little is known about scheduling during overloads, in particular, in the presence of task dependencies—e.g., due to synchronization constraints. We consider real-time tasks that are subject to time/utility function (or TUF) time constraints, which allow task urgency to be expressed independently of task importance—e.g., the most urgent task being the least important. The urgency/importance decoupling allowed by TUFs is especially important during overloads, when not all tasks can be optimally completed. We consider the timeliness optimization objective of maximizing the total accrued utility and the number of deadlines satisfied during overloads, while ensuring task mutual exclusion constraints and freedom from deadlocks. This problem is NP-hard. We develop a class of polynomial-time heuristic algorithms, called the *Global Utility Accrual* (or GUA) class of algorithms.

The algorithms construct a directed acyclic graph representation of the task dependency relationship, and build a global multiprocessor schedule of the zero in-degree tasks to heuristically maximize the total accrued utility and ensure mutual exclusion. Potential deadlocks are detected through a cycle-detection algorithm, and resolved by aborting a task in the deadlock cycle. The GUA class of algorithms include two algorithms, namely, the Non-Greedy Global Utility Accrual (or NG-GUA) and Greedy Global Utility Accrual (or G-GUA) algorithms. NG-GUA and G-GUA differ in the way schedules are constructed towards meeting all task deadlines, when possible to do so. We establish several properties of the algorithms including conditions under which all task deadlines are met, satisfaction of mutual exclusion constraints, and deadlock-freedom.

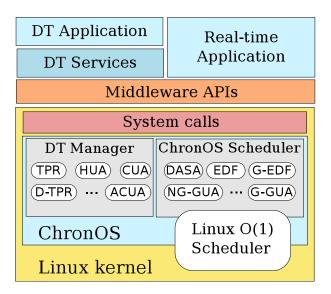

We create a Linux-based real-time kernel called ChronOS for multiprocessors. ChronOS is extended from the PREEMPT\_RT real-time Linux patch, which provides optimized interrupt service latencies and real-time locking primitives. ChronOS provides a scheduling framework for the implementation of a broad range of real-time scheduling algorithms, including utility accrual, non-utility accrual, global, and partitioned scheduling algorithms.

We implement the GUA class of algorithms and their competitors in ChronOS and conduct experimental studies. The competitors include G-EDF, G-NP-EDF, G-FIFO, gMUA, P-EDF and P-DASA. Our study reveals that the GUA class of algorithms accrue higher utility and satisfy greater number of deadlines than the deadline-based scheduling algorithms by as much as 750% and 600%, respectively. In addition, we observe that G-GUA accrues higher utility than NG-GUA during overloads by as much as 25% while NG-GUA satisfies greater number of deadlines than G-GUA by as much as 5% during underloads.

This work was supported by the US National Science Foundation CCF (Software and Hardware Foundations) under Grant 0915895.

# Dedication

I dedicate this thesis to my wife, Kalpana.

Without your support this would not have been possible.

## Acknowledgments

I would like to thank my advisor, Dr. Binoy Ravindran, for his help and guidance on both technical and personal topics. It has been an honor to work under him and I am highly indebted to him for his trust in me.

I would also like to thank Dr. Paul Plassmann and Dr. Robert Broadwater, for serving on my committee and providing their valuable feedback and direction. In addition, I would like to thank all of my colleagues at the real-time systems lab. I would particularly like to thank Matthew Dellinger and Sherif Fahmy for their support and encouragement. It was a pleasure to work with them and make ChronOS a reality.

Finally, I would like to thank my family and friends for all the love and support they have given me, without which this thesis would not have been possible.

All figures in thesis are the work of the author, unless specified otherwise.

# Contents

| 1        | Intr | roduction                                            | 1  |

|----------|------|------------------------------------------------------|----|

|          | 1.1  | Timeliness Model                                     | 2  |

|          | 1.2  | Multiprocessor Real-Time Scheduling                  | 4  |

|          | 1.3  | Multiprocessor Real-Time Scheduling During Overloads | 6  |

|          | 1.4  | Research Contributions                               | 7  |

|          | 1.5  | Thesis Organization                                  | Ĉ  |

| <b>2</b> | Rel  | ated Work                                            | 10 |

|          | 2.1  | Classification Based on Degree of Task Migration     | 10 |

|          | 2.2  | Classification Based on Utilization Load             | 11 |

|          | 2.3  | Summary                                              | 12 |

| 3        | Mo   | dels and Objective                                   | 14 |

|          | 3.1  | Thread Model                                         | 14 |

|          | 3.2  | Timeliness Model                                     | 14 |

|          | 3.3  | Resource Model                                       | 15 |

|          | 3.4  | Processor Model                                      | 15 |

|          | 3.5  | Abort Model                                          | 15 |

|          | 3.6  | Scheduling Objective                                 | 16 |

| 4        | The  | e GUA Class of Real-Time Scheduling Algorithms       | 17 |

|          | 4.1  | Ensuring Mutual Exclusion                            | 17 |

|   | 4.2 | Maximizing Accrued Utility                                   |

|---|-----|--------------------------------------------------------------|

|   | 4.3 | Deadlock Detection and Resolution                            |

|   | 4.4 | Assigning Zero In-degree Phases to Processors                |

|   | 4.5 | Data Structures and Auxiliary Functions                      |

|   |     | 4.5.1 Data Structure for Timeliness Model                    |

|   |     | 4.5.2 Data Structure for Resource Model                      |

|   |     | 4.5.3 Auxiliary Functions                                    |

|   |     | 4.5.4 Creation of DAG with Detection/Resolution of Deadlocks |

|   | 4.6 | Non-greedy Global Utility Accrual (NG-GUA)                   |

|   | 4.7 | Greedy Global Utility Accrual (G-GUA)                        |

|   | 4.8 | Algorithm Properties                                         |

| _ | CI. |                                                              |

| 5 |     | conOS Real-Time Linux 37                                     |

|   | 5.1 | Background                                                   |

|   | 5.2 | Architecture                                                 |

|   |     | 5.2.1 PREEMPT_RT Real-Time Patch                             |

|   | 5.3 | ChronOS Real-Time Scheduler                                  |

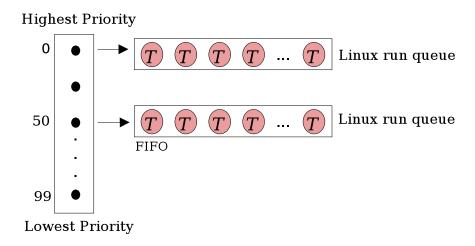

|   |     | 5.3.1 Priority Bit-map and Run-queues                        |

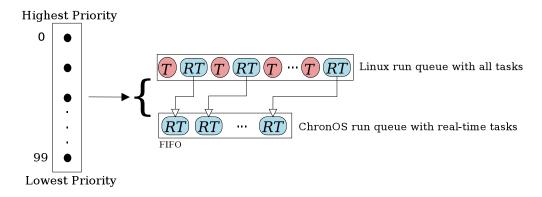

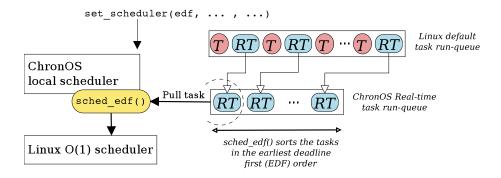

|   |     | 5.3.2 Scheduling Real-Time Tasks                             |

|   | 5.4 | Multiprocessor Scheduling                                    |

|   |     | 5.4.1 Partitioned Scheduling                                 |

|   |     | 5.4.2 Global Scheduling                                      |

|   |     | 5.4.2.1 Application Concurrent Scheduling Model              |

|   |     | 5.4.2.2 Stop-the-World Scheduling Model                      |

|   |     | 5.4.3 Mapping Tasks to Processors                            |

|   | 5.5 | Implementing Scheduling Algorithms in ChronOS                |

|   |     | 5.5.1 Single-processor Scheduling                            |

|   |     | 5.5.2 Multiprocessor Scheduling                              |

|   |     |                                                              |

| 6            | Exp | oerime: | ntal Results                                      | 52  |

|--------------|-----|---------|---------------------------------------------------|-----|

|              | 6.1 | Exper   | imental Setup                                     | 52  |

|              |     | 6.1.1   | Platform Specifications                           | 52  |

|              |     | 6.1.2   | Test Application                                  | 52  |

|              |     | 6.1.3   | Performance Parameters                            | 53  |

|              | 6.2 | Result  | ts Without Dependencies                           | 54  |

|              |     | 6.2.1   | Comparison with Global Scheduling Algorithms      | 54  |

|              |     |         | 6.2.1.1 Two-core Platform Results                 | 56  |

|              |     |         | 6.2.1.2 Four-core Platform Results                | 67  |

|              |     |         | 6.2.1.3 Eight-core Platform Results               | 78  |

|              |     | 6.2.2   | Comparison with Partitioned Scheduling Algorithms | 85  |

|              | 6.3 | Result  | ts With Dependencies                              | 90  |

|              |     | 6.3.1   | Varying CPU utilization Load                      | 91  |

|              |     | 6.3.2   | Varying Lock Critical Section Length              | 97  |

|              |     | 6.3.3   | Varying Number of Locks per Task                  | 100 |

|              | 6.4 | Overh   | nead Measurements                                 | 103 |

|              | 6.5 | Concl   | usions                                            | 107 |

| 7            | Cor | nclusio | ns and Future Work                                | 108 |

|              | 7.1 | Contr   | ibutions                                          | 111 |

|              | 7.2 | Future  | e Work                                            | 111 |

|              |     | 7.2.1   | Parallelizing Schedule Creation                   | 111 |

|              |     | 7.2.2   | Reducing Scheduling Overheads                     | 112 |

|              |     | 7.2.3   | Cache-Aware Algorithms                            | 112 |

|              |     | 7.2.4   | Approximate Algorithms                            | 112 |

| $\mathbf{A}$ | Chr | ronOS   | System Calls                                      | 113 |

| В            | Chr | onOS    | Kernel Data Structures                            | 114 |

| C Sample ChronOS Scheduling Kernel Modules | 117 |

|--------------------------------------------|-----|

| Bibliography                               | 120 |

# List of Figures

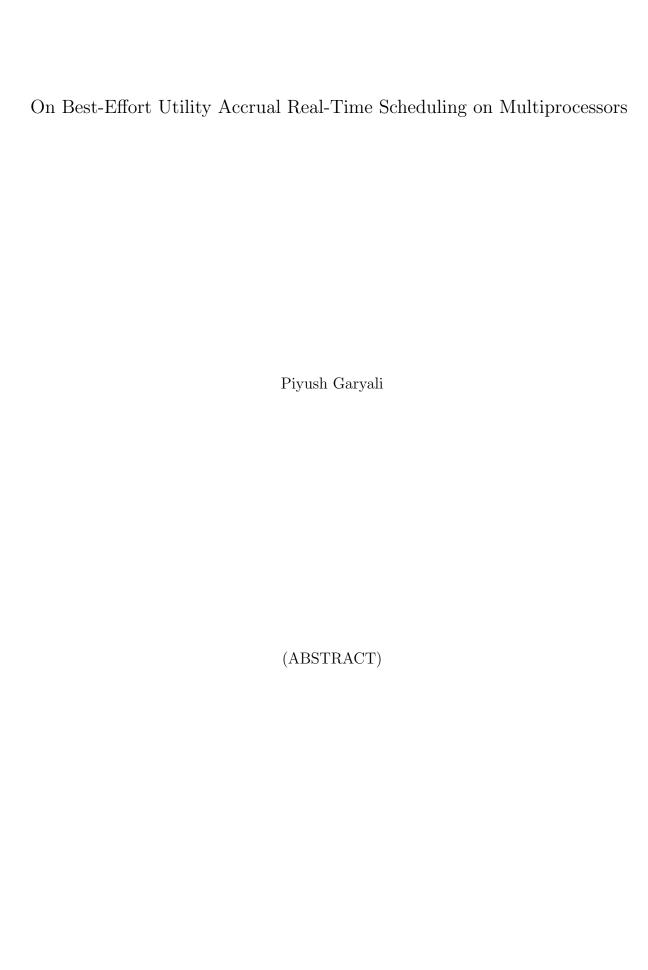

| 1.1 | Example TUF time constraints. (a) MITRE Airborne Warning and Control System (AWACS) association TUF [30]; (b-c) GD/CMU air defense plot correlation, track maintenance, and missle control TUFs [58]; (d) step TUFs | 3  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

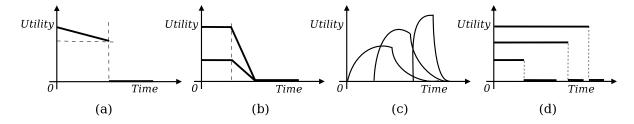

| 1.2 | Sample EDF schedule on two processors – (a) that cannot be scheduled; and (b) that can be scheduled                                                                                                                 | 5  |

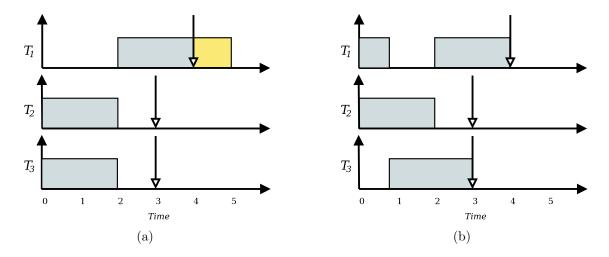

| 1.3 | Schedulability bounds of multiprocessor scheduling algorithms from [49]                                                                                                                                             | 6  |

| 2.1 | Characterization of scheduling algorithms during underloads $(U \leq m)$ and overloads $(U > m)$ based on ability to meet all deadlines and bounded best-effort real-time time interval                             | 12 |

| 4.1 | A phase and resource dependency chain with nine phases and three resources                                                                                                                                          | 18 |

| 4.2 | Directed Acyclic Graph (DAG) for the dependency chain shown in Fig 4.1. The nodes with a zero in-degree are eligible for final schedule in order to preserve mutual exclusion.                                      | 19 |

| 4.3 | Computing the global value density for a graph                                                                                                                                                                      | 19 |

| 4.4 | A phase and resource dependency chain with a deadlock condition                                                                                                                                                     | 20 |

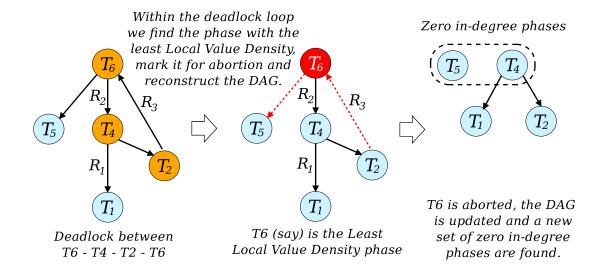

| 4.5 | Deadlock detection and resolution                                                                                                                                                                                   | 21 |

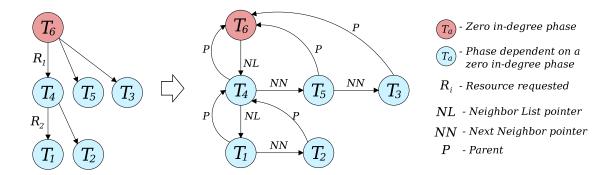

| 4.6 | Data structure representation of the DAG                                                                                                                                                                            | 23 |

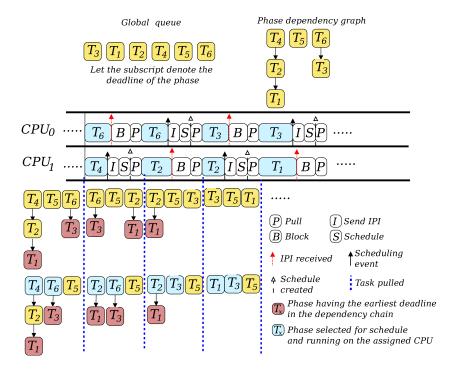

| 4.7 | Sample schedule for NG-GUA                                                                                                                                                                                          | 29 |

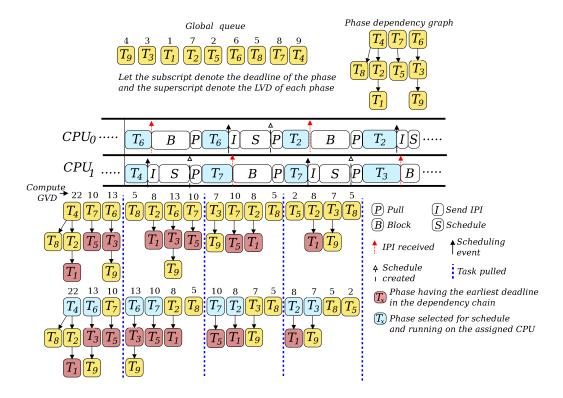

| 4.8 | Sample schedule for G-GUA                                                                                                                                                                                           | 32 |

| 5.1 | ChronOS architecture                                                                                                                                                                                                | 38 |

| 5.2 | Linux real-time priority bitmap and run-queues                                                                                                                                                                      | 40 |

| 5.3 | ChronOS real-time priority run-queue for a given real-time priority                                                                                                                                                 | 41 |

| 5.4  | ChronOS scheduling approach on a single-processor system                                                              | 43 |

|------|-----------------------------------------------------------------------------------------------------------------------|----|

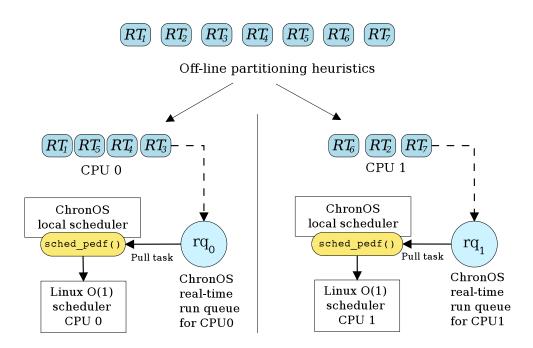

| 5.5  | ChronOS partitioned scheduling approach on a multiprocessor system                                                    | 44 |

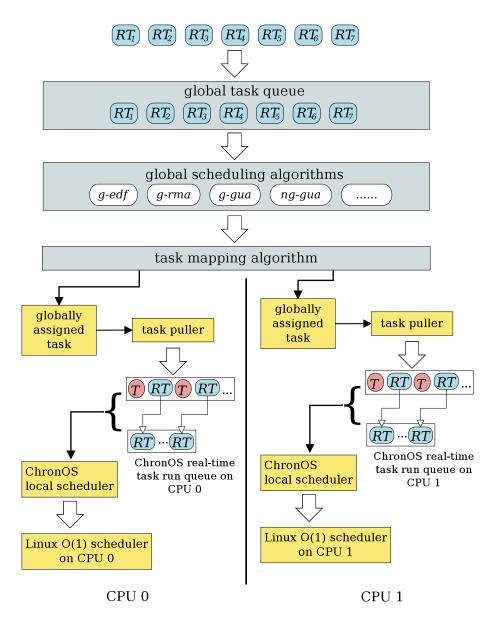

| 5.6  | ChronOS global scheduling approach on a multiprocessor system                                                         | 45 |

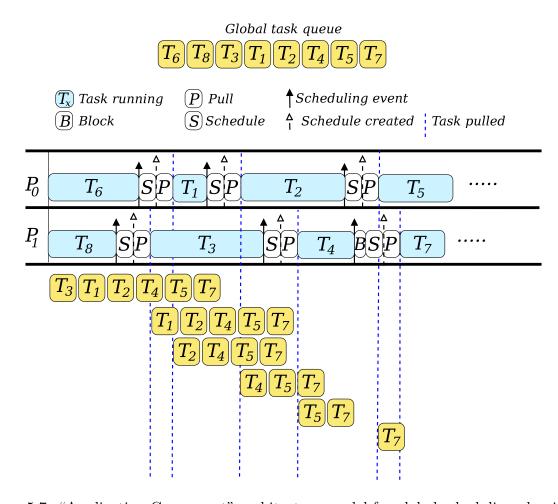

| 5.7  | "Application Concurrent" architecture model for global scheduling algorithms                                          | 47 |

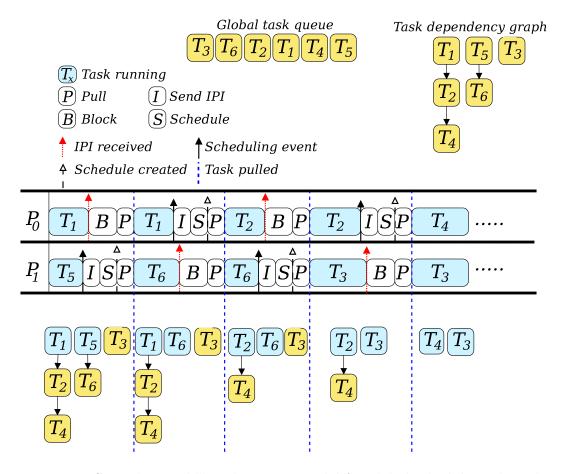

| 5.8  | "Stop-the-World" architecture model for global scheduling algorithms                                                  | 48 |

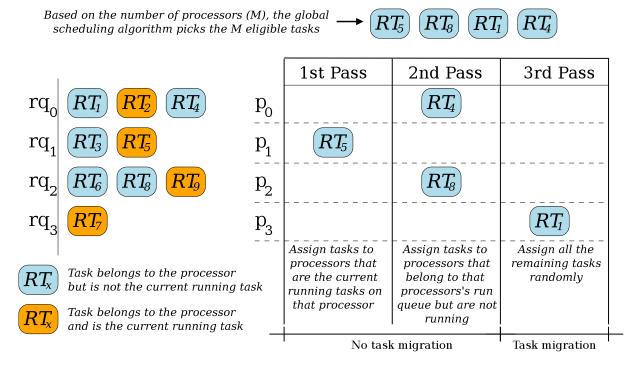

| 5.9  | Task mapping for global scheduling algorithms in ChronOS                                                              | 50 |

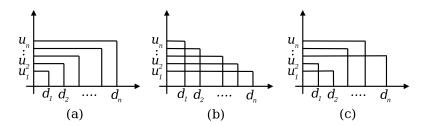

| 6.1  | Task-sets created with variable TUFs (a) Increasing Utility (IU); (b) Decreasing Utility (DU); (c) Random Utility(RU) | 54 |

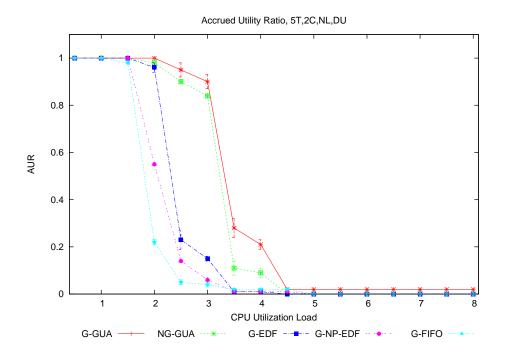

| 6.2  | AUR vs. CPU utilization (5T, 2C, NL, DU)                                                                              | 57 |

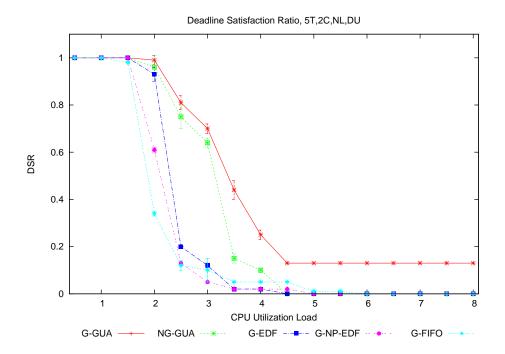

| 6.3  | DSR vs. CPU utilization (5T, 2C, NL, DU)                                                                              | 58 |

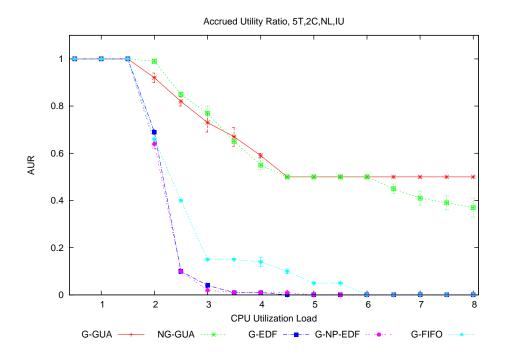

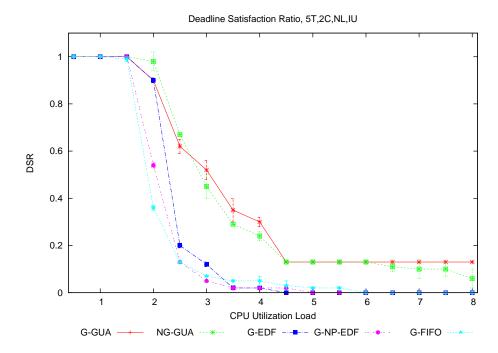

| 6.4  | AUR vs. CPU utilization (5T, 2C, NL, IU)                                                                              | 59 |

| 6.5  | DSR vs. CPU utilization (5T, 2C, NL, IU)                                                                              | 59 |

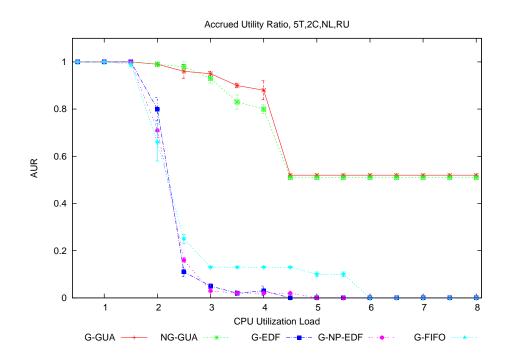

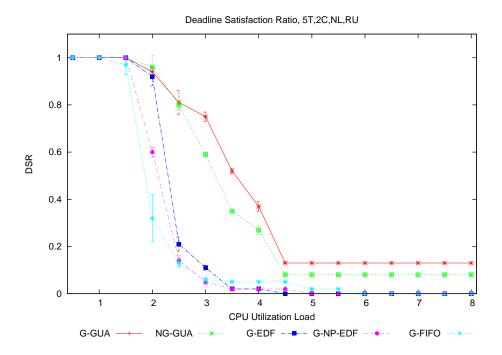

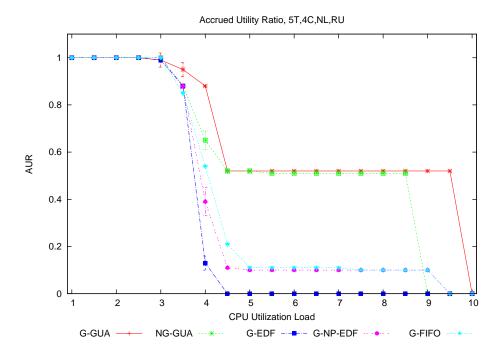

| 6.6  | AUR vs. CPU utilization (5T, 2C, NL, RU)                                                                              | 60 |

| 6.7  | DSR vs. CPU utilization (5T, 2C, NL, RU)                                                                              | 60 |

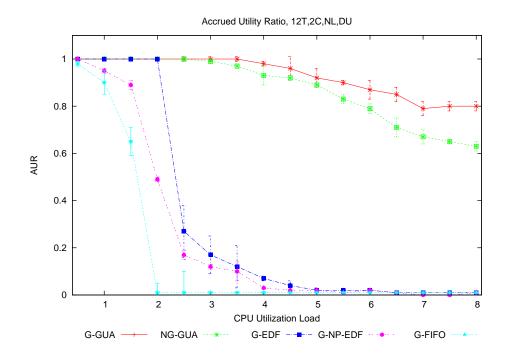

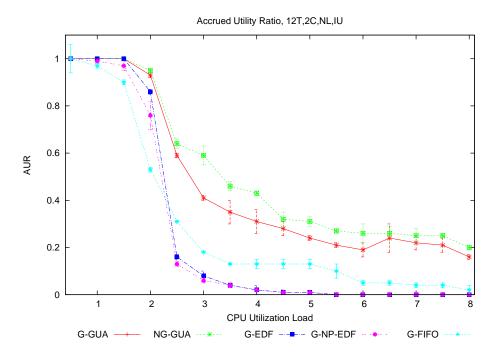

| 6.8  | AUR vs. CPU utilization (12T, 2C, NL, DU)                                                                             | 61 |

| 6.9  | DSR vs. CPU utilization (12T, 2C, NL, DU)                                                                             | 62 |

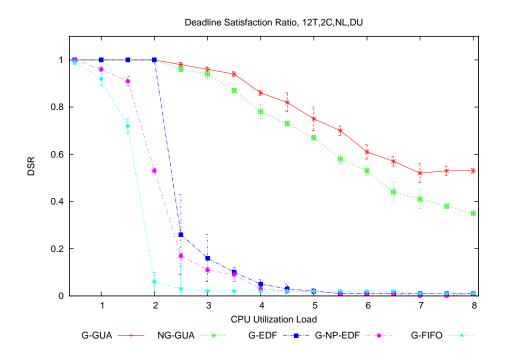

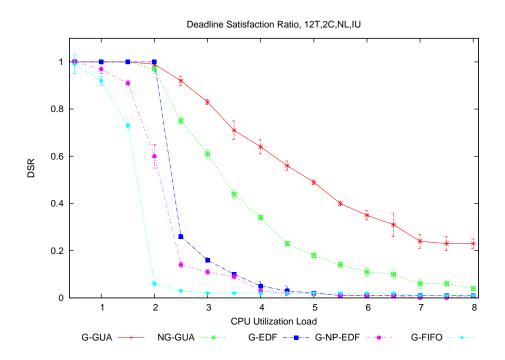

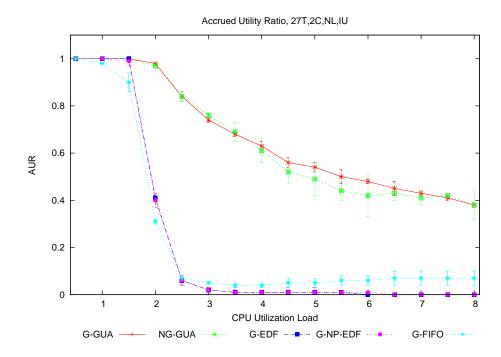

| 6.10 | AUR vs. CPU utilization (12T, 2C, NL, IU)                                                                             | 62 |

| 6.11 | DSR vs. CPU utilization (12T, 2C, NL, IU)                                                                             | 63 |

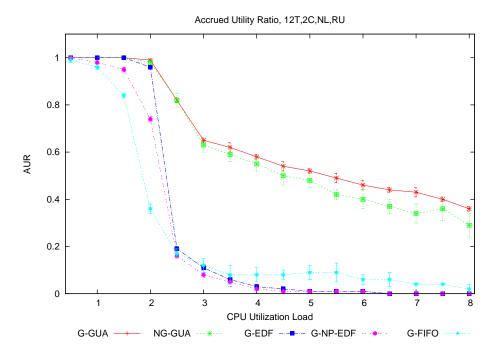

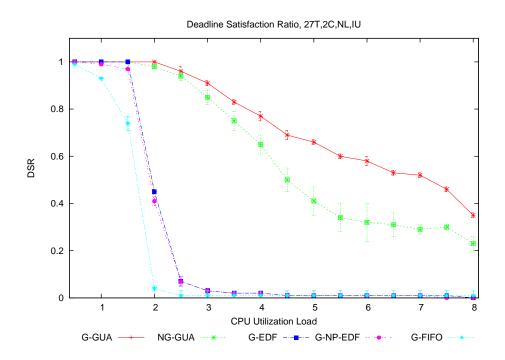

| 6.12 | AUR vs. CPU utilization (12T, 2C, NL, RU)                                                                             | 63 |

| 6.13 | DSR vs. CPU utilization (12T, 2C, NL, RU)                                                                             | 64 |

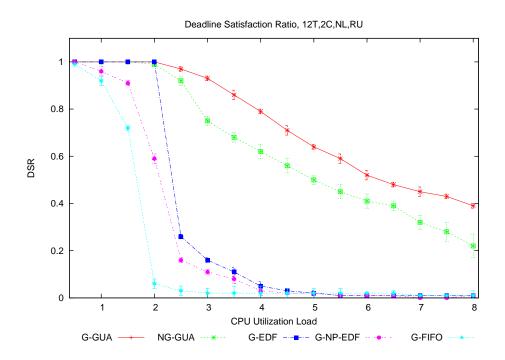

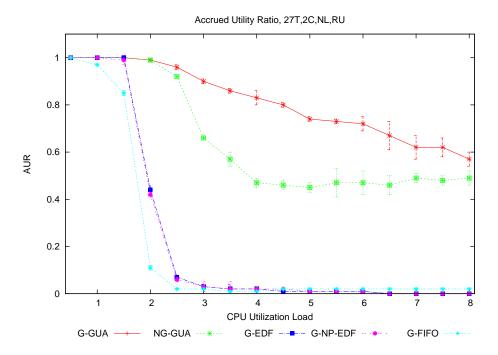

| 6.14 | AUR vs. CPU utilization (27T, 2C, NL, DU)                                                                             | 64 |

| 6.15 | DSR vs. CPU utilization (27T, 2C, NL, DU)                                                                             | 65 |

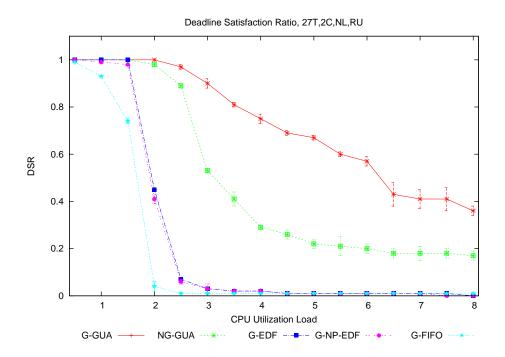

| 6.16 | AUR vs. CPU utilization (27T, 2C, NL, IU)                                                                             | 65 |

| 6.17 | DSR vs. CPU utilization (27T, 2C, NL, IU)                                                                             | 66 |

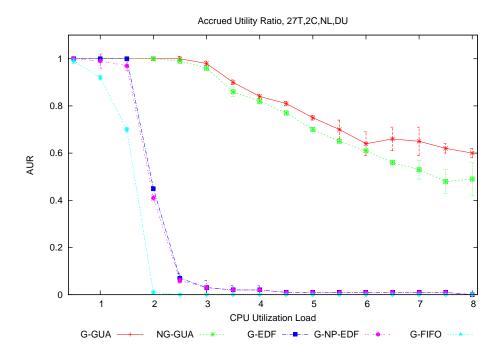

| 6.18 | AUR vs. CPU utilization (27T, 2C, NL, RU)                                                                             | 66 |

| 6.19 | DSR vs. CPU utilization (27T, 2C, NL, RU)                                                                             | 67 |

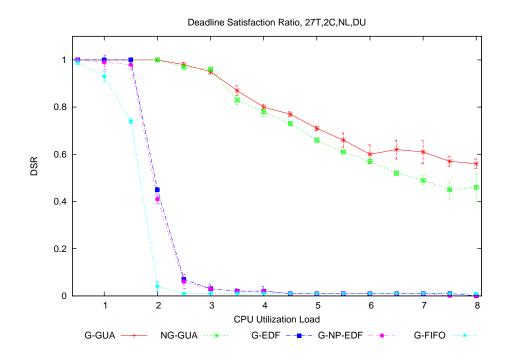

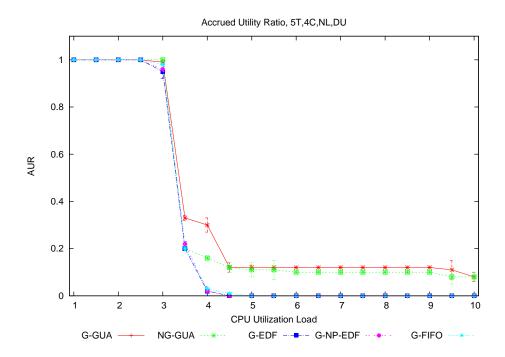

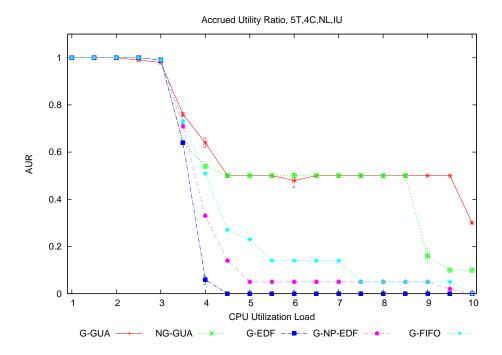

| 6.20 | AUR vs. CPU utilization (5T, 4C, NL, DU)                                                                              | 68 |

| 6.21 | DSR vs. CPU utilization (5T, 4C, NL, DU)                                                                              | 69 |

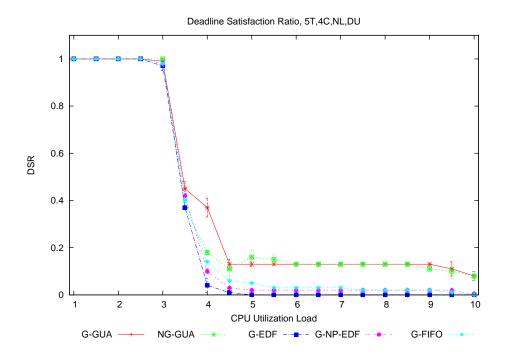

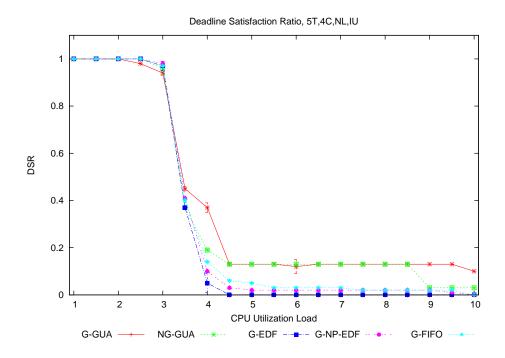

| 6.22 | AUR vs. CPU utilization (5T, 4C, NL, IU)    | 69 |

|------|---------------------------------------------|----|

| 6.23 | DSR vs. CPU utilization (5T, 4C, NL, IU)    | 70 |

| 6.24 | AUR vs. CPU utilization (5T, 4C, NL, RU)    | 70 |

| 6.25 | DSR vs. CPU utilization (5T, 4C, NL, RU)    | 71 |

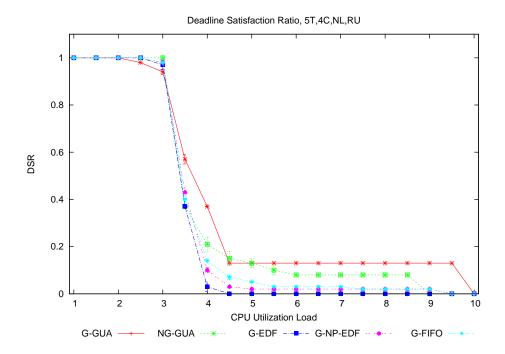

| 6.26 | AUR vs. CPU utilization (12T, 4C, NL, DU)   | 72 |

| 6.27 | DSR vs. CPU utilization (12T, 4C, NL, DU)   | 72 |

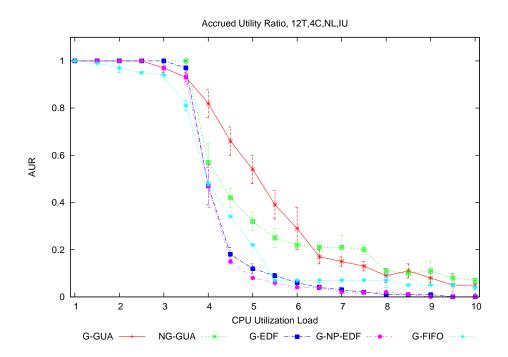

| 6.28 | AUR vs. CPU utilization (12T, 4C, NL, IU)   | 73 |

| 6.29 | DSR vs. CPU utilization (12T, 4C, NL, IU)   | 73 |

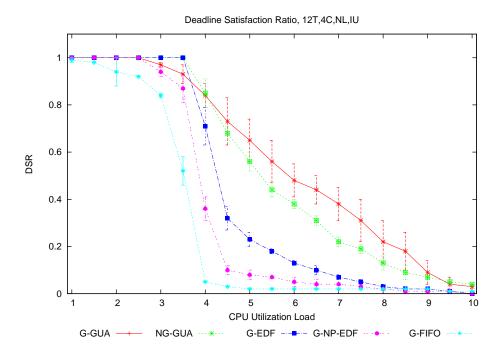

| 6.30 | AUR vs. CPU utilization (12T, 4C, NL, RU)   | 74 |

| 6.31 | DSR vs. CPU utilization (12T, 4C, NL, RU)   | 74 |

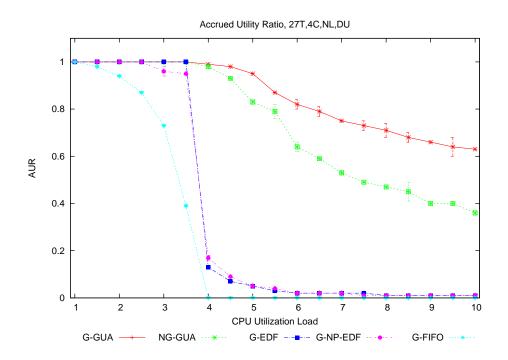

| 6.32 | AUR vs. CPU utilization (27T, 4C, NL, DU)   | 75 |

| 6.33 | DSR vs. CPU utilization (27T, 4C, NL, DU)   | 75 |

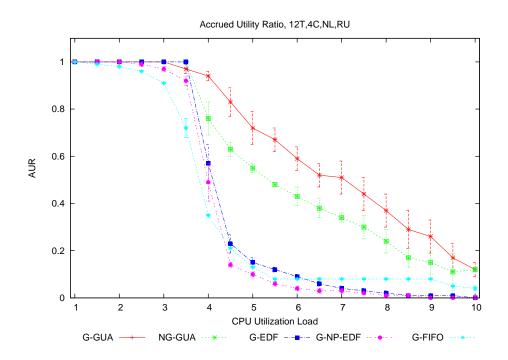

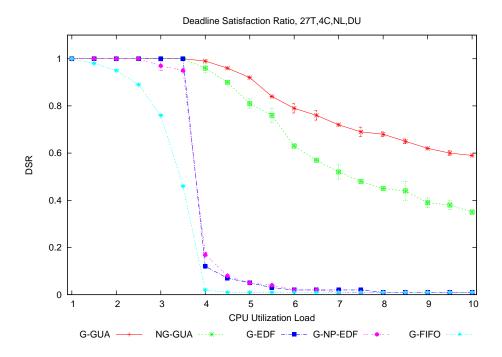

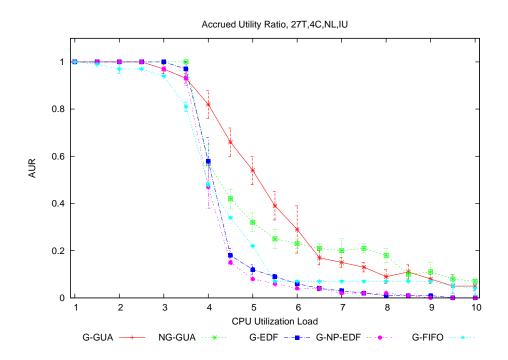

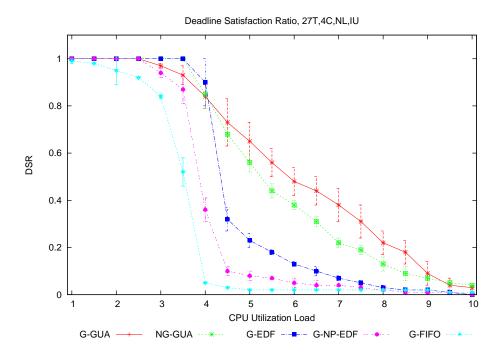

| 6.34 | AUR vs. CPU utilization (27T, 4C, NL, IU)   | 76 |

| 6.35 | DSR vs. CPU utilization (27T, 4C, NL, IU)   | 76 |

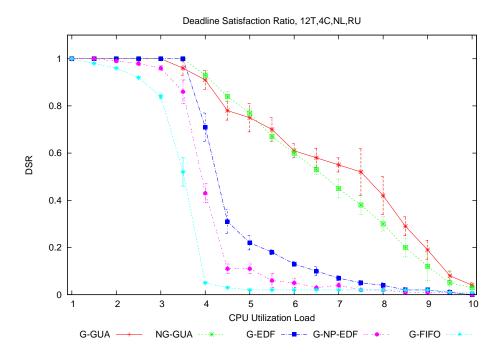

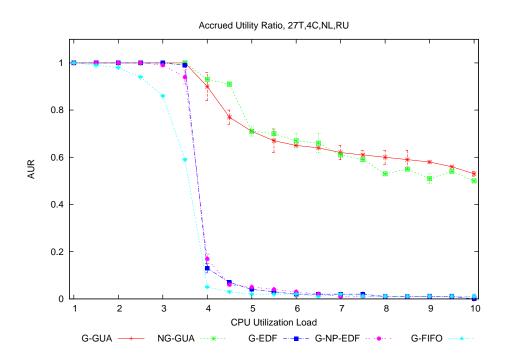

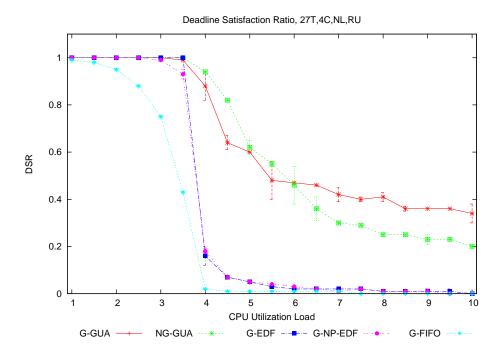

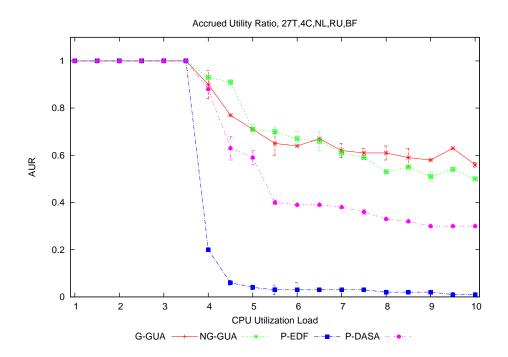

| 6.36 | AUR vs. CPU utilization (27T, 4C, NL, RU)   | 77 |

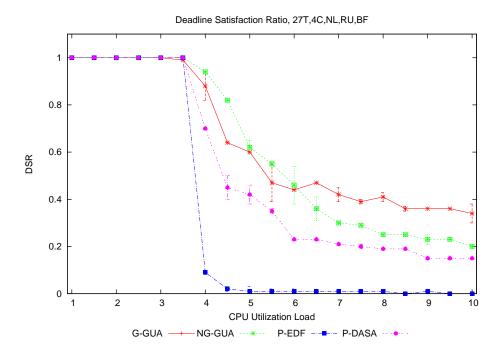

| 6.37 | DSR vs. CPU utilization (27T, 4C, NL, RU)   | 77 |

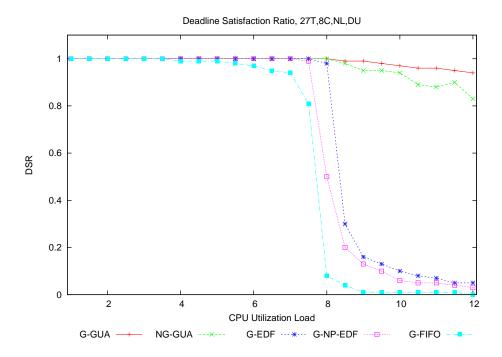

| 6.38 | AUR vs. CPU utilization (27T, 8C, NL, DU)   | 79 |

| 6.39 | DSR vs. CPU utilization (27T, 8C, NL, DU)   | 79 |

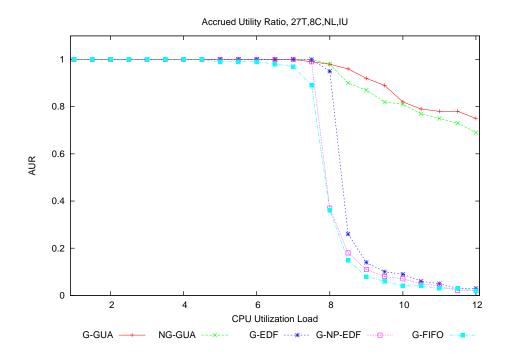

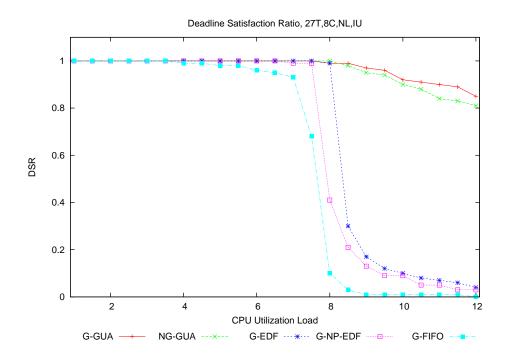

| 6.40 | AUR vs. CPU utilization (27T, 8C, NL, IU)   | 80 |

| 6.41 | DSR vs. CPU utilization (27T, 8C, NL, IU)   | 81 |

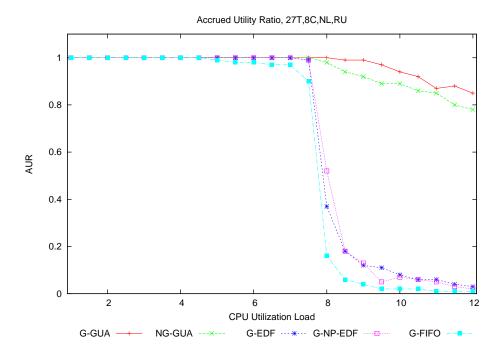

| 6.42 | AUR vs. CPU utilization (27T, 8C, NL RU)    | 81 |

| 6.43 | DSR vs. CPU utilization (27T, 8C, NL, RU)   | 82 |

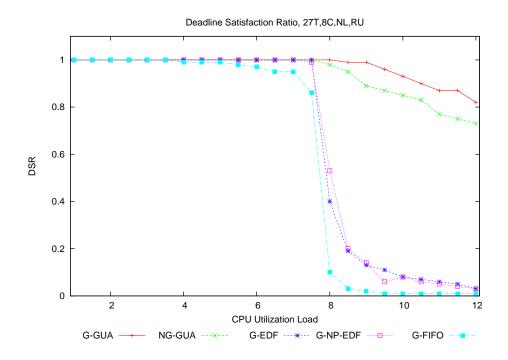

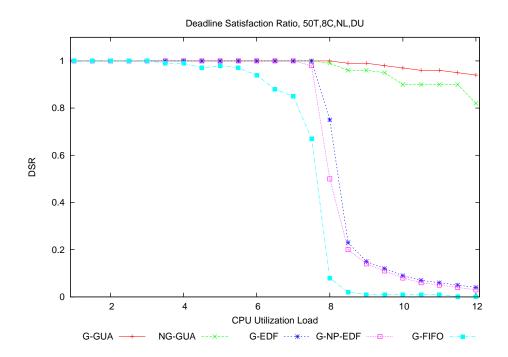

| 6.44 | AUR vs. CPU utilization (50T, 8C, NL, DU)   | 82 |

| 6.45 | DSR vs. CPU utilization (50T, 8C, NL, DU)   | 83 |

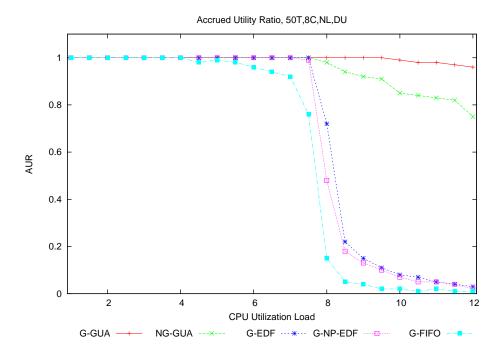

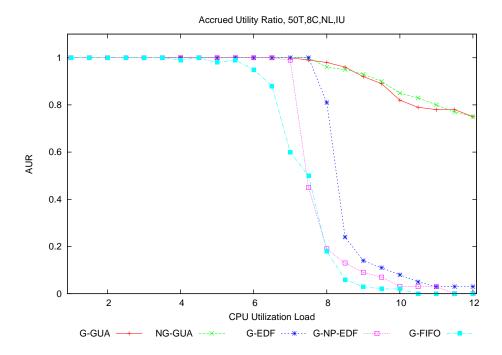

| 6.46 | AUR vs. CPU utilization (50T, 8C, NL, IU)   | 83 |

| 6.47 | DSR vs. CPU utilization (50T, 8C, NL, IU)   | 84 |

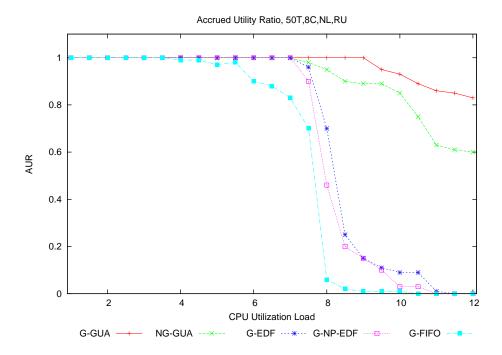

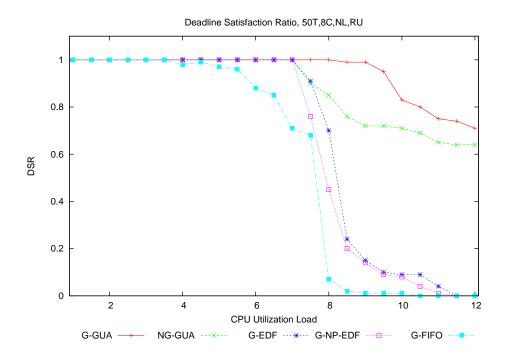

| 6.48 | AUR vs. CPU utilization (50T, 8C, NL, RU)   | 84 |

| 6 49 | DSR vs. CPII utilization (50T, 8C, NL, RII) | 85 |

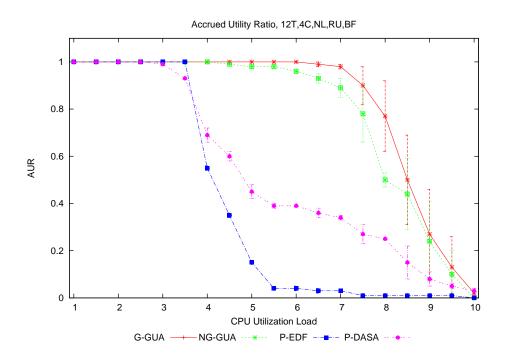

| 6.50 | AUR vs. CPU utilization (12T, 4C, NL, RU, BF)                                              | 88  |

|------|--------------------------------------------------------------------------------------------|-----|

| 6.51 | DSR vs. CPU utilization (12T, 4C, NL, RU, BF)                                              | 88  |

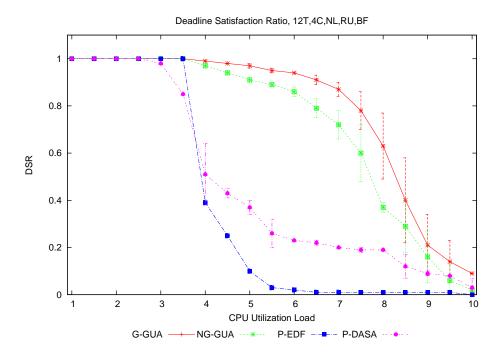

| 6.52 | AUR vs. CPU utilization (27T, 4C, NL, RU, BF)                                              | 89  |

| 6.53 | DSR vs. CPU utilization (27T, 4C, NL, RU, BF)                                              | 89  |

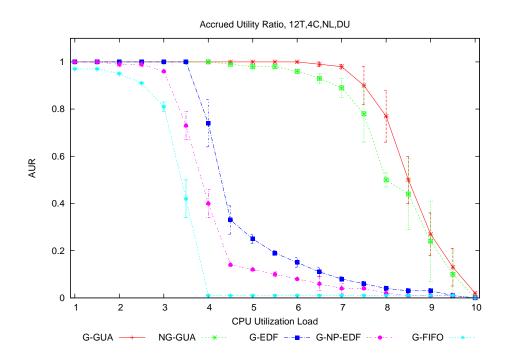

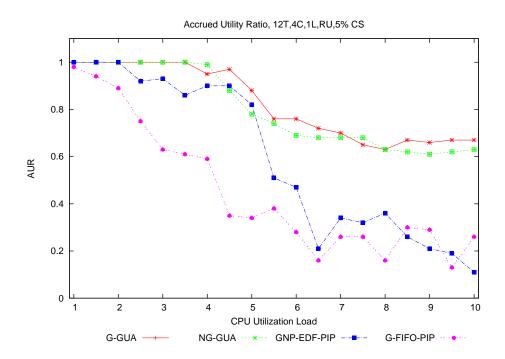

| 6.54 | AUR vs. CPU utilization (12T, 4C, 1L, RU, 5% CS)                                           | 92  |

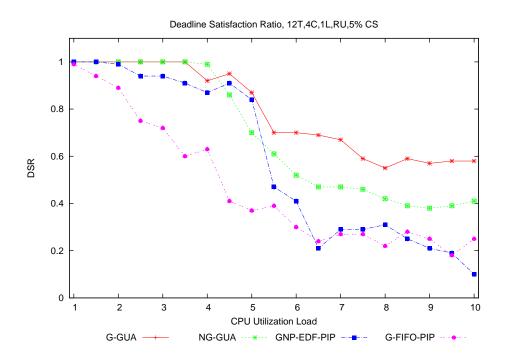

| 6.55 | DSR vs. CPU utilization (12T, 4C, 1L, RU, 5% CS)                                           | 93  |

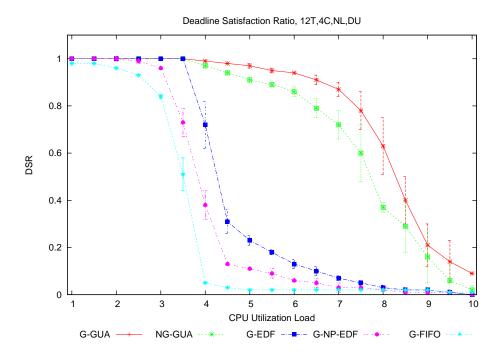

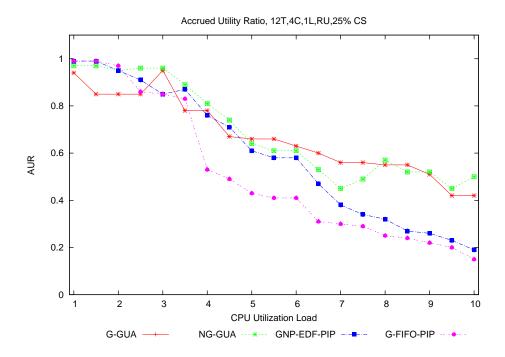

| 6.56 | AUR vs. CPU utilization (12T, 4C, 1L, RU, 25% CS)                                          | 93  |

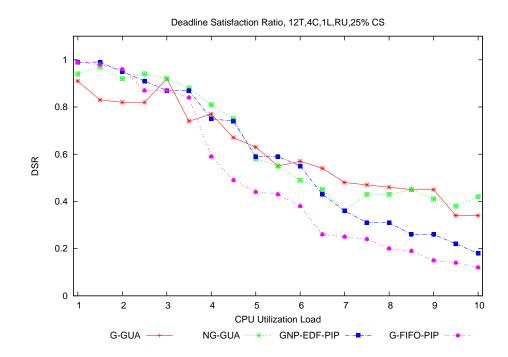

| 6.57 | DSR vs. CPU utilization (12T, 4C, 1L, RU, 25% CS)                                          | 94  |

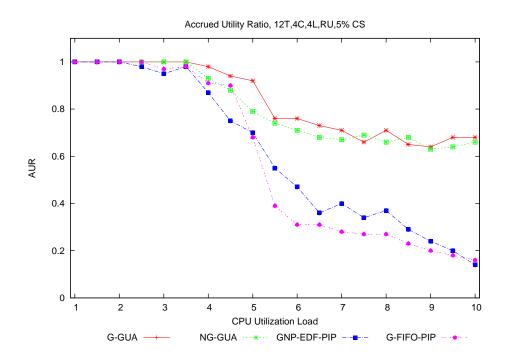

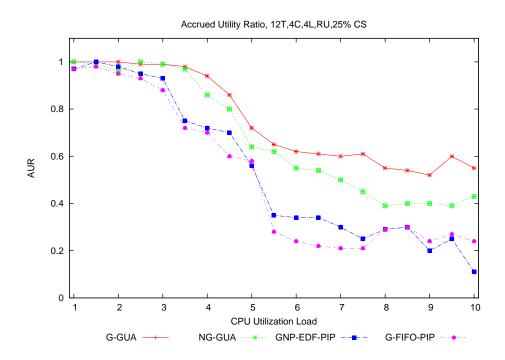

| 6.58 | AUR vs. CPU utilization (12T, 4C, 4L, RU, 5% CS) $\ldots \ldots \ldots$                    | 95  |

| 6.59 | DSR vs. CPU utilization (12T, 4C, 4L, RU, 5% CS) $\dots \dots \dots$                       | 95  |

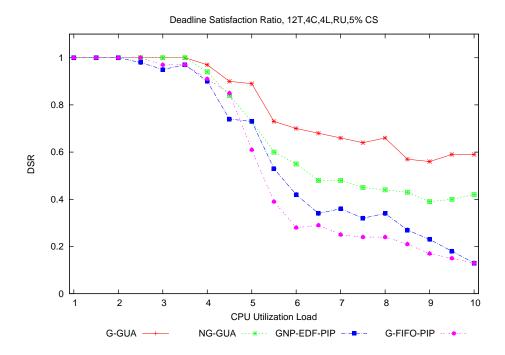

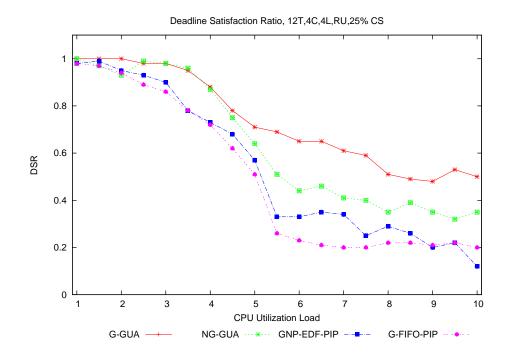

| 6.60 | AUR vs. CPU utilization (12T, 4C, 4L, RU, 25% CS)                                          | 96  |

| 6.61 | DSR vs. CPU utilization (12T, 4C, 4L, RU, 25% CS)                                          | 96  |

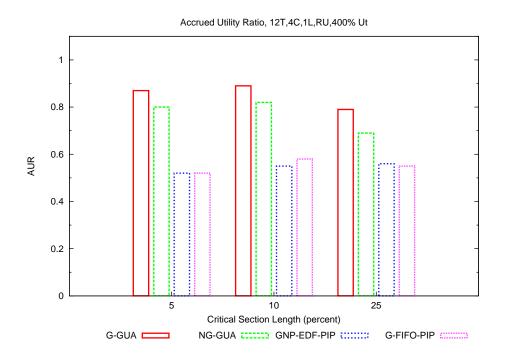

| 6.62 | AUR vs. Critical section length (12T, 4C, 1L, RU, 400% CPU utilization) $$ .               | 98  |

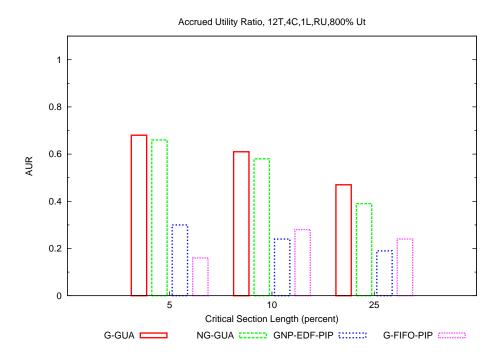

| 6.63 | AUR vs. Critical section length (12T, 4C, 1L, RU, 800% CPU utilization) $$ .               | 98  |

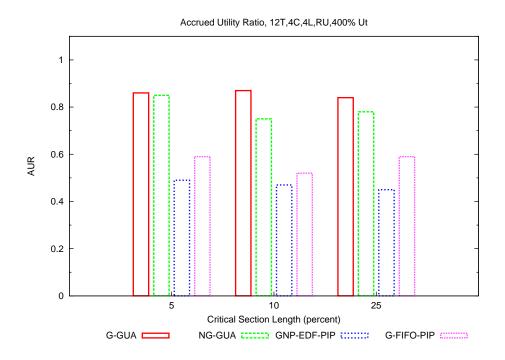

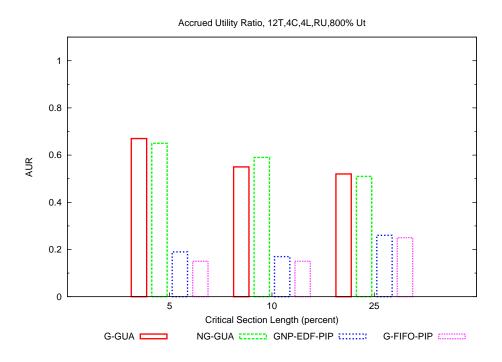

| 6.64 | AUR vs. Critical section length (12T, 4C, 4L, RU, 400% CPU utilization) $$ .               | 99  |

| 6.65 | AUR vs. Critical section length (12T, 4C, 4L, RU, 800% CPU utilization) $$ .               | 99  |

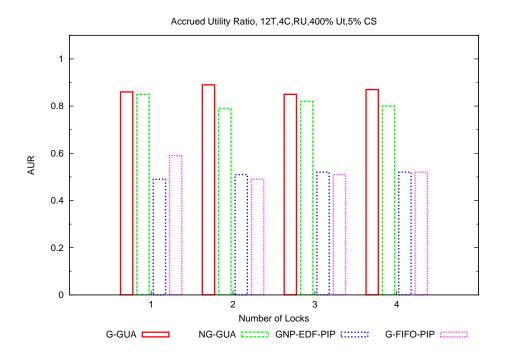

| 6.66 | AUR vs. Number of locks (12T, 4C, RU, 5% CS, 400% CPU utilization) $$                      | 101 |

| 6.67 | AUR vs. Number of locks (12T, 4C, RU, 25% CS, 400% CPU utilization) $$ .                   | 101 |

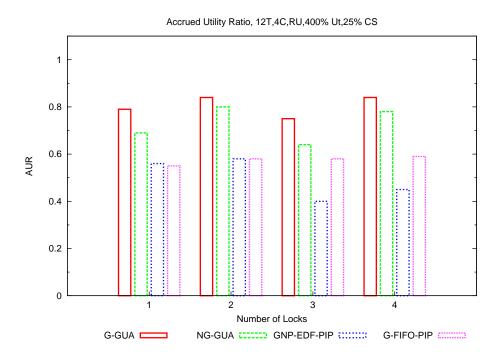

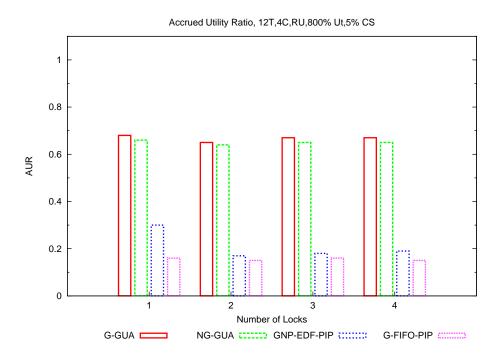

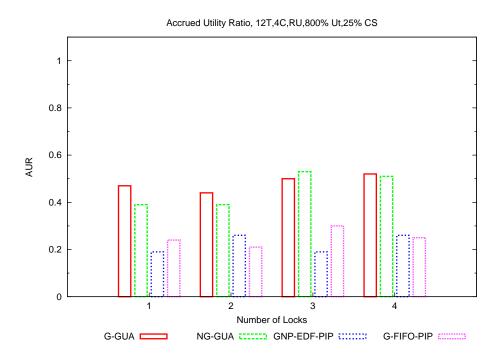

| 6.68 | AUR vs. Number of locks (12T, 4C, RU, 5% CS, 800% CPU utilization) $$                      | 102 |

| 6.69 | AUR vs. Number of locks (12T, 4C, RU, 25% CS, 800% CPU utilization)                        | 102 |

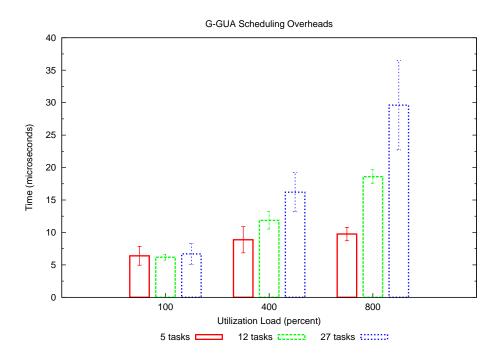

| 6.70 | Scheduling overheads for G-GUA under variable utilization load                             | 104 |

| 6.71 | Scheduling overheads for NG-GUA under variable utilization load $\ \ldots \ \ldots$        | 104 |

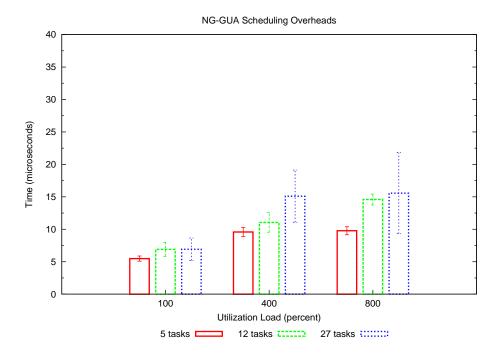

| 6.72 | $\operatorname{G-GUA}$ vs. NG-GUA, scheduling overheads with variable number of tasks $$ . | 105 |

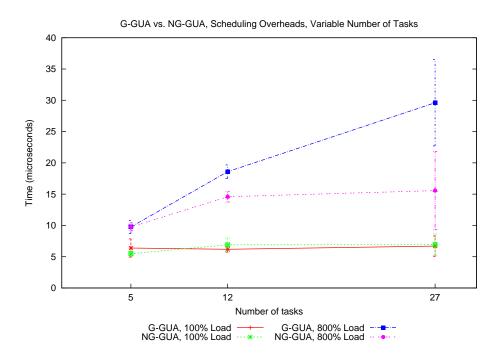

| 6.73 | Comparison of scheduling overheads at $100\%$ utilization load                             | 105 |

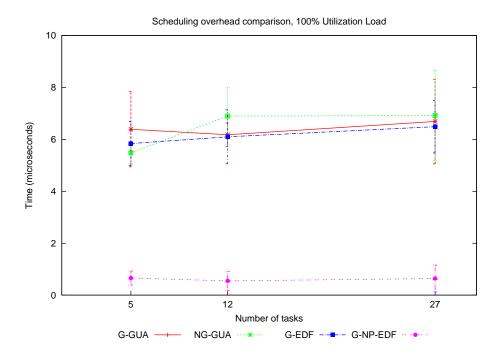

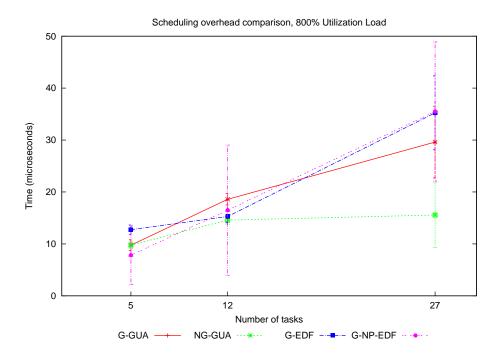

| 6.74 | Comparison of scheduling overheads at 800% utilization load                                | 106 |

# List of Algorithms

| 1 | Creation of DAG with detection/resolution of deadlocks | 26 |

|---|--------------------------------------------------------|----|

| 2 | NG-GUA: Non-greedy Global Utility Accrual              | 28 |

| 3 | G-GUA: Greedy Global Utility Accrual                   | 31 |

# List of Tables

| 6.1 | Specifications of the various platforms used for experimental evaluation                                                   | 53 |

|-----|----------------------------------------------------------------------------------------------------------------------------|----|

| 6.2 | Legend used in experimental results, based on TUF-based models, for comparison with other global scheduling algorithms     | 56 |

| 6.3 | Legend used in experimental results for comparison with other partitioned scheduling algorithms                            | 86 |

| 6.4 | Legend used in experimental results for comparison with other global scheduling algorithms in the presence of dependencies | 91 |

## Nomenclature

ACUA Asynchronous Consensus-based Utility Accrual scheduling algorithm, page 38

API Application Programming Interface, page 38

AUR Accrued Utility Ratio, page 53

CPU Central Processing Unit, page 11

CRT-RQ ChronOS Real-Time Run-Queue, page 41

CUA Consensus-based Utility Accrual scheduling algorithm, page 38

D-TPR Distributed Thread Polling with bounded Recovery, page 38

DAG Directed Acyclic Graph, page 17

DASA Dependent Activity Scheduling Algorithm, page 7

DMS Deadline Monotonic Scheduling, page 2

DSR Deadline Satisfaction Ratio, page 53

DT Distributed Thread, page 37

DU Decreasing Utility model, page 55

EDF Earliest Deadline First, page 2

G-EDF Global Earliest Deadline First scheduling algorithm, page 28

G-FIFO Global First In First Out scheduling algorithm, page 38

G-GUA Greedy Global Utility Accrual, page 7

G-NP-EDF Global Non-Preemptive Earliest Deadline First scheduling algorithm, page 38 gMUA Global Multiprocessor Utility Accrual, page 6

GNU Gnu is Not Unix, page 37

GPLv2 GNU Public License version 2.0, page 37

GVD Global Value Density, page 19

HT Hyper-Threading, page 78

HUA Handler-assured Utility Accrual scheduling algorithm, page 38

HVDF Highest Value Density First scheduling algorithm, page 38

IPI Inter-Processor Interrupt, page 48

IRQ Interrupt Request, page 39

IU Increasing Utility model, page 54

LLF Least Laxity First, page 2

LLREF Largest Local Remaining Execution time First scheduling algorithm, page 5

LVD Local Value Density, page 19

MOCA Multiprocessor On-Line Competitive Algorithm, page 6

NG-GUA Non-Greedy Global Utility Accrual, page 7

P-DASA Parallel Dependent Activity Scheduling Algorithm, page 44

P-EDF Partitioned Earliest Deadline First scheduling algorithm, page 10

PFair Proportionate Fair Scheduling Algorithm, page 11

PIP Priority Inheritance Protocol, page 22

POSIX Portable Operating System Interface [for Unix], page 39

PUD Potential Utility Density, page 7

RMS Rate Monotonic Scheduling algorithm, page 2

RU Random Utility model, page 55

SMP Symmetrical Multiprocessor System, page 40

STW Stop-the-World architecture model, page 46

TPR Thread Polling with bounded Recovery, page 38

TUF Time/Utility Functions, page 3

UA Utility Accrual, page 3

## Chapter 1

## Introduction

Recently, there has been a shift in the computer industry from increasing clock rates to designing multi-core and hyper-threading architectures in a quest to produce faster computers [65]. Motivated by heat and power issues, most chip manufacturers have chosen the route of increasing system and chip level parallelism in preference to increasing clock rates in order to satisfy the need for improving performance. This trend extends to embedded systems [14] as well as to traditional computing systems. Consequently, the design of multi-processor<sup>1</sup> real-time scheduling algorithms has become important in order to allow real-time applications to take advantage of these emerging architectures.

Scheduling of real-time multiprocessor systems has received increased attention recently [18]. However, most of these works target "underloaded" systems—i.e., systems where the total application task utilization demand, U, is always less than the total available processing capacity of the system, which is m for an m-processor system. Majority of the research focus in multiprocessor real-time systems is on developing scheduling algorithms and understanding their schedulability utilization bounds—i.e., task utilization bounds below which all task deadlines are met. The premise of this approach is that it is possible to determine the worst-case execution-time behaviors of applications (e.g., task arrival behaviors, task worst-case execution times) and thereby determine the total task utilization demands. Once the task utilization demand is known, task schedulability—i.e., the ability to meet all task deadlines—can be ensured off-line by selecting the appropriate scheduling algorithm with a higher utilization bound.

For some applications (e.g., [68, 30, 66]), it is difficult to determine worst-case execution-time behaviors a priori, as they are subject to run-time exigencies, such as execution time overruns and unpredictable thread arrival patterns, causing transient and permanent overloads. When overloads occur, often, such applications desire graceful timeliness degradation—e.g., meeting as many deadlines of high importance tasks as possible, irrespective of task urgency.

<sup>&</sup>lt;sup>1</sup>We will use multiprocessor and multi-core interchangeably in the rest of the thesis unless explicitly stated otherwise.

#### 1.1 Timeliness Model

The state-of-the-real-time practice is to handle application time constraints using the concept of *priorities*. This approach is the basis for the vast majority of real-time OS, language, and middleware standards including POSIX [42], Real-time CORBA [61], Ada 95 [5], and RTSJ [71]. However, using priorities have inherent shortcomings, which include:

- 1. The process of assigning time constraints to priorities is generally difficult, and sometimes intractable. Often, there is significant loss of information during this process which makes it difficult to dependably satisfy time constraints.

- 2. Real-time systems usually comprise of various sub-systems. In order to assign priorities to express urgency, it is necessary to know the entire system and its various sub-systems, along with the knowledge of the global assignment of priorities for the entire system. Such knowledge can sometimes be difficult to obtain due to organizational boundaries.

- 3. The urgency and importance of a real-time task can be orthogonal—e.g., the most important task can be the most urgent; the most important task can be the least urgent, etc. However, a priority cannot express both. This causes serious difficulties during overload situations, when not all task deadlines can be met, and applications desire to differentially allocate resources in the order of decreasing task importance, irrespective of task urgency—e.g., most important task first; second-most important task second, and so on.

One solution that overcomes these shortcomings is to provide system developers with abstractions for directly specifying time constraints (instead of mapping time constraints to priorities) and using those time constraint specifications to manage resources (instead of indirectly managing resources through the priority artifact). This is the basis for the traditional real-time theory [47, 54]. In that theory, time constraints (which are largely limited to deadlines) are mapped to fixed priorities in algorithms such as Rate Monotonic Scheduling (RMS) [53] and Deadline Monotonic Scheduling (DMS) [53], or are mapped to dynamic priorities as in Least Laxity First (LLF) [59], or are directly used for scheduling as in Earliest Deadline First (EDF) [41].

However, deadline and deadline-based scheduling suffer from some drawbacks. A deadline of a task can be expressed in two forms. First, as a binary-valued expression which evaluates to the deadline being met or not met; and second, a linear-valued expression for the penalty of lateness. However, the penalty of being late per unit time is constant irrespective of how late the task actually is. Thus, deadlines per se cannot be used to distinguish between task urgency and task importance, which is a limitation during overloads. Furthermore, classical deadline-based scheduling algorithms (e.g., EDF) suffer from the *domino* effect [55] during overloads. This is because, these algorithms always favor tasks with an earlier deadline,

irrespective of how close such tasks are towards missing their deadlines. This results in those tasks missing their deadlines, and also causing others, which are now delayed, to miss their deadlines.

Timeliness optimality criteria that can be specified using deadlines fall into the following categories: (i) the criterion of meeting all deadlines; (ii) criteria that are based on number of missed deadlines—e.g., minimize the number of deadline misses; upper bound the number of deadlines missed; and (iii) the criteria expressed using lateness—e.g., minimize the maximum lateness; upper bound the lateness.

Figure 1.1: Example TUF time constraints. (a) MITRE Airborne Warning and Control System (AWACS) association TUF [30]; (b-c) GD/CMU air defense plot correlation, track maintenance, and missle control TUFs [58]; (d) step TUFs

The shortcomings of deadlines and deadline-based scheduling are overcome in the Time/U-tility Function (TUF) model, first introduced in [43]. A TUF specifies the utility obtained by the completion of a task, as a function of that task's completion time. Figure 1.1 shows some example TUFs. Figure 1.1(a)-(c) show time constraints of some applications in the defense domain [30, 58]. A TUF decouples importance and urgency, with the urgency measured as a deadline on the X-axis, and importance measured as a utility (or value) on the Y-axis. The classical deadline is a special case of a TUF: a binary-valued, downward "step" TUF. Figure 1.1(d) shows an example.

When task time constraints are expressed using TUFs, the scheduling optimality criteria are often based on accrued utility—e.g., maximizing the sum of the tasks' attained utilities. Such criteria are called *Utility Accrual* (or UA) criteria and scheduling algorithms that optimize such criteria are called UA scheduling algorithms (e.g., [31, 55]).

UA scheduling algorithms that maximize total accrued utility under downward "step" TUFs, default to EDF during underloads, since EDF satisfies all deadlines during underloads. As a result, these algorithms obtain optimal total accrued utility during underloads. During overloads, UA scheduling algorithms favor tasks from whom greater utility can be accrued (as that generally tends to maximize the total accrued utility), irrespective of task urgency. This behavior of UA scheduling algorithms is called "best-effort" — i.e., the algorithms strive their best to feasibly complete as many high importance tasks as possible (where task importance is explicitly described using TUFs). Note that the optimal timeliness behavior

<sup>&</sup>lt;sup>2</sup>Note that the term "best-effort" as used in the networking context is intended to mean "least-effort."

of EDF is a special case of UA-scheduling.

A number of UA algorithms have been designed in the past. These cover a wide range of problem spaces: from processor scheduling [55, 31, 22, 50, 51, 52, 27]; to memory management and garbage collection [28, 23, 34]; to non-blocking synchronization [22, 24, 26]; to energy management [72, 73, 7, 74]; to packet scheduling [69, 70]; and to network routing [19, 20, 62]; They also cover step TUFs [31]; to non-step TUFs [22, 24, 26, 69, 72, 19, 62]; to abitrarily-shaped TUFs [50].

### 1.2 Multiprocessor Real-Time Scheduling

One unique aspect of multiprocessor real-time scheduling is the degree of run-time migration that is allowed for job instances of a task across processors (at scheduling events). Example migration models include: (1) full migration, where jobs are allowed to arbitrarily migrate across processors during their execution. This usually implies a global scheduling strategy, where a single shared scheduling queue is maintained for all processors and a processor-wide scheduling decision is made by a single (global) scheduling algorithm; (2) no migration, where tasks are statically (off-line) partitioned and allocated to processors. At run-time, job instances of tasks are scheduled on their respective processors by processors' local scheduling algorithm, like single processor scheduling; and (3) restricted migration, where some form of migration is allowed—e.g., at job boundaries.

The partitioned scheduling paradigm has several advantages over the global approach. First, once tasks are allocated to processors, the multiprocessor real-time scheduling problem becomes a set of single processor real-time scheduling problems, one for each processor, which has been well-studied and for which optimal algorithms exist. Second, not migrating tasks at run-time means reduced run-time overhead as opposed to migrating tasks that may suffer cache misses on the newly assigned processor. If the task set is fixed and known a priori, the partitioned approach provides appropriate solutions [15].

The global scheduling paradigm also has advantages over the partitioned approach. First, if tasks can join and leave the system at run-time, then it may be necessary to reallocate tasks to processors in the partitioned approach [15]. Second, the partitioned approach cannot produce optimal real-time schedules — one that meets all task deadlines when task utilization demand does not exceed the total processor capacity — for periodic task sets [63], since the partitioning problem is analogous to the bin-packing problem which is known to be NP-hard in the strong sense. Third, in some embedded processor architectures with no cache and simpler structures, the overhead of migration has a lower impact on the performance [15]. Finally, global scheduling can theoretically contribute to an increased understanding of the properties and behaviors of real-time scheduling algorithms for multiprocessors. (See [40] for a detailed discussion on this).

Carpenter et al. [18] have catalogued multiprocessor real-time scheduling algorithms con-

sidering the degree of job migration and the complexity of priority mechanisms employed. The latter includes classes such as (1) *static*, where task priorities never change, e.g., rate-monotonic (RM); (2) *dynamic but fixed within a job*, where job priorities are fixed, e.g., earliest-deadline-first (EDF); and (3) *fully-dynamic*, where job priorities are dynamic.

The Pfair class of algorithms [11] that allow full migration and fully dynamic priorities have been shown to be theoretically optimal—i.e., they achieve a schedulable utilization bound (below which all tasks meet their deadlines) that equals the total capacity of all processors. However, Pfair algorithms incur significant run-time overhead due to their quantum-based scheduling approach [32, 63]. Under Pfair, tasks can be decomposed into several small uniform segments, which are then scheduled, causing frequent scheduling and migration.

Figure 1.2: Sample EDF schedule on two processors – (a) that cannot be scheduled; and (b) that can be scheduled.

Thus, scheduling algorithms other than Pfair—e.g., global-EDF [15, 10, 2] have also been intensively studied though their schedulable utilization bounds are lower. Figure 1.2(a) shows an example task set that global-EDF cannot feasibly schedule. In Figure 1.2(a), task  $T_1$  will miss its deadline when the system is given two processors. However, for the same task-set, there exists a schedule that meets all task deadlines, as shown in Figure 1.2(b).

There have also been efforts on designing optimal multiprocessor real-time scheduling algorithms that are not based on time quantum, unlike Pfair. Examples include the Largest Local Remaining Execution Time (or LLREF) algorithm and its derivatives [25, 21, 37].

Interestingly, all of these works exclude any run-time exigencies and consequent transient/permanent overloads—i.e., they presume that it is possible to determine the worst-case execution-time behaviors of applications (e.g., task arrival behaviors, task worst-case execution times), determine the total task utilization demands, and thus conduct off-line task schedulability, as mentioned before. Thus, the need for graceful timeliness degradation and best-effort timing assurances are outside their scope.

In [49], Lakshmanan et al. provide a classification of multiprocessor scheduling algorithms based on their schedulability bounds and we summarize the classification in Figure 1.3. In the global scheduling space, (at the time of writing this thesis), PFair and LLREF are the only known optimal multiprocessor scheduling algorithms that are able to meet all deadlines and have the optimal utilization bound of 100% (i.e., U = m) [11]. The dynamic priority algorithms that include deadline-based algorithms, such as G-EDF, and UA-based algorithms that default to G-EDF, such as gMUA, have the higher utilization bound of 50% [6, 22] (i.e.,  $U \approx m/2$ ). On the other hand, fixed priority algorithms, such as RMS, have a utilization bound of 33% [4] (i.e.,  $U \approx 3m/8$ ). In the partitioned scheduling space, both the dynamic priority algorithms, such as P-EDF and the fixed priority algorithms like P-DMS, have a utilization bound of 50% [56] (i.e.,  $U \approx m/2$ ). However, in [49], a version of P-DMS called PDMS-HPTS-DS, that uses high priority task-splitting (HPTS) with decreasing order of size (DS) is shown to have a utilization bound of 65%.

Figure 1.3: Schedulability bounds of multiprocessor scheduling algorithms from [49].

# 1.3 Multiprocessor Real-Time Scheduling During Overloads

Almost all of the past work on overload real-time scheduling [55, 31, 22, 50, 51, 52, 27], has focused on single processor systems, with very few exceptions. The only multiprocessor overload real-time scheduling algorithms that we are aware of (at the time of writing this thesis) include the Multiprocessor On-Line Competitive Algorithm (or MOCA) [48] and Global Multiprocessor Utility Accrual (or gMUA) [22] algorithms.

In [48], the authors determine the inherent upper bound on the best competitive ratio, in terms of accrued utility, that can be achieved by an online scheduler. They present a scheduling algorithm, MOCA, with a competitive ratio within a constant factor of the best competitive ratio found. MOCA divides the processors in a system into several "bands", each band being assigned a certain utility density. MOCA attempts to schedule an incoming task on a band that corresponds to its utility. If it is not possible to do so, the task is moved down the bands until one is found that can schedule it. As a result of this design, if a large number of low utility tasks arrive, they will quickly exhaust the lower bands of the system. This scenario may cause incoming low utility tasks to be rejected even though bands associated with higher utilities are idle.

gMUA is a global, best-effort real-time scheduling algorithm for multiprocessors. Like its single-processor counterparts [55, 31, 22, 50, 51, 52, 27], during underloads (i.e.,  $U \leq m$ ), gMUA defaults to global-EDF, and thus meets all deadlines (and accrues optimal total utility) up to a utilization bound of m/2. Also, like its single-processor counterparts, during overloads, the algorithm constructs a global multiprocessor schedule, favoring tasks from whom greater utility can be accrued, irrespective of task urgency, yielding graceful timeliness degradation and best-effort timeliness behavior.

Both MOCA and gMUA exclude task dependencies—i.e., they exclude task synchronization constraints (e.g., due to mutual exclusion) or precedence constraints.

#### 1.4 Research Contributions

Thus, we observe a clear gap in the literature: how to schedule real-time tasks on multiprocessors that are subject to run-time uncertainties causing transient and permanent overloads, and task dependencies, such that optimal total utility can be accrued when possible and best-effort timeliness behavior, otherwise?

This problem is NP-hard because its one-processor version is shown to be NP-hard [31]. We solve this problem in the thesis by developing a class of polynomial-time heuristic algorithms, called the *Global Utility Accrual* (or GUA) class of algorithms. The algorithms construct a directed acyclic graph representation of the task dependency relationship, and build a global multiprocessor schedule of the zero in-degree tasks to ensure mutual exclusion. Potential deadlocks are detected through a cycle-detection algorithm, and resolved by aborting a task in the deadlock cycle. We use the heuristics of the Potential Utility Density (or PUD), which was defined by Clark in [31], to heuristically maximize the total accrued utility.

The GUA class of algorithms include two algorithms, namely, the Non-Greedy Global Utility Accrual (or NG-GUA) and Greedy Global Utility Accrual (or G-GUA) algorithms. NG-GUA and G-GUA differ in the way schedules are constructed towards meeting all task deadlines, when possible to do so. While NG-GUA constructs a global schedule that defaults to G-EDF's schedulability bound, G-GUA does not default to any algorithm. However, both

NG-GUA and G-GUA try to maximize the total accrued utility. The greediness in the name of these algorithms describes the tendency of the algorithms to accrue as much total utility as possible. As the names suggest, G-GUA is more greedy for utility accrual when compared to NG-GUA. We establish several properties of the algorithms including conditions under which all task deadlines are met, satisfaction of mutual exclusion constraints, and deadlock-freedom. We also establish the asymptotic cost of both the algorithms.

We create a Linux-based real-time kernel called ChronOS for multiprocessors. ChronOS is extended from the PREEMPT\_RT real-time Linux patch [60], which provides optimized interrupt service latencies and real-time locking primitives. ChronOS provides a scheduling framework for the implementation of a broad range of real-time scheduling algorithms, including utility accrual, non-utility accrual, global, and partitioned scheduling algorithms. ChronOS provides a modular approach for development of the scheduling algorithms which can be implemented as kernel modules using the provided scheduler plugins.

We implement the GUA class of algorithms and their competitors in ChronOS and conduct experimental studies. The competitors include: EDF, G-EDF, G-NP-EDF, G-FIFO, gMUA, G-FIFO-PIP, G-NP-EDF-PIP, P-EDF and P-DASA. Our study reveals the following results:

- (1) In the absence of dependencies, the GUA class of algorithms accrue higher utility and satisfy greater number of deadlines than the deadline-based algorithms (G-EDF, G-NP-EDF) by as much as 750% and 600%, respectively.

- (2) In the absence of dependencies, the GUA class of algorithms accrue higher utility and satisfy greater number of deadlines compared to the partitioned algorithms by as much as 90% and 75%, respectively for P-DASA; and 450% and 600%, respectively for P-EDF.

- (3) As gMUA defaults to NG-GUA without dependencies, the performance of NG-GUA and gMUA is similar.

- (4) However, G-GUA outperforms NG-GUA and gMUA by accruing 25% more utility, while both NG-GUA and gMUA satisfy 5% more deadlines during underloads than G-GUA.

- (5) In the presence of dependencies, both NG-GUA and G-GUA accrue higher utility and satisfy greater number of deadlines than G-NP-EDF-PIP by as much as 250% and 150%, respectively.

To summarize, the research contributions of the thesis include:

- 1. the GUA class of multiprocessor real-time scheduling algorithms that allow tasks to be subject to run-time uncertainties, overloads, and dependencies, and yield optimal total utility when possible and best-effort timeliness behavior otherwise the first such multiprocessor real-time scheduling algorithms to do so.

- 2. the ChronOS multiprocessor real-time Linux kernel that provides optimized interrupt service latencies and real-time locking primitives (by virtue of PREEMPT\_RT patch) and a scheduling framework that allows the implementation of a broad range of real-time

scheduling algorithms, including utility accrual, non-utility accrual, global, and partitioned scheduling algorithms – the first such multiprocessor real-time Linux kernel.

## 1.5 Thesis Organization

The rest of the thesis is organized as follows: Chapter 2 overviews past and related work in the multiprocessor real-time scheduling space, and contrasts them with the thesis's problem space. Chapter 3 describes our models and scheduling objective. Chapter 4 presents the GUA class of algorithms, including G-GUA and NG-GUA. The algorithm rationale, design, pseudo-code description, and algorithm properties are described in this chapter.

Chapter 5 describes the ChronOS real-time Linux. We report our experimental studies in Chapter 6. Finally, we conclude the thesis in Chapter 7.

## Chapter 2

## Related Work

In this chapter we survey the past and related work focusing on the problem of scheduling on multiprocessors. The work can be classified into two categories — (i) classification based on the degree of run-time migration; and (ii) classification based on the utilization load. We discuss these in Sections 2.1 and 2.2, respectively.

## 2.1 Classification Based on Degree of Task Migration

Carpenter et al. [18] have classified the scheduling algorithms based on the degree of run-time migration, considering three categories: (i) no migration; (ii) restricted migration; (iii) and full migration.

No migration refers to the approach of partitioned scheduling. In this approach, tasks are assigned to processors using an off-line assignment algorithm and each processor runs an instance of an independent single processor algorithm. Partitioned Earliest Deadline First (P-EDF) [2] is one example that uses the optimal uniprocessor scheduling algorithm EDF. As the partitioned approach involves partitioning the tasks among processors, it can be shown to be equivalent to the NP-Hard bin-packing problem. The tasks are usually partitioned using polynomial time heuristic algorithms such as, first-fit, worst-fit and best-fit. In [9], Baruah et al. present an optimized first-fit partitioning algorithm. The key idea of the algorithm is to assign tasks to processor bins such that the tasks assigned to the processors create a feasible schedule.

In the restricted migration category, jobs are executed entirely on a single processor but they are allowed to migrate on job boundaries – with different jobs of the same task allowed to execute on different processors. Each job's runtime context needs to be maintained only on a single processor. However, the task-level context is allowed to be migrated. In [2], for a restricted migration model, where migration is allowed only at job boundaries, Anderson

et al. present an EDF-based partitioning scheme and scheduling algorithm that ensures bounded tardiness.

The *full migration* algorithms are the global algorithms that place no restriction upon interprocessor migration. The key idea of global scheduling is to maintain a single ready queue that has all the tasks released in the system which are eligible to be scheduled. The global queue is maintained according to some scheduling discipline and tasks are dispatched from this queue to any free processor.

Most of the global scheduling algorithms default to a single processor optimal algorithm such as Earliest Deadline First (EDF), or Rate Monotonic (RMS) algorithm. G-EDF [15] (Global Earliest Deadline First) orders the global queue based on the earliest deadline first order and the tasks are assigned to processors accordingly. However, once a scheduling event is triggered on one processor, a new schedule is created for which all tasks executing on other processors need to be preempted. In [10], Baruah derives the feasibility conditions for the non-preemptive version of G-EDF called the G-NP-EDF (Global non-preemptive EDF). In [32], Devi et al. derive the tardiness bounds for G-EDF and G-NP-EDF.

In [11, 12] Baruah et al. present a different global scheduling approach, called PFair [11] (Proportionate Fair) scheduling, which divides a task into quantum sized "sub-tasks" that are treated as the scheduleable entities. Each "sub-task" must execute within a "window" of time slots, where the last "window" is the deadline of the task. This approach has been shown to realize full system utilization and hence Pfair-based algorithms are optimal during underloads  $(U \leq m)$  [11, 12]. A particularly efficient version of Pfair scheduling, PD<sup>2</sup>, was developed in [3] and its scalability was showcased in [16]. However, Pfair algorithms incur significant scheduling overheads due to their quantum-based scheduling approach as shown in [32]. Although, Pfair is optimal during underloads, its behavior during overloads follows an EDF-like pattern. This is because Pfair continues to use the notion of earliest deadline, even at the "sub-task" level. In [25] Cho et al. describe the LLREF scheduling algorithm. LLREF is a optimal real-time scheduling algorithm for multiprocessors which is not based on time quanta.

#### 2.2 Classification Based on Utilization Load

Scheduling algorithms can also be classified based on those that assume the total utilization  $U \leq m$ , where m is the number of CPUs and those that assume U to be arbitrary. The former condition is referred to as underload while the later is referred to as overload. For multiprocessor systems, it has been shown that partitioned and non-Pfair global scheduling have similar schedulability bounds [18] and that these bounds are significantly below full system utilization. Algorithms that are not specifically designed to address overloads can suffer an unacceptable amount of degradation when they occur [13, 48]. What is needed is a set of algorithms that are designed with overload scheduling specifically in mind. This would

allow these algorithms to successfully schedule as many high importance tasks as possible during overloads.

On single processor systems, Utility Accrual algorithms, such as DASA [31] and LBESA [55], that maximize accrued utility for downward "step" TUFs default to EDF during underloads, since EDF satisfies all deadlines during underloads, consequently maximizing possible accrued utility. During overloads, they favor more important activities, irrespective of urgency. Thus, deadline scheduling's optimal timeliness behavior is a special case of utility accrual scheduling for single processor systems.

For a multiprocessor system, gMUA [22] and MOCA [48] scheduling algorithms provide best-effort utility accrual during overloads. gMUA defaults to global-EDF, a non-optimal scheduling algorithm, during underloads. During overloads, gMUA tries to maximize accrued utility. MOCA, on the other hand, divides the processors into "bands" where each band is assigned a certain utility density. MOCA attempts to schedule an incoming task on a band that corresponds to its utility. If it is not possible to execute the task on its utility band, MOCA moves the task down the bands until one is found that can schedule it. As a result of this design, if a large number of low utility tasks arrive, they will quickly exhaust the lower bands of the system and this scenario may cause incoming low utility tasks to be rejected even though bands associated with higher utilities are idle.

Both gMUA and MOCA suffer from lack of support for resources, such as locks, and their behavior in the presence of dependencies has not been studied.

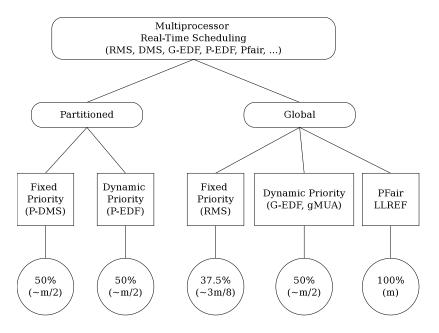

| U > m $U <= m$                                     | PD <sup>2</sup><br>LLREF | G-EDF<br>G-NP-EDF                    | P-EDF                                | G-GUA<br>NG-GUA                      |

|----------------------------------------------------|--------------------------|--------------------------------------|--------------------------------------|--------------------------------------|

| Meet all<br>deadlines                              | No<br>Yes                | $No$ $No$ meets only if $U \le -m/2$ | $No$ $No$ meets only if $U \le -m/2$ | $No$ $No$ meets only if $U \le -m/2$ |

| Bound<br>best-effort<br>real-time<br>time interval | No<br>Yes                | No<br>Yes                            | $No$ $No$ meets only if $U \le -m/2$ | Yes<br>Yes                           |

Figure 2.1: Characterization of scheduling algorithms during underloads  $(U \leq m)$  and overloads (U > m) based on ability to meet all deadlines and bounded best-effort real-time time interval.

### 2.3 Summary

Figure 2.1 gives a summary of the classification discussed in this chapter. We observe the following:

- 1. During underloads (for  $U \leq m$ ) only Pfair (PD<sup>2</sup>) and LLREF scheduling algorithms can meet all deadlines. This is primarily because these algorithms have been proven to be optimal during underloads.

- 2. During underloads, G-EDF, G-NP-EDF and P-EDF scheduling algorithms can only meet their deadlines upto  $U \approx m/2$ .

- 3. During underloads, an optimal best-effort behavior can be seen in  $Pfair(PD^2)$  and LLREF. This is due to the fact that they are optimal during underloads.

- 4. During overloads, none of the scheduling algorithm can meet their deadlines.

- 5. During overloads, none of the scheduling algorithms provide a best-effort bound on the real-time interval.

- 6. There are no scheduling algorithms that provide best-effort behavior during overloads in the presence of dependencies.

There is a clear gap in the past work, that establishes a need for best-effort utility accrual real-time scheduling algorithms for multiprocessors, that provides best-effort behavior during overloads for dependent tasks. We bridge this gap by designing the NG-GUA and G-GUA scheduling algorithms which we discuss in detail in the subsequent chapters.

## Chapter 3

## Models and Objective

#### 3.1 Thread Model

We consider the programming model where each task,  $T_i$ , can have a periodic or an aperiodic execution. Each such invocation of the task,  $T_i$ , is referred to as phase  $J_i$ . Each phase has an estimated best-faith<sup>1</sup> execution time  $e_i$  and a deadline  $d_i$ . No specific task arrival pattern is assumed.

Tasks can be implemented using threads on an operating system. There are two models that can be used. A single thread can be created that represents the task and all its phases. At the end of the task's period, the thread goes to sleep and wakes up at the next period. Hence, each phase of the task can be executed on the same thread with a call to a function such as <code>sleep\_until\_next\_period()</code> between phase invocations. We call this the "thread-is-a-task" model. On the other hand, an individual thread could represent each phase of a task. Hence, at the invocation of each phase of a given task, a separate thread is fired. We call this the "thread-is-a-phase" model.

#### 3.2 Timeliness Model

We specify the time constraint of each task using a Time/Utility Function (TUF) [43]. A TUF allows us to decouple the urgency of a task from its importance. This decoupling is a key property allowed by TUFs since the urgency of a phase may be orthogonal to its importance. A task  $T_i$ 's TUF is denoted as  $U_i(t)$ . A classical deadline is unit-valued—i.e.,  $U_i(t) = \{1,0\}$ , since importance is not considered. Downward step TUFs generalize classical deadlines where  $U_i(t) = \{\{m\}, 0\}$ . We focus on downward step TUFs, and denote the maximum, constant utility of a TUF  $U_i(t)$ , simply as  $U_i$ .

<sup>&</sup>lt;sup>1</sup>This is an estimate of execution time, not an upper bound, and may be violated at runtime

Each TUF has an initial time  $I_i$ , which is the earliest time for which the TUF is defined, and a termination time  $X_i$ , which, for the special case of downward "step" TUFs we consider, is its discontinuity point. Equations 3.1a-b describe the mathematical representation of a downward "step" TUF.

$$U_{i}(t) > 0, \forall t \in [I_{i}, X_{i}], \forall i$$

$$(3.1a)$$

$$U_{i}(t) = 0, \forall t \notin [I_{i}, X_{i}], \forall i$$

(3.1b)

#### 3.3 Resource Model

A resource  $R_j$  has a critical section length,  $C_j$ . The length of the critical section can be variable. Any phases  $J_i$  can request a resource  $R_j$  and enter critical sections by invoking APIs such as ResRequest(). Until the request for  $R_j$  is granted, the phase is said to be blocked on the resource. Once  $R_j$  is granted to  $J_i$ , we refer to  $J_i$  as the Owner of the resource.  $J_i$  invokes ResRelease()<sup>2</sup> to complete the critical section. There is no restriction on the number of phases that may request a resource. However, a phase can only be blocked on a single resource which is being owned by another phase. We refer to this as the single-unit resource model.

#### 3.4 Processor Model

We consider a multiprocessor/multi-core architecture with M cores/processors. In the rest of the thesis, cores and processors will be used interchangeably unless explicitly stated otherwise.

#### 3.5 Abort Model

We consider the model in which any phase that has blown its deadline can be aborted by the system. The phase is sent an abort signal which is handled by the phase using an abort\_handler. The handler is used by the phase to release any resources that it may have requested or owned.

<sup>&</sup>lt;sup>2</sup>These sample APIs have been used for the sake of explanation of the concept

## 3.6 Scheduling Objective

As mentioned earlier, the problem of scheduling real-time tasks on multiprocessors that are subject to run-time uncertainties causing transient and permanent overloads, is NP-Hard.

Our primary objective is to design a class of polynomial-time heuristic<sup>3</sup> algorithms that provide best-effort utility accrual during overloads in the presence of dependencies (such as locks) on a multiprocessor system. The algorithms should yield optimal total utility when possible and best-effort timeliness behavior otherwise.

<sup>&</sup>lt;sup>3</sup>Another approach of solving this problem is by designing approximate algorithms. We chose the heuristics route because it is easier to design a heuristic algorithm as compared to an approximation. Also, the insights provided by a heuristic algorithm can be useful in the design of approximate algorithms.

# Chapter 4

# The GUA Class of Real-Time Scheduling Algorithms

In this chapter we present the Global Utility Accrual (GUA) class of algorithms. We discuss two algorithms in detail — Non-Greedy Global Utility Accrual (NG-GUA) and Greedy Global Utility Accrual (G-GUA). The non-greedy variant defaults to Global Earliest Deadline First scheduling algorithm with Priority Inheritance Protocol (G-EDF-PIP) during underloads, while maximizing the total accrued utility during overloads. On the other hand, the greedy algorithm uses the concept of Global Value Density (GVD) to maximize accrued utility during both underloads as well as overloads.

### 4.1 Ensuring Mutual Exclusion

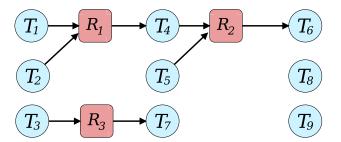

When resources, such as locks, are used, it is important to ensure mutual exclusion. Consider Figure 4.1 which shows a dependency chain consisting of nine phases and three resources. Phases  $T_1$  and  $T_2$  require resource  $R_1$ , which is owned by  $T_4$ . Phases  $T_4$  and  $T_5$  require resource  $R_2$ , which is owned by phase  $T_6$ . Phase  $T_3$  requires resource  $R_3$ , which is owned by phase  $T_7$ . Phases  $T_8$  and  $T_9$  do not require any resources and are independent. In order to ensure mutual exclusion, we can only schedule phases that do not have a dependency on other phases.

We construct a global precedence graph, which is a directed acyclic graph (DAG), of the phases with the nodes representing the phases and the edges representing the resources being requested. Figure 4.2 gives the graph representation of the dependency chain shown in Figure 4.1. Phase  $T_6$  owns resource  $R_2$ , which is being requested by phases  $T_4$  and  $T_5$  and therefore they are dependent on phase  $T_6$ . This is represented in the graph as an edge  $R_2$  from  $T_6$  directed towards phases  $T_4$  and  $T_5$ . In a similar fashion, phase  $T_4$  currently owns resource  $R_1$ , which is being requested by phases  $T_1$  and  $T_2$ . Hence, we see an edge from

Figure 4.1: A phase and resource dependency chain with nine phases and three resources

phase  $T_4$  towards phases  $T_1$  and  $T_2$ . Similarly, we have an edge from phase  $T_7$  to  $T_3$ , which requires resource  $R_3$  that is being owned by phase  $T_7$ . Phases  $T_8$  and  $T_9$  do not have any resources requested and hence are represented as independent nodes.

All the nodes in the given DAG that do not have any edges from any other node are referred to as zero in-degree phases. In order to construct a schedule that respects mutual exclusion, we consider only the zero in-degree phases, as these represent phases that are not dependent on any other phase.

### 4.2 Maximizing Accrued Utility

In order to define a measure for the benefit that a given phases' completion can bring to the total accrued utility of the system, we use the concept of Potential Utility Density (or PUD), which was first defined by Clark in [31]. PUD is defined as the ratio of the remaining execution time of a phase at time t to the utility of the phase defined by the TUF at time t, i.e., U(t). The PUD of a phase is a dynamic value as it depends on the remaining execution time of a phase and hence at any given time it denotes the "return on investment" that can be gained for each unit of processing time assigned to that particular phase.

Clark defines and uses PUD in DASA [31] when considering phases that are dependent on each other. Clark considers the PUD of the entire group involved in a dependency relationship and uses the concept as an indicator of the urgency to execute a phase that blocks other phases; and also as a measure of the total benefit that the system will accrue if the entire dependency chain is executed while respecting mutual exclusion. However, as DASA is a uniprocessor scheduling algorithm, only a single phase can be executed at any given time t.

The problem with multiprocessor scheduling is, that it is possible for a scheduler to schedule a phase and one or more of its dependents on two or more processors concurrently. This does not benefit the total system utility accrual given the fact that the phase blocked on a resource is going to waste its CPU cycles. In order to prevent this, we use the DAG to find the set of zero in-degree phases that do not have any dependency relationship among each

Figure 4.2: Directed Acyclic Graph (DAG) for the dependency chain shown in Fig 4.1. The nodes with a zero in-degree are eligible for final schedule in order to preserve mutual exclusion.

other and hence can be executed concurrently on any given M processors (as discussed in Section 4.1).

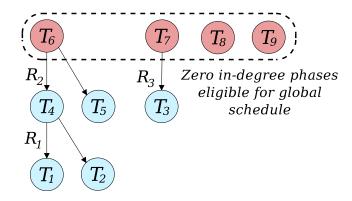

However, given a set of N zero in-degree phases, we require a method to select the M phases that, when executed on the M processors, would maximize the total accrued utility of the system. For this we define the term  $Global\ Value\ Density$  (or GVD). To avoid any confusion with the PUD of a phase, we define the term  $Local\ Value\ Density$  (or LVD) which is equal to the PUD of a given phase and is used instead of PUD in the rest of the thesis. GVD is computed only for the  $zero\ in-degree$  phases and it is defined as the sum of the LVD's of individual phases that are in a dependency relation with the given zero in-degree phase.

Consider Figure 4.3. We compute the GVD for phases  $T_6$ ,  $T_8$  and  $T_9$  as these represent the current set of zero in-degree phases. The GVD for  $T_6$  is computed as:  $GVD(T_6) = GVD(T_4) + GVD(T_5) + LVD(T_6)$ . This is equivalent to:  $GVD(T_6) = LVD(T_6) + LVD(T_4) + LVD(T_5) + LVD(T_1) + LVD(T_2)$ . The GVD for  $T_8$  and  $T_9$  is equivalent to their respective LVDs as these phases do not have dependents.

Figure 4.3: Computing the global value density for a graph

### 4.3 Deadlock Detection and Resolution

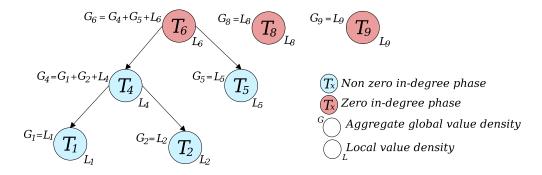

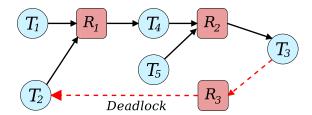

A deadlock can occur if a phase  $T_1$ , which owns a resource  $R_1$ , makes a request for another resource  $R_2$ , which is being owned by a phase currently blocked on a resource  $R_i$  in the dependency chain of  $T_1$ . Figure 4.4 gives an example of a deadlock. Phase  $T_4$  requires resource  $R_2$  which is currently owned by phase  $T_3$ . Phase  $T_3$  requires resource  $R_3$  which is owned by phase  $T_2$ . However, phase  $T_2$  is currently blocked on resource  $R_1$  which is owned by  $T_4$ . Hence the deadlock.

Figure 4.4: A phase and resource dependency chain with a deadlock condition.

A deadlock can be detected during the construction of the DAG. For the given set of phases that are ready for being scheduled, the construction of the DAG involves traversing the list of ready phases and creating a graph that establishes an edge relationship between nodes. For each phase  $T_i$ , we use API calls such as ResRequested( $T_i$ ) and Owner( $R_i$ ) to find the parent node in the DAG. We compute the relationship between all the dependent nodes in the chain. While the dependency chain is being computed, a list  $\sigma_i$  is created with a reference to the nodes in the dependency chain of  $T_i$  such that at every step in the construction of the DAG, we check  $\sigma_i$  to verify if the node has already been inserted into the DAG. If the node is already in  $\sigma_i$ , it establishes the presence of a deadlock.

Fig 4.5 shows the process of DAG construction for the dependency chain of Figure 4.4. We see that there is deadlock between phases  $T_6 \to T_2 \to T_4 \to T_6$ . At this point we need to remove one of the phases from the deadlocked loop to resolve the deadlock. We remove the Least Local Value Density (or Least-LVD) phase amongst the phases that are currently in a deadlock. The rationale behind this approach is to ensure that we only abort a phase that provides the least utility to the total system accrued utility.

Aborting a phase involves marking the phase for immediate completion by sending it a signal. The phase can catch this signal and invoke its abort\_handler to perform a cleanup; releasing resources such as locks.

### 4.4 Assigning Zero In-degree Phases to Processors

In order to assign the zero in-degree phases to the processors, we use the concept of the "least sum of total phase remaining execution time" on each processor, which was first described

Figure 4.5: Deadlock detection and resolution.

by Cho in [22].

Let us assume a set of zero in-degree phases along with their respective remaining execution times:  $\{T_1:10\}, \{T_2:12\}, \{T_3:5\}, \{T_4:15\}$ . Let us consider a multiprocessor system with M=2. Initially, the sum of the remaining execution times for phases on each processor is set to zero:  $\{p_1:0\}, \{p_2:0\}$ . This is because no phase has been currently assigned to the processors. Now,  $T_1$  can be assigned either to  $p_1$  or  $p_2$ . Let us assume that  $T_1$  is assigned to  $p_1$ .  $T_1$ 's remaining phase execution cost gets added to  $p_1$ . We have,  $\{p_1:10\}, \{p_2:0\}$ .  $T_2$  gets assigned to  $p_2$  and we get,  $\{p_1:10\}, \{p_2:12\}$ . At this point,  $T_3$  needs to be assigned to the processors that has the least sum of total phase remaining execution time, which is  $p_1$ . The process continues until all the phases have been assigned to processors.

## 4.5 Data Structures and Auxiliary Functions

Before describing the algorithms in detail we list the member variables that can be added to the phase data structure to describe the timeliness model and the DAG representation of the resource model.

### 4.5.1 Data Structure for Timeliness Model

The following member variables can be used to define the timeliness model for each phase:

#### J.ExecCost

The good faith execution cost of phase J.

#### J.Deadline

The deadline of phase J.

#### J.RemExec

The remaining execution time of a phase J. This represents the time that is left of the phase's execution cost. The value can be updated every time the phase is preempted by the scheduler or just before the new schedule is created. This value is used for the calculation of the Value Density for the phase.

### J. Utility

The utility of the phase J as represented by its TUF.

#### J.LocalValDen

The Local Value Density (LVD) of a phase J. The LVD is calcuated as  $\frac{J.Utility}{J.RemExec}$ .

### 4.5.2 Data Structure for Resource Model

The following member variables can be used to define the resource model for each phase represented as a DAG:

#### J.AggUtil

The aggregate utility of a phase J. This is used for the calculation of the Global Value Density.

#### J.AggExec

The aggregate remaining execution time of a phase J. This is used for the calculation of the Global Value Density.

#### J.GlobalValDen

The Global Value Density (GVD) of a phase J. GVD is calculated as  $\frac{\Sigma J.AggUtil}{\Sigma J.AggExec}$  for phase J and all its dependents.

#### J.PIPDeadLn

The PIP deadline of a zero in-degree phase J is equal to the deadline of the phase in J's dependency chain that has the earliest deadline. The PIP deadline is only calculated for zero in-degree phases. If a zero in-degree phase J does not have any dependents, the PIP deadline is equal to J. Deadline.

### J.InDegree

The total number of links that come into a phase J in the DAG. The in-degree of a phase J can not be more than one.

### J.OutDegree

The total number of links that go out of a phase in the DAG. A phase J can have a value of zero or more for the out-degree.

#### J.ResourceReq

The reference to the resource that has been requested by a phase J.

### J.NeighborList

The reference to the first dependent child node of a phase J in the DAG.

### J.NextNeighbor

The reference to the next dependent child node of a phase J in the DAG.

### J.Parent

The reference to the phase which owns the resource that the phase J has requested. Figure 4.6 illustrates how the DAG can be represented using J.NeighborList, J.NextNeighbor and J.Parent.

Figure 4.6: Data structure representation of the DAG

### 4.5.3 Auxiliary Functions

In this section, we define the auxiliary functions that are used by the NG-GUA and G-GUA scheduling algorithms. These methods perform small functions which are implementation independent.

#### InsertList( $J, \sigma$ )

Insert the phase J into the list  $\sigma$ .

### RemoveList $(U, \sigma)$

Remove phase J from the list  $\sigma$ .

### ComputeGVD( $\sigma_{in}$ )

For the given list of zero in-degree phases in  $\sigma_{in}$ , compute the global value density, which is calculated as  $\frac{\Sigma J.AggUtil}{\Sigma J.AggExec}$  for phase J and its dependents represented as child nodes of the zero in-degree phase in the graph.

### $SortByGVD(\sigma_{in})$

Sort the list  $\sigma_{in}$  by the decreasing global value density and return the new ordered list in  $\sigma_{out}$ .

### $SortByDeadLn(\sigma_{in})$

Sort the list  $\sigma_{in}$  by the decreasing deadline (EDF order) and return the new ordered list in  $\sigma_{out}$ .

#### $HeadOf(\sigma)$

Return the phase J which is at the head of the list  $\sigma$ .

### $InsDeadLnPos(J, \sigma)$

Insert phase J in the list  $\sigma$  at its deadline position.

### $FindZIDPhases(\sigma_t)$

Return the list  $\sigma_z$  of zero in-degree phases in  $\sigma_t$ .

### $FindPIPDeadLn(\sigma_z)$

For each zero in-degree phase  $J \in \sigma_z$ , assign the PIP deadline for J equal to the deadline of the phase which has the earliest deadline amongst the dependents of J. If J does not have any dependents, the PIP deadline of J equals its deadline.

### RemoveLeastLVD( $\sigma$ )

Remove the phase with the least LVD from  $\sigma$ .

### RemoveLeastGVD( $\sigma$ )

Remove the phase with the least GVD from  $\sigma$ .

#### IsPresent $(J, \sigma)$

Return true if the phase J is present in list  $\sigma$ , else return false.

#### IsFeasible( $\sigma$ )

Return true if the given schedule in list  $\sigma$  is feasible. For  $\sigma$  to be feasible, the predicted completion time of each phase in  $\sigma$  must never exceed its deadline.

### IsEmpty( $\sigma$ )

Return true if the list  $\sigma$  is empty, else return false.

#### InsertEdge (J, DepJ)

Insert an edge between DepJ and J.

### RemoveEdge(J)

Remove all in-degree and out-degree edges of J.

### Owner(R)

Return the phase J that holds resource R. If there is no phase that holds resource R, return NULL.

### ResRequested(J)

Return the resource R requested by phase J.

#### FindProcessor()

Return the processor p which has the least sum of total phase execution cost.

### FindProcessor(cpu\_mask)

This version of FindProcessor() takes an argument called cpu\_mask, which is a list of processors that have been checked before and need to be masked (avoided) while selecting the processor with the least sum of total phase execution cost. If all the processors on the system are included in the mask, the function returns NULL.

### AddCpuToMask(p, cpu\_mask)

Add processor p to the cpu\_mask. The cpu\_mask can be a bit array where each bit corresponds to each online processor, in which case, set the bit corresponding to p.

#### FindLeastLVD(J)

For the given phase J's dependency chain, find the phase with the least Local Value Density (LVD).

### UpdateCpuEC(p, J, b)