## CCM Totem-Pole Bridgeless PFC with Ultra-Fast IGBT

Bo Zhou

Thesis submitted to the faculty of the Virginia Polytechnic Institute and State University In partial fulfillment of the requirements for the degree of

> Master of Science In Electrical Engineering

Jih-Sheng Lai, Chair Dong S. Ha Douglas J. Nelson

November 25, 2014 Blacksburg, VA

Keywords: Totem-pole, Bridgeless PFC, ADP1048, Zero-crossing

Copyright 2014, Bo Zhou

**CCM Totem-Pole Bridgeless PFC with Ultra-Fast**

**IGBT**

Bo Zhou

Bradley Department of Electrical and Computer Engineering

(ABSTRACT)

The totem pole PFC suffers from the Mosfet body diode reverse recovery issue

which limits this topology adopted in the CCM high power condition. As the ultra-fast

IGBT which is capable of providing 100 kHz switching frequency is available in the

market, it is possible to apply the totem pole PFC in CCM high power condition. The

thesis provides a method by implementing the ultra-fast IGBT and SiC diode to replace

the MOSFET in this topology.

To verify the method, a universal 1.5kW CCM totem pole PFC is designed and

tested. The design adopts the ADP1048 programmable digital PFC controller by adding

external logic gate for totem-pole PFC. ADP1048 greatly simplifies the design process

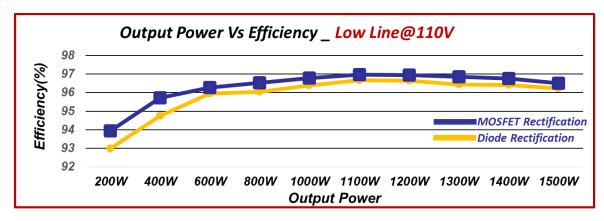

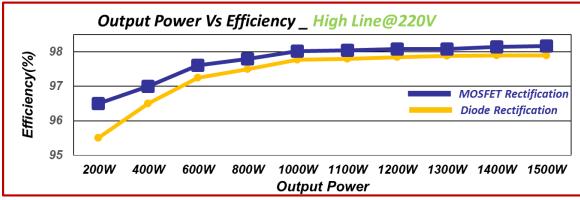

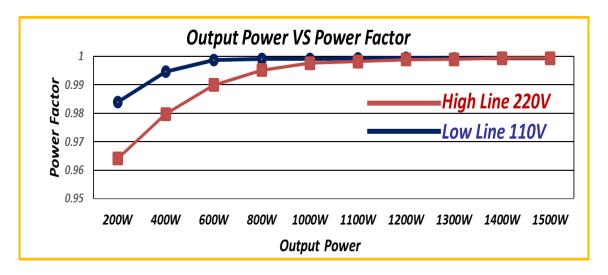

and satisfies the design requirements. The experiment results verify that the totem-pole

PFC can be applied into CCM high power condition by using the method. The DC output

voltage is well regulated. The power factor is higher than 0.98 when the load is above

400W. The measured efficiency can achieve up to 96.7% at low line and 98.2% at high

line condition with switching frequency 80 kHz.

Keywords: Totem Pole PFC, ADP1048, Ultra-fast IGBT, CCM

**To my Parents**Mingxue Zhou and Min Wang

To my wife Zheng Zhao

## Acknowledgements

I would like to express my sincere appreciation to my advisor, Dr. Jason Lai, for all of his patience, guidance, encouragement, and support throughout my graduate studies. Being his student is my great honor. He is the one who brought me into power electronics field. His profound knowledge, rigorous attitude toward research and creative thinking has been a source of inspiration for me throughout the years and will benefit my career as well as my whole personal life. Without his kind support and encouragement, I would never reach this far.

I am grateful to my committee members: Dr. Dong S. Ha and Dr. Douglas J. Nelson for their interests, suggestions and kind supports for my research work.

It has been a great pleasure to work in Future Energy Electronics Center (FEEC), not only because of the talented colleagues but also the friendship. I cherish the wonderful time that we worked together. I would like to thank Mr. Gary Kerr, Dr. Wensong Yu, Dr. Younghoon Cho, Dr. Zakariya Dalala, Dr. Thomas LaBella, Mr. Zaka Ullah Zahid, Ms. Hongmei Wan, Mr. Wei-han Lai, Mr. Cong Zheng, Mr. Baifeng Chen, Mr. Rui Chen, Mr. Lanhua Zhang, Miss. Yuwei Bai, Miss. Xiaonan Zhao, Mr.Chungyi Lin, Mr. Yuchen Liu, Mr. Jason Dominic, Mr. Andrew Amrhein, Mr. Shiwei Mao, for their helpful discussions, great supports and precious friendship. Especially thank Dr. Ruixiang Hao, Dr. Rui Chen and Mr. Bin Gu for their help on my dissertation.

Last but not least, I offer my deepest gratitude to my wife, Zheng Zhao for her everlasting love, support, confidence and encouragement for all my endeavors.

## **Table of Contents**

| Chapter 1: Int | roduction1                                          |

|----------------|-----------------------------------------------------|

| 1.1            | Background and Research Objective                   |

| 1.2            | Thesis Outline                                      |

| Chapter 2: Pov | ver Factor Correction4                              |

| 2.1            | Power Factor Definition                             |

| 2.2            | Active Power Factor Correction Control Methods      |

| 2.2.1          | Peak Current Control Method                         |

| 2.2.2          | Hysteresis Current Control Method                   |

| 2.2.3          | Average Current Control Method                      |

| 2.3            | Bridgeless Boost PFC Topology Overview              |

| 2.3.1          | Traditional Boost Bridgeless PFC                    |

| 2.3.2          | Semi-Bridgeless Boost PFC                           |

| 2.3.3          | Dual Boost Bridgeless PFC with Bidirectional Switch |

| 2.3.4          | Pseudo Totem-Pole Bridgeless PFC Topology           |

| 2.3.5          | Totem-Pole Bridgeless Boost PFC Topology            |

| 2.3.6          | Bridgeless PFC topologies comparison                |

| Chapter 3: A N | Method for CCM Totem-Pole PFC22                     |

| 3.1            | Ultra-Fast IGBT Implemented in CCM Totem-Pole PFC   |

| 3.1.1          | Ultra-Fast IGBT Introduction                        |

| 3.1.2          | Ultra-fast IGBT and SiC Diode in Totem-pole PFC     |

| 3.2            | Totem-Pole PFC Circuit Structure                    |

| 3.3            | Operation Mode Analysis                                  | 24    |  |  |

|----------------|----------------------------------------------------------|-------|--|--|

| 3.3.1          | Positive Half Line Cycle Operation                       | 24    |  |  |

| 3.3.2          | Negative Half Line Cycle Operation                       | 26    |  |  |

| 3.4            | Zero Crossing Ring Issue with Mosfet Rectification       |       |  |  |

| 3.5            | 3.5 CCM Totem-Pole PFC Control Loop Design               |       |  |  |

| 3.5.1          | 3.5.1 PFC Control Method                                 |       |  |  |

| 3.5.2          | Inner Current Loop Design                                | 34    |  |  |

| 3.5.3          | Outer Voltage Loop Design                                | 38    |  |  |

| 3.5.4          | Simulation Results                                       | 41    |  |  |

| Chapter 4: Imp | plement ADP1048 Controller for CCM Totem-Pole PFC Design | gn 45 |  |  |

| 4.1            | ADP1048 Introduction                                     | 46    |  |  |

| 4.2            | 1.5kW Totem-Pole PFC Design Specification                | 49    |  |  |

| 4.3            | Power Stage Component Design                             | 50    |  |  |

| 4.3.1          | Inductor Design                                          | 50    |  |  |

| 4.3.2          | Capacitor Design                                         | 52    |  |  |

| 4.3.3          | Power Switch Selection                                   | 55    |  |  |

| 4.4            | Control Design with ADP1048                              | 56    |  |  |

| 4.4.1          | Modified ADP1048 PWM Signal for Totem-Pole PFC           | 56    |  |  |

| 4.4.2          | Input Voltage Sensing Design                             | 58    |  |  |

| 4.4.3          | Output Voltage Sensing Design                            | 59    |  |  |

| 4.4.4          | Input Current Sensing Design                             | 59    |  |  |

| 4.4.5          | ADP1048 Control Setting                                  | 60    |  |  |

| Chapter 5: Exp | periment Setup and Results                               | 67    |  |  |

| 5.1        | Experiment Setup        | 67 |

|------------|-------------------------|----|

| 5.2        | Measurement Data        | 69 |

| Chapter 6: | Summary and Future Work | 77 |

| 6.1        | Summary                 | 77 |

| 6.2        | Novelty of Work         | 78 |

| 6.3        | Future Work             | 78 |

| Bibliograp | hy                      | 79 |

## **List of Figures**

| Figure 2.1 Illustration of Power Factor                                      | 4  |

|------------------------------------------------------------------------------|----|

| Figure 2.2 Traditional Boost PFC Topology                                    | 6  |

| Figure 2.3 Peak Current Mode Control Scheme                                  | 8  |

| Figure 2.4 Peak Current Mode Control Waveform                                | 8  |

| Figure 2.5 Peak Current Mode Control Current Perturbation                    | 9  |

| Figure 2.6 Hysteresis Current Mode Control Scheme                            | 10 |

| Figure 2.7 Hysteresis Current Mode Control Waveform                          | 11 |

| Figure 2.8 Average Current Mode Control Scheme                               | 12 |

| Figure 2.9 Average Current Mode Control Scheme                               | 12 |

| Figure 2.10 Dual Boost Bridgeless PFC Topology                               | 14 |

| Figure 2.11 Semi-Boost Bridgeless PFC                                        | 15 |

| Figure 2.12 Dual Boost Bridgeless PFC with bidirectional switch              | 16 |

| Figure 2.13 Pseudo Totem-Pole Bridgeless PFC Topology                        | 17 |

| Figure 2.14 Totem-Pole Bridgeless Boost PFC Topology                         | 18 |

| Figure 2.15 Reverse Recovery Issue in Totem-pole PFC                         | 19 |

| Figure 3.1 Totem-pole PFC with ultra-fast IGBT and Diode Line Rectification  | 23 |

| Figure 3.2 Totem-pole PFC with ultra-fast IGBT and MOSFET Line Rectification | 24 |

| Figure 3.3 Totem-pole PFC Positive line cycle when switch is ON              | 25 |

| Figure 3.4 Totem-pole PFC Positive line cycle when switch is OFF             | 25 |

| Figure 3.5 Totem-pole PFC Negative line cycle When Switch is On              | 26 |

| Figure 3.6 Totem-pole PFC Negative line cycle When Switch is off             | 27 |

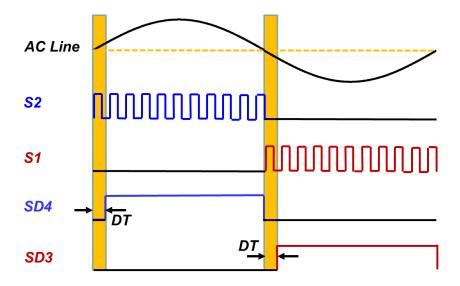

| Figure 3.7 Totem-pole PFC Switching Signal                                   | 27 |

| Figure 3.8 Drain to Source Voltage Ring Waveform                             | 28 |

| Figure 3.9 Zero Crossing Voltage Ring Issue Analysis                         | 29 |

| Figure 3.10 Zero Crossing Voltage Ring Issue Analysis                                  |

|----------------------------------------------------------------------------------------|

| Figure 3.11 MOSFET Line Rectification PWM Signal                                       |

| Figure 3.12 Boost PFC Average Current Control Diagram                                  |

| Figure 3.13 PFC Small Signal Model Block Diagram                                       |

| Figure 3.14 power stage control to current small signal model                          |

| Figure 3.15 Control to Current $G_{id}(s)$ Bode Plot                                   |

| Figure 3.16 Current Loop Compensation Bode Plot                                        |

| Figure 3.17 Simplified Voltage Loop Diagram                                            |

| Figure 3.18 Low Frequency Voltage Loop Small Signal Model                              |

| Figure 3.19 Low Frequency Voltage Loop Small Signal Model for Constant Power 40        |

| Figure 3.20 Voltage Loop Compensation Bode Plot                                        |

| Figure 3.21 Totem-pole PFC Simulation Circuit                                          |

| Figure 3.22 Totem-pole PFC Simulation Results with Different Levels 44                 |

| Figure 4.1 Control Diagram with ADP1048 in Totem-Pole PFC Circuit 45                   |

| Figure 4.2 ADP1048 Pins Configuration, Analog Devices, "ADP1047/ADP1048 Digital        |

| Power Factor Correction Controller with Accurate AC Power Metering'                    |

| Datasheet. Used under fair use, 201447                                                 |

| Figure 4.3 ADP1048 Functional Block Diagram, Analog Devices, "ADP1047/ADP1048          |

| Digital Power Factor Correction Controller with Accurate AC Power Metering'            |

| Datasheet. Used under fair use, 201449                                                 |

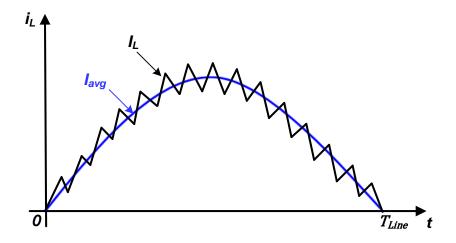

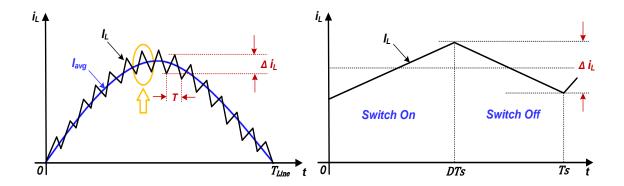

| Figure 4.4 Inductor Current (a) Half Line Cycle (b) One Switching Cycle 51             |

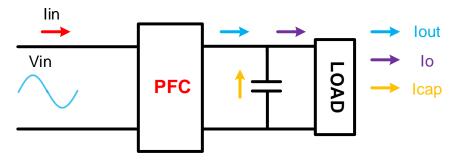

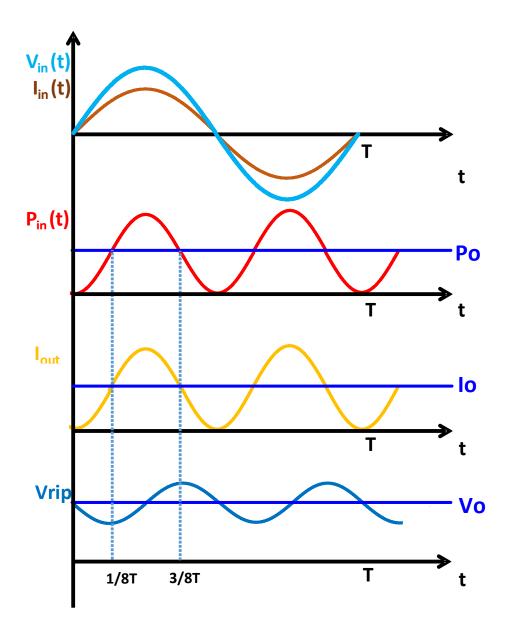

| Figure 4.5 PFC diagram53                                                               |

| Figure 4.6 Output Voltage Ripple Waveform53                                            |

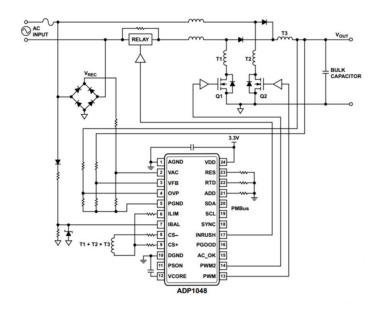

| Figure 4.7 Schematic of Dual Boost Bridgeless PFC Circuit with ADP1048, Analog Devices |

| "ADP1047/ADP1048 Digital Power Factor Correction Controller with Accurate              |

| AC Power Metering" Datasheet. Used under fair use, 2014                                |

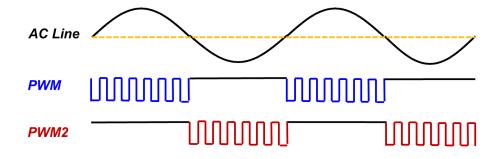

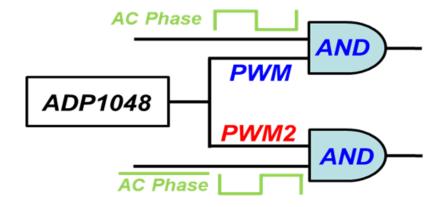

| Figure 4.8 ADP1048 Bridgeless Mode PWM Signal             | 57 |

|-----------------------------------------------------------|----|

| Figure 4.9 Modified ADP1048 PWM Signal Diagram            | 58 |

| Figure 4.10. Input Sensing Circuit Diagram                | 58 |

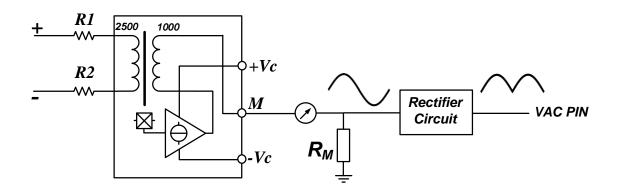

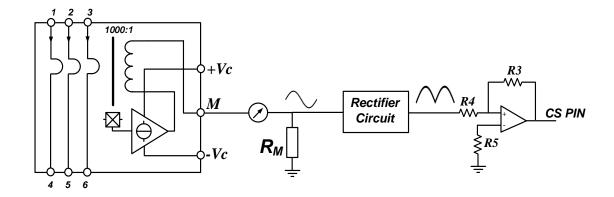

| Figure 4.11 Input Current Sensing Circuit Diagram         | 60 |

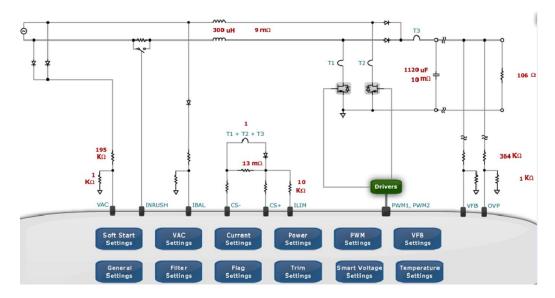

| Figure 4.12 GUI Main Interface Window                     | 61 |

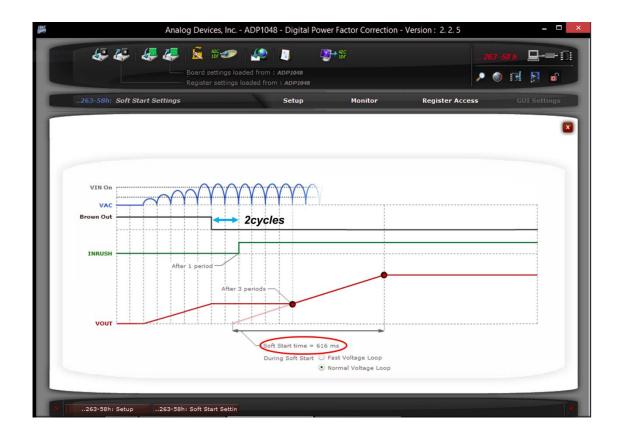

| Figure 4.13 Soft Start Setting in GUI                     | 62 |

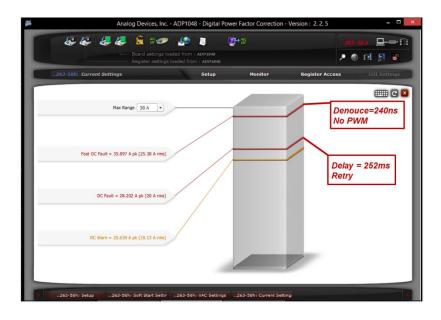

| Figure 4.14 Current Limit Setting in GUI                  | 63 |

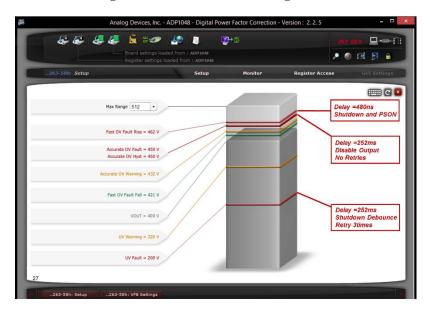

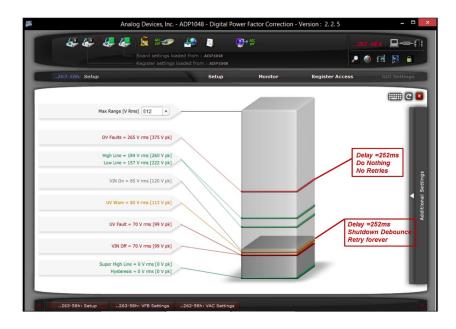

| Figure 4.15 Voltage Limit Setting in GUI                  | 63 |

| Figure 4.16 Power Setting in GUI                          | 64 |

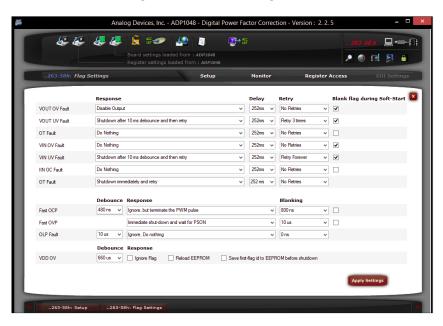

| Figure 4.17 Flag Setting in GUI                           | 64 |

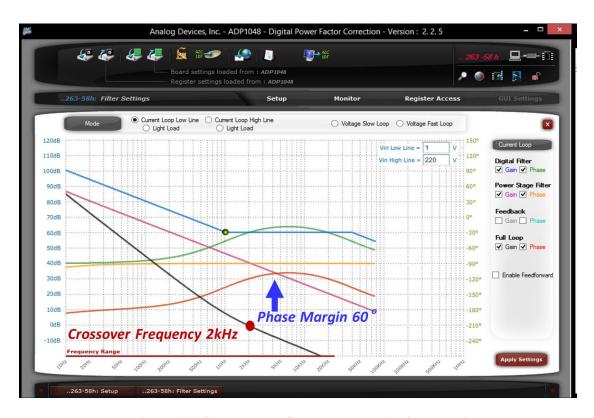

| Figure 4.18 Current Loop Compensator Design for Low Line  | 65 |

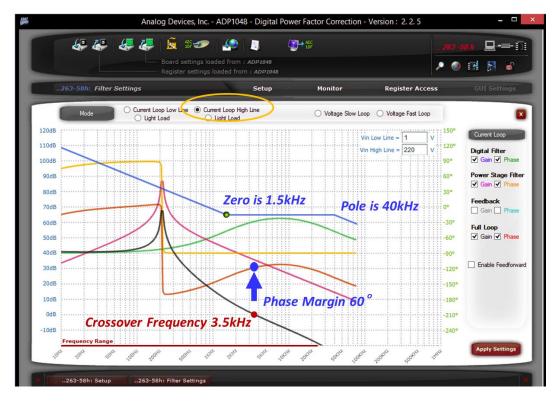

| Figure 4.19 Current Loop Compensator Design for High Line | 66 |

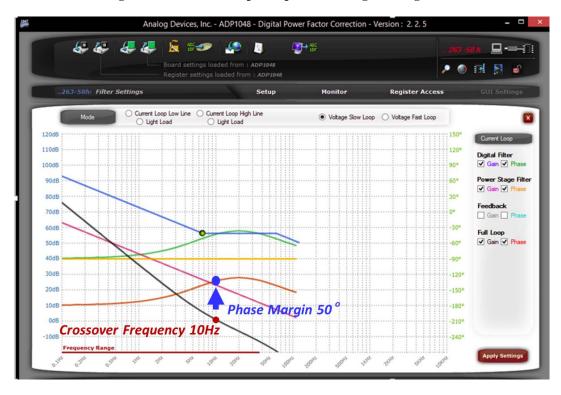

| Figure 4.20 Voltage Loop Compensator Design               | 66 |

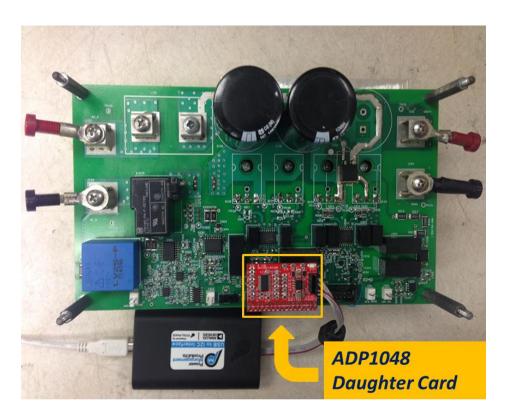

| Figure 5.1 Test-bed hardware prototype                    | 67 |

| Figure 5.2 Output Power Vs Efficiency Curve               | 69 |

| Figure 5.3 Output Power Vs Power Factor Curve             | 70 |

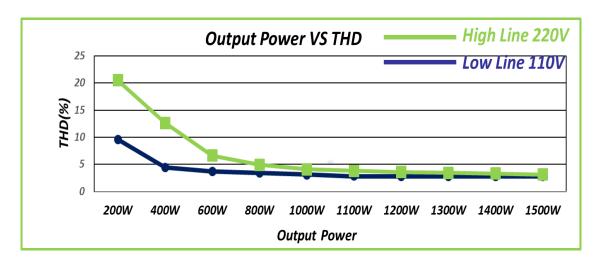

| Figure 5.4 THD under different power level                | 71 |

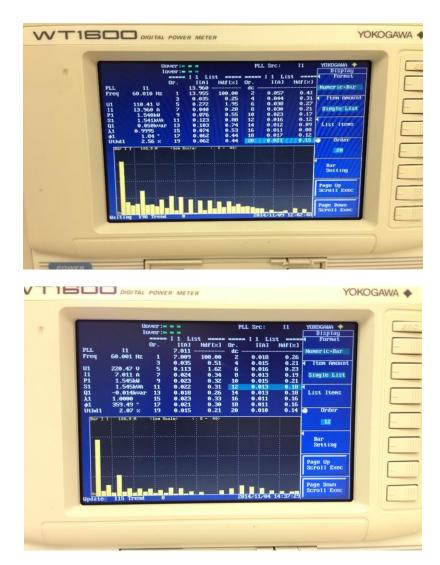

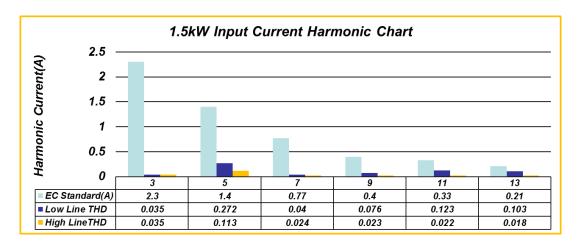

| Figure 5.5 THD shown in Yogakawa digital power meter      | 71 |

| Figure 5.6 1.5 kW Input Current Harmonic                  | 72 |

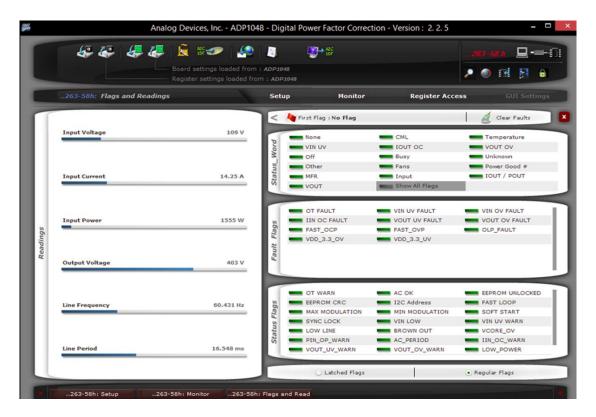

| Figure 5.7 1500W Testing ADP1048 Monitor at 110V input    | 72 |

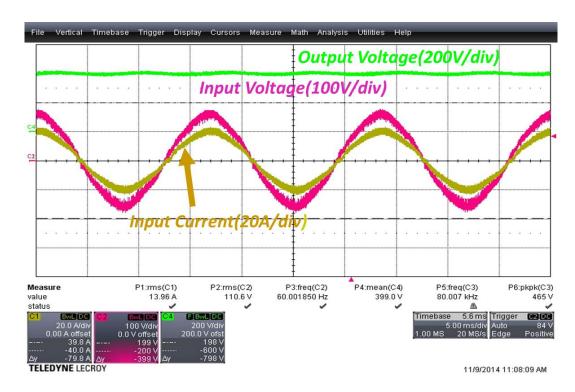

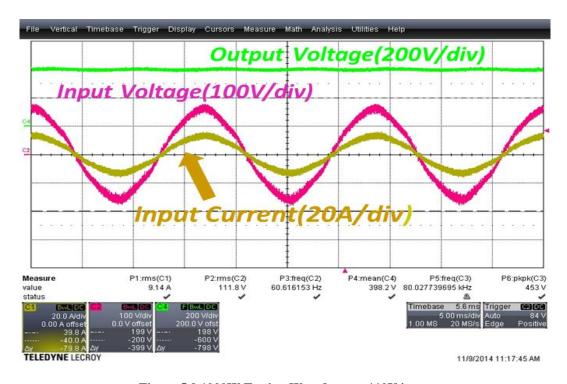

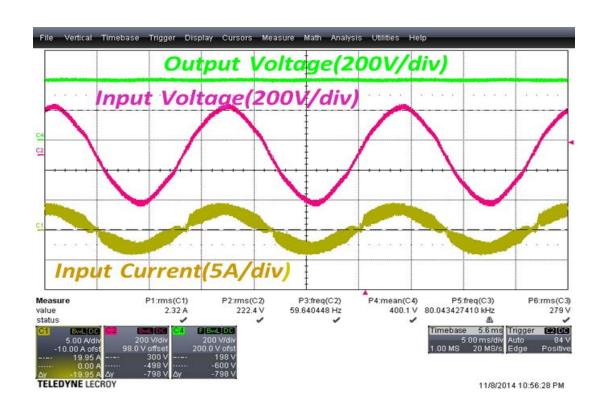

| Figure 5.8 1500W Testing Waveform at 110V input           | 73 |

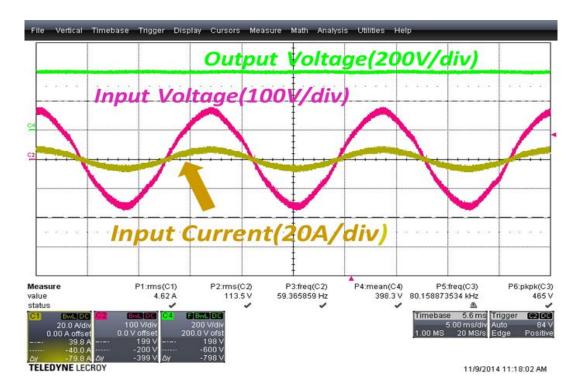

| Figure 5.9 1000W Testing Waveform at 110V input           | 73 |

| Figure 5.10 500W Testing Waveform at 110V input           | 74 |

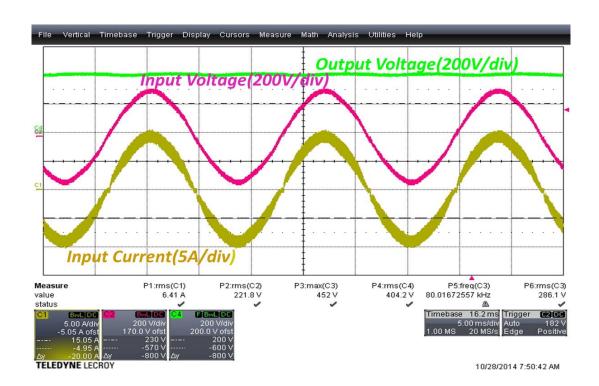

| Figure 5.11 1500W Testing Waveform at 220V input          | 75 |

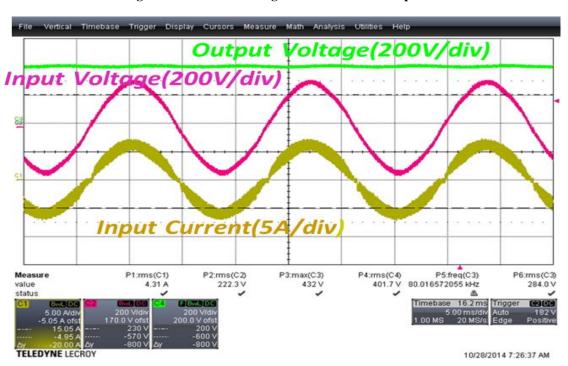

| Figure 5.12 1000W Testing Waveform at 220V input          | 75 |

| Figure 5.13 500W Testing Waveform at 220V input           | 76 |

## **List of Tables**

| Table 2.1 Comparisons of different bridgeless PFC topologies             | 21          |

|--------------------------------------------------------------------------|-------------|

| Table 4.1 ADP1048 pin function description Analog Devices, "ADP1047/ADP1 | 048 Digital |

| Power Factor Correction Controller with Accurate AC Power                | Metering'   |

| Datasheet. Used under fair use, 2014.                                    | 48          |

| Table 4.2 1.5KW Totem-Pole PFC Design Specification                      | 50          |

| Table 5.1 Experiment Major Components                                    | 68          |

| Table 5.2 Testing Conditions                                             | 68          |

| Table 5.3 Experiment Equipment                                           | 69          |

## Chapter 1:

## Introduction

#### 1.1 Background and Research Objective

Power factor correction technology is an essential part of power electronic products to meet environmental protection requirements. With all types of electrical appliances drawing power from the grid and more and more stringent power quality norms required by international organizations, power factor correction has become the focus of the development of the power electronics industry. If the input current to the grid has a displacement and large harmonic distortion, it will result in low power factor. The low power factor will cause the energy wasted. The distorted current will cause harmonic and pollute the grid. On one hand, the current flowing through the line impedance causes a voltage drop, which in turn makes the grid distortion occurred; on the other hand, it has an harmful impact on the other electrical equipment connecting to the grid, such as instrument measurement error, protection equipment malfunction, lines and distribution transformers overheating etc. The main design target of implementing power factor correction in the power supplies is to meet the international standards for power factor and harmonic content requirements. For example, some countries impose EN61000-3-2 standards [1-5].

With the development of PFC technology and semiconductor technology, how to improve the PFC efficiency has become a hot topic. For a conventional boost PFC, the loss in the rectifier bridge is significant especially in low voltage high current case [6-12].

In order to reduce the conduction losses in the rectifier bridge, some bridgeless PFC topologies are proposed. For high-power bridgeless PFC, how to improve the efficiency and reduce the size, cost, ease of design is the direction for the designers.

Compared with semi-bridgeless Boost PFC, totem-pole PFC has fewer components, more efficient advantages. However, due to the internal MOSFET body diode reverse recovery problems, the totem-pole PFC is not applicable in CCM high power applications [8][13-16]. In the past, the limited switching frequency of IGBT results in it is not realistic to use IGBT in totem-pole PFC. However in nowadays, with advanced semiconductor technologies, there have been IGBTs which can be switched more than 100 kHz, such as Infineon's ultra-fast IGBT [17-19]. With the fast IGBT appearance, it is possible to apply CCM totem-pole PFC in high power condition. Thus research of how to apply fast IGBT and SiC diode in totem-pole PFC also provides an alternation for high-power bridgeless PFC application.

In addition, how to choose the controller chip that is easy to implement and can shorten the product design cycle is also one of the important factors engineers take into consideration. As the first digital programmable PFC chip, ADP1048 meets the needs of PFC design [40]. ADP1048 can convert all signals to the digital domain and allow the adjustment of one PMBUS through the interface and the report all the parameters, including accurate measurement of the input voltage, current and power. Compared with DSP, ADP1048 is less expensive and easier to use. ADP1048 also provides an intuitive graphical user interface (GUI), which help designers optimize PFC systems without the need of programming and compiling the complex code in DSP. This is also helpful in avoiding the code verification time in industry. However, bridgeless PFC mode in

ADP1048 is designed for semi-bridgeless boost bridgeless PFC, some external circuits are required to apply it in totem-pole PFC topology. Based on the above discussion, it is very interesting and promising to apply ADP1048 in totem pole PFC design.

#### 1.2 Thesis Outline

The thesis focuses on designing a universal CCM high power totem pole PFC by implementing ADP1048 programmable digital PFC controller. Chapter 1 introduces the research background and motivation. Chapter 2 reviews different bridgeless boost PFC topologies and control methodologies. Chapter 3 discusses the method for applying the totem pole PFC in CCM high power condition and analyzes the operation modes and simulates it in PSIM. Chapter 4 describes the design process of the power stage component selection and ADP1048 control setting. Chapter 5 shows the experiment results, including efficiency and THD. Chapter 6 presents the summary of this work and outlooks the future work.

## Chapter 2:

## **Power Factor Correction**

#### 2.1 Power Factor Definition

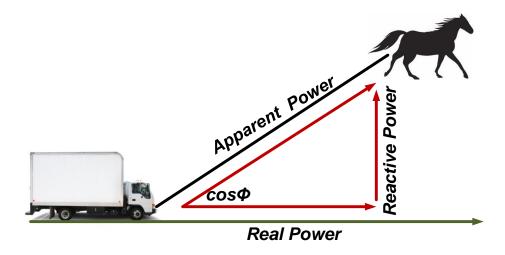

In electrical area, the power factor is defined as the utilization rate of the power from grid. It is the ratio of real power (P) to the apparent power (|S|).

$$PF = \frac{Real\ Power}{Apparent\ Power} \tag{2.1}$$

The power factor equation can be shown in Figure 2.1:

**Figure 2.1 Illustration of Power Factor**

If the voltage and current are ideal sinusoidal waveform, the PF=cosφ. But for the sinusoidal voltage and non-sinusoidal current, the PF should be equal to:

$$PF = \frac{V_{rms} \cdot I_{rms_{-1}}}{V_{rms} \cdot I_{rms}} \cdot \cos \phi = K_d \cdot \cos \phi$$

(2.2)

$K_d$  is the ratio of the fundamental of line current RMS value to the total line current RMS value.

$$K_{d} = \frac{I_{rms\_1}}{\sqrt{I_{rms\_1}^{2} + I_{rms\_2}^{2} + \dots + I_{rms\_n}^{2}}}$$

(2.3)

n is the nth order of harmonic current.

Define the total harmonic distortion (THD) as:

$$THD = \frac{I_h}{I_{rms\_1}} = \frac{\sqrt{I_{rms\_2}^2 + I_{rms\_3}^2 + \dots + I_{rms\_n}^2}}{I_{rms\_1}}$$

(2.4)

$I_h$  is the sum of total harmonic current RMS values.

Thus the distortion factor  $K_d$  equals to:

$$K_d = \frac{1}{\sqrt{1 + THD^2}} \tag{2.5}$$

The power factor can be represented as:

$$PF = \frac{\cos\phi}{\sqrt{1 + THD^2}}\tag{2.6}$$

From the power factor expression, the reasons leading to poor power factor are line current has large amount of high order harmonic and the different phase between input voltage and current. Therefore, to improve the power factor, the line current should keep the same phase with the sinusoidal line voltage and attenuate the line current harmonics [20].

#### 2.2 Active Power Factor Correction Control Methods

The active power factor correction (APFC) uses active switch device associating with passive component to shape the input current waveform and control the output voltage. Proper control method can make the power factor approximated to unity PF [20].

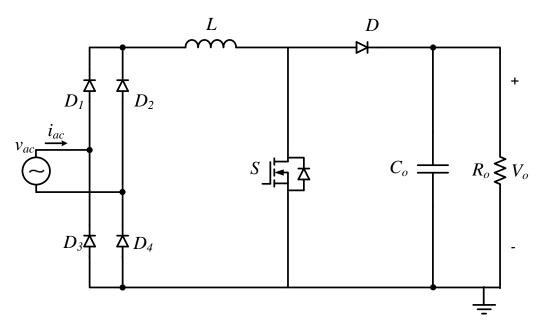

The APFC always adopts boost, buck, buck-boost, Cuk, sepic or flyback topologies based on the inductor and switch positions in the circuit [20]. Boost converter as shown in

Figure 2.2 is the most popular topology for PFC application. The boost inductor is in series with the input line terminal which is easy to implement average current control and achieve smaller current ripple. The switch in boost PFC is not floating, which is another benefit that makes the driver circuit easy to design. The boost PFC also has low current stress [2-24].

Figure 2.2 Traditional Boost PFC Topology

Based on the different PFC power level, the active PFC operation mode can be categorized as DCM (Discontinued Current Mode), CRM (Critical Conduction Mode) and CCM (Continuous Current Mode). The DCM PFC adopts voltage follower control method which has simple control circuit (only one voltage loop) and the inductor is working at DCM making the boost diode avoid the reverse recovery problem. But the DCM current is discontinuous, so the input needs bigger size filter and switch current RMS value is higher than CCM which increases the switch conduction loss. The DCM is only suitable for low power level condition. Because the inductor current is continuous, the CCM control is suitable for high power level. The CCM control method, including the Hysteresis Current Control, Peak Current Control, Average Current Control, is based on the multiplier approach control theory [25-30].

#### 2.2.1 Peak Current Control Method

The peak current control scheme is shown in Figure 2.3. The current reference is generated from the output of the voltage loop error amplifier multiplying the rectifier input voltage. The switch is turned on keeping steps with the constant clock trigger and is turned off when the sensing switch current touches the current reference.

Figure 2.3 Peak Current Mode Control Scheme

**Figure 2.4 Peak Current Mode Control Waveform**

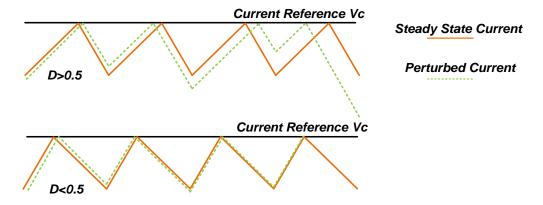

When the inductor current rising slope Sn is higher than falling slope which means the duty D<0.5, the current perturbation will decay after several switching cycles.

When the inductor current rising slope Sn is lower than falling slope which means the duty D>0.5, the current perturbation will grows and the system will lose stability [23]. The constant frequency peak current mode inherited instability issue is shown in Figure 2.5.

Figure 2.5 Peak Current Mode Control Current Perturbation

An external ramp is needed to add for keeping the system stable when the D>0.5. But adding external ramp increase the difficulty of design. The peak current control is simple for design but the disadvantages are the current loop gain is low at low frequency, current THD is higher than average current control and the sub-harmonic issue is serious even with the external ramp. The disadvantages of the peak current mode control limit the application in CCM control method.

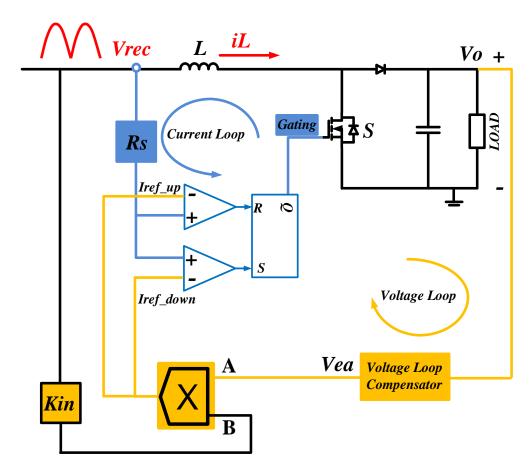

#### 2.2.2 Hysteresis Current Control Method

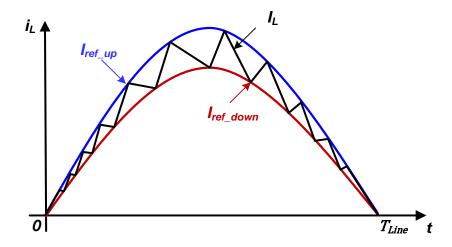

The hysteresis current control scheme is shown in Figure 2.6. There are two current references: upper limit threshold  $I_{ref\_up}$  and lower limit threshold  $I_{ref\_down}$ . When the current touches the lower threshold current reference, the switch is turned on and inductor current will increase. When the current touches the upper threshold current

reference, the switch is turned off and current will decrease. The current is limited in the hysteresis band and the power switch gating signal is depended on the two current references.

**Figure 2.6 Hysteresis Current Mode Control Scheme**

**Figure 2.7 Hysteresis Current Mode Control Waveform**

The hysteresis current method can control the hysteresis band range to decrease the inductor current ripple. But in this method, switching frequency is variable and the load impact the switching frequency great causing the filter circuit difficult to design.

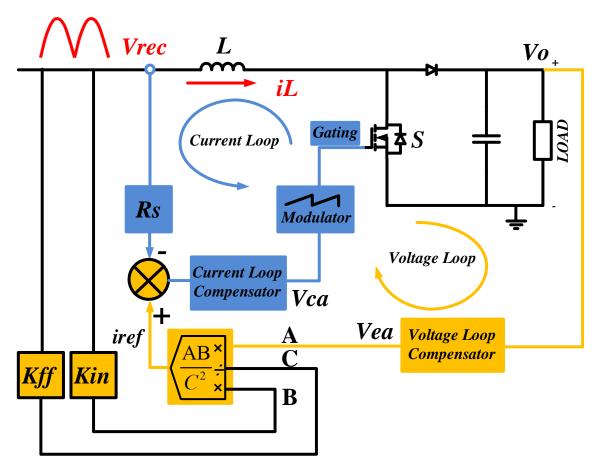

#### 2.2.3 Average Current Control Method

The average current control scheme is shown in Figure 2.8. The controller multiplies the sensed input voltage with the power reference generated from the output of voltage loop compensator, and divided by the square of input voltage RMS value to get the input current reference. The current error amplifier compensates the error between sensed current and current reference. The output of the current compensator drives the PWM modulator to generate the gating signals for helping line current to track the input voltage waveform and get the desired output voltage.

Figure 2.8 Average Current Mode Control Scheme

**Figure 2.9 Average Current Mode Control Scheme**

The average current control is most widely used method for boost PFC converter especially in high power level. It can achieve low THD, accuracy current tracking and low EMI.

#### 2.3 Bridgeless Boost PFC Topology Overview

The electronics devices such as laptops, cell phone, panel computer, workstations, and data severs increasingly challenge AC/DC power supplies for higher efficiency requirements. The environment organization and government regulations are forcing designers to look for any possible opportunity to minimize power losses [31-32]. Although the conventional boost PFC is the most popular topology among the AC/DC converter, the conduction loss from line bridge rectifier is significant and limits to enhance the efficiency of the whole circuit. To solve this problem, Bridgeless Boost PFC is proposed and attracts wide range attention. It is effective to reduce the number of devices on the current path to reduce considerable conduction loss and improve the total efficiency. Generally, the bridgeless PFC can cut down the number of devices and improve the efficiency and power density [7-12].

So far, many boost bridgeless topologies have been proposed. Researches on bridgeless topologies become to a hot spot in power electronic area. In this section, some simple and usually implemented structures are reviewed.

#### 2.3.1 Traditional Boost Bridgeless PFC

The configuration of traditional boost bridgeless PFC is shown in Figure 2.10. The current only flows through two semiconductor devices at every moment, whereas the number for traditional boost PFC shown in

Figure 2.2 is three. The power switch MOSFET instinct body diodes are used to replace two slow diodes and provide the return path. The topology is not only beneficial in reducing the number of semiconductor devices in the whole circuit and conduction loss, but also solves the heat dissipation of the input rectifier bridge problem.

Figure 2.10 Dual Boost Bridgeless PFC Topology

However, the implementation of traditional boost bridgeless PFC is limited by the high common-mode noise problem which caused by the high frequency switches  $S_I$  and  $S_2$ .

In the traditional boost PFC, the output ground is always connected to the input ac source through the input rectifier bridge whenever the positive or negative half-line cycle.

For the traditional boost bridgeless PFC, during the positive half-line cycle, the output ground is always connected to the ac source through the power switch  $S_2$  body diode, but during the negative half-line cycle, the output ground has high frequency pulsating and the amplitude is equal to output voltage. This high frequency pulsating voltage source charge and discharge the equivalent parasitic capacitance between the output ground and the ac line, causing a significantly increased common-mode noise. To solve the serious common mode noise, a larger EMI filter is needed. The inherent drawback of the traditional boost bridgeless topology limits the implementations for the PFC design.

#### 2.3.2 Semi-Bridgeless Boost PFC

To reduce the high common-mode noise, the semi-boost bridgeless PFC is modified by adding two slow diodes and second inductor to supply a LF path between the output ground and ac source. This derivative topology is presented in Figure 2.11.

Figure 2.11 Semi-Boost Bridgeless PFC

This topology consists of two DC/DC boost converter. During the positive half-line cycle, the output ground is connected to the ac source through the slow diode D3. During the negative half-line cycle, the output ground is connecting to the ac source through the slow diode  $D_4$ . The symmetric inductors also can be expected as a common-mode filter to reduce the common-mode. This topology can achieve the common-mode noise as the same level as the traditional boost PFC. However, the major drawback of this topology is low components utilized rate and high cost of the design product.

#### 2.3.3 Dual Boost Bridgeless PFC with Bidirectional Switch

Another modified topology based on the basic bridgeless PFC is shown in Figure 2.12. This topology can also survive from the common-mode noise problem by adding two diodes. During the positive half-line cycle, the output ground is connected to the ac source through the diode  $D_4$ . During the negative half-line cycle, the positive output bus is connected to the ac source through the diode  $D_1$ . So the output voltage is no longer in a floating status.

Figure 2.12 Dual Boost Bridgeless PFC with bidirectional switch

The major drawback of the topology is that the gate voltage for each switch is different and requires isolated gate drive transformer which makes the drive circuit design difficult. Besides when the switch is off, the current flows through two high frequency diodes which increase the conduction loss significantly.

#### 2.3.4 Pseudo Totem-Pole Bridgeless PFC Topology

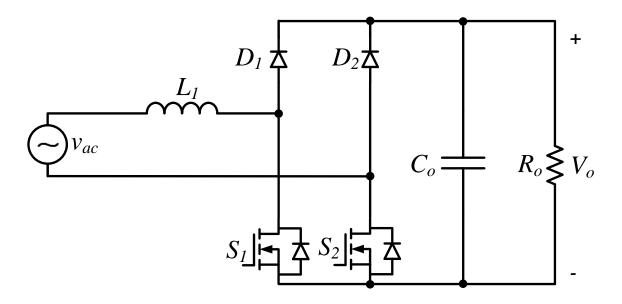

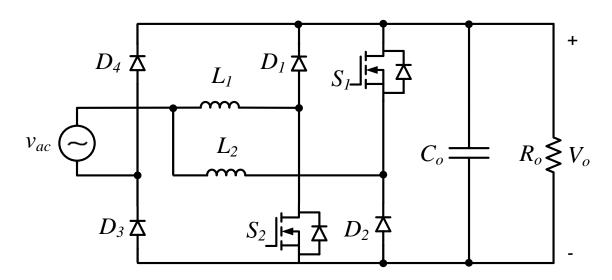

Figure 2.13 presents another variation topology of dual boost bridgeless PFC. Based on the location of two switches, this topology is named as pseudo totem-pole bridgeless PFC. This topology does not suffer from the common-mode noise problem as does the basic bridgeless boost PFC.

During the positive half-line cycle, the output ground is connected to the ac source through the slow diode  $D_3$ . During the negative half-line cycle, the output voltage bus connects to the ac source through the slow diode  $D_4$ .

Figure 2.13 Pseudo Totem-Pole Bridgeless PFC Topology

The two switches need to be driven with different PWM signals and isolated gate drivers. This topology practical implementation is also limited by the difficult control and driver circuit design.

#### 2.3.5 Totem-Pole Bridgeless Boost PFC Topology

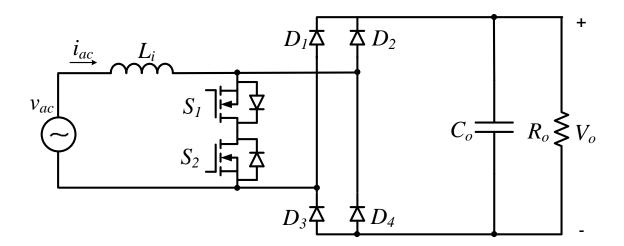

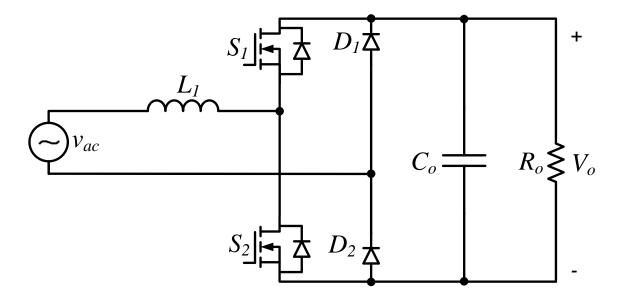

The topologies shown in above either have the common-mode noise problems or have to add the extra components to reduce the common mode noise. Compared with these topologies, the totem-pole Bridgeless PFC shown in Figure 2.14 seems attractive for implementation, because it has the advantage of the simple structure and lowest components cost same as the basic bridgeless PFC, but also does not create large common-mode noise.

Figure 2.14 Totem-Pole Bridgeless Boost PFC Topology

The totem-pole PFC successfully suppresses the common-mode noise by changing the semiconductors positions of the basic bridgeless boost PFC shown in Figure 2.10. During in the positive half-line cycle, the output ground is connected the ac source

through the  $D_2$ , and during the negative half-line cycle, the positive terminal of the output voltage is connected the ac source through the  $D_I$ .

Although the totem-pole PFC has more advantages than other topologies, it has not attracted widespread implementation in practical. Because the slow recovery body diode of the MOSFET make the totem-pole PFC only suitable for Discontinuous Current Mode(DCM) or Critical Mode operation. The body diodes of the switches in the totem-pole PFC play the same effect as the traditional boost PFC fast-recovery diode. For example, as shown in Figure 2.15, in CCM operation mode, during switch  $S_2$  off, the switch  $S_2$  body diode works as the fast diode and provide a current path for the input current. At the moment of the switch  $S_2$  is turning on, the current through the switch S1 include the input current and the  $S_1$  body diode's reverse recovery current. This phenomenon will cause the severely high losses and even make device damaged by the potential overshoot issue.

Figure 2.15 Reverse Recovery Issue in Totem-pole PFC

Therefore, the instinct issue makes the totem-pole PFC applications with mosfet switch limited with the DCM or Critical Mode operation. Some ZVS control methods are proposed to reduce the reverse recovery of the diode, but extra components need to be added to achieve the CCM operation mode. Besides the cost increase, the power range, complicated current sense and control are other drawbacks for these soft-switching methods.

IGBT parallels with a *SiC* diode can replace the MOSFET in the totem-pole, and the *SiC* diode does not have the reverse recovery issue. This method is workable in theoretically, but it is impractically by considering the conventional IGBT working frequency is usually around 30 kHz [33]. Under this frequency, the size of inductor is huge and the power density decreases. So the conventional IGBT used in totem-pole PFC is also impractical. In general, although the totem-pole PFC has the apparent advantages, the conventional switches characteristic cannot make the topology accepted in wide range.

#### 2.3.6 Bridgeless PFC topologies comparison

Table 2.1 shows the number of components, CM noises, and applicable operation mode comparison during these bridgeless PFC topologies.

Table 2.1 Comparisons of different bridgeless PFC topologies.

| Topology           | Traditional<br>Boost PFC | Traditional<br>BLPFC | Semi-Boost<br>BLPFC | Bidirectional<br>BLPFC | Pseudo<br>BLPFC   | Totem-pole<br>BLPFC |

|--------------------|--------------------------|----------------------|---------------------|------------------------|-------------------|---------------------|

| Switches           | 1                        | 2                    | 2                   | 2                      | 2                 | 2                   |

| Slow Diode         | 4                        | 0                    | 2                   | 0                      | 2                 | 2                   |

| Fast Diode         | 1                        | 2                    | 2                   | 4                      | 2                 | 0                   |

| Freewheeling diode | 0                        | 2                    | 2                   | 2                      | 2                 | 2                   |

| Input<br>Inductor  | 1                        | 1                    | 2                   | 1                      | 2                 | 1                   |

| Output Cap         | 1                        | 1                    | 1                   | 1                      | 1                 | 1                   |

| Total<br>Number    | 8                        | 8                    | 11                  | 10                     | 11                | 8                   |

| Driver<br>Circuit  | Easy                     | Easy                 | Easy                | Complex                | Complex           | Complex             |

| CM Noise           | Small                    | Large                | Small               | Small                  | Small             | Small               |

| Operation<br>Mode  | CCM<br>DCM<br>CRM        | CCM<br>DCM<br>CRM    | CCM<br>DCM<br>CRM   | CCM<br>DCM<br>CRM      | CCM<br>DCM<br>CRM | DCM<br>CRM          |

## Chapter 3:

## A Method for CCM Totem-Pole PFC

# 3.1 Ultra-Fast IGBT Implemented in CCM Totem-Pole PFC

#### 3.1.1 Ultra-Fast IGBT Introduction

The conventional IGBTs are usually adopted in low switching frequency and high current applications. As the requirement of higher switching frequency in power converter field, the application range of IGBT is limited. However, the IGBT technology achieves extraordinary progress recently. Such as Infineon, it launched the breakthrough technology called as TRENCHSTOP 5 and released the H5/F5 ultra-fast IGBT with switching frequency up to 100 kHz [33]. The TRENCHSTOP IGBT technology achieves the high switching speed while remaining the IGBT intrinsic features such as low conduction loss, high voltage rate, high current density, low cost [34-35]. The new generation ultra-fast IGBT has the high possibility of replacing the MOSFET in high frequency and high power switch power supply applications.

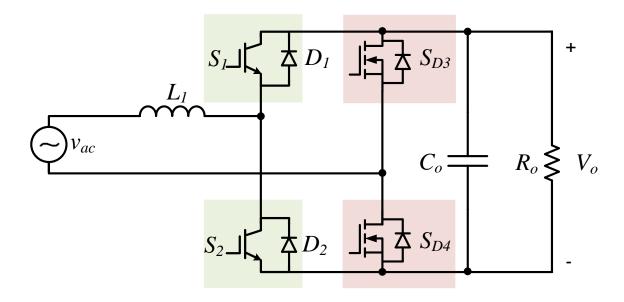

#### 3.1.2 Ultra-fast IGBT and SiC Diode in Totem-pole PFC

The totem-pole PFC with MOSFET is not workable in CCM operation because of the MOSFETs' instinct body diode reverse recovery. The combination of ultra-fast IGBTs and *SiC* diode replacing the MOSFET in the totem-pole PFC makes the topology possible to be used in CCM operation, because the ultra-fast IGBTs are capable of

switching above 100 kHz and the *SiC* diode can provide the current path when switch IGBT is off without the reverse recovery current. This method will be verified in experiments in later Chapter 5.

#### 3.2 Totem-Pole PFC Circuit Structure

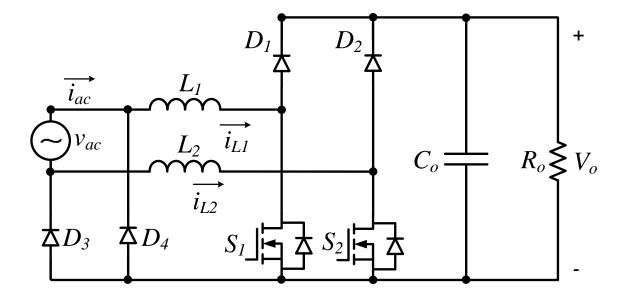

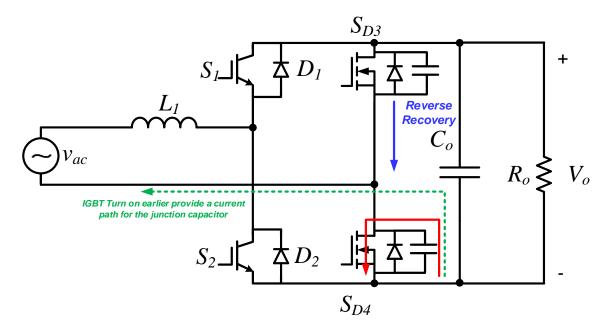

The totem-pole PFC based on the ultra-fast IGBT diagram is shown in Figure 3.1. The ultra-fast IGBTs offer the high efficiency in hard switching, low  $Q_g$ , low conduction loss and high switching frequency. The characteristics of the ultra-fast IGBTs and SiC diodes enable the high switching frequency PFC under CCM operation. The totem-pole PFC based on the ultra-fast IGBT diagrams are shown in Figure 3.1.

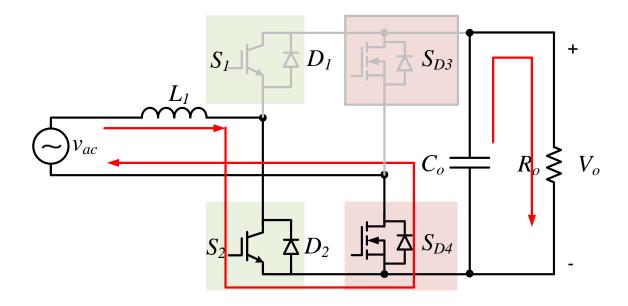

Figure 3.1 Totem-pole PFC with ultra-fast IGBT and Diode Line Rectification

Figure 3.2 Totem-pole PFC with ultra-fast IGBT and MOSFET Line Rectification

Figure 3.1 includes two slow diodes  $D_3$  and  $D_4$  which are used for line rectification. For further boosting the efficiency, the line rectification diode can be replaced by the low  $R_{dson}$  MOSFETs. Figure 3.2 diagram shows the totem-pole PFC with MOSFET line rectification. The new topology only replaces the line rectifiers  $D_3$  and  $D_4$  with MOSFETs  $S_{D3}$  and  $S_{D4}$  which are controlled by two additional PWM signals synchronizing with the half line cycle.

#### 3.3 Operation Mode Analysis

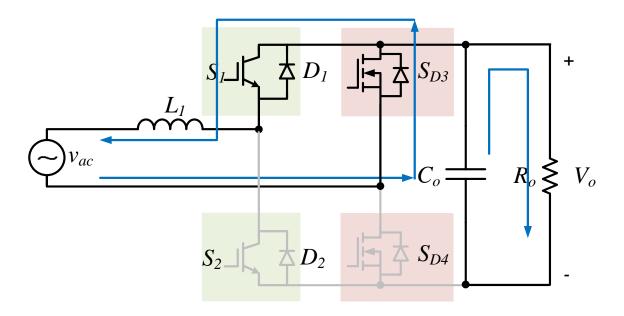

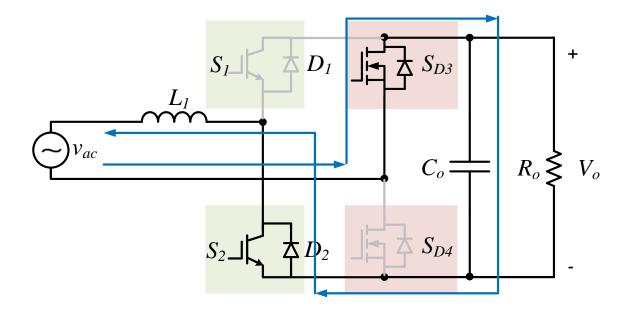

#### 3.3.1 Positive Half Line Cycle Operation

The positive half line cycle operation of the totem-pole PFC is shown in Figure 3.3 and Figure 3.4. There are only two semiconductors in the current path. When the switch  $S_2$  is on, the ac source charges the inductor  $L_1$  and the output capacitor supplies the energy for load. The MOFET  $S_{D4}$  is conducting current and connecting the ac source to the output ground.

Figure 3.3 Totem-pole PFC Positive line cycle when switch is ON

When the switch  $S_2$  is off, the inductor  $L_I$  discharges the energy to the output and the SiC  $D_I$  freewheels the inductor current. The Mosfet  $S_{D4}$  is conducting current and connecting the ac source to the output ground.

Figure 3.4 Totem-pole PFC Positive line cycle when switch is OFF

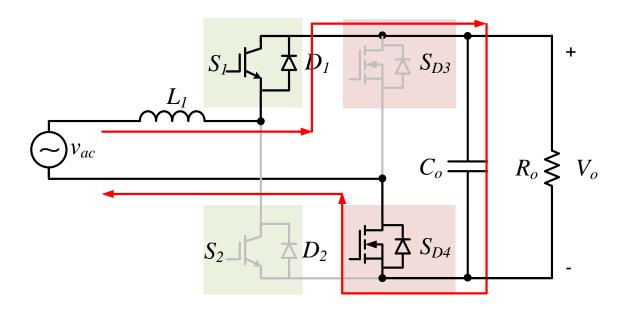

# 3.3.2 Negative Half Line Cycle Operation

The negative half line cycle operation of the totem-pole PFC is shown in Figure 3.5 and Figure 3.6. There are only two semiconductors in the current path. Similarly to the positive half line cycle, when the switch  $S_I$  is on, the ac source charges the inductor  $L_I$  and the output capacitor supplies the energy for load. The MOSFET  $S_{D3}$  is conducting current and connecting the ac source to the positive terminal output.

Figure 3.5 Totem-pole PFC Negative line cycle When Switch is On

When the switch  $S_I$  is off, the inductor  $L_I$  discharges the energy to the output and the SiC  $D_2$  freewheels the inductor current. The MOSFET  $S_{D3}$  is conducting current and connecting the ac source to the positive terminal output.

Figure 3.6 Totem-pole PFC Negative line cycle When Switch is off

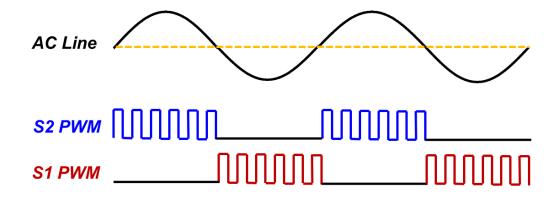

Based on the analysis for the Totem-Pole PFC operation modes, the switch  $S_1$  and  $S_2$  PWM signal should be working as:

Figure 3.7 Totem-pole PFC Switching Signal

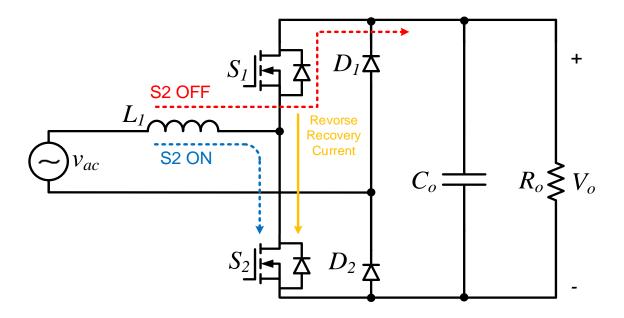

# 3.4 Zero Crossing Ring Issue with Mosfet Rectification

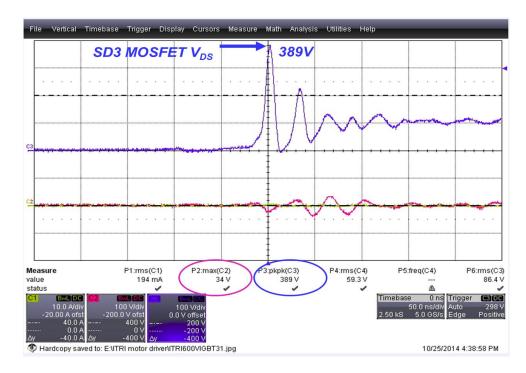

For further boosting the efficiency, two low  $R_{dson}$  MOSFETs can replace the bridge diodes. But there is a serious voltage ring across the MOSFET from drain to

source if the IGBT and MOSFET turn on at the same time. The testing waveform is shown in Figure 3.8 which presents the problem.

Figure 3.8 Drain to Source Voltage Ring Waveform

From the waveform, during the zero crossing stage, there is a huge voltage ring on the MOSFET SD3. The input voltage is only 34V but the  $V_{DS}$  on the MOSFET is almost 390V. This phenomenon can be explained in Figure 3.9.

Figure 3.9 Zero Crossing Voltage Ring Issue Analysis

When the line voltage crosses the zero from negative to positive, the  $S_{D4}$  takes up most of the output voltage. If the MOSFET  $S_{D4}$  with IGBT  $S_2$  turns on at same time, because the  $S_2$  current path has an inductor, the switch  $S_2$  cannot provide a very fast current path for the  $S_{D4}$  junction capacitor to outpour the energy. The current from the  $S_{D4}$  junction capacitor will go through the  $S_{D4}$  channel and the di/dt is very high. The voltage on the  $S_{D3}$  also increase very fast which makes a reverse recovery current also go through the  $S_{D4}$ . This is the reason the huge ring on the MOSFET appears while line rectification MOSFET and switch IGBT turn on at same time.

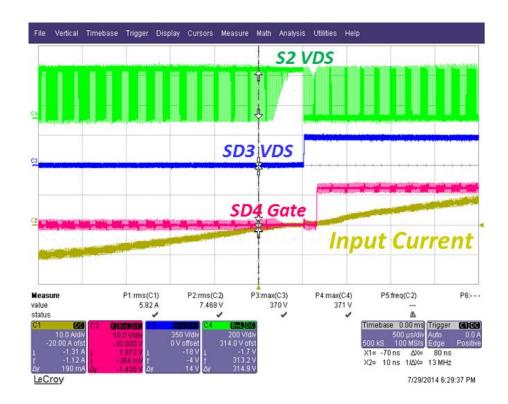

To solve this problem, the line rectification MOSFET should be turned on later than the switch IGBT for several switching cycles. If the IGBT  $S_2$  start switching before the SD4 turning on, the established inductor current will discharge the junction capacitor ensuring ZVS for SD4. The body diode reverse recovery of SD3 also can be avoided.

There is no large di/dt, so the voltage ring will be minimized. The waveform is shown in Figure 3.10.

Figure 3.10 Zero Crossing Voltage Ring Issue Analysis

Based on the zero crossing issue, when the totem pole PFC implements the MOSFET as the line rectification, the switch and line rectification MOSFET PWM signal should act as the Figure 3.11.

Figure 3.11 MOSFET Line Rectification PWM Signal

# 3.5 CCM Totem-Pole PFC Control Loop Design

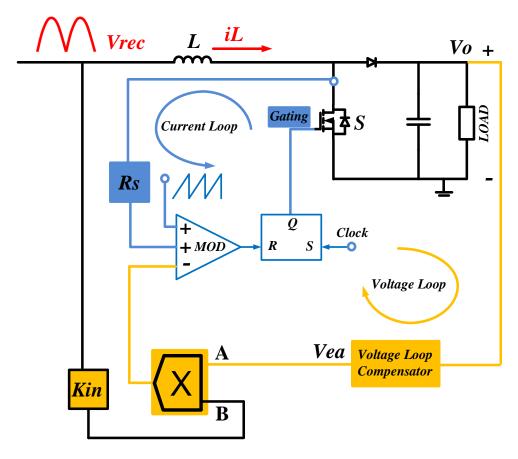

#### 3.5.1 PFC Control Method

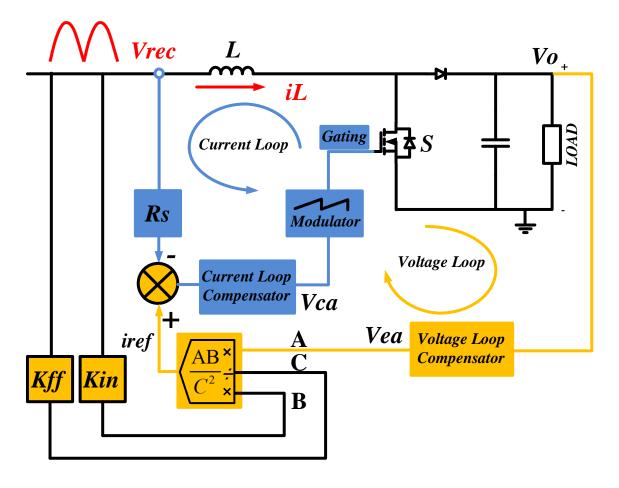

Since the totem-pole PFC is working as a boost converter during each half line cycle, the control method is same as the traditional CCM boost PFC. As mentioned in the Chapter 2, the high power CCM boost PFC always use the average current control method. The average current control diagram of boost PFC is shown in Figure 3.12.

The target of the PFC is to make the input current proportional to the input voltage and this causes the input impedance to be a resistive load to the input power as shown in (3.1):

$$\frac{V_{in}(t)}{I_{in}(t)} = R_{in} \tag{3.1}$$

Assume  $P_{in} = P_{out}$  thus:

$$\frac{V_{in\_RMS}^{2}}{R_{in}} = P_{in} = P_{out}$$

(3.2)

Substitute the  $R_{in}$ , and get the input current shown in (3.3):

$$I_{in}(t) = \frac{P_{out} \times V_{in}(t)}{V_{in-RMS}^{2}}$$

(3.3)

(3.3) shows that the controller multiplies the sensed input voltage signal  $\bf B$  with the power reference  $\bf A$  generated from the output of voltage loop compensator, and divided by the square of input voltage RMS value  $\bf C$  to get the input current reference. The theory is also presented in the Figure 3.12.

Figure 3.12 Boost PFC Average Current Control Diagram

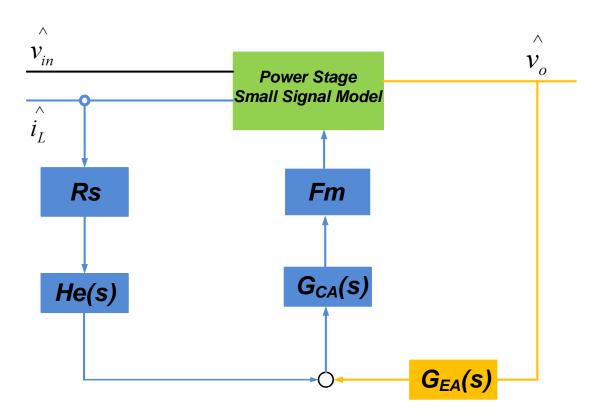

The average current PFC control system includes a fast current loop, a slow voltage loop and an input voltage feedforward loop. The fast current loop is used to force the input current to be proportional to the input voltage, which seeks the PF equal to 1. The voltage loop regulates the bus voltage at 380-400V. The input voltage feedforward loop is used to balance the input voltage variation for the voltage loop. The voltage loop and current loop have different bandwidth and need to design the loop independently. The current bandwidth should be well above the line frequency usually 2 kHz to 10 kHz to track the current well and decrease the distortion around the zero crossing [24]. Because the switching frequency is much higher than the line frequency, the input voltage can be regarded as a constant voltage during several switching cycles. The small signal model block for the PFC is shown in Figure 3.13.

Figure 3.13 PFC Small Signal Model Block Diagram

For frequency between line frequency and half of the switching frequency ( $f_L \le f \le f$ ), the sampling-effect  $H_e(s)$  is approximately equal to 1[30]. Therefore, the inner current loop is simplified as:

$$T_{current} = F_m \cdot R_s \cdot G_{CA}(s) \cdot G_{id}(s)$$

(3.4)

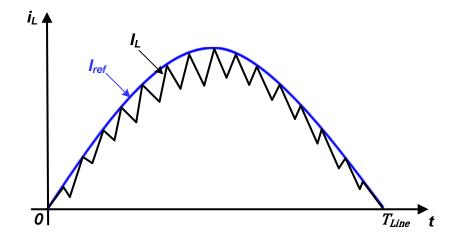

### 3.5.2 Inner Current Loop Design

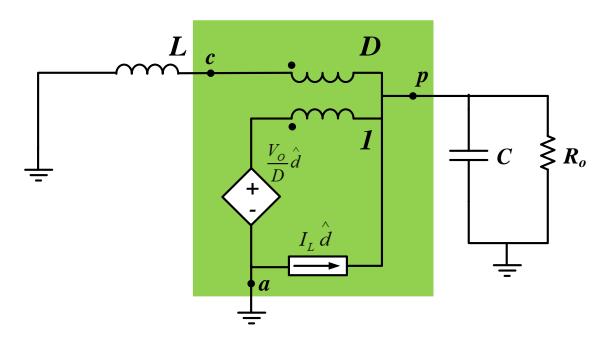

Because the switching frequency is much higher than the line frequency, the input voltage can be regarded as the constant voltage during several switching cycles. PWM three terminal model can be used to establish the power stage small signal model [23]. Ignoring the capacitor and inductor series resistance, the power stage control to current small signal model is shown in Figure 3.14.

Figure 3.14 power stage control to current small signal model

Based on the circuitry, the control to current transfer function can be derived as:

$$G_{id}(s) = \frac{\hat{i}}{\hat{d}} = \frac{2V_o}{R_L(1-D)^2} \cdot \frac{1 + \frac{R_L Cs}{2}}{1 + \frac{Ls}{R_L(1-D)^2} + \frac{LCs^2}{(1-D)^2}}$$

(3.5)

The capacitor impedance is 1/sC, so at high frequency range the impedance is approximately equal to zero. The control to current transfer function can be simplified as:

$$G_{id}(s) = \frac{\hat{i}}{\hat{d}} = \frac{V_o}{sL}$$

(3.6)

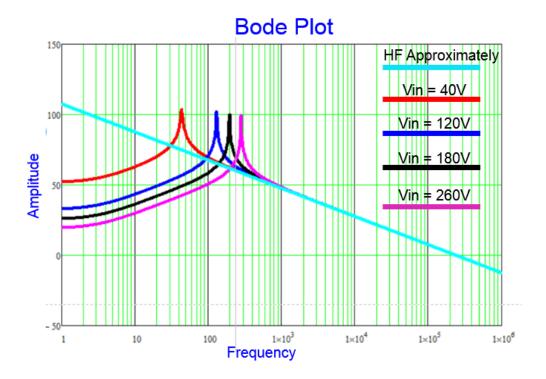

Based on the design parameter value for the 1.5 KW PFC, the bode plot of the control to current transfer function  $G_{id}(s)$  is shown in Figure 3.15.

Figure 3.15 Control to Current Gid(s) Bode Plot

From the bode plot, different input voltage and load decide the  $G_{id}(s)$  low frequency gain value. However the curves of different input voltage are overlapped at the high frequency range. The current loop bandwidth is always higher than 2 kHz so the simplified  $G_{id}(s)$  transfer function can be used for the current loop design.

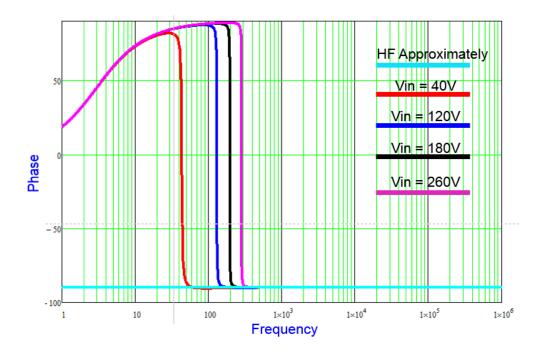

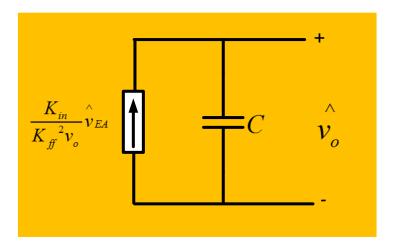

Use the integral and lead-lag compensation to achieve current loop stable. The integrator is used to boost the low frequency gain and the zero is required to make sure the sufficient phase margin. For this design, the current compensation includes one integrator, one zero at 1kHz and one pole at 40 kHz. The compensator loop bode plots are shown as Figure 3.16:

**Figure 3.16 Current Loop Compensation Bode Plot**

From the compensated current loop, the low frequency gain is enough to track the current reference. The crossover frequency is 2kHz and phase margin is  $60^{\circ}$  which make the current loop stable enough.

## 3.5.3 Outer Voltage Loop Design

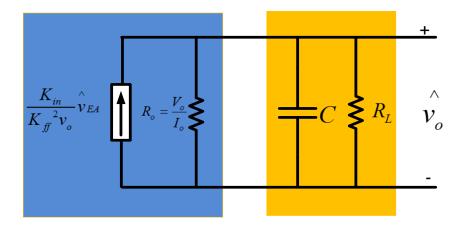

The voltage loop compensation is independent to the compensated current loop. Based on the small signal model diagram Figure 3.13, the voltage loop diagram can be simplified as Figure 3.17:

Figure 3.17 Simplified Voltage Loop Diagram

The voltage loop control to output small signal model can be derived by using the power balance equation. Based on the average current control diagram Figure 3.12, when the input current track the input voltage well, the current reference is:

$$i_{in} = \frac{K_{in}}{K_{ff}^2 v_{in}^2} v_{in} v_{EA}$$

(3.7)

Assuming efficiency is 100%, based on the power balance  $P_{in}=P_{out}$ , so the equation is:

$$i_{in}v_{in} = i_{out}v_{out} \tag{3.8}$$

Substitute (3.7) into (3.8), then get:

$$\frac{K_{in}v_{in}}{K_{ff}^{2}v_{in}^{2}}v_{in}v_{EA} = i_{o}v_{o}$$

(3.9)

Adding perturbation to the equation and assume input voltage without perturbation, the equation can be derived as:

$$\frac{K_{in}v_{in}}{K_{ff}^{2}v_{in}^{2}}v_{in}(v_{EA} + v_{EA}) = (i_{o} + i_{o})(v_{o} + v_{o})$$

(3.10)

Neglect the nonlinear term, then (3.10) can be derived to:

$$\hat{i}_{o} = \frac{K_{in}}{K_{ff}^{2} v_{out}} \hat{v}_{EA} - \frac{i_{o}}{v_{o}} \hat{v}_{o}$$

(3.11)

Based on the equation, a small signal model diagram is shown below:

Figure 3.18 Low Frequency Voltage Loop Small Signal Model

Assume the load power is constant, we can get the:

$$dP_o = dV_o I_o + dI_o V_o = 0 (3.12)$$

From the Eq. 3.12, we can get:

$$R_{o} = \frac{dV_{o}}{dI_{o}} = -\frac{V_{o}}{I_{o}} = -R_{L}$$

(3.13)

So the small signal model diagram for the constant power is shown as Figure 3.19:

Figure 3.19 Low Frequency Voltage Loop Small Signal Model for Constant Power

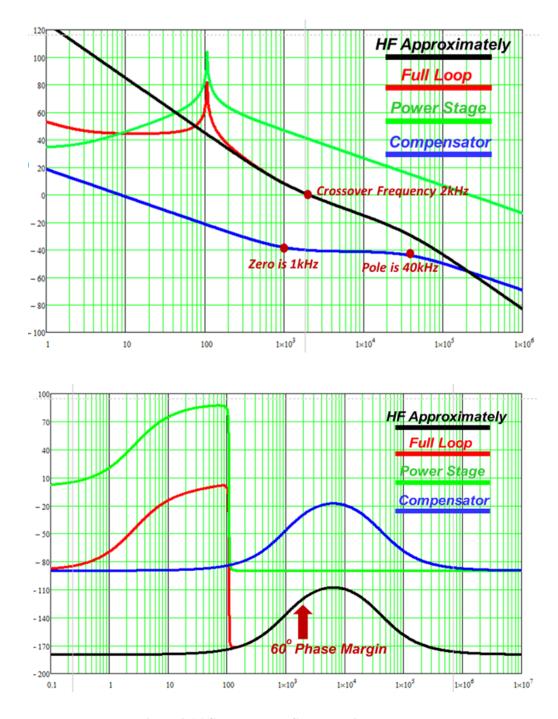

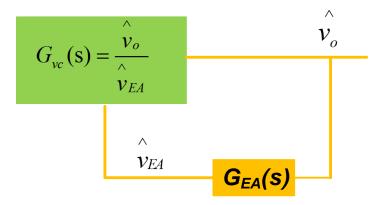

Based on the constant power condition, the control to output voltage loop transfer function is shown as:

$$G_{vc}(s) = \frac{\hat{v}_o}{\hat{v}_{FA}} = \frac{K_{in}}{K_{ff}^2 V_o C s}$$

(3.14)

The output voltage have inherited second harmonic ripple and this will import the second harmonic component into the voltage loop. The current reference will be affected and make the input current distortion. Therefore, the voltage bandwidth should be well below the 120 Hz to alleviate the second harmonic component at the output of the voltage compensator. For the design requirement, the bandwidth of the voltage loop usually should be chosen at 10 -20 Hz and phase margin is 50°. Based on the 1.5 kW PFC with ADP1048 design parameter, the transfer function Bode plot is shown in Figure 3.20:

**Figure 3.20 Voltage Loop Compensation Bode Plot**

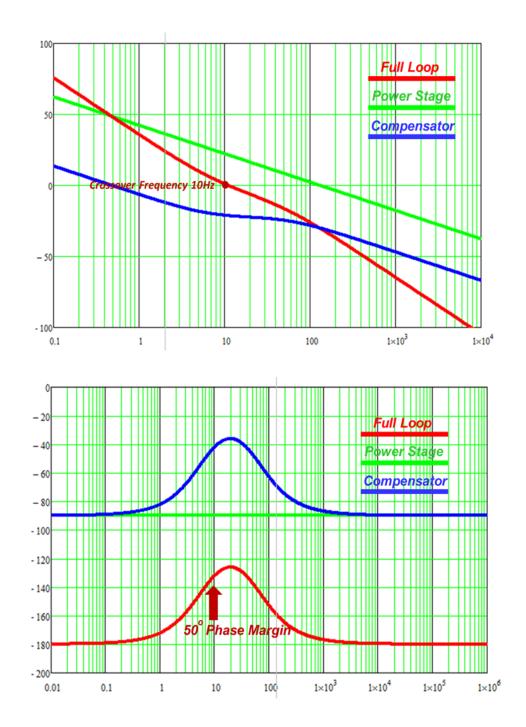

# 3.5.4 Simulation Results

The simulation is designed for the totem-pole PFC topology. The simulation power stage parameters values are all depended on the hardware design in the Chapter 4.

The control loop compensator is designed the same as the previous sections. The simulation adopts the same compensator at different power level. The simulation circuit is shown as Figure 3.21

Figure 3.21 Totem-pole PFC Simulation Circuit

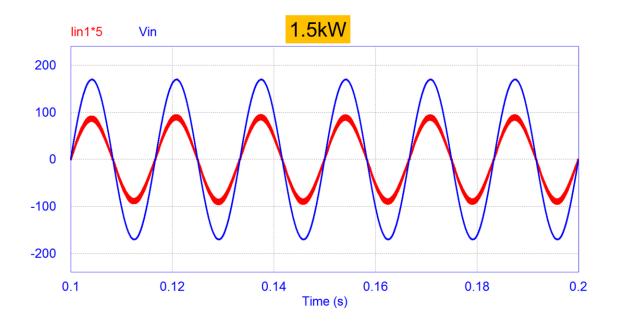

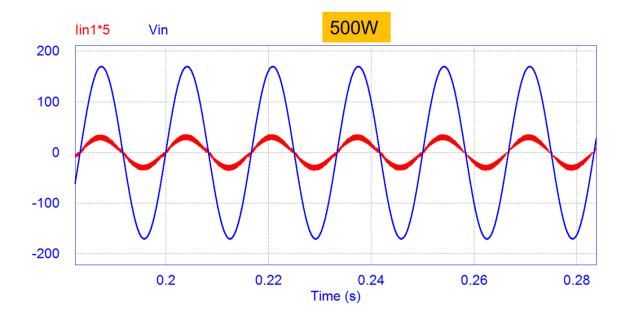

Figure 3.22 shows the simulation results with different power level:

Figure 3.22 Totem-pole PFC Simulation Results with Different Levels

From the waveforms, the input current tracks the line voltage well at different power level. The results present the control loop design is qualified for the power stage parameters.

# Chapter 4:

# Implement ADP1048 Controller for CCM Totem-Pole PFC Design

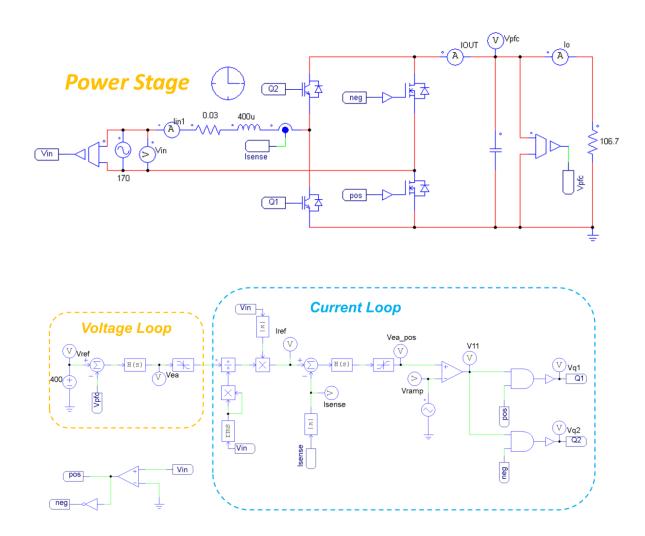

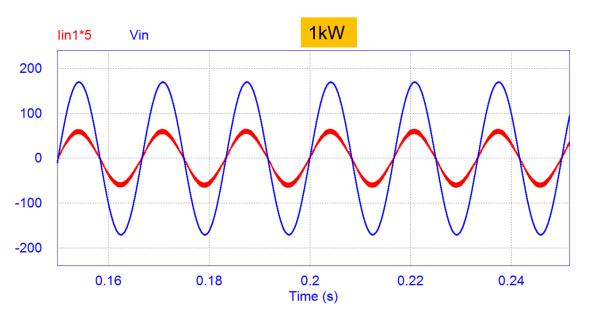

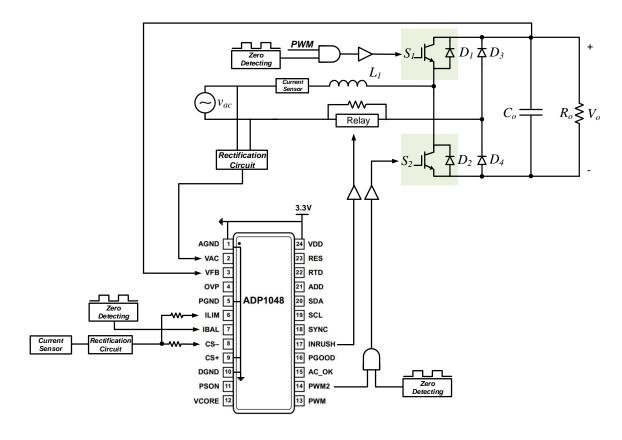

This Chapter introduces the design of a totem-pole PFC with ADP1048 controller. The general features and pins functions of ADP1048 are presented. After that is the design of the power stage components, control method design process and the related circuits to finally accomplish the proposed 1.5 kW totem-pole PFC design.

The simplified design circuit is shown in Figure 4.1.

Figure 4.1 Control Diagram with ADP1048 in Totem-Pole PFC Circuit

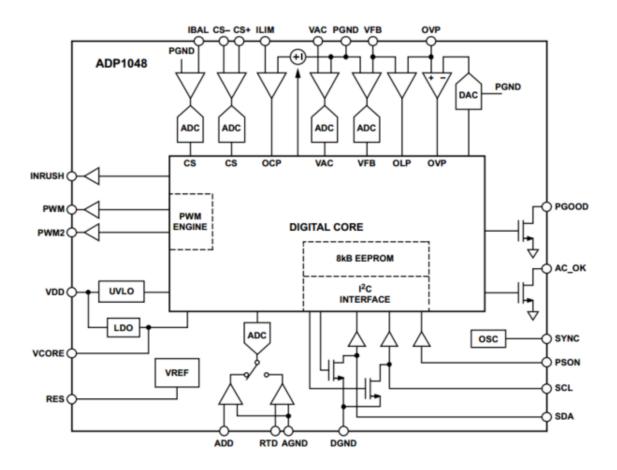

### 4.1 ADP1048 Introduction

ADP1048 is a flexible digital PFC controller which has more advantages than the DSP and analog controller. There is no any complex programming required and all the parameters can be written or adjusted through an easy-to-use GUI. It has enough functions to serve as a PFC controller and its cost is cheaper than the DSP. Comparing to the analog PFC controller, the advantages such as easier design process and more flexible functions attract the engineers.

The ADP1048 controller has interleaved and bridgeless PFC operation mode. The digital PFC function is based on the boost PFC with average current control method. The sensing signals are converted into the digital domain to provide maximum flexibility. The design parameter setting and programmed values can be stored into the internal EEPROM allowing standalone control without a microcontroller. ADP1048 can provide accurate input voltage, current and power RMS value. The inrush current signal for soft start can reduce components amounts without complicated design optimization. This controller also has enhanced dynamic response, smart frequency for efficiency optimization, multiple programmable fault detections and protections, digital EMI reduction, external frequency synchronization advanced features [37].

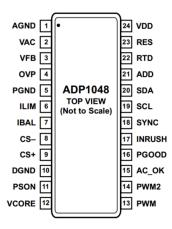

The ADP1048 pin configurations are shown in Figure 4.2:

Figure 4.2 ADP1048 Pins Configuration, Analog Devices, "ADP1047/ADP1048 Digital Power Factor Correction Controller with Accurate AC Power Metering" Datasheet. Used under fair use, 2014.

The Pin function descriptions are shown as Table 4.1

Table 4.1 ADP1048 pin function description Analog Devices, "ADP1047/ADP1048 Digital Power Factor Correction Controller with Accurate AC Power Metering" Datasheet. Used under fair use, 2014.

| Pin1(AGND)Analog GroundPin2(VAC)Input Line Voltage SensePin3(VPB)Feedback Voltage SensePin4(OVP)Overvoltage ProtectionPin5(PGND)Power GroundPin6(ILIM)Fast Current LimitingPin7(IBAL)Detect ac Line Phase and Zero CrossingsPin8(CS-)Differential Current Sense Negative InputPin9(CS+)Differential Current Sense Positive InputPin10(DGND)Digital GroundPin11(PSON)Power Supply Enable SignalPin12(VCORE)Output of 2.5V RegulatorPin13(PWM)PWM Output for PFC RegulationPin14(PWM2)Interleaved/Bridgeless PWM OutputPin15(AC_OK)Open-Drain OutputPin16(PGOOD)Open-Drain OutputPin17(INRUSH)Inrush Current Control Signal to an Eternal Inrush DriverPin19(SCL)12C Serial Clock InputPin20(SDA)12C Serial Data Input and OutputPin21(ADD)Address Select InputPin22(RTD)Thermistor InputPin23(RES)Internal Voltage ReferencePin24(VDD)Positive Supply Input                           |               |                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------|

| Pin3(VPB) Feedback Voltage Sense Pin4(OVP) Overvoltage Protection Pin5(PGND) Power Ground Pin6(ILIM) Fast Current Limiting Pin7(IBAL) Detect ac Line Phase and Zero Crossings Pin8(CS-) Differential Current Sense Negative Input Pin9(CS+) Differential Current Sense Positive Input Pin10(DGND) Digital Ground Pin11(PSON) Power Supply Enable Signal Pin12(VCORE) Output of 2.5V Regulator Pin13(PWM) PWM Output for PFC Regulation Pin14(PWM2) Interleaved/Bridgeless PWM Output Pin15(AC_OK) Open-Drain Output Pin16(PGOOD) Open-Drain Output Pin17(INRUSH) Inrush Current Control Signal to an Eternal Inrush Driver Pin18(SYNC) Parallel PFC Controller to synchronize to reduce interference Pin19(SCL) I2C Serial Clock Input Pin20(SDA) I2C Serial Data Input and Output Pin21(ADD) Address Select Input Pin22(RTD) Thermistor Input Pin23(RES) Internal Voltage Reference | Pin1(AGND)    | Analog Ground                                                 |

| Pin4(OVP) Overvoltage Protection  Pin5(PGND) Power Ground  Pin6(ILIM) Fast Current Limiting  Pin7(IBAL) Detect ac Line Phase and Zero Crossings  Pin8(CS-) Differential Current Sense Negative Input  Pin9(CS+) Differential Current Sense Positive Input  Pin10(DGND) Digital Ground  Pin11(PSON) Power Supply Enable Signal  Pin12(VCORE) Output of 2.5V Regulator  Pin13(PWM) PWM Output for PFC Regulation  Pin14(PWM2) Interleaved/Bridgeless PWM Output  Pin15(AC_OK) Open-Drain Output  Pin16(PGOOD) Open-Drain Output  Pin17(INRUSH) Inrush Current Control Signal to an Eternal Inrush Driver  Pin18(SYNC) Parallel PFC Controller to synchronize to reduce interference  Pin19(SCL) I2C Serial Clock Input  Pin20(SDA) I2C Serial Data Input and Output  Pin21(ADD) Address Select Input  Pin22(RTD) Thermistor Input  Pin23(RES) Internal Voltage Reference               | Pin2(VAC)     | Input Line Voltage Sense                                      |

| Pin5(PGND) Power Ground Pin6(ILIM) Fast Current Limiting Pin7(IBAL) Detect ac Line Phase and Zero Crossings Pin8(CS-) Differential Current Sense Negative Input Pin9(CS+) Differential Current Sense Positive Input Pin10(DGND) Digital Ground Pin11(PSON) Power Supply Enable Signal Pin12(VCORE) Output of 2.5V Regulator Pin13(PWM) PWM Output for PFC Regulation Pin14(PWM2) Interleaved/Bridgeless PWM Output Pin15(AC_OK) Open-Drain Output Pin16(PGOOD) Open-Drain Output Pin17(INRUSH) Inrush Current Control Signal to an Eternal Inrush Driver Pin18(SYNC) Parallel PFC Controller to synchronize to reduce interference Pin19(SCL) I2C Serial Clock Input Pin20(SDA) I2C Serial Data Input and Output Pin21(ADD) Address Select Input Pin22(RTD) Thermistor Input Pin23(RES) Internal Voltage Reference                                                                   | Pin3(VPB)     | Feedback Voltage Sense                                        |

| Pin6(ILIM) Fast Current Limiting Pin7(IBAL) Detect ac Line Phase and Zero Crossings Pin8(CS-) Differential Current Sense Negative Input Pin9(CS+) Differential Current Sense Positive Input Pin10(DGND) Digital Ground Pin11(PSON) Power Supply Enable Signal Pin12(VCORE) Output of 2.5V Regulator Pin13(PWM) PWM Output for PFC Regulation Pin14(PWM2) Interleaved/Bridgeless PWM Output Pin15(AC_OK) Open-Drain Output Pin16(PGOOD) Open-Drain Output Pin17(INRUSH) Inrush Current Control Signal to an Eternal Inrush Driver Pin18(SYNC) Parallel PFC Controller to synchronize to reduce interference Pin19(SCL) I2C Serial Clock Input Pin20(SDA) I2C Serial Data Input and Output Pin21(ADD) Address Select Input Pin22(RTD) Thermistor Input Pin23(RES) Internal Voltage Reference                                                                                           | Pin4(OVP)     | Overvoltage Protection                                        |

| Pin7(IBAL) Detect ac Line Phase and Zero Crossings  Pin8(CS-) Differential Current Sense Negative Input  Pin9(CS+) Differential Current Sense Positive Input  Pin10(DGND) Digital Ground  Pin11(PSON) Power Supply Enable Signal  Pin12(VCORE) Output of 2.5V Regulator  Pin13(PWM) PWM Output for PFC Regulation  Pin14(PWM2) Interleaved/Bridgeless PWM Output  Pin15(AC_OK) Open-Drain Output  Pin16(PGOOD) Open-Drain Output  Pin17(INRUSH) Inrush Current Control Signal to an Eternal Inrush Driver  Pin18(SYNC) Parallel PFC Controller to synchronize to reduce interference  Pin19(SCL) I2C Serial Clock Input  Pin20(SDA) I2C Serial Data Input and Output  Pin21(ADD) Address Select Input  Pin22(RTD) Thermistor Input  Pin23(RES) Internal Voltage Reference                                                                                                            | Pin5(PGND)    | Power Ground                                                  |

| Pin8(CS-) Differential Current Sense Negative Input Pin9(CS+) Differential Current Sense Positive Input Pin10(DGND) Digital Ground Pin11(PSON) Power Supply Enable Signal Pin12(VCORE) Output of 2.5V Regulator Pin13(PWM) PWM Output for PFC Regulation Pin14(PWM2) Interleaved/Bridgeless PWM Output Pin15(AC_OK) Open-Drain Output Pin16(PGOOD) Open-Drain Output Pin17(INRUSH) Inrush Current Control Signal to an Eternal Inrush Driver Pin18(SYNC) Parallel PFC Controller to synchronize to reduce interference Pin19(SCL) I2C Serial Clock Input Pin20(SDA) I2C Serial Data Input and Output Pin21(ADD) Address Select Input Pin22(RTD) Thermistor Input Pin23(RES) Internal Voltage Reference                                                                                                                                                                               | Pin6(ILIM)    | Fast Current Limiting                                         |

| Pin9(CS+) Differential Current Sense Positive Input Pin10(DGND) Digital Ground Pin11(PSON) Power Supply Enable Signal Pin12(VCORE) Output of 2.5V Regulator Pin13(PWM) PWM Output for PFC Regulation Pin14(PWM2) Interleaved/Bridgeless PWM Output Pin15(AC_OK) Open-Drain Output Pin16(PGOOD) Open-Drain Output Pin17(INRUSH) Inrush Current Control Signal to an Eternal Inrush Driver Pin18(SYNC) Parallel PFC Controller to synchronize to reduce interference Pin19(SCL) I2C Serial Clock Input Pin20(SDA) I2C Serial Data Input and Output Pin21(ADD) Address Select Input Pin22(RTD) Thermistor Input Pin23(RES) Internal Voltage Reference                                                                                                                                                                                                                                   | Pin7(IBAL)    | Detect ac Line Phase and Zero Crossings                       |

| Pin10(DGND) Digital Ground Pin11(PSON) Power Supply Enable Signal Pin12(VCORE) Output of 2.5V Regulator Pin13(PWM) PWM Output for PFC Regulation Pin14(PWM2) Interleaved/Bridgeless PWM Output Pin15(AC_OK) Open-Drain Output Pin16(PGOOD) Open-Drain Output Pin17(INRUSH) Inrush Current Control Signal to an Eternal Inrush Driver Pin18(SYNC) Parallel PFC Controller to synchronize to reduce interference Pin19(SCL) I2C Serial Clock Input Pin20(SDA) I2C Serial Data Input and Output Pin21(ADD) Address Select Input Pin22(RTD) Thermistor Input Pin23(RES) Internal Voltage Reference                                                                                                                                                                                                                                                                                       | Pin8(CS-)     | Differential Current Sense Negative Input                     |

| Pin11(PSON) Power Supply Enable Signal  Pin12(VCORE) Output of 2.5V Regulator  Pin13(PWM) PWM Output for PFC Regulation  Pin14(PWM2) Interleaved/Bridgeless PWM Output  Pin15(AC_OK) Open-Drain Output  Pin16(PGOOD) Open-Drain Output  Pin17(INRUSH) Inrush Current Control Signal to an Eternal Inrush Driver  Pin18(SYNC) Parallel PFC Controller to synchronize to reduce interference  Pin19(SCL) I2C Serial Clock Input  Pin20(SDA) I2C Serial Data Input and Output  Pin21(ADD) Address Select Input  Pin22(RTD) Thermistor Input  Pin23(RES) Internal Voltage Reference                                                                                                                                                                                                                                                                                                      | Pin9(CS+)     | Differential Current Sense Positive Input                     |

| Pin12(VCORE) Output of 2.5V Regulator  Pin13(PWM) PWM Output for PFC Regulation  Pin14(PWM2) Interleaved/Bridgeless PWM Output  Pin15(AC_OK) Open-Drain Output  Pin16(PGOOD) Open-Drain Output  Pin17(INRUSH) Inrush Current Control Signal to an Eternal Inrush Driver  Pin18(SYNC) Parallel PFC Controller to synchronize to reduce interference  Pin19(SCL) I2C Serial Clock Input  Pin20(SDA) I2C Serial Data Input and Output  Pin21(ADD) Address Select Input  Pin22(RTD) Thermistor Input  Pin23(RES) Internal Voltage Reference                                                                                                                                                                                                                                                                                                                                              | Pin10(DGND)   | Digital Ground                                                |

| Pin13(PWM) PWM Output for PFC Regulation  Pin14(PWM2) Interleaved/Bridgeless PWM Output  Pin15(AC_OK) Open-Drain Output  Pin16(PGOOD) Open-Drain Output  Pin17(INRUSH) Inrush Current Control Signal to an Eternal Inrush Driver  Pin18(SYNC) Parallel PFC Controller to synchronize to reduce interference  Pin19(SCL) I2C Serial Clock Input  Pin20(SDA) I2C Serial Data Input and Output  Pin21(ADD) Address Select Input  Pin22(RTD) Thermistor Input  Pin23(RES) Internal Voltage Reference                                                                                                                                                                                                                                                                                                                                                                                     | Pin11(PSON)   | Power Supply Enable Signal                                    |

| Pin14(PWM2) Interleaved/Bridgeless PWM Output  Pin15(AC_OK) Open-Drain Output  Pin16(PGOOD) Open-Drain Output  Pin17(INRUSH) Inrush Current Control Signal to an Eternal Inrush Driver  Pin18(SYNC) Parallel PFC Controller to synchronize to reduce interference  Pin19(SCL) I2C Serial Clock Input  Pin20(SDA) I2C Serial Data Input and Output  Pin21(ADD) Address Select Input  Pin22(RTD) Thermistor Input  Pin23(RES) Internal Voltage Reference                                                                                                                                                                                                                                                                                                                                                                                                                               | Pin12(VCORE)  | Output of 2.5V Regulator                                      |

| Pin15(AC_OK)Open-Drain OutputPin16(PGOOD)Open-Drain OutputPin17(INRUSH)Inrush Current Control Signal to an Eternal Inrush DriverPin18(SYNC)Parallel PFC Controller to synchronize to reduce interferencePin19(SCL)I2C Serial Clock InputPin20(SDA)I2C Serial Data Input and OutputPin21(ADD)Address Select InputPin22(RTD)Thermistor InputPin23(RES)Internal Voltage Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Pin13(PWM)    | PWM Output for PFC Regulation                                 |

| Pin16(PGOOD) Open-Drain Output  Pin17(INRUSH) Inrush Current Control Signal to an Eternal Inrush Driver  Pin18(SYNC) Parallel PFC Controller to synchronize to reduce interference  Pin19(SCL) I2C Serial Clock Input  Pin20(SDA) I2C Serial Data Input and Output  Pin21(ADD) Address Select Input  Pin22(RTD) Thermistor Input  Pin23(RES) Internal Voltage Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Pin14(PWM2)   | Interleaved/Bridgeless PWM Output                             |

| Pin17(INRUSH) Inrush Current Control Signal to an Eternal Inrush Driver  Pin18(SYNC) Parallel PFC Controller to synchronize to reduce interference  Pin19(SCL) I2C Serial Clock Input  Pin20(SDA) I2C Serial Data Input and Output  Pin21(ADD) Address Select Input  Pin22(RTD) Thermistor Input  Pin23(RES) Internal Voltage Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Pin15(AC_OK)  | Open-Drain Output                                             |

| Pin18(SYNC) Parallel PFC Controller to synchronize to reduce interference Pin19(SCL) I2C Serial Clock Input Pin20(SDA) I2C Serial Data Input and Output Pin21(ADD) Address Select Input Pin22(RTD) Thermistor Input Pin23(RES) Internal Voltage Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Pin16(PGOOD)  | Open-Drain Output                                             |

| Pin19(SCL)  I2C Serial Clock Input  Pin20(SDA)  I2C Serial Data Input and Output  Pin21(ADD)  Address Select Input  Pin22(RTD)  Thermistor Input  Pin23(RES)  Internal Voltage Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Pin17(INRUSH) | Inrush Current Control Signal to an Eternal Inrush Driver     |

| Pin20(SDA)  I2C Serial Data Input and Output  Pin21(ADD)  Address Select Input  Pin22(RTD)  Thermistor Input  Pin23(RES)  Internal Voltage Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Pin18(SYNC)   | Parallel PFC Controller to synchronize to reduce interference |

| Pin21(ADD) Address Select Input Pin22(RTD) Thermistor Input Pin23(RES) Internal Voltage Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Pin19(SCL)    | I2C Serial Clock Input                                        |

| Pin22(RTD) Thermistor Input Pin23(RES) Internal Voltage Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Pin20(SDA)    | I2C Serial Data Input and Output                              |

| Pin23(RES) Internal Voltage Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Pin21(ADD)    | Address Select Input                                          |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Pin22(RTD)    | Thermistor Input                                              |

| Pin24(VDD) Positive Supply Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin23(RES)    | Internal Voltage Reference                                    |