# High Frequency GaN Characterization and Design Considerations

# Xiucheng Huang

Dissertation submitted to the faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

Doctor of Philosophy In Electrical Engineering

Fred C. Lee, Chair Qiang Li Dong S. Ha Jaime De La Ree Alfred L. Wicks

Sep 6th, 2016 Blacksburg, Virginia

Keywords: Gallium nitride, high frequency, high density, soft-switching, gate drive, PCB integration, EMI

## High Frequency GaN Characterization and Design Considerations

### Xiucheng Huang

#### **ABSTRACT**

The future power conversion system not only must meet the characteristics demanded by the load, but also have to achieve high power density with high efficiency, high ambient temperature, and high reliability. Density and efficiency are two key drivers and metrics for the advancement of power conversion technologies.

Generally speaking, a high performance active device is the first force to push power density to meet the requirement of modern systems. Silicon has been a dominant material in power management since the late 1950s. However, due to continuous device optimizations and improvements in the production process, the material properties of silicon have increasingly become the limiting factor. Workarounds like the super junction stretch the limits but usually at substantial cost.

The use of gallium nitride devices is gathering momentum, with a number of recent market introductions for a wide range of applications such as point-of-load (POL) converters, off-line switching power supplies, battery chargers and motor drives. GaN devices have a much lower gate charge and lower output capacitance than silicon MOSFETs and, therefore, are capable of operating at a switching frequency 10 times greater. This can significantly impact the power density of power converters, their form factor, and even current design and manufacturing practices. To realize the benefits of GaN devices resulting from significantly higher operating frequencies, a number of issues have to be addressed, such as converter topology, soft-switching technique, high frequency gate driver, high frequency magnetics, packaging, control, and thermal management.

This work studies the insight switching characteristics of high-voltage GaN devices including some specific issues related to the cascode GaN. The package impact on the switching performance and device reliability will be illustrated in details. A stack-die package is proposed for cascode GaN devices to minimize the impact of package parasitic inductance on switching transition. Comparison of hard-switching and soft-switching operation is carried based on device model and experiments, which shows the necessity of soft-switching for GaN devices at high frequency.

This work also addresses high dv/dt and di/dt related gate drive issues associated with the higher switching speed of GaN devices. Particularly, the conventional driving solution could fail on the high side switch in a half-bridge configuration due to relative large common-mode noise current. Two simple and effective driving methods are proposed to improve noise immunity and maintain high driving speed.

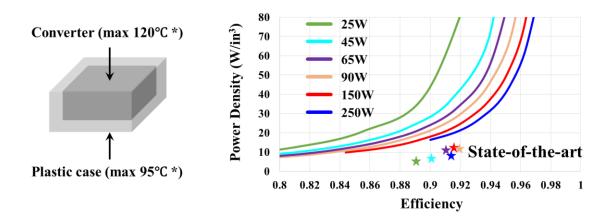

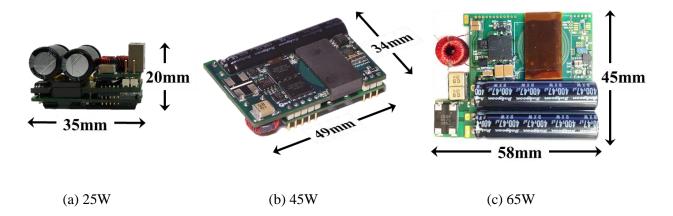

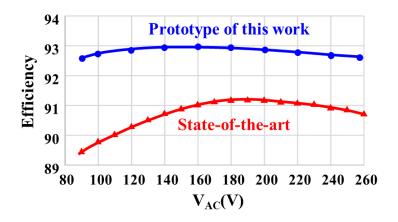

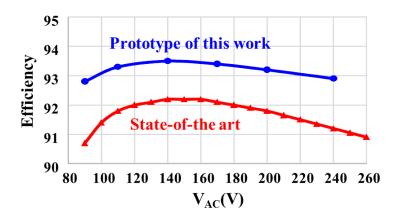

Finally, this work illustrates the utilization of GaN in an emerging application, high density AC-DC adapter. Many design considerations are presented in detail. The GaN-based adapter is capable of operating at 1-2 MHz frequency with an improved efficiency up to 94%. Several design examples at different power levels, with a power density in the range of 20~35W/in<sup>3</sup>, which is a three-fold improvement over the state-of-the-art product, are successfully demonstrated.

In conclusion, this work is focus on the characterization, and evaluation of GaN devices. Packaging, high frequency driving and soft-switching technique are addressed to fully explore the potential of GaN devices. High density adapters are demonstrated to show the advance of GaN device and its impact on system design.

## High Frequency GaN Characterization and Design Considerations

### Xiucheng Huang

### GENERAL AUDIENCE ABSTRACT

This work is focus on the characterization, evaluation and application of new wide-band-gap semiconductor devices – GaN devices. Due to superior physics property compared to existing semiconductor material, GaN device is able to switch at much higher frequency and this brings significant impact on the field of power electronics. The potential impact of GaN goes beyond the simple measures of efficiency and power density. It is feasible to design a system with a more integrated approach at higher frequency, and therefore, it is easier for automated manufacturing. This will bring significant cost reductions in power electronics equipment and unearth numerous new applications which have been previously precluded due to high cost.

To realize the benefits of GaN devices resulting from significantly higher operating frequencies, a number of issues have to be addressed, such as device packaging, power converter topology, thermal management, high frequency magnetics and system control. This dissertation discusses the most critical issues related to GaN devices with proper solutions. A practical design example of AC-DC adapter is demonstrated with much improved efficiency, density and manufacturability.

# To My Family:

My parents: Hongkun Huang and Baozhen Weng

My Parents in law: Yongjie Du and Yimin Tian

My wife: Weijing Du

My daughter: Bella Huang

# Acknowledgments

With sincere appreciation in my heart, I would like to thank my advisor, Dr. Fred Lee, for his guidance, encouragement, and support during the past five years. It is him who shows me the strength and right way to do research and pursue the beauty of power electronics. His rigorous research attitude and logical way of thinking have been a great value for me. I believe everything I've learned from Dr. Lee will benefit my future career.

I would also like to thank Dr. Qiang Li for his valuable guidance during my research. I still remember the weekly individual meeting with him when I just join CPES and it was so important to help me build the initial skill set and explore the right research area. He is more than a professor to me, but a model that I want to follow in the past and the future.

Moreover, with sincere gratitude, I would thank Dr. Fred Lee, Ms. Lee, Dr. Qiang Li and Ms. Luman Chen for their selfless help when my wife is in the period of confinement. They help us to get through the difficulty and this precious memory will bear in mind forever.

It is an honor for me to have Professor Dong S. Ha, Professor Jaime De La Ree and Professor Alfred L. Wicks as my committee members. I am truly thankful to them for all comments from different technical perspective which would broad my knowledge significantly.

It is fortunate to study GaN devices, which are considered to have significant impact on power electronics, since I came to CPES. It is even more fortunate to have my colleague and friend, Zhengyang Liu. We work together from day one and explore the unknown knowledge about GaN devices. We have faced tons of difficulties when we conducted research without much of reference, but we never gave up. "No pain, no gain", and I understood these words deeply in my heart. I am also especially indebted to my colleagues in the GaN Group. We have many valuable discussions during day and night. Many of the ideas in this work are inspired by casual talk. I would like to thank all the members of our teams: Dr.Wenli Zhang, Dr. David Reusch, Dr. Mingkai Mu, Mr. Alex Ji, Mr. Yucheng, Mr. Chao Fei, Mr. Bin Li, Mr. Shishuo Zhao, Mr. Junjie Feng, Mr. Zhengrong Huang, Mr. Tao Liu.

I would also like to thank colleagues in the power management consortium (PMC) of CPES. It has been a great pleasure to work with the talented, creative, helpful and dedicated colleagues. Dr. Yingyi Yan, Dr. Weiyi Feng, Dr. Yipeng Su, Dr. Shuilin Tian, Dr. Pei-Hsin Liu, Dr.Dongbin Hou, Mr. Wei Zhang, Mr. Li Jiang, Mr. Syed Bari, Mr. Xuebin Chen Mr. Zhongsheng Cao, Mr. Xuebing Chen, Ms. Virginia Li, Mr. Mohamed Ahmed.

My thanks also go to all of the other students I have met in CPES. It is precious memory to live and work with them in the past five years. Many visiting scholars have brought their expertise and valuable discussion during my research. Dr. Li Wang, Dr Xin Ming, Dr. Yan-Cun Li, Dr. Kenichiro Tanaka, Dr.Shuojie She, Mr. Chaofeng Cai. Thank you for the help and friendship.

I would also like to thank all the wonderful staffs in CPES: Ms. Linda Gallagher, Ms. Teresa Shaw, Ms. Teresa Rose, Ms. Marianne Hawthorne, Ms. Linda Long, Mr. Doug Sterk and Mr. David Gilham for their support and help over the past six years.

With much love and gratitude, I want to thank my parents: Hongkun Huang and Baozhen Weng; my parents in law: Yongjie Du, Yimin Tian; who have always been there with their love and support.

Finally but not the least, I would like to thank my wife Weijing Du and my daughter Bella Huang. You are always the special one and mean a lot to me. I want to be with you all my life.

The information, data, or work presented herein was funded in part by the Office of Energy Efficiency and Renewable Energy (EERE), U.S. Department of Energy, under Award Number DE-EE0006521 with North Carolina State University, PowerAmerica Institute. This work was also supported in part by PMC at CPES: Chicony Power, CSR Zhuzhou Institute Co., Ltd., Delta Electronics, Huawei Technologies, Infineon Technologies, Inventronics Inc, Linear Technology, Murata Manufacturing Co., Ltd., NEC TOKIN Corporation, NXP Semiconductors, ON Semiconductor, Panasonic Corporation, Richtek Technology, Sonos, Texas Instruments.

This work was conducted with the use of GaN device samples by EPC, Navitas, Panasonic, and Transphorm of the CPES Industry Consortium Program.

# **Disclaimer**

The information, data, or work presented herein was funded in part by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United

States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

# Table of Contents

| Chapter 1. Introduction                                         | 1  |

|-----------------------------------------------------------------|----|

| 1.1 Background and Motivation                                   | 1  |

| 1.2 Overview of GaN Power Devices                               | 3  |

| 1.2.1 Why GaN                                                   | 3  |

| 1.2.2 Enhancement Mode and Depletion Mode GaN Devices           | 6  |

| 1.2.3 Steady-state Characteristics of 600V GaN Devices          | 9  |

| 1.2.4 Reverse Conduction of GaN Devices                         | 10 |

| 1.3 Challenges of GaN devices                                   | 11 |

| 1.3.1 Switching Characteristics                                 | 12 |

| 1.3.2 Package Impact on Switching Behavior and Gate Reliability | 13 |

| 1.3.3 High dv/dt and di/dt                                      | 13 |

| 1.4 Impact of GaN Devices on System Level Design                | 14 |

| 1.4.1 High Frequency Magnetics                                  | 14 |

| 1.4.2 High Frequency EMI                                        | 15 |

| 1.4.3 High Frequency control                                    | 15 |

| 1.5 GaN Based Applications                                      | 16 |

| 1.6 Dissertation Outline                                        | 16 |

| Chapter 2. Switching Characterization of GaN Devices            | 18 |

| 2.1 Switching Loss Mechanism Analysis of GaN Devices            | 18       |

|-----------------------------------------------------------------|----------|

| 2.1.1 GaN device loss model                                     | 18       |

| 2.1.2 Turn-on transition                                        | 25       |

| 2.1.3 Turn-off transition                                       | 28       |

| 2.2 Packaging Impact on Switching Loss                          | 32       |

| 2.3 Special Issues in Cascode GaN Devices                       | 38       |

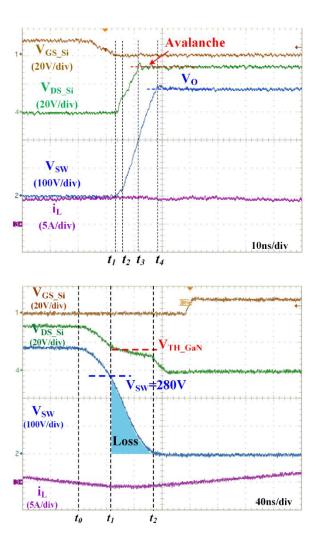

| 2.3.1 Si MOSFET Avalanche                                       | 39       |

| 2.3.2 GaN Internal Switching Loss                               | 41       |

| 2.3.3 Failure I: Internal GaN Gate Ringing                      | 45       |

| 2.3.4 Failure II: Divergent Oscillation at High Current         | Turn-off |

| Condition                                                       | 46       |

| 2.3.5 Proposed Solution: Better Package and Charge Balance      | 50       |

| 2.4 Conclusion                                                  | 65       |

| Chapter 3. Design Considerations for GaN Devices                | 66       |

| 3.1 Soft-switching or hard-switching                            | 66       |

| 3.2 High Frequency Gate Drive                                   | 74       |

| 3.2.1 The di/dt Issue and Solutions                             | 76       |

| 3.2.2 The dv/dt Issue (Common mode Noise Current) and Solutions | 78       |

| 3.4 Conclusion                                                  | 86       |

| Chanter 4 System Design of GaN Based AC-DC Adapters             | 87       |

| 4.1 State-of-the-art Practice                                      | 87       |

|--------------------------------------------------------------------|----------|

| 4.2 MHz Active Clamp Flyback Converter for Adapters Po < 75W       | 91       |

| 4.2.1 Soft-switching with Active Clamping Circuit                  | 91       |

| 4.2.2 MHz Flyback Transformer                                      | 96       |

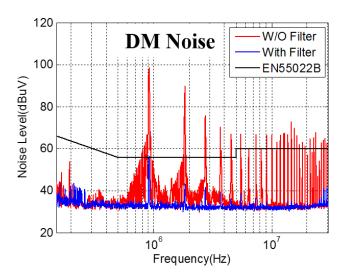

| 4.2.3 MHz Flyback Converter EMI Characterization and Filter Design | n107     |

| 4.2.4 High Frequency Control of Active Clamp Flyback Converter     | 119      |

| 4.2.5 Experiments Results and Discussion                           | 127      |

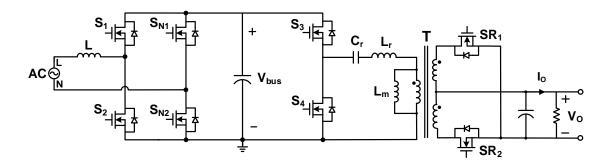

| 4.3 Universal adapter design for a wide power range                | 132      |

| 4.3.1 System Structure of Proposed Universal Adapter               | 133      |

| 4.3.2 First Stage: Totem-pole Bridgeless Rectifier with            | Harmonic |

| Injection                                                          | 134      |

| 4.3.3 Second Stage: LLC-DCX                                        | 143      |

| 4.3.4 Experiment Results and Discussion                            | 147      |

| 4.4 Conclusion                                                     | 155      |

| Chapter 5. Conclusion and Future Work                              | 157      |

| 5.1 Conclusion                                                     | 157      |

| 5.2 Future Work                                                    | 159      |

| Appendix A. GaN Analytical Loss Model                              | 160      |

| Appendix B. GaN Converter with Inverse Coupled Inductor            | 193      |

| References                                                         | 219      |

# List of Figures

| Figure 1.1 Roadmap of Intel microprocessors                                                  | 1     |

|----------------------------------------------------------------------------------------------|-------|

| Figure 1.2 Specific on-resistance vs breakdown voltage for Si, SiC, GaN                      | 5     |

| Figure 1.3 Basic structure of GaN device                                                     | 7     |

| Figure 1.4 Basic structure of d-mode GaN device, (a) on state, (b) off state                 | 7     |

| Figure 1.5 Cascode GaN: a d-mode GaN in series with a low voltage Si MOSFET                  | 8     |

| Figure 1.6 Basic structure of enhancement mode GaN device, (a) on state, (b) off state       | 8     |

| Figure 1.7 Reverse conduction of e-mode GaN devices: (a) e-mode GaN, (b) cascode GaN         | 10    |

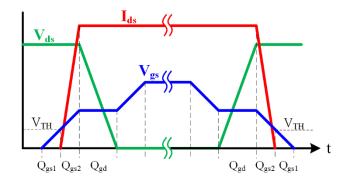

| Figure 1.8 Hard-switching turn-on transient of GaN device                                    | 12    |

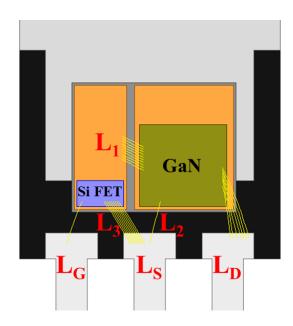

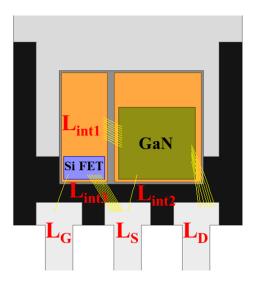

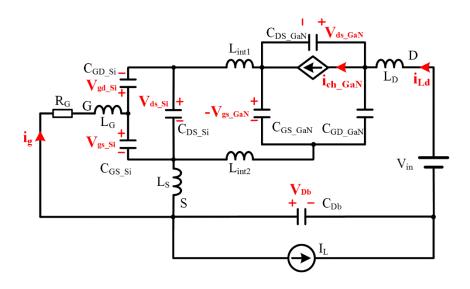

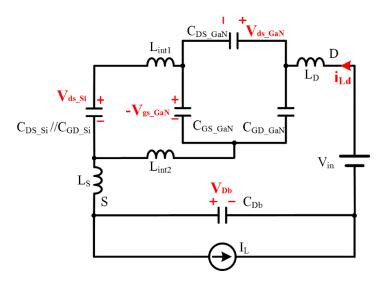

| Figure 2.1 Packaging parasitics of a cascode GaN device                                      | 19    |

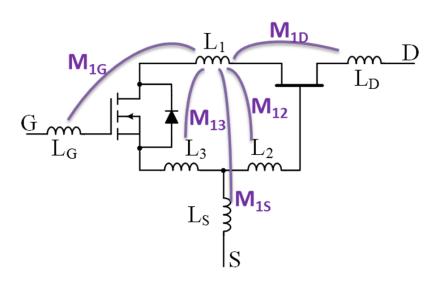

| Figure 2.2 Comparison of switching waveforms w/ original model and modified model            | 20    |

| Figure 2.3 Equivalent circuit during the first stage of turn on transition                   | 21    |

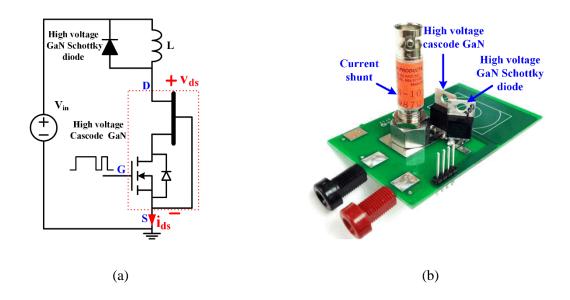

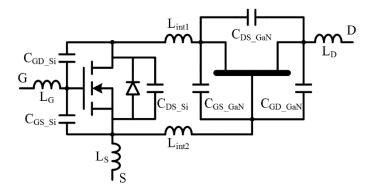

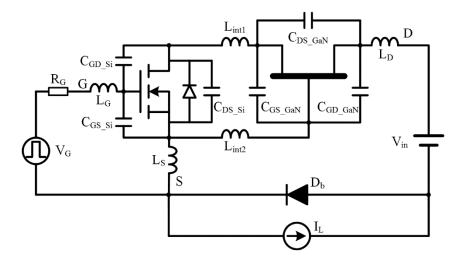

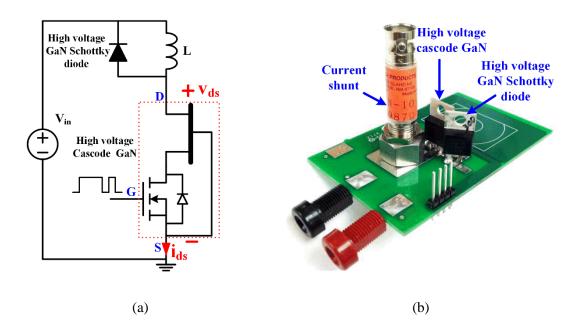

| Figure 2.4 Model validation with double-pulse-test circuit: (a) diagram, (b) prototype       | 24    |

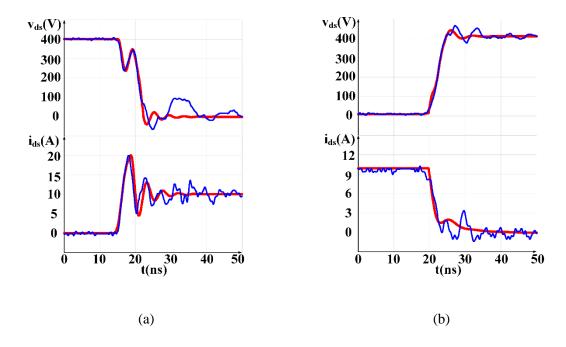

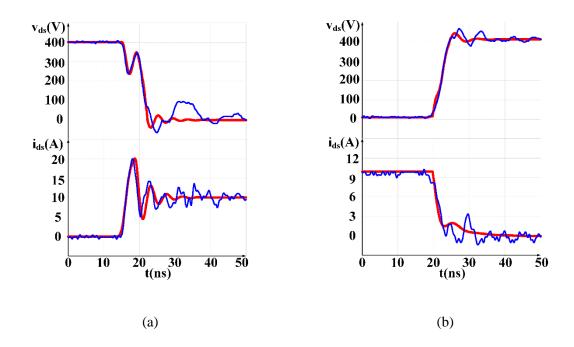

| Figure 2.5 Turn on/off waveforms comparisons (Blue line: experiment, red line: analytical mo | odel) |

| (a) Turn on @10A, (b) Turn off@10A                                                           | 24    |

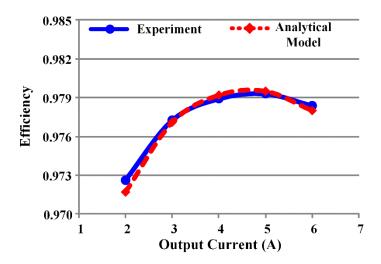

| Figure 2.6 Efficiency comparison between experimental and calculation results based on prop  | osed  |

| model                                                                                        | 25    |

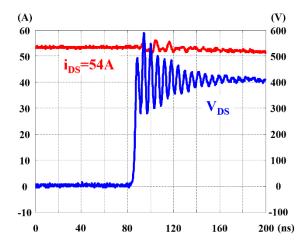

| Figure 2.7 Hard-switching turn-on waveforms                                                  | 26    |

| Figure 2.8 Turn-on switching loss of different GaN devices                                   | 28    |

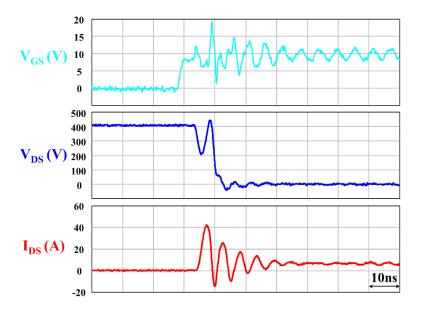

| Figure 2.9 Hard-switching turn-off waveforms                                                 | 29    |

| Figure 2.10 Turn-off mechanism of different types of GaN devices: (a) e-mode, (b) cascode    | 30    |

| Figure 2.11 Turn-off switching loss of different GaN devices                                 | 31    |

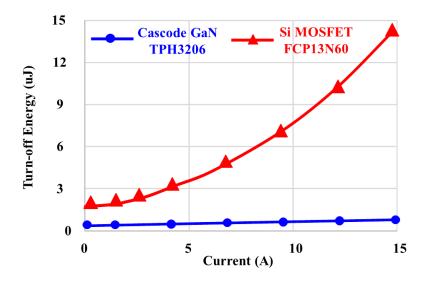

| Figure 2.12 Comparison of turn-off switching loss: GaN vs. Si                                | 32    |

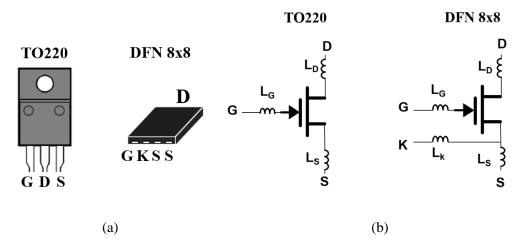

| Figure 2.13 Package and related inductance of 600V e-mode GaN devices: (a) Packages for 6    | 500V  |

| e-mode GaN, (b) Package related inductance                                                   | 33    |

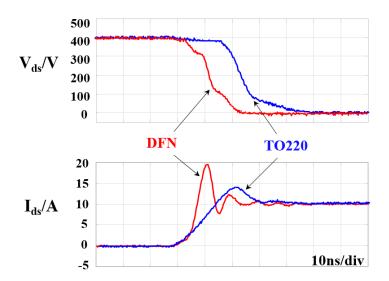

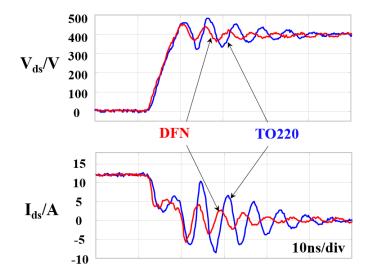

| Figure 2.14 Turn-on transition of different packages                                         | 34    |

| Figure 2.15 Turn-off transition of different packages                                   | 34          |

|-----------------------------------------------------------------------------------------|-------------|

| Figure 2.16 Switching energy of different package                                       | 35          |

| Figure 2.17 Two different packages for cascode GaN devices: (a) To 220 Package, (b)     | ) Stack die |

| package                                                                                 | 36          |

| Figure 2.18 Two packages related parasitic inductance: (a) TO220 package, (b)           | Stack-die   |

| package                                                                                 | 37          |

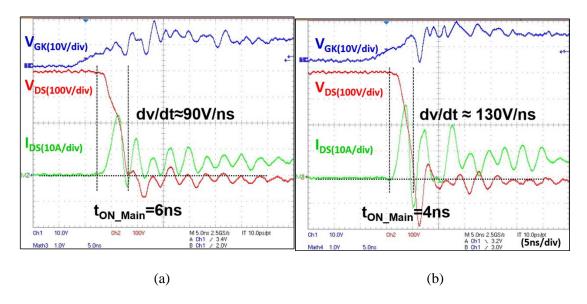

| Figure 2.19 Turn-on waveform comparison between (a) TO-220 package, and (b)             | Stack-die   |

| package                                                                                 | 37          |

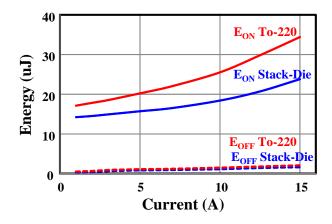

| Figure 2.20 Switching energy comparison of different packages                           | 38          |

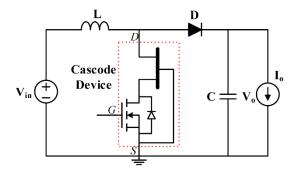

| Figure 2.21 Boost converter with cascode GaN device                                     | 38          |

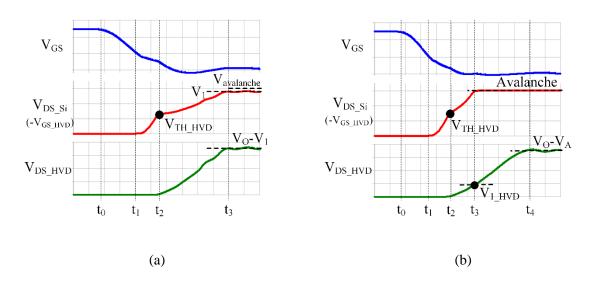

| Figure 2.22 Two possible turn-off transition of cascode GaN devices                     | 39          |

| Figure 2.23 Si MOSFET reaches avalanche during turn-off transition                      | 40          |

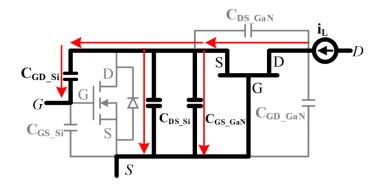

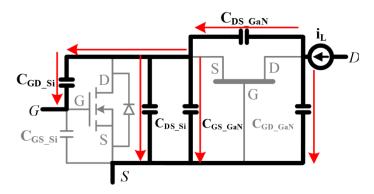

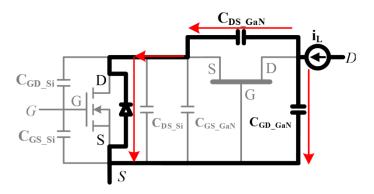

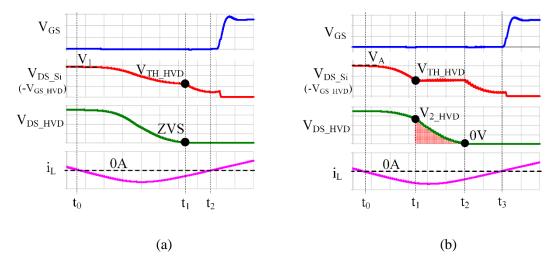

| Figure 2.24 Two possible ZVS turn-on transition of cascode GaN devices                  | 42          |

| Figure 2.25 GaN internal switching loss during ZVS turn-on transition                   | 42          |

| Figure 2.26 The relationship of internal turn-on switching loss and mismatch charge     | 44          |

| Figure 2.27 GaN gate breakdown due to parasitic ringing during turn-off transition: (a) | di/dt loop  |

| during turn-off transition, (b) Key waveforms during turn-off transition                | 45          |

| Figure 2.28 Illustration of divergent oscillation                                       | 47          |

| Figure 2.29 Equivalent circuits during oscillation period                               | 48          |

| Figure 2.30 GaN gate voltage spike elimination with stack-die package                   | 51          |

| Figure 2.31 Adding an extra capacitor in cascode GaN devices                            | 52          |

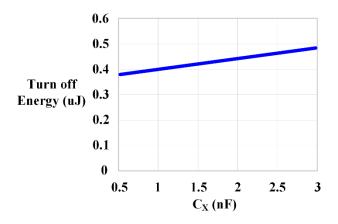

| Figure 2.32 Impact of an extra capacitor on turn-off switching loss                     | 53          |

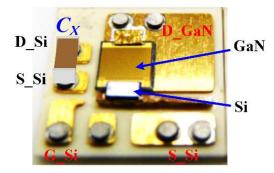

| Figure 2.33 Chip-on-chip package for cascode GaN device with an extra capacitor         | 54          |

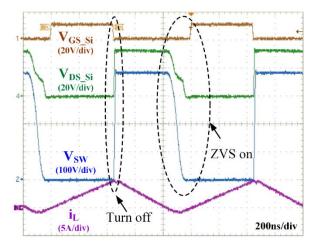

| Figure 2.34 Experimental waveforms without external capacitor                           | 55          |

| Figure 2.35 Experimental waveform with external capacitor                               | 56          |

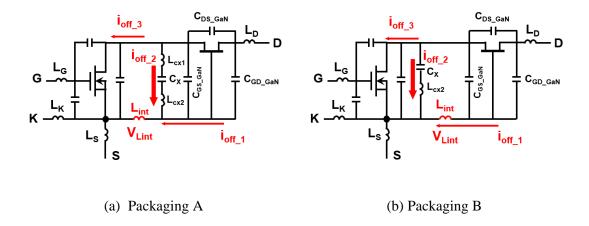

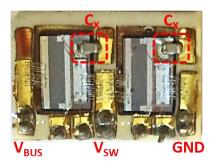

| Figure 2.36 Two possible packaging approach with Cx                                     | 58          |

| Figure 2.37 Equivalent circuit of two different packaging approaches                          | 59   |

|-----------------------------------------------------------------------------------------------|------|

| Figure 2.38 Current distribution in different packages                                        | 60   |

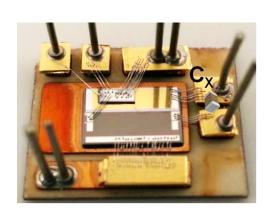

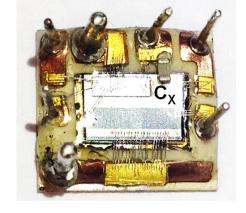

| Figure 2.39 Prototypes of two different packaging approaches                                  | 61   |

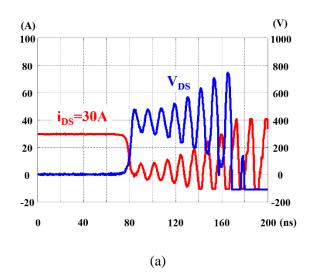

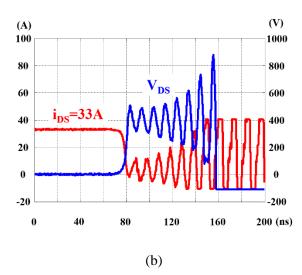

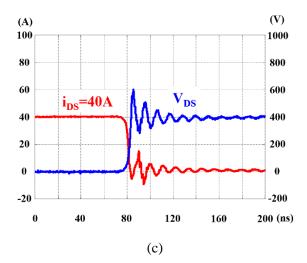

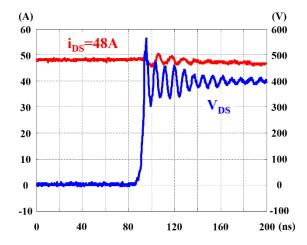

| Figure 2.40 Experimental results with different packaging approaches (a) Packag-ing A and     | d B  |

| without $C_X$ (b) Packaging A with $C_X$ (c) Packaging B with $C_X$                           | 63   |

| Figure 2.41 Experiment with packaging B, without shunt resistance                             | 63   |

| Figure 2.42 Half bridge module of cascode GaN devices with packaging B approach               | 64   |

| Figure 2.43 Experiment with half bridge module of cascode GaN devices with packaging          | g B  |

| approach                                                                                      | 64   |

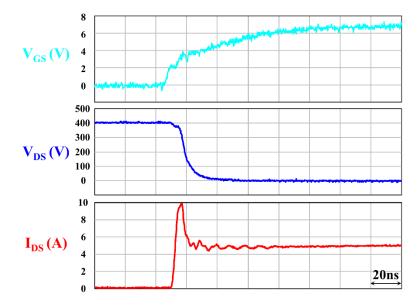

| Figure 3.1 Hard-switching turn-on transient of GaN device with severe parasitic ringing       | 67   |

| Figure 3.2 Hard-switching turn-on transient of GaN device with less parasitic ringing by slow | ving |

| down switching speed                                                                          | 67   |

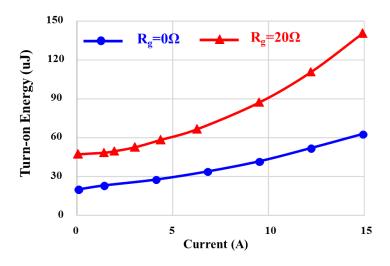

| Figure 3.3 Hard-switching turn-on energy vs. R <sub>g</sub>                                   | 68   |

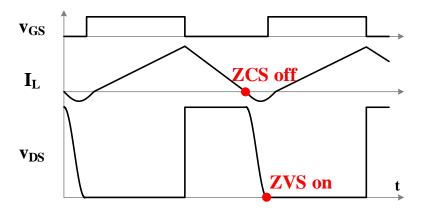

| Figure 3.4 CRM operation principle                                                            | 69   |

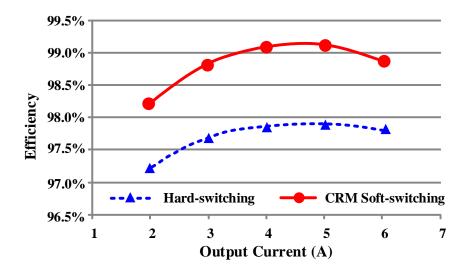

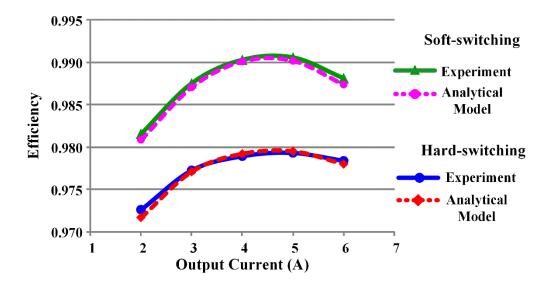

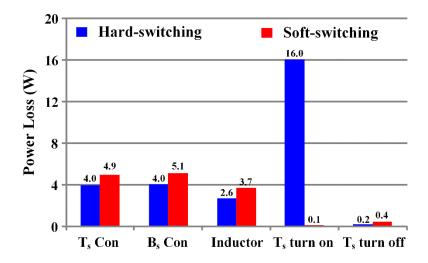

| Figure 3.5 Hard-switching vs. CRM soft-switching                                              | 70   |

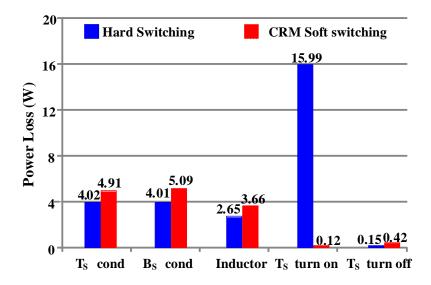

| Figure 3.6 Loss breakdown at 6A                                                               | 70   |

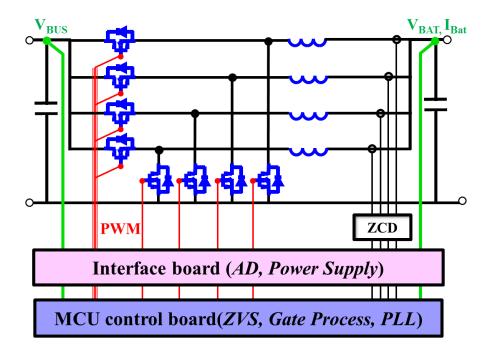

| Figure 3.7 4-phase bidirectional buck/boost converter for energy storage system               | 71   |

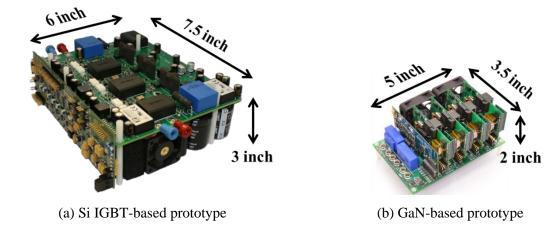

| Figure 3.8 Comparison of GaN-based prototype and Si IGBT-based prototype                      | 72   |

| Figure 3.9 5 MHz converter with the cascode GaN switch                                        | 73   |

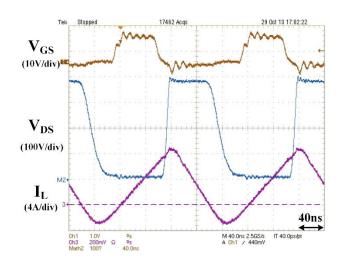

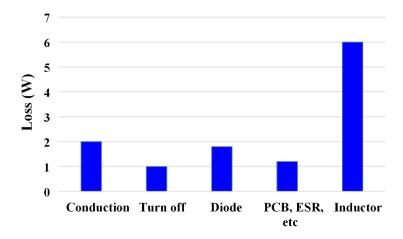

| Figure 3.10 Loss breakdown of 5 MHz CRM boost converter with cascode GaN device               | 74   |

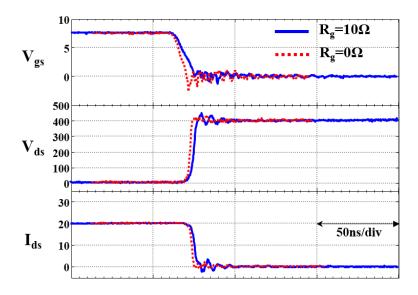

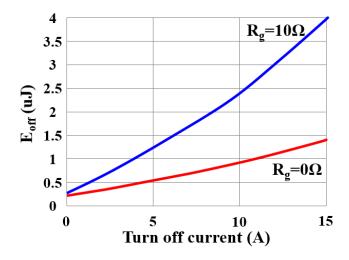

| Figure 3.11 Turn-off transition with different gate resistance                                | 75   |

| Figure 3.12 Turn-off energy with different gate resistance                                    | 75   |

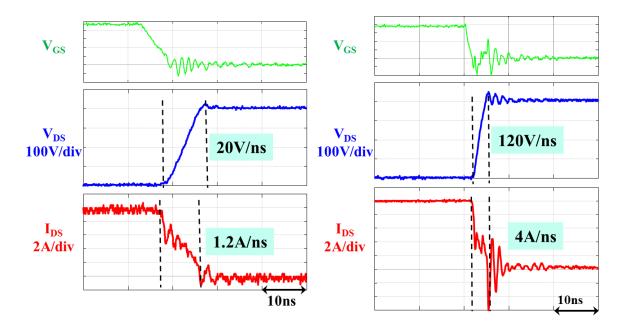

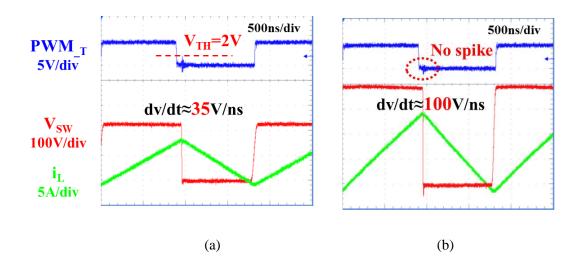

| Figure 3.13 High dv/dt and di/dt induced by GaN devices: (a) Si MOSFET, (b) GaN switch        | 76   |

| Figure 3.14 di/dt impact on gate drive loop                                                   | 77   |

| Figure 3.15 High di/dt induces voltage on the gate                                            | 77   |

| Figure 3.16 Smaller voltage spike with less CSI                                               | 78   |

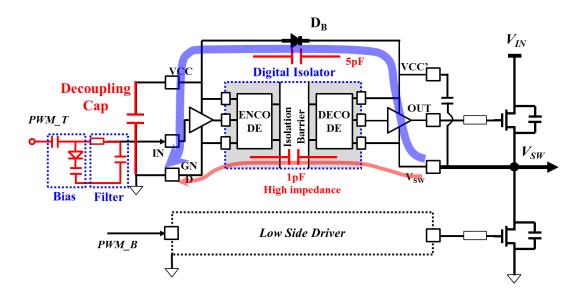

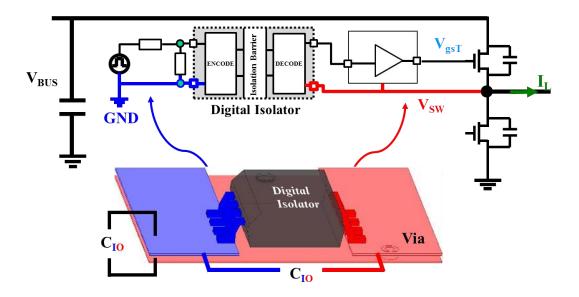

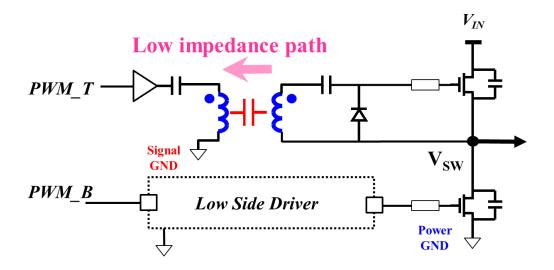

| Figure 3.17 High dv/dt causes common-mode current across parasitic capacitance of level shifter |

|-------------------------------------------------------------------------------------------------|

| or isola-tor (cascode GaN is used as an example)79                                              |

| Figure 3.18 High dv/dt deteriorates the PWM signal                                              |

| Figure 3.19 Proposed high side gate drive circuit                                               |

| Figure 3.20 PCB layout impact on dv/dt immunity for high side driver                            |

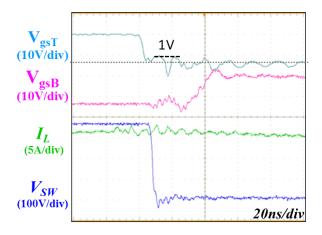

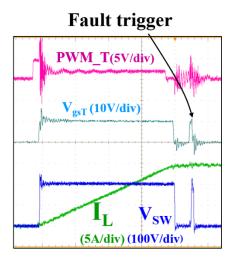

| Figure 3.21 Experimental waveform of improved dv/dt immunity for high side driver82             |

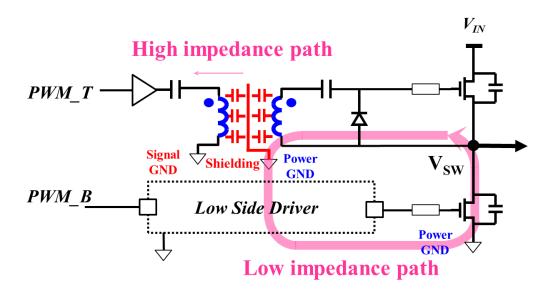

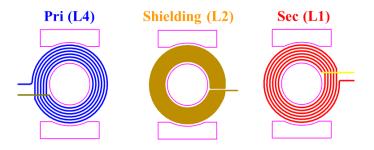

| Figure 3.22 Conventional driving transformer is susceptible to noise due to large parasitic     |

| capacitance                                                                                     |

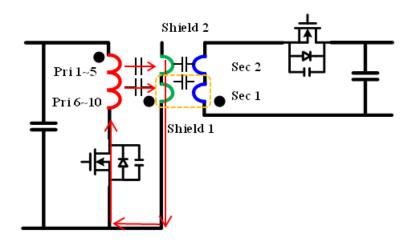

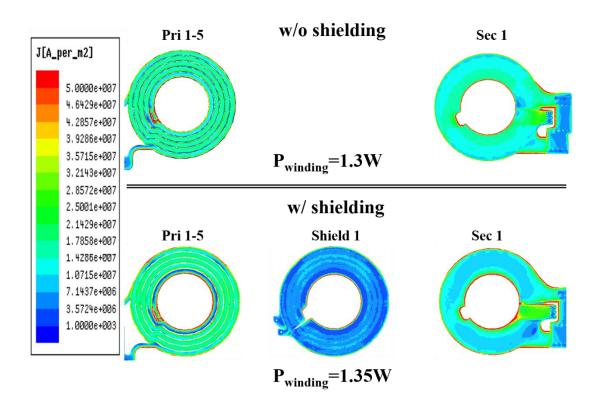

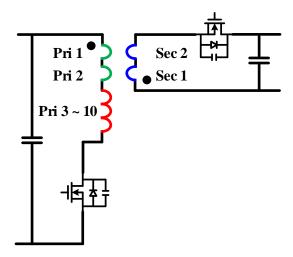

| Figure 3.23 Novel driving transformer with shielding                                            |

| Figure 3.24 Proposed driving transformer with shielding                                         |

| Figure 3.25 Comparison of driving transformer: (a) w/o shielding, (b) w/ shielding85            |

| Figure 4.1 Applications of AC-DC adapter                                                        |

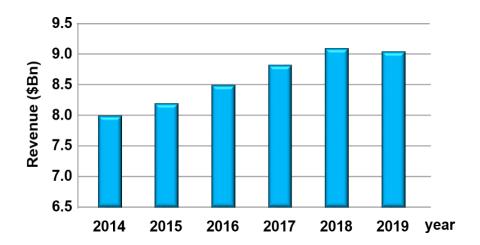

| Figure 4.2 Adapter market information Figure 4.2 [D.1]                                          |

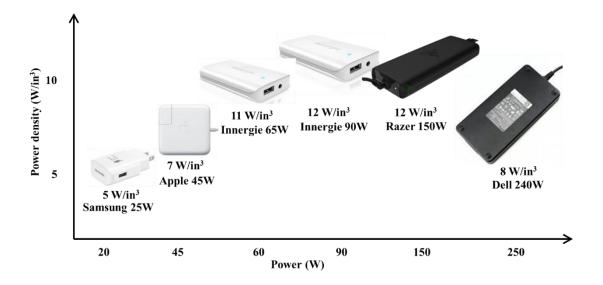

| Figure 4.3 State-of-the-art AC-DC adapters                                                      |

| Figure 4.4 Inside the Apple adapter90                                                           |

| Figure 4.5 Theoretical limit of power density vs. efficiency (max 95°C with plastic case)91     |

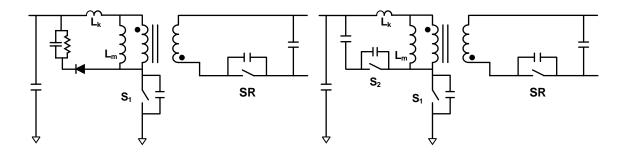

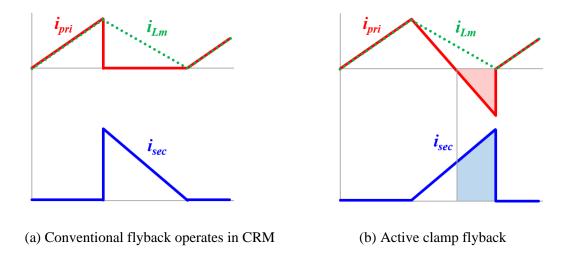

| Figure 4.6 Conventional flyback vs. Active clamp flyback                                        |

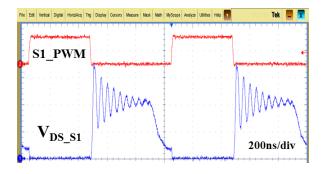

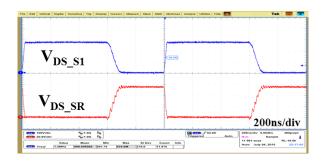

| Figure 4.7 Key waveforms of two flyback topology operating at 1MHz93                            |

| Figure 4.8 Comparison of ideal transformer winding current94                                    |

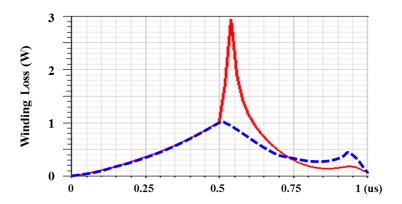

| Figure 4.9 Time-domain winding loss of two flyback topologies (red solid line: conventional     |

| flyback; blue dash line: active clamp flyback)                                                  |

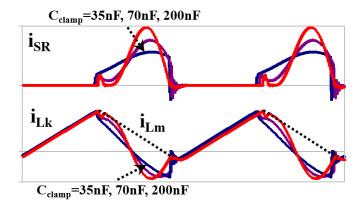

| Figure 4.10 Impact of clamping capacitor on primary and secondary current waveforms96           |

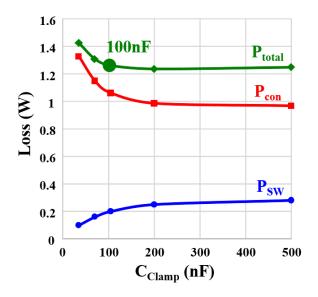

| Figure 4.11 Impact of clamping capacitor on converter loss                                      |

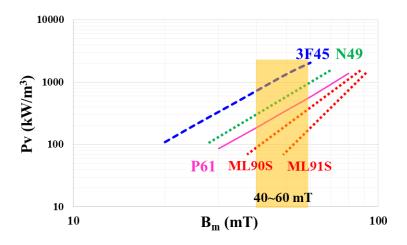

| Figure 4.12 Comparison of core loss density of different core material98                        |

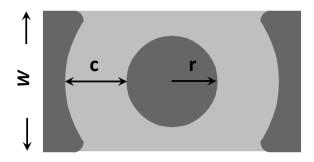

| Figure 4.13 ER core shape for MHz design99                                                      |

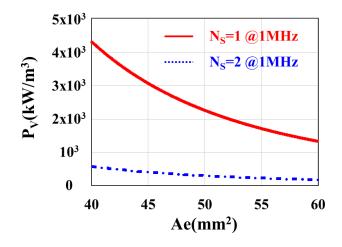

| Figure 4.14 Core loss density vs. N <sub>S</sub>                                          | 100    |

|-------------------------------------------------------------------------------------------|--------|

| Figure 4.15 Cross section view of the transformer winding (red line represents primary wi | nding, |

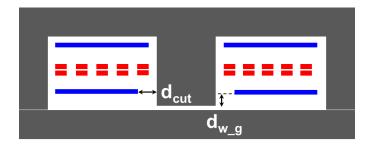

| blue line represents secondary winding)                                                   | 100    |

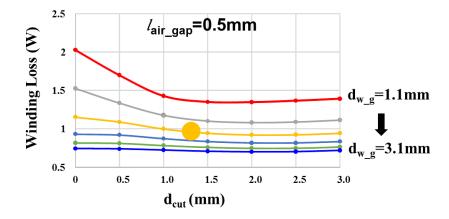

| Figure 4.16 Relationship of winding loss and distance between winding and air gap         | 101    |

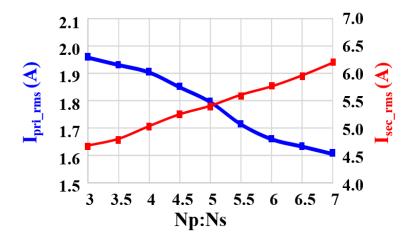

| Figure 4.17 Impact of turns ratio on converter current                                    | 102    |

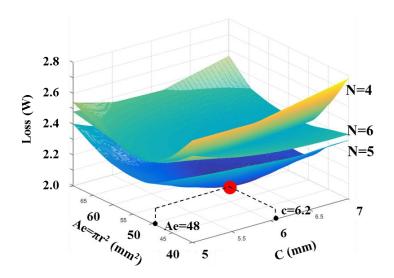

| Figure 4.18 Related loss vs. transformer parameters                                       | 103    |

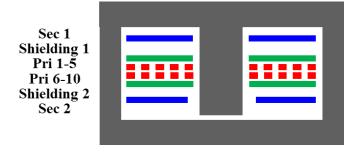

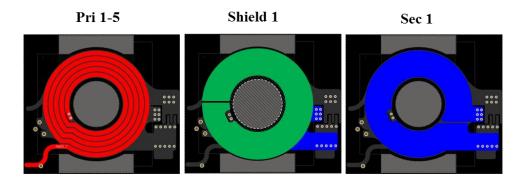

| Figure 4.19 Flyback transformer winding structure with shielding                          | 105    |

| Figure 4.20 Flyback transformer with shielding                                            | 105    |

| Figure 4.21 3D FEA simulation of flyback transformer with and without shielding layer     | 106    |

| Figure 4.22 Integrated shielding layer as the primary winding                             | 107    |

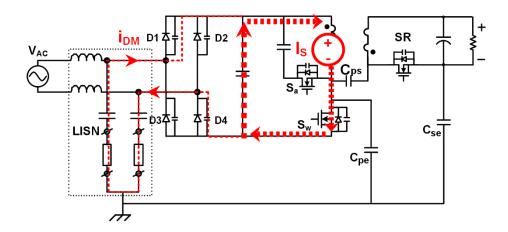

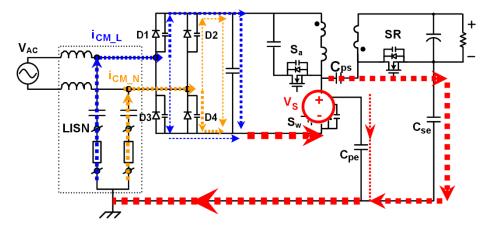

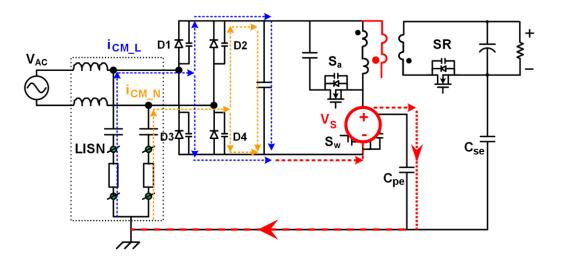

| Figure 4.23 EMI noise propagation path of active clamp flyback converter                  | 109    |

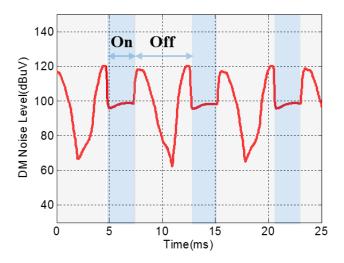

| Figure 4.24 DM noise of switching frequency using zero-span mode in spectrum analyzer     | 110    |

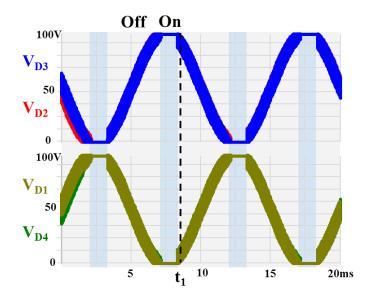

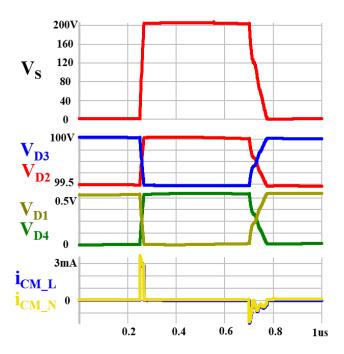

| Figure 4.25 Diode bridge voltage waveforms in line cycle                                  | 111    |

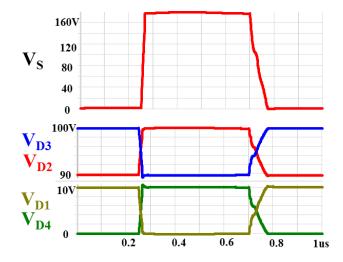

| Figure 4.26 Diode bridge voltage waveform at t <sub>1</sub> instant                       | 111    |

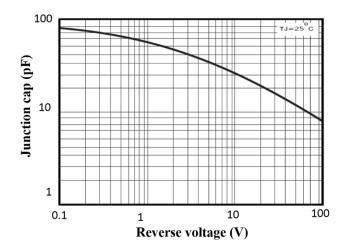

| Figure 4.27 Diode junction capacitance characteristics                                    | 112    |

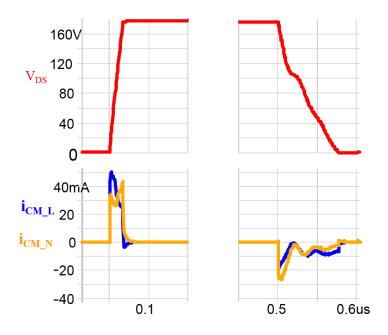

| Figure 4.28 CM noise current in L line and N line                                         | 112    |

| Figure 4.29 CM noise propagation path with shielding                                      | 113    |

| Figure 4.30 Detailed diode-bridge voltage waveform and CM noise current in L line and     | N line |

| right after diode bridge is off                                                           | 114    |

| Figure 4.31 EMI noise measurement                                                         | 115    |

| Figure 4.32 DM noise of switching frequency using zero-span mode in spectrum analyzer     | 116    |

| Figure 4.33 EMI filter for conventional adapter application                               | 117    |

| Figure 4.34 One-stage EMI filter for MHz flyback converter                                | 118    |

| Figure 4.35 Choke material comparison                                                     | 119    |

| Figure 4.36 Picture of CM/DM choke for MHz flyback converter                              | 119    |

| Figure 4.37 Control of MHz active clamp flyback converter for adapter application         | 121    |

| Figure 4.38 Trajectory analysis of resonance in active clamp flyback converter         | 122       |

|----------------------------------------------------------------------------------------|-----------|

| Figure 4.39 Conventional ZVS detection using auxiliary winding voltage                 | 124       |

| Figure 4.40 Proposed ZVS detection method                                              | 125       |

| Figure 4.41 Proposed DCM clamp method [D.25]                                           | 126       |

| Figure 4.42 Three prototypes employs MHz active clamp flyback topology                 | 127       |

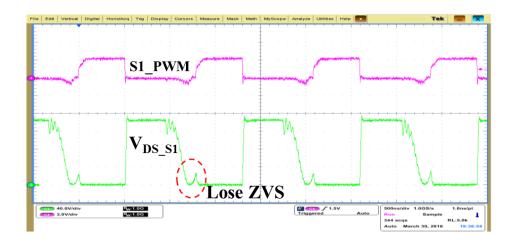

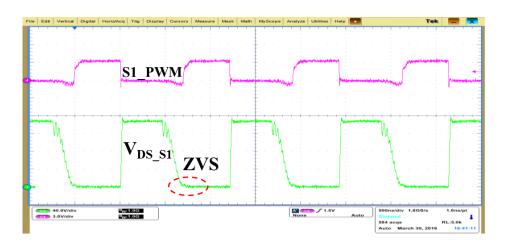

| Figure 4.43 Experimental waveforms of different ZVS detection method                   | 128       |

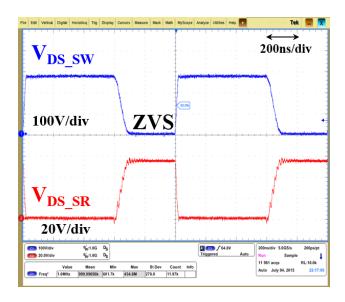

| Figure 4.44 65W prototype experiment waveforms                                         | 129       |

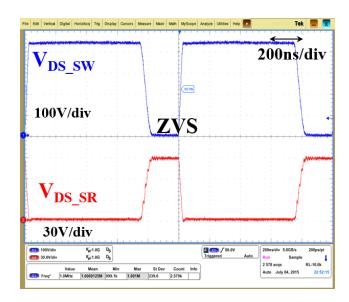

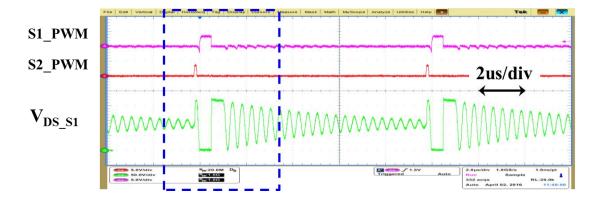

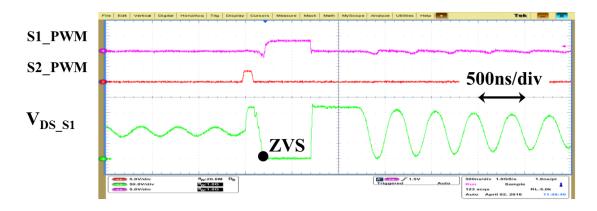

| Figure 4.45 Experimental waveforms of proposed DCM clamp method                        | 130       |

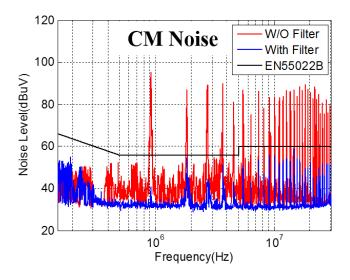

| Figure 4.46 Prototype EMI noise measurement with and without filter                    | 131       |

| Figure 4.47 Efficiency comparison of the prototype and state-of-the-art products       | 132       |

| Figure 4.48 Universal two-stage structure for adapters using a wide power range        | 134       |

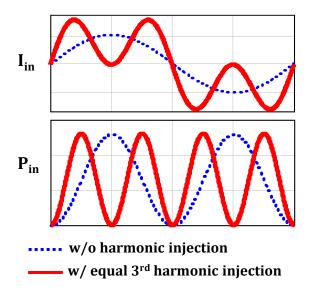

| Figure 4.49 Impact of harmonic injection on input power for below 75W adapters         | 136       |

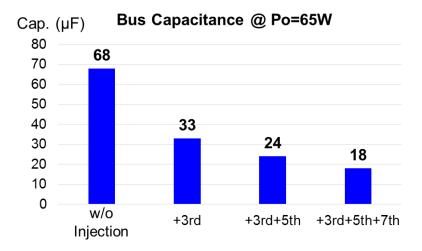

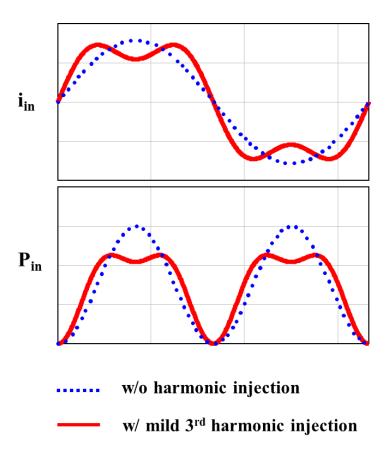

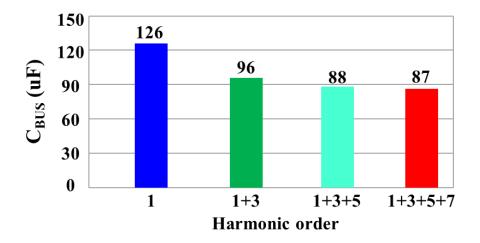

| Figure 4.50 Relationship of bus cap reduction with harmonic injection                  | 137       |

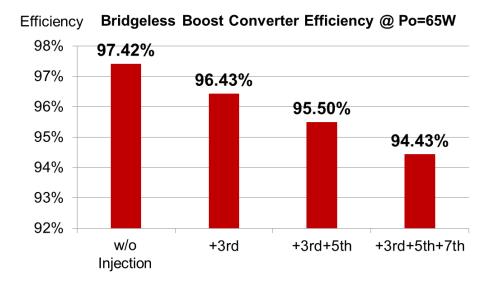

| Figure 4.51 Relationship of first stage efficiency with harmonic injection             | 138       |

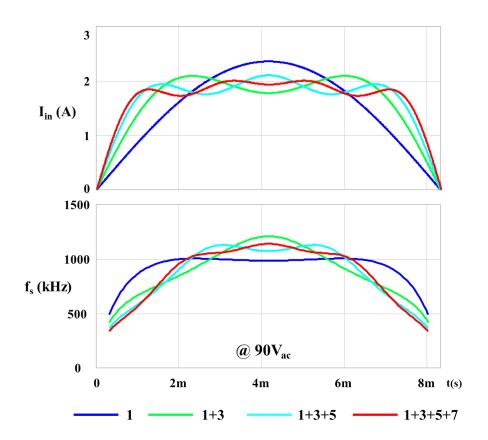

| Figure 4.52 Impact of harmonic injection on input power for adapters above 75W         | 139       |

| Figure 4.53 Bus capacitance reduction with harmonics injection                         | 140       |

| Figure 4.54 Impact of harmonic injection on switching frequency                        | 141       |

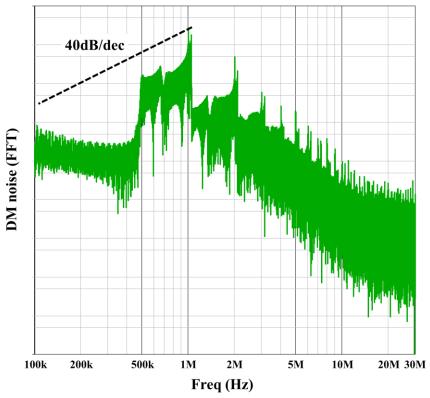

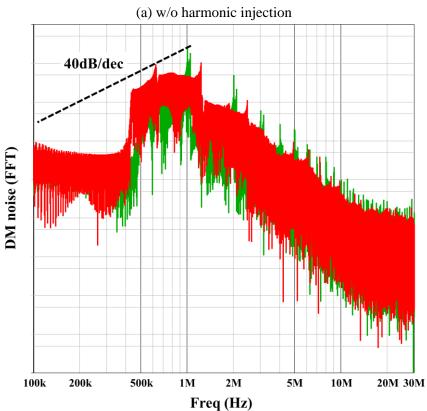

| Figure 4.55 Impact of harmonic injection on EMI noise spectrum                         | 143       |

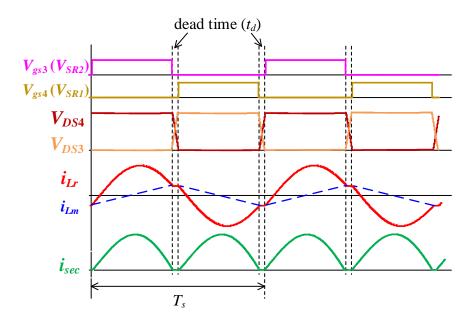

| Figure 4.57 Key waveforms of LLC converter operating at Fs=Fo                          | 144       |

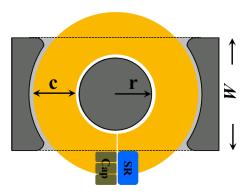

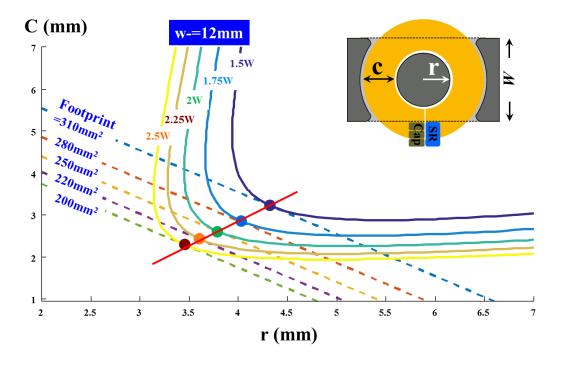

| Figure 4.58 PCB winding based LLC-DCX transformer integrated SR and caps               | 145       |

| Figure 4.59 Transformer loss vs. core radius r and window width c                      | 146       |

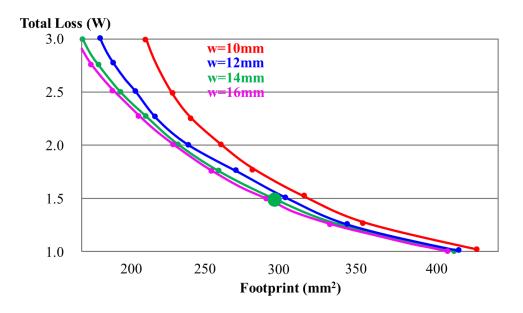

| Figure 4.60 Transformer and footprint tradeoff                                         | 147       |

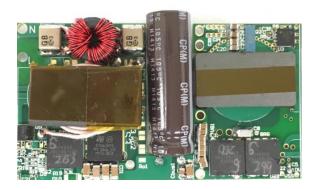

| Figure 4.61 Two-stage prototypes                                                       | 148       |

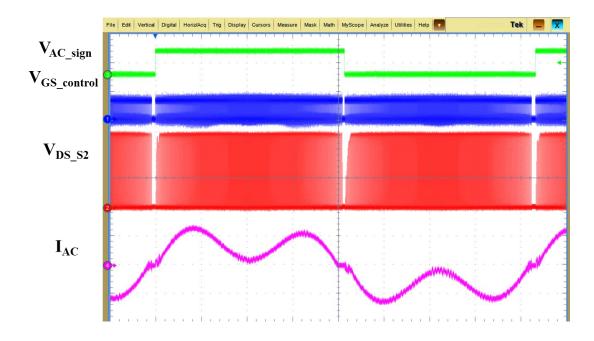

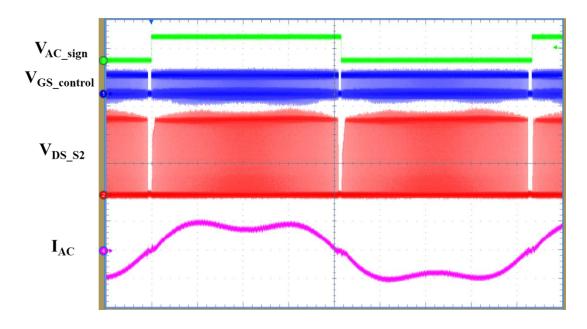

| Figure 4.62 Key waveforms of totem-pole rectifier                                      | 150       |

| Figure 4 63 Cap reduction/voltage ripple reduction with harmonic injection in 65W prot | otyne 151 |

| Figure 4.64 Cap reduction/voltage ripple reduction with harmonic injection in 150               | W   |

|-------------------------------------------------------------------------------------------------|-----|

| prototype1                                                                                      | 52  |

| Figure 4.65 One-stage filter for proposed 150W 2-stage adapter                                  | 52  |

| Figure 4.66 EMI measurement results of 150W prototype                                           | 53  |

| Figure 4.67 Measured efficiency of proposed 2-stage adapters                                    | 54  |

| Figure 4.68 Achievement of higher density and higher efficiency adapter                         | 55  |

| Appendix A                                                                                      |     |

| Figure.A 1 Piecewise linear approximation of the conventional loss model                        | 60  |

| Figure.A 2 Package of a cascode GaN                                                             | 63  |

| Figure.A 3 Equivalent cascode GaN transistor including parasitic inductors and capacitors1      | 65  |

| Figure.A 4 Simplified equivalent circuit to analyze switching loss of cascode GaN transistor1   | 66  |

| Figure.A 5 Equivalent circuit during turn on Stage I                                            | 67  |

| Figure.A 6 Equivalent circuit during turn on Stage II1                                          | 68  |

| Figure.A 7 Further simplified equivalent circuit during turn on Stage II1                       | 69  |

| Figure.A 8 Equivalent circuit during turn on Stage III                                          | 71  |

| Figure.A 9 Equivalent circuit during turn on Stage V                                            | 74  |

| Figure.A 10 Equivalent circuit during turn on Stage VI                                          | 76  |

| Figure.A 11 Equivalent circuit during turn off Stage I                                          | 77  |

| Figure.A 12 Equivalent circuit during turn off Stage II                                         | 79  |

| Figure.A 13 Equivalent circuit during turn off Stage III                                        | 81  |

| Figure.A 14 Equivalent circuit during turn off Stage IV                                         | 83  |

| Figure.A 15 Further simplified equivalent circuit during turn off Stage IV                      | 83  |

| Figure.A 16 Model validation with double-pulse-test circuit: (a) diagram, (b) prototype1        | 86  |

| Figure.A 17 Turn on/off waveforms comparisons (Blue line: experiment, red line: analytical mode | el) |

| (a) Turn on @10A, (b) Turn off@10A                                                              | 87  |

| Figure.A 18 Efficiency comparison between experimental and calculation results based on               |

|-------------------------------------------------------------------------------------------------------|

| proposed model                                                                                        |

| Figure.A 19 Efficiency comparison between experimental results and calculation results based on       |

| proposed model                                                                                        |

| Figure.A 20 Buck converter loss breakdown based on proposed loss model191                             |

| Appendix B                                                                                            |

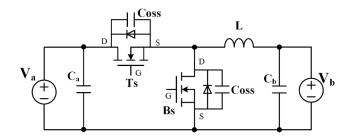

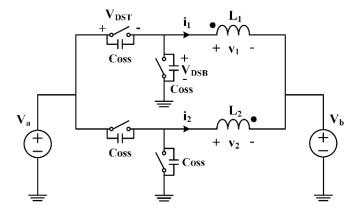

| Figure B. 1 Bidirectional buck/boost converter                                                        |

| Figure B. 2 Key waveforms of CRM operation for buck/boost converter                                   |

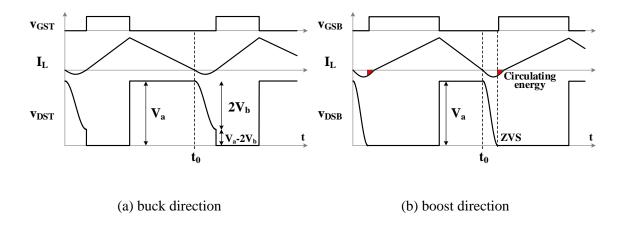

| Figure B. 3 Relationship between T <sub>r</sub> and T <sub>s</sub> in CRM                             |

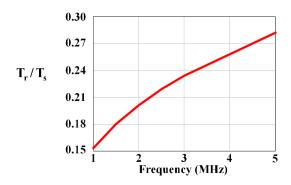

| Figure B. 4 Inductor current rms value increases with frequency in CRM197                             |

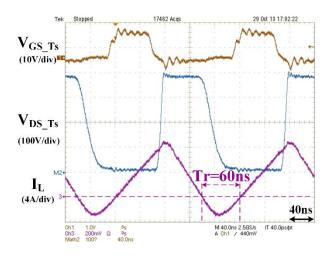

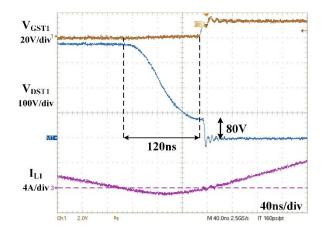

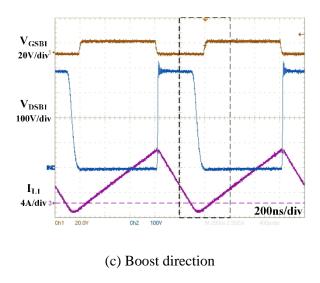

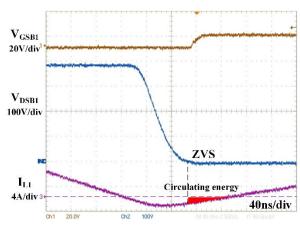

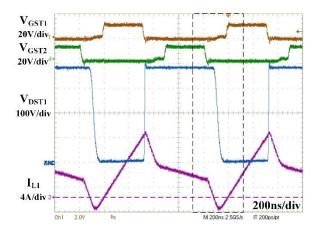

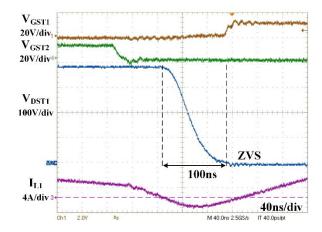

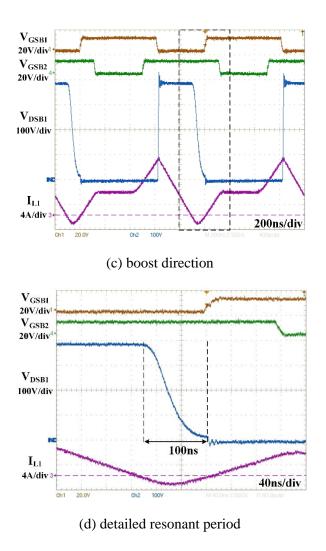

| Figure B. 5 CRM operation experimental waveforms at 5MHz                                              |

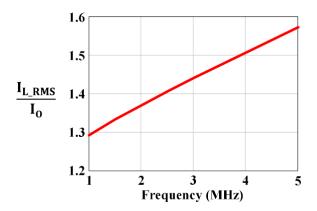

| Figure B. 6 Interleaved buck/boost converter with inverse coupled inductor                            |

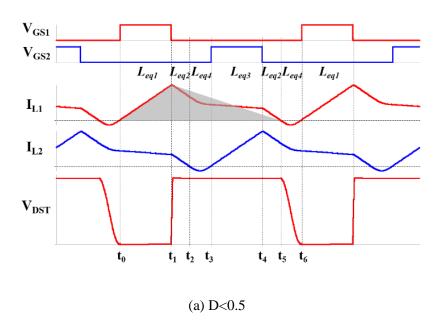

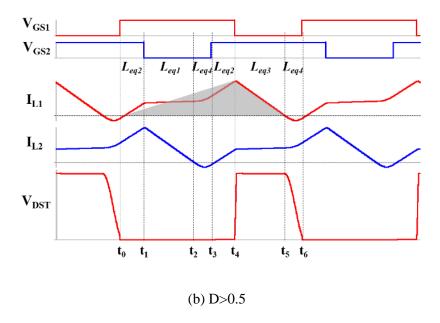

| Figure B. 7 Key waveforms of CRM with coupled inductor considering resonant period200                 |

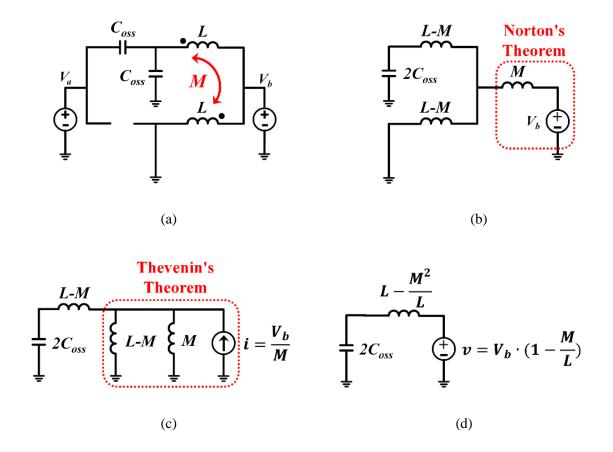

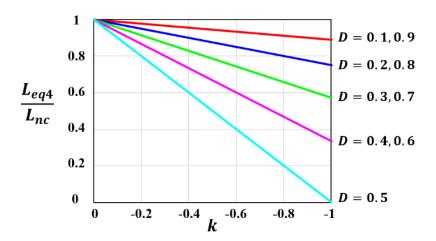

| Figure B. 8 Equivalent inductance derivation via equivalent circuit @D<0.5 (a) Initial circuit during |

| resonant period (b) Decoupled inductor (c) Circuit derivation with Norton's Theorem (d) Circuit       |

| derivation with Thevenin's Theorem                                                                    |

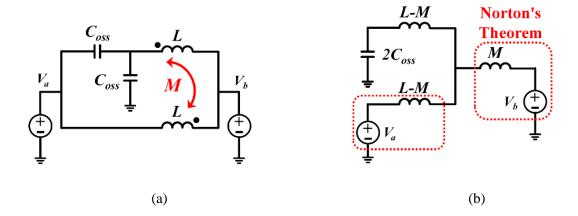

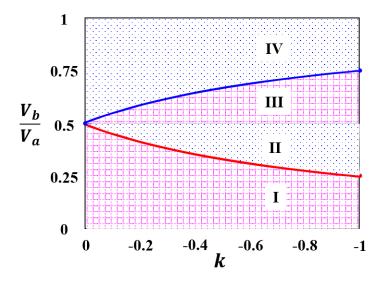

| Figure B. 9 Equivalent inductance derivation via equivalent circuit @D>0.5 (a) Initial circuit during |

| resonant period (b) Decoupled inductor (c) Circuit derivation with Norton's Theorem (d) Circuit       |

| derivation with Thevenin's Theorem                                                                    |

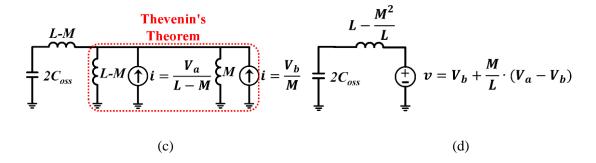

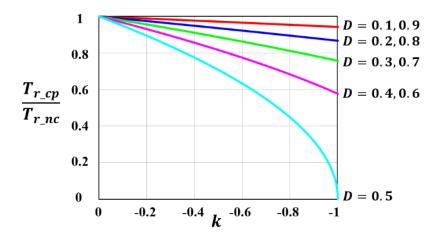

| Figure B. 10 Reduction of resonant inductance with different coupling coefficient and voltage gain    |

|                                                                                                       |

| Figure B. 11 Reduction of resonant period with different coupling coefficient and voltage gain 207    |

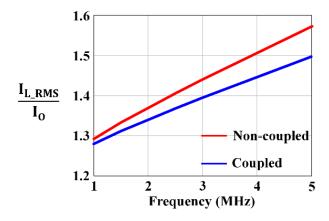

| Figure B. 12 Reduction of inductor current rms value with coupled inductor                            |

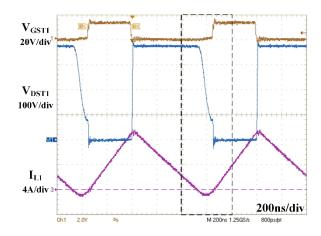

| Figure B. 13 Coupled inductor modifies CRM operation                                                  |

| Figure B. 14 Comparison of coupled and non-coupled inductor                                           |

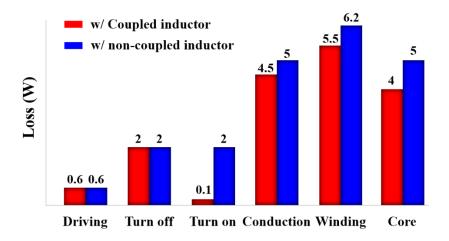

| Figure B. 15 Experimental waveforms of CRM operation with non-coupled inductor214                     |

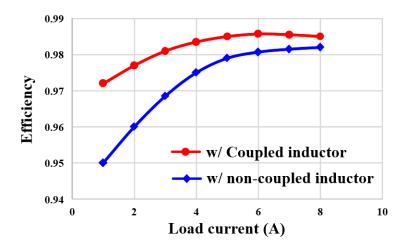

| Figure B. 16 Experimental waveforms of CRM operation with coupled inductor | 216 |

|----------------------------------------------------------------------------|-----|

| Figure B. 17 Loss breakdown of two-phase buck direction at full load       | 217 |

| Figure B. 18 Efficiency comparison over wide load range of buck direction  | 217 |

# List of Tables

| Table 1.1 Material properties of GaN, SiC, and Si                               | 4   |

|---------------------------------------------------------------------------------|-----|

| Table 1.2 Device parameter comparison                                           | 9   |

| Table 2.1 Parasitic inductance of package and PCB layout                        | 23  |

| Table 2.2 Package-related parasitic inductance values                           | 33  |

| Table 2.3 Parasitic inductance of different packaging                           | 59  |

| Table 3.1 Commercial high side gate driver                                      | 80  |

| Table 4.1 High frequency Core Material Comparison                               | 97  |

| Table 4.2 Parameters of the one-stage EMI filter                                | 118 |

| Table 4.3 Parameters of the EMI filter for 150W prototype                       | 152 |

| Appendix B                                                                      |     |

| Table B. 1 Coupled inductor equivalent inductance <sup>[15]</sup>               | 200 |

| Table B. 2 Comparison between non-coupled inductor and inverse coupled inductor | 205 |

# **Chapter 1. Introduction**

This chapter presents the motivations, objectives and overview of this dissertation. The advantages and challenge of gallium nitride (GaN) devices are described and the potential applications are investigated. A review in this field is provided, followed by the dissertation outline and the scope of research.

# 1.1 Background and Motivation

IT industry is growing rapidly in the last three decades. The microprocessors, which is also known as the central processing unit or CPU, are the key component in most of the applications such as computer systems and portable devices. To achieve better performance, more transistors are being integrated into the microprocessor.

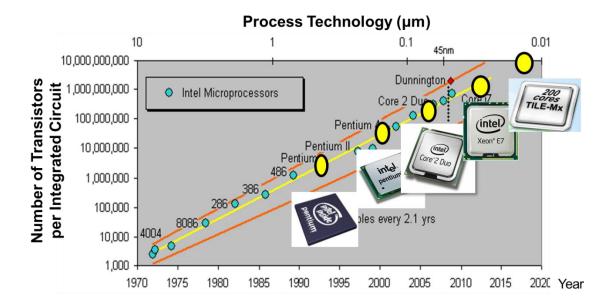

Figure 1.1 Roadmap of Intel microprocessors

Figure 1.1 shows the CPU integrated transistor counts against the dates of introduction. The yellow line is the exponential growth with transistor counts doubling every two years, which is known as the Moore's law. Since the introduction of the high performance Pentium series CPU in the middle of 90s, Intel is still able to follow Moore's law up to date. It is even exciting that Tilera corp., another CPU manufacturer, announced that they are developing 200 cores processor in one chip. The advance of the processor has significant impact on the electronics equipment. It is noticeable that the progress of all forms of mobile devices are progressing at an amazing rate with ever increasing performances and shrinking in size and weight, while their power supply counterparts are bulky with meager power density. For example, the latest MacBook Air laptop is more than 10 times faster than the first generation and its weight reduces to 2.4lb now, while the accompanying 45W adapter remains the same form factor and it weighs 0.4lb. Moreover, the manufacturing and the assembly process for adapter remains labor-intensive.

High performance active semiconductor devices have always been the first force to improve efficiency and power density of modern power conversion system. Since its introduction in the mid-1970s, the silicon (Si) MOSFET, with its greater switching behavior, has replaced the bipolar transistor. To date, the Si MOSFET has been optimized up to its theoretical limit, even beyond the limit, e.g. super junction devices and IGBTs [A.1], [A.2]. The device optimization innovations may continue for quite some time and certainly will be able to leverage the low cost structure of the power MOSFET and knowhow of a well-educated base of designers who have learned to squeeze every ounce of performance out of their power conversion circuits and systems [A.3].

The Si MOSFET devices switching loss (majorly turn-on loss) can be further reduced

with soft-switching technique. However, the gate drive loss, turn-off switching loss and circulating conduction loss for soft-switching are still excessive, which limit the switching frequency to few hundreds of kilohertz (kHz) in most applications.

The GaN power devices first appeared in about 2004 and are designed for radio frequency (RF) amplifier [A.4]. Even though GaN devices are still in the early stage, the figure of merit (FOM) improves significantly with 10 years development, and they are far better than the state-of-the-art Si MOSFETs. GaN devices are capable to operate at a switching frequency 10 times higher than Si MOSFET, and therefore, this can significantly impact the power density of power converters, their form factor, and even current design and manufacturing practices.

To realize the benefits of GaN devices resulting from significantly higher operating frequencies, a number of issues have to be addressed, such as converter topology, softswitching technique, gate driver, high frequency magnetics, packaging, control, and thermal management. Some of the key issues are recognized by the author and are addressed in this work.

### 1.2 Overview of GaN Power Devices

### **1.2.1 Why GaN**

The advance of GaN devices stems from the basic physical properties of GaN material compared with other semiconductor material, such as Si and SiC. Table 1.1 identifies the key electrical properties of the three materials which have been considered as the success candidate in power electronics field [A.3], [A.5]. It is worthwhile to point out that 4H-SiC is dominant polytype among all SiC polytypes due to identical mobilities in the two planes

of the semiconductor [A.6].

Table 1.1 Material properties of GaN, SiC, and Si

| Properties                                              | GaN   | 4H-SiC | Si   |

|---------------------------------------------------------|-------|--------|------|

|                                                         |       |        |      |

| Bandgap, $E_g(eV)$                                      | 3.39  | 3.26   | 1.12 |

|                                                         |       |        |      |

| Breakdown field, E <sub>crit</sub> (MV/cm)              | 3.3   | 2.2    | 0.23 |

|                                                         |       |        |      |

| Saturated drift velocity, Vs (10 <sup>7</sup> cm/s)     | 2.5   | 2.0    | 1.0  |

|                                                         |       |        |      |

| Electron mobility, μ <sub>n</sub> (cm <sup>2</sup> /Vs) | 2000* | 650    | 1500 |

| 3,712(*****)                                            |       |        |      |

| Thermal conductivity, λ (W/cm·K)                        | 1.3   | 1.5    | 3.8  |

|                                                         | ,_    |        | •    |

GaN and SiC have much higher bandgap energy which means capability of higher temperature operation. GaN has highest electrical breakdown field which results in power devices with higher breakdown voltage. Consequently, the die of power devices could be smaller with given breakdown voltage. The drift velocity of GaN is more than twice the drift velocity of Si, therefore, it is expected that GaN devices could be switched at higher frequencies than their Si counterparts.

More vivid way of translating these basic crystal parameters into a comparison of device performance is to calculate the best theoretical performance that could be achieved in each of these candidates. The theoretical on-resistance of each candidate can be calculated as [A.5]

$$R_{on} = \frac{4V_{BR}^2}{\varepsilon_s \mu_n E_{crit}^3} \tag{1.1}$$

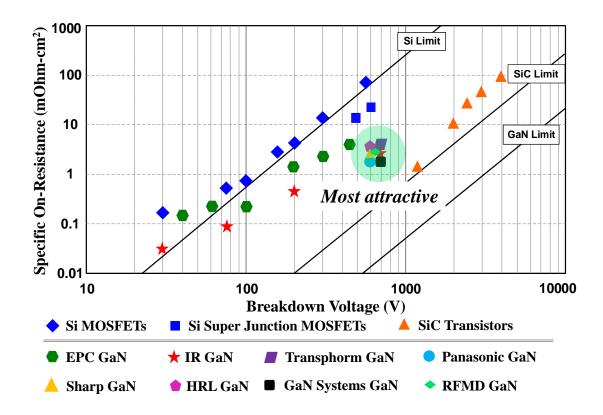

where  $V_{BR}$  is desired breakdown voltage,  $\mathcal{E}_{S}$  is the dielectric constant,  $E_{crit}$  is the electric breakdown field and  $\mu_{n}$  is the electron mobility. This equation can be plotted as shown in Figure 1.2. The theoretical limit of GaN is at least three order of magnitude lower than that of Si.

Figure 1.2 Specific on-resistance vs breakdown voltage for Si, SiC, GaN

Due to continuous device optimization and improvement in the production process, the Si devices are very close to the theoretical limit. Workarounds like the super junction stretch the limits but usually at substantial cost. SiC devices are booming since late 1990s and they are majorly targeting at high-voltage and high-temperature applications due to high critical field and thermal conductivity [A.7], [A.8]. The commercial SiC device are typically rated higher than 1.2 kV with maximum 200°C junction temperature. Another

concern about SiC devices is the cost which prevents wide adoption of SiC in IT industry and consumer electronics.

The first generation of GaN HEMTs, which target at the field of power electronics, have proved that the GaN HEMT has a superior relationship between the on resistance and breakdown voltage than the Si MOSFET due to a higher electrical field strength and enhanced mobility of electrons in the two dimensional electron gas (2DEG) [A.9]. This translates into a GaN HEMT with a smaller die size for a given R<sub>ds\_on</sub> and breakdown voltage which directly increases power density. Among all the voltage rating GaN devices, 600V parts are deemed to be most attractive to device manufacturers, which reflects a huge market of AC-DC and DC-DC power supplies for a wide range applications. The research in this work is also focus on 600V GaN devices and the applications for high efficiency and high density power conversion.

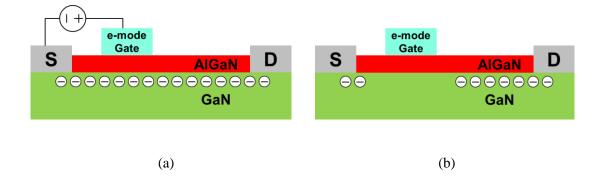

## 1.2.2 Enhancement Mode and Depletion Mode GaN Devices

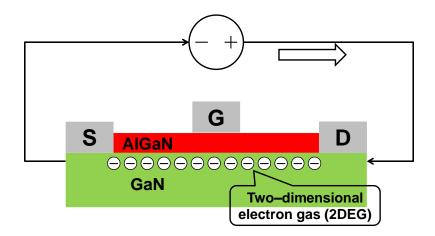

Figure 1.3 shows the typical GaN device structure including the 2DEG at the junction of the AlGaN-GaN boundary in which the electrons have extremely high mobility that produces the low on resistance [A.3]. According to different gate structure, GaN devices can be divided into two categories, depletion-mode (d-mode) and enhancement-mode (e-mode) GaN device.

Figure 1.3 Basic structure of GaN device

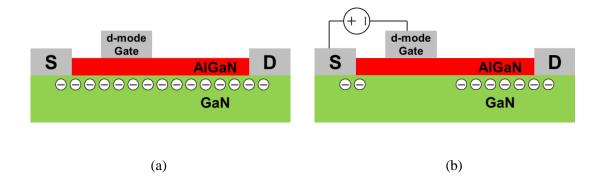

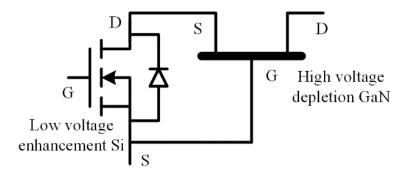

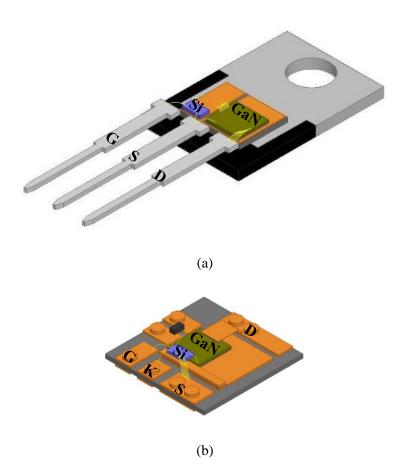

The d-mode GaN is more nature based on the GaN device crystal structure [A.5]. The device is normally on without applied gate voltage, as shown in Figure 1.4 (a). A negative voltage is necessary to turn off the d-mode GaN device, which makes it inconvenient for circuit design especially at the power converter startup period. To solve this issue, a low voltage Si MOSFET is used in series to drive the GaN device which is well known as cascode structure, and is shown in Figure 1.5 [A.10].

Figure 1.4 Basic structure of d-mode GaN device, (a) on state, (b) off state

Figure 1.5 Cascode GaN: a d-mode GaN in series with a low voltage Si MOSFET

On the other hand, several techniques have been developed to provide a built-in modification of the 2DEG at the gate electrode. There are three popular gate structures that have been used to create e-mode GaN device: recessed gate [A.11], implanted gate [A.12], and pGaN gate [A.13][A.14]. Different from the d-mode GaN device, the e-mode GaN device is in off state if no external V<sub>gs</sub> applied, while it is turned on with a positive V<sub>gs</sub>, as shown in Figure 1.6. One of the desirable common features for e-mode GaN devices is gate overdrive protection. The driving safety margin of commercial available e-mode GaN is quite small, which requires a dedicated gate drive design [A.15], [A.16], [A.17].

Figure 1.6 Basic structure of enhancement mode GaN device, (a) on state, (b) off state

### 1.2.3 Steady-state Characteristics of 600V GaN Devices

Table 1.2 lists commercial available GaN devices and a state-of-the-art Si MOSFET with similar on resistance. The devices parameters clearly show that GaN devices have much smaller  $Q_g$  (4~10 times reduction) and  $C_{oss}$  (2~6 times reduction), which indicates higher frequency operation capability. It is interesting to notice that commercial available e-mode GaN device has better parameters than d-mode GaN in cascode configuration. To the best of the author's knowledge, it is possibly caused by different manufactory process.

As listed in table 1.2, e-mode GaN has lower threshold voltage compared to cascode GaN which actually is a Si MOSFET gate. The required gate drive voltage of e-mode GaN to fully turn on the device is very close to the maximum allowed gate voltage, while cascode GaN has a larger driving safety margin due to Si MOSFET gate.

Table 1.2 Device parameter comparison

|                              | E-Mo      | de GaN      | Cascode GaN   |            | Si MOSFET   |

|------------------------------|-----------|-------------|---------------|------------|-------------|

|                              | Panasonic | GaN Systems | Infineon / IR | Transphorm | Infineon    |

|                              | PGA26E19  | GS66504P    | XIRGAN60S002  | TPH3206    | IPX60R165CP |

| $R_{ds\_on} (m\Omega)$       | 154       | 110         | 135           | 150        | 150         |

| C <sub>oss_tr</sub> (pF)     | 34        | 72          | 84            | 105        | 220         |

| Q <sub>g</sub> (nC)          | 4         | 3.3         | 8.8           | 6.2        | 39          |

| V <sub>GS_max</sub> (V)      | -10~4.5   | ±10         | ±20           | ±18        | ±20         |

| V <sub>TH</sub> (V)          | 1.2       | 1.6         | 5             | 2.1        | 3           |

| Required V <sub>GS</sub> (V) | 3         | 7           | 10            | 8          | 10          |

| I <sub>DSS</sub> (μA)        | 35        | 200         | 115           | 8          | 10          |

Another critical parameter is leakage current (I<sub>DSS</sub>), which is a significant source of power loss at light load or standby condition. The GaN device from Transphorm has a smaller leakage current even compared with Si MOSFET. The GaN devices from other manufacturers have larger leakage current. The data is a sign of the relative immaturity of GaN technology. It is believed that GaN devices will mature to the point where the leakage current is well controlled.

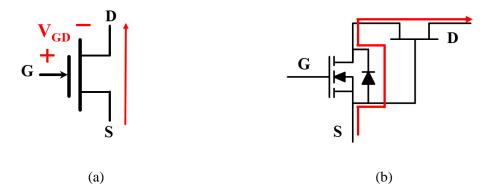

#### 1.2.4 Reverse Conduction of GaN Devices

GaN devices have the bi-directional current flow capability in nature due to physical structure. While the reverse conduction principle of e-mode and cascode GaN devices are different.

E-mode GaN can conduct in the reverse direction when the drain voltage is lower than the gate by at least  $V_{TH}$ , as shown in Figure 1.7 (a). The voltage drop  $V_{SD}$  is determined by the reverse current  $I_{SD}$ , transconduction  $g_m$ , threshold voltage  $V_{TH}$ , and applied gate-source voltage  $V_{GS}$ , as given by (1.2). It is obvious that  $V_{SD}$  increase with  $I_{SD}$  and the first term is considerable even at low current due to the non-linearity of  $g_m$ . It should be pointed out that  $V_{SD}$  increases significantly if  $V_{GS(off)}$  has initial negative bias in off state.

Figure 1.7 Reverse conduction of e-mode GaN devices: (a) e-mode GaN, (b) cascode GaN

$$V_{SD} = \frac{I_{SD}}{g_m} + V_{TH} - V_{GS(off)}$$

(1.2)

The cascode GaN has a different mechanism of reverse conduction. The body diode of Si MOSFET is conducting the reverse current and the GaN gate-source voltage is clamped by the diode forward voltage drop. The d-mode GaN is fully turned on and the GaN on resistance is added to the total voltage drop of reverse conduction, which is given in (1.3).

$$V_{SD} = V_{bd\_Si} + I_{SD} \cdot R_{DS\_GaN} \tag{1.3}$$

The voltage drop of cascode GaN is slightly lower than e-mode GaN due to different mechanism. However, they are both higher than Si MOSFET and they may lead a higher conduction loss in certain power conversion circuits. This issue can be partially solved by optimizing dead-time [A.18], [A.19].

# 1.3 Challenges of GaN devices

The GaN devices parameters are so superb and it may lead an illusion to circuit designer that the circuit performance can be significantly improved by simply plugging and replacing Si MOSFET. However, researchers found out that the circuit performance may be worse or even not work with GaN devices without deeply understanding the technical challenges raised by GaN [A.20]. These challenges includes dynamic switching behavior, packaging impact and high frequency gate driver, etc.

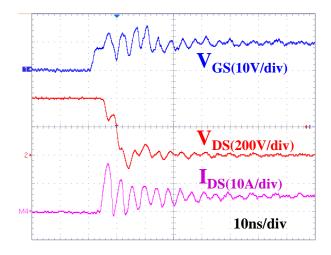

### 1.3.1 Switching Characteristics

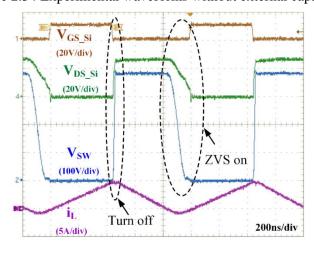

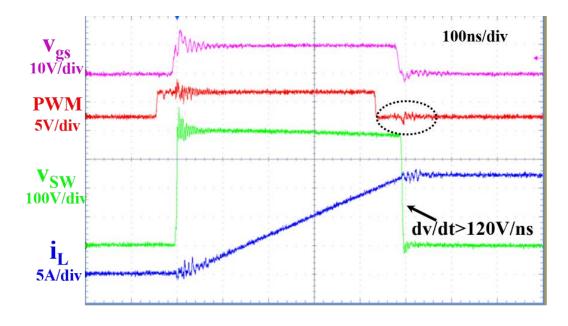

The switching speed of GaN devices are extremely fast that create significant parasitic ringing in hard-switching condition, as shown in Figure 1.8. High frequency ringing causes significant power loss as well as severe EMI noise. Soft-switching should be investigated both from loss and noise perspective.

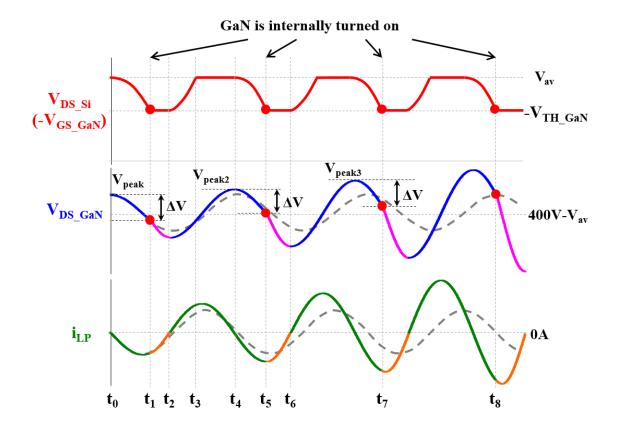

Figure 1.8 Hard-switching turn-on transient of GaN device

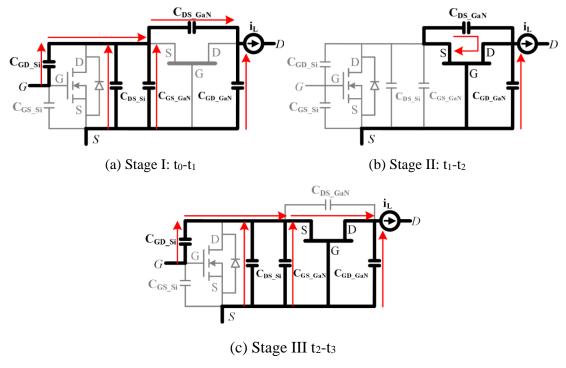

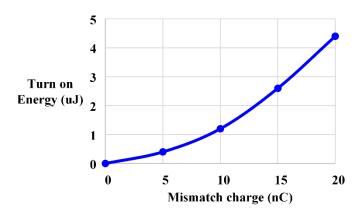

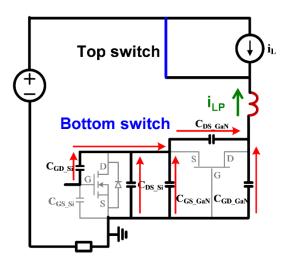

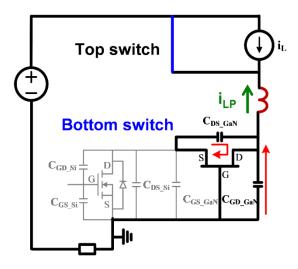

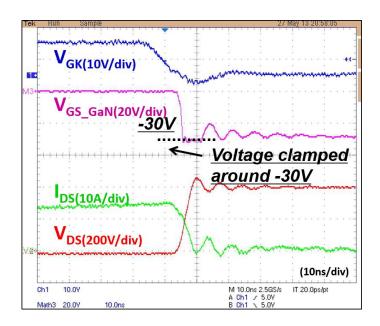

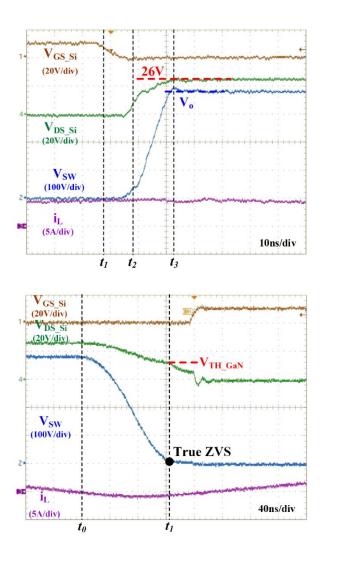

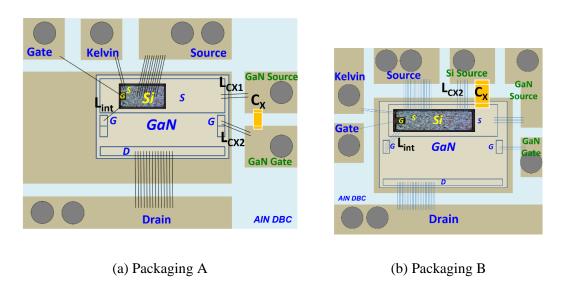

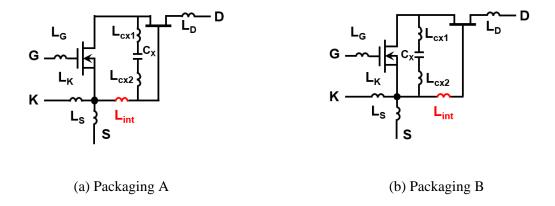

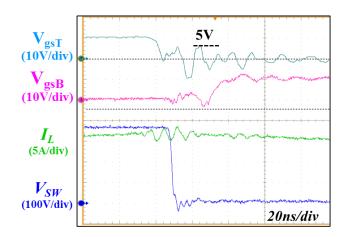

The cascode GaN devices have special switching characteristics due to two-discrete dies in one package. The interaction between the d-mode GaN and the low voltage Si MOSFET may induces undesired features, such as Si MOSFET reaches avalanche during turn-off transition, and d-mode GaN device loses zero-voltage turn-on condition internally during soft-switching turn-on process in every switching cycle. The worst occasion is that the cascode GaN may be subject to divergent oscillation under high-current turn-off condition. These phenomenon should be carefully studied to improve switching performance and avoid device failure.

### 1.3.2 Package Impact on Switching Behavior and Gate Reliability

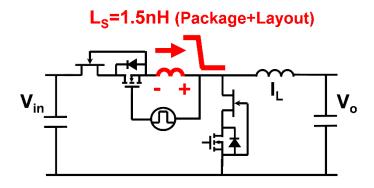

The impact of device packaging has been studied in depth on Si MOSFET, SiC, and low voltage eGaN FET [A.20], [A.22], [A.23]. Package becomes very important to GaN devices with high switching speed. The package parasitic may hinder the switching transition and even generates severe ringing which can destroy the device [A.21]. However, some of the GaN devices manufacturers, who seek for simple replacement of Si devices, are still fabricating devices with long-lead through-hole package.

The common source inductance, which is defined as the inductor shared by the power loop and driving loop has a significant inpact on the switching loss. The power loop inductance plays an important role on the voltage and current ringing after the switching transition. The high voltage e-mode GaN is similar to Si MOSFET or SiC devices in terms of packaging structure, but with much higher switching speed. The cascode GaN has two dies in one package which introduces more package related parasitic inductance. It is essential to investigate the package of GaN for both e-mode GaN and cascode GaN devices to achieve minimum switching loss and less parasitic ringing.

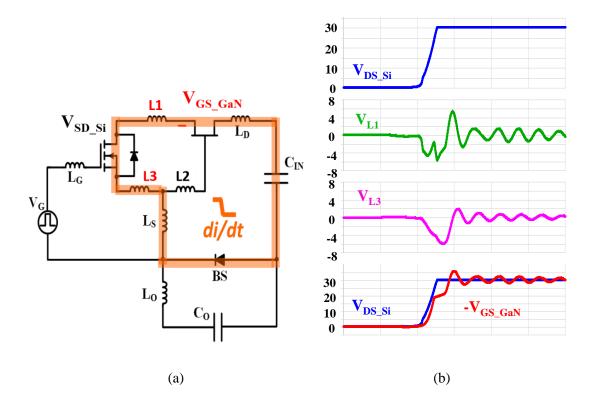

### 1.3.3 High dv/dt and di/dt

GaN devices have a much lower gate charge and lower output capacitance than Si MOSFETs and, therefore, dv/dt and di/dt during switching transition is 3-5 times higher than that of Si MOSFETs.

Di/dt may induce an opposing voltage drop on the common source inductance which prevents either turn-on or turn-off from the gate drive circuit. It is strongly related to devices packaging and PCB layout. Dv/dt can couple through any parasitic capacitance

from switching node to ground. It may interference input PWM signal and cause false on/off issue. These issues have to be addressed to avoid becoming a limiting factor on circuit design.

# 1.4 Impact of GaN Devices on System Level Design

The potential impact of GaN goes beyond the simple measures of efficiency and power density. It is feasible to design a system with a more integrated approach at higher frequencies, and therefore, it is easier for automated manufacturing. This will bring significant cost reductions in power electronics equipment and unearth numerous new applications which have been previously precluded due to high cost.

## 1.4.1 High Frequency Magnetics

The traditional magnetic design is in hand-made fashion which is intensive labor involved manufacturing process. The cost is a concern and the parameter variation is another circuit design issue. PCB winding based transformer is only feasible when the switching frequency is over several hundreds of kHz due to less turns number and smaller core size. The leakage inductance and parasitic capacitance of transformer can be well controlled by PCB manufacture.

Generally speaking, GaN offers an opportunity to design the high frequency magnetics in a different way. Some key factors requires to be taken into considerations, such as high frequency core material, winding structure and fringing effect [A.24], [A.25], [A.26].

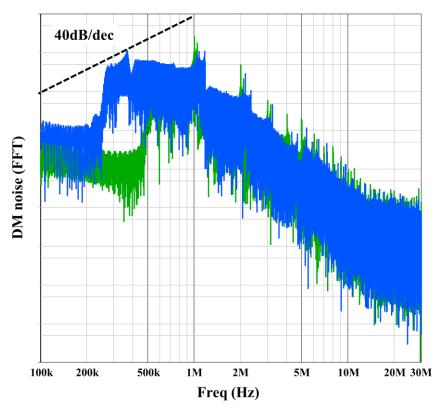

### 1.4.2 High Frequency EMI

GaN devices are double-edged sword from EMI perspective. High switching speed creates high dv/dt which increases the common-mode noise and corresponding filter size. High switching frequency, however, increases the corner frequency of the EMI filter, which reduces the EMI filter size. The concern is generally true with the system that is constructed with traditional magnetic design. However, the common mode noise can be significantly reduced by CPES developed balance technique [A.27], [A.28] and shielding technique [A.29]. The implementation of advanced EMI reduction technique and related system impact should be carefully investigated in different applications. In addition, the EMI filter structure and core material are crucial to achieve optimal performance, which should be carefully studied.

## 1.4.3 High Frequency control

To realize MHz frequency operation, the high frequency control is one of the most important factors, especially in soft-switching operation. It is crucial to detect soft-switching condition with minimal delay and generates precise PWM signal accordingly. There is no commercial control chip for front-end application that can operates above 1MHz. It is meaningful to implement the high frequency control concept with low-cost micro-controllers, which can be integrated to analog or mixed analog-digital control chip later on.

# 1.5 GaN Based Applications

GaN devices are already making inroads which stem directly from the improvements in figure of merits (FOM) over Si MOSFET. The applications includes point-of-load converters [A.18], [A.19], [A.20], [A.30], [A.31], class-D audio amplification [A.32], power factor correction [A.33][A.34][A.35][A.36], bus converter [A.37], motor drive [A.38], and PV inverters [A.39]. Additionally, GaN devices enable new applications that are not possible with Si MOSFET, such as envelope tracking [A.40], high frequency wireless power transfer [A.41] and LiDAR [A.3].

One of the biggest market of power supplies, in both volume and revenue, is the ac-dc adapter/charger for consumer electronics. The market is projected to surpass \$8 billion in 2015 and reach \$9 billion by 2018; with much of this growth being driven by smart phones, tablets and a number of emerging applications. The adapter is strongly driven by efficiency and power density for all forms of portable electronics. Most adapters only operate at relatively low frequencies (<100 kHz), with state-of-the-art efficiency up to 91.5%. However, low-frequency operation limits the adapter power density to 6-9 W/in<sup>3</sup>. The emerging GaN device is deemed a game-changing device in this particular application, with improved efficiency and significant size reduction. Systematic design of adapters with different output power will be illustrated in this work to show the advance of GaN devices and the impact on system level.

### 1.6 Dissertation Outline

Taking into account the challenges associated with GaN devices as well as the impact

on system level design practice, several issues have been addressed in this dissertation.

Chapter 1: Research background, motivation, and literature review.

Chapter 2: Switching characterization of GaN devices, including packaging impact

and special issues in cascode GaN devices. The switching loss mechanism of both e-mode

and cascode GaN devices will first be explained and compared; then the package impact

on switching performance of GaN device will be illustrated in details. The special issues

in cascade GaN devices caused by capacitance mismatch are analyzed in detail and

corresponding solutions are validated with numerous experiments.

Chapter 3: Design considerations of GaN devices. A thorough comparison of hard-

switching and soft-switching is made which indicates that GaN devices still need soft-

switching to fully explore potential. High frequency gate drive design for GaN devices to

achieve high switching speed and handle high dv/dt and di/dt is presented.

Chapter 4: Application of GaN devices in AC-DC adapters. It will focus on the

topology, high frequency transformer design, EMI characterization and high frequency

control (majorly for ZVS achievement).

Chapter 5: Conclusion and future work.

# Chapter 2. Switching Characterization of GaN

# **Devices**

Understand the switching characteristics of GaN switches, is essential to use GaN devices in circuit design correctly and efficiently. In this chapter, the switching loss mechanism of both e-mode and cascode GaN will first be explained and compared; then the package impact on switching performance of GaN device will be illustrated in details; finally, the special issues of cascode GaN devices are discussed and proposed solution is validated by experiments.

# 2.1 Switching Loss Mechanism Analysis of GaN Devices

#### 2.1.1 GaN device loss model

The fast switching ability of GaN devices will certainly reduce switching related loss compared to Si MOSFET. However, the switching voltage and current have more ringing due to high dv/dt and di/dt across the parasitics, shown in Figure 1.8, which may generate additional loss. More importantly, the switching loss analysis is highly desirable for predicting maximum device junction temperature and overall power converter efficiency.

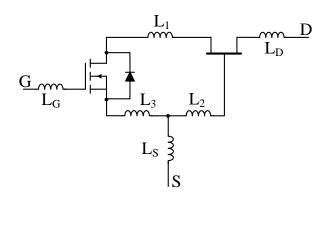

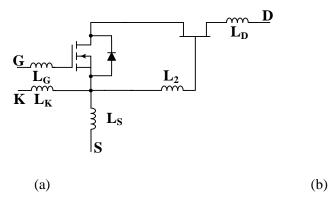

Device manufacturer usually provides a Pspice based simulation model for simple circuit level simulation. However, this kind of model is lack of accuracy in terms of neglecting packaging and PCB layout related parasitic inductance. Taking a cascode GaN device from Transphorm as an example, the package introduces six pieces of parasitic inductance as shown in Figure 2.1. Moreover, as the currents with fast transitions are

confined in such a small area, the coupling effects between different conductors are significant. The coupling coefficients of  $L_1$  with the other inductances are labeled in Figure 2.1(b). The methodology of parasitic inductance extraction of the cascode GaN device is summarized in [B.1].

(a) Simplified bonding diagram of a cascode GaN device

(b) Equivalent circuit of cascode GaN considering all parasitic inductance

Figure 2.1 Packaging parasitics of a cascode GaN device

The comparison of switching waveforms based on manufacturer original model and modified model are shown in Figure 2.2. It clearly shows that the voltage and current ringing amplitude and slew rate are completely misaligned. It indicates the inaccuracy of the system parasitics, which include the device parasitics. With parasitic extraction of the device and PCB layout, the model presented in Figure 2.2(b) can effectively reproduce the experimental waveforms.

Figure 2.2 Comparison of switching waveforms w/ original model and modified model

The author has also developed a mathematical based analytical model [B.2], which is based on device physical parameters listed in datasheet. It is independent of Pspice simulation model and can be applied to any devices. Moreover, analytical model separate

transition into several sub-stages, which helps engineers to better understand the physical meaning of device operation.

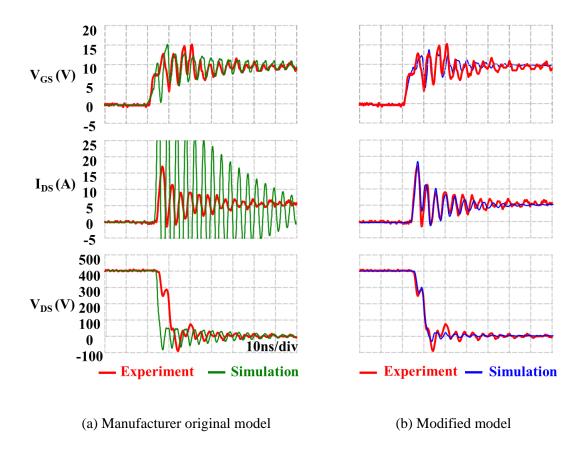

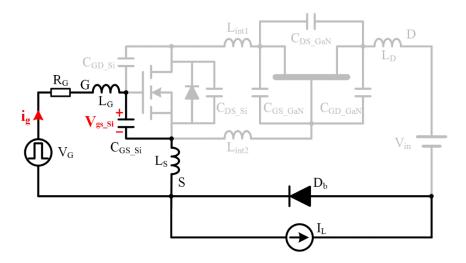

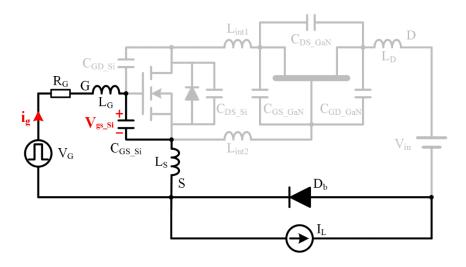

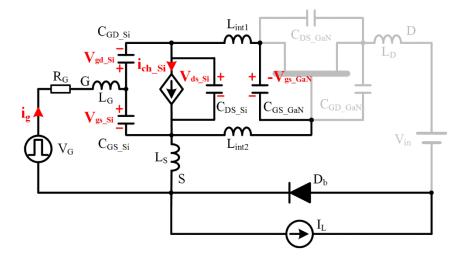

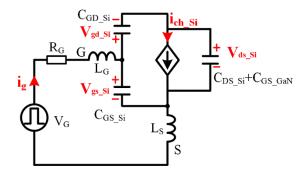

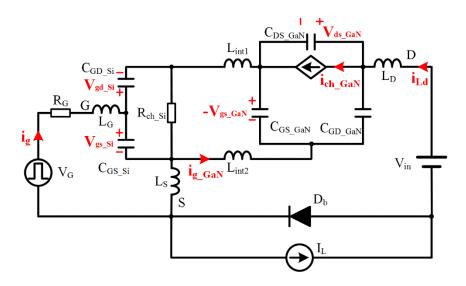

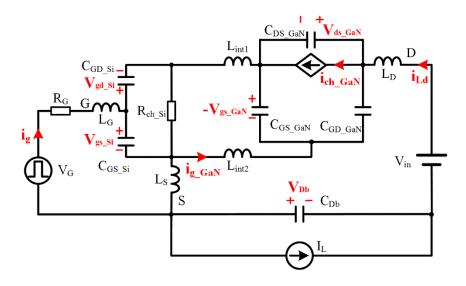

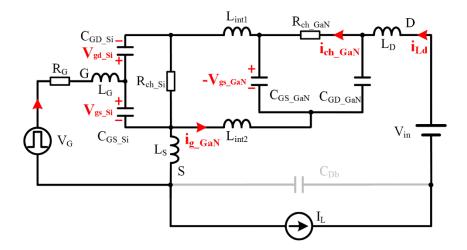

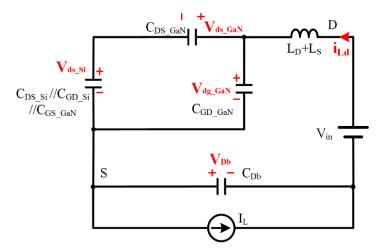

In order to show the derivation process of analytical model, the first stage of turn on transition of a cascode GaN in a buck converter is shown in Figure 2.3. More details about GaN device analytical loss model are illustrated in Appendix I. When the gate voltage V<sub>G</sub> is applied, the resultant gate current charges the gate-source equivalent capacitance. In fact, C<sub>GS\_Si</sub> is much larger than any of the other capacitors in the cascode GaN transistor, thus the majority of the gate current charges C<sub>GS\_Si</sub>. As the GaN and silicon MOSFET are open circuit, almost no drain current flows into this circuit. During this period, the power stage does not change and current source I<sub>L</sub> keeps flowing through D<sub>b</sub>. Based on the equivalent circuit, the following equations are obtained:

Figure 2.3 Equivalent circuit during the first stage of turn on transition

$$V_G = (L_G + L_S) \frac{di_g}{dt} + R_G \cdot i_g + v_{gs\_Si}$$

(2.1)

$$i_g = C_{GS\_Si} \frac{dv_{gs\_Si}}{dt} \tag{2.2}$$

The Laplace and inverse Laplace transforms are applied to solve the differential equations. The silicon MOSFET gate-source voltage  $v_{gs\_Si}(t)$  is shown below. This stage ends when  $v_{gs\_Si}$  reaches the threshold voltage of silicon MOSFET  $V_{TH\_Si}$ .

$$v_{gs\_Si}(s) = \frac{1}{s} \cdot \frac{V_G}{s^2 \cdot (L_G + L_S)C_{GS\ Si} + s \cdot R_G C_{GS\ Si} + 1}$$

(2.3)

$$v_{gs\_Si}(t) = V_G \cdot \left(1 - \frac{s_{11}e^{s_{12}t} - s_{12}e^{s_{11}t}}{s_{11} - s_{12}}\right)$$

(2.4)

where

$$s_{11} = \sqrt{\frac{1}{4} \left(\frac{R_G}{L_G + L_S}\right)^2 - \frac{1}{(L_G + L_S)C_{GS\_Si}}} - \frac{R_G}{2(L_G + L_S)}$$

,  $s_{12} =$

$$-\sqrt{\frac{1}{4}(\frac{R_G}{L_G+L_S})^2-\frac{1}{(L_G+L_S)C_{GS\_Si}}}-\frac{R_G}{2(L_G+L_S)}.$$

In order to verify the analytical model, two sets of experiments are carried out: a double-pulse test to compare the waveforms, and a buck converter to validate the switching loss. Common sense would dictate that the common source inductance, which is defined as the inductor shared by the power loop and driving loop, has a significant impact on the switching loss. In addition, the power loop inductance plays an important role in the switching performance. Therefore, the PCB is designed to eliminate the common source inductance (excluding package inductance) and to minimize the power loop inductance. The package and layout inductance are extracted from Ansoft Q3D FEA simulation and the value is summarized in Table 2.1. The PCB layout parasitic inductance is lumped together as two parts: one is the driving loop inductance, and the other is power loop inductance. The double pulse test circuit has larger power loop inductance since the current shunt introduces extra inductance and the PCB layout adds more inductance to accommodate the current shunt.

Table 2.1 Parasitic inductance of package and PCB layout

|                   | $L_{Dri\_Loop}$ | $L_{Power\_Loop}$ |

|-------------------|-----------------|-------------------|

| Double-pulse test | 3.3nH           | 7.7nH             |

| Buck Converter    | 3.3nH           | 3.7nH             |

Figure 2.4 shows the double-pulse-test circuit diagram and prototype. The main switch is a 600V cascode GaN transistor, and terminal voltage  $v_{ds}$  and current  $i_{ds}$  are recorded to compare with the calculation results. The freewheeling diode is a 600V GaN Schottky diode with no reverse recovery charge. Both of these GaN devices are from Transphorm Inc. The current waveform is measured by a coaxial shunt resister with high bandwidth and minimized parasitic inductance.

Figure 2.5 shows waveform comparisons between the double-pulse-test and the calculated results of the proposed analytical model during the transition period. The figure clearly shows that the analytical model can match with the experiments on the voltage and current slope, as well as the magnitude and main transition time. The oscillation frequency and damping effect have some differences due to inaccurate high frequency parasitic inductance and AC resistance. As the value of the parasitic inductance and AC resistance is influenced by several factors, including conductor position, current direction and oscillation frequency, which are difficult to be predicted

Figure 2.4 Model validation with double-pulse-test circuit: (a) diagram, (b) prototype

Figure 2.5 Turn on/off waveforms comparisons (Blue line: experiment, red line: analytical model)

(a) Turn on @10A, (b) Turn off@10A

The second method used to validate the accuracy of the proposed analytical model is to observe the converter efficiency over a wide load range. A 500 kHz 380V/200V continues current mode (CCM) buck converter is built using a cascode GaN transistor as

the top and bottom switch. In the calculation terms, the inductor loss is measured by Mu's method [B.3]. The conduction loss is calculated based on the steady state current and on-resistance, which takes the temperature coefficient into consideration. The driving loss can be approximately calculated as:

$$P_{dri}(t) = Q_a V_G F_S (2.5)$$

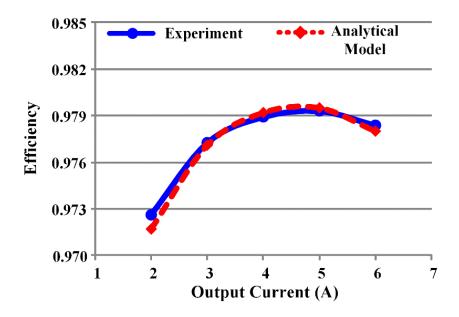

Figure 2.6 shows the converter efficiency comparison between the experimental results and the calculation results based on the proposed model. The calculated efficiency matches well with the experimental results over a wide load range. The difference is within 0.1%.

Figure 2.6 Efficiency comparison between experimental and calculation results based on proposed model

As the accuracy of the model is validated by numerous experimental results, then the model can be applied to analyze the switching loss mechanism of GaN devices.

#### 2.1.2 Turn-on transition

It is noticed that the switching behavior of e-mode GaN switches is quite similar with

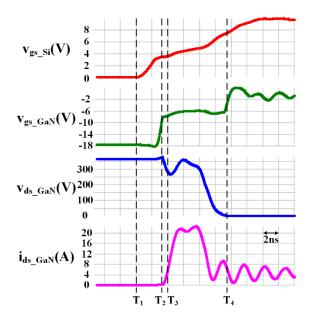

Si MOSFET except for the much higher switching speed. The detailed analysis can refer to literature [B.4]. On the other hand, the study on the switching behavior of cascode GaN is less comprehensive. To better illustrate the switching loss mechanism of the cascode GaN switch, typical turn-on switching waveforms of the control switch in a half-bridge configuration based circuit, which are derived from the device model, are shown in Figure 2.7.

Figure 2.7 Hard-switching turn-on waveforms

$V_{gs\_Si}$  is the gate-source voltage of the low voltage silicon MOSFET in the cascode structure. The other three waveforms are the gate-source voltage, drain-source voltage and drain-source current of the GaN HEMT in the cascode structure. The switching loss of the low voltage silicon MOSFET is negligible, which is true in this condition. At  $T_1$  instant, the gate voltage is applied to the silicon MOSFET. Then  $V_{gs\_Si}$  is charged up and the channel becomes conductive. The gate-source voltage of the GaN HEMT which is in reverse parallel with the drain-source voltage of the silicon MOSFET, is charged towards

the threshold voltage. At T<sub>2</sub> instant, the GaN HEMT is conductive and i<sub>ds GaN</sub> starts to increase. At T<sub>3</sub> instant, the GaN HEMT current reaches the inductor current and then the GaN HEMT current supports both inductor current and reverse recovery charge current of free-wheeling switch during T<sub>3</sub> to T<sub>4</sub>. During this period, the current overshoot is huge and it may saturates the channel as the GaN HEMT is not yet fully turned on in normal cases. Therefore, V<sub>ds\_GaN</sub> increases instead of decreases in the first half of this stage. In fact, this phenomenon can also be observed with standalone switch under high voltage test condition [B.5], [B.6]. Eventually the voltage across free-wheeling switch is charged up with the overshoot current of the control switch, and this allows the V<sub>ds\_GaN</sub> to be decreased to zero. The integral of voltage and current during the turn-on transition generates switching loss, which is in the magnitude of tens of uJ. This becomes significant at MHz frequency operation. It is worthwhile to point that the cascode GaN switch has some reverse recovery charge due to the series low voltage silicon MOSFET. However, the value of this charge is at least two orders of magnitude less than the comparable high voltage silicon MOSFET that has a similar on-resistance.

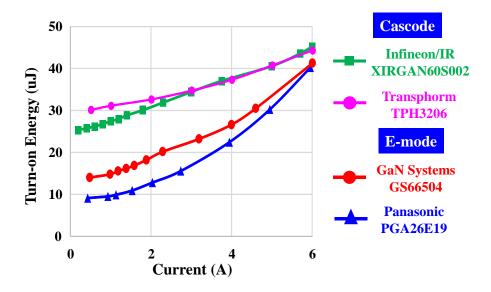

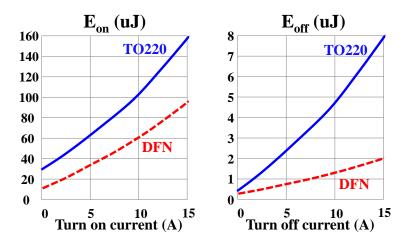

The turn-on switching loss of different GaN devices, which are listed in table 1.2, are shown in Figure 2.8. The loss curves delivers two messages. First, the turn-on switching loss of cascode GaN is higher than e-mode GaN due to low voltage Si MOSFET body diode Q<sub>rr</sub> effect. Secondly, the turn-on switching loss is in a range of few tens of uJ, which is few tens of watts if the switching frequency is 1MHz. The huge turn-on switching loss is definitely an enemy to further push frequency.

Figure 2.8 Turn-on switching loss of different GaN devices

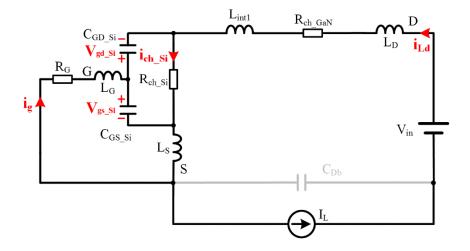

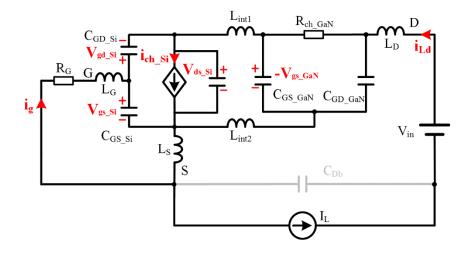

### 2.1.3 Turn-off transition

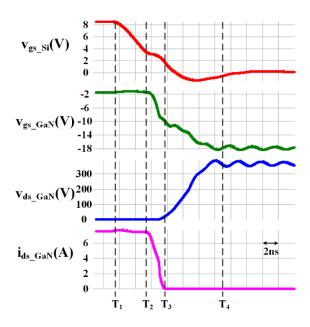

The key waveforms for control switch turn-off transition is shown in Figure 2.9. At  $T_1$  instant, the gate driving signal is removed, and then the silicon MOSFET gradually enters the saturation region. The drain-source voltage of silicon MOSFET increases which also means  $v_{gs\_GaN}$  decreases. At  $T_2$  instant, the GaN HEMT enters the saturation region and the channel current starts to decrease and  $V_{ds\_GaN}$  starts to increase. Because of the internal current source turn off mechanism, which is unique to cascode structure,  $V_{gs\_GaN}$  shortly drops below the pinch off value at  $T_3$  [B.2]. Then the rest of the terminal current charges the  $C_{oss}$  and consequently  $V_{ds\_GaN}$  rises to the steady state value. The inductor current transfers from the control switch to the free-wheeling switch. It clearly shows that the voltage and current transition time is short and the energy dissipation is about 0.2uJ. This value is extremely small compared to the same level Si MOSFET which is typically larger than 5uJ. During the turn off transition, the low voltage silicon MOSFET dissipates about

0.2uJ energy.

Figure 2.9 Hard-switching turn-off waveforms

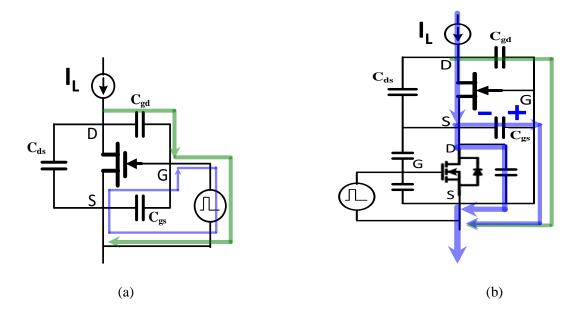

Even though e-mode GaN can achieve fast turn-off as well and the terminal waveforms look very similar, the insight turn-off mechanisms are different from each other. Figure 2.10 compares the basic principle of turn-off transitions for two types of GaN devices. For e-mode GaN devices, the gate discharging current is limited by gate driver circuit. In addition, the current charging miller capacitance ( $C_{gd}$ ) also flows into driving circuit, which further decrease the gate discharging current. This phenomenon is well known as miller effect [B.7].

For cascode GaN devices, the GaN gate discharging current is provided by power loop, which is relatively larger than external gate drive current. It can be considered as a constant current source to discharge gate voltage, which usually helps to reduce the switching loss [B.8], [B.9]. Moreover, the current charging miller capacitance C<sub>gd</sub> directly flows to source

terminal, which bypasses  $C_{\rm gs}$ . These unique features of cascode GaN make the turn-off loss extremely small and not sensitive to the turn-off current.

Figure 2.10 Turn-off mechanism of different types of GaN devices: (a) e-mode, (b) cascode

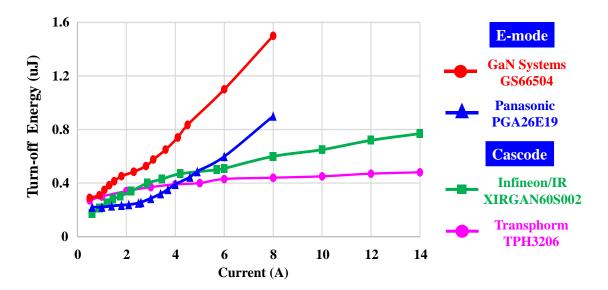

The turn-off switching loss of different GaN devices are shown in Figure 2.11. At lower turn-off current condition, all GaN devices can achieve very small turn-off loss. As the current increases, the turn-off loss of e-mode GaN devices increases due to stronger miller effect. However, the turn-off loss of cascode GaN is almost constant over wide current range.

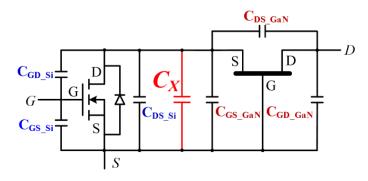

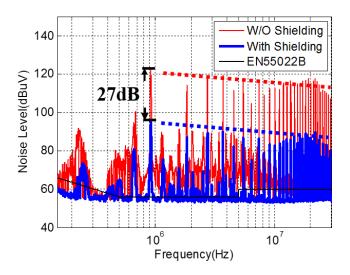

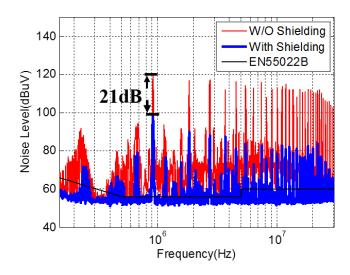

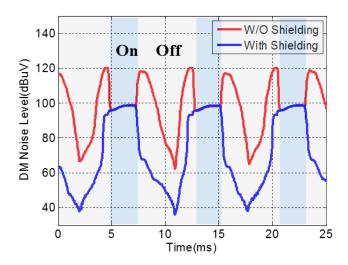

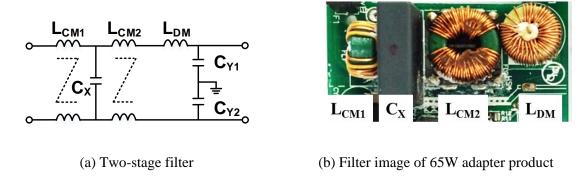

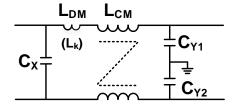

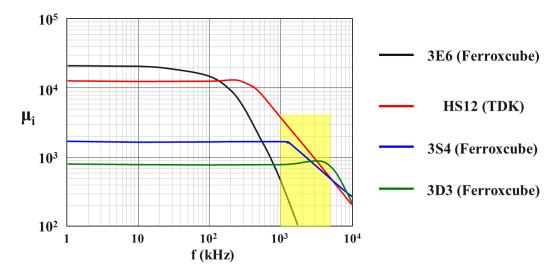

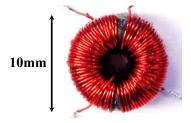

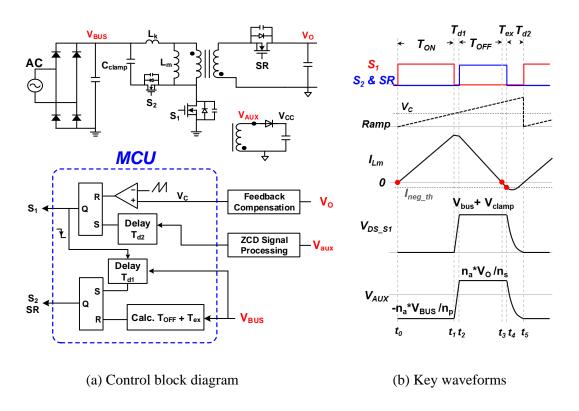

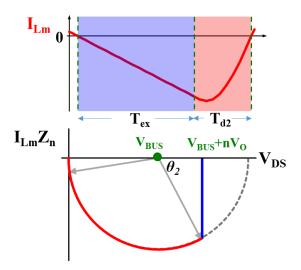

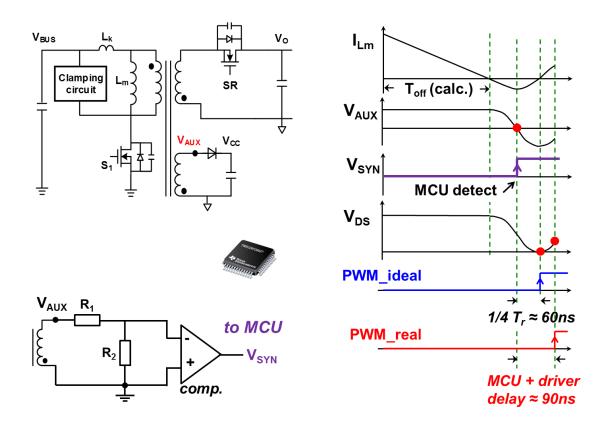

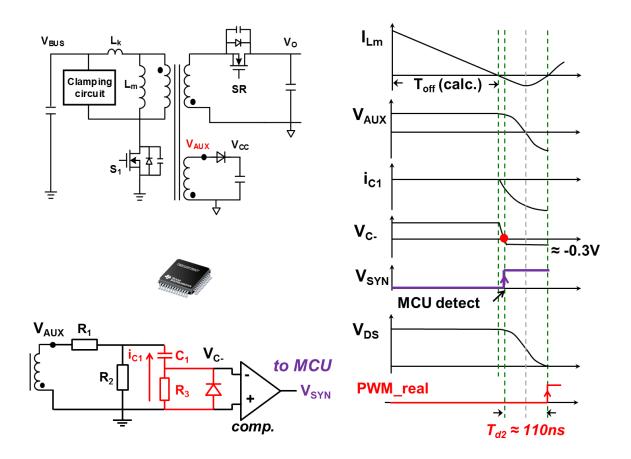

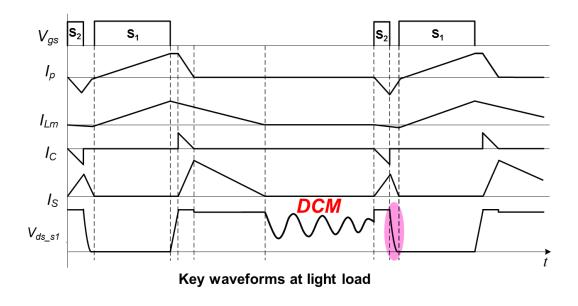

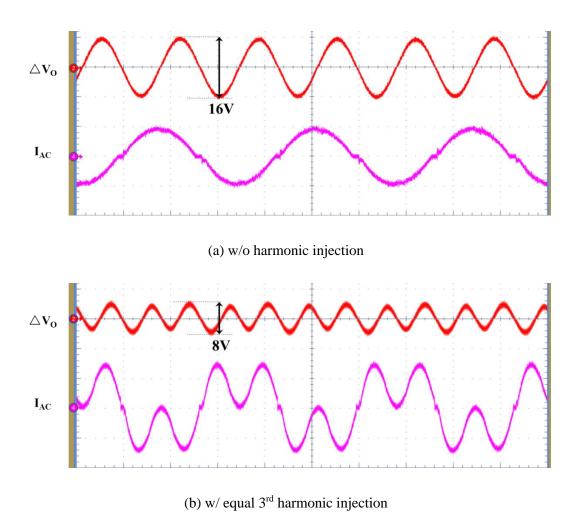

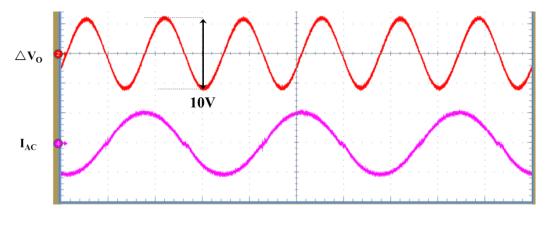

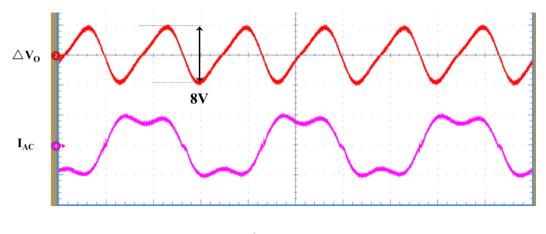

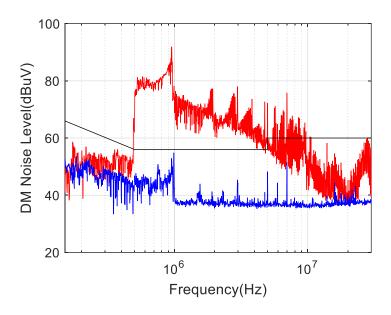

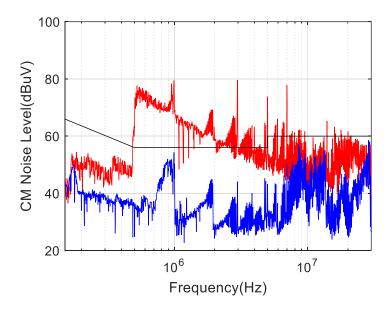

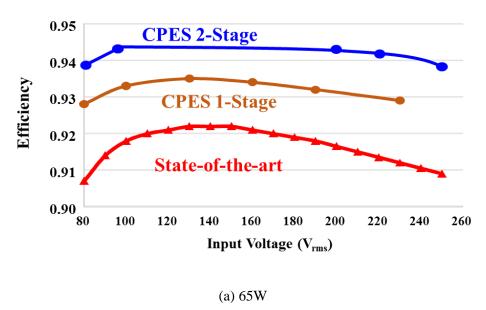

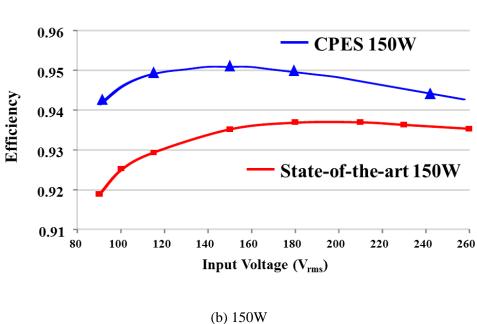

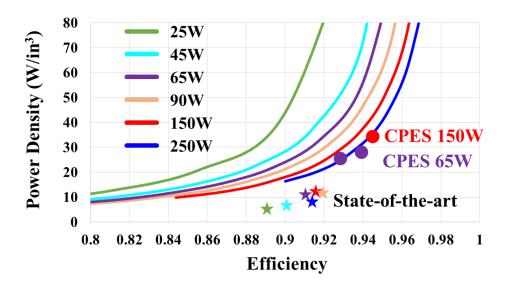

Figure 2.11 Turn-off switching loss of different GaN devices