# Control of DC Power Distribution Systems and Low-Voltage Grid-Interface Converter Design

# Fang Chen

Dissertation submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical Engineering

Dushan Boroyevich (Co-Chair)

Rolando Burgos (Co-Chair)

Virgilio A. Centeno

William T. Baumann

Alfred L. Wicks

March 22, 2017 Blacksburg, Virginia

Keywords: dc power distribution, microgrid, droop control, load sharing, grid interface converter, single phase ac-dc

Copyright 2017, Fang Chen

# Control of DC Power Distribution Systems and Low-Voltage Grid-Interface Converter Design

# Fang Chen

## **Abstract**

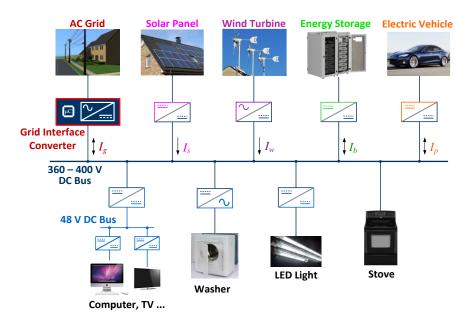

DC power distribution has gained popularity in sustainable buildings, renewable energy utilization, transportation electrification and high-efficiency data centers. This dissertation focuses on two aspects of facilitating the application of dc systems: (a) system-level control to improve load sharing, voltage regulation and efficiency; (b) design of a high-efficiency interface converter to connect dc microgrids with the existing low-voltage ac distributions, with a special focus on common-mode (CM) voltage attenuation.

Droop control has been used in dc microgrids to share loads among multiple sources. However, line resistance and sensor discrepancy deteriorate the performance. The quantitative relation between the droop voltage range and the load sharing accuracy is derived to help create droop design guidelines. DC system designers can use the guidelines to choose the minimum droop voltage range and guarantee that the sharing error is within a defined range even under the worst cases.

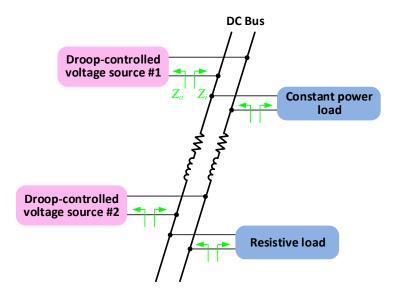

A nonlinear droop method is proposed to improve the performance of droop control. The droop resistance is a function of the output current and increases when the output current increases. Experiments demonstrate that the nonlinear droop achieves better load sharing under heavy load and tighter bus voltage regulation. The control needs only local information, so the advantages of droop control are preserved. The output impedances of the droop-controlled power converters are also modeled and measured for the system stability analysis.

Communication-based control is developed to further improve the performance of dc microgrids. A generic dc microgrid is modeled and the static power flow is solved. A secondary control system is presented to achieve the benefits of restored bus voltage,

enhanced load sharing and high system efficiency. The considered method only needs the information from its adjacent node; hence system expendability is guaranteed.

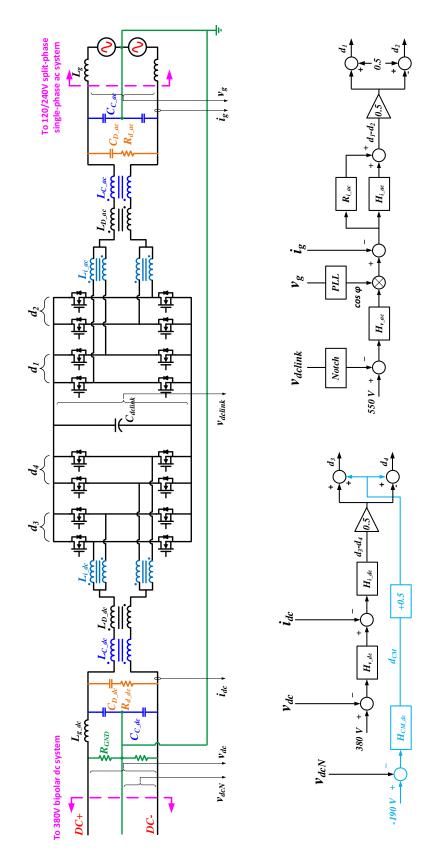

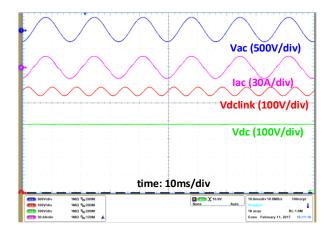

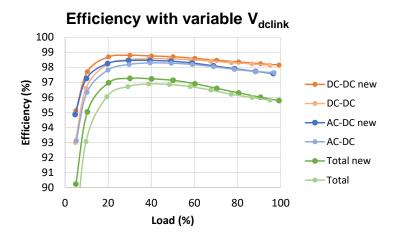

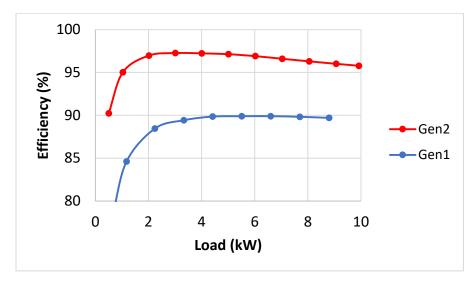

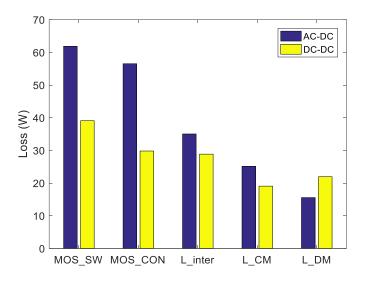

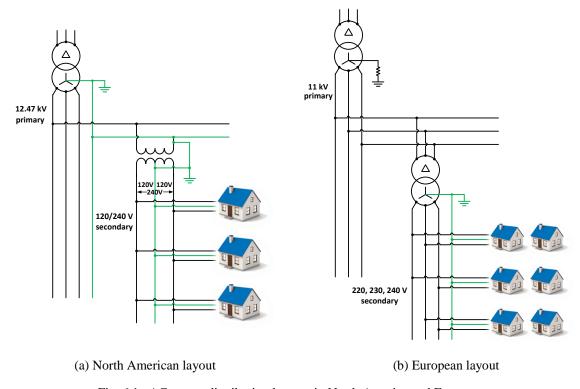

A high-efficiency two-stage single-phase ac-dc converter is designed to connect a 380 V bipolar dc microgrid with a 240 V split-phase single-phase ac system. The converter efficiencies using different two-level and three-level topologies with state-of-the-art semiconductor devices are compared, based on which a two-level interleaved topology using silicon carbide (SiC) MOSFETs is chosen. The volt-second applied on each inductive component is analyzed and the interleaving angles are optimized. A 10 kW converter prototype is built and achieves an efficiency higher than 97% for the first time.

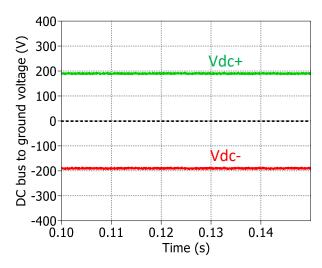

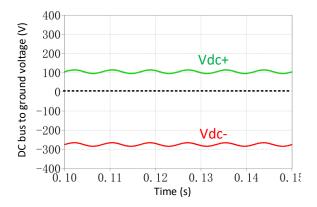

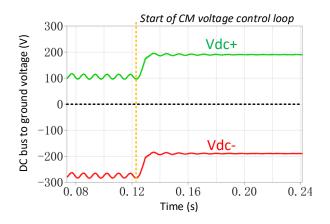

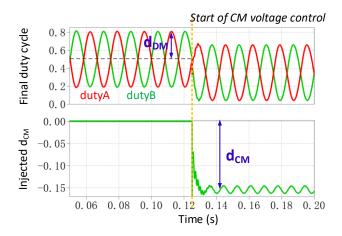

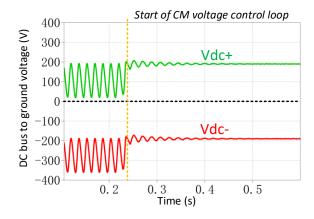

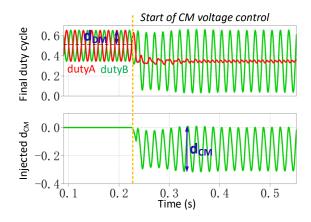

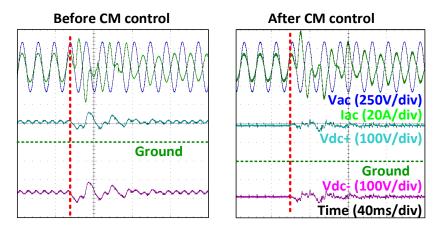

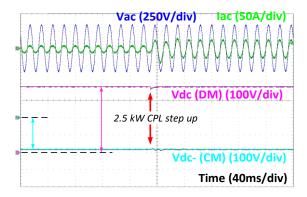

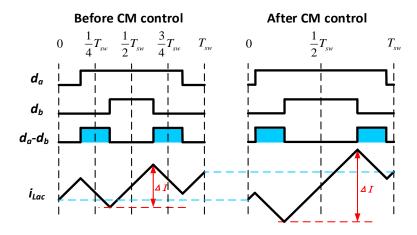

An active CM duty cycle injection method is proposed to control the dc and low-frequency CM voltage for grounded systems interconnected with power converters. Experiments with resistive and constant power loads in rectification and regeneration modes validate the performance and stability of the control method. The dc bus voltages are rendered symmetric with respect to ground, and the leakage current is reduced. The control method is generalized to three-phase ac-dc converters for larger power systems.

# Control of DC Power Distribution Systems and Low-Voltage Grid-Interface Converter Design

# Fang Chen

# General Audience Abstract

DC power distribution gains popularity in sustainable buildings, renewable energy utilization, transportation electrification and high-efficiency data centers. This dissertation focuses on two aspects of facilitating the application of dc systems: (a) system-level control to improve load sharing, voltage regulation and efficiency; (b) a high-efficiency converter design to connect dc microgrids with the existing low-voltage ac utility, with a special focus on controlling the dc bus to ground voltage.

An analytical model is established to solve the power flow and voltage distribution in a generic dc system. The impact from cable resistance and measurement error on droop control is quantitatively analyzed, based on which droop design guidelines are proposed. DC system designers can use the conclusion to choose a minimum droop voltage range and guarantee a predefined load sharing accuracy. A nonlinear droop control method and a communication-based control method are proposed to further improve the dc system performance. The benefits include better load sharing, tighter voltage regulation and higher system efficiency.

To connect dc grids with the low-voltage ac distribution, a high-efficiency bidirectional ac-dc interface converter is designed and built. Different converter topologies with state-of-the-art power semiconductor devices are evaluated. Based on the comparison, an interleaved converter is selected and achieves an efficiency higher than 97% with an optimized passive component design. This converter is also capable of generating symmetric dc bus to ground voltages using a dedicated common-mode voltage control system, and is thus suitable for bipolar dc distribution systems.

# Dedicated to:

My parents:

Xihuan Chen, Weimin Fang

My grandparents:

Chonghao Chen, Yuxian Zhu

Guoliang Fang, Shumin Li

# Acknowledgements

Foremost, I would like to express my sincere gratitude to my advisors Dr. Dushan Boroyevich and Dr. Rolando Burgos, who provided me with this great opportunity to learn and research at the Center for Power Electronics Systems (CPES). I am very fortunate to have both of them as my Ph.D. advisors. Their visions and knowledge guided me on the path of exploring power electronics. Their encouragement supported me and motivated me to embrace the continuous challenges. Their humorous attitude towards life and meticulous attitude towards work showed me a model for being an interesting and responsible person. These experiences and qualities will be my invaluable assets.

In addition to my advisors, I would like to thank the rest of my committee, Dr. Alfred L. Wicks, Dr. Virgilio A. Centeno, Dr. William T. Baumann, and Dr. Douglas K. Lindner, for giving me valuable advice and insightful suggestions from different technical perspectives. It has been wonderful to have them on my advisory committee.

I wish to thank the CPES director, Dr. Fred C. Lee, for his inspiring guidance and strict requirements through the Renewable Energy and Nanogrids (REN) min-consortium weekly meetings. I learned a great deal from him about organizing the logic of my research and presentations.

My special thanks goes to Dr. Josep M. Guerrero and Dr. Juan Carlos Vasquez for inviting me to conduct part of my research at Aalborg University, Denmark. I would also like to thank those who helped me during this study abroad time. This experience in Europe not only enriched my knowledge but broadened my horizons as well.

I would like to thank the CPES administrative staff members, Ms. Marianne Hawthorne, Ms. Teresa Shaw, Ms. Trish Rose, Ms. Linda Long, Mr. David Gilham, and Ms. Lauren Shutt for their support and help during my time at CPES.

I also would like to thank all my fellows at CPES. Their help, mentorship, and friendship provided a basis for the accomplishment of this work. Although I cannot list all of them, I would like to take this chance and thank those who made valuable input to my work. They are Dr. Dong Dong, Dr. Xuning Zhang, Dr. Zhiyu Shen, Dr. Mingkai Mu, Dr. Marko Jaksic, Dr. Bo Wen, Dr. Lingxiao Xue, Dr. Zheming Zhang, Dr. Daocheng Huang,

Dr. Shuilin Tian, Dr. Yang Jiao, Mr. Igor Cvetkovic, Mr. Wei Zhang, Mr. Jun Wang, Mr. Qiong Wang, Mr. Chi Li, Mr. Ming Lv, Mr. Zhongsheng Cao, Mr. Xuebing Chen, Ms. Niloofar Rashidi, Ms. Christina DiMarino, Mr. Yi-Hsun Hsieh, Mr. Alinaghi Marzoughi, Ms. Bingyao Sun, Mr. Ruiyang Qin, Mr. Shishuo Zhao, Mr. Yadong Lyu, Mr. Sungjae Ohn, Ms. Ye Tang, Mr. Yue Xu, Ms. Qian Li, and so many others.

With much love and gratitude, I want to thank my parents Xihua Chen and Weimin Fang, for their endless love, encouragement, and support throughout my life. Thank you for educating me from a very early age, creating a better environment for my education and supporting me in pursuing my Ph.D. abroad. I owe you so much and I am so lucky to be your son!

Finally, I must thank my girlfriend Li Wang, who came to the U.S. with me, accompanied me and encouraged me. I would not have accomplished this work without you being here.

I am sure I have missed expressing my appreciation to many people. To you all, thank you so much!

This work is supported by the Wide Band Gap High-Power Converters & Systems (WBG-HPCS) mini-consortium (formerly known as Renewable Energy and Nanogrids (REN) mini-consortium).

Fang Chen Table of Contents

# Table of Contents

| Chapter 1. Introduction                                                 | 1  |

|-------------------------------------------------------------------------|----|

| 1.1. Research background and motivations                                | 1  |

| 1.2. Literature review                                                  | 6  |

| 1.2.1. Power architecture development for dc microgrids                 | 6  |

| 1.2.2. Control methods for dc microgrids                                | 9  |

| 1.2.3. Low-voltage utility interface converter design for dc microgrids | 15 |

| 1.3. Challenges and research objectives                                 | 20 |

| 1.3.1. Challenges in the deployment of dc power distribution            | 20 |

| 1.3.2. Research objectives                                              | 23 |

| 1.4. Dissertation outline                                               | 24 |

| Chapter 2. Design of Droop Control for DC Power Distribution Systems    | 26 |

| 2.1. The benefit and realization of droop control in dc systems         | 26 |

| 2.2. Analysis of factors degrading the performance of droop control     | 29 |

| 2.2.1. The effect of cable resistance                                   | 29 |

| 2.2.2. The effect of voltage offset                                     | 34 |

| 2.2.3. Experimental verification                                        | 35 |

| 2.3. Quantitative analysis for two-source systems                       | 36 |

| 2.3.1. Identification of the worst source and load locations            | 36 |

| 2.3.2. Load sharing accuracy as a function of source power ratings      | 37 |

| 2.3.3. Load sharing accuracy as a function of droop voltage range       | 39 |

| 2.4. Generalization to three-source and multi-source multi-load systems | 41 |

| 2.4.1. Analysis for the side source                                     | 41 |

| 2.4.2. Analysis for the middle source                                   | 43 |

| 2.4.3. Generalization to multi-source system                            | 44 |

| 2.5. Proposed droop design guidelines for dc systems                    | 45 |

| 2.6. Conclusion                                                         | 46 |

Fang Chen Table of Contents

| Chapter 3. A Nonlinear Droop Control to Improve Load Sharing and Voltage Regulation                         | 48    |

|-------------------------------------------------------------------------------------------------------------|-------|

| 3.1. Review of techniques to improve the load sharing and voltage regulation of droop control               | 48    |

| 3.2. The proposed nonlinear droop control                                                                   | 50    |

| 3.2.1. The principle of the proposed nonlinear droop control                                                | 50    |

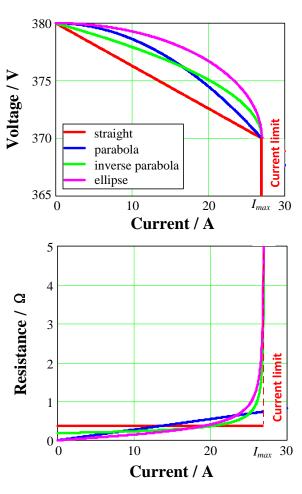

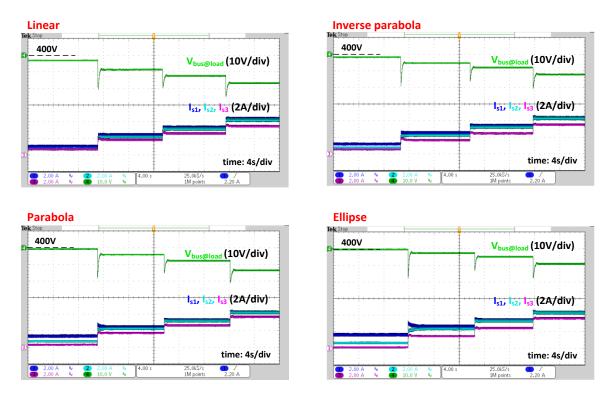

| 3.2.2. Comparison of different nonlinear droop profiles                                                     | 51    |

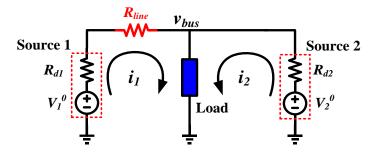

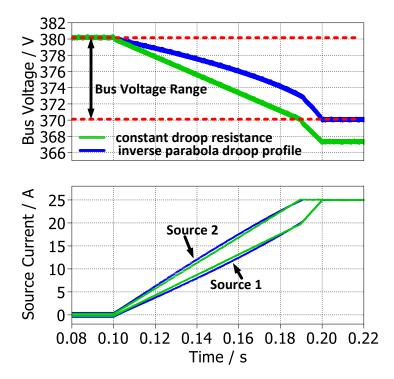

| 3.2.3. Performance comparison between linear and nonlinear droops                                           | 53    |

| 3.3. Experimental verification                                                                              | 54    |

| 3.3.1. Single-source droop characteristic test                                                              | 54    |

| 3.3.2. Comparison between traditional linear droop and proposed nonlinear droop                             | 55    |

| 3.4. Output impedance and stability considerations                                                          | 62    |

| 3.4.1. Review of dc system stability criteria                                                               | 62    |

| 3.4.2. Output impedance small-signal modeling for droop-controlled voltage sources                          | 64    |

| 3.4.3. Measurement of the output impedance for power converters                                             | 67    |

| 3.5. Conclusion                                                                                             | 72    |

| Chapter 4. DC System Power Flow Analysis and Performance Improvement Using Nearest-N                        | Node  |

| Communication                                                                                               | 74    |

| 4.1. Review of microgrid control strategies with communication links                                        | 74    |

| 4.2. Static power flow analysis of a generic dc microgrid                                                   | 76    |

| 4.3. DC system efficiency analysis and optimization                                                         | 79    |

| 4.4. A distributed power flow control strategy using nearest-node communication                             | 84    |

| 4.5. Experimental verification                                                                              | 90    |

| 4.5.1. Hardware-in-the-loop test bed                                                                        | 90    |

| 4.5.2. Validation of the static system model                                                                | 92    |

| 4.5.3. Validation of the distributed power flow control method                                              | 95    |

| 4.6. Conclusion                                                                                             | 97    |

| Chapter 5. A High-Efficiency Transformer-less Single-Phase Utility-Interface Converter for 380 V Microgrids | DC 99 |

| 5.1. Design application and requirements                                                                    | 99    |

| 5.1.1. Gird-interface converter for future residential houses                                               | 99    |

| 5.1.2. Residential ac and dc grid interfaces                                                                | 100   |

| Fang Chen | Table of Contents |

|-----------|-------------------|

|           |                   |

| 5          | 5.1.3. Applicable standards                                               | 102        |

|------------|---------------------------------------------------------------------------|------------|

| 5.2        | . Converter topology selection                                            | 103        |

| 5          | 5.2.1. Two-stage topology to decouple the common-mode voltage             | 103        |

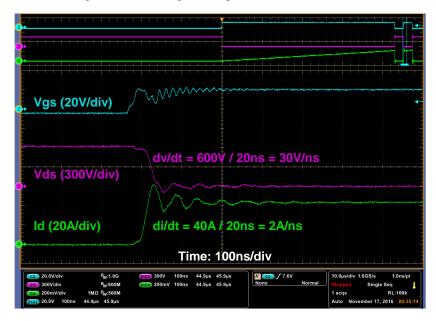

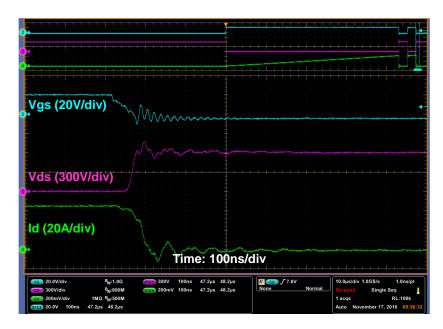

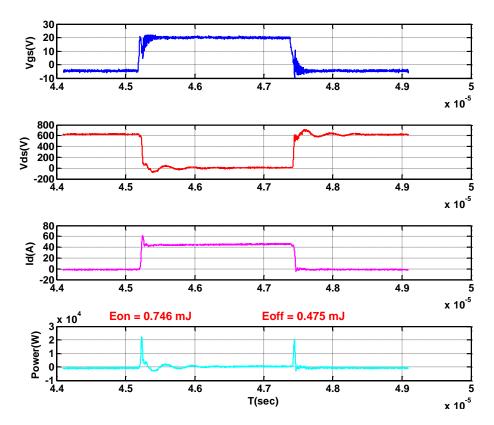

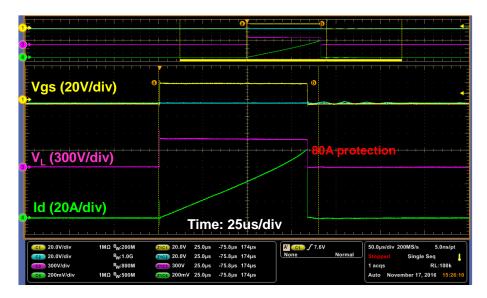

| 5          | 5.2.2. Selection of the phase-leg structure to achieve high efficiency    | 104        |

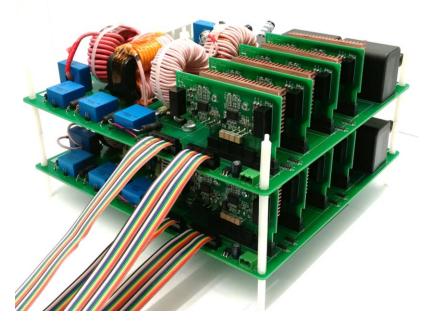

| 5.3        | S. Power stage design                                                     | 113        |

| 5          | 5.3.1. Pluggable phase-leg module design                                  | 113        |

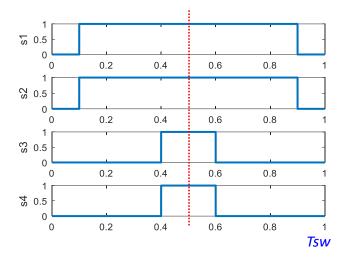

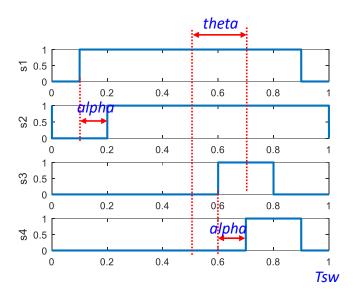

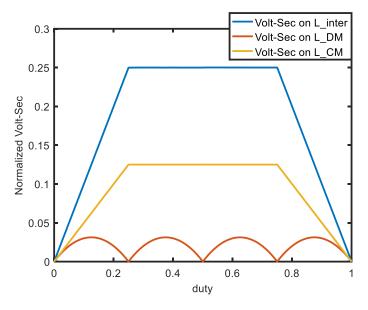

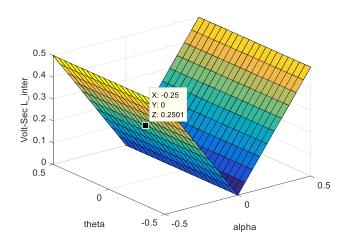

| 5          | 5.3.2. Interleaving angle selection and filter design                     | 119        |

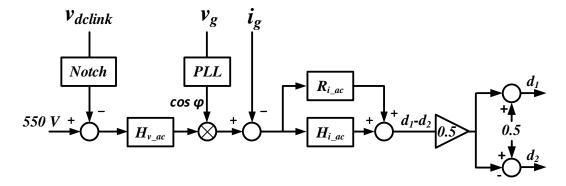

| 5.4        | . Control system design                                                   | 130        |

| 5          | 5.4.1. Control system for the differential-mode quantities                | 130        |

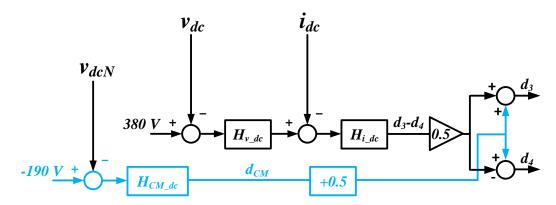

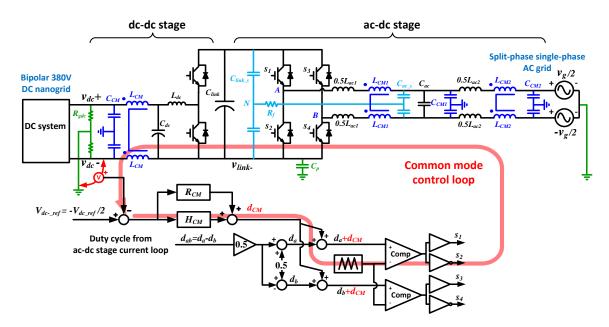

| 5          | 5.4.2. Control system for common-mode voltages                            | 131        |

| 5.5        | . Experimental results                                                    | 137        |

| 5.6        | 5. Conclusion                                                             | 141        |

| Chapter 6  | 6. Low-Frequency Common-Mode Voltage Control for Systems Interconnected   | with Power |

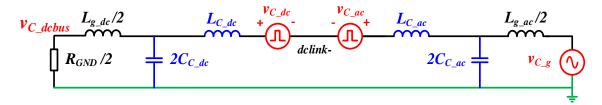

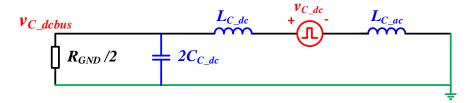

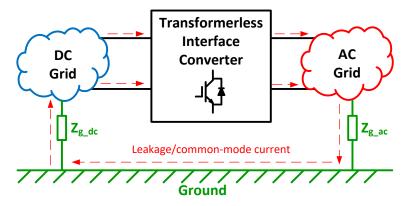

| 6.1        | . Problems when grounded systems are connected by non-isolated converters | 142        |

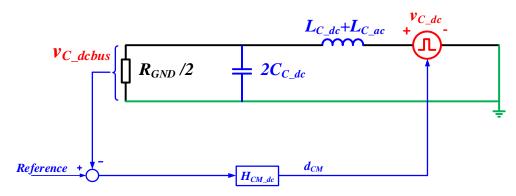

| 6.2        | 2. Principle of the active low-frequency common-mode voltage control      | 145        |

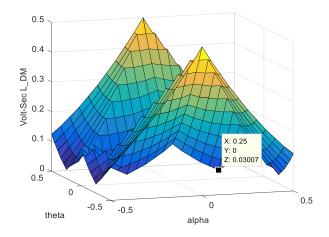

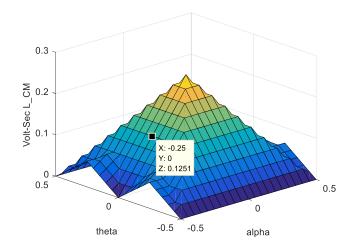

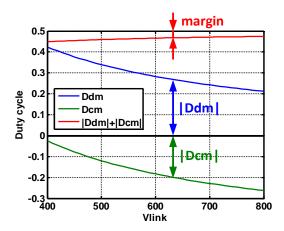

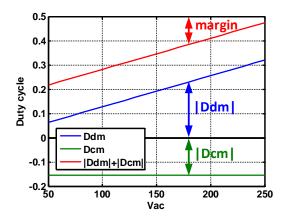

| 6.3        | 6. Operating range of the common-mode duty cycle injection                | 147        |

| 6          | 6.3.1. The impact from dc-link voltage and ac voltage                     | 150        |

| 6          | 6.3.2. The impact from asymmetric ac grounding                            | 152        |

| 6.4        | . Common-mode circuit small-signal modeling and control loop design       | 153        |

| 6.5        | 6. Generalization to three-phase ac interface                             | 157        |

| 6.6        | 5. Experimental results and impact on ac current                          | 158        |

| 6.7        | . Conclusion                                                              | 163        |

| Chapter 7  | 7. Summary, Conclusions and Future Work                                   | 164        |

| 7.1        | . Summary                                                                 | 164        |

| 7.2        | 2. Conclusions                                                            | 164        |

| 7.3        | 5. Future work                                                            | 165        |

| References | S                                                                         | 167        |

| Appendix   |                                                                           | 186        |

| Fang Chen                                                 | Table of Contents |  |

|-----------------------------------------------------------|-------------------|--|

| A.1 MATLAB code to calculate the volt-second on inductors | 186               |  |

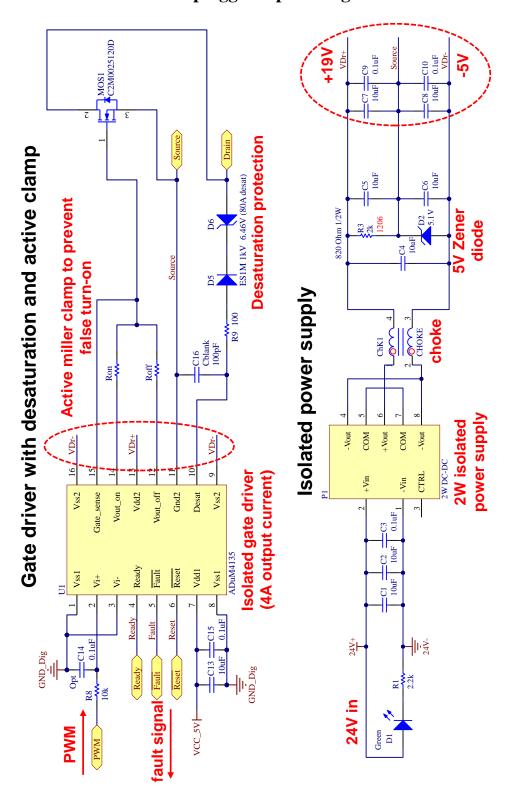

| A.2 Circuit schematic of the pluggable phase-leg card     | 189               |  |

# List of Figures

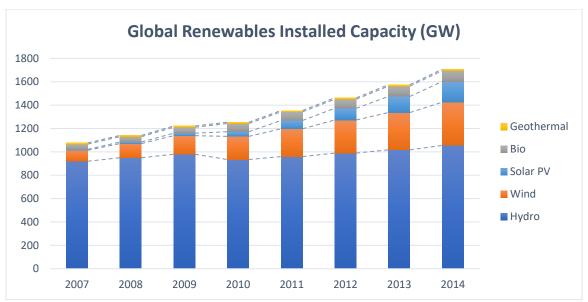

| Fig. 1.1. Trend of global renewables installed capacity.                                          | 2  |

|---------------------------------------------------------------------------------------------------|----|

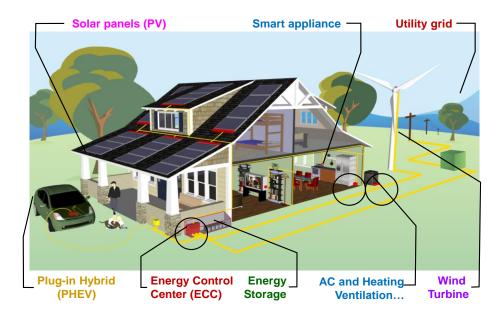

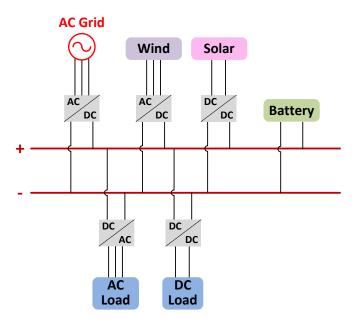

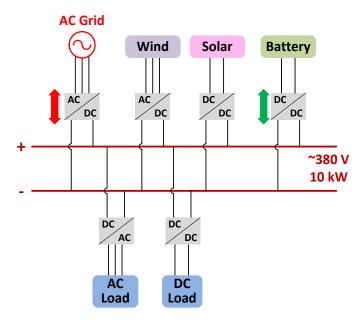

| Fig. 1.2. Initiative of dc nanogrid for future houses at CPES, Virginia Tech.                     | 5  |

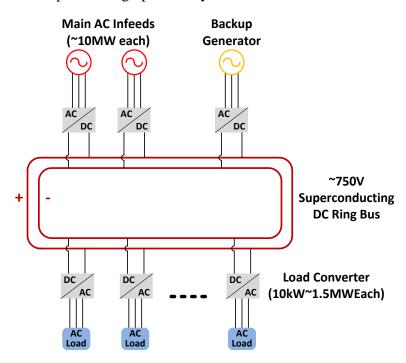

| Fig. 1.4. General LVdc industrial power distribution with UPS features.                           | 6  |

| Fig. 1.5. Single bus dc microgrid with battery directly tied.                                     | 7  |

| Fig. 1.6. DC microgrid with power management.                                                     | 8  |

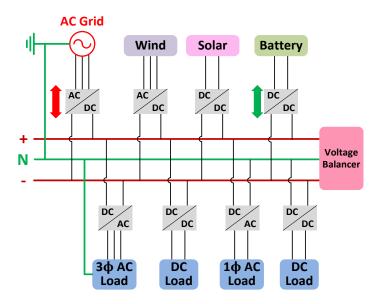

| Fig. 1.7. Bipolar dc bus with voltage balancer.                                                   | 8  |

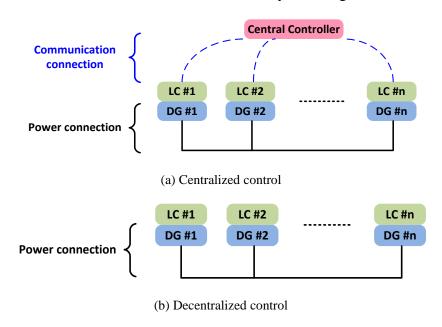

| Fig. 1.8. Control structures for dc microgrid.                                                    | 10 |

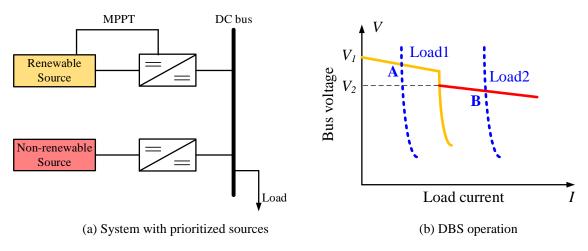

| Fig. 1.9. Principle of the dc bus signaling.                                                      | 12 |

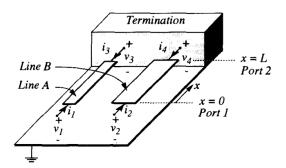

| Fig. 1.11. Definitions of DM and CM signals in coupled pair transmission lines [108].             | 17 |

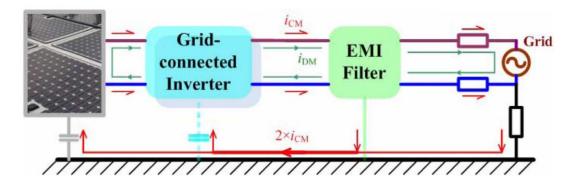

| Fig. 1.12. The CM path in PV applications [110].                                                  | 18 |

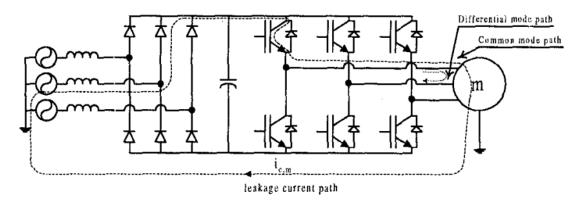

| Fig. 1.13. CM and DM current paths in motor drive applications [114].                             | 18 |

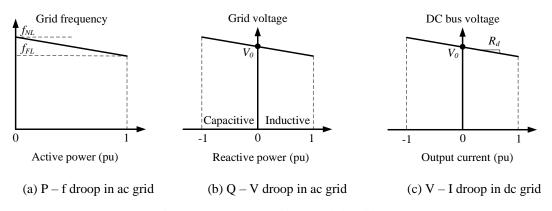

| Fig. 2.1. Droop control in ac and dc grids.                                                       | 27 |

| Fig. 2.2. Droop control in a two-source one-load dc system.                                       | 28 |

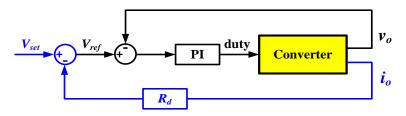

| Fig. 2.3. A control structure to realize virtual droop resistance.                                | 29 |

| Fig. 2.4. Impact of line resistance on voltage distribution.                                      | 30 |

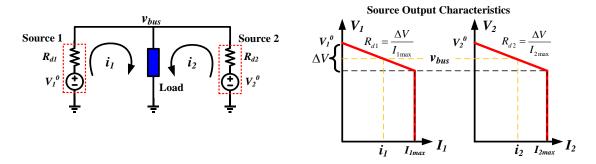

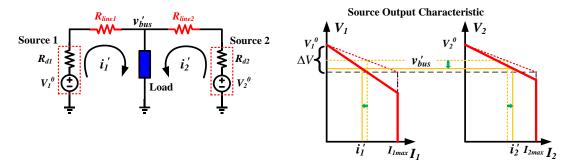

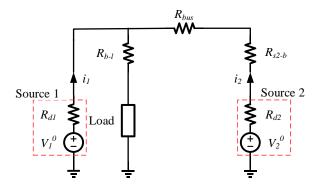

| Fig. 2.5. Two sources droop with cable resistances.                                               | 31 |

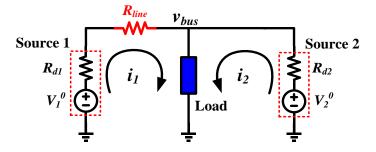

| Fig. 2.6. System to analyze the effect of line resistance.                                        | 32 |

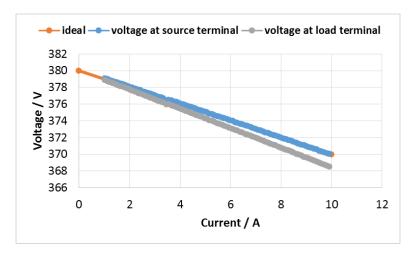

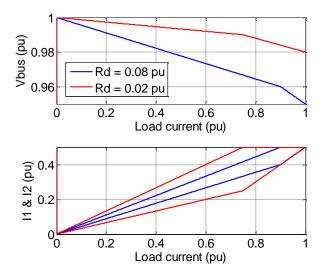

| Fig. 2.7. Load sharing and voltage regulation comparison with different droop resistances.        | 33 |

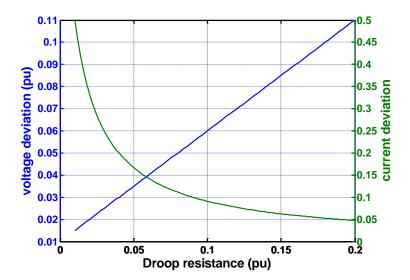

| Fig. 2.8. Trade-off between voltage regulation and load sharing when choosing a droop resistance. | 34 |

| Fig. 2.9. Impact of voltage offset on load sharing.                                               | 35 |

| Fig. 2.10. Load sharing experiment with line resistance and measurement error.                    | 36 |

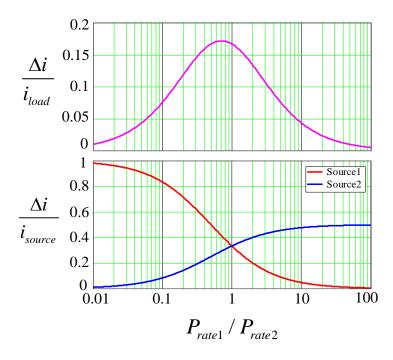

| Fig. 2.11. The worst source and load locations for two-source systems.                            | 37 |

| Fig. 2.12. Sharing error as a function of source ratings.                                         | 38 |

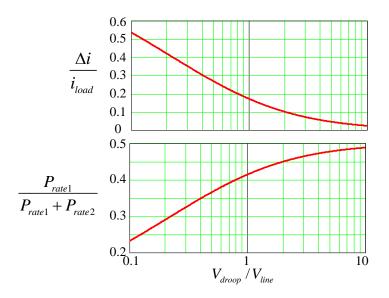

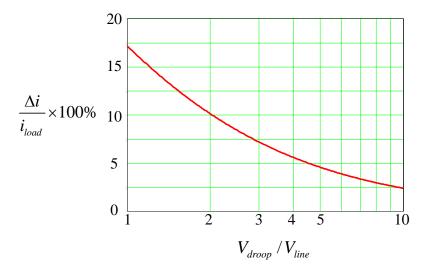

| Fig. 2.13. Sharing error as a function of droop voltage range.                                    | 40 |

| Fig. 2.14. Quantitative relation between droop voltage range and load sharing accuracy.           | 40 |

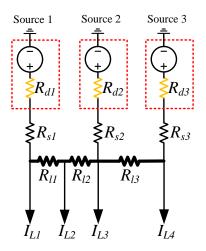

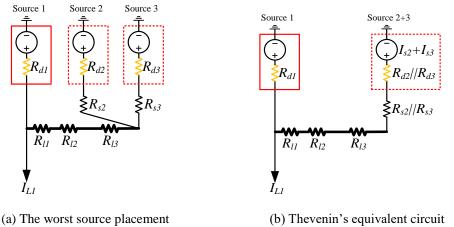

| Fig. 2.15. A three-source multi-load system.                                                      | 41 |

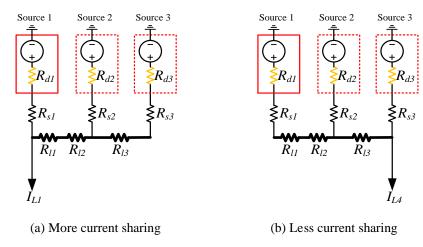

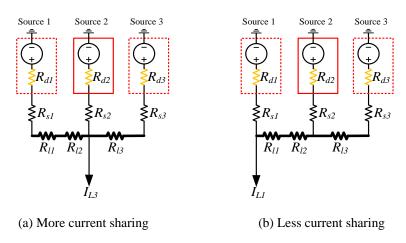

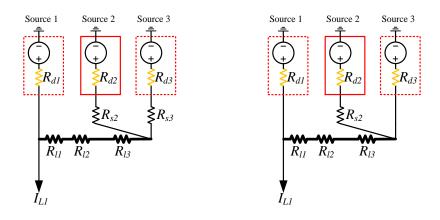

| Fig. 2.16. Two extreme cases for side Source 1.                                                   | 42 |

| Fig. 2.17. Source placement and combination for the most current sharing from Source 1.           | 43 |

| Fig. 2.18. Two worst cases for the middle source.                                                 | 43 |

| Fig. 2.19. The worst source and cable placement for the middle source to take the least load.     | 44 |

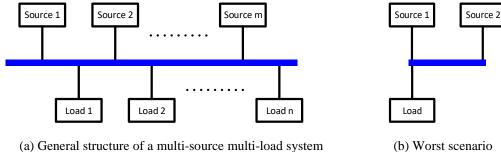

| Fig. 2.20. A multi-source multi-load system and its worst case.                                   | 45 |

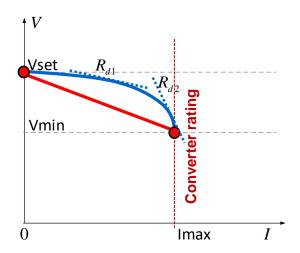

| Fig. 3.1. Diagram of the proposed nonlinear droop control.                                        | 51 |

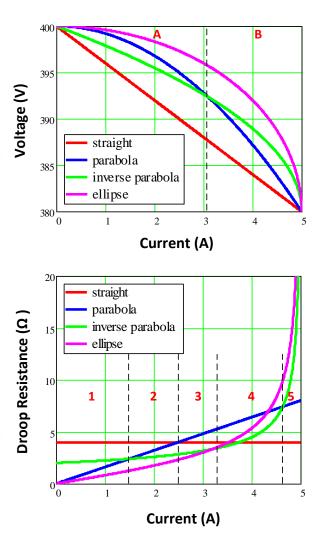

| Fig. 3.2. Different droop curves and corresponding droop resistances.                             | 52 |

| Fig. 3.3. Two-source paralleling test with inserted cable.                                        | 54 |

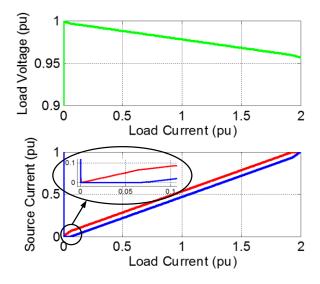

| Fig. 3.4. Simulation comparison between the traditional and proposed droop methods.               | 54 |

| Fig. 3.5. Single-source droop characteristic test.                                                | 55 |

| Fig. 3.6. Linear droop with negligible cable resistance.                             | 56 |

|--------------------------------------------------------------------------------------|----|

| Fig. 3.7. Nonlinear droop with negligible cable resistance.                          | 56 |

| Fig. 3.8. Linear droop ( $R_d = 1 \Omega$ ) with 0.2 $\Omega$ cable resistance.      | 57 |

| Fig. 3.9. Linear droop ( $R_d = 0.5 \Omega$ ) with 0.2 $\Omega$ cable resistance.    | 57 |

| Fig. 3.10. The linear droop $(R_d = 1 \Omega)$ with 0.2 $\Omega$ cable resistance.   | 58 |

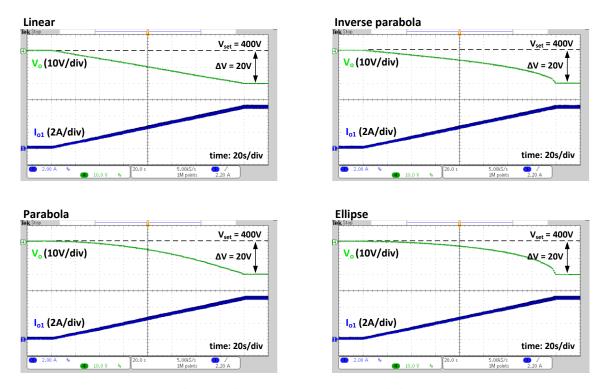

| Fig. 3.11. The inverse parabola droop with 0.2 $\Omega$ cable resistance.            | 58 |

| Fig. 3.12. A three-source dc system with tie-line resistance and measurement error.  | 59 |

| Fig. 3.13. Segments to compare different droop profiles.                             | 60 |

| Fig. 3.14. Droop comparison in Segment 1.                                            | 61 |

| Fig. 3.15. Droop comparison in Segment 2.                                            | 61 |

| Fig. 3.16. Droop comparison in Segment 3.                                            | 61 |

| Fig. 3.17. Droop comparison in Segment 4.                                            | 61 |

| Fig. 3.18. Droop comparison in Segment 5.                                            | 61 |

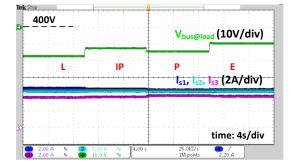

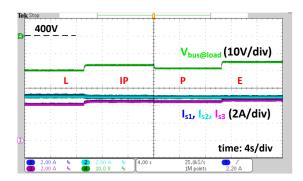

| Fig. 3.19. Load step test for different droop profiles.                              | 62 |

| Fig. 3.20. A zonal dc bus system with distributed sources and loads.                 | 63 |

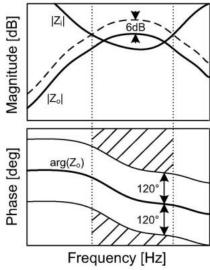

| Fig. 3.21. Bode plot of the GMPM criterion.                                          | 64 |

| Fig. 3.22. Nyquist plot of the GMPM criterion.                                       | 64 |

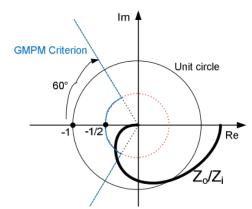

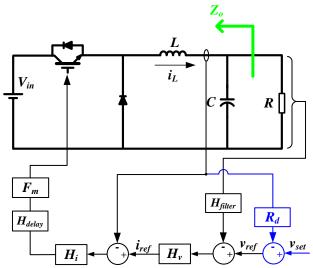

| Fig. 3.23. Buck converter with droop control loop.                                   | 65 |

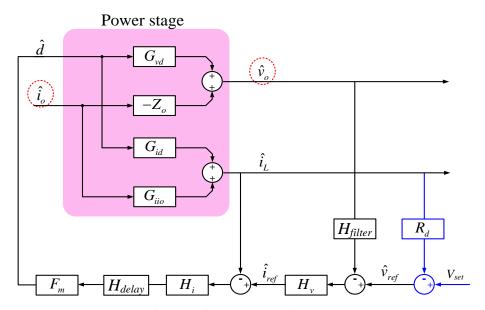

| Fig. 3.24. Control diagram of a droop-controlled voltage source converter.           | 65 |

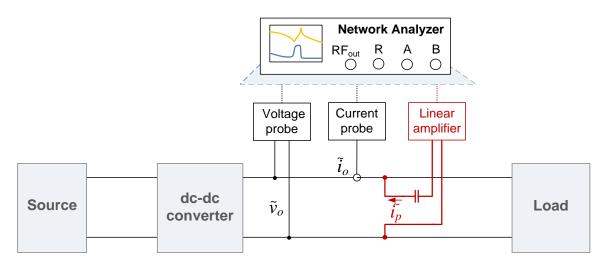

| Fig. 3.25. Converter output impedance measurement circuit.                           | 68 |

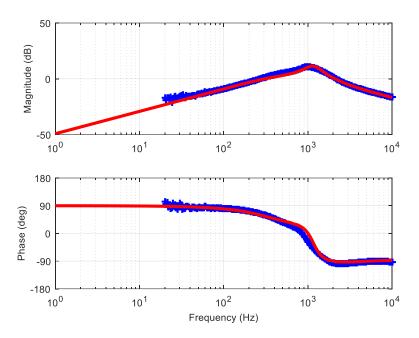

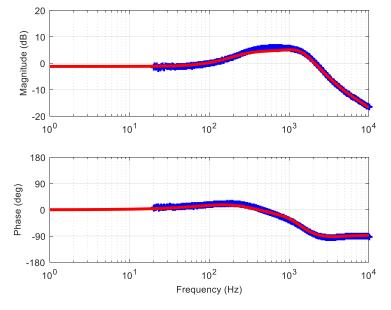

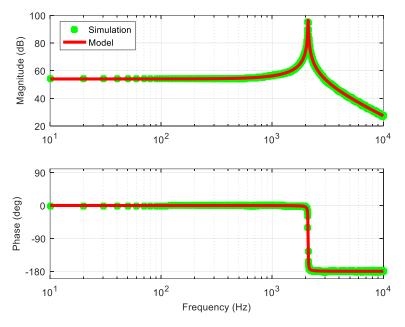

| Fig. 3.26. The modeled and measured output impedance without droop control.          | 69 |

| Fig. 3.27. Modeled and measured output impedance with linear droop control.          | 69 |

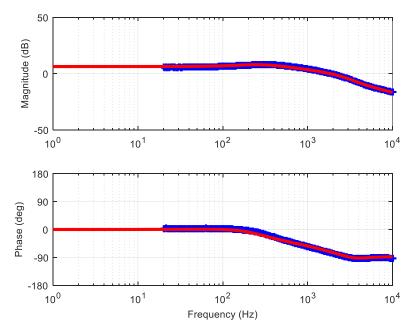

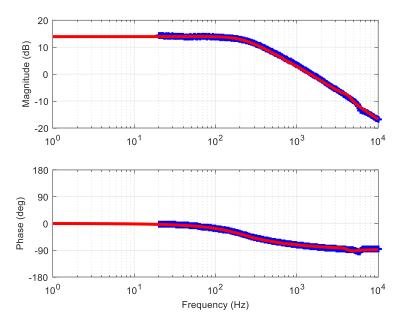

| Fig. 3.28. Output impedance of the ellipse droop under light load.                   | 70 |

| Fig. 3.29. Output impedance of the ellipse droop under medium load.                  | 70 |

| Fig. 3.30. Output impedance of the ellipse droop under heavy load.                   | 71 |

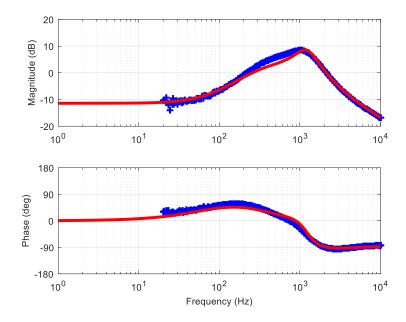

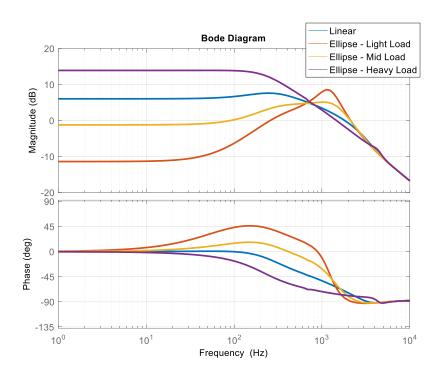

| Fig. 3.31. Output impedance comparison between linear and ellipse droop.             | 72 |

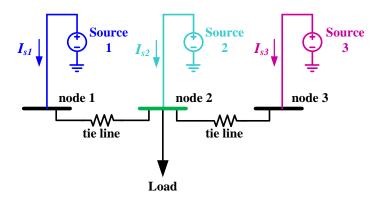

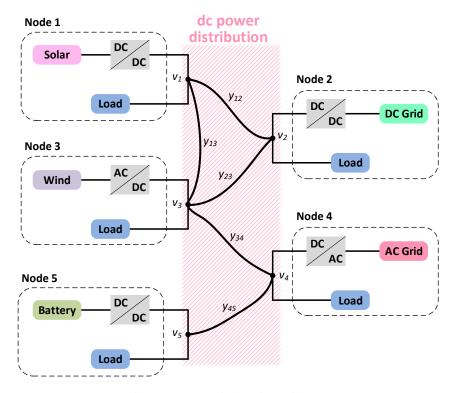

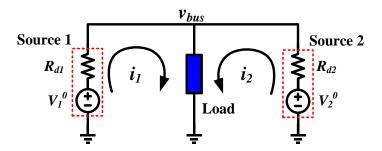

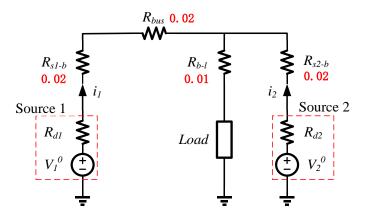

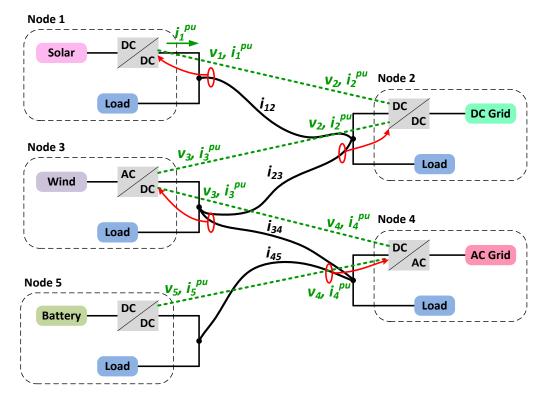

| Fig. 4.1. A generic dc microgrid.                                                    | 76 |

| Fig. 4.2. A two-source one-load system with negligible cable resistance.             | 80 |

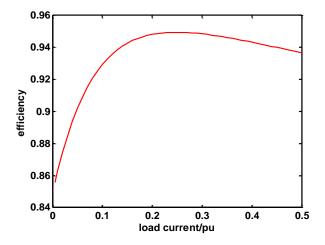

| Fig. 4.3. A typical power converter efficiency curve.                                | 80 |

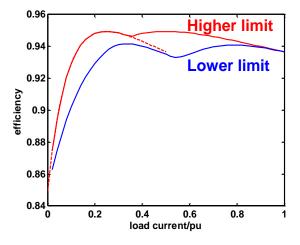

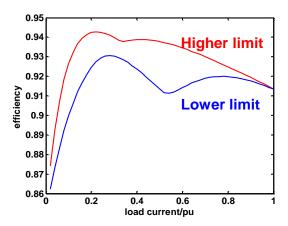

| Fig. 4.4. Two-source paralleling efficiency.                                         | 81 |

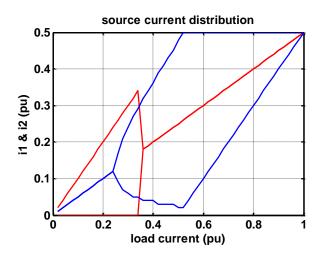

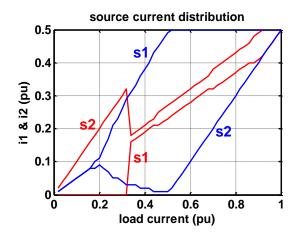

| Fig. 4.5. Source current distribution for higher and lower system efficiency limits. | 82 |

| Fig. 4.6. A two-source system with cable resistance.                                 | 82 |

| Fig. 4.7. Two-source paralleling efficiency with cable losses.                       | 83 |

| Fig. 4.8. Source current distribution with cable losses.                             | 83 |

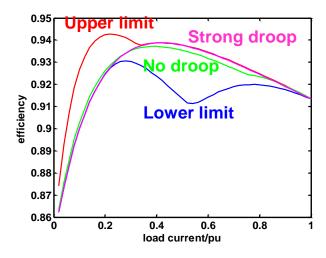

| Fig. 4.9. The system efficiency with no droop and strong droop.                      | 84 |

| Fig. 4.10. The system structure with nearest-node communication.                     | 86 |

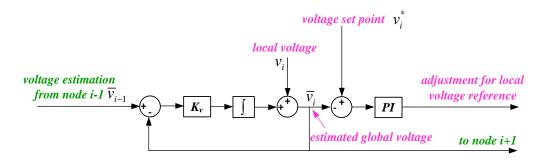

| Fig. 4.11. Bus voltage restoration module.                                           | 87 |

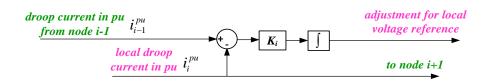

| Fig. 4.12. Load sharing enhancement module (proportional to source ratings).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 87       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

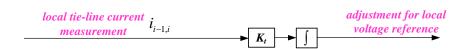

| Fig. 4.13. Tie-line current control module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 88       |

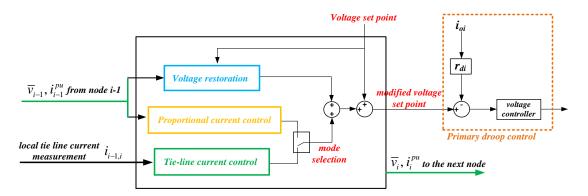

| Fig. 4.14. The proposed power flow controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 88       |

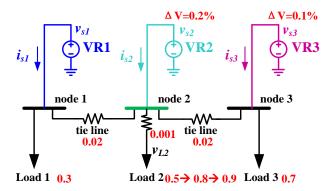

| Fig. 4.15. The evaluated three-source three-load dc distribution system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 89       |

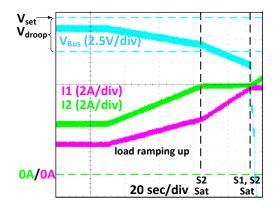

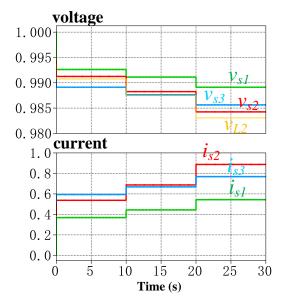

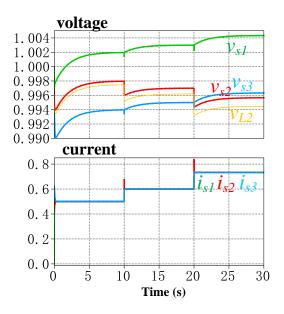

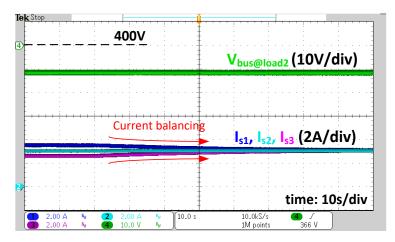

| Fig. 4.16. Voltage and current without secondary control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 90       |

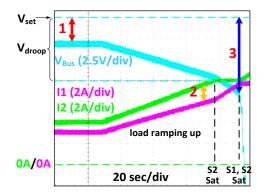

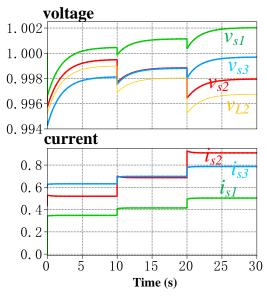

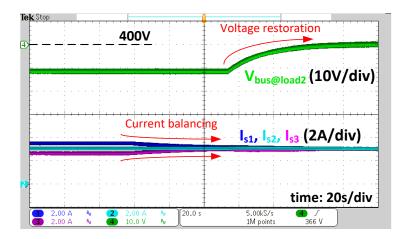

| Fig. 4.17. Voltage and current with voltage restoration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 90       |

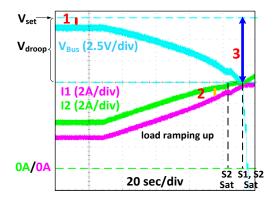

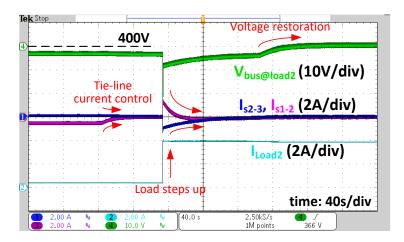

| Fig. 4.18. Voltage and current with voltage restoration and current sharing control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 90       |

| Fig. 4.19. Voltage and current with voltage restoration and tie-line current control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 90       |

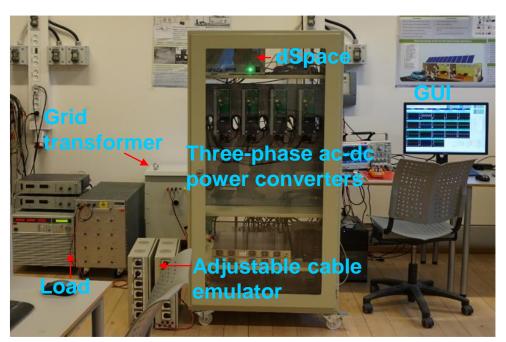

| Fig. 4.20. Experimental setup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 91       |

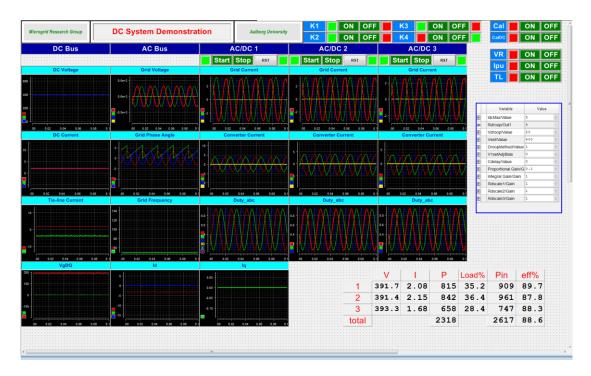

| Fig. 4.21. The designed graphical user interface (GUI).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 92       |

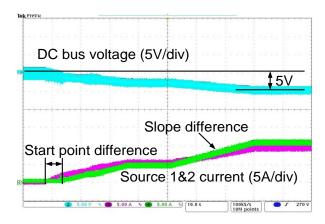

| Fig. 4.22. Bus voltage and source current with tie-line resistances.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 93       |

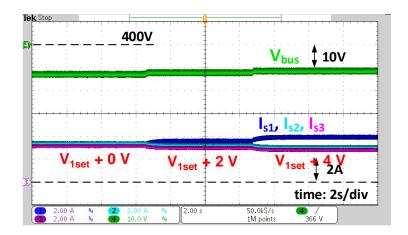

| Fig. 4.23. Bus voltage and source current with drifted voltage set points.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 94       |

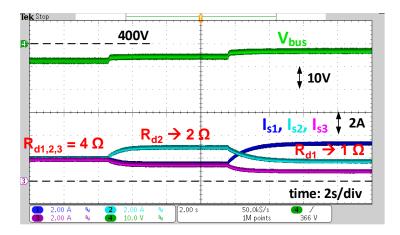

| Fig. 4.24. Bus voltage and source current with different droop resistances.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 95       |

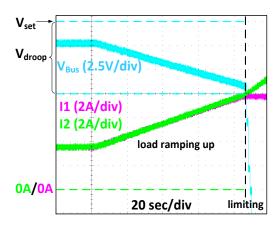

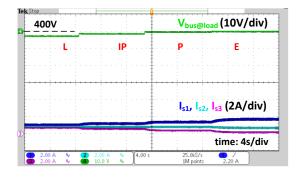

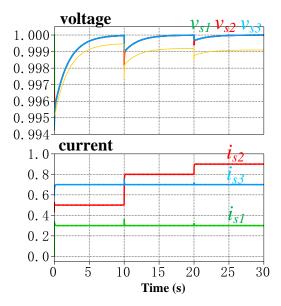

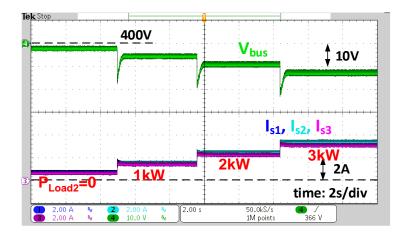

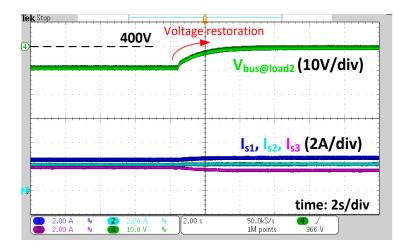

| Fig. 4.25. Experimental waveforms with voltage restoration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 96       |

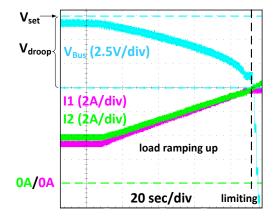

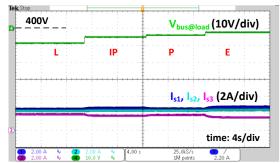

| Fig. 4.26. Experimental waveforms with current balancing control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 96       |

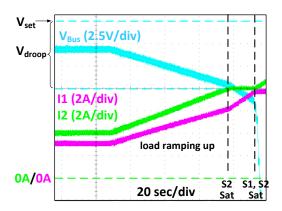

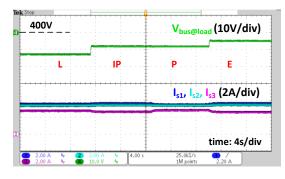

| Fig. 4.27. Experimental waveforms with both voltage restoration and current balancing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 97       |

| Fig. 4.28. Experimental waveforms with direct tie-line current control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 97       |

| Fig. 5.1. DC power distribution in a future home.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 100      |

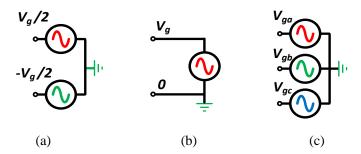

| Fig. 5.2. Different residential ac distribution interfaces: (a) split-phase single-phase system; (b) asyn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | nmetric  |

| single-phase system; (c) three-phase system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 101      |

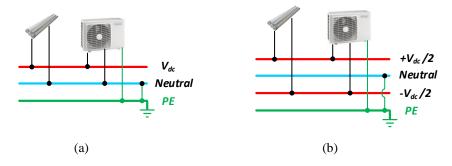

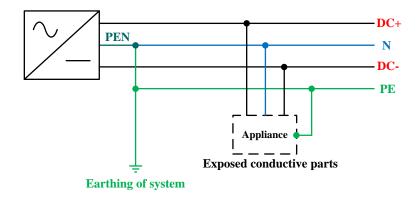

| Fig. 5.3. Configurations of dc power distribution systems: (a) unipolar; (b) bipolar.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 101      |

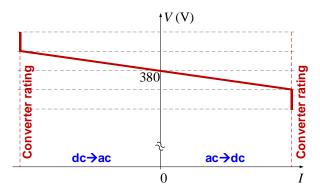

| Fig. 5.4. DC side droop characteristic of the ECC converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 102      |

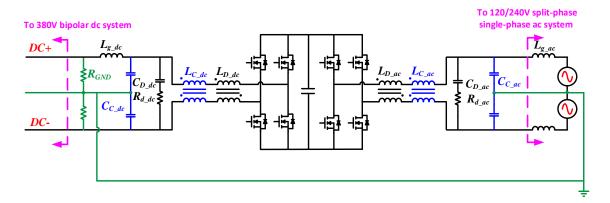

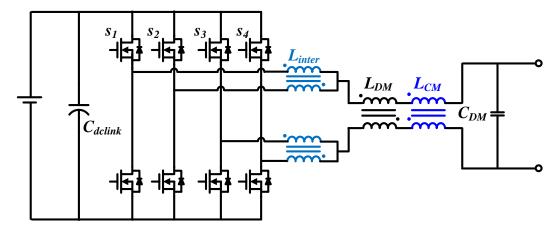

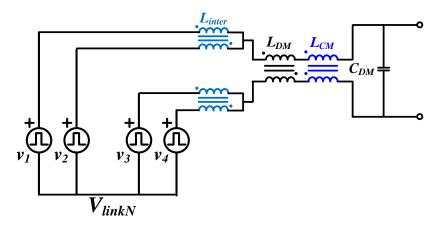

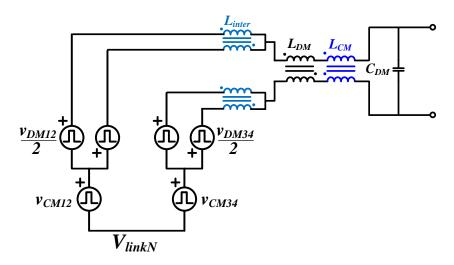

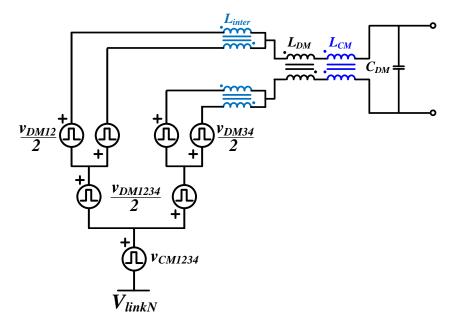

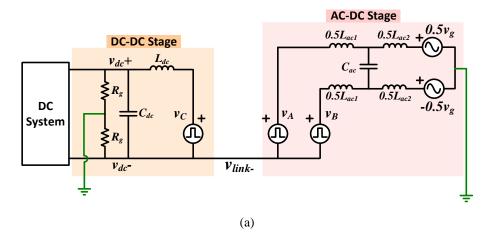

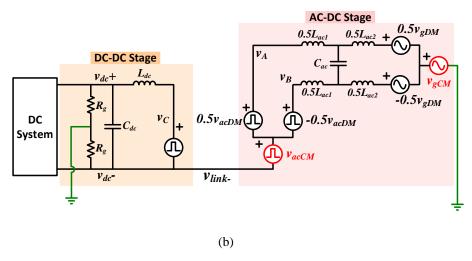

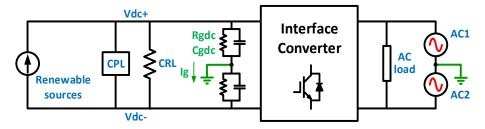

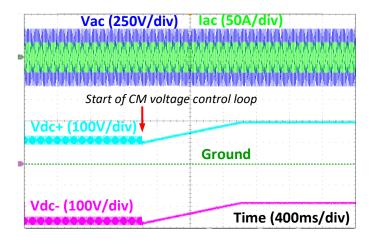

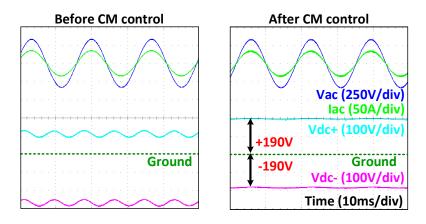

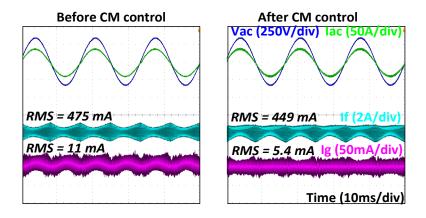

| Fig. 5.5. Two-stage bidirectional single-phase ac-dc converter with common-mode decoupling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 103      |

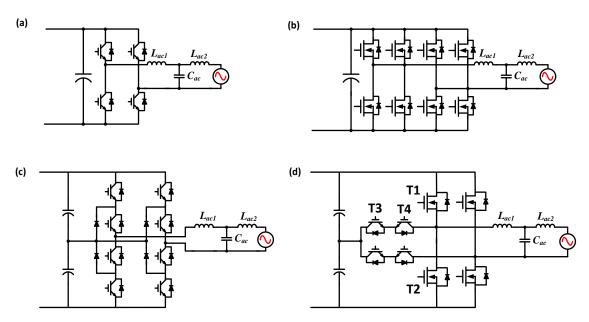

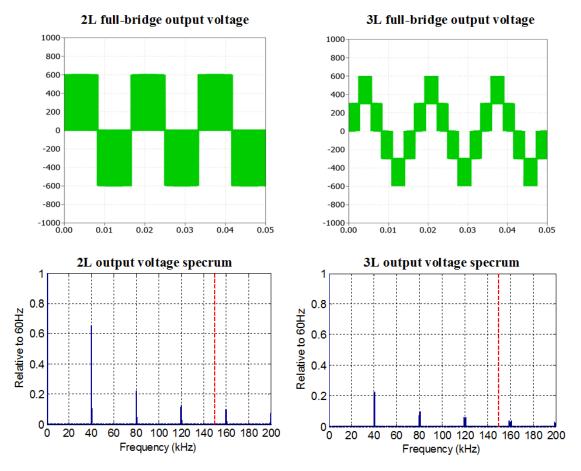

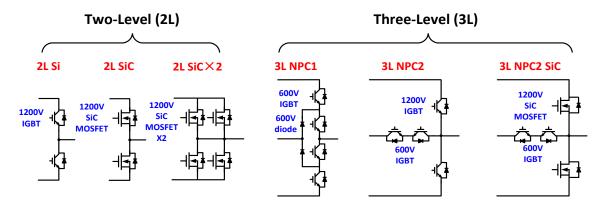

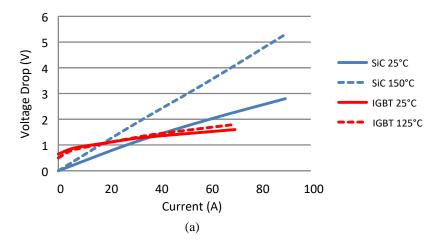

| Fig. 5.6. Evaluated bidirectional ac-dc topologies: (a) 2L full-bridge; (b) 2L full-bridge with particles and the particles of the particles o | ralleled |

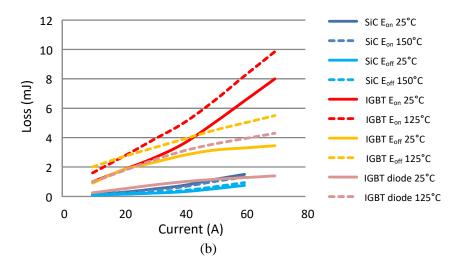

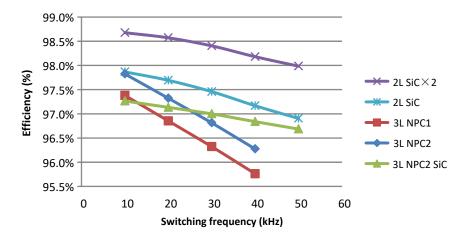

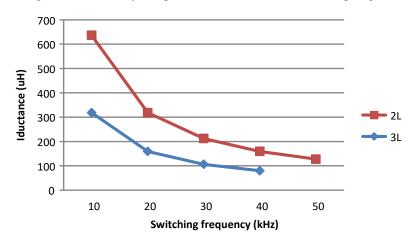

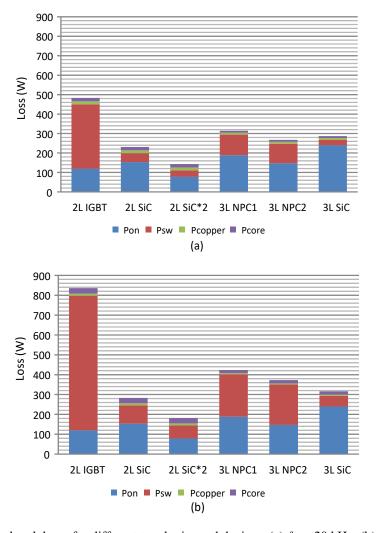

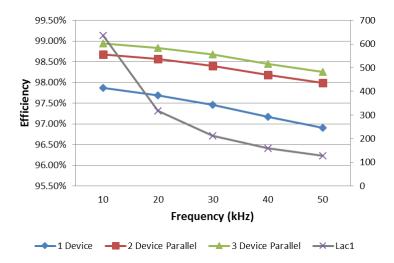

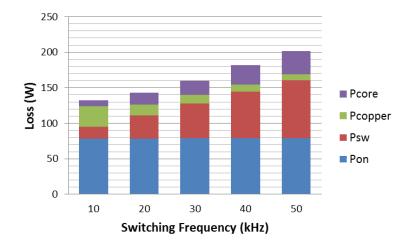

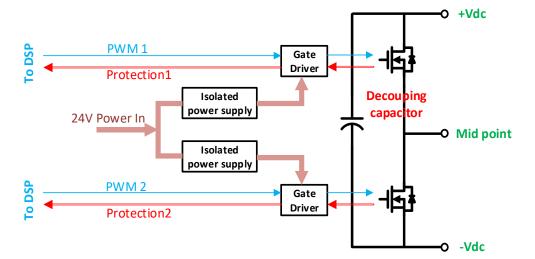

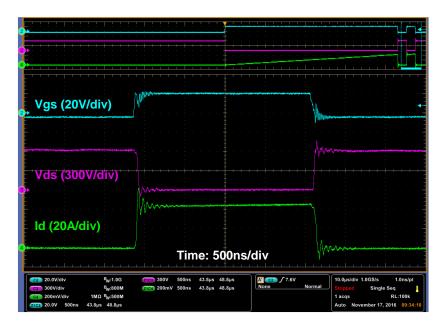

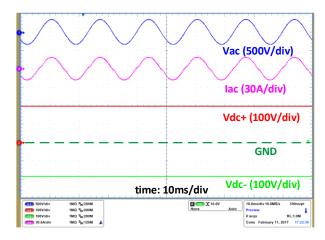

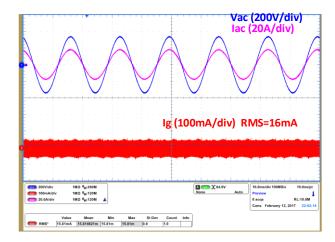

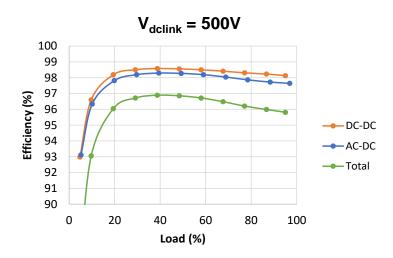

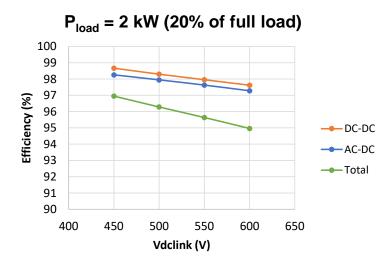

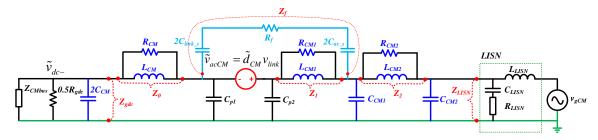

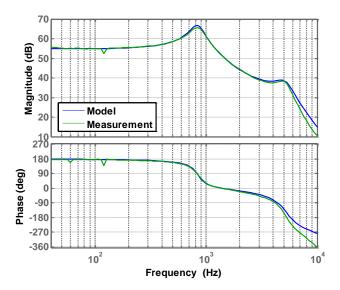

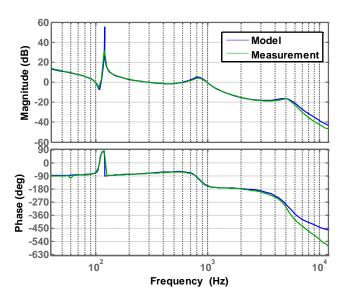

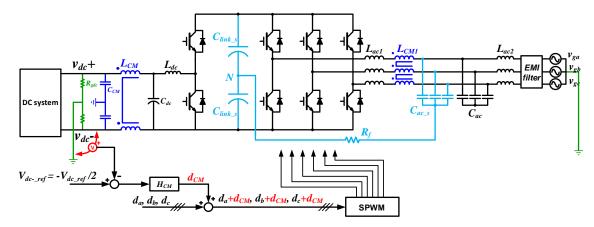

| MOSFETs; (c) 3L diode clamped; (d) 3L T-type.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 105      |