# Characterization and Application of Wide-Band-

## **Gap Devices for High Frequency Power Conversion**

### Zhengyang Liu

Dissertation submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical Engineering

Fred C. Lee (Chair)

Qiang Li

Dong S. Ha

Virgilio A. Centeno

Alfred L. Wicks

May 2<sup>nd</sup>, 2017 Blacksburg, Virginia

Keywords: Gallium nitride, high frequency, soft switching, package, rectifier/inverter

© 2017, Zhengyang Liu

## Characterization and Application of Wide-Band-

## **Gap Devices for High Frequency Power Conversion**

### Zhengyang Liu

#### **Abstract**

Advanced power semiconductor devices have consistently proven to be a major force in pushing the progressive development of power conversion technology. The emerging wide-band-gap (WBG) material based power semiconductor devices are considered as gaming changing devices which can exceed the limit of silicon (Si) and be used to pursue groundbreaking high-frequency, high-efficiency, and high-power-density power conversion.

The switching performance of cascode GaN HEMT is studied at first. An accurate behavior-level simulation model is developed with comprehensive consideration of the impacts of parasitics. Then based on the simulation model, detailed loss breakdown and loss mechanism analysis are studied. The cascode GaN HEMT has high turn-on loss due to the reverse recovery charge and junction capacitor charge, and the common source inductance (CSI) of the package; while the turn-off loss is extremely small attributing to unique current source turn off mechanism of the cascode structure.

With this unique feature, the critical conduction mode (CRM) soft switching technique is applied to reduce the dominant turn on loss and significantly increase converter efficiency. The switching frequency is successfully pushed to 5MHz while maintaining high efficiency and good thermal performance.

Traditional packaging method is becoming a bottle neck to fully utilize the advantages of GaN HEMT. So an investigation of the package influence on the cascode GaN HEMT is also conducted. Several critical parasitic inductance are identified, which cause high turn on loss and high parasitic ringing that may lead to device failure. To solve the issue, the stack-die package is proposed to eliminate all critical parasitic inductance, and as a result, reducing turn on loss by half and avoiding potential failure mode of the cascode GaN device effectively.

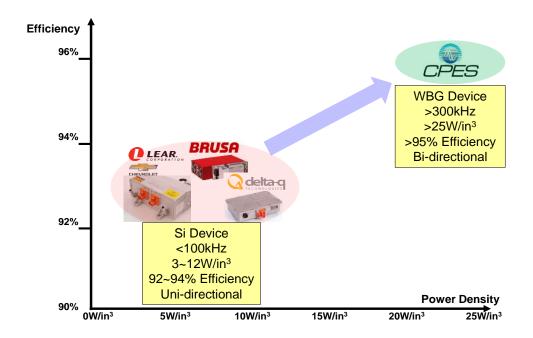

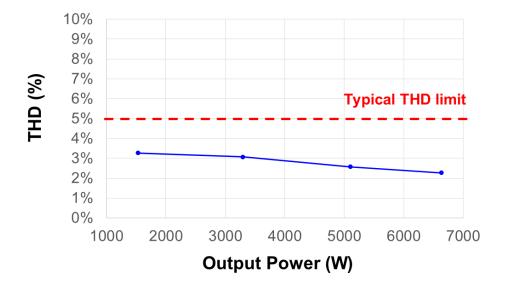

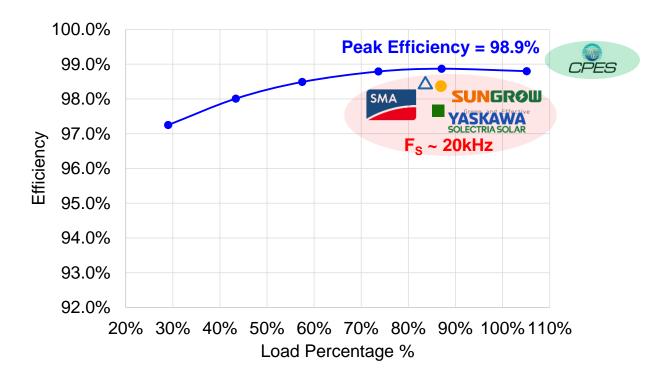

Utilizing soft switching and enhanced packaging, a GaN-based MHz totem-pole PFC rectifier is demonstrated with 99% peak efficiency and 700 W/in<sup>3</sup> power density. The switching frequency of the PFC is more than ten times higher than the state-of-the-art industry product while it achieves best possible efficiency and power density. Integrated power module and integrated PCB winding coupled inductor are all studied and applied in this PFC.

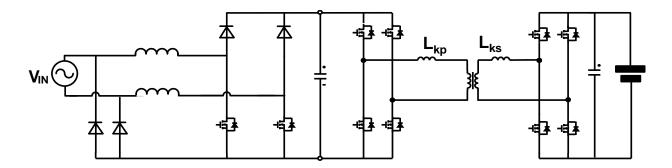

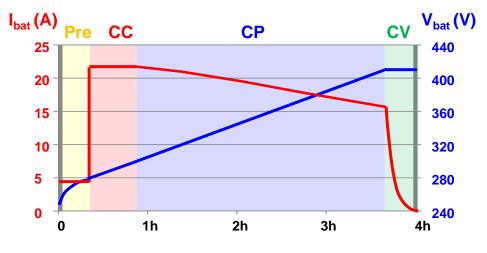

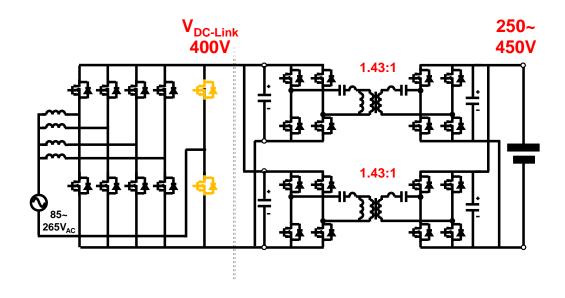

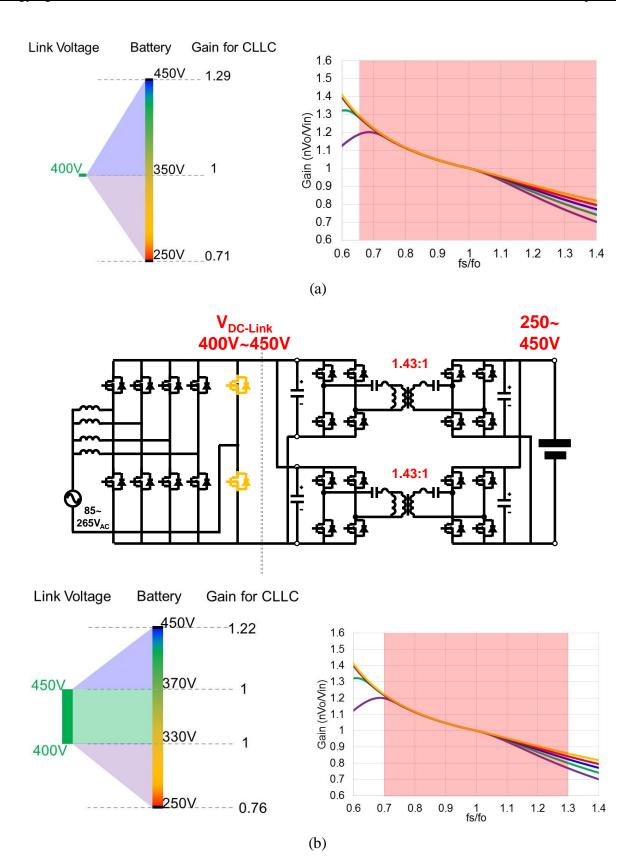

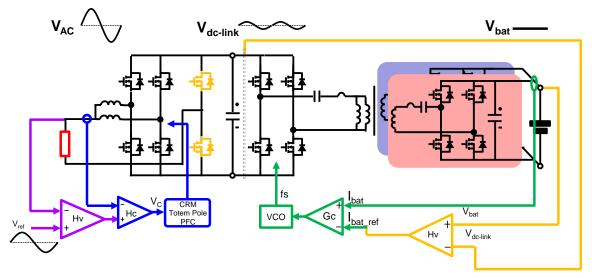

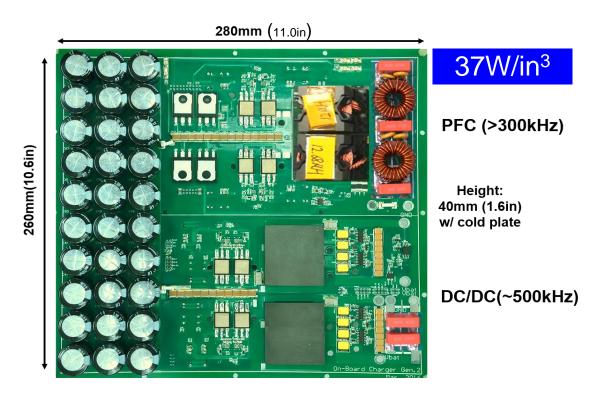

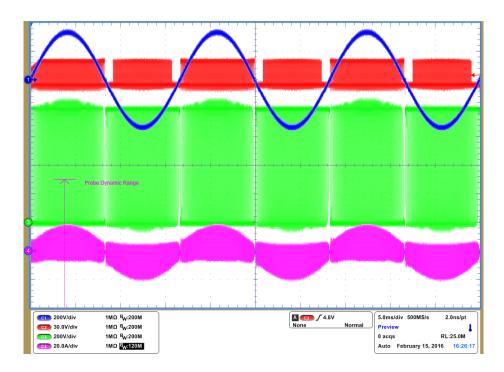

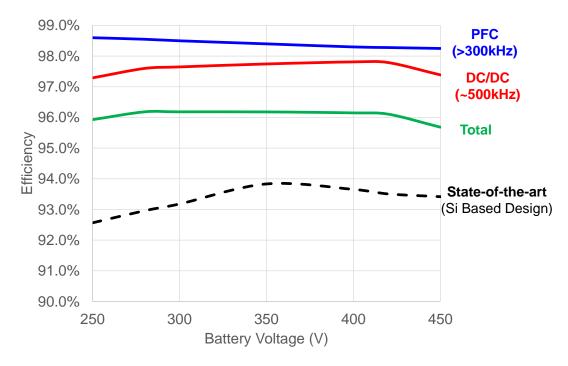

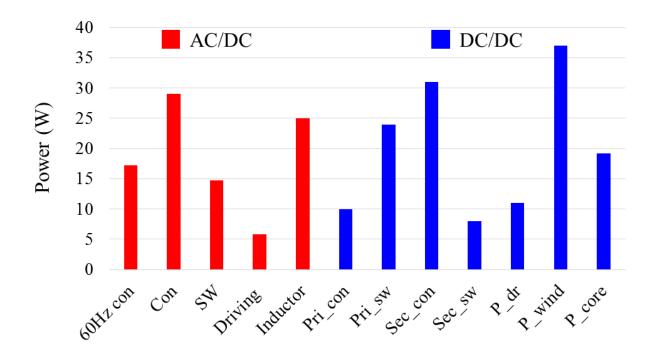

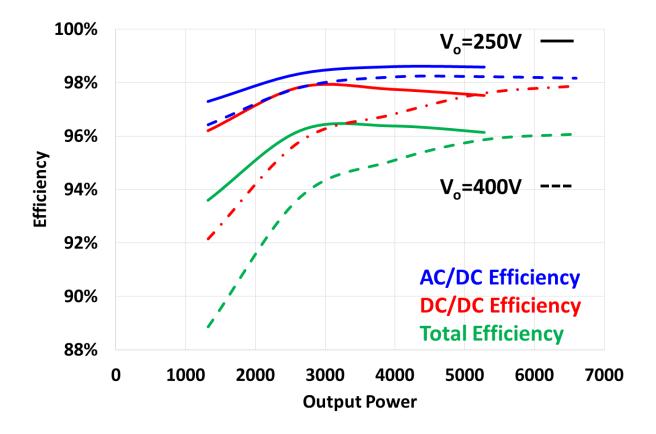

Furthermore, the technology of soft switching totem-pole PFC is extended to a bidirectional rectifier/inverter design. By using SiC MOSFETs, both operating voltage and power are dramatically increased so that it is successfully applied into a bidirectional on-board charger (OBC) which achieves significantly improved efficiency and power density comparing to the best of industrial practice. In addition, a novel 2-stage system architecture and control strategy are proposed and demonstrated in the OBC system.

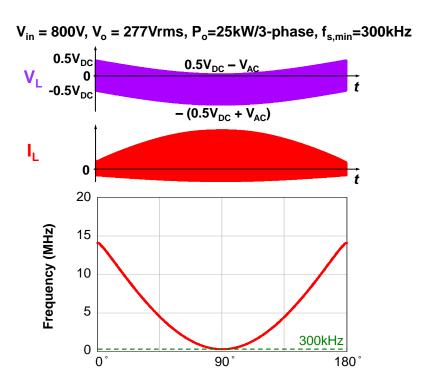

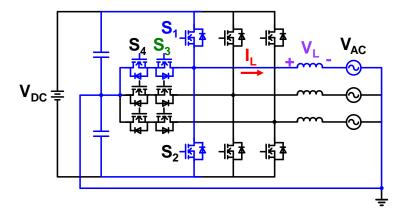

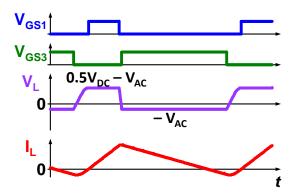

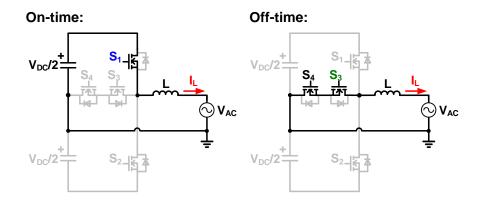

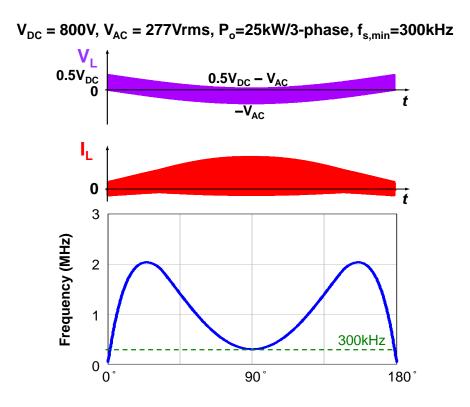

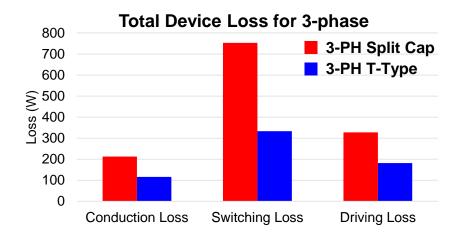

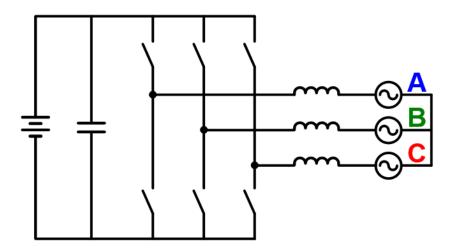

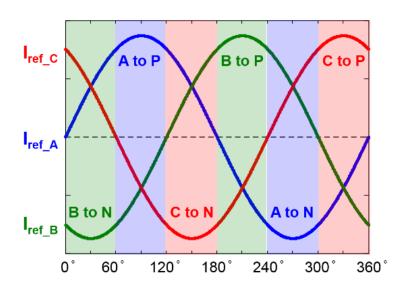

As a continued extension, the critical mode based soft switching rectifier/inverter technology is applied to three-phase AC/DC converter. The inherent drawback of critical mode due to variable frequency operation is overcame by the proposed new modulation method with the idea of frequency synchronization. It is the first time that a critical mode based modulation is demonstrated in the most conventional three phase H-bridge AC/DC converter, and with 99% plus efficiency at above 300 kHz switching frequency.

# Characterization and Application of Wide-Band-

### **Gap Devices for High Frequency Power Conversion**

### Zhengyang Liu

### **General Audience Abstract**

Power electronics and power conversion are enabling technologies for almost any applications that are powered by electricity. It is very widely used in consumer electronics, household and industrial appliances, automobiles, utilities, infrastructures, and etc. It is essential but at the same time people want it to be invisible. Therefore the development of power electronics is consistently moving toward high efficiency (less and less energy waste), high density (small volume and less weight), high reliability, and low cost.

Thanks to the development of silicon (Si) based semiconductor technology, especially silicon based power semiconductor devices, a great amount of achievements had been made in last three decades. However such high speed progress probably cannot be maintained for any longer since Si-based power devices are approaching their glass ceiling (theoretical limit) of what can be ultimately achieved. That is why people are looking for power devices made with material different than Si but with greater potential.

Gallium Nitride (GaN) and Silicon Carbide (SiC) based power devices are chosen due to its great potential. It is believed to outperform Si-based devices by 2-3 orders which means power converters made with GaN and/or SiC can be even more efficient, smaller and lighter, more

reliable, and of course with less cost. The most important approach to achieve such objective is high switching frequency.

In order to turn the vision into reality, there are a lot of technology barriers in front of us, which in summary are how to understand the device and how to use the device into real applications with efficient high frequency operation.

Therefore the major achievement of this work is comprehensive evaluation of GaN devices, and then demonstration of GaN and SiC in several AC/DC power converters for different applications.

In the evaluation of GaN devices, an accurate simulation model was built and verified. Then based on the assistance of the model, switching loss mechanism is elaborated. The major conclusion is GaN has large turn on loss and very small turn off loss so that soft switching, which at least achieves zero-voltage-switching (ZVS) turn on, is important for GaN.

Packaging related issues are addressed as well including analysis of package impacts on device performance and a new proposal of advanced package. It is very proud to claim that the proposal now are widely used by GaN device manufacturers into their real commercial products.

After the know-how of how to use GaN was built, the potential of GaN was demonstrated in several different applications. The focus of this dissertation is on its application in AC/DC rectifier/inverter. Critical mode based totem-pole rectifier/inverter were built for 1 kW server power, 6.6 kW on board charger, and 25 kW solar inverter. A series of challenges were identified and the corresponding solutions were proposed. Today, the proposed design is becoming a benchmark and many of the industrial people are adopting our technology and applying it into real high performance products

# To My Family

# And To Whom It May Concern

### Acknowledgments

First and foremost I would like to thank my advisor, Dr. Fred C. Lee for his guidance and education. His profound knowledge, rich experience, rigorous attitude, and challenging spirit deeply motivated me and will remain with me all the time. It is most honored to be advised by Dr. Lee. The experience of studying at CPES is absolutely unparalleled.

I am very grateful to my other committee members Dr. Qiang Li, Dr. Dong S. Ha, Dr. Virgilio Centeno, and Dr. Alfred L. Wicks. I cannot forget how Dr. Li helped me went through the most hard time of my research in CPES. He is always logical, patient, and gentle. Thanks for all the constructive and helpful suggestions offered by Dr. Li.

A special thanks to my colleague Dr. Xiucheng Huang. I am lucky to work with him from the first day I came to CPES. I learnt lots of hands-on experience from him, and got inspired many times through the discussion with him. It is a great honor that the joint work with Xiucheng was quickly recognized by many people in academia and industry within last few years.

Another special thanks to my colleagues Mr. Zhengrong Huang, Mr. Bin Li and Mr. Yuchen Yang. We have worked very closely on several projects and without their contribution we cannot achieve so much.

I would like to thank the previous package lab manager Dr. Wenli Zhang as well. Without his help, I cannot demonstrate my idea with real prototypes.

I really appreciate the communications and suggestions from Dr. Dushan Boroyevich, Dr. Paolo Mattavelli, Dr. Khai Ngo, Dr. Rolando Burgos, and Dr. Guo-Quan Lu in High Density Integration (HDI) group. Their generous inputs make my work more thorough.

It is a great pleasure to study and work at CPES. I would like to thank all my colleagues in the Power Management Consortium (PMC) group: Dr. David Reusch, Dr. Mingkai Mu, Dr. Yingyi Yan, Dr. Weiyi Feng, Dr. Daocheng Huang, Dr. Zijian Wang, Mr. Shu Ji, Mr. Haoran Wu, Dr. Yipeng Su, Mr. Wei Zhang, Mr. Li Jiang, Dr. Shuilin Tian, Dr. Pei-Hsin Liu, Dr. Dongbin Hou, Dr. Yang Jiao, Mr. Sizhao Lu, Mr. Chao Fei, Mr. Xuebing Chen, Ms. Yincan Mao, Mr. Zhongsheng Cao, Mr. Syed Bari, Mr. Tao Liu, Ms. Virginia Li, Mr. Junjie Feng, Mr. Yi-Hsun Hsieh, Mr. Mohamed Ahmed, Mr. Yadong Lyu, Mr. Rimon Gadelrab, Mr. Shishuo Zhao, Dr. Xinke Wu, Dr. Xin Ming, Dr. Weijing Du, Dr. Shuojie She, Mr. Yan-Cun Li, Dr. Kenichiro Tanaka, Dr. Minfan Fu, Mr. Furong Xiao, Mr. Guo Xu, and Dr. Rong Xu. My thanks also go to many of the other students and visiting scholars I have met in CPES.

The wonderful staffs make my life in CPES easier and happier. I sincerely thank Ms. Teresa Shaw, Mr. Douglas Sterk, Mr. David Gilham, Ms. Linda Gallagher, Ms. Teresa Rose, Ms. Marianne Hawthorne, Ms. Linda Long, Mr. Igor Cvetkovic, and Ms. Lauren Shutt for their help and support.

I particularly want to thank my dear friends including but not limited to Dr. Yipeng Su, Dr. Xiucheng Huang, Dr. Yang Jiao, Dr. Bo Wen, Mr. Chao Fei, Dr. Xin Ming, Mr. Bin Li, Mr. Jiawei Zhao, and Mr. Joseph Kozak who drink and drunk with me in Blacksburg sharing lots of happiness and sadness. "Beer is proof that God loves us and wants us to be happy".

Six years in CPES Virginia Tech, there are too many people who ever gave me help that I cannot mention one by one. I take this chance to thank all of them.

In addition, this work was supported by CPES Power Management Consortium, and the Engineering Research Center Shared Facilities supported by the National Science Foundation under NSF Award Number EEC-9731677. Any opinions, findings and conclusions or

recommendations expressed in this material are those of the author and do not necessarily reflect those of the National Science Foundation.

The information, data, or work presented herein was funded in part by the Office of Energy Efficiency and Renewable Energy (EERE), U.S. Department of Energy, under Award Number DE-EE0006521 with North Carolina State University, PowerAmerica Institute.

The information, data, or work presented herein was funded in part by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

This material is partially based upon work supported by the U.S. Department of Energy, Office of Energy Efficiency and Renewable Energy, under the project of High Efficiency High Density GaN Based 6.6kW Bi-Directional On-board Charger for PEVs, through Delta Products Corp, under contract number DE-EE0006834.

The author would like to thank Transphorm for providing GaN device samples; and to thank Simplis Technologies for proving simulation software.

# **Table of Contents**

| Chapte | r 1. Introduction                                              | 1  |

|--------|----------------------------------------------------------------|----|

| 1.1    | Overview of Wide-Band-Gap (WBG) Power Devices                  | 1  |

| 1.2    | Enhancement Mode GaN vs Depletion Mode GaN                     | 5  |

| 1.3    | Characteristics of 600 V Cascode GaN HEMT                      | 9  |

| 1.4    | Proposed Dissertation Outline                                  | 16 |

| Chapte | r 2. Characterization and Modeling of GaN Device               | 18 |

| 2.1    | Package Parasitics Extraction and Simulation Model Development | 20 |

| 2.2    | Switching Loss Mechanism Analysis and Soft Switching           | 39 |

| 2.3    | Package Impacts of Cascode GaN                                 | 46 |

|        | 2.3.1 Common Source Inductance of Cascode GaN Package          | 46 |

|        | 2.3.2 Potential Failure Mode                                   | 50 |

|        | 2.3.3 Package Improvement Method                               | 54 |

|        | 2.3.4 Evaluation of GaN HEMT in Stack-Die Package              | 60 |

| Chapte | r 3. Application of GaN for PFC above MHz                      | 65 |

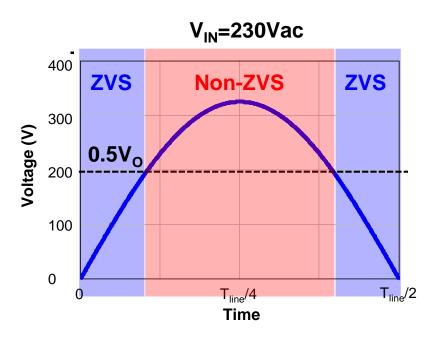

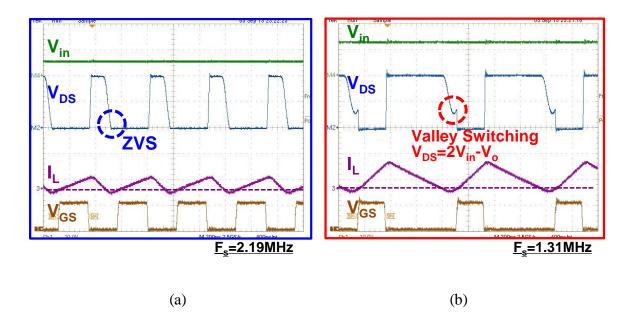

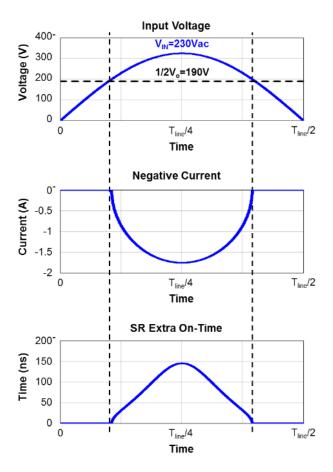

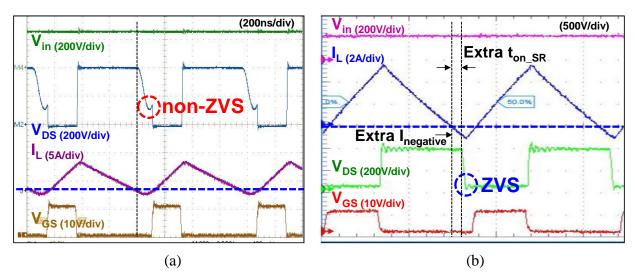

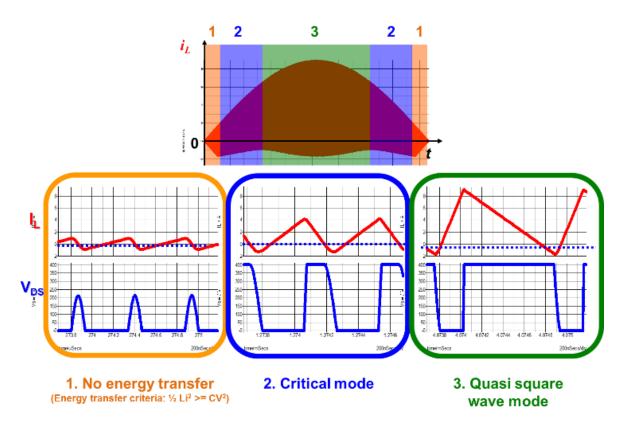

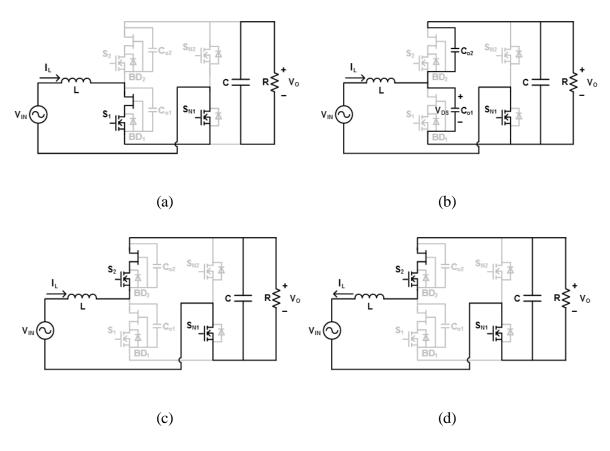

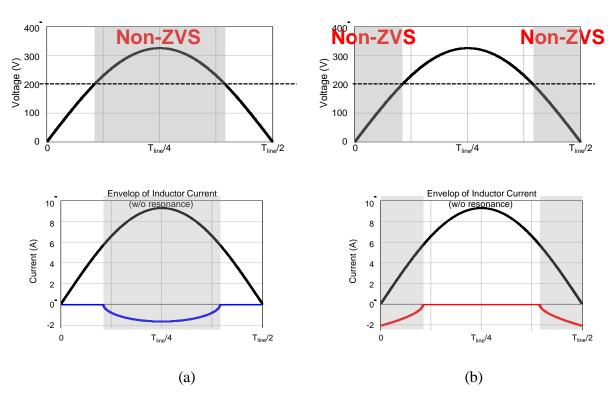

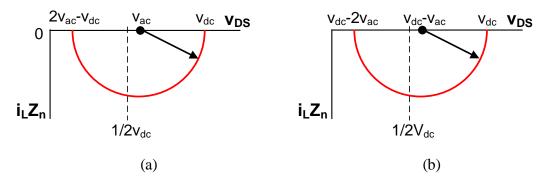

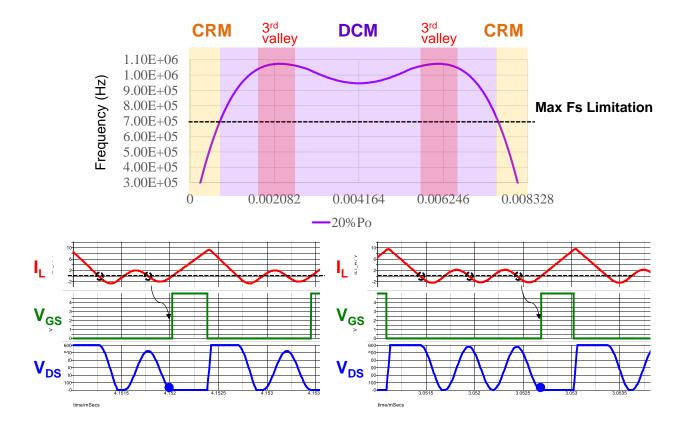

| 3.1    | Modified CRM for Achieving ZVS                                 | 69 |

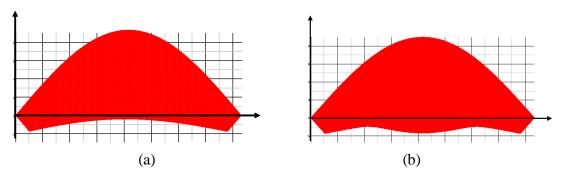

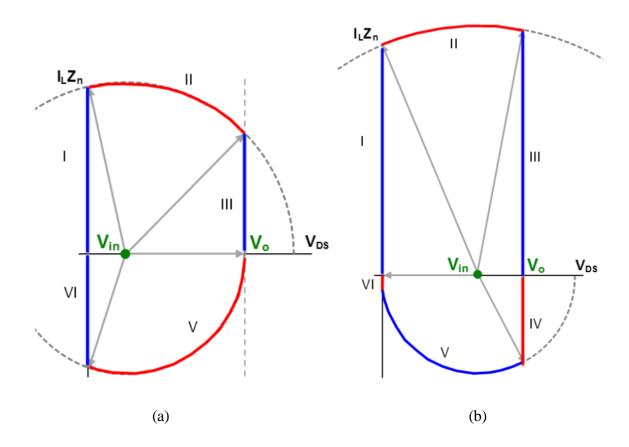

| 3.2    | Programmed On-Time to Reduce THD                               | 75 |

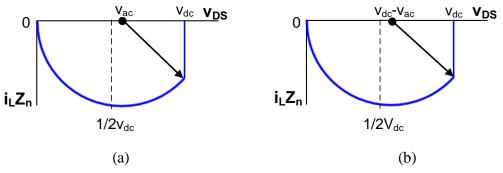

|        | 3.2.1 Operation Mode Analysis                                  | 77 |

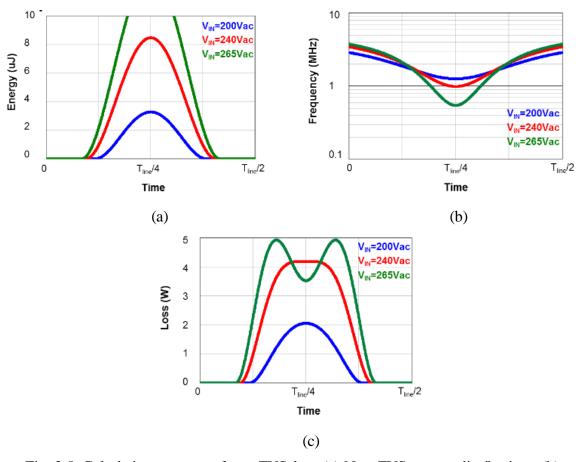

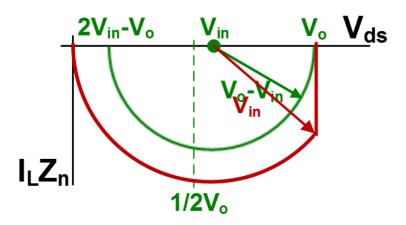

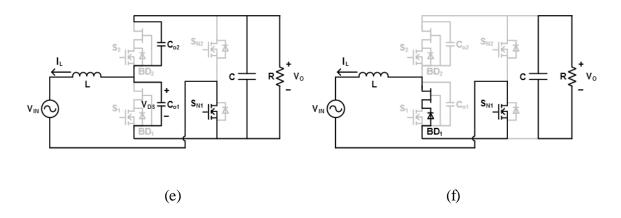

|        | 3.2.2 State-Space Trajectory Analysis                          | 83 |

|        | 3.2.3 Proposed Programmed On-Time Control                      | 84 |

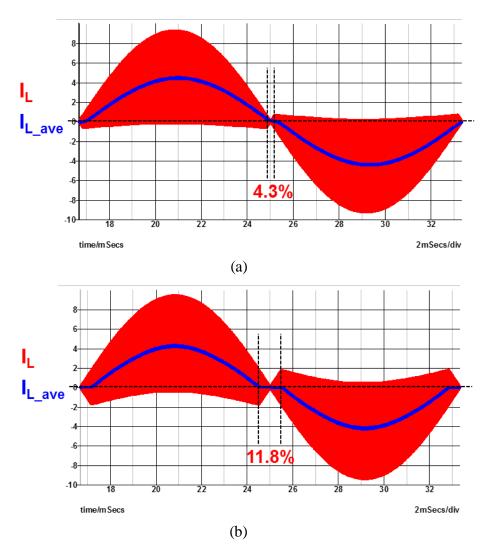

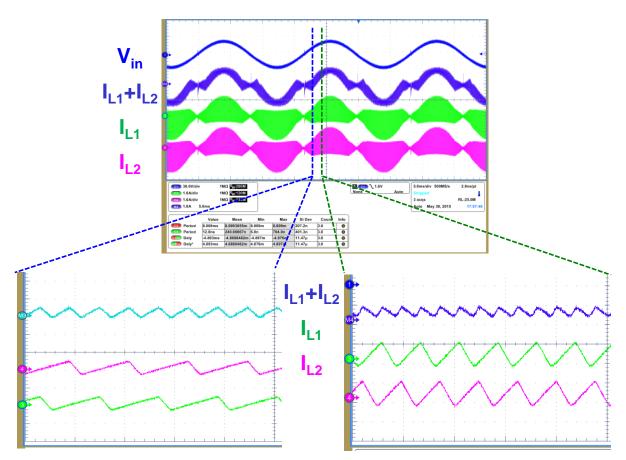

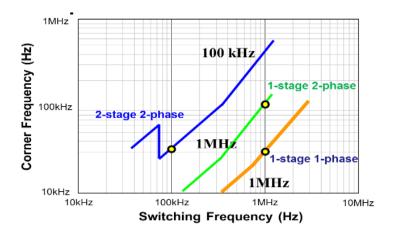

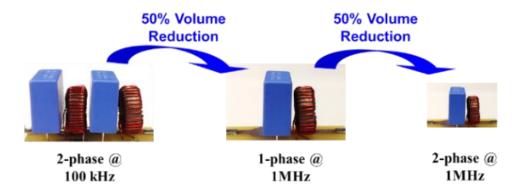

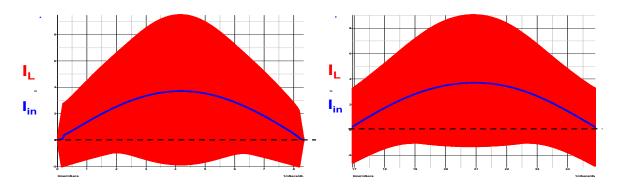

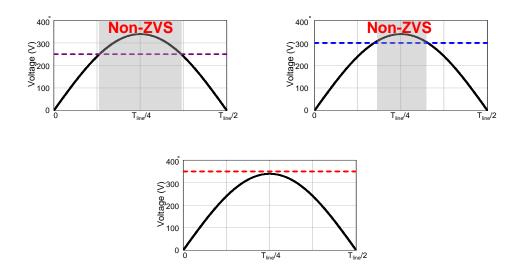

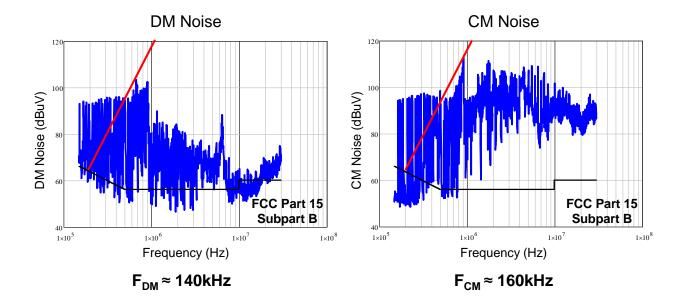

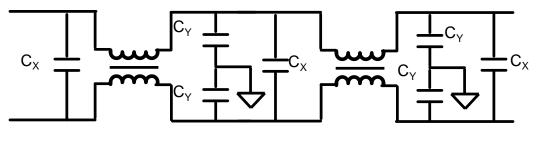

| 3.3    | Challenge of Interleaving to Reduce Current Ripple                 | 87             |

|--------|--------------------------------------------------------------------|----------------|

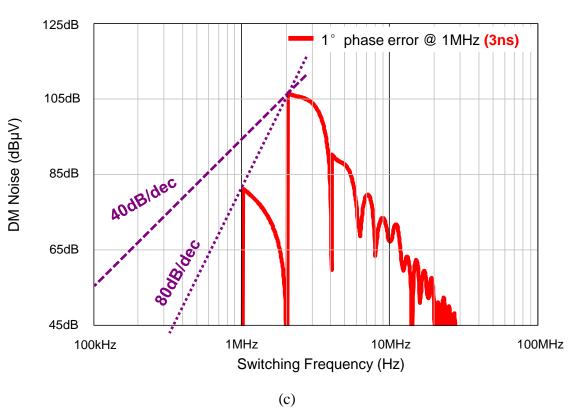

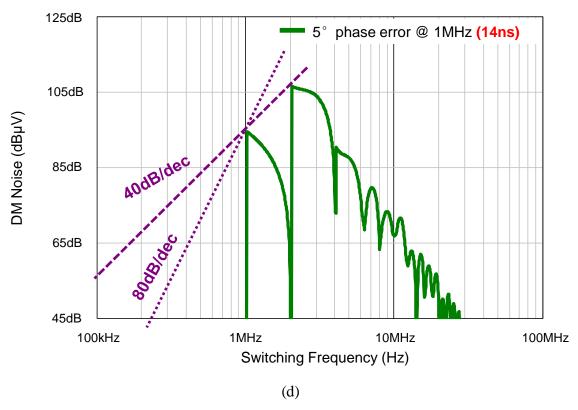

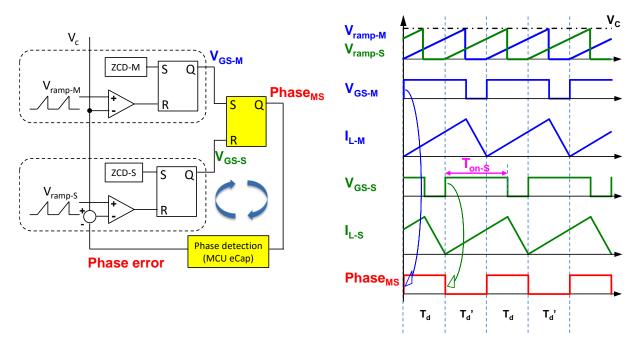

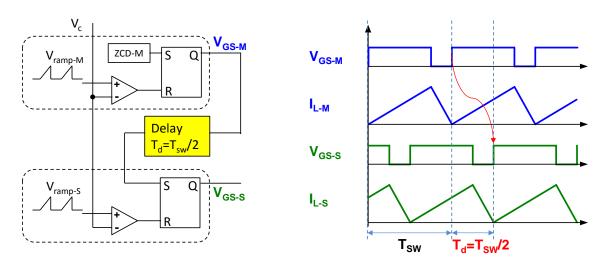

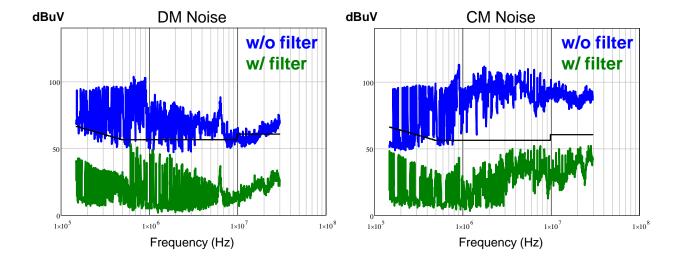

|        | 3.3.1 Impact of Interleaving Control on MHz Totem-Pole PFC and its | s Differential |

|        | Mode (DM) Filter                                                   | 87             |

|        | 3.3.2 Performance Comparison between Closed-loop Interleaving an   | d Open-loop    |

|        | Interleaving for MHz CRM Totem-Pole PFC                            | 90             |

|        | 3.3.3 Optimization of Open-Loop Interleaving                       | 98             |

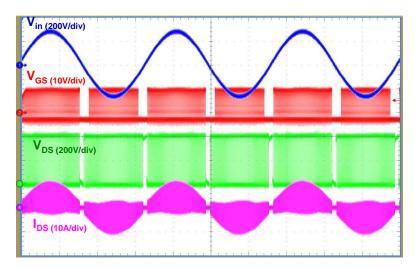

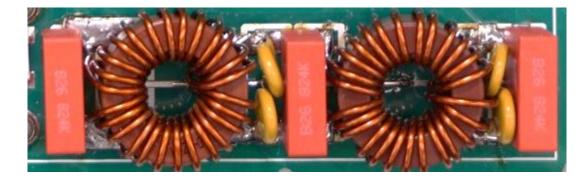

| 3.4    | Hardware Demonstration                                             | 103            |

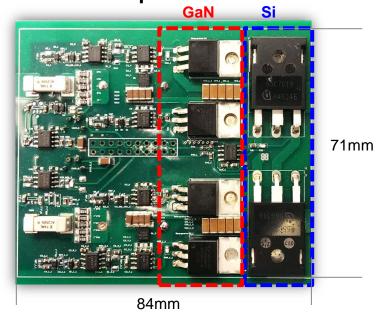

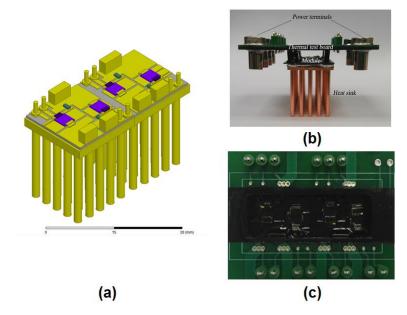

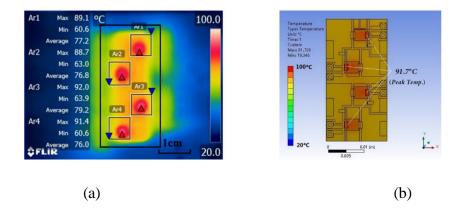

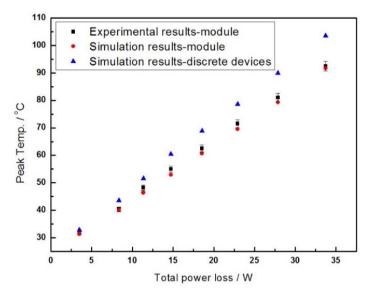

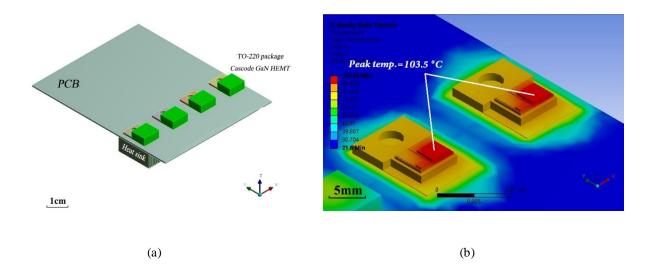

|        | 3.4.1 Discrete GaN vs. GaN Module                                  | 103            |

|        | 3.4.2 Discrete Inductor vs. Integrated Magnetics                   | 111            |

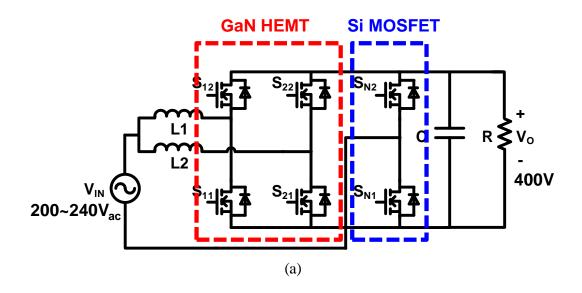

| Chapte | er 4. Bidirectional Rectifier/Inverter                             | 120            |

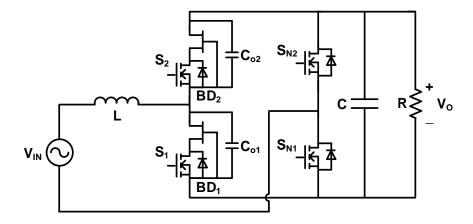

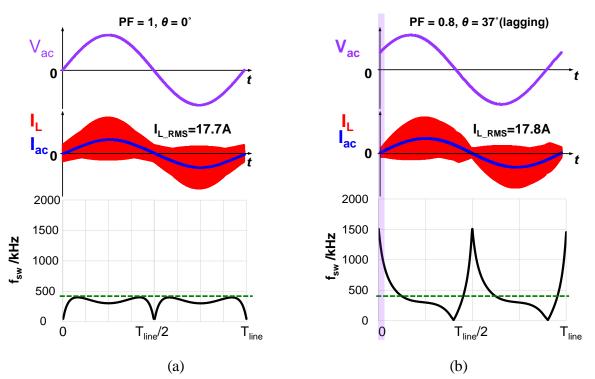

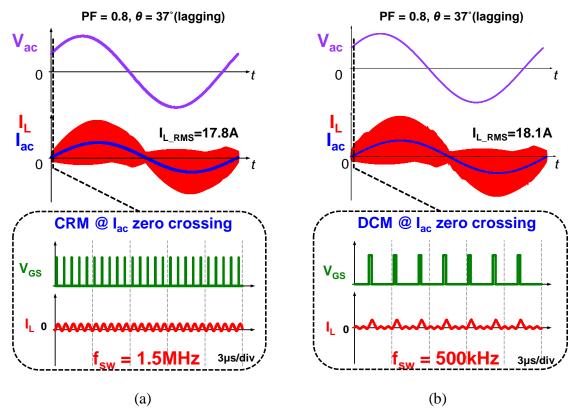

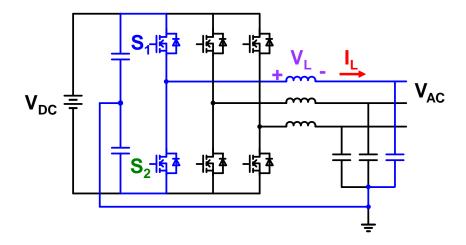

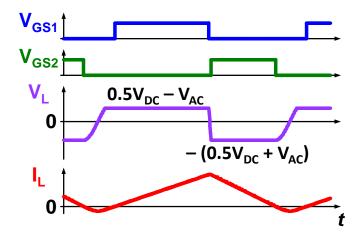

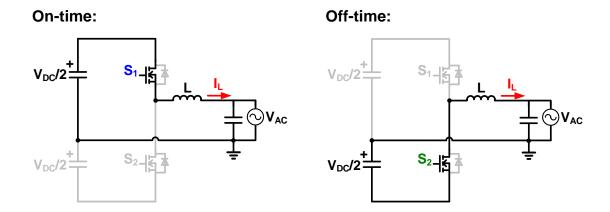

| 4.1    | Design Consideration for Grid Interface                            | 120            |

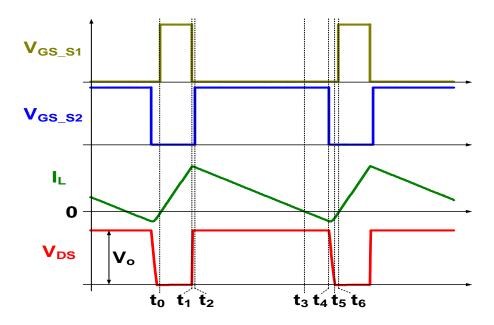

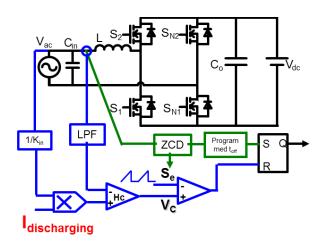

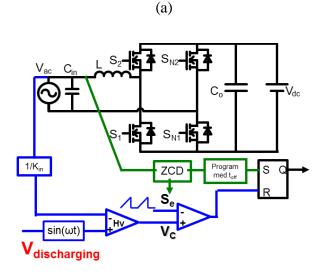

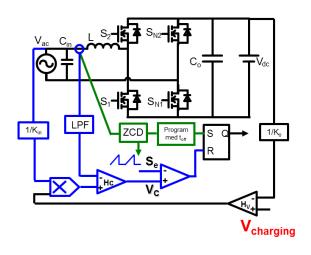

|        | 4.1.1 Development of Universal Controller                          | 120            |

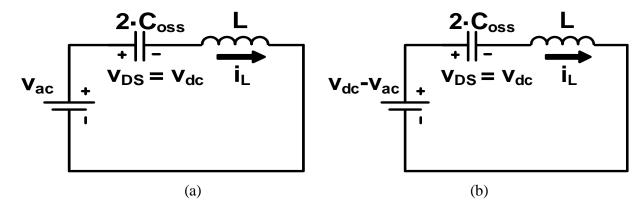

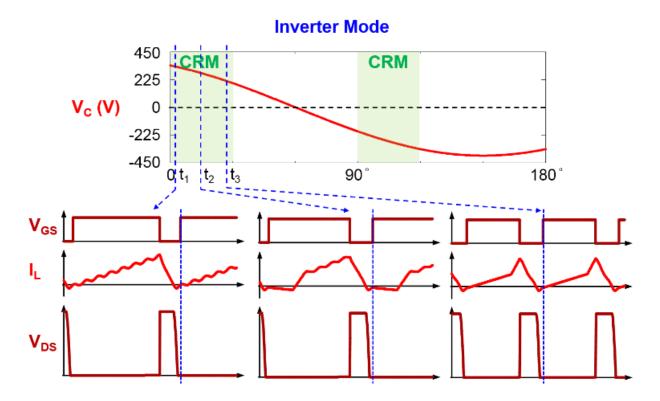

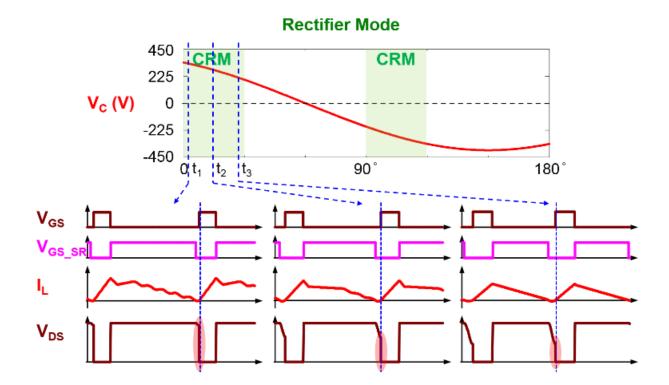

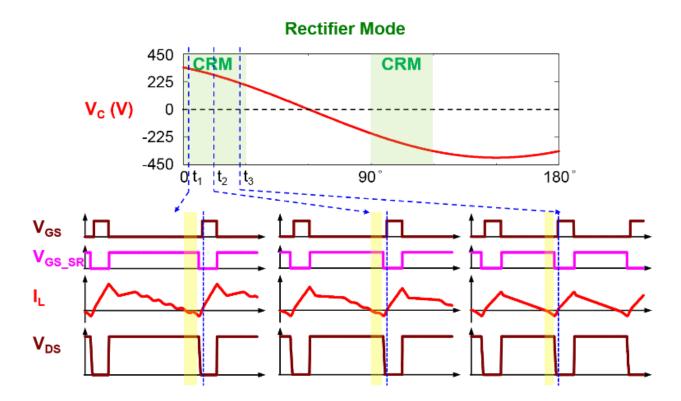

|        | 4.1.2 Achieving ZVS in Both Rectifier and Inverter                 | 125            |

|        | 4.1.3 Light Load Efficiency Improvement                            | 129            |

|        | 4.1.4 Provide Reactive Power                                       | 131            |

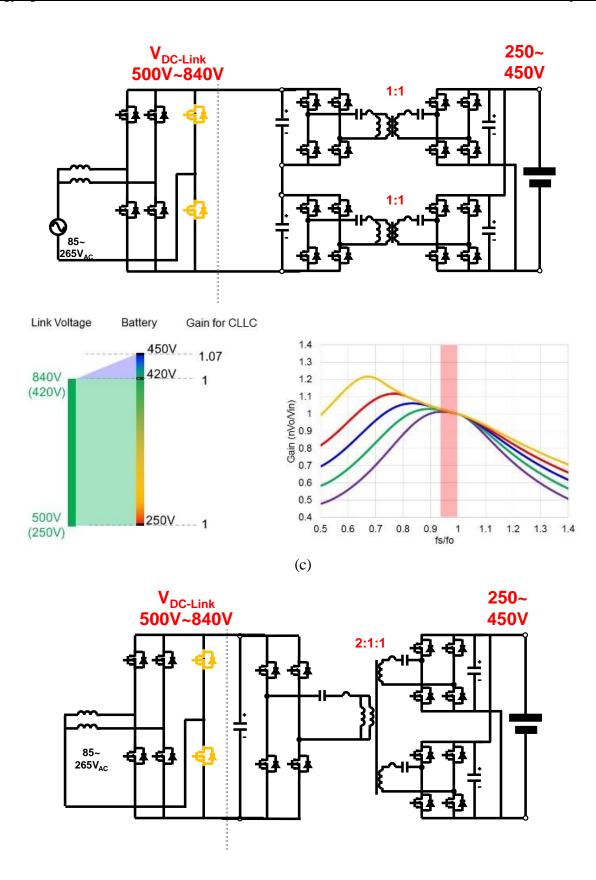

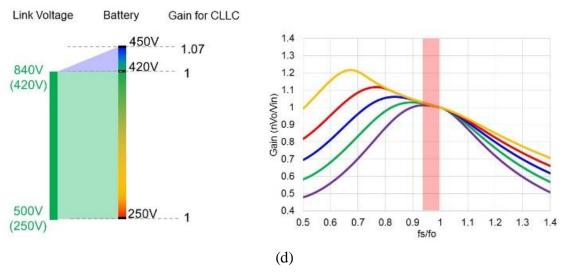

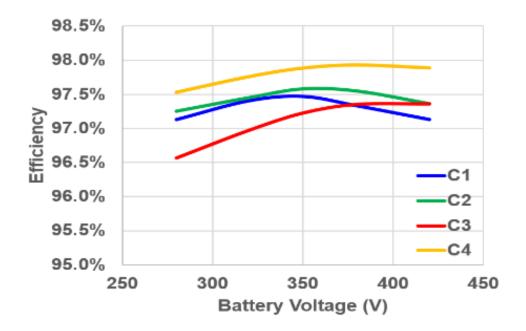

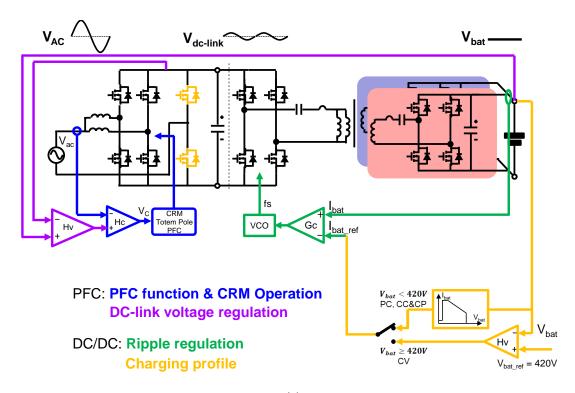

| 4.2    | Proposed Novel System Architecture for On Board Charger (OBC)      | 133            |

| 4.3    | Hardware Demonstration                                             | 142            |

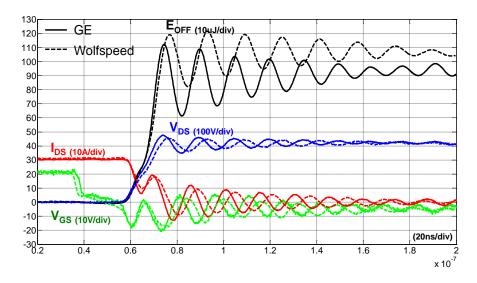

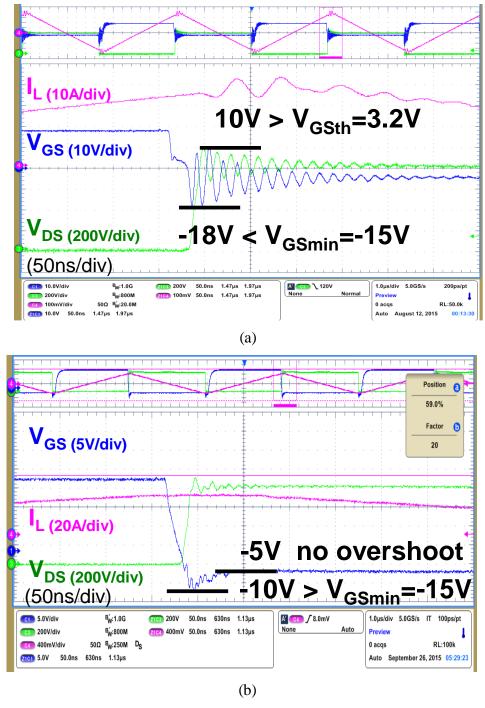

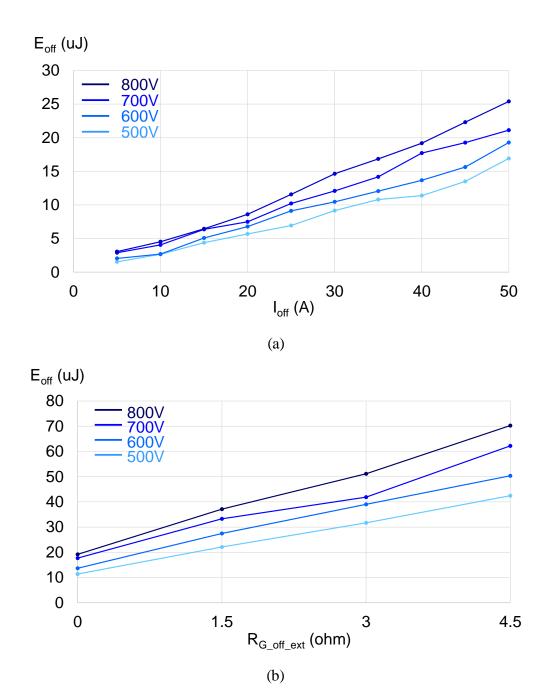

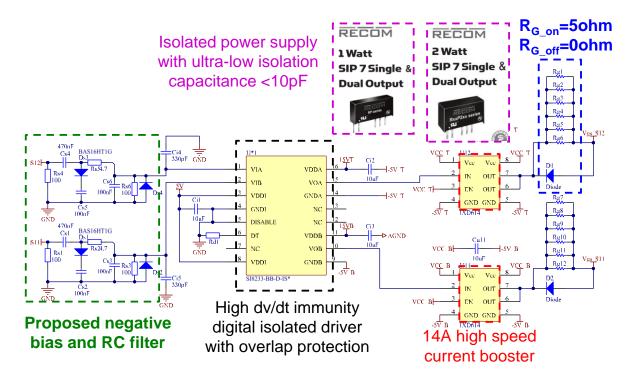

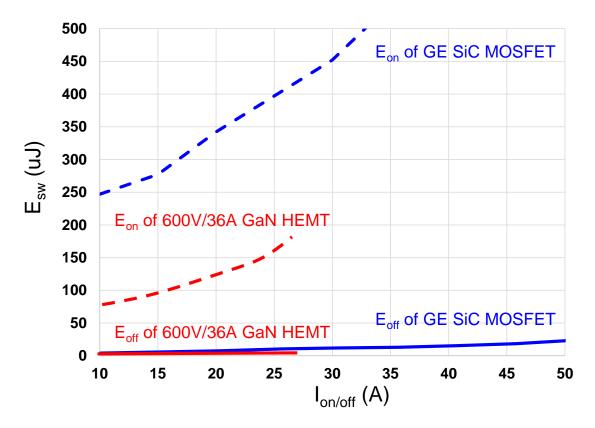

|        | 4.3.1 Evaluation of Suitable 1.2kV SiC MOSFET                      | 142            |

|        | 4.3.2 Prototype and Experimental Results                           | 150            |

| Chapte | er 5. Extension to Three-Phase Rectifier/Inverter                  | 158            |

| Refere | nce                                                | 185 |

|--------|----------------------------------------------------|-----|

| Chapte | er 6. Conclusions and Future Work                  | 183 |

| 5.3    | Hardware Demonstration                             | 179 |

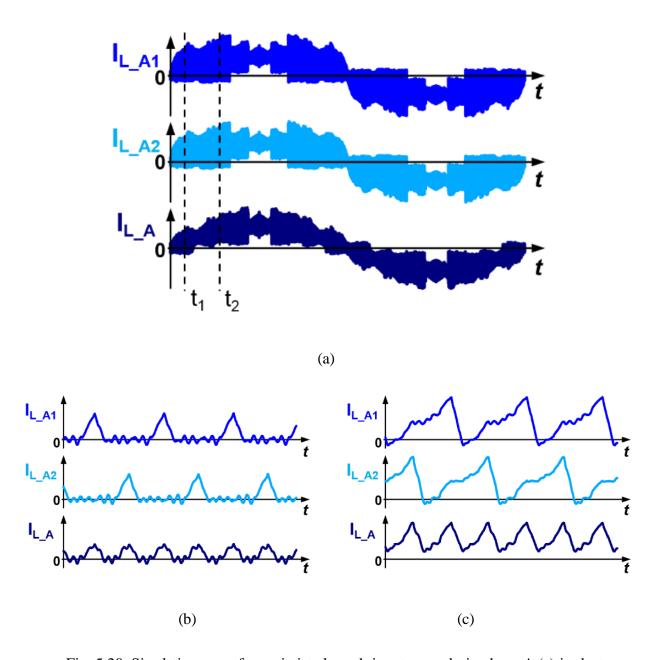

|        | 5.2.3 Simulation Verification                      | 176 |

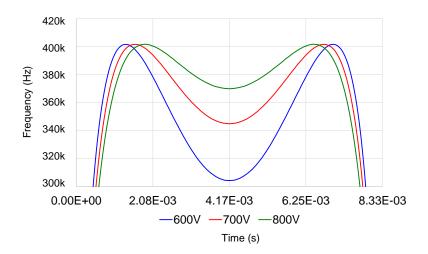

|        | 5.2.2 Frequency Synchronization                    | 170 |

|        | 5.2.1 Extension from Single-Phase to Three-Phase   | 164 |

| 5.2    | Proposed DPWM + CRM + Fs. Sync. DCM Modulation     | 164 |

| 5.1    | Prior Art of Three-Phase Rectifier/Inverter in CRM | 159 |

# **List of Figures**

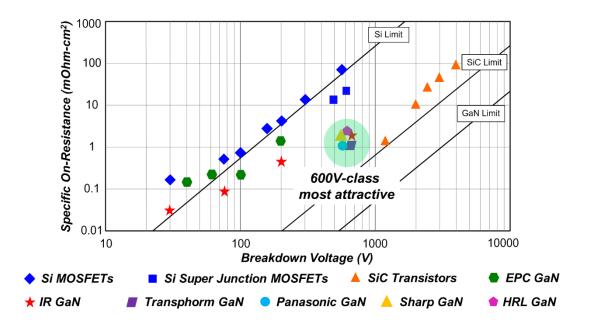

| Fig. 1.1. Specific on-resistance vs breakdown voltage for Si, SiC, and GaN                                         | 4        |

|--------------------------------------------------------------------------------------------------------------------|----------|

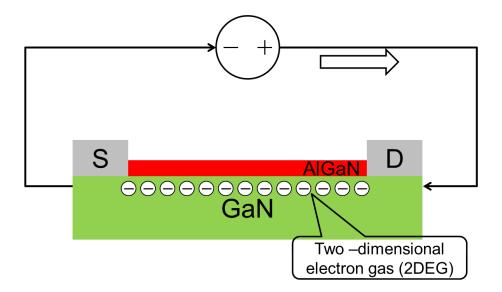

| Fig. 1.2. Basic structure of GaN device and its piezoelectric property                                             | 5        |

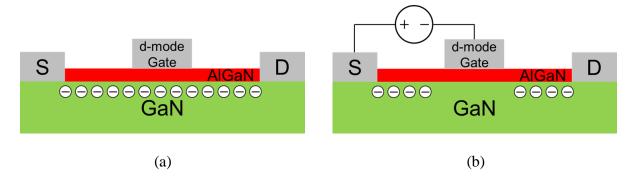

| Fig. 1.3. Basic structure of depletion mode GaN device, (a) on state, (b) off state                                | 6        |

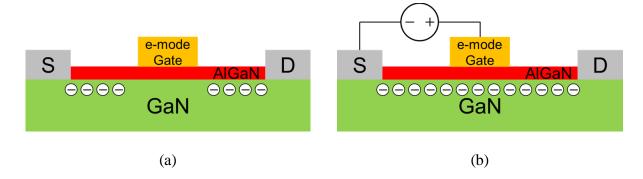

| Fig. 1.4. Basic structure of enhancement mode GaN device, (a) off state, and (b) on state                          | 6        |

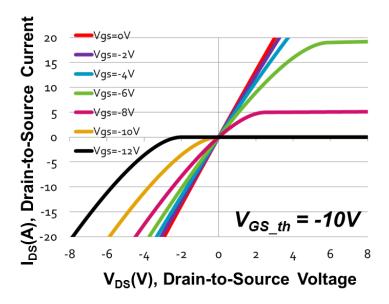

| Fig. 1.5. I-V characteristics of depletion mode GaN                                                                | 7        |

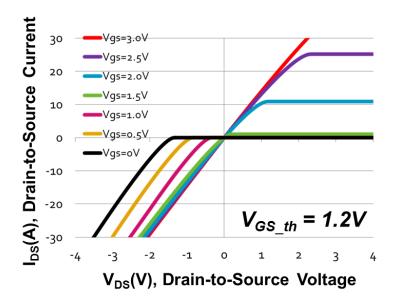

| Fig. 1.6. I-V characteristics of enhancement mode GaN                                                              | 7        |

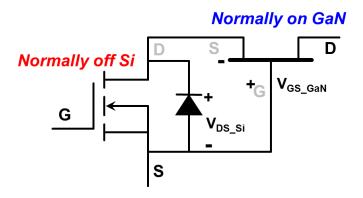

| Fig. 1.7. Cascode structure for depletion mode GaN                                                                 | 10       |

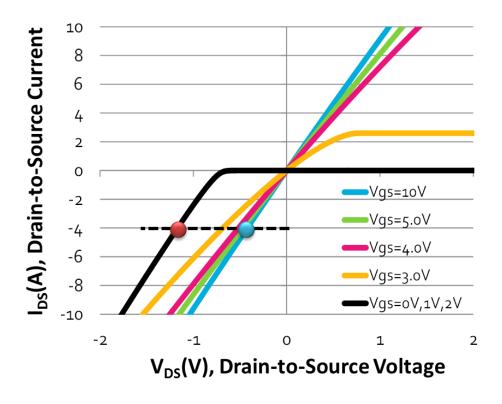

| Fig. 1.8. I-V characteristics of cascode GaN HEMT.                                                                 | 12       |

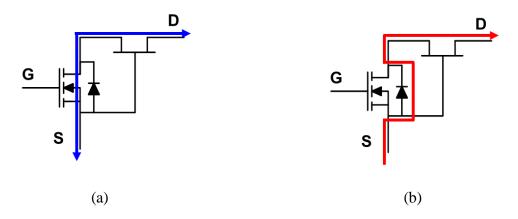

| Fig. 1.9. Conduction principle of cascode GaN HEMT, (a) Vgs=10V, (b) Vgs=0V                                        | 13       |

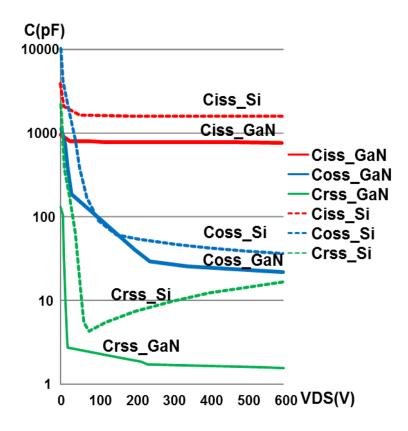

| Fig. 1.10. C-V characteristics comparison between cascode GaN and state-of-the-art Si                              | 15       |

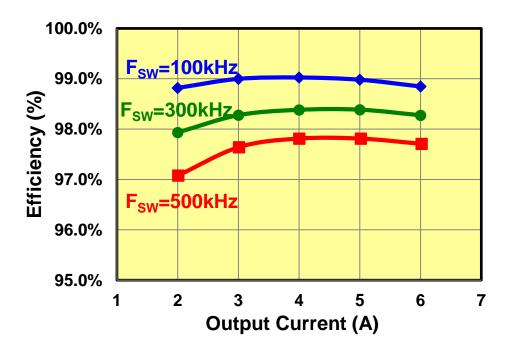

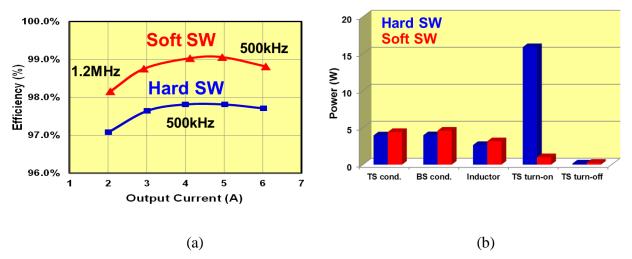

| Fig. 2.1. Buck converter test circuit (CCM, $V_{in}$ =380V, $V_o$ =200V, $I_{o\_full}$ =6A, $I_{ripple\_p2p}$ =3A) | 18       |

| Fig. 2.2. Tested efficiency of buck converter at different switching frequency                                     | 19       |

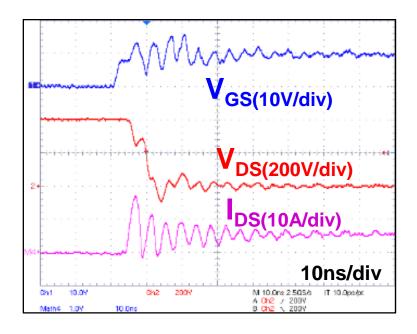

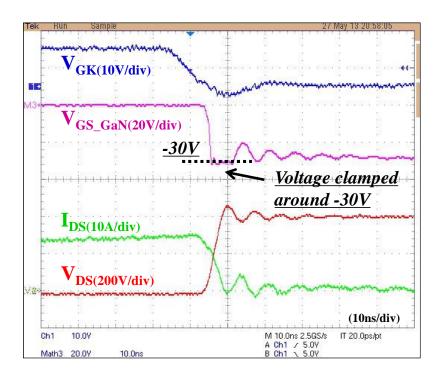

| Fig. 2.3. Tested turn-on waveform at 380V/5A                                                                       | 19       |

| Fig. 2.4. (a) Experimental waveform and (b) simulation waveform comparison                                         | 20       |

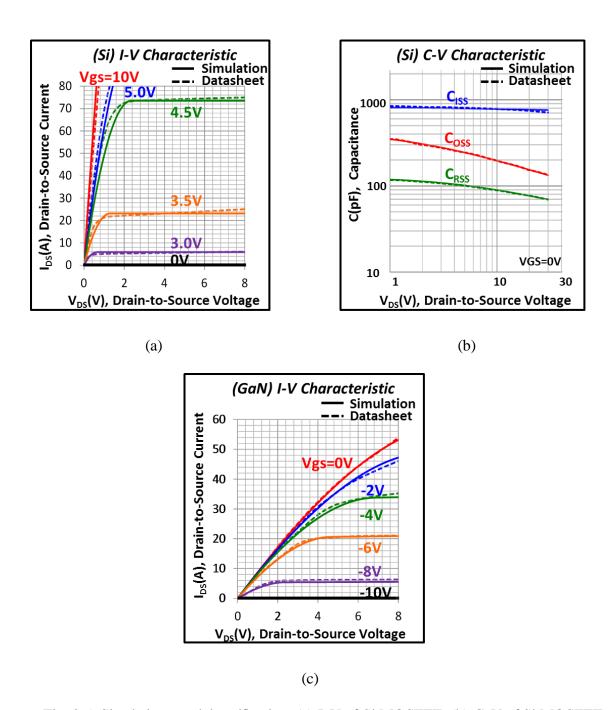

| Fig. 2.5. Simulation model verification (a) I-V of Si MOSFET, (b) C-V of Si MOSFET, and (c) I-V                    | of GaN   |

| HEMT                                                                                                               | 21       |

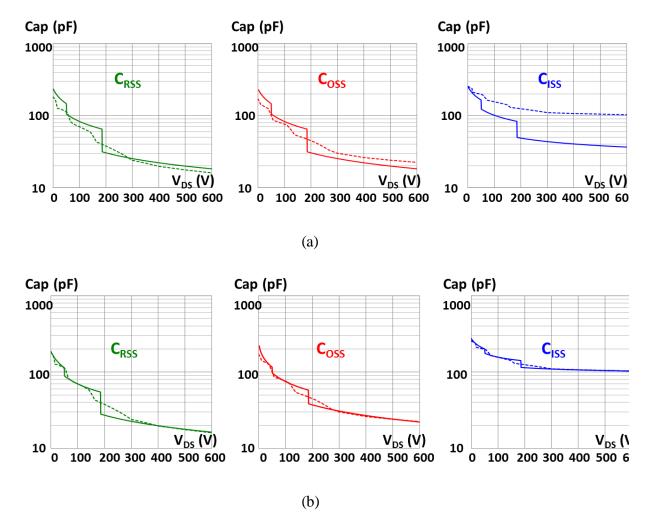

| Fig. 2.6. C-V characteristic (a) before modification and (b) after modification. (solid line is from sim           | ulation, |

| dashed line is from datasheet, all curves are obtained under $V_{\text{GS}}$ =-24V)                                | 22       |

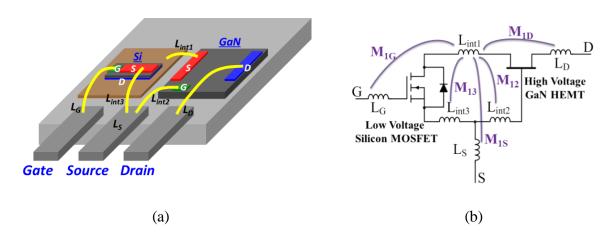

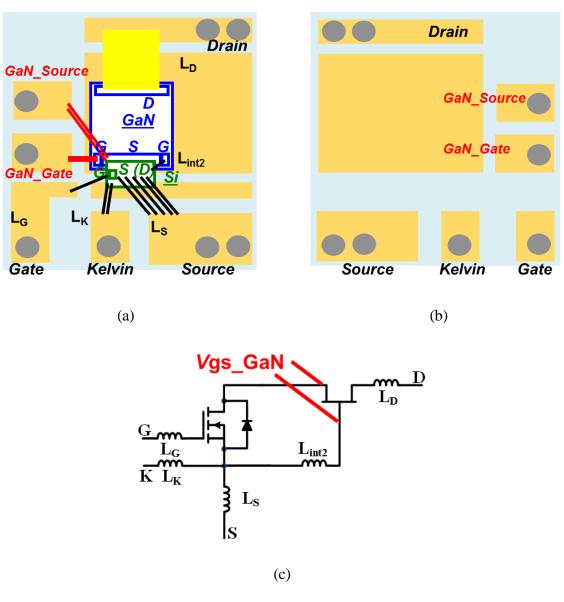

| Fig. 2.7. TO-220 cascode GaN HEMT package (a) bonding diagram and (b) schematic                                    | 23       |

| Fig. 2.8. Current directions of conductors in cascode package during (a) turn-on and (b) turn-off                  | 24       |

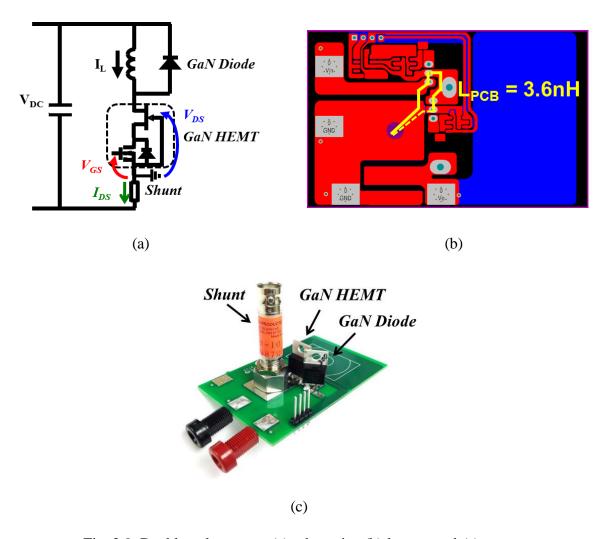

| Fig. 2.9. Double-pulse-tester (a) schematic, (b) layout, and (c) prototype                                         | 26       |

| Fig. 2.10. PCB parasitic inductance extraction process                                                             | 27       |

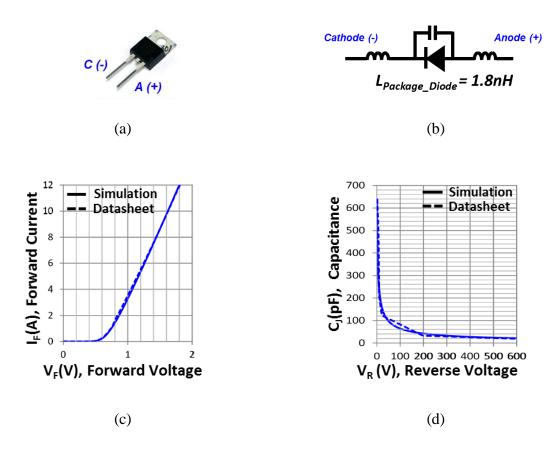

| Fig. 2.11. 600V GaN Schottky diode (a) package, (b) model, (c) I-V curve, (d) C-V curve                            | 28       |

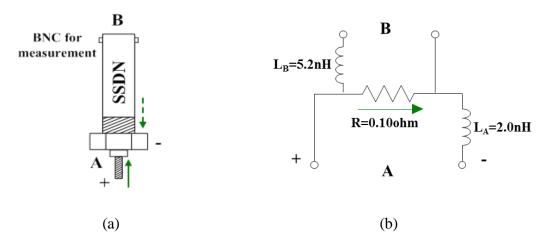

| Fig. 2.12. High bandwidth coaxial current shunt (a) prototype, (b) model                                           | 29       |

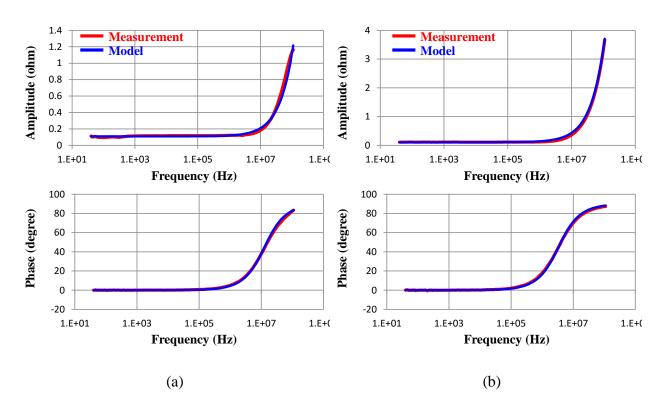

| Fig. 2.13. Current shunt impedance (a) terminal A, (b) terminal B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

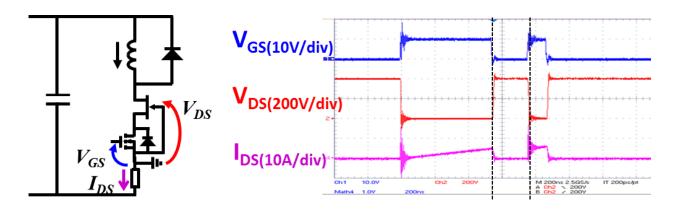

| Fig. 2.14. Double pulse test typical waveform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1          |

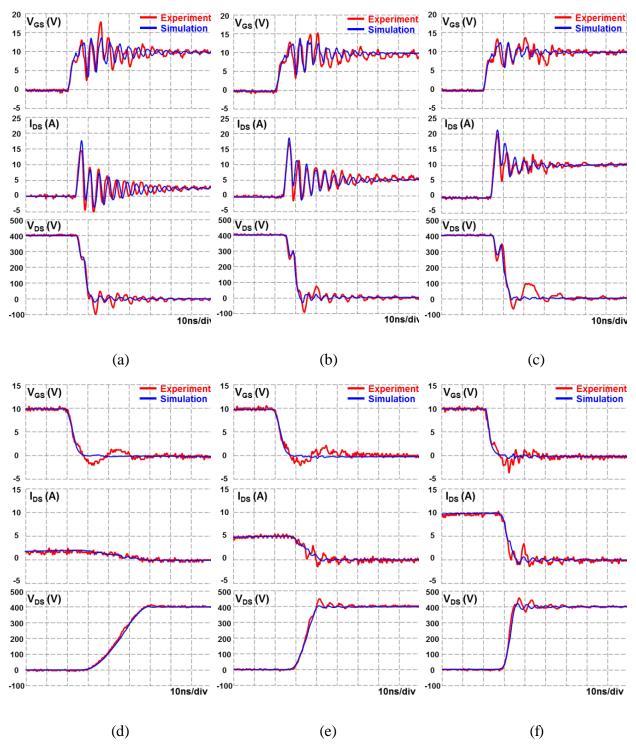

| $Fig.\ 2.15.\ Zoom-in\ switching\ waveforms\ (a)\ 400V/2A\ turn\ on;\ (b)\ 400V/5A\ turn\ on;\ (c)\ 400V/10A\ turn\ on;$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | n;         |

| (d) 400V/2A turn off; (e) 400V/5A turn off; (f) 400V/10A turn off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2          |

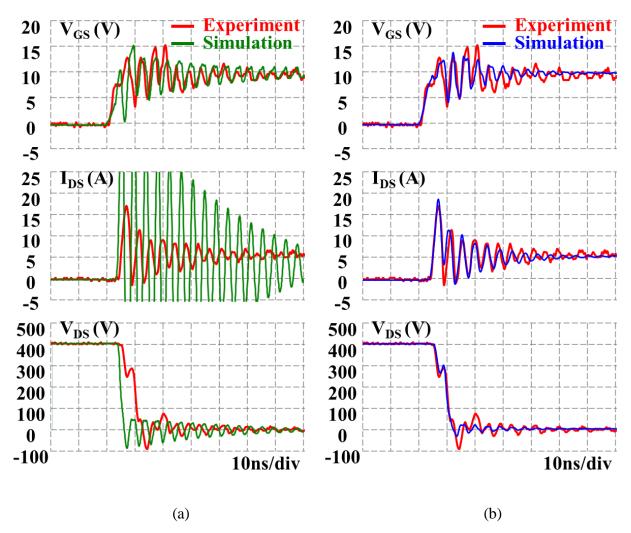

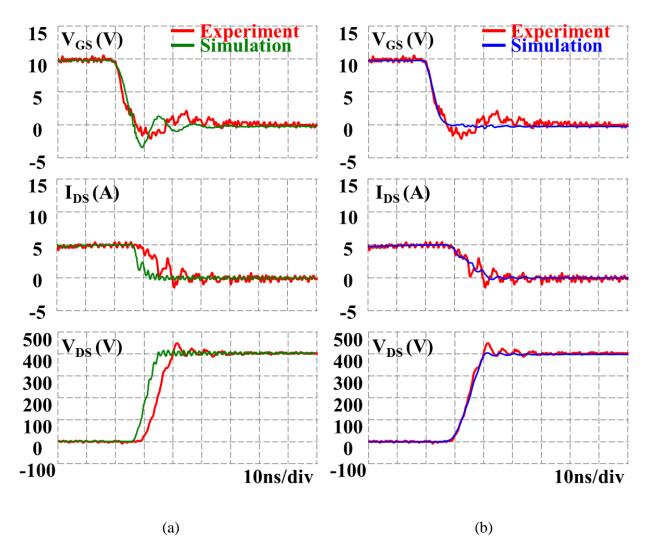

| Fig. 2.16. Simulation model comparison (a) before modification and (b) after modification (turn o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | n          |

| waveforms under 400V/5A condition)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3          |

| Fig. 2.17. Simulation model comparison (a) before modification and (b) after modification (turn of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ff         |

| waveforms under 400V/5A condition)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4          |

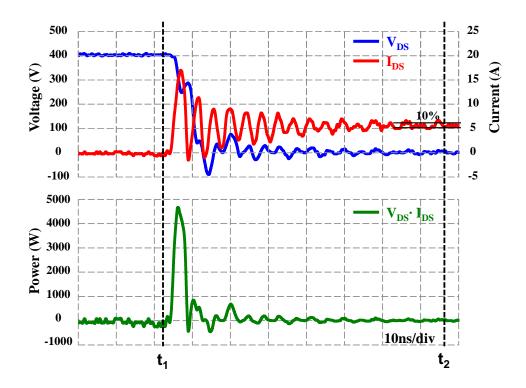

| Fig. 2.18. Calculation of turn-on energy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5          |

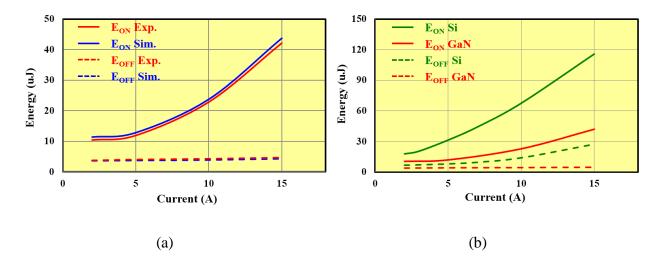

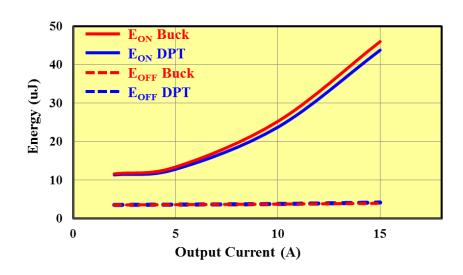

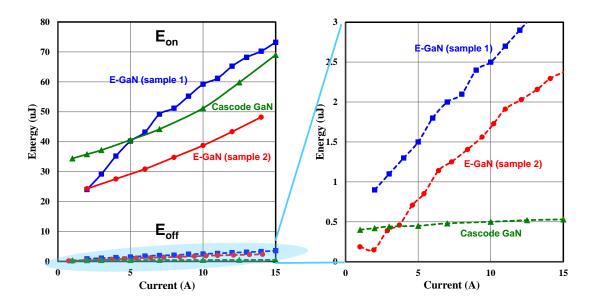

| Fig. 2.19. DPT switching energy comparison (a) experimental and simulation results of GaN, (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ))         |

| comparison between GaN and Si                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6          |

| Fig. 2.20. DPT turn-on waveform comparison between GaN and Si                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7          |

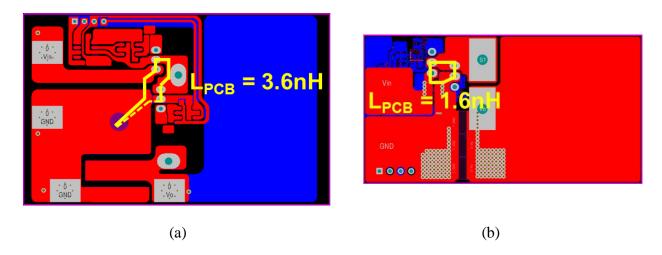

| Fig. 2.21. Layout comparison between (a) double-pulse tester and (b) buck converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8          |

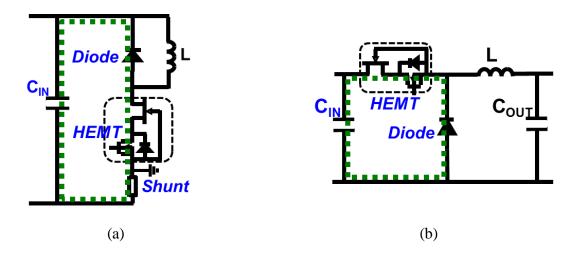

| Fig. 2.22. Schematic comparison between (a) double-pulse tester and (b) buck converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8          |

| Fig. 2.23. Switching energy comparison between DPT and Buck                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9          |

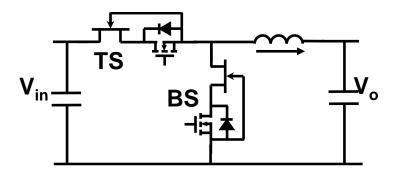

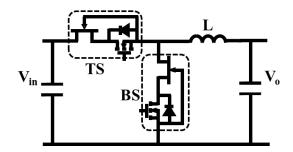

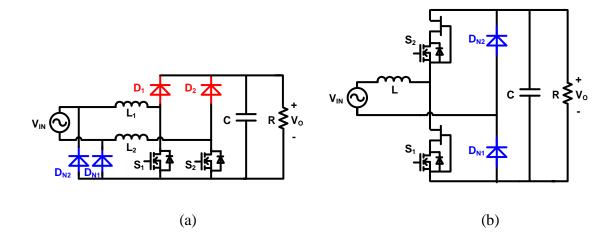

| Fig. 2.24. Bi-direction buck-boost converter schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0          |

| Fig. 2.25. Critical conduction mode operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0          |

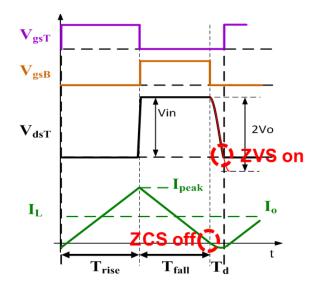

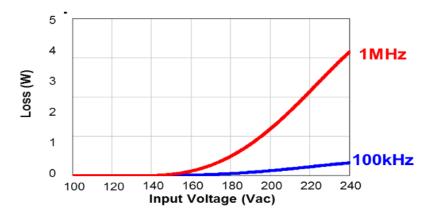

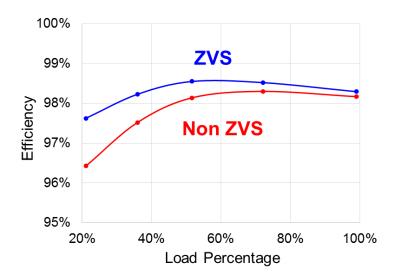

| Fig. 2.26. Comparison between hard switching and soft switching (a) Buck converter efficiency, (b) los                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | S          |

| breakdown at full load4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ·1         |

| Fig. 2.27. Buck converter TS turn-on waveforms at CCM hard-switching condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -2         |

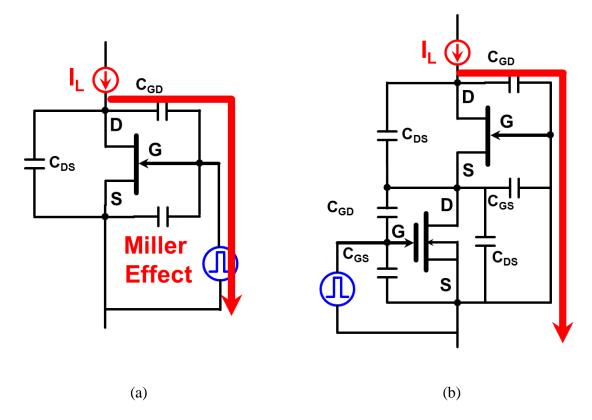

| Fig. 2.28. Turn-off equivalent circuit comparison (a) N-off GaN, (b) cascode GaN4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .3         |

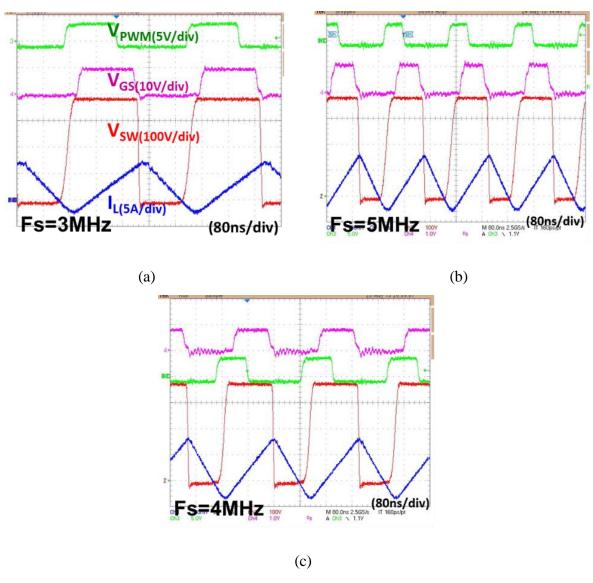

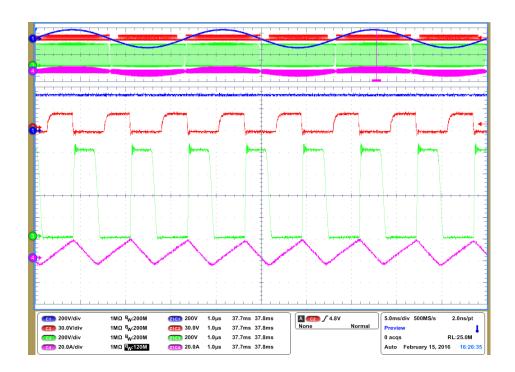

| Fig. 2.29. CRM buck waveforms at (a) 3 MHz, (b) 4 MHz, (c) 5 MHz4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4          |

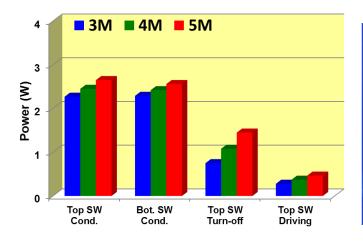

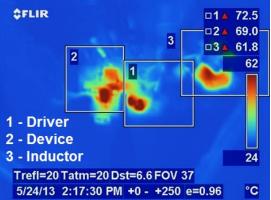

| Fig. 2.30. Loss breakdown at 3-5 MHz4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5          |

| Fig. 2.31. Thermal image at 5 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5          |

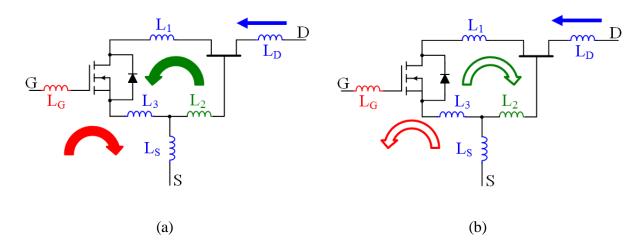

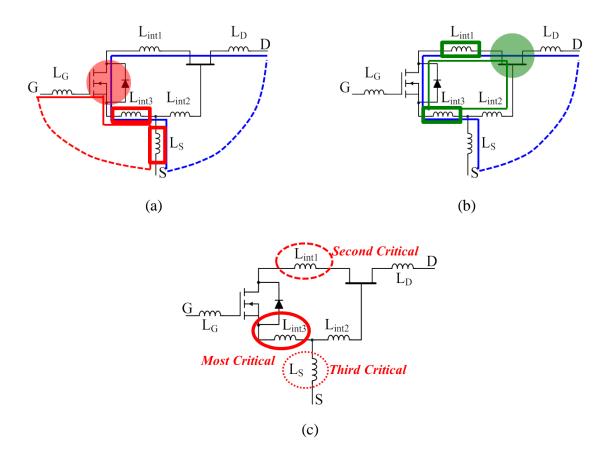

| Fig. 2.32. Common source inductance in cascode package (a) Si's perspective, (b) GaN's perspective, (common source inductance in cascode package (a) Si's perspective, (b) GaN's perspective, (common source inductance in cascode package (a) Si's perspective, (b) GaN's perspective, (common source inductance in cascode package (a) Si's perspective, (b) GaN's perspective, (common source inductance in cascode package (a) Si's perspective, (b) GaN's perspective, (common source inductance in cascode package (a) Si's perspective, (b) GaN's perspective, (common source inductance in cascode package (a) Si's perspective, (b) GaN's perspective, (common source inductance in cascode package (a) Si's perspective, (common source inductance in cascode package (a) Si's perspective, (common source inductance in cascode package (a) Si's perspective, (common source inductance in cascode package (a) Si's perspective, (common source inductance in cascode package (a) Si's perspective, (common source inductance in cascode package (a) Si's perspective, (common source inductance in cascode package (a) Si's perspective, (common source inductance in cascode package (a) Si's perspective, (common source inductance in cascode package (a) Si's perspective, (common source inductance in cascode package (a) Si's perspective, (common source inductance in cascode package (a) Si's perspective, (common source in cascode package (a) Si's perspectiv | <b>2</b> ) |

| for cascode structure 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7          |

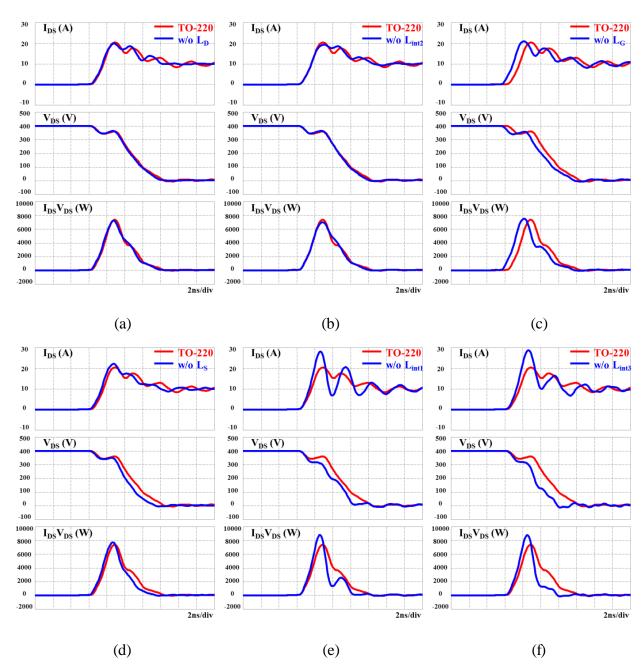

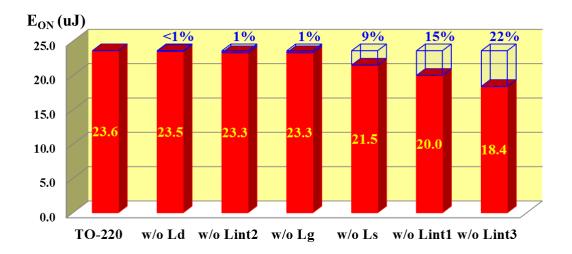

| Fig. 2.33. Top switch hard-switching turn-on waveforms comparison at 400 V/10 A                                                                                       | 48  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 2.34. Device turn-on loss comparison at 400V/10A                                                                                                                 | 49  |

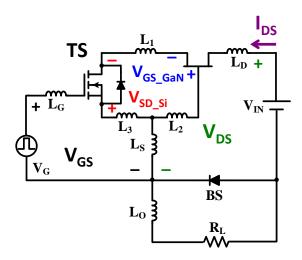

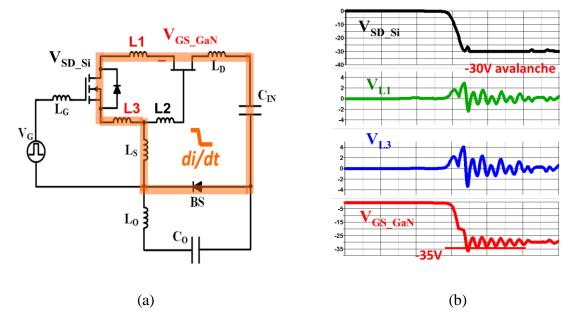

| Fig. 2.35. Equivalent circuit of a buck converter with the cascode GaN HEMT                                                                                           | 51  |

| Fig. 2.36. Turn-on waveform at 400V/4.5A (a) with package parasitic inductance, (b) without packa                                                                     | ge  |

| parasitic inductance                                                                                                                                                  | 51  |

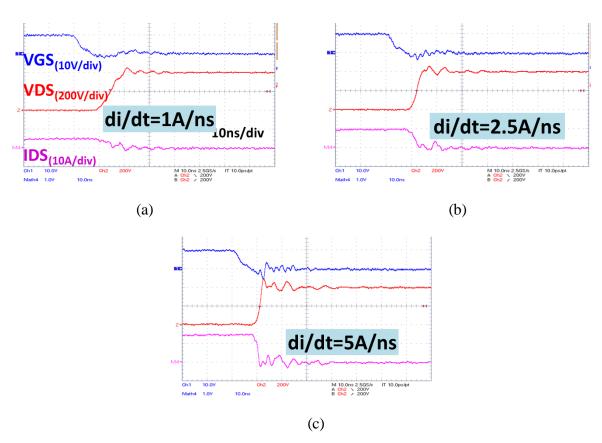

| Fig. 2.37. Di/dt at different turn-off current (a) $I_{OFF}$ =5A, (b) $I_{OFF}$ =10A, (c) $I_{OFF}$ =15A                                                              | 53  |

| Fig. 2.38. Turn-off at 400 V/12 A (a) buck circuit schematic, (b) simulation waveform                                                                                 | 53  |

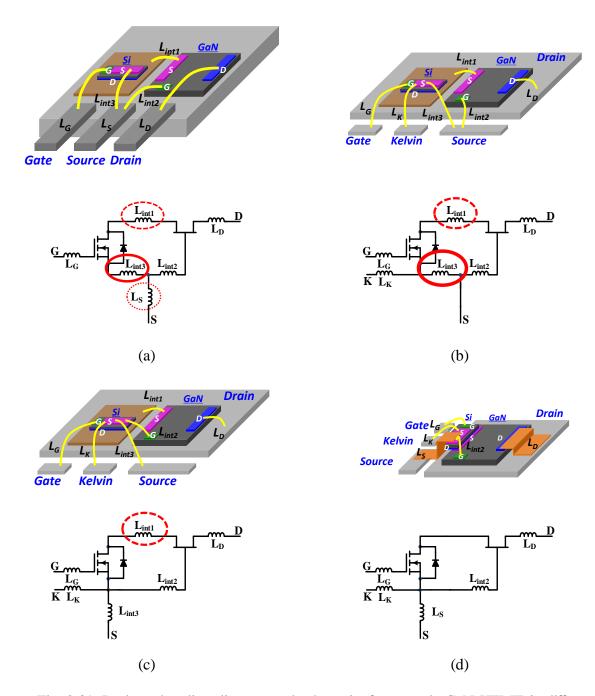

| Fig. 2.39. Package bonding diagram and schematic for cascode GaN HEMT in different packages. (a) To                                                                   | O-  |

| 220, (b) PQFN, (c) PQFN plus, (d) Stack-die                                                                                                                           | 55  |

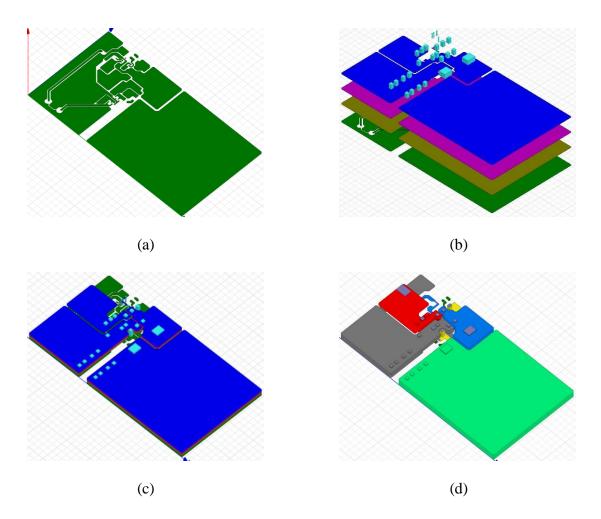

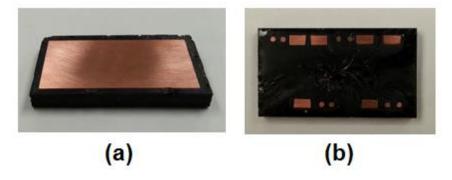

| Fig. 2.40. Design of stack-die package for cascode GaN HEMT (a) top view, (b) bottom view, and (                                                                      | (c) |

| schematic                                                                                                                                                             | 57  |

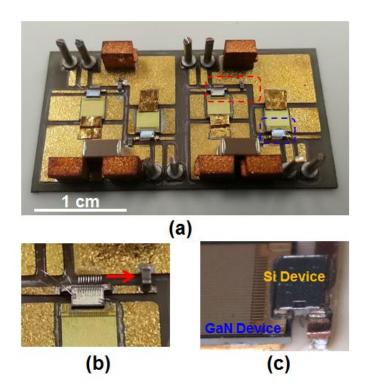

| Fig. 2.41. Packaged stack-die device mounted on the double-pulse tester board with transparent silicon                                                                | ne  |

| elastomer glob-top encapsulation                                                                                                                                      | 59  |

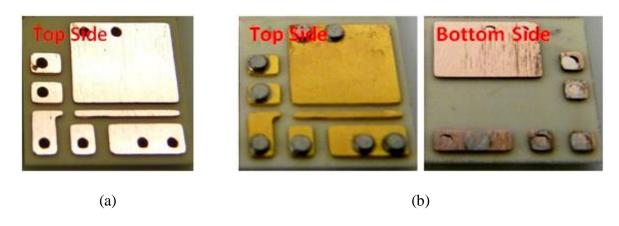

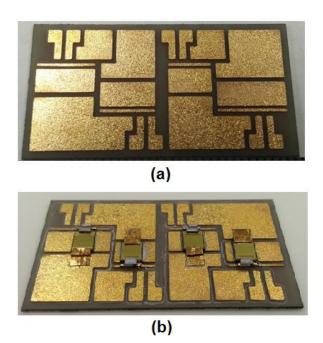

| Fig. 2.42. Patterned $Al_2O_3$ – DBC substrate: (a) top surface pads after etching and laser drilling, (b) electrons and laser drilling, (b) electrons are substrate. | :o- |

| plated Au top surface with soldered pins and ground bottom surface                                                                                                    | 59  |

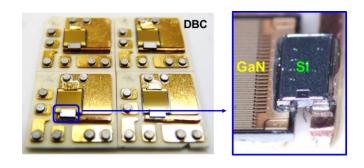

| Fig. 2.43. Die attachment                                                                                                                                             | 60  |

| Fig. 2.44. Wire bonding process                                                                                                                                       | 60  |

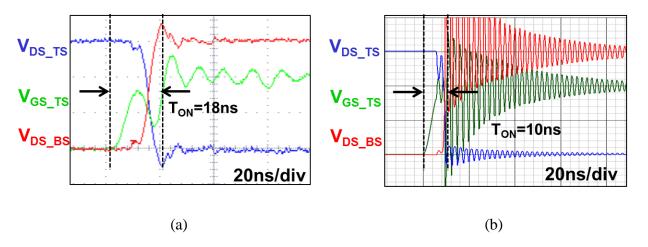

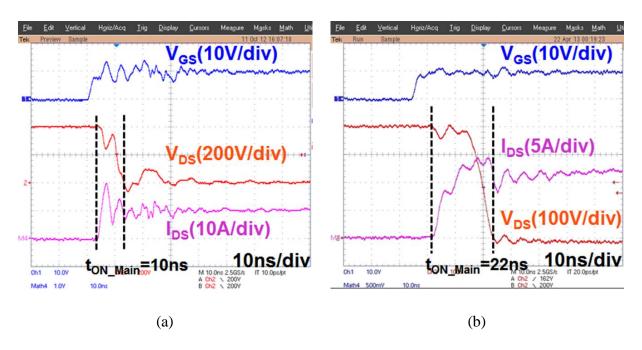

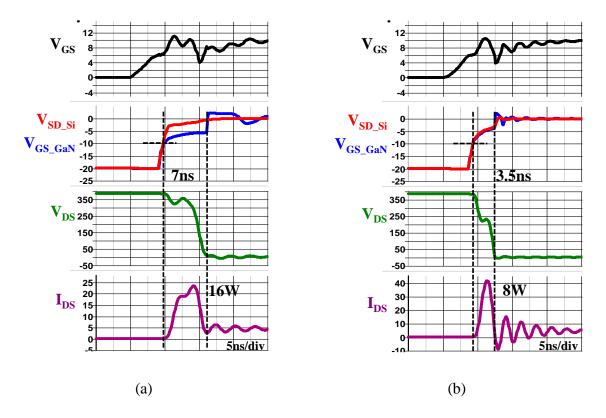

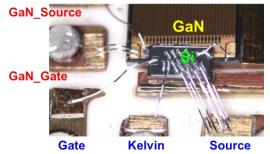

| Fig. 2.45. Turn-on waveform comparison (a) TO-220 package, (b) stack-die package                                                                                      | 61  |

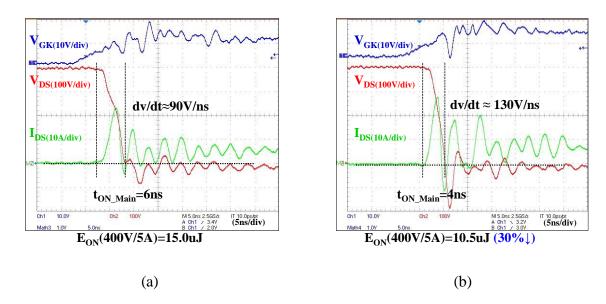

| Fig. 2.46. Switching energy comparison for different packages                                                                                                         | 61  |

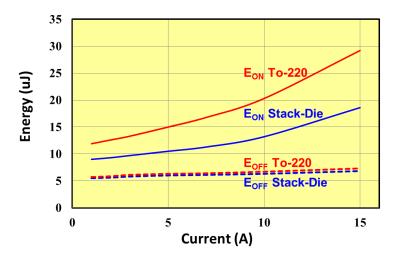

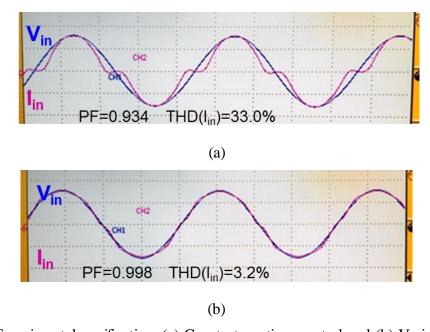

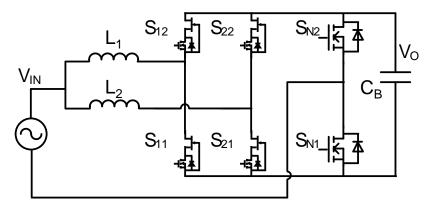

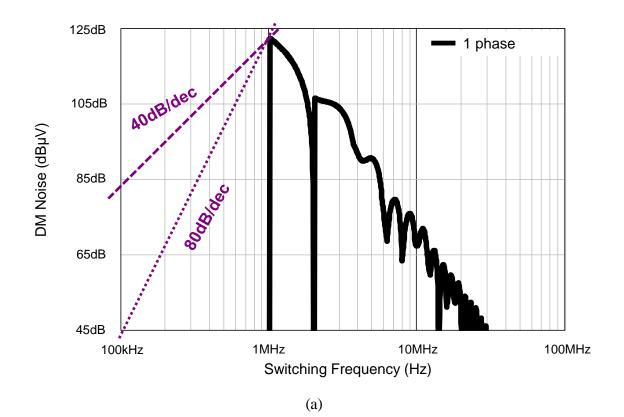

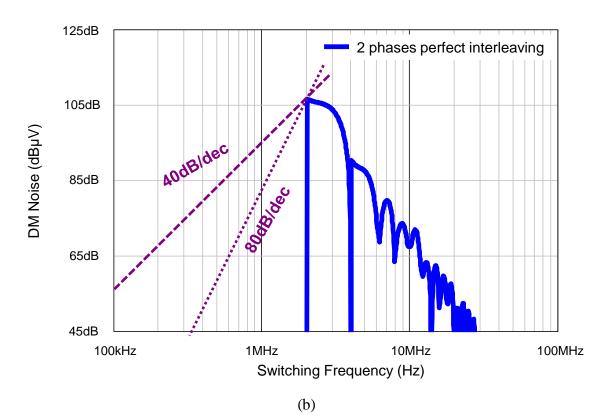

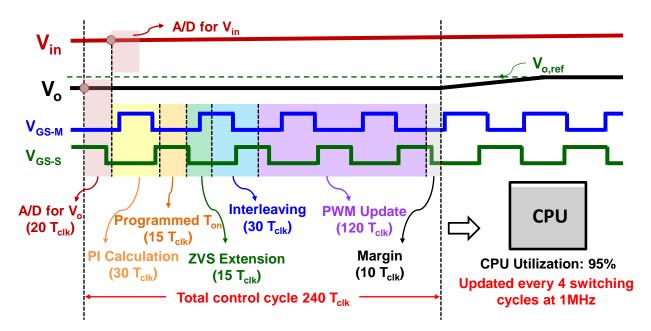

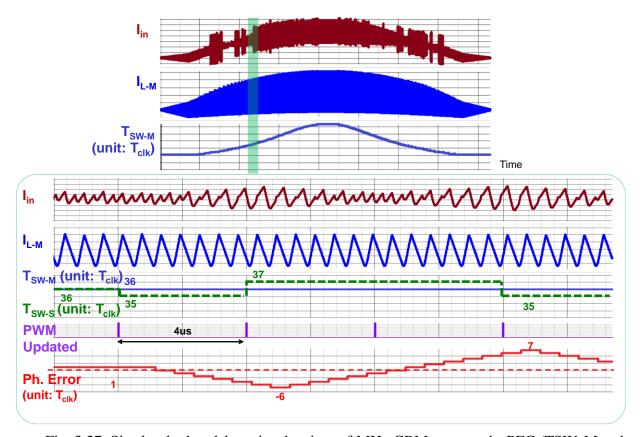

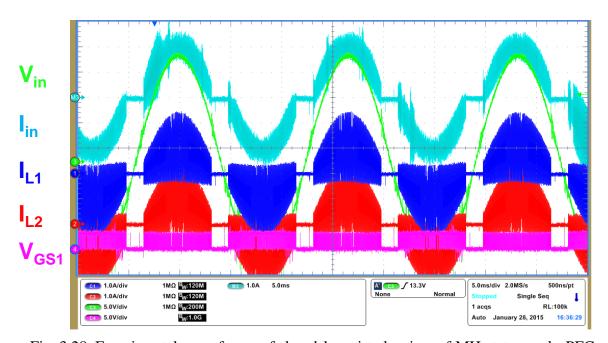

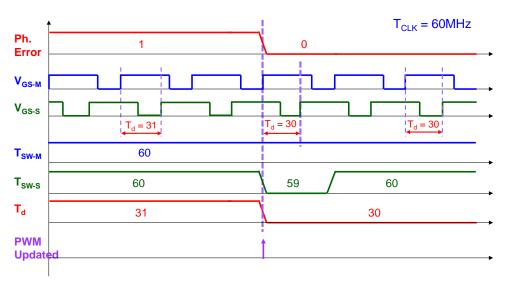

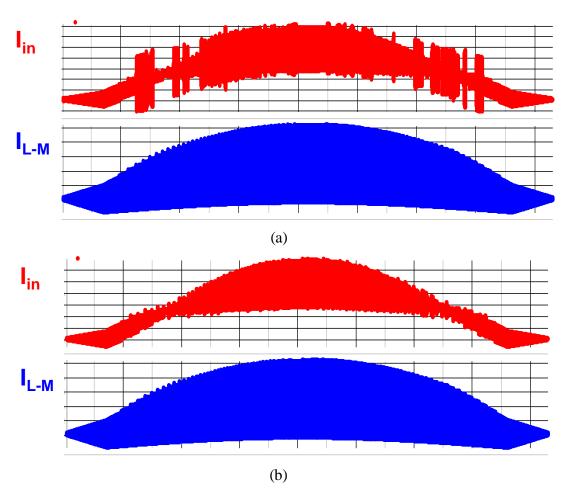

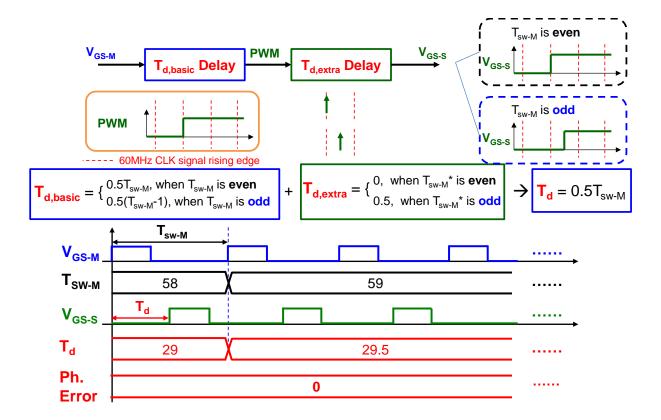

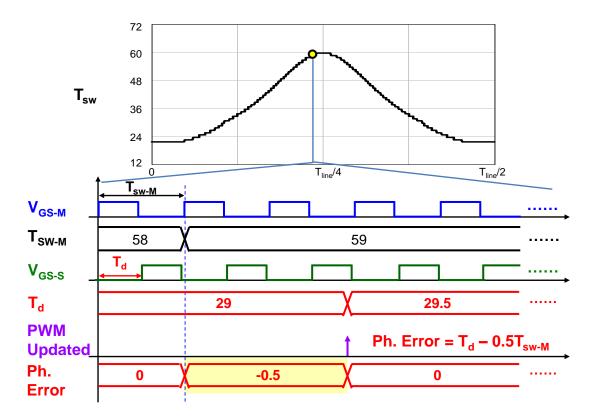

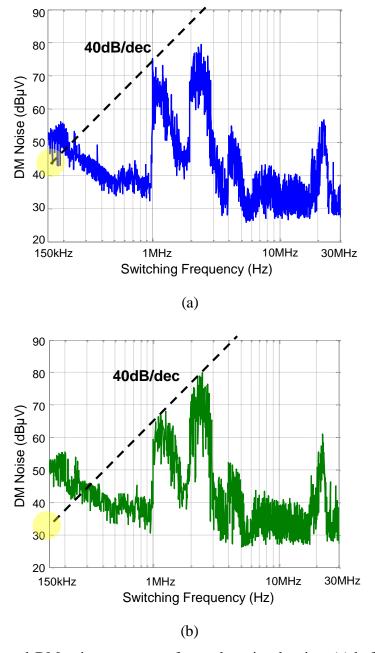

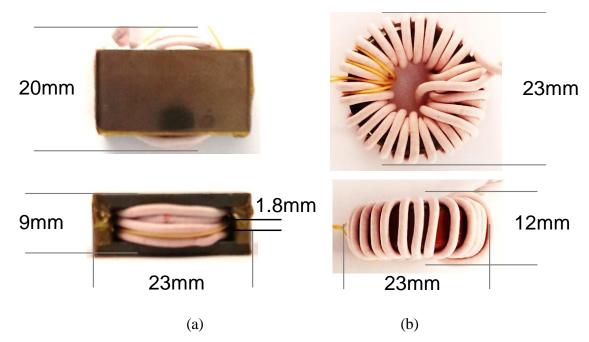

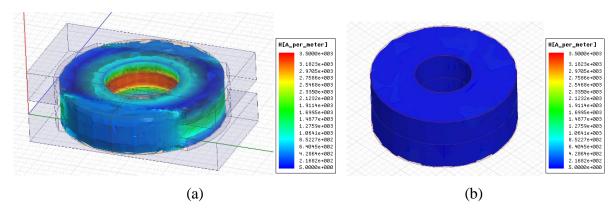

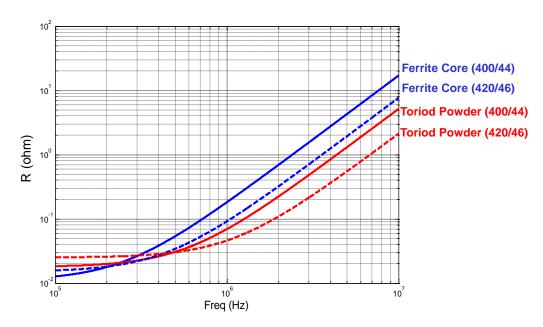

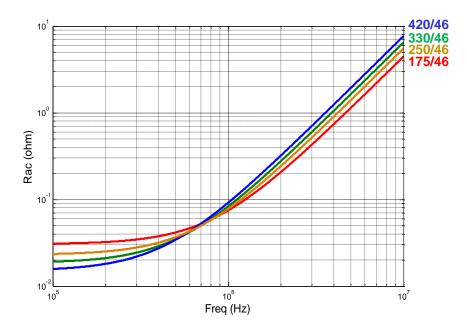

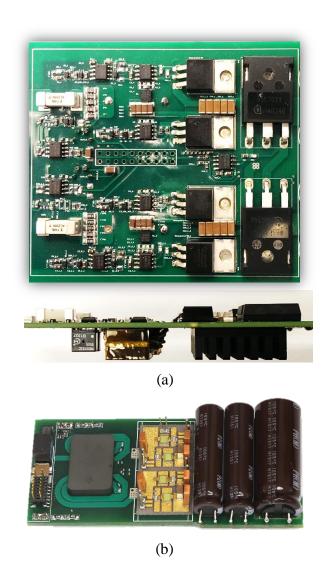

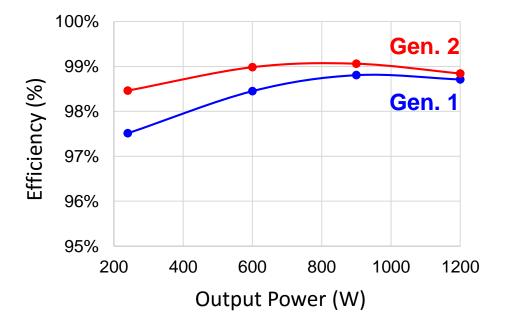

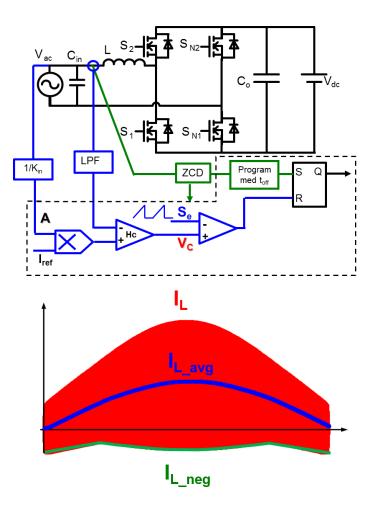

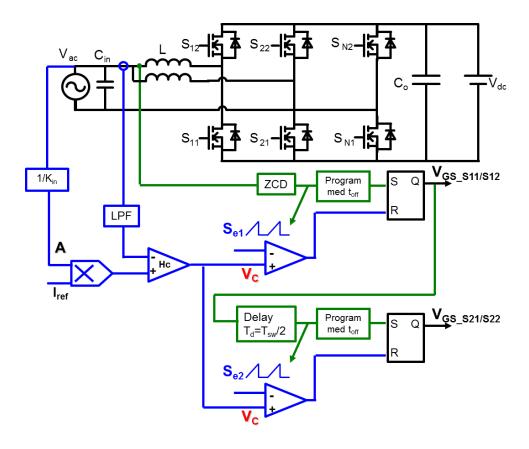

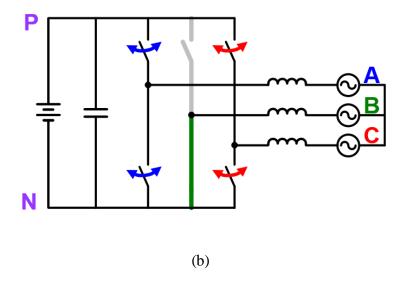

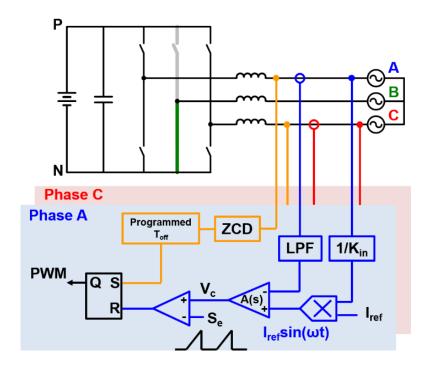

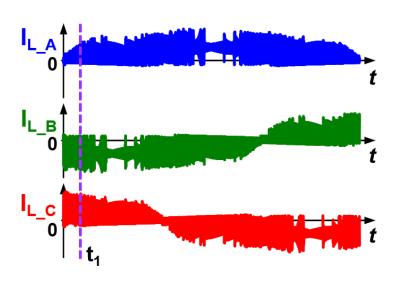

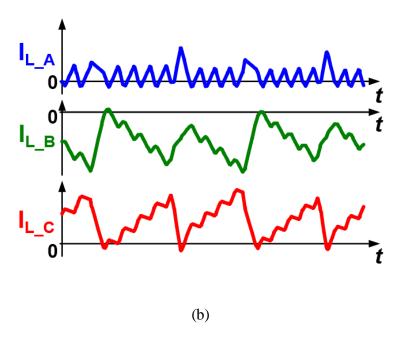

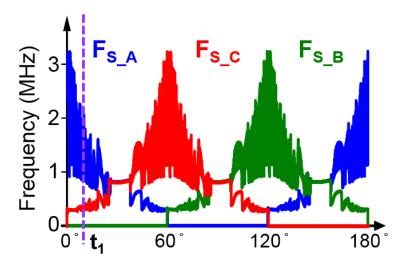

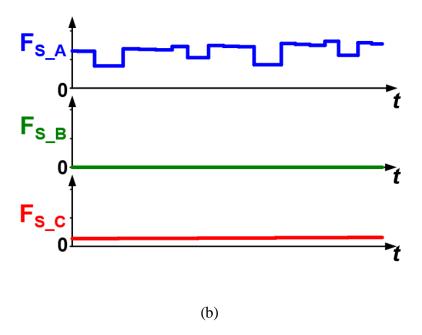

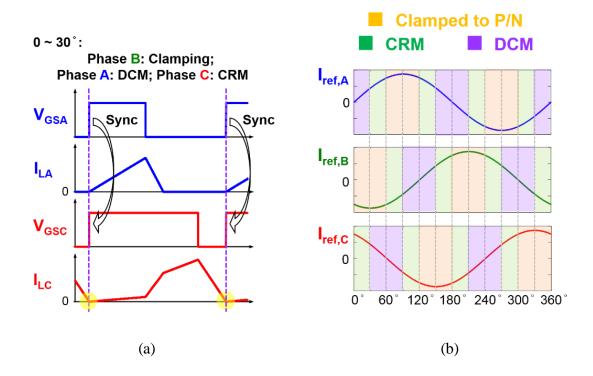

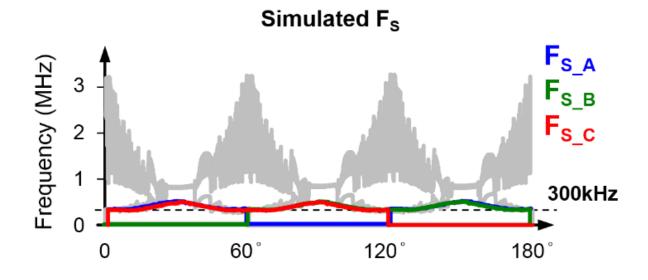

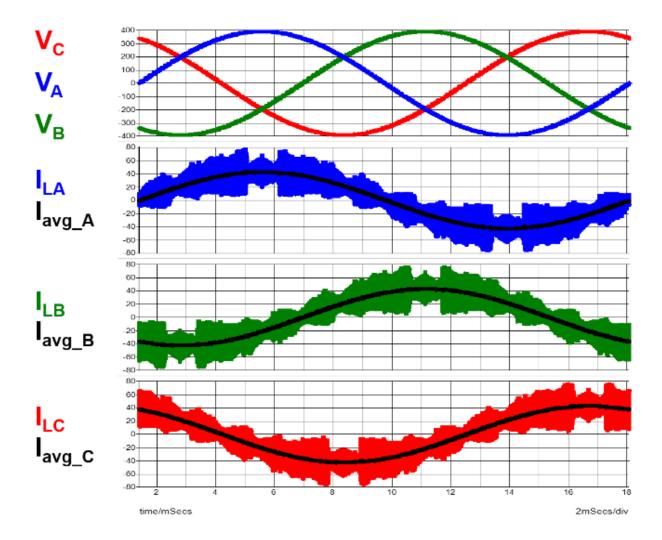

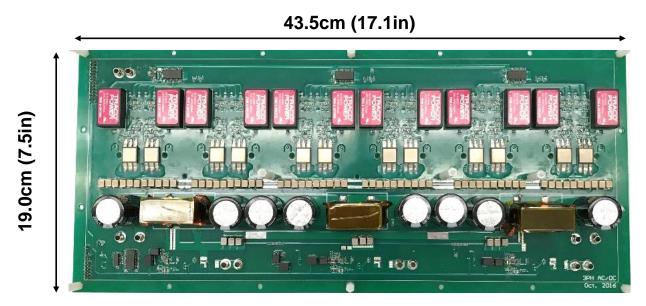

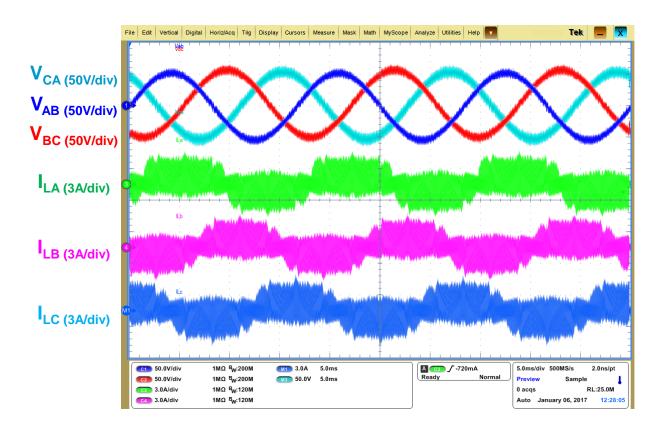

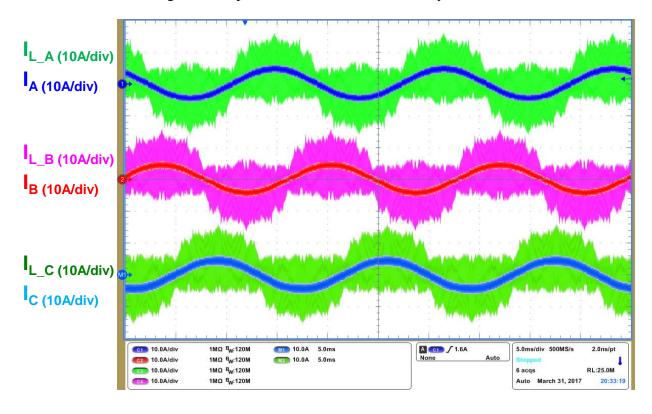

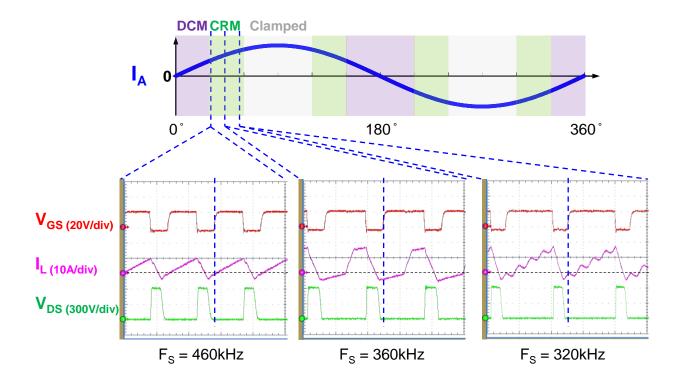

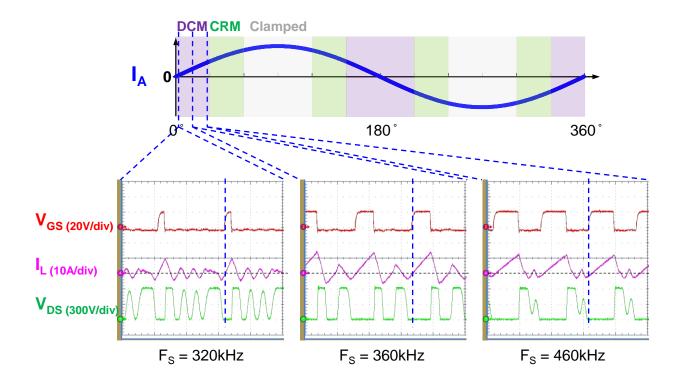

| Fig. 2.47. Simulated $V_{GS\_GaN}$ for (a) TO-220, (b) PQFN, (c) PQFN plus, (d) stack-die                                                                             | 62  |