## Optimizing Programmable Logic Design Security Strategies

Jonathan P. Graf

Dissertation submitted to the faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

In

**Computer Engineering**

Peter M. Athanas, Chair

Ezra A. Brown

Mark T. Jones

Cameron D. Patterson

Joseph G. Tront

April 29, 2019

Blacksburg, Virginia

Keywords: FPGA, trust, design security, design integrity, design confidentiality, trustworthy computing, game theory

Copyright 2019 Jonathan P. Graf

## Optimizing Programmable Logic Design Security Strategies Jonathan P. Graf

### (ABSTRACT)

Abstract - A wide variety of design security strategies have been developed for programmable logic devices, but less work has been done to determine which are optimal for any given design and any given security goal. To address this, we consider not only metrics related to the performance of the design security practice, but also the likely action of an adversary given their goals. We concern ourselves principally with adversaries attempting to make use of hardware Trojans, although we also show that our work can be generalized to adversaries and defenders using any of a variety of microelectronics exploitation and defense strategies. Trojans are inserted by an adversary in order to accomplish an end. This goal must be considered and quantified in order to predict the adversary's likely action. Our work here builds upon a security economic approach that models the adversary and defender motives and goals in the context of empirically derived countermeasure efficacy metrics. The approach supports formation of a two-player strategic game to determine optimal strategy selection for both adversary and defender. A game may be played in a variety of contexts, including consideration of the entire design lifecycle or only a step in product development. As a demonstration of the practicality of this approach, we present an experiment that derives efficacy metrics from a set of countermeasures (defender strategies) when tested against a taxonomy of Trojans (adversary strategies). We further present a software framework, GameRunner, that automates not only the solution to the game but also enables mathematical and graphical exploration of "what if" scenarios in the context of the game. GameRunner can also issue "prescriptions," sets of commands that allow the defender to automate the application of the optimal defender strategy to their circuit of concern. We also present how this work can be extended to adjacent security domains. Finally, we include a discussion of future work to include additional software, a more advanced experimental framework, and the application of irrationality models to account for players who make subrational decisions.

## Optimizing Programmable Logic Design Security Strategies

Jonathan P. Graf

### (GENERAL AUDIENCE ABSTRACT)

We present a security economic model that informs the optimal selection of programmable logic design security strategies. Our model accurately represents the economics and effectiveness of available design security strategies and accounts for the varieties of available exploits. Paired with game theoretic analysis, this model informs microelectronics designers and associated policy makers of optimal defensive strategies. Treating the adversary and defender as opponents in a two-player game, our security economic model tells us how either player will play if it is known in advance how their opponent plays. The additional use of game theory allows us to determine the optimal play of both players simultaneously without prior knowledge other than models of players beliefs.

# Dedication

This work is dedicated to my wife, Leanna, and my son, Jack. Thank you for supporting me during the early mornings, late nights, and weekends that were required for Daddy to get his "doctor degree" and fulfill a life goal.

## Acknowledgements

In addition to Leanna and Jack, heartfelt thanks are due to many others:

To Peter Athanas, who, for the 15 years after advising my master's degree studies, kept cheerfully prodding me to finish my doctoral dissertation. Your optimism continued when a sponsor declined to let me publish my original topic in 2008 as well as when I chased by professional goals instead of my academic ones. Your assessment in 2016 that my professional research concepts could be crafted to fulfill my dissertation requirements pushed me over the edge to re-commit to finishing. Without your encouragement, I never would have attempted something as challenging (foolhardy?) as trying to finish a doctorate while also starting a business. Thank you for being unrelentingly optimistic! There are so many other things to thank you for – the training you provided in your classes and while I worked in your lab, the time you always provide when asked, and the example you set for how to help people grow by giving them the tools to explore challenging ideas in a fun and creative environment. The list could go on. I am sincerely grateful.

To my committee, Ezra Brown, Mark Jones, Cameron Patterson, and Joseph Tront. Thank you for the many hours spent discussing ideas in your offices, refining concepts in document drafts, and philosophizing over coffee.

To Scott Harper, my most frequent collaborator in various capacities at Virginia Tech, Luna Innovations, MacAulay-Brown, and Graf Research. We have worked together on more projects than can be named – including this one – so suffice it to say that I am better both professionally and personally for your collaboration and friendship. I am deeply grateful for both. To my Graf Research colleagues who collaborated directly with me on this work, Whitney Batchelor, Ed Carlisle, and Ryan Marlow. Your contributions to this work – ideas, refinements, corrections, conversations, travel, and software development – made it far better. It was also far more fun to complete due to the presence of each of you on the research team. Among the many contributions you each made in our collaboration, let me highlight a few for which I am specifically grateful. Whitney: thank you for exploring the background and related work with me, for contributions to the subrationality discussion, and for helping me properly express many of the mathematical ideas written here. Ed: thank you for work implementing the GameRunner software, for the weeks spent back and forth refining the game visualization techniques to their present form, and for performing empirical Trojan testing. Ryan: thank you for your work developing Trojan detection techniques and automating Trojan detection testing. Again, I am deeply grateful to each of you.

To my Graf Research colleagues who collaborated with me on closely related research programs, Ali Asgar Sohanghpurwala, Timothy Dunham, Michael Capone, and Alan Cook. Thank you for the privilege of working with you, exchanging ideas, refining concepts, and creating new technologies to solve interesting microelectronics security challenges. Solving problems with creative teams of bright people like you is the joy of my career; thank you for your contributions to such a fulfilling professional experience. Thank you also for the friendship and fun that have accompanied the R&D.

To my former colleagues at Luna and MacAulay-Brown, with whom I collaborated on both large DARPA and Air Force programs and innumerable small projects related to microelectronics security. In addition to my named co-authors – Scott Harper, Lee Lerner, Stephen Craven, Barry Polakowski, Stephen Baka, Kevin Urish, John Hallman, Brian Knight, and others – there are too many brilliant innovators and software developers who made major contributions both to projects and my career to name. Thank you all for the personally and intellectually fulfilling journey together while collaborating on those projects. Thank you also for all the enormously fun conversations over beer.

To Barry Polakowski, my boss and collaborator at Luna Innovations and MacAulay-Brown. Thank you for your support of my early doctoral coursework and my career. I am grateful for the professional growth experiences of our collaboration and for the fond memories from our many travels working on microelectronics security projects, crisscrossing the country to share what our R&D teams accomplished.

To Luna Innovations, thank you for sponsoring the coursework for my doctorate way back in the mid-aughts.

Finally, to my sponsors across multiple branches of the United States Department of Defense who supported my research. Thank you for the privilege of working for and with the very best in order to make our small contribution to make our country and the world just a little bit better. While there are too many to name, two deserve special thanks in the context of this work. To Dean Collins, thank you for your support of my team's early ideas in microelectronics trust. It was a privilege to work for you in the crucible of the DARPA Trust program, which not only refined early trust ideas but also set my career direction. To Matthew Casto, sponsor of portions of this work, it is a rare pairing to be sponsored by an ambitious researcher working on a mid-career PhD while attempting the same myself. Thank you for your support and congratulations on finishing!

This work was performed partially under internal research funding from the Graf Research Corporation and partially under funding from the United States Air Force. The portions of this work derived from publications [9] and [10] are based upon work supported by the United States Air Force under Contract No. FA8650-17-C-1148 and released under case numbers and 88ABW-2019-1182 and 88ABW-2018-4079, respectively. Any opinions, findings and conclusions or recommendations expressed in this material are those of the author(s) and do not necessarily reflect the views of the United States Air Force or the Graf Research Corporation.

# Contents

| List of Figur | res                                     | xi   |

|---------------|-----------------------------------------|------|

| List of Table | es                                      | . XV |

| List of Equa  | itions                                  | xvii |

| List of Acro  | nymsx                                   | viii |

| Chapter 1. I  | ntroduction                             | 1    |

| 1.1           | Summary of Contributions                | 4    |

| 1.2           | Document Organization                   | 7    |

| 1.3           | Related Contributions                   | 9    |

| 1.4           | Summary of Sponsorship                  | . 10 |

| Chapter 2. B  | Background                              | . 12 |

| 2.1           | Attack and Defense                      | . 15 |

|               | 2.1.1 Trust Background                  | . 15 |

|               | 2.1.2 FPGA Anti-Tamper Background       | . 25 |

| 2.2           | Metrics, Strategies, and Games          | . 29 |

|               | 2.2.1 Models and Metrics for IC Trojans | . 29 |

|               | 2.2.2 Game Theory                       | . 33 |

| Chapter 3. Security Economics and Game Theory |         |                                    |    |

|-----------------------------------------------|---------|------------------------------------|----|

| 3.1                                           | Player  | rs4                                | 10 |

| 3.2                                           | Collec  | cting Variables of Concern4        | 1  |

|                                               | 3.2.1   | Strategies                         | 1  |

|                                               | 3.2.2   | Probabilities4                     | 12 |

|                                               | 3.2.3   | Economic Variables4                | 13 |

| 3.3                                           | Assen   | nbling Utility Functions4          | 16 |

| 3.4                                           | Step (  | Games                              | 17 |

| 3.5                                           | Game    | s and Solution Concepts4           | 19 |

|                                               | 3.5.1   | Player Rationality5                | 50 |

|                                               | 3.5.2   | Computing Game Solutions5          | 52 |

| 3.6                                           | Exam    | ple Trust Game5                    | 52 |

|                                               | 3.6.1   | Playing the Trust Game5            | 53 |

|                                               | 3.6.2   | Solving Related Games5             | 57 |

| Chapter 4.                                    | Experim | ental Game5                        | 59 |

| 4.1                                           | Game    | Scenario: Defender and Adversary5  | ;9 |

|                                               | 4.1.1   | Defender and Adversary Economics6  | 50 |

|                                               | 4.1.2   | Step Games: HDL and 3PIP6          | 52 |

| 4.2                                           | Strate  | gies and Probabilities6            | 53 |

|                                               | 4.2.1   | Adversary Strategies               | 54 |

|                                               | 4.2.2   | Defender Strategies                | 58 |

|                                               | 4.2.3   | Empirically-Derived Probabilities7 | 2  |

| 4.3                                           | Auton   | nation and GameRunner7             | 74 |

| Chapter 5.                                    | Results |                                    | 19 |

| 5.1                                           | Result  | ts and Nash Equilibria7            | 19 |

| 5.2                                     | Analy   | sis                                                     | 85  |

|-----------------------------------------|---------|---------------------------------------------------------|-----|

|                                         | 5.2.1   | Expected Utility Theory and the Nash Equilibrium        | 85  |

|                                         | 5.2.2   | Analysis of Sensitivity to Error                        | 88  |

|                                         | 5.2.3   | Further Exploration of Results with GameRunner          | 96  |

| 5.3                                     | Expan   | ding the Defender Strategies: Sets of Countermeasures   | 107 |

| 5.4                                     | Discus  | ssion: How do we know this works?                       | 116 |

| Chapter 6. O                            | ngoing  | Work and Applications                                   | 124 |

| 6.1                                     | Advar   | ncing the Framework                                     | 125 |

|                                         | 6.1.1   | Hardware Trojan Test Article Database                   | 125 |

|                                         | 6.1.2   | Automated Detection Method Application                  | 126 |

|                                         | 6.1.3   | A User Software Application                             | 127 |

|                                         | 6.1.4   | OpTrust Framework                                       | 127 |

| 6.2                                     | Advar   | ncing the Theory                                        | 134 |

|                                         | 6.2.1   | Sequential Games and Repeated Play                      | 135 |

|                                         | 6.2.2   | Alternative Solution Concepts and Subrational Game Play | 136 |

|                                         | 6.2.3   | How Should We Then Play?                                | 141 |

| 6.3                                     | Applic  | cations                                                 | 142 |

|                                         | 6.3.1   | Direct Application of this Work                         | 142 |

|                                         | 6.3.2   | Applications of the General Detection Game              | 144 |

|                                         | 6.3.3   | Applications of the General Prevention Game             | 147 |

| Chapter 7. C                            | onclusi | ons                                                     | 150 |

| 7.1                                     | Final ( | Contribution Summary                                    | 150 |

| Appendix A: Detection Method Results153 |         |                                                         | 153 |

| Bibliography                            |         |                                                         | 156 |

# **List of Figures**

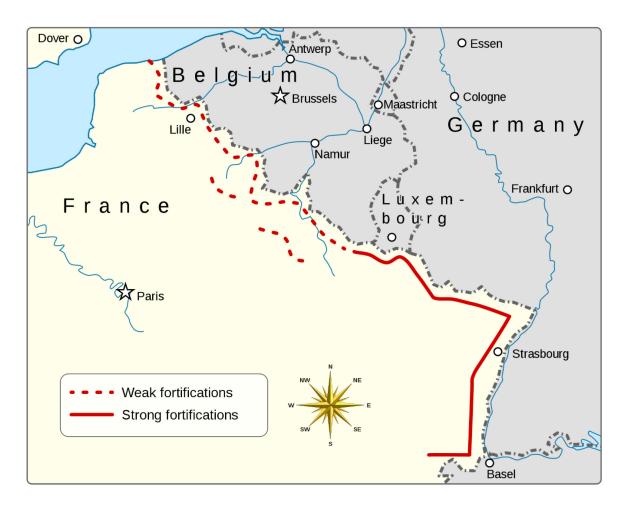

| Figure 1. Maginot Line between France and Germany [3]                                |

|--------------------------------------------------------------------------------------|

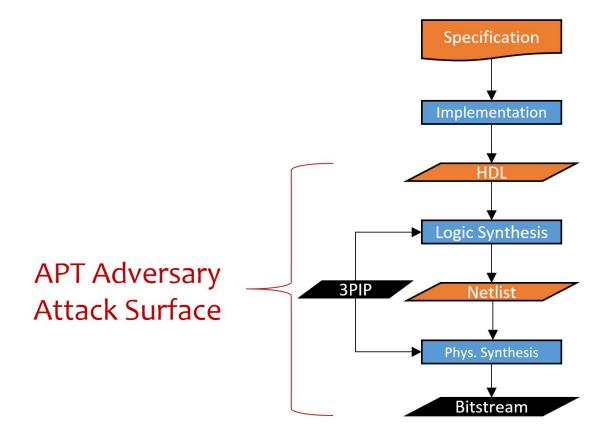

| Figure 2. Attack Surface Available to the APT-Enabled Adversary 22                   |

| Figure 3. Desired Utility of Security Economics/Game Theory for Hardware             |

| rojan Detection Strategy Selection                                                   |

| Figure 4. The ASIC and FPGA Device Games Decomposed into Step Games 48               |

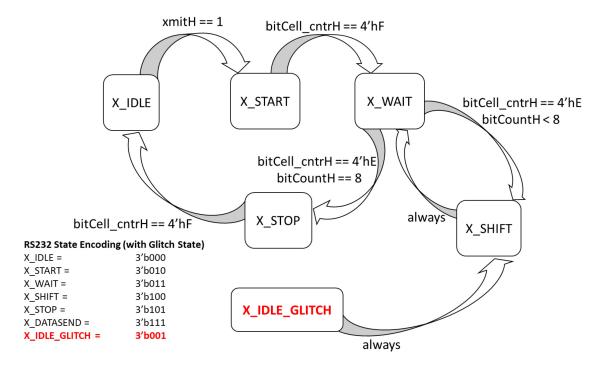

| Figure 5. Glitch State Trojan in RS232 (RS232-TjGlitchState) [10]67                  |

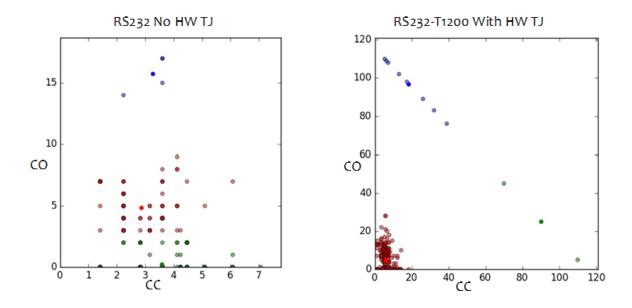

| Figure 6. SCOA clustering result for circuit RS232-T1200 [10]70                      |

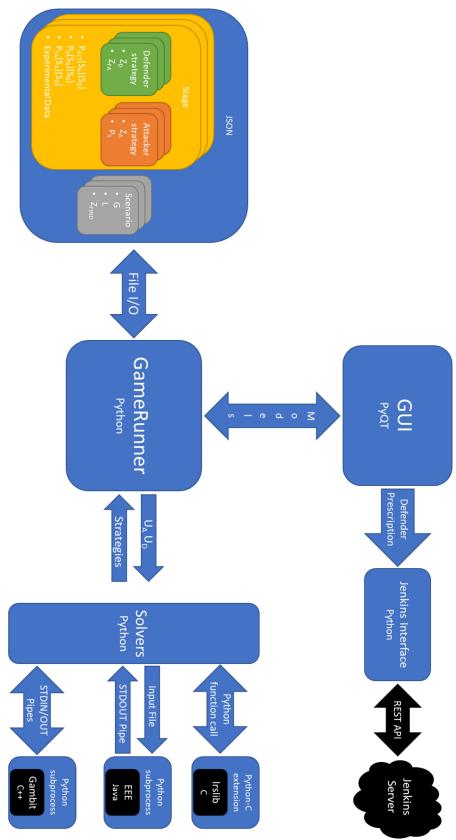

| Figure 7. GameRunner Block Diagram [9]75                                             |

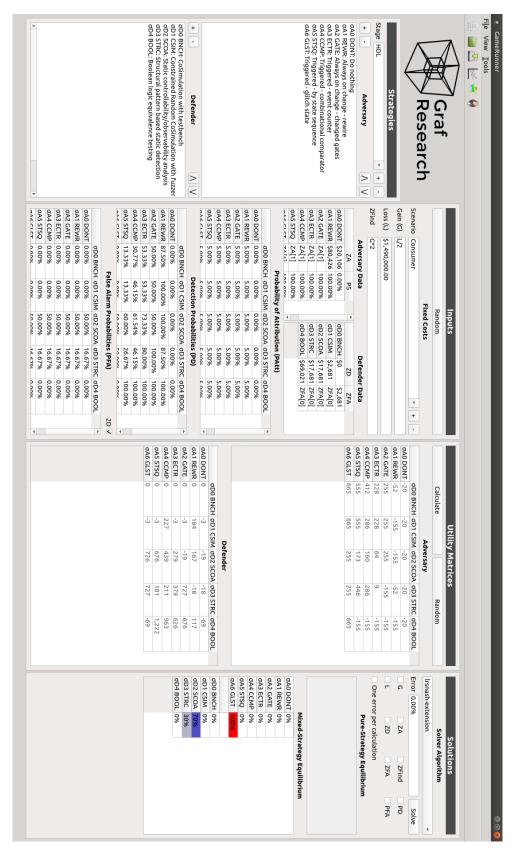

| Figure 8. GameRunner Graphical User Interface                                        |

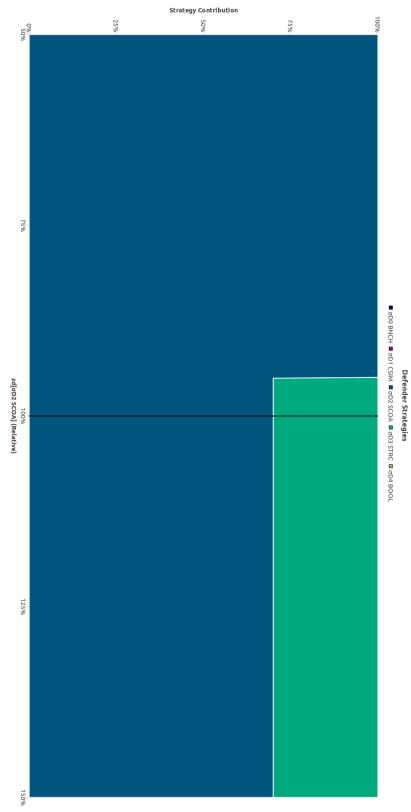

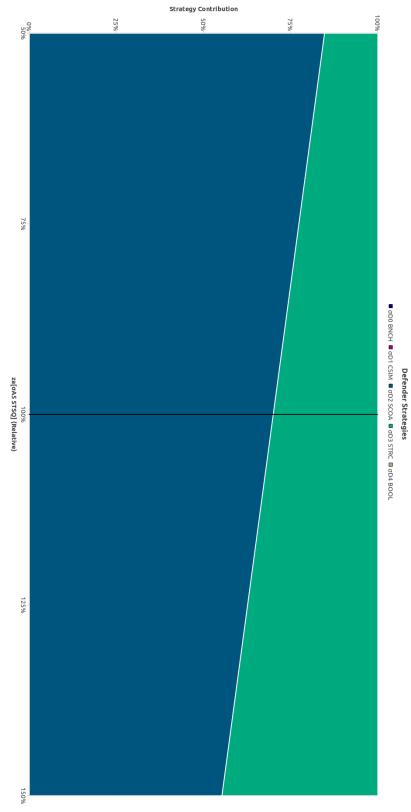

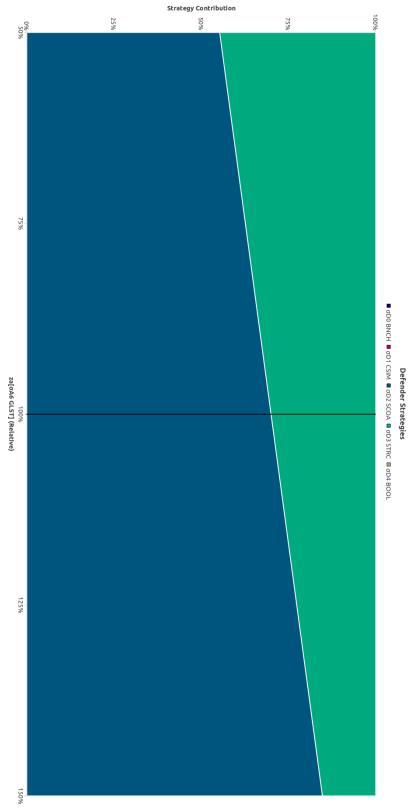

| Figure 9. Defender Strategies as $Z_D(SCOA)$ sweeps from 50% to 150% of its          |

| stimated value; all other variables fixed; HDL Step Game in the Consumer Economy. 91 |

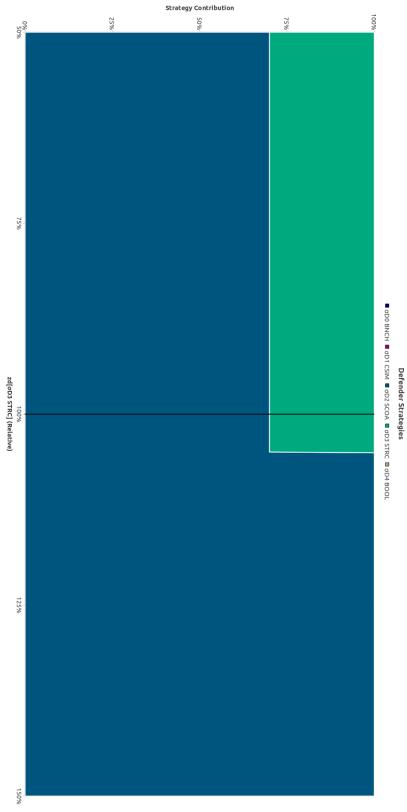

| Figure 10. Defender Strategies as $Z_D(STRC)$ sweeps from 50% to 150% of its         |

|                                                                                      |

estimated value; all other variables fixed; HDL Step Game in the Consumer Economy. 92

Figure 11. Defender Strategies as  $Z_A(STSQ)$  sweeps from 50% to 150% of its estimated value; all other variables fixed; HDL Step Game in the Consumer Economy. 94

| Figure 12. Defender Strategies as $Z_A(GLST)$ sweeps from 50% to 150% of its               |

|--------------------------------------------------------------------------------------------|

| estimated value; all other variables fixed; HDL Step Game in the Consumer Economy. 95      |

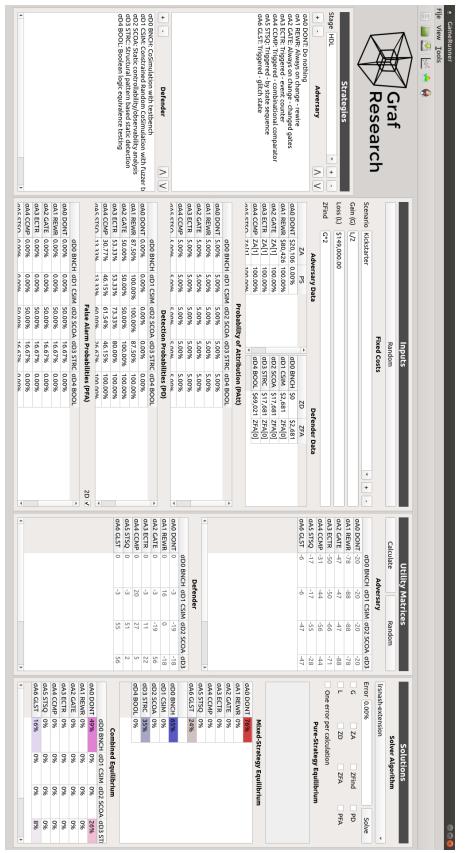

| Figure 13. GameRunner Solving the HDL Step Game in the Kickstarter Economy                 |

|                                                                                            |

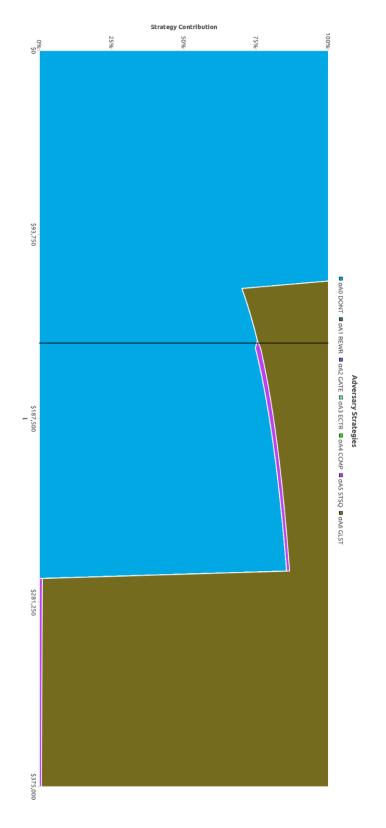

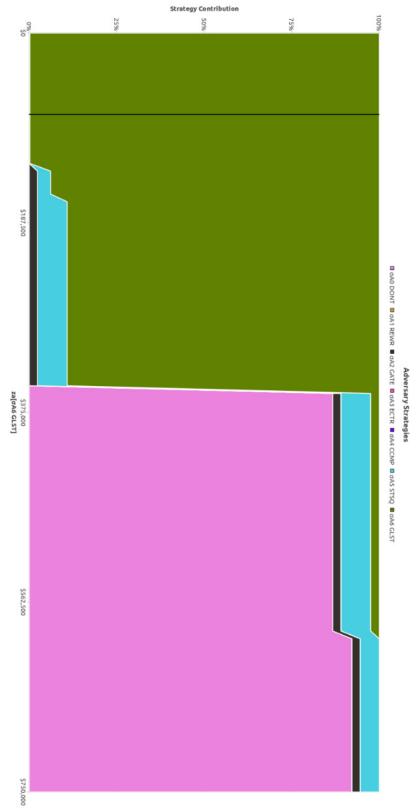

| Figure 14. Adversary Strategies as L sweeps from \$0 to \$375,000 with $G = L/2$           |

| and $Z_{find} = 2G$ ; all other variables fixed; HDL Step Game                             |

| Figure 15. Defender Strategies as <i>L</i> sweeps from \$0 to \$375,000 with $G = L/2$ and |

| $Z_{find} = 2G$ ; all other variables fixed; HDL Step Game                                 |

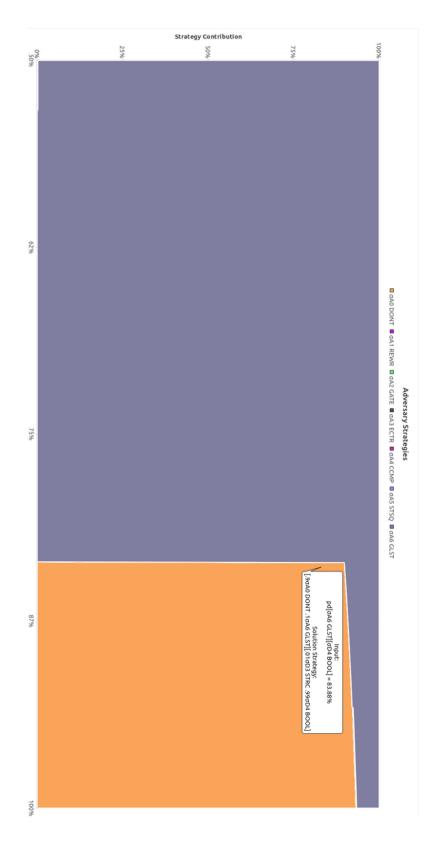

| Figure 16. Adversary Strategies as $P_D$ (GLST, BOOL) sweeps from 50% to 100%;             |

| all other variables fixed; HDL Step Game in the Consumer Economy 103                       |

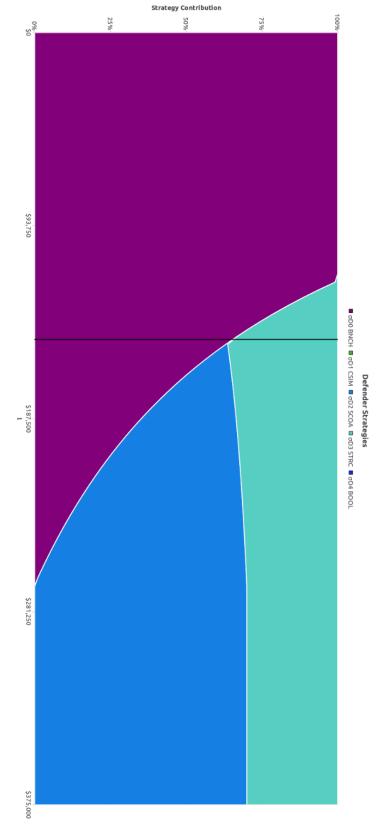

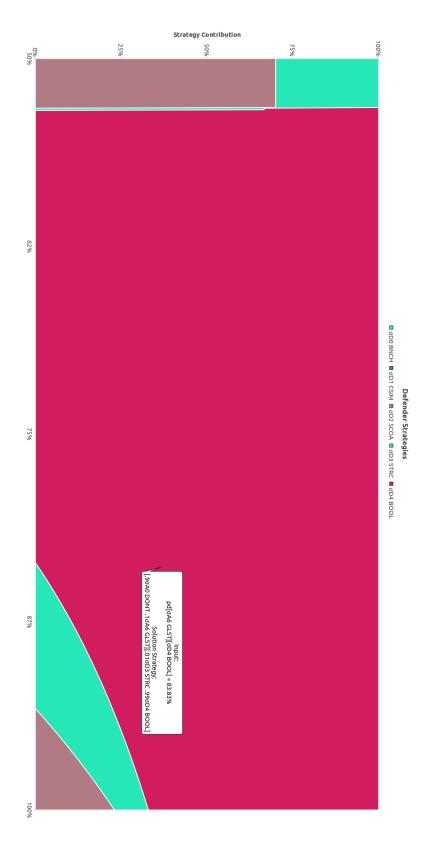

| Figure 17. Defender Mixed Strategies as $P_D(GLST, BOOL)$ sweeps from 50% to               |

| 100%; all other variables fixed; HDL Step Game in the Consumer Economy 104                 |

| Figure 18. Adversary Mixed Strategies as $Z_A(GLST)$ sweeps from \$0 to \$750,000;         |

| all other variables fixed; HDL Step Game in the Consumer Economy 106                       |

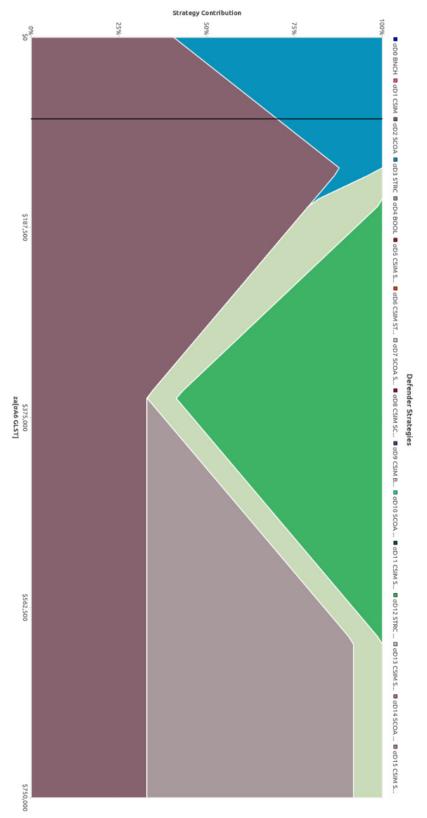

| Figure 19. GameRunner Solving the HDL Step Game, Consumer Economy,                         |

| Defender Strategies Employed in Countermeasure Sets                                        |

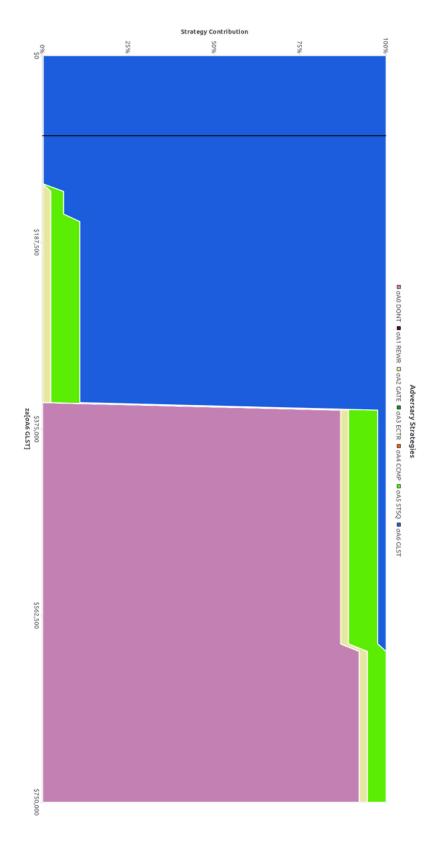

| Figure 20. Adversary Strategies as $Z_{find}$ sweeps from \$0 to \$20,000,000; all other   |

| variables fixed; HDL Step Game with Defender Strategies Employed in Countermeasure         |

| Sets                                                                                       |

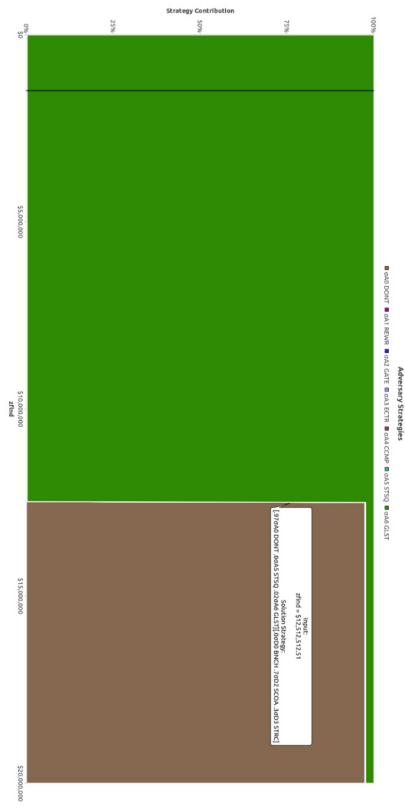

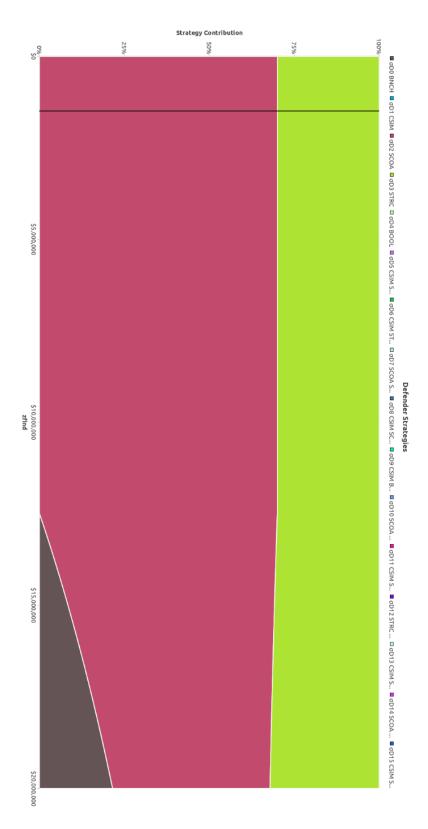

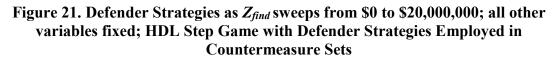

| Figure 21. Defender Strategies as $Z_{find}$ sweeps from \$0 to \$20,000,000; all other    |

| variables fixed; HDL Step Game with Defender Strategies Employed in Countermeasure         |

| Sets                                                                                       |

| Figure 22. Adversary Strategies as $Z_A$ (GLST) sweeps from \$0 to \$750,000; all    |  |  |

|--------------------------------------------------------------------------------------|--|--|

| other variables fixed; HDL Step Game under the Consumer Economy with Defender        |  |  |

| Strategies Employed in Countermeasure Sets                                           |  |  |

| Figure 23. Defender Strategies as $Z_A$ (GLST) sweeps from \$0 to \$750,000; all     |  |  |

| other variables fixed; HDL Step Game with Defender Strategies Employed in            |  |  |

| Countermeasure Sets                                                                  |  |  |

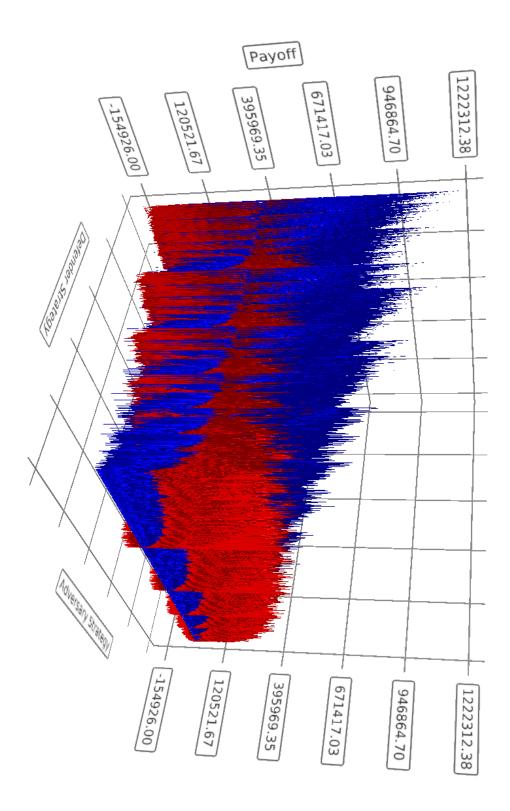

| Figure 24. GameRunner-Created 3D Graph of Adversary (Red) and Defender               |  |  |

| (Blue) Utility Function Payoffs under All Possible Mixed Strategies; HDL Game in the |  |  |

| Consumer Economy                                                                     |  |  |

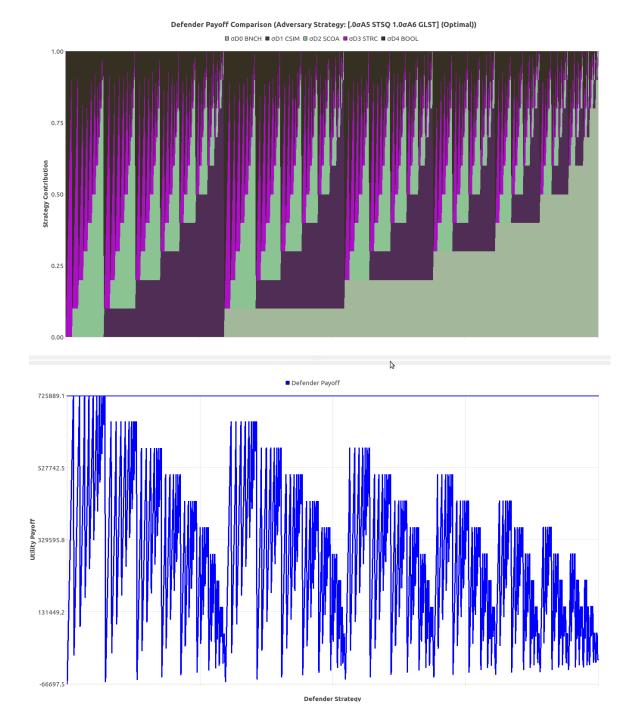

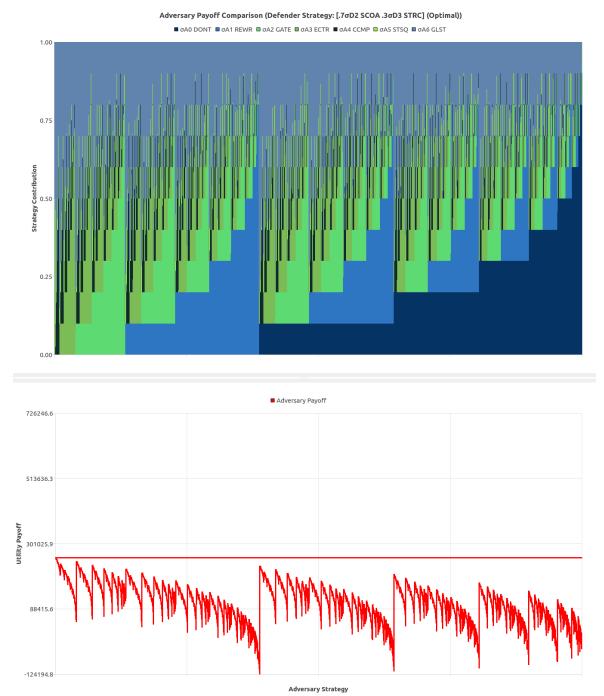

| Figure 25. GameRunner-Created 2D Graph of Defender Mixed Strategy Sets               |  |  |

| (Top) and the Resulting Defender Payoffs (Below) When the Adversary Plays the Nash   |  |  |

| Equilibrium-Selected Optimal Strategy; HDL Game in the Consumer Economy 122          |  |  |

| Figure 26. GameRunner-Created 2D Graph of Defender Mixed Strategy Sets               |  |  |

| (Top) and the Resulting Defender Payoffs (Below) When the Adversary Plays the Nash   |  |  |

| Equilibrium-Selected Optimal Strategy; HDL Game in the Consumer Economy 123          |  |  |

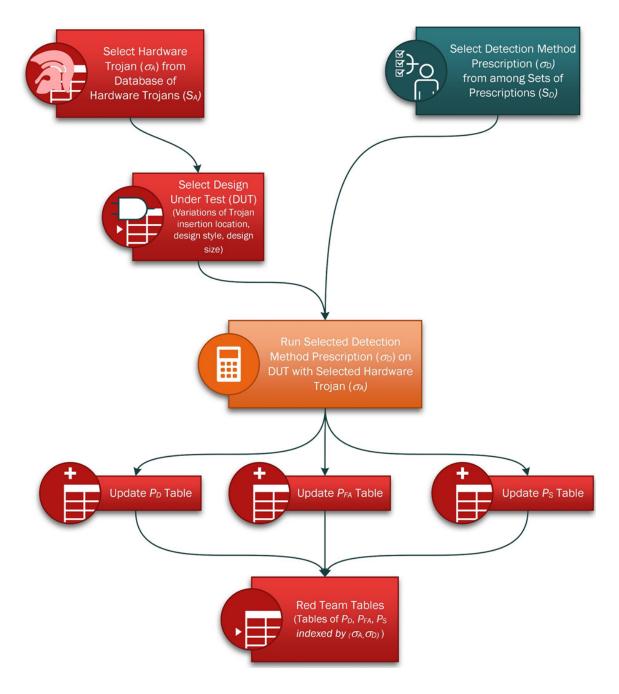

| Figure 27. Red Team Table Generation128                                              |  |  |

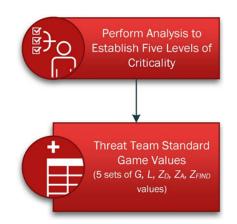

| Figure 28. Threat Team Standard Game Generation                                      |  |  |

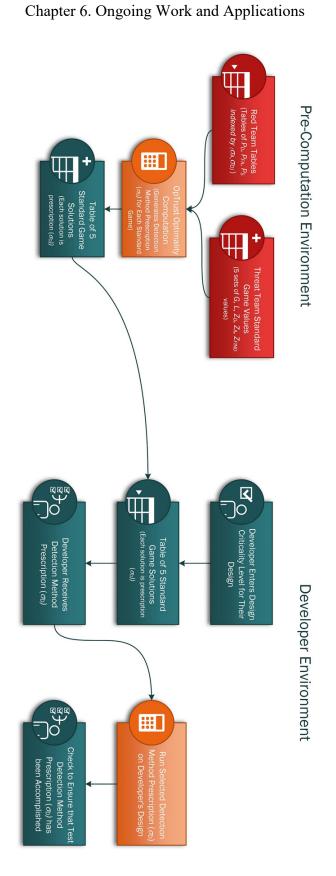

| Figure 29. Separation of Pre-Computation Environment and Developer                   |  |  |

| Environment                                                                          |  |  |

## **Figure Acknowledgements**

Figure 1 was created by Wikimedia user Goran tek-en and was shared at https://commons.wikimedia.org/wiki/File:Maginot\_Line\_ln-en\_svg.svg under Creative Commons Attribution-ShareAlike 3.0 Unported. Please see https://creativecommons.org/licenses/by-sa/3.0/). No changes were made to the image.

Figure 5 and Figure 6 are derived from [10], a collaborative work between the author of this dissertation and cited co-authors of [10].

Figure 7 is from [9], a collaborative work between the author of this dissertation and the cited co-authors of [9].

All other figures are the original work of the author.

# **List of Tables**

|       | Table 1. The Trust Game in Normal Form                                     | . 53 |

|-------|----------------------------------------------------------------------------|------|

|       | Table 2. Example Adversary Strategies and Costs                            | . 54 |

|       | Table 3. Example Defender Strategies and Costs                             | . 55 |

|       | Table 4. Table of $P_D(\sigma_A, \sigma_D)$ Values                         | . 55 |

|       | Table 5. Table of $P_{FA}(\sigma_D)$ Values                                | . 55 |

|       | Table 6. The Trust Game in Normal Form Showing Tuples of (Adversary Utilit | ty,  |

| Defen | der Utility) in \$K's                                                      | . 56 |

|       | Table 7. Hypothetical Trust Game Solution via IEDS                         | . 56 |

|       | Table 8. Game Scenarios                                                    | 61   |

|       | Table 9. Adversary Strategies and Costs                                    | . 65 |

|       | Table 10. Defender Strategies and Costs                                    | . 71 |

|       | Table 11. Three Economies (All Values \$)                                  | . 72 |

|       | Table 12. P <sub>D</sub> by Adversary and Defender Strategy                | . 80 |

|       | Table 13. P <sub>FA</sub> by Defender Strategy                             | . 80 |

|       | Table 14. Two-Player Strategic Game: HDL Step, Kickstarter Economy         | . 81 |

| Table 15. Two-Player Strategic Game: HDL Step, Consumer Economy                |

|--------------------------------------------------------------------------------|

| Table 16. Two-Player Strategic Game: HDL Step, Network Device Economy 82       |

| Table 17. Two-Player Strategic Game: 3PIP Step, Kickstarter Economy            |

| Table 18. Two-Player Strategic Game: 3PIP Step, Consumer Economy               |

| Table 19. Two-Player Strategic Game: 3PIP Step, Network Device Economy 84      |

| Table 20. <i>P<sub>D</sub></i> by Adversary and Defender Strategy (SCOA, STRC) |

| Table 21. P <sub>FA</sub> by Defender Strategy (SCOA, STRC)    89              |

| Table 22. $P_D$ by Adversary and Defender Strategy with Defender Strategies    |

| Employed in Countermeasure Sets                                                |

| Table 23. $P_{FA}$ by Defender Strategy with Defender Strategies Employed in   |

| Countermeasure Sets                                                            |

| Table 24. Two-Player Strategic Game: HDL Step, Consumer Economy, Defender      |

| Strategies Employed in Countermeasure Sets                                     |

| Table 25                                                                       |

| Table 26. Raw Detection Method Results by Adversary Strategy Taxonomy          |

| Category                                                                       |

# **List of Equations**

| Eq. 1. Adversary Utility Function                               | 46  |

|-----------------------------------------------------------------|-----|

| Eq. 2. Defender Utility Function                                | 47  |

| Eq. 3. Simplified Adversary Utility Function                    | 53  |

| Eq. 4. Adversary Expected Utility                               | 86  |

| Eq. 5. Defender Expected Utility                                | 86  |

| Eq. 6. Possible Rationality-Weighted Adversary Utility Function | 140 |

| Eq. 7. Possible Rationality-Weighted Defender Utility Function  | 141 |

| Eq. 8. Defender Utility Function in the Prevention Game         | 149 |

| Eq. 9. Adversary Utility Function in the Prevention Game        | 149 |

# List of Acronyms

| 3PIP  | Third-Party Intellectual Property                                    |

|-------|----------------------------------------------------------------------|

| AES   | Advanced Encryption Standard                                         |

| AI    | Artificial Intelligence                                              |

| APT   | Advanced Persistent Threat                                           |

| ASIC  | Application Specific Integrated Circuit                              |

| ATPG  | Automated Test Pattern Generation                                    |

| AWS   | Amazon Web Services                                                  |

| BLE   | Boolean Logic Equivalence (generally)                                |

| BNCH  | Testbench (Trojan defender strategy in this work)                    |

| BOOL  | Boolean Logic Equivalence (Trojan defender strategy in this work)    |

| CCMP  | Combinational Comparator (Trojan adversary strategy in this work)    |

| CEP   | DARPA Common Evaluation Platform                                     |

| CPU   | Central Processing Unit                                              |

| CSIM  | Constrained Random Simulation (Trojan detection method in this work) |

| DARPA | Defense Advanced Research Projects Agency                            |

| DMEA  | Defense Microelectronics Activity                                    |

| DoD   | United States Department of Defense                                  |

| DONT  | Do Nothing (Trojan adversary strategy in this work)                  |

| DPA   | Differential Power Analysis                                          |

| DSP   | Digital Signal Processor                                             |

| DUT   | Design/Device Under Test                                             |

| ECTR        | Event Counter (Trojan adversary strategy in this work)                   |

|-------------|--------------------------------------------------------------------------|

| EDA         | Electronic Design Automation                                             |

| EEE         | Enumeration of Extreme Equilibria algorithm                              |

| eFPGA       | Embedded Field Programmable Gate Array                                   |

| EUT         | Expected Utility Theory                                                  |

| FPGA        | Field Programmable Gate Array                                            |

| GATE        | Change Gates (Trojan adversary strategy in this work)                    |

| GLST        | Glitch State Trojan (Trojan adversary strategy in this work)             |

| GNU         | GNU's Not Unix!                                                          |

| GPU         | Graphics Processing Unit                                                 |

| GUI         | Graphical User Interface                                                 |

| HDL         | Hardware Description Language                                            |

| HLL         | High Level Language                                                      |

| HLS         | High Level Synthesis                                                     |

| HRNG        | Hardware Random Number Generator                                         |

| HTH         | Hardware Trojan Horse                                                    |

| IC          | Integrated Circuit                                                       |

| IEDS        | Iterated Elimination of Dominated Strategies                             |

| ΙΟ          | Input/Output                                                             |

| IP          | Intellectual Property                                                    |

| JSON        | JavaScript Object Notation                                               |

| LRS         | Revised Reverse Search vertex enumeration algorithm                      |

| MPI         | Message Passing Interface                                                |

| MPSoC       | Multi-Processor System-on-Chip                                           |

| NP-Complete | Non-Polynomial Complete                                                  |

| PUF         | Physically Unclonable Function                                           |

| RAM         | Random Access Memory                                                     |

| REWR        | Rewire (Trojan adversary strategy in this work)                          |

| SEM         | Scanning Electron Microscope                                             |

| SCOA        | Sandia Controllability Observability Algorithm (Trojan defender strategy |

|             | in this work                                                             |

|             |                                                                          |

| SHARP  | Stochastic Human behavior model with Attractiveness and Probability |

|--------|---------------------------------------------------------------------|

|        | weighting                                                           |

| SoC    | System-on-Chip                                                      |

| SRAM   | Static Random-Access Memory                                         |

| STRC   | Structural detection (Trojan defender strategy in this work)        |

| STSQ   | State Sequence (Trojan adversary strategy in this work)             |

| SU-QRE | Subjective Utility Quantal Response Equilibrium                     |

| TCL    | Tool Command Language                                               |

| TSS    | Trusted Silicon Stratus                                             |

| VLSI   | Very Large Scale Integration                                        |

| VM     | Virtual Machine                                                     |

# **Chapter 1. Introduction**

Microelectronics security commonly requires a designer to play the role of defender. This defender must protect components of their design from an adversary who wishes to gain from some aspect of the designer's system at the expense of the designer. These encounters between the adversary and the defender may be modeled as two-player strategic games. From these games, means of optimizing strategies for both players to accomplish their goals may be discovered. This dissertation concerns itself with these encounters and how to accurately construct game representations of the subject encounters and how to interpret the conclusions of the games to the advantage of each player. These encounters are explored principally in the context of integrated circuit design security, with a focus on Field Programmable Gate Arrays (FPGAs) and the binary files that configure them: bitstreams. We delve in depth into the considerations of a designer who wishes to ensure that they produce an FPGA bitstream design that is free from any unwanted content.

This unwanted content is produced by an adversary who wishes to accomplish an exploitation goal by inserting a Hardware Trojan Horse (HTH). FPGAs present two major HTH domains of concern. The first is the traditional domain, wherein the HTH is a malevolent Hardware circuit constructed during the manufacture of a device. The second domain comprises HTH circuits configured by programming otherwise benign portions of the FPGA hardware through malicious alteration of the bitstream. We also treat, more briefly, the general area of design security for systems that contain bitstreams, other firmware, software, and hardware considerations. Additionally, we posit that similar game models may be used to determine design confidentiality strategies, where the designer

wishes to keep secret certain properties of their design – most often, its implementation details – from an adversary who wishes to extract those properties.

Within our primary focus, we must establish a mechanism for reasoning about Hardware Trojan Horse (HTH) detection strategies. This requires considering a more complex set of influences than those treated in traditional circuit verification practice. In addition to traditional concerns about the coverage a verification method might accomplish with respect to some defect, the relationship between the creator of the Trojan (the adversary) and developer of Trojan detection methods (the defender) is governed by strategies, incentives, and creativity. While an undetected defect (e.g., a manufacturing flaw or an implementation bug) being searched for by a traditional verification method may cause outcomes as grave as those caused by an HTH, there is no guiding intelligence making rational choices about how to optimally produce those outcomes. Rather, we often assume they occur randomly, and this assumption is then built into the requirements of verification techniques to discover the subject defect. For example, when pursuing optimal coverage of stuck-at-0/1 or bridging faults [1], we may treat their occurrence in different circuit regions as more or less equivalently likely. Questions of detection approach optimality collapse into an overall circuit coverage metric. With all other costs constant, a method that accomplishes the best overall circuit coverage is the most preferred.

Conversely, with HTH detection, the adversary does have the opportunity to make optimal choices about whether, which, and where to use an HTH to accomplish their goals. When considering how to optimally defend against such adversaries, we must consider more than rudimentary metrics about defensive solutions such as likelihood of detecting a Trojan. We must also consider the adversary's desired outcome, their strategies for accomplishing it, and the resources they have at their disposal to expend in pursuit of it. As we will see, in many cases, the intuitions derived from verification best practices can fail in the face of an informed adversarial attack. It will be shown that the HTH detection methods with both the highest probability of detection and the lowest false alarm rates are not always the optimal play for defenders that face a rational adversary who is simultaneously optimizing their HTH strategy. In fact, we will see that high-performing detection methods can fool the defender into creating a Maginot Line of defenses in an arrangement that guarantees only that the adversary will attack in a manner for which they have not prepared [2].

As in Figure 1, if a defender invests enormous resources in a baseline defensive strategy – but does not consider how their strategy will cause their adversary to react – they risk being vulnerable to an adversary who optimizes their approach to a defender's known weaknesses. Verification best practices provide our Maginot Line. They are static defenses that consider only those HTH attacks that take the expected form of errors and bugs that can be detected by verification methods. As we will see, if the adversary knows which verification methods are available, they will go to the trouble of creating useful HTH attack vectors that do not conform to the defender's expectations. They will "invade through the Low Countries" and bypass the defenses.

Figure 1. Maginot Line between France and Germany [3]

Given this challenge, a framework for optimal decision making in this adversarydefender interaction is necessary. This work introduces a novel use of game theory to produce the requisite formal, reliable, neutral, and automated framework for quickly optimizing defender strategies [3,5,6,7,8,9]. The games are constructed to consider first the baseline strategies of each player and optimize the selection of adversarial and defensive strategies in that context. We present and refine the game variables and probabilities; demonstrating empirical means of populating the probability values involved; performing an experiment on an example dataset; and creating software to automate this experimentation, analyze and visualize its results, and automate the user response. We further demonstrate its applicability both to systems and other domains of microelectronics security.

### **1.1 Summary of Contributions**

Contribution 1: The introduction of security economic models that incorporate the efficacy of FPGA Trojan detection methods and the incentives of both the adversary and defender in hardware Trojan encounters. Prior models applied to this problem ignored the components of adversary and defender beliefs.

Impact: Allows an adversary or a defender to optimize their strategy if they know the strategy of the other party. Because the components of the security economic models are built to allow data from empirical testing of both adversary and defender strategies to directly affect model outcomes, data from both red team testing and real-world encounters may now directly improve our knowledge of adversary and defender strategy elections. This claim is demonstrated through the implementation of a software tool that makes use of these models and a series of experiments in Chapters 3-5.

Contribution 2: The introduction of a simple two-person strategic game theoretic model that leverages the aforementioned security economic models and the Nash equilibrium solution concept. The body of work documented in this dissertation holds claim to the first publication that applied two-person strategic games to microelectronics security. The refinement of that model into the FPGA-Trojan-focused game model featured in this work combines the benefits of the Contribution 1 player models with the ability to solve games to predict those players' actions.

Impact: Allows an adversary or defender to simultaneously predict their opponent's optimal play as well as their own best response. Red team and real-world encounter data can be used to continuously improve these predictions, due to the fidelity of the Contribution 1 models. This claim is demonstrated through the implementation of a software tool that makes use of these models and a series of experiments in Chapters 3-5.

Contribution 3: Improvement to the FPGA Trojan game model to account for the entire attack surface available to an adversary, margin of error in derived and measured game variables, and mixed strategy solutions for adversary and defender. Contemporary works in games for Hardware Trojans consider only 3<sup>rd</sup>-Party IP and device vendors as potential adversaries; this work considers and models the design and deployment lifecycle of the device as the attack surface available to the adversary. This work also provides software mechanisms to explore game results when model variables are altered.

Impact: The first fully comprehensive model that simultaneously accounts for every adversarial entry point into a bitstream, predicts the optimal adversary behavior, and suggests optimal defense. This claim is demonstrated through the implementation of a software tool that makes use of these models and a series of experiments in Chapters 3-5.

Contribution 4: Universal game models for microelectronics security for activities that involve the detection and prevention of malice. The models allow any microelectronics security encounter that involves an adversary and a defender to be structured as a 2-person strategic game, including in the context of design integrity, design security, anticounterfeiting, and other scenarios. To our knowledge, this dissertation marks the first attempt in literature to express general microelectronics security game models that can be applied to this range of solutions.

Impact: Demonstrates the broad application of the game theoretic approach to other adversary/defender interactions in microelectronics security. The models that

satisfy this claim are documented as the general system game, general detection game, and general prevention game in Chapter 6.

Contribution 5: An automated method of determining and applying optimal detection strategies for hardware Trojan detection, based on the models of Contributions 1-3. This contribution is evidenced by a software guidance tool, GameRunner, that maintains security economic metrics and game models, provides guidance based on input adversary and defender strategy metrics, and provides means of quantitatively demonstrating the claimed improvement on outcomes. To our knowledge, this is the first such guidance method that automates the application of optimal strategies for hardware Trojan detection.

Impact: Provides automated guidance of optimal defensive strategies without requiring the user to have special knowledge of security economics or game theory, enabling broad application. This automation obviates the need for users of the tool to understand the game theory behind the decisions made by the tool. They must simply apply the guidance by running the script. This claim is demonstrated through the implementation of GameRunner and a series of experiments in Chapters 3-5.

Contribution 6: Novel visualization techniques which allow for the exploration of the investment-security state space within the context of complex adversary-defender engagements. This contribution is evidenced by GameRunner, a software program that can be used to depict such strategies and their benefits in exploring domain-specific complex games. Prior software tools for game solving are general game solvers.

Impact: Provides a simplified way of reasoning about where investment should be made to improve outcomes for either opponent while abstracting the advanced mathematics underlying the tool behind a graphical interface. The visualizations that result from this analysis allow for the ability to explore the impact of individual variables on the mixed strategy results leads to useful observations, including visual cues of where the influence of individual variables begin to dominate the decision making of the players. This claim is demonstrated through a series of analyses in Chapter 5.

### **1.2** Document Organization

This document is organized as follows.

**Chapter 2. Background.** In this chapter, we cover the background of general microelectronics design security practices, FPGA-specific design security practices, and game theory as applied to microelectronics security.

**Chapter 3. Security Economics and Game Theory**. In this chapter we establish the security economic and game theoretic underpinnings of our model. We discuss our rationale for the construction of games and the selection of game solution concepts, including insights on correct game construction. We explore the variables of concern, the utility functions, and the concept of "step games" used in our model. We briefly treat player rationality and mechanisms for computing game solutions. We include a set of example game solutions, demonstrating the use of the iterated elimination of dominated strategies (IEDS) and Nash equilibrium solution concepts. This "by hand" solution concept illustrates the value of the game in a simplified scenario prior to the more in-depth assessments of the following chapters. Portions of this chapter were published as the following works:

- [5] J. Graf, "Toward Optimal Hardware Trojan Detection through Security Economics and Game Theory," in *GOMACTech 2016 Proceedings*, March 2016, paper 14.4.

- [6] J. Graf, "Trust games: How Game Theory Can Guide the Development of Hardware Trojan Detection Methods," in *Hardware Oriented Security and Trust* (*HOST*), 2016 IEEE International Symposium on, May 2016.

The publication of these works contributed to invitations to present the following invited lectures derived in part from those works:

- [20] J. Graf, "Optimizing Forward Design Trust for FPGAs," invited lecture delivered to *Single Event Effects Symposium / Military and Aerospace Programmable Logic Devices Workshop*, San Diego, CA, May 25, 2017.

- [23] J. Graf, "Measuring Trust," invited lecture delivered to Single Event Effects Symposium / Military and Aerospace Programmable Logic Devices Workshop, San Diego, CA, May 24, 2018.

• [24] J. Graf, "Optimal Trust Strategies," invited lecture delivered to the National Academy of Sciences for the *National Academies Study on Secure and Reliable Microelectronics for AF Systems*, Washington, DC, June 19, 2018.

**Chapter 4. Experiment.** In this chapter, we present an experiment conducted to demonstrate the practical value of the game, illustrating the construction of player strategies, the use of game variables, the design of our game solving tool, and its automated solving functions.

**Chapter 5. Results.** In this chapter, we discuss the results of this experiment as well as the GameRunner software we created for exploring game solutions and directing defensive responses. We use GameRunner to explore several "what-if" scenarios that emerge from the game in the experiment. We include an analysis of whether we can be confident that this approach provides value. The discussion in Chapters 4 and 5 were published as:

- [9] J. Graf, W. Batchelor, S. Harper, R. Marlow, E. Carlisle, and P. Athanas, "A Practical Application of Game Theory to Optimize Selection of Hardware Trojan Detection Strategies," manuscript submitted to the *Journal of Hardware and Systems Security*, 2019.

- [10] R. Marlow, S. Harper, W. Batchelor, and J. Graf, "Hardware Trojan Detection using Xilinx Vivado," in 2018 IEEE National Aerospace and Electronics Conference, 2018.

**Chapter 6. Ongoing Work and Applications.** In this chapter we discuss the continuing work that has resulted from the above-documented research and results. This includes exploration of subrational game play and applications to a variety of new domains of microelectronics security. While many publications are planned related to this work as it continues, the following papers have been published thus far based on the work described in this chapter:

[3] J. Graf and P. Athanas, "How Threats Drive the Development of Secure Reconfigurable Devices," in 2008 IEEE National Aerospace and Electronics Conference, 2008, pp. 239–245.

- [7] J. Graf, "Towards system-level adversary attack surface modeling for microelectronics trust," in 2016 IEEE National Aerospace and Electronics Conference (NAECON) and Ohio Innovation Summit (OIS), 2016, pp. 474–477.

- [8] J. Graf, "OpTrust: Software for Determining Optimal Test Coverage and Strategies for Trust," in *GOMACTech 2017 Proceedings*, March 2017.

**Chapter 7. Conclusions.** In this chapter, we present our concluding thoughts and speculation about future directions.

## **1.3 Related Contributions**

Prior to this work, the author has made other contributions to the field of secure microelectronics. A subset of this work is cited in this publication, and is collected here for the committee's consideration:

- [10] J. Graf and P. Athanas, "A key management architecture for securing offchip data transfers," in *Field Programmable Logic and Application, ser. Lecture Notes in Computer Science*, J. Becker, M. Platzner, and S. Vernalde, Eds. Springer Berlin Heidelberg, 2004, vol. 3203, pp. 33–42.

- [12] A. J. Mahar, P. M. Athanas, S. D. Craven, J. N. Edmison, and J. Graf, Design and Characterization of a Hardware Encryption Management Unit for Secure Computing Platforms," in 39th Hawaii International International Conference on Systems Science (HICSS-39 2006), CD-ROM / Abstracts Proceedings, 4-7 January 2006, Kauai, HI, USA, 2006.

- [13] P. Athanas, J. Bowen, T. Dunham, C. Patterson, J. Rice, M. Shelburne, J. Suris, M. Bucciero, and J. Graf, "Wires on demand: Run-time communication synthesis for reconfigurable computing," in 2007 International Conference on Field Programmable Logic and Applications, Aug 2007, pp. 513–516.

- [14] J. Graf, J. Hallman, and S. Harper, "Trust in the FPGA Supply Chain using Physically Unclonable Functions," in *GOMACTech 2010 Proceedings*, March 2010, paper 22.4, pp. 317–319.

- [15] J. Graf, S. Harper, and L. Lerner, "Ensuring Design Integrity through Analysis of FPGA Bitstreams and IP cores," in *Proceedings of the International Conference on Engineering of Reconfigurable Systems and Algorithms (ERSA)*, 2012.

- [16] J. Graf, S. Harper, and L. Lerner, "The Integrity of FPGA Designs: Capabilities Enabled by Unlocking Bitstreams and 3rd-Party IP," in *GOMACTech 2012 Proceedings*, March 2012, paper 18.3, pp. 201–204.

- [17] J. Graf, S. Harper, J. Hallman, and B. Knight, "Managing Risk to Field Programmable Gate Array Trust: A Deployment Framework for DoD Instruction 5200.44," in *GOMACTech 2014 Proceedings*, March 2014, paper 6.1, pp. 77–80.

- [18] S. Baka, J. Hallman, S. Harper, and **J. Graf**, "Trust and Reuse of 3rd-Party IP," in *GOMACTech 2014 Proceedings*, March 2014, paper 2.4, pp. 25–28.

- [19] K. Urish and J. Graf, "Mitigation of Space-Reliability Reduction Trojans in FPGA Designs," in *GOMACTech 2015 Proceedings*, March 2015, paper 7.1, pp. 91–94.

- [20] J. Graf and A. A. Sohanghpurwala, "Private Verification for FPGA Bitstreams," in *GOMACTech 2017 Proceedings*, March 2017.

- [21] S. Harper, J. Graf, W. Batchelor, T. Dunham, and P. Athanas, "Introducing a Trust Metric Foundation and Deriving Trust-for-Buck," in *GOMACTech 2019 Proceedings*, March 2019.

## **1.4 Summary of Sponsorship**

This work has been sponsored by the United States Air Force under a series of Small Business Innovative Research contracts awarded to the Graf Research Corporation:

- AF161-150, Optimal Strategies for Cloud-Based Trust Assessment, Phase 1, contract FA8650-16-M-1808, June 14, 2016 – March 13, 2017; \$149,998; Principal Investigator: Jonathan Graf.

- AF161-150, Optimal Strategies for Cloud-Based Trust Assessment, Phase 2, contract FA8650-17-C-1148, September 28, 2017 – December 30, 2019, \$749,740; Principal Investigator: Jonathan Graf.

AF161-150, Optimal Strategies for Cloud-Based Trust Assessment, Phase 3, contract in negotiations #TBD, 2019 – 2026 (estimated), \$49.9M (estimated); Principal Investigator: Jonathan Graf.

# Chapter 2. Background

Security in the context of FPGAs is a term whose meaning is as broad as the applications served by the devices. FPGAs are growing in resources and complexity, driven by demand from a burgeoning array of new applications. From the simple low-power traditional FPGAs whose silicon is dedicated almost exclusively to programmable logic to the emerging FPGA Multi-Processor System on Chip (MPSoC) device class, FPGAs continue to realize their promise for novel processing architectures in a variety of domains. Recently, the same-die close coupling of heterogeneous processing structures with hardened security resources has created the potential for FPGAs to serve a wide variety of new security applications. Modern FPGAs provide cryptographic accelerators, physically unclonable functions (PUFs), and hardware random number generators (HRNGs). On the MPSoC high end, these features are combined on the same die with programmable FPGA fabric, centralprocessing units (CPUs), graphics processor units (GPUs), digital signal processors (DSPs), and programmable input-output (IO) resources. This pairing of processing and security resources raises the possibility of using them to create tightly integrated, custom secure processors for future high-security networked applications. FPGAs with these features hold the potential of revolutionizing the security posture for high-security Internet of Things (IoT) applications such as autonomous vehicles, intelligent energy grid devices, home automation, various industrial and commercial control systems, and the datacenter. Within these applications, FPGAs can provide their embedded security features to a variety of security application domains, including information assurance, mission assurance, and cyber-physical systems security.

Each of those security applications may be undermined, however, if the design of the FPGA is not secure. The fulcrum on which FPGA design security pivots is the programming *bitstream*. The bitstream is a binary design container whose bit values mold the silicon resources of the FPGA into the user-specified application by populating logic look-up tables (LUTs) and block RAMs (BRAMs) while also parameterizing complex CPUs, GPUs, IOs, DSPs, and routing switch matrices. The majority of modern FPGAs store this bitstream at runtime in a static RAM (SRAM) memory array that is integrated with the silicon device resources.<sup>1</sup> The FPGA designer produces the bitstream using electronic design automation (EDA) tools.

The early part of the design cycle consists of steps similar to those used to create any digital electronic integrated circuit (IC). The implementation of the identified requirements for a new FPGA is usually accomplished using a hardware description language (HDL) such as Verilog or VHDL.<sup>2</sup> The designer's HDL description goes through a series of transformations to become a bitstream. These HDL statements are *synthesized* to become a netlist of connected logic primitives called a netlist. The netlist is *mapped* to resources of the types present on the target FPGA device. If sufficient resources are present, the EDA tools identify the specific individual resources on the FPGA where each function will be realized (*placement*) and connects them with specific routing resources (*routing*), resulting in a placed-and-routed netlist (*placelist*). At any of the previous design representations (HDL, netlist, or placelist), the designer may augment their design with circuits produced by and purchased from third parties, commonly referred to as 3rd-Party IP (3PIP). With the final placelist in hand, a bitstream compiler translates it into the bit settings required to

<sup>&</sup>lt;sup>1</sup> There are other classes of FPGA that store the bitstream value in flash or anti-fuse memories, but this document focuses on SRAM FPGAs due to their ubiquity.

<sup>&</sup>lt;sup>2</sup> New high-level synthesis (HLS) programming models are becoming popular that allow the use of high level languages (HLLs) to program FPGAs. Mature HLL-to-gates ecosystems include the C-to-gates functions of Xilinx Vivado HLS design environment and the OpenCL integration into Altera Quartus Prime. HLS typically does not bypass the steps described here; rather, it precedes and automatically produces the HDL that is then used in subsequent steps.

realize the design on the FPGA. Those bit settings are arranged in an addressable order that will be understood by the on-device FPGA configuration engine, allowing them to properly distribute the bits to the appropriate resource upon device startup. The bits in this order are referred to as the bitstream.

This bitstream sits at the midpoint between the two major fields of FPGA design security. The first field looks backwards from the point the bitstream is made and examines the above-described design flow. It asks whether the bitstream contains *only* what the designer intended *and no other function*. Specifically, this field considers whether an adversary may have introduced a malicious function into the bitstream in the form of a hardware Trojan. This field of study is referred to as *FPGA design integrity*, or more often, simply as *FPGA Trust*. The second field looks forward from the point a trusted bitstream is in hand and asks how the confidentiality and integrity of that bitstream might be preserved throughout the deployed lifecycle of the design. The collective name for using measures to prevent, detect, and respond to adversarial exploitation in order to preserve bitstream confidentiality and integrity is *FPGA anti-tamper*. As we will see in the section that follows, both of these fields emerged from early research concerns raised by the US Department of Defense (DoD) and have blossomed into robust areas of academic [25][36] and commercial [26][27] interest.

The primary field of our work in this document is FPGA Trust; thus, this is the primary focus of this background section. However, we include a treatment of FPGA anti-tamper for two reasons. First, as we will see in subsequent chapters, the fields are directly related. For example, we demonstrate that an HTH can be inserted for the sole purpose of making subsequent tamper easier in Chapter 4. Second, we will also show that the models used to assess FPGA trust have direct analogues in the fields of trust assessment in different devices (e.g., Application Specific Integrated Circuits (ASICs)), different embodiments (e.g., software), and adjacent fields of security (FPGA anti-tamper). We revisit alternative uses of our model in Chapter 6.

The remainder of this chapter is organized as follows. In Section 2.1 we cover the background for our major areas of concern for FPGA security, FPGA Trust, as well as a brief treatment of the adjacent field of FPGA anti-tamper. In 2.2, we cover the background

literature for work that attempts to measure and strategize about hardware Trojans as well as the general use of game theory to optimize security concerns.

### 2.1 Attack and Defense

Attacks against microelectronic devices and their related defenses can take many forms. In this document, we are primarily concerned with the fields of trust and anti-tamper.

#### 2.1.1 Trust Background

In the last fifteen years, hardware Trojan design and detection have been studied and characterized [28]. Several taxonomies [29,30] have been published that sort HTH's into categories based on the stage in a product lifecycle at which they are inserted, their activation mechanism, their effects, their location, and their physical characteristics. Similarly, a maturing literature reveals a wide variety of countermeasures for design-time Trojan detection via behavioral functional validation, formal verification, side-channel analysis, or varieties of structural analysis. Countermeasures may also be employed that seek to make it difficult to insert a Trojan in the first place or make it easier to detect Trojans in running devices [28]. FPGA Trust is best understood in the context of the general challenge of microelectronics trust, which is concerned with keeping the physical implementation of a manufactured IC free of hardware Trojans.

### 2.1.1.1 Microelectronics Trust

The earliest public call to address microelectronics trust in general came in 2005 when the Defense Science Board highlighted it as a critical challenge for the DoD [31]. The responses to this call took many forms, but two are worth brief mention as historical references. First, on the basis of key learnings from a series of small exploratory projects (e.g., [32], which started in 2004), the Defense Advanced Research Projects Agency (DARPA) launched the DoD-focused Trusted Integrated Circuits (TRUST) program [33][34][35]. Second, soon after DARPA TRUST brought interest to the area, the first IEEE International Symposium on Hardware-Oriented Security and Trust (HOST) emerged from the test and verification community at the 2008 Design Automation Conference [36]. After these two seminal events initiated the organized response to the hardware Trojan threat, research has grown into many areas, which are summarized in the following sections.

### 2.1.1.2 IC Hardware Trojans

The portion of integrated circuit trust that relates directly to FPGA bitstream trust is the concern of logical hardware Trojan insertion at design time. Hardware Trojans are generally defined as having both a *trigger* circuit and a *payload* circuit. The trigger "starts" the payload when an event is detected. The event detected by the trigger could be a signal transition, the present state of a state machine, an external influence, or a series of sequential states across multiple timeframes. Notably, the trigger could simply be the power-on of the device, in which case there would be no additional circuitry for the trigger and the payload circuit will always be active.

The traditional HTH taxonomies of [29] and [30] are constructed based on six hardware Trojan attributes:

- 1. Insertion Phase

- 2. Abstraction Level

- 3. Activation Mechanism

- 4. Effects

- 5. Location

- 6. Physical Characteristics

As we will see, in this work, we use taxonomies such as these as organizing principles that subdivide the attack surface upon which adversaries and defenders play their games. Both we and others have created HTH example circuits that fit into these taxonomies, providing ample circuits for experimentation. For example, the *trust-HUB.org* website, founded on the work of Salmani et al [37] and extended by others [38], contains benchmark circuits organized by the above attributes. This repository of circuits is used for benchmarking hardware Trojan detection methods through the use of common circuits. It allows any user to simply "dial-up" a circuit of interest by supplying its desired attributes. It should be noted that this feature may be used just as easily by an adversary as by a researcher. The circuits in the repository are, in some cases, quite sophisticated and specifically designed to evade detection.

## 2.1.1.3 IC Trojan Countermeasures

The most straightforward strategy to prevent hardware Trojans is to control every aspect of the design and manufacturing process. However, the costs involved make this strategy available only to wealthy companies and governments. For example, this is the primary strategy of the Defense Microelectronics Activity (DMEA) Trusted Foundry Program [39]. Since owning custom fabrication facilities and controlling all the personnel, software, and equipment in the microelectronics supply chain is beyond the means of most designers, alternative means of preventing IC Trojans is desired. For those who want to have access to the latest manufacturing processes but cannot afford to own their own leading edge fabs, potential exists in an emerging area of research called *split-manufacturing*, where a portion of IC manufacturing takes place in an untrusted fab with access to the latest silicon process technologies, leaving final metallization to be accomplished in a trusted facility. See for example the work of Vaidyanathan et al [40] and the other performers funded by the ongoing Intelligence Advanced Research Projects Agency "Trusted Integrated Chips" program [41]. However, since this requires two fabs (one contracted, one controlled) and coordination between the two, such an approach is still beyond the reach of most IC designers. Further, since it has no analog to FPGA Trojans in the bitstream, this document focuses on other prevention strategies.

If complete control over the process is not available, one proposed strategy has been to make it difficult to insert a hardware Trojan in the first place by either making the circuit hard to understand or leaving little room in the circuit for a Trojan to be inserted. Recent circuit obfuscation techniques include those proposed by Roy et al. [42], whose EPIC method inserts random gates to obfuscate circuit function; Chakraborty et al., whose methods obfuscate the data flow in circuits [43] [44]; Li et al. who apply structural transformations to the circuit that are unlocked by a secret key [45]; and Zhang et al [46], who use muxes whose paths are determined by the resolution of on-chip Physically Unclonable Functions (PUFs).

One challenge to using these methods to prevent hardware Trojan insertion is that they significantly increase the complexity of circuit test and often cost circuit area, making adoption impractical. Another challenge is that the introduction of re-organized circuits, randomized gates, re-mapped dataflow, and novel physical features introduce risks to yield.

This limits adoption due to the risk designers take in using an obfuscated netlist that puts other design goals (e.g., timing, area, performance) at risk. While some studies, such as those by Rajendran et al. [47], have shown that these obfuscation methods show some promise to preventing the reverse engineering of netlists protected by these methods, more recent literature disagrees. In general, the use of obfuscation is a departure from traditional security doctrine, wherein obfuscation and scrambling techniques are eschewed in favor of more mathematically provable techniques [48]. In the context of software obfuscation, Barak et al demonstrated that mathematically perfect obfuscation is theoretically impossible under general circumstances [49]. By a similar argument, Shamsi et al [50] argue that circuit locking – a popular obfuscation technique – can never be perfectly implemented. Machine-learning techniques have proven effective against a variety of circuit obfuscation strategies [56]. Nonetheless, research is ongoing and may yield future advances. A less costly strategy for preventing hardware Trojans in VLSI devices is simply to fill the circuit with "filler cells" and associated digital-signature-based selfauthentication methods to prevent an adversary's ability to add any new circuitry, per the work of Xiao et al [48][52].

In this document, the HTH countermeasures of primary interest are HTH *detection* strategies.<sup>3</sup> Contrary to the efficacy controversies of prevention countermeasures, detection strategies are well attested. Furthermore, they can be made widely available and do not change the design. These may be divided into those that can be applied during design and those that are applied after the device is manufactured. This document focuses on those that may be applied by the designer themselves at design time, since those methods translate directly to the challenge of FPGA Trojan detection.

Within the category of detection methods, some have focused on reverse engineering circuits to expose their contents for examination. This has utility, for example, in the case of 3<sup>rd</sup>-Party IP evaluation or post-manufacturing ASIC evaluation. For example, REFSM was developed by Meade et al. [53]. It helps to extract control logic from a flattened netlist and permit the partitioning of the circuit. Another such top-down functional analysis tool,

<sup>&</sup>lt;sup>3</sup> While we focus on detection strategies, the models we develop are equally applicable to any HTH countermeasure strategy.

developed by Li et al. [54], mines data gathered from functional simulations to extract knowledge of functions. Other reverse engineering-oriented work attempts to develop new solutions (or circumventions) of the subgraph isomorphism problem – the common NP-complete graph theoretic challenge of searching for small circuit patterns within a larger circuit. For example, see Bouchaour et al. [55]. These methods can raise the abstraction level of the composition of the circuit, exposing implementation details along the way. Charaborty et al [56] demonstrated how machine learning can be brought to bear to assist in determining the function of circuits. Quijada et al [57] demonstrate automated extraction techniques from Scanning Electron Microscope (SEM) based circuit delayering for the purpose of post-manufacturing Trojan assessment. Circuit reverse engineering methods are revisited in the FPGA trust section.

Other Trojan detection methods that apply to design-stage evaluation rely instead on verification techniques to find hardware Trojans. For example, the FANCI technique of Waksman et al. [58] seeks to find Trojans based on models of Trojan triggers. It uses a Boolean functional analysis to determine which circuitry appears *stealthy* in its behavior when subjected to traditional logic simulation. They define stealthy to mean "nearly unused." Similarly, the VeriTrust method from Zhang et al. [59] seeks to find only the trigger portion of the hardware Trojan using the assumption that it will not be activated. A limitation of both FANCI and VeriTrust is that they only look at one sequential stage of a circuit at any given time. That is, they only evaluate the combinational logic between two register stages. Taking advantage of this feature, Zhang et al [60] showed that stealthy implicitly-triggered circuits can be developed that escape FANCI, VeriTrust, and their more simplistic predecessors. Their DeTrust technique spreads the trigger circuitry across both combinational logic blocks and multiple sequential levels to allow its function to blend in with the rest of the good circuitry in the design. The same paper suggests improvements to FANCI and VeriTrust that may account for these even-stealthier triggers, but the techniques must be applied over at least as many sequential stages of the circuit as the Trojan trigger has been spread over. This can be a computationally expensive prospect, making it impossible to guarantee that it can be completed for any given circuit. Salmani [140] proposed another method for circuit detection based on static controllability and observability calculations, processed by a machine learning analysis, which has the advantage of being computationally inexpensive.

Notably, this snapshot of the state-of-the-art is typical of the past decade of hardware Trojan and Trojan detection method development. Just as in any domain of cybersecurity, the adversary creates a method to which the defender reacts. The adversary reacts again with an improvement. The cycle continues.

# 2.1.1.4 FPGA Trust

Trojans that are purely logical – along with their related detection methods – are the same for FPGAs as they are for any general IC. Just as with ICs in general, Trojans implemented out of the FPGA's logic resources may be inserted via modified 3PIP, altered HDL, altered netlists, or via malicious EDA tools. Thus, the above discussion of logical HTHs for ICs applies to FPGAs as well. However, there are notable differences between Trojans that must be physically realized in a traditional IC and those that will be realized as components of an FPGA bitstream. Those differences also demand a different perspective on detection methods in FPGAs, with most of the difference expressed in the unique manner in which FPGA circuits are created: by applying a programming bitstream to a set of programmable logic resources.

To illustrate this, let us consider an adversary who makes use of the now-common advanced persistent threat (APT) style of network attack to gain access to the defender's network.<sup>4</sup> On this network, the defender is producing a design for realization in either an ASIC or an FPGA. If that design is to be realized in an ASIC, the economies that drive ASIC markets indicate it will be implemented in many systems. The hardware Trojan they insert might risk accidental discovery simply because of how many systems might use that processor. This may deter the adversary from their goal for risk of discovery. Furthermore, the adversary faces the challenge that they are inserting their Trojan at design time. Unless the fab responsible for manufacturing the ASIC is also complicit in the act, they run the risk that the fab will discover the Trojan. Fabs use many testing techniques that are undisclosed to their users to ensure yield, which adds further discovery risk for the

<sup>&</sup>lt;sup>4</sup> A version of this discussion was published in [7].

adversary. Finally, even if the Trojan in the ASIC makes it all the way through the fab, the adversary has no means of testing the implemented Trojan to ensure it works prior to its deployment on a large scale.<sup>5</sup> An adversary may be able to overcome these hurdles, though it is outside the scope of this work to speculate about how. It is, however, worthwhile to note that fewer of the above hurdles exist for an adversary wishing to insert a Trojan in an FPGA.

FPGAs are used for designs focused on specific applications whose smaller deployment base does not economically justify the manufacture of an ASIC. These applications can be large Internet routers, industrial control systems, defense systems, or cyber-physical systems. The adversary may target these systems with greater specificity if their entry point is a specific FPGA design used in those systems. Returning to the adversary with an APT-enabled network entry point, for an FPGA design, they are able to see every aspect of that design. The attack surface available to this type of adversary is illustrated in Figure 2. If they have access to the design systems, they are able to access not only the 3PIP, HDL, netlists, and placelists (just as in the ASIC case) but also the final deployment format: the bitstream. Quite often for FPGAs, all of these files reside on the same workstation. From these available choices – which represent the attack surface – the adversary may select the most appropriate point of Trojan insertion and the associated style of change based on what their goal might be. Thus, the adversary may not only insert the Trojan in the system, but - given an APT with the common feature of data exfiltration - they may also retrieve the bitstream with the Trojan in it for testing. Since FPGAs are commodity devices, the adversary can purchase the specific commodity FPGA for which the bitstream is destined to program and test their Trojan in the actual design and ensure it is working. The unique ability for adversaries to select a highly-specific target, the fact that there is no fab involved in the deployment process, and the fact that the Trojan can be tested "remotely" prior to deployment make FPGAs a unique target for Trojans. In these ways, FPGA bitstreams during the design step are similar to software in that they are vulnerable to comprehensive exploitation over-the-wire by a sufficiently advanced adversary.

<sup>&</sup>lt;sup>5</sup> Unless, again, they have cooperation with an insider at the fab.

Figure 2. Attack Surface Available to the APT-Enabled Adversary

The bitstream itself presents an additional component of the attack surface to the adversary. Several papers have demonstrated that the bitstream is subject to reverse engineering. Note and Rennaud [61] produced the first bitstream reverse engineering tool, though their approach was not comprehensive in understanding all features of the bitstream.<sup>6</sup> Significant improvements were subsequently shown by Bergeron et al. [65],

<sup>&</sup>lt;sup>6</sup> Prior to Note and Rennaud, several authors published *design tools* that performed bitstream-level manipulations and leverage detailed knowledge of the bitstream format. Examples include the Xilinx JBits design framework demonstrated by Guccione and Patterson [62][63], the alternate wire database of Steiner and Athanas [64], and the wires-on-demand runtime communications synthesis technique of Athanas et al. [13] (to which the author was a contributor). While these design tools contained knowledge of bitstream function, this section is concerned not with design tools but with tools explicitly developed to reverse engineer the bitstream into a general netlist format.