# Algorithms and Frameworks for Accelerating Security Applications on HPC Platforms

#### Xiaodong Yu

Dissertation submitted to the Faculty of the

Virginia Polytechnic Institute and State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in

Computer Science & Applications

Danfeng (Daphne) Yao, Chair Michela Becchi Ali R. Butt Matthew Hicks Xinming (Simon) Ou

> August 1, 2019 Blacksburg, Virginia

Keywords: Cybersecurity, HPC, GPU, Intrusion Detection, Automata Processor, Android

Program Analysis, Cache Side-Channel Attack

Copyright 2019, Xiaodong Yu

# Algorithms and Frameworks for Accelerating Security Applications on HPC Platforms

Xiaodong Yu

(ABSTRACT)

Typical cybersecurity solutions emphasize on achieving defense functionalities. However, execution efficiency and scalability are equally important, especially for real-world deployment. Straightforward mappings of cybersecurity applications onto HPC platforms may significantly underutilize the HPC devices' capacities. On the other hand, the sophisticated implementations are quite difficult: they require both in-depth understandings of cybersecurity domain-specific characteristics and HPC architecture and system model.

In our work, we investigate three sub-areas in cybersecurity, including mobile software security, network security, and system security. They have the following performance issues, respectively:

1) The flow- and context-sensitive static analysis for the large and complex Android APKs are incredibly time-consuming. Existing CPU-only frameworks/tools have to set a timeout threshold to cease the program analysis to trade the precision for performance. 2) Network intrusion detection systems (NIDS) use automata processing as its searching core and requires line-speed processing. However, achieving high-speed automata processing is exceptionally difficult in both algorithm and implementation aspects. 3) It is unclear how the cache configurations impact time-driven cache side-channel attacks' performance. This question remains open because it is difficult to conduct comparative measurement to study the impacts.

In this dissertation, we demonstrate how application-specific characteristics can be leveraged to optimize implementations on various types of HPC for faster and more scalable cybersecurity executions. For example, we present a new GPU-assisted framework and a collection of optimization strategies for fast Android static data-flow analysis that achieve up to 128X speedups against the plain GPU implementation. For network intrusion detection systems (IDS), we design and im-

plement an algorithm capable of eliminating the state explosion in out-of-order packet situations, which reduces up to 400X of the memory overhead. We also present tools for improving the usability of Micron's Automata Processor. To study the cache configurations' impact on time-driven cache side-channel attacks' performance, we design an approach to conducting comparative measurement. We propose a quantifiable success rate metric to measure the performance of time-driven cache attacks and utilize the GEM5 platform to emulate the configurable cache.

# Algorithms and Frameworks for Accelerating Security Applications on HPC Platforms

#### Xiaodong Yu

#### (GENERAL AUDIENCE ABSTRACT)

Typical cybersecurity solutions emphasize on achieving defense functionalities. However, execution efficiency and scalability are equally important, especially for the real-world deployment. Straightforward mappings of applications onto High-Performance Computing (HPC) platforms may significantly underutilize the HPC devices' capacities. In this dissertation, we demonstrate how application-specific characteristics can be leveraged to optimize various types of HPC executions for cybersecurity. We investigate several sub-areas, including mobile software security, network security, and system security. For example, we present a new GPU-assisted framework and a collection of optimization strategies for fast Android static data-flow analysis that achieve up to 128X speedups against the unoptimized GPU implementation. For network intrusion detection systems (IDS), we design and implement an algorithm capable of eliminating the state explosion in out-of-order packet situations, which reduces up to 400X of the memory overhead. We also present tools for improving the usability of HPC programming. To study the cache configurations' impact on time-driven cache side-channel attacks' performance, we design an approach to conducting comparative measurement. We propose a quantifiable success rate metric to measure the performance of time-driven cache attacks and utilize the GEM5 platform to emulate the configurable cache.

## Acknowledgments

First and foremost, I would like to express my deepest gratitude to my advisor, Prof. Danfeng (Daphne) Yao. She helps me overcome the huge difficulties during my Ph.D. study, introduces me to the field of cybersecurity, and shares with me her invaluable knowledge and experience. I have learned so much from Prof. Yao, such as the research methodologies, presentation and communication skills, paper reviewing approaches, and scientific writing ability. Without her guidance, support, and encouragement, it would not be possible for me to complete my Ph.D.

I would like to especially thank Prof. Michela Becchi, who was my Master's advisor at the University of Missouri and serves as my Ph.D. thesis committee member. She introduces me into the world of HPC and continuously supports me throughout my Ph.D. study. She not only inspires and guides me to conduct research but also provides me plenty of great suggestions regarding my academic and personal lives, and future career.

I also would like to express my sincere gratitude to the committee members, Prof. Ali R. Butt, Prof. Matthew Hicks, and Prof. Xinming (Simon) Ou, for their insightful comments and valuable suggestions for my dissertation. I am also very grateful to many other researchers, including my AMD internship mentor Daniel Lowell, Prof. Kirk W. Cameron, Prof. Wu-chun Feng, and Dr. Hao Wang, for their guidance on my HPC research.

I have been fortunate to work with and be a friend of my labmates and fellow collaborators: Sharmin Afrose, Md Salman Ahmed, Dr. Long Cheng, Myles Frantz, Yuan Luo, Sazzadur Rahaman, Dr. Ke Tian, Ya Xiao, Xuewen Cui, Dr. Kaixi Hou, Dr. Konstantinos Krommydas, Da Zhang, Dr. Jing Zhang, Dr. Hao Gong, Dr. Fengguo Wei, Jon Bernard, Tyler Chang, Chandler Jearls, Dr. Bo Li, Thomas Lux, and Li Xu. It has been a pleasure to get to know many other friends in our CS department: Dr. Zheng Song, Tong Zhang, Xinwei Fu, Yin Liu, Run Yu, Hang Hu, Gagandeep Panwar, Yufeng Ma, Xuan Zhang, Shuo Niu/Yanshen Yang couple, Yali Bian/Siyu Mi couple, Ziqian Song/Mu Xu couple, and so forth. I also would like to thank my friends from many other areas: Dr. Yumin Dai and Dr. Hao Li/Gehui Liu couple from Dept. of Chemistry, Wei Cui and Dr. Chuanhui Chen/Zuoping Zhang couple from Dept. of Physics, Xu Dong from Dept.

of Biomedical Engineering, Qianzhou Du from Dept. of Business Information Technology, etc. I appreciate all these friends making my life in Blacksburg rich and colorful. You are my treasures. My best wishes to all of you for future endeavors.

Finally, I am immensely grateful to my family. My parents, Sanmao Yu and Junhui Song, provide me unconditional loves and endless supports. Their loves always save me when I was very down during my Ph.D. study. My love, Wei Xu, is my resource of courage and enthusiasm. Her company makes it possible for me to go through the tough period of my life.

## **Contents**

| 1 | Intr | oductio                                             | n                                           | 1  |

|---|------|-----------------------------------------------------|---------------------------------------------|----|

|   | 1.1  | Automata-based Algorithms for Security Applications |                                             | 2  |

|   |      | 1.1.1                                               | Regular Expressions & Finite Automata       | 2  |

|   |      | 1.1.2                                               | Deep Packet Inspection (DPI)                | 3  |

|   |      |                                                     | 1.1.2.1 Automata-based Matching Core        | 4  |

|   |      |                                                     | 1.1.2.2 Out-of-order Packets Issue          | 4  |

|   | 1.2  | Securi                                              | ty Application Accelerations on HPC Devices | 6  |

|   |      | 1.2.1                                               | General-purpose Devices                     | 7  |

|   |      | 1.2.2                                               | Automata Processor                          | 8  |

|   | 1.3  | Andro                                               | id Program Analysis for Security Vetting    | 10 |

|   |      | 1.3.1                                               | Android Program Analysis Tools              | 10 |

|   |      | 1.3.2                                               | High-Performance Android Program Analysis   | 11 |

|   | 1.4  | Cache                                               | Side-Channel Attacks                        | 13 |

|   |      | 1.4.1                                               | Categories of Cache Side-Channel Attacks    | 13 |

|   |      | 1.4.2                                               | Cache Configurations' Impact                | 14 |

|   | 1.5  | Dissertation Contributions                                          | 15 |

|---|------|---------------------------------------------------------------------|----|

|   | 1.6  | Dissertation Organization                                           | 17 |

| 2 | Lite | rature Review                                                       | 18 |

|   | 2.1  | Algorithm Optimizations                                             | 18 |

|   |      | 2.1.1 Finite Automata Optimizations                                 | 18 |

|   |      | 2.1.2 Algorithms for Out-of-Order Packets in DPI                    | 19 |

|   | 2.2  | HPC devices Based Accelerations                                     | 20 |

|   |      | 2.2.1 GPU                                                           | 20 |

|   |      | 2.2.2 Automata Processor                                            | 21 |

|   | 2.3  | Security Vettings for Android                                       | 23 |

|   |      | 2.3.1 Android Static Analysis Tools                                 | 23 |

|   |      | 2.3.2 Andorid Data-Flow Graph Constructions                         | 24 |

|   | 2.4  | Cache Side-Channel Attacks & Countermeasures                        | 25 |

|   |      | 2.4.1 Time-Driven Attacks                                           | 25 |

|   |      | 2.4.2 Access-Driven Attacks                                         | 26 |

|   |      | 2.4.3 Implementations' and Systems' Impacts                         | 26 |

|   |      |                                                                     |    |

| 3 | Scal | able Automata-based Pattern-Matching Algorithm for Out-of-Order DPI | 27 |

|   | 3.1  | Introduction                                                        | 27 |

|   | 3.2  | O³FA Design                                                         | 30 |

|   |      | 3.2.1 O <sup>3</sup> FA Data Structure                              | 32 |

| <i>1</i> 1 | Introdu            | action                                                     | 56 |

|------------|--------------------|------------------------------------------------------------|----|

| Fran       | nework             | for Approximate Pattern Matching on the Automata Processor | 56 |

| 3.6        | Conclu             | sions and Future Work                                      | 54 |

|            |                    | 3.5.3.4 Traversal Overhead                                 | 53 |

|            |                    | 3.5.3.3 Memory Bandwidth Overhead                          | 53 |

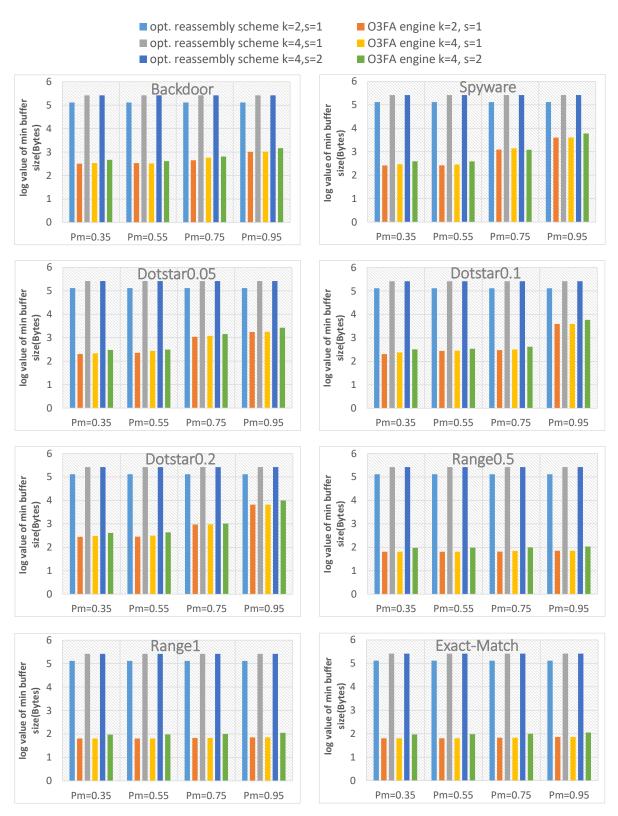

|            |                    | 3.5.3.2 Buffer Size Savings                                | 50 |

|            |                    | 3.5.3.1 O <sup>3</sup> FA Memory Footprint                 | 49 |

|            | 3.5.3              | Experiment Results                                         | 49 |

|            | 3.5.2              | Packet Reordering                                          | 48 |

|            | 3.5.1              | Datasets & Streams                                         | 48 |

| 3.5        | Evalua             | tion                                                       | 47 |

|            | 3.4.3              | Worst-case Analysis                                        | 46 |

|            | 3.4.2              | O³FA Engine Work Flow                                      | 45 |

|            | 3.4.1              | O³FA Engine Architecture                                   | 43 |

| 3.4        | O <sup>3</sup> FA- | based System                                               | 43 |

|            | 3.3.5              | Functionally Equivalent Packets                            | 41 |

|            | 3.3.4              | Quick Retrieval Table                                      | 40 |

|            | 3.3.3              | Prefix- and Suffix-DFA with State Map                      | 38 |

|            | 3.3.2              | Compressed Suffix-NFA                                      | 36 |

|            | 3.3.1              | Index Tags                                                 | 35 |

| 3.3        | Optimi             | zations                                                    | 34 |

| 4.2  | Backg   | round and Motivations                                   | 59 |

|------|---------|---------------------------------------------------------|----|

|      | 4.2.1   | Automata Processors                                     | 59 |

|      | 4.2.2   | Motivations                                             | 60 |

| 4.3  | Paradi  | gms and Building Blocks in APM                          | 62 |

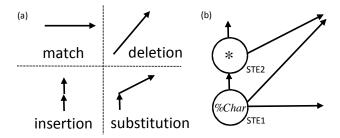

|      | 4.3.1   | Approximate Pattern Matching on AP                      | 62 |

|      | 4.3.2   | Paradigms in Approximate Pattern Matching               | 64 |

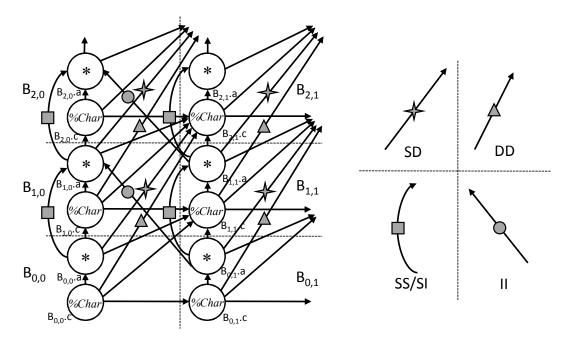

|      | 4.3.3   | Inter-Block Transition Connecting Mechanism             | 66 |

| 4.4  | Frame   | work Design                                             | 69 |

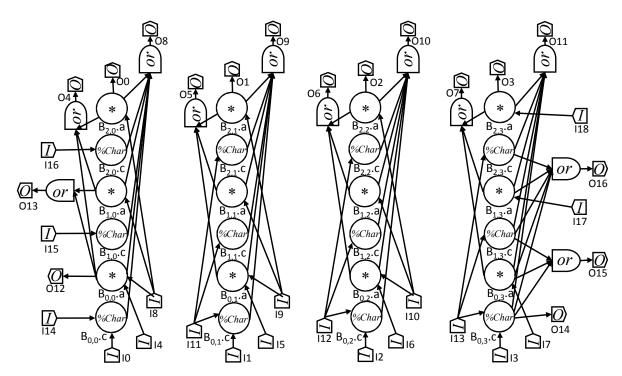

|      | 4.4.1   | From Building Blocks to Automata                        | 69 |

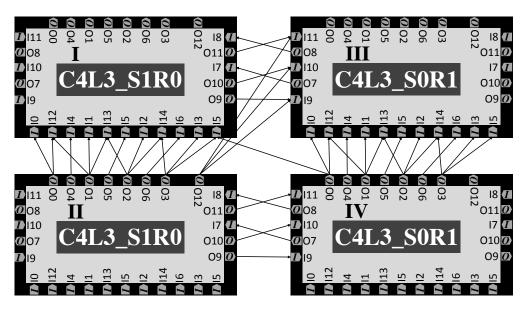

|      | 4.4.2   | Design Cascadable Macros                                | 70 |

|      | 4.4.3   | Cascadable Macro based Automata Construction Algorithm  | 75 |

| 4.5  | Evalua  | ntion                                                   | 77 |

|      | 4.5.1   | Synthetic Patterns                                      | 77 |

|      | 4.5.2   | Real-world Dataset                                      | 80 |

| 4.6  | Conclu  | asions                                                  | 85 |

| GPI  | J-based | Android Program Analysis Framework for Security Vetting | 86 |

| 01 ( |         |                                                         |    |

| 5.1  | Introd  | uction                                                  | 86 |

| 5.2  | Backg   | round Knowledge                                         | 90 |

|      | 5.2.1   | Static Analysis for Android Apps                        | 90 |

|      | 5.2.2   | Worklist-based DFG Building Algorithm                   | 91 |

| 5 3  | Our Di  | ain GPI I Implementation                                | 02 |

|     | 5.3.1    | Basic De   | esign                                                        | . 93  |

|-----|----------|------------|--------------------------------------------------------------|-------|

|     |          | 5.3.1.1    | Using Summary-based Analysis                                 | . 93  |

|     |          | 5.3.1.2    | Two-level Parallelization                                    | . 94  |

|     |          | 5.3.1.3    | Dual-Buffering Data Transfer                                 | . 94  |

|     | 5.3.2    | Performa   | ance Analysis                                                | . 96  |

|     |          | 5.3.2.1    | Comparison with CPU Counterpart                              | . 96  |

|     |          | 5.3.2.2    | Performance Bottlenecks                                      | . 97  |

| 5.4 | The O    | ptimizatio | n Designs                                                    | . 98  |

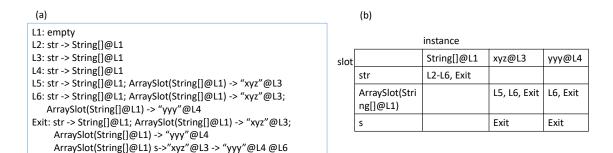

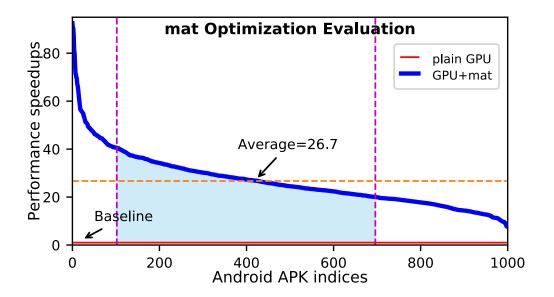

|     | 5.4.1    | Optimiza   | ation 1: Matrix-based Data Structure for Data-Facts          | . 99  |

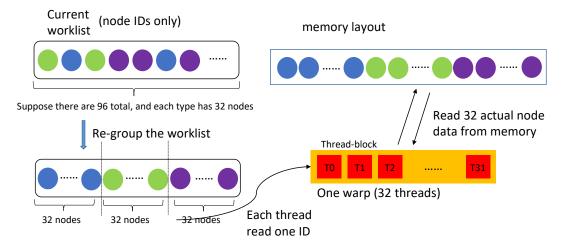

|     | 5.4.2    | Optimiza   | ation 2: Memory Access Pattern Based Node Grouping           | . 100 |

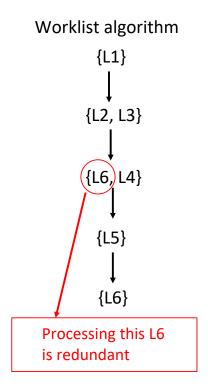

|     | 5.4.3    | Optimiza   | ation 3: Worklist Merging                                    | . 101 |

| 5.5 | Frame    | work Eval  | uation                                                       | . 102 |

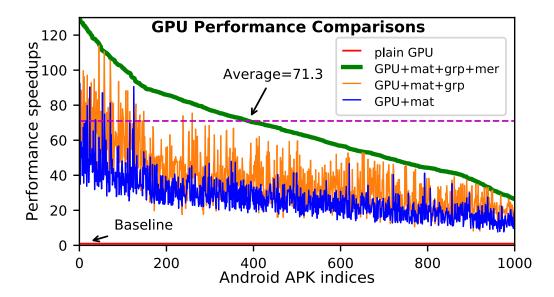

|     | 5.5.1    | Overviev   | w of GPU Implementation's Performance                        | . 103 |

|     | 5.5.2    | Evaluation | on of Matrix Data Structure Optimization                     | . 104 |

|     | 5.5.3    | Evaluation | on of Memory Access Pattern Based Node Grouping Optimization | 107   |

|     | 5.5.4    | Evaluation | on of Worklist Merging Optimization                          | . 108 |

| 5.6 | Conclu   | ision      |                                                              | . 109 |

| Con | nparativ | ve Measur  | rement of Cache Configurations' Impacts on the Performance   | of    |

| Cac | he Timi  | ng Side-C  | Channel Attacks                                              | 111   |

| 6.1 | Introdu  | uction     |                                                              | . 111 |

| 6.2 | Racko    | round      |                                                              | 113   |

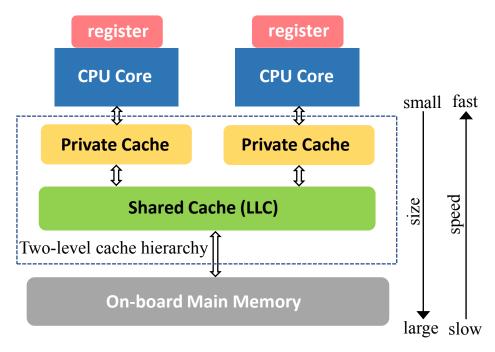

|     | 6.2.1   | CPU Cache Hierarchy                                               | 114 |

|-----|---------|-------------------------------------------------------------------|-----|

|     | 6.2.2   | Bernstein's Cache Timing Attack                                   | 115 |

|     | 6.2.3   | GEM5 Platform                                                     | 116 |

| 6.3 | Measu   | rement Design                                                     | 116 |

|     | 6.3.1   | Cache Parameters for Configuration                                | 117 |

|     |         | 6.3.1.1 Private and Shared Cache Size                             | 118 |

|     |         | 6.3.1.2 Private and Shared Cache Associativity and Cacheline Size | 119 |

|     |         | 6.3.1.3 Replacement Policies                                      | 119 |

|     |         | 6.3.1.4 Cache Clusivity                                           | 120 |

|     | 6.3.2   | Metric Definition: the Success Rate of an Attack                  | 120 |

| 6.4 | Measu   | rement Results                                                    | 121 |

|     | 6.4.1   | Private Caches' Impacts                                           | 122 |

|     | 6.4.2   | Shared Caches' Impacts                                            | 124 |

|     | 6.4.3   | CLS, RPs, and CCs's Impacts                                       | 125 |

| 6.5 | Discus  | sion                                                              | 126 |

| 6.6 | Limita  | tions                                                             | 127 |

| 6.7 | Conclu  | ısion                                                             | 128 |

| Con | clusion | and Future Work                                                   | 129 |

| Con |         |                                                                   |     |

| 7.1 | Summ    | aries                                                             | 129 |

| 7.2 | Future  | Work                                                              | 132 |

|     | 721     | High Performance Network Security                                 | 132 |

| Bibliography |                                   | 135   |

|--------------|-----------------------------------|-------|

| 7.2.3        | High-Performance System Security  | . 133 |

| 7.2.2        | High-Performance Program Security | 132   |

# **List of Figures**

| 1.1 | (a) NFA and (b) DFA accepting regular expressions a.*bc and bcd                                                                                                                                                                             | 3  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

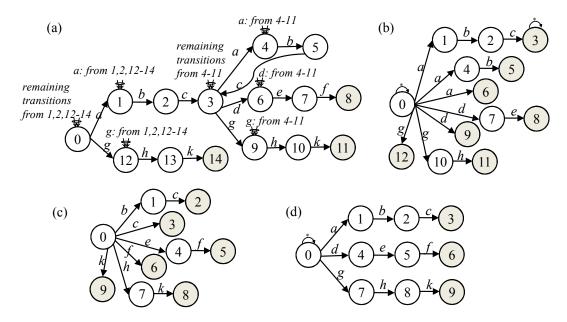

| 3.1 | (a) DFA accepting pattern set $\{abc.*def,ghk\}$ , (b) prefix-FA, (c) anchored suffix-FA and (d) unanchored suffix-FA built upon corresponding prefix set, anchored suffix set and unanchored suffix set. Accepting states are colored gray | 35 |

| 3.2 | (a) asNFA and (b) csNFA built upon anchored suffix set $\{bcdca, cdca, dca, ca, a\}$ . Accepting states are colored gray                                                                                                                    | 37 |

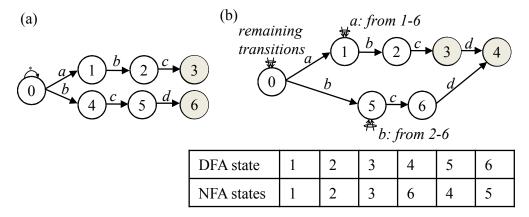

| 3.3 | (a) NFA format and (b) sDFA with states map for unanchored suffix set $\{.*abc, .*bcd\}$ . Accepting states are colored gray                                                                                                                | 39 |

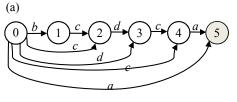

| 3.4 | (a) original NFA format, (b) optimized NFA, (c) pDFA with states map for prefix set $\{.*abc.*,.*ab,.*a,.*bc,.*b\}$ . Accepting states are colored gray                                                                                     | 40 |

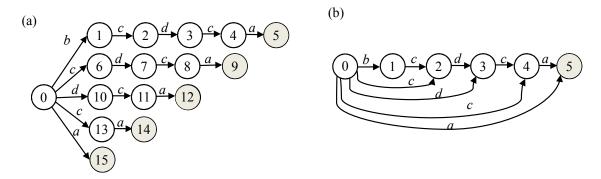

| 3.5 | (a) csNFA and (b) quick retrieval table for anchored suffix set $\{bcdca, cdca, dca, ca, a\}$ . Accepting states are colored gray. Each char. position is a pair of index tag and offset, i.e., $\langle tag, offset \rangle$               | 41 |

| 3.6 | (a) NFA format and (b) pDFA with states map built upon prefix set $\{.*ab.*, .*a, .*bc, .*b\}$ . (c) Construction of functionally equivalent packet to packet $P_2 = eabc$ .                                                                | 42 |

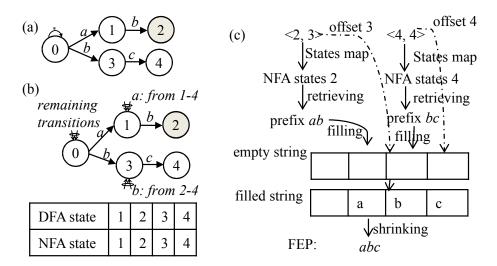

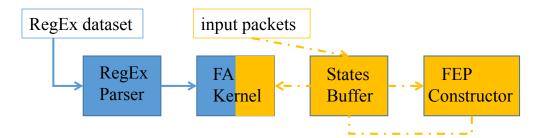

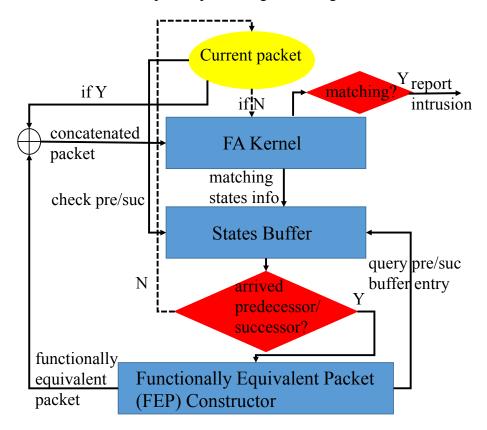

| 3.7 | Overview of the O <sup>3</sup> FA engine. The blue parts are dataset processing components; the yellow parts are input packet processing components                                                                                         | 44 |

| 3.8  | no arrived successor/predecessor packets                                                                                                                                                                                                        | 46 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.9  | Minimum buffer size requirements for optimized reassembly scheme and $O^3FA$ engine on eight datasets. Note that the vertical coordinate is in logarithmic scale. $$                                                                            | 51 |

| 4.1  | ANML codes for a simple APM AP automaton                                                                                                                                                                                                        | 61 |

| 4.2  | AP automaton                                                                                                                                                                                                                                    | 61 |

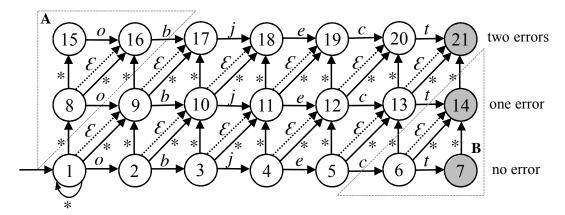

| 4.3  | Levenshtein automaton for pattern "object", allowing up to two errors. A gray colored state indicates a match with various numbers of errors                                                                                                    | 63 |

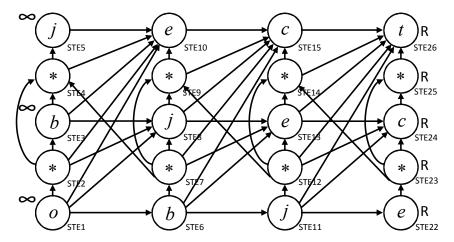

| 4.4  | Optimized STE and transition layout for Levenshtein automata for the pattern "object" allowing up to two errors                                                                                                                                 | 65 |

| 4.5  | (a) Four paradigms in APM applications. (b) A building block for Levenshtein automata having all four paradigms                                                                                                                                 | 65 |

| 4.6  | Inter-block transition connection mechanism for two-consecutive errors: The right part shows five cases we consider. The left part shows a part of Levenshtein automata having six blocks and how the inter-block connections are applied on it | 67 |

| 4.7  | There are four instances that from a three layers four columns cascadable macro.  They are vertically and horizontally cascaded to form a larger AP automaton that have six layers and eight columns                                            | 74 |

| 4.8  | Port design layout for a three layers four columns macro                                                                                                                                                                                        | 74 |

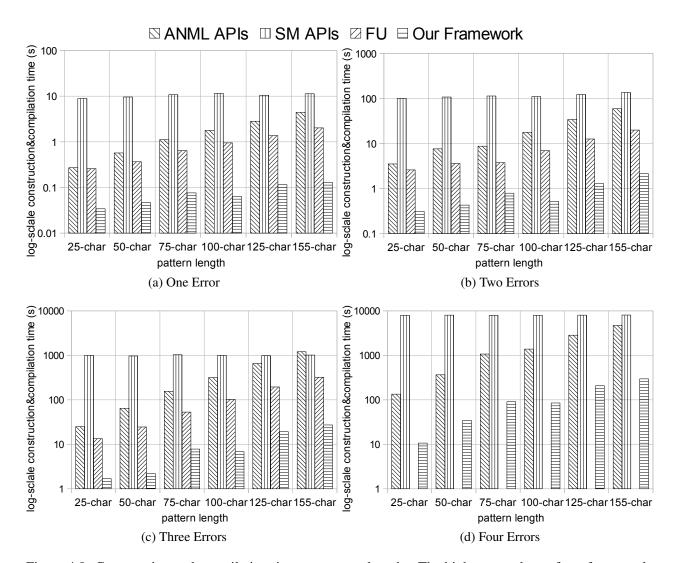

| 4.9  | Construction and compilation time vs. pattern lengths. The highest speedups of our framework over FU, ANML_APIs, SM_APIs are highlighted                                                                                                        | 79 |

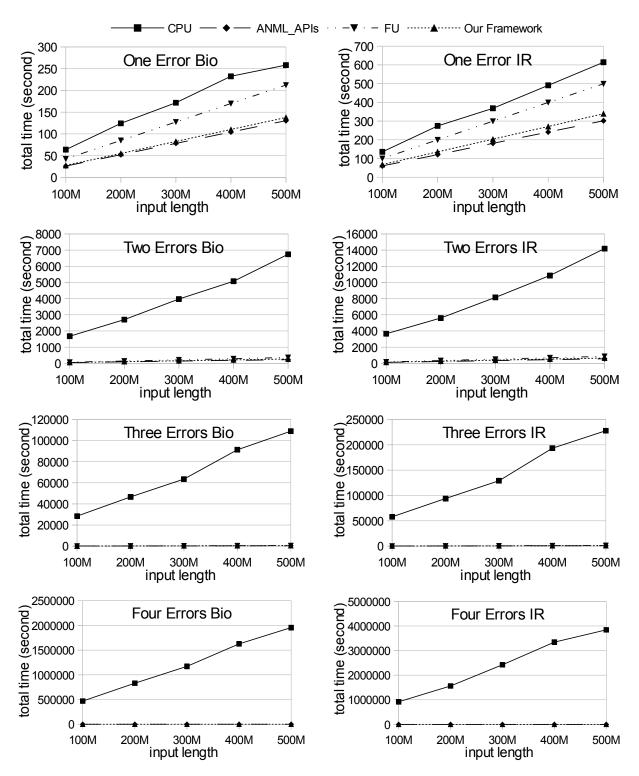

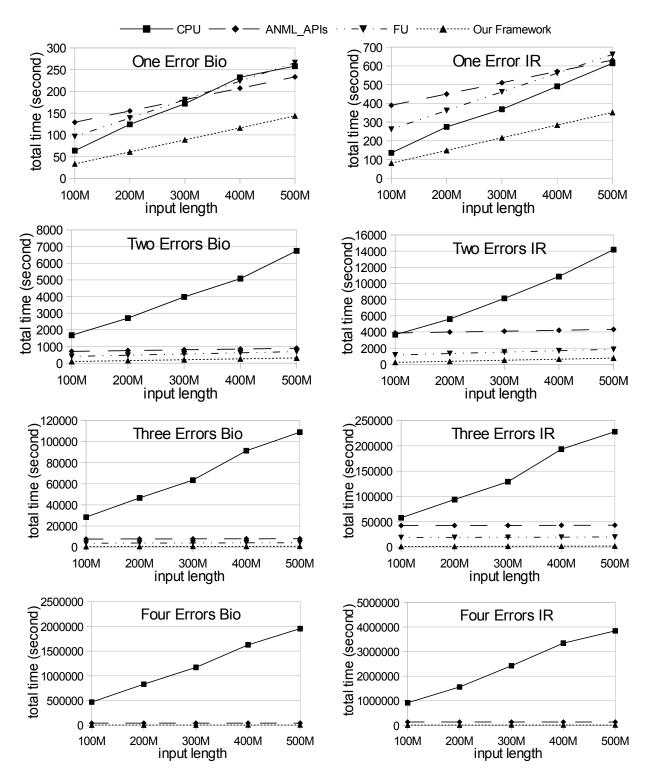

| 4.10 | Computational time comparison between AP (with three different construction approaches) and the CPU counterpart. Notice that FU approach can't support more than three errors                                                                   | 83 |

| 4.11 | proaches) and CPU implementation. Notice that FU approach cant support more than three errors                                                                                                                                                                                                                              |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

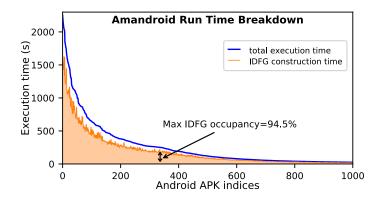

| 5.1  | The execution time of Amandroid. We analyze 1000 Android APKs. The x-axis represents APK indices. The APKs are sorted according to the descending order of Amandroid run time. The y-axis shows the execution time. The blue line indicates overall run time while the orange line indicates the IDFG construction time 87 |

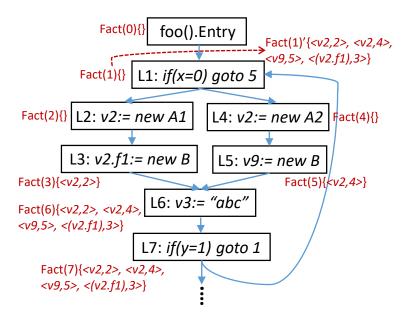

| 5.2  | A sample DFG. Each box is a ICFG node. Blue arrow-lines indicate the ICFG paths. Each node has a fact set colored in red                                                                                                                                                                                                   |

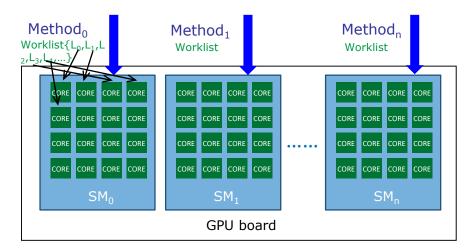

| 5.3  | The two-level parallelization. Different methods are processed on different SM.  Each core processes one ICFG node in the current corresponding worklist 94                                                                                                                                                                |

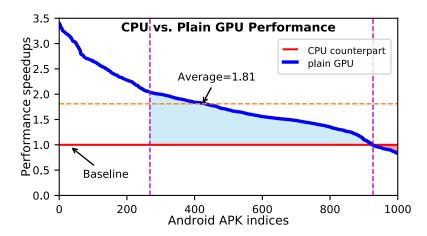

| 5.4  | The performance comparison between the plain GPU implementation and the CPU counterpart. The x-axis represents the APK indices, y-axis indicates the speedups compared to the CPU performances. the APKs are sorted according to the descending order of GPU implementation's speedups                                     |

| 5.5  | (a) is the straightforward data structure of point-to fact set. (b) is the unified compact point-to fact matrix                                                                                                                                                                                                            |

| 5.6  | The scheme of node grouping. Three colors indicate three different types of nodes. 100                                                                                                                                                                                                                                     |

| 5.7  | An example shows a case that the worklist merging can eliminate redundant processing                                                                                                                                                                                                                                       |

| 5.8  | The GPU implementation's performance overview. The x-axis indicates the app APK IDs while the y-axis indicates performance speedups against the plain GPU implementation.                                                                                                                                                  |

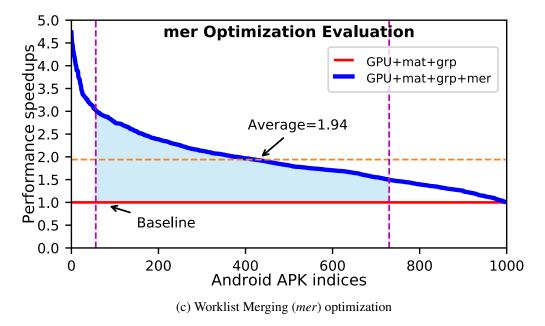

| 5.9  | Performance comparisons between the GPU implementation with and without (a)              |

|------|------------------------------------------------------------------------------------------|

|      | matrix data structure (mat) optimization; (b) memory access pattern based node           |

|      | grouping (grp) optimization; (c) worklist merging (mer) optimization. The x-axis         |

|      | indicates the app APK IDs while the y-axis indicates the speedups against the GPU        |

|      | implementation without (a) <i>mat</i> , (b) <i>grp</i> , and (c) <i>mer</i> respectively |

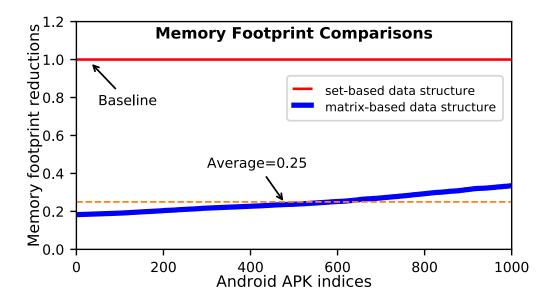

| 5.10 | Memory footprint comparison between the matrix-based and set-based data struc-           |

|      | ture for storing the data-facts. The x-axis indicates the app APK IDs while the          |

|      | y-axis indicates the memory footprint                                                    |

| 6.1  | A generic cache model. It is a two-level hierarchy: each CPU core has its own            |

|      | private cache; all cores could access a shared cache through the private cache 114       |

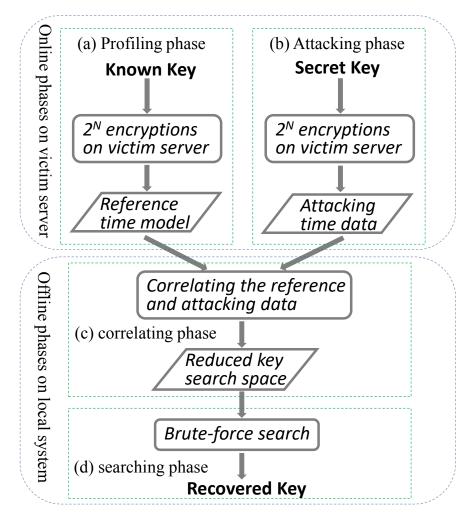

| 6.2  | The workflow of Bernstein's time-driven attack. It consists of two online phases:        |

|      | (a) profiling phase and (b) attacking phase, and two offline phases: (c) correlating     |

|      | phase and (d) searching phase                                                            |

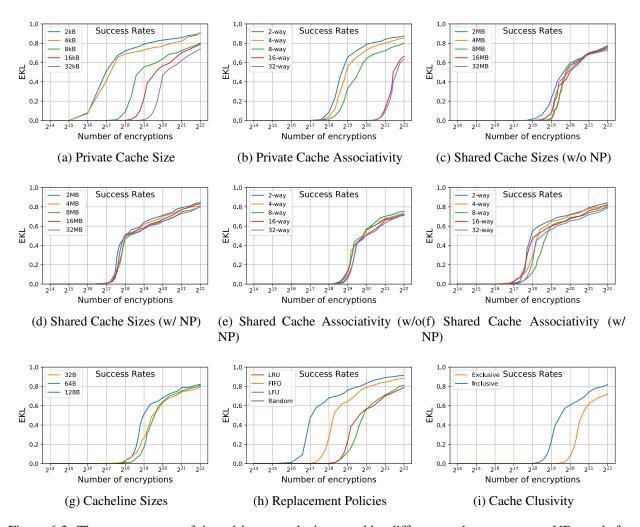

| 6.3  | The success rates of time-driven attacks impacted by different cache parameters.         |

|      | NP stands for the neighbor processes running on the neighbor CPU core. The x-            |

|      | axis represents the numbers of encryptions conducted during the attacking phase          |

|      | (Fig. 6.2(b)). The y-axis indicates the equivalent key lengths (Section 6.3.2) 123       |

## **List of Tables**

| 3.1 | Memory footprint of FA kernels (MB)                                                         | 50 |

|-----|---------------------------------------------------------------------------------------------|----|

| 3.2 | Ratio between the number of csNFA states traversed and the number of input char-            |    |

|     | acters processed (%)                                                                        | 53 |

| 3.3 | O <sup>3</sup> FA traversal overhead compared to conventional stream reassembly methods (%) | 54 |

| 4.1 | Paradigm sets for common distances                                                          | 56 |

| 4.2 | Inter-block transitions connecting rules for two-consecutive errors                         | 59 |

| 4.3 | Port design rules according to paradigm                                                     | 72 |

| 4.4 | Dataset Characteristics                                                                     | 30 |

| 4.5 | Compilation Profile                                                                         | 31 |

| 5.1 | Dataset Characteristics                                                                     | )3 |

| 5.2 | Worklist Profiling                                                                          | )8 |

| 6.1 | Measurement Environment                                                                     | 22 |

## Chapter 1

## Introduction

Most traditional cybersecurity solutions emphasize on achieving defense functionalities. The cybersecurity community largely overlooks the importance of execution efficiency and scalability, especially for real-world deployment. On the other hand, High-Performance Computing (HPC) devices have been widely used to accelerate a variety of scientific applications. However, straightforwardly mapping the cybersecurity applications onto HPC platforms usually may significantly underutilize the HPC devices' capacities. Unfortunately, security applications have not drawn enough attention in HPC community, and sophisticatedly implementing them are quite tricky: they require both in-depth understandings of cybersecurity domain-specific characteristics and HPC architecture and system model.

In this dissertation, we bridge the gap between the cybersecurity and HPC communities from both algorithm and implementation aspects. We investigate three sub-areas in cybersecurity, including mobile software security, network security, and system security. We demonstrate how application-specific characteristics can be leveraged to optimize various types of HPC executions for cybersecurity. For example, For network intrusion detection systems (IDS), we design and implement an algorithm capable of eliminating the state explosion in out-of-order packet situations, which reduces up to 400X of the memory overhead. We also present tools for improving the usability of HPC programming. We present a new GPU-assisted framework and a collection of optimization

strategies for fast Android static data-flow analysis. To study the cache configurations' impact on time-driven cache side-channel attacks' performance, we design an approach to conducting comparative measurement.

## 1.1 Automata-based Algorithms for Security Applications

In this section, we will introduce the regular expressions and their finite automata based representation first, and then explain how they can be used as the computational core of deep packet inspection.

#### 1.1.1 Regular Expressions & Finite Automata

A regular expression, usually abbreviated as regex, is a string of characters that can be used to create a search pattern. Regex is a powerful tool to parse and compactly store a large amount of data; it is also essential for efficiently searching given patterns against the input text. Regex's syntax complies with the formal language theory. There are two de facto syntax set standards: The POSIX and the Perl. Each regular expression must consist of literal characters and meta characters. The meta characters have special meanings and are the keys of regex's strong expressive power. Although meta characters are syntax standard specific, most common meta characters are actually universal. For example, the well-known metacharacter dot-star ".\*", representing a random text with arbitrary length, is shared by all syntax standards.

To allow multi-regex search, current approaches implement the regex-set through finite automata (FA), either in their deterministic or in their non-deterministic form (DFA and NFA, respectively). In automata-based approaches, the matching operation is equivalent to a FA traversal guided by the content of the input stream. Worst-case guarantees on the input processing time can be met by bounding the amount of per character processing.

Being the basic data structure in the regular expression matching engine, the finite automaton must

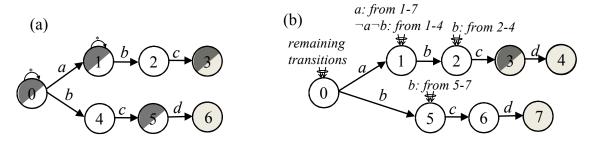

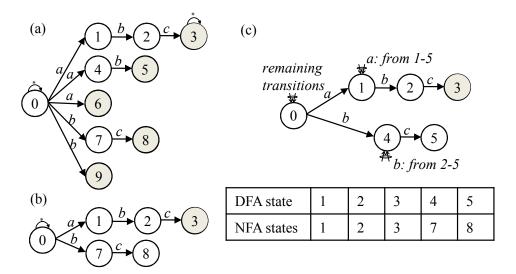

Figure 1.1: (a) NFA and (b) DFA accepting regular expressions a.\*bc and bcd.

be deployable on a reasonably provisioned hardware platform. As the size of pattern-sets and the expressiveness of individual patterns increase, limiting the size of the automaton becomes challenging. The exploration space is characterized by a trade-off between the size of the automaton and the worst-case bound on the amount of per-character processing. NFA and DFAs are at the two extremes in this exploration space. NFAs have a limited size but can require expensive per-character processing, whereas DFAs offer limited per-character processing at the cost of a possibly large automaton. As an example, in Figure 1.1 we show the NFA and DFA accepting regular expressions *a.\*bc* and *bcd* (notice that the dot-star metacharacter ".\*" represents any segment with any length). In the figure, Accepting states are colored gray. The states active after processing input stream *acbc* are highlighted using diagonal filling. In the NFA, states 0 and 1 have a self-loop on any characters of the alphabet. In the DFA, state 1 has incoming transitions on character *b* from states 1 to 7, and incoming transitions from states 1 to 4 on any characters other than *a* and *b* (incoming transitions to states 0, 2 and 5 can be read in the same way). As can be seen, the NFA consists of fewer states (7 against 8), while the DFA leads to less per-character processing (1 versus 4 concurrently active states).

### **1.1.2** Deep Packet Inspection (DPI)

Deep packet inspection (DPI) is a one of the fundamental networking operations. It inspects and manages the network traffics. A traditional form of DPI comprises searching the packet payload against a set of patterns. It then filters the packets by blocking, re-routing, or logging them according to the searching results. Compared to the conventional packet filtering examining only

packet headers, DPI is an advanced method that can detect the malicious or abnormal contents in the payloads.

#### 1.1.2.1 Automata-based Matching Core

DPI is most notably known as the core of network intrusion detection systems (NIDS). NIDS is an essential part of network security device. A NIDS receives and processes packets, and then reports the possible intrusions. In the signature-based NIDS, every pattern represents a signature of malicious traffic; the payload of incoming packets is inspected against all available signatures, then a match triggers pre-defined actions on the interested packets. A regular expression can cover a wide variety of pattern signatures [1, 2, 3]. Because of their expressive power, regular expressions have been increasingly adopted to express pattern sets in both industry and academia. Accordingly, many well-known open-source NIDS – such as Snort<sup>1</sup> and Bro<sup>2</sup> – employ automata-based matching engine as their core; moreover, most major networking companies offer their own NIDS solutions (e.g., security appliances from Cisco<sup>3</sup> and Juniper Networks<sup>4</sup>) and also use automata-based matching cores.

In addition to NIDS, emerging applications like content-based networking [4, 5] require inspecting packets at line rate. Their tasks involve regular expression matching hence also demand the automata-based matching cores.

#### 1.1.2.2 Out-of-order Packets Issue

In real-world scenarios, a network data stream can span multiple packets. Those packets can arrive at network security devices out of order due to multiple routes, packet retransmission, or NIDS evasion. This is referred to as packet reordering. Previous work analyzing Internet traffic has reported that about 2%-5% of packets are affected by reordering [6, 7, 8]. However, these studies

<sup>&</sup>lt;sup>1</sup>http://www.snort.org

<sup>&</sup>lt;sup>2</sup>http://www.bro-ids.org

<sup>&</sup>lt;sup>3</sup>http://www.cisco.com/en/US/products/ps6120/index.html

<sup>&</sup>lt;sup>4</sup>http://www.juniper.net/us/en/products-services/security/idp-series

have focused on benign traffic; while attackers may intentionally mis-order legitimate traffic to trigger denial-of-service (DoS) attacks [8]. NIDS face challenges [9] when processing data streams that span across out-of-order packets, especially when performing regular-expression matching against traffic containing malicious content located across packets boundaries. In such cases, the malicious patterns are split and carried by multiple packets; and NIDS cannot detect them by processing those packets individually.

Several solutions have been proposed to address the problem of processing out-of-order packets in NIDS. One approach that is widely adopted in current network devices is packet buffering and stream reassembling [8, 10, 11, 12]. In this case, incoming packets are buffered and packet streams are reassembled based on the information in the header fields. Regular expression matching is then performed on the reassembled data stream. This approach is intuitive and easy to implement, but can be very resource intensive and vulnerable to DoS attacks whereby attackers exhaust the packet buffer capacity by sending long sequences of out-of-order packets. Recently, researchers have proposed several new solutions [13, 14, 15] aimed to relieve packet-buffer pressure or even avoid packet buffering and reassembling. This is done by tracking all possible traversal paths or leveraging data structures such as suffix trees. While they alleviate the burden of handing out-of-order packets to some extent, these methods are either applicable only to simple patterns (exact-match strings or fixed-length patterns), or suffer from bad worst-case properties (and are therefore still vulnerable to DoS attacks).

In this thesis, we aim to provide a solution that (1) can process out-of-order packets without requiring packet buffering and stream reassembling, (2) relies only on finite automata, and (3) can handle regular expressions with complex sub-patterns [16]. One of the main challenges in this design comes from handling regular expressions that include unbounded repetitions of wildcards and large character sets. This is because these sub-patterns can represent unbounded sets of exactmatch sub-strings which cannot be exhaustively enumerated. Our solution leverages the following observation: all exact-match strings that match a repetition sub-pattern are functionally equivalent from the point of view of the regular expression matching engine and interchanging them will not affect the final matching result. Our proposed solution consists of regular DFAs coupled with a

set of supporting FAs either in NFA or DFA form. The supporting FAs are used to detect and record – using only a few states (typically no more than five) – segments of packets that can potentially be part of a match across packet boundaries. While processing packets out-of-order, those segments can be dynamically retrieved from the recorded states, and can be then used to resolve matches across packet boundaries. To be efficient, any automata-based solution requires minimizing the number of automata, their size, and the number of states that can be active in parallel. Our proposal includes optimizations aimed to achieve these goals.

## 1.2 Security Application Accelerations on HPC Devices

Many security applications require the efficient implementations on the hardware in order to satisfy the scalability and timeliness requests in the real-life scenarios. Given the broad utilization of regex matching, there is a high demand of high-speed automata processing.

From an implementation perspective, automata-based regex matching engines can be classified into two categories: memory-based [17, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27] and logic-based [28, 29, 30, 31]. For the former, the FA is stored in memory; for the latter, it is stored in (combinatorial and sequential) logic. Memory-based implementations can be (and have been) deployed on various parallel platforms: general purpose multi-core processors, network processors, ASICs, FPGAs, and GPUs; logic-based implementations typically target FPGAs. Of course, for the logic-based approaches, updates in the pattern-set require the underlying platform to be reprogrammed. In a memory-based implementation, design goals are the minimization of the memory size needed to store the automaton and of the memory bandwidth needed to operate it. Similarly, in a logic-based implementation the design should aim at minimizing the logic utilization while allowing fast operation (that is, a high clock frequency).

#### 1.2.1 General-purpose Devices

Modern general-purpose HPCs, including CPUs [32, 33, 34, 35, 36, 37], GPUs [38, 39, 40, 41, 42, 43] and Intel's Xeon Phi [44, 45, 46, 47, 48], have been widely used to accelerate a variety of scientific applications. In recent years, GPUs gain the popularity due to their massive parallelisms [49, 50, 51, 52, 53, 54, 44, 55, ?]. Most proposals have target NVIDIA GPUs, whose programmability has greatly improved since the advent of CUDA [56]. The main architectural traits of these devices can be summarized as follows. NVIDIA GPUs comprise a set of Streaming Multiprocessors (SMs), each of them containing a set of simple in-order cores. These in-order cores execute the instructions in a SIMD manner. GPUs have a heterogeneous memory organization consisting of high latency global memory, low latency read-only constant memory, lowlatency read-write shared memory, and texture memory. GPUs adopting the Fermi architecture, such as those used in this work, are also equipped with a two-level cache hierarchy. Judicious use of the memory hierarchy and of the available memory bandwidth is essential to achieve good performance. With CUDA, the computation is organized in a hierarchical fashion, wherein threads are grouped into thread blocks. Each thread-block is mapped onto a different SM, while different threads in that block are mapped to simple cores and executed in SIMD units, called warps. Threads within the same block can communicate using shared memory, whereas threads from different thread blocks are fully independent. Therefore, CUDA exposes to the programmer two degrees of parallelism: fine-grained parallelism within a thread block and coarse-grained parallelism across multiple thread blocks. Branches are allowed on GPU through the use of hardware masking. In the presence of branch divergence within a warp, both paths of the control flow operation are in principle executed by all CUDA cores. Therefore, the presence of branch divergence within a warps leads to core under-utilization and must be minimized to achieve good performance.

#### 1.2.2 Automata Processor

Recently, Automata Processor (AP) [57] is introduced by Micron for the non-deterministic FA (NFA) simulations. Micron AP can perform parallel automata processing within memory arrays on SDRAM dies by leveraging memory cells to store trigger symbols and simulate NFA state transitions. The AP includes three kinds of programmable elements: State Transition Elements (STE), Counter Elements (CE) and Boolean Elements (BE), which implement states/transitions, counters and logical operators between states, respectively. Each STE includes a 256-bit mask (one bit per ASCII symbol), and symbols triggering state transitions are associated to states (and encoded into STEs) rather than to transitions. Transitions between states are then implemented through a routing matrix consisting of programmable switches, buffers, routing lines, and crosspoint connections. Micron's current generation of AP board (AP-D480) includes 16 or 32 chips organized into two to four ranks (8 chips per rank), and its design can scale up to 48 chips. Each AP chip consists of two half-cores. There are no routes either between half-cores or inter-chips, which implies that NFA transitions across half-cores and chips are not possible. Programmable elements are organized in blocks: each block consists of 16 rows, where a row includes eight groups of two STEs and one special purpose element (CE or BE). Each chip contains a total of 49,152 STEs, 768 CE and 2,304 BE, organized in 192 blocks and equally residing in both half-cores. Current boards allow up to 6,144 elements per chip to be set as report elements.

AP automata can be described in Automata Network Markup Language (ANML) – an XML-based language. The ANML is low-level that requires programmers to manipulate STEs and interconnections between them. AP SDK provides some high-level APIs e.g., regular expression [58] and string matching [59] to ease the programming for some applications; however, the lack of flexibility and customization ability of them would force users to resort to ANML for their own applications. Programming on AP is still a cumbersome task, requiring considerable developer expertise on both automata theory and AP architecture.

A more severe problem is the scalability. For reconfigurable devices like AP, a series of costly processes are needed to generate load-ready binary images. These processes include synthesis,

map, place-&-route, post-route physical optimizations, etc., leading to non-negligible configuration time. For a large-scale problem, the situation becomes worse because multi-round reconfiguration might be involved. Most previous research on AP [60, 61, 62, 63, 64, 65, 66, 67] excludes the configuration cost and only focuses on the computation. Although these studies reported hundreds or even thousands of fold speedups against the CPU counterparts, the end-to-end time comparison, including configuration and computation, is not well understood.

We believe a fair comparison has to involve the configuration time, especially when the problem size is extremely large to exceed the capacity of a single AP board. For example, the claimed speedups of AP-based DNA string search [68] and motif search [61] can reach up to 3978x and 201x speedup over their CPU counterparts, respectively. In contrast, if their pattern sets are scaling out and the reconfiguration overhead is included, the speedups will plummet to only 3.8x and 24.7x [69]. In these cases, the configuration time could be very high for three reasons: (1) The large-scale problem size needs multiple rounds of binary image load and flush. (2) In each round, once a new binary image is generated, it will use a full compilation process, which time is as high as several hours. (3) During these processes, the AP device is forced to stall and wait for new images in an idle status.

In this thesis, we highlight the importance of counting the reconfiguration time towards the overall AP performance, which would provide a better angle for researchers and developers to identify essential hardware architecture features. To this end, we propose a framework allowing users to fully and easily explore AP device capacity and conduct fair comparison to counterpart hardware [70, 71]. It includes a hierarchical approach to automatically generate AP automata and cascadeable macros to ultimately minimize the reconfiguration cost. Though this framework is general, in this thesis we focus on Approximate Pattern Matching (APM) for a better demonstration. Specifically, it takes the types of paradigms, pattern length, and allowed errors as input, and quickly and automatically generates corresponding optimized ANML APM automata for users to test the AP performance. During the generation, enabling our cascadeable macros can maximize the reuse of pre-compiled information and significantly reduce the time on reconfiguration, hence allows users to conduct performance comparison that is fair to both sides. We evaluate this frame-

work using both synthesis and real-world datasets, and conduct end-to-end performance comparison between AP and CPU. We show, even including the multi-round reconfiguration costs, AP with our framework can achieve up to 461x speedup against CPU counterpart. We also show using our cascadeable macros can save 39.6x and 17.5x configuration time compared to using non-macro and conventional macros respectively.

## 1.3 Android Program Analysis for Security Vetting

In this section, we first introduce how existing tools use the static program analysis to realize the Android security vetting, and then explain why it is difficult to achieve fast and scalable Android static analysis on HPC platforms.

#### 1.3.1 Android Program Analysis Tools

Android operating system so far holds 86% smartphone OS market share [72]. End users frequently install and utilize the Android apps for their daily life including many security critical activities like online bank login, email communication and so on. It has been widely reported the security problems, for example, the data leaks, the intent injections, and the API misconfigurations, exist in the Android devices due to malicious and vulnerable apps [73, 74, 75, 76, 77, 78, 79, 80, 81]. An efficient vetting system for the new and updated Android apps is desired to keep the app store clean and safe. On the other hand, the Google play store currently has more than 3.5 million<sup>5</sup> Android apps available, and around 7K<sup>6</sup> new apps are released through play store each day. Moreover, most popular existing apps provide updates weekly or even daily. These huge scales and high frequencies make the prior entering market app vetting extremely challenging. Bosu et al. [82] experimentally show that analyzing 110K real-world APPs costs more than 6340 hours, even using the optimized analysis approaches. Apparently, a fast and scalable implementation is the key to

<sup>&</sup>lt;sup>5</sup>https://www.statista.com/statistics/266210/number-of-available-applications-in-the-google-play-store/

<sup>&</sup>lt;sup>6</sup>https://www.statista.com/statistics/276703/android-app-releases-worldwide/

make app vetting practical.

In recent years, plenty of Android program analysis tools including FlowDroid [83], IccTA [84], DialDroid [82], and AmanDroid [85] have been proposed. Most of them conduct static analysis on the Dalvik bytecodes to discover the security problems of Android apps. Static analysis can provide a comprehensive picture of the APP's possible behaviors, whereas the dynamic analysis can only screen the behaviors during the dry run. However, static analysis suffers from the inherent undecidability of code behaviors; any static analysis method must make a trade-off between the run-time and the analysis precision. Typically, a 10MB app could take around 30 minutes to be statically analyzed and is defined as a large-size app. We use one of the state-of-art Android Static Analysis tools – Amandroid [85] to analyze 1000 random chosen Android APKs. The blue line in Fig. 5.1 shows the execution time: Amandroid takes up to 38min to analyze a single APK. Accordingly, many existing analysis tools set the cut-off threshold at 30min for a single app. However, Google raised the app size limit in the play store to 100MB in 2015, and a majority of modern commodity apps has dozens of MegaBytes. It is manifest that current Android static analysis implementations must be accelerated to accommodate the app size growth.

### 1.3.2 High-Performance Android Program Analysis

Over the past decade, parallel devices become very popular computing platforms and successfully accelerate a verity of domain applications. More recently, due to the massive parallelism and computational power, Graphic Processing Unit (GPU) stands out and is trendy hardware in general-purpose parallel computing. It has been broadly adopted in Bioinformatics [49], Biomedical [52], Natural Language Processing [86] and so on. However, this trend doesn't draw enough attention in security community. Only a handful of previous work [87, 88, 89, 90, 91, 92, 93, 94, 95, 96] implement the program analysis on modern parallel hardware; only three work [87, 90, 95] out of them leverage the GPU, and all discuss the acceleration of the common pointer analysis algorithm; none of them consider the Android program analysis. On the other hand, straightforward mapping of an application onto GPU usually is sub-optimal or even under-performs its serial coun-

terpart. The additional application-specific tuning is required to achieve optimal performance. For example, the industrial standard generic GPU sparse matrix-vector multiplication (SpMV) library cuSPARSE [97] can achieve up to 15X speedups against the CPU version. The CT image reconstruction uses SpMV as its computational core. However, mapping the reconstruction to GPU by directly calling cuSPARSE achieves only 3X speedups. On the contrary, a fine-grained design leveraging this application's domain characteristics can increase the performance to 21-fold against CPU [52].

In this thesis, we propose a GPU-assisted Android static analysis framework. To our best knowledge, this is the first work attempting to accelerate the Android program analysis on HPC platform. We find that implementing the IDFG construction on GPU using the generic approaches (i.e., leveraging no application-specific characteristics) can largely underutilize the GPU computation capacity. We identify four performance bottlenecks existing in the plain GPU implementations: frequent dynamic memory allocations, a large number of branch divergences, workload imbalance, and irregular memory access patterns. Accordingly, we exploit the application-specific characteristics to propose three optimizations that refactor the algorithm to fit the GPU architecture and execution model. (i) Matrix-based data structure for data-facts. It uses the fixed-size matrix-based data structure to substitute the dynamic-size set-based data structure to store the data-facts. This optimization can efficiently avoid dynamic memory allocations. It also can reduce the memory consumption since it removes the copies of repetitive data-facts. (ii) Memory access based node grouping. It groups the ICFG nodes based on their memory access patterns. Compared to the original statement type based node grouping, this optimization can significantly reduce the branch divergences since it leads to only three groups (while the original grouping yields 17 groups). It can also maximize memory bandwidth usage. (iii) Worklist merging. This optimization postpones the processing of worklist's tail subset to significantly mitigate the workload imbalance issue. It also can avoid the redundant processings by merging the repetitive nodes in the worklist. We evaluate the three proposed optimizations using 1000 Android APKs. We find the first and third optimizations can significantly improve the performance compared to the plain GPU implementation, while the second optimization can slightly improve the performance. The GPU implementation with all

three optimizations can achieve optimal performance; it can achieve up to 128X speedups compared to the optimal performance.

#### 1.4 Cache Side-Channel Attacks

In this section, we will first introduce different types of cache side-channel attacks, and then explain why it remains unclear about the impact of cache configurations on the performance of time-driven cache side-channel attacks.

#### 1.4.1 Categories of Cache Side-Channel Attacks

Timing-based cache side-channel attacks have been comprehensively studied since its debut in 1996 [98]. The time information of cache access leaks secret contents, specifically through the time difference of cache hits and misses. These attacks can be broadly categorized into three types based on the leakage observation method [99, 100]: (1) access-driven attacks, (2) trace-driven attacks, (3) and time-driven attacks. The access-driven attacks manipulate specific cache-lines and observe the access behaviors of cryptographic operations on these cache-lines. The trace-driven attacks observe the cache hit-miss traces during the encryption/decryption. Different from the former two, the time-driven attacks simply observe the total execution time of the cryptographic operations. All types derive the secret contents by analyzing the observation.

Time-driven attacks are the primary type in the early age of side-channel attacks. In the last decade, access-driven attacks, for example, the notorious meltdown attack [101], gain popularity. They have a higher resolution and lower noises, hence require fewer measurements than time-driven attacks. Fine-grained variants of access-driven attack have been proposed, including PRIME+PROBE [102], FLUSH+RELOAD [103], and FLUSH+FLUSH [104]. However, all access-driven attacks require that the attacker's process have access to specific cache addresses that shared by the victim's process.

Recently, some proposals leverage new hardware technologies to defend the access-driven attacks. For example, the CATalyst [105] exploits Intel's Cache Allocation Technology (CAT) (CAT isolates shared cache space for victim's process) to physically revoke the accessibility of attacker's process. Given the attackers' access privilege is not an assurance, studying time-driven attacks are still worthwhile since they demand no adversary's intervention during the observations.

#### 1.4.2 Cache Configurations' Impact

Researchers have been speculating that cache configurations can impact the performances of time-driven side-channel attacks [106, 107, 108]. For example, intuitively, a bigger cache size would make the attacks on AES more difficult, as it can hold a larger portion of the precomputed S-box lookup table in the cache. However, we are not aware of any previous work that provides experimental data to demonstrate how cache configuration parameters influence time-driven attacks. It is extremely challenging to conduct performance comparisons under the same system with different cache configurations, as none of the existing CPU products provide configurable caches. This challenge prevents the experimental study about the impact of cache parameters on time-driven attacks.

In this dissertation, we overcome the aforementioned difficulty and conduct a comprehensive study on how cache configurations impact the success rates of time-driven attacks [109]. We leverage a modular platform – GEM5 [110] to measure the performances of time-driven attacks under various cache configurations. GEM5 is one of the most popular cycle-accurate full-system emulators in the computer-system architecture community [111, 112]. We leverage GEM5 to emulate the X86\_64 system with a configurable cache.

In our work, we measure the performance of Bernstein's cache timing attack on AES [106]. Bernstein's attack is one of the most classic time-driven attacks and still feasible on model processors [113, 114]. To make its performance comparable, we propose a new metric to quantify the its success rate. In the measurement, we run Bernstein's attacks on GEM5 instances with different

cache configurations and provide systematic experimental data to describe the correlation of cache parameters and the attack's performance.

#### 1.5 Dissertation Contributions

In this thesis, our scientific contributions can be summarized as the follows:

- We present O<sup>3</sup>FA, a new finite automata-based DPI engine to perform regular-expression matching on out-of-order packets in real-time, i.e., without requiring flow reassembly.

- We propose several optimizations to improve the average and worst-case behavior of the O<sup>3</sup>FA engine, and we analyze how the packet ordering affects the buffer size.

- We evaluate our O<sup>3</sup>FA engine on various real-world and synthetic datasets. Our results show

that our design is very efficient in practice. The O<sup>3</sup>FA engine requires 20x-4000x less buffer

space than conventional buffering & reassembling-based solutions, with only 0.0007%-5%

traversal overhead.

- We highlight the importance of counting the reconfiguration time towards the overall AP performance, especially the for large-scale and/or frequently updated datasets.

- We provide a framework for users to easily and fairly conduct performance comparison between AP and its counterparts. It uses a hierarchical approach to automatically generate AP automata and cascadeable macros to ultimately minimize reconfiguration costs.

- We evaluate our framework with AP using both synthesis and real-world datasets, and conduct end-to-end performance comparison (configuration+computation) between AP and CPU. Even including the configuration cost, AP can still achieves hundreds of times speedup against its counterparts.

- We propose a GPU-assisted framework for static program analysis based Android security vetting. It constructs Data-Flow Graphs using GPU and can support multiple vetting tasks by adding lightweight plugins onto the DFGs.

- We identify four performance bottlenecks in the plain GPU implementation: frequent dynamic memory allocations, large number of branch divergences, workload imbalance, and irregular memory access patterns. To breakthrough the bottlenecks, we leverage the application-specific characteristics to propose three fine-grained optimizations, including matrix-based data structure for data-facts, memory access based node grouping, and worklist merging.

- We evaluate the efficacy of proposed optimizations using 1000 Android APKs. The first and third optimizations can significantly improve the performance compared to the plain GPU implementation while the second one can slightly improve the performance. The optimal GPU implementation can achieve up to 128X speedups against the plain GPU implementation.

- We use the GEM5 platform to investigate the cache configurations' impacts on time-driven cache side-channel attacks. We configure the GEM5's cache through seven parameters: Private Cache Sizes, Private Cache Associativity, Shared Cache Sizes, Shared Cache Associativity, Cacheline Sizes, Replacement Policy, and Clusivity.

- We extend the traditional success-fail binary metric to make the cache timing side-channel attacks' performances comparable. We define the *equivalent key length* (*EKL*) to describe the success rates of the attacks under a certain cache configuration.

- We systematically measure and analyze each cache parameter's influence on the attacks' success rate. Based on the measurement results, we find the private cache is the key to the success rates; the 8KB, 16-way private cache can achieve the optimal balance between the security and the cost. Although the shared cache's impacts are trivial, running neighbor processes can significantly increase the success rates of the attacks. The replacement policies

and cache clusivity also have impacts on the attacks' performances: Random replacement leads to the highest success rates while the LFU/LSU leads to the lowest; the exclusive policy makes the attacks harder to succeed compared to the inclusive policy. We then use these findings to enhance both the cache side-channel attacks and defenses and strengthen future systems.

## 1.6 Dissertation Organization

The rest of this dissertation is organized as follows. In Chapter 2, we present state-of-the-art existing works that relate to our targeted problems and some background knowledge required to understand the proposals in this dissertation. In Chapter 3 and 4, we present our work for high-performance network security. In Chapter 3, we introduce the O<sup>3</sup>FA engine, a new regular expression-based DPI architecture that can handle out-of-order packets on the fly without requiring packet buffering and stream reassembly. In Chapter 4, we address the programmability and scalability issues in the emerging Micron's Automata Processors, and accordingly propose the ROBOTOMATA framework that contains a hierarchical code auto-generating approach and the cascadeable macros. In Chapter 5, we present our contribution to high-performance mobile software security. We propose an Android security vetting framework that uses the highly optimized GPU-based DFG construction as the core. In Chapter 6, we present the work for high-performance system security. We design a comparative measurement to systematically study how cache configurations impact the success rates of time-driven cache attacks. Finally, Chapter 7 conclude my dissertation work.

## Chapter 2

## **Literature Review**

### 2.1 Algorithm Optimizations

In this section, we will present the existing work related to finite automata optimization and the out-of-order packet DPI respectively.

### 2.1.1 Finite Automata Optimizations

NFAs have a limited size but can require expensive per-character processing, whereas DFAs offer limited per-character processing but suffer from the well-known state explosion problem. Each DFA state corresponds to a set of NFA states that can be simultaneously active [115]. Therefore, given an N-state NFA, the functionally equivalent DFA may potentially have up to 2N states. This state explosion problem may limit the DFAs ability to handle large and complex sets of regular expressions (typically those that include bounded and unbounded repetitions of wildcards or large character sets). Existing proposals targeting DFA-based solutions have focused on two aspects: (i) designing compression schemes aimed at minimizing the DFA memory footprint; and (ii) devising new automata to alternate DFAs in case of state explosion. Alphabet reduction [116, 21, 117, 118], run-length encoding [116], default transition compression [21, 17], state merging [20] and delta-

FAs [119] fall in the first category, while multiple-DFAs [116, 120], hybrid-FAs [20], history-based-FAs [19], XFAs [23], counting-FAs [22], and JFAs [26] fall in the second one. All these solutions, however, have been designed to operate on reassembled packet streams.

#### 2.1.2 Algorithms for Out-of-Order Packets in DPI

The classic approach to tackle the packet reordering problem is to buffer the received data packets, reorder them, and finally reassemble the packet stream (or packet flow). Dharmapurikar et al., [8] proposed a system to buffer and reorder packets. Their system consists of a packet analyzer, an out-of-order packet processing unit and a buffer manager, and mitigates the risk of denial of service attacks by forcing attackers to use multiple attacking hosts. However, the system is still vulnerable to attacks exhausting the buffer capacity. Similar packet buffering and stream reassembly solutions have also been proposed and adopted in the industry (e.g. Cisco [10], Nortel Networks [11], and Netrake [12]).

Despite its widespread adoption, this buffering and reassembling approach is vulnerable to Denial of Service attacks whereby attackers exhaust the buffer capacity by sending long sequences of out-of-order packets. There have been a handful of proposals attempting to reduce these risks by avoiding packet buffering and stream reassembly. Varghese et al., [121] proposed Split-Detect. This system splits the signatures of malicious traffic into pieces, performs deep packet inspection on these sub-signatures, and diverts the TCP packets for reassembly from the fast path to the slow path upon detection of any of these sub-signatures. Split-Detect can achieve up to 90% storage requirement reduction compared to conventional NIDS. However, rather than avoiding stream reassembly, it offloads it to the slow path. In addition, Split-Detect is restricted to exact-match signatures and patterns with a fixed length. Our proposal works also on arbitrarily sized patterns. Johnson et al., [15] proposed a DFA-based solution that, for each packet, performs parallel traversals from each and all DFA states. This proposal is based on the observation that, since the initial DFA state is unknown when processing an out-of-order packet, any DFA state must be considered a potential initial state. A post-processing step will then be performed to reconstruct valid traver-

sals at packet boundaries. Although this scheme may be effective in the presence of non-malicious traffic (where the traversal is limited to a few DFA states), it does not provide a good worst-case bound, and it may involve a large amount of post-processing. More recently, Chen et al., [14] proposed AC-Suffix-Tree. This scheme avoids packet buffering and stream reassembly by combining an Aho-Corasick DFA with a suffix tree. Zhang et al., [13] proposed On-Line Reassembly (OLR), a scheme that stores patterns in a DAWG. Both these solutions, however, apply only to exact-match patterns and are unable to handle regular expressions, which are more common in real-world applications. Our scheme does not suffer from this limitation.

#### 2.2 HPC devices Based Accelerations

Previous work has focused on accelerating regular expression matching on a variety of parallel architectures: general purpose multi-core processors [20, 21, 29, 19, 18, 120, 23, 26], network processors [122, 123, 124], FPGAs [28, 125, 126, 30], ASIC-[116, 17, 127] and TCAM-[128, 129, 130] based systems. In all these proposals, particular attention has been paid to providing efficient logic- and memory-based representations of the underlying automata (namely, DFAs, NFAs and equivalent abstractions).

#### 2.2.1 **GPU**

Recent work [131] has considered exploiting the GPUs massive hardware parallelism and high-bandwidth memory system in order to implement high-throughput networking operations. In particular, a handful of proposals [132, 133, 134, 27, 25, 50, 51] have looked at accelerating regular expression matching on GPU platforms. Most of these proposals use the coarse-grained block-level parallelism offered by these devices to support packet- (or flow-) level parallelism intrinsic in networking applications.

Gnort [132, 133], proposed by Vasiliadis et al, represents an effort to port Snort IDS to GPUs.

To avoid dealing with the state explosion problem, the authors process on GPU only a portion of the dataset consisting of regular expressions that can be compiled into a DFA, leaving the rest in NFA form on CPU for separate processing. As a result, this proposal speeds up the average case, but does not address malicious and worst case traffic. Gnort represents the DFA on GPU memory uncompressed, and exploits parallelism only at the packet level (i.e., it does not leverage any kind of data structure parallelism to further speed up the operation).

Smith et al [134] ported their XFA proposed data structure [23] to GPUs, and compared the performance achieved by an XFA and a DFA-based solution on datasets consisting of 31-96 regular expressions. They showed that a G80 GPU can achieve a 10-11X speedup over a Pentium 4, and that, because of the more regular nature of the underlying computation, on GPU platforms DFAs are slightly preferable to XFAs. It must be noted that the XFA solution is suited to specific classes of regular expressions: those that can be broken into non-overlapping sub-patterns separated by .\* terms. However, these automata cannot be directly applied to regular expressions containing overlapping sub-patterns or  $[^{\circ}c_1...c_k]$ \* terms followed by sub-pattern containing any of the  $c_1,...,c_k$  characters.

More recently, Cascarano et al [27] proposed iNFAnt, a NFA-based regex matching engine on GPUs. Since state explosion occurs only when converting NFAs to DFAs, iNFAnt is the first solution that can be easily applied to rule-sets of arbitrary size and complexity. In fact, this work is, to our knowledge, the only GPU-oriented proposal which presents an evaluation on large, real-world datasets (from 120 to 543 regular expressions). The main disadvantage of iNFAnt is its unpredictable performance and its poor worst-case behavior.

#### 2.2.2 Automata Processor

Recent studies have revealed Micron AP can improve performance for many applications from data mining [135, 60], machine learning [62], bioinformatics [61], intrusion detection [63, 136], graph analysis [64], and so on [137, 65, 138, 139, 67]. Among them, FU [140], SM APIs [59], and

RAPID [69] are highly related with this work.

Tracy et al. [140] propose a functional unit (FU) approach to accelerate APM problems. They decompose a Levenshtein automata to 8 FUs, then represent FUs in ANML and pre-compile&save them as macros. This approach can benefit all Levenshtein automata by reducing placement&routing overhead to some extent. However, it still requires significant inter-instance routing and compiling time for large-scale automata as shown in our experiments.

Programming on AP with ANML demands expertises of both automata structures and AP architecture. Therefore, String Matching (SM) APIs [59] are introduced recently to provide high-level abstracts for APM. Taking user-provided patterns and distances, SM APIs can generate binary images accordingly. However, if either the given distance or the pattern length doesn't fit any template in the library of SM APIs, it is necessary to construct automata and place-and-route them from scratch during the compilation. As shown in our experiments, SM APIs cannot support some large-scale problem sizes.

Angstadt et al. [69] propose RAPID, a high-level programming model for AP. RAPID bypasses the pre-compiled macros; instead, RAPID places and routes a small repetitive portion of the whole program, saves it as a small binary image, and loads this portion as many times as need on the AP board. However, this scheme may underperform pre-compiling strategy in the case that the desired pattern is large and its pattern lengths vary, because the repetitive portion of program is usually smaller than a macro. Another drawback of this method is losing the flexibility of cascadable macros once the portion of program is saved as a binary image which can be only loaded and executed.

Wadden et al . [141] propose ANMLZoo, a benchmark suite for automata processors. It has a subset targeting on APM, and explores how different distance types, error numbers and pattern lengths affect fan-in/fan-out of each STE then further affect configuration complexity. However, it doesn't fully explore the AP's capacity since doesn't leverage any pre-compiled information. Moreover, users still need to manually manipulate the AP automata when extending the benchmarks.

# 2.3 Security Vettings for Android