# Design and Implementation of a Radiation Hardened GaN Based Isolated DC-DC Converter for Space Applications

# Victor Turriate

Thesis submitted to the faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

Master of Science In Electrical Engineering

Dushan Boroyevich (Chair) Rolando Burgos (Co-Chair) Daniel M. Sable Steve C. Southward

September 20, 2018 Blacksburg, VA, USA

Keywords: Gallium Nitride, Phase Shifted Full Bridge, Current Doubler Rectifier, space, radiation hardened, rad-hard, DC-DC converter

Copyright (Victor Turriate©)

# Design and Implementation of a Radiation Hardened GaN Based Isolated DC-DC Converter for Space Applications

#### Victor Turriate-Gastulo

#### **ABSTRACT**

Power converters used in high reliability radiation hardened space applications trail their commercial counterparts in terms of power density and efficiency. This is due to the additional challenges that arise in the design of space rated power converters from the harsh environment they need to operate in, to the limited availability of space qualified components and field demonstrated power converter topologies. Recently released radiation hardened Gallium Nitride (GaN) Field Effect Transistors (FETs) with their inherent radiation tolerance and superior performance over Silicon Power Metal Oxide Semiconductor Field Effect Transistors (MOSFETs), however, offer a promising alternative to improve power density and performance of space power converters.

This thesis presents a practical implementation of the Phase Shifted Full Bridge DC-DC Isolated converter with synchronous rectification for space applications using newly released radiation hardened GaN FETs. A survey outlining the benefits of new radiation hardened GaN FETs for space power applications compared to existing radiation hardened power MOSFETs is included. In addition, this work summarizes the main design considerations to implement the selected converter topology for space applications. Furthermore, the overall design process followed to design the DC-DC converter power stage, as well as a comprehensive power loss analysis are included.

This work also includes details to implement a conventional hard-switched Full Bridge DC-DC converter using radiation hardened GaN FETs for this application. An

efficiency and component stress comparison was performed between the hard-switched Full Bridge design and the Phase Shifted Full Bridge DC-DC converter design. This comparison highlights the benefits of phase shift modulation (PSM) and zero voltage switching (ZVS) for GaN FET applications. Furthermore, different magnetic designs were characterized and compared for efficiency in both converters. The DC-DC converters implemented in this work regulate their outputs to a nominal 20 V, delivering 500 W from a nominal 100 V DC Bus input. Failure mode and effects analysis (FMEA) and protection circuitry required for complete radiation qualification of the Phase Shifted Full Bridge DC-DC converter topology are not addressed by this work.

# Design and Implementation of a Radiation Hardened GaN Based Isolated DC-DC Converter for Space Applications

#### Victor Turriate-Gastulo

#### GENERAL AUDIENCE ABSTRACT

Recently released radiation-hardened Gallium Nitride (GaN) Field Effect Transistors (FETs) offer the opportunity to increase efficiency and power density of space DC-DC power converters. The current state of the art for space DC-DC power conversion trails their commercial counterparts in terms of power density and efficiency. This is mainly due to two factors. The first factor is related to the additional challenges that arise in the design of space rated power converters from the harsh environment they need to operate in, to the limited availability of space qualified components and field demonstrated converter topologies. The second factor lies in producing reliable radiation hardened power Metal Oxide Semiconductor Field Effect Transistors (MOSFETs).

GaN FETs not only have better electrical performance than power MOSFETs, they have also demonstrated inherent tolerance to radiation. This results in less structural device changes needed to make GaN FETs operate reliably under high radiation compared to their MOSFETs counterparts. This work outlines the design implications of using newly released radiation hardened GaN FETs to implement a fixed frequency isolated Phase Shifted Full Bridge DC-DC converter while strictly abiding to the design constraints found in space-power converter applications. In addition, a one-to-one performance comparison was made between the soft-switched Phase Shift modulated Full Bridge and the conventional hard-switched Full Bridge DC-DC converter. Finally, different magnetic designs were evaluated in the laboratory to assess their impact on converter efficiency.

To

Miriam Turriate

Gloria Gastulo

Godofredo Turriate

#### ACKNOWLEDGEMENTS

I would like to take this opportunity to thank my advisor, Dr. Dushan Boroyevich, not only for his support and guidance during my last couple of years at the CPES, but also for influencing my decision to enter the field of power electronics during my undergraduate years at Virginia Tech. I would also like to thank Dr. Rolando Burgos for his valuable guidance and support throughout my projects at CPES, and for the opportunities provided through the Wide Bandgap Generation Fellowship sponsored by the United States Department of Energy. Additionally, I would like to thank Dr. Steve Southward for his time as a committee member and for the lessons imparted in his control courses. It is also important to thank Dr. Fred Lee and Dr. Qiang Li for providing me with important knowledge to complete this work through their courses.

I am also very grateful to Dr. Dan Sable for his time as a committee member, for his guidance, and for making this thesis possible by sponsoring my research through VPT, Inc. I would also like to thank Leonard Leslie, John Hodock, Jeremy Ferrell, Douglas Sterk, Nathan Kees, David Reusch, and Phillip Kugel for their technical guidance during my collaboration with VPT, Inc. In addition, I would like to express my gratitude to Brandon Witcher from VPT for his friendship, mentorship and for sharing his valuable technical insight during our technical discussions.

In addition, I would like to thank Ms. Linda Long, Ms. Na Ren, Ms. Theresa Shaw, Ms. Trish Rose, Ms. Marianne Hawthorn, Ms. Lauren Shutt, and Mr. David Gilham of the CPES administrative staff. I would also like to thank all my CPES friends and colleagues. And, for making my second time at Virginia Tech the most memorable, I want to thank Amy Romero, Emma Raszmann, Niloofar Rashidi Mehrabadi, Grace Watt, Christina

DiMarino, Alex Chu (AKA Chupac, Chulius, etc.), Mudit Khanna, Joseph "Pepe" Kozak, Slavko Mocevic, Sungjae Ohn, Paul Rankin, Qiong Wang, Erick Aponte, Lee Gill, and Christopher Salvo.

Finally, but most importantly, I want to thank my parents, Gloria Gastulo and Godofredo Turriate, and my siblings Juan Carlos and Gloria for their love and encouragement in all my endeavors. In addition, a lifetime would not be sufficient to reciprocate and express my gratitude to Miriam for all her love, great patience, and support during this process. Also, for believing in my professional and academic expeditions even when they meant quitting our jobs and selling our house to test life in different horizons, sacrificing financial and emotional stability and postponing her own goals and dreams so that I could pursue some of mine—as eccentric as they sounded more than two years ago.

# **Table of Contents**

| Chapter 1.1. |     | Introductionkground                                             |    |

|--------------|-----|-----------------------------------------------------------------|----|

| 1.2.         |     | liation Effects on Power Converters and Power MOSFETS           |    |

| 1.2.         |     | Single Event Effects                                            |    |

| 1.2.         |     | Total Ionizing Dose and Displacement Damage Dose                |    |

| 1.3.         |     | mmercial and Radiation Hardened Power MOSFETS                   |    |

| 1.3.         |     | nefits of Radiation Hardened GaN FETs                           |    |

| 1.4.         |     | search Scope and Objectives                                     |    |

| 1.6.         |     | esis Outline                                                    |    |

|              |     |                                                                 |    |

| 2.1.         |     | ppology Selection<br>mary Side Power Stage Selection            |    |

| 2.2.         | Sec | ondary Side Rectifier Selection                                 | 21 |

| Chapter 3.1. |     | Isolated DC-DC Full Bridge Converter Designoduction             |    |

| 3.2.         | Ger | neral Design Considerations                                     | 26 |

| 3.2.         | 1.  | Signal Isolation for Space Power Applications                   | 26 |

| 3.2.         | 2.  | Rad-hard GaN FET Gate Driver                                    | 27 |

| 3.2.         | 3.  | Part Procurement and Prototyping Costs                          | 28 |

| 3.2.         | 4.  | Gate Control for Power Transistors                              | 29 |

| 3.2.         | 5.  | Analog Control                                                  | 31 |

| 3.2.         | 6.  | Current Sensing for Peak Current Mode Control                   | 33 |

| 3.2.         | 7.  | Resonant Inductance for ZVS in Phase Shifted Full Bridge        |    |

| 3.3.         | Gat | e Driver Design for Phase Shift Control                         | 45 |

| 3.3.         | 1.  | Proposed Circuit                                                | 45 |

| 3.3.         | 2.  | Pulsed Width Modulation to Phase Shift Modulation               | 47 |

| 3.3.         | 3.  | Current Doubler Control for Phase Shifted Full Bridge Converter | 48 |

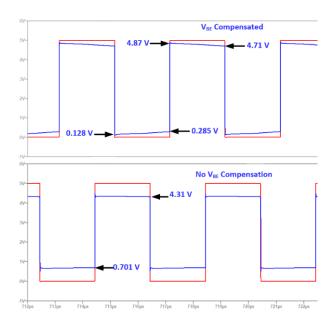

| 3.3.         | 4.  | GaN FET Gate Driver Power                                       | 50 |

| 3.3.         | 5.  | Control Signal Conditioning and Dead-time Control               | 54 |

| 3.3.         | 6.  | Pulse Transformer Design Considerations                         | 57 |

| 3.4.         | Pul | se Transformer Design                                           | 61 |

| 3.5.         | Gat | e Driver Design for Full Bridge Control                         | 63 |

| 3.5          | .1. | Full Bridge DC-DC Converter PWM Control                     | 64    |

|--------------|-----|-------------------------------------------------------------|-------|

| 3.5          | .2. | Current Doubler Rectifier Control for Full Bridge Converter | 68    |

| 3.6.         | Pha | se Shifted Full Bridge Power Stage Design                   | 70    |

| 3.6          | .1. | Initial Power Stage Calculations                            | 73    |

| 3.6          | .2. | Output Inductor Design                                      | 75    |

| 3.6          | .3. | Transformer Design                                          | 78    |

| 3.7.         | Pov | ver Loss Analysis                                           | 80    |

| 3.7          | .1. | Transformer Power Losses                                    | 80    |

| 3.7          | .2. | Inductor Power Losses                                       | 81    |

| 3.7          | .3. | Full Bridge Power Stage Losses                              | 82    |

| 3.7          | .4. | Rectifier Power Stage Losses                                | 83    |

| 3.7          | .5. | Miscellaneous Power Losses                                  | 84    |

| 3.7          | .6. | Efficiency Approximation                                    | 84    |

| Chapter 4.1. |     | Hardware Implementationnted Circuit Board Layout            |       |

| 4.1          | .1. | Rad-Hard GaN FETs Paralleling                               | 87    |

| 4.1          | .2. | GaN FET Gate Driver Layout Consideration                    | 90    |

| 4.1          | .3. | Current Sense Layout                                        | 92    |

| 4.2.         | Pro | totype Board Stack                                          | 94    |

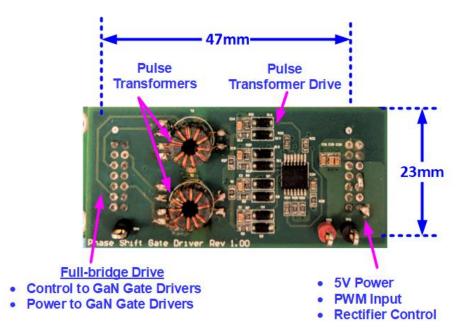

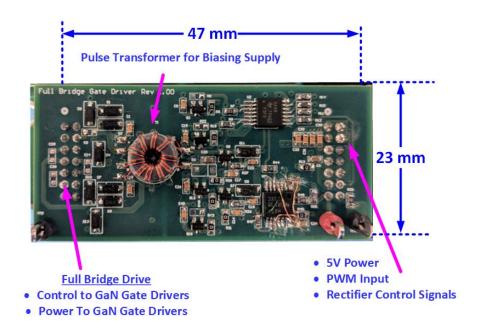

| 4.3.         | Pha | se Shift Gate Driver Board                                  | 96    |

| 4.4.         | Ful | l Bridge Gate Driver Board                                  | 97    |

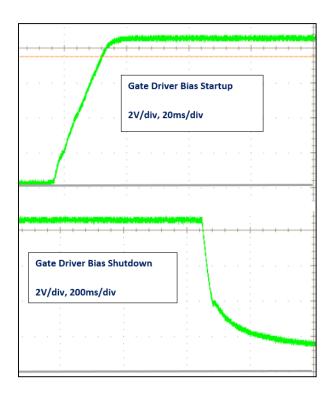

| Chapter 5.1. |     | Experimental Resultsase Shift Gate Driver                   |       |

| 5.1          | .1. | Pulse Transformer Characterization                          | . 100 |

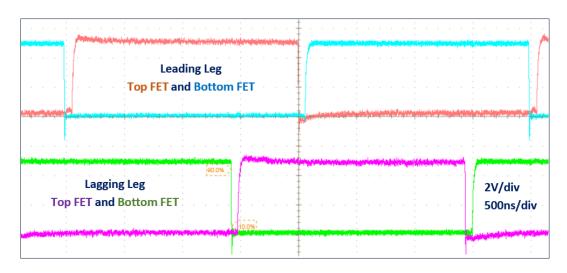

| 5.1          | .2. | Phase Shift Gate Driver Test Results                        | . 100 |

| 5.2.         | Ful | l Bridge Gate Driver                                        | . 103 |

| 5.3.         | Cui | rent Sense Signal for PCMC                                  | . 104 |

| 5.4.         | Rac | l-hard GaN FET Paralleling                                  | . 106 |

| 5.5.         | Eff | iciency Results                                             | . 109 |

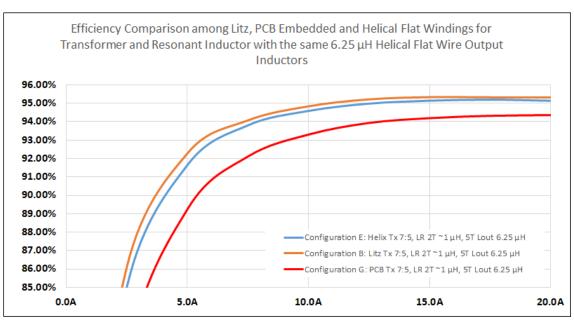

| 5.5          | .1. | Transformer Evaluation                                      | . 109 |

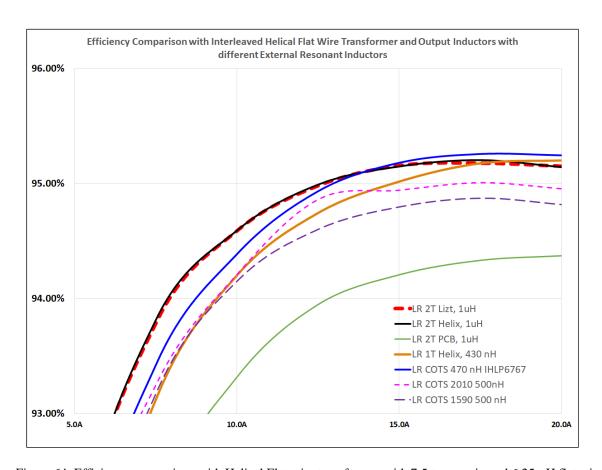

| 5.5          | .2. | External Resonant Inductor Evaluation                       | . 111 |

| 5.5          | .3. | Most Efficient Phase Shifted Full Bridge Configuration      | . 113 |

| 5.5          | .4. | Phase Shifted Full Bridge versus Full Bridge Converter      | . 115 |

| Chapter | 6 Conclusions                         | 119 |

|---------|---------------------------------------|-----|

| 6.1.    | Conclusions from Gate Driver Design   | 119 |

| 6.2.    | Conclusions from Power Stage Design   | 122 |

| 6.3.    | Collection of Practical Circuits      | 123 |

| 6.4.    | Prospective Areas for Future Research | 124 |

| Referen | ces                                   | 127 |

# **List of Figures**

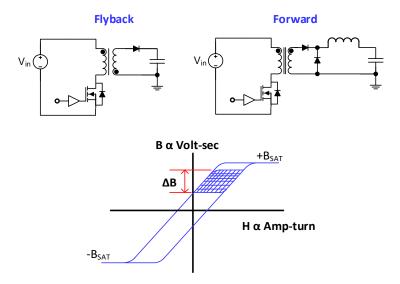

| Figure 1. Common single ended isolated topologies used in space converters 2                                             |

|--------------------------------------------------------------------------------------------------------------------------|

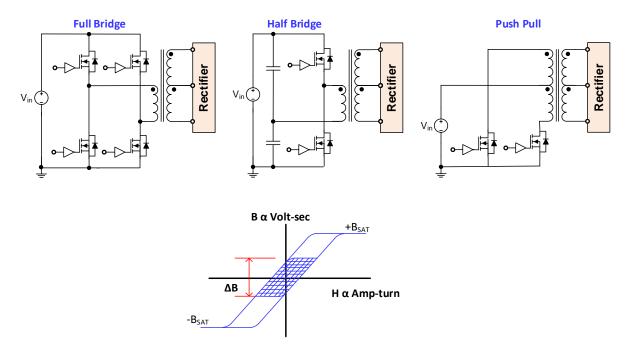

| Figure 2. Common double ended isolated topologies                                                                        |

| Figure 3. Freebird Semiconductor FBG20N18B, 200V, 26 m $\Omega$ rad-hard GaN FET next to an SO-8 IC package              |

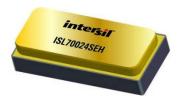

| Figure 4. Intersil ISL70024SEH, 200V, 45 m $\Omega$ rad-hard GaN FET [32]                                                |

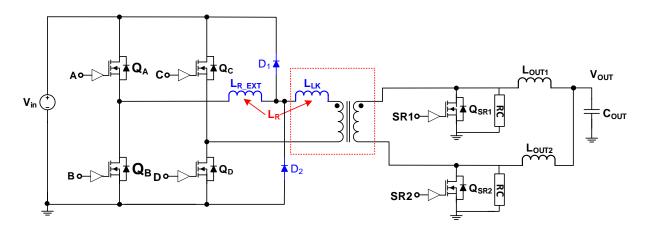

| Figure 5. Phase Shifted Full Bridge DC-DC converter with Current Doubler Rectifier 20                                    |

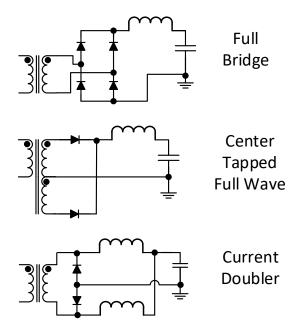

| Figure 6. Common output rectifiers for isolated DC-DC converters                                                         |

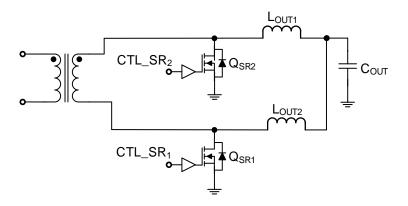

| Figure 7. Current Doubler synchronous rectifier                                                                          |

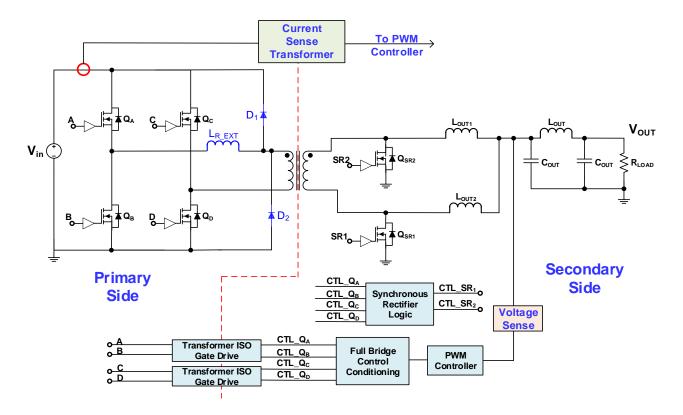

| Figure 8. Block diagram for isolated DC-DC converter power stage and control 26                                          |

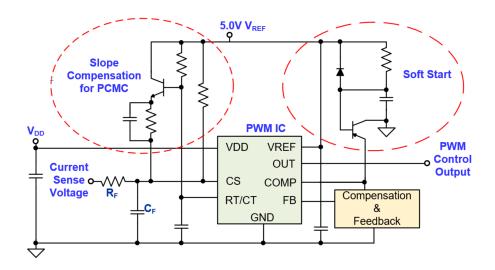

| Figure 9. Single Ended PWM Controller and peripheral circuitry                                                           |

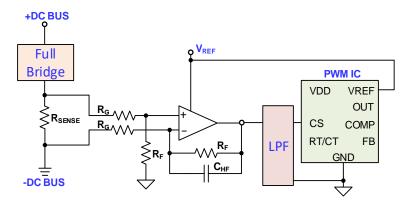

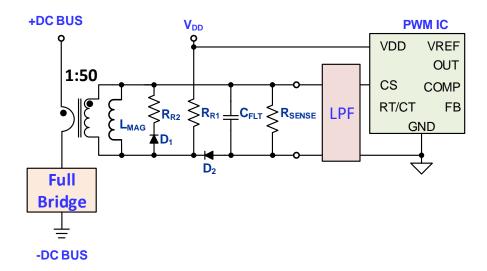

| Figure 10. Current sensing on DC bus return path with a sense resistor and op-amp 33                                     |

| Figure 11. Sensed current output: 10 MHz (red) and 100 MHz (blue) op-amp GBW 35                                          |

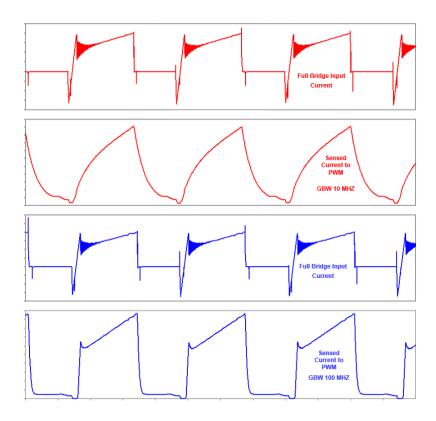

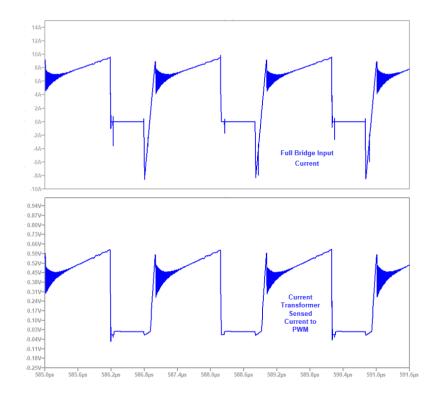

| Figure 12. Current transformer with forced reset placed at positive DC bus                                               |

| Figure 13. Current transformer sense: DC Bus current (top) and sensed current before low pass filter (bottom)            |

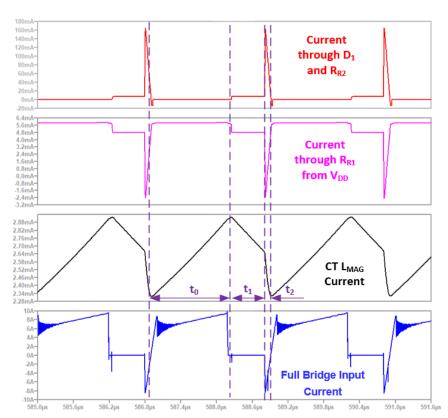

| Figure 14. Current transformer sensor reset action during phase shift modulation 38                                      |

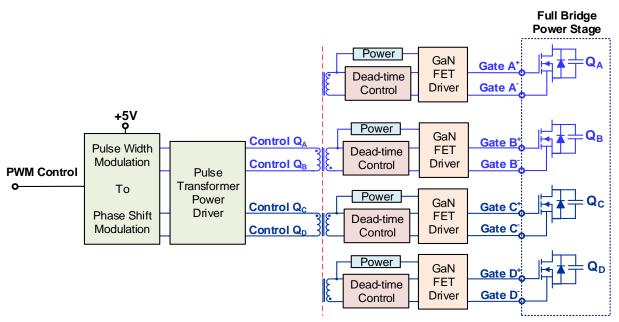

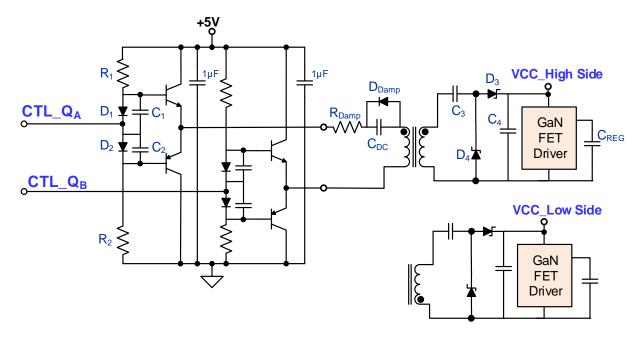

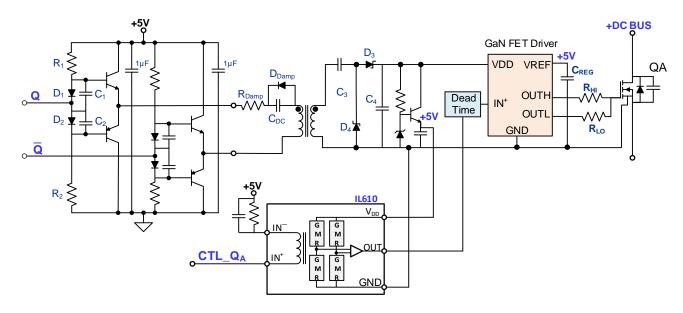

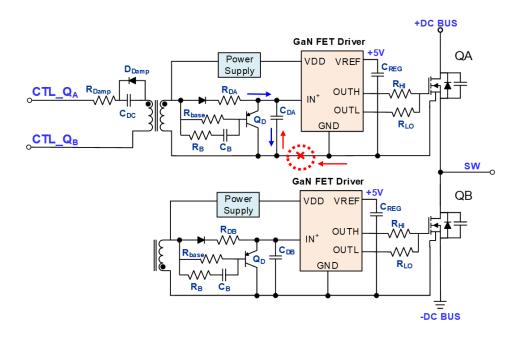

| Figure 15. Gate driver block diagram for Full Bridge stage switches A, B, C, and D 46                                    |

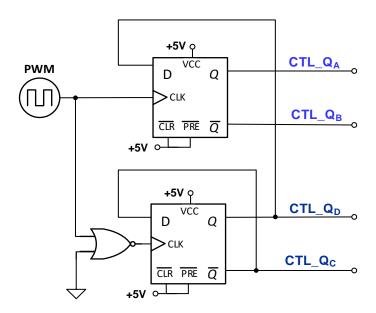

| Figure 16. PWM to Phase Shift Modulation circuit for Full Bridge power stage 47                                          |

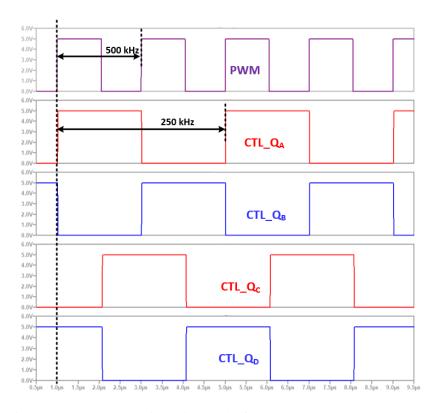

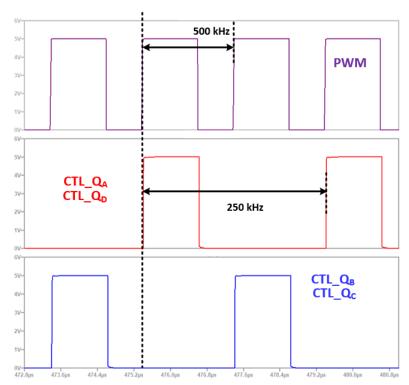

| Figure 17. PWM to PSM simulation results from SPICE at 50% PWM duty cycle 48                                             |

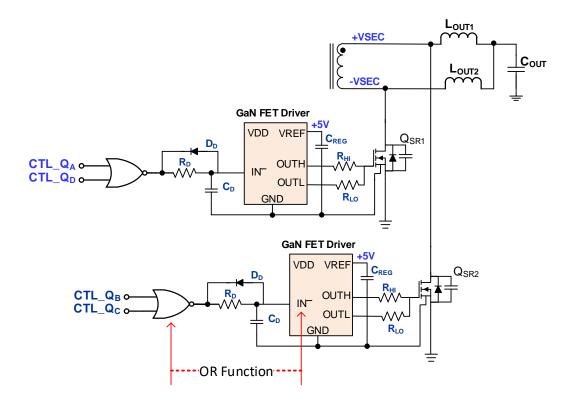

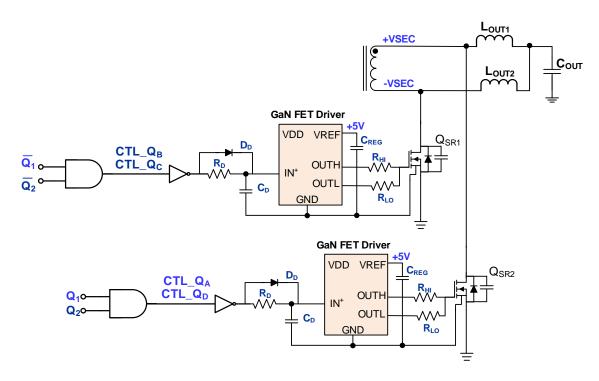

| Figure 18. Current Doubler Synchronous Rectifier gate control for Phase Shifted Full Bridge DC-DC converter              |

| Figure 19. Current Doubler Synchronous Rectifier gate timing for Phase Shifted Full Bridge DC-DC converter               |

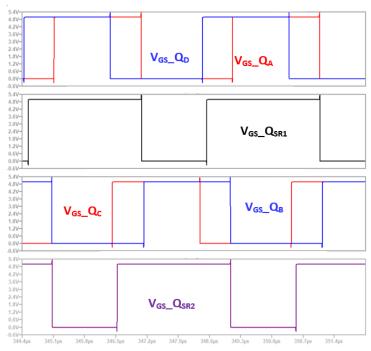

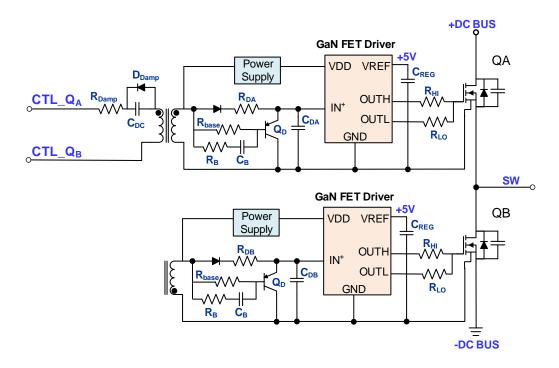

| Figure 20. Pulse transformer push-pull power stage and isolated power supply for GaN FET gate driver IC for one half-leg |

| Figure 21. Base-emitter compensated push-pull output (top) versus uncompensated output (bottom)                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

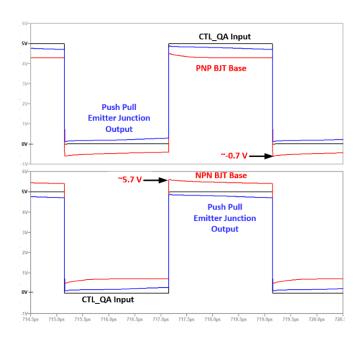

| Figure 22. Base-emitter junction compensation signals showing input to PNP (top) and NPN (bottom) BJTs in the push-pull power stage at control signal for GaN FET $Q_A \dots 52$ |

| Figure 23. Control signal conditioning with PNP BJT fast turn OFF for one of the Full Bridge half-legs                                                                           |

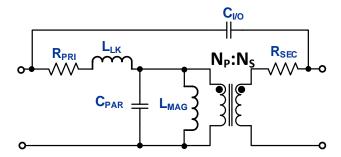

| Figure 24. Pulse transformer equivalent circuit model                                                                                                                            |

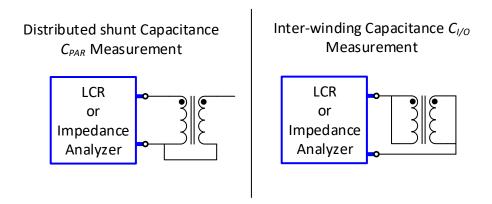

| Figure 25. Pulse transformer parasitic capacitance measurement setup                                                                                                             |

| Figure 26. PWM control signal derivation for Full Bridge DC-DC converter 65                                                                                                      |

| Figure 27. Hard-switched Full Bridge DC-DC converter gate timing                                                                                                                 |

| Figure 28. Self-powered gate driver for one GaN FET ( <i>Q</i> <sub>A</sub> ) in Full Bridge DC-DC converter                                                                     |

| Figure 29. Current Doubler Synchronous Rectifier gate control for Full Bridge DC-DC converter                                                                                    |

| Figure 30. Current Doubler Synchronous Rectifier timing for hard-switched Full Bridge DC-DC converter                                                                            |

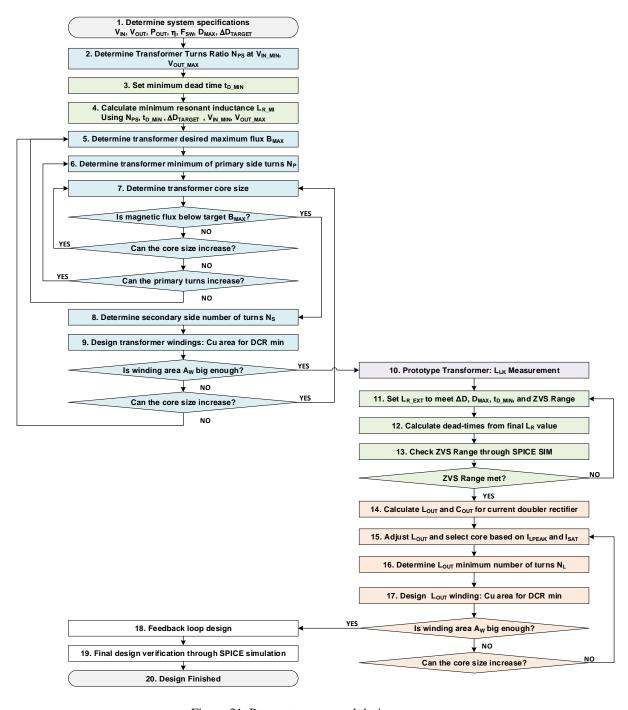

| Figure 31. Power stage general design process                                                                                                                                    |

| Figure 32. Leading leg resonant tank circuit for ZVS of Q <sub>A</sub>                                                                                                           |

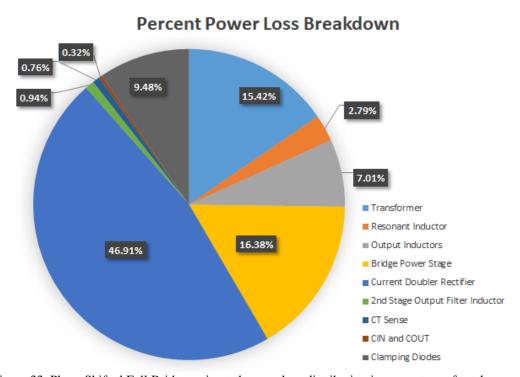

| Figure 33. Phase Shifted Full Bridge estimated power loss distribution in percentage of total power loss at nominal operating point                                              |

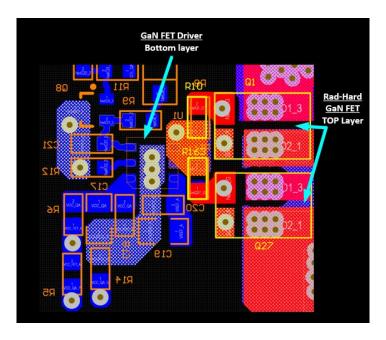

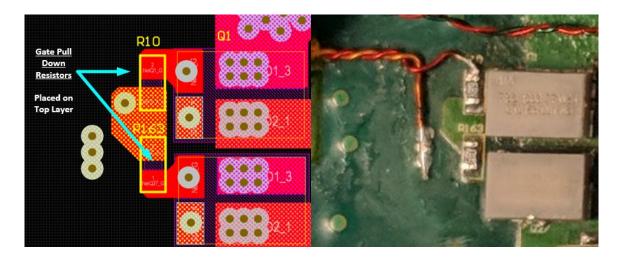

| Figure 34. PCB layout showing top (red) and bottom (blue) layers for top switch Q <sub>A</sub> in Full Bridge power stage                                                        |

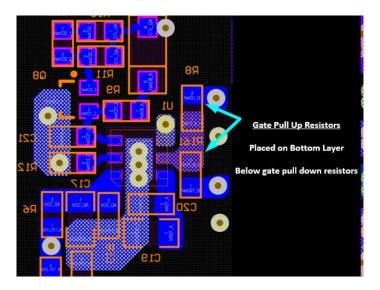

| Figure 35. Gate pull up resistors on bottom layer (blue) for top switch Q <sub>A</sub> in Full Bridge power stage                                                                |

| Figure 36. Gate pull down resistors on top layer (red) for top switch Q <sub>A</sub> in Full Bridge power stage                                                                  |

| Figure 37. Full Bridge power stage input current flow from +DC Bus to -DC Bus return (ground, green plane)                                                                       |

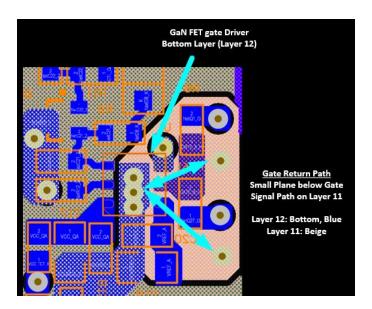

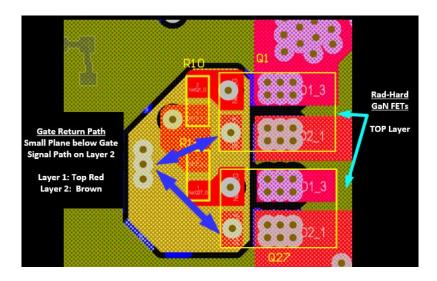

| Figure 38. Gate driver layout showing rad-hard GaN FET gate return path, layer 12 (blue) and layer 11 (Beige)                                                                    |

| Figure 39. Gate driver layout showing rad-hard GaN FET gate return path, layer 1 (red) and layer 2 (brown)                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

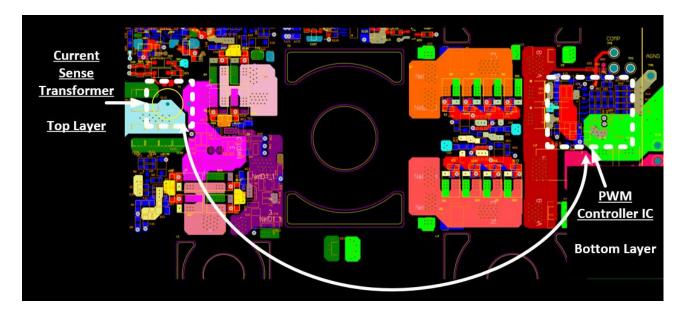

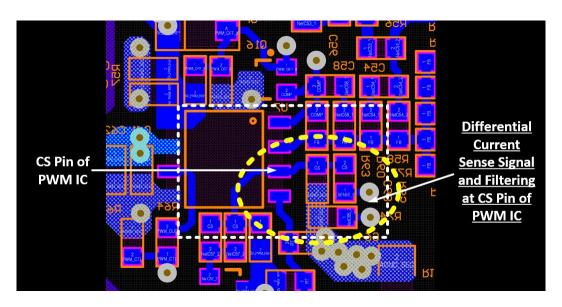

| Figure 40. Location of current sense transformer sensing and PWM controller IC destination                                                                         |

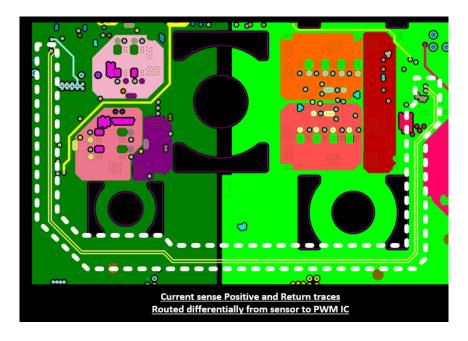

| Figure 41. Differential current sense route for positive and return traces, from current transformer sensor to PWM IC input                                        |

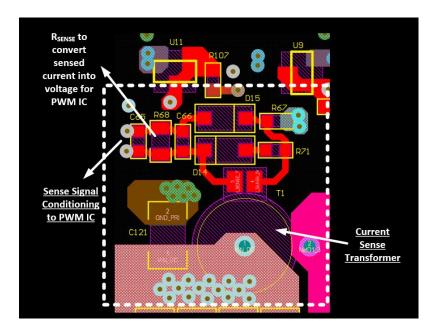

| Figure 42. Current sensor layout, top layer in red                                                                                                                 |

| Figure 43. PWM IC Receiving end showing differentially routed current sense signal, input and filtering into CS pin of PWM IC                                      |

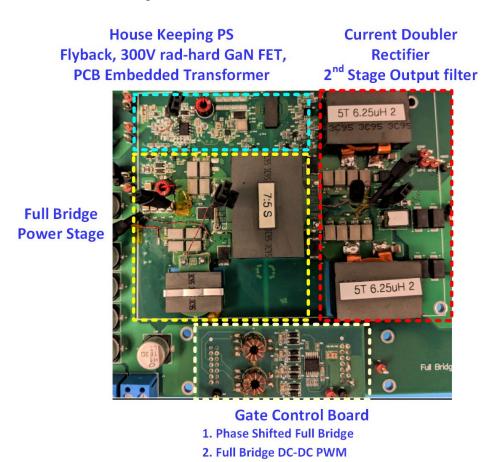

| Figure 44. Phase Shifted Full Bridge Prototype Rev. 1.00. 95                                                                                                       |

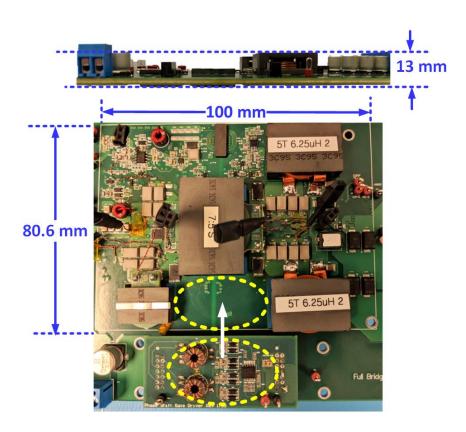

| Figure 45. Phase Shifted Full Bridge DC-DC converter dimensions                                                                                                    |

| Figure 46. Self-powered gate driver for rad-hard GaN FET based Phase Shifted Full Bridge DC-DC converter                                                           |

| Figure 47. Self-powered gate driver for rad-hard GaN FET based Full Bridge DC-DC converter                                                                         |

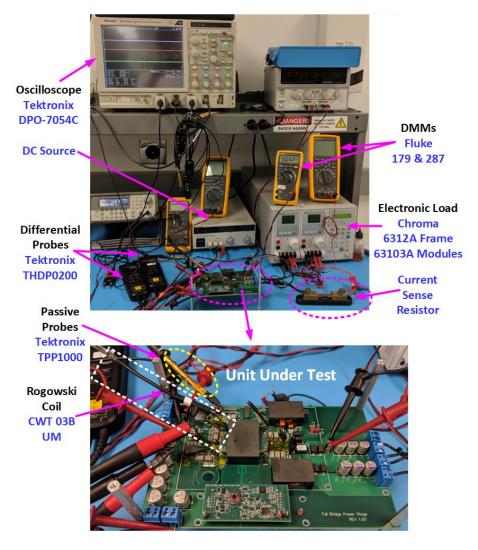

| Figure 48. Test Setup and equipment                                                                                                                                |

| Figure 49. Gate driver generated startup and shutdown bias voltage waveforms for GaN gate driver chip                                                              |

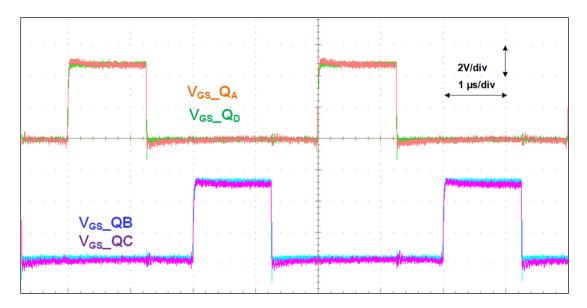

| Figure 50. Gage-source voltage waveforms for leading leg (QA and QB) and lagging legs (QC, and QD) GaN FETs operating at 100V input, 400W load, 20V output         |

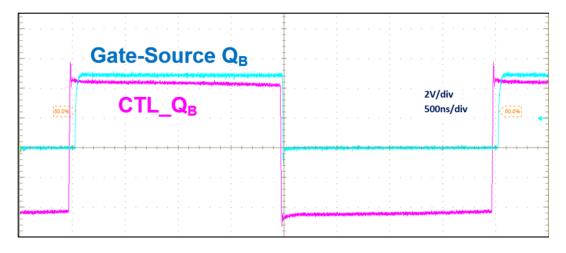

| Figure 51. Pulse transformer output for low-side rad-hard GaN FET QB (purple) and GaN gate driver IC output directly the gate-source node of GaN FET QB (blue)     |

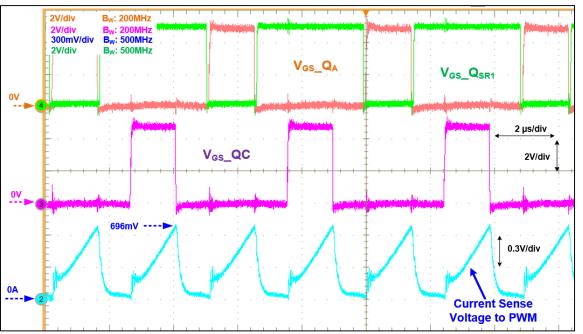

| Figure 52. Full Bridge DC-DC Converter rad-hard GaN FET Gate-source voltage at full load, 100 V input, 20 V output                                                 |

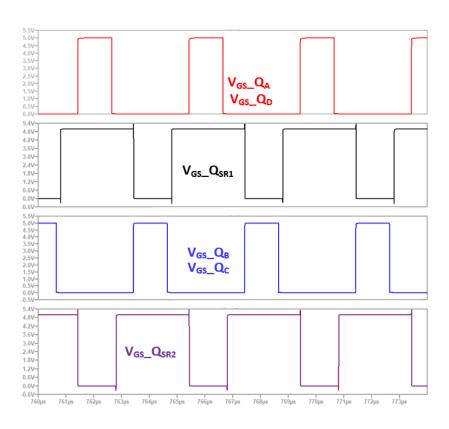

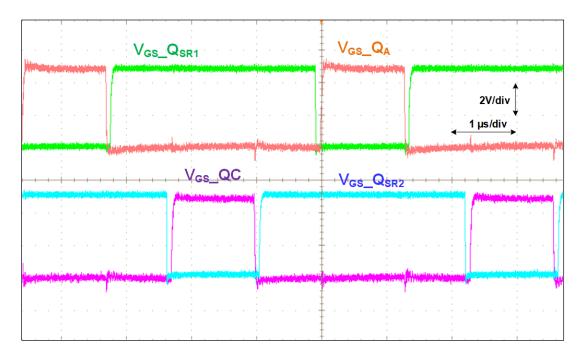

| Figure 53. Full Bridge power stage and current double rectifier gate-source voltage waveforms for rad-hard GaN FETs running at 500 W, 100 V input, 20 V output 104 |

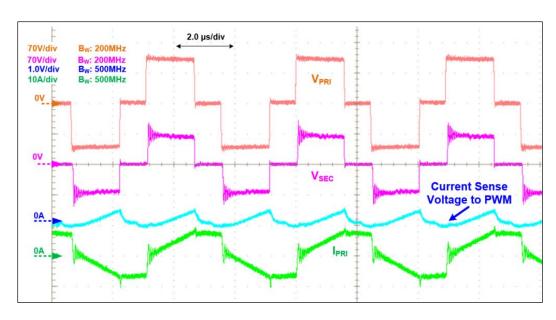

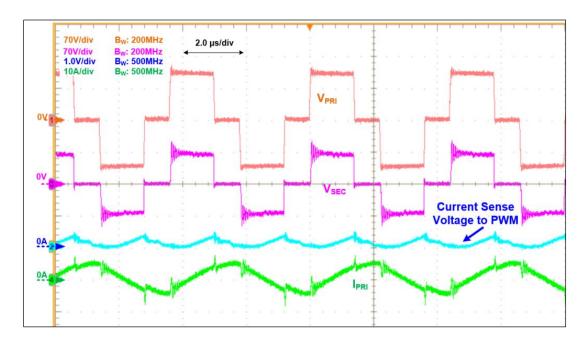

| Figure 54. Current sense voltage into PWM current sense pin shown in blue for Phase Shifted Full Bridge operating at full load                                     |

| Figure 55. Current sense voltage into PWM current sense pin shown in blue for Phase Shifted Full Bridge operating at 1.0A load                                     |

| Figure 56. Current sense voltage into PWM current sense pin shown in blue for hard switched Full Bridge DC-DC converter operating at 400 W load                    |

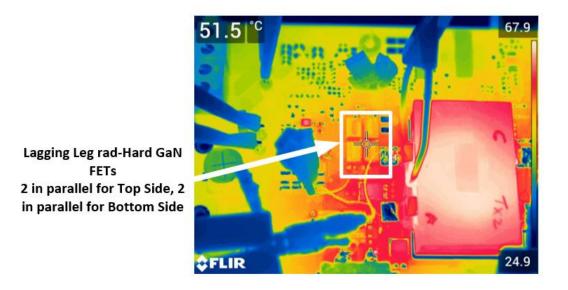

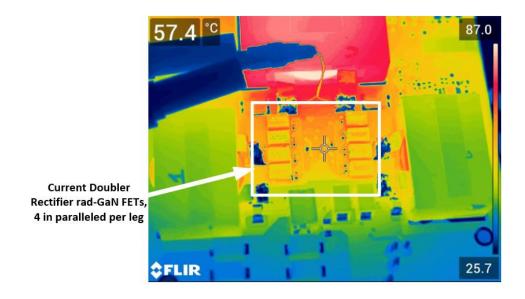

| Figure 57. Thermal images showing good heat distribution at paralleled rad-hard GaN FETs in the lagging phase leg for the full bridge power stage 500 W load operation 107                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 58. Thermal images showing good heat distribution at paralleled rad-hard GaN FETs in the Current Doubler rectifier for 500 W load operation                                                             |

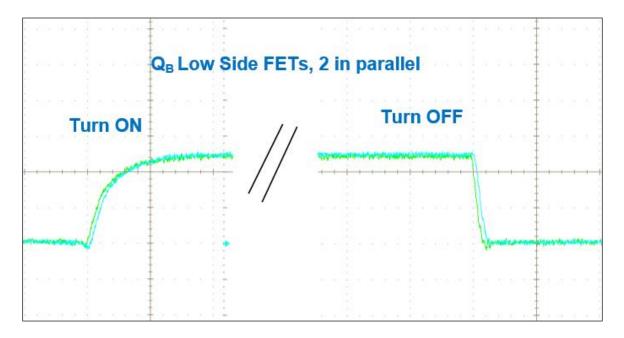

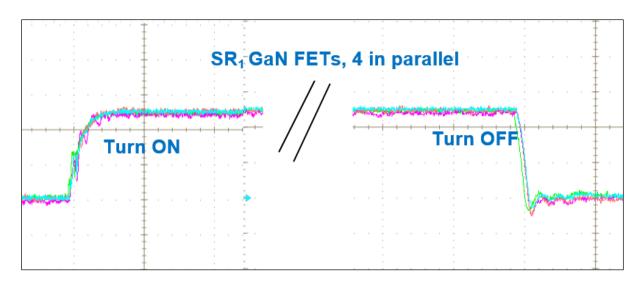

| Figure 59. Q <sub>B</sub> gate-source voltage waveforms for each of the two devices in parallel during turn ON and turn OFF, 400W load                                                                         |

| Figure 60. Rectifier rad-hard GaN FETs gate-source voltage waveforms for each of the four devices in parallel during turn ON and turn OFF                                                                      |

| Figure 61. Different transformer windings evaluated: Helical Flat Wire, PCB Embedded and Litz Wire                                                                                                             |

| Figure 62. Efficiency comparison for Phase Shifted Full Bridge with different transformer windings                                                                                                             |

| Figure 63. EQ20 3C95 ferrite magnetic core based resonant inductors with Litz (left) and Helical Flat Wire                                                                                                     |

| Figure 64. Efficiency comparison with Helical Flat wire transformer with 7:5 turns ratio and 6.25 µH flat wire helical output inductors for different resonant inductors constructions                         |

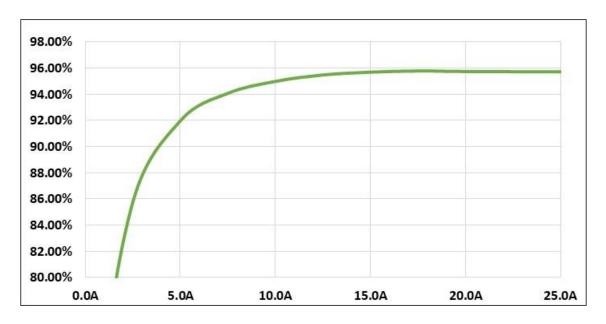

| Figure 65. DC-DC Converter Efficiency with best magnetic winding configuration at 100V input, 20V output                                                                                                       |

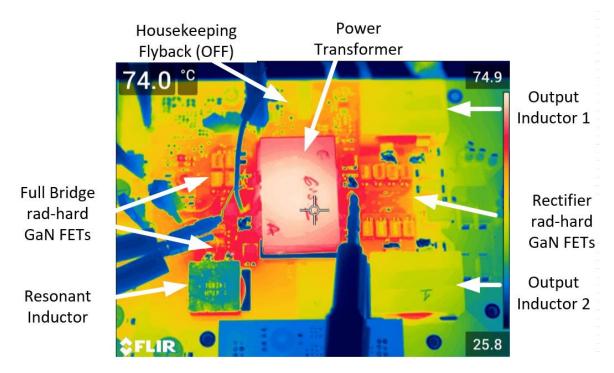

| Figure 66. Thermal image of DC-DC Converter running at 500W load, 100V input, 20V output, 30 min operation, free-air                                                                                           |

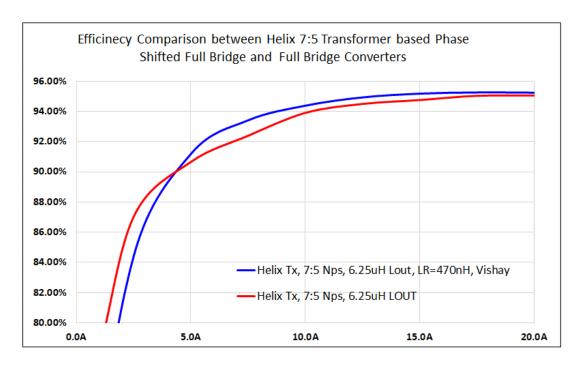

| Figure 67. Efficiency comparison for Phase Shifted Full Bridge and conventional Full bridge converters                                                                                                         |

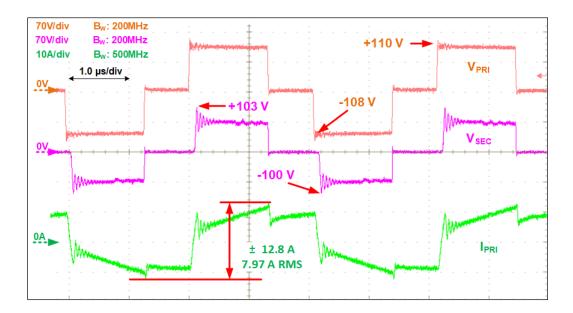

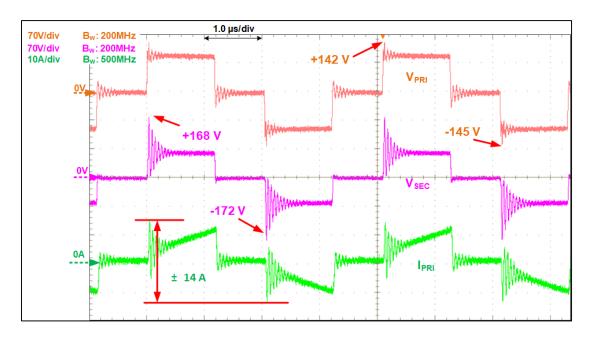

| Figure 68. Phase Shifted Full Bridge DC-DC Converter: primary FETs peak voltage (orange), rectifier FETs peak voltage (purple), and transformer primary current (green) at 400 W load, 100V input, 20 V output |

| Figure 69. Full Bridge DC-DC Converter: primary FETs peak voltage (orange), rectifier FETs peak voltage (purple), and transformer primary current (green) at 400 W load, 100V input, 20 V output               |

| Figure 70. Dead time controller current flow from source node into C <sub>DA</sub> , circled "x" is where signal must be separated by increasing trace impedance                                               |

# **List of Tables**

| Table 1. Common Power Levels for Different DC-DC Converter Topologies [8] $3$                    |

|--------------------------------------------------------------------------------------------------|

| Table 2. Comparison of Rad-Hard and Commercial Power MOSFETs                                     |

| Table 3. High Reliability and Space Hybrid Isolated DC-DC Converters                             |

| Table 4. Commercial Rated Isolated DC-DC Converters                                              |

| Table 5. Radiation Effects between Power eGaN FETS and Power MOSFETs 12                          |

| Table 6. Specifications of Currently available 200V Rad-hard GaN FETs 12                         |

| Table 7. DC-DC Converter Specifications                                                          |

| Table 8. DC-DC Double Ended Topologies Comparison                                                |

| Table 9. Phase Shifted Full Bridge efficiency over frequency at 100 V input, 500W load operation |

| Table 10. Conventional Full Bridge efficiency over frequency at 100 V input, 500W load operation |

| Table 11. Physical Comparison of Output Rectifiers                                               |

| Table 12. Efficiency Comparison of Output Rectifiers                                             |

| Table 13. Commercial GaN Driver versus Rad-hard GaN Driver                                       |

| Table 14. Commercial Parts Used in Prototype and their Space Version Equivalents 29              |

| Table 15. SNC54 Propagation Delays at 5V Logic over -55 C to 125 C Temperature 31                |

| Table 16. Current Sense Transformer Ferrite Core Specifications                                  |

| Table 17. Current Sense Transformer Specifications                                               |

| Table 18. Pulse Transformer Ferrite Core Specifications                                          |

| Table 19. Calculated Pulse Transformer Parameters                                                |

| Table 20. FBG20N18B 200 V, 18 A 26 m $\Omega$ Rad-Hard GaN FET Parameters for Full Bridge Stage  |

| Table 21. FBG20N18B 200 V, 18 A 26 m $\Omega$ Rad-Hard GaN FET Parameters for Rectifier Stage    |

| Table 22. Output Inductor Specifications                                                     |

|----------------------------------------------------------------------------------------------|

| Table 23. Transformer Design Specifications                                                  |

| Table 24. RMS Currents calculated for Power Loss Analysis                                    |

| Table 25. Power Loss Breakdown at 100 V Input, 20 V Output, 500 W Load 8                     |

| Table 26. Power loss analysis validation, results from SPICE simulation                      |

| Table 27. Pulse Transformer Characterization with Impedance Analyzer                         |

| Table 28. Summary of Transformer Evaluation                                                  |

| Table 29. Summary of External Resonant Inductor Evaluation at 400 W, 100 V input, 2 V output |

| Table 30. Collection of Practical Circuits                                                   |

# **Chapter 1 Introduction**

# 1.1. Background

Power converters in high reliability space or military applications usually trail their commercial counter parts in terms of power density and efficiency. For space applications, there are two important factors affecting performance and power density of DC-DC converters. The first factor is related to the mission critical nature of space power converters, which favors the use of field-demonstrated isolated topologies such as the Forward and Flyback DC-DC converters [1-4]. The Forward and Flyback DC-DC converters operate with a single semiconductor switch on the primary side connecting an impedance (inductance) between the DC Bus and ground as shown in Figure 1. These two single ended converters are favored in space applications because a direct path from the DC Bus to ground cannot be formed during transient fault conditions generated by the single events effects (SEE) in [5, 6] impacting the primary side transistor. In addition, Flyback and Forward converters have simple transistor gate drive timing requirements with low side primary gate drive and easy implementation of low-side transistor gate drive for synchronous rectification.

However, isolated single ended topologies like the Forward and Flyback converters operate their transformer only in one quadrant of the magnetic B-H curve as shown in Figure 1. This results in suboptimal magnetic core utilization, which makes the Flyback and Forward converters less suited at power levels above 100 W and 300 W, respectively [7, 8]. Nevertheless, to overcome the power limits of single ended topologies in space applications demanding power in the kilo-watt range, Forward converters are used in paralleled or in multiphase arrangements in many cases at the expense of system efficiency and power density.

Figure 1. Common single ended isolated topologies used in space converters

Table 1 summarizes different power converter topologies in relation to the power levels at which they are traditionally used [7, 8]. For isolated converters delivering over 300 W, double-ended topologies such as push-pull, half-bridge, and full bridge converters are better suited. Double-ended converters use transformers more efficiently by allowing transformer operation over two quadrants in the magnetic hysteresis B-H curve as shown in Figure 2. The push-pull converter has a simple low-side power MOSFET gate drive; however, it requires two windings in the transformer primary side which over complicates its transformer design. In addition, the voltage stress in the primary side switches is two times the input voltage  $V_{\rm IN}$ .

On the other hand, the half bridge and full bridge converters have better transformer window area utilization with only one primary winding required. In addition, the voltage stress on the primary side switches typically does not exceed the input DC voltage  $V_{\rm IN}$ . For these two reasons, the half bridge and full bridge converters can yield better efficiency and power density than a push pull converter. Furthermore, implementing zero voltage switching (ZVS) schemes allow the half bridge and full bridge converters to achieve very high efficiencies, power density,

and reduced electromagnetic interference (EMI). However, the benefits of half bridge and full bridge converters come at the expense of complex transistor gate drive requirements involving high side and low side gate driver design and accurate gate control timing between all switches to avoid shoot-through failures.

Table 1. Common Power Levels for Different DC-DC Converter Topologies [8]

| Topology             | Power Range    | Transformer<br>Utilization | Active<br>Switches | Switch Voltage Stress                      |

|----------------------|----------------|----------------------------|--------------------|--------------------------------------------|

| Flyback              | ≤ 100 W        | Single Ended               | 1                  | $V_{IN} + N_{PS} \bullet V_{OUT}$          |

| Forward              | 50 W to 200 W  | Single Ended               | 1                  | $V_{IN} / (1-D) = 2 \cdot V_{IN} @ D=50\%$ |

| Active-Clamp Forward | 50 W to 300 W  | Semi-Double Ended          | 2                  | $V_{IN} / (1-D)$                           |

| Push-Pull            | 100 W to 500 W | Double Ended               | 2                  | 2 • V <sub>IN</sub>                        |

| Half Bridge          | 100 W to 500 W | Double Ended               | 2                  | $V_{IN}/2$                                 |

| Full Bridge          | ≥ 500 W        | Double Ended               | 4                  | $V_{ m IN}$                                |

Figure 2. Common double ended isolated topologies

Even with proper gate driver design, radiation exposure in space can still cause the top and bottom switches in a half bridge or full bridge converters to falsely turn ON simultaneously resulting in shoot-through current and possibly catastrophic converter failure. For this reason, the implementation of the half bridge and full bridge converters for space applications becomes even more complex than what is normally encountered in commercial applications once radiation effects and failure modes encountered in space are considered.

Power Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) are the second factor limiting performance and power density of space rated DC-DC converters. Power MOSFETs are very susceptible to damage and degradation from irradiation found in space, in special to ionizing radiation [6, 9, 10, 11]. Achieving radiation tolerance in power MOSFETs results in larger and less efficient devices [12, 13]. Radiation hardened power MOSFETs are also more expensive due to the extensive screening and qualification testing required. The next sections describe the main factors that make radiation-hardened power MOSFETs—and in turn space rated power converters—inferior in size and performance than their commercial equivalents.

# 1.2. Radiation Effects on Power Converters and Power MOSFETS

Radiation effects in microelectronics are classified according to irradiation types, with Single Event Effects (SEE), Total Ionizing Dose (TID) and Displacement Damage Dose (DDD) [5, 6, 9, 10] being the most relevant to space power converter applications. Radiation effects in electronic circuits are caused by heavy particles (protons, neutrons, ions) traveling through the microelectronic device atomic structure. In power converters, these charged particles can cause intrinsic p-n junctions to conduct inside power MOSFETs. They can also cause structural changes to the lattice of power MOSFETs resulting in electrical performance degradation [5]. In addition,

these particles can create electrical energy spikes at the input and outputs of power management and protection electronic circuits in power converters, which also adversely affects converter performance.

### 1.2.1. Single Event Effects

Catastrophic damage from SEE in power MOSFETs mainly take the form of Single Event Gate Rupture and Single Event Burnout. In Single Event Gate Rupture (SEGR), a heavy particle strikes the power MOSFET and punctures the device's gate-oxide layer. This causes the gate electrode to fuse producing a conductive path through the gate oxide of the MOSFET or any MOS type of device (e.g. CMOS or BiCMOS based microelectronics) [5]. The fact that power MOSFETs are more susceptible to SEE in their OFF state—when they are blocking a high voltage—exacerbates the effects of SEGR. Increasing the gate-oxide thickness and de-rating the voltage applied to power MOSFETs reduces its susceptibility to SEGR [5, 6, 14]. This results in larger power MOSFETs, which in turn have larger parasitic capacitances and ON-state resistance (R<sub>DSON</sub>) than a power MOSET used in a commercial application. The higher figure of merit (FOM) due to high input capacitance and R<sub>DSON</sub> negatively affect radiation hardened (rad-hard) power MOSFET's performance.

Furthermore, SEE from heavy ion radiation in power MOSFETs create current pockets that can result in turn ON of the parasitic bipolar junction transistor (BJT) inside the device. This creates a direct conductive path from drain to source in the power MOSFET causing destructive failure known as Single Event Burnout (SEB) [5, 14]. SEB is more frequent in N-channel power MOSFETs [5, 14], which are the heart of the majority of power converters for space. The parasitic BJT in an N-MOSFET is an NPN BJT device. This NPN BJT has higher current gain than its PNP BJT counterpart found in P-channel power MOSFETs. The higher current gain in a NPN BJT

means that very little base current from SEE is needed to turn on the parasitic BJT, resulting in SEB destructive failure of the MOSFET [5, 6, 14, 15].

On the other hand, non-destructive radiation effects in power converters due to SEE usually come in the form of Single Event Transients (SET). SET happen as charged particles strike microelectronics causing electric spikes at the inputs or outputs of electronic circuits [5, 6]. In power converters, SET can result in false triggering of comparators and operational amplifiers used in power converter telemetry and fault protection circuits. In addition, Single Event Transients can cause false triggering of gate control signals of power MOSFETs. Usually, only additional filtering and bigger decoupling capacitance are used to reduce the effects of SET in power converter circuits.

# 1.2.2. Total Ionizing Dose and Displacement Damage Dose

Total Ionizing Dose (TID) refers to cumulative long term effects of ionizing radiation in microelectronics. Radiation in space can cause charged particles to deposit in the oxide layers of microelectronic devices and accumulate over time. TID mainly affects devices with Silicon Dioxide (SiO<sub>2</sub>) insulators such as the metal-oxide layers found in CMOS circuits and MOSFETs. BJTs are less susceptible to TID because they usually do not contain gate oxides. Therefore, TID is usually not a pronounced problem for BJT based circuits [5, 6, 14]. The main manifestation of TID in BJTs circuits come from devices using oxide isolation layers where charge trapping can affect minority carriers in the base. This results in reduced current gain, i.e. more base current injection required for the same collector current [5].

The effects of TID in power MOSFETs are due to trapped charge build-up causing lattice and oxide layer defects that result in changes in the power MOSFET threshold voltage [6]. Charge entrapment from TID cause N-MOSFETs threshold voltage to lower, making them harder to turn

OFF. Therefore, TID results in higher leakage current in N-MOSFETs. On other the hand, charge entrapment has the opposite effect in P-MOSFETs, resulting in harder to turn ON devices [5, 9, 14]. N-Type power MOSFETs are the workhorse of power converters, and TID has the potential of causing catastrophic converter damage if the power MOSFET device turns ON inadvertently from the altered threshold voltage level. TID mitigation involves reducing the oxide layer size in power MOSFETs [5, 14]. Thus, SEGR and TID robustness require a trade-off of gate oxide size to make power MOSFETs more robust to both type of radiation effects.

Displacement Damage Dose (DDD) radiation is due to heavy particles shifting atoms in the Silicon semiconductor lattice and altering the material's charge carrier concentrations [5, 6]. DDD usually affects minority carrier concentrations in semiconductors and reduce carrier mobility [5, 6]. BJTs use both minority and majority carriers (i.e. bipolar carrier conduction) for proper operation. BJT based analog circuits and BiCMOS (Bipolar and CMOS transistors) circuits will suffer degradation from DDD. Structural lattice damage from DDD in BJTs traps minority carriers, and in the same manner as TID, it results in reduced BJT current gain [5]. When selecting bandgap references, operational amplifiers, and comparators for peripheral circuitry in power converter applications, consideration of TID and DDD radiation effects is important. Changes in offset voltages and currents, bias currents, open loop voltage gain, and device saturation voltages are the main manifestation of performance degradation under radiation doses in BJT circuits [5]. Worstcase and tolerance sensitivity analysis via SPICE simulation are common methods to determine performance degradation of BJT circuits due to radiation effects. Power MOSFETs, unlike BJTs, are unipolar (i.e. only majority carrier) devices. Therefore, Displacement Damage Dose effects do not adversely affect power MOSFETs significantly [6, 9].

# 1.3. Commercial and Radiation Hardened Power MOSFETS

Radiation hardened Silicon (Si) MOSFETs are expensive due to the longer engineering development cycles, low quantities produced, and extensive qualification testing they require. Rad-hard power MOSFETs are also bulkier due to the structural changes required for reliable operation under radiation, which results in a high FOM and reduction of space power converter performance. Comparing the datasheet of a 300 kRad (Si) rad-hard power N-MOSFET to a similar commercial power N-MOSFET, the differences in performance, size, and cost are evident. For instance, the IRHNA67260 is a 300 kRad (Si) N-MOSFET from International Rectifier rated for 200V drain-source voltage (V<sub>DS</sub>). This device has a room ambient R<sub>DSON</sub> of 28mΩ at a 40 A test drain current, I<sub>D</sub>. This device is available in a surface mount (SMT) SMD-2 package with dimensions of 13.56 mm x 17.65 mm, and height of 3.58 mm [16]. Cost information for the IRHNA67260 is not easily obtainable, but the cost of a similar 200V rad-hard power MOSFET, the JANSF2N7269U from Microsemi, is \$570 per piece for a quantity of 50 order [17].

For a one-to-one comparison with a commercial device, Infineon's IRFS4227TRL and Toshiba's TPH2900ENH can be studied [18, 19]. Both of these N-MOFETS have  $R_{DSON}$  values from 26 m $\Omega$  to 29 m $\Omega$ , with 200V rated  $V_{DS}$  and 33 A to 62 A of rated current. Their cost is around \$2.81 per piece for a quantity of 50 order. Deviating from a one-to-one comparison, superior commercial MOSFETs with 200 V  $V_{DS}$  are available, such as Infineon's IPT111N20NFD [20] with an  $R_{DSON}$  of 11 m $\Omega$  and costing around \$7.78 per piece on a quantity of 50 order. These commercial N-MOSFET are not only cheaper and smaller, the all have better figure of merit than the rad-hard N-MOSFET from Microsemi and International Rectifier, as summarized in Table 2.

Table 2. Comparison of Rad-Hard and Commercial Power MOSFETs

| Part Number              | JANSF2N7269            | IRHNA67260                 | IRFS4227TRL           | TPH2900ENH            | IPT111N20NFD        |

|--------------------------|------------------------|----------------------------|-----------------------|-----------------------|---------------------|

| Manufacturer             | Microsemi              | International<br>Rectifier | Infineon              | Toshiba               | Infineon            |

| Type                     | Rad-hard               | Rad-Hard                   | Commercial            | Commercial            | Commercial          |

| R <sub>DSON</sub> (25°C) | $100~\mathrm{m}\Omega$ | 28 mΩ                      | $26~\mathrm{m}\Omega$ | $29~\mathrm{m}\Omega$ | 11 mΩ               |

| Maximum Q <sub>G</sub>   | 170 nC                 | 240 nC                     | 98 nC                 | 22 nC                 | 87 nC               |

| FOM                      | 17 n                   | 6.72 n                     | 2.55 n                | 0.64 n                | 0.96 n              |

| $V_{DS}$                 | 200 V                  | 200 V                      | 200 V                 | 200 V                 | 200 V               |

| $I_{D}(100^{\circ}C)$    | 16.0 A                 | 56.0 A                     | 62.0 A                | 33.0 A                | 96.0 A              |

|                          | 11.5 mm                | 13.56 mm                   | 10.67 mm              | 5.2 mm                | 10.1 mm             |

| Package Size             | X                      | X                          | X                     | X                     | X                   |

|                          | 16 mm                  | 17.65 mm                   | 15.88 mm              | 6.3 mm                | 11.88 mm            |

| Height                   | 3.6 mm                 | 3.58 mm                    | 4.83 mm               | 1 mm                  | 2.4 mm              |

| Package Type             | SMD-1                  | SMD-2                      | D2Pak                 | 8-PowerVDFN           | PG-HSOF-8           |

| Volume                   | 663 mm <sup>3</sup>    | 856.8 mm <sup>3</sup>      | 818.4 mm <sup>3</sup> | 32.76 mm <sup>3</sup> | 288 mm <sup>3</sup> |

| Price (50 qty.)          | \$570                  | ~\$570                     | \$2.88                | \$2.51                | \$7.78              |

To illustrate the differences in performance and power density between space-rated DC-DC converters and their commercial counterparts, state of the art high-reliability (HI-REL) and space hybrid isolated converters rated for 5.0 V outputs at 100 W are compared against similar commercial offerings. HI-REL converters from VPT, Inc. achieve 90% efficiency with 3.6 kW/L power density, while a space hybrid only gets to about 78% efficiency at 4.0 kW/L power density [1, 2]. In contrast, commercial DC-DC converters from Murata and Artesyn with similar specifications achieve 93% and 92% efficiencies, respectively. These two commercial rated DC-DC converters also have higher power densities than their HI-REL and space counter parts, achieving power densities from 4.4 kW/L to 4.8 kW/L [21, 22].

Power density in this thesis is defined as not only the power stage but the complete DC-DC power module solution that includes internal housekeeping power supplies, controller, gate drivers, fault protection and other periphery circuitry unless stated otherwise. Table 3 and Table 4 summarize the specifications and power densities for the HI-REL, space, and commercial DC-DC converter modules described in this section.

Table 3. High Reliability and Space Hybrid Isolated DC-DC Converters

| Part Number        | VHR100+2805S                           | SVRFL2805S                       |  |

|--------------------|----------------------------------------|----------------------------------|--|

| Manufacturer       | VPT                                    | VPT                              |  |

| Type               | HI-REL                                 | Space, Hybrid                    |  |

| Input Range        | 16 V to 40 V                           | 18 V to 40 V                     |  |

| Nominal Input      | 28 V                                   | 28 V                             |  |

| Output Voltage     | 5 V                                    | 5 V                              |  |

| Typical Efficiency | 90%                                    | 78%                              |  |

| Output Power       | 100 W                                  | 100 W                            |  |

| Power Density      | $3.6 \text{ kW/L} (59 \text{ W/in}^3)$ | 4.0 kW/L (65 W/in <sup>3</sup> ) |  |

Table 4. Commercial Rated Isolated DC-DC Converters

| Part Number        | AVQ100-24S05                     | UVQ-5/20-D24P                    |

|--------------------|----------------------------------|----------------------------------|

| Manufacturer       | Artesyn                          | Murata                           |

| Type               | COTS                             | COTS                             |

| Input Range        | 18 V to 36 V                     | 18 V to 36 V                     |

| Nominal Input      | 24 V                             | 24 V                             |

| Output Voltage     | 5 V                              | 5 V                              |

| Typical Efficiency | 93%                              | 92%                              |

| Output Power       | 100 W                            | 100 W                            |

| Power Density      | 4.8 kW/L (79 W/in <sup>3</sup> ) | 4.4 kW/L (72 W/in <sup>3</sup> ) |

### 1.4. Benefits of Radiation Hardened GaN FETs

GaN FETs do not have many of the design challenges encountered in producing reliable rad-hard power MOSFETs. In recent years, radiation testing results show that the Enhancement mode GaN FETs, also known as high electron mobility transistors (HEMTs), are very tolerant to radiation environments found in space [23-28]. This is due to the strong atomic bond of the Gallium Nitride binary compound [27, 28], as well as the physical structure of enhancement mode GaN FETs (eGaN FETs).

Enhancement mode GaN FETs were tested in [24, 29] for SEE and total dose. SEE results from [24] show that many first-generation eGaN FETs from EPC mostly operated within their datasheet limits, with a few exceptions where the drain-source leakage increased or the devices catastrophically failed. In general, early radiation testing results for first-generation commercial

eGaN FETs from EPC demonstrated more robustness to SEE than their rad-hard power MOSFETs counter parts [24]. In addition, second-generation EPC eGaN FETs demonstrated higher SEE radiation robustness with no SEGR failures occurring, but with SEB occurring at voltages close to the device's drain-source ratings [29].

In addition, eGaN FETs are very robust to ionizing radiation due to the lack of a metal-oxide layer, which mitigates charge entrapment issues from TID in high radiation environments [24], [26]. Early radiation testing performed in first generation eGaN FETs from EPC showed less than 4% threshold voltage (V<sub>TH</sub>) variation and less than 3% R<sub>DSON</sub> changes with 5 V applied to the gate while exposed to 500 kRad (Si) ionizing doses. With the devices in the OFF stage, higher variation was reported (18% V<sub>TH</sub>, and 8% R<sub>DSON</sub> variation) [24]. Second-generation eGaN FETs from EPC showed no performance degradation from TID up to 1.0 MRad (Si) [29].

Accordingly, DC-DC converters using eGaN FETs have demonstrated superior power density and efficiency compared to power converters that use rad-hard power MOSFETs when exposed to similar doses of radiation [30]. Table 5 shows a brief comparison between power eGaN FETs and power MOSFETs under the most common types of radiation described in this thesis and obtained from [23, 24, 26].

Table 5. Radiation Effects between Power eGaN FETS and Power MOSFETs

| Radiation Type       | MOSFET                                                                                    | eGaN FET                                                                                              |  |

|----------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|

| Total Ionizing Dose  | Atomic change in lattice:                                                                 | Strong bond, reinjection of carriers from AlGaN/GaN interface                                         |  |

| And                  | Carrier concentration altered                                                             | • Carrier concentration in 2DEG less affected                                                         |  |

| Displacement Damage  | Metal Oxide layer traps charge:  • Threshold voltage changes                              | Field Effect Transistor:  • No oxide layer to trap charge                                             |  |

| Single Event Effects | SE Gate Rupture (SEGR)  • Catastrophic failure  SE Burn Out (SEB)  • Catastrophic failure | SE Gate Rupture (SEGR)  • No Catastrophic failure observed  SE Burn Out (SEB)  • Catastrophic failure |  |

|                      | Bulkier die to meet tolerance levels                                                      | Almost no die change, mainly packaging                                                                |  |

| Conclusion           | Very susceptible to radiation                                                             | Very tolerant to radiation                                                                            |  |

|                      | High FOM: low performance                                                                 | Low FOM: good performance                                                                             |  |

There are currently two commercially available rad-hard enhancement mode GaN FET alternatives to 200 V rad-hard MOSFETs. One is the FBG20N18B from Freebird Semiconductor, and the other is the newly released ISL70024SEH from Intersil. Table 6 shows the main electrical and physical characteristics of these two rad-hard eGaN FETs [31, 32].

Table 6. Specifications of Currently available 200V Rad-hard GaN FETs

| Part Number            | FBG20N18B              | ISL70024SEH        |

|------------------------|------------------------|--------------------|

| Manufacturer           | Freebird Semiconductor | Intersil           |

| Total Dose             | 300 kRad(Si)           | 100 kRad(Si)       |

| Maximum RDSON          | $26~\mathrm{m}\Omega$  | 45 mΩ              |

| Maximum QG             | 6.0 nC                 | 6.0 nC             |

| FOM                    | 0.156 n                | 0.270 n            |

| $V_{DS}$               | 200 V                  | 200 V              |

| I <sub>DS</sub> (25°C) | 18.0 A                 | 7.5 A              |

| Package Size           | 3.8 mm x 5.6 mm        | 4.83 mm x 9.13 mm  |

| Height                 | 2.3 mm                 | 2.02 mm            |

| Volume                 | 49 mm <sup>3</sup>     | 89 mm <sup>3</sup> |

The FBG20N18B and ISL70024SEH rad-hard GaN FETs electrical parameters shown in Table 6 are greatly superior to the IRHNA67260 rad-hard MOSFET from International rectifier summarized in Table 2. In fact, the FOMs for both rad-hard GaN FETs are better than the FOMs

of the commercial MOSFET devices from Toshiba and Infineon as outlined in Table 2. Moreover, The FBG20N18B and ISL70024SEH rad-hard GaN FETs are also smaller by a factor of 7 to 10 compared to the rad-hard N-MOSFET from International Rectifier. GaN FETs performance under high radiation as described earlier, besides the benefits that GaN FETs offers in terms of FOM and power density compared to power MOSFETs, makes recently released rad-hard GaN FETS a very attractive replacement for rad-hard MOSFETs. Figure 3 and Figure 4 show the physical packages for the 200 V rad-hard eGaN FETs from Freebird and Infineon presented in this section.

Figure 3. Freebird Semiconductor FBG20N18B, 200V, 26 mΩ rad-hard GaN FET next to an SO-8 IC package

Figure 4. Intersil ISL70024SEH, 200V, 45 mΩ rad-hard GaN FET [32]

# 1.5. Research Scope and Objectives

The principal objective of this work is to validate Freebird Semiconductor's FBG20N18B rad-hard GaN FETs in the Phase Shifted Full Bridge topology while achieving a design with high efficiency and power density. The secondary objective is to understand the implications of achieving a practical design of a Phase Shifted Full Bridge DC-DC converter bounded by design

constraints found in space applications. In addition, the converter built in this work shall transition effortlessly into a version with space rated components for further rad-hard qualification testing of the topology. For this, however, the converter designed in this work might require additional circuitry to ensure proper fault protection and fault recovery management. Performance verification the converter under radiation and across temperature is outside the scope of this thesis. Table 7 summarizes the main specifications for the converter implemented in this work.

Table 7. DC-DC Converter Specifications

| Parameter             | Notes/Conditions                                                                                                       | Minimum | Nominal | Maximum                                |

|-----------------------|------------------------------------------------------------------------------------------------------------------------|---------|---------|----------------------------------------|

| Input Voltage         |                                                                                                                        | 95 V    | 100 V   | 120 V                                  |

| Output Voltage        | Adjustable range                                                                                                       | 18 V    | 20 V    | 24 V                                   |

| Output Voltage Ripple | 0.25 % of nominal V <sub>OUT</sub> , peak to peak                                                                      |         |         | 50m V                                  |

| Output Power          |                                                                                                                        |         | 400 W   | 500 W                                  |

| Output Current        | $V_{OUT} \le 18 \text{ V}$                                                                                             |         |         | 22.22 A                                |

|                       | $V_{OUT} \ge 18 \text{ V}$                                                                                             |         |         | P <sub>OUT_MAX</sub> /V <sub>OUT</sub> |

| Switching Frequency   |                                                                                                                        |         | 500 kHz |                                        |

| Efficiency Target     | $V_{IN} = 96.5 \text{ V} - 100.5 \text{ V},$<br>$V_{OUT} = 18 \text{ V},$<br>$P_{OUT} = 300 \text{ W} - 400 \text{ W}$ | 95 %    |         |                                        |

| Ambient Temperature   |                                                                                                                        | -25 °C  | 25 °C   | 100 °C                                 |

| Height                | Design goal                                                                                                            |         |         | 15 mm                                  |

| PCB Area              | ~90.3 cm <sup>2</sup> (14in <sup>2</sup> )                                                                             |         |         | 177 mm x 50 mm                         |

| Load Capacitance      | Extra capacitor added by user at the load                                                                              | 0       |         | 300 μF                                 |

### 1.6. Thesis Outline

Pairing new radiation-hardened GaN FETs with topologies capable of achieve high efficiency and power density by better utilization of magnetics—such is the case in half and full bridge based topologies—can yield significant performance improvements for DC-DC converters in space applications. This work seeks to implement a practical design for a Phase Shifted Full Bridge DC-DC converter for space applications using newly released rad-hard GaN FETs. This thesis describes in detail the design considerations to implement the Phase Shifted Full Bridge DC-

DC converter with a Current Doubler Synchronous Rectifier for space applications. Freebird Semiconductor FBG20N18B 200 V, 18 A, 26 mΩ rad-hard GaN FET was selected for the Full Bridge and synchronous rectifier power stages. Converter topology selection, and in depth description of design considerations specific to space power converter applications are included. In addition, this thesis presents complete power-loss breakdown analysis for the selected topology, as well as final design choices to meet converter specifications. A Phase Shifted Full Bridge DC-DC converter prototype incorporating the design considerations outlined in this work was built and evaluated. In addition, a second converter operating as a conventional hard switched Full Bridge DC-DC converter making use of the same rad-hard GaN FETs and synchronous rectifier power stage was built. The performance of the hard switched Full Bridge DC-DC converter was compared against Phase Shifted Full Bridge design for efficiency and component stress.

Chapter 1 presents a brief introduction to radiation effects in power converters, followed by a comparison between commercial and rad-hard MOSFETs, as well as a comparison between commercial and high-reliability space state of the art DC-DC converter solutions. The potential of rad-hard GaN FETs for space power conversion to increase power density and efficiency for state of the art space power conversion, coupled by the use of double-ended topologies like the Phase Shifted Full Bridge is introduced.

Chapter 2 includes the considerations for topology selection, and it presents justifications for selecting a Phase Shifted Full Bridge on the primary side power stage, and a Current-Doubler synchronous rectifier on the output side power stage.

The first part of Chapter 3 describes in detail the design considerations and circuits solutions to implement a practical Phase Shifted Full Bridge DC-DC converter with a Current Doubler Synchronous rectifier for space applications. In particular, this chapter provides details

about isolated GaN FET gate driver design for the bridge and rectifier stages for soft switched and hard switched operation of full bridge based converters. The second part of this chapter provides details on the process followed to design the Phase Shifted Full Bridge converter. This section also includes a description on magnetics design, as well as power loss and efficiency approximation.

Chapter 4 provides details about the implemented hardware prototypes for the DC-DC converter as well as the gate driver boards for the Phase Shifted Full Bridge and Full Bridge converters. In addition, this chapter describes the design considerations followed for printed circuit board (PCB) layout and routing of the DC-DC converter power stage and sensitive auxiliary circuits, with special focus paid to rad-hard GaN FETs paralleling and GaN FET gate driver PCB layout and routing.

Chapter 5 presents all experimental results. Both soft-switched and hard-switched full bridge DC-DC converters were tested with their respective control loops closed to ensure magnetic devices flux balance and stability over load. Chapter 5 demonstrates gate-driver signal integrity for the phase shift modulated controller and the hard-switched controller boards. Power transformer voltage and current waveforms, gate-source control signals for all rad-hard GaN FETs, and efficiency comparisons between hard-switched and soft switched converters with different magnetics constructions are included in this chapter.

Chapter 6 provides a summary of the design, and includes an overall conclusion from the work conducted in this thesis. This chapter also includes suggestions for potential areas of research building up from this work.

# **Chapter 2 Topology Selection**

# 2.1. Primary Side Power Stage Selection

In this document, *primary side* refers to the input side of a transformer. Table 8 presents a comparison of different options for isolated DC-DC power converters based on the half-bridge and full bridge converter topologies for this application. Any half-bridge based converter topology excite the power transformer to up  $\pm \frac{1}{2}$  the input voltage  $V_{IN}$ . Full bridge based topologies on the other hand excite the power transformer all the way to  $\pm$  the full DC bus  $V_{IN}$ . Therefore, half-bridge based converters have twice the RMS current on the transformer primary side compared to a full bridge based converter. This results in slightly higher efficiency for full bridge based topologies.

Table 8. DC-DC Double Ended Topologies Comparison

| Topology                     | Frequency | Active<br>Switches | Transformer<br>Primary<br>Voltage | Secondary<br>Voltage Stress                    | Operation           |

|------------------------------|-----------|--------------------|-----------------------------------|------------------------------------------------|---------------------|

| Half Bridge                  | Fixed     | 2                  | $\pm V_{IN}/2$                    | $V_{IN}$ / $2N_{PS}$                           | Hard-switched       |

| Asymmetrical<br>Half Bridge  | Fixed     | 2                  | $\pm V_{IN}/2$                    | $V_{OUT}/\left(1-D\right)$ $V_{OUT} \bullet D$ | ZVS, load dependent |

| LLC<br>Half Bridge           | Variable  | 2                  | $\pm V_{IN}/2$                    | 2 • V <sub>OUT</sub>                           | Wide range ZVS      |

| Full Bridge                  | Fixed     | 4                  | $V_{\rm IN}$                      | $V_{IN}$ / $N_{PS}$                            | Hard-switched       |

| Phase Shifted Full<br>Bridge | Fixed     | 4                  | V <sub>IN</sub>                   | V <sub>PRI</sub> / N <sub>PS</sub>             | ZVS, load dependent |

| ZVT<br>Full Bridge           | Fixed     | 4                  | $V_{\rm IN}$                      | $V_{PRI} / N_{PS}$                             | ZVS, load dependent |

There are four main requirements driving topology selection in this work. The first three are the nominal output power requirement of 400 W, maximum input voltage of 120 V, and minimum efficiency of 95 %. To achieve high power density and efficiency, a converter topology capable of achieving ZVS to reduce switching losses due to the 120 V input is preferred. In addition, operating in ZVS reduces EMI of the converter, which is especially important due to the

high dv/dt switching transitions achievable with GaN power devices. The fourth important requirement is fixed-frequency operation. Fixed-frequency pulse-width-modulation (PWM) is favored over frequency modulated control schemes in noise sensitive space and military applications. Power converters are the main source of electromagnetic interference (EMI). In military and space applications, it is important to know at which frequencies power converters are running. This allows synchronization of system's power converters oscillators for EMI reduction, and in addition allows for better optimization of local passive and active filtering at the system components. Managing EMI in military and space applications are key requirements to operate highly sensitive instrumentation and RF power amplifiers in space. For this reason, frequency modulated resonant topologies achieving ZVS DC-DC conversion like the LLC are often not desirable in space or military applications.

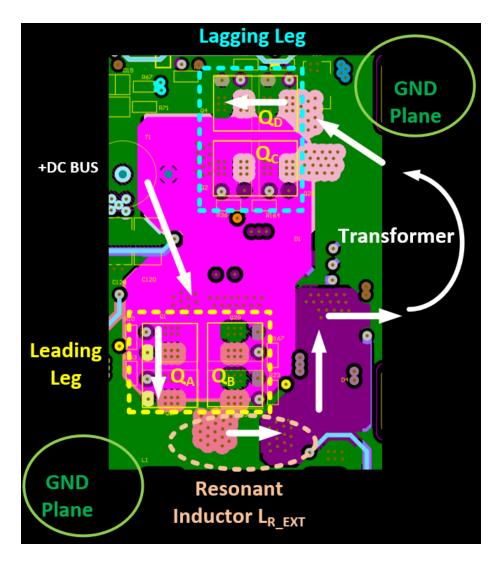

Based on the four main requirements mentioned, the two topologies suited for this application are the Phase Shifted Full Bridge topology and the conventional Full Bridge DC-DC converter topology. The Phase Shifted Full Bridge has the ability to achieve ZVS yielding high efficiency and lower EMI around medium to full load operation while operating with fixed frequency control. In addition, the small output capacitance  $C_{OSS}$  of the selected FBG20N18B radhard GaN FETs reduces the amount of circulating energy needed to achieve ZVS operation in the primary side. The main risk of implementing this topology for space power applications lies in the ability to effectively control dead times of the power transistors in the full bridge and synchronous rectifier stages over temperature and aging. For a Phase Shifted Full Bridge, the dead time between the top and bottom devices shown as  $Q_A$  and  $Q_B$  for one phase leg, and  $Q_C$  and  $Q_D$  for the other, must be accurately maintained over different operating conditions to avoid shoot-through power losses or catastrophic failures depending on the energy stress level.

The risk of shoot-through is lower in a conventional hard-switched full bridge because all the full bridge switches open during the OFF time, which can add robustness in power converter applications for space at the cost of lower efficiency and higher component voltage stress due to higher voltage ringing from increased dv/dt transitions. The Full Bridge converter would also create more EMI, especially if implemented using GaN FETs that have the ability to commutate very fast.

Table 9 and Table 10 present design comparisons between the Phase Shifted Full Bridge and the Full Bridge PWM DC-DC converter as part of topology selection for the primary side. Both converters were simulated at 500 W load, 100 V input, and 20 V outputs with transformer primary to secondary turns ratios set to 1.5 at different switching frequencies. Under the same operating conditions but with switching frequency varied from 200 kHz to 300 kHz, a switching frequency of 250 kHz results in the highest efficiency for the Phase Shifted Full Bridge. On the other hand, a lower switching frequency on the power stage would yield the highest efficiency in the hard switched Full Bridge. This is expected as the switching losses would be much higher in the conventional Full Bridge DC-DC converter. From this comparison, however, the Phase Shifted Full Bridge DC-DC converter running at a 250 kHz transformer switching frequency is the most efficient when compared to the traditional hard switched Full Bridge DC-DC converter under the same operation conditions. This comparison along with the four requirements previously outlined favor the use of the Phase Shifted Full Bridge shown in Figure 5 for this application.

Table 9. Phase Shifted Full Bridge efficiency over frequency at 100 V input, 500W load operation

| Phase Shifted Full Bridge |          |          |          |  |

|---------------------------|----------|----------|----------|--|

| Power Stage Frequency     | 200 kHz  | 250 kHz  | 300 kHz  |  |

| Output Voltage            | 20.62 V  | 20.65 V  | 20.58 V  |  |

| I <sub>IN</sub> RMS       | 6.79 A   | 6.71 A   | 6.66 A   |  |

| I <sub>IN</sub> PEAK      | 12.22 A  | 11.03 A  | 10.56 A  |  |

| I <sub>PRI</sub> RMS      | 8.27 A   | 8.00 A   | 7.79 A   |  |

| I <sub>SEC</sub> RMS      | 12.26 A  | 11.90 A  | 11.60 A  |  |

| P <sub>OUT</sub>          | 493.25 W | 494.84 W | 491.41W  |  |

| P <sub>IN</sub>           | 511 W    | 510.65 W | 511.32 W |  |

| Efficiency                | 96.53%   | 96.90%   | 96.11%   |  |

Table 10. Conventional Full Bridge efficiency over frequency at 100 V input, 500W load operation

| Full Bridge DC-DC Converter |          |          |          |  |

|-----------------------------|----------|----------|----------|--|

| Power Stage Frequency       | 200 kHz  | 250 kHz  | 300 kHz  |  |

| Output Voltage              | 20.73 V  | 20.78 V  | 20.81 V  |  |

| I <sub>IN</sub> RMS         | 7.13 A   | 7.11 A   | 7.25A    |  |

| I <sub>IN</sub> PEAK        | 12.78 A  | 12.33 A  | 12.15 A  |  |

| I <sub>PRI</sub> RMS        | 7.53 A   | 7.5029A  | 7.63 A   |  |

| I <sub>SEC</sub> RMS        | 11.25 A  | 11.219A  | 11.423A  |  |

| P <sub>OUT</sub>            | 498.07 W | 500.17 W | 501.68 W |  |

| $P_{\mathrm{IN}}$           | 517.64 W | 520.31 W | 523.28 W |  |

| Efficiency                  | 96.22%   | 96.13%   | 95.87%   |  |

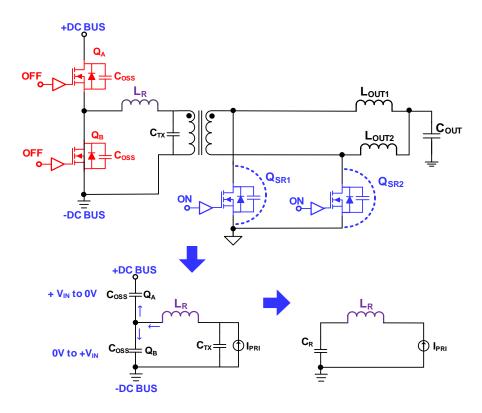

Figure 5. Phase Shifted Full Bridge DC-DC converter with Current Doubler Rectifier

# 2.2. Secondary Side Rectifier Selection

In this document, *secondary side* refers to the output side of a transformer. There are three full-wave rectifier topologies commonly used with double-ended isolated converters. These are the full wave rectifier using a center-tapped transformer secondary, the full bridge rectifier using four switches, and the Current Doubler rectifier. Figure 6 shows these three rectifier topologies shown with diodes for simplicity.

Figure 6. Common output rectifiers for isolated DC-DC converters

Table 11. Physical Comparison of Output Rectifiers

| Туре               | Full Bridge<br>Rectifier | Center-Tapped<br>Full Wave | Current Doubler<br>Rectifier |

|--------------------|--------------------------|----------------------------|------------------------------|

| Secondary Windings | 1                        | 2                          | 1                            |

| Switches           | 4                        | 2                          | 2                            |

| Gate Drive         | High & Low Side          | Low Side                   | Low Side                     |

| Complexity         | High                     | Medium                     | Low                          |

| Inductor           | 1                        | 1                          | 2                            |

| Inductor Current   | $I_{OUT}$                | $I_{OUT}$                  | I <sub>OUT</sub> / 2         |

Table 11 summarizes the key physical differences among the output rectifiers described in this section. Maximum output current, efficiency, and design complexity determined the selection of the output rectifier for the DC-DC converter implemented by this work. Table 12 presents a power loss comparison among all three output rectifiers running with a Phase Shifted Full Bridge converter running a 500 kHz PWM control signal (250 kHz on the power stage) to deliver 500 W at a regulated 20 V output from a 100 V DC input. From this comparison, the Current Doubler rectifier yields the highest efficiency for this application.

Table 12. Efficiency Comparison of Output Rectifiers

|                                      | <b>Current Doubler</b>  | Full Bridge              | Center Tapped            |

|--------------------------------------|-------------------------|--------------------------|--------------------------|

| L <sub>OUT</sub>                     | $6.25~\mu H, 2~m\Omega$ | $3.125 \mu H, 2 m\Omega$ | $3.125~\mu H, 2~m\Omega$ |

| Duty Cycle                           | 0.70                    | 0.73                     | 0.70                     |

| I <sub>OUT</sub> Peak to Peak Ripple | 4.61 A                  | 4.50 A                   | 4.774 A                  |

| P <sub>OUT</sub>                     | 498.98 W                | 492.1 W                  | 499.91 W                 |

| P <sub>IN</sub>                      | 532.76 W                | 561.17 W                 | 536.95 W                 |

| Power Loss                           | 33.78 W                 | 69.07 W                  | 37.04 W                  |

| Efficiency                           | 93.66%                  | 87.69%                   | 93.10%                   |

| Normalization To CDR                 | 1.00                    | 0.94                     | 0.99                     |

The Current Doubler rectifier works similarly to a 2-phase Buck converter. It splits the load current into two inductors, which reduces the size and conduction losses of the output filter. The combined current at the output is two times the transformer switching frequency ( $F_{SW}$ ), and the multi-phase behavior of the rectifier provides output ripple current cancellation. This results in a smaller RMS current stress in output capacitors, and reduces the amount of output filtering capacitance  $C_{OUT}$  required. Another advantage of the Current Doubler rectifier is that it requires a single secondary winding on the transformer. This reduces complexity and allows for better optimization of the power transformer. In addition, synchronous rectification can be implemented with low side (ground referenced) gate drive control signals, which reduces gate drive circuit complexity. Therefore, to reduce complexity of the gate control scheme for the synchronous