# The Design of the Node for the Single Chip Message Passing (SCMP) Parallel Computer

by

Mark Bucciero

Thesis submitted to the faculty of the Virginia Polytechnic Institute and State University in a partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE

in

**Computer Engineering**

James M. Baker, Chairman Jim Armstrong Thomas Martin

March 23, 2004

Blacksburg, Virginia

Keywords: Processor, parallel, node, system on chip, single chip computer, SCMP

Copyright 2004, Mark Bucciero

#### The Design of the Node for the Single Chip Message Passing (SCMP) Parallel Computer

Mark Bucciero

James M. Baker, PhD, committee chair

Bradley Department of Electrical and Computer Engineering

#### Abstract

Current processor designs use additional transistors to add functionality that improves performance. These features tend to exploit instruction level parallelism. However, a point of diminishing returns has been reached in this effort. Instead, these additional transistors could be used to take advantage of thread level parallelism (TLP). This type of parallelism focuses on hundreds of instructions, rather than single instructions, executing in parallel. Additionally, as transistor sizes shrink, the wires on a chip become thinner. Fabricating a thinner wire means increasing the resistance and thus, the latency of that wire. In fact, in the near future, a signal may not reach a portion of the chip in a single clock cycle. So, in future designs, it will be important to limit the length of the wires on a chip.

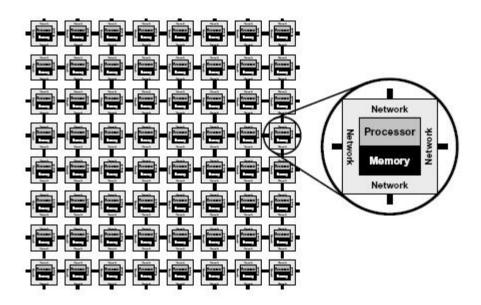

The SCMP parallel computer is a new architecture that is made up of small processing elements, called nodes, which are connected in a 2-D mesh with nearest neighbor connections. Nodes communicate with one another, via message passing, through a network, which uses dimension order worm-hole routing. To support TLP, each node is capable of supporting multiple threads, which execute in a non-preemptive round robin manner. The wire lengths of this system are limited since a node is only connected to its nearest neighbors.

This paper focuses on the System C hardware design of the node that gets replicated across the chip. The result is a node implementation that can be used to create a hardware model of the SCMP parallel computer.

# Acknowledgements

An extra special thanks goes to Dr. James M. Baker and his family. Dr. Baker, you always gave me the freedom to work on what I wanted, when I wanted. This approach taught me to become self motivated in my work. It may have taken me a little longer to realize what was happening, but I do appreciate your style and patience. You always listened to my research opinions, good or bad. We talked about them, and you always made sure I understood what I had not considered. Thanks for always inviting me and whomever I wanted to bring to tailgate with you before football games. The food and company was always outstanding.

To all those who have worked on or are currently are working on the SCMP project, thank you for keeping me in the loop and making sure I was thinking about all aspects of the problem, rather than just my own.

Thanks to Brian Gold for not being shy about telling me what I did wrong. I am a much humbler person having worked with you. I always enjoyed our days working and our nights out.

To Alicia Petta for always being supportive of my work/life and empathetic about my complaining even when I did not work enough to complain about it. You always make me think about things other than work, and make sure I keep the big picture in mind.

I would like to thank Alison Lazarevich for her listening ear and constant encouragement. You inspire me to be more than I think I can be.

Special thanks go to Michael Carr for keeping me sane and always making the time for video games. I feel better knowing there is someone out there with similar problems to mine.

Thanks to Marie Dotson for her constant friendship and loving me just the way I am. My college years would not have been nearly as good without you.

To my mother, for making me feel special no matter what she had going on in her life. To my father, for his constant wisdom and for reading the technical babble that follows. Thanks to Paul and Sarah for always making sure I sharpen the saw by attending their holiday parties.

# **Table of Contents**

| Acknowledgements                                                                                               | <i>iii</i>     |

|----------------------------------------------------------------------------------------------------------------|----------------|

| Table of Contents                                                                                              | iv             |

| Table of Figures                                                                                               | v              |

| Table of Tables                                                                                                | vi             |

| Chapter 1 Introduction                                                                                         | 1              |

| 1.1 Motivation         1.2 Overview of SCMP         1.3 Significance of Thesis         1.4 Thesis Organization |                |

| Chapter 2 The SCMP Node                                                                                        | 5              |

| 2.1 Description         2.2 Hardware Partitioning         2.3 Instruction Set                                  | 9              |

| Chapter 3 Hardware Implementation                                                                              | 14             |

| <ul> <li>3.1 Memory</li> <li>3.2 Memory Controller</li> <li>3.3 Instruction Cache</li></ul>                    |                |

| Chapter 4 Contexts and Context Management                                                                      | 25             |

| <ul> <li>4.1 Shared Hardware</li> <li>4.2 Context Management Table and Control</li></ul>                       | <b> 26</b><br> |

| Chapter 5 Additions to the Basic SCMP Node                                                                     | 39             |

| 5.1 Floating Point Support<br>5.2 Exception Handling                                                           |                |

| Chapter 6 Software Support and Simulation                                                                      | 47             |

| 6.1 Hardware Simulation of the Block of the SCMP Node<br>6.2 Results                                           |                |

| Chapter 7 Summary and Future Work                                                                              | 52             |

| 7.1 Summary<br>7.2 Future Work                                                                                 |                |

| References                                                                                                     | 56             |

| Appendix A The SCMP Instruction Set Architecture                                                               | 58             |

| Vita                                                                                                           | 60             |

# Table of Figures

| Figure 1.1: The SCMP parallel computer connects nodes in a 2-D mesh with nearest                                                       |    |

|----------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                                                        | 3  |

| Figure 2.1: The bold wires show the additional wires needed and the longest wire lengt                                                 |    |

| added in a shared memory system.                                                                                                       | 5  |

| Figure 2.2: Images (a), (b), and (c) show the different parts of a message in the SCMP                                                 |    |

|                                                                                                                                        | 6  |

| Figure 2.3: The CMT contains the information needed to determine if a context is read to execute and where that execution should begin |    |

| Figure 2.4: A block diagram of the SCMP node.                                                                                          |    |

| Figure 2.5: The left figure shows how the nodes are numbered on the SCMP parallel                                                      | 10 |

| computer. The right figure depicts how a message would be routed from node 3 t                                                         | 0  |

| node 2                                                                                                                                 |    |

| Figure 3.1: A block diagram of the memory on the SCMP processor                                                                        |    |

| Figure 3.2: A block diagram of the memory controller.                                                                                  |    |

| Figure 3.3: When a read request is made, the acknowledge signal is received on the next                                                |    |

| clock edge. If the acknowledge signal is positive, the actual data is valid two cycl                                                   |    |

| after the request was made                                                                                                             |    |

| Figure 3.4: A block diagram of the instruction cache for the SCMP parallel computer.                                                   |    |

| Figure 3.5: A block diagram of the ALU                                                                                                 |    |

| Figure 3.6: A block diagram of the Network Interface Unit (NIU)                                                                        |    |

| Figure 4.1: A block diagram of the context management scheme                                                                           |    |

| Figure 4.2: A visual representation of a CMT entry                                                                                     |    |

| Figure 4.3: The timing of a context switch.                                                                                            |    |

| Figure 4.4: A block diagram of the CMT & control part of the context management                                                        |    |

| scheme                                                                                                                                 | 28 |

| Figure 4.5: Shows how to find the location of a node on the SCMP parallel computer                                                     | 31 |

| Figure 4.6: The registers of a node are organized in a matrix to allow single cycle                                                    |    |

| accesses                                                                                                                               | 35 |

| Figure 4.7: A block diagram of the Contexts and Control section of the context                                                         |    |

| • •                                                                                                                                    | 36 |

| Figure 5.1: A bit was added to the flits to indicate whether or not floating point data wa                                             | is |

| being used.                                                                                                                            |    |

| Figure 5.2: The bit assignment in the EMASK register                                                                                   | 44 |

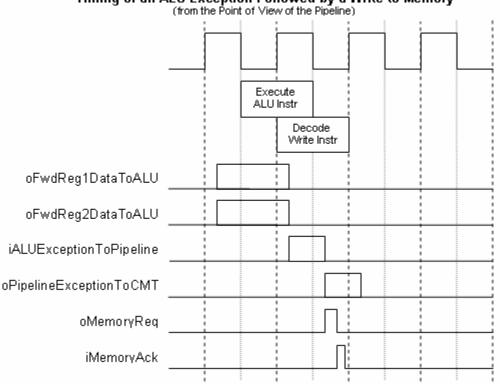

| Figure 5.3: The timing of an exception between the ALU and the pipeline                                                                | 46 |

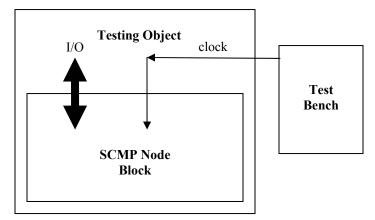

| Figure 6.1: A general case of how individual blocks were tested.                                                                       |    |

| Figure 6.2: A timing diagram from the ALU test bench                                                                                   |    |

| Figure 6.3: A timing diagram of the test for the memory controller.                                                                    | 49 |

# **Table of Tables**

| Table 2.1: The hardware division of an SCMP node.                                       | 9  |

|-----------------------------------------------------------------------------------------|----|

| Table 3.1: The input and output ports and descriptions of the memory block's signals 1  | 5  |

| Table 3.2: The signal names with corresponding descriptions of the memory controller    |    |

| block. The other signals are those of a memory interface (See Chapter 3.1) with the     | e  |

| appropriate naming convention1                                                          | 17 |

| Table 3.3: The signal names and descriptions for the instruction cache block 1          | 9  |

| Table 3.4: Input and output signals for the ALU.    2                                   | 21 |

| Table 3.5: The signal names and descriptions for the NIU of the SCMP node               | 22 |

| Table 4.1: Describes the interface between the CMT and the memory controller            | 29 |

| Table 4.2: Signals that control pipeline accesses to the CMT.       3                   | 30 |

| Table 4.3: A description of the interface between the NIU and the CMT and its control.3 | 52 |

| Table 4.4: Description of the interface between the pipeline and the contexts           | 37 |

| Table 4.5: Description of the interface between the NIU and the contexts                | 38 |

| Table 5.1: Exceptions handled in the SCMP node.       4                                 | 2  |

| Table 6.1: The program used to test the SCMP node with a portion of its results. (This  |    |

| program was created and tested by Priyadarshini Ramachandran.)                          | ;1 |

|                                                                                         |    |

# Chapter 1 Introduction

Will processor speeds continue to increase with Moore's Law? Will a paradigm shift in processor design be necessary to make full use of shrinking technologies and increasing clock speeds? This thesis presents a portion of a new processor architecture that will hopefully allow processor speeds to continue to increase with Moore's Law.

This thesis begins by discussing the limitations of current processor technology and introduces a new architecture that can work within these limitations, while extending the bounds of processor speeds that can be achieved. The significance of this research and a brief outline of the remainder of this document are also given.

#### 1.1 Motivation

Today's processor designs use reduced transistor sizes to improve processor performance in two ways. First, as the transistor has gotten smaller, its switching speed has increased. Faster switching speeds allow for the same processor design to execute the same program in less time. Second, when a smaller transistor technology is introduced, more transistors can be placed on a die of the same size. In fact, the International Technology Roadmap for Semiconductors (ITRS) estimates that a chip will contain one billion transistors by the year 2007 [1]. These additional transistors are used to add functionality to a design to make a program execute in fewer clock cycles. However, these design techniques cannot continue to improve processor performance at the rate of Moore's law.

With these smaller transistors, the cross sectional area of the wires on a silicon die will be reduced. This thinner wire leads to increased resistance per unit area. One study projects that when transistor technology reaches 70 nm, less than 20% of a chip could be reached in a single clock cycle [2]. Eventually, processor speeds will be determined by the lengths of the wires on the chip and not by the switching speed of a transistor [3].

One effect of making smaller transistors is that a larger number of them can be placed on the same die. Current processor architectures use these extra transistors to add new features to a design. However, the extra logic needed to support the new features tends to use the additional transistors, so the wire lengths still span the entire chip. Thus, a more complex processor design will have wire latency issues in the near future [3][4][5].

The additional transistors on a chip tend to be used to exploit instruction level parallelism (ILP). It makes sense because if more instructions can be executed at once, then the program will execute faster. The additional hardware necessary to increase performance by exploiting ILP creates additional design and test time. The design of a new algorithm to make use of ILP must first be tested on a number of applications to determine its worth. Then, a hardware implementation of that algorithm needs to be developed and tested. Finally, when the new design is fabricated, it must also be tested. The process of creating and testing a new design has shown little improvement in ILP performance for a general application. Thus, the concern is that exploiting ILP has reached a point of diminishing returns [5].

This concern has lead to an increased interest in thread level parallelism (TLP). TLP takes small groups of instructions and executes them in parallel. Therefore, its concept is coarser than ILP, which exploits the finest grain of parallelism, a single instruction. Diefendorff believes that coarser grained parallelism will become the dominant force in microprocessor design [6].

Processor designs of the future will also need to consider the 'Memory Wall' effect [7]. The basic idea is that memory speeds will not continue to increase with processor speeds. Thus, the processor will have to delay for long periods of time during an off chip memory access. One way to counter this effect would be to put all the memory needed by the processor on the chip itself. This configuration would allow the memory speed to be the same as level 1 cache, which is orders of magnitude faster than an off chip memory access.

## 1.2 Overview of SCMP

One possible architecture alternative is the single chip message passing (SCMP) parallel computer. The SCMP architecture supports thread level parallelism and attempts to minimize the length of the wires on the chip [8]. This architecture uses the transistors on the chip to create a number of simple processing elements, called nodes. The individual nodes are small and global signals are avoided to limit the lengths of the wires on the chip. Thus, the clock speed of the SCMP processor can be determined by transistor switching speed rather than the wire latency.

The nodes on the chip exploit TLP and, to keep them simple, provide no support for ILP. Each node can maintain multiple threads, with each thread being on the order of tens to hundreds of instructions. The threads on a node execute in round robin non-preemptive fashion. These threads are used to keep a node busy so context switches occur while one thread is waiting for data. Some multimedia applications, such as videoconferencing, contain enough TLP to use up to 64 nodes for processing [6]. Current parallel architectures cannot efficiently support thread level granularity because of the cost of communication. Also, the uniprocessors used in other parallel architectures were designed to make use of ILP instead of TLP.

Nodes on the chip each have their own local memory to counter the 'Memory Wall' effect [7]. Memory is distributed on the chip to keep the wire lengths as short as possible. When a program is loaded, the same image of that program is copied into the memory on each node. This fact simplified programming for SCMP since one node could write data values to known locations on another node.

The SCMP parallel computer is a message passing system similar to that of the Pica and the J-Machine [9][10]. The nodes on the chip are connected in a 2-D mesh, so each node is connected to its four nearest neighbors. Messages are sent between nodes using dimension order worm-hole routing. Since each node is only connected to its nearest neighbors, the wire lengths on the chip remain short. Thus, communication between nodes can happen in less than one clock cycle. In addition, there is only one physical channel between nodes. Therefore, messages that attempt to use the same physical

channel can be multiplexed over the single link using virtual channels [11]. For more information on the network, see "Balancing Performance, Area, and Power in an On-Chip Network" by Brian Gold [12].

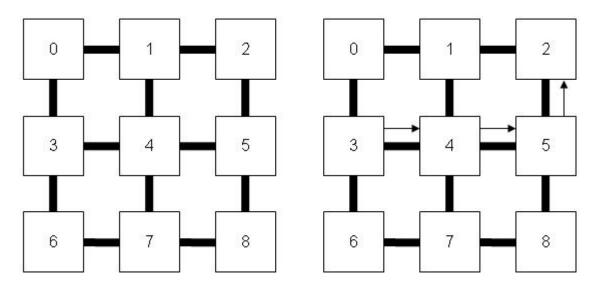

Figure 1.1: The SCMP parallel computer connects nodes in a 2-D mesh with nearest neighbor connections.

## 1.3 Significance of Thesis

The major parts of the SCMP parallel computer are the node that is replicated across the chip and the network that connects the nodes. The crux of this thesis effort was the design and implementation of a single node for the SCMP architecture. Some aspects of the SCMP node were determined before this thesis effort began. These features will be explained later in this document and include: the instruction set, the message format, and the Context Management Table (CMT) format. The goal of this research was to design the node around these requirements and still have the node function properly.

Without nodes, the SCMP chip becomes a network back plane with no computational abilities. The design includes everything from formatting messages for the network, to thread management, to memory access and control. The goal was to create a fully functional 32 bit RISC processor that would fully support all of the needs of the SCMP instruction set.

Currently, the SCMP software simulator assumes a certain number of clock cycles per instruction. Once this work is completed, the simulator can be modified to mimic the actual hardware design. Thus, a clock cycle accurate software simulator would be created. This new simulator could then be used to test a set of benchmarks on the SCMP

parallel processor. These benchmarks were chosen so that the performance of the SCMP processor could be compared to others like it.

## 1.4 Thesis Organization

The requirements for the SCMP node must be defined before its design and implementation can be discussed. Chapter 2 of this thesis gives a detailed description of all of the parts of a node. Chapter 3 presents the implementation of the majority of the SCMP node. Chapter 4 discusses the implementation of the context and context management portion of the node. A full chapter was dedicated to this topic because of its complexity.

After the node was initially designed, some changes in the requirements for the node were identified. The design was changed to include floating point support and exception handling. These changes and their implementation are discussed in Chapter 5.

Once the hardware was designed and implemented, it was necessary to test its functionality. Chapter 6 describes the software used and the hardware simulation support created for a SCMP node. This software includes a test bench that creates a node and a module to load a program into memory and start the simulation. After it completed, the simulation results were verified. Finally, a summation and some possibilities for future work are given in Chapter 7.

## Chapter 2 The SCMP Node

The node that is replicated across the SCMP parallel computer needs to be simple enough so up to 64 nodes can be included on a single chip. Also, the wire lengths need to be short enough so that a node can perform all of its operations in one clock cycle. However, it is complex enough to support thread level parallelism, message passing, and memory management [8]. Since each node also has its own local memory, support is necessary to share data between nodes. To support these extra features, the SCMP node has a unique instruction set (see Chapter 2.3). This chapter describes what is required of an SCMP node and how it was subdivided for hardware development.

## 2.1 Description

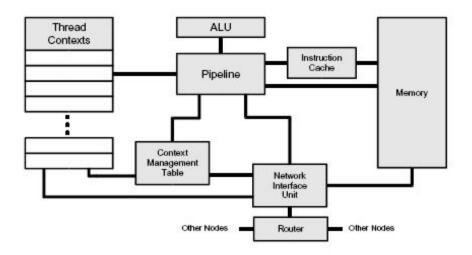

Each node of the SCMP parallel computer acts as a generic processor, so it must be designed to handle any general task. To satisfy this requirement, the node supports all types of operations. These operations include but are not limited to: arithmetic, logic, memory, thread access, thread management, and networking. In addition, a central control unit, in this case a pipeline, is needed to manage all of these operations.

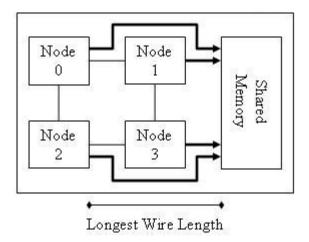

This processor architecture is proposed as a design alternative to combat the problems of wire latencies and unmanageable complexity. In order to minimize the wire latency, global signals are not allowed in the SCMP design. Therefore, the on chip memory must be distributed to each node rather than being shared between nodes, which would require wires to be as long as the chip. Figure 2.1 depicts the shared memory design approach. For example, the IBM Power4 takes this approach to placing two 64 bit nodes on a single chip [13]. Similarly, the MAJC [14], Hydra [15], Blue Gene [16], and CMP [17] architectures also use this configuration.

Figure 2.1: The bold wires show the additional wires needed and the longest wire length added in a shared memory system.

The SCMP parallel computer is a MIMD system because each node can operate independently on its own data stream. Therefore, it is important to have an easy way to share data among the processors on the chip. The SCMP network uses an active message passing scheme. When a message reaches its destination node, it enters through the network interface unit (NIU). The NIU, then, determines the type of message from the information contained in the message header. The incoming message is either a thread message, which creates a new thread to execute, or a data message, which writes directly to memory.

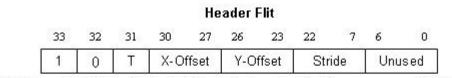

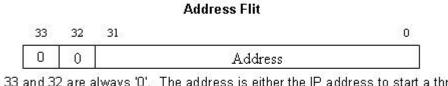

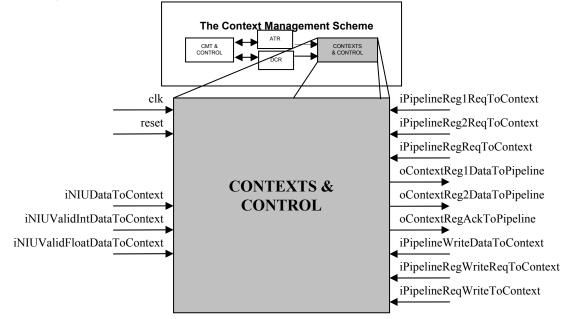

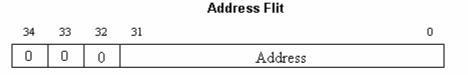

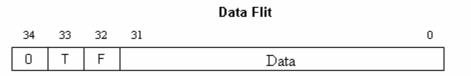

Messages in the SCMP network are sent in small pieces, called flits (<u>fl</u>ow control digits). A message consists of a header flit, an address flit, numerous data flits, and a tail flit. The header flit, shown in Figure 2.2, contains which type of message (thread or data) is being sent; the destination node (given in x and y coordinates); and the bit that signals it is a header flit set to one. In the case of a thread message, the address flit contains the instruction pointer at which a thread is to begin execution. On the other hand, the address flit of a data message contains the memory address at which data will be written. The data for the data flits is generated directly from the registers or from the memory. This method limits the amount of data that is copied when creating a message, which should improve message throughput. There can be any number of data flits following the address flit. The tail flit is the last data flit of a message and is signified by the tail bit being set to one.

(a) Bit 33 is set to '1' to indicate that this is the header flit of the message. Bit 31 is used as the message type ('1' for thread and '0' for data).

(b) Bits 33 and 32 are always '0'. The address is either the IP address to start a thread or a memory location to begin copying.

| 33 | 32 | 31 |      | 0 |

|----|----|----|------|---|

| 0  | 0  |    | Data |   |

(c) Data is sent in these flits. Bit 32 is used to indicate the tail flit. When that bit is set, the message is complete.

Figure 2.2: Images (a), (b), and (c) show the different parts of a message in the SCMP network.

The routing of messages between nodes is done through an on chip router that uses dimension order worm-hole routing. This type of routing means that the header flit makes a path through the network for the rest of the message to follow. In addition, messages are always routed first in the x direction, then in the y direction. Routing messages in this pattern ensures that dead lock will not occur in the network.

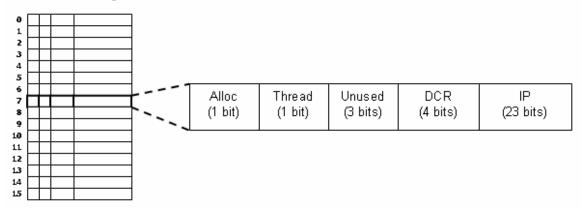

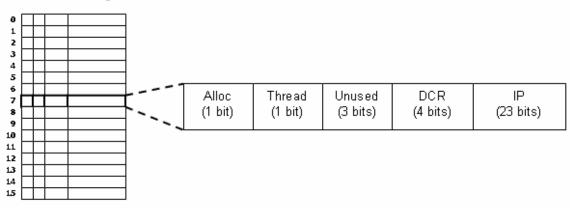

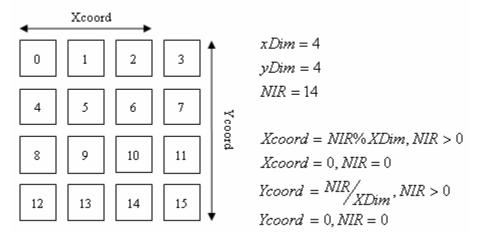

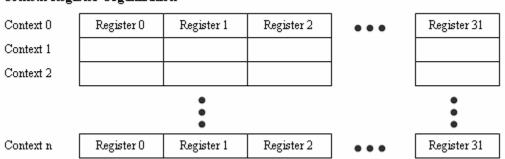

When a thread message arrives at the NIU of a node, a space to store the thread, called a context, is requested. Since the SCMP node is designed to handle multiple threads, there are multiple contexts (currently 16). Each context contains 32 32-bit general purpose registers that are used to store data. The context management table (CMT) keeps track of those contexts that are in use and those that are free. Each CMT entry has four main fields: the Alloc bit – set to one if a context is in use; the Thread bit – set to one if this context was to be scheduled for execution; the Data Context Register (DCR) – an identifier that points to the context that can be used as additional data storage; and the instruction pointer – the memory address for the thread to begin its execution. It is important to note that the IP value in a CMT field is only valid when a thread begins execution or restarts after a suspension. There is an IP register within the node pipeline that keeps track of the actual instruction that is executing. Figure 2.3 depicts a CMT entry with the named fields.

#### Context Management Table

**Figure 2.3**: The CMT contains the information needed to determine if a context is ready to execute and where that execution should begin.

Once a CMT entry is assigned to the incoming message, the address flit value is written to the IP value of the CMT entry. The data flits following the address flit are written directly in to the register block for that context. Therefore, only 32 data values can be sent in a thread message. If more flits are sent, the data values did not have a place to be stored. As a result, if a thread message contains more than 32 data flits, the additional flits are ignored.

A context is scheduled for execution when both its Alloc and Thread bits are set in the CMT entry for that context. Threads are scheduled in round robin non-preemptive

fashion. This type of scheduling ensures that no thread will be starved as long as one of them does not enter an infinite loop. The Active Thread Register (ATR) acts as a pointer in to the CMT for the currently executing context. When a thread ends or suspends, a search occurs for the next thread that is ready to execute. If the thread suspends, the ATR is used to identify which CMT entry should be modified to save the suspended thread information. The IP field of the CMT entry is updated with the address of the instruction that will begin its execution the next time the thread is scheduled.

All of the context switches occur in hardware. This design allows for minimal delay from the end/suspend operation on one context to the start of the next.

Once a thread begins execution, it runs until it either completes or suspends. A thread can be suspended specifically with a suspend instruction or due to failure of an instruction in the pipeline. For example, the send instructions are used to inject messages into the network. If the network buffers are full, then the send instruction fails, and the thread suspends.

When a data message arrives at a node, the address flit contains the first address in memory to which data is written. The appropriate values are extracted from the data flits and written sequentially into memory. This message type is used frequently when large blocks of data need to be transferred from one node to another. Unlike the thread message, the data message type does not have a limitation on the number of data flits that can be sent.

In addition, no memory space on the SCMP node is protected. A careless programmer could easily write into the code space of a program. In this situation, the outcome of the program would be unknown. Therefore, it is very important that space be allocated for the incoming message before it arrives. Since all addresses used are physical addresses, space cannot be dynamically allocated for an incoming message.

Now that the SCMP parallel computer has been described, let us consider other similar projects currently being researched. As previously noted, the SCMP node does not support instruction level parallelism within a thread. The SCMP node is different from the RAW architecture [18], which does support ILP in addition to coarser levels of parallelism. The RAW processor also uses a message passing model between nodes and distributes memory among the nodes. However, only a small amount of memory is included on the chip, so many memory accesses will need to access off chip memory. Therefore, the RAW architecture may still suffer the Memory Wall effect. Also, unlike SCMP, the compiler for the RAW machine is allowed to access some of the hardware features on the chip. This permission allows the compiler to statically schedule certain events. For example, the compiler can insert an instruction to set a switch to allow a certain message to pass through that router.

The focus of the IRAM project [19] is to integrate DRAM on the chip with a single processing element. It is different from SCMP since SCMP uses many processing

elements. However, the IRAM venture is nearly identical to a single SCMP node. The difference is in the network capabilities provided to the SCMP node.

An SMT system [20] uses a different paradigm than the systems described above, but it does exploit thread level parallelism. The chip of an SMT processor contains many functional units. Each thread in the system is given the capability to use as many of these units as possible. In other words, in a given clock cycle, instructions from different threads are executing at the same time in different functional units. This design, however, does not account for either the Memory Wall effect or the wire latency phenomenon expected in smaller transistor technologies.

## 2.2 Hardware Partitioning

This design of an SCMP node lends itself to a hardware partitioning. The partitioning of such a large design effort made it more manageable, since the different parts could be developed, modified, and tested individually. The division was done with the objective of decreasing design time, while increasing design accuracy. A single node of the SCMP parallel computer was divided into the following blocks: ALU, contexts and context management, instruction cache, memory management, network interface unit (NIU), and pipeline. Table 2.1 lists these blocks with a short description of the responsibilities for each unit.

| Block Name                      | Description                                             |  |  |

|---------------------------------|---------------------------------------------------------|--|--|

| Arithmetic Logic Unit (ALU)     | Responsible for calculations, comparisons, and shifting |  |  |

| Contexts and Context Management | Manages the registers and threads running on a given    |  |  |

|                                 | processor                                               |  |  |

| Instruction Cache               | Stores instruction words for faster execution times     |  |  |

| Memory Management               | Controls accesses to the node's local memory            |  |  |

| Network Interface Unit (NIU)    | Injects and ejects messages to and from the network     |  |  |

| Pipeline                        | Acts as the node controller                             |  |  |

**Table 2.1**: The hardware division of an SCMP node.

One major concern about partitioning the hardware design was creating and maintaining the interfaces between the blocks. This concern arose because if one block had its interface changed, the affected block must also change its interface. Therefore, it was of paramount importance to create interfaces that covered the scope of the required operations but allowed the flexibility to add or change the functionality. Creating the interfaces in this way eliminated the above concern because the interfaces were not required to change or accommodate change in the functionality of a block in a node. Figure 2.4 depicts an SCMP node with its interconnections. The connections show which blocks interact with which other blocks but not the actual interface that was developed.

Figure 2.4: A block diagram of the SCMP node.

The pipeline is modeled after the MIPS 32 processor core and consists of five stages: fetch, decode, execute, memory access, and write back. Documentation for this processor family can be found at MIPS Technologies, Inc. [23]. The MIPS pipeline functionality was modified to accept the SCMP instruction set and to control the various blocks of the node.

The interfaces and operations that each block performs are considered the hardware implementation of the node. These descriptions are given in Chapter 3, for the ALU, instruction cache, memory management, NIU, and pipeline. In Chapter 4, the details of the contexts and context management are given. The contexts and CMT are described in a separate chapter because of their complexity. The testing and verification of each block and the complete node are presented in Chapter 6. Please refer to the appropriate chapter for further information

## 2.3 Instruction Set

With the extra hardware support required for the SCMP node, special instructions were needed in the instruction set to make use of these features. The special instructions are discussed here. The full list of instructions is given in Appendix A.

In addition to the NIU, the node pipeline can also manipulate the CMT. The pipeline can perform a memory write to the CMT or use the alloc instruction. A memory write could succeed in allocating a context, but there is a potential conflict if the NIU requests a new context in the same clock cycle. In this case, both the pipeline and the NIU viewed the context as free, and thus both allocate it. Therefore, an instruction, alloc, was required to atomically allocate a context to the pipeline. Using the alloc instruction, if both the pipeline and the NIU request a context in the same cycle, the pipeline would be given priority and succeed, while the NIU request would fail. The alloc instruction is used to set the Alloc bit of a free context to one. The return value of this instruction is a pointer to the CMT entry that has been allocated. This command effectively removes a context from the list of available contexts for use by the NIU or the pipeline. After the alloc instruction succeeds, the user can write to the Thread bit, the DCR, and the IP fields in the CMT entry. The free instruction is used to clear the Alloc bit of the designated CMT entry. However, a thread cannot use the free instruction on its own CMT entry.

If a thread contains an intensive amount of processing, it is able to give up control of the processor and let the other active threads have execution time. The suspend instruction is used to accomplish this operation. Since the contexts are not preemptive, operations are guaranteed to be atomic. Therefore, the suspend instruction also allows for synchronization to take place. For example, let us say a thread is waiting for a memory location to change from zero to one. The value in the designated memory location is accessed and its value checked. If the value is zero, then the thread would use the suspend instruction to allow other threads to execute. The likely case is that one of the other threads will change the value at that memory location to one. Then, when the original thread checked the memory value again, if it changed to one, the thread would continue its execution. If it had not changed, the thread would repeat the suspend instruction until the value changed.

The last instruction of any thread is the end instruction. This instruction signals the CMT to clear the Alloc bit of the entry pointed to by the ATR. The freed CMT entry is then added back to the list of contexts available for use by the NIU or the pipeline. Then, the next context to execute can begin its execution. As previously stated, contexts are scheduled in round robin fashion, and both the Alloc and Thread bits must be set for a context to be scheduled.

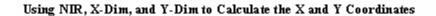

The other special SCMP instructions involve sending a message. As previously described, a message begins with the header and address flits. Both of these flits can be generated using the sendh instruction, which has two variations. The first type takes the form: sendh <register>, type, address. The register operand contains the destination node number. Nodes on the SCMP chip are numbered from left to right and top to bottom. Figure 2.5 shows such a numbering scheme. Since there are two types of messages, the type field names the message type (thread or data). The third operand is an address. If it is a thread message, then the context begins execution at this address. The address is the location to start writing to memory, if it is a data message.

Figure 2.5: The left figure shows how the nodes are numbered on the SCMP parallel computer. The right figure depicts how a message would be routed from node 3 to node 2.

The second form of the sendh instruction is as follows: sendh <register1>, type, <register2>[, stride]. The first three values are the same as before, but the address is contained in the second register reference rather than in an immediate value. The stride value is optional and signifies how far apart values should be stored in memory for a data message. The first value will be stored at the address given in register2, and the second value will be stored at <register2>+4\*stride. For example, if a data message writes to a column in a matrix, the addresses written to would be spaced evenly, but by more than one address, in memory.

After the header and address flits are sent, data follows. There are three different ways to send data. The first two are very similar and take the forms: send <register> and send2 <register1>, <register2>. Both of these instructions send data directly from a register(s) into the network. This procedure limits the amount of data copying that occurs, with the objective being that messages will reach their destination faster. The worm-hole routing allows the header flit to pave the way for the other flits of the message, which do not have specific knowledge of the destination node. The third way to send data is the sendm instruction. It takes the form, sendm <register1>, <register2>. This instruction copies bytes from memory and injects them directly into the network. As before, this tactic minimizes the copying that occurs before a message is sent. The first register contains the address of the first four bytes to copy and the stride between the values.

To end a message, a tail flit needs to be sent. Similar to the above, there are three different ways to end a message: sende, send2e, and sendme. A bit is contained in each flit to indicate if this one is the tail flit. The data is sent in the same fashion as described above for the send instructions, but the tail bit is set in the flit with the last data value to indicate it is the end of the message.

The discussion of the instruction set for the SCMP node completes the description of its operational design and functional requirements. The major components of the node were introduced in this chapter. The design objectives of the SCMP node and the hardware partitioning used to optimize its design were presented. The required messaging and message formats used by the SCMP components were described, along with the instruction set developed to provide the expected functionality. The next 2 chapters will discuss the hardware implementation of the SCMP node that was developed for this thesis.

# **Chapter 3 Hardware Implementation**

After the functionality of each block of the node had been designed, the interfaces between the blocks were created. A specific naming convention was developed so that each signal between blocks could be identified quickly and easily. If a signal was an input to a block, it began with a lower case 'i'. Similarly, a block output signal started with a lower case 'o'. The name of the signal took the following form: <source block name><description>To<destination block name>.

The description of each signal was intended to be straightforward enough so that the purpose of the signal would be understood. For example, if an enable signal was generated from the pipeline to the memory, then its signal name would be PipelineEnableToMemory. The signal name at the pipeline would start with an 'o', and at the memory, it would start with an 'i'.

Once the interfaces were defined, each block was implemented in System C. System C is a hardware modeling language, like VHDL or Verilog, but with C++ syntax. System C is a good example of a system description language that can be used to model Systems-On-a-Chip [21]. This chapter and the one following describe in detail the interface and implementation of each of the SCMP blocks. Research for this thesis focused on the design and implementation of the SCMP memory controller, the Network Interface Unit, and the ALU. SystemC models of the on-chip memory and instruction cache were also developed.

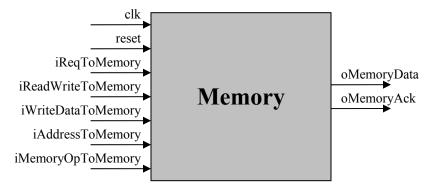

## 3.1 Memory

The memory block of the SCMP node was created for simulation purposes only. It is expected that a synthesized SCMP chip will use a third party vendor static RAM or embedded DRAM chip, if the latter technology continues to improve. However, there are restrictions that must be considered when choosing a third party chip. The memory must be synchronous, byte addressable, and allow accesses of 1, 2, and 4 bytes on even boundaries.

Since the SCMP parallel computer attempts to store everything it needs for a program on the chip, the memory access time becomes paramount. Therefore, it is assumed that the local on chip memory for each node is fast enough to be accessible in one clock cycle. However, there is not a guaranteed response time for gaining access to the memory space of another node. The response time depends on things like network traffic, if the destination node is already receiving a message, and accessibility to the actual memory. Three units in a node can access the memory: the pipeline, the instruction cache, and the network interface unit. See Chapter 3.2 to learn how each unit can gain access to memory.

The implementation of this block is straightforward. The memory is single ported, so no collision avoidance is required. Each memory address is 32 bits wide with the bytes stored in big endian format. The inputs and outputs of this block are depicted in Figure 3.1. Access to the memory is accomplished through a request/acknowledge sequence.

That is, the unit that wishes to access memory makes a request and then waits one clock cycle for the acknowledge signal. If the acknowledge is set, the data is valid, but if not, the access is denied.

Figure 3.1: A block diagram of the memory on the SCMP processor.

The reset of this block is asynchronous and sets the oMemoryAck line to '0'. Any request made to memory during a reset is ignored. A request is made on a rising clock edge, if the iReqToMemory signal is set. Then, a read or a write operation is performed, based on the input iReadWriteToMemory, on the number of bytes given by iMemoryOpToMemory. For the appropriate setting of the signals to this block, see Table 3.1.

| Signal Name        | Туре | Bit Width | Description                                             |

|--------------------|------|-----------|---------------------------------------------------------|

| clk                | In   | 1         | Rising Edge active clock                                |

| reset              | In   | 1         | Asynchronous reset to put the unit into a known state   |

| iReqToMemory       | In   | 1         | Signal is a 1 if a request is made to read or write to  |

|                    |      |           | memory, 0 otherwise                                     |

| iReadWriteToMemory | In   | 1         | Signal is a 1 to signify a read, 0 for a write. Is only |

|                    |      |           | used when a request is made.                            |

| iWriteDataToMemory | In   | 32        | If a write request is made, this bus contains the data  |

| _                  |      |           | that will be written.                                   |

| iAddressToMemory   | In   | 23        | The address in memory that is to be manipulated         |

| iMemoryOpToMemory  | In   | 2         | If set to "00", do a 4 byte operation                   |

|                    |      |           | If set to "01", do a 1 byte operation                   |

|                    |      |           | If set to "10", do a 2 byte operation                   |

|                    |      |           | If set to "11", do a 8 byte operation (See Chapter 5)   |

| oMemoryData        | Out  | 32        | If a read request is made, this bus contains the data.  |

|                    |      |           | The data is valid the cycle after the address           |

|                    |      |           | was presented.                                          |

| oMemoryAck         | Out  | 1         | Set to 1 if the oMemoryData bus is carrying valid       |

| -                  |      |           | data for the pipeline, 0 otherwise.                     |

**Table 3.1**: The input and output ports and descriptions of the memory block's signals.

If a 1 or 2 byte read access is made, the result is shifted to the least significant bits, so the correct value would be stored in a register. Similarly, on a write operation, the 1 or 2 byte value to be written is given in the least significant bits and shifted to the appropriate location in the 32-bit value. The output on a read would be valid on the next rising clock

edge. This data is also signified when the oMemoryAck line is set. On a write operation, the acknowledge signal signifies success.

## 3.2 Memory Controller

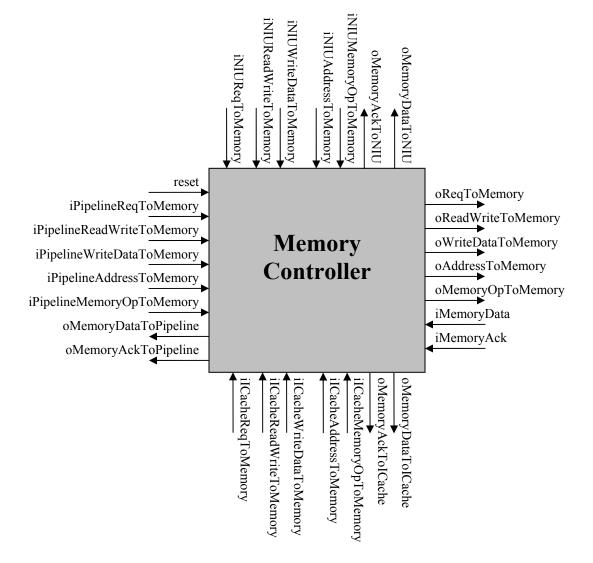

Since multiple units need access to the memory, their requests must be arbitrated. The pipeline needs memory access to retrieve/modify data values. The instruction cache needs to read instructions from memory. The NIU also needs to read or write data values to memory. However, the pipeline is not deep enough to allow this unit to be synchronous. If it is activated by a clock edge, then the pipeline would not receive the read value until after it should be written to a register. Therefore, this block is asynchronous and is triggered whenever a request signal changes or the acknowledge signal from memory changes. Figure 3.2 below shows the inputs and outputs to each of the three blocks and to memory.

Figure 3.2: A block diagram of the memory controller.

If two or three blocks request access at the same time, a method is needed to determine which block has the highest priority. The priorities are chosen with the objective of limiting the number of clock cycles that the pipeline has to stall. This measure is used because contexts are executed in non-preemptive fashion. Therefore, the faster one thread finishes, the faster the next one can start/continue its execution. As a result, the pipeline receives the highest priority, so its operations are unaffected. Then, the instruction cache has the next highest priority. The only time the cache can access memory is on a cache miss, since the pipeline needs an instruction to continue thread execution. Finally, the NIU received the lowest priority. When the NIU accesses memory, it cannot affect the execution of a context unless it wrote to a synchronization variable. If so, the context waiting for a sync would suspend, and the NIU would be able to access the memory before the pipeline could restart after a context switch. In addition, a message can back up in the network for a few cycles without harming overall performance.

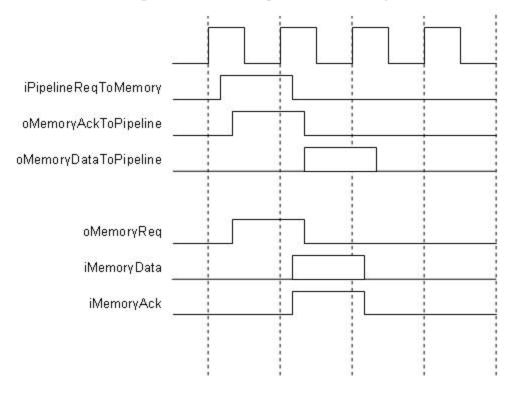

The implementation of this block multiplexes the three inputs over one channel. The interesting part of this implementation is in the acknowledgement execution. See Table 3.2 for a list of the acknowledge signals and refer to Table 3.1 for a reference to the memory interface. Since this unit is asynchronous and its outputs are stable by the next rising clock edge, the acknowledge signal is not used to indicate valid data, but is used as an indicator of the acceptance of the request. Figure 3.3 depicts the timing of a memory operation through the memory controller.

The Context Management Table (CMT) is memory mapped to addresses 0xFFFFF00 - 0xFFFFFFF. Therefore, the port from the memory controller to the memory is also split to the context logic. When the address is in the appropriate range, the CMT logic responds with the appropriate value while the memory ignores the request.

| Signal Name          | Туре | Bit Width | Description                                 |

|----------------------|------|-----------|---------------------------------------------|

| Reset                | In   | 1         | Asynchronous reset to put the unit into a   |

|                      |      |           | known state                                 |

| oMemoryAckToICache   | Out  | 1         | Set to 1 if the oMemoryData bus is carrying |

|                      |      |           | data for the instruction cache, 0           |

|                      |      |           | otherwise.                                  |

| oMemoryAckToNIU      | Out  | 1         | Set to 1 if the oMemoryData bus is carrying |

|                      |      |           | data for the NIU, 0 otherwise.              |

| oMemoryAckToPipeline | Out  | 1         | Set to 1 if the oMemoryData bus is carrying |

|                      |      |           | data for the pipeline, 0 otherwise.         |

| oMemoryAck           | Out  | 1         | Set to 1 if the oMemoryData bus is carrying |

|                      |      |           | data for the pipeline, 0 otherwise.         |

**Table 3.2**: The signal names with corresponding descriptions of the memory controller block. The other signals are those of a memory interface (See Chapter 3.1) with the appropriate naming convention.

#### Memory Read from Memory Controller's Perspective

**Figure 3.3**: When a read request is made, the acknowledge signal is received on the next clock edge. If the acknowledge signal is positive, the actual data is valid two cycles after the request was made.

If the request is accepted, the operation is completed by the next rising clock edge. In other words, it is known if the memory operation is permitted on the clock edge after it is requested, but would not be completed until two clock edges later. This design also means that requests to memory did not need to be buffered since a unit can request again as soon as it is denied.

The acknowledge signal from memory triggers the memory controller. On a read operation, data is passed back to the appropriate unit and the acknowledge signal to the requesting unit is set to '0'. Once the requester knows the operation is permitted, data is known to be valid on the next clock cycle.

Another feature of the memory controller is that it abstracts away the memory interface from the three requesting units. When a third party vendor memory design is used, only the memory interface from the controller to the memory will need to change. The three requesting units can keep the same interface, and the memory controller can be changed to translate the current interface to the new one

#### 3.3 Instruction Cache

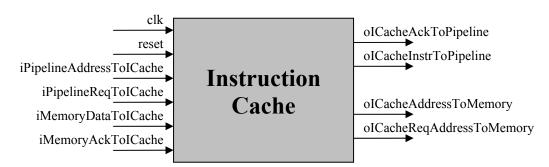

Even though a data value can be read from the memory in one cycle, the memory is not designed to be dual ported. If the memory has two separate access points with collision control, then one port can be dedicated to be the instruction cache and the other to the pipeline and the NIU. Since that is not the case, a separate storage space is needed for the instructions since one needs to be read each clock cycle for an executing context. Therefore, an instruction cache was created with the interface shown in Figure 3.4 and described in Table 3.3.

Figure 3.4: A block diagram of the instruction cache for the SCMP parallel computer.

When it is possible to fabricate the SCMP parallel computer, this block will probably be substituted with a third party instruction cache. Thus, this block was used for simulation and testing of the hardware and the interfaces. It was important, for simulation purposes, that the instruction cache be flexible so the different types of cache line replacement could be attempted. Therefore, the instruction cache was implemented so that it could be direct mapped, x-way set associative, and fully associative by changing the constants in the icacheconf.h header file.

The constants that control the instruction cache are as follows: iCacheSizeLength, controlled the size of the instruction cache in bytes; iCacheLinesPerSetLength, determines the associativity of the cache; and iCacheInstPerLineLength, sets the number of instructions that are in each cache line. Each of these cache parameters determines its actual value by shifting a '1' to the left the number of times indicated in these constants. For example, if iCacheSizeLength is 15, then iCacheSize would be 32 KB, or 2<sup>15</sup>.

| Signal Name              | Туре | Bit Width | Description                                    |

|--------------------------|------|-----------|------------------------------------------------|

| clk                      | In   | 1         | Rising Edge active clock                       |

| reset                    | In   | 1         | Asynchronous reset to put the unit into a      |

|                          |      |           | known state                                    |

| iPipelineAddressToICache | In   | 23        | The address of the instruction the pipeline is |

|                          |      |           | trying to fetch.                               |

| iPipelineReqToICache     | In   | 1         | When set to a '1', the pipeline is making a    |

|                          |      |           | request for an instruction. On a '0', no       |

|                          |      |           | request is made.                               |

| iMemoryDataToICache      | In   | 32        | On a cache miss, the data for the cache line   |

Table 3.3: The signal names and descriptions for the instruction cache block.

|                           |     |    | will come back on this port.                                                                      |

|---------------------------|-----|----|---------------------------------------------------------------------------------------------------|

| iMemoryAckToICache        | In  | 1  | When set to a '1', the data coming from<br>memory is valid. When a '0', the data is<br>not valid. |

| oICacheAckToPipeline      | Out | 1  | Set to a '1' when there is a cache hit. '0' otherwise.                                            |

| oICacheInstrToPipeline    | Out | 32 | The instruction that was fetched.                                                                 |

| oICacheAddressToMemory    | Out | 23 | On a cache miss, this is the address of the 4 byte value being fetched.                           |

| oICacheReqAddressToMemory | Out | 1  | Set to a '1', when cache needs to fill a line.<br>The signal is a '0' otherwise.                  |

The important part of the instruction cache implementation is to understand what a set consists of and how many sets are in the cache. When a cache is x-way set associative, it means that there are x lines in a set. Those lines are filled associatively. Each line in the set has a valid signal to indicate when a line is full. And a line identifier is associated with each line to identify which instructions are in that line. Line replacement for each set is done in round robin fashion. The hope is that a context contains few enough instructions so that there would be a high locality of reference and adjacent lines could be reused often. Therefore, each set also needs a reference to which line was to be filled next.

The other important aspect of the instruction cache is how to calculate the number of sets needed to create the cache. For example, if the cache is 32 KB in size, it could hold 8 K of instructions (4 bytes per instruction). Assuming that each cache line has 8 instructions and the cache is 4-way set associative, then the number of sets in this cache is calculated as follows:

$$32KB * \frac{1instruction}{4B} * \frac{1line}{8instructions} * \frac{1set}{4lines} = 2^8 \text{ or } 256 \text{ sets}$$

Therefore, 8 bits are needed to identify a set in the cache. An address in the SCMP node is currently 23 bits (8MB of addressable space). The lowest 2 bits of an address must be 0 so that a request is made on an even 4 byte boundary. The next 3 bits are needed to identify which instruction is referenced from the cache line. Therefore, the line identifier needs to be 23-8-3-2=10 bits.

When a request is made to the instruction cache, its implementation accesses the appropriate set and queries all of the lines in that set for a valid line ID match. If the line is present, then it is a cache hit. On a cache miss, the address requested and the address of the start of the corresponding line are saved. The nextLineToFill value is used to determine which line should be replaced in the set. The cache uses the request/acknowledge sequence described in Chapter 3.2 about the memory controller. Once the line is filled, the instruction can be positively acknowledged the next time it gets requested.

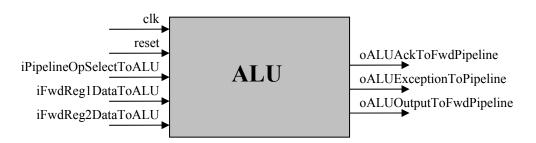

## 3.4 ALU

The <u>Arithmetic Logic Unit (ALU)</u> is a synchronous logic block, triggered by the falling edge of the clock, used for any integer based mathematical function. On a reset, this unit

sets the acknowledgement signal to '0'. The figure below depicts the ALU as a black box with its inputs and outputs labeled. Table 3.4 then describes the use of each of the signals.

Figure 3.5: A block diagram of the ALU.

| Signal Name             | Туре | Bit Width | Description                                                                                                  |

|-------------------------|------|-----------|--------------------------------------------------------------------------------------------------------------|

| clk                     | In   | 1         | Rising Edge active clock                                                                                     |

| reset                   | In   | 1         | Asynchronous reset to put the unit into a known state                                                        |

| iPipelineOpSelectToALU  | In   | 7         | The instruction opcode tells the ALU which<br>operation to perform. Only one can be<br>calculated at a time. |

| iFwdReg1DataToALU       | In   | 32        | Data on which operation is performed                                                                         |

| iFwdReg2DataToALU       | In   | 32        | Data on which operation is performed                                                                         |

| oALUOutputToFwdPipeline | Out  | 32        | The result of the operation performed.                                                                       |

| oALUExceptionToPipeline | Out  | 32        | Set to the ESTATUS value of the corresponding exception.                                                     |

| oALUAckToFwdPipeline    | Out  | 1         | Acknowledge that was set when the data and exception values were valid. '0' otherwise.                       |

The pipeline controls when the ALU performs an operation via the OpSelect input. The pipeline identifies which operations the ALU is responsible to perform since all ALU opcodes occurred sequentially in the instruction set. For a complete list of instructions, see Appendix A.

The ALU is a simple block because it is synchronous and each ALU function is implemented behaviorally without optimizations. When an opcode that the ALU is responsible for is present at the OpSelect input, the appropriate operation is performed on Reg1 and Reg2. It is assumed that all operations except multiply, divide, and modulo take only one clock cycle to execute. The other instructions took 5, 19, and 19 cycles respectively. Once an operation begins, the pipeline must wait until the acknowledge signal is set to be sure that the output data is valid. Since the pipeline does not execute instructions out of order, it is forced to stall until the ALU operation is completed.

## 3.5 NIU

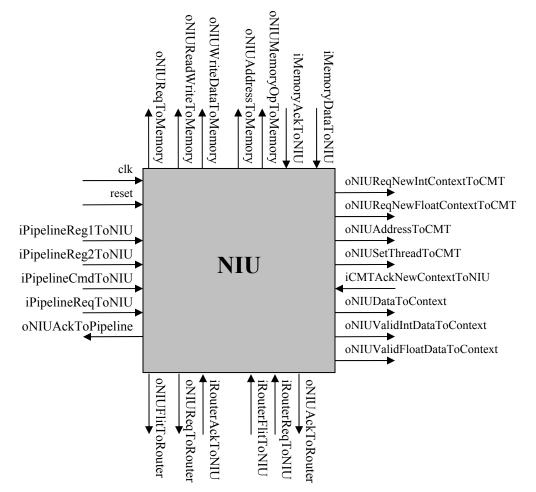

The Network Interface Unit (NIU) is used to create flits to inject into the network and to accept and perform operations on flits from the network. Both the inject and eject

functions of the NIU are further divided into two parts. When sending a message into the network, it can be generated from either the pipeline, using register values, or from the on chip memory, reading data. When a message arrives at a node, it can either create a new context, using the CMT/context interface or write values to memory, using the memory interface. Figure 3.6 below is a block diagram of the NIU.

Figure 3.6: A block diagram of the Network Interface Unit (NIU).

The signals from the NIU to the memory controller are identified in Chapter 3.1, which describes the memory interface. Similarly, those signals between the NIU and the context management logic will be discussed in Chapter 4. Since those signals are described elsewhere, they will not be discussed here. This section describes the operation of the NIU in terms of the NIU/pipeline and NIU/router signals. Table 3.5 describes these signals in detail.

Table 3.5: The signal names and descriptions for the NIU of the SCMP node.

| Signal Name | Туре | Bit Width | Description                                           |

|-------------|------|-----------|-------------------------------------------------------|

| clk         | In   | 1         | Rising Edge active clock                              |

| reset       | In   | 1         | Asynchronous reset to put the unit into a known state |

| iPipelineReg1ToNIU | In  | 32 | A data value from a register to be sent in a message.                                                                           |

|--------------------|-----|----|---------------------------------------------------------------------------------------------------------------------------------|

| iPipelineReg2ToNIU | In  | 32 | A second value from a register to be sent in a message.                                                                         |

| iPipelineCmdToNIU  | In  | 7  | The command tells the NIU which data<br>values are valid and what operation to<br>perform on the data.                          |

| iPipelineReqToNIU  | In  | 1  | When set to '1', the input command and data are valid. '0' otherwise.                                                           |

| oNIUAckToPipeline  | Out | 1  | Set to a '1' when the request is satisfied. If<br>a '0', the requesting thread will<br>suspend.                                 |

| oNIUFlitToRouter   | Out | 34 | A flit contains a 32 bit data value, a bit to<br>indicate the start of a message, and a<br>bit to specify the end of a message. |

| oNIUReqToRouter    | Out | 1  | When set to a '1', the flit data is valid. '0' otherwise.                                                                       |

| iRouterAckToNIU    | In  | 1  | If set to a '1', the router has stored the flit in a buffer successfully. '0' otherwise.                                        |

| iRouterFlitToNIU   | In  | 34 | A flit arriving at the node.                                                                                                    |

| iRouterReqToNIU    | In  | 1  | When set to a '1', the flit data is valid. '0' otherwise.                                                                       |

| oNIUAckToRouter    | Out | 1  | Set to a '1' when the NIU accepts the flit.<br>When a '0', the flit remains buffered<br>in the network.                         |

When the pipeline executes any of the send instructions, data is sent to the NIU from the pipeline. The type of instruction is identified by the <iPipelineCmdToNIU> signal, which is the opcode decoded by the pipeline. One instruction can send up to two flits. To accept two flits per clock cycle, either two flits need to be sent in one clock cycle or flits need to be buffered in the NIU. For this implementation, it is assumed that the router is capable of receiving two flits in one clock cycle. Therefore, a flit could be sent out on the rising and falling edge of the node clock and no buffering is necessary. If this method is found not to be realistic, then buffers can be added to this unit.

Only one message at a time can be constructed by the NIU and injected into the network. This limitation means that once a sendh instruction is received, a sende instruction is required before another sendh. In other words, after a message begins, any other request to start a new message is denied. Both the send and sendm instructions have a version of the instruction that indicates the tail flit of a message. The end of a message is known by the opcode passed to the NIU.

When a sendh instruction is detected, the <iPipelineReg1ToNIU> bus contains the address needed by either the thread message or the data message. The <iPipelineReg2ToNIU> signal contains the following data: the type of message is in the highest bit position, the destination node is in the next 6 most significant bits (for 64 nodes), and the lowest 11 significant bits contain the immediate stride value, if needed. The sendh instruction generates two flits. First, the header flit contains the type of message and the routing information needed to reach the destination node. Second, the address flit contains the starting place for either type of message.

When a sendm instruction is detected, then the <iPipelineReg1ToNIU> bus contains the start address to read from memory. Also, the stride value between memory accesses and the number of values to read are given by the <iPipelineReg2ToNIU> signal. Only one flit is injected into the network per clock cycle because the memory can only process one request per clock cycle.

On a send instruction, <iPipelineReg1ToNIU> contains the register value to inject in to the network. Similarly, when a send2 instruction is detected, both the <iPipelineReg1ToNIU> and <iPipelineReg2ToNIU> buses contain register values to send as part of a message.

A message is guaranteed to be sent in the same order the instructions are issued. For example, if a sendm is followed by a send2 instruction, then the sendm must complete its execution before the send2 instruction is accepted by the NIU.

Similar to the inject portion of the NIU, the eject section can only accept one message at a time. When a header flit arrives at the NIU from the router, the type of message is determined and, if necessary, the stride value is stored. Once the address flit arrives at the NIU, the incoming message manipulates the appropriate interface, either the memory interface or the CMT/context interface. If a data flit arrives at the NIU before its associated header and address flits are successfully written to memory or allocated to a context, then the data flit is denied access, and the flit will be buffered by the router.

With the completion of the NIU implementation, the major components of the SCMP node were designed and implemented, and the messaging, sequencing, and interfaces between the various components were defined. System C models of the on-chip memory and instruction cache were also developed. The heart of the SCMP node and the focus of this thesis were the design and implementation of the SCMP memory controller, the Network Interface Unit, and the ALU. The remaining components of the SCMP node, the CMT and the contexts, are responsible for managing the threads on a node and are described in the next chapter.

# Chapter 4 Contexts and Context Management

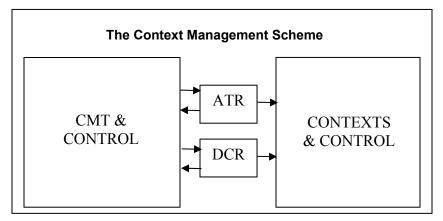

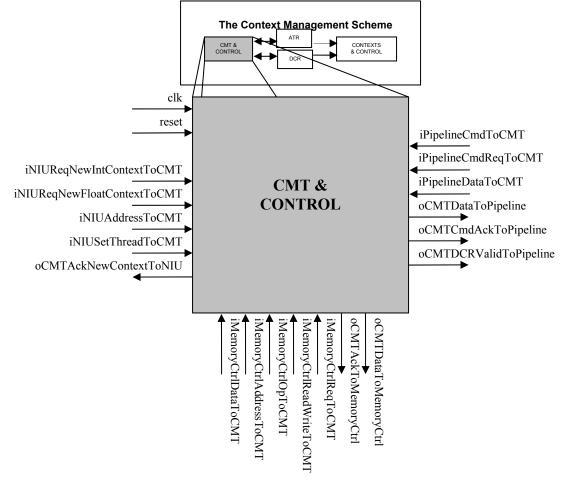

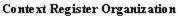

As was previously explained, the context management scheme is broken up into two main blocks: the Context Management Table (CMT) and control, and the Context Register File (CRF) and control. This division of hardware allows for the parts to be developed and tested both individually and concurrently. Figure 4.1 depicts the overall context management scheme with the CMT and CRF sub-blocks.

Figure 4.1: A block diagram of the context management scheme.

The CMT and Control block is responsible for allocating and deallocating contexts and for scheduling threads. Meanwhile, the Contexts and Control block is in charge of accessing the registers of each context. These blocks cannot, however, be separated because both interact with the same control registers. This chapter presents a detailed implementation of the hardware for each of the sub blocks and the shared hardware between the two. The Contexts and Control block was designed and both the CMT and Contexts were implemented in System C as a part of this research effort.

## 4.1 Shared Hardware

There are two main registers that are shared between the CMT control and the CRF control: the Active Thread Register (ATR) and the Data Context Register (DCR). Each of these registers is 4 bits long in order to access the 16 possible contexts. The actual length is determined by the constant that set the number of contexts in the node.

The ATR contains the context identifier of the currently executing thread. The CMT needs this value for many of its commands (see Chapter 4.2). For example, when a thread ends, the CMT control needs to modify the CMT entry corresponding to that thread. Therefore, the ATR is used as an index into the CMT so the end instruction can be executed. Similarly, the CRF control uses the ATR as an index into its register set (see Chapter 4.3). As an example, if an instruction reads or writes to a register(s), then the ATR is used to access the appropriate register set in the CRF. The ATR requires a valid signal to ensure that a context is currently executing. If the ATR is not valid, then a context to execute cannot be found and one is searched for during each clock cycle.

A context may increase the number of registers it uses through the DCR. If a program requires more that its own 32 registers, it can allocate a second context to itself and use these registers in its own calculations. In this case, the DCR is used as the context identifier of this second context. When a register in this extended range (32-63) is accessed, the DCR is used as the index into the CRF. Unlike the ATR, the DCR does not require a valid signal because context 0 cannot be used as a data context (see Chapter 5.2). Although the CMT and contexts cannot be separated, the following sections describe each block's implementation in detail.

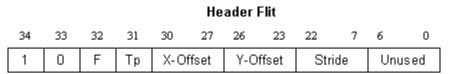

## 4.2 Context Management Table and Control

Each entry in the context management table has four parts:

- The Alloc bit If the context is allocated, this bit is set to 1. The context is free for use as a data context or a thread context, if this bit is set to 0.

- The Thread bit If the context was allocated and this bit is a 1, the context is a thread and will be scheduled for execution. When the context is allocated and this bit is a 0, the context is currently being used as a data context, or is being filled by the Network Interface Unit (NIU).

- The DCR A 4 bit value that stores the context ID of a thread's data context. If the value is 0x0, the context does not have a data context. (The number of bits in this field is determined by a constant, which is based on the number of contexts on each processor.)

- The IP Address A 23 bit value that contains the instruction pointer of a thread context. This value does not have meaning if the context is a data context. (The number of bits in this field is determined by a constant, which is based on the size of memory for each processor.) It is important to note that the 2 lowest significant bits will always be "00" because instructions are 4 byte aligned.

There are a total of 29 bits in each CMT entry. Each CMT entry is chosen to be 32 bits wide to allow easy expansion of either the IP, if the memory size increases, or DCR field, if the number of contexts on a processor is increased. Figure 4.2 shows the breakdown, by bit, of these fields in a CMT entry.

#### **Context Management Table**

Figure 4.2: A visual representation of a CMT entry.

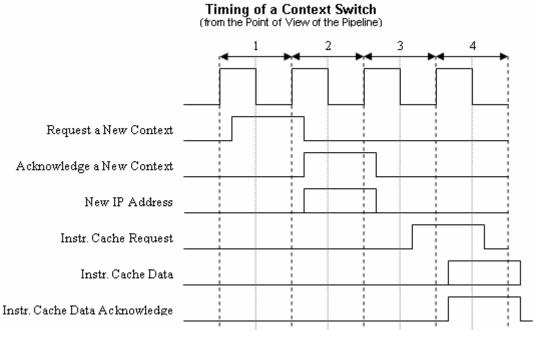

Hardware support is used to manage the threads of a node to minimize the number of clock cycles during a context switch [9]. In theory, from the time the pipeline detects an end or a suspend instruction to the time when the pipeline receives another valid instruction from the instruction cache, it takes four clock cycles. This calculation assumes that there is another context ready for execution and the instruction requested is already in the instruction cache. Figure 4.3 shows the timing of this ideal context switch from the pipeline's perspective.

Figure 4.3: The timing of a context switch.

Both the pipeline and the NIU can control the bits of a CMT entry. The pipeline can control any entry in the CMT. The CMT is memory mapped, so the pipeline can read

and write to an entry in the CMT. However, a context cannot change its own entry. Also, the pipeline can use the alloc and free instructions to modify the CMT. The Network Interface Unit (NIU) can also allocate a context by using a thread message. Figure 4.4 depicts the CMT and control with the interfaces to each of the units that could access it. Then, the input and output signals of the CMT control are described in the sections that follow.

Figure 4.4: A block diagram of the CMT & control part of the context management scheme.

| Signal Name | Туре | Bit Width | Description                                           |

|-------------|------|-----------|-------------------------------------------------------|