## An Investigation of Fundamental Frequency Limitations for HF/VHF Power Conversion

### Chucheng Xiao

Dissertation submitted to the faculty of the Virginia Polytechnic Institute and State

University in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

In

The Bradley Department of Electrical and Computer Engineering

Dr. Willem G. Odendaal, Chairman

Dr. Jacobus D. van Wyk

Dr. Ahmad Safaai-Jazi

Dr. Guo Q. Lu

Dr. Elaine P. Scott

July 12, 2006 Blacksburg, Virginia

Keywords: frequency limitations, high frequency, very high frequency, power conversion

Copyright 2006, Chucheng Xiao

### An Investigation of Fundamental Frequency Limitations for HF/VHF Power Conversion

#### **Abstract**

By Chucheng Xiao

W.G. Odendaal, Chairman

The volume reduction in power converters over the past several decades can chiefly be attributed to increases in switching frequency. It is to be expected that the trends towards miniaturization will maintain steady pressure to keep this pace of increasing switching frequencies of power converters. However certain fundamental limits in high frequency power conversion are being reached as frequencies are being pushed deeper into the megahertz range, inhibiting substantial further increases.

The work reported in this dissertation is intended to systematically investigate the fundamental frequency limitations, identify some of the solutions for HF/VHF power conversion and to provide guidelines and tools to optimize the performance of power converters by maximizing frequency.

A number of multi-megahertz power converters are examined to evaluate the present status and future trend of HF/VHF power conversion. An interesting trend between power level and frequency is observed. A general limitation about the power level and frequency, independent of design details, is derived from the physics of the semiconductor devices, which determines the upper bound of the power levels as frequency increases.

A 250 MHz DC-DC power converter (derived from the Class E power amplifier) is analyzed and demonstrated with discrete components, which again verifies the trend between power level and frequency. The power losses in the semiconductor devices are discussed, and optimization criteria for minimizing the power losses of the devices, are discussed. By relating the power losses to the semiconductor materials' properties, a

methodology for selecting proper materials is identified for high frequency and high efficiency power conversion.

The frequency scaling effects of passive components, still dominating the volume of the modern power converter, is analyzed. A generic multi-disciplinary methodology is developed to analyze and maximize frequency and performance of passive components in terms of power density and efficiency. It is demonstrated how the optimum frequency can be identified, and how power conversion efficiency deteriorates beyond this optimum under a fixed maximum temperature.

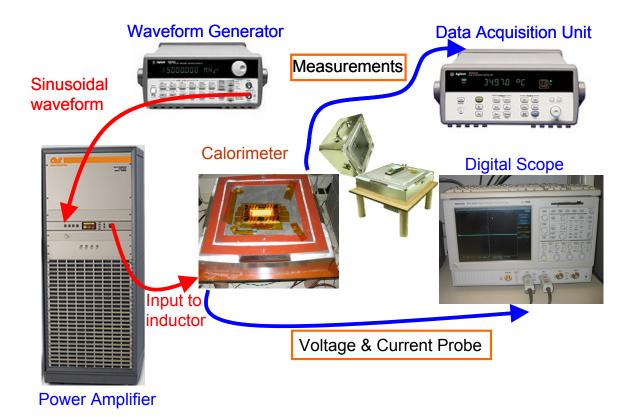

Power loss measurement is becoming more challenging as higher frequency and higher efficiency power conversion. To achieve an accurate power loss measurement in a high frequency, high efficiency power electronics system or component, limitations of electrical measurement are identified, and various calorimetric methods are surveyed. Calorimetric methods are more accurate due to the direct heat loss measurement. An advanced calorimetric system is proposed, analyzed, and tested, demonstrating about 5% error in total losses up to 25W.

### Acknowledgements

I would like to express deep and sincere gratitude to those who made this work possible.

Thank you so much for my advisor, Dr. Odendaal. You have been giving me so much valuable guidance and continuous support, which has been my source of inspiration to accomplish this work. From the first day I met with you, I learned so much from the weekly discussion and I got so much encouragement to solve the research issues one by one. Without your support, this work would have been simply impossible to accomplish. It is really fortunate for me to have this opportunity to study under your mentorship.

I would also like to express my appreciation to constant help and encouragement from my committee members: Prof. van Wyk, Prof. Ahmad S.J., Prof. E.P. Scott and Prof. G.Q. Lu. Your instructions and suggestions helped me a lot to improve my research and presentation capabilities.

I would like to thank all the supports and helps from the staff and faculties of CPES. Without you, things can't be done smoothly.

I very appreciated the happy times with all my colleagues in CPES and kind helps and advices from them.

I would forever remember the constant supports, love, encouragement, understandings and sacrifice from my family for so many years of studying life.

This work made use of ERC Shared Facilities supported by the National Science Foundation under Award Number EEC-9731677.

To my father Bingyan & mother Lamei and My wife Xiaoyan & sons

### **Table of Contents**

| ABSTRACT                                                                        | II   |

|---------------------------------------------------------------------------------|------|

| ACKNOWLEDGEMENTS                                                                | IV   |

| TABLE OF CONTENTS                                                               | VI   |

| TABLE OF FIGURES                                                                | IX   |

| LIST OF TABLES                                                                  | XIV  |

| CHAPTER 1 INTRODUCTION                                                          | 1    |

| 1.1. BACKGROUND                                                                 | 1    |

| 1.2. LIMITATIONS OF HF/VHF POWER CONVERSION                                     | 2    |

| 1.2.1. Introduction                                                             | 2    |

| 1.2.2. Monolithic Integration and Converters-On-a-Chip                          | 3    |

| 1.2.3. Modeling and Design                                                      | 4    |

| 1.2.4. Semiconductor Device Technologies                                        | 5    |

| 1.2.5. Circuit Toplogies and Control Strategies for VHF Power Conversion        | 7    |

| 1.2.6. Device Characteristics for future HF/VHF conversion technologies         | 8    |

| 1.2.7. Passive Components                                                       | 9    |

| 1.2.8. Packaging and Integration Techniques                                     | . 11 |

| 1.2.9. Thermal Management                                                       | . 12 |

| 1.2.10. Measurement Issues                                                      | . 12 |

| 1.3. OBJECTIVE OF THIS STUDY                                                    | 13   |

| 1.3.1. Chapter 2: HF/VHF Power Conversion Technology Review and Discussion      | . 14 |

| 1.3.2. Chapter 3: Analysis and Design of RF Class E DC-DC power converter       | . 14 |

| 1.3.3. Chapter 4: Fundamental Frequency Limitations of Passive Components for   |      |

| HF/VHF Power Conversion                                                         | . 15 |

| 1.3.4. Chapter 5: Power Loss Measurement Techniques for HF/VHF power conversion | ı    |

| Applications                                                                    | . 15 |

| CHAPTER 2 HF/VHF POWER CONVERSION TECHNOLOGY REVIEW AND                         |      |

| DISCUSSION                                                                      | 17   |

| 2.1.  | Introduction                                                       | 17       |

|-------|--------------------------------------------------------------------|----------|

| 2.2.  | RESONANT SWITCHING TECHNIQUES IN CONVENTIONAL CONVERTERS           | 18       |

| 2.3.  | HIGH SPEED SWITCHING DEVICES IN CONVENTIONAL CONVERTERS            | 19       |

| 2.4.  | MONOLITHICALLY INTEGRATED CONVENTIONAL POWER CONVERTERS BY VL      | SI 22    |

| 2.5.  | NEW ARCHITECTURE DC-DC CONVERTERS DERIVED FROM CLASS E POWER A     | MPLIFIER |

|       |                                                                    | 27       |

| 2.6.  | TRENDS OF POWER LEVEL WITH INCREASING FREQUENCY                    | 30       |

| СНАРТ | TER 3 ANALYSIS AND DESIGN OF RF CLASS E DC-DC POWER                |          |

|       | ERTER                                                              | 36       |

| 3.1.  | Introduction                                                       | 26       |

| 3.1.  | ANALYSIS OF CLASS E RF DC-DC CONVERTER                             |          |

| 3.2.  |                                                                    |          |

| 3.2   |                                                                    |          |

| 3.2   |                                                                    |          |

| 3.2   |                                                                    |          |

|       | 2.5. Resonant gate driver of Class E inverter                      |          |

| 3.2   |                                                                    |          |

| 3.2   |                                                                    |          |

| СПУРТ | TER 4 FUNDAMENTAL FREQUENCY LIMITATIONS OF PASSIVE                 |          |

|       | ONENTS FOR HF/VHF POWER CONVERSION                                 | 78       |

|       |                                                                    |          |

| 4.1.  | BACKGROUND                                                         |          |

| 4.2.  | SETTING UP THE MODEL                                               |          |

| 4.3.  | PERFORMANCE OF MAGNETICS AS A FUNCTION OF FREQUENCY                |          |

| 4.4.  | PERFORMANCE OF DIELECTRICS IN A CAPACITOR AS A FUNCTION OF FREQUEN |          |

| 4.5.  | EXPERIMENTAL VERIFICATION ON FREQUENCY SCALING EFFECTS OF INTEGR   |          |

|       | CTOR                                                               |          |

| 4.6.  | SUMMARY                                                            | 120      |

| CHAPT | TER 5 POWER LOSS MEASUREMENT TECHNIQUES FOR HF/VHF P               | OWER     |

| CONVE | ERSION APPLICATIONS                                                | 121      |

| 5.1.  | Introduction                                                       | 121      |

| 5.2.  | LIMITATIONS OF ELECTRICAL MEASUREMENTS FOR POWER LOSS MEASUREME    | NT 122   |

| 5.2   | 2.1. Background                                                    | 122      |

| 5.2.2.   | Direct Wattmeter Measurement [139]                     | 125 |

|----------|--------------------------------------------------------|-----|

| 5.2.3.   | Digital Measurement Techniques                         | 126 |

| 5.3. R   | EVIEW OF CALORIMETRIC METHOD FOR LOSS MEASUREMENT      | 129 |

| 5.3.1.   | Introduction                                           | 129 |

| 5.3.2.   | Basic Principle of Operation                           | 130 |

| 5.3.3.   | Open-type Balance Calorimeter                          | 132 |

| 5.3.4.   | Double-jacketed, Closed Type Calorimeter               | 134 |

| 5.3.5.   | Calorimeter Based on Heat-flux Sensor                  | 137 |

| 5.3.6.   | Summary                                                | 138 |

| 5.4. P   | ROPOSED CALORIMETER FOR LOSS MEASUREMENT               | 139 |

| 5.4.1.   | Introduction                                           | 139 |

| 5.4.2.   | Thermal analysis of the proposed calorimeter           | 143 |

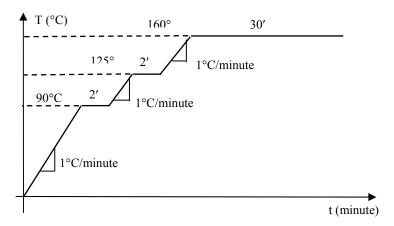

| 5.4.3.   | Calibration and experiment                             | 150 |

| 5.5. S   | UMMARY                                                 | 152 |

| CHAPTER  | 6 CONCLUSION AND FUTURE WORK                           | 154 |

| 6.1. C   | ONCLUSION                                              | 154 |

| 6.2. F   | UTURE WORK                                             | 158 |

| REFEREN  | CES                                                    | 160 |

| APPENDIX | X I IMPLEMENTATION OF RF DC-DC POWER CONVERTER         | 176 |

| APPENDIX | X II VOLTAGE MEASUREMENT PROBE                         | 185 |

| APPENDIX | X III DESIGN OF THE PROPOSED CALORIMETER               | 188 |

| APPENDIX | X IV FABRICATION PROCESSING OF THE INTEGRATED INDUCTOR | 194 |

| VITA     |                                                        | 198 |

### **Table of Figures**

| Fig. 1.1 Size evolution of modular telecom power conversion units [2]             | 2        |

|-----------------------------------------------------------------------------------|----------|

| Fig. 1.2 Evolution of power semiconductor devices.                                | 5        |

| Fig. 1.3 Frequencies of different power supply technologies used in power convers | sion vs. |

| time.                                                                             | 6        |

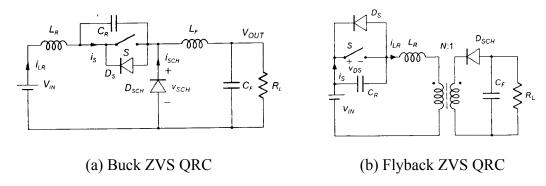

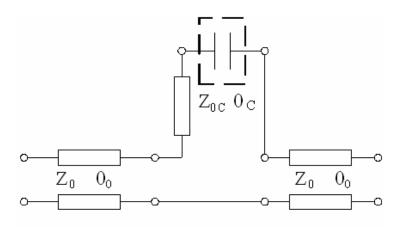

| Fig. 2.1 Basic structures for soft resonant switching                             | 18       |

| Fig. 2.2 Basic circuit diagram of ZVS QRC in [37].                                | 19       |

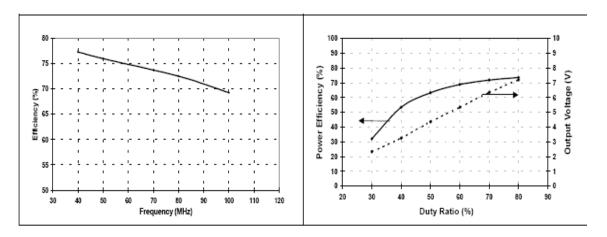

| Fig. 2.3 Experimental results of Buck in [39]                                     | 21       |

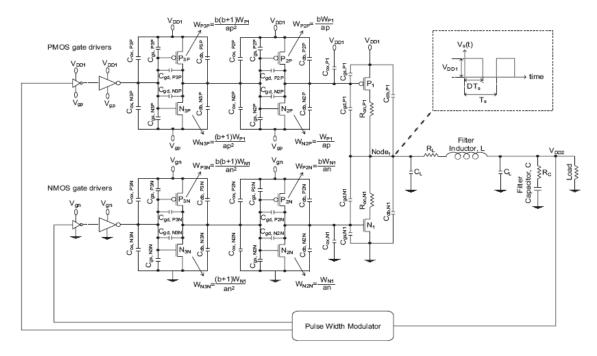

| Fig. 2.4 Parasitic impedances and transistor geometric sizes of Buck converter    | 25       |

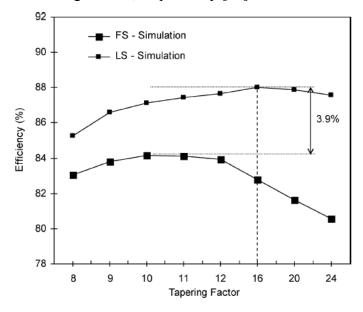

| Fig. 2.5 Maximum efficiency with low-swing (LS) and full-swing (FS) Buck cor      | iverters |

| vs. tapering factors.                                                             | 26       |

| Fig. 2.6 Schematic of DC-DC converter operating at 22 MHz.                        | 28       |

| Fig. 2.7 Layout of 4.5 GHz DC-DC converter.                                       | 29       |

| Fig. 2.8 Switching DC-DC power converter at 100 MHz.                              | 30       |

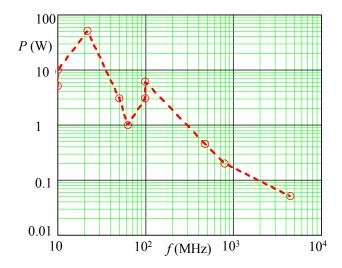

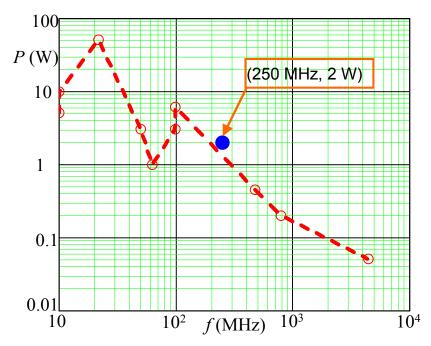

| Fig. 2.9 Power level vs frequency for selected converters.                        | 32       |

| Fig. 2.10 Efficiency vs frequency for selected converters.                        | 32       |

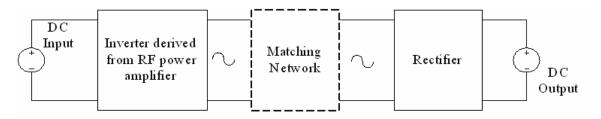

| Fig. 3.1 Block diagram of proposed RF DC-DC converter.                            | 36       |

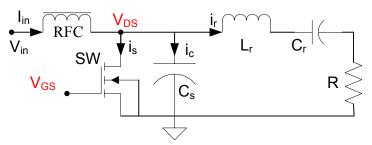

| Fig. 3.2 Class E inverter.                                                        | 37       |

| Fig. 3.3 Series resonant circuit.                                                 | 38       |

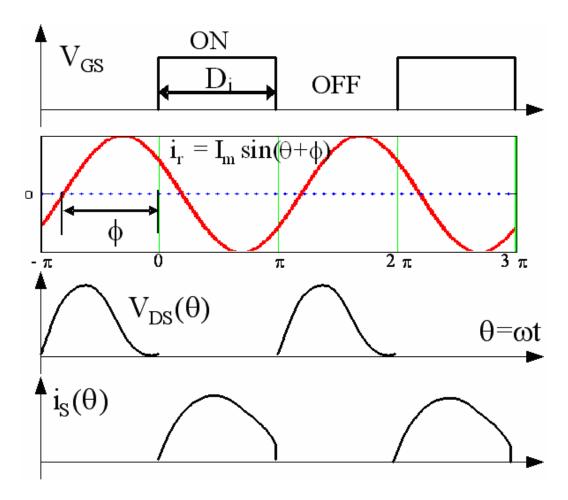

| Fig. 3.4 Waveforms of Class E inverter.                                           | 39       |

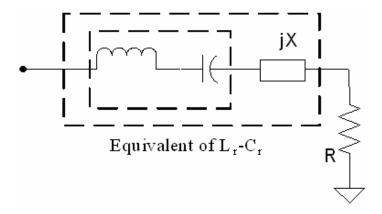

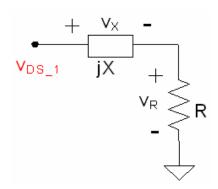

| Fig. 3.5 Equivalent circuit of series resonant circuit at the operating frequency | 42       |

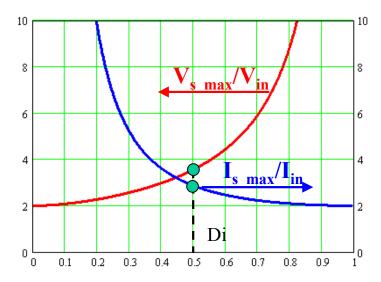

| Fig. 3.6 Normalized peak switch current and voltage vs. duty cycle.               | 44       |

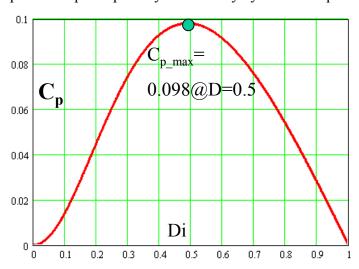

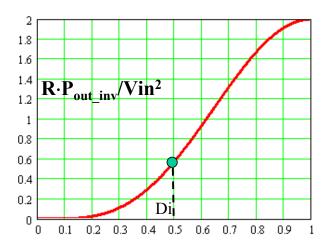

| Fig. 3.7 Power output capability C <sub>p</sub> vs Duty cycle D <sub>i</sub> .    | 44       |

| Fig. 3.8 Normalized output power vs duty cycle.                                   | 45       |

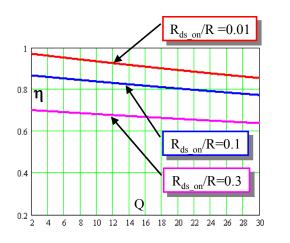

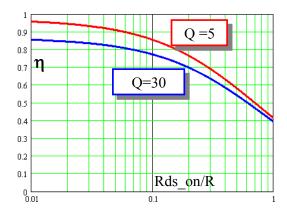

| Fig. 3.9 Efficiency vs Q ( $D_i = 50\%$ )                                         | 51       |

| Fig. 3.10 Efficiency vs $R_{ds\_on}/R$ ( $D_i = 50\%$ ).                          | 51       |

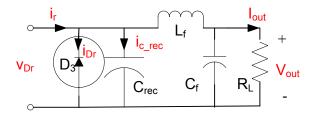

| Fig. 3.11 ZVS rectifier                                                           | 53       |

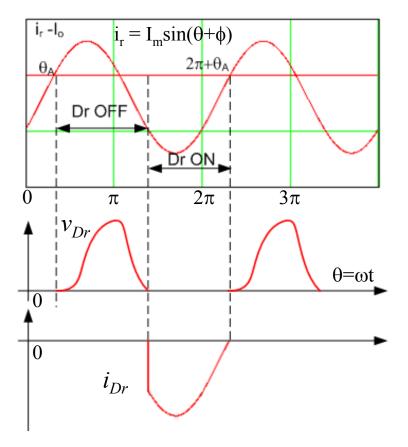

| Fig. 3.12 Main waveforms of rectifier.                                            | 54       |

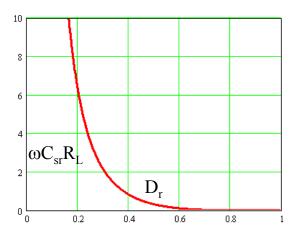

| Fig. 3.13 $\omega C_{rec} R_L \text{vs } D_r$                                      | 55 |

|------------------------------------------------------------------------------------|----|

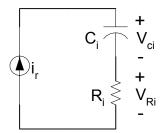

| Fig. 3.14 Equivalent circuit of the rectifier.                                     | 56 |

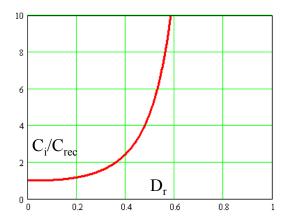

| Fig. 3.15 $R_i/R_L$ as a function of $D_r$ .                                       | 57 |

| Fig. 3.16 C <sub>i</sub> /C <sub>rec</sub> vs D <sub>r</sub> .                     | 58 |

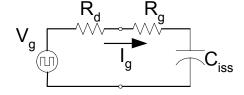

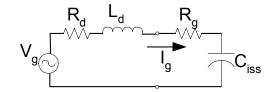

| Fig. 3.17 Simplified equivalent gate drive circuit for the square wave drive       | 58 |

| Fig. 3.18 Simplified equivalent resonant gate drive circuit                        | 60 |

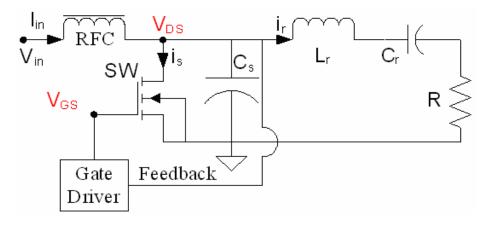

| Fig. 3.19 Class E inverter with self-oscillating gate driver.                      | 61 |

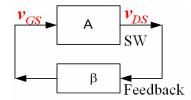

| Fig. 3.20 General Feedback oscillation.                                            | 61 |

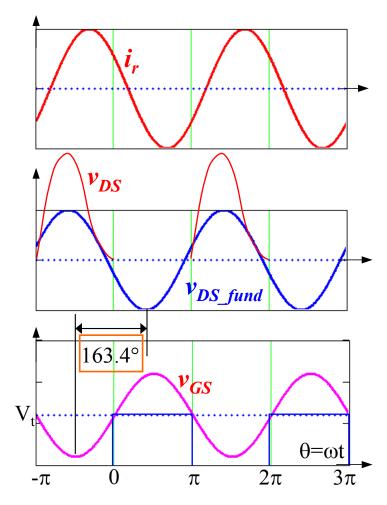

| Fig. 3.21 Phase shift between gate signal and fundamental of drain-source voltage  | 62 |

| Fig. 3.22 Block diagram of basic feedback circuit.                                 | 63 |

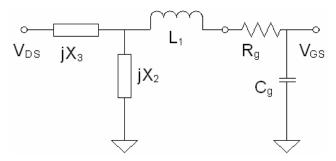

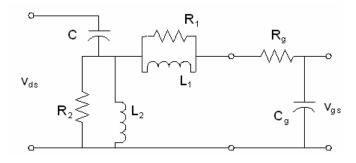

| Fig. 3.23 Simplified feedback circuit.                                             | 63 |

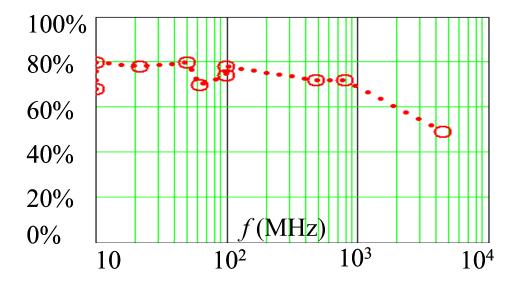

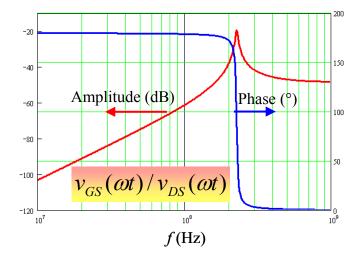

| Fig. 3.24 Frequency response of V <sub>GS</sub> /V <sub>DS_fund</sub> .            | 64 |

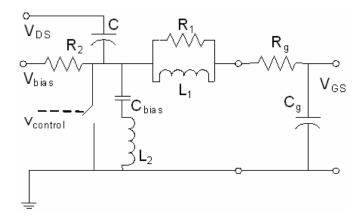

| Fig. 3.25 Feedback oscillating gate driver.                                        | 65 |

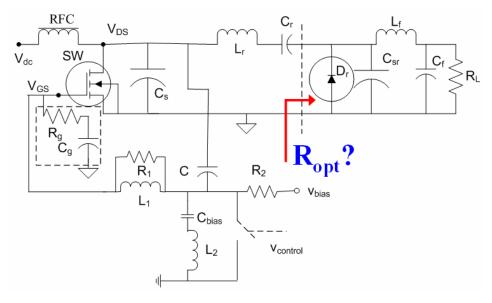

| Fig. 3.26 RF DC-DC power converter.                                                | 66 |

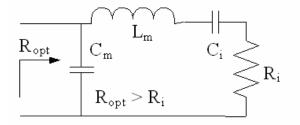

| Fig. 3.27 Matching network for $R_{opt} > R_{pi}$ .                                | 66 |

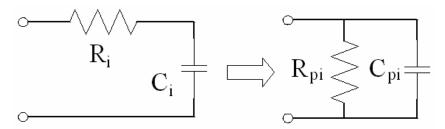

| Fig. 3.28 Series combination conversion into parallel combination                  | 67 |

| Fig. 3.29 Matching network for $R_{opt} \le R_{pi}$ .                              | 67 |

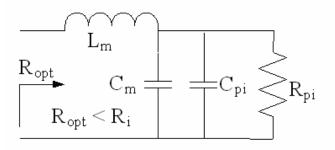

| Fig. 3.30 The proposed RF DC-DC power converter.                                   | 69 |

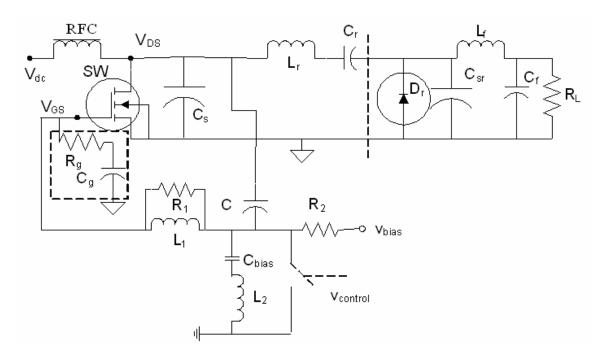

| Fig. 3.31 Prototype of RF DC-DC power converter at 250 MHz                         | 69 |

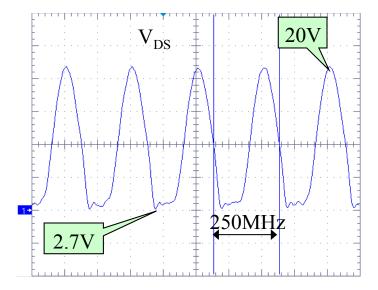

| Fig. 3.32 Drain-source voltage of SW at 250 MHz operating frequency                | 70 |

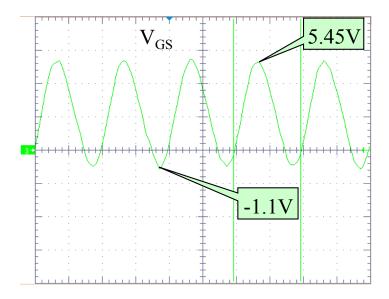

| Fig. 3.33 Gate driver signal of SW in the DC-DC converter                          | 70 |

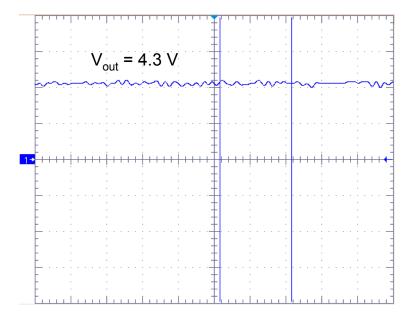

| Fig. 3.34 Output voltage of the converter.                                         | 71 |

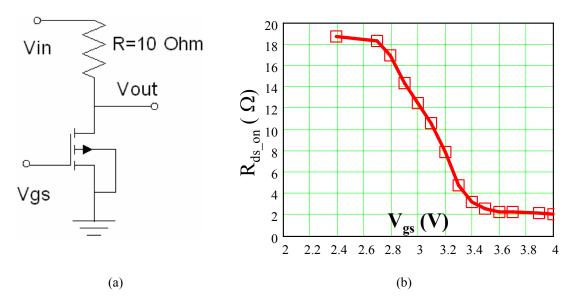

| Fig. 3.35 R <sub>ds on</sub> of SW vs gate-source voltage.                         | 72 |

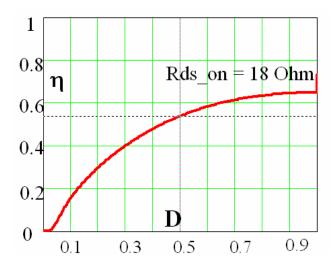

| Fig. 3.36 Efficiency vs Duty cycle for 18Ω ON-resistance.                          | 72 |

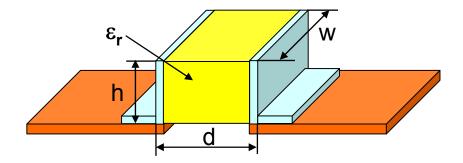

| Fig. 3.37 Series mounting of a chip capacitor on the circuit board.                | 73 |

| Fig. 3.38 Equivalent circuit model of structure above.                             |    |

| Fig. 3.39 Trend-line between power level and frequency of the selected converters  |    |

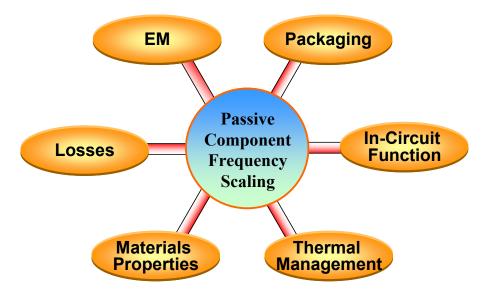

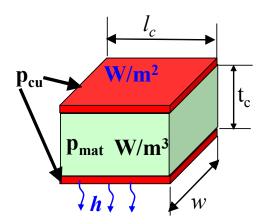

| Fig. 4.1 Multi-disciplinary issues of passive component frequency scaling investig |    |

|                                                                                    |    |

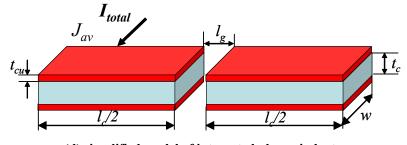

| Fig. 4.2 Structure of the integrated planar passive components.                    |    |

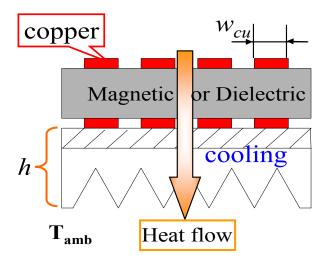

| Fig. 4.3 Simplified thermal model of integrated passive components                 |    |

| Fig. 4.4 Heat transfer of the simplified thermal model.                               | 85    |

|---------------------------------------------------------------------------------------|-------|

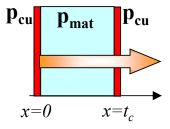

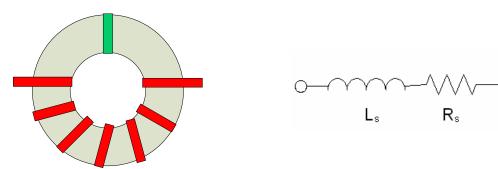

| Fig. 4.5 Toroidal inductor and its series equivalent circuit                          | 86    |

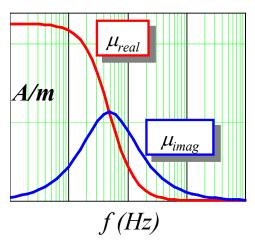

| Fig. 4.6 Frequency dependency the complex permeability.                               | 87    |

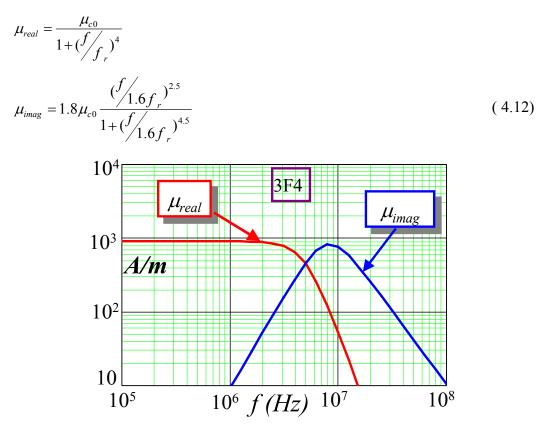

| Fig. 4.7 Complex permeability of 3F4 as a function of frequency.                      | 88    |

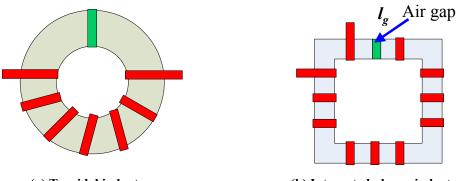

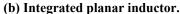

| Fig. 4.8 Various equivalent integrated planar inductors.                              | 89    |

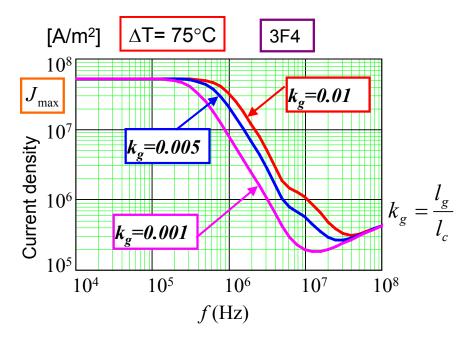

| Fig. 4.9 Maximum current density as a function of frequency.                          | 93    |

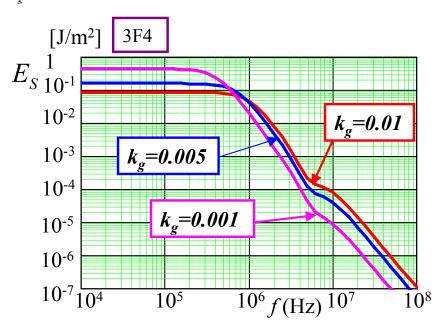

| Fig. 4.10 Energy density as a function of frequency.                                  | 93    |

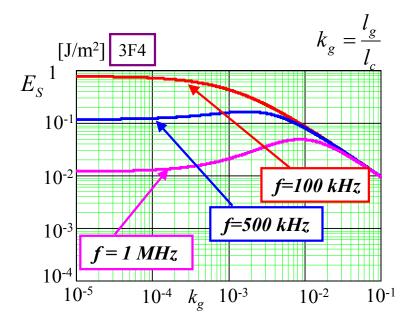

| Fig. 4.11 Energy density as a function of $k_{\rm g}$ for different frequency         | 94    |

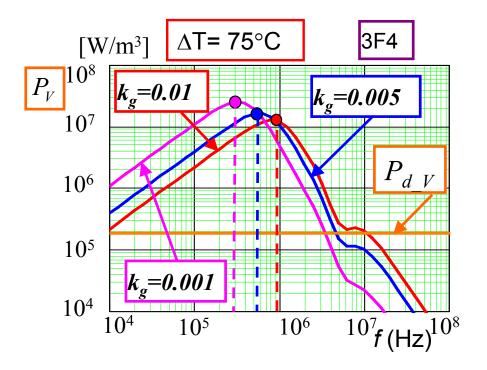

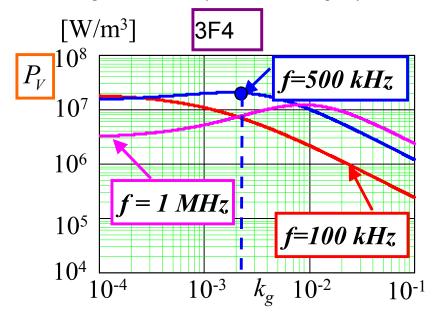

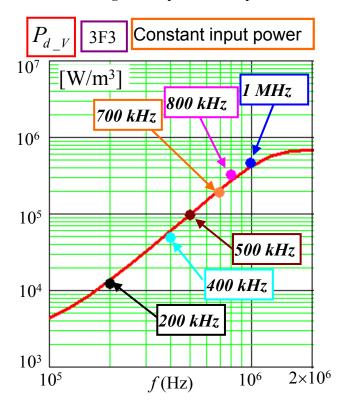

| Fig. 4.12 Power density as a function of frequency.                                   | 95    |

| Fig. 4.13 Power density as a function of form factor k <sub>g</sub> .                 | 95    |

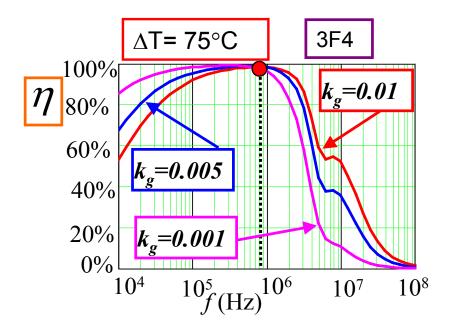

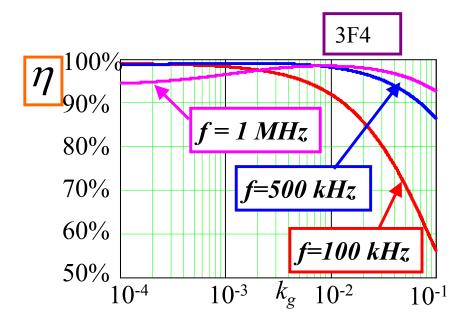

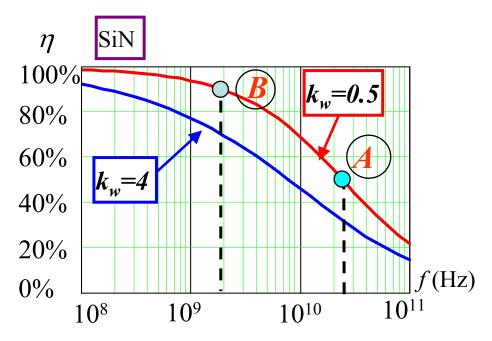

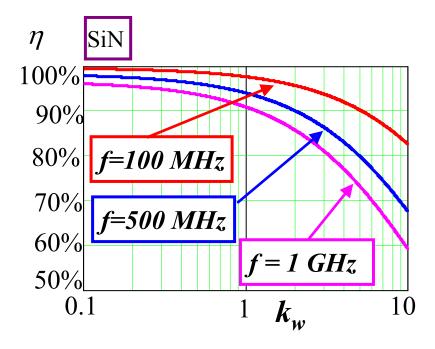

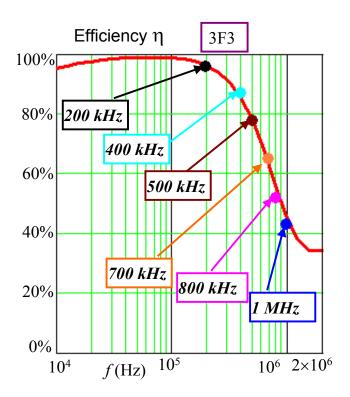

| Fig. 4.14 Power conversion efficiency as a function of frequency                      | 96    |

| Fig. 4.15 Power conversion efficiency as a function of form factor $k_{\rm g}$        | 96    |

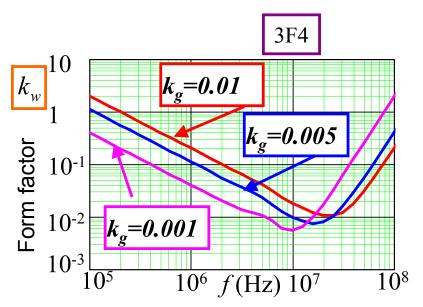

| Fig. 4.16 Form factor $k_{\rm w}$ as a function of frequency.                         | 97    |

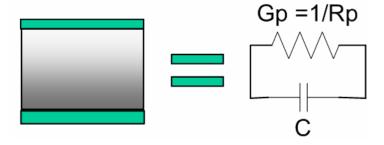

| Fig. 4.17 A parallel plate capacitor.                                                 | 98    |

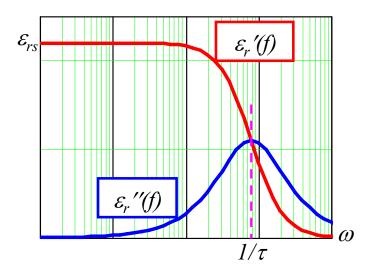

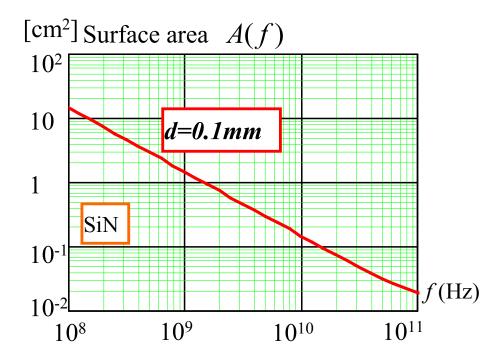

| Fig. 4.18 relative permittivity as a function of frequency                            | . 100 |

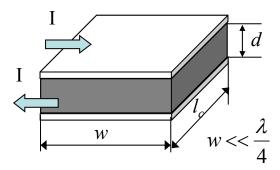

| Fig. 4.19 Integrated planar capacitor with a pair of parallel plates                  | . 102 |

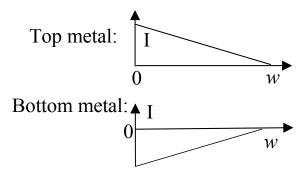

| Fig. 4.20 Current distribution along the plates.                                      | . 102 |

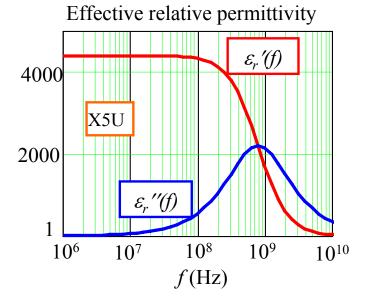

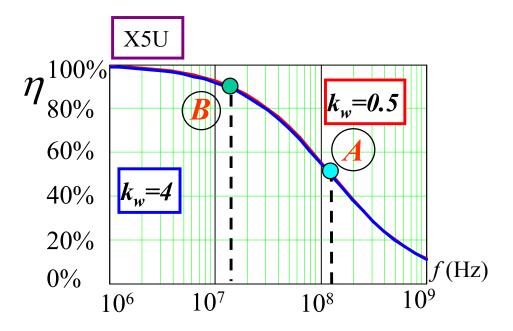

| Fig. 4.21 frequency-dependent relative permittivity of X5U.                           | . 105 |

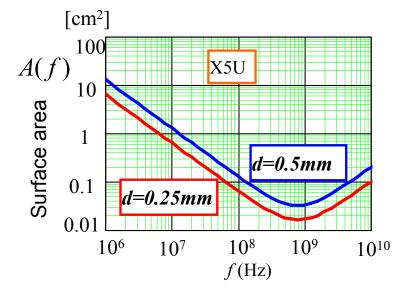

| Fig. 4.22 Surface area changes with frequency.                                        | . 105 |

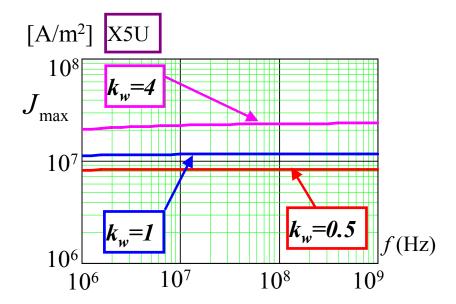

| Fig. 4.23 Maximum current density through the cap as a function of frequency          | . 106 |

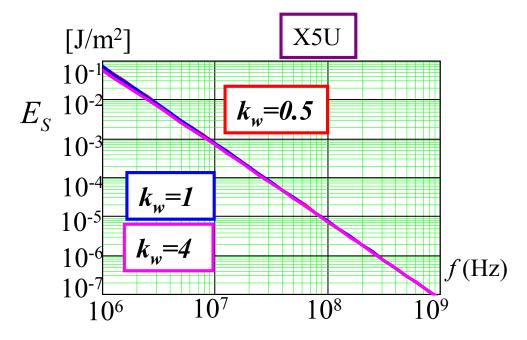

| Fig. 4.24 Energy density vs. frequency                                                | . 106 |

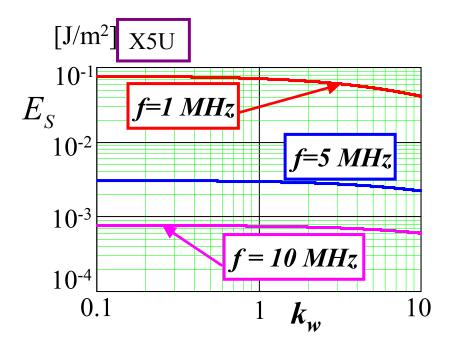

| Fig. 4.25 Energy density vs. form factor $k_{\rm w}$ under different frequencies.     | . 107 |

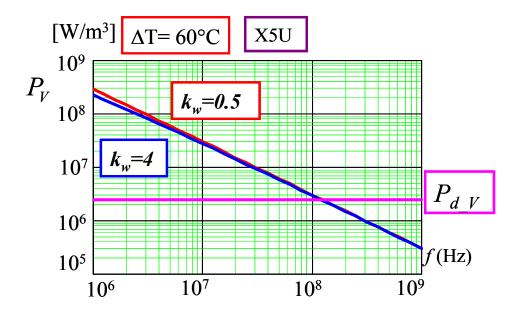

| Fig. 4.26 power density as a function of frequency along with the power loss density. | . 108 |

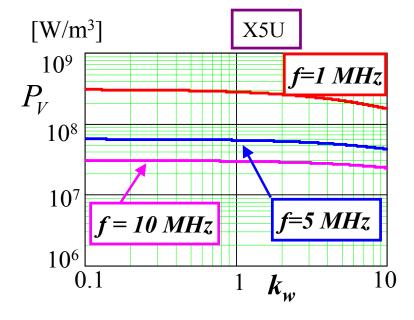

| Fig. 4.27 power density as a function of form factor k <sub>w</sub> .                 | . 108 |

| Fig. 4.28 power conversion efficiency vs frequency.                                   | . 109 |

| Fig. 4.29 power conversion efficiency as a function of form factor $k_{\rm w}$        | . 109 |

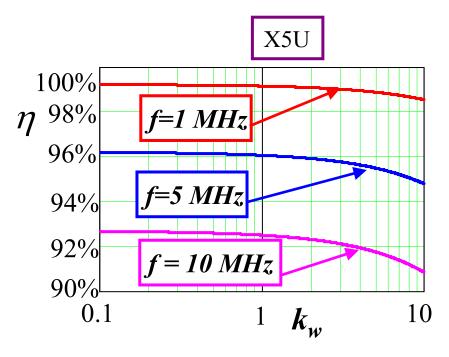

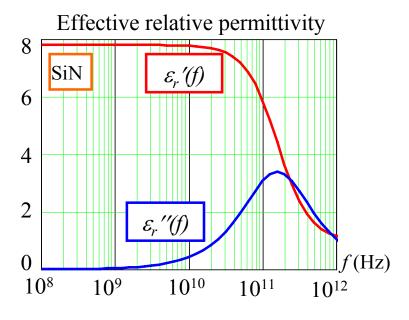

| Fig. 4.30 relative permittivity as a function of frequency                            | . 110 |

| Fig. 4.31 surface area of cap as a function of frequency.                             | . 111 |

| Fig. 4.32 power conversion efficiency vs frequency.                                   | . 111 |

| Fig. 4.33 power conversion efficiency as a function of form factor k <sub>w</sub>     | . 112 |

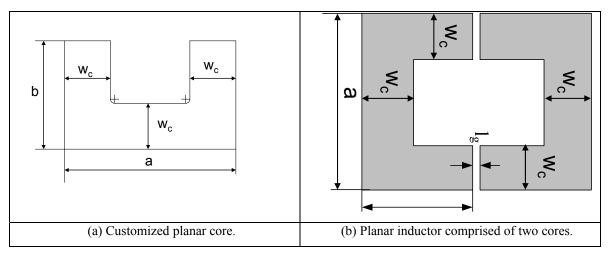

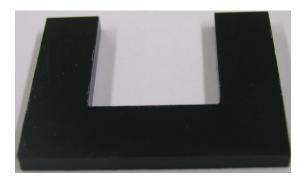

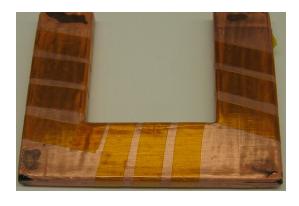

| Fig. 4.34 Customized planar core and the inductor under study.                        | . 113 |

| Fig. 4.35 Inductor sample for experiment.                                              | 113     |

|----------------------------------------------------------------------------------------|---------|

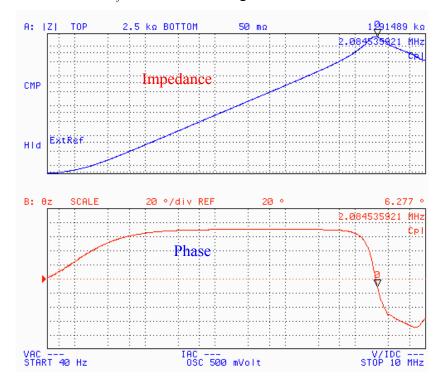

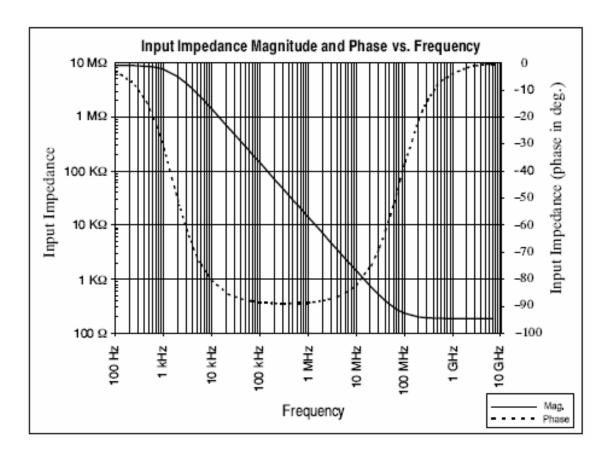

| Fig. 4.36 Impedance characteristics of the inductor.                                   | 114     |

| Fig. 4.37 Diagram of the planar inductor and the chamber.                              | 115     |

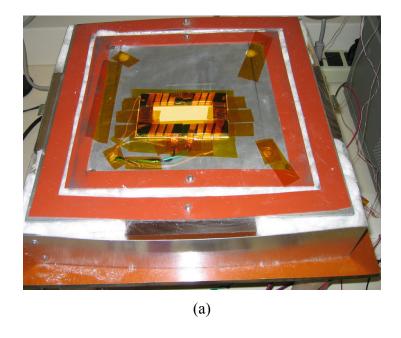

| Fig. 4.38 Experiment setup.                                                            | 118     |

| Fig. 4.39 Measured power loss density as a function of frequency.                      | 118     |

| Fig. 4.40 Measured efficiency as a function of frequency.                              | 119     |

| Fig. 4.41 Measured temperature vs frequency.                                           | 119     |

| Fig. 5.1 Percentage error of loss measurement vs efficiency for given error of voltage | ge and  |

| current.                                                                               | 125     |

| Fig. 5.2 Automated measurement system for core loss.                                   | 127     |

| Fig. 5.3 Percentage error caused by sampling uncertainty in phase angle versus         | phase   |

| angle for different N                                                                  | 127     |

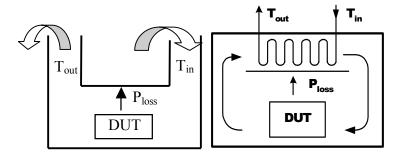

| Fig. 5.4 Types of calorimeter.                                                         | 130     |

| Fig. 5.5 Block diagram of calorimeter illustrated in [141].                            | 132     |

| Fig. 5.6 Block diagram of DCC in [168].                                                | 133     |

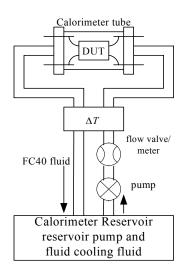

| Fig. 5.7 Flow calorimeter                                                              | 134     |

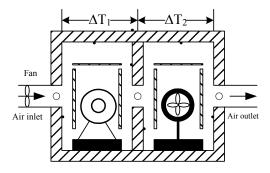

| Fig. 5.8 Schematic of double-jacket calorimeter.                                       | 135     |

| Fig. 5.9 Diagram of calorimetric wattmeter designed in [155]                           | 136     |

| Fig. 5.10 Schematic of calorimeter based on heat flux sensor                           | 137     |

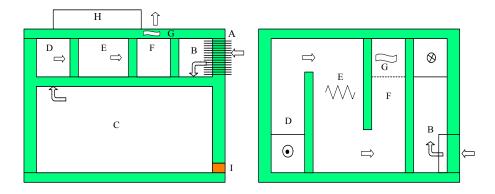

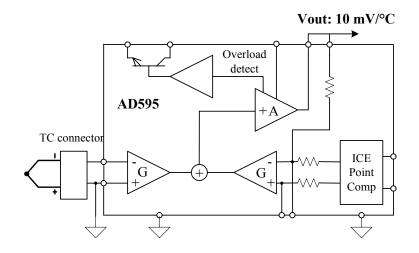

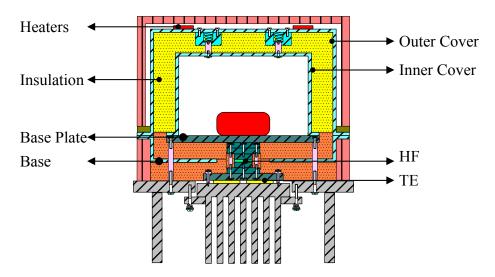

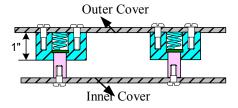

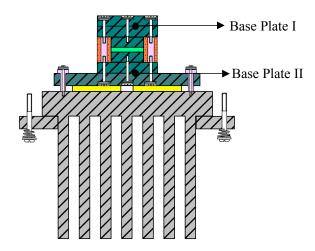

| Fig. 5.11 Schematic of the proposed calorimeter.                                       | 140     |

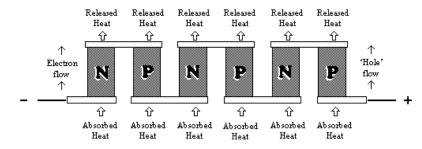

| Fig. 5.12 Schematic of a TE module                                                     | 142     |

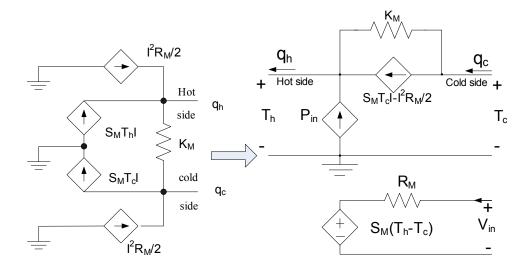

| Fig. 5.13 Equivalent thermal model of TE module.                                       | 143     |

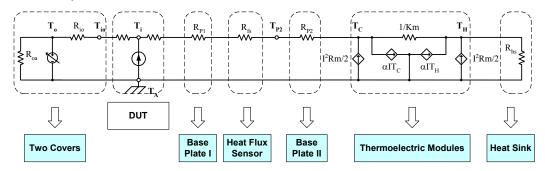

| Fig. 5.14 Complete thermal model of the proposed calorimeter.                          | 144     |

| Fig. 5.15 Locations of temperature points of the calorimeter in the thermal simula     | itions. |

|                                                                                        | 145     |

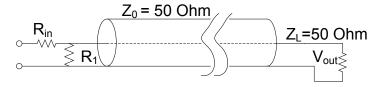

| Fig. 5.16 Thermal model of the power leads into the calorimeter                        | 147     |

| Fig. 5.17 Temperature distribution for 3 diameters of the wire: 0.5 mm, 1.09 mm, as    | nd 1.9  |

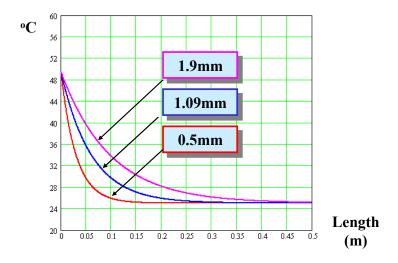

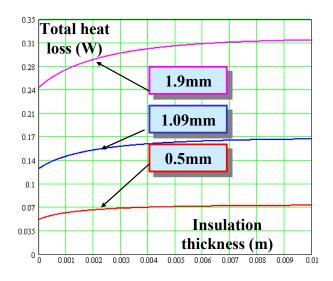

| mm when b=1 mm.                                                                        | 149     |

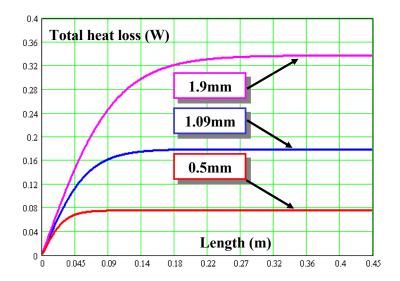

| Fig. 5.18 Total heat loss for 3 diameters of wire: 0.5 mm, 1.09 mm, and 1.9 mm         | 149     |

| Fig. 5.19 Heat leakage as a function of length for given diameters: 0.5 mm, 1.09 mr    | n, and  |

| 1 9 mm when h = 1 mm                                                                   | 150     |

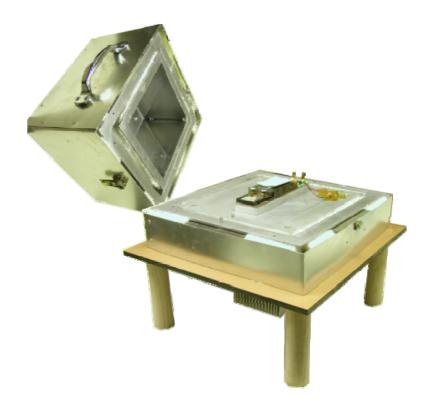

| Fig. 5.20 Prototype of the proposed calorimeter                          | 151 |

|--------------------------------------------------------------------------|-----|

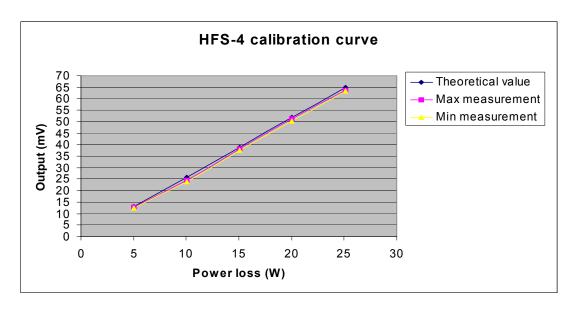

| Fig. 5.21 Comparison between measured results and theoretical values     | 152 |

| Fig. 6.1 Power density and efficiency variation with switching frequency | 157 |

### **List of Tables**

| Table 2.1 Summary of multi-megahertz power converters.           | 31  |

|------------------------------------------------------------------|-----|

| Table 2.2 Physical properties of several semiconductor materials | 35  |

| Table 3.1 Component values of RF DC-DC power converters.         | 68  |

| Table 3.2 Properties of several semiconductor materials          | 77  |

| Table 4.1 Definition of design constraints.                      | 92  |

| Table 4.2 Dimensions of customized ferrite core                  | 113 |

| Table 4.3 Dimension and properties of the parts in Fig. 4.37     | 116 |

| Table 4.4 Measurement results.                                   | 117 |

| Table 5.1 SOURCE BANDWIDTH VS. SYSTEM BANDWIDTH                  | 129 |

| Table 5.2 Date of heat flux sensors                              | 141 |

| Table 5.3 Dimensions of the covers.                              | 145 |

| Table 5.4 Simulation results of the apparatus                    | 146 |

| Table 5.5 Calibration results                                    | 152 |

### **Chapter 1 Introduction**

### 1.1. Background

Two of the most important performance criteria accompanying the application-driven trends in DC-DC power convertsion today are power density and efficiency. Higher frequencies and higher levels of integration are necessary to increase power density. It is predicted that power densities of about 20 W/cm<sup>3</sup> to 30 W/cm<sup>3</sup> will appear around 2015 and switching frequencies 5 to 10 times higher than those of today are necessary to achieve these goals, according to the survey in [6].

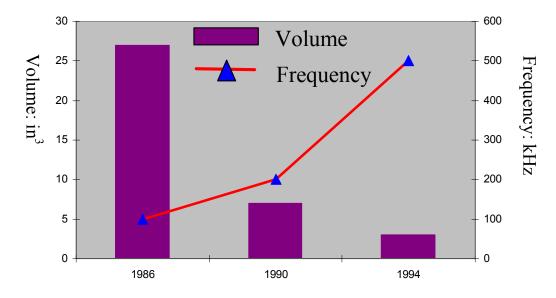

The rationale behind pushing power converter switching frequencies has historically been connected to the desire to reduce the volumes of the electromagnetic passive components, i.e. transformers, inductors and capacitors. An evolution of modular telecommunications power conversion units over a ten-year period is shown in Fig. 1.1 [2]. During that period the switching frequencies have gradually risen from the 75-kHz range to the 1-MHz range, which resulted in substantially reduced physical sizes of passive components.

In principle, a higher frequency means that the circuit needs to process a proportionally smaller amount of energy during each cycle for the same amount of power. The sizes of energy storage and transfer components such as filters, resonant tanks, AC-decoupling capacitors, snubbers, power transfer transformers, depending to some degree on the frequency operation, will scale down as the frequency increases. There are several exceptions to this rule, for instance the presence of DC or low frequency harmonics (i.e. a boost inductor with a large DC bias), or other limits on dimensional downscaling, such as voltage isolation thicknesses and safety requirements, (i.e. transformers having HV windings), turns and turns-ratio trade-offs, required cooling surfaces, mechanical or packaging limits, among others.

Fig. 1.1 Size evolution of modular telecom power conversion units [2].

Today the power densities of DC-DC power converters are being driven higher by the application demands more than ever. It is unlikely that demands for smaller volumes, squeezed into lower profiles over smaller circuit real-estate, with better performance, lower cost and, above all, higher efficiencies will relax anytime soon. Over the past several decades, raised frequency has been the dominant factor that enabled dramatic power density increases [1][2]. It is to be expected that these trends towards miniaturization and higher levels of integration will also maintain steady pressure to keep this pace of increasing switching frequencies of power converters.

#### 1.2. Limitations of HF/VHF Power Conversion

### 1.2.1. Introduction

Power converters are moving towards much higher power densities and lower profile to accommodate the available real-estate, volume and profile requirements and cost factors while improving or maintaining efficiency. And more recently there has been more demand for power converters to provide greatly improved transient response to meet the needs of fast switching loads. All these present more and more stringent challenges to power electronics engineers, though a series of improvements in technology with circuits, materials, packaging and switching frequency have already led to unprecedented gains in power densities, efficiency, transient response and reliability of power converters over last decades [1].

### 1.2.2. Monolithic Integration and Converters-On-a-Chip

The continued miniaturization of power converters by pushing switching frequencies up to multi-MHz (even up to hundreds of MHz) ranges, could eventually lead to the ultimate realization of on-chip power conversion. The implementation of power converter-on-chip may be required with functional integration of the devices, controls, magnetics and capacitors. This represents the key research challenge for integration into chip scale package, which will result in the actual mixing integration of analog, digital, and RF or power circuitry on the same packaging structure. There are several advantages to VHF power conversion as described below:

- ✓ Firstly, a miniaturized power converter can be easily placed closer to the load to reduce voltage drops due to interconnect resistances and inductances. This can also facilitate the power requirements of high current, rapidly changing load demanded by the microprocessors and new generation ICs in the future-computer and in telecom applications.

- ✓ Secondly, higher operation frequency of the monolithic power converter can improve the transient response, which is especially beneficial to the voltage regulator module in the microprocessor. Note that today, the push for higher frequencies is not only from the standpoint of reducing size, but also for improvements in the transient response. In the VRM application, a moderate compromise of efficiency seems to be acceptable if transient response can be improved sufficiently [1].

- ✓ Thirdly, a higher operation frequency facilitates tighter voltage regulation required in modern microprocessors and new generation ICs with smaller filters.

- Fourthly, monolithic power converters can easily be distributed all across the system to supply different loads, as opposed to having external power converters [4]. This enables another level of single-chip and on-chip power conversion. Power supplied from a board-mounted module or regulator module can be further broken down into smaller chip-like solutions to optimize the power management. For applications such as mobile phones, this can be important for various voltage levels required within the chip [4].

- ✓ Finally, minimization of the areas occupied by fully integrated power converters is critical in ultimately reducing the production cost.

### 1.2.3. Modeling and Design

Improvements in converter performances, size, weight and cost along with the increasing switching frequency have been achieved mainly through the technological advances and improvements in devices, materials, components and circuit designs, packaging techniques, and better thermal management. Therefore the efforts to achieve higher power density while maintaining or improving efficiency by means of pushing switching frequencies involves coupled multi-disciplinary issues in electrical, thermal, mechanical, and material properties of the components and packaging. However, it is also important to note that further advances are becoming more limited since certain fundamental limits in high frequency power conversion are being reached as the switching frequency is becoming higher and higher. These fundamental frequency limitations should be identified and understood for future high-frequency high-efficiency power conversion technologies.

### 1.2.4. Semiconductor Device Technologies

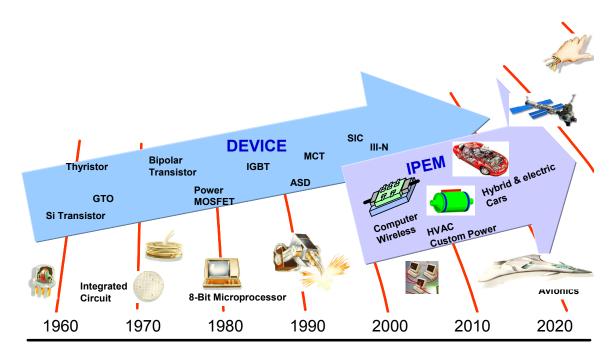

Every major increase in frequency would have been impossible without the advances in power semiconductor device technologies. From the original mercury arc devices to the present mainly silicon-based devices, the technology has seen a device volume reduction of 3~4 orders of magnitude – depending somewhat on power level [3]. Semiconductor devices capable of operating up to GHz range are already available thanks to the continued advancement of the technology. The evolution and future trend of power semiconductor devices are shown in Fig. 1.2. Accompanying the advances in semiconductor devices is the simultaneous increase of the switching frequencies [1]. Fig. 1.3 shows the progression of increases in switching frequencies concurrent with evolution of semiconductor technologies.

Fig. 1.2 Evolution of power semiconductor devices.

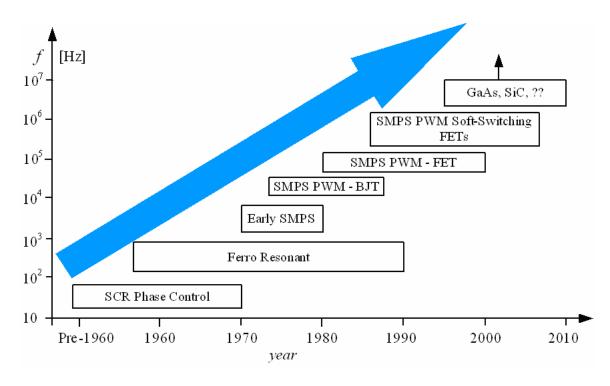

Fig. 1.3 Frequencies of different power supply technologies used in power conversion vs. time.

Notably, the introduction of the power MOSFETs in the early 1980's pushed switching frequencies into hundreds of kHz, then into MHz ranges with the applications of soft-switching techniques that later took advantage of the parasitic components in the circuitry [5] by means of functional integration. Modern device technologies are steadily bringing us closer to radio frequency power conversion at hundreds of MHz, even up to GHz, with continuous scaling, i.e., shrinking size (gate length), radical improvements in processing technology and development of new device structures (such as RF MOSFETs or MESFETs) [29].

Despite the fact that 3~4 orders of magnitude volume reduction have already been achieved in power semiconductor devices that can operate up to GHz frequencies under certain conditions, most power converters still operate well below the low megahertz range today and only an order of magnitude reduction in the overall volume has been achieved over the past 50 years [3]. This reflects some of the challenges peculiar to higher frequency power conversion. Clearly, there are limiting factors that seem to inhibit

further increases in switching frequencies. Exactly what they are and where the limit lies are not well understood, and not so clear.

## 1.2.5. Circuit Toplogies and Control Strategies for VHF Power Conversion

#### **Load-Range Requirements**

Firstly, power converters must operate efficiently over a wide load range from a variable input voltage. However, existing circuit topologies and control strategies commonly used at low frequencies become unsuitable when used at such high frequencies (tens of MHz ~ hundreds of MHz). The operation of conventional PWM DC-DC power converters becomes limited due to very short transition times. The resonant, soft-switching techniques are essential for operation in the HF/VHF ranges. Moreover, appreciable circuit parasitic values must be cleverly exploited to reduce power losses. This approach is effective for full load conditions, however, the circulating current losses are typically unacceptable in systems that must operate efficiently over a wide load range.

#### Output Regulation

Output regulation represents another challenge for VHF frequency operation. Controlling and regulation methods employed in conventional power converters are no longer suitable for VHF power converters. In order to ensure efficient operation and required regulation under wide load range and variable input, a new system structure is required to overcome these difficulties, such as the structure proposed in [18][19]. It is comprised of many cellular switching power converters to increase the total power level. The output regulation can be implemented by adjusting the number of the operating converter cells according to the variable load and input. In this way every operating cell in the structure will always operate at an optimum operating point so that maximum efficiency can be maintained even under light conditions. The control circuitry can be implemented in digital micro-controllers.

#### **Converter Dynamics**

Moreover, converter dynamics and control circuit implementation complexities escalate at higher switching frequencies. Therefore, innovative circuit topologies and control circuitries are needed to solve these problems and make power converters operate efficiently at HF/VHF.

## 1.2.6. Device Characteristics for future HF/VHF conversion technologies

Power semiconductor devices with high speed and low loss must be developed in order to achieve a dramatic increase in switching frequency and still allowing acceptable efficiencies. The frequency-dependent losses of the power devices in the power converters, including gate drive losses and switching losses, increase as functions of frequency. Switching loss is associated with switching when both voltage and current are changing and energy exchanges taking place with drain-source capacitances that are discharged during every cycle. To reduce this loss, soft-switching techniques are often employed. For example ZVS (zero-voltage-switching) can virtually eliminate the losses associated with the drain-to-source capacitance.

Gate drive loss is the result of energy transfer induced by charging and discharging the gate capacitance of power devices. Gate drive loss increases almost linearly with switching frequency. This loss often becomes a limiting factor for high frequency operation. To reduce the loss, the energy can be recovered and reused in subsequent cycles by employing resonant gate drivers. Thus, the desired characteristics of future devices for high switching frequency are smaller gate capacitances and resistances.

Conduction loss is proportional to the on-resistance of the devices. Lower onresistance of the devices will result in lower conduction losses. However as frequency is pushed higher, the conventional power devices are approaching their performance limitations imposed by their material properties. The inherent design trade-off lowering ON-resistance AND reducing capacitance in a power device, should be optimized for high speed and high efficiency operation. The power-frequency products of semiconductor devices also limit the achievable power densities. Thus a future HF/VHF power conversion technology will require further advances in the device technologies. Novel structure and wide band-gap semiconductor devices, such as silicon carbide and gallium nitride devices, as well as novel silicon devices like a super junction FETs, are under way for breaking through the device limitations [6] to achieve the low gate capacitances and resistances while maintaining reasonably low on-resistances.

### 1.2.7. Passive Components

Compared to the performance improvements in the power devices, it is clearly the inadequate performance of passive components where we must turn our attention to. In seeking equal or greater benefit by reducing volumes of passive components more commensurate with those of the power devices, radical increases in operating frequencies are required. Unfortunately, no major breakthroughs have been achieved in the passive materials for high frequency operation, and passive components still dominate the volumes of power converters.

#### Magnetic components

In the continued efforts to minimize power converter volume, the miniaturization of energy storage and transfer passive components is usually the most difficult obstacle, especially for magnetic components. At lower switching frequencies, the passive components dominate the volumes of power converters. The losses associated with capacitive components or magnetic components are small for low frequencies. But at higher frequencies, the losses become the most important consideration. For most ferrite materials, core losses increase dramatically with frequency in the megahertz range because the eddy current losses, hysteresis losses and HF copper losses increase with frequency. The rapid increases of core losses offset the volumetric utilization and inhibit the increase of switching frequency due to efficiency or thermal constraints. The permeabilities of ferrites also depend on frequency. As a result, higher switching frequencies do not always lead to smaller sizes of magnetic components.

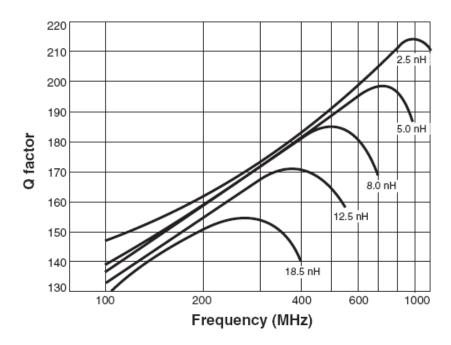

However, the trend to smaller magnetic components at higher frequencies has driven many new research efforts to develop new magnetic materials and fabrication techniques [7][8] to optimize the high frequency performance. The thin-film or microfabricated magnetic components usually operate below 10 MHz at present. But the permalloy, ferrite polymer compounds and other materials appear to be promising for higher frequency operation [9]. Most of the thin-film magnetic materials to date have been restricted to low power conversion and limited current handling capability. This suggests that in order to increase current handling capability and power level, magnetic materials with high resistivity, low coercivity, and high saturation magnetization are required along with the capability of being deposited in multi-layers. It is interesting to note that some soft magnetic materials with such features have been addressed in a 3.3- to 1.1-V, 7A dc-dc converter at frequencies beyond 10 MHz [10]. On the other hand, if the operation frequency of the power converter can be increased sufficiently, the magnetic components can be implemented without magnetic cores due to low inductance required. This provides an opportunity to integrate the magnetic components on silicon wafer, allowing further integration with power devices and control circuitry within a single silicon die. Silicon-integrated magnetics should achieve reasonable component size and quality-factor Q with some improved fabrication techniques such as micromachining techniques proposed in [11][12].

Therefore, in order to achieve dramatic reductions in magnetic components sizes, either new magnetic materials that do not suffer frequency-dependent loss limitation are required, or the operating frequencies of power converters must be sufficiently high so that air-core magnetics can be employed effectively.

#### Capacitive components

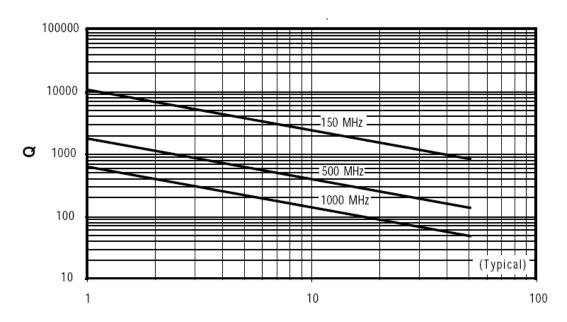

Compared to the semiconductor devices and the magnetics, capacitor technologies are already suitable for frequencies of 10 MHz and beyond through advanced manufacturing techniques and new materials. This has primarily been stimulated by the improvements in ceramic capacitors with high values of capacitance per unit volume, ultra-low ESL and ESR. Ceramics can potentially take the lead in this regard, particularly

with the recent advent of new materials and multilayer ceramic capacitors, which have demonstrated production capacitance scalability (>  $10~\mu F$ ). Capacitor development for the future will focus on smaller grain size of dielectrics to allow thinner dielectric processing. A new evolving "nanostructure multilayer" capacitor technology mentioned in [13], getting inorganic high dielectric constant coatings built up by interleaving electrodes in a multilayer construction, shows a great potential for HF/VHF power conversion. Typical examples of such materials are ZrTiO<sub>3</sub>, TiO<sub>2</sub> and CaTiO<sub>3</sub>, which are  $0.1-10~\mu m$  thick and contain 100-10000 layers.

Ultimately, the dielectric materials are also limited due to their frequency-dependent properties, i.e., the dielectric constant, a complex quantity, that changes with frequency. A higher switching frequency leads to the increased losses including dielectric loss and Ohmic loss, and derated performance of a capacitor. In order to achieve higher frequency operation with higher efficiencies, better materials are required to reduce capacitor dissipation factor by 1/3 to 1/10 and increase capacitor energy and power densities 2 to 10 times those available today [13].

### 1.2.8. Packaging and Integration Techniques

High frequency conduction losses [14] and increased contact resistances in conductors or interconnections, due to the skin effects, proximity effects or the distributed effects at HF/VHF, become more pronounced, resulting in distorted performances and reduced efficiency. Radiation leakage and losses become more severe, thermal noise must be accounted for, and new scaling laws come into effect. Therefore, higher levels of integration and packaging techniques are critical to minimize these adverse effects physically. Merely extending conventional packaging could bring about modest improvements in electromagnetic characteristics, enabling higher frequencies as a result of better discrete layout, tighter packing of components, smaller parasitic planning of interconnections, better heat-sinking, lower profile and modular construction. But it is not enough to achieve the order of magnitude improvement that is really needed [3]. A more aggressive packaging approach is necessary to develop higher levels of integration.

A number of technologies, such as the Metal Post Parallel Plate Structure (MPIPPS), Buried Power Technology, Power Overlay Technology, and Flip Chip on Flex Technology, have been developed to allow lower inductance interconnection structures, better thermal management and flat integrated packages. To be one of the promising candidates in this field, it is essential to develop a 3D integrated system approach in the form of a highly Integrated Power Electronics Modules to incorporate electromagnetic integration of passive components, non-wire-bond power stage integration, advanced materials and thermal management – and eventually advanced power semiconductor devices for the further development of power conversion.

#### 1.2.9. Thermal Management

More advanced and more efficient thermal management will also be required to effectively remove the heat through smaller surface areas to satisfy the increasing demand for faster, smaller, lighter, cheaper and more reliable HF/VHF power converters. The average power densities and heat dissipation rates have increased nearly two-fold in the last decade. The common cooling techniques such as heat sink and heat pipe technologies will no longer be capable of meeting the thermal management demands of future systems. It is obvious that more aggressive thermal management techniques are required to handle the increased heat loads at this level of integration. There are many technologies emerging but the most promising in the near future are liquid cooling, refrigeration and spray cooling. Other technologies include embedded micro-heat pipes, micro- or mini-channel heat sinks, and micro-machined air-jet array impingement, among others [20], to name but a few.

#### 1.2.10. Measurement Issues

The measurements of the electrical quantities are becoming more challenging with the power converters advancing into higher frequencies, higher efficiency, and smaller volume. For high frequency signal and highly distorted signals, conventional

measurement equipments are no longer suitable due to their limited bandwidth and dynamic frequency response limitations. The interferences from high dv/dt or di/dt signals, the intrusion of probes or oscilloscopes into the circuits, among others, all contribute to aberrations of the measurements. Among these, accurate power loss measurements are becoming increasingly difficult as frequency and efficiency are being pushed higher.

In summary, the implementation of HF/VHF power converters is limited by many coupled multi-disciplinary issues in electrical, mechanical, thermal, material properties. These fundamental frequency limitations include:

- Circuit topology and control strategy;

- Power semiconductor device technology;

- Energy storage and transfer capabilities of passive components;

- Packaging, interconnection, and integration techniques;

- Thermal management;

- Measurements.

### 1.3. Objective of this Study

The objective of this thesis is to systematically investigate the fundamental frequency limitations for HF/VHF power conversion technology. The main aim is to provide necessary tools for analysis and design towards optimizing power density and efficiency by maximizing frequency. The necessary guidelines will be provided to identify the fundamental reasons of the limitations. Since the investigation involves complex and coupled multi-disciplinary issues coupled in various ways, a good qualitative insight into the frequency scaling effects and the tradeoffs between different performance functions is indispensable in understanding the HF/VHF performances in order to optimize the design. The dissertation is arranged as follows:

## 1.3.1. Chapter 2: HF/VHF Power Conversion Technology Review and Discussion

In this chapter numerous multi-megahertz switching converters, that were demonstrated successfully in the literature, are reviewed, trends are recognized and some conclusions are drawn from these trends. The topologies and power conversion technologies suitable for high frequency operation (> 10 MHz) are described. The implementations and main features of these converters are summarized. In regards to the development of HF/VHF power conversion, the trade-offs between the power level and the operating frequency are identified and illustrated. A general relation about the power-frequency limit is derived from the physics of the semiconductor devices, which show how the ultimate limitations depend on the material properties of the semiconductor devices in the converters.

## 1.3.2. Chapter 3: Analysis and Design of RF Class E DC-DC Power Converter

In this chapter the DC-DC power converter derived from Class E power amplifier is analyzed. The operating principles and designs of this kind of converter are described in detail. The Class E DC-DC converter is a promising option for operating at radio frequencies and beyond due to its excellent soft switching characteristics. A prototype 250 MHz power converter is designed and implemented with discrete surface mount components along with the experiment results. A theoretical guideline is discussed about how to optimize the semiconductor devices to reduce power losses incurred in the device and improve the efficiency for HF/VHF power conversion. A criterrion for comparison, the product of on-resistance and input capacitance of device, is identified in terms of semiconductor material properties for high frequency and high efficiency power conversion.

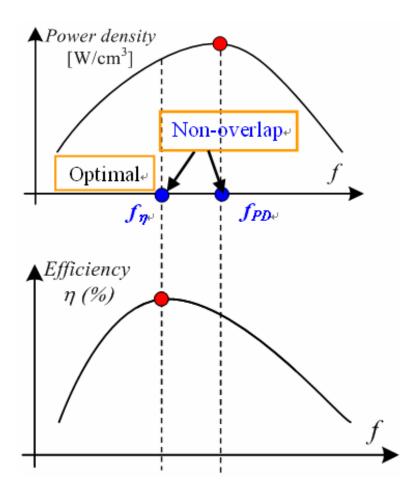

## 1.3.3. Chapter 4: Fundamental Frequency Limitations of Passive Components for HF/VHF Power Conversion

The frequency scaling limitations of integrated passive components are discussed in this chapter. As mentioned earlier, increasing frequency has been the primary approach for reducing passive component volumes. It is also a well known fact that at some frequency no further advantage is obtained, and yet it is unclear where this 'optimum' frequency (or limit) lies. This chapter addresses this question. A methodology is developed to theoretically analyze the complex multi-disciplinary interplay of design parameters, to maximize frequency whilst optimizing performance of integrated passive components for power conversion in terms of efficiency and power density. Among others the materials, thermal management, packaging and in-circuits functions are considered. The performances of integrated planar magnetic components and capacitive components in terms of power density and power conversion efficiency are evaluated as a function of frequency scaling. The analysis demonstrate how the methodology can be used to identify the most optimum power conversion frequency for a given set of specifications, circuit function, selection of materials and packaging technology and limitations, and thermal constraints.

## 1.3.4. Chapter 5: Power Loss Measurement Techniques for HF/VHF power conversion Applications

Finally, measurement techniques are discussed for high frequency applications. Emphasis is placed on power loss measurement techniques, including electrical and thermal techniques, along with their advantages and disadvantages. The electrical power loss measurement techniques are limited by their large errors even with highly sophisticated digital equipment. In theory higher accuracy is possible by measuring loss directly. Calorimetric methods provide the means for measuring losses directly and consequently, it is considered to be the most promising method available for accurate power loss measurement. This method has the advantage of being able to measure the power losses under normal operating conditions and being independent of electrical

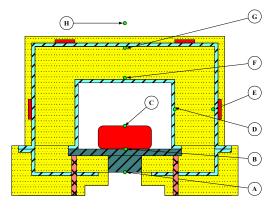

quantities of the device under test. A calorimeter suitable for accurate power loss measurement is proposed and described in this chapter. The measurement system is based on the principle of direct measurement of heat flux. It can implement temperature control and can measure heatsink-mounted components such as active IPEMs, passive IPEMs, and integrated magnetics. A prototype is built and the calibration result of this calorimeter demonstrated about 5% error in total losses.

# Chapter 2 HF/VHF Power Conversion Technology Review and Discussion

#### 2.1. Introduction

To examine how switching frequencies in power converters are being pushed higher and higher, some published literature that discuss power converters having switching frequencies of 10 MHz and beyond are reviewed in this chapter.

Since 1970's, there have been major efforts from researchers to achieve high power density and faster transient response of DC-DC converters by increasing switching frequency. High efficiency and high switching speed are of critical importance to achieve the design objectives in these high frequency DC-DC power converters. As a result new techniques and converter topologies have emerged to realize high frequency operation, such as ZCS and ZVS resonant switching techniques [30], and of RF Class E resonant converters [31][32]. The availability of devices and new VLSI processes have enabled DC-DC converters operating beyond 10 MHz [33][34][35]. Efforts to operate these circuits beyond 10 MHz have been plagued with a number of problems, limiting the overall conversion efficiency and power density of converters.

Basically, HF/VHF DC-DC power converters can be implemented in two ways. One is the improvement of conventional PWM converters such as Buck converters, Boost converters and Flyback converters. The other method is the introduction of new topologies and architectures such as Class E converters. These two kinds of methods are described below.

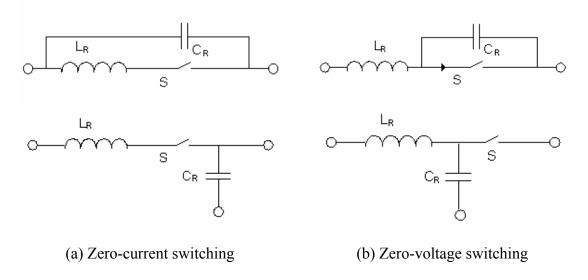

## 2.2. Resonant switching techniques in conventional converters

One of the fundamental limitations towards increasing the frequency of conventional PWM power converters is the presense of parasitic elements in the circuit. There are two ways to deal with this problem. The first is to minimize the parasitic elements in the circuit. However, it is impossible to reduce the parasitics beyond a minimum level, e.g. for offline converters [36]. Another approach is to use resonant switching techniques to employ the parasitics to the circuit's advantage and include the parasitics in the circuit design. Popular methods using this technique are zero-voltage switching (ZVS) and zero-current switching (ZCS). The basic structures of resonant switch are shown in Fig. 2.1.

Fig. 2.1 Basic structures for soft resonant switching

The essence of ZVS is to shape the drain-to-source voltage waveforms of devices so they become zero prior to turning on. The ZCS technique shapes the device's current waveform so that the device is turned off when its current is zero [30]. Thus the resonant switching techniques allow very low switching losses and permits efficient operation at increased frequencies. ZCS is somehow limited to the lower megahertz range since this

technique can not solve the problem of switching loss associated with capacitive discharge at turn-on [30].

There has ever been intensified efforts on resonant converters to operate in the 2-20 MHz range in the mid to late 1980's [1][37]. In [37] Buck and Flyback ZVS quasi-resonant converters (QRC's) were presented. The experimental results of Buck ZVS QRC (Fig. 2.2a) showed switching frequencies from 6.6 MHz at 25 W to 16.7 MHz at 2.5 W and 80% efficiency at full load. However, a high voltage stress in the order of 8 times the input voltage for a 7:1 load range, was applied to MOSFET. The experimental Flyback ZVS QRC in Fig. 2.2b operated from 3 MHz at 20 W with  $V_{in} = 45$  V to 13 MHz at 5 W with  $V_{in} = 60$  V,  $V_{out} = 5$ V. Efficiency of the converter was typically 70%.

Fig. 2.2 Basic circuit diagram of ZVS QRC in [37].

In summary, the ZVS technique is suitable for very high frequency operation. However high voltage stress made single-ended ZVS converters unsuitable for wide load range applications.

## 2.3. High speed switching devices in conventional Converters

Conventional MOSFET-based converters may operate at frequencies as high as 10 MHz by using novel switching techniques such as ZVS or ZCS. But increasing operating frequencies above 10 MHz for such converters necessitates new advanced power semiconductors with high speed and low losses. Incorporation of such new devices

into conventional power converters for high frequency operation has been successfully demonstrated in the literature as described below.

High speed GaAs vertical field-effect transistors (VFETs) with less than 2ns switching have been incorporated in 10 MHz, PWM Boost and Buck 5 W power converters that demonstrated good efficiency (>85%) and very high power densities (500 W/in³) [33]. Benefits of GaAs VFETs over silicon MOSFETs include: 10-to-1 improvement in switching speeds, and reductions in specific resistances and device capacitances. GaAs VFET lacks the parasitic diode of a MOSFET, reducing reverse recovery losses. The two drawbacks of the device technology at present are its normally-on characteristics caused by depletion mode operation and technological immaturity.

In [38] a PWM boost converter with an operating frequency of 10 MHz was implemented with GaAs's HBT's in hybrid form for a portable wireless transmitter to meet the requirements of smaller size and higher bandwidth. Power efficiency at 1 W with 74% efficiency was reported in this literature.

Gallium Arsenide (GaAs) MESFET power switches like MESFET and Schottky barrier rectifiers applied in Buck [39], Boost [40], Cuk [43], Flyback [44] DC-DC converters have allowed switching frequencies up to 100 MHz, even up to 250 MHz [42]. The primary advantages for using GaAs over silicon are low ON resistance, low voltage, fast switching speed, and semi-insulating substrate [39]. This mainly comes from intrinsically higher electron mobility of GaAs (5000 cm<sup>2</sup>/Vs for GaAs, 600 cm<sup>2</sup>/Vs for silicon with  $10^{17}$  cm<sup>-3</sup> doping density) and higher energy bandgap. Since the on-resistance to input capacitance factor  $R_{on}C_{iss}$  is inversely proportional to the electron mobility, GaAs switches are expected to provide much lower power losses than silicon switches [41].

A 40 MHz to 100 MHz step down 10 V to 5 V (8 V) converter using GaAs power MESFET was demonstrated with an output power of 2.6 Watts and power efficiency of 77% at 40 MHz in [39]. A prototype based on hybrid circuit technology was implemented on an alumna subtrate with 1 A - 15 V X-band power MESFET, an X-band

MESFET based gate driver, a 110 nH – HF ferrite based very low loss inductor and various DC decoupling chip capacitors. Experimental results of the converter are shown in Fig. 2.3. If a MESFET power transistor with 0.5 Ohm ON state resistance instead of 4 Ohm in the prototype was used, more than 85% efficiency could be achieved at 100 MHz.

Fig. 2.3 Experimental results of Buck in [39].

A GaAs-based 5 V/10 V - 2 W Boost converter operated at 100 MHz was presented in [40] with 69% efficiency with small passive components: a 23 nH planar inductor (4×4 mm²) and a 47 nF surface mount capacitor (1×2 mm²). The hybrid technology prototype Boost converter was assembled on a 10 mil Alumina substrate. A 0.7  $\mu$ m technology 2 A-12 V commercial MESFET, a 150×150  $\mu$ m 27 V Schottky rectifier and a gate driver were carefully mounted with very tight interconnection ribbons in order to avoid parasitic oscillations.

Two principal limitations of high switching frequencies (>20 MHz) DC-DC converters are: relatively small breakdown voltage of HF switches, and HF losses of passive components. Novel large gap III-V power devices such as heterojunction bipolar transistors (HBTs), high electron mobility transistors and the hetrojunction isolated gate FETs should be investigated for potential use. Concerning passive components, especially ferrite based inductors, the limitations are related to the limited cut-off frequency of UHF ferrite materials (generally < 300 MHz). It should be interesting to

investigate RF techniques by using Transmission Line based components like BALUNs in order to replace conventional inductors and transformers. Also a smart power monolithic technology, that involves the gate drivers and the power devices, would allow us to avoid the effect of the parasitic inductances and reduce the size of the circuit [41][43]. A more compact design should be possible by using MMIC technology.

A simplified comparative theory in [42] highlighted the intrinsic advantages of GaAs over conventional silicon devices for very high frequency applications. Taking into account the maturity and reliability, cut-off frequency of higher than 20 GHz, GaAs MESFET/HEMT devices constitute a real solution for converters operating up to hundreds of MHz like the modulated power supply RF amplifiers. The feasibility of ultrahigh frequency DC-DC converters using GaAs power switches opened new perspectives in the power electronics domain in terms of compact size and speed.

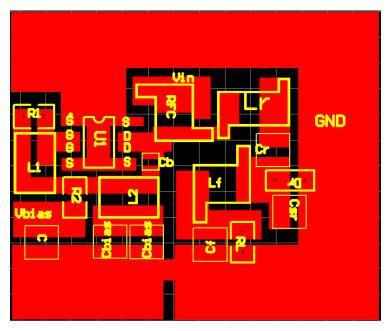

# 2.4. Monolithically integrated conventional power converters by VLSI

High switching frequency is the key design parameter that enables full integration of a high efficiency power converter. By evolving to higher switching frequencies, values of inductors and capacitors are reduced to values that are suitable for integration. Due to tight area constraints, integrated capacitors and inductors above certain values are not acceptable for integration. On the other hand, the VLSI process technology allows us to integrate both active and passive devices of power converters onto the same die. In a typical nonintegrated converter, significant energy is dissipated by the parasitic impedances of the interconnects among the nonintegrated devices (inductors, capacitors, power transistors, and PWM circuitry). An integrated converter on a chip can potentially lower the parasitic losses as the lengthes of interconnects between different components are reduced. Additional energy savings can be realized by utilizing advanced deep submicrometer fabrication technologies with lower parasitic impedances [46][47][48].

Full integration of power converters is challenging because monolithic magnetics technology can't provide high quality inductors. Integrated inductors usually have poor parasitic impedance characteristics: low Q-values and low self-resonant frequencies, which can degrade efficiency of power converters. Therefore new magnetic materials or improved fabrication techniques are required to achieve the desirable characteristics. New integrated microinductor technology using CoZrTa with relatively small parasitic impedances and higher cut-off frequencies (> 3GHz) has been reported in [52]. Therefore on-chip integration of active and passive components of power converters permits switching frequencies higher than typical switching frequencies found in conventional converters. Examples of on-chip integrated DC-DC power converters are illustrated below.

The SiGe BiCMOS process is well suited for portable wireless applications due to its significant advantages: high speed, low noise figure, excellent linearity, and less dependence of speed upon high field strength and supply voltage. It has been successfully applied in a DC-DC power converter for wireless applications. A DC-DC converter design for on-chip integration with a WCDMA power amplifier has been presented in [35] to increase transmitter efficiency and improve battery life. The synchronous rectifier (SR) Buck converter was implemented in IBM's 0.35  $\mu$ m SiGe BiCMOS 6HP process. Simulation results show an average efficiency of 78.8% over power amplifier operating conditions and a peak efficiency of 86%. The converter was optimized for operation at 88.7 MHz. The inductor value (9.1 nH) is small enough to be integrated on-chip, however the series resistance of on-chip inductors (1  $\sim$  2  $\Omega$ ) is too large for power conversion applications. Therefore output inductor and capacitor are implemented off-chip [35] in the converter.

Similarly a 100 MHz two-phase interleaved SR Buck converter was implemented by the use of 0.18 µm SiGe BiCMOS process for wireless applications, but with high quality integrated passive devices [45]. The inductor quality factor limits the efficiency of converter. The inductor quality factor is limited by metal line resistivity, capacitive

coupling to the substrate and magnetic coupling to the substrate. The metal line resistance is lowered by removing the first few internal turns of the spiral inductor, which do not contribute too much to the total inductance. By use of thick electroplated copper layer after the 5<sup>th</sup> layer of Cu metallization and far above the substrate, a high quality factor inductor was implemented [45].

On-die switching DC-DC converters can be fabricated in existing CMOS (80 nm – 180 nm) [47] [51] for future microprocessor power delivery. As pointed out in [51], increasing input voltage to VRM (voltage regulator module), and moving the VRM closer to the microprocessor by integrating it either in the package or the die itself alleviates some problems associated with low voltage, high current distribution networks. In fact, integrating the DC-DC converter onto the same die as a microprocessor can improve energy efficiency, enhance the quality of voltage regulation, and decrease the number of I/O pads dedicated for power delivery on the microprocessor die. Furthermore, reliability of voltage conversion circuitry can be enhanced, area can be reduced, and overall cost can be decreased by using an integrated circuit technology [46].

Comprehensive circuit models of the parasitic impedances of monolithic switching DC-DC converters were presented in [47][48] to analyze the frequency dependent efficiency characteristics of the Buck converter as switching frequency is increased to permit full integration. An optimum circuit configuration with maximized efficiency was derived from this model. The effects of scaling the active and passive devices and the related switching and conduction losses on the total power characteristics of a buck converter were examined. The independent variables of the proposed model in [47] are the switching frequency and inductor current ripple. An estimation of efficiency from the analytical model is within 2.4% of the simulation results at the target design point. An efficiency of 88.4% at switching frequency of 477 MHz was demonstrated by simulation for voltage conversion from 1.2 V – 0.9 V volts while supplying 9.5A current. The area occupied by the converter is 12.6 mm² assuming an 80 nm CMOS technology. By including gate voltages and tapering factors of MOSFETs as independent parameters in the model proposed in [48], estimation of efficiency is now within 0.3% of circuit

simulation. An efficiency of 84.1% at 102 MHz was achieved by simulation for voltage conversion from 1.8 V to 0.9 V assuming 0.18 µm CMOS technology.

In order to achieve the desirable efficiencies at such high frequencies, MOSFET power dissipation reduction techniques were applied to improve the efficiency based on the parasitic circuit models of the monolithic Buck converter (Fig. 2.4) in [47][48]and [51].

Fig. 2.4 Parasitic impedances and transistor geometric sizes of Buck converter.

Firstly, an optimum MOSFET channel width exists that minimizes the total MOSFET related power, due to the fact that increasing MOSFET width reduces the conduction losses while increasing the switching losses.

Secondly, the impact of tapering factor on maximum efficiency is also analyzed [48]. As shown in Fig. 2.5, at a certain range of tapering factor, dynamic switching losses dominate the total losses. The efficiency increases with higher tapering factor in the range dominated by switching losses. After peak efficiency is reached, increasing short-circuit losses in the power MOSFET gate drivers begin to dominate. Hence, efficiency degrades

with further increasing tapering factor. The optimum tapering factors are 10 and 16 for the full-swing and low swing circuits, respectively [53].

Fig. 2.5 Maximum efficiency with low-swing (LS) and full-swing (FS) Buck converters vs. tapering factors.

Another technique to improve the efficiency, involving low swing MOSFET gate driving, was investigated in [48] [53] to improve the efficiency of a DC-DC converter. The total power dissipation of the low swing buck converter is reduced by 24.5% as compared to the full swing maximum efficiency configuration, resulting in 3.9% higher in efficiency than that of full swing DC-DC converter (Fig. 2.5). Energy recycling drivers or ZVS switching can also be employed to reduce switching losses, as illustrated in [51].

DC-DC converter efficiency is strongly dependent on the switching frequency, so that it is clearly a primary design variable in the analysis. The efficiency was analyzed over some frequency range varying the circuit configuration. The maximum efficiency circuit configurations determined by the model was simulated, verifying the circuit operation and performance characteristics. The global maximum efficiency with a full-swing converter was 84.1% based on a tapering factor of 10. The switching frequency of maximum efficiency configuration is 102 MHz.

The integrated 4-phase Buck DC-DC converters implemented in a 90 nm CMOS technology were demonstrated with off-chip air-core inductors in [49] and [50]. At 480 MHz operating frequency the measured efficiency was 72% for a voltage conversion from 1.8~V-0.9~V while supplying 0.5~A load current in [49]. The efficiency of 80%-87% at switching frequency of 100 to 317 MHz was demonstrated in [50] for a voltage conversion from 1.2-0.9V while supplying 0.3A output current.

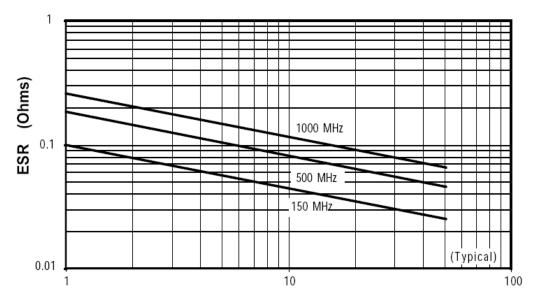

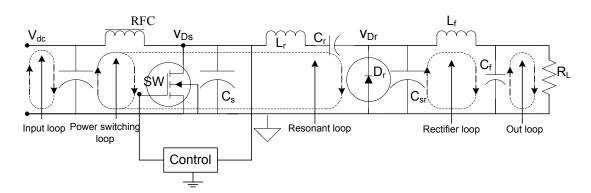

# 2.5. New architecture DC-DC converters derived from Class E power amplifier

This new family of high switching frequency DC-DC converter has emerged since 1980's [54][55][56]. The name "Class E" comes from switching mode RF power amplifier circuits [57][58]. The idea of Class E DC-DC converter was first published by Gutmann in 1980 [54]. As the switching frequency increases to VHF range, the conventional converters with square waveforms become limited mainly due to short transition times and parasitics. On the other hand, the DC-DC converter derived from the Class E power amplifier provides a promising option for operation at microwave frequencies due to its excellent soft switching characteristics. The Class E DC-DC converter uses the same principles as the class E power amplifier. It is based on sinusoidal waveform operation and the zero voltage switching technique.

The switching-mode Class E power amplifier is employed as the resonant inverter due to its high efficiency and simplicity. The rectifier should offer high efficient and high frequency rectification. The underlying principle of Class E operation is to shape the voltage and current waveforms of the switch so that two waveforms are displaced in time from each other. Matching networks can be added to provide both the required voltage-current waveform displacement and the necessary impedance transformation between the rectifier and inverter. When Class E conditions are met, the power dissipation during the switching transitions will be minimized. The parasitics of semiconductor device and passive components can be incorporated into circuit design. Applications of this RF circuit design principle to high frequency DC-DC power converters have been reported in

[56][59][60][61]. With the advanced semiconductor devices and processing technologies available now, high-efficiency operation becomes possible at hundreds of MHz.

The experimental results for a 10 MHz 5 W 25 V to 5 V converter constructed using RF bipolar switch and a Schottky rectifier verified the basic design approach in 1980 [56] and indicated that efficient load and line regulation could be provided with narrow band frequency control. An efficiency of 68% was obtained and it was predicted that 75% efficiency could be obtained with better optimization of inductor Q. Later in 1988 a converter prototype operating at 22 MHz was demonstrated (Fig. 2.6). It consisted of a self-oscillating, ZVS inverter section that fully utilized internal MOSFET capacitances. Output voltage was regulated by narrow band frequency control, implemented with reverse biased varactor diodes in the gate circuit. A peak efficiency of 78% was obtained for 50V nominal input and 5V output.

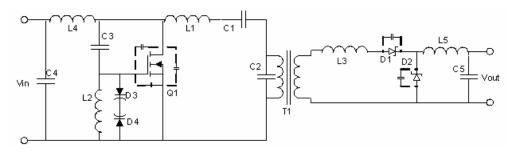

Fig. 2.6 Schematic of DC-DC converter operating at 22 MHz.

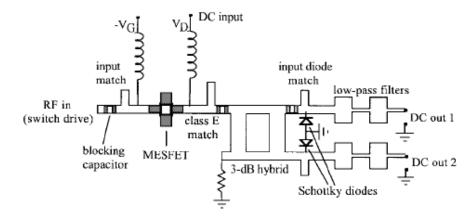

In the work reported in [59] a 4.5 GHz DC-DC power converter was investigated, the highest frequency DC-DC converter reported to date. The converter consisted of a switching-mode Class E power amplifier and diode rectifiers (Fig. 2.7). The Class E amplifier was implemented using transmission lines instead of lumped elements. The output power of the Class E amplifier could be shared by two half-wave rectifiers using a 3-dB hybrid as shown in Fig. 2.7. The two DC outputs could be connected in series or in parallel, giving more choices for output voltage or current value. The overall efficiency of 64% was achieved for a 87  $\Omega$  load with an output 2.15 V. The output power of the Class E power amplifier could be coupled through a 10 dB directional coupler to a single rectifier circuit. A conversion efficiency of 49% across a 135  $\Omega$  load was mentioned in [59]. The fact that the converter was realized without any discrete magnetic components

provided potential for planar, compact and low-profile realization. The approach was amenable to monolithic integration, which would enable very small overall dimensions.

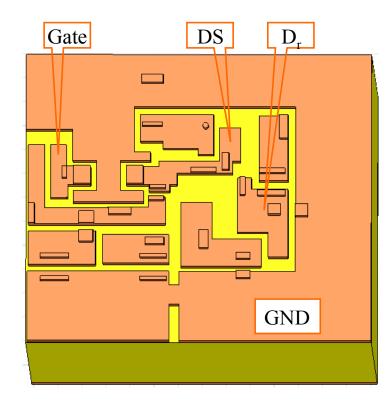

Fig. 2.7 Layout of 4.5 GHz DC-DC converter.

The Class E DC-DC converter was shown in [60] to be an excellent candidate for on-chip switching converters because of high efficiency at high switching frequencies. A 200 mW, 800 MHz integrated Class E DC-DC was designed using a 0.6 µm CMOS process. A 22 nH spiral inductor was designed on the Metal 3 layer. The 50 pF resonant capacitor was implemented with a pair of parallel poly silicon plates. An integrated feedback controller with a VCO was used for output voltage regulation. The layout of the inverter without its choke inductor, synchronous class E rectifier without output low-pass filter inductor and capacitor, VCO, and delay circuit were designed. It was pointed out in this paper that a complete integration could be accomplished by using the second harmonics class E inverter, which didn't need a larger inductance for a choke coil [62].

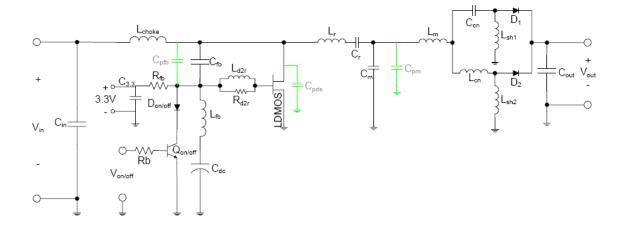

Class E DC-DC converter can be implemented using discrete components, as described in [61]. The experimental evaluation of prototype with cells operating at 100 MHz was demonstrated (Fig. 2.8). Output power ranged from 2.5 W to 6 W, with an average efficiency greater than 77.5%. An underlying feature of the design approaches presented in this paper was that the energy conversion and regulation functions were partitioned in ways that were compatible with the effective implementation of ultra-high frequency circuit designs and techniques.

Fig. 2.8 Switching DC-DC power converter at 100 MHz.

# 2.6. Trends of Power Level with Increasing Frequency

Numerous megahertz switching converters have been reviewed in the previous section. The topologies, techniques for improving efficiency, and implementation techniques are all described along with their main performance features. The implementations of high frequency power converters can be basically classified into two categories in terms of topologies and system architectures:

- Improvements of conventional PWM converters such as Buck -, Boost -, and Flyback -converters and others through:

- Resonant switching techniques;

- High-speed semiconductors to replace conventional MOSFETS in the converters;

- New topologies and architectures suitable for high frequency operation such as Class E DC-DC converters.

In terms of processing technologies, there are four kinds of ways to implement power converters:

- Discrete implementation;

- Hybrid integration techniques;

- Monolithically integration by VLSI;

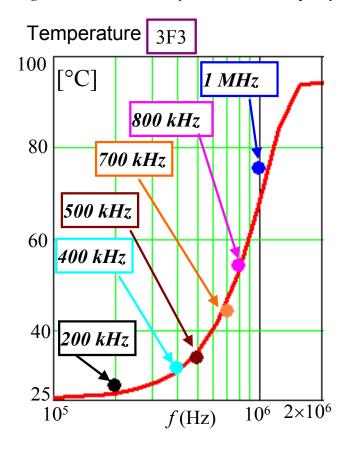

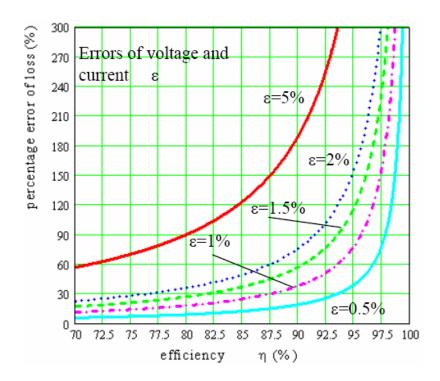

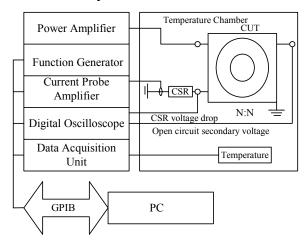

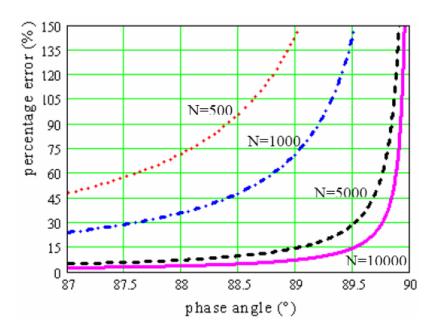

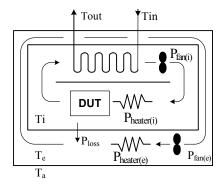

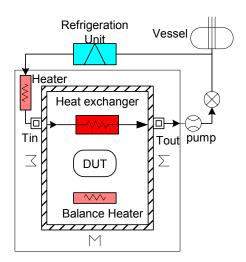

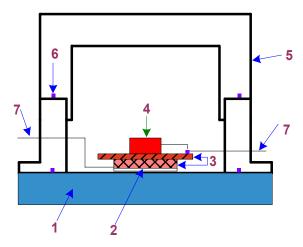

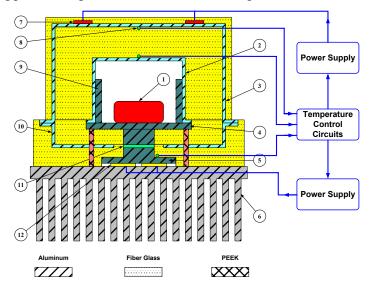

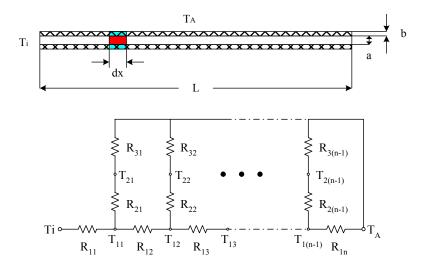

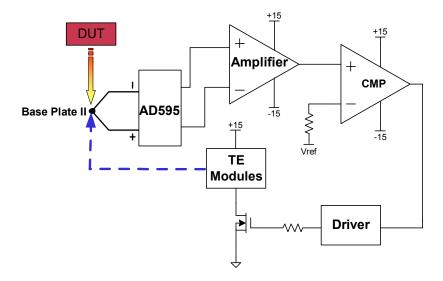

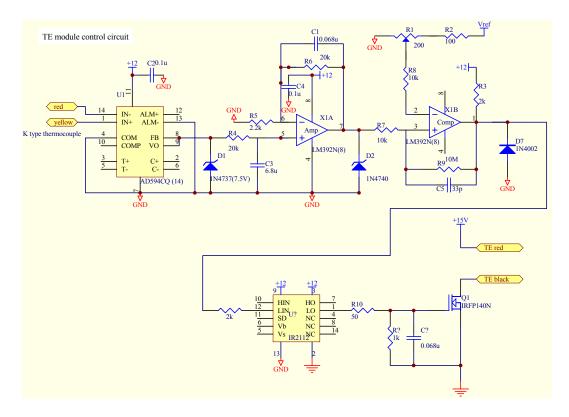

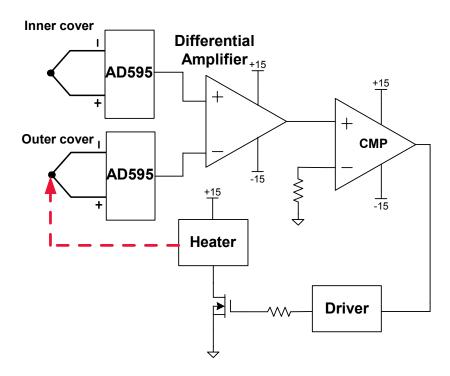

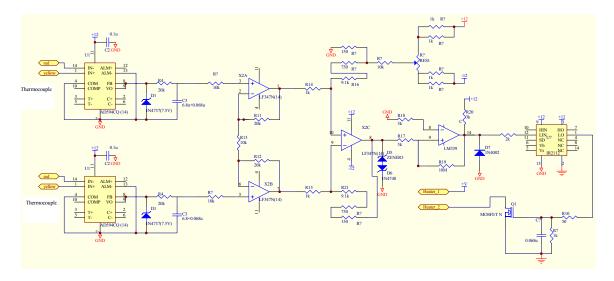

- Distributed implementation based on microwave theory.