# Power Converter and Control Design for High-Efficiency Electrolyte-Free Microinverters

#### Bin Gu

Dissertation submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

> Doctor of Philosophy In Electrical Engineering

Jih-Sheng Lai, Chair William T. Baumann Kathleen Meehan Virgilio A. Centeno Douglas J. Nelson

November 20, 2013 Blacksburg, Virginia

Keywords: Microinverter, Hybrid transformer, Electrolyte-free, High efficiency, Maximum power point tracking, Double line ripple power, MOSFET inverters

Copyright 2013, Bin Gu

## Power Converter and Control Design for High-Efficiency

## Electrolyte-Free Microinverters

#### Bin Gu

Bradly Department of Electrical and Computer Engineering

#### **ABSTRACT**

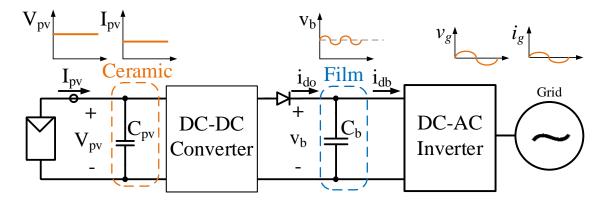

Microinverter has become a new trend for photovoltaic (PV) grid-tie systems due to its advantages which include greater energy harvest, simplified system installation, enhanced safety, and flexible expansion. Since an individual microinverter system is typically attached to the back of a PV module, it is desirable that it has a long lifespan that can match PV modules, which routinely warrant 25 years of operation. In order to increase the life expectancy and improve the long-term reliability, electrolytic capacitors must be avoided in microinverters because they have been identified as an unreliable component. One solution to avoid electrolytic capacitors in microinverters is using a two-stage architecture, where the high voltage direct current (DC) bus can work as a double line ripple buffer.

For two-stage electrolyte-free microinverters, a high boost ratio dc-dc converter is required to increase the low PV module voltage to a high DC bus voltage required to run the inverter at the second stage. New high boost ratio dc-dc converter topologies using the hybrid transformer concept are presented in this dissertation. The proposed converters have improved magnetic and device utilization. Combine these features with the converter's reduced

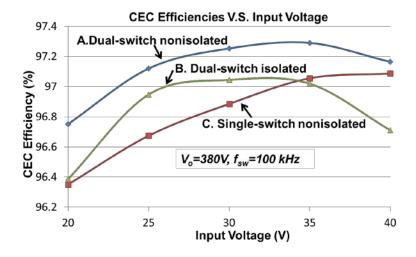

switching losses which results in a low cost, simple structure system with high efficiency. Using the California Energy Commission (CEC) efficiency standards a 250 W prototype was tested achieving an overall system efficiency of 97.3%.

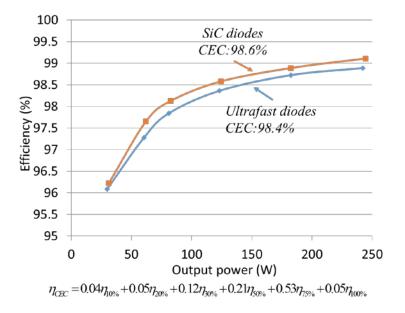

The power inversion stage of electrolyte-free microinverters requires a high efficiency grid-tie inverter. A transformerless inverter topology with low electro-magnetic interference (EMI) and leakage current is presented. It has the ability to use modern superjunction MOSFETs in conjunction with zero-reverse-recovery silicon carbide (SiC) diodes to achieve ultrahigh efficiency. The performance of the topology was experimentally verified with a tested CEC efficiency of 98.6%.

Due to the relatively low energy density of film capacitors compared to electrolytic counterparts, less capacitance is used on the DC bus in order to lower the cost and reduce the volume of electrolyte-free microinverters. The reduced capacitance leads to high double line ripple voltage oscillation on DC bus. If the double line oscillation propagates back into the PV module, the maximum power point tracking (MPPT) performance would be compromised. A control method which prevents the double line oscillation from going to the PV modules, thus improving the MPPT performance was proposed.

Finally, a control technique using a single microcontroller with low sampling frequency was presented to effectively eliminate electrolyte capacitors in two-stage microinverters without any added penalties. The effectiveness of this control technique was validated both by simulation and experimental results.

# Dedication

In memory of my mother, JinFeng Zhu (1954-2008), whose courage and diligence continue to inspire.

#### ACKNOWLEDGEMENTS

I would like to express my deep gratitude to my advisor, Dr. Jih-Sheng Lai, for his guidance, encouragement, and financial support throughout my Ph.D. studies. His profound knowledge and rigorous attitude toward research has been inspiring me throughout my four years of research and study at Virginia Tech and will benefit my professional career as well.

I would like to express my special and sincere thanks to my formal advisor, Dr. Fang Zheng Peng. Ten years ago, he led me to the field of power electronics. I deeply respect him not only for his broad knowledge, but the attitude for perfection. Without his kind support and encouragement, I would never reach this far.

I am grateful to my committee members: Dr. Kathleen Meehan, Dr. William T. Baumann, Dr. Virgilio A. Centeno and Dr. Douglas J. Nelson for their suggestions and kind supports for my research work.

It has been a great pleasure to work in Future Energy Electronics Center (FEEC), not only because of the talented colleagues but also the friendship. I cherish the wonderful time that we worked together. I would like to thank Mr. Gary Kerr, Dr. Wensong Yu, Dr. Chien-Liang Chen, Dr. Hao Qian, Dr. Pengwei Sun, Dr. Huang-Jen Chiu, Dr. Yen-Shin Lai, Dr. Ahmed Koran, Dr. Ben York, Dr. Younghoon Cho, Dr. Zheng Zhao, Dr. Bo-yuan Chen, Dr. Kuan-Hung Wu, Dr. Ethan Swint, Dr. Hongbo Ma, Dr. Zakariya Dalala, Mr. Jason Dominic, Mr. Lanhua Zhang, Mr. Chris Hutchens, Mr. Brett Whitaker, Mr.

Thomas LaBella, Mr. Zaka Ullah Zahid, Mr. Zidong Liu, Mr. Daniel Martin, Mr. Alex Kim, Ms. Hongmei Wan, Mr. Wei-han Lai, Mr. Yaxiao Qin, Mr. Cong Zheng, Mr. Hsin Wang, Mr. Baifeng Chen, Mr. Bo Zhou, Mrs. Le Du, Mr. Eric Raraci, Ms. Rachael Born, Ms. Hyun-Soo Koh, Mr. Rui Chen, Mr. Chia-His Chang, Mr. Po-Yi Yeh, and Mr. Seungryul Moon, for their helpful discussions, great supports and precious friendship.

The love and support of a family is irreplaceable in both life and education. I offer my deepest gratitude to my wife, JingYao Zhang, my father, SongCai Gu, my grandma, GuiFen Yin, my sister, Yan Gu, my sister-in-law, LiYong Hou, and my nephew JiaCen, Hou for their everlasting love, support and encouragement for all my endeavors.

This work is sponsored by the U.S. Department of Energy (DOE)

SunShot Initiative High Penetration Solar Program under the

Grant Number DE-EE0002062.

# CONTENTS

| CHAPTER 1 INTRODUCTION                         |                            |

|------------------------------------------------|----------------------------|

| 1.1 RESEARCH BACKGROUND AND MOTIVATIONS.       | 1                          |

| 1.2 State-of-the-art microinverter techno      |                            |

| 1.2.1 Reviews of the existing microinverter a  |                            |

| 1.2.2 Techniques to eliminate electrolytic ca  |                            |

| 1.3 Objectives of the research project         | =                          |

| 1.4 Major contributions and outline of the     | E DISSERTATION17           |

| CHAPTER 2 HYBRID TRANSFORMER HIGH              | BOOST RATIO DC-DC          |

| CONVERTER TOPOLOGIES                           | 22                         |

| 2.1 SPECIFICATIONS AND DEMANDS                 | 23                         |

| 2.2 REVIEW OF THE STATE-OF-THE-ART HIGH BOO    | ST RATIO DC-DC CONVERTER   |

| TOPOLOGIES                                     | 25                         |

| 2.2.1 Coupled-inductor PWM converters          | 26                         |

| 2.2.2 Current-fed PWM converters               | 27                         |

| 2.2.3 LLC resonant converters                  | 28                         |

| 2.3 Proposed hybrid transformer high boos      | T RATIO DC-DC CONVERTER30  |

| 2.4 OPERATION PRINCIPLE                        |                            |

| 2.4.1 Topological stages and key waveforms     |                            |

| 2.4.2 Voltage stress derivation of the power   |                            |

| 2.4.3 Energy transfer analysis                 |                            |

| 2.4.4 Summary of design procedure              |                            |

| 2.5 EXPERIMENTAL VERIFICATIONS                 |                            |

| 2.6 DERIVING A FAMILY OF HYBRID TRANSFORME     |                            |

| 2.7 Summary                                    | 54                         |

| CHAPTER 3 ADVANTAGES OF HYBRID TRA             |                            |

| CONVERTERS                                     | 56                         |

| 3.1 OPTIMIZED MAGNETIC UTILIZATION             | 57                         |

| 3.2 Improved power device utilization          |                            |

| 3.3 Reduced switching losses                   |                            |

| 3.4 SUMMARY                                    | 64                         |

| CHAPTER 4 HIGH-EFFICIENCY TRANSFOR             | MERLESS INVERTER FOR       |

| SINGLE-PHASE ELECTROLYTE-FREE MICR             | OINVERTERS65               |

| 4.1 COMMON MODE VOLTAGE AND GROUND LOOP        | LEAKAGE CURRENT IN SINGLE- |

| PHASE TWO-STAGE MICROINVERTERS                 | 66                         |

| 4.2 Basic full-bridge inverters                | 68                         |

| 4.2.1 Modulation strategies for full bridge in |                            |

| 4.2.2 CM voltage test for hybrid unipolar PV   |                            |

| $4.3~{ m Transformerless}$ inverter topologies |                            |

| 4.3.1 Topologies using additional freewheeli   | ng separation switches 75  |

| 4.3.2 Topologies using asymmetrical buck-choppers                | 78    |

|------------------------------------------------------------------|-------|

| 4.3.3 Topologies based on neutral-point-clamped inverter         |       |

| 4.4 MATCHED PAIR OF SUPERJUNCTION MOSFETS WITH SIC-SCHOTT        |       |

| FOR HIGH EFFICIENCY PV INVERTER APPLICATIONS                     | 82    |

| 4.4.1 Conduction loss models                                     | 83    |

| 4.4.2 Switching loss models                                      |       |

| 4.5 Proposed high reliability and high efficiency transforme     |       |

| INVERTER                                                         |       |

| 4.5.1 Proposed topology and operation analysis                   |       |

| 4.5.2 Leakage current analysis for the proposed transformerless  |       |

|                                                                  |       |

| 4.5.3 Calculation and comparison of the power semiconductor de   |       |

| losses for Several Existing MOSFET transformerless Inverters.    |       |

| 4.5.4 Loss reduction with MOSFETs replacing IGBTs as power       |       |

| for the proposed transformerless inverter                        |       |

| 4.6 Experimental verification                                    |       |

| 4.7 SUMMARY                                                      |       |

|                                                                  |       |

| CHAPTER 5 MODELING AND CONTROL OF ELECTROLYTE-F                  |       |

| MICROINVERTERS                                                   | 117   |

| 5.1 ENERGY STORAGE CAPACITORS IN SPTS MICROINVERTERS             | 117   |

| 5.2 EFFECTS OF DOUBLE LINE RIPPLE IN SPTS MICROINVERTERS         | 119   |

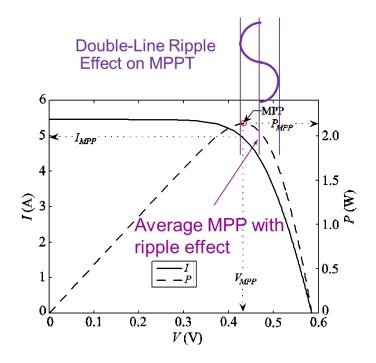

| 5.2.1 Effect of double line ripple on MPPT performance           | 119   |

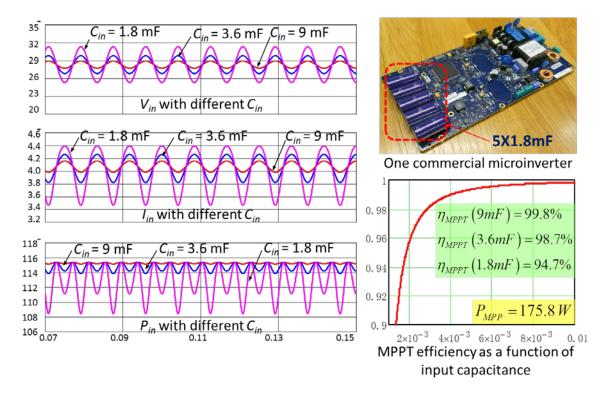

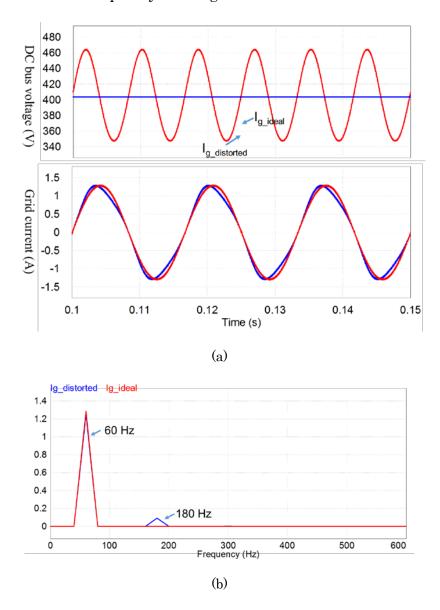

| 5.2.2 Effect of double line ripple on grid current distortion    | 121   |

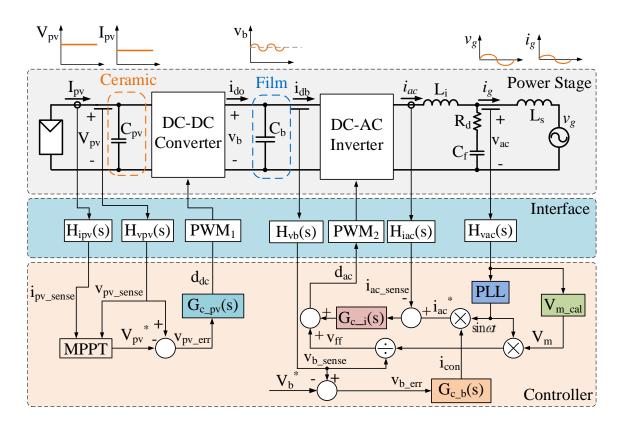

| 5.3 System control architecture of the electrolyte-free          |       |

| MICROINVERTER                                                    | 123   |

| 5.4 Modeling and control of hybrid transformer DC-DC conve       | RTERS |

| WITH DOUBLE LINE RIPPLE REJECTION                                | 125   |

| 5.4.1 Small-signal modeling of PV modules                        |       |

| 5.4.2 Small-signal model of power stage of hybrid transformer of |       |

| converter                                                        |       |

| 5.4.3 Transfer function block diagram                            |       |

| 5.4.4 Design of PV voltage loop contorller with high double line |       |

| capability                                                       |       |

| 5.4.5 Simulation and experimental verifications                  |       |

| 5.5 MODELING AND CONTROL OF THE GRID-TIE INVERTER WITH GRID C    |       |

| DISTORTION REDUCTION                                             |       |

| 5.5.1 Control block diagram                                      |       |

| 5.5.2 Grid synchronization using phase-locked loop (PLL)         |       |

| 5.5.3 Grid voltage magnitude $V_m$ calculation                   |       |

| 5.5.4 Design of grid current controller                          |       |

| 5.6 DESIGN OF DC BUS CONTROLLER                                  |       |

| 5.7 EXPERIMENTAL VERIFICATIONS                                   |       |

| 5.8 SUMMARY                                                      |       |

| O.O COMMITTEE                                                    |       |

| CHAPTER 6 CONCLUSIONS AND FUTURE WORKS                   | 156 |

|----------------------------------------------------------|-----|

| 6.1 Major results and contributions of this dissertation | 156 |

| 6.2 Future works                                         | 158 |

| REFERENCE                                                | 160 |

# LIST OF FIGURES

| Figure 1.1 Photograph of two mono-crystalline photovoltaic (PV) modules: (a           | ı) |

|---------------------------------------------------------------------------------------|----|

| 60 cells, and (b) 72 cells                                                            | .1 |

| Figure 1.2 PV grid-tie inverter systems.                                              |    |

| Figure 1.3 Three different types of microinverters                                    | .5 |

| Figure 1.4 Microinverters with a pseudo DC link                                       | .7 |

| Figure 1.5 Microinverters using cycloconverter technologies [B22], [B23]              | .8 |

| Figure 1.6 Two-stage microinverters.                                                  | 10 |

| Figure 1.7 Grid side power and its decomposition.                                     | 11 |

| Figure 1.8 Commercial 175 W microinverter M190-72-240 from Enphase,                   |    |

| which requires 9 mF of electrolyte capacitors to buffer the double line               |    |

| ripple                                                                                | 12 |

| Figure 1.9 Extra ripple power circuit used to buffer the double line ripple           |    |

| power and eliminate electrolytic capacitors in single-stage microinverte              | rs |

| with PV-side and AC-side buffing techniques                                           | 13 |

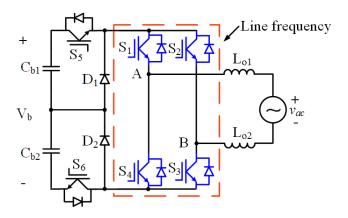

| Figure 1.10 Single-phase two-stage microinverters using high voltage                  |    |

| intermediate DC bus capacitor C <sub>b</sub> as double line ripple power buffer       | 14 |

| Figure 1.11 commercial 300 W electrolyte-free microinverter MICRO-0.3-I               |    |

| from Power-One Inc.                                                                   | 14 |

| Figure 1.12 Cost breakdown in year 2010 for 5 kW residential PV system                |    |

| with one string inverter: total \$5.71/W; DOE SunShot target is \$1.5/W i             | .n |

| 2020 [A3]                                                                             |    |

| Figure 2.1 Electrical specifications of CS6P-240P PV module [F7]                      |    |

| Figure 2.2 I-V curves of CS6P-240P PV module [F7].                                    |    |

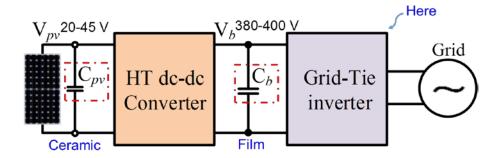

| Figure 2.3 Microinverters with two-stage architecture                                 |    |

| Figure 2.4 Coupled-inductor PWM dc-dc converters.                                     |    |

| Figure 2.5 Current-fed PWM converters.                                                |    |

| Figure 2.6 LLC resonant converters.                                                   | 28 |

| Figure 2.7 Derive hybrid transformer high boost ratio dc-dc converter by              |    |

| introducing resonant voltage doubler into traditional boost-flyback                   |    |

|                                                                                       | 31 |

| Figure 2.8 Topological states of the high boost ratio dc-dc converter with            |    |

| hybrid transformer.                                                                   |    |

| Figure 2.9 Key waveforms for different operation stages                               |    |

| Figure 2.10 Waveforms for energy transfer analysis                                    |    |

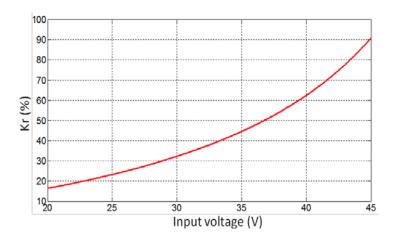

| Figure 2.11 K <sub>r</sub> V.S. V <sub>in</sub> curve.                                |    |

| Figure 2.12 Photograph of the prototype circuit, specifications, and selection        |    |

| of components.                                                                        |    |

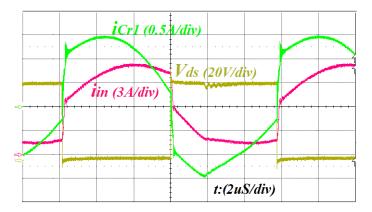

| Figure 2.13 Experimental waveforms of current of the resonant capacitor $C_{ m r}$    |    |

| voltage of switch $M_1$ and input current with $P_0$ =220W, $V_0$ =400V, $V_{in}$ =30 |    |

| and f <sub>s</sub> =88kHz.                                                            | _  |

| Figure 2.14 Experimental waveforms of switch voltage, output diode voltage            |    |

| input current and current of resonant capacitor of the proposed converte              | er |

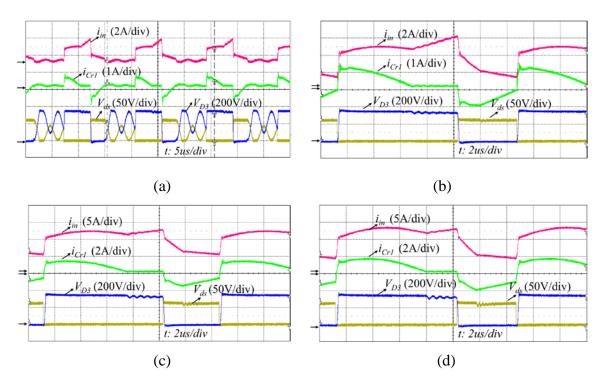

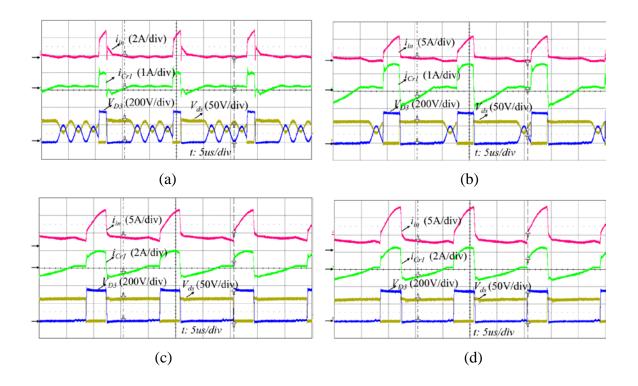

| with 20V input, 400V output under different output power level: (a) 30W, (b) 110W, (C) 160W and (d) 220W46 |

|------------------------------------------------------------------------------------------------------------|

| Figure 2.15 Experimental waveforms of switch voltage, output diode voltage,                                |

| input current and current of resonant capacitor of the proposed converter                                  |

| with 30V input, 400V output under different output power level: (a) 30W,                                   |

| (b) 110W, (C) 160W and (d) 220W                                                                            |

| Figure 2.16 Experimental waveforms of switch voltage, output diode voltage,                                |

| input current and current of resonant capacitor of the proposed converter                                  |

| with 45V input, 400V output under different output power level: (a) 30W,                                   |

| (b) 110W, (C) 160W and (d) 220W48                                                                          |

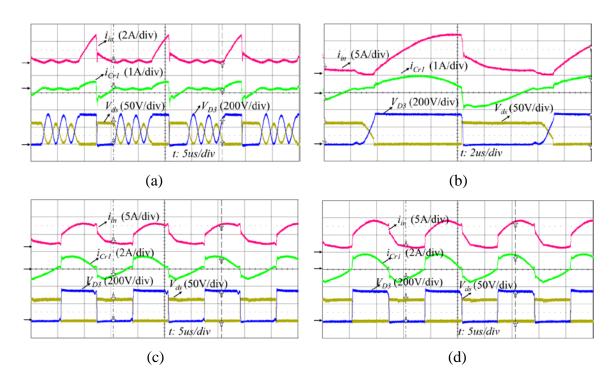

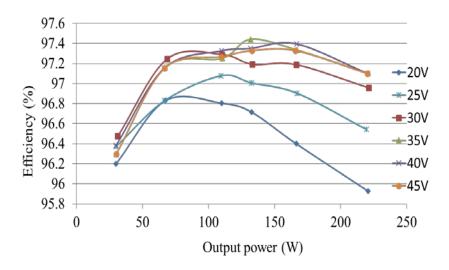

| Figure 2.17 Conversion efficiency V.S. output power for different input                                    |

| voltages                                                                                                   |

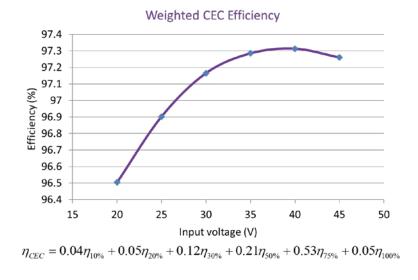

| Figure 2.18 CEC efficiency at different input voltages                                                     |

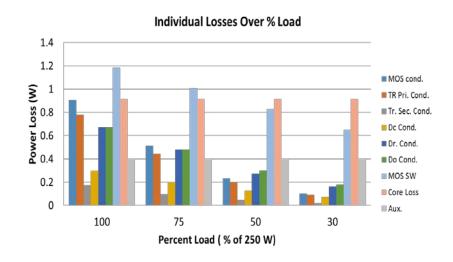

| Figure 2.19 Loss breakdown at different load conditions                                                    |

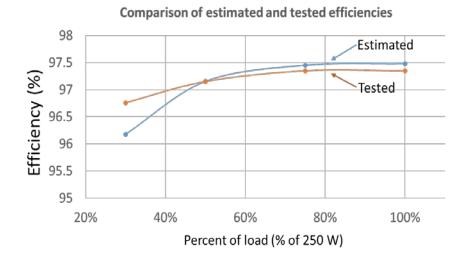

| Figure 2.20 Comparison of estimated and tested efficiencies at different load                              |

| conditions                                                                                                 |

| Figure 2.21 A family of hybrid transformer dc-dc converters using RVD for                                  |

| microinverter applications                                                                                 |

| Figure 2.22 CEC efficiency comparison                                                                      |

| Figure 3.1 Notations of the symbol in Table 3-157                                                          |

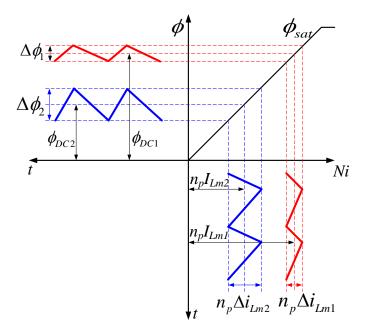

| Figure 3.2 Total flux in the magnetic core versus MMF: variables with                                      |

| subscript 1 are for converter in [C9], variables with subscript 2 are for                                  |

| the proposed converter; $n_p$ is primary turns                                                             |

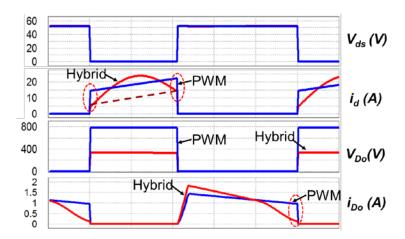

| Figure 3.3 Switching waveforms of the hybrid transformer dc-dc converter                                   |

| and traditional boost-flyback reboost PWM dc-dc converter63                                                |

| Figure 4.1 Single-phase two-stage microinverters, where a high efficiency                                  |

| grid-tie inverter is required to invert the high DC bus voltage to AC grid                                 |

| voltage65                                                                                                  |

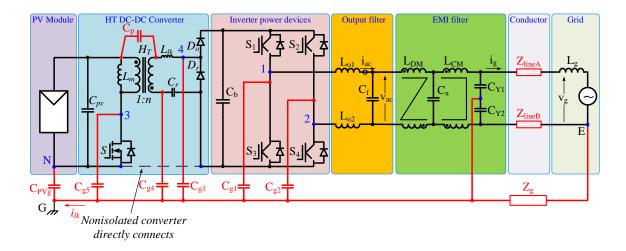

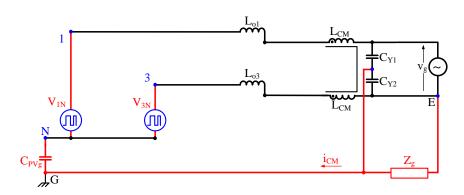

| Figure 4.2 System circuit diagram with key common mode voltage sources,                                    |

| key parasitic elements and the total ground leakage current $i_{lk}$ , for                                 |

| isolated version, $i_{lk}$ is limited by $C_p$ , while for nonisolated version, $i_{lk}$                   |

| needs to be limited by topologies, i.e., minimizing the magnitude of the                                   |

| CM source voltages68                                                                                       |

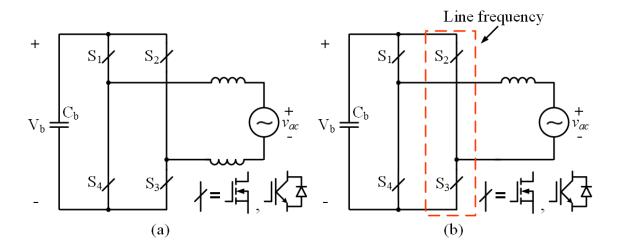

| Figure 4.3 Traditional full bridge inverters: (a) with two symmetrical output                              |

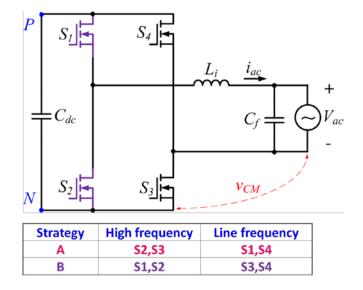

| inductors, (b) with single output inductor70                                                               |

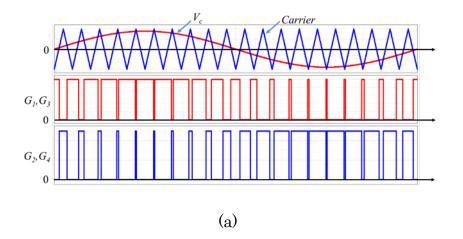

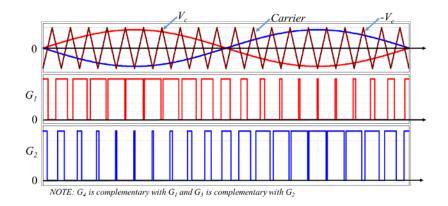

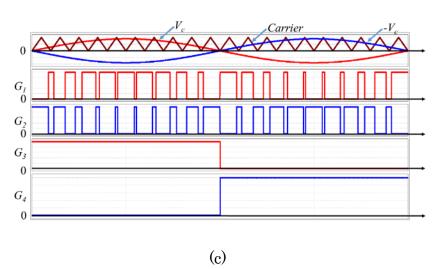

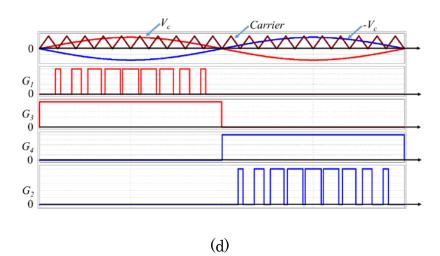

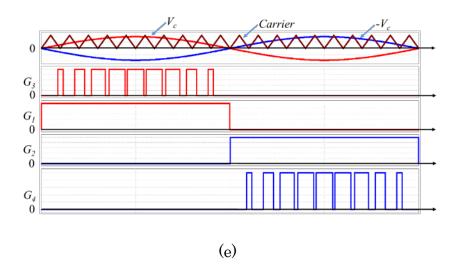

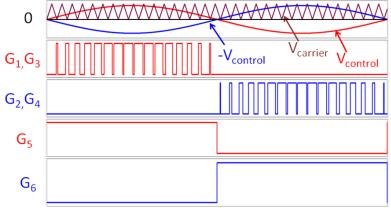

| Figure 4.4 Five different modulation strategies for basic full bridge inverters:                           |

| (a) bipolar modulation, (b) unipolar modulation, (c) hybrid modulation1,                                   |

| (d) hybrid modulation2, and hybrid modulation3. $V_c$ represents                                           |

| modulation signal, Carrier is carrier signal, $G_i$ ( $i=1,2,3,4$ ) represents the                         |

| driver signal for switch $i$ , $G_i$ high means switch on and $G_i$ low means                              |

| switch off72                                                                                               |

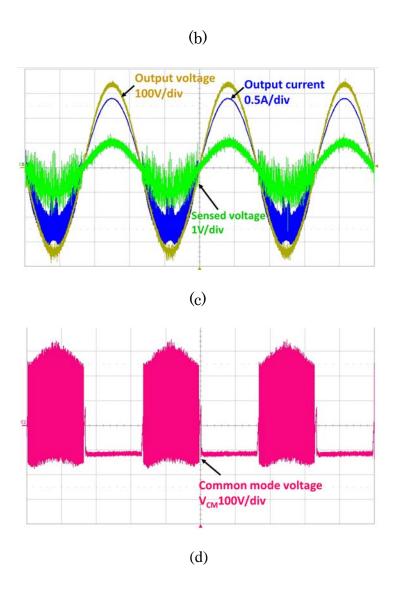

| Figure 4.5 CM voltage test for single-inductor full bridge inverter with two                               |

| different hybrid modulation strategies73                                                                   |

| Figure 4.6 Test waveforms for CM voltages74                                                                |

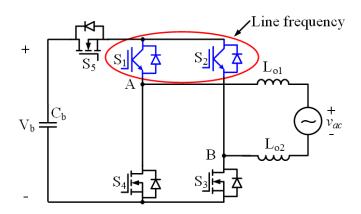

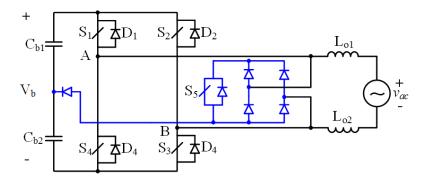

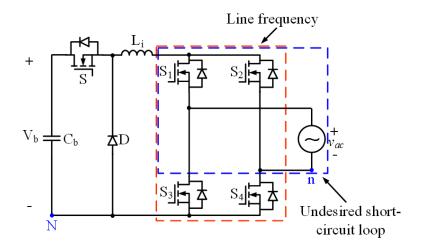

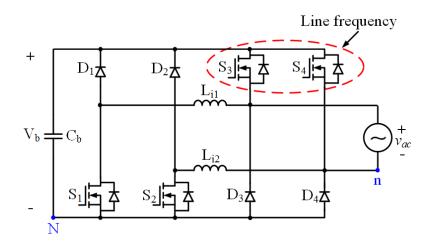

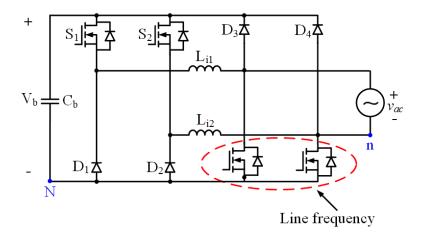

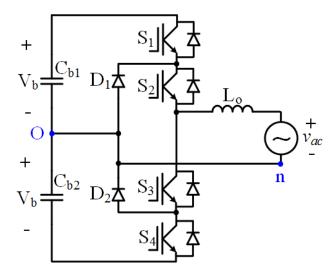

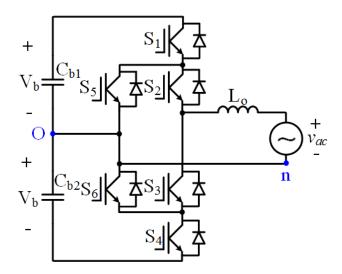

| Figure 4.7 Transformerless inverter topologies using additional freewheeling                                        |

|---------------------------------------------------------------------------------------------------------------------|

| separation switches                                                                                                 |

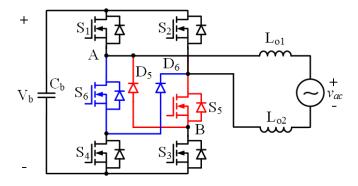

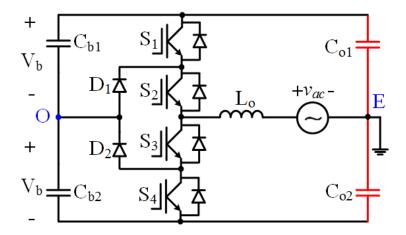

| Figure 4.8 Transformerless inverter topologies using asymmetrical buck-                                             |

| choppers80                                                                                                          |

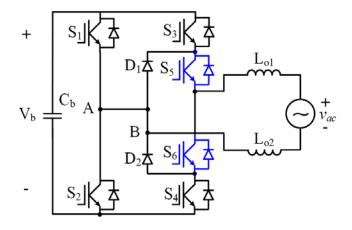

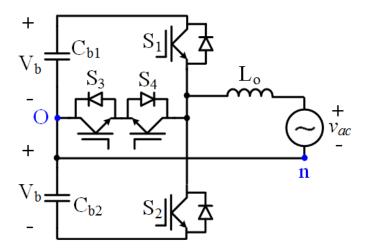

| Figure 4.9 Transformerless inverter topologies based on NPC inverter 82                                             |

| Figure 4.10 Equivalent circuits for first-order conduction loss models for                                          |

| MOSFETs, IGBTs and diodes84                                                                                         |

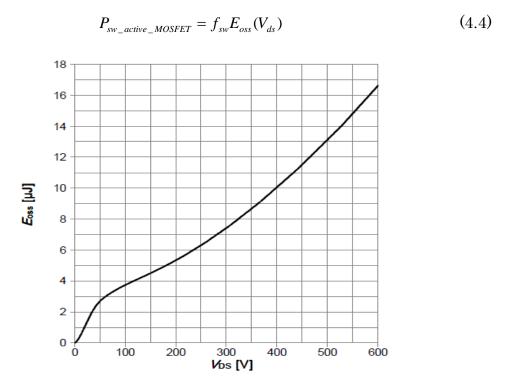

| Figure 4.11 Typical Coss stored energy from datasheet of Infineon                                                   |

| IPB65R099C6 CoolMOS transistor [F9]85                                                                               |

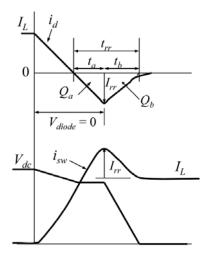

| Figure 4.12 Simplified waveforms showing switching losses induced in the                                            |

| main switches and diodes during diode reverse recovery                                                              |

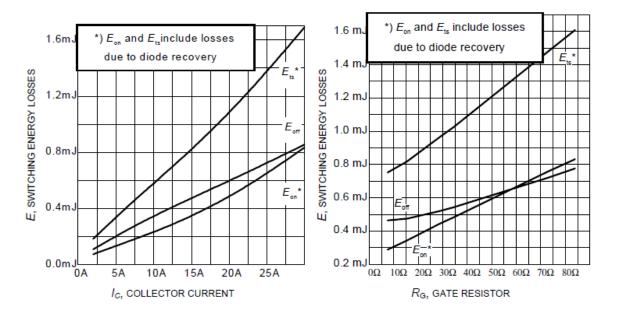

| Figure 4.13 Typical switching energy losses of IGB15N60T IGBT, (a) as a                                             |

| function of collector current and (b) as a function of gate resistor. (Test                                         |

| conditions: inductive load, $T_j=175$ °C, $V_{CE}=400$ V, $V_{GE}=0/15$ V, $R_g=15\Omega$ ).87                      |

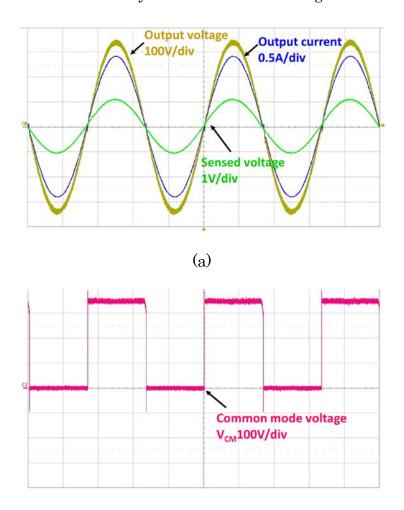

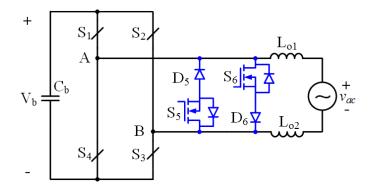

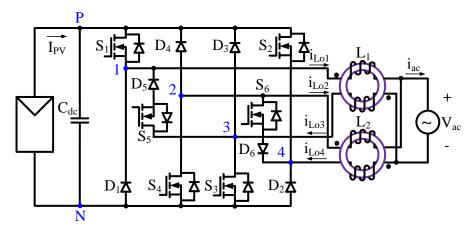

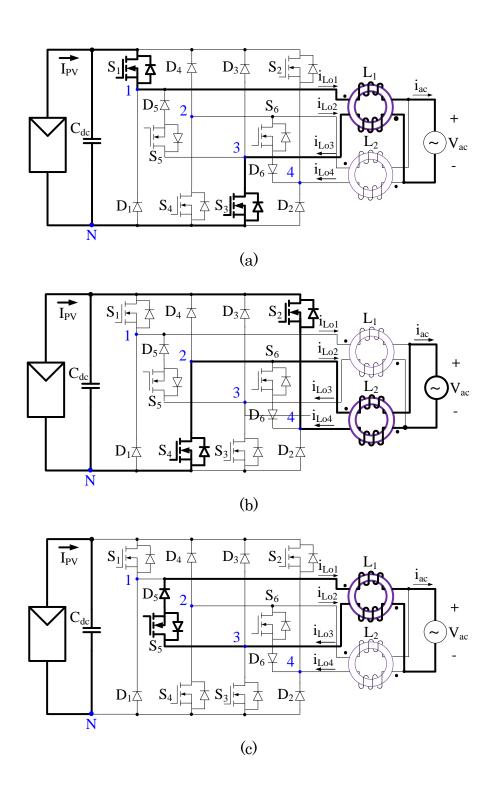

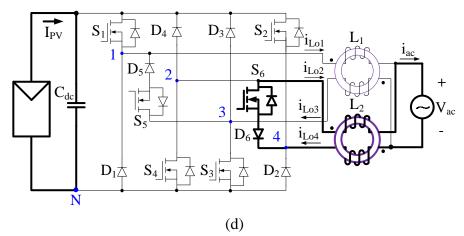

| Figure 4.14 Proposed high efficiency and reliability PV transformless inverter                                      |

| topology94                                                                                                          |

| Figure 4.15 Gating signals of proposed transformerless PV inverter94                                                |

| Figure 4.16 Topological stages of the proposed inverter: (a) active stage of                                        |

| positive half-line cycle, (b) freewheeling stage of positive half-line cycle,                                       |

| (c) active stage of negative half-line cycle, and (d) freewheeling stage of                                         |

| negative half-line cycle96                                                                                          |

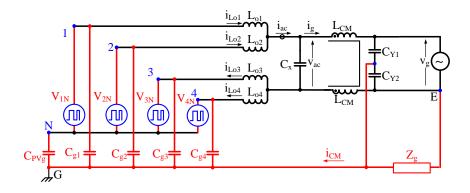

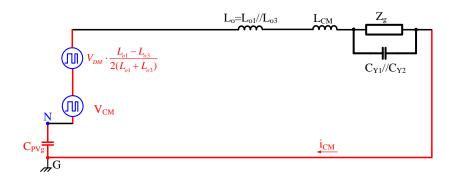

| Figure 4.17 Leakage current analysis model for the proposed transformerless                                         |

| PV inverter98                                                                                                       |

| Figure 4.18 Simplified CM leakage current analysis model for positive half-                                         |

| line cycle98                                                                                                        |

| Figure 4.19 Simplified single-loop CM model for positive half-line cycle99                                          |

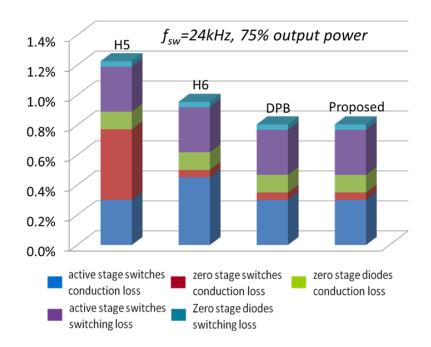

| Figure 4.20 Power semicondcutor device losses distribution comparison for                                           |

| H5, H6, DBC and proposed transformerless PV inverters with 75% of the                                               |

| rated output power104                                                                                               |

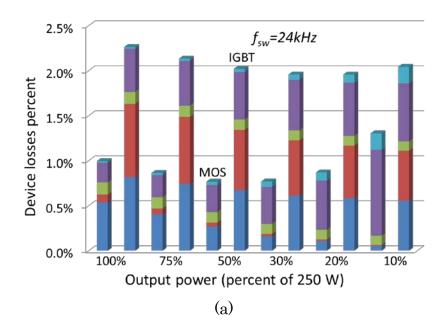

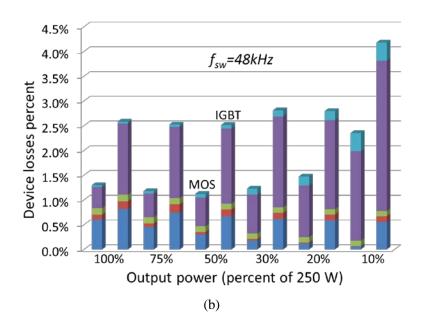

| Figure 4.21 Power semiconductor device losses distributaion comparion for                                           |

| the proposed inverter using MOSFETs and IGBTs at different output                                                   |

| power: (a) 24 kHz switching frequency, and (b) 48 kHz switching                                                     |

| frequency                                                                                                           |

| Figure 4.22 Block diagram of the complete inverter test system                                                      |

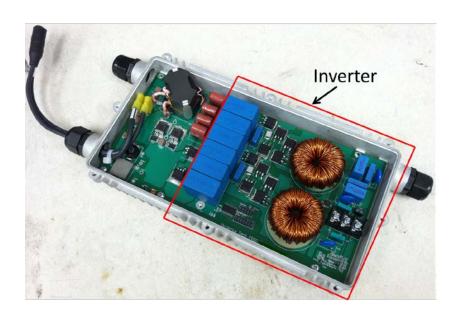

| Figure 4.23 Prototype board                                                                                         |

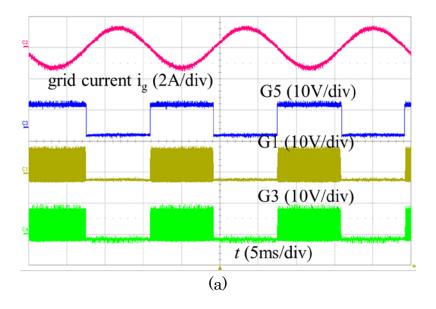

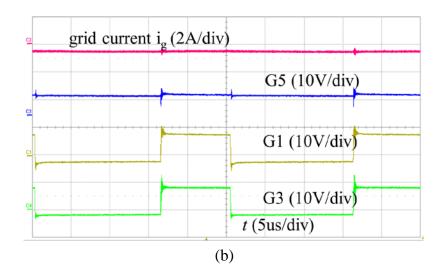

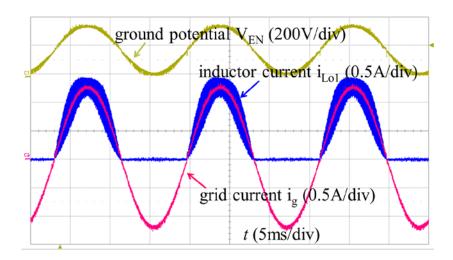

| Figure 4.24 Switch gating signals: (a) in the grid cycle and (b) in the PWM                                         |

| cycle                                                                                                               |

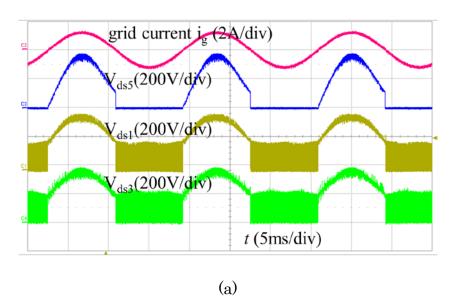

| Figure 4.25 Drain-source voltage waveforms of the switches S <sub>1</sub> , S <sub>3</sub> and S <sub>5</sub> : (a) |

| in the grid cycle, and (b) in the PWM cycle111                                                                      |

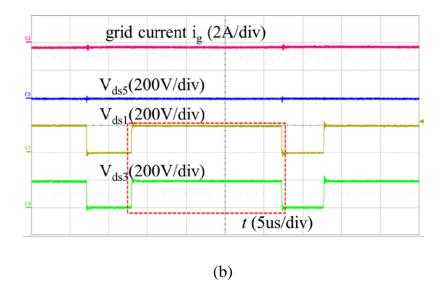

| Figure 4.26 Experimental waveforms of ground potential V <sub>EN</sub> , grid current                               |

| and current of inductor $L_{o1}$                                                                                    |

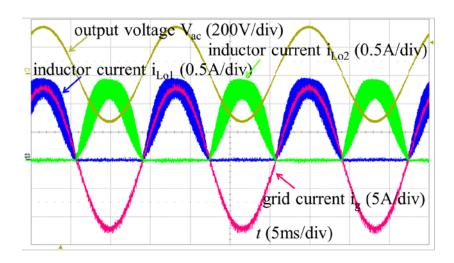

| Figure 4.27 The experimental waveforms of grid current and the inductor                                             |

| currents $i_{Lo1}$ and $i_{Lo2}$                                                                                    |

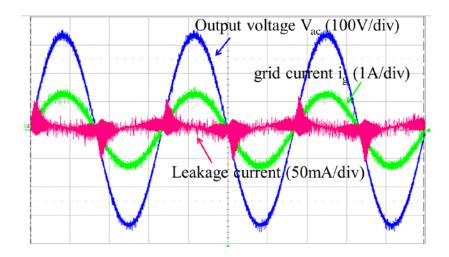

| Figure 4.28 Leakage current test waveforms                                                                          |

| Figure 4.29 Measured efficiency as a function of the output power with ultrafast and SiC diodes respectively at the switching frequency 24 kHz                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.1 Energy storage capacitors in SPTS microinverters                                                                                                               |

| Figure 5.3 MPPT efficiency degradation analysis from the double line ripple current propagation back to PV module caused by the dry-out of electrolytic capacitors        |

| Figure 5.4 Simulation results showing the double line ripple effect on the grid current (a) time domain, (b) FFT analysis of grid current122                              |

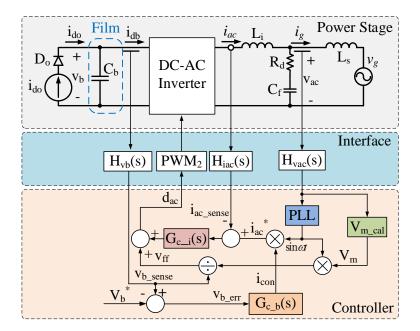

| Figure 5.5 System control structure                                                                                                                                       |

| Figure 5.6 Electrical small-signal model of PV module                                                                                                                     |

| Figure 5.7 State-space averaging using dominating states: (a) S on, (b) S off.                                                                                            |

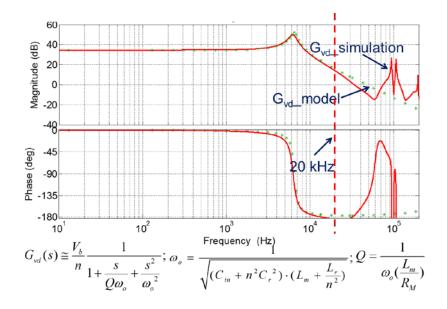

| Figure 5.8 Bode plots for transfer function G <sub>vd</sub> (s): the red one is from                                                                                      |

| simulation using Simplis software and the green one is from                                                                                                               |

| mathematical modeling132                                                                                                                                                  |

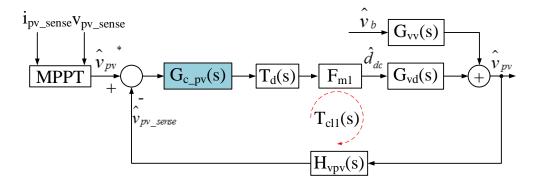

| Figure 5.9 Control block diagram of the dc-dc converter                                                                                                                   |

| Figure 5.10 Transfer function block diagram of the dc-dc converter                                                                                                        |

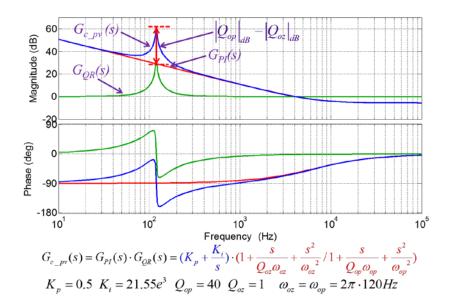

| Figure 5.11 Bode plots for PI, QR and proposed controllers                                                                                                                |

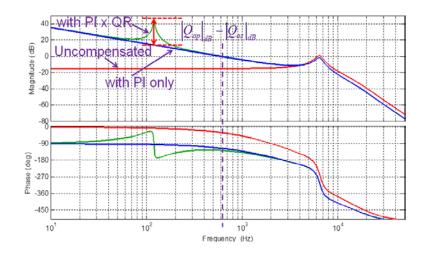

| Figure 5.12 Bode plots of $T_{\rm cl1}(s)$ for three cases: uncompensated, compensated with PI controller only and compensated with proposed PI cascaded QR               |

| controller                                                                                                                                                                |

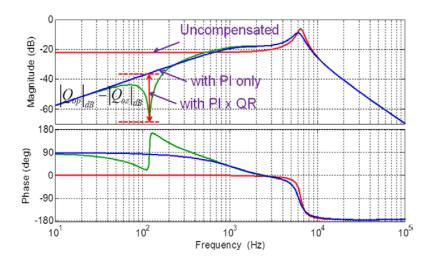

| Figure 5.13 Bode plots of G <sub>vv</sub> (s) for three cases: uncompensated, compensated with PI controller only and compensated with proposed PI cascaded QR controller |

| controller                                                                                                                                                                |

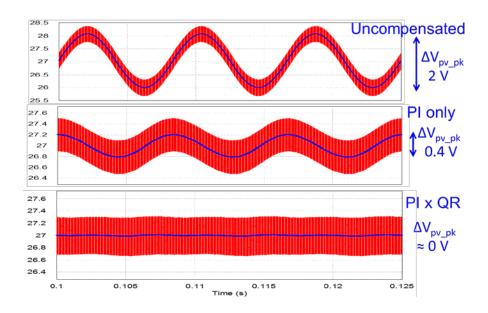

| cases: uncompensated, compensated with PI controller only and                                                                                                             |

| compensated with proposed PI cascaded QR controller, at the condition of                                                                                                  |

| DC bus peak-to-peak double line ripple voltage 29.1 V138                                                                                                                  |

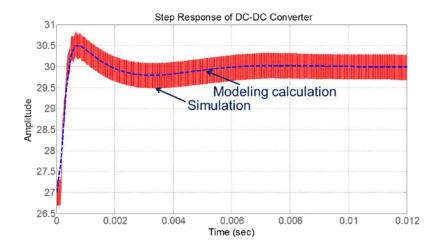

| Figure 5.15 Step response of dc-dc converter using the proposed controller.                                                                                               |

|                                                                                                                                                                           |

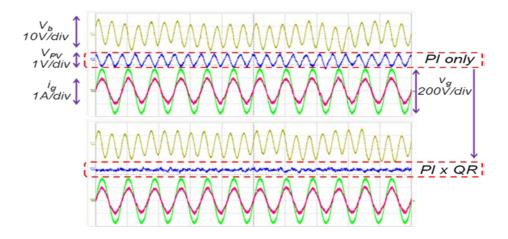

| Figure 5.16 Key experimental waveforms showing the improved double line ripple rejection compensated with PI×QR controller compared to PI                                 |

| controller only with the PV module CS6P-240P at the condition of 170 W                                                                                                    |

| output power                                                                                                                                                              |

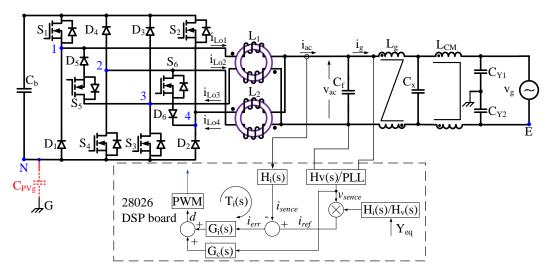

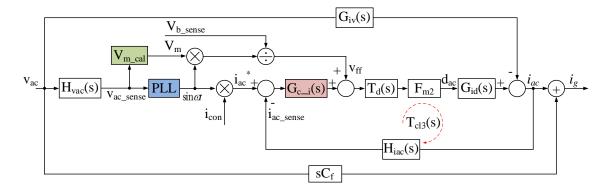

| Figure 5.17 Control block diagram of grid-tie inverter                                                                                                                    |

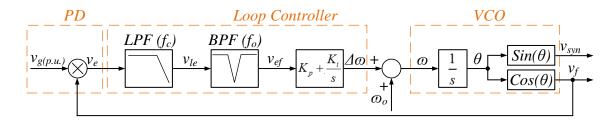

| Figure 5.18 Structure of grid synchronization PLL                                                                                                                         |

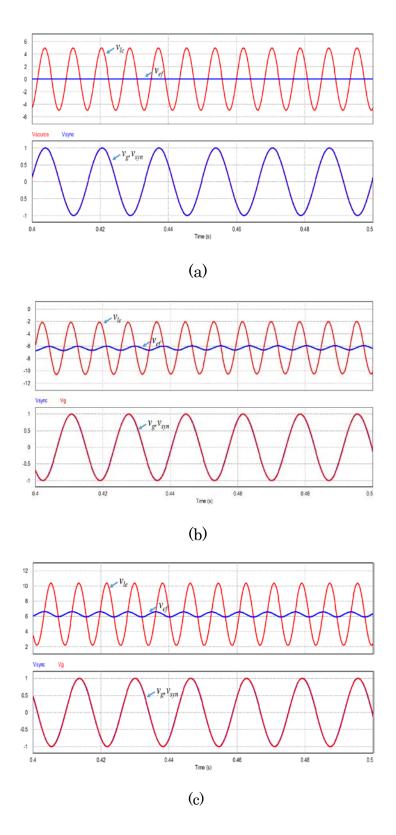

| Figure 5.19 Simulation results for PLL with grid frequencies: (a) $f_g$ =60 Hz, (b)                                                                                       |

| $f_g$ =59 Hz and (c) $f_g$ =61 Hz                                                                                                                                         |

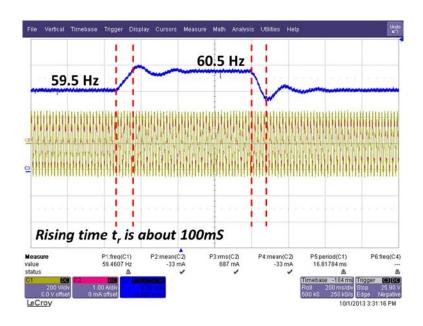

| Figure 5.20 Dynamic response of PLL                                                                                                                                       |

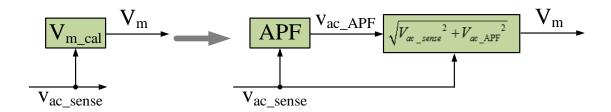

| Figure 5.21 Grid voltage magnitude V <sub>m</sub> calculation144                                                                                                          |

| Figure 5.22 Transfer function block diagram of ac current control145                                                                                                      |

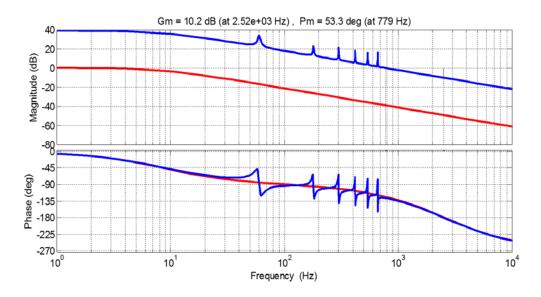

| Figure 5.23 Bode plot of the loop gain T <sub>cl2</sub> (s) with 3 <sup>rd</sup> , 5 <sup>th</sup> , 7 <sup>th</sup> , 9 <sup>th</sup> and 11 <sup>th</sup> |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| harmonic compensators.                                                                                                                                      | .146 |

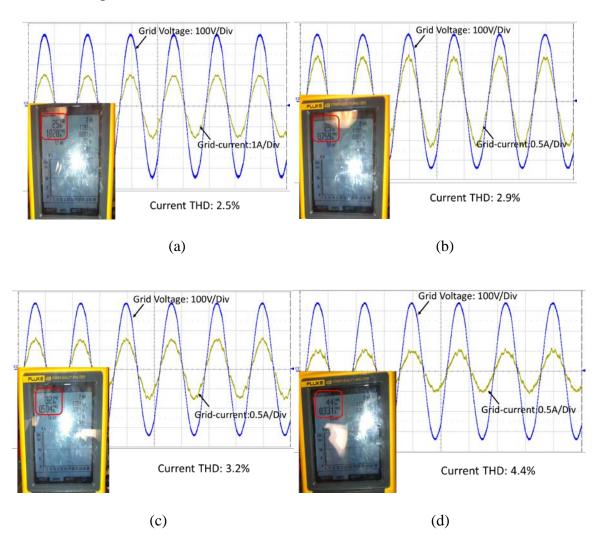

| Figure 5.24 Experimental results for grid current control with $V_b$ =380 V,                                                                                |      |

| Vac= 240 Vac, and nominal AC current 1.04 Aac. Test conditions: (a)                                                                                         |      |

| 100%, (b) 75%, (c) 50%, (d) 30% (e) 20% power and (f) grid current jur                                                                                      | nps  |

| from 20% to 100% power                                                                                                                                      | .148 |

| Figure 5.25 Transfer function block diagram of dc bus control loop                                                                                          | .149 |

| Figure 5.26 Bode plots for PI, QNF and PI cascaded QNF controller                                                                                           | .151 |

| Figure 5.27 Bode plots for loop gain $T_{cl3}$ with the cases of PI, QNF and PI                                                                             |      |

| cascaded QNF controllers                                                                                                                                    | .151 |

| Figure 5.28 Simulation results for DC bus voltage loop control: (a) PI                                                                                      |      |

| controller only, (b) PI cascaded QNF controller                                                                                                             | .152 |

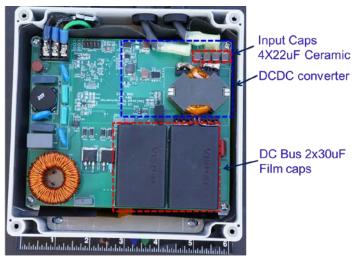

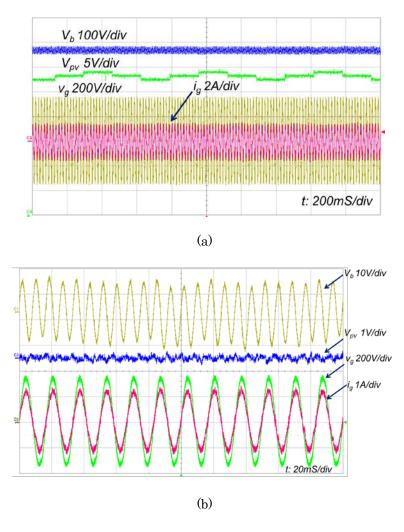

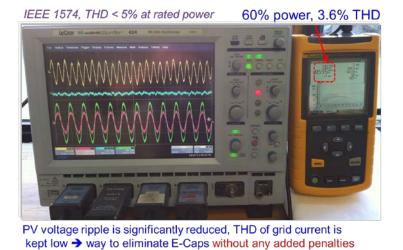

| Figure 5.29 Photograph of the prototype board                                                                                                               | .153 |

| Figure 5.30 Key experimental waveforms                                                                                                                      | .154 |

| Figure 5.31 Photograph showing the low THD of the grid current and low                                                                                      |      |

| double line oscillation in the PV terminal voltage                                                                                                          | .155 |

# LIST OF TABLES

| Table 2-1 Pros and cons of the state-of-the-art high boost ratio dc-dc |     |

|------------------------------------------------------------------------|-----|

| converters                                                             | 29  |

| Table 3-1 Specification and power stage parameters                     | 56  |

| Table 4-1 Specification and power devices for efficiency evaluations   | 100 |

| Table 4-2 Total losses of power devices at different CEC output power  |     |

| conditions at 24 kHz switching frequency                               | 103 |

| Table 4-3 Specifications and power stage devices for prototype circuit | 108 |

| Table 5-1 Specifications for prototype circuit                         | 153 |

|                                                                        |     |

#### Chapter 1 Introduction

#### 1.1 Research background and motivations

The electrical energy consumption continues to grow as more human activities are dependent on electricity. Due to the depletion of fossil fuels and increasingly serious environmental pollution, the demand for the utilization of renewable energy sources to generate electricity is increasing. Among these renewable energy sources, photovoltaic (PV) energy has experienced remarkable growth over the past decade. The world's cumulative PV capacity has achieved 102 GW in the year 2012 and would expected to reach 288 GW in 2017 [A1].

Figure 1.1 Photograph of two mono-crystalline photovoltaic (PV) modules: (a) 60 cells, and (b) 72 cells [F7].

The PV energy generated from sunlight is captured by PV modules in Figure 1.1, which are composed of a cluster of PV cells in series. The power

generated by the PV modules are electric DC power. Integrating the DC power from the PV modules into the existing 'alternating current' (AC) power distribution infrastructure can be achieved through grid-tie inverters. The inverters must guarantee that the PV modules are operating at the maximum power point (MPP), which is the operating condition where the most energy is captured. Another function for inverters to implement is the need to control the current injected into the AC grid synchronous with the grid voltage at the lowest harmonic distortion levels. Therefore PV inverters have a huge impact on the performance of PV grid-tie systems.

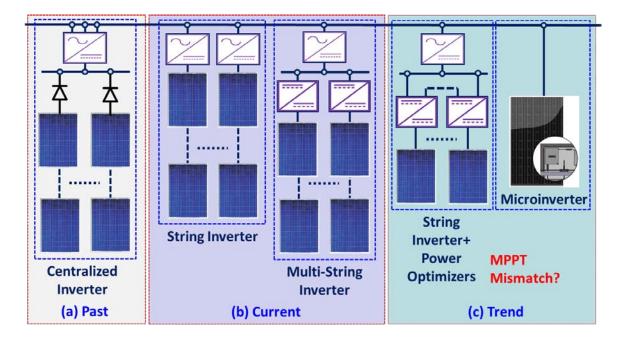

Depending on different levels of MPPT implementation for PV modules, several PV inverter technologies coexist [B1]. As shown in Figure 1.2(a), centralized inverters, which are normally three-phase connected, interface a large cluster of parallel-connected PV strings into the grid. Each PV string is composed of a large number of modules in series, generating high voltage to allow the grid-connected operation of centralized inverters. Centralized PV systems have some limitations, such as: high voltage DC cables between PV strings and the inverter, mismatch losses due to centralized MPPT, losses in the string diodes and risks of hotspots in the PV modules during partial shading. String and multi-string inverters, as shown in Figure 1.2(b) are distributed version of the centralized inverters, where each single string of PV modules are independently managed. String-level power process of PV modules can eliminate the cost intensive DC cabling. There are no losses

associated with string-diodes and string-level MPPT is assumed to increase the overall efficiency, when compared to the centralized inverters.

Figure 1.2 PV grid-tie inverter systems.

In order to overcome the mismatch losses between PV modules of traditional string and multi-string inverter architectures, two new PV gridtie inverter concepts, as shown in Figure 1.2(c) have been developed. A circuit called a power optimizer, which is a dc-dc converter embedded into PV modules of traditional string PV inverter systems. This increases the system energy output for PV modules by constantly tracking the MPPT of each module individually. However, the mismatch losses may still exist due to the series connection of power optimizers.

Microinverter, as shown in Figure 1.2(c), converts the DC power from each individual PV module directly to the AC gird. For PV systems using microinverters, they have the advantage of reducing the impact of shading,

debris or snow covering the PV module, which would reduce the power output. Each microinverter harvests optimum power by performing MPPT for its connected module, eliminating the mismatch losses in PV systems. The installation of each microinverter for an individual PV module can simplify system installation, reduce maintenance cost, and allow flexible upgrade.

The main criteria for widespread adoption of microinverters in PV industry are low cost, high conversion efficiency, and long lifespan. Electrolyte capacitors have been identified as one of the limiting components which determine the lifespan of PV grid-tie inverters [A13]-[A18]. Since microinverters are typically attached to the back side of the PV module, this exposes an individual microinverter to high temperatures causing accelerated operational degradation. So the electrolyte capacitors must be avoided to design a long-lifespan microinverter.

The motivations of this research project are to address the high-efficiency, improved lifespan and low-cost challenges of the microinverters.

#### 1.2 State-of-the-art microinverter technologies

This section will give a review of existing microinverter topologies. The techniques used to eliminate electrolytic capacitor are also studies.

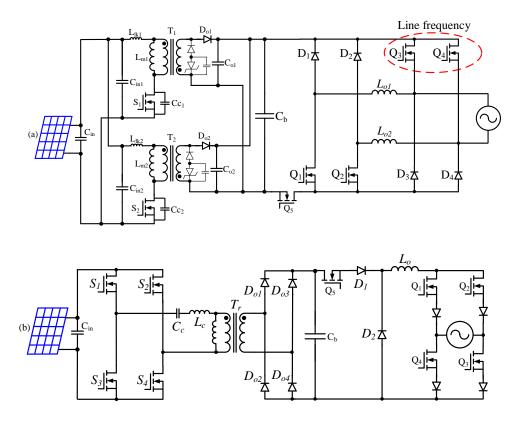

#### 1.2.1 Reviews of the existing microinverter topologies

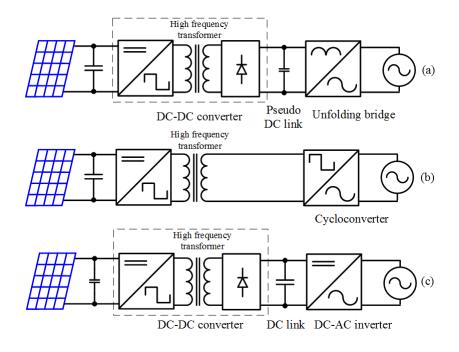

Microinverters can be categorized into three groups according to the different DC-link configurations: with a DC link, pseudo DC link, and without a DC link, as shown in Figure 1.3 [B2].

Figure 1.3 Three different types of microinverters.

#### I) Microinverters with a pseudo DC link

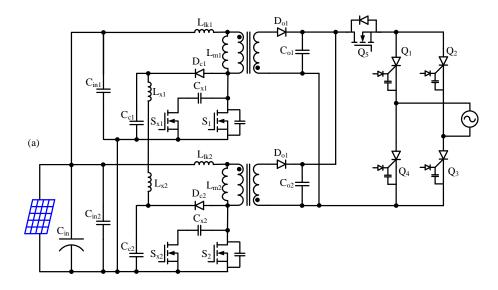

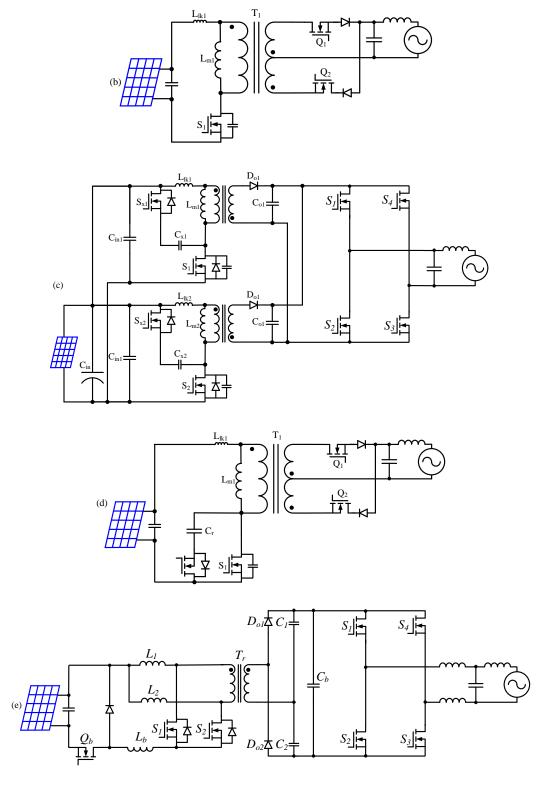

Figure 1.3(a) shows microinverters with a pseudo DC link. The mode of operation for the pseudo DC link microinverter is where the voltage on the pseudo DC link has a rectified sinusoidal waveform, then an unfolding inverter operating at line frequency, which converts the rectified-sine waveform into the sine waveform synchronized with the grid voltage. Normally, the microinverters with pseudo DC links also referred as single-stage microinverters since only the first dc-dc stage works with high-frequency. Quite a few single-stage microinverter topologies have been proposed [F3], [B4]-[B21], as shown in Figure 1.4. The most popular topology for the dc-dc stage is the flyback converter [F3], [B4]-[B20] due to its buckboost gain feature and simple structure. The dc-dc stage of topology in Figure 1.4(a), [F3], [B4]-[B11] is an interleaved quasi-resonant flyback converter

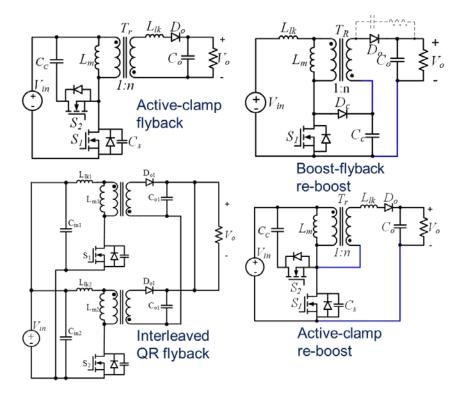

followed by a full-wave unfolding stage. The quasi-resonant operation dc-dc stage can reduce the switching losses and allow the microinverter to run at higher switching frequencies. The two interleaved units of the dc-dc stage run together at high power to reduce the conduction losses. When the grid side power is low only one unit runs to limit the switching frequency and reduce the core loss. The dc-dc stage in Figure 1.4(b) is also a flyback converter, however a center-tapped transformer [B12]-[B16] is used as the unfolding stage to generate the sinusoidal waveform. Some topologies used active-clamping techniques [B17]-[B20] to capture the leakage energy of the flyback transformer, the downsides to this approach is that there are higher circulating losses and higher number of components. The dc-dc stage of the topology in Figure 1.4(e) is a buck cascaded boost converter, which works as boost converter at high grid line voltage and as buck converter at low grid line voltage.

Figure 1.4 Microinverters with a pseudo DC link.

## II) Microinverters without DC link

If removing the rectifier diodes and replacing the unfolding bridge with a cycloconverter, microinverters can be implemented without using DC link, as show in Figure 1.3(b). The microinverter topologies using cycloconverters are shown as in Figure 1.5, where the low voltage DC voltage is changed to a high frequency AC voltage and amplified to a higher level compatible with the AC grid. A cycloconverter directly converts the AC voltage or current with high-frequency to grid frequency. Due to the high stresses on the AC bidirectional switches and complex control, the development of this type of microinverter is limited.

Figure 1.5 Microinverters using cycloconverter technologies [B22], [B23].

#### III) Microinverters with DC link

Microinverters with DC link, as shown in Figure 1.3(c), are referred to as two-stage microinverters, where both dc-dc and dc-ac stages work at high frequency. The dc-dc stage boosts the low voltage of the PV module to a high DC bus voltage compatible with the AC grid voltage to run the dc-ac inverter.

Normally, the dc-ac stage is a full-bridge inverter, [F4], [B24]-[B29], while the dc-dc stage can be a high boost ratio voltage-fed [F4], resonant [B24], [B25] or current-fed [B26]-[B29] converter. The dc-ac full-bridge inverter normally requires careful design considerations [F4], [B24]-[B27], [B29] to use modern high speed MOSFET devices to achieve high efficiency. The dc-dc stage can use soft-switching techniques, like quasi-resonant [F4], resonant [B24], [B25] or active-clamping [B26], [B28] to reduce the switching losses and achieve high efficiency.

Figure 1.6 Two-stage microinverters.

#### 1.2.2 Techniques to eliminate electrolytic capacitors in microinverters

Microinverters have a power level ranging from 150 W to 300 W, normally use a single-phase connection to the grid. For a single-phase system, the PV-side power is

$$P_{PV} = V_{PV} \times I_{PV} \tag{1.1}$$

which is a DC power. The grid-side power is

$$P_{g}(t) = P_{g_{avg}} + P_{g_{avg}} cos(2\omega_{g}t)$$

(1.2)

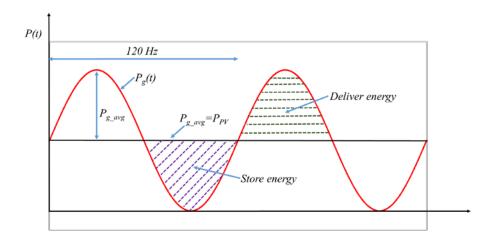

which is composed of a DC average power plus a double line ripple power. As shown in Figure 1.7, a basic electrical feature of a single-phase system is that the energy delivered includes both an average power that transfers useful energy and a double line ripple power that flows back and forth in the system. So the energy storage components that are required in single-phase microinverters used to store and retrieve this double line ripple energy must satisfy the power balance of the system.

Figure 1.7 Grid side power and its decomposition.

The most commonly-used energy storage component in microinverters are large electrolytic capacitors due to its high energy density. For example, as shown in Figure 1.8, a commercial 175 W microinverter M190-72-240 from Enphase [F3] requires 5×1.8 mF for a total capacitance of 9 mF. This electrolyte capacitor bank is used to buffer the double line ripple from going to the PV module. In order to increase the life expectancy and improve the long-term reliability, electrolytic capacitors need to be avoided in microinverters [A13]-[A17].

175 W Microinverter

Figure 1.8 Commercial 175 W microinverter M190-72-240 from Enphase [F3], which requires 9 mF of electrolyte capacitors to buffer the double line ripple.

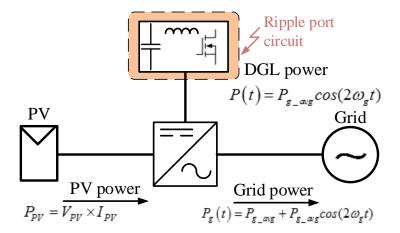

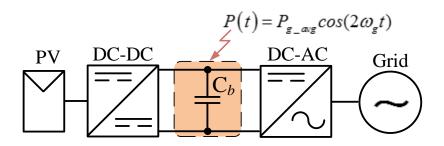

Different techniques have recently been presented to employ film capacitors as energy storage components in single-phase microinverters to increase the lifespan [B3], [B30]-[B37]. These techniques can be categorized three types: PV-side, dc-link, and ac-side decoupling techniques [B3]. Among these three techniques, PV-side and ac-side decoupling techniques requires adding extra circuits, as shown in Figure 1.9, to buffer the double line ripple energy. However this results in cost increase, overall efficiency reduction, and control complexity [B3]. Figure 1.10 shows the dc-link decoupling technique used for single-phase two-stage (SPTS) microinverters that can use the film capacitors as intermediate dc bus capacitors without adding extra circuits [B3], [F4]. Although SPTS microinverters have one more energy transfer stage than single-stage ones, the efficiencies can be comparable to single-stage microinverters by using soft-switching techniques, new converter topologies and modern high performance semiconductor devices. One example

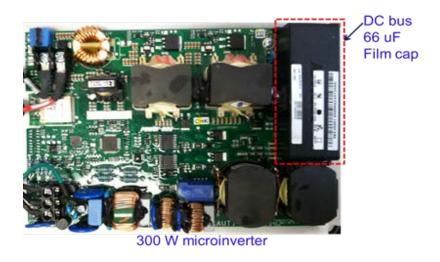

of a two-stage microinverter with high efficiency by the company Power-One Inc., is shown in Figure 1.11, with a reported CEC efficiency of 96% for a power range of 300 W [F4]. This product illustrates that the two-stage architecture is an optimal solution to eliminate the electrolytic capacitors compared to using the "ripple port" technique.

Since SPTS electrolyte-free microinverters have one additional energy transfer stage compared to the single-stage microinverters, both the high boost ratio dc-dc converter and the dc-ac inverters are required to have high efficiency to achieve high system efficiency.

Figure 1.9 Extra ripple power circuit used to buffer the double line ripple power and eliminate electrolytic capacitors in single-stage microinverters with PV-side and AC-side buffing techniques.

Figure 1.10 Single-phase two-stage microinverters using high voltage intermediate DC bus capacitor C<sub>b</sub> as double line ripple power buffer.

Figure 1.11 commercial 300 W electrolyte-free microinverter MICRO-0.3-I from Power-One Inc. [F4].

### 1.3 Objectives of the research project

Although the advantages of microinverters have been recognized, wide adoption of microinverters still presents many challenges. The research work in this project is to address these challenges with the following objectives.

#### • High CEC efficiency

A growing demand for maximized energy extraction from PV sources have stimulated substantial technology development efforts towards highefficiency PV grid-tie inverters. The efficiency of PV inverters is weighted for specific power levels in the California Energy Commission (CEC). The individual efficiencies, at 10%, 20%, 30%, 50%, 75%, and 100% of nominal power, are weighted and summed up according to:

$$\eta_{CEC} = 0.04\eta_{10\%} + 0.05\eta_{20\%} + 0.12\eta_{30\%} + 0.21\eta_{50\%} + 0.53\eta_{75\%} + 0.05\eta_{100\%}$$

(1.3)

Today's string inverters based on innovative transformerless technologies [D5]-[D16] have reached a CEC efficiency of 98% [D7]. With the latest SiC devices, the CEC efficiency of transformerless inverters have the potential to improve [D8]. Today's commercial PV microinverters normally have a CEC efficiency that ranges from 93.5% to 96.0% [F3]-[F6]. In order to achieve a system CEC efficiency over 95%, the first-stage high boost ratio dc-dc converter must have a CEC efficiency over 97%.

#### Low electronic cost, high power density and low profile

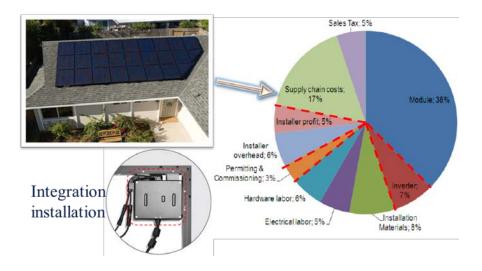

Figure 1.12 shows the cost breakdown of a 5 kW residential PV system in year 2010, the total cost of which is \$5.71/W [A3]. Breaking down the total cost, the inverter hardware accounts for 7% and the installation labor accounts for about 30%. This PV system used the string technology, where a cluster of PV modules share a common inverter. If microinverters are used, each PV module requires its own dedicated microinverter, which leads to increased electronics costs compared to the system using string technology. With the continuous decreasing price of PV modules [A4], the cost of PV inverters and installation labor are becoming more dominant in the overall

system cost. As a result of the SunShot target \$1.5/W in 2020 [A3], cost reduction of microinverters becomes more stringent. Microinverters should be designed with high power density and low profile to make integration with the PV module easier and reduce the installation labor cost.

Figure 1.12 Cost breakdown in year 2010 for 5 kW residential PV system with one string inverter: total \$5.71/W; DOE SunShot target is \$1.5/W in 2020 [A3].

#### No electrolytic wear-out mechanism

In order to fairly compare the capital invested on a PV project, the levelized cost of energy (LCOE) instead of initial investment cost is normally used to evaluate the system cost, which is defined as [A15]

LCOE =

$$\frac{\text{Total Life Cyle Cost}}{\text{Total Lifetime Enegy Production}} = \frac{\sum_{n=0}^{N} \frac{C_n}{(1+d)^n}}{\sum_{n=0}^{N} \frac{Q_n}{(1+d)^n}}$$

(1.4)

where  $C_n$  is the cost for installation, module, balance of the system, inverter, finance in year n;  $Q_n$  is produced energy in year n; N is the lifetime of the system; d is the discount rate.

Lowering LCOE requires not only reducing the electronic cost but also increasing the lifespan of the microinverters. The improved lifespan provided by the avoidance of electrolytic capacitors saves the maintenance and repair costs. This can in turn contribute to the reduction of LCOE of the systems.

#### Improved MPPT performance and grid current quality

Although film capacitors have far more lifetime, the energy density of film capacitors are much lower compared to the electrolytic counterparts. In order to reduce the volume and save the cost of the microinverters, the capacitance must be reduced. This will lead to high double line ripple oscillation on the DC bus. The propagation of this double line oscillation back to PV module will compromise the MPPT performance. Also if this double line oscillation goes to the grid side, the grid current will be distorted. So advanced control techniques are required to reject the propagation of this double line ripple oscillation to PV side and grid side to improve the MPPT performance and grid current quality.

#### 1.4 Major contributions and outline of the dissertation

High boost ratio dc-dc converters using hybrid transformer with CEC efficiency over 97% are proposed in this project. The magnetic core in the proposed converter combines the functions of traditional transformer and

coupled-inductor. As a result, the power device utilization is improved and magnetic core utilization is optimized compared to traditional transformer-isolated or coupled-inductor high boost ratio dc-dc converters. As a result of incorporating the resonant operation mode into the traditional high boost ratio pulse-width modulation (PWM) converters, the turn-off and turn-on losses of the switches are reduced. The improved power device utilization can reduce the cost of the converter, the optimized magnetic utilization allows the converters to use smaller magnetic core, and the reduced switching losses can increase the efficiency of the converters under all load conditions. Therefore, the proposed converters are attractive for the microinverter applications. Experimental results validate the performance of the proposed converters.

A transformerless MOSFET inverter topology with CEC efficiency 98.6% is presented. The proposed topology works separately during the positive and negative half grid line cycle using a split-phase structure, which eliminates the shoot-through issue of traditional full-bridge inverters. The body diode reverse recovery issue of MOSFET devices are also avoided and fast-speed superjunction MOSFET devices can be employed to achieve ultrahigh efficiency. The effectiveness of the proposed topology is experimentally verified.

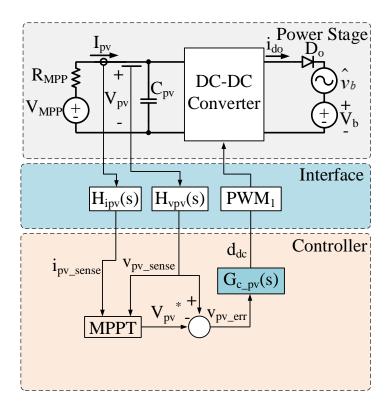

An average model of the high boost ratio dc-dc converter is derived. A control technique is proposed to reject the double line ripple voltage oscillation on the PV module, improving the accuracy of the MPPT.

Simulation and experimental results validate the control design. The system model of single-phase two-stage microinverter is derived. A control technique only using simple low cost microcontroller with low sampling frequency to eliminate the electrolytic capacitors without any added penalties is presented. Detailed control methodology is depicted and design guideline is suggested. Experiments are performed and the results are utilized to validate the effectiveness of the proposed control technique.

The dissertation will be organized as following:

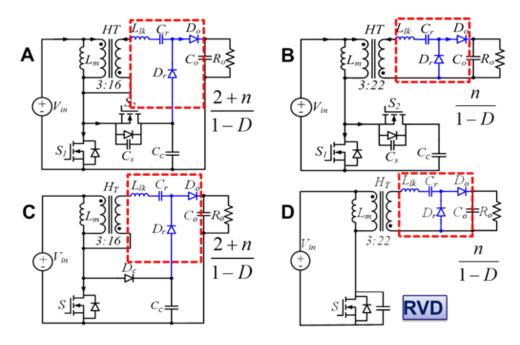

Chapter2-The high boost ratio dc-dc converter for SPTS microinverters requires high efficiency over wide power range, low cost and simple structure. A historical review of the existing coupled-inductor, current-fed and resonant high boost ratio dc-dc converter topologies shows that none of them can satisfy these requirements simultaneously. A new high boost ratio dc-dc converter using hybrid transformer concept suitable for microinverter applications is presented. The operation principle of the proposed converter is discussed and a design guideline is suggested. The experimental results are given to justify the effectiveness of the proposed converter. Finally, a family of hybrid transformer dc-dc converters are presented by using basic "resonant voltage doubler" (RVD) cell.

Chapter 3-This chapter evaluates the performance of the hybrid transformer dc-dc converters through power device utilization (PDU), magnetic utilization (UD), switching loss characteristics and cost-effectiveness. These evaluations

prove the suitability of hybrid transformer dc-dc topologies for PV microinverter applications.

Chapter 4-This chapter analyzes the performance of single-phase transformerless inverter with regards to the efficiency, EMI and leakage current. A review of existing transformerless inverter topologies is presented. The analysis of the loss models for power semiconductor devices used in gridtie inverter show that using latest superjunction MOSFETs and SiC devices ultrahigh efficiency can be achieved in transformerless inverters. Then a new high reliability and high efficiency transformerless inverter topology that can use superjunction MOSFETs and SiC devices to achieve ultrahigh efficiency is presented.

Chapter5-This chapter analyzes the energy storage requirements in single phase PV inverters. Effects of double line ripple on MPPT accuracy and grid current distortion are elaborated. The small-signal model of the hybrid transformer dc-dc converter using approximate state-space averaging model is derived. A control method to rejection the double line ripple oscillation on the PV module is presented and experimentally justified. The system model of SPTS microinverter is derived. A control technique which can eliminate electrolyte capacitors without any added penalties in microinverter is presented. Experiments are performed and the results justify the effectiveness of the proposed control technique.

Chapter 6- Major results and contributions of this research project are summarized. Based upon the implementation experience and experimental results, future works are directed.

# Chapter 2 Hybrid Transformer High Boost Ratio DC-DC Converter Topologies

Solar energy is becoming a mainstream source of electricity. Integrating the solar energy from the PV modules into the existing power distribution infrastructure requires grid-tie inverters. Microinverter, which performs MPPT for each individual PV module and directly feeds ac power from the PV modules to the existing ac grid is becoming a new trend. Microinverter is typically attached at the back, or may be seamlessly integrated onto the metal frame of PV module, hence it is highly desirable that microinverters have a long lifespan that can match PV modules, which routinely warrant 25 years of operation [A13]-[A18], [F7].

The electrolytic capacitors have been identifies as one of the most unreliable components in PV grid-tie inverters [A14]-[A17]. Hence it is desirable to avoid the electrolytic capacitors in microinverters. Two techniques are commonly used to eliminate electrolytic capacitors [B3]. One is "ripple port" technique, which added an additional ripple port circuit buffer the double line ripple power [B3]. However this leads to efficiency suffering, cost penalty and control complexity. Another technique is using two-stage architecture, where the inherent high voltage DC bus can be used as energy buffer to reduce the capacitance requirements hence allowing to use low-capacitance film capacitors. The two-stage technique does not require additional circuits, which avoids cost and complexity penalties [B3].

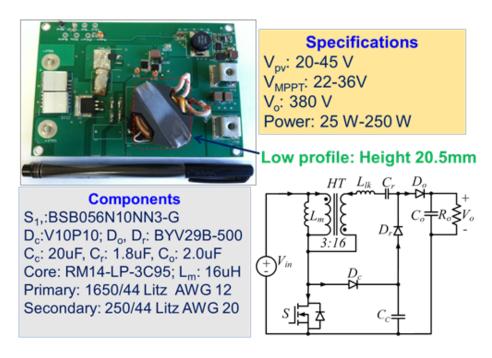

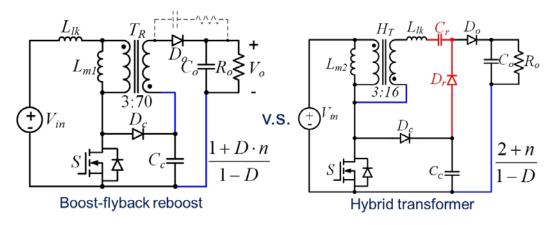

In two-stage architecture, a high boost ratio dc-dc converter is required to increase the low PV module voltage to a high DC bus voltage for following stage grid-tie inverter. This chapter proposes a new high boost ratio dc-dc converter using hybrid transformer concept, which has advantages of high efficiency over wide input voltage and output power range, smaller size, low cost and low component counts. Experimental results based on a 250 W prototype board justify the effectiveness of the proposed converter. By introducing resonant voltage double (RVD) cell into traditional coupled-inductor PWM converters, a group of hybrid transformer dc-dc converters suitable for microinverters are derived and the performance of these converters are compared.

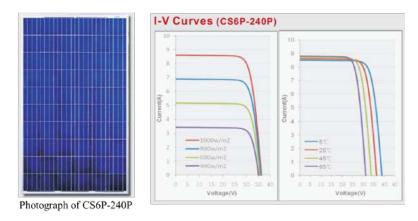

#### 2.1 Specifications and demands

In order to verify the performance of the designed microinverter, PV module CS6P-240P from CanadianSolar Inc. [F7] were ordered for system integration and field demonstration test, which has 25-year module power output warranty with the electrical specifications as shown in Figure 2.1. The nominal maximum power  $P_{max}$  is 240 W with optimum operation voltage  $V_{mp}$  29.9 V, open circuit voltage  $V_{oc}$  36.6 V under standard test conditions (STC) of irradiance of 1000W/m², spectrum AM 1.5 and cell temperature of 25°C. Figure 2.2 shows a cluster of typical I-V curves of CS6P-240P module under different irradiance and cell temperature conditions. There is only one MPP on each curve, which needs the dc-dc converter to accomplish the tracking of

this point. In order to maximize the energy capture from the PV modules, the dc-dc converter needs to have high efficiencies over wide input voltage and output power ranges.

| lectrical Data                      |      | CS6P-220P              | CS6P-225P | CS6P-230P | CS6P-235P | CS6P-240P |

|-------------------------------------|------|------------------------|-----------|-----------|-----------|-----------|

| Nominal Maximum Power at STC (Pmax) |      | 220W                   | 225W      | 230W      | 235W      | 240W      |

| Optimum Operating Voltage (Vmp)     |      | 29.2V                  | 29.4V     | 29.6V     | 29.8V     | 29.9V     |

| Optimum Operating Current (Imp)     |      | 7.53A                  | 7.65A     | 7.78A     | 7.90A     | 8.03A     |

| Open Circuit Voltage (Voc)          |      | 36.6V                  | 36.7V     | 36.8V     | 36.9V     | 37.0V     |

| Short Circuit Current (Isc)         |      | 8.09A                  | 8.19A     | 8.34A     | 8.46A     | 8.59A     |

| Operating Temperature               |      | -40℃~+85℃              |           |           |           |           |

| Maximum System Voltage              |      | 1000V (IEC) /600V (UL) |           |           |           |           |

| Maximum Series Fuse Rating          |      | 15A                    |           |           |           |           |

| Power Tolerance                     |      | +5W                    |           |           |           |           |

| Temperature Coefficient             | Pmax | -0.43%/C               |           |           |           |           |

|                                     | Voc  | -0.34 %/℃              |           |           |           |           |

|                                     | Isc  | 0.065 %/C              |           |           |           |           |

|                                     | NOCT | 45°C                   |           |           |           |           |

Figure 2.1 Electrical specifications of CS6P-240P PV module [F7].

Figure 2.2 I-V curves of CS6P-240P PV module [F7].

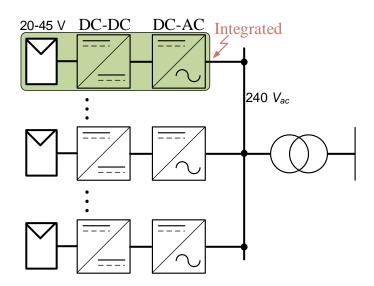

The designed microinverter in this dissertation feeds the energy from the PV module to the grid through single-phase 240 V<sub>ac</sub> 60 Hz system, which is normally available for U.S. residential houses. The microinverter has two main tasks under given PV module and grid electrical specifications:

$\bullet$  To amplify and invert the DC PV power with the voltage range from 20 V to 45 V and maximum power 250 W into a 60 Hz current to feed to 240  $V_{ac}$  grid.

• To implement MPP to maximize the energy capture from the PV module The configuration of two-stage microinverters as shown in Figure 2.3, has a high boost ratio dc-dc converter followed by a dc-ac inverter. The dc-dc conversion stage requires a high efficiency, high boost ratio dc-dc converter to increase the low dc input voltage from the PV module to a higher dc voltage. This voltage has to be higher than the peak output voltage of the dc-ac inverter, nominally in the 380 V-400 V range for the 240 V<sub>ac</sub> grid system. The main reason why two-stage configuration was selected in this project is that the two-stage design can avoid electrolytic capacitors.

Figure 2.3 Microinverters with two-stage architecture.

#### 2.2 Review of the state-of-the-art high boost ratio dc-dc converter topologies

This section gives a review of the state-of-the-art high boost ratio dc-dc converter topologies, including three groups according to the energy transfer mechanics. The pros and cons of each group of converters will be analyzed according to the suitability for the microinverter applications.

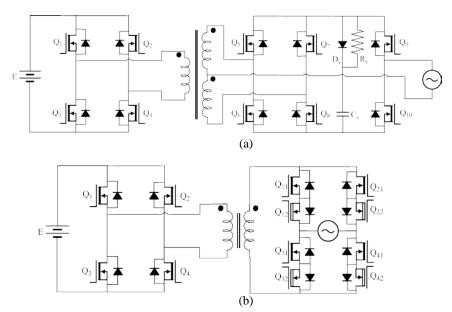

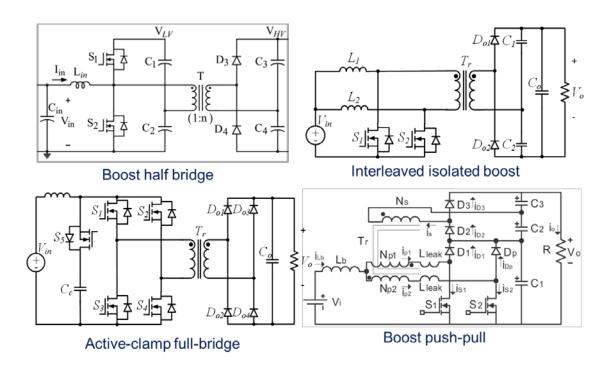

#### 2.2.1 Coupled-inductor PWM converters

The first group of high boost ratio dc-dc converters are converters using coupled-inductors, as shown in Figure 2.4 [C1], [C7]-[C24]. The high boost ratio of this type of converters is from the transformer effect of the coupled-inductor. The structure of this type of converter is simple and duty ratio range is narrow even for wide input voltage applications as a result of the buck-boost gain feature. However, this type of converters has poor magnetic utilization, which results in high volume design for a given transferred power. The voltage stress of output diodes is equal to the output DC bus voltage plus the secondary-reflected input voltage. For two-stage micro-inverters, this voltage may be as high as 800 V, so normally 1200 V SiC diodes with zero reverse-recovery must be used to reduce the diode turn-off losses. However, this will lead to high cost penalty.

Figure 2.4 Coupled-inductor PWM dc-dc converters.

# 2.2.2 Current-fed PWM converters

Second type of high boost ratio dc-dc converters are current-fed PWM converters, as shown in Figure 2.5 [C25]-[C43]. This type of converters inherits the high boost gain of traditional simple boost converter and the input current ripple is low. However, this type of converters requires more magnetic components, which result in high cost and large volume. For the circuits like boost half bridge and boost push-pull dc-dc converters, the voltage stresses on the main devices are clamped by the auxiliary switches or diodes, however the efficiency of these two converters suffers from the cascaded structures.

Figure 2.5 Current-fed PWM converters.

# 2.2.3 LLC resonant converters

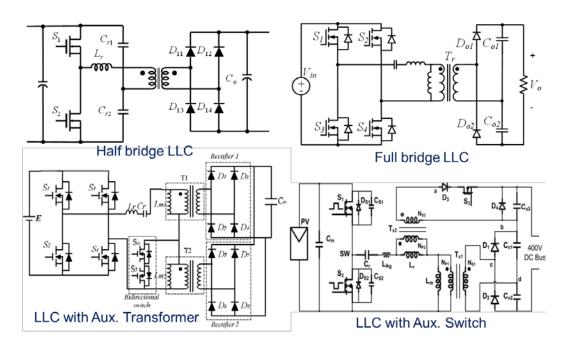

Figure 2.6 LLC resonant converters.

The third type of converters are LLC resonant converters, as shown in Figure 2.6 [C44]-[C55], which are very popular in computer industry for the applications where hold up time is required. Traditional half-bridge and fullbridge LLC resonant converters have high peak efficiency at resonant frequency. They can run with high frequency to reduce the magnetic sizes as a result of zero-voltage-switching (ZVS) of active switches and zero-currentswitching (ZCS) of output diodes. The voltage regulation of traditional LLC converters is achieve by variable frequency. For the applications with wide input voltage range, like PV modules, the operation frequencies may be far from resonant frequency. This will results in high circulating losses and LLC converters may lose ZVS or ZCS. In order to improve the voltage regulation capability of traditional LLC resonant converters, some improved versions of LLC resonant converter, such as LLC with auxiliary transformer or LLC with auxiliary switch were proposed. However, these improved converters have very complex structures resulting in high cost and complex control.

Table 2-1 summarizes the pros and cons of the state-of-the-art high boost ratio dc-dc converters. It indicates that new high boost ratio dc-dc topologies with high efficiency, simple structure and low cost are desired for two-stage microinverters.

Table 2-1 Pros and cons of the state-of-the-art high boost ratio dc-dc converters

| Type | Pros | Cons |

|------|------|------|

|      |      |      |

| Coupled-inductor | <ul><li>Simple structure</li><li>Low duty range</li></ul> | <ul><li> Poor magnetic utilization</li><li> High voltage stresses on output diodes</li></ul> |

|------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------|

|                  |                                                           | Two or three magnetics                                                                       |

| Current-         | High voltage gain                                         | Efficiency suffers from                                                                      |

| fed              | Low input current ripple                                  | leakage inductors or                                                                         |

|                  |                                                           | cascaded-structure                                                                           |

| LLC<br>resonant  | High peak efficiency                                      | Complex control                                                                              |

|                  | Potential high frequency                                  | Complex structure and high                                                                   |

|                  | operation                                                 | cost due to aux. circuits                                                                    |

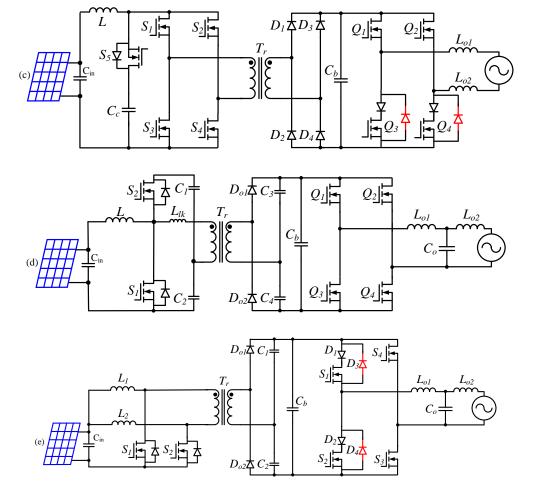

# 2.3 Proposed hybrid transformer high boost ratio dc-dc converter

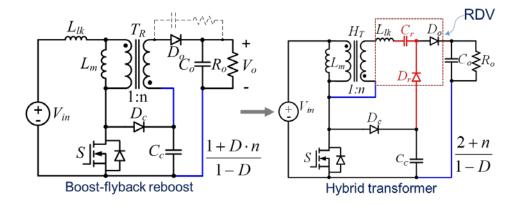

For application of microinverters, the high efficiency over a wide power range is extremely important because the performance is weighted differently for specific load levels in the CEC or European Union (EU) standards. In this section, a high boost ratio dc-dc converter with hybrid transformer is presented to achieve high system level efficiency over wide input voltage and output power ranges, while still maintain low cost and simple structure. As shown in Figure 2.7, by introducing a RVD, which is composed of leakage inductance of  $L_{lk}$ , a small resonant capacitor  $C_r$ , diodes  $D_r$  and  $D_o$  into the energy transfer path, a hybrid operation mode, which combines PWM and resonant power conversions [C4],[C5], is introduced into the proposed high boost ratio dc-dc converter.

Figure 2.7 Derive hybrid transformer high boost ratio dc-dc converter by introducing resonant voltage doubler into traditional boost-flyback reboost PWM converter.

In the proposed converter, the inductive and capacitive energy can be transferred simultaneously to the high voltage dc bus increasing the total power delivered decreasing the losses in the circuit. As a result of the energy transferred through the hybrid transformer that combines the modes where the transformer operates under normal conditions and where it operates as a coupled-inductor, the magnetic core can be used more effectively and smaller magnetics can be used. The continuous input current of the converter causes a smaller current ripple than that of previous high boost ratio converter topologies that used coupled-inductors. The lower input current ripple is useful in that the input capacitance can be reduced and it is easier to implement a more accurate MPPT for PV modules. The conduction losses in the transformer are greatly reduced because of the reduced input current RMS value through the primary side. The voltage stress of the active switch is always at a low voltage level and independent of the input voltages. Due to

the introduction of the resonant portion of the current, the turn-off current of the active switch is reduced. As a result of the decreased RMS current value and smaller turn-off current of the active switch, high efficiency can be maintained at light output power level and low input voltage operation. Because of the resonant capacitor transferring energy to the output of the converter, all the voltage stresses of the diodes are kept under the output dc bus voltage and independent of the input voltage.

#### 2.4 Operation principle

This section gives the basic operation principle of the proposed converter, then the device voltage stresses and conversion ratio are derived, finally the design procedure is suggested.

## 2.4.1 Topological stages and key waveforms

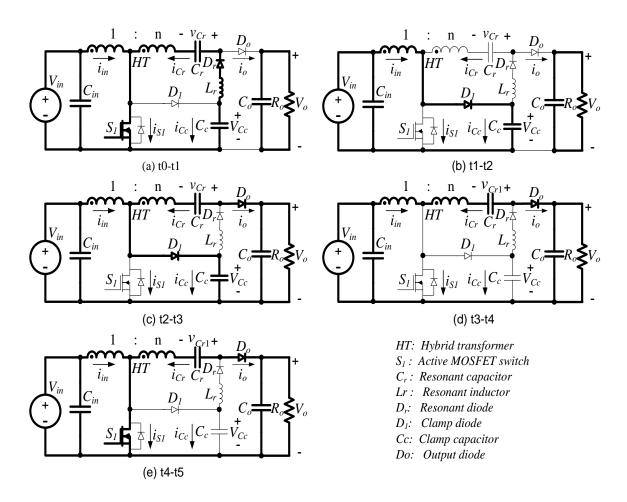

Figure 2.8 illustrates the five steady state topology stages of the proposed dc-dc converter for one switching cycle. Figure 2.9 shows the key voltage and current waveforms for specific components of the converter over the switching cycle.

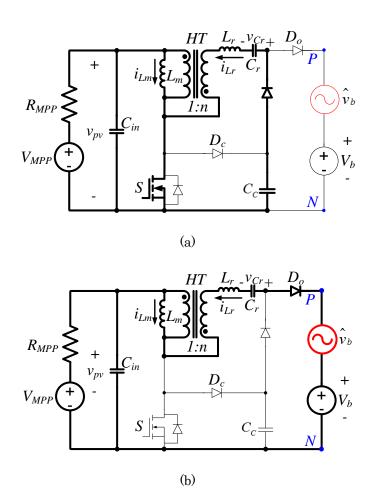

$C_{in}$  is the input capacitor; HT is the hybrid transformer with the turn ratio 1: n;  $S_I$  is the active MOSFET switch;  $D_I$  is the clamping diode, which provides a current path for the leakage inductance of the hybrid transformer when  $S_I$  is off;  $C_c$  captures the leakage energy from the hybrid transformer and transfers it to the resonant capacitor  $C_r$  by means of a resonant circuit composed of  $C_c$ ,  $C_r$ ,  $L_r$  and  $D_r$ ;  $L_r$  is a resonant inductor, which operates in the

resonant mode;  $D_r$  is a diode used to provide a unidirectional current flow path for the operation of the resonant portion of the circuit.  $C_r$  is a resonant capacitor, which operates in the hybrid mode by having a resonant charge and linear discharge. The turn on of  $D_r$  is determined by the state of the active switch  $S_L$   $D_o$  is the output diode similar to the traditional coupled-inductor boost converter;  $C_o$  is the output capacitor.  $R_o$  is the equivalent resistive load.

Figure 2.8 Topological states of the high boost ratio dc-dc converter with hybrid transformer.

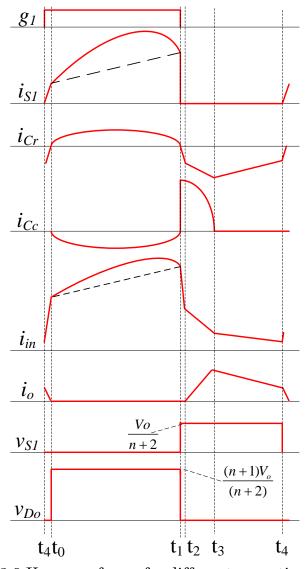

Figure 2.9 Key waveforms for different operation stages.

For the waveforms in Figure 2.9,  $g_1$  represents the driver signal for the active MOSFET switch  $S_i$ ;  $i_{SI}$  is the current of the MOSFET  $S_i$ ;  $i_{Cr}$  is the current of the resonant capacitor  $C_i$ ;  $i_{Cc}$  is the current of clamping capacitor  $C_i$ ;  $i_{in}$  is the primary side current of hybrid transformer;  $i_0$  is the current through the output diode;  $v_{SI}$  and  $v_{Do}$  are the voltage waveforms of the active switch MOSFET  $S_I$  and the output diode  $D_0$  respectively. For simplicity, we assume

that the dc input voltage is a stiff voltage source with a constant voltage  $V_{in}$ , the load is a resistor and all the switch and diodes are ideal devices.

The five operation modes are briefly described as follows.

$[t_0,t_1]$ , [Fig. 2.8 (a)]: In this period, MOSFET  $S_I$  is on, the magnetizing inductor of the hybrid transformer is charged by input voltage;  $C_r$  is charged by  $C_c$  and the secondary-reflected input voltage  $n V_{in}$  of the hybrid transformer together by the resonant circuit composed of secondary side of the hybrid transformer ,  $C_r$ ,  $C_c$ ,  $L_r$  and  $D_r$ . The energy captured by  $C_c$  is transferred to  $C_r$ , which in turn is transferred to the load during the off time of the MOSFET. The current in MOSFET  $S_1$  is the sum of the resonant current and linear magnetizing inductor current as shown in Fig. 5. There are two distinctive benefits that can be achieved by the linear and resonant hybrid mode operation. The first benefit is that the energy is delivered from source during the capacitive mode and inductive mode simultaneously. Compared to previous coupled-inductor high boost ratio dc-dc converters with only inductive energy delivery, the dc current bias is greatly reduced, decreasing the size of the magnetics. Second the turn-off current is decreased; this causes a reduction in the turn-off switching losses.

[t<sub>1</sub>,t<sub>2</sub>], [Fig. 2.8 (b)]: At time t<sub>1</sub>, MOSFET  $S_I$  is turned off, the clamping diode  $D_I$  is turned on by the leakage energy stored in the hybrid transformer during the time period that the MOSFET is on and the capacitor  $C_c$  is charged which causes the voltage on the MOSFET to be clamped.

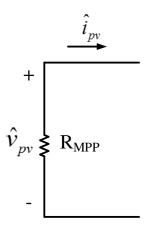

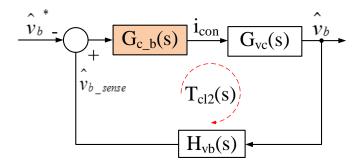

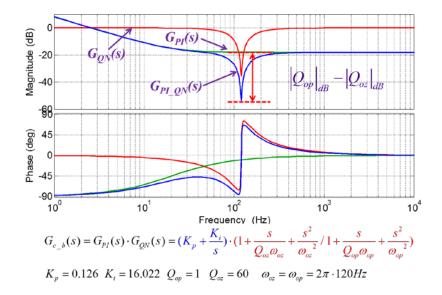

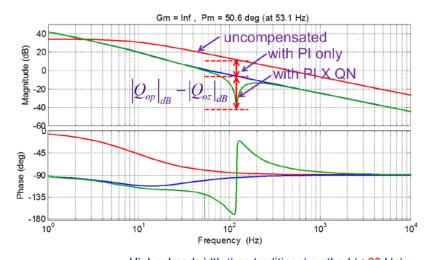

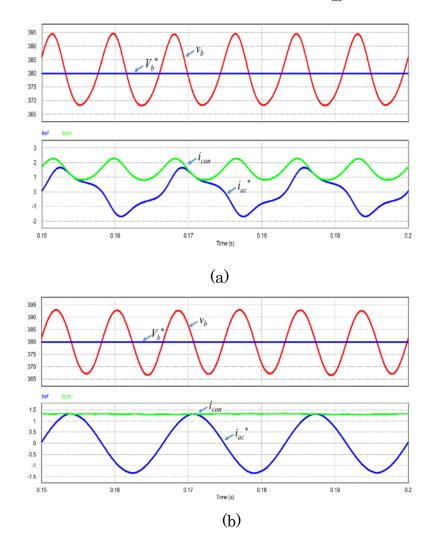

[t<sub>2</sub>, t<sub>3</sub>], [Fig. 2.8 (c)]: At time t<sub>2</sub>, the capacitor  $C_c$  is charged to the point that the output diode  $D_o$  is forwarded-biased. The energy stored in the magnetizing inductor and capacitor  $C_r$  is being transferred to the load and the clamp diode  $D_I$  continues to conduct while  $C_c$  remains charged.