# An Investigation of Differential Power Analysis Attacks on FPGA-based Encryption Systems

Larry T. McDaniel III

Thesis submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

Master of Science In Electrical Engineering

Dr. Tom Martin, Chair Dr. Peter Athanas Dr. Mark Jones

May 29, 2003 Blacksburg, Virginia

Keywords: DPA, SPA, power analysis, Data Encryption Standard, FPGA, cryptography, smart cards.

© 2003, Larry McDaniel

# An Investigation of Differential Power Analysis Attacks on FPGA-based Encryption Systems

#### Larry T. McDaniel III

#### **Abstract**

Hardware devices implementing cryptographic algorithms are finding their way into many applications. As this happens, the ability to keep the data being processed or stored on the device secure grows more important. Power analysis attacks involve cryptographic hardware leaking information during encryption because power consumption is correlated to the key used for encryption. Power analysis attacks have proven successful against public and private key cryptosystems in a variety of form factors. The majority of the countermeasures that have been proposed for this attack are intended for software implementations on a microcontroller. This project focuses on the development of a VHDL tool for investigating power analysis attacks on FPGAs and exploring countermeasures that might be used.

The tool developed here counted the transitions of CLB output signals to estimate power and was used to explore the impact of possible gate-level countermeasures to differential power analysis. Using this tool, it was found that only a few nodes in the circuit have a high correlation to bits of the key. This means that modifying only a small portion of the circuit could dramatically increase the difficulty of mounting a differential power analysis attack on the hardware. Further investigation of the correlation between CLB outputs and the key showed that a tradeoff exists between the amount of space required for decorrelation versus the amount of decorrelation that is desired, allowing a designer to determine the amount of correlation that can be removed for available space. Filtering of glitches on CLB output signals slightly reduced the amount of correlation each CLB had. Finally, a decorrelation circuit was proposed and shown capable of decorrelating flip-flop outputs of a CLB, which account for less than 10% of the CLB outputs signals.

# Acknowledgements

First, I have to thank God for bringing me to this point in my life and giving me the motivation and determination to conquer new problems. Thank you to Dr. Tom Martin, my advisor, for his incredible amount of advice and encouragement. I would also like to thank Dr. Peter Athanas and Dr. Mark Jones for serving on my thesis committee and Dr. Ezra Brown and Dr. Scott Midkiff for originally serving as part of my committee.

To Kimberly, my wife, thank you for being a constant source of support and accepting of my long hours in the lab. To my friends, thank you for being a part of non-work activities that have made my time at Virginia Tech enjoyable. Finally, to my Mom, Dad, and family, thank you for all your encouragement and guidance in my life.

# **Table of Contents**

| Abstract                                | ii |

|-----------------------------------------|----|

| Acknowledgements                        |    |

| List of Tables                          | V  |

| List of Figures                         | vi |

| Chapter 1 – Introduction                | 1  |

| 1.1 Overview                            | 1  |

| 1.2 Outline of Contents                 | 2  |

| Chapter 2 – Literature Review           | 4  |

| 2.1 Data Encryption Standard            | 4  |

| 2.2 Differential Power Analysis         | 8  |

| 2.3 Countermeasures to DPA              | 12 |

| Chapter 3 – Experimental Framework      | 22 |

| 3.1 The DES Core and Test Verification  | 22 |

| 3.2 Finding Nodes of Interest.          | 24 |

| Chapter 4 Results and Analysis          | 32 |

| 4.1 Count Results & Simple Analysis     | 33 |

| 4.2 Analysis Using Visual Test & T-test | 36 |

| 4.3 A Decorrelation Circuit             | 41 |

| 4.4 Glitches and Filtering.             | 46 |

| Chapter 5 – Conclusions                 | 51 |

| 5.1 Summary of Results                  | 51 |

| 5.2 Future Work                         | 52 |

| References                              | 53 |

| Appendix A                              | 56 |

| Vita                                    | 81 |

# **List of Tables**

| Table 2.1 | <br>Table Representation of S-Box 1                   | 7  |

|-----------|-------------------------------------------------------|----|

| Table 3.1 | <br>Effective capacitance summery                     | 26 |

| Table 4.1 | <br>Comparison of Count Differences                   | 36 |

| Table 4.2 | <br>XNOR Truth Table                                  | 44 |

| Table 4.3 | <br>Comparison of Results With and Without Filtering. | 48 |

# **List of Figures**

| Figure 2.1 | <br>DES Algorithm, based upon information in [19]                         | 5  |

|------------|---------------------------------------------------------------------------|----|

| Figure 2.2 | <br>DES Round, based upon information in [26]                             | 6  |

| Figure 2.3 | <br>S-Box Substitution, based upon information in [26]                    | 7  |

| Figure 2.4 | <br>Using capacitors as isolation elements, based upon information        | 18 |

|            | in [27]                                                                   |    |

| Figure 2.5 | <br>Power characteristics in Truth Table form for Differential Logic      | 20 |

|            | (left) and Dynamic Logic (right), based upon information in [30]          |    |

| Figure 3.1 | <br>Outline of Chapter 3                                                  | 22 |

| Figure 3.2 | <br>Block Diagram of Spartan II, based upon information in [34]           | 24 |

| Figure 3.3 | <br>Instantiation of two buffer components                                | 28 |

| Figure 3.4 | <br>Flow of C++ Code synth2test.cpp.                                      | 29 |

| Figure 3.5 | <br>Example of If Statement based upon information in New Process         | 30 |

| Figure 4.1 | <br>Outline of Chapter 4                                                  | 32 |

| Figure 4.2 | <br>Excerpt of Count Results File.                                        | 33 |

| Figure 4.3 | <br>Average Count Differences based upon information in Least to          | 34 |

|            | Greatest                                                                  |    |

| Figure 4.4 | <br>Zoomed in Version of Figure 4.3.                                      | 35 |

| Figure 4.5 | <br>Three Cases that Occur in a Visual Test, based upon information       | 37 |

|            | in [13]                                                                   |    |

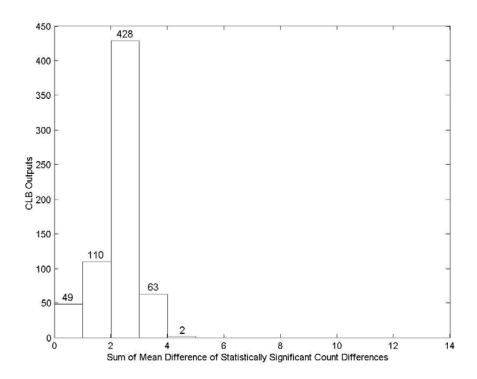

| Figure 4.6 | <br>Histogram of how many CLB outputs are correlated to each bit of       | 39 |

|            | the key                                                                   |    |

| Figure 4.7 | <br>Histogram of CLB outputs with a mean difference of statistically      | 40 |

|            | significant count differences in each range                               |    |

| Figure 4.8 | <br>Sum of mean difference of statistically significant count differences | 40 |

|            | per bit of the key                                                        |    |

| Figure 4.9 | <br>Histogram of the number of bits of the key that have a sum of         | 41 |

|             | mean difference of statistically significant count differences in       |    |

|-------------|-------------------------------------------------------------------------|----|

|             | each of the ranges                                                      |    |

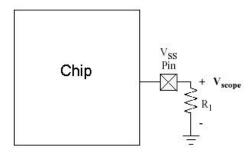

| Figure 4.10 | <br>Resistor Connected between $V_{SS}$ pin and True Ground, based upon | 42 |

|             | information in [21]                                                     |    |

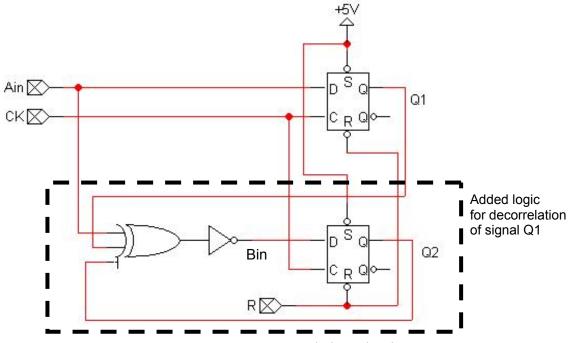

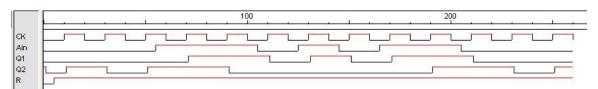

| Figure 4.11 | <br>Decorrelation Circuit.                                              | 43 |

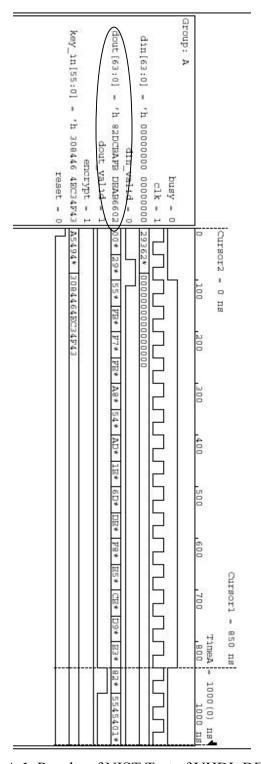

| Figure 4.12 | <br>Output of Test on Decorrelation Circuit.                            | 44 |

| Figure 4.13 | <br>Excerpt showing new VHDL code needed to create Decorrelation        | 45 |

|             | Circuit                                                                 |    |

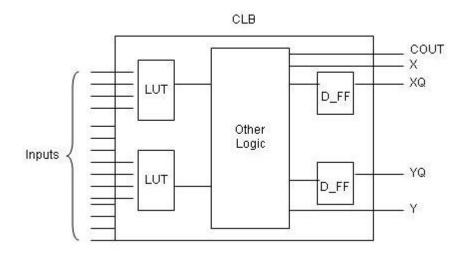

| Figure 4.14 | <br>Basic Xilinx Spartan II CLB Circuitry, based upon information in    | 46 |

|             | [Xil01]                                                                 |    |

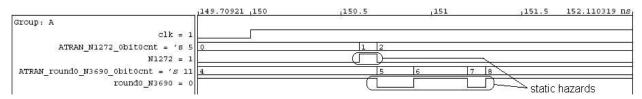

| Figure 4.15 | <br>Plot showing Static Hazards occurring on two CLB outputs            | 46 |

| Figure 4.16 | <br>Plot showing a Dynamic Hazard occurring on a CLB output             | 47 |

| Figure 4.17 | <br>Excerpt Showing Code Used to Filter Glitches                        | 47 |

| Figure 4.18 | <br>Histogram of CLB outputs with a mean difference of statistically    | 49 |

|             | significant count differences in each range after filtering             |    |

| Figure A.1  | <br>Results of NIST Test of VHDL DES Core                               | 56 |

| Figure A.2  | <br>freedes.vhd, VHDL DES Core                                          | 57 |

| Figure A.3  | <br>tb_des.vhd, Test Bench for VHDL DES Core                            | 70 |

| Figure A.4  | <br>C++ Code to Alter the Synthesized VHDL Code                         | 74 |

| Figure A.5  | <br>Excerpts of Matlab code used for visual test and t-test             | 78 |

# **Chapter 1 – Introduction**

#### 1.1 Overview

As devices such as smart cards become more prevalent in our society, the security of the information stored on them must be considered. A smart card is a credit card size device used for a variety of security applications [32]. Typical uses of smart cards include memory devices, cellular telephony, pay TV, computer access control, identification cards, and digital cash or debit cards [27]. Smart cards are an important part of plans by banking and credit companies to replace conventional magnetic strip cards. It is the goal of these companies to reduce overhead by not having a debit card purchase cleared by a central server, but instead to have the purchase cleared by the card itself [32]. Consequently, the ability to keep what is being processed on chips and processors secret is becoming more important. For instance, if an attacker were to determine the secret key of a smartcard used to hold cash, the attacker could then essentially print money. Thus, the encryption scheme used in each device comes under more and more scrutiny.

Most attacks in the past have centered on the mathematics of the algorithm including differential [2] and linear cryptanalysis [18]. It has long been assumed that if the algorithm itself is secure then any implementation of it is also secure. The truth is that a hardware implementation of an encryption scheme is susceptible to several types of attacks where important information is leaked during cryptographic operations. These attacks, typically referred to as side channel attacks [29], include electromagnetic radiation [10], faulty hardware [5, 3], timing attacks [16], simple power analysis [17], and differential power analysis (DPA) [17]. All of the above mentioned side channel attacks work because there is a correlation between what is measured and the internal operations of the device, which relate to the secret key [29]. The focus of this thesis will be on techniques to foil DPA attacks on cryptographic algorithms implemented in hardware. Power attacks are considered the most difficult to control of all the leakage style attacks [20]. Power attacks are not theoretical or limited to certain types of cards. These attacks

have been used to extract keys from about 50 different products in a variety of physical form factors [17].

The focus of this thesis was two fold. The first goal was to develop a tool for investigating power analysis attacks on synthesized VHDL models without the use of transistor level models or schematics. The second was to explore countermeasures that might be used on FPGAs. Specifically, the implementation of a DES core on an FPGA will be the hardware of primary study. The majority of all research in this field has focused on solutions implemented in software and typically only applies to the DES algorithm implemented on a microprocessor. In contrast, this project will explore gatelevel solutions to thwart DPA attacks.

#### 1.2 Outline of Contents

The remainder of this thesis is organized as follows. An introduction to current research involving differential power analysis is presented in Chapter 2. This includes a discussion of the statistical algorithms, the equipment necessary for implementing the attacks, the general steps to performing the attack against the Data Encryption Standard (DES), and how DPA can be used to break other cipher systems including Advanced Encryption System (AES) and RSA. Chapter 2 also reviews previously proposed countermeasures in order to address their effectiveness and vulnerability. Most of these methods are software related as opposed to the purpose of this project, which is to explore hardware solutions.

Chapter 3 gives the details of the software and methodology used to study DPA and possible solutions on FPGAs. It then presents a VHDL DES core that was modified for the purposes of this project, and includes finding the nodes of importance, instrumenting the synthesized file to record the necessary information, and how to adjust the method if a different FPGA architecture is used. Finally, the information retrieved is processed for the purposes of exploring hardware solutions to DPA.

Chapter 4 explores the correlation between switching events on CLB output signals and bits of the key. The count results are first examined by comparing the differences of the count results. The results are then investigated using statistical methods, including the visual test and the t-test. These tests allow the results to be explored in terms of each CLB output and each bit of the key. Then a decorrelation hardware solution is proposed, and its effects on circuit size are discussed. Next, the details of implementing new circuitry into a synthesized VHDL file are explored. The correlated signals are then filtered to remove glitches and the new results recorded and analyzed. These results are compared to the original count results to examine the benefits of designing a glitch free circuit. Finally, other possible solutions to DPA on a FPGA are explored.

Chapter 5 summarizes the thesis and presents a brief discussion on possible research directions which can extend the investigations presented in this work.

# **Chapter 2 – Literature Review**

This chapter provides an overview of the background material related to this project. Section 2.1 gives a brief description of the Data Encryption Standard, particularly exploring the parts that are of interest concerning a differential power analysis (DPA) attack. Then, in Section 2.2, the basic DPA attack on DES is described along with how the attack can be tailored to attack other cryptosystems. Finally, some of the proposed countermeasures to DPA are discussed along with drawbacks and ways of circumventing the countermeasures.

### 2.1 Data Encryption Standard

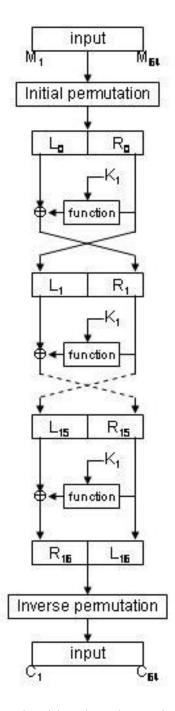

This section will give a brief overview of the parts of the Data Encryption Standard (DES) that apply to the discussion of power attacks that follow. This description is adapted from [9], [19], and [26], where a more detailed explanation can be found. The DES algorithm takes 64 bit blocks of plain text (PT) and combines it with a 56 bit key to produce a 64 bit block of cipher text (CT). The initial key is 64 bits but every eighth bit is only used for parity and is removed before the key is used. The DES algorithm consists of 16 rounds preceded by an initial permutation and followed by a final permutation, which is the inverse of the initial permutation. Figure 2.1 shows the basic steps in the DES algorithm.

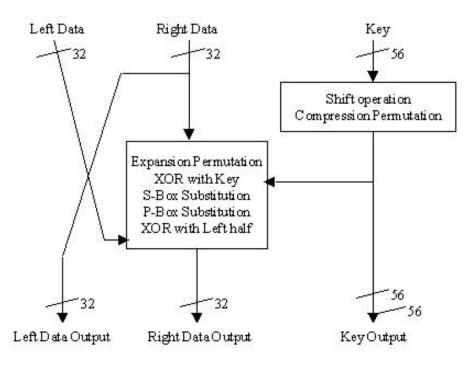

Since the rounds are where the power analysis attacks are focused, they are described in more detail here. Figure 2.2 shows the operations that take place during a round of DES.

Figure 2.1 DES Algorithm, based upon information in [19]

Figure 2.2 DES Round, based upon information in [26]

Prior to starting the first round, the plain text is split into a left and a right side, 32 bits each. The key for the encryption is first split into two 28 bit halves and then the halves are circular shifted by one or two places depending on the round. After being shifted, 48 bits are selected via the compression permutation. The right side of the data being encrypted, R<sub>i-1</sub>, is the left part of the data for the next round, L<sub>i</sub>. The right side also goes through a series of permutations, substitutions, and XORs to create the right side for the next round. The following equations show the operations that take place in a round to create the two halves of the data for the next round.

$$L_{i} = R_{i-1}$$

$$R_{i} = L_{i-1} \otimes f(R_{i-1}, K_{i})$$

(2.1)

The function that is part of the equation for the right side,  $f(R_{i-1}, K_i)$ , consists of the expansion permutation, a XOR with the key for this round,  $K_i$ , S-Box substitutions, and a P-Box Permutation. The expansion permutation expands the 32 bits of the right side by repeating some of the bits. The XOR operation with the key produces a result of 48 bits

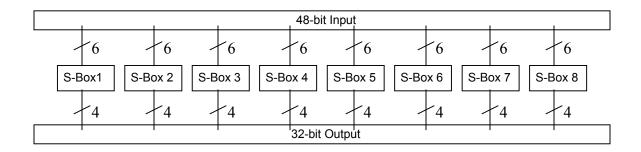

that enter the S-Box substitutions. There are eight S-Boxes and a set of six bits is entered into each S-Box, so the six most significant bits are the input to S-Box 1 and the next six are the input to S-Box 2 and so on. Figure 2.3 shows the operation of all eight S-boxes and table 2.1 shows a table representation of S-box 1.

Figure 2.3 S-Box Substitution, based upon information in [26]

|        | Table 2.1 Table Representation of S-Box 1 |      |      |      |      |      |      |      |      |

|--------|-------------------------------------------|------|------|------|------|------|------|------|------|

|        | Bits 2 through 5                          |      |      |      |      |      |      |      |      |

|        |                                           | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 |

|        | 00                                        | 1110 | 0100 | 1101 | 0001 | 0010 | 1111 | 1011 | 1000 |

|        | 01                                        | 0000 | 1111 | 0111 | 0100 | 1110 | 0010 | 1101 | 0001 |

|        | 10                                        | 0100 | 0001 | 1110 | 1000 | 1101 | 0110 | 0010 | 1011 |

| 9      | 11                                        | 1111 | 1100 | 1000 | 0010 | 0100 | 1001 | 0001 | 0111 |

| 1<br>& |                                           | 1000 | 1001 | 1010 | 1011 | 1100 | 1101 | 1110 | 1111 |

| Bits   | 00                                        | 0011 | 1010 | 0110 | 1100 | 0101 | 1001 | 0000 | 0111 |

| В      | 01                                        | 1010 | 0110 | 1100 | 1011 | 1001 | 0101 | 0011 | 1000 |

|        | 10                                        | 1111 | 1100 | 1001 | 0111 | 0011 | 1010 | 0101 | 0000 |

|        | 11                                        | 0101 | 1011 | 0011 | 1110 | 1010 | 0000 | 0110 | 1101 |

Table 2.1 shows that each S-Box has four numbered rows, 0-3, and 16 columns, 0-15, and produces a four bit output. The most significant and least significant bits of the six inputs are combined to select the row and the middle four select the column. For instance, if the input to a S-Box is 110010 then this would select the value of 1100 on row 2 at column 9. All eight S-Boxes produce four bit outputs to form 32 bits of data. Finally, these 32 bits enter the P-Box Permutation, which jumbles the bits to produce a 32 bit output. This output is then XOR'd with the left hand bits of the previous round to produce the right hand bits for the next round. These same operations are completed for each of the first 15 rounds. The 16<sup>th</sup> round is different from the first 15 in that the two

sides of data are not swapped, as can be seen in Figure 2.1.

### 2.2 Differential Power Analysis

Differential power analysis (DPA) was announced by Kocher et al. in 1999 and has become a hot topic of research. The method stems from timing attacks discussed in [16]. Timing attacks are able to discover information about the algorithm by observing the time each operation takes [16]. DPA attacks belong to a family of attacks that try to discover information about the key by examining the electronic consumption of a device during the execution of a cryptographic computation [11]. Power analysis is considered a passive attack because it is carried out by watching externally the interaction of the chip with a possibly modified reader [27]. Smart cards can also be attacked using active attacks, which are attacks where the chip is extracted, modified, probed, partially destroyed, or used in an unusual environment. Active attacks rely on special knowledge along with requiring the use of costly equipment [27, 12]. Since active attacks leave clear signs of tampering, passive attacks are a much better approach in situations where the attacker does not want anyone to know the card has been attacked [27]. Another reason that the DPA attack is impressive is that the secret key can be discovered without finding out anything about the particular implementation of the algorithm [11]. To perform the entire DPA attack requires skills in statistics and cryptography for the attack, as well as programming skills and experience in instrumentation to build up an automatic measurement system and electronic skills to improve results [1].

Kocher et al. were also the first to discuss Simple Power Analysis (SPA), which is a simpler derivative of DPA. SPA looks at the power trace and with a fine enough resolution the attacker can draw conclusion as to which operations are being carried out [29]. The typical attack on a Data Encryption Standard (DES) implementation on a smart card shows a trace where the 16 rounds of the DES operation can easily be seen.

SPA is used to reveal a sequence of microprocessor instructions and can thus be used to

break cryptographic implementations in which the execution path depends on the data being processed. There are particular operations that occur in cryptographic alogorithms implemented in software that SPA can attack including the DES key schedule, DES permutations, comparisons, multipliers, and exponentiators. In the case of DES operations, conditional branches are usually the cause of significant power consumption differences [17]. An exponentiator that computes binary exponentiation using the square and multiply algorithm provides a good example of the usefulness of SPA. Consider, for the example, if the attacker sees following operation order SMSSMSSSSMSSSSM, where S and M stand for square and multiply operations, respectively. From this information, the attacker could easily determine the key to be 10110010001 [29]. Although the above traces and examples show the effectiveness of SPA, it can easily be defeated in software by avoiding such practices as a branch being dependent of on some part of the secret key. In addition, the power variations of most hardwired implementations of symmetric cryptographic algorithms are small enough that SPA cannot yield any information about the key [17].

DPA builds on the SPA concept by combining power traces with a statistical approach. DPA has roots in timing attacks that were first proposed in [16]. Timing attacks worked because the systems implementing the cryptographic algorithms took differing amounts of time depending on the inputs. Therefore, by studying the amount of time required to perform operation of the secret key, the attackers are able to gleam information that could enable them to break the cryptosystem [16]. The main concept behind DPA is to correlate what is being seen on the power traces back to information about the key. The reason the information can be easily correlated back to key information is that most components today use CMOS gates, where the majority of power is dissipated when the gates switch, commonly referred to as dynamic power [6].

Below is a description of a DPA attack on DES according to [17], [11], and [12]. An attack on DES is being considered since DPA was first demonstrated against DES. In this description, it will be assumed that the attacker knows the plaintext and is varying it. This is commonly referred to as a known plaintext attack. First, the attacker performs

some number of encryption operations, N, varying the plaintext input for each iteration. For each encryption, a power trace is recorded and saved for use later. In order to make the power trace reasonable in size, the power is only recorded for the part of the algorithm that the attacker is interested in. For a known plaintext attack the part to concentrate on is the first round. Each plaintext input will be referred to as  $PT_i$  where i is equal to one to N and each power trace will be labeled  $P_i$  where  $P_{ij}$  is the point on power trace  $P_i$  at time j. Once the attacker has acquired N traces, the average power is calculated. This is done by calculating the average power at each point in time j using the equation below.

$$\overline{P}_{j} = \frac{1}{N} \sum_{i=1}^{N} P_{ij}$$

(2.2)

Knowing the average value at every point in time the average trace can be constructed. The next step is for the attacker to choose a target bit. A typical first choice is the first output bit of the first S-Box of the first round of the DES algorithm. The value of this bit will be referred to as *b*. This bit only depends on six bits of the secret key and bits from the right side of the plaintext which is being varied by the attacker.

The attacker then makes a guess at the value of the six key bits that affect b. In statistical terms this is referred to as forming a hypothesis, called  $H_0$ . Once a guess has been made, then the theoretical value of b can be determined for each of the N iterations. The power traces are then split into two groups. The first group consists of power traces for which the theoretical value of b is zero,  $P^0$ , and the other group consists of traces for which the value is one,  $P^1$ .

The average power trace for the group in  $P^0$  is calculated using the following equation.

$$\overline{P}_{j}^{0} = \frac{1}{N} \sum_{i=0}^{N} P_{ij}^{0}$$

(2.3)

Once that is known, the attacker can statistically compare  $\overline{P}^0$  to  $\overline{P}$  using the t-test to determine whether or not a correlation exists. If the choice of the key is incorrect, the power traces will be uncorrelated and the statistical difference between the two will approach zero. However, if key choice is correct then there will be statistical differences in the traces. If the power traces are uncorrelated, then  $H_0$  is false and a new guess has to be made for the six bits of the secret key and the process starts over. There are only  $2^6$  possible key combinations for bit b.

After the correct set of key bits is found, the attacker can move on to the second S-Box and then continue to move through each of the S-Box until all 48 bits of the sub key are discovered. The final eight bits of the secret key can be found by performing DPA on the next round of the algorithm or simply by brute force. The speed of the attack can be increased by attacking all four output bits of a S-Box at once. Equation 2.4 below gives a value for how many traces are needed for a d bit attack assuming *N* traces are used for the one bit attack.

$$N_d = \frac{(2^{d-1} * N)}{d^2} \tag{2.4}$$

Working through this equation for a four bit attacks shows that it requires half the number of samples as a one bit attack [20]. To perform the attack on the four output bits of the S-Box, a hypothesis is formed about all four bits and the resulting traces are grouped into sixteen categories. A comparison is made between the average of the traces in the group corresponding to the hypothesis and the overall average with a spike occurring in the differential trace when the guess is correct. DPA can be used to attack Triple DES by first finding the outer key and then using it to decrypt the cipher text and then attacking the next key.

The key to using DPA to attack other systems lies in the selection equation. For the DES attack discussed above, the selection function focused on the first output bit of the first S-Box of the first round. For AES, the attack is altered by concentrating the selection

function on the key scheduling part of the algorithm. This is a particularly good place to focus on because the power at this point in the algorithm is only a function of the key and not data [4]. Leaking during asymmetric operations, in cryptosystems such as RSA, tends to be much larger compared to the leakage that occurs in symmetric systems [17]. RSA smart cards are vulnerable to DPA attacks and even SPA can reveal enough characteristics of the RSA decryption to allow the attacker to recover the key [24]. The selection function for DPA can be set up to test exponent bit guesses and determine whether predicted intermediate values are correlated [17]. Also, since most RSA implementations make use of the Chinese Remainder Theorem [24], the selection equation can be centered on the reduction or recombination processes of the theorem [17].

Since some countermeasures attempt to increase noise to make DPA tougher, a short discussion of how noise affects the attack is presented here. During a DPA attack, more noise means that the number of traces needed increases [12]. Noise reduction can play an important role when trying to recover side channel information because signals sizes are so small. Four basic types of noise exist in a DPA attack: external, intrinsic, quantization, and algorithmic. Intrinsic, due to the random movement of charge carriers within conducters, and quantization noise, due to the quantizer in the A/D convertor used to sample the power, are small compared to the size of the side channel signals. External noise can be reduced through careful use of the measuring equipment, good circuit design, and filtering. This type of noise can be thought of as white noise and thus can be removed using a matched filter. Finally, algorithmic noise is reduced through the averaging that takes place during the DPA attack [21].

#### 2.3 Countermeasures to DPA

This section discusses countermeasures that have been proposed in the literature since the announcement of DPA. Most solutions proposed involve changes in software, and to date very few have addressed solutions in hardware. Countermeasures will be discussed

in similar order to when they appeared in literature, with the exception that all software proposals will be discussed first, followed by hardware proposals. A brief description of each will be given along with tradeoffs of that idea or ways attackers can still recover the side channel information.

The ideas of how to counteract DPA were first presented in [17], where the authors roughly describe the characteristics of several categories of countermeasures. The first of these categories includes approaches that attempt to reduce signal sizes. This is typically attempted by using constant execution path code, choosing operations that leak less information to the power trace, balancing Hamming weights, or by physical shielding [17]. The idea of choosing operations that leak less information can be implemented by replacing important assembler instructions by ones whose signature is tougher to analyze, or reengineering important circuitry that carries out the arithmetic operations or memory transfers. One solution that involves the balancing of Hamming weights is to have every piece of data represented by itself and the inverse of itself combined, which requires twice as much storage space. Also, for this to be successful, a register must be cleared prior to each write or information can be leaked [29]. The reduction of signal sizes in any of these ways typically cannot reduce the signal size to zero, and thus the attacker can still discover information to perform DPA given enough traces [17]. For instance, in [21], the authors discuss methods to remove noise to make reduced signal sizes easier to detect. One possible exception is physical shielding, which if used aggressively can make DPA attacks infeasible, but at the expense of both cost and space. Kocher et al. also discussed countering a DPA attack by adding noise into the power trace [17]. Here the main goal is to add enough random noise to make the attack infeasible, but to add minimal overhead [20]. Special implementation techniques for hardware or software are used to reduce the signal to noise ratio (SNR) to a level where the spikes from the DPA analysis are hidden in the noise [12]. The best that can be hoped for with this method is an increase in the number of samples required to accomplish the attack [17].

Random process interrupts (RPI) was one of the first proposed solutions. This idea stems from the fact that power analysis attacks are possible because operations being attacked

occur at a constant place in time [21]. RPIs can be created in two ways, either by introducing randomness into timing, or execution order [29]. Random timing shifts must be introduced so that the computed means can no longer be correlated back to a particular operation [11]. Timing shifts do not provide complete defense since an attacker can use statistical techniques, such as cross correlation, to realign the power traces [29]. The randomization of the execution order seems more likely to provide protection against DPA attacks, but can cause other problems if not done carefully [17]. The basic idea of randomizing execution order is that dummy instructions are randomly placed between actual instructions so that the operation order from one encryption to another differs. This desynchronization effect causes the spikes from the DPA selection function to become smeared across consecutive cycles [8]. It is argued that this type of countermeasure must be done extensively in order to be effective, but a mechanism that would allow for aggressive randomization is not provided [29]. Even with extensive randomization, Clavier et al. have developed an integration process to recover the spike. They propose a sliding window DPA, which involves the integration of the samples over which the spike has become smeared. The first step in the process is to perform a regular DPA attack and develop the differential curve from the selection function. The second step is the integration or the adding of the consecutive power values over the samples the spike was smeared. The authors suggest thinking of this step in terms of a comb where each tooth corresponds to a point on the differential trace. All the values pointed to by the teeth of the comb are added to perform the integration. The number of extra cycles required when randomization of execution order is employed, N'', is given by Equation 2.5.

$$N" = k^2 N \tag{2.5}$$

In the above equation, N is the number samples required to perform DPA on a circuit where randomization is not used and k stands for the number of samples over which the peak is spread. Using the integration technique, this number can be reduced to just k more samples. Another equation for the number of samples needed is 2np, where p is the probability with which RPIs happen and p is number of samples the peak is smeared

across [8]. The more exotic approach of randomizing the order in which the S-Boxes are completed has been proposed, but this again requires extensive randomization which in the case of S-Boxes causes performance penalties [12]. S-Box randomization can also be undone using integration [7]. For the few cases where the algorithm is being implemented on a threaded processor, random threads could be used to execute random encryptions in hopes of masking data. The downside to this approach is that it increases computational cost considerably [29].

This next set of countermeasures all strive to defeat DPA via altering the cryptographic algorithm so the secret key is not used within the main operation. There are three types of these countermeasures: balanced algorithm, information blinding, and information splitting. For an algorithm to be considered balanced it must be designed so that all operations only have a very slight dependence on the input data [29]. Information blinding works on the premise that a new value is created by the combination of the sensitive data with some random value in a reversible way. Examples of this include the XOR of the values or the modular addition [21]. Information splitting consists of splitting values into a number of other states [29]. An interesting implementation that is uses information blinding and splitting to keep the data from the attacker is presented in [11]. There the authors suggest that any intermediate value V that occurs in the process of the algorithm that in some way depends on the input or output should be split in k values in a way that V equals a function of these k values. There are two conditions that must be met in order for this process to mask the value of V. First, knowing one of the k V values does not allow the attacker to determine information about the other values or V itself. Secondly, the function that recombines the k values is such that any value performed on V can be performed on the k values individually.

For the DES algorithm, the authors propose simply creating two V values where the recombination function is the XOR of the two values. This requires the reworking of all operations that are carried out in the algorithm. These include permutation of the bits of V, expansion of the bits of V, XOR of V with some value V' of the same type, XOR between V and a value depending on the key, and transformations of V using the S-

Boxes. For the first two operation mentioned above the same operation that was used on V can know be used on the two V values,  $V_I$  and  $V_2$ . Now for the third operation, both  $V_I$  and  $V_I$  are XORed together along with both part twos and the XOR function can still be used to recombine them. Then for the fourth operation either part one or two of V is XORed with the valued derived from the key. The fifth operation involving the S-Boxes is where things get complicated. It basically consists of creating the new S-Boxes that take in 12 bits and produce 4 instead of the original which takes in 6 and produces 4. This is also joined with a random function A to provide the new equation shown below [11].

$$(V_1, V_2) = S'(V_1, V_2) = (A(V_1, V_2), S(V_1 \otimes V_2) \otimes A(V_1, V_2))$$

(2.6)

This will at least lead to a doubling in the computing resources needed, which is not feasible [29]. Also, the author themselves admit that this method requires too much storage space for the new S-Boxes and A functions. Some alternatives are proposed which attempt to reduce the sized required by only requiring nine new S-boxes [11]. New research has also shown that the DPA attack can be adjusted to handle masking [30]. Information blinding techniques appear to be more successful in systems where exponentiation is part of the algorithm, but at the expense of computational time. Also, the changes must be examined thoroughly to avoid causing other nonintended weaknesses [17]. Since the S-Boxes are the heart of the algorithm and provide the security [31], this could be where potential weaknesses that [17] warned about could be introduced. S-Boxes were specially designed to prevent classic mathematical attacks and changes in them could make the new system susceptible to these older attacks.

Other software countermeasures that have been suggested include using nonlinear key updates where a hashing function is used on the key to attempt to destroy partial information gathered by the attacker, and the use of key counters to keep attackers from gathering a large number of samples [17]. Most software proposals are ad-hoc solutions that are based upon simplistic techniques. The proposals miss the importance of this type of attack and its underlying basis, and can be nullified by signal processing [7].

The threat of DPA stems from the fact that hardware leaks information during processing, so a fundamental countermeasure would be to implement cryptographic algorithms in hardware that either does not leak information or dissipates power in a random manner. Despite this easily specified objective, hardware solutions are typically difficult to design, analyze, and test [21]. Few hardware solutions have been proposed to this point; the ones that have been proposed are discussed below. The hardware countermeasures are grouped into two catogories: one where control on the input power to the chip is implemented and one where the circuitry is changed to avoid the leaking of information.

Several techniques are presented in [27] that are part of the first category. One idea is to control the input power using a sensor that will measure the actual power supplied to the chip and then attempt to equalize it by controlling a current sink [27]. A problem with this method is that the current change happens so rapidly that any compensation technique is likely to lag behind [30]. Another solution along this line is to place a capacitor across power supply lines to smooth the power consumption curve, but physical limitations constrain the size of such a capacitor [27]. Any attempt to make the power consumed by a smart card absolutely uniform by changing the physical design is unsuccessful because sensitive digital oscilloscopes can capture any nonuniformity and then that data can be analyzed to reveal useful information. Also, the attempt to cause every instruction executed to switch the same number of gates is very unnatural and requires twice as much area and total power consumption, along with slowing down the operation of the card. Another method for controlling input power is to use an internal battery to remove the external power pins. This would keep attackers from being able to obtain power traces without tampering with the card. The downside is that batteries small enough to fit onto a chip are expensive and have a short life span. It would not be practical to have easy access to the battery because that would mean that a power trace could easily be obtained and then the usefulness of the approach is circumvented. To avoid having to replace the battery, it has been proposed to use rechargeable batteries. The reader could be used to recharge them, but rechargeable batteries of this size cannot hold a charge for long amounts of time and thus would have to be recharged at the beginning of each use causing an unreasonable charging delay at each use. Also, rechargeable batteries will wear out after relatively few charges and then must be replaced [27].

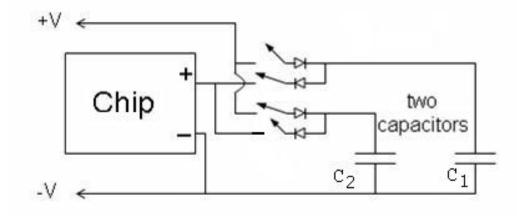

Along the same lines, but without all the issues surrounding the battery on chip is the idea proposed by [27] of decorrelating the power supply from a smart card by using capacitors as power isolation elements. Figure 2.5 shows the configuration of this countermeasure.

**Figure 2.4** Using capacitors as isolation elements, based upon information in [27]

The basic idea is that capacitor one  $(C_1)$  is discharging and powering the chip while the second capacitor  $(C_2)$  is charged by the power supply and then the roles are reversed. The cyclic process that is proposed is to first disconnect  $C_1$  from power supply and then second connect  $C_1$  to chip. Thirdly, disconnect  $C_2$  from chip and fourthly connect  $C_2$  to external power and continue the cycle. This setup means that the power supply is never connected directly to the chip. Thus the supplied current is uniform while the power used by the chip is still irregular. Also diodes are used to avoid any leakage current when both capacitors are connected to the chip. The author recommends using a 1 uF capacitor and also discusses ways the capacitors can be embedded in to the smart chip while claiming only the addition of a few cents to the overall cost of the smart card. Instead of using a time limit or voltage level for when the capacitors should switch it should be triggered by a fixed number of instructions. One issue that still remains is that an attacker can still infer the power consumed by the chip during discharging period, which determines the

initial current at the beginning of the next charging cycle. This information leakage can be reduced in two ways: firstly making the discharging cycle as long as possible and secondly using new circuitry that discharges the capacitor to a fixed value after it is disconnected from the chip so that it always has to be charged the same amount. Capacitors have several advantages to on-chip batteries including being smaller and cheaper than batteries. Also, capacitors can be recharged an unlimited number of times, have no memory effects, and can be recharged in a fraction of second, all qualities that are disadvantages of batteries. Since the capacitor can only hold charge for about 100 instructions to complete, they must be recharged continually to complete long tasks, but this should not have adverse effects on the operation of the chip [27]. Unfortunately, as with batteries, capacitors are still size prohibitive when it comes to placing them on chips [30].

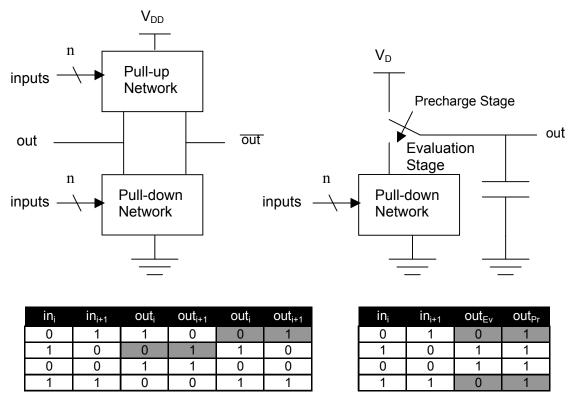

The most recent hardware countermeasure proposed is by [30]. The authors claim that software countermeasures attack the problem at the algorithmic level and power- related countermeasures attack the problem at the architectural level, while the issues related to DPA originate at the logic level. The main idea behind this proposal is that the simplest solution to DPA is to have the encryption module or at least the sensitive parts of it implemented in a logic family that has power consumption independent of the signal transitions. To do this, the proposal is to implement items in a logic family that combines differential and dynamic logic. In differential logic, the attacker can differ between 0-1/1-0 transitions and 0-0/1-1 transitions because power is only consumed during the first two transitions. On the other hand, in dynamic logic, one can differentiate between 0-1/1-1 transitions and 0-0/1-0 transitions since only the first two consume power. In Figure 2.5, a generic form of both of these logic types along with their power characteristics in a truth table form is presented. For this figure, the gray areas represent the transitions that consume power.

Figure 2.5 Power characteristics in Truth Table form for Differntial Logic (left) and Dynamic Logic (right), based on information in [30]

Consequently, neither of these types of logic styles by themselves will resist DPA. The idea of [30] is to combine the two together along with sense amplifier technology so that none of the four transitions can be differentiated from the others. The authors label this as Sense Amplifier Based Logic (SABL).

While it is true that the output transitions will offset each other, the capacitance driven by the outputs must also be matched. According to the authors, this proposal requires about twice as much space and energy than a standard CMOS implementation [30]. Another issue is that since SABL has the precharge element of dynamic logic, certain limitations apply to how many gates can be cascaded together. Cascading has to be done by either inserting an inverter between each gate or by alternating gates with n pull-down networks with gates having p pull-up networks. The use of inverters limits the number of gates that can be cascaded together to the number that can evaluate in one clock period and only noninverting logic can be used [33]. The second alternative eliminates the

disadvantages of the first, but the speed of the circuit will be degraded because of the mobility of holes in the p transistor gates [25]. Finally, the use dynamic circuits requires extra design effort to ensure correct operation under all circuit conditions including timing sequences, charge leakage, and noise sensitivity [33].

# **Chapter 3 – Experimental Framework**

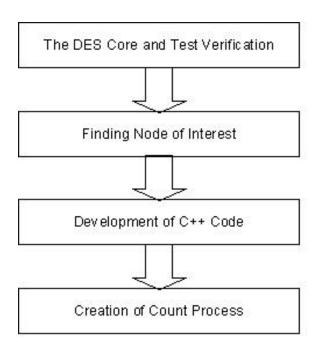

This chapter discusses the DES core that was used for experiments in this project. The coding of the DES algorithm will be examined along with the test procedure to prove the core works correctly. The chapter then explains changes that were made to the core and why they were needed. The chapter concludes with a description of the tool that was created to instrument the synthesized code to count transitions and collect them in a usable format.

Figure 3.1 Outline of Chapter 3

#### 3.1 The DES Core and Test Verification

The DES core that is used throughout this project was developed by [15] and is distributed free of charge. After examining the VHDL code and determining it would work for needs of this project, the next step was to ensure code worked correctly. To ensure correct operation of the algorithm it was tested using a known answer test from

Changes made to the provided DES code were minimal and were only needed to facilitate collection of data. Most changes were made to the test bench in order to ensure proper timing. The VHDL DES code and its test bench after changes are presented in Figures A.2 and A.3, respectively. The changes are marked by comment lines before and after the changes describing why the changes were made. These changes have no effect on the operation of the core, but are needed to control items added later that collect samples while the DES algorithm is being processed.

The code for this core was written so that it could be instantiated in two ways, either with the des\_fast component or with the des\_small component. For the purposes here only the des\_small component was used and thus items pertaining to the des\_fast component were removed prior to synthesizing. Next, the component declarations for des\_small and des\_round are made. The component des\_small involves the input and output ports for the system, while des\_round controls what feeds into and is received from each of the 16 rounds in the DES algorithm. Next inside the package are function declarations for the different parts of the algorithm. These parts include the initial permutation, final permutation, key permutation, compression permutation, expansion permutation, S-Box substitutions, P-Box permutation, and the key shift. For more information on the operation of these items refer to Section 2.1 or [9].

Overall, the des\_small entity controls the input and output of the system, the des\_round entity, and functions that occur outside the rounds. The des\_round entity controls the functions that occur within a DES round when activated by the des\_small entity. Once the code was understood and found to work correctly, the next step was to synthesize the code. Finally, the synthesized VHDL model was simulated with the

original test bench to ensure that it worked correctly.

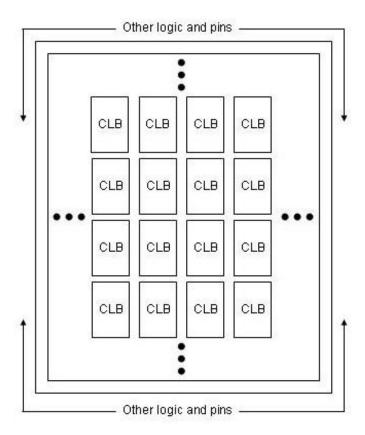

### 3.2 Finding Nodes of Interest

In the case of an FPGA with synthesized DES code being loaded into it, every transition of a signal can possibly leak information through side channels. This section explains how to determine which signals should be examined and how to locate these important signals. The architecture of an FPGA causes the leakage of some signals to be much more prevalent on a power trace. The general architecture of a Xilinx FPGA consists of many blocks of logic or combinational logic blocks (CLB) connected together. Figure 3.2 shows the positioning of CLBs in a Spartan II FPGA with interconnects running between them.

Figure 3.2 Block Diagram of Spartan II, based upon information in [34]

The signals that are the output of CLBs are the signals most likely to leak information at a level that would affect the power trace. As will be explained shortly, the signals internal to the CLB dissipate much less power than the output signals. Thus, since a DPA attack is conducted on the power dissipation of a circuit, these signals can be ignored. To make this argument clear, a discussion of power in CMOS circuits is presented.

The equation for total power of a CMOS circuit is given by [Cha93].

$$P_{total} = p_t (C_L V_{dd} f_{clk} V) + I_{sc} V_{dd} + I_{leakage} V_{dd}$$

$$\tag{3.1}$$

The first term in Equation 3.1 represents the dynamic component of power where  $p_t$  is probability that a power consuming transition occurs,  $C_L$  is the load capacitance, V is the voltage swing,  $V_{dd}$  is the supply voltage, and  $f_{clk}$  is the clock frequency. The term  $p_t$  is also known as the activity factor of the circuit. The second term represents the direct-path short circuit current  $I_{sc}$ , which occurs when both the NMOS and PMOS transistors are active at the same time causing a short circuit from power to ground. The final term represents the power consumed through leakage current,  $I_{leakage}$ , which can arise from substrate injection and subthreshold effects and is primarily determined by fabrication technology considerations. In a well-designed circuit the dominant term is the dynamic power, which is represented by the first term in Equation 3.1 and reproduced below [Cha93].

$$P_d = p_t(C_L V_{dd} f_{clk} V) (3.2)$$

In most CMOS circuits, the voltage swing is equal to  $V_{dd}$ , so the supply voltage is just squared [Cha93]. The two factors that are important to DPA, transitions and capacitance, are found in Equation 3.2. The factors  $p_t$  and  $f_{clk}$  both play a part in the transitions of the circuit. In some texts, [25] and [33] for example, the equation for dynamic power is stated as shown below.

$$P_d = C_L V_{dd}^2 f (3.3)$$

For this equation, f stands for the number of times the gate is switched on and off in a second or the combination of  $p_t$  and  $f_{clk}$ . From Equation 3.3, it can be seen that for any given signal in an FPGA that only f varies widely during execution. For the case of a configured FPGA,  $V_{dd}$  and  $C_L$  are constant for a given node. The  $C_L$  term is the effective capacitance seen by the gate. In the case of a CLB output, this value consists of the capacitance of interconnects it crosses and the gates driven. Since the capacitance of each node is not known, but constant, the power of any signal can be estimated from its transition count [22]. This allows the dynamic power to be estimated without the need of a transistor level model or schematic. If the capacitance of each node were known, then it could be used to weight the equation to better estimate power consumption.

In [28], the authors study the dynamic power consumed by a Xilinx Virtex II FPGA by isolating different resources and finding their effective capacitance. Table 3.1 shows the effective capacitance found by [28] for FPGA components.

| Table 3.1    | Effective capacitance summery |                  |  |  |  |  |

|--------------|-------------------------------|------------------|--|--|--|--|

| Туре         | Resource                      | Capacitance (pF) |  |  |  |  |

|              | Ixbar                         | 9.44             |  |  |  |  |

| Interconnect | Oxbar                         | 5.12             |  |  |  |  |

| per CLB      | Double                        | 13.20            |  |  |  |  |

|              | Hex                           | 18.40            |  |  |  |  |

|              | Long                          | 26.10            |  |  |  |  |

| Logic        | LUT inputs                    | 26.40            |  |  |  |  |

| per CLB      | FF inputs                     | 2.88             |  |  |  |  |

|              | Carry                         | 2.68             |  |  |  |  |

| Clocking     | Global wiring                 | 300              |  |  |  |  |

|              | Local                         | 0.72             |  |  |  |  |

The results in Table 3.1 show that, other than global wiring for clocking, the resources with the largest effective capacitance are inputs to LUTs. The components with the second highest effective capacitance are interconnects. There are several types of interconnects in an FPGA, but all have a high effective capacitance [28]. Although the capacitance values were found for a Xilinx Virtex II FPGA, it is assumed that the relative

ordering of component capacitances is the same for the Spartan II architecture used here, since both have very similar CLBs and interconnect components.

To verify this statement, the Standard Delay Format (SDF) file for the synthesized code of the DES core was examined. The SDF file is part of the IEEE VITAL simulation process. This file is created by the place and route tool and represents the back annotated delay of each component. For each input to a gate in the circuit, an input and output delay is given. The input delay represents the delay seen by a signal driving that input due to capacitance along that wire. The ouput delay models the internal delay of the component. In examining the SDF file for the synthesized DES core, the input delay to a X BUF component representing X or Y output was not specified, meaning that the default value of 0 ns was used. The inputs to flip-flops driven by internal CLB circuitry have a delay of 0.496 ns. Finally, the delay of LUT components was typically in the range of 1.5 to 3 ns, with some values over 4 ns. These findings show a correspondence between the effective capacitance found for the Virtex II family and the Spartan II device used here. Thus, since LUTs are driven by either input ports or outputs of CLBs, these results show that CLB outputs drive much larger capacitive loads then any of the signals internal to the CLB. Consequently, the switching of CLB outputs will have a much larger impact on the power trace found during processing. Thus, the internal signals are assumed to be negligible for this discussion and the focus will be on the CLB outputs.

Given the argument that the outputs of CLBs are the most heavily loaded signals, the correlation between power consumption and bits of the key can be estimated by finding the correlation between transitions on CLB outputs and bits of the key. To do this, the synthesized VHDL code was instrumented to find this correlation. The first step was to determine how the outputs of CLBs are labeled in the synthesized file. Since each FPGA family uses different naming conventions, this step must be done anytime the target FPGA family is changed. One way of determining the naming conventions for a particular family is to open the FPGA map generated by the Xilinx synthesis tool and examine it using FPGA editor, which is part of the Xilinx ISE. The map file displays how the tool placed the synthesized code onto the FPGA. Once in the editor, the outputs

of multiple CLBs can be explored to find the signal names. These signal names can then be searched for in the synthesized VHDL code to determine which component produced them. For instance, some signals will be the output of flip-flops, which are the X\_FF components in the Xilinx Spartan II family. Knowing the components from which CLB outputs are produced is the first step, but these components can possibly be used for other signals in the FPGA and must be inspected. If they are used for signals other than CLB outputs then observing the name given to the components can usually differentiate the outputs of CLBs from other signals. To make this discussion clear, Figure 3.3 shows the declaration of two buffer components.

**Figure 3.3** Instantiation of two buffer components

In Figure 3.3, the first buffer serves as an output of a CLB for the Spartan II FPGA family. The second, however, is not an output of a CLB. The buffer component is used with signals other than CLB outputs but its name signifies it as a CLB output. The component name is the alphanumeric characters given before the colon. In this family, a component name that ends in XUSED is the X output of a CLB. The architecture of a CLB will be discussed further in Chapter 4. See Figure 4.14 for a diagram of a Xilinx Spartan II CLB.

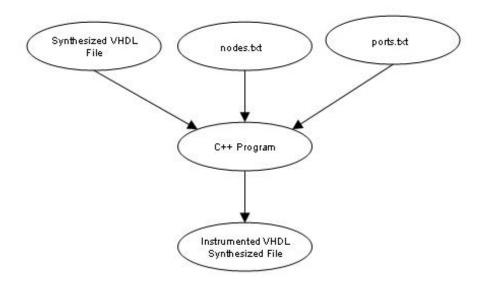

Once the names of CLB output components are known, the next step is to collect all the signals that are outputs of these components. The C++ code that was used to find the nodes of importance along with other operations is listed in Figure A.4.

**Figure 3.4** Flow of C++ Code synth2test.cpp

The flow of this C++ code is shown in Figure 3.4. The code has three inputs: the synthesized VHDL file, a file named nodes.txt, and a file named port.txt. The code reads the file nodes.txt to determine the component types that are important. This file makes the code adaptable for different families of FPGAs. The C++ code reads in a line of the synthesized code and compares it to all the lines of the nodes.txt file. When a match is found the output of that component is saved as an important signal for use later. When other FPGAs are used, the only thing that needs to be altered is contents of the file nodes.txt. If this code was run consistently on different families then the code could be altered to request the user to enter the family being used and use that response to choose the file that matches the family used. The ports.txt file is used to signify which port that the code needs to use when setting up the count process. This port is always set to key in here, but for another version of DES VHDL code it might need to be changed if the key input port has a different name. For this VHDL DES core, there are 889 CLB outputs found when it is synthesized to a Spartan II FPGA. Finally, the C++ code produces the instrumented VHDL synthesized file, which is discussed further in Section 3.3.

As discussed above, the transitions of the CLB output signals are important in finding a

correlation between the hardware and the key. To monitor these transitions, a new process is created in the synthesized VHDL file. For each CLB output, two transition counts are maintained for each bit of the key, one for when the bit is a zero and one for when the bit is a one. With a 56 bit key, this creates 112 signals from one CLB output. Finally, a total count signal is created to keep track of all transitions that occur to the CLB output. Thus, 113 signals must be created for each CLB output.

The C++ code discussed above and presented in Figure A.4 of Appendix A instruments the synthesized VHDL to create this process. After the first cycle through the file to find the important signals, the next step was to cycle through the file a second time to add the counting process to the VHDL file. As mentioned, for every important signal, 113 count signals must be declared; this is the first step of the second cycle. Once the end of the file is reached for the second time, the new process is created. Inside the process there is an "if" statement used to increment each count signal. Figure 3.5 gives an example of one of these "if" statements.

```

if (round0_N1718'event and key_in(55) = '0') then

ATRAN_round0_N1718_55bit0cnt <= ATRAN_round0_N1718_55bit0cnt + 1;

end if;

if (round0_N1718'event and key_in(55) = '1') then

ATRAN_round0_N1718_55bit1cnt <= ATRAN_round0_N1718_55bit1cnt + 1;

end if;</pre>

```

Figure 3.5 Example of If Statement from New Process

The "if" clause is triggered by a transition on the CLB output and the bit of the key that corresponds to the count signal. In this case, the CLB output is round0\_N1718 and the bit of the key that is of importance is 55. The naming convention used for these new signals can also observed in Figure 3.5. A generic form of this naming convention is ATRAN\_<br/>

original signal name>\_<br/>

bit #>bit<br/>

bit value>cnt. ATRAN is used at the beginning to easily differentiate these signals from the others. As far as the suffix, <br/>

bit #> represents the bit of the key that is observed by this count signal and <br/>

bit value>

signifies whether signal is looking for the bit of the key to be a one or zero. The "if" statement in Figure 3.5 increments the count signal when an event occurs on the original signal and the 55<sup>th</sup> bit of the key is a zero. The second "if" statement is the same except it triggers when the 55<sup>th</sup> bit is a one. These are just two of the "if" statements of the 113 that correspond to the CLB output signal.

With 889 CLB outputs that must be observed and 113 signals created for each, this means that over one hundred thousand signals are created for this new process. Trying to read all the count values from a trace window is unrealistic so the VHDL code was also modified to write to a file using the TEXTIO package of VHDL. This allows a file to be opened, written to each time the process is triggered, and closed at the end of the process. Writing to the file required the addition of several changes to the test bench, as was mentioned earlier. The changes allowed the encryption entity to write to the file while keeping the decryption entity from writing. Each time the process is triggered, the file is overwritten so that at the end of simulation, the file only contains the final counts of each signal. In order to perform the write operations above, a couple of new lines are needed for each new signal so that every time the process is triggered the new count value is written to the output file. Once the final outputs are written to the text file, the counts can be analyzed using a mathematical software package such as Matlab.

As the need occurred, the C++ code was altered to create other output files. For instance, it was used to create a file containing the count signal names in the order in which they were created. Also, since the statistical tests described in Chapter 4 require the variance of each count signal, the C++ was altered to create a VHDL process that would record a count signal value after each encryption. In this process, each count signal counts transitions from the time din\_valid becomes high until dout\_valid becomes high. At the dout\_valid signal, the value of each count signal is written to the file and then cleared. This file was then used to find the variance of each count signal.

## **Chapter 4 Results and Analysis**

This chapter presents the analysis of the transition count results recorded by the modified VHDL file described in chapter 3. Figure 4.1 shows the outline of this chapter. As mentioned, the modified VHDL file writes all results to a text file. These results are examined by comparing the differences in counts. This chapter also describes how these results can be analyzed statistically using the visual test or the t-test. After the signals have been fully analyzed, ways of decorrelating the nodes from the secret key are explored. This includes the specification and development of a decorrelation circuit for outputs of flip-flops. The effects that glitches have on the results are then examined. Finally, design changes that could lead to decorrelation of signals or could make decorrelation hardware simpler are discussed.

Figure 4.1 Outline of Chapter 4

### 4.1 Count Results & Simple Analysis

Chapter 3 discussed how the output file is created from the VHDL code. Figure 4.2 is an excerpt of the count results file after 1000 encryptions. The order of the results corresponds to the order they were created by the C++ code used to edit the synthesized VHDL code, which allows the count value to be matched with its signal name.

| Current Outputs |                              |

|-----------------|------------------------------|

| 20795           | ←ATRAN_round0_N3690_0bit0cnt |

| 20438           | ←ATRAN_round0_N3690_0bit1cnt |

| 20885           | ←ATRAN_round0_N3690_1bit0cnt |

| 20348           |                              |

| 20952           |                              |

| 20281           |                              |

| 20802           |                              |

| 20431           |                              |

| 20802           |                              |

| 20431           |                              |

| 20791           |                              |

| 20442           |                              |

Figure 4.2 Excerpt of Count Results File

In Figure 4.2, the numbers represent the total transitions recorded by each count signal. As can be seen in Figure 4.2, the first value is the count value for the 'ATRAN\_round0\_N3690\_0bit0cnt' signal in the generic form ATRAN\_<original signal name>\_<key bit #>bit<key bit value>cnt. This means the signal 'round0\_N3690' transitioned 20795 times during encryptions when the zeroth bit of the key was zero. The next number represents the transitions seen by the 'ATRAN\_round0\_N3690\_0bit1cnt' signal and so on.

These values are then loaded into Matlab for analysis. Having the 113 count signals per CLB output signal in the VHDL code allows each of the outputs to be analyzed in terms of each bit of the key. The first step is to determine how large the average difference over 1000 encryptions is between the <br/>bit #>bit0cnt and <br/>bit #>bit1cnt signals where the bit number is the same for each. The larger the difference in these values the greater the

chance that they will be found to be statistically different in the statistical testing, which will be described in Section 4.2.

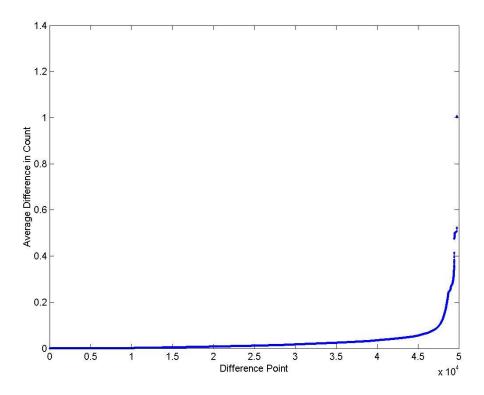

Figure 4.3 is a sorted plot showing the average count difference between <br/>bit #>bit0cnt and <br/>bit #>bit1cnt for every count signal over 1000 encryptions. Figure 4.3 shows only 49,784 difference values instead of the original 100,457 signals. This is because there is only one point on the plot for every difference between the two versions of the signal representing the same bit of the key. Thus, having 889 CLB outputs brings the number of necessary points to 49,784.

Figure 4.3 Average Count Differences from Least to Greatest

As can be seen in Figure 4.3, the majority of the values are relatively small. It is not until the points are well past 30,000 that the values begin increasing quickly. Figure 4.4 is the same graph zoomed in to show points starting at 48,000. This plot shows the points having the largest average count differences with much more detail.

**Figure 4.4** Zoomed in Version of Figure 4.3

Figure 4.4 shows that most of the differences fall well below a value of 0.2. The first difference value to exceed 0.1 is at point 47,605. The average count differences in group A are more than twice as large as those in B. Group A contains 48 points while group B contains 288 points. Figures 4.3 and 4.4 show that only a few points have a large average difference in transitions between when the bit of the key is a 1 and a 0. Thus, only a small fraction of the circuit will have to be modified to reduce the correlation between power consumption and bits of the key.

To reinforce this point, consider the following data. The sum of differences over all the count signals is 1,394,600 with an average count difference of 28.0128 over 1000 encryptions. Group A accounts for 3.46% of the differences, while group B accounts for 10.35%. Table 4.1 shows a comparison of how much of the total count difference can be removed by decorrelating a certain percentage of the total difference values.

| Table 4.1 Comparison of Count Differences |                                              |          |  |  |  |

|-------------------------------------------|----------------------------------------------|----------|--|--|--|

| # Difference Values                       | % of Total Diff Values % of Total Count Diff |          |  |  |  |

| 4046                                      | 8.1271%                                      | 50.4747% |  |  |  |

| 12269                                     | 24.6445%                                     | 75.0200% |  |  |  |

| 22383                                     | 44.9602%                                     | 90.2500% |  |  |  |

This table shows that relatively few difference values can account for a large percentage of the total count differences. For instance, just 4046 difference values of the 49,784 total values account for over 50% of the total count differences. The values required to account for 75% and 90% percent of the total count differences are also presented.

### 4.2 Analysis Using Visual Test & T-test

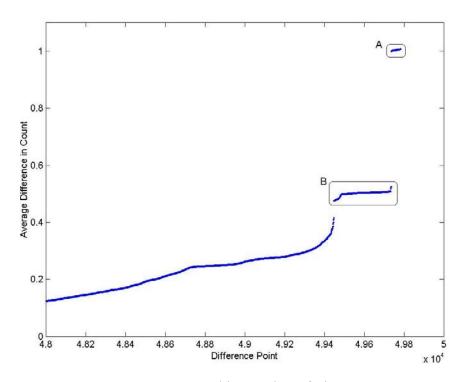

While finding nodes whose count difference is large is instructive, it is also necessary to ensure the difference in counts between the <bit #>bit0cnt and <bit #>bit1cnt signals are statistically significant. To do this, statistical hypothesis testing is employed. A hypothesis is typically tested with either the visual test or the t-test [13]. Before proceeding to the analysis of the results, both of these statistical testing methods are briefly described here based on descriptions in [13].

The t-test is used to determine whether two unpaired samples of data are significantly different. It involves about seven calculations, which are described in [13], to make the decision. In [1], the authors found that simply finding the mean difference between two samples is sufficient for determining whether two samples are significantly different. Despite this, all data for this project was statistically compared. The visual test is a simpler alternative to the t-test. For the visual test, the confidence interval of each sample is computed separately and can be found with the following equation [13].

confidence interval =

$$\bar{x} \pm (t - value) \sqrt{\left(\frac{var}{n}\right)}$$

(4.1)

In the equation above,  $\bar{x}$  is the mean of the sample, var is the sample variance, and n is the number of elements in the sample. The t-value is found from a t-value table using the

percentage of confidence desired and the degrees of freedom. A confidence interval is computed for both of the samples and then both are compared to produce one of the three following cases:

- Case 1. The confidence intervals do not overlap and thus the samples are significantly different.

- Case 2. The confidence intervals overlap to the point that the mean of one sample is within the interval of the other sample and thus the samples are not significantly different.

- Case 3. The confidence intervals only slightly overlap and neither sample's mean falls within the other's interval. In this case, no visual conclusion can be drawn and the t-test is needed for determining if the difference in the samples is significant.

Figure 4.5 shows the visual representation of each of the three cases that occur in a visual test where the dot is the sample mean and the line represents the confidence interval.

Figure 4.5 Three Cases that Occur in a Visual Test, based upon information in [13]

For the most part, the visual test was used here for the first test because it requires fewer calculations than the t-test. The t-test was employed to handle situations where the third case of the visual test occurred. For all statistical testing below, a confidence factor of 99.5% was used. Given this background on the statistical testing techniques, the next step is to use them to analyze the count results.

To perform the visual test, the average, variance, and confidence intervals were calculated in Matlab using the output file of the instrumented VHDL code. Excerpts of

the Matlab code used are presented in Figure A.5 of Appendix A. Once the confidence interval was known for each count signal, the next step was to determine how many of the count comparisons fell into Case 1 or Case 3 of the visual test. It was found that 1267 of the 47,605 differences, about 2.5%, could be grouped into Case 1, meaning that the count signal ending in <key bit #>bit0cnt was definitely statistically different from the one ending in <key bit #>bit1cnt. 3340 more of the differences, or about 6.7%, fell into Case 3, meaning that they had to be evaluated using the t-test to determine whether the two signals were truly significantly different. This means that 42,998 differences (over 90%) were statistically insignificant. So if all the differences in Case 3 were found to differ significantly, less than 10% would be statistically different.

The t-test was employed to determine which of the count differences that fell into Case 3 were actually statistically different. The t-test showed that 3022 of the 3340 count differences originally in Case 3 were statistically different. These, along with those in Case 1 of the visual test, bring the total number of statistically significant count differences to 4289, about 8.6% of the total count differences. The 1267 differences in Case 1 are spread over 536 CLB outputs and the 3022 differences found with the t-test are spread over the same outputs plus 116 more. Consequently, 652 CLB outputs are correlated to bits of the key.

Next, the count results of these 652 CLB outputs will be investigated in several ways to better understand their correlation to the key. It is important to note that the figures presented in the rest of this section examine just the statistically significant count signals and in terms of each of the 652 CLB outputs or bits of the key, while earlier Figures 4.3 and 4.4 showed all count signals individually.

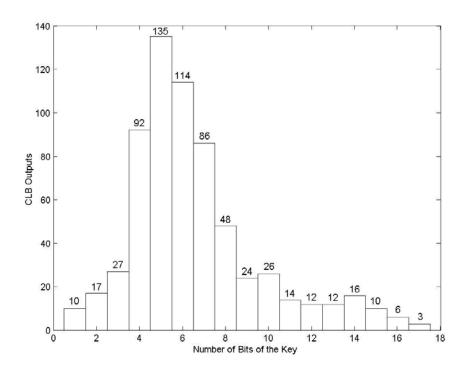

Figure 4.6 Histogram of how many CLB outputs are correlated to each bit of the key

Figure 4.6 presents a histogram showing the number of CLB outputs that are correlated to the different number of bits. From Figure 4.6 it can be seen that only a small portion of the CLB outputs are correlated to more than ten bits of the key. Decorrelating less than 9.34% of the CLB outputs will remove over 25% of the correlations. Futhermore, over 50% of the correlations can be removed by decorrelating 24.3% of the CLB outputs.