# A SECURE ADAPTIVE NETWORK PROCESSOR

# Scott J. Harper

Dissertation submitted to the faculty of Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

Doctor of Philosophy In Electrical Engineering

Dr. Peter M. Athanas, Chair Dr. Nathaniel J. Davis Dr. Mark T. Jones Dr. Scott F. Midkiff Dr. Srinidhi Varadarajan

April 30<sup>th</sup>, 2003 Bradley Department of Electrical and Computer Engineering Blacksburg, Virginia

Keywords: Secure Hardware, Network Processing, Reconfiguration

Copyright 2003 by Scott J. Harper ALL RIGHTS RESERVED

### A SECURE ADAPTIVE NETWORK PROCESSOR

# Scott J. Harper

(ABSTRACT)

Network processors are becoming a predominant feature in the field of network hardware. As new network protocols emerge and data speeds increase, contemporary general-purpose network processors are entering their second generation and academic research is being actively conducted into new techniques for the design and implementation of these systems. At the same time, systems ranging from secured military communications equipment to consumer devices are being updated to provide network connectivity. Many of these devices require, or would benefit from, the inclusion of device security in addition to data security. Whether it is a top-secret encryption scheme that must be concealed or a personal device that needs protection against unauthorized use, security of the device itself is becoming an important factor in system design. Unfortunately, current network processor solutions were not developed with device security in mind. A secure adaptive network processor can provide the means to fill this gap while continuing to provide full support for emerging communication protocols. This dissertation describes the concept and structure of one such device. Analysis of the hardware security provided by the proposed device is provided to highlight strengths and weaknesses, while a prototype system is developed to allow it to be embedded into practical applications for investigation. Two such applications are developed, using the device to provide support for both a secure network edge device and a user-adaptable network gateway. Results of these experiments indicate that the proposed device is useful both as a hardware security measure and as a basis for user adaptation of information-handling systems.

# **ACKNOWLEDGEMENTS**

Many thanks go to the Virginia Tech Bradley Department of Electrical and Computer Engineering and its faculty, staff, and students that have made my time spent here both rewarding and enjoyable. I would like to thank all of the members of the Configurable Computing Lab for always keeping things interesting, particularly those with whom I have worked in the past and those who have contributed to the effort of the Secure Communications Group. May all of our work find a host of useful applications.

This work was funded in part by the United States Office of Naval Research (ONR) under grant #N00014-00-1-0549 – the NAVCIITI effort. I would like to thank the ONR for their continued support of cutting-edge research.

# **CONTENTS**

| Acknowledgements                                                                                                                                      | iii      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Contents                                                                                                                                              | iv       |

| List of Figures                                                                                                                                       | viii     |

| List of Tables                                                                                                                                        | X        |

| Chapter 1 : The Introduction                                                                                                                          | 1        |

| 1.1 Scope                                                                                                                                             | 1        |

| 1.2 Problem Overview                                                                                                                                  | 2        |

| 1.3 Solution Synopsis                                                                                                                                 | 4        |

| 1.4 Contributions and Claims                                                                                                                          |          |

| 1.5 Dissertation Outline                                                                                                                              | 6        |

| Chapter 2 : The Background                                                                                                                            |          |

| 2.1 Network Processing                                                                                                                                |          |

| 2.2 Embedded Device Security                                                                                                                          |          |

| 2.3 Current State of the Art for Network Processing                                                                                                   | 11       |

| 2.3.1 GENERAL-PURPOSE COMMERCIAL NETWORK PROCESSING CHIPS                                                                                             | 12       |

| 2.3.1.1 INTEL: Level One IXP Family                                                                                                                   |          |

| 2.3.1.2 IBM: PowerNP Family                                                                                                                           |          |

| 2.3.1.3 Motorola: C-Port Digital Communications Processors                                                                                            | 13<br>11 |

| 2.3.1.5 PMC-Sierra: RM9000                                                                                                                            | 14<br>15 |

| 2.3.1.6 Chameleon: CS2112 Reconfigurable Communications Processor                                                                                     |          |

| 2.3.2 Fixed-function Commercial Network Processing Devices                                                                                            |          |

| 2.3.2.1 Lucent / Agere: APP1200 Pattern Processor and APP1400 Routing Switch Processor to APP750NP Classification Engine and APP750TM Traffic Manager |          |

| 2.3.2.2 IDT (Solidum): PAX.core                                 | 16 |

|-----------------------------------------------------------------|----|

| 2.3.3 NETWORK PROCESSING RESEARCH IN ACADEMIA                   |    |

| 2.3.3.1 USC/ISI GRIP Gigabit Rate IPsec Card                    |    |

| 2.3.3.2 Washington University Field Programmable Port Extender. |    |

| 2.3.3.3 UCLA Layer Seven Network Processor Accelerator          |    |

| 2.3.3.4 University of Edinburgh MIR Mixed-version IP Router     | 20 |

| 2.4 Background Summary                                          | 20 |

| Chapter 3 : The Concept                                         | 22 |

| 3.1 Processor Overview                                          | 22 |

| 3.2 Processor Structure                                         | 25 |

| 3.2.1 User Discovery System                                     | 26 |

| 3.2.2 USER AUTHENTICATION INTERFACE                             |    |

| 3.2.3 CONFIGURATION INTERFACE                                   | 29 |

| 3.2.3.1 Key Management                                          | 29 |

| 3.2.3.2 Token Contents                                          | 32 |

| 3.2.3.3 Configuration Interface Security Analysis               |    |

| 3.2.4 Data Processing System                                    | 35 |

| 3.3 Concept Summary                                             | 37 |

| Chapter 4 : The Structure  4.1 System Overview                  |    |

| 4.2 Configuration Management                                    |    |

| 4.2.1 Authorization                                             | 40 |

| 4.2.2 STREAM MANAGEMENT                                         |    |

| 4.2.3 Configuration Stream Requests                             |    |

| 4.2.4 User-based Reconfiguration                                |    |

| 4.3 Structure Summary                                           | 46 |

|                                                                 |    |

| Chapter 5 : The Experiments                                     | 47 |

| 5.1 Foundation Platform                                         | 47 |

| 5.1.1 RECONFIGURABLE BASE                                       | 48 |

| 5.1.2 PLATFORM RECONFIGURATION                                  | 51 |

| 5.1.3 FOUNDATION PLATFORM ANALYSIS                              | 53 |

| 5.2 Secured DSN Receiver                                        |    |

|                                                                 | 53 |

| 5.2.1 DSN Receiver Operational Details                          |    |

|                                                                 | 55 |

| 5.2.4 DSN RECEIVER SYSTEM ANALYSIS                             | 61  |

|----------------------------------------------------------------|-----|

| 5.3 Secured Network Gateway                                    | 62  |

| 5.3.1 Network Gateway Structure                                |     |

| 5.3.2 Secure Network Gateway Analysis                          |     |

| 5.4 Summary of Experiments                                     | 65  |

| or summary or experiments                                      |     |

| Chapter 6 : The Results and Analysis                           | 67  |

| 6.1 Security Analysis                                          | 68  |

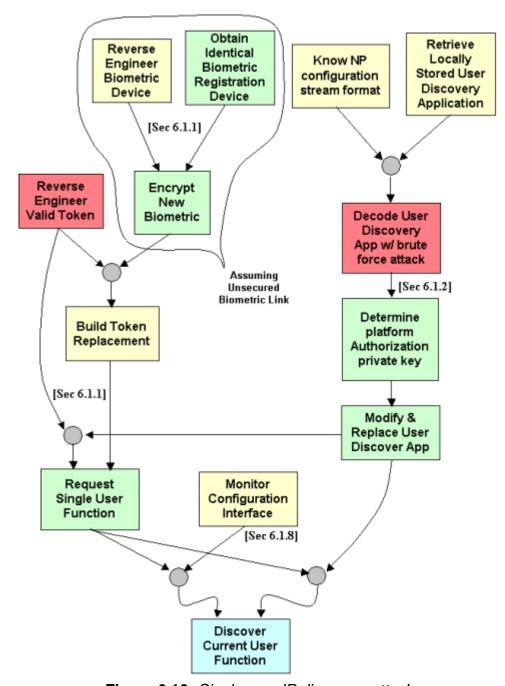

| 6.1.1 AUTHORIZATION REPLACEMENT ATTACK                         | 70  |

| 6.1.2 AUTHORIZATION PLATFORM REPLACEMENT ATTACK                |     |

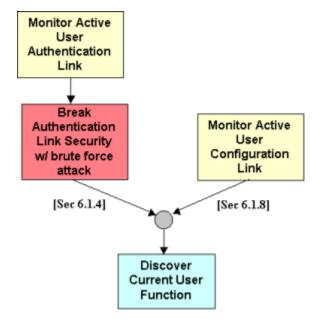

| 6.1.3 AUTHORIZATION MAN-IN-THE-MIDDLE ATTACK                   |     |

| 6.1.4 AUTHORIZATION INTERFACE SNOOPING ATTACK                  |     |

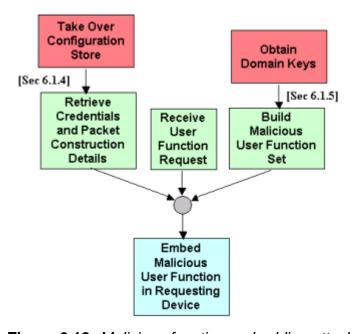

| 6.1.5 CONFIGURATION STORE REPLACEMENT ATTACK                   |     |

| 6.1.6 CONFIGURATION PLATFORM REPLACEMENT ATTACK                | 78  |

| 6.1.7 CONFIGURATION MAN-IN-THE-MIDDLE ATTACK                   |     |

| 6.1.8 CONFIGURATION INTERFACE SNOOPING ATTACK                  | 81  |

| 6.1.9 OTHER ATTACKS                                            |     |

| 6.1.10 ATTACK ANALYSIS SUMMARY                                 |     |

| 6.2 Objectives Reexamined and Device Comparison                | 84  |

| 6.2.1 Interfaces must be secured                               | 86  |

| 6.2.2 HARDWARE DETAILS MUST BE UNOBSERVABLE                    |     |

| 6.2.3 DEVICE MUST CONTAIN NO IP UNLESS A VALID USER IS PRESENT |     |

| 6.2.4 OBJECTIVE SUMMARY AND COMPARISONS                        |     |

| 6.3 Contributions                                              | 93  |

| 6.4 Future Directions                                          | 95  |

| 6.4.1 FULL IMPLEMENTATION OF SECURITY SCHEME                   |     |

| 6.4.2 Configuration Store and Tokens                           |     |

| 6.4.3 Single-device Packaging                                  |     |

| 6.4.4 Cores for General Implementation                         |     |

| 6.4.5 APPLICATIONS                                             |     |

|                                                                |     |

| Bibliography                                                   |     |

| Glossary                                                       | 104 |

| Appendix A : SLAAC1-V XVPI Programmer                          | 108 |

| Appendix B: Wired Network Data Classifier                      |     |

| Appendix C: Wireless Data Packetization                        |     |

| Appendix D : Radio Data Output Arbiter                         |     |

| ADDENUIS D. NAUR DAIA VIIIDUL ALDIKL                           |     |

| Appendix E: Radio Packet Classifier | 130 |

|-------------------------------------|-----|

|                                     |     |

|                                     |     |

| Vita                                | 136 |

# LIST OF FIGURES

| Figure 2.1: USC/ISI GRIP Gigabit Rate IPsec Card                   | 18 |

|--------------------------------------------------------------------|----|

| Figure 2.2: Washington University FPX                              | 19 |

| Figure 3.1: User discovery system                                  | 26 |

| Figure 3.2: User discovery states                                  | 27 |

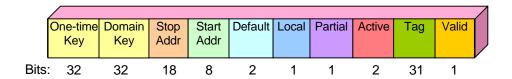

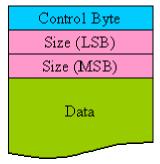

| Figure 3.3: Configuration data security header                     | 30 |

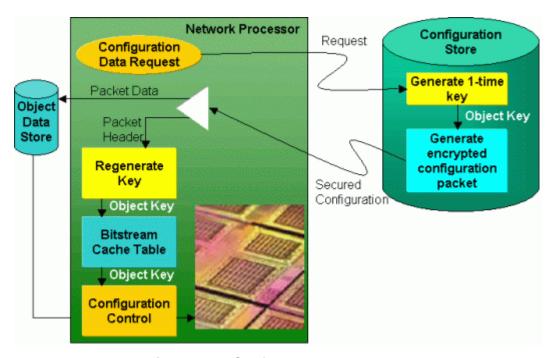

| Figure 3.4: Network processor configuration data reception         | 31 |

| Figure 3.5: Token data content                                     | 33 |

| Figure 3.6: Data processing system (user function)                 | 36 |

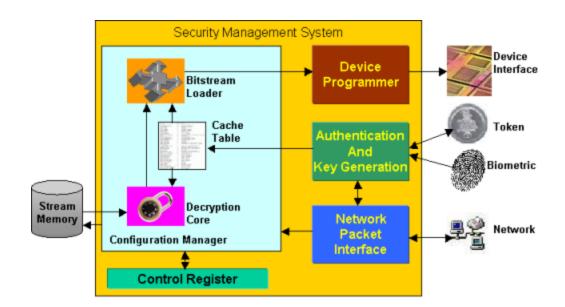

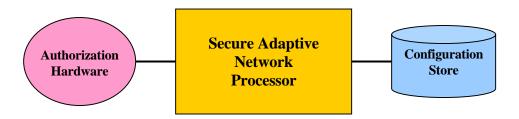

| Figure 4.1: Basic system block diagram                             | 39 |

| Figure 4.2: 128-bit cache table entry for configuration management | 41 |

| Figure 4.3: Conversion from user discovery to user function mode   | 42 |

| Figure 4.4: Configuration management                               | 43 |

| Figure 4.5: Configuration key handling                             | 44 |

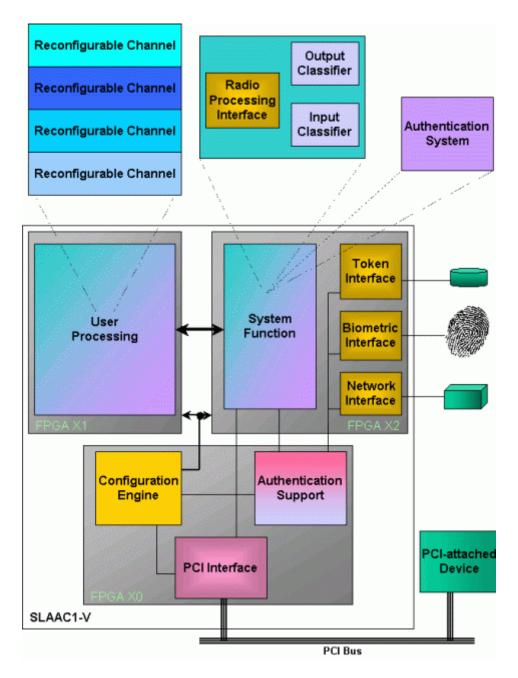

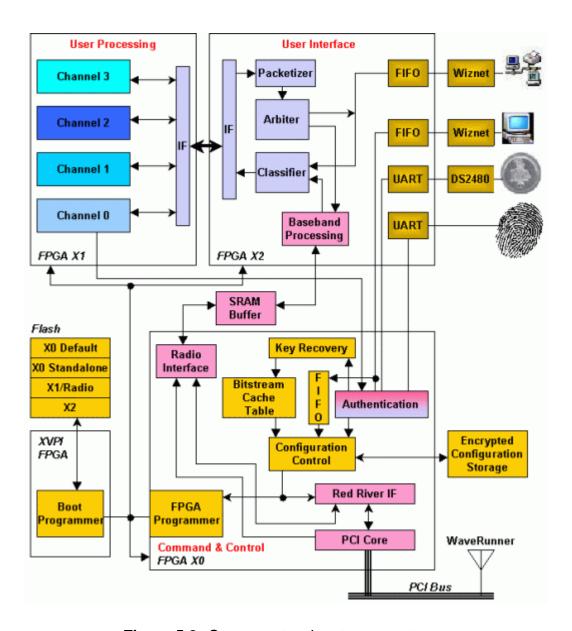

| Figure 5.1: SLAAC1-V block diagram                                 | 49 |

| Figure 5.2: Network processor embedding                            | 50 |

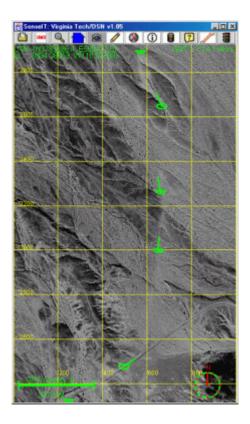

| Figure 5.3: SensIT DSN user interface                              | 54 |

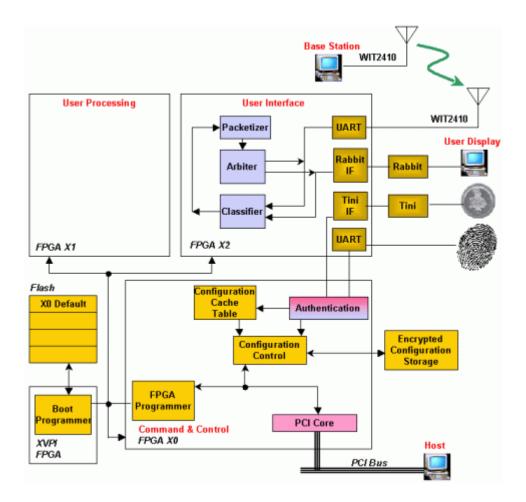

| Figure 5.4: DSN receiver prototype                                 | 56 |

| Figure 5.5: Wireless packet header                                 | 58 |

| Figure 5.6: Wired network input packet                             | 59 |

| Figure 5.7: Incoming data control byte                             | 60 |

| Figure 5.8: Secure network gateway prototype                       | 63 |

| Figure 6.1: Basic security analysis block diagram                  | 68 |

| Figure 6.2: Authorization replacement attack                       | 70 |

| Figure 6.3: Authorization platform replacement attack              | 73 |

| Figure 6.4: Authorization man-in-the-middle attack                 | 75 |

| Figure 6.5: Authorization snooping attack                          | 75 |

| Figure 6.6: Configuration store replacement attack                 | 77 |

| Figure 6.7: Configuration platform replacement attack              | 79 |

| Figure 6.8: Configuration man-in-the-middle attack     | 80 |

|--------------------------------------------------------|----|

| Figure 6.9: Configuration snooping attack              | 81 |

| Figure 6.10: Single user IP discovery attack           | 84 |

| Figure 6.11: Alternate single user IP discovery attack | 85 |

| Figure 6.12: Malicious function embedding attack       | 85 |

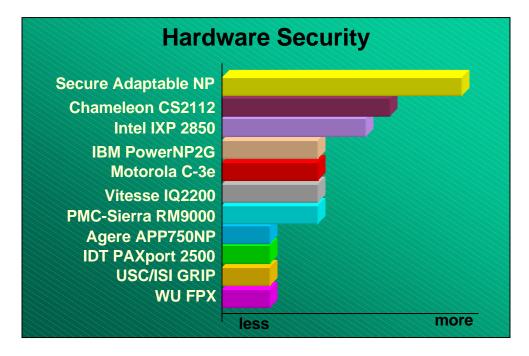

| Figure 6.13: Hardware security comparison              | 90 |

| Figure 6.14: System self-containment by device         | 91 |

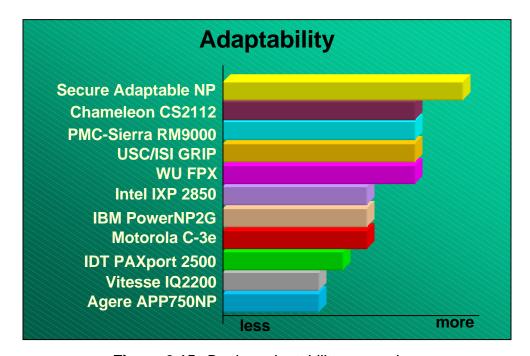

| Figure 6.15: Device adaptability comparison            | 92 |

# LIST OF TABLES

| Table 3.1: Design maxims                   | 25 |

|--------------------------------------------|----|

| Table 5.1: DSN user class partition matrix | 55 |

| Table 6.1: Attack consideration matrix     | 69 |

| Table 6.2: Attack resistance matrix        | 87 |

"Learn as much by writing as by reading." - Lord Acton

# **CHAPTER 1**

### THE INTRODUCTION

Network processors are becoming a predominant feature in the field of network hardware. As new network protocols emerge and data speeds increase, contemporary general-purpose network processors are entering their second generation and academic research is being actively conducted into new techniques for the design and implementation of these systems. At the same time, systems ranging from secured military communications equipment to consumer devices such as cellular telephones and PDAs are being updated to provide network connectivity. Many of these devices require, or would benefit from, the inclusion of device security in addition to data security. Whether it is a top-secret encryption scheme that must be concealed or a personal device that needs protection against unauthorized use, security of the device itself is becoming an important factor in system design. Unfortunately, current network processor solutions were not developed with device security in mind. A secure adaptive network processor can provide the means to fill this gap while continuing to provide full support for emerging communication protocols.

# 1.1 Scope

This dissertation outlines the development of a network processing system that is capable of securely reconfiguring itself while running – a secure adaptive network processor. This effort is driven by the need for flexibility and performance in network data-processing

systems as well as the need for security in the hardware supporting these systems. The solution presented here provides a high degree of both flexibility and security without sacrificing system performance. To demonstrate these features, a secure processor prototype is constructed and embedded in a network system where it is subjected to real network traffic for experimental evaluation.

#### 1.2 Problem Overview

Network system development and consumer appetite for information-handling devices are both evolving at a rapid rates. As this evolution occurs, manufacturers are continuously producing new custom hardware to handle the latest protocols and process content for the end user. The end users are keeping abreast of the wave by constantly purchasing new hardware to handle the hottest fashion and provide the most recent features. Both are interesting in protecting their hardware investment and would like to see that investment provide a more lasting service.

Portable devices, including cell phones, Personal Digital Assistants (PDAs), and laptop computers are playing an increasing role in the lives of consumers. As these devices become more integrated with the daily routines of the end-users, they are more likely to contain more personal information, including telephone numbers, birthdates, contact lists, and perhaps even credit card, bank account, or other billing information. Loss of a device containing this type of information is not only inconvenient; it can easily lead to identity theft [1]. As the theft of devices like cellular phones becomes more common [2], end-users would like to see products that not only contain the latest features, but also provide some assurance of security. For example, a cellular telephone that allows a user to change providers and technologies without buying new hardware would certainly find a place in the pockets of consumers. These same users would also derive comfort from the idea that this leading-edge adaptable communication hardware is keyed to them personally and will not function should it be lost or stolen.

Manufacturers would also welcome network hardware that conceals their intellectual property while providing a simple path for patching and upgrading their

technology. With a stable hardware platform, they could focus on adding the features that set them apart from the competition.

As this evolution in communication systems takes place, network hardware options are evolving as well. Older network systems relied upon application-specific integrated circuits (ASICs) to provide processing of network traffic. These ASICs provide the high throughput required, but lack the flexibility needed to support changing network protocols. From a security standpoint, ASICs also fall short, as they can be disassembled at any time to discover their contents. This type of an attack on a system not only causes a loss of system integrity, but also results in a loss of the intellectual property contained within the device.

Newer network systems require programmable hardware resources and some have turned to general-purpose processors. Support for network protocols and data rates, however, require significant processor overhead and, as outlined in Section 2.1, there is little indication that contemporary general-purpose processors operate fast enough to support increasing throughput requirements. In addition, processor-based systems are susceptible to security attacks based upon known processor functions and operational monitoring. Exploitation of known processor weaknesses might allow attackers to interfere with system operation. Attacks made against the power connections of system based upon a general-purpose processor can provide information regarding processor data content, including secret keys [3,4,5]. Monitoring of processor connections allows interested parties to easily replicate the system, taking with them the intellectual property of that system.

In an effort to provide better support for modern network systems, researchers have begun developing specialized network processors. The resulting processors range from pattern processors and Ethernet classifiers [32,33,34] to systems consisting of general-purpose RISC (Reduced Instruction Set Computer) cores [21,24,26,29] or reconfigurable hardware with additional special-purpose coprocessors designed to assist in common network packet processing tasks [31,35,36,38,41] (see Section 2.3). In general, these network processors are intended to provide more flexibility than custom Application-Specific Circuits (ASICs) coupled with more efficient handling of network traffic than

general-purpose processors can provide. Network processors also serve to prolong networking hardware lifetimes beyond ASIC solutions since they can be programmed to support alternate protocols or modifications to existing protocols.

Unfortunately, most of the currently available network processors have not been developed with security in mind. Current devices are designed primarily for efficient packet routing and high throughput, and remain somewhat limited in their flexibility and lack native data processing (encryption, compression, etc.) capabilities. Those devices that do provide some security or data processing support provide only limited support for data encryption. Additional processing support must be added in the form of a coprocessor, while no attempt to secure the device itself against unwanted use or reverse engineering is made. In addition, these processors often are based upon an existing microprocessor core that does not include a direct hardware implementation of instructions that are fundamental to the task at hand. This dependence on a fixed instruction set provides a readily accessible programming interface, but limits both the potential performance gains and the flexibility of the network processor. It can also present a security concern as the processor language is predefined and the instruction stream can be monitored and interpreted.

### 1.3 Solution Synopsis

A reconfigurable processor can provide both the flexibility and performance required in current cutting-edge and future network applications while adding a significant level of device security. It can provide custom data-flow processing of network traffic, allowing for on-the-fly encryption and other in-packet data processing tasks, and can adapt its structure to support new fundamental processing tasks required by a particular network. Furthermore, the device can adapt to support individual user needs and be reconfigured after the user is gone to remove all traces of that support from prying eyes. This degree of flexibility serves to increase both the performance and security of the device by allowing for direct hardware support of network protocols and concealment of that support.

By allowing processor reconfiguration to take place at run-time, a network node gains the ability to adapt fluidly to new data handling requirements. Without completely

halting information flow within a node, the network processor can update existing data handling routines or add new ones. Run-time reconfiguration of the processor hardware also allows hardware modifications to be specified within the network traffic, eliminating the need to manually locate and modify individual nodes when an update is required.

The ability of a processor to reconfigure itself at run-time not only enhances datahandling capabilities, but also allows for an advanced degree of hardware security. This type of device allows for construction of a system that contains only a generic user discovery application when not in use. The system can adapt its data handling functions to support a particular individual while they are using it, then return to a generic state when the are done. This type of system resists reverse engineering attempts, as it only contains information pertaining to its operation while a valid user is present.

The investigation and development of one such adaptive network processor prototype is presented here. With a focus on the added benefit of hardware security, a prototype system based upon Field Programmable Gate Arrays (FPGAs) is developed and tested in a network environment.

#### 1.4 Contributions and Claims

The objectives of this effort are (a) to demonstrate the viability of a secured run-time reconfigurable processor for streaming-data communication applications, and (b) to develop structured methods for assembling and reconfiguring this type of processor. The processor prototype is developed on a modified commercial FPGA platform and demonstrated in a wired/wireless network system. The primary challenge faced in this effort is the development of a processor structure that supports secure run-time reconfiguration and, more fundamentally, allows its hardware configuration to be modified while running. To support this effort, a technique for obtaining and utilizing hardware reprogramming information was developed and a method for providing reconfiguration information to the system was created. The primary benefits attained through this, which advance the state-of-the-art, are a manageable reconfigurable network processing system and protection of the intellectual property contained within that system. The concept of

system security presented here is not limited to network processing, however. It may be directly applied to any processing system that requires enhanced protection from reverse engineering.

The strengths and weaknesses of the working prototype are analyzed and experimental results are examined to determine the effectiveness of the implementation. The resulting contributions of this work are fourfold:

- 1. A secure system structure capable of supporting reconfigurable network processing is developed.

- 2. A key management technique for securing network processor assembly data and its transfer to the system is provided.

- 3. A simple user-customization and upgrade path for the underlying hardware of a network processing system is defined.

- 4. A prototype is produced to demonstrate and evaluate the secure network processing concepts introduced above.

As Chapter 2 more fully discusses, the ability to modify hardware within a processor at run-time provides a significantly greater degree of hardware security than traditional ASIC or microprocessor-based approaches. In addition, it considerably extends the life of network hardware by allowing it to adapt fully to protocols that have not yet been conceived while providing the potential to handle data more efficiently than systems based upon microprocessors.

#### 1.5 Dissertation Outline

This document describes a solution to the problem presented in Section 1.2. Chapter 2 provides background information as it reviews work that has been done in the fields of network processor design and secure embedded hardware. In Chapter 3, an overview of the structure and operation of the secure run-time reconfigurable network processing

solution is presented. Chapter 4 details a physical implementation of the solution in a prototyping platform. Experiments using this prototype as a secure configurable wireless network gateway and as a wireless end-user network interface are discussed in Chapter 5. Finally, Chapter 6 summarizes the work and provides some insight into future directions.

# **CHAPTER 2**

"How can we accept

another to keep our secret

if we have been unable to

keep it ourselves?"

- Francois De La

Rochefoucauld

### THE BACKGROUND

A network data rates and processing requirements continue to increase, specialized network processors are being developed as an alternative to the general-purpose processors and Application-Specific Integrated Circuits (ASICs) traditionally found in network data handling systems. These network processors are designed to provide systems with both ASIC-like speeds and microprocessor-like flexibility. Although the presently available commercial devices are primarily designed much like augmented RISC machines, current research is investigating the use of reconfigurable logic to provide additional speed and flexibility to end product designs.

As network devices become more prolific, applications requiring enhanced device security will arise. Military use of network systems for encrypted data traffic might depend on algorithms that are not publicly available. It is desirable for the structure of these systems to remain hidden. In the commercial realm, it is easily within the foreseeable future that applications such as cellular telephones customize themselves on a per-user basis. Reconfigurable processing provides an excellent basis for this, and enhanced device security can serve to protect corporate investment in the intellectual property that goes in to the technology. From a consumer viewpoint, it is also desirable to protect these new devices from unauthorized use. Enhanced security within the device itself provides user-specific customization without creating a device that is easily modified for unauthorized use.

This chapter provides an introduction to network processing and embedded device security in Sections 2.1 and 2.2, respectively. Section 2.3 contains an overview of the current state-of-the-art in the area of network processing. Section 2.4 summarizes the findings, and defines the security shortfall in current network processor approaches. A solution to this shortfall is described in depth in Chapter 3, and is the focus of the remainder of this document.

#### 2.1 Network Processing

Traditional network data-handling systems (switches, routers, edge devices, etc.) use either ASICs for performance [6,7] or general-purpose processors for flexibility and cost reduction [8,9]. Unfortunately, these devices do not offer the combination of speed and flexibility sought in current network systems [10,11]. ASICs provide high-speed data processing, but do not contain sufficient flexibility to adapt to new protocols and features [10]. Additionally, ASIC development is a costly and time-consuming process, requiring significant numbers of ASIC designers and millions of dollars in foundry fees just to produce a single device [10,11,12]. This level of investment in a device is a limiting factor to innovation, and can cause even the most well established players to hesitate before updating an established technology or pursuing a new direction. General-purpose processors are quite flexible, but do not offer the performance required for some network system tasks [10]. At the current rate of growth for both network interface and general-purpose processor speeds, this performance gap is continuing to widen [10]. These issues have created a demand for specialized network processors.

To meet this demand, several network processor solutions have been developed. These hardware solutions range from full single-chip network processors to individual special purpose programmable network processing devices, all falling into one of the following general categories: *general-purpose* processors and *focused-function* devices.

A *network processor* is defined here as a re-programmable processing device that is designed specifically for use in a networking environment. It must be able to provide computing services for the continuous data flows that comprise a networking environment.

To accomplish this, its instruction set or architecture is tailored to tasks (such as pattern matching, traffic classification, buffering, and queuing) that are common in a network environment.

#### 2.2 Embedded Device Security

Device security becomes a concern as network-attached devices become more ubiquitous and competition among vendors increases. For some applications, such as military communications, it is important to protect the network hardware itself from attempts to reverse engineer or replicate its operation (or from incompetence). From the manufacturer's standpoint, it is also important to protect the intellectual property (IP) investment contained in a network product. Gathering the core system function into a single device limits the number of exposed interfaces that can be monitored to determine system function. Organizations involved in proprietary network data manipulation can take advantage of this by encapsulating all IP functionality within a network processor. Unfortunately, current network processors (see Section 2.3) are not designed to meaningfully provide this type of security.

Solutions based upon conventional ASIC and processor techniques fall short of providing the full protection for the algorithms they contain. ASICs retain their functionality even when the system is not operating. As a result, an ASIC can be opened and studied to determine its internal structure [13]. A conventional processor may not retain information regarding tasks when not in operation, but it is vulnerable to busmonitoring attacks while running [14]. In a processor-based system, the IP investment is in the code fed to the processor at run-time. Monitoring device pins allows this code to be copied or modified. Knowledge of the processor internals allows for the copied code to be decompiled into the algorithms used by the system.

A reconfigurable logic device, such as a Field Programmable Gate Array (FPGA), does not need to retain its function while the system is not in operation. When unpowered, the FPGA is a generic reconfigurable device containing no user-specific function. While operating, it can remain a generic piece of hardware running a simple user discovery

application until a valid user presents credentials to the system. Once a user is validated by the system, the device can be configured to include functionality tailored to that user. While common FPGA configuration streams are clear text, protection of the information using a standard cryptographic protocol can provide for a measure of security as this data is transferred to the device [15,16]. When a user has finished with the system, the device can be reprogrammed to once again contain an innocuous application, removing all traces of the user function. If power is removed, even this user function is lost, thus protecting against offline ASIC-like reverse engineering. The fact that all functional data is transferred at once, prior to operation, also reduces the susceptibility to bus-snooping attacks while in operation.

In both processor-based and FPGA-based systems, program information is often held in static random-access memory (SRAM). In both cases, a secure application must take care to eradicate itself from the RAM, since it may be possible to detect the residual information in SRAM cells after power has been removed [17]. Since many FPGA technologies hold configuration information in SRAM, this means care must be taken when a user is done with the system. To prevent recovery of data from the SRAM after a valid user has left, the innocuous application programmed back in must occupy the full region of the device in which the user application was embedded, or at least sufficient area to obscure the user operation.

### 2.3 Current State of the Art for Network Processing

Network processing is an active field both academically and commercially. Commercial network processors are viewed as the next step towards high-speed data traffic processing and are currently enjoying a second generation as the initial multitude of network processor companies merge together into a few key players. At the same time, academic research continues into new methods of providing network services in reconfigurable hardware. This section identifies the contemporary key corporate network processor entities and discusses current academic research directed toward moving the network processor into reconfigurable hardware.

#### 2.3.1 General-purpose Commercial Network Processing Chips

#### 2.3.1.1 INTEL: Level One IXP Family

In late 1999, the integrated circuit manufacturer Intel Corporation acquired Level One Communications Incorporated in an effort to enter the network processing business. Level One provided several networking solutions including the IXP1200 Network Processor [18]. The IXP1200 consisted of an Intel StrongARM RISC processor and six programmable multithreaded micro-engines. The micro-engines operated using an instruction set specifically designed for networking and communications applications requiring efficient data handling. Operating at 162 MHz, the processor was capable of supporting low-speed switching and routing in real time [19]. Intel currently offers this device in the original format or updated to a 232 MHz package with the functionality unchanged. Additional devices in the family now include the IXP1240 (adding Cyclic Redundancy Check, or CRC, functions) [20] and IXP1250 (adding Error Correcting Code, or ECC, and CRC functions) [21]. None of these processors were designed with device security as a priority, and as such, they remain susceptible to standard microprocessor-based attacks such as bus snooping and RAM monitoring.

More recent products in the IXP line include the IXP2850 [22]: a network processor designed to provide some security function acceleration. This device is built upon the foundation of the previous Intel network processors, adding in hardware support for data security including the Data Encryption Standard (DES), Triple DES (3DES), Advanced Encryption Standard (AES), and early Secure Hash Algorithm (SHA-1). In addition, it supports applications requiring a higher data rate, allowing for multi-gigabit-per-second packet forwarding and traffic management. This device enables designs that must process secured data at high rates by coupling the cryptographic support functions with the network processing hardware. It has not, however, addressed hardware security. Hash table data and the instruction stream itself are stored off-chip, allowing for the use of simple bus-monitoring techniques to acquire data, keys, and program functionality.

#### 2.3.1.2 IBM: PowerNP Family

IBM has been developing network processor technology in-house since the initial release of the PowerNP NP4GS3 [23]. This device is designed to handle multi-gigabit Ethernet traffic, using a PowerPC 405 control processor to govern the actions of sixteen RISC protocol processors [24]. Table data and policing rules are stored on-chip in a 384KB RAM. External dynamic and static RAM is used for large control repositories and data storage. The most recent addition to the PowerNP family is the NP2G [25]. An extension of the NP4GS3 technology, this device reduces the number of protocol processors to twelve, while adding an on-chip switching engine and additional MAC (Medium Access Control) support.

The PowerNP family is not designed to provide inherent support for secure applications. While the use of internal instruction storage does reduce bus transfers, initial loading of this memory can be observed on exposed interfaces. In addition, support for data security would need to be provided by an external coprocessor.

#### 2.3.1.3 Motorola: C-Port Digital Communications Processors

In the late 1990s, C-Port Corporation developed a network processor similar to the IXP1200. Called the Digital Communications Processor (the C-5 DCP), it supported cell and packet processing, table lookup, and queue management [26]. Sixteen RISC-based Channel Processors and five coprocessors provided data processing within the DCP. The channel processors consisted of a RISC core to manage characterization, classification, traffic scheduling, and policy enforcement, with additional send and receive serial data processors to handle field parsing, extraction, deletion, insertion, framing, and CRC checking. The five coprocessors included an Executive Processor (XP), a Fabric Processor (FP), a Table Lookup Unit (TLU), a Queue Management Unit (QMU), and a Buffer Management Unit (BMU). The XP managed the overall DCP and coordinated it with external processors, while the FP was used to scale the device.

Motorola has since acquired C-Port Corporation, where this network processing line has continued to grow. In April of 2002, Motorola announced the introduction of a

three gigabit-per-second entry in the C-Port family: the C-3e [27]. This device provides 3 Gbps data handling bandwidth with a flexible architecture including eight external PHYs and on-board Ethernet MACs driven by seventeen RISC (MIPS) processors for packet forwarding and thirty-two additional Serial Data Processors for data processing.

Like the IBM PowerNP family, these devices were not designed for secure applications. All instruction and table storage are off-chip, allowing for monitoring attacks, and secure protocol processing would require external coprocessor support.

#### 2.3.1.4 Vitesse: GigaPOWER and TeraPOWER to IQ2200

In the second quarter of 2000, Vitesse Semiconductor Corporation bought both XaQti and SiTera corporations for their network processing lines. SiTera produced a network acceleration chip set for use with external processors, while XaQti's Active Flow Processors were flow-based dedicated processors that performed specific tasks such as packet processing and parsing [28]. Active Flow processors were based on programmable hardware that was modified via firmware upgrades. XaQti was pursuing two product lines: the GigaPOWER family (several Active Flow Processors coupled with an integrated Ethernet Media Access Controller) and the TeraPOWER family (multiple chips that may be combined to form a network processing solution)[28].

Vitesse's current product line includes the IQ2000 and IQ2200 families of network processors. Unlike their more Fixed-function POWER predecessors, the IQ2200 families are stand-alone devices that provide services for network traffic. The IQ2200 consists of four 400MHz 32-bit RISC processors fed by a classification engine [29]. With a wide range of port options and built-in gigabit Ethernet MACs, the IQ2200 is well suited to stand-alone network applications. Like the IBM and Motorola offerings, these devices were not built with security in mind. As a result, they suffer from the same shortcomings seen in the above systems when used as secure network devices.

#### 2.3.1.5 PMC-Sierra: RM9000

PMC-Sierra produces a wide range of networking products ranging from packet processors and classifiers to MIPS processor systems targeted toward communications. Designed to be part of a network processing solution, the RM9000x2 is their current next-generation processor. It contains dual 1 GHz MIPS processor cores, a 160 Gbps multi-port memory fabric, and a 500 MHz transport interface that allows for 16 Gbps data I/O traffic [30]. While it is in no way itself secure, this device represents the leading edge of general-purpose processor technology for network processing today.

#### 2.3.1.6 Chameleon: CS2112 Reconfigurable Communications Processor

Sunnyvale, California's Chameleon Systems is taking a more generally reconfigurable approach to network processing. Their Reconfigurable Communications Processor (RCP) combines a reconfigurable fabric with an ARC processor, PCI controller, and memory controller to provide a fully customizable stream processing solution. The reconfigurable fabric allows for processing contexts to be interchanged in a single clock cycle, in theory reducing power consumption and increasing device utilization [31,32].

This reconfigurable approach should allow for secure protocol cores to be embedded within the device. In addition, the use of configurable logic, rather than general-purpose processors means that there is no external instruction stream to monitor while the device is operating. The system does, however, remain vulnerable to bus monitoring attacks during the initial configuration sequence. An attacker familiar with the configuration data format could intercept the configuration stream and extract the application structure from it, gaining the Intellectual Property (IP) invested in the application. Furthermore, there is no structure in place to validate a user. Malicious parties might modify the user application and reprogram the device for their own ends.

#### 2.3.2 Fixed-function Commercial Network Processing Devices

2.3.2.1 Lucent / Agere: APP1200 Pattern Processor and APP1400 Routing Switch Processor to APP750NP Classification Engine and APP750TM Traffic Manager

Another company producing network-processing hardware in the late 1990's was Agere Corporation. Its products included both a Fast Pattern Processor (the APP1200) and a Routing Switch Processor (the APP1400) [33]. The pattern processor performed wirespeed recognition, classification and re-assembly of packet traffic. The routing switch processor performed wire-speed queuing, traffic management, traffic shaping, packet modification and re-assembly. Agere was acquired by Lucent in 2001 and then spun back off as Agere a short time later. The current line of processors includes higher-speed versions of the APP1200 and APP1400 – the APP750NP Classification Engine and the APP750 Traffic Manager [34].

As network processing chip sets, not one of these devices acting alone provides the processing needed for most applications. Instead, they are typically combined with each other and additional external processors to provide a full network processing system. Secure data processing applications would require additional coprocessors and result in a hardware implementation that would be more difficult to secure.

Programming of the APP*x* devices is done via a proprietary Functional Programming Language and an Agere Scripting Language. This provides a reduction in the number of lines of code required for a typical application, but limits the system to more specific applications.

#### 2.3.2.2 IDT (Solidum): PAX.core

Solidum Systems has also been working in the network processing realm since the late 1990s. Acquired by Integrated Device Technology (IDT) in September 2002, they continue to provide a unique line of classification processors. Their PAX product line is geared specifically toward the task of classification. The original PAX.core 1000, for example, was a gigabit classification core designed for insertion in other VLSI solutions. It

was built using a state machine engine and optional functional units (host interface, checksum, configurable counters) implemented in an FPGA bed. The current line is represented by the PAX.port 1200 and 2500 architectures. These programmable classification processors are optimized for content inspection and regular expression matching at gigabit-per-second data rates [35].

All of Solidum's products are programmed using their proprietary PAX hardware description language. By allowing modification of the fundamental system, rather than just the code running on the processor, these products provide more potential flexibility than processor core—based classification engines. In addition, the use of an FPGA base clearly demonstrates that FPGA technology is suitable for high-speed network processing.

#### 2.3.3 Network Processing Research in Academia

#### 2.3.3.1 USC/ISI GRIP Gigabit Rate IPsec Card

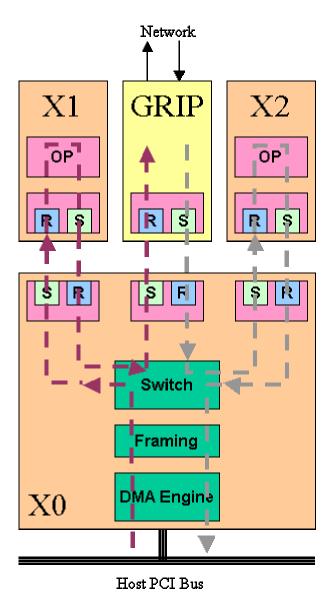

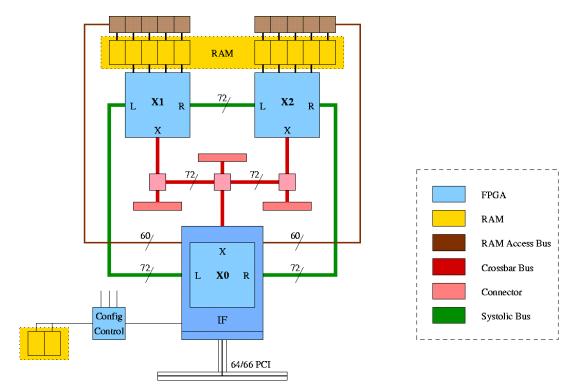

In April of 2002, researchers at the University of Southern California's Information Sciences Institute demonstrated a first-generation giga-bit rate packet processing system implemented in several FPGAs [36]. Coupling a gigabit Ethernet MAC with an FPGA prototyping platform, the researchers sought to address the performance bottleneck imposed by the Central Processing Unit (CPU) in single-processor gigabit networking systems. Packet processing functions including basic routing, encryption, and framing are performed in the reconfigurable components. As shown in Figure 2.1, three separate Xilinx *Virtex XCV1000* [37] FPGAs (X0, X1, X2) are used to process data traffic. In the depicted example, X0 performs packet header processing functions including switching and framing, while X1 and X2 perform data transformation operations such as encryption and decryption. This work clearly demonstrates the utility of reconfigurable logic in next-generation network systems.

Figure 2.1: USC/ISI GRIP Gigabit Rate IPsec Card [36]

#### 2.3.3.2 Washington University Field Programmable Port Extender

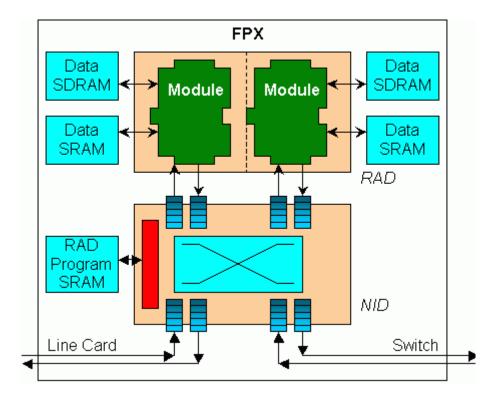

A more mature reconfigurable network processing solution is the focus of ongoing research at Washington University in St. Louis, Missouri. The Field Programmable Port Extender (FPX) system uses FPGAs to allow reprogrammable hardware modules to be dynamically installed into network devices [38]. An FPX module contains a static network interface *NID* FPGA (Xilinx *Virtex XCV600E*) and a single reprogrammable user application *RAD* device (Xilinx *Virtex XCV1000E*) as shown in Figure 2.2. These modules are inserted into

an existing network stream to provide user-specified traffic processing including routing, buffering, and packet content modification.

Figure 2.2: Washington University FPX [39]

Recent work on this system has included the development of an interface that allows FPX modules to be programmed remotely via a TCP/IP (Transmission Control Protocol over Internet Protocol) network [39]. The NCHARGE tool suite includes both an application programming interface (API) that allows applications to communicate with the FPX and a Web-based user interface to manage control and configuration.

NCHARGE provides no provision for security and the FPX system is not itself secured hardware. The combination does, however, demonstrate the usefulness of an FPGA network processing system and its ability to adapt to network events.

#### 2.3.3.3 UCLA Layer Seven Network Processor Accelerator

UCLA researchers G. Memik, S. O. Memik, and W. H. Smith are also working to advance FPGA-based network processing. They have come up with a reconfigurable OSI Layer Seven accelerator designed to enhance existing network processing applications [40]. Implementing tree lookup and pattern matching algorithms in the reconfigurable logic, they found via simulation that task execution times could be improved by a factor of twenty over the same system implementing the task in software without an accelerator. Within the structure of the simulation experiment, they tested a single-configuration accelerator design composed of a multiplexed set of modules and a design in which new tasks required reconfiguration of the accelerator. Their results indicated that both designs provide a significant performance boost to networking tasks and, moreover, that reconfigurable logic is a viable solution to network processing bottlenecks.

#### 2.3.3.4 University of Edinburgh MIR Mixed-version IP Router

In 2002, Gordon Brebner of the University of Endinburgh [41] described a gigabit IP router that fits on a single Xilinx *Virtex-II Pro XC2VP7* [42] FPGA device. This router takes advantage of the configurability of the FPGA to maintain system performance as traffic migrates from IPv4 to IPv6. Although the work preceded the *Virtex-II Pro* release, and was therefore not implemented in hardware, results did indicate that a prototype would be capable of operation at gigabit Ethernet rates. The results obtained by Brebner clearly pave the way for a single-chip reconfigurable network processor solution.

## 2.4 Background Summary

Network processors are becoming more predominant in the field of network hardware. As new network protocols emerge and data speeds increase, this trend can only continue. Several approaches to the design of a network processor currently exist. All of these approaches provide some means efficiently handling high-speed network traffic and adapting to new protocols. The current design techniques used to build these network processors do not, however, fully conceal the internal algorithms, nor do they provide support for security of the hardware itself. When the reputation of a network company is

based upon its ability to process data more efficiently than the competition, it is important to protect the intellectual property of a design. When that design is critical to the security of the user, it is important that that security not be breached.

As these systems find their way into applications in which the algorithms themselves need to be provided the utmost security (military encryption, etc.), it becomes more important to conceal the device function and control user access. Toward this end, a new scheme is needed to maintain the speed and flexibility of network processors while providing an additional level of device security. An ideal device provides an efficient means of run-time reconfiguration to support leading-edge network protocols, adapts as these protocols change, and implements an efficient method for concealing the internal operation and configuration/programming data presented at its ports. Chapter 3 describes one such system.

# **CHAPTER 3**

"Vision – It reaches beyond the thing that is, into the conception of what can be. Imagination gives you the picture. Vision gives you the impulse to make the picture your own."

- Robert Collier

### THE CONCEPT

Several approaches to network processor design were described in Chapter 2. Although each design had something to offer, it was shown that none of them provided sufficient device security to fully protect network systems from intellectual property theft or malicious use. In this chapter, a new approach to network processor design is presented that provides for enhanced device security. This design allows for the flexibility and performance required of the network processor while providing an enhanced level of device security.

Section 3.1 presents an overview of the design, while a general description of the components of this new network processor system structure is contained in Section 3.2. Detailed description of a specific implementation may be found in Chapter 4.

#### 3.1 Processor Overview

A significant amount of current research has been directed toward the design of reconfigurable network systems, as illustrated by the examples in Section 2.3.3. Past work at Virginia Tech has also shown that it is possible to rapidly develop fully functional processor prototypes in reconfigurable hardware [43], and has demonstrated the usefulness of this technology for processing continuously streaming data [44] as well as for handling network traffic [45]. The secure network processor concept presented here expands upon

that work to define a network processor structure that provides a level of hardware device security beyond that available using the processors surveyed in Chapter 2. The new structure takes advantage of reconfigurable hardware to allow for both user-based operation and concealment of the intellectual property (IP) contained in a design. Due to its malleable hardware nature, the resultant system benefits from an extended product life cycle, an easy upgrade path, and an inherent user customization capability. It is worth noting that while the full security aspects of this type of processor may not be useful in all network processing systems, the additional benefits to system upgradeability and customization may be useful in most installations that can trade off any added up-front expense of reconfigurable hardware for an upgrade path that does not require hardware modification.

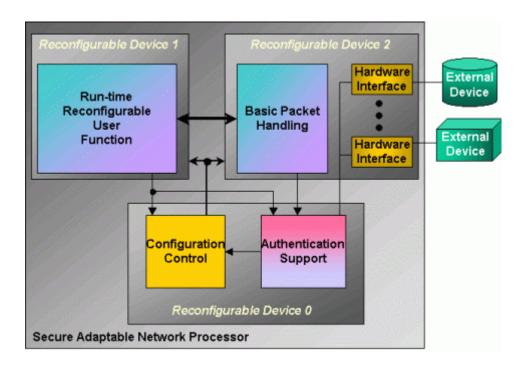

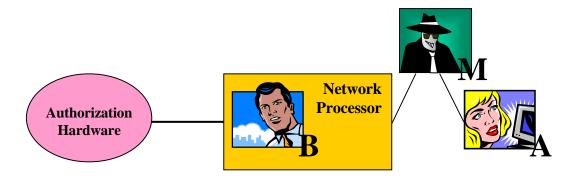

This new level of device security is, in part, achieved by taking advantage of runtime hardware reconfiguration to structurally divide the processor function into two modes – *user discovery* and *user function*. In the *user discovery* mode, the network processor contains a simple application that waits for a valid user to arrive. When the user arrives, this application acts as part of a security system to establish the validity of that user and determine the desired device functionality. Upon user verification, the device reconfigures itself with the protected application and enters *user function* mode. Should the user leave, the device removes all traces of the protected application and once again enters the generic user discovery mode.

The modal division of device operation allows the intellectual property (IP) implemented in specific user functions to be more effectively concealed since the device does not contain the IP when a valid user is not present. While this does not protect against a malicious valid user, it does eliminate the risk of reverse engineering of normal user functionality based upon system structure that is present in ASIC-based devices (see Section 2.2). Furthermore, while a malicious valid user may be able to observe their own system operation, they would not be able to determine the operation of other user systems, nor would they obtain other user credential or biometric information, since the innocuous application embedded between users will remove all trace of the previous user.

Of course the underlying strength of this user-based security is dependent upon the strength of the chosen user validation method. Since the discovery mode application is responsible for user validation and is always available at the device, it could potentially be reverse-engineered by extracting it from local storage and decrypting it without a valid user present. If successful, an attacker will have discovered the local encryption key used for the initially loaded application. As a result, this type of attack could result in the attacker gaining the ability to use the reconfigurable hardware for another purpose. If local keys for initial application encoding are varied between devices, the attacker will not, however, gain the ability to use the hardware of other secure adaptable network processors. Furhtermore, reverse engineering of the discovery application does not provide the credentials or biometric information required to obtain, decode, and embed any user-specific configuration information (Section 3.2). As a result, only a single piece of hardware is lost in the attack, not its function or content. Since the underlying hardware is generally available the attacker could have simply built a similar reconfigurable system with considerably less effort if use of the hardware is their goal. It is, however, possible that an attacker could modify the discovery application, and then entice a valid user to register, thus obtaining that user's configuration information. The encryption used for the user discovery application and the chosen user validation method should, therefore, be resistant to this type of probing in an ideal system.

With an unknown internal structure, bus monitoring or power analysis attacks also become less lucrative. Observation of bus signals while the device is in user function mode may reveal nothing about the device IP since user functionality is wrapped into a single device package that does not require an instruction stream for operation. Similarly, power or timing analysis attacks are more difficult in hardware-based systems than processor-based designs [4]. In processor-based systems, it is difficult to avoid this type of attack by modifying code structure [5]; in a secure adaptable network processor like the one described here, additional circuitry can easily be added at any time to offset (or help mask) timing and power fluctuations. This is somewhat offset by the fact that user configurations must be loaded into the system as users arrive. While bus monitoring of an active system may yield no useful information, monitoring of the configuration operation could

potentially reveal the internal device structure. To prevent this sort of attack, configuration must be done in a secure manner.

To achieve the desired level of security, three design maxims must be observed as listed in Table 3.1.

#### Table 3.1: Design maxims

- Interfaces that might be subject to observation must be secured.

- 2. Hardware details must be unobservable so that device operation cannot be inferred examination of the device.

- 3. The device must not contain any useful user-specific IP unless a valid user is present.

In short: The system must be resistant to board-level attacks, both online and offline.

#### 3.2 Processor Structure

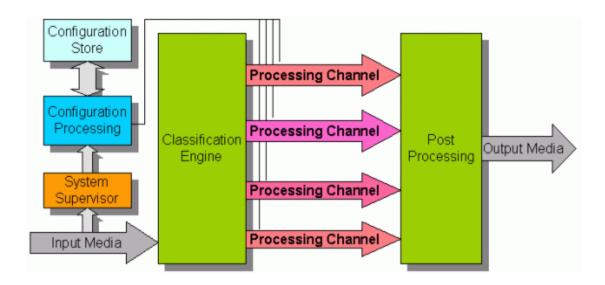

Any description of this network processor design structure must consist of more than just a data processing engine outline. To provide for user identification and functional reconfiguration, external connections must be defined. Furthermore, each of these connections must be secured to prevent observation as per the first design maxim. The system description provided here is divided into four parts: the *user discovery system*, the *user authentication interface*, the *configuration interface*, and the *data processing system*. Section 3.2.1 outlines the operation of the user discovery system, while Section 3.2.2 provides an example of securing the user authentication interface and Section 3.2.3 gives an example of securing the configuration interface. Finally, Section 3.2.4 describes a potential user data processing structure for the network processor.

#### 3.2.1 User Discovery System

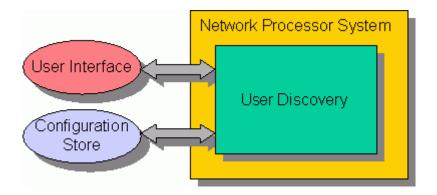

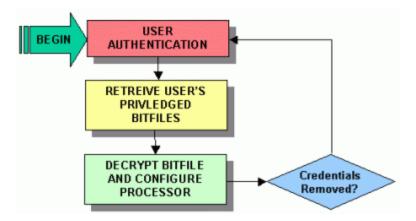

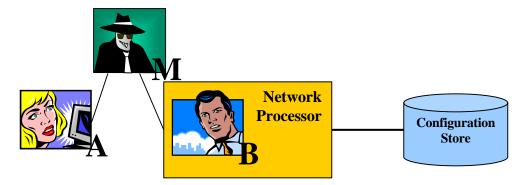

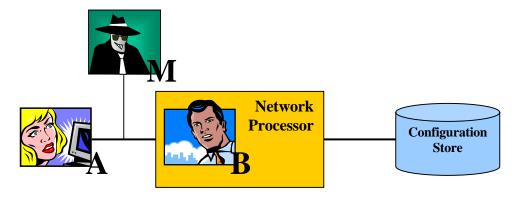

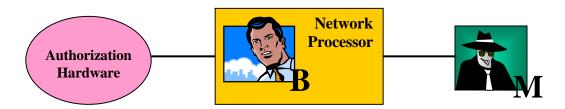

In its initial state, this network processor consists of nothing more than a generic reconfigurable hardware device. When power is applied, the system loads a user discovery system through the same encrypted interface that user applications are loaded (discussed later in Section 3.2.3). The state of the powered system prior to user authentication is shown in Figure 3.1, and, as required by the third design maxim above, contains no user-specific function. This system is designed only to recognize valid users and configure the device appropriately. The state diagram of Figure 3.2 outlines the function of the user discovery system.

Figure 3.1: User discovery system

When a user arrives at the system, they identify themselves through the user interface. Once the system is satisfied that a user is valid (see Section 3.2.2), it determines the required configuration(s) for that user, retrieves them from a *Configuration Store*, decrypts them (see Section 3.2.3), and configures the device for user operation. The resulting user data processing system (see Section 3.2.4) replaces the user discovery system in the network processor, allowing discovery resources to be utilized for the user application.

Figure 3.2: User discovery states

#### 3.2.2 User Authentication Interface

User authentication depends upon an external interface to the network processor. A user must be able to signal the processor system when they wish to use it and the system must be aware of the fact that they have gone. In the scheme presented here, a biometric signature and a token device identify the user to the system. The token used contains a description of the system desired by the user and sufficient processing power to perform some fundamental security tasks as described in the following sections.

The user authentication interface is exposed to the world and, as per the first maxim, must be protected. The desired level of protection is accomplished by implementing a two-level interface security scheme. At the first level, the network processor and token verify each other and create a secured data path between them. At the

second level, the token identifies the user and utilizes the secure data path to provide keys for configuration stream decryption. The token produces these keys using information supplied by the network processor and a set of user credentials that remain in the token. Alternative security schemes may be used for this link, but may result in a decreased security level.

The initial step in establishing user functionality is the creation of a secure link between the user token and the network processing system. When the network processor detects a token insertion, it begins this process by generating a random number, encrypting it with a public key, and sending the encrypted number to the token. Meanwhile, the token verifies the identity of the current user over another secured link (not dealt with here, see [46] for a device that provides a biometrically secured token). When the token receives both the random number and a valid user signal, it decrypts the number received from the network processor and uses it as part of the encryption for a return packet. The returned data identifies the device configuration(s) desired by the user.

This scheme depends upon a public key / private key pair that is embedded in the hardware. In essence, this and the particular encryption scheme used become shared secrets of the platform and token. Guessing the shared secrets by monitoring the signals is difficult in this case, however, as the encryption scheme is not known (and could potentially vary over time or users) and the data transferred from the network processor to the token consists of a random number generated and encrypted internally by the network processor at the start of each user session. Data returned to the network processor from the token is similarly difficult to interpret as it is secured by a scheme that uses the (decrypted) random number initially sent by the network processor. Finally, the secure link should be designed such that it requires an occasional refresh cycle in which the authentication process is repeated to verify that a valid user is still present and to change the key used for data flowing on the link. For details of a particular implementation of this type of scheme, see [47]. For an analysis of some of the weaknesses of this scheme, see Section 3.2.3.3.

## **3.2.3** Configuration Interface

Upon establishing a secure link to the token, the network processor uses the returned configuration identification information to obtain configuration data from the Configuration Store. The Configuration Store depicted in Figure 3.1 will very likely be external to the network processor device. As such, care must be taken to protect both data held in the Configuration Store and the flow of that data from it to the network processor. All configuration data kept in the Configuration Store is therefore pre-encrypted by the developer and then further encrypted using a one-time key and padded with a security header prior to sending it to the network processor. Locally stored user configuration credential information is used by the Configuration Store to generate this one-time key as explained in Section 3.2.3.1. The one-time key generation and padding techniques employed allow for key reconstruction and data decryption by a receiving system that contains the same credential data and is aware of the key reconstruction technique. While it is still possible that the configuration data may be intercepted and decoded, the use of a one-time key guarantees that the effort required for the individual packet decoding process will not provide access to other encrypted configuration data provided by the Configuration Store. Furthermore, the fact that the packaged configuration data is itself encrypted means that the IP contained in the configuration data of the decoded packet still requires additional decoding before it reveals its information. Upon receipt by a valid user, both the packet and the embedded configuration information are decrypted. The configuration information is then used to reconfigure the network processor device. Some potential weaknesses of this scheme are outlined in Section 3.2.3.3. For an example of a commercial scheme similar to the packetization technique used here, see the Constructive Key Management<sup>TM</sup> (CKM<sup>TM</sup>) technique developed by TecSec, Incorporated for secure data transfer applications [48].

## 3.2.3.1 Key Management

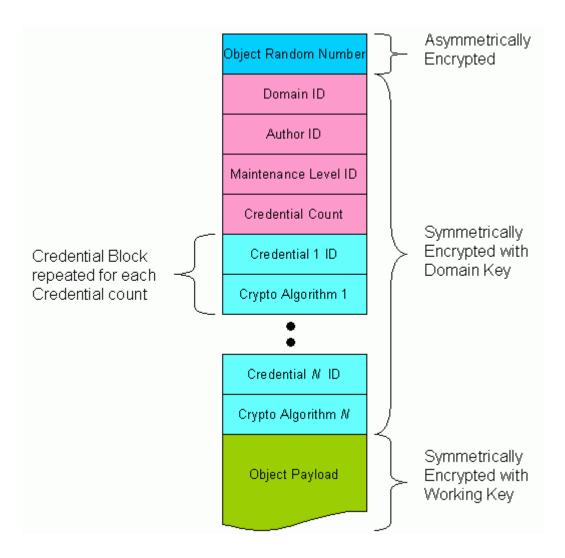

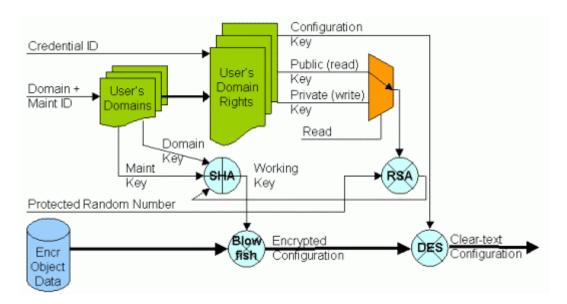

The packet returned by the Configuration Store is encrypted with a one-time use key and accompanied by a *security header*. The security header (shown in Figure 3.3) contains an asymmetrically encrypted random number along with symmetrically encrypted tags

Figure 3.3: Configuration data security header

identifying the user domain, author, and number of credentials used. A credential identifier and an identification of the algorithm used to encrypt the random number are included for each credential used in constructing the data set. This header is passed to the token, which processes it to produce a working key for the data. An example of the process by which this happens is summarized in Figure 3.4, where RSA and Blowfish encryption algorithms are combined with a secure hash algorithm to extract the encrypted configuration data from a received configuration object. Once the data has been extracted, it is decrypted using a domain configuration key and the appropriate algorithm to produce a clear-text configuration data stream.

Figure 3.4: Network processor configuration data reception

The first element of the data transfer is an *encrypted random number*. This number allows the transfer to have a unique working key that is disposed of after the transfer is complete. The random number is encrypted using the credentials identified later in the header. Decryption of the number allows the recipient to reconstruct a working key required to interpret the data portion of the transfer.

A domain identifier, an author identifier, a maintenance level, and a credential count are encrypted with the domain key and follow the random number. The maintenance level identifier is a two-part (forward and backward) index into an array of Maintenance Level Domain Keys. These keys are shared secrets among member of a domain that can be accessed by a user within the range specified by the forward and backward indexes. The recipient attempts to decrypt this section of the header with each of their maintenance level domain keys in turn. If they have the correct privileges, one of the keys will result in a domain identifier match, which means the correct key has been found.

Given a correct domain key, the credential blocks (consisting of a *credential identifier* and *algorithm identifier*) are decrypted. The shared secret credential key and identified algorithm for each credential are applied in the order given to the encrypted random number to produce the working random number.

A *credential* provides permission to read or write a class of data within a domain, and credentials of this sort allow stratification of information within that domain. Each credential has an identifier that indexes a public/private key pair. This key pair is a shared secret among class members within the domain. The public key provides write permission for a class of data while the private key provides read permission. It is possible to grant a user read permission to a class without write permission. Similarly, a user may be privileged to write data to a class, but may not be allowed to read from that class.

The token contains a *combiner* that uses the working random number along with the domain key to reproduce the one-time key for the transferred data payload. This working key is transferred via the secure link back to the network processor, which uses it to decrypt the data contained in the payload and produce the original encrypted configuration.

Finally, the token passes the appropriate domain configuration key to the network processor and the encrypted configuration is decrypted to produce a clear-text bitstream that is used to configure the network processor for the current user function.

While the proposed key management technique does provide a significant level of information security, it is still susceptible to some limiting factors. Implementation of this technique requires significant processing resources on the token device. The key generation process may potentially require several cryptographic schemes since each credential can be associated with a separate algorithm. This limitation will, however, become less of a factor as technology allows for more processing on token devices. The complexity of the algorithm also limits the speed of the configuration process. In systems where configuration speed is critical, a lighter-weight security system may need to be employed.

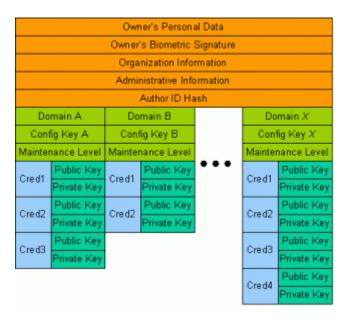

#### 3.2.3.2 Token Contents

A domain-oriented approach to key management is employed to promote management of user groups and stratification of users within groups (Section 3.2.3.1). To support this approach, the token must contain the elements listed in Figure 3.5. These elements are

placed into a tamper-resistant token device to secure them from inspection. The token must also contain sufficient processing capabilities to perform the tasks outlined in the previous section. One such device token is the Dallas Semiconductor Java-Powered iButton [49]. For an example showing the programming of this device, see [47].

Figure 3.5: Token data content

#### 3.2.3.3 Configuration Interface Security Analysis

As indicated previously, this secure network processor is most vulnerable during user configuration. While the proposed authentication, key management, and configuration schemes do provide a significant amount of security, they still remain susceptible to certain types of security attacks.

The weaknesses of this network processor lie primarily in the interfaces. The interface to the Configuration Store is considered to be open to snooping. Data read from it may, in general, be accessed by any interested party and stored for later analysis. It is argued above that this may not pose a significant threat in terms of IP loss. However, should the interface be a general network system, there is the threat of a third party exercising a Denial-of-Service (DoS) attack on a device. Flooding the network processor

with data may cause its reconfiguration process to slow dramatically. The network processor does reject any packets that it did not specifically request (or cannot verify), however, minimizing the effect of the attack. A more serious DoS attack would be to flood the Configuration Store with data. Since the Configuration Store is listening for requests from any network processor implementing this scheme, it may take more resources to determine that a request is not from a valid source. Although the Configuration Store will not reply unless a request is validated, operation of the request-receiving port could be hampered. This will affect the configuration times of all legitimate network processors using that storage device. A scheme implementing several distributed configuration storage systems may help alleviate both this type of attack and general loading of a single device.

Perhaps a more serious attack on the Configuration Store interface would be to supplant the system that supplies configuration information with the goal of providing false configuration information to the network processor. The supply of invalid information is not in itself sufficient to configure the device, as the information must be supplied when the device is requesting configuration. The supplied information must also correspond to the requested data in terms of formatting, configuration encryption, and credential-based encoding. Clearly, the success of this type of attack would require intimate knowledge of the key management technique as well as the credentials and domain configuration keys that are applied to various configurations. Using an incorrect technique or credential set would simply result in configuration data that the network processor was unable to decode. As a result, it would fail to configure. Analysis of the Configuration Store itself would not provide sufficient information to produce this information. While full compromise of the Configuration Store would be a serious problem, the configuration data that it contains is encrypted with a set of keys of which it is not aware.

If an attacker where to possess a full set of domain configuration keys and take over a Configuration Store system, configuration information would be compromised. In addition, the attacker could correctly format malicious configuration data and feed it to network processors as data is requested. In similar systems, an authentication server is used to reduce the likelihood of an attack in which a malicious system mimics the response

of a valid server. In this case, however, the information supplied by an authentication server would be redundant, as the data exchange format provides its own authentication and would require that the malicious system be a valid configuration server.

The interface used for user authentication is also exposed. The scheme used to provide security at this interface has been designed to eliminate the risk of man-in-the-middle attacks and reduce the effectiveness of brute force attacks. The interface itself is susceptible to flooding, but it is not part of an external network so the risk of this is less than that of someone simply cutting the wires to the interface. For a full analysis of the authentication interface security scheme, see [47].