# Design, Analysis and Experimental Evaluation of a Virtual Synchronous Machine Based Control Scheme for STATCOM Applications

#### Chi Li

Thesis submitted to the faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

Master

In

**Electrical Engineering**

Rolando Burgos Lamine Mili Dushan Boroyevich

August 20th, 2015 Blacksburg, Virginia

Keywords: virtual synchronous machine, STATCOM, control

## Design, Analysis and Experimental Evaluation of a Virtual Synchronous Machine Based Control Scheme for STATCOM Applications

Chi Li

#### **ABSTRACT**

Because renewable energy sources are environment-friendly and inexhaustible, more and more renewable energy power plants have been integrated into power grids worldwide. To compensate for their inherent variability, STATCOMs are typically installed at the point of common coupling (PCC) to help their operation by regulating the PCC voltage. However under different contingencies, PCC voltage fluctuations in magnitude and frequency may impede the STATCOM from tracking the grid frequency correctly, hence worsening its overall compensation performance, and putting at risk the operation of the power plant. Further, the virtual synchronous machine (VSM) concept has recently been introduced to control grid-connected inverters emulating the behavior of rotating synchronous machines, in an effort to eliminate the shortcomings of conventional d-q frame phase-locked loops (PLL).

In this dissertation, the VSM concept is extended by developing a STATCOM controller with it, which then behaves like a fully-adjustable synchronous condenser, including the adjustment of its "virtual" inertia and impedance. An average model in two D-Q frames is proposed to analyze the inherent dynamics of the VSM-based STATCOM controller with insight into impacts from the virtual parameters and a design guideline is then formulated. The proposed controller is compared against existent d-q frame STATCOM control strategies, evincing how the VSM-based approach guarantees an improved voltage regulation performance at the PCC by adjusting the phase of its compensating current during frequency fluctuations, in both simulation and experiment.

Secondly, the dynamics of the VSM-based STATCOM controller in large signal sense is studied, especially its capability to ride through faults. Analysis is carried out with phasors to obtain a fundamental understanding at first and followed by state space equations to predict the transients analytically, which is validated by matching both simulation and experiment. The effects of two outer loops are also reviewed and some possible solutions are suggested and evaluated. Moreover, the relationship between the virtual inertia and the actual inertia is established and the

dc capacitor sizing is discussed in a possibly more economical way. The start-up process of a VSM-based STATCOM is presented to implement a practical prototype as well.

#### ACKNOWLEDGEMENTS

First, I would like to express my sincere gratitude to my advisor, Dr. Rolando Burgos, for his guidance, help and encouragement. I will not be able to achieve all these without his patience in leading me and experience in power electronics. I am always encouraged by him technically and emotionally when I feel down and can hardly proceed productively.

I would also like to thank Dr. Dushan Boroyevich, whose foresight often inspires me to think deeper and further rather than being confined to a specific technical issue. His challenging questions can always reveal something I ignore and impel me to find answers out of the box.

Dr. Lamine Mili and Dr. Yaman Evrenosoglu are also people I want to thank for their interests in my work and opinions from the power system society to improve my research outcomes. I also would like to express my gratitude to Dr. Mili for his accepting the invitation to come to Blacksburg for my defense.

I would like to thank the support from the Center for Power Electronics Systems (CPES) Renewable Energy and Nanogrids (REN) Mini-consortium.

The great CPES staff have made it easy for me to focus on my progress and I would like to thank them all: Ms. Marianne Hawthorne, Ms. Teresa Shaw, Ms. Teresa Rose, Ms. Linda Long, Mr. David Gilham, and Dr. Wenli Zhang.

Many senior students have offered me great help during these years, especially Dr. Zhiyu Shen, for his help in guidance in experiments, Dr. Xuning Zhang for his advice in debugging my hardware, Mr. Igor Cvetkovic for the cooperation and Dr. Bo Wen for his enlightenment for some break-through in my research.

It is a pleasure to work with the talented colleagues in the renewable energy and nanogrids (REN) mini-consortium who offered me help and support. I would like to thank Dr. Marko Jaksic especially for his hardware, Dr. Yang Jiao, Mr. Jun Wang, Mr. Sizhao Lu, Mr. Wei Zhang, Mr. Fang Chen, Mr. Shishuo Zhao, Mr. Yadong Lv, Mr. Alinaghi Marzoughi, and Ms. Ye Tang.

I also would like to thank all my friends in Blacksburg who made my life enjoyable and beautiful: Mr. Qiong Wang, Ms. Bingyao Sun, Mr. Ming Lv, Mr. Chao Fei, Mr. Zhongsheng Cao, Mr. Xuebing Chen, Ms, Yincan Mao, Dr. Lingxiao Xue, Mr. Bo Zhou, Dr. Shuilin Tian, Mr. Xiucheng Huang, Mr. Zhemin Zhang, Mr. Zhengyang Liu, Mr. Yuchen Yang, Mr. Zhengrong Huang, Mr. Junjie Feng, Mr. Lujie Zhang.

Finally but most importantly, I would like to thank my parents, Mr. Yang Li and Dr. Suping Huang for their love, encouragement and support from all respects since I was born. I feel blessed to have them in my life.

## TABLE OF CONTENTS

| List of F | igures . | ix                                        |

|-----------|----------|-------------------------------------------|

| List of T | ables    | xiii                                      |

| Chapter   | I. In    | ntroduction1                              |

| 1.1       | Backg    | round1                                    |

| 1.2       | Synch    | ronization for grid-interfaced converters |

| 1.2.      | 1 P      | hase locked loop                          |

| 1.2.      | 2 P      | ower-balance-based synchronization        |

| 1.3       | Motiv    | ation and outlines5                       |

| Chapter   | II. B    | asics of Static Synchronous Compensators  |

| 2.1       | Basic    | operation of STATCOM7                     |

| 2.2       | Conve    | entional STATCOM control                  |

| 2.2.      | 1 A      | BC frame control                          |

| 2.2.      | 2 D      | -Q frame PLL-oriented vector control9     |

| 2.2.      | 3 E      | ffect of PLL                              |

| 2.3       | Functi   | onalities and applications                |

| 2.3.      | 1 St     | tability issues                           |

| 2.3.      | 2 V      | oltage regulation                         |

| 2.3.      | 3 L      | ong term issues                           |

| 2.4       | Topolo   | ogies and configurations16                |

| 2.4.      | 1 B      | asic topology                             |

| 2.4.      | 2 M      | Iulti-phase converter                     |

| 2.4.      | 3 M      | Iulti-level converter   20                |

| 2.5     | Sui    | nmary                                                    | 24 |

|---------|--------|----------------------------------------------------------|----|

| Chapter | r III. | Virtual Synchronous Machine Control Concept              | 25 |

| 3.1     | Bas    | sic concept                                              | 25 |

| 3.2     | Ov     | erview on control schemes                                | 25 |

| 3.3     | On     | going activities                                         | 31 |

| 3.3     | 3.1    | Modeling and design                                      | 31 |

| 3.3     | 3.2    | Applications                                             | 32 |

| 3.4     | Sui    | mmary                                                    | 32 |

| Chapter | r IV.  | Analysis and Comparison of VSM and D-Q Frame Controllers | 33 |

| 4.1     | Inti   | roduction of the test bed                                | 33 |

| 4.2     | VS     | M control                                                | 35 |

| 4.2     | 2.1    | Loop structure                                           | 35 |

| 4.2     | 2.2    | Effects of virtual parameters.                           | 37 |

| 4.3     | De     | sign rules of VSM controller                             | 44 |

| 4.4     | Co     | mparisons between two controllers                        | 45 |

| 4.4     | 4.1    | Comparisons in frequency domain                          | 45 |

| 4.4     | 1.2    | Comparisons in time domain                               | 49 |

| 4.5     | Exp    | perimental verification                                  | 52 |

| 4.5     | 5.1    | Hardware set-up.                                         | 54 |

| 4.5     | 5.2    | Transient responses.                                     | 56 |

| 4.5     | 5.3    | Transfer functions                                       | 61 |

| 4.6     | A l    | arger power system case study                            | 66 |

| 4.7     | Sui    | mmary                                                    | 70 |

| Chapter | · V    | Practical Considerations of VSM-Controlled STATCOM       | 72 |

| 5.1 In     | troduction                                            | . 72 |

|------------|-------------------------------------------------------|------|

| 5.2 A      | nalysis on large transients                           | . 75 |

| 5.2.1      | Preliminary assumptions                               | . 75 |

| 5.2.2      | Phasor analysis                                       | . 75 |

| 5.2.3      | State-space equations                                 | . 77 |

| 5.2.4      | Experimental verification                             | . 80 |

| 5.3 E      | ffects of outer loops                                 | . 81 |

| 5.3.1      | Effect of Pf loop                                     | . 81 |

| 5.3.2      | Effect of QV loop                                     | . 82 |

| 5.4 Po     | ossible solutions                                     | . 85 |

| 5.5 F      | inal design guideline                                 | . 87 |

| 5.6 D      | C capacitor considerations                            | . 88 |

| 5.6.1      | Relationship between virtual inertia and real inertia | . 88 |

| 5.6.2      | DC capacitor sizing                                   | . 88 |

| 5.7 St     | tart-up process                                       | . 90 |

| 5.8 S      | ummary                                                | . 92 |

| Chapter VI | . Conclusions and Future Work                         | . 94 |

| References |                                                       | 95   |

## LIST OF FIGURES

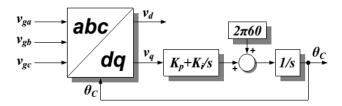

| Figure I-1 Control blocks of SRF-PLL                                         | 3             |

|------------------------------------------------------------------------------|---------------|

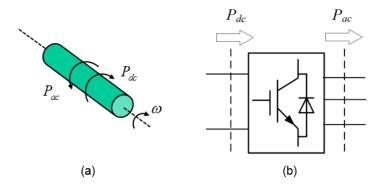

| Figure I-2 Virtual synchronous machine concept                               | 4             |

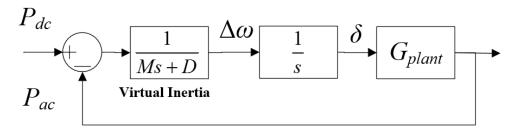

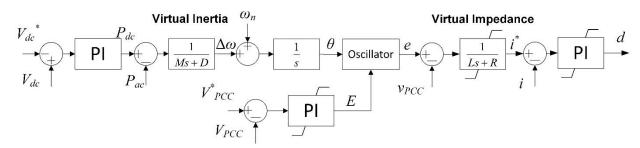

| Figure I-3 Control blocks of basic VSM controller                            | 5             |

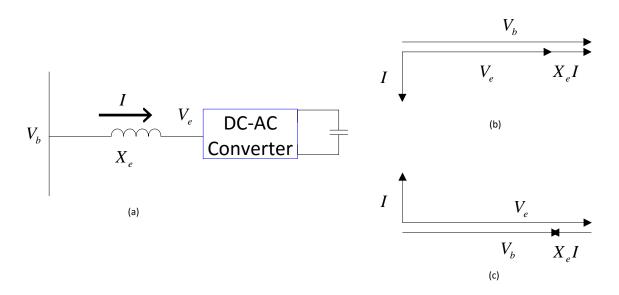

| Figure II-1 Basic concept of STATCOM: (a) basic topology of STATCOM; (b) ind | ductive mode; |

| (c) capacitive mode                                                          | 7             |

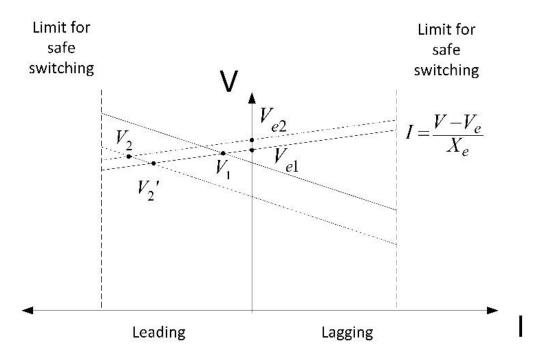

| Figure II-2 Operating characteristics of STATCOM                             | 8             |

| Figure II-3 ABC frame STATCOM controller                                     | 9             |

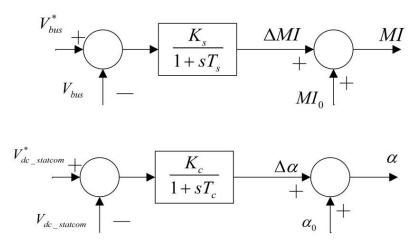

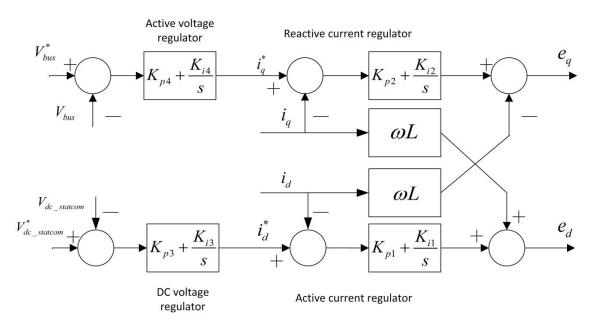

| Figure II-4 D-Q frame PLL-oriented STATCOM controller                        | 10            |

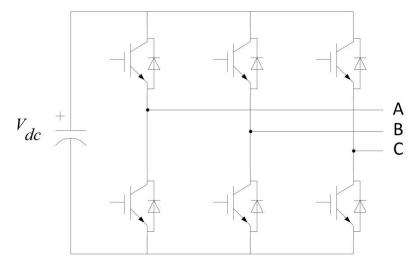

| Figure II-5 2-level VSC                                                      | 17            |

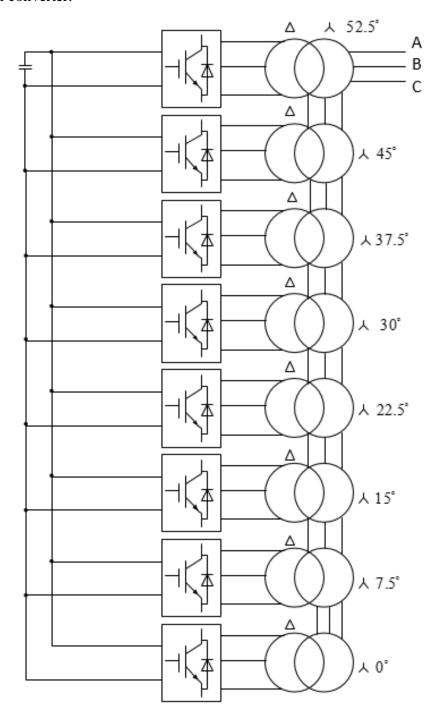

| Figure II-6 True-48-pulse topology                                           | 18            |

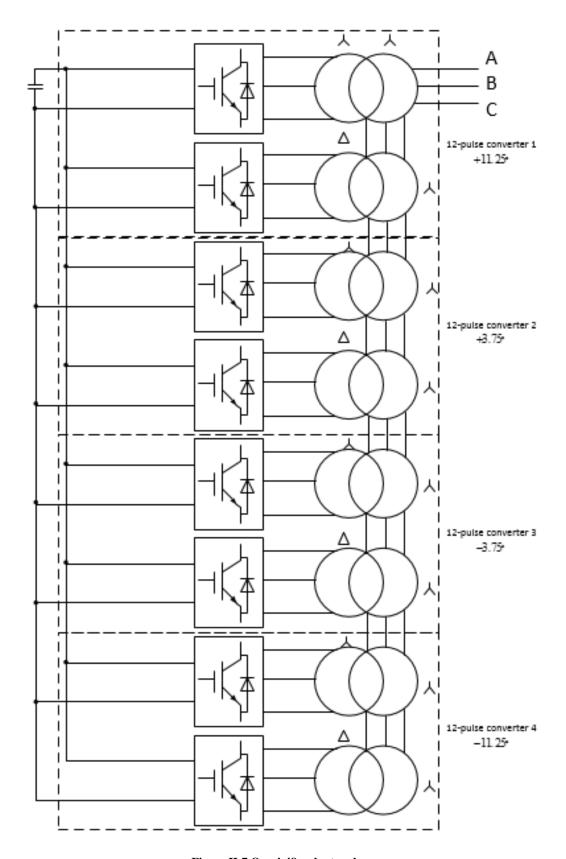

| Figure II-7 Quasi-48-pulse topology                                          | 19            |

| Figure II-8 Diode clamped converter – single phase                           | 21            |

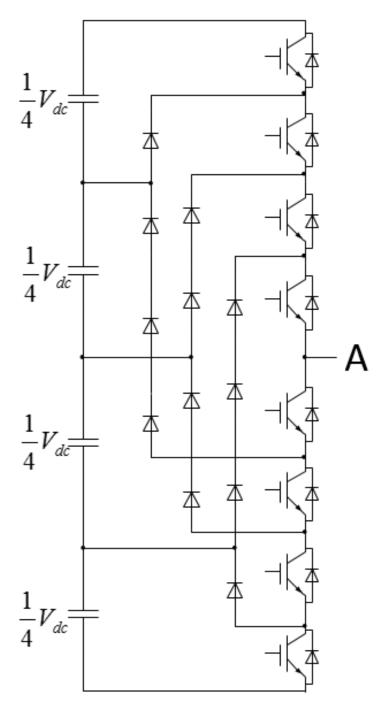

| Figure II-9 Capacitor clamped converter – single phase                       | 22            |

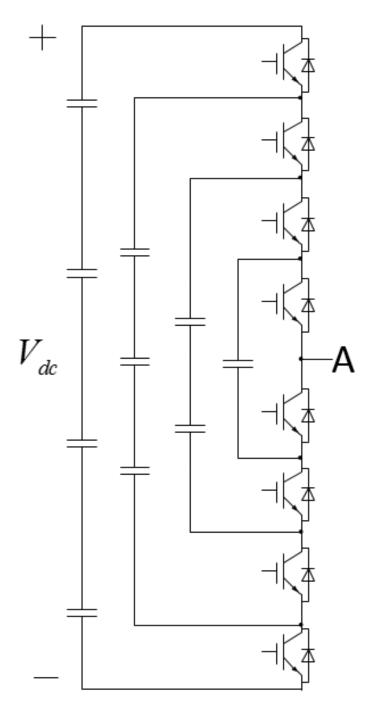

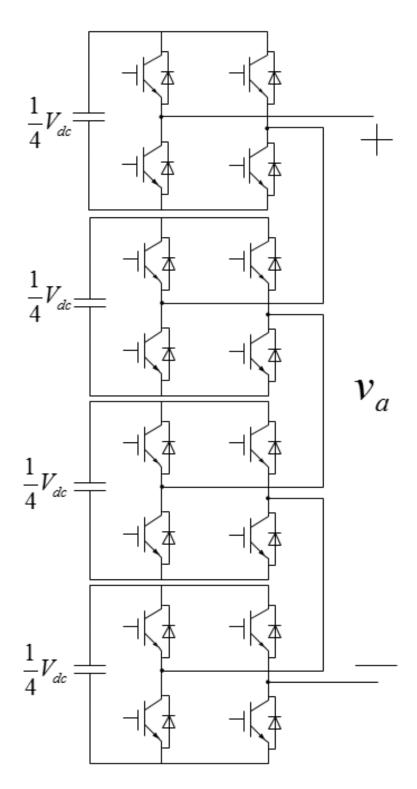

| Figure II-10 H-bridge cascaded converter – single phase                      | 23            |

| Figure III-1 VSM control scheme without current loop                         | 27            |

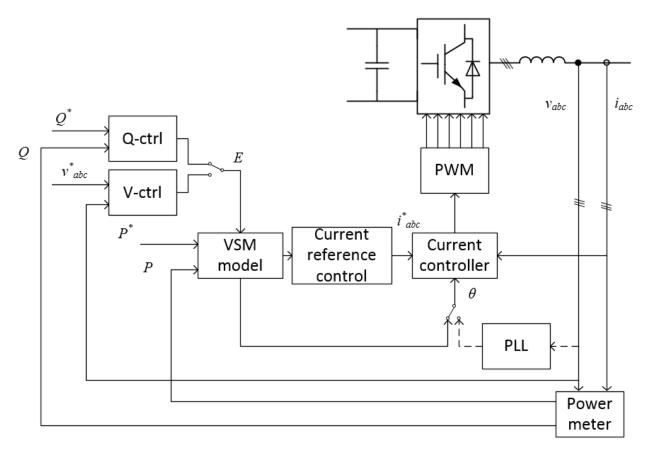

| Figure III-2 VSM control scheme with current loop type 1                     | 29            |

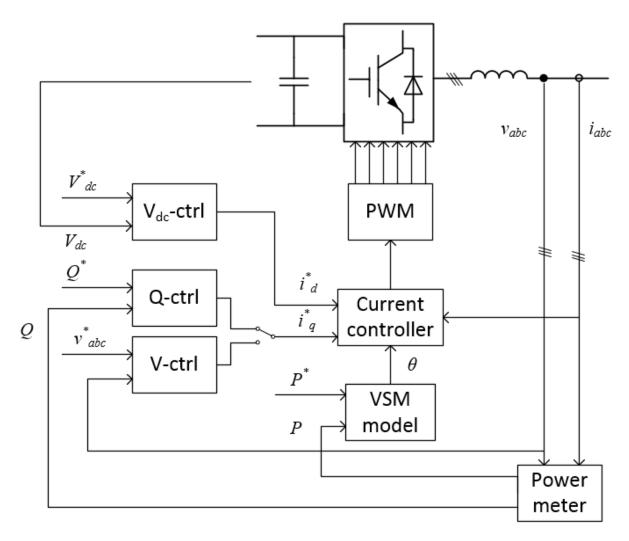

| Figure III-3 VSM control scheme with current loop type 2                     | 30            |

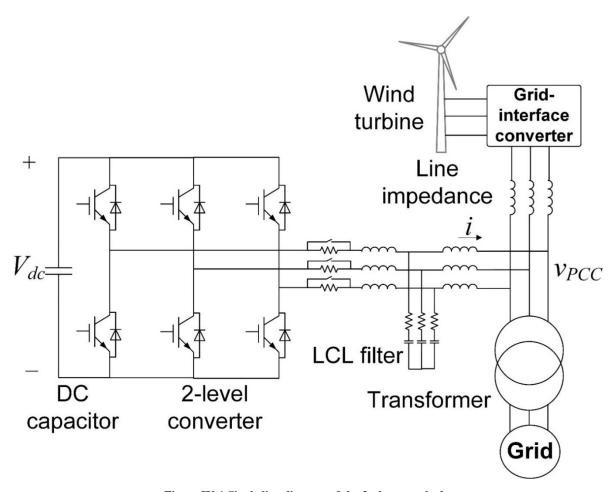

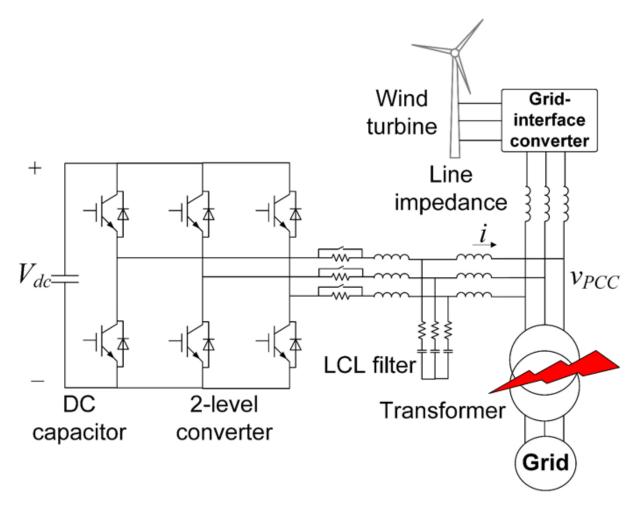

| Figure IV-1 Single line diagram of the 3-phase test bed                      | 34            |

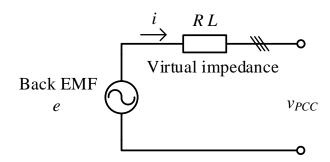

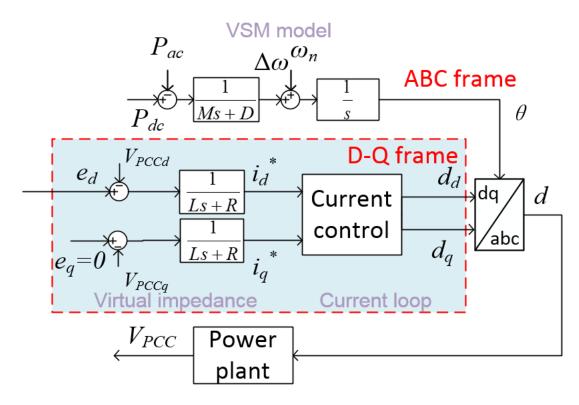

| Figure IV-2 Equivalent circuit of VSM controlled STATCOM                     | 35            |

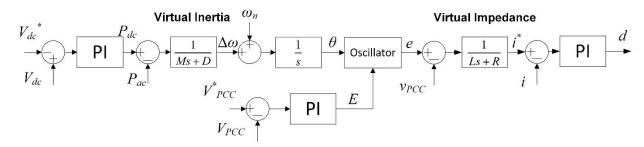

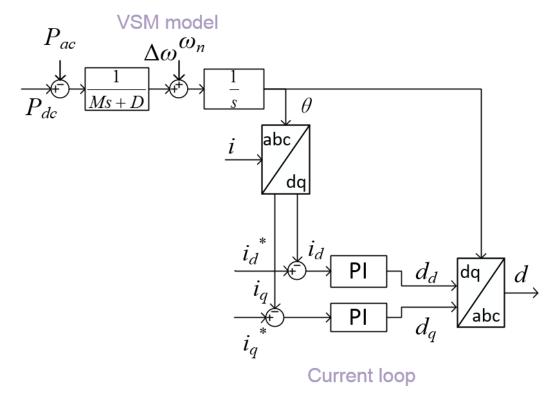

| Figure IV-3 VSM control blocks for STATCOM                                   | 35            |

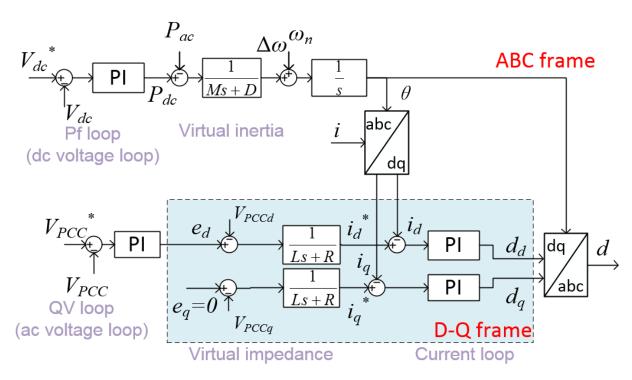

| Figure IV-4 Practical VSM control blocks for STATCOM                         | 37            |

| Figure IV-5 Control blocks of power loop and power plant                     | 38            |

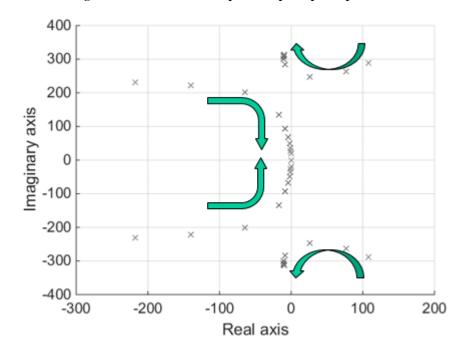

| Figure IV-6 Open loop system poles trajectory with <i>M</i> increasing       | 38            |

| Figure IV-7 Open loop system poles trajectory with <i>D</i> increasing                  | . 39         |

|-----------------------------------------------------------------------------------------|--------------|

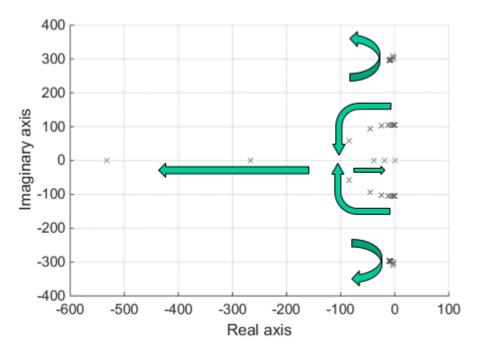

| Figure IV-8 Control blocks of power loop and current loops                              | . 40         |

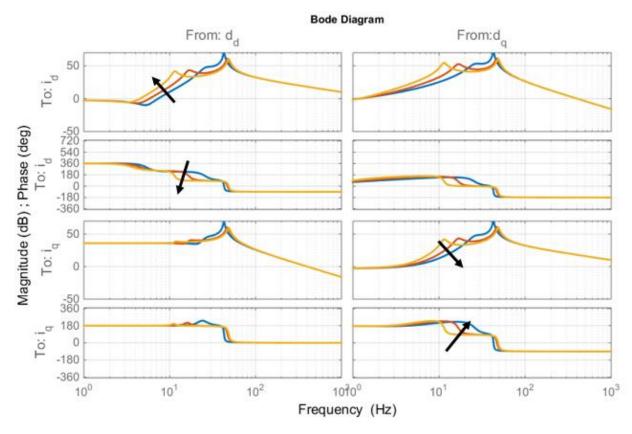

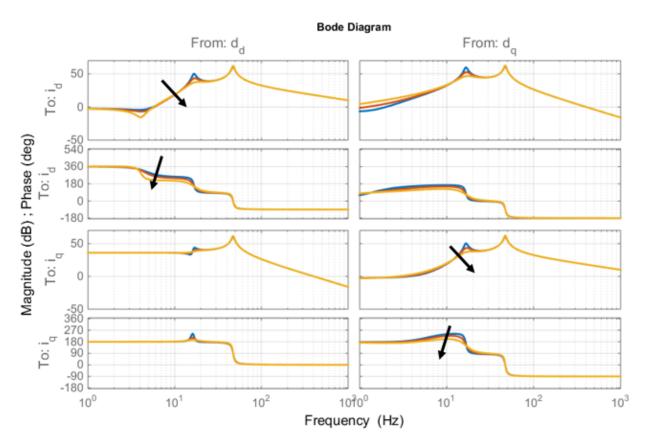

| Figure IV-9 Effect of <i>M</i> on current loop transfer functions                       | . 40         |

| Figure IV-10 Effect of <i>D</i> on current loop transfer functions                      | . 41         |

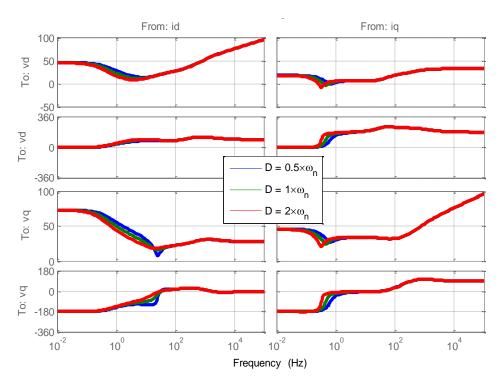

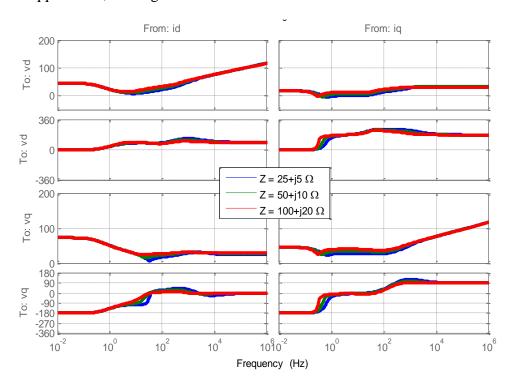

| Figure IV-11 Effect of <i>D</i> on ac impedance                                         | . 42         |

| Figure IV-12 Control blocks of power loop, current loop and virtual impedance           | . 43         |

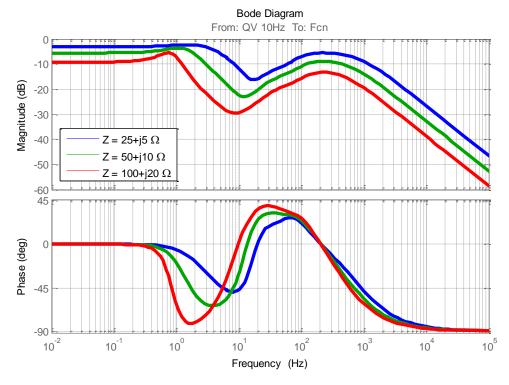

| Figure IV-13 Effect of Z on QV loop transfer function                                   | . 43         |

| Figure IV-14 Effect of Z on ac impedance                                                | . 44         |

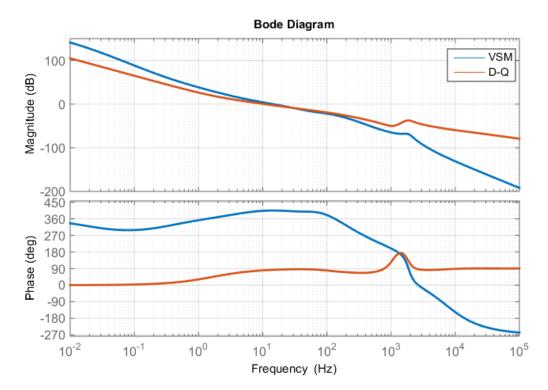

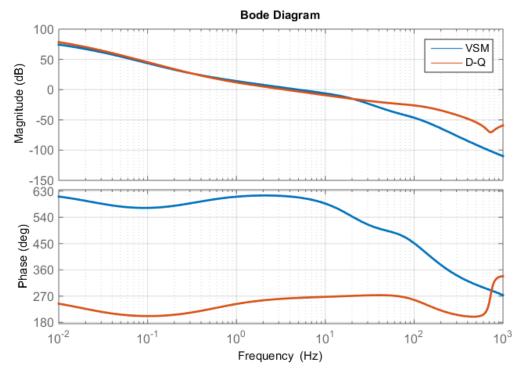

| Figure IV-15 Synchronization loop gain of two controllers                               | . 46         |

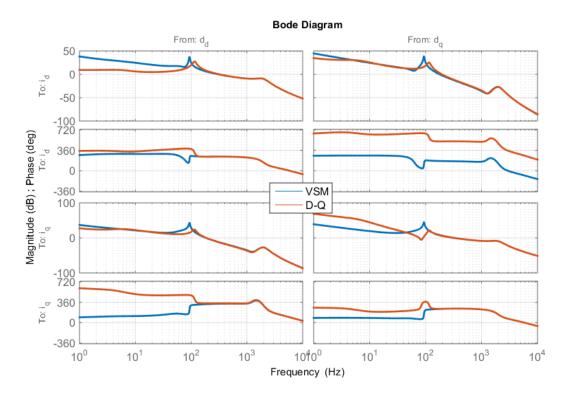

| Figure IV-16 Current loop gain of two controllers                                       | . 47         |

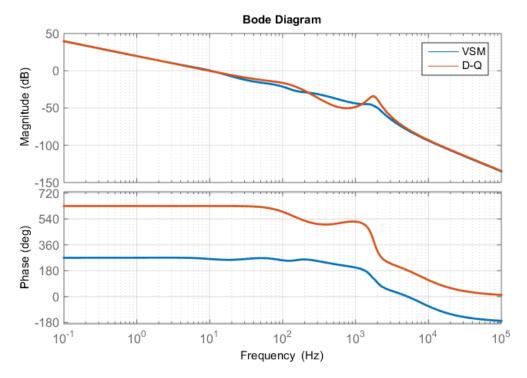

| Figure IV-17 AC voltage loop gains of two controllers                                   | . 48         |

| Figure IV-18 DC voltage loop gains of two controllers                                   | . 48         |

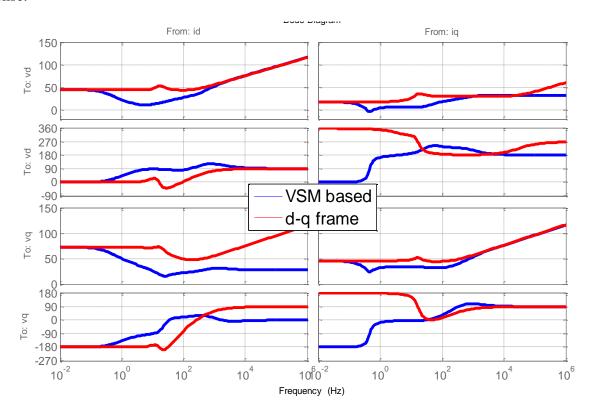

| Figure IV-19 AC impedance of two controllers                                            | . 49         |

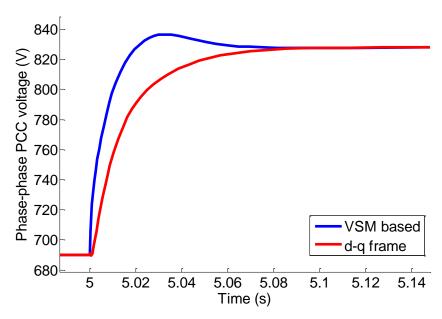

| Figure IV-20 PCC voltage regulation performance when reference changes                  | . 50         |

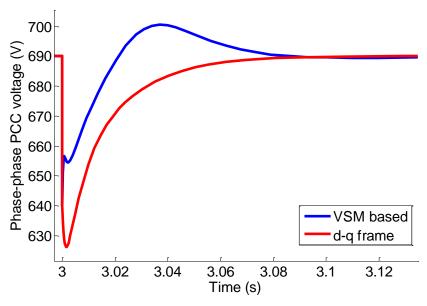

| Figure IV-21 PCC voltage regulation performance during voltage sag                      | . 51         |

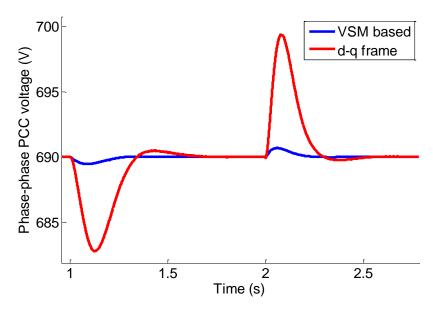

| Figure IV-22 PCC voltage regulation when frequency fluctuates                           | . 52         |

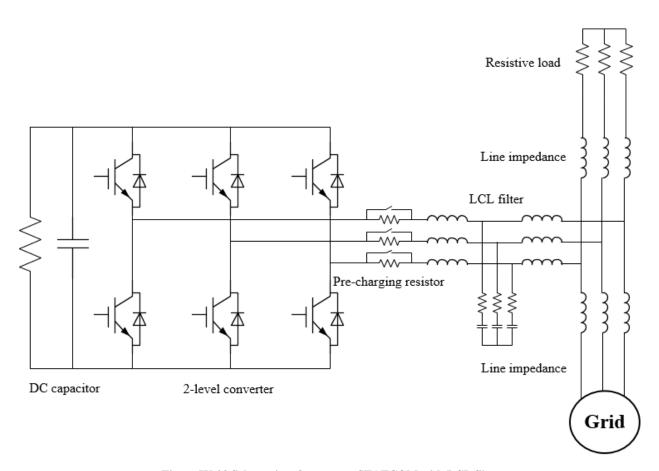

| Figure IV-23 Schematics of prototype STATCOM with LCL filter                            | . 53         |

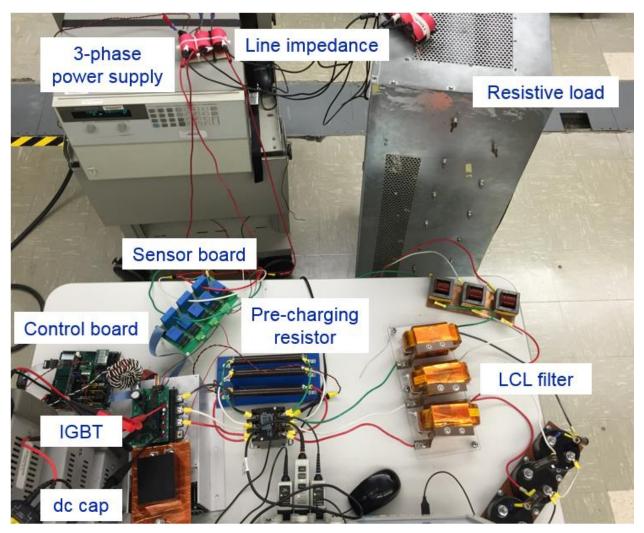

| Figure IV-24 Hardware set-up for prototype STATCOM                                      | . 55         |

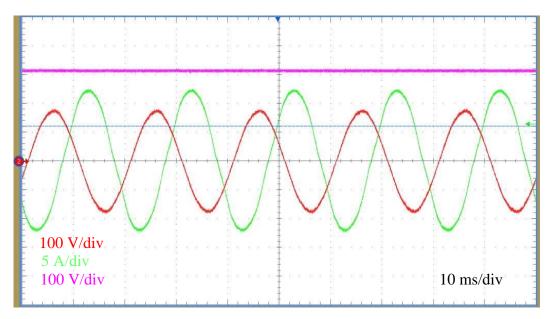

| Figure IV-25 Steady-state waveforms of prototype STATCOM                                | . 56         |

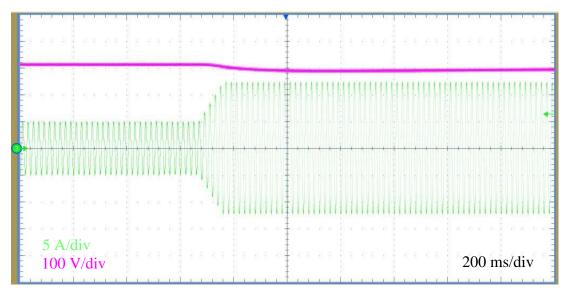

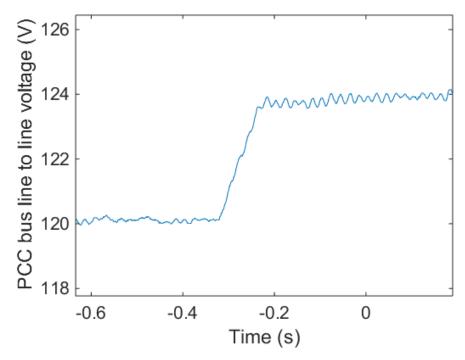

| Figure IV-26 Waveforms when reference changes with D-Q controller                       | . 57         |

| Figure IV-27 PCC voltage regulation performance when reference changes with D-Q contro  |              |

| Figure IV-28 Waveforms when reference changes with VSM controller                       | . 58         |

| Figure IV-29 PCC voltage regulation performance when reference changes with VSM control | ller<br>. 58 |

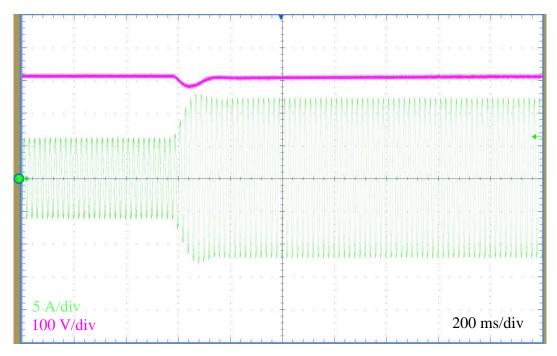

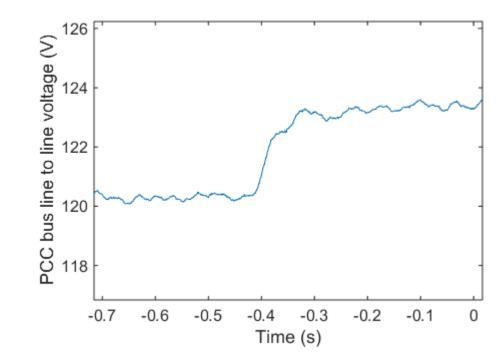

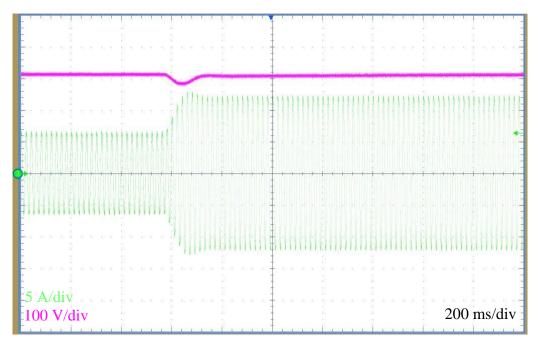

| Figure IV-30 Waveforms during voltage sags with D-Q controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 59 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

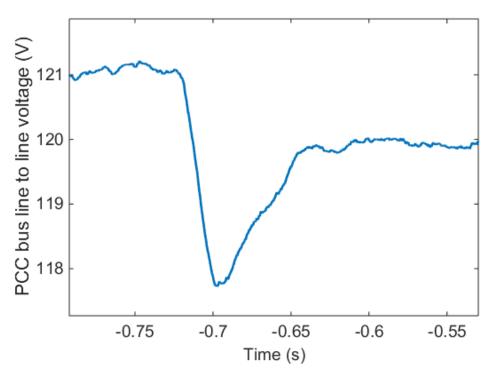

| Figure IV-31 PCC voltage regulation performance during voltage sags with D-Q controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 59 |

| Figure IV-32 Waveforms during voltage sags with VSM controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 60 |

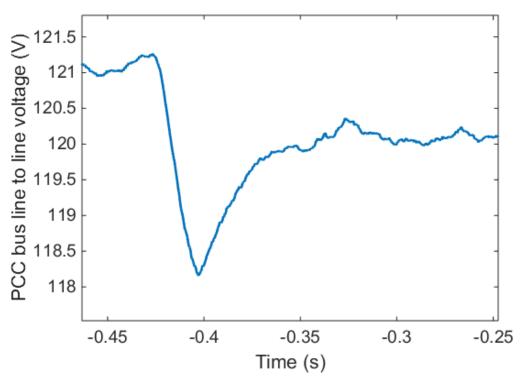

| Figure IV-33 PCC voltage regulation performance during voltage sags with VSM controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 60 |

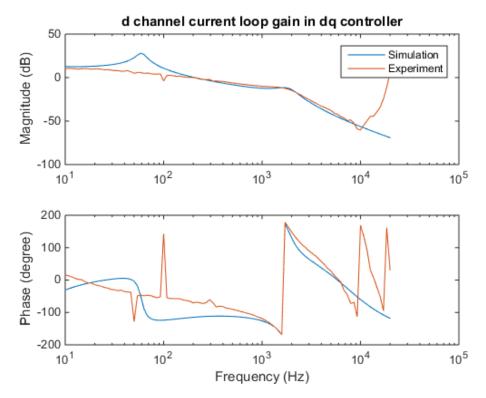

| Figure IV-34 d channel current loop gain in D-Q controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 62 |

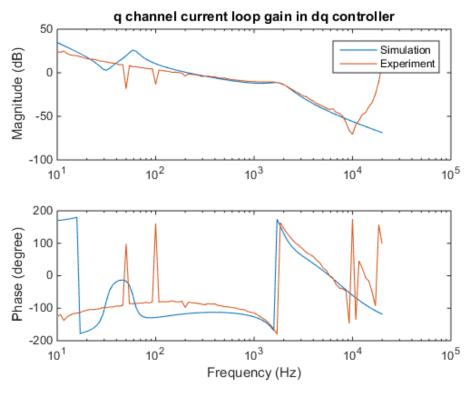

| Figure IV-35 q channel current loop gain in D-Q controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 62 |

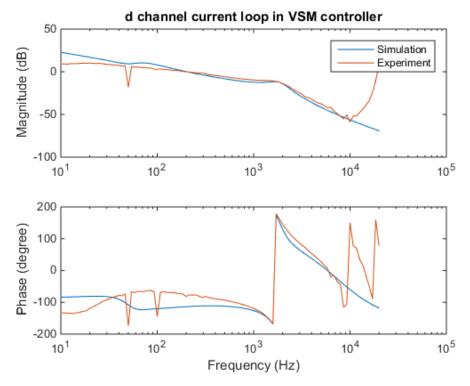

| Figure IV-36 d channel current loop gain in VSM controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 63 |

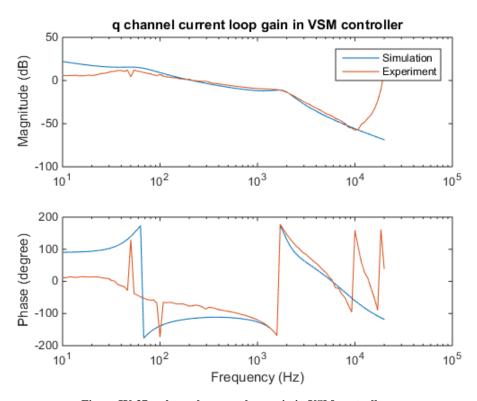

| Figure IV-37 q channel current loop gain in VSM controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 63 |

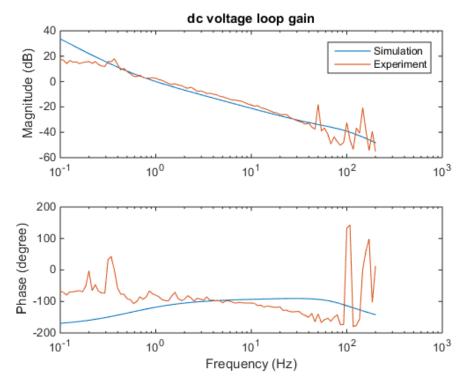

| Figure IV-38 dc voltage loop gain in D-Q controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 64 |

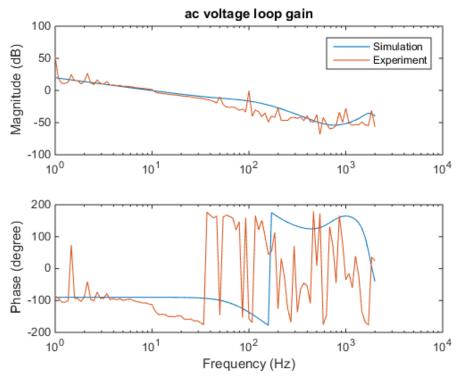

| Figure IV-39 ac voltage loop gain in D-Q controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 64 |

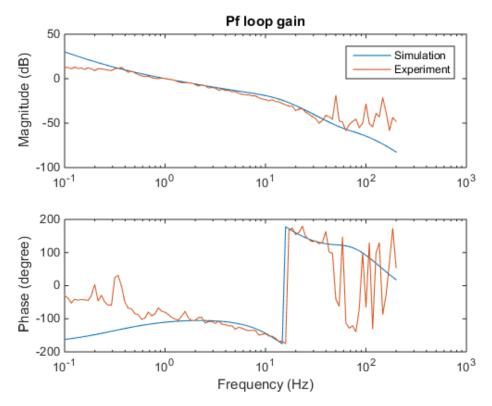

| Figure IV-40 Pf loop gain in VSM controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 65 |

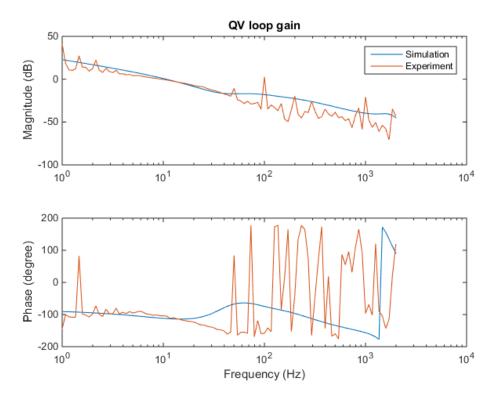

| Figure IV-41 QV loop gain in VSM controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 65 |

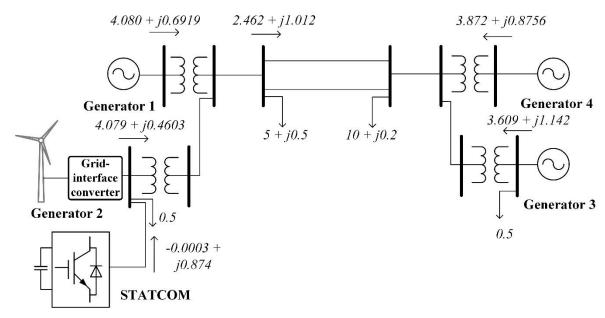

| Figure IV-42 A 4-generator 2-area power system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 66 |

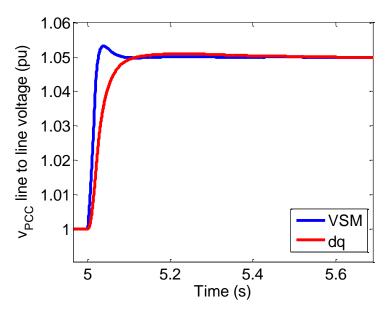

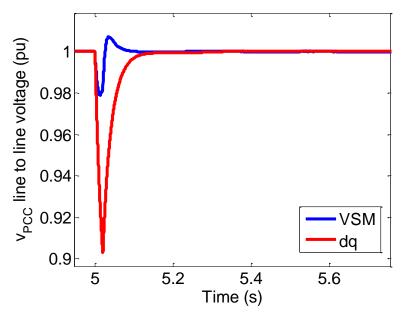

| Figure IV-43 PCC voltage regulation performance when reference changes in a larger system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 67 |

| Figure IV-44 STATCOM output power when reference changes in a larger system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 67 |

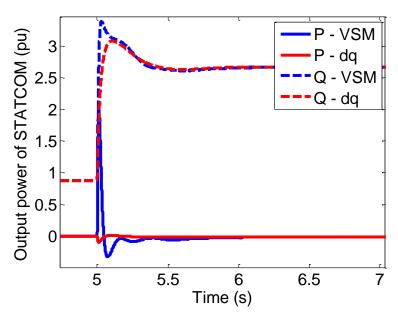

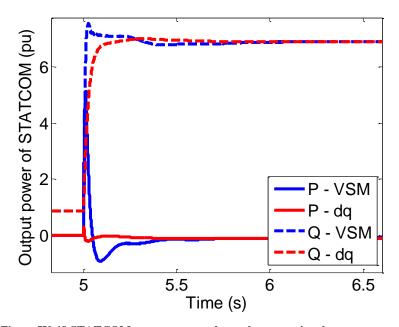

| Figure IV-45 PCC voltage regulation performance when frequency fluctuates in a larger systematic systematic properties of the system |    |

| Figure IV-46 STATCOM output power when frequency fluctuates in a larger system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 68 |

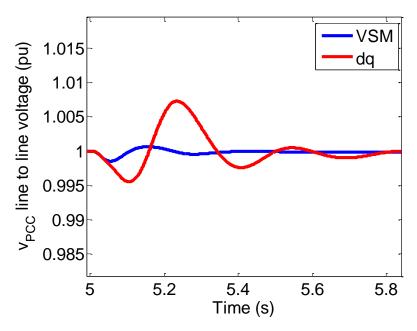

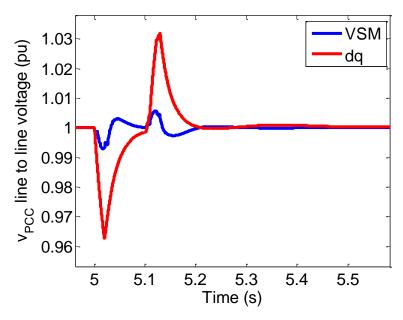

| Figure IV-47 PCC voltage regulation performance when voltage sags in a larger system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 69 |

| Figure IV-48 STATCOM output power when voltage sags in a larger system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 69 |

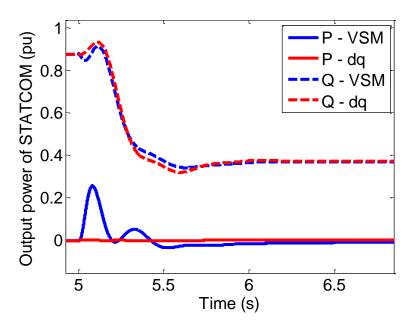

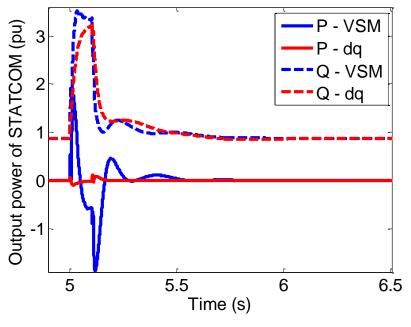

| Figure IV-49 PCC voltage regulation performance during fault in a larger system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 70 |

| Figure IV-50 STATCOM output power during fault in a larger system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 70 |

| Figure V-1 Three-phase fault in the test bed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 73 |

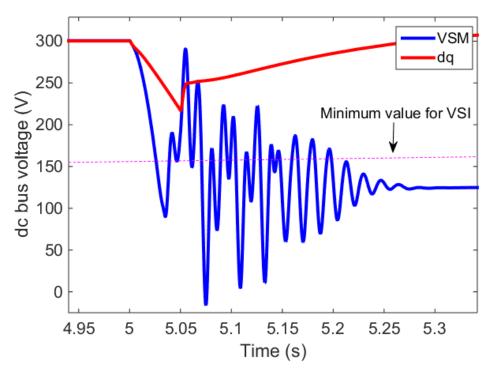

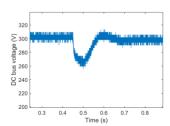

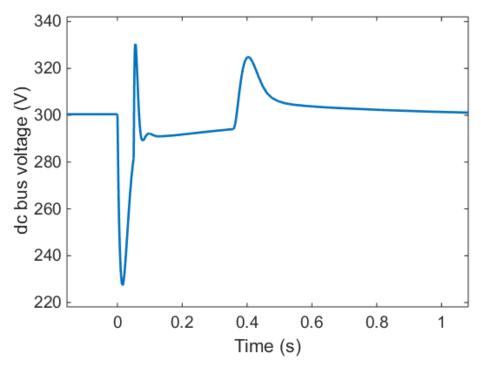

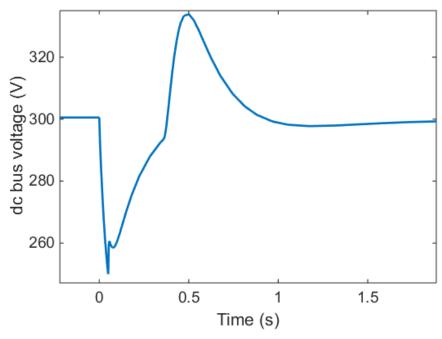

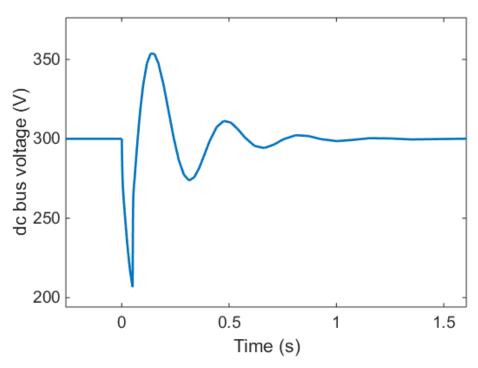

| Figure V-2 Dynamics of dc bus voltage of two controllers under fault                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 74 |

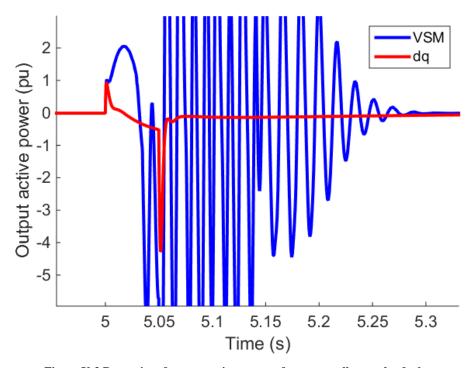

| Figure V-3 Dynamics of output active power of two controllers under fault                 | 74 |

|-------------------------------------------------------------------------------------------|----|

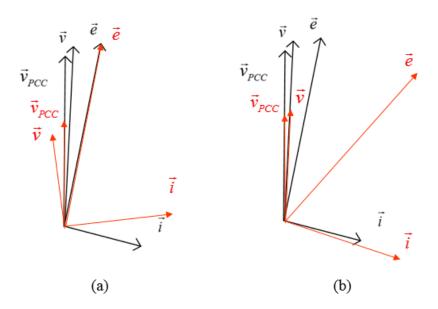

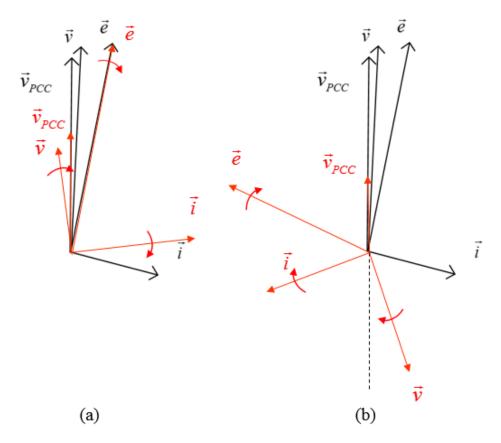

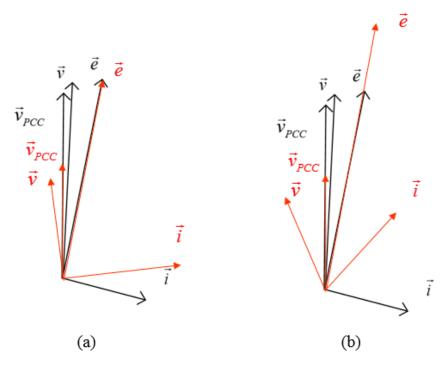

| Figure V-4 Phasor diagrams of VSM-STATCOM during faults                                   | 76 |

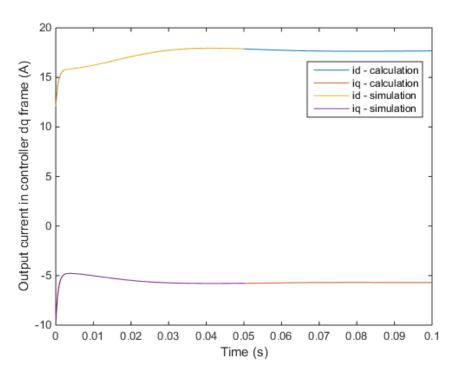

| Figure V-5 Transients of output current in controller D-Q frame during fault with consta  |    |

| Figure V-6 Transients of frequency and phase of back EMF during fault with constant back. |    |

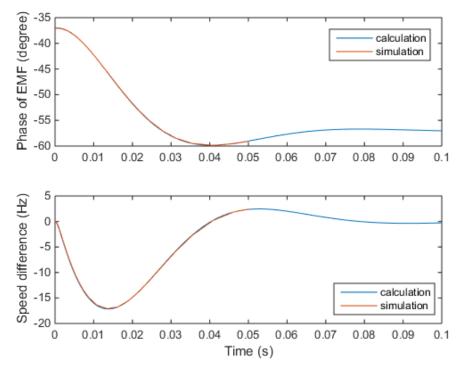

| Figure V-7 Transients of output power during fault with constant back EMF                 |    |

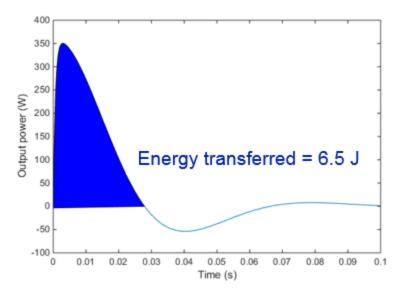

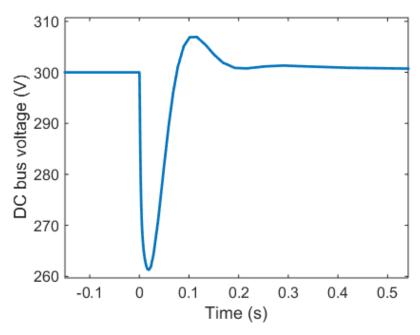

| Figure V-8 Transients of dc bus voltage during fault with constant back EMF               | 80 |

| Figure V-9 Transients of dc bus voltage during large voltage drop                         | 81 |

| Figure V-10 Phasor diagrams of VSM-STATCOM during faults with Pf loop                     | 82 |

| Figure V-11 Phasor diagrams of VSM-STATCOM during faults with QV loop                     | 83 |

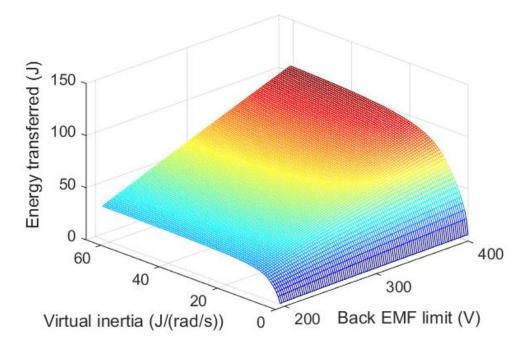

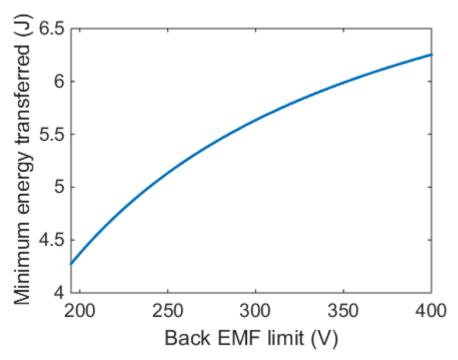

| Figure V-12 Transferred energy as a function of virtual inertia and back EMF limit        | 84 |

| Figure V-13 Minimum transferred energy vs. back EMF limit                                 | 84 |

| Figure V-14 Dynamics of dc bus voltage under fault with 1/5 virtual inertia               | 85 |

| Figure V-15 Dynamics of dc bus voltage under fault with 5 times dc capacitor              | 86 |

| Figure V-16 Dynamics of dc bus voltage under fault with limiters on back EMF              | 86 |

| Figure V-17 Practical VSM control blocks for STATCOM                                      | 88 |

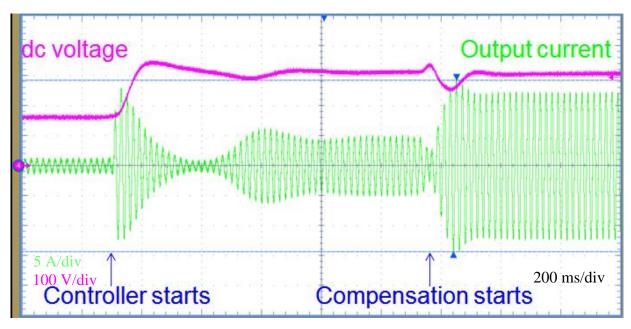

| Figure V-18 Start-up process of VSM-STATCOM.                                              | 92 |

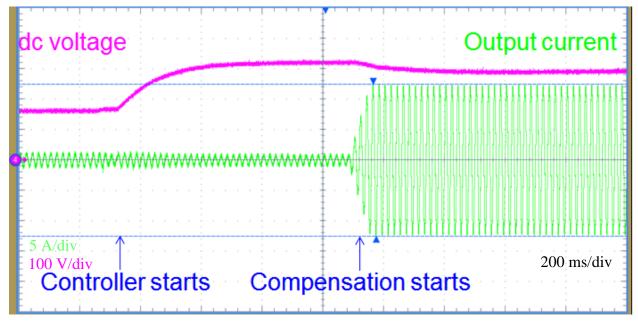

| Figure V-19 Start-up process of DO-STATCOM                                                | 92 |

## LIST OF TABLES

| Table IV-1 Parameters of the test bed in simulation   | 34 |

|-------------------------------------------------------|----|

| Table IV-2 Bandwidths of each loop in two controllers | 45 |

| Table IV-3 Parameters of the prototype test bed       | 53 |

| Table V-1 Start-up procedure for VSM-STATCOM          | 91 |

### **Chapter I. INTRODUCTION**

#### 1.1 Background

Faced with more and more severe environment pollution and fossil resource scarcity, people have been seeking renewable and green energy, wind and solar mainly for now, to increasingly support power generation in the existing power grid. Many countries have promulgated acts and policies to encourage research and deployment of renewable energy and as a result the number of wind and solar farms is growing significantly in recent decades. However, due to less control over renewable sources, the output power can be unpredictable because they are often running in the maximum power point tracking (MPPT) mode. This randomness together with their lack of inertia, or spinning reserve, makes renewable energy not preferable from the grid's point of view due to the potential source-load power imbalance, uncertainty of operation and potentially harsh transients.

Additional compensation is often necessary to ensure a safe and economic operation when connected to the grid; e.g., it is a common solution to use STATCOMs to compensate large wind or solar farms to help the point of common coupling (PCC) voltage regulation and also enhance stability during transients. Compared to other applications of STATCOMs, compensation of renewable energy present interesting challenges not only because of the uncontrollable and random nature of the sources, but also due to the typically weak grid conditions since large wind or solar farms are often located in remote areas. When there is a grid contingency such as sources or loads switching in or out and single-phase or three-phase faults and also when the output power of renewable energy is fluctuating, variation in magnitude and frequency of PCC voltage as well as harmonics and unbalance is often observed, which prevents STATCOMs from tracking the PCC voltage accurately and thus influences the regulation performance of the latter.

In recent years, the virtual synchronous machine (VSM) concept has been introduced [1], as well as virtual synchronous generator (VSG) [2], or synchronverter [3, 4] and power synchronization control [5], inertial emulation [6] and synchronous power controller [7], which controls grid-connected inverters emulating the behavior of conventional

synchronous machines to obtain a better, grid-friendly transient response, and has been proposed primarily as a means to replace d-q frame phase-locked loops (PLL) that oftentimes introduce problems in their operation. Although the main concept proposed is the same in [1-3, 5-10], fundamental aspects and modeling details differ significantly between these approaches as different orders of differential equations of synchronous machines are used [9]. Regardless, the two main benefits of VSM-based control are power-based synchronization, which eliminates the PLL [4] and its potential instability [11], and virtual inertia, which is programmable during disturbances to achieve faster response than physical synchronous machines. As such, the key advantage of VSM type controllers over d-q frame controllers is the way to synchronize, where VSM-type remains inherently in harmony with the electrical system, while the d-q frame controller relies on the PLL to orient its control system and operation. This property prevents VSM type controllers from fighting with each other and running into instability, improves the transient responses when contingencies happen, and can remain stable even under islanding conditions.

There are different approaches of the concept, some using virtual inertia only [1, 2, 5, 6, 10], some adding virtual impedance also [7] and some implementing the full model of a synchronous machine [3]. Virtual impedance and virtual inertia will be implemented in the strategy proposed in this article to make the STATCOM operate as a variable synchronous condenser. With virtual inertia, the STATCOM will naturally synchronize with the grid accurately if there is any change in the frequency without any risks of losing synchronization. Virtual impedance can limit the harmonic produced by the converter itself and also reject that from the system ensuring immunity under harmonic perturbation, where additionally negative sequence impedance can be added to enhance the response in case of unbalanced phase voltages exists in the system; e.g., during asymmetrical faults. In such way, the VSM-based STATCOM will be less sensitive to power or voltage fluctuation induced by renewable energy sources or the grid itself, featuring better synchronization performance and thus achieving an improved voltage regulation than the conventional STATCOM controlled in the d-q frame. Furthermore, the VSM-based STATCOM can actively adapt to different scenarios using its adjustable "virtual" inertia and impedance. Furthermore, the VSM-based STATCOM can actively adapt to different scenarios using its adjustable "virtual" inertia and impedance.

#### 1.2 Synchronization for grid-interfaced converters

For converters that interface with the ac power grid, synchronization is the fundamental task before other functionalities are implemented. In order to work together with each other, the same frequency with appropriate phases is essential either achieved by obtaining phase information from the system or by participating in the frequency regulation.

#### 1.2.1 Phase locked loop

Typically a phase locked loop (PLL) serves to bridge a converter to a power grid, using different mechanics from the way how the dominating synchronous machines or generators stay synchronized in harmony naturally in the existing power system. A synchronous reference frame PLL (SRF-PLL) is easy to use and present a good performance on ideal occasions and many other enhanced PLLs have been proposed to get a better behavior against harmonic and negative component disruption. A traditional way is to use PLL based on synchronous reference frame, which translates the 3-phase sinusoidal voltage in abc frame into dc voltage in d-q frame in the steady state by Park's transformation [12]. A compensator is designed for a feedback loop to regulate the q channel component into zero, as shown in Figure I-1. The structure is simple to implement and however it may present some instability when multiple grid-connected converters are connected together as shown in [11, 13].

Figure I-1 Control blocks of SRF-PLL

#### 1.2.2 Power-balance-based synchronization

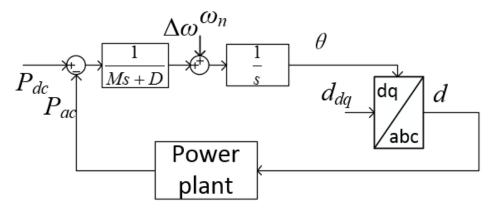

The VSM and other similar concepts share the same method to synchronize, which is derived from the Newton's Law and called swing equation (1) describing the movements of an imaginary rotating shaft in Figure I-2 (a) corresponding to a 3-phase converter in Figure I-2 (b)

$$\frac{d\delta}{dt} = \omega - \omega_n$$

$$M \frac{d\omega}{dt} = P_{dc} - P_{ac} - D(\omega - \omega_n)$$

(1),

where  $\delta$  is known as the power angle,  $\omega$  and  $\omega_n$  are the detected frequency and grid frequency respectively, M and D are virtual angular momentum and virtual damping coefficient,  $P_{dc}$  and  $P_{ac}$  are input active power from dc side and output active power from ac side of the converter respectively. In that sense, the imaginary shaft is rotating at the speed  $\omega$  which is driven by  $P_{dc}$  and braked by  $P_{ac}$ .

Figure I-2 Virtual synchronous machine concept

The dc input power is often a controllable variable and remains constant if no commands are given while the ac output power is determined by the power transfer equation

$$P_{ac} = P_{\text{max}} \sin \delta \qquad (2),$$

where  $P_{max}$  is a constant relative to the operating condition. If  $\omega$  is greater than  $\omega_n$ ,  $\delta$  and thus  $P_{ac}$  will become larger, and then  $\omega$  will be decreased by the unbalance of input and output power, and vice versa. In the steady state, the two power will be equal and the frequency will be eventually the grid frequency and hence the converter is synchronized with the grid. If (1) is implemented in the controller for the converter, the synchronization behavior will be exactly the same with the rotating shaft, showing an emulation of synchronous machines. A basic structure of VSM based controller is depicted as Figure I-3 Control blocks of basic VSM controller with only virtual inertia presented where the transfer function  $G_{plant}$  represents the power transfer equation (2).

Figure I-3 Control blocks of basic VSM controller

#### 1.3 Motivation and outlines

The virtual synchronous machine concepts have been proved in various references [1-3, 5-9] that it shows no worse response than the traditional D-Q frame PLL-oriented controllers and much greater behavior when it comes to islanding mode with the capability to enhance the stability of the power system. Indeed, the main benefits for VSM-controlled grid-interfaced converters are the friendliness to the grid and the ability to participate and even support the grid frequency and voltage. However in existing papers, many researchers have only proposed their concepts lacking in the analysis and insights into the basics of this kind of control methods and basically there is no complete design procedure. There is more to be done to explore the potentials of this methods by playing with programmable parameters which determines the output characteristics under different kinds of transients. It is necessary to look into the state-space equations or transfer functions to know what the impacts from the virtual parameters is.

Additionally, most of the papers are focused on inverters with the dc side connected with either PV panels, battery systems or HVDC ends [6, 14-20], while only one [21] has applied the idea to STATCOM but no details have been offered. The benefits of using VSM control in the STATCOM application over the conventional D-Q frame one has yet to be shown to demonstrate the advantages.

In such, the thesis will go as the following:

Chapter 2 gives an introduction of STATCOMs. The basic operation, conventional control schemes, typical applications and common topologies are presented.

Chapter 3 offers a review of virtual synchronous machine control concept and classifies all methods based on their control structure. Some existing applications are also provided.

Chapter 4 explains the VSM control application to STATCOM and offers small signal analysis given operating points based on proposed two D-Q frames, namely the system D-Q frame and the controller D-Q frame. From that the transfer functions can be obtained and parameter choices can be made with comparison with conventional D-Q frame controllers in both frequency and time domain. The VSM controlled STATCOM shows similar voltage regulation performance when there is only voltage variation in the system but a much better performance when the frequency is fluctuating. The design rules are based on trade-offs. Then a prototype STATCOM with both VSM and D-Q frame controller implemented. The control methods are verified in the hardware experiments. Without a synchronous generator running, the tests are limited with voltage fluctuation being the only case conducted. Also a larger power system with 4 generators divided into 2 areas with 2 tie lines connected where the power system is more practical to study the influence of the VSM controller. Similarly transient responses are compared between VSM and D-Q frame controllers and the same conclusion is extended to this test case.

Chapter 5 first describes a possible issue of the VSM controller during large transients, which is intrinsic in this control method and may lead to voltage collapse. A phasor explanation is given to show the nature behind and analytical analysis based on non-linear differential equations is provided to predict possible phenomenon. Moreover, some feasible solutions are proposed and compared to overcome the limitation of the VSM controller. This chapter is an addition to Chapter 2 as a consideration of large transients as well as a must to check if the STATCOM can sustain after given faults.

The last chapter summaries the work and discusses some possible future work.

# Chapter II. BASICS OF STATIC SYNCHRONOUS COMPENSATORS

#### 2.1 Basic operation of STATCOM

This kind of advanced compensator is based on converter composed of force-commutated power electronic devices and topology, first proposed by Gyugyi in 1979 [22]. Although the DC source of STATCOM can be both current and voltage, the most practical and used one is voltage source converter (VSC), shown in Figure II-1, along with its basic operation mode.

Figure II-1 Basic concept of STATCOM: (a) basic topology of STATCOM; (b) inductive mode; (c) capacitive mode

The VSC-STATCOM generates an AC voltage  $V_e$  V<sub>e</sub>and shunt connects to the bus with the voltage  $V_b$  V<sub>b</sub> via an equivalent inductance  $X_e$ X<sub>e</sub>, which is often the leakage inductance of a transformer, where all the values are reflected to the primary side of a transformer. By controlling the output voltage of the converter by either firing angles or DC link voltage, it is easy to obtain a continuously controllable  $V_e$  V<sub>e</sub> to control the compensating current and thus the reactive power compensation. The capacitor at DC side can be regarded as a reactive power source in a STATCOM. In practical applications, the losses of a STATCOM are compensated by the power system, that is, the STATCOM will