### An Access Layer Protocol for Parallel Networks

by

### Rajesh Kumar

Thesis submitted to the Faculty of the

Virginia Polytechnic Institute and State University

in partial fulfillment of the requirements for the degree of

Master of Science

in

Electrical Engineering

**APPROVED**

Dr. S. F. Midkiff, Chairman

Dr. N. J. Davis, IV

Dr. I. Jacobs

May 1993

Blacksburg, Virginia

C.2

5655

V855

1993

K863

C.2

### An Access Layer Protocol for Parallel Networks

by

#### Rajesh Kumar

Dr. S. F. Midkiff, Chairman

### Electrical Engineering

#### (ABSTRACT)

Parallelism can be applied to local area networks to achieve higher data rates using existing hardware technologies. Parallelism can be employed at the different layers of the Open Systems Interconnection (OSI) reference model. This research proposes and analyzes a technique that permits the use of different degrees of parallelism at different protocol layers. A new protocol layer, called the *access layer* is defined. The protocol and functionality for this layer are defined. The definitions make provision for incorporating an error correction coding procedure known as *cross channel coding*. A software simulator was built for the proposed parallel network. The simulator has a detailed model of the access layer and was used to verify the functionality defined for the access layer and to estimate the performance of the parallel network. The simulation results indicate that although the access layer processes data in serial, it is not a bottleneck in the parallel system. Other insights obtained from the experiments are also presented.

## Acknowledgments

I would like to express my sincere gratitude to my major professor, Dr. S. F. Midkiff for his willing assistance and guidance throughout my program of study. I am also grateful for the direction he provided my research work, without which it would have been very difficult to complete this thesis.

A special thanks to Dr. I. Jacobs and Dr. N. J. Davis, IV, for their helpful suggestions and for serving on my committee.

Many thanks to Scott Harper and Joe Wiencko for their help and to my friend, Raj Kumar, for his encouragement.

I am grateful for the employment at the Forestry department which helped sustain my studies when other sources were lacking.

Finally, I would to thank my family, Achan, Amma and Akkan, whose encouragement and prayers have made it all possible.

Acknowledgments

# Table of Contents

| Acknowled     | gments                                  | iii |

|---------------|-----------------------------------------|-----|

| Table of Co   | ontents                                 | iv  |

| List of Illus | trations                                | vii |

| List of Tab   | les                                     | ix  |

| Chapter 1.    | Introduction                            | 1   |

|               | Motivation                              |     |

| 1.2.          | Research                                | 2   |

| 1.3.          | Organization of the Thesis              | 4   |

| Chapter 2.    | Background and Literature Review        | 5   |

|               | Gigabit Local Area Networks             |     |

| 2.2.          | Motivation for the Use of Parallelism   | 6   |

| 2.3.          | Related Work                            | 7   |

|               | Overview of Proposed Parallel Network   |     |

|               | Access Layer Architecture               |     |

| Chapter 3.    | The Access Layer                        | 16  |

| 3.1.          | Need and Required Functionality         | 16  |

| 3.2.          | The AL Protocol                         | 17  |

|               | 3.2.1. Cross Channel Coding             | 17  |

|               | 3.2.2. Definitions and Terminology      | 19  |

|               | 3.2.3. Transmission of Data             | 24  |

|               | 3.2.4. Reception of Data                | 42  |

| 3.3.          | Implications of CCC                     | 51  |

| Chapter 4.    | A Simulator for the Access Layer        | 55  |

|               | Objectives of the Simulator             |     |

| 4.2.          | Simulation Scheme                       | 56  |

|               | 4.2.1. Type of Simulator                | 56  |

|               | 4.2.2. Design Approach                  |     |

|               | 4.2.3. High-Level View of the Simulator |     |

| 4.3.          | Choice of Components                    |     |

|               | 4.3.1. The Common Bus                   |     |

|                      | 4.3.2. Data Link Layer Standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60                             |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

|                      | 4.3.3. CCC/CCD Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 61                             |

| 4.4.                 | Models for System Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 61                             |

|                      | 4.4.1. Application Layer Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 61                             |

|                      | 4.4.2. Processor (PPs and ALP) Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 62                             |

|                      | 4.4.3. M Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 62                             |

|                      | 4.4.4. Shared Memory Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 63                             |

|                      | 4.4.5. FDDI Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 64                             |

| 4.5.                 | Timing Assumptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65                             |

|                      | 4.5.1. M Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                |

|                      | 4.5.2. FDDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                |

|                      | 4.5.3. Protocol Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                |

|                      | 4.4.4. Access Layer Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                |

|                      | 4.4.5. CCC/CCD Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                |

| 4.6.                 | Implementation of Node Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 68                             |

|                      | 4.6.1. Transfer of Data from Application to Transport/Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                |

|                      | Layers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                |

|                      | 4.6.2. Data Sufficiency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                |

|                      | 4.6.3. The Splitting Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                |

|                      | 4.6.4. M Bus: Enqueueing and Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                |

|                      | 4.6.5. FDDI Token Rotation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 75                             |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                |

|                      | 4.6.6. Transfer of Data from AL to Transport/Network layers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                |

| Chapter 5.           | 4.6.6. Transfer of Data from AL to Transport/Network layers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 76                             |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 76<br>77                       |

| 5.1.                 | 4.6.6. Transfer of Data from AL to Transport/Network layers  Simulation Experiments and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 76<br>77                       |

| 5.1.                 | 4.6.6. Transfer of Data from AL to Transport/Network layers  Simulation Experiments and Results  Objective and Measured Quantities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 767777                         |

| 5.1.                 | 4.6.6. Transfer of Data from AL to Transport/Network layers  Simulation Experiments and Results  Objective and Measured Quantities  System Configuration and Monitoring Methods for Experiments  5.2.1. System Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 76777878                       |

| 5.1.<br>5.2.         | 4.6.6. Transfer of Data from AL to Transport/Network layers  Simulation Experiments and Results  Objective and Measured Quantities  System Configuration and Monitoring Methods for Experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 76777878                       |

| 5.1.<br>5.2.         | 4.6.6. Transfer of Data from AL to Transport/Network layers  Simulation Experiments and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7677787879                     |

| 5.1.<br>5.2.         | 4.6.6. Transfer of Data from AL to Transport/Network layers  Simulation Experiments and Results Objective and Measured Quantities  System Configuration and Monitoring Methods for Experiments 5.2.1. System Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 767778787980                   |

| 5.1.<br>5.2.         | 4.6.6. Transfer of Data from AL to Transport/Network layers  Simulation Experiments and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 76777878798080                 |

| 5.1.<br>5.2.         | 4.6.6. Transfer of Data from AL to Transport/Network layers  Simulation Experiments and Results Objective and Measured Quantities  System Configuration and Monitoring Methods for Experiments 5.2.1. System Configuration 5.2.2. Monitoring Methods and Steady State Detection Experimental Cases                                                                                                                                                                                                                                                                                                                                                                                                                                | 7677787879808183               |

| 5.1.<br>5.2.         | 4.6.6. Transfer of Data from AL to Transport/Network layers  Simulation Experiments and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7677787879808183               |

| 5.1.<br>5.2.         | 4.6.6. Transfer of Data from AL to Transport/Network layers  Simulation Experiments and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7677787980818383               |

| 5.1.<br>5.2.         | 4.6.6. Transfer of Data from AL to Transport/Network layers  Simulation Experiments and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 76777878798080818383           |

| 5.1.<br>5.2.<br>5.3. | 4.6.6. Transfer of Data from AL to Transport/Network layers  Simulation Experiments and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7677787879808183838484         |

| 5.1.<br>5.2.<br>5.3. | 4.6.6. Transfer of Data from AL to Transport/Network layers  Simulation Experiments and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7677787879808183838484         |

| 5.1.<br>5.2.<br>5.3. | 4.6.6. Transfer of Data from AL to Transport/Network layers  Simulation Experiments and Results Objective and Measured Quantities System Configuration and Monitoring Methods for Experiments 5.2.1. System Configuration 5.2.2. Monitoring Methods and Steady State Detection Experimental Cases 5.3.1. Parameters Varied for the Study 5.3.2. Base Case 5.3.3. Cases 2 and 3: Packet Size 5.3.4. Cases 4, 5 and 6: Destination 5.3.5. Cases 7 and 8: CCC m Parameter 5.3.6. Cases 9 and 10: Data Sufficiency 5.3.7. Case 11: Distributing Packets with No CCC Experimental Results and Implications 5.4.1. Base Case: Utilization Results 5.4.2. Cases 2 and 3: Packet Size                                                     | 7677787980818383848484         |

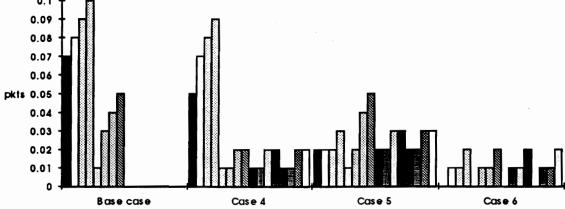

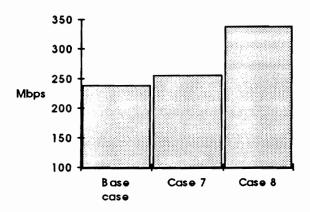

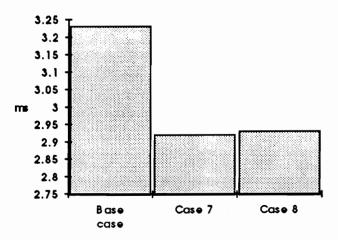

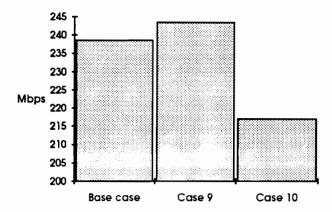

| 5.1.<br>5.2.<br>5.3. | 4.6.6. Transfer of Data from AL to Transport/Network layers  Simulation Experiments and Results Objective and Measured Quantities System Configuration and Monitoring Methods for Experiments 5.2.1. System Configuration 5.2.2. Monitoring Methods and Steady State Detection  Experimental Cases 5.3.1. Parameters Varied for the Study 5.3.2. Base Case 5.3.3. Cases 2 and 3: Packet Size 5.3.4. Cases 4, 5 and 6: Destination 5.3.5. Cases 7 and 8: CCC m Parameter 5.3.6. Cases 9 and 10: Data Sufficiency 5.3.7. Case 11: Distributing Packets with No CCC  Experimental Results and Implications 5.4.1. Base Case: Utilization Results 5.4.2. Cases 2 and 3: Packet Size 5.4.3. Cases 4, 5 and 6: Destination Distribution | 76777878798081838384848687     |

| 5.1.<br>5.2.<br>5.3. | 4.6.6. Transfer of Data from AL to Transport/Network layers  Simulation Experiments and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 767778787980818383848686869097 |

| 5.1.<br>5.2.<br>5.3. | 4.6.6. Transfer of Data from AL to Transport/Network layers  Simulation Experiments and Results Objective and Measured Quantities System Configuration and Monitoring Methods for Experiments 5.2.1. System Configuration 5.2.2. Monitoring Methods and Steady State Detection  Experimental Cases 5.3.1. Parameters Varied for the Study 5.3.2. Base Case 5.3.3. Cases 2 and 3: Packet Size 5.3.4. Cases 4, 5 and 6: Destination 5.3.5. Cases 7 and 8: CCC m Parameter 5.3.6. Cases 9 and 10: Data Sufficiency 5.3.7. Case 11: Distributing Packets with No CCC  Experimental Results and Implications 5.4.1. Base Case: Utilization Results 5.4.2. Cases 2 and 3: Packet Size 5.4.3. Cases 4, 5 and 6: Destination Distribution | 767778787980818383848486879097 |

Table of Contents

| 5.5.       | Verification of CCD Functionality         | 105 |

|------------|-------------------------------------------|-----|

|            | Summary                                   |     |

| Chapter 6. | Conclusion                                | 108 |

|            | Research Summary                          |     |

|            | Suggestions for Further Research          |     |

| References |                                           | 112 |

| Appendix A | A. Cross Channel Coding Equations         | 116 |

|            | Notation                                  | 116 |

|            | Encode Equations                          |     |

|            | Decode Equations                          |     |

| Appendix I | B. System Parameters and Timing Estimates | 120 |

| Appendix ( | C. Simulation Results                     | 122 |

| Vita       |                                           | 127 |

|            |                                           |     |

# List of Illustrations

| Figure 2.1. Proposed parallel network                                             |

|-----------------------------------------------------------------------------------|

| Figure 2.2. Parallel network node implementation                                  |

| Figure 3.1. Data request format                                                   |

| Figure 3.2. AL header format                                                      |

| Figure 3.3. Data indication format                                                |

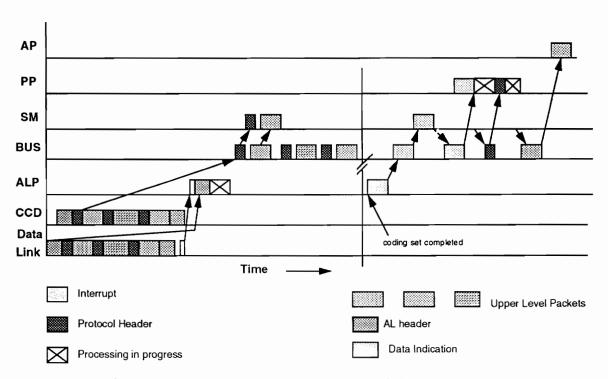

| Figure 3.4. Graphical representation of data transmission                         |

| Figure 3.5. Sub-fields of the SERV_CLASS field                                    |

| Figure 3.6. COMP field for Example 3.1                                            |

| Figure 3.7. SERV_CLASS field for Example 3.1                                      |

| Figure 3.8. Graphical representation of data reception                            |

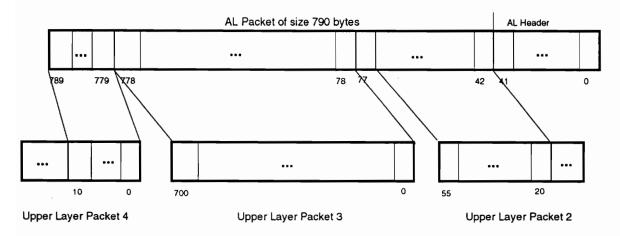

| Figure 3.9. Reconstruction of upper layer packets in Example 3.2                  |

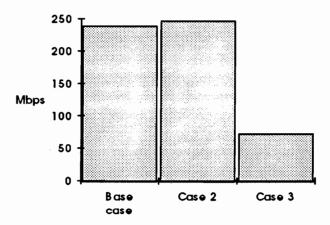

| Figure 5.1a. Throughput for base case and cases 2 and 3                           |

| Figure 5.1b. Packet latency for base case and cases 2 and 3                       |

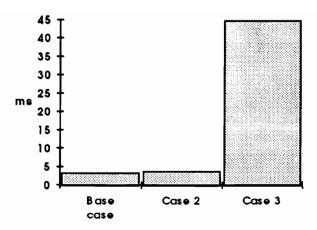

| Figure 5.2. Utilization Results for Base Case and Cases 2 and 3                   |

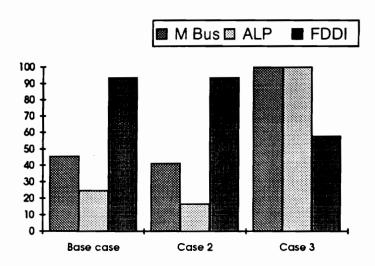

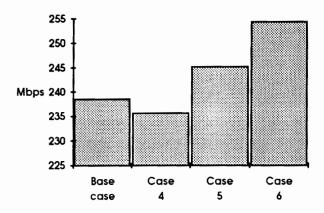

| Figure 5.3a. Throughput for base case and cases 4, 5, and 6                       |

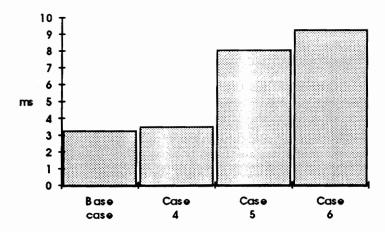

| Figure 5.3b. Packet latency for base case and cases 4, 5, and 6                   |

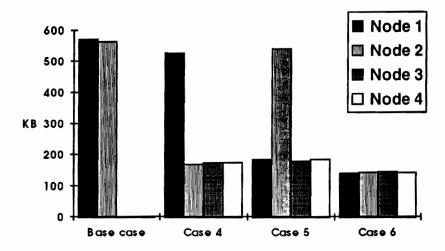

| Figure 5.4a. Average size of shared memory for base case and cases 4, 5, and 694  |

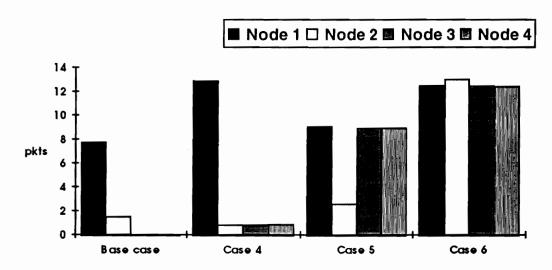

| Figure 5.4b. Average size of FDDI transmit queues for the base case and cases 495 |

| Figure 5.4c. Average size of FDDI receive queues for base case and cases 4, 597   |

| Figure 5.5a. Throughput for base case and case 7 and 8                            |

| Figure 5.5b. Packet latency for base case and cases 7 and 8                       |

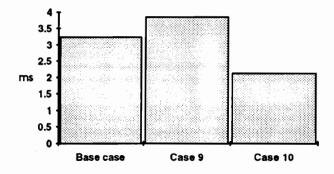

| Figure 5.6a. Throughput for base case and cases 9 and 10                          |

| Figure 5.6b. Packet latency for base case and cases 9 and 10                      |

List of Illustrations vii

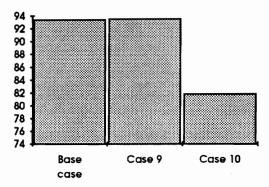

| Figure 5.7. Percentage utilization of FDDI rings for base case and cases 9 and 10 | 102 |

|-----------------------------------------------------------------------------------|-----|

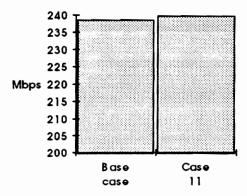

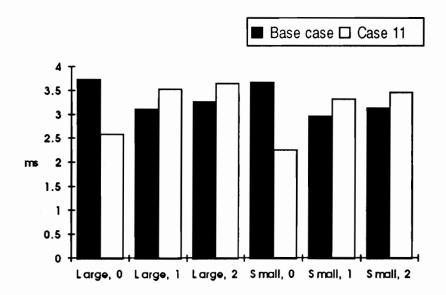

| Figure 5.8a. Throughput for base case and case 11                                 | 103 |

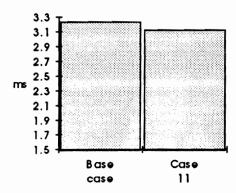

| Figure 5.8b. Latency for base case and case 11.                                   | 103 |

| Figure 5.9. Packet latency from Table 5.12.                                       | 104 |

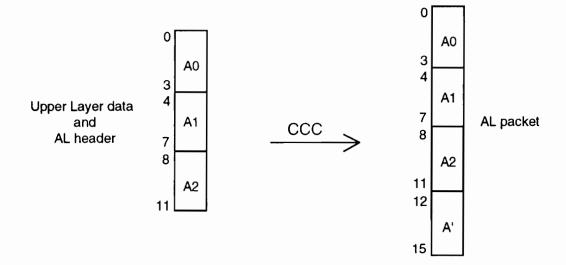

| Figure A.1. Addition of CCC code bits to form an AL packet for m = 1              | 117 |

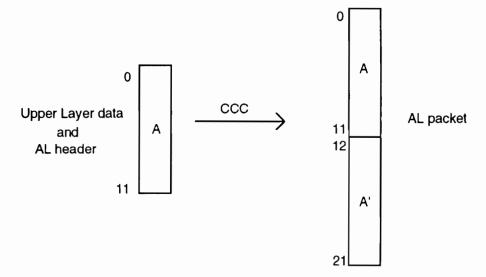

| Figure A.2. Addition of CCC bits to form an AL packet for m = 2                   | 118 |

List of Illustrations viii

# List of Tables

| Table 5.1. Parameters for Each Case                                          | 85    |

|------------------------------------------------------------------------------|-------|

| Table 5.2a. M Bus and ALP Utilization for the Base Case                      | 86    |

| Table 5.2b. Utilization of FDDI Rings for the Base Case                      | 86    |

| Table 5.3. Throughput and Latency for Base Case and Cases 2 and 3            | 87    |

| Table 5.4. Utilization Results for Base Case and Cases 2 and 3               | 89    |

| Table 5.5. Throughput and Latency for Base Case and Cases 4, 5 and 6         | 91    |

| Table 5.6. Utilization of FDDI Rings for Base Case and Cases 4, 5, and 6     | .92   |

| Table 5.7a. Average Size of the Shared Memory in KB for the Base Case        | .93   |

| Table 5.7b. Average Length, in Number of Packets, of FDDI Transmit Queues    | .95   |

| Table 5.7c. Average Length, in Number of Packets, of the FDDI Receive Queues | .96   |

| Table 5.8. Throughput and Latency for Base Case and Cases 7 and 8            | .98   |

| Table 5.9. Throughput and Latency for the Base Case and Cases 9 and 10       | . 100 |

| Table 5.10. Utilization of FDDI Rings for Base Case and Cases 9 and 10       | . 101 |

| Table 5.11. Throughput and Latency for the Base Case and Case 11             | . 103 |

| Table 5.12. Latencies Based on Packet Type for the Base Case and Case 11     | . 104 |

| Table B.1. Timing Estimates for Simulation Experiments                       | . 121 |

| Table C.1. Latency and Throughput                                            | . 122 |

| Table C.2. Packet Latency (ms) for Different Packet Classes                  | . 123 |

| Table C.3. Utilization of the M Bus                                          | . 123 |

| Table C.4. Utilization of the ALP                                            | . 123 |

| Table C.5. Utilization of FDDI Rings                                         | . 124 |

| Table C.6. Average and maximum shared memory sizes                           | . 124 |

| Table C.7. Maximum FDDI Transmit Queue Lengths                               | . 124 |

List of Tables

| Table C.8a. Average FDDI Transmit Queue Lengths | 125 |

|-------------------------------------------------|-----|

| Table C.8b. Average FDDI Transmit Queue Lengths | 125 |

| Table C.9. Maximum FDDI Receive Queue Lengths   | 125 |

| Table C.10a. Average FDDI Receive Queue Lengths | 126 |

| Table C 10h Average FDDI Receive Queue Lengths  | 126 |

List of Tables x

## Chapter 1. Introduction

One strategy to meet the demand for higher data rate computer networks is to use parallelism. A joint project between Virginia Tech and Old Dominion University investigated the use of parallelism in local area networks. The research described in this thesis proposes and analyzes a technique that permits the use of different degrees of parallelism at different network protocol layers. A new protocol layer, called the *access layer* (AL) is defined. The protocol and functionality for this layer are defined. A software simulator was built for the proposed parallel network. This simulator was used to verify the functionality of the AL and to obtain performance measures for the entire parallel network.

#### 1.1. Motivation

A number of different strategies are being used to meet the growing demand for higher data rate networks. Most strategies depend on the development of new transmission technologies. One strategy that can make use of currently available technology is to exploit parallelism in computer networks. Apart from the gain in bandwidth, parallelism can also provide improved fault tolerance, scalability and flexibility over a serial approach. Parallelism can be used at the different protocol layers of the OSI reference model. The parallel network project [1] proposed the use of parallelism at the software-intensive

upper-layers and at the hardware-intensive lower-layers. Multiple "protocol processors" can be used at the upper layers, while multiple channels can be used at the data link layer.

To achieve the full benefits of parallelism, the parallelism at the upper and lower layers should be transparent to each other. A mechanism is then needed to map between the parallelism at these layers. The access layer (AL) is such a mechanism. The AL is positioned between the network and data link layers of the OSI protocol stack.

The AL is a serial operating point in the parallel network. Therefore, it has the potential to be a system bottleneck. A major goal in specifying the AL functionality is to ensure that the AL does not become a bottleneck.

#### 1.2. Research

The first objective of this research was to define the AL protocol and associated functionality for the proposed parallel network. The definition had to satisfy a number of criteria. In keeping with the layered approach, the AL protocol must make no, or few, assumptions of the protocol at the adjacent layers. The AL functionality also had to include a means for using an error correction coding procedure known as *cross channel coding* [2]. The second part of the research was to verify the defined functionality and to study the impact of the AL on the performance of the network.

The AL functionality was defined in two stages. In the first stage the transmission of packets from the upper layers was considered. The second stage developed the steps for processing frames received over the physical channels. The IEEE 802 [5] standards were used as a guide in defining the AL protocol. Criteria such as conforming with existing standards, providing for future needs and the potential for efficient implementation were

considered when making decisions such as address widths and header sizes. A software simulator was built for verification and performance estimation. The writing of this simulator often went in parallel with the protocol definition phase. The simulator models one implementation of the entire proposed parallel network. It contains a detailed model of the AL that facilitates functional verification. Parameters such as throughput, latency and utilization are monitored on an end-to-end basis for obtaining performance measures.

The twin objectives of defining the AL protocol and verifying its functionality were achieved. The protocol definition was in terms of a specification of the steps to perform during transmission and reception of packets. The simulator was used to verify the AL functionality. Performance measures were obtained for a prototype of the proposed parallel network.

Analyses of the performance results indicated that the AL was not the bottleneck for most of the cases considered by the simulation experiments. The AL appeared to be the bottleneck only when the average packet size became very small. Larger packet sizes were found to be better for higher throughput and lower latency. Packets are classified according to the destination node and a cross channel coding parameter called "m." The average packet latency was reduced, without affecting throughput, if the total number of such classes was reduced. Whenever cross channel coding is used, packets are split over all available physical channels. When it is not used, packets can be sent without splitting them equally over all channels. However, the additional complexity due to unbalanced loading of the physical channels was not found to justify the gains from such a strategy.

### 1.3. Organization of the Thesis

This chapter has provided a brief introduction to the research. Chapter 2 discusses background relevant to the research, including a discussion of the parallel network project and the architecture of the AL. The chapter also includes a survey of relevant literature. The next chapter presents and discusses the AL protocol and functionality in detail. The functionality for the transmission and reception of packets is discussed separately and examples are provided. Chapter 4 discusses the simulator that was developed to study the AL. The models for the various system components and functions are discussed. A discussion of simulation experiments and results is presented in Chapter 5. The implications of the results are also examined. The final chapter provides a summary and some suggestions for further research.

Appendix A provides the expressions for cross channel coding and decoding for the particular case studied in the simulation experiments. Appendix B lists the relevant parameters of the devices used in the simulator and the timing estimates used in the performance studies. Appendix C provides complete results for the simulation experiments.

## Chapter 2. Background and Literature Review

This chapter presents background and a review of the current literature. It begins with a short discussion on gigabit networks. The motivation for the use of parallelism as the basis for building a gigabit network is presented next. This is followed by a literature review. The fourth section provides an overview of the proposed parallel network and the concluding section discusses the architecture chosen for the access layer.

### 2.1. Gigabit Local Area Networks

There is a trend towards local area networks (LANs) with throughputs of 1 Gbps or greater [15]. A significant number of applications have been identified for such LANs. These include serving as high-speed LAN backbones, enabling a network-based high performance computing environment and permitting large-scale distributed computing [7, 8].

Building a gigabit LAN is not a simple matter of scaling an existing system. They demand a totally new approach [6, 8]. In long-haul gigabit networks, the propagation delay, rather than the capacity of the network, dominates the response time. Kleinrock [6] suggests that this latency be hidden by adopting parallel processing or pipelining at the application layer. Propagation delay is, however, not very significant for LANs since the links are much shorter. Kung [8] identifies several problems specific to gigabit LANs. These

include highly bursty traffic and increased mismatches in bandwidth of the network and the host connections to the network. Additional requirements for gigabit LANs are low-latency communication and robust performance. Clearly, new approaches and techniques are needed to make gigabit LANs feasible. One such approach is to use parallelism.

### 2.2. Motivation for the Use of Parallelism

The standard approach for increasing data rates is to use new technologies to develop faster networks. However, the limitations of this are well known from the design of general purpose computers [16]. An approach with greater potential is the use of parallelism in the network nodes and in the network itself. This provides the potential for large increases in network bandwidth in a manner similar to how parallel computing techniques are used to achieve dramatic advances in computational power.

Apart from bandwidth gains, the use of parallelism gives the network greater flexibility, scalability and fault-tolerance. Some nodes in a network may need only a fraction of the total network capacity. These nodes can use fewer parallel components to satisfy their requirements. Such a node can satisfy future needs for increased capacity by adding more components. This kind of flexibility is either not possible or is very difficult with monolithic systems. Using a similar strategy of adding more components, it is possible to scale the entire network upwards. The degree of parallelism used will change, while the basic network architecture remains the same.

Parallel systems are inherently more reliable than serial systems. If properly designed, a parallel system will fail only when all of the parallel components at some point have failed.

A parallel system can continue to function at partial capacity when some components fail, instead of totally collapsing. In other words, the use of parallelism makes "graceful degradation" possible. In a serial system, the failure of even one component usually causes the entire system to fail.

Parallel networks can also use layering, and parallelism can be introduced at different network layers. Such networks need mechanisms to make the parallelism at each layer transparent to that at adjacent layers. When such techniques are used, parallel networks can take advantage of technology advances at a particular layer as easily as monolithic networks.

#### 2.3. Related Work

A review of related literature is presented in this section. The discussion begins with an alternative to parallelism for building gigabit LANs. This is followed by reviews of several efforts aimed at achieving Gbps rates for transport protocol processing. The final area considered is network access methods for high-speed LANs.

Kung [8] explains why traditional methods in network analysis and design may not be applicable to gigabit LANs. Kung believes that the limited capacity of a shared-medium architecture, such as a bus or a ring, is not suitable for gigabit LANs. The solution he proposes is a switch-based architecture, much like the existing telephone network. Other key features are fast congestion notification by providing feedback from the points of congestion, link-by-link flow control, rather than end-to-end flow control, and cell-level multiplexing. Cell-level multiplexing involves splitting large data packets into small *cells*. This enables small, higher priority packets to be transferred with low latencies even when

they are sent behind a large data packet. This switch-based approach is a radical shift from the traditional one, and, as Kung points out, needs to be validated before implemented. An important point is that the implementation of this proposal requires that several new standards be established, including the specification of interfaces to existing standards.

The access layer defined in this thesis assumes the availability of a transport layer which can handle gigabit rates. There are two practical approaches to develop a transport protocol implementation that can handle these rates [12]. These are to develop a dedicated hardware solution for a specific protocol [11] or to use parallel processing [1, 12, 10].

A multiprocessor architecture is proposed by Zitterbart [10] for implementing OSI transport layer protocols at Gbps rates. The author discusses the concept of division of the protocol layers into horizontal sub-layers. Each layer is divided into two parts: a *send part* which is responsible for the data transfer from layer (N + 1) to layer (N - 1), and a *receive part* which transfers data from layer (N - 1) to layer (N + 1). Each part is implemented on separate microprocessors and can function independent of each other. Simulation results for a prototype implementation of the OSI TP4 transport layer protocol are presented. Speed-ups of up to seven times over a single processor implementation were obtained. This approach requires significant amount of special-purpose hardware. However, given that hardware intensive solutions are becoming less expensive, the particular methods presented in this paper are promising.

Another scheme that uses parallel processing to achieve transport protocol processing at Gbps rates is presented by Jain, Schwartz and Bashkow [12]. The authors propose a multiprocessor architecture that assumes hardware support to perform any lower layer

protocol processing. The parallelism is at the packet level. A processor-pool is used for processing the transport protocol and each processor has a local memory into which the next packet to be processed is written. Packets are scheduled on these processors in a deterministic manner. A shared memory is used to maintain global state information. Since the packets are stored in local memory, there is not much contention for shared memory access. High-speed buses are assumed between the transport layer processor-pool and the low-level processors which interface to the network. A detailed throughput and delay analysis is presented in the paper which indicates that the proposed architecture will meet the performance requirements for processing received packet at 1 Gbps. The authors suggest that transmission processing at Gbps rates will be possible with four additional processors and modest extensions to the architecture

A hardware-intensive approach is taken by Kanakia and Cheriton [11]. The authors present the design of a network adapter board (NAB) that implements key transport protocol functions in special purpose hardware. The NAB interfaces to the host processor and to the network. Even with special purpose hardware, the NAB uses parallelism in the form of pipelining to process the transport protocol. The main components of the NAB are a processor, buffer memory and the packet pipeline. Buffer memory is used to match speeds between the host bus and the network and as a staging area for transmission and reception processing. Dual-port RAM is used for the buffer memory to reduce contention. A prototype using a 68020 processor was built. The throughput of a single data stream at the user level falls short of the expected performance for networks in the 100 Mbps range or higher. The authors estimate that upgrading the prototype to use a high performance processor, such as MIPS RISC processor, would boost the throughput of a single transaction closer to the 100 Mbps range. They believe that further refinements

in the internal network adapter design and possibly host interface and transport protocols are required to push performance to a higher range.

All three approaches described above utilize parallelism in some form to achieve gigabit rates. Fairly strict anderence to the OSI layered model is maintained in all three cases. The interface to the data link layer in each case is suitable for connecting to the access layer that is defined in this thesis.

The access layer assumes the availability of a network adapter to interface to the data link layer. Some approaches in developing adapters for high-speed LANs are now discussed. Rege [13] presents the architecture and implementation of an FDDI adapter. This adapter is designed to meet the ultimate performance goal of transmitting 450,000 packets per second. This is an ultimate goal because the maximum packet carrying capacity of FDDI is 450,000 packets of 28 bytes each. The adapter implements all the functions at the physical layer and a major subset of the functions at the data link layer. It uses a three-stage pipeline to process packets without CPU interference. A ring interface is specified for communicating between the pipelined stages. Rings operate as queues that allow buffering between pipelined stages, enabling these stages to proceed in an asynchronous fashion. The memory subsystem on the adapter consists of the packet buffer memory and a packet memory interface unit. This unit has separate buses to connect to the pre-FDDI ring pipeline stage and to the post-host bus stage. microprocessor subsystem along with local memory forms the intelligent on-board adapter manager (AM). The AM also implements the station management (SMT) functions of the FDDI protocol. One implementation of the adapter architecture is also presented in this paper. This implementation meets the 100 Mbps throughput for transmit and receive streams when the packet size is at least 69 bytes. Below this size, the throughput falls off rapidly.

Ippoliti and Albanese [14] point out that it is not possible, even with custom VLSI implementations, to build a serial media access controller (MAC) for gigabit rates. They propose a parallel MAC to achieve this goal. The physical network is a set of synchronized parallel channels in a fiber optic transmission system. Each channel has a double unidirectional bus topology and a throughput of 139 Mbps. There is a separate MAC entity for each channel. The parallel MAC layer has a fast packet bus (FPB) with the upper-layer service processors. These processors compete for use of the FPB via round-robin arbitration. Every packet from these processors is split over all parallel channels. However, the MAC processing is done on only one channel. The output controller of the adapter splits the packet to be sent among the output buffers of all the channels. Since the channels are synchronized, all fragments of a packet arrive simultaneously at the destination. Hence, it is feasible to reduce overhead by putting the MAC header on only one channel. It must be noted that this MAC connects to a particular physical network. This is in contrast to the access layer which can function with any data link standard.

Martini and Rupprecht [16] point out that a disadvantage of parallel approaches, such as the one used by Ippoliti and Albanese in the Metrocore project [14], is the static distribution of workload. Thus, performance degradation due to temporarily overloaded units cannot be avoided by a dynamic distribution of workload. The authors provide a brief outline of a new parallel network concept based on Petri nets. In their scheme, protocol modules are sequential programs executed on several general purpose microcomputers. They achieve speed-up by taking advantage of all classes of protocol

inherent parallelisms. The access layer, as defined in this thesis, can incorporate dynamic load distribution if network loading information is available to it.

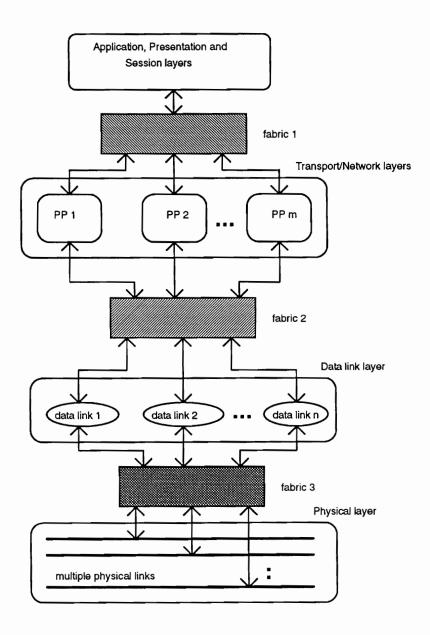

Figure 2.1. Proposed parallel network.

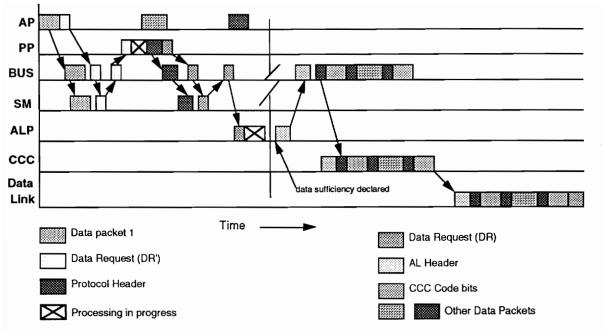

### 2.4. Overview of Proposed Parallel Network

The project which initiated this research proposed the use of parallelism as the basis for building a gigabit LAN. The network, as visualized in the project, is shown in Figure 2.1. The project uses the OSI seven layer model as a reference for specifying the use of parallelism. Parallelism at the application layer is more in the realm of general-purpose computing and is not considered. The first point for introducing parallelism is at the software-intensive upper protocol layers. These include the network, transport, session and presentation layers. In general, however, session and presentation layer processing are not often cleanly separated from the application layer implementations and can be assumed to be executed by the host processor. Transport and network layer protocols involve a significant amount of processing and are sought to be implemented on multiple protocol processors (PPs). Parallelism could be at the connection, packet or process level. The data processed by these parallel PPs are then distributed to multiple entities at the data link layer. This is the second point of parallelism. The data link entities are based on standards such as Ethernet and FDDI. The final point for using parallelism is at the physical layer, where time-division, wavelength-division or space-division multiplexing could be used.

The "fabric" between each point of parallelism keeps the parallelism at each layer or layers transparent to the adjacent points. If this transparency is absent, any change in the parallelism at any layer will impact on the configuration of the adjacent layers. This will negatively affect the network flexibility, scalability and fault tolerance, which are the features sought to be improved by introducing parallelism. Therefore, the fabric is essential to gain the full benefits of parallelism. The access layer is the fabric between the

transport/network layers and the data link layer. In a simplistic implementation the fabric at each point could have null functionality.

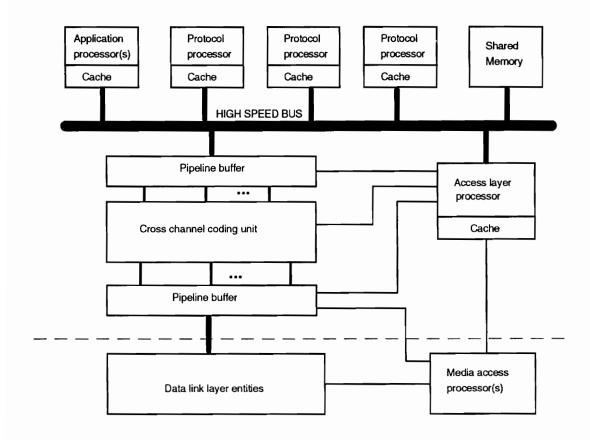

**Figure 2.2.** Parallel network node implementation.

### 2.5. Access Layer Architecture

After considering several options, a bus-based architecture was chosen as the most feasible for the AL. The definition and study of the AL protocol which forms fabric 2 in Figure 2.1 is the main objective of this research. The parallel network node implementation assumed for this study is shown in Figure 2.2.

All processors except the media access processor(s) are connected to the common bus. This includes the access layer processor, the application processor(s) and the protocol processors. All data is stored in the shared memory which is also connected to the common bus. The bus controller is not shown in the figure. All processors have sufficient local memory, shown in Figure 2.2 as cache, for storing control information such as data requests and data indications.

The AL incorporates the use of an error correction coding scheme called *cross channel* coding (CCC). The coding procedure, discussed in greater detail in Chapter 3, is controlled by the access layer processor, while the actual coding is performed by a separate coding unit. The post-coding pipeline buffers can also serve as the input buffers of the data link layer entities.

# Chapter 3. The Access Layer

This chapter discusses the Access Layer (AL) protocol in detail. First, the need for the AL and its basic function are discussed. This is followed by a brief introduction to cross channel coding (CCC), which is incorporated into the AL protocol. The AL protocol is then explained. The chapter concludes with a summation of the implications of CCC on the AL protocol.

### 3.1. Need and Required Functionality

Parallelism can be applied to the different protocol layers of the OSI reference model. In addition to increased bandwidth, other major advantages of parallelism are scalability and fault tolerance. To realize the full benefits of parallelism and to maintain layering in the system, the degree of parallelism at each layer should be transparent to adjoining layers. Hence, a mechanism is needed to map the degree of parallelism at each layer to that at adjacent layers.

The AL maps upper layer parallelism (multiple protocol processors) to lower layer parallelism (multiple physical channels). During this mapping the AL can also adopt a suitable coding procedure for increased reliability. At the transmitting end, the AL must divide and/or merge the available upper layer packets to create AL packets which are then distributed among the available lower layer channels. At the receiving end, the AL has to

reorganize the arriving AL packets into the original upper layer packets and deliver these rebuilt packets to the local upper layer. For the purpose of rebuilding split or merged packets, the AL must attach a header to each AL packet.

The AL at each node has all the information needed to translate the node addresses to the physical channel addresses. This information includes the connectivity of the physical channels, the virtual addresses of all the nodes in the network and the mapping between these addresses and the physical channel addresses.

### 3.2. The AL Protocol

The discussion of the AL protocol begins with an overview of the CCC scheme. The AL protocol is then presented. A step-by-step explanation of its functionality, including transmission and reception processing, is given.

### 3.2.1. Cross Channel Coding

CCC is an error correction scheme which is particularly suitable for parallel channels. This coding procedure, proposed by Wiencko [2], takes advantage of the simultaneous transmission of multiple packets to the same destination over multiple (parallel) channels. Redundant information is sent as *code bits* in each AL packet so that lost or erroneous packets can be rebuilt at the receiving end rather than being retransmitted. The AL does not guarantee reliable service, so the use of CCC is not essential. However, its use increases reliability because CCC enables the AL to recover a limited amount of data that has been lost due to errors. In the absence of CCC or a similar technique, the upper layers

must request retransmission to get such data. Hence, the use of CCC may also reduce the latency in delivering packets to the upper layers.

Consider a case where there are four physical channels between the source and destination nodes. The available data can be split over these four channels to maximize throughput. Consider that the data is transmitted as four packets, with one on each channel. CCC can be applied to these four packets. The set of packets undergoing CCC together is referred to as a *coding set*. The actual encoding process depends on the degree of reliability that is required. For the case of four packets, coding can be done so that at most one or at most two of the four transmitted packets can be rebuilt at the receiving node. In CCC terminology, the number of packets sent is n and of these m can be rebuilt from the other n - m packets. Since one packet from each set of packets undergoing coding is sent over a particular channel, n is usually equal to the number of available channels. In the above case, n = 4 and m = 1 or 2.

In general, the coding procedure involves first splitting the data in each of the n packets into equal size parts. The number of parts depends on the relative values of n and m. Code bits for each channel are then generated by exclusive-ORing (XOR) specific combinations of certain parts of all packets. The code bits are attached to the ends of the respective packets. At the receiving end, if a packet arrives error free, the data can be forwarded to the upper layers and the code bits can be simply discarded. To rebuild any m or fewer packets, the code and data bits of n - m packets are necessary. The decoding involves a similar splitting and XOR procedure.

The key to CCC is the fact that  $a \oplus b \oplus b = a$ . The coding and decoding equations for the n = 4, m = 1 and the n = 4, m = 2 cases are presented in Appendix A.

The most important implication of using CCC is that all the n packets that undergo coding together, forming a coding set, have to be of equal size.

### 3.2.2. Definitions and Terminology

This section contains definitions and explanations for terms which have special meaning in the context of the AL protocol. This includes descriptions of the various headers and entities including data requests and data indications.

#### 3.2.2.1. Protocol Processor Header

Protocol processors (PPs) create a *PP header* in accordance with the particular transport/network layer protocols that are used by the upper layers. The actual format of the header depends on the particular protocols, e.g., TCP/IP or UDP/IP.

#### 3.2.2.2. Upper Layer Packets

Upper layer packets are passed to the AL by the network layer for transmission to the destination node. In OSI terminology, these packets form the service data units (SDUs) to the AL [3]. These packets are a combination of the data sent by the application processor(s) and the PP header. The AL has to deliver these packets without fragmentation to the upper layers at the destination node.

#### 3.2.2.3. Destination Class

Every upper layer packet belongs to a particular destination class, or dest\_class. A destination class is the combination of destination node and the required m value for CCC. Only packets belonging to the same destination class can be in the same coding set.

### 3.2.2.4. Data Request

A PP issues a data request (DR) to the AL whenever it has a packet to transmit. The DR format is shown in Figure 3.1.

| ID  | SVCA | DVCA | SIZE | SERV_CLASS | DATA_PTR |

|-----|------|------|------|------------|----------|

| (4) | (6)  | (6)  | (4)  | (2)        | (4)      |

Figure 3.1. Data request format.

The numbers in parentheses in Figure 3.1 indicate the number of bytes in each field. The fields are defined as follows.

ID:

A unique identifier used to distinguish between the DRs generated at a node. The AL uses this value when it is building the header for AL packets. The ID can be any integer in  $[1, 2^{32} - 1]$ . Mutually exclusive ranges from this set are reserved for each upper layer PP to ensure the uniqueness of the ID.

SVCA:

Source virtual channel address, i.e., the virtual channel address (VCA) of the source node. Addressing is discussed in Section 3.2.3.5.

DVCA:

Destination virtual channel address, i.e., the VCA of the destination node.

SIZE:

Specifies the size of the upper layer packet in bytes.

SERV\_CLASS: Specifies the class of service desired for this packet. This specification could have originated from the application processor. The service

required typically corresponds to the value of m for CCC. This field can also be used by the upper layer to specify particular lower layer channels that are to be used to transmit this packet.

DATA\_PTR: Pointer to the shared memory locations in which the upper layer packet is stored.

#### 3.2.2.5. AL Header

The AL attaches an AL header to each of the packets that it transmits over the physical channels. This header is of variable size and has the format shown in Figure 3.2.

| ID  | SCA | DCA | SIZE | SERV_CLASS | CSET | СОМР | SPLIT_PAT |

|-----|-----|-----|------|------------|------|------|-----------|

| (4) | (6) | (6) | (4)  | (2)        | (4)  | (4)  | ≥ 4       |

Figure 3.2. AL header format.

As with the DR format, the numbers in parentheses in Figure 3.2 refer to the number of bytes in that particular field. The fields defined are as follows.

ID: A unique identifier that the AL assigns to each packet that it creates.

SCA: The *source channel address* is the physical address of the source node on the physical channel over which this AL packet is to be sent.

DCA: The *destination channel address* is the physical address of the destination node on the physical channel over which this AL packet is to be sent.

SIZE:

Specifies the size of the AL packet in bytes, including the AL header and data bits, but not including the cross channel code bits.

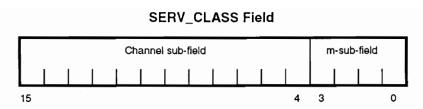

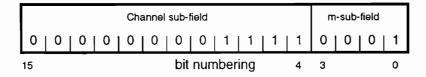

SERV\_CLASS: This field is split into two sub-fields. The upper twelve bits form the *channel* sub-field, while the lower four bits form the *m* sub-field. Details of the SERV\_CLASS field are provided in Section 3.2.3.6.1 dealing with the creation of AL headers.

CSET:

A unique identifier for the *coding set* to which this packet belongs. The CSET field is identical for all AL packets belonging to a particular coding set.

COMP:

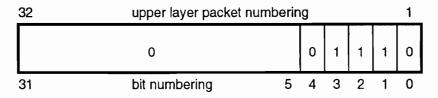

This field is a 32-bit, bit-coded datum. The number of set (1) bits is the number of upper layer packets that have been used for this AL packet. Only a subset of the upper layer packets used in a coding set are used for a given AL packet in that coding set. The positions of the set bits are used to identify this subset. The use of a fixed size COMP field implies that a maximum of 32 upper layer packets can be used in one coding set. The construction of this field is explained in Section 3.2.3.6.1.

SPLIT\_PAT:

The *splitting pattern* is a variable size field. It is a minimum of 4 bytes and a maximum of 128 bytes in length. The data in an AL packet is made up of parts of different upper layer packets. SPLIT\_PAT specifies which part of the AL packet belongs to each upper layer packet used for this AL packet. This field, the COMP field, and an implicit channel ordering are used to rebuild the upper layer packets at the receiver.

With the minimum SPLIT\_PAT field of 4 bytes, the minimum size for an AL header is 34 bytes.

#### 3.2.2.6. AL Packets

AL packets are the protocol data units (PDUs) created by the AL. These packets form the SDUs for the data link layer. AL packets are composed of the AL header, data from upper layer packets and cross channel code bits.

#### 3.2.2.7. Channel Header and Lower Layer Packets

Depending on the actual physical channel that is used, the channel controller adds a header of its own to the AL packets. This *channel header* usually includes physical addresses and an error detection code. Cyclic redundancy checks (CRCs) are commonly used. The combination of AL packet and channel header forms a *lower layer packet*.

#### 3.2.2.8. Data Indication

A data indication (DI) is created by the AL and passed to the upper layer to indicate the availability of a new upper layer packet. The DI is the counterpart of the DR at the receiving end. A DI has the format shown in Figure 3.3.

| ID  | SVCA | DVCA | SIZE | DATA_PTR |

|-----|------|------|------|----------|

| (4) | (6)  | (6)  | (4)  | (4)      |

Figure 3.3. Data indication format.

The numbers in parentheses in Figure 3.3 represent the number of bytes in each field. The SVCA and DVCA fields have the same meaning as in a DR. The other fields are defined as follows.

ID: An identifier assigned by the AL to the DI. It is used by the PPs to distinguish between DIs when processing received packets.

SIZE: The size of the upper layer packet in bytes. It should be identical to the SIZE field of the DR that was used at the transmitting node, to send this packet.

DATA\_PTR: Specifies the address in shared memory where the upper layer packet is stored.

### 3.2.3. Transmission of Data