## Form-Factor-Constrained, High Power Density, Extreme Efficiency and Modular Power Converters

Qiong Wang

Dissertation submitted to the faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

Doctor of Philosophy In Electrical Engineering

Rolando Burgos, Chair Dushan Boroyevich Qiang Li Mantu K. Hudait Pradeep Raj

> May 9<sup>th</sup>, 2018 Blacksburg, VA

Keywords: High efficiency, high power density, form-factor-constrained, modularity, modular power converter, more-electric aircraft, bi-level integrated synthesis, optimization, wide-bandgap semiconductor, ac/dc converter, Vienna rectifier, dc/ac converter, T-type inverter

# Form-Factor-Constrained, High Power Density, Extreme Efficiency and Modular Power Converters

#### Qiong Wang

#### **ABSTRACT**

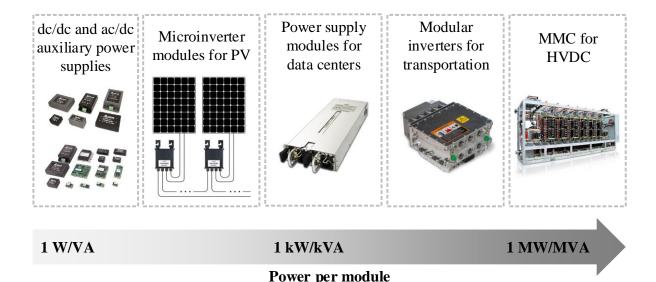

Enhancing performance of power electronics converters has always been an interesting topic in the power electronics community. Over the years, researchers and engineers are developing new high performance component, novel converter topologies, smart control methods and optimal design procedures to improve the efficiency, power density, reliability and reducing the cost. Besides pursuing high performance, researchers and engineers are striving to modularize the power electronics converters, which provides redundancy, flexibility and standardization to the end users. The trend of modularization has been seen in photovoltaic inverters, telecommunication power supplies, and recently, HVDC applications.

A systematic optimal design approach for modular power converters is developed in this dissertation. The converters are developed for aerospace applications where there are stringent requirement on converter form factor, loss dissipation, thermal management and electromagnetic interference (EMI) performance. This work proposed an optimal design approach to maximize the nominal power of the power converters considering all the constraints, which fully reveals the power processing potential. Specifically, this work studied three-phase active front-end converter, three-phase isolated ac/dc converter and inverter. The key models (with special attention paid to semiconductor switching loss model), detailed design procedures and key design considerations are elaborated. With the proposed design framework, influence of key design variables, e.g. converter topology, switching frequency, etc. is thoroughly studied.

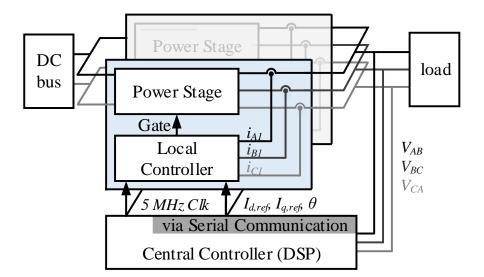

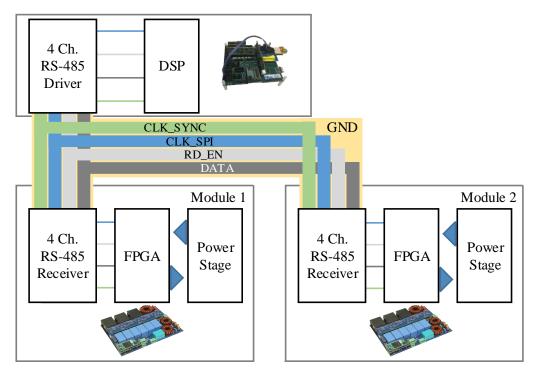

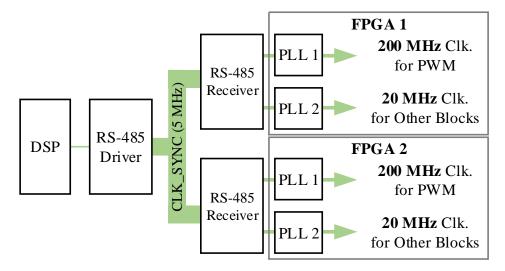

Besides optimal design procedure, control issues in paralleling modular converters are discussed. A master-slave control architecture is used. The slave controllers not only follow the command broadcasted by the master controller, but also synchronize the high frequency clock to the master controller. The control architecture eliminates the communication between the slave controllers but keeps paralleled modules well synchronized, enabling a fully modularized design.

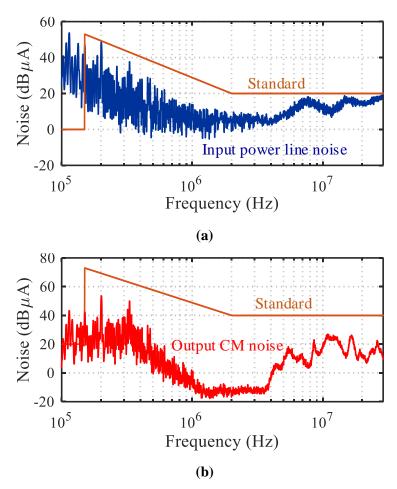

Furthermore, the implementation issues of modularity are discussed. Although modularizing converters under form factor constraints adds flexibility to the system, it limits the design space by forbidding oversized components. This work studies the influence of the form factor by exploring the maximal nominal power of a double-sized converter module and comparing it with that of two paralleled modules. The tradeoff between modularity and performance is revealed by this study. Another implementation issue is related to EMI. Scaling up system capacity by paralleling converter modules induces EMI issues in both signal level and system level. This work investigates the mechanisms and provides solutions to the EMI problems.

# Form-Factor-Constrained, High Power Density, Extreme Efficiency and Modular Power Converters

#### Qiong Wang

#### GENERAL AUDIENCE ABSTRACT

As penetration of power electronics technologies in electric power delivery keeps increasing, performance of power electronics converters becomes a key factor in energy delivery efficacy and sustainability. Enhancing performance of power electronics converters reduces footprint, energy waste and delivery cost, and ultimately, promoting a sustainable energy use. Over the years, researchers and engineers are developing new technologies, including high performance component, novel converter topologies, smart control methods and optimal design procedures to improve the efficiency, power density, reliability and reducing the cost of power electronics converters. Besides pursuing high performance, researchers and engineers are striving to modularize the power electronics converters, enabling power electronics converters to be used in a "plug-and-play" fashion. Modularization provides redundancy, flexibility and standardization to the end users. The trend of modularization has been seen in applications that process electric power from several Watts to Megawatts. This dissertation discusses the design framework for incorporating modularization into existing converter design procedure, synergically achieving performance optimization and modularity.

A systematic optimal design approach for modular power converters is developed in this dissertation. The converters are developed for aerospace applications where there is stringent

requirement on converter dimensions, loss dissipation, and thermal management. Besides, to ensure stable operation of the onboard power system, filters comprising of inductors and capacitors are necessary to reduce the electromagnetic interference (EMI). Owning to the considerable weight and size of the inductors and capacitors, filter design is one of the key component in converter design. This work proposed an optimal design approach that synergically optimizes performance and promotes modularity while complying with the entire aerospace requirement. Specifically, this work studied three-phase active front-end converter, three-phase isolated ac/dc converter and three-phase inverter. The key models, detailed design procedures and key design considerations are elaborated. Experimental results validate the design framework and key models, and demonstrates cutting-edge converter performance.

To enable a fully modularized design, control of modular converters, with focus on synchronizing the modular converters, is discussed. This work proposed a communication structure that minimizes communication resources and achieves seamless synchronization among multiple modular converters that operate in parallel. The communication scheme is demonstrated by experiments.

Besides, the implementation issues of modularity are discussed. Although modularizing converters under form factor constraints adds flexibility to the system, it limits the design space by forbidding oversized components. This work studies the impact of modularity by comparing performance of a double-sized converter module with two paralleled modules. The tradeoff between modularity and performance is revealed by this study.

#### Acknowledgement

I would like to thank my advisor, Dr. Rolando Burgos guiding me to this point. It is his attitude towards perfection, patience in teaching and experience on power electronics that helps me finish this work, technically and emotionally. Under his guidance, I started to have the technical abilities and faith to explore in the field of power electronics

I am very grateful to Dr. Dushan Boroyevich, who does not only aid me in solving technical problems but also in providing the direction. His creative ways of thinking teaches me what makes a real researcher.

I want to thank Dr. Qiang Li, Dr. Mantu Hudait and Dr. Pradeep Raj for kindly accepting the invitation to be in the committee and their kind suggestions and questions during the thesis examination and defense.

I would like to express my sincere gratitude to Dr. Xuning Zhang and Dr. Bo Wen. They have mentored me since the first day I started this work. I deeply appreciate their unselfish help and share of knowledge on this work.

I would like to thank all the professors, staffs and students in CPES family. It is my honor to work with all of you. You make CPES lab a place not only for doing research but also for living a wonderful life.

Special thanks goes out to UTC Aerospace Systems that supports this work. In addition, I want express my sincere gratitude to Mr. Adam White, Mr. John Sagona and Dr. Mustansir Kheraluwala, who have been working with me on this work from UTC Aerospace Systems side.

Their experience in power electronics product development provides solid foundation for the complete of this work.

Finally but most importantly, I would like to thank my parents, Mr. Weichu Wang and Mrs. Yanli Zhao and my middle school sweet heart, Ms. Yanfei Liu. Their support and encouragement is the fundamental power that drives me forward. Their love makes me stay positive towards my research and life.

## Table of Contents

| Table of    | Contentsviii                                                                 |

|-------------|------------------------------------------------------------------------------|

| Chapter     | 1. Introduction                                                              |

| 1.1         | Application: More-Electric Aircrafts                                         |

| 1.2         | Design of Power Electronics Converters                                       |

| 1.3         | Modular Power Electronics                                                    |

| 1.4         | Organization of This Work                                                    |

| Chapter 2   | 2. Measurement and Characterization of SiC MOSFET Switching Transients 23    |

| 2.1         | Chapter Introduction and Prior Art                                           |

| 2.2         | Hardware Setup for Top-Device-Switching and Bottom-Device-Switching Tests 27 |

| 2.3         | Analysis on Switching Transients                                             |

| 2.4         | Comparison between Devices with Different Die Sizes                          |

| 2.5         | Comparison between 2 <sup>nd</sup> and 3 <sup>rd</sup> Generation Devices    |

| 2.6         | Chapter Conclusion                                                           |

| Chapter     | 3. Nominal Power Maximization of Power Converters – An Active Front-End      |

| Converter C | ase Study51                                                                  |

| 3.1         | Chapter Introduction and Prior Art                                           |

| 3.2         | Nominal Power Maximization for Form-Factor-Constrained Converter             |

| 3.3     | Design Procedure, Key Models and Design Results                             | 58     |

|---------|-----------------------------------------------------------------------------|--------|

| 3.4     | Constructed Prototype and Experimental Results                              | 81     |

| 3.5     | Method for Turn-off Delay Compensation                                      | 85     |

| 3.6     | Chapter Conclusion                                                          | 92     |

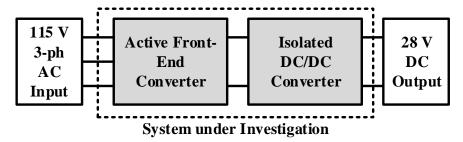

| Chapter | 4. Two-Stage Three-Phase Isolated AC/DC Converter                           | 94     |

| 4.1     | Chapter Introduction and Prior Art                                          | 94     |

| 4.2     | Nominal Power Maximization of Two-Stage Form-Factor-Constrained Convergence | verter |

|         | 96                                                                          |        |

| 4.3     | Design of Active Front-End Converter                                        | 100    |

| 4.4     | Design of Isolated DC/DC Converter                                          | 106    |

| 4.5     | Design Results of the Two-Stage System                                      | 117    |

| 4.6     | Constructed Prototype and Experimental Results                              | 120    |

| 4.7     | Chapter Conclusion                                                          | 123    |

| Chapter | 5. Modular Inverter                                                         | 125    |

| 5.1     | Chapter Introduction and Prior Art                                          | 125    |

| 5.2     | Nominal Power Maximization of Modular Inverter                              | 128    |

| 5.3     | Converter Design Procedure                                                  | 129    |

| 5.4     | Module Design Results                                                       | 135    |

| 5.5     | Paralleling Modular Inverters                                               | 148    |

| 5.6 C       | napter Conclusion | 162 |

|-------------|-------------------|-----|

| Chapter 6.  | Conclusion        |     |

| References. |                   | 167 |

### Chapter 1. Introduction

Since its introduction in 1950s, power electronics has been one of the key enablers in industry. As the world is seeking a more sustainable future, power electronics represents the key technology in tackling the emerging challenges, e.g. renewable electricity, zero-emission vehicle and transportation electrification. This work focuses on power electronics converters in more-electric aircrafts (MEA), where electrical components replaces onboard mechanical, pneumatic and hydraulic systems to reduce take-off weight. The MEA demands high reliability, high availability, high power density and high efficiency. This works discusses the underlying technologies that enables the high performance power converter, the design framework that systematically explores the optimal design, and demonstrates the prototypes that satisfies the MEA demand.

This chapter presents the application background, followed by literature review on design framework and modularity of power electronics converters.

#### 1.1 Application: More-Electric Aircrafts

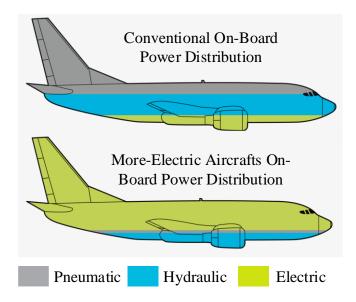

For decades, the aerospace industry has been striving to reduce the cost and environmental impact of aircrafts. Reducing take-off weight is one of the major approaches of reducing fuel use and emissions. The concept of more-electric aircraft (MEA) is proposed in this context. The MEA uses electrical components to replace onboard mechanical, hydraulic and pneumatic systems to decrease take-off weight. This concept is depicted by Fig. 1-1 [1], where the electrical system consumes the most non-propulsive power in a MEA while the pneumatic and hydraulic systems

consume the most in a conventional aircraft. A study conducted by NASA expects a 10% reduction in the take-off weight and a 9% reduction in fuel burn for a 200-seater aircraft by switching to MEA technologies [2].

Fig. 1-1. Breakdown of non-propulsive onboard power on a conventional aircraft and a more-electric aircraft. A more-electric aircraft uses more electric power to execute flight control, air conditioning, etc.

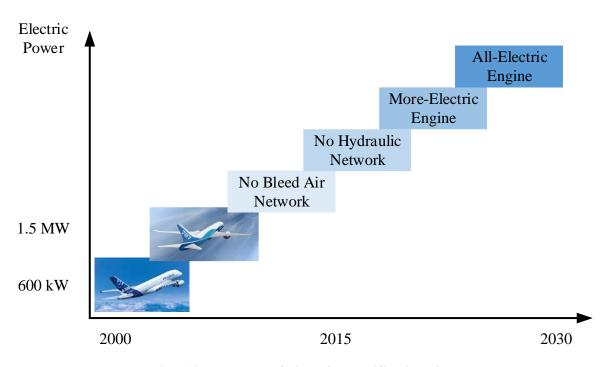

The aerospace industry has started the practice of MEA concept. In early 2000, electrical system replaces one of the three traditional hydraulic systems on Airbus A380. The 600 kVA system is the first high power electrical system on commercial aircrafts. Later, the Boeing 787 Dreamliner extends the use of electrical systems in an innovative manner. It incorporates a nobleed-air system that eliminates pneumatic systems and uses electric system to support the functions that are formerly powered by bleed air [3]. Furthermore, Boeing 787 uses 230 Vac variable frequency (360 Hz ~ 800 Hz) distribution system, which eliminates the gearboxes between jet engines and generators and further reduces take-off weight [3]. The total electrical capacity on a Boeing 787 is 1.5 MW, representing 150 % more electrical load than Airbus A380. Although, the transition to all-electric aircraft is still many years in the future, the aerospace industry is taking

steps towards the goal. Recently, Airbus, Siemens and Rolls Royce team up to develop a hybridelectric flight demonstrator where one out of the four jet engines is replaced by a 2 MW motor [4]. A roadmap of aircraft electrification from Boeing (shown in Fig. 1-2) [3] shows the millstones towards all-electric aircraft. It is projected electrical system will gain more penetration, and ultimately, drive the aircraft directly.

Fig. 1-2. Roadmap of aircraft electrification [3].

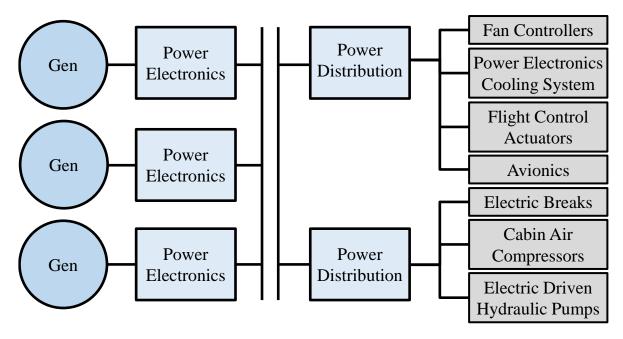

Power electronics is a key enabling technology in the MEA. Taking Boeing 787 as an example, it has a total of 1 MW of power electronics load. The interconnecting power electronics converters and the associated loads are summarized in Fig. 1-3. The power electronics converters convert variable frequency outputs of generator to various onboard buses (±270 Vdc, 28 Vdc, 230 Vac and 115 Vac) to power the loads. The MEA demands high reliability, high availability, high power density and high efficiency power converters. Besides, it puts stringent design requirements such as electromagnetic interference (EMI) requirement, power quality requirement and thermal

management requirement [5, 6]. The design framework of the converters should tackle the requirements while optimizing the performance, which is one of the main research topic in this work.

Fig. 1-3. Power electronics load on a more-electric aircraft [3]. Power electronics converters are the key components interconnecting the generators, buses and loads.

#### 1.2 Design of Power Electronics Converters

#### 1.2.1 Generic Design Framework

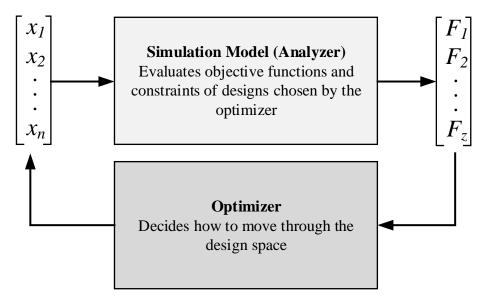

Design is the process of conceiving a system that will subsequently by implemented and operated for some beneficial purpose [7]. In the context of this work, it refers to the conceiving of a power electronics converter or system. Modern system design involves optimization, of which the goal is to find a system design that will minimize some objective function. A generic design framework is formulated as:

$$\min/\max F(x) \tag{1},$$

$$s.t. g(x) \le 0 \tag{2},$$

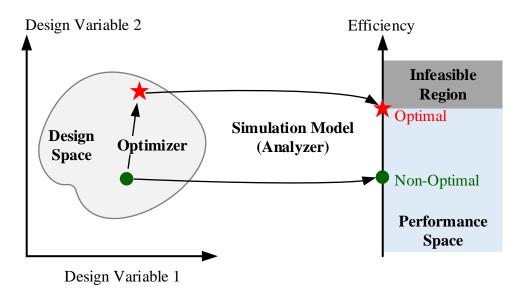

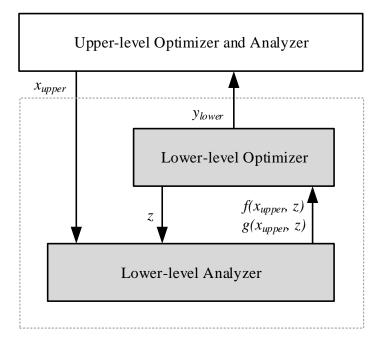

where  $F(x) = [F_1(x) \cdots F_z(x)]^T$  is the objective function,  $x = [x_1 \cdots x_i \cdots x_n]^T$  is the design vector consisting of the design variables, s.t. is the abbreviation of "subject to", and  $g(x) = [g_1(x) \cdots g_n(x)]^T$  represent design constraints [7]. The design framework is also depicted as block diagrams showing in Fig. 1-4, where the simulation model takes design vector x as input, evaluates the objective function F(x) and design constraints g(x), and the optimizer takes F(x) as input and searches for new design vectors that can further optimize F(x).

Fig. 1-4. Generic design framework, modified from [7].

At the core of the design are the simulation model and optimizer. The simulation model is categorized into physical model and mathematical model, and the mathematical model is further categorized into analytical model and numerical model. A literature review on simulation models used in power electronics converter design is presented in section 1.2.3. The optimization

algorithm is categorized into direct search, numerical methods and metaheuristic methods. A literature review on optimization algorithms used in power electronics is presented in section 1.2.3.

#### 1.2.2 Performance Measures of Power Electronics Converters

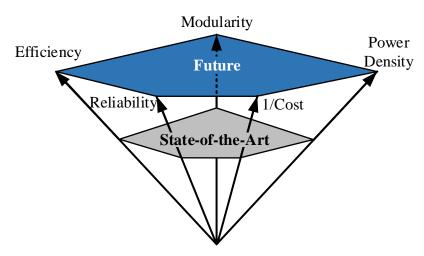

Fig. 1-5. Main performance measures of power electronics converters and the trend, modified from [8].

Performance of power electronics converters is measured by various performance indices, namely, efficiency, power density, cost, reliability and modularity [8]. Power converter designers are pursuing higher efficiency, higher power density, higher reliability, higher modularity while lower cost (including manufacture cost, maintenance cost and operational cost), and this trend is depicted by Fig. 1-5. However, owning to the coupling of performance measures, enhancing multiple performance measures might be conflicting. For example, to increase power density, a common approach is to increase switching frequency such that smaller passive components are required to handle the energy in switching frequency. However, it induces elevated semiconductor switching loss and ac conduction loss. Therefore, a tradeoff study is necessary, and the final design selection in most cases represents compromise between performance measures (e.g. compromise between efficiency and power density).

#### 1.2.3 Design of Power Electronics Converters

The design framework for power electronics converters should be able to handle a number of issues dictated by the nature of converter design:

- ▶ There might be a number of conflicting objective functions (stated in section 1.2.2).

- The design of power electronics converter involves various disciplines, namely, electrical circuit, electromagnetism, semiconductor, thermodynamics, etc. Different simulation and modeling tools are used to analyze these disciplines. The design framework should allow easy data transfer between the tools, e.g. data transfer between Matlab Simulink that is in charge of circuit analysis and ANSYS Maxwell that simulates inductor designs.

- ► The design might involve multiple design teams. The design framework should be able to operate in a distributed manner but allowing easy data transfer between teams. Even for single designer, a distributed design framework can accelerate the process by operating concurrent design using a multiprocessor computer.

Many design approaches have been proposed and used in design of power electronics components and converters. These approaches target at optimizing different objective functions using various simulation models and optimization algorithms under a variety of design frameworks. The following paragraphs present the literature review from the aforementioned aspects.

#### ► Objective Functions

Common objective functions used in design of power electronics components and converters are efficiency (or loss), power density (or size and weight), cost and reliability. Prior the introduction of multi-objective optimization [8], design variable (topology, switching frequency,

devices, etc.) selection in most designs are based either on rule-of-thumb (e.g. a 70 kHz switching frequency to facilitate EMI filter design) and experience of the designer or on single-objective (depicted in Fig. 1-6) optimization. The objective function of the single-objective optimization includes efficiency [9-15] and weight or power density [16-21].

The experience-based procedure is unable to guarantee an optimal design because it highly depend on knowledge experience of the designer. The single-objective optimization based procedure may result in poorly designed overall system if a single objective function is aggressively pursued [22], e.g. aggressively pursuing high efficiency may results in bulky, lossy and costly design.

Fig. 1-6. Single-objective optimization framework. An example of two-design-variable system is shown. The objective function is efficiency and is to be maximized. The simulation model calculates the efficiency and evaluates design constraints based on design variables. The optimizer searches for the design vector that leads to optimal efficiency.

[8, 23] introduce multi-objective optimization to design of power electronics systems. This approach concurrently evaluates multiple objective functions, e.g. efficiency and power density, thus a more comprehensive design is achieved. The objective functions being evaluated using the

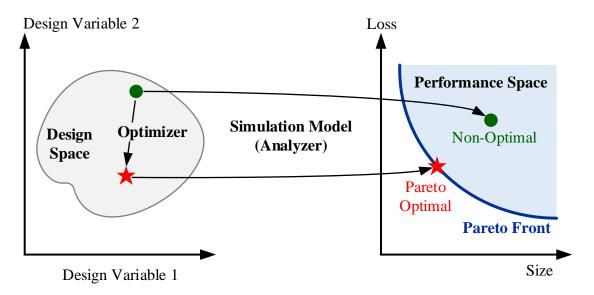

multi-objective optimization approach are efficiency-power density [5, 24-27], efficiency-weight [28, 29], efficiency-cost [30], efficiency-power density-cost [31] and efficiency-volume-failure rate [32]. Although the design that optimizes performance of all objective functions best suits the problem, it is rarely found since the optimization of multiple objective functions is likely to be conflicting, i.e. enhancing one objective function by adjusting design variables may worsen the other objective functions. Therefore, the outcome of a multi-objective optimization is usually depicted by Pareto front (two objectives) [8] or surface (three objectives) [31, 32] that represents tradeoff between objective functions. Pareto front (or surface) is the set of all Pareto optimal (also referred to as Pareto efficient) designs. A design is Pareto optimal if it is impossible to improve any performance indices without making at least one other performance index worse off. The design procedure and the outcome of a two-objective optimization is visualized by Fig. 1-7 as an example.

Fig. 1-7. Multi-objective optimization framework. An example of two-design-variable system is shown. The objective functions are loss and size, and they are to be minimized. The Pareto optimal designs (it is impossible to reduce the loss and size of the Pareto optimal designs

# concurrently) form the Pareto front, demonstrating the tradeoff between the two objective functions.

Some other objective function including current quality [33], insulation capacitance of isolated power supplies [34], leakage magnetic field of wireless chargers for electric vehicles [35] and parasitic parameters in power modules and gate driving circuits [36, 37] are found in literatures.

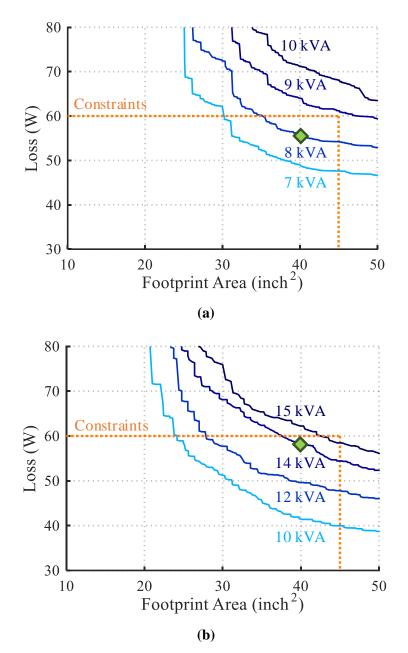

This work uses nominal power as objective function. For the problem of concern, maximizing the nominal power exploits the form factor limit and loss budget of the modular converter and leads to optimal design.

#### ► Optimization Algorithm

For the optimizer, various algorithms has been used for searching optimal designs of power electronics component and converters, e.g. direct search as in [5, 9, 24-27, 35, 38-40], numerical algorithms as in [8, 41] and heuristic algorithms as in [36, 37, 42-47]. However, deriving numerical models used in numerical algorithms is impractical owning to the complexity and nonlinear nature of power electronics systems. The metaheuristic algorithms, e.g. genetic algorithm, particle swarm and simulated annealing, render non-deterministic results. Their convergence and ability to find global optimal points highly depend on the initial values and optimization settings. However, there is no clear guidelines on setting these parameters for power electronics applications. Therefore, direct search is used herein.

#### ➤ Simulation Models

At the core of the design is simulation models, of which the accuracy and complexity determines the fidelity and calculation speed of the design. The simulation models used in analyzing performance of key components (semiconductor devices, magnetic components) are discussed as follow.

For semiconductor devices, most literatures focus on characterization of the switching transients and switching loss. Although analytical models using data sheet information [48-51] and SPICE models [52, 53] provides quick estimation of switching loss, performing double pulse tests (DPT) [54-57] is able to take the device temperature [56-59], parasitics of external connections (e.g. printed circuit board) and capability of the gate drivers into account, thus rendering more complete and accurate modeling. An empirical model of switching loss (with respect to switching current, voltage, temperature, etc.) can be built from DPT results and is later used in converter design. A few circuit simulation software, e.g. PLECS, has included similar empirical models for real-time switching loss and temperature estimation. In this work, a complete characterization of candidate devices is presented in Chapter 2.

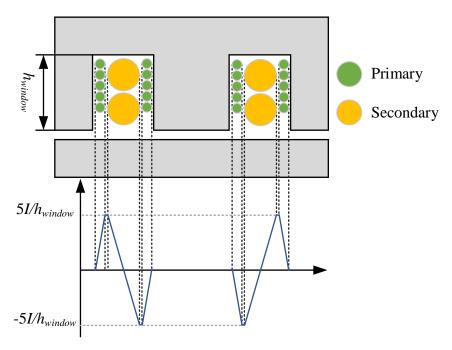

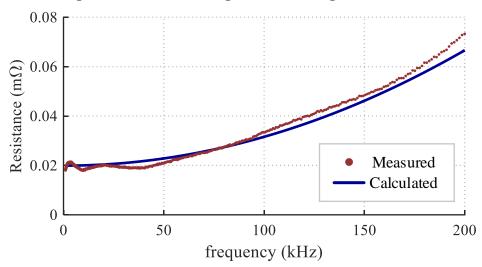

For design of magnetic components, the focuses are on winding loss modeling and core loss modeling. Finite element analysis (FEA) software (e.g. ANSYS Maxwell) is widely used in modeling winding loss considering skin effect, proximity effect and fringing effect. For analytical solutions, [60] is widely used in modeling winding loss of solid conductors. It is also being used in modeling winding loss of planar magnetics of high switching frequency power converters where the winding (implemented by PCB trace) is too thin to be finely meshed in FEA software [61]. For applications using litz wire, the winding loss can be calculated by methods discussed in [62-65]. These methods requires the knowledge of the magnetic field that penetrates the winding, which is either calculated through 1D approximation [66] or through FEA simulation. Core loss is mostly modeled by empirical models such as Steinmetz's equation [67], generalized Steinmetz's equation [68] and improved Steinmetz's equation [69]. The excitation of the latter is not limited to sinusoidal excitation, which suites the design of pulse width modulated converters. However, these

models neglects the flux density dc bias. Advanced models [65, 70-72] takes this factor into account by deriving empirical models based on experimental data. However, deriving the model for a variety of cores could be time consuming as the influence of dc bias is depend of operation point and material.

Furthermore, virtual prototyping and multi-domain simulation are interesting topics to the power electronics community [20, 73, 74]. This methodology links the analysis of different disciplines, e.g. electric, magnetics, thermal and mechanical, allowing for concurrent multi-domain design and optimization. An example of virtual prototyping is demonstrated by [75] where the authors use iSight to integrate the electrical and thermal design of an integrated (IPEM). Ref. [76] proposes a tool that integrates the electric, thermal and parasitic analysis model for power module design. It uses order reduction (MOR) techniques to replace FEA-type simulation, which improves the calculation speed. The virtual prototyping tool could improve the fidelity of the simulation models since coupling effect of various disciplines are considered concurrently. It might potentially be integrated with optimization tools for fully automated prototyping of power electronics converters.

#### ► Design Framework

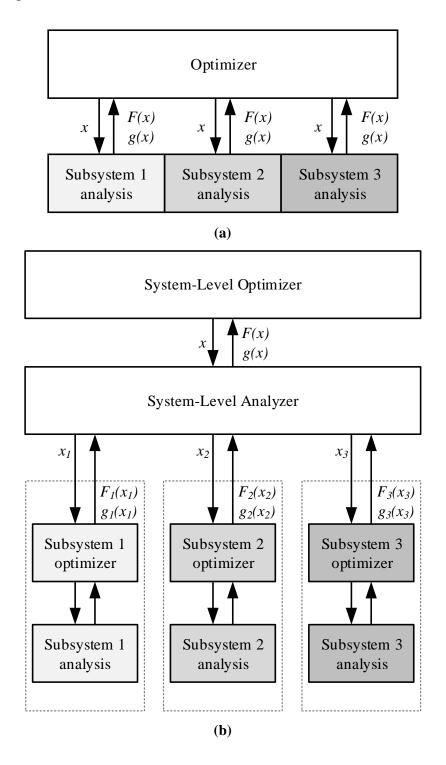

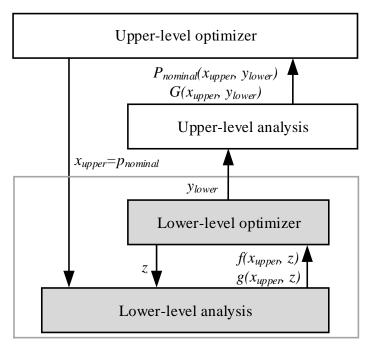

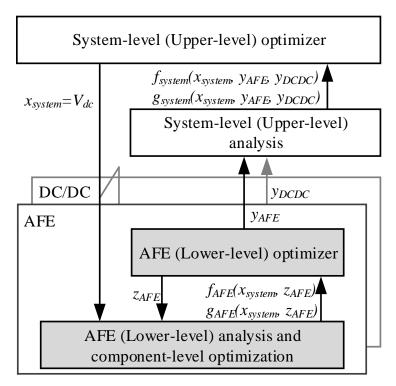

The optimization framework belongs to one of the two categories: single-level optimization and multi-level optimization. The two frameworks are visualized in Fig. 1-8 (a) and (b) [7].

The single-level optimization (shown in Fig. 1-8 (a)) has one optimizer oversees the value of the design variables and objective. The value of design variable changes according to the centralized optimizer. The subsystem analyzers are asked to evaluate constraints and objective

functions. Single-level architecture is mostly used in optimization of key components in a converter. Examples are [9, 34, 35, 61, 77].

Fig. 1-8. Single-level and multi-level optimization framework, modified from [7] (a) Single-level framework, centralized optimization. (b) Multi-level optimization, distributed optimization.

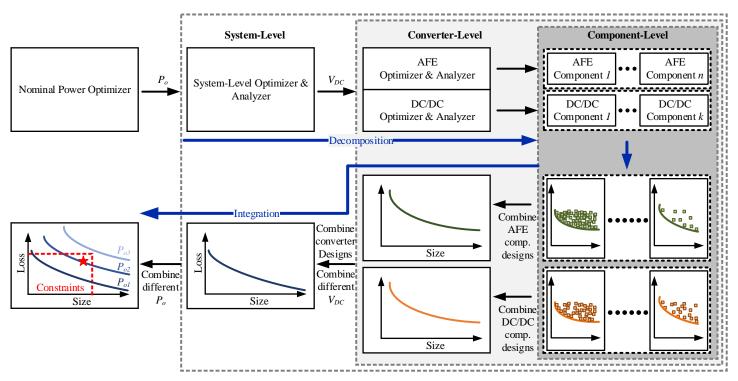

Contrary to the single-level optimization, multi-level (shown in Fig. 1-8 (b)) optimization distributes not only the optimization but also decision making through the subsystems. This framework provides autonomy to various disciplines and facilitates concurrent calculation. Thanks to the multidisciplinary nature of power electronics converters, most literatures [9, 21, 24-27, 31, 35, 38, 39, 44, 74, 78-80] employs a multi-level design architecture, e.g. there are inner loops for component design and output loop for selection of converter-level parameters. However, the design procedures presented in these literatures are developed specifically for the topology of concern, and is not readily transferrable to other topologies and applications. This work generalizes the design framework using the concept of bi-level problem programming (presented in following paragraphs), making it easier to adopt. Besides optimizing converter performance, this work uses the multi-level optimization framework to: maximize nominal power of modular converters (presented in Chapter 3); design a two-stage converter where the two stages are strongly coupled (presented in Chapter 4); compare topologies and investigate the impact of key design variables in converter design (presented in Chapter 3 and Chapter 5).

The multi-level optimization for engineering problems has been widely discussed in aerospace community where the design normally involves large number of design variables and integration of various disciplines [81]. There are two mainstream multi-level frameworks, namely, collaborative optimization (CO) [82] and bi-level integrated system synthesis (BLISS) [83-85] used in aerospace community. In CO, the system-level optimizer provides design variable targets to the subsystems, and the subsystem optimizer finds designs that minimizes the difference

between current states and the targets while complying with the local constraints [83, 85]. A CO problem has two levels and the system-level problem is formulated as:

$$\min F_{svs} \tag{3},$$

$$\operatorname{wrt}: x_0 = \operatorname{target} \operatorname{variables}$$

(4),

s.t.

$$J_k = 0 \forall \text{ subproblems}_k$$

(5),

where wrt stands for "with regard to". The system-level optimizer searches for  $x_0$  such that it minimizes objective function  $F_{sys}$  and reduces  $J_k$  (termed compatibility constraints). The subproblems are formulated as:

$$\min J_k = (\text{target variables} - k^{th} \text{ local variables})^2$$

(6),

s.t.

$$k^{th}$$

local constraints (7).

All the design variables in CO is overseen by both system-level and subsystem-level optimizers, and it decouples the design of subsystems by letting optimizers of both levels changes the design variables. The CO suits optimization problems where the design variables are limited but strong coupling between subproblems exists. For power electronics converter design, where there are a large number of design variables, the CO could be too complicated to solve.

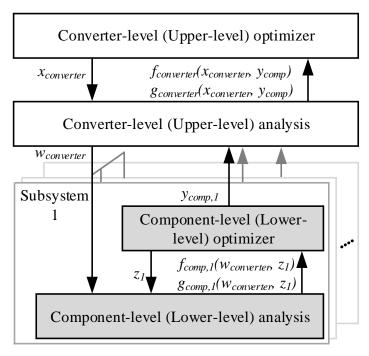

Fig. 1-9. Simplified block diagram of bi-level integrated system synthesis, modified from [83].

In BLISS, instead of providing design variable targets, it sends system-level design variables to the subsystem analyzers, and these variables stay as constant during the subsystem design [83]. A simplified BLISS design framework modified from [83] (original figure is Figure 8.16 in [83], the surrogate input  $y^v$  and weighing term w are omitted) is depicted in Fig. 1-9. The subsystem-level (lower-level) optimizer searches for local design variables that minimizes the local objective functions while complying with local constraints. The system-level (upper-level) optimizer searches for system-level design vector that optimizes the ultimate objective function while complying with the system-level constraints. The complete BLISS is formulated based on response surface methodology and post-optimal analysis such as sensitivity analysis [84, 85], which is too complicated to be used in design of power electronics converters.

Nevertheless, BLISS is essentially a bi-level programming problem (BLPP) [86], which is defined as "a mathematical program that contains an optimization problem in the constraints" [87]. The upper-level problem of a bi-level optimization is formulated as:

$$\min F(x_{upper}, y_{lower}) \tag{8},$$

s.t.

$$G(x_{upper}, y_{lower}) \le 0$$

(9),

where the F represents upper-level objective function, G represents upper-level constraints,  $x_{upper}$  is the upper-level design variable, and  $y_{lower}$  is the lower-level design vector that solves the lower-level problem ("the optimization problem in the constraints") and is defined by the lower-level optimization problem below:

$$\min f(x_{upper}, z) \tag{10},$$

s.t.

$$g(x_{unner}, z) \le 0$$

(11),

$$y_{lower} \in \arg\min\{f(x_{upper}, z) : g(x_{upper}, z)\}$$

(12),

where z is the lower-level design vector, and  $g(x_{upper}, z)$  represents lower-level constraints.

The framework of BLPP fits design of power electronics converter. The converter-level variables, e.g. topology, switching frequency and values of passive components, are constant in component design. The design of components needs optimizers that searches for component-level design variables. The objective function of converter-level design is likely to be component-level objective functions combined in certain manner, e.g. converter loss is the sum of component loss. These converter design procedures matches the structure of BLPP. Therefore, BLPP is used in this work. Furthermore, for more complicated power converter system or design, e.g. two-stage converter, BLPP can be cascaded to form a multi-level framework that consists of more than two levels. Detailed design framework is elaborated in Chapter 3 and Chapter 4.

#### 1.3 Modular Power Electronics

Fig. 1-10. Modular power electronics converters in various applications from watt-level to megawatt-level.

Since the first introduction of power electronics building blocks (PEBB) by U.S. Office of Naval Research (ONR) [88], modularizing power electronics converters has gain tremendous interest, a trend that has be seen in power supplies in small auxiliary power supplies [89], renewable energy applications [90], telecommunication power supplies [91], vehicular applications [92], and recently, high voltage DC (HVDC) applications [93, 94]. Some of the modular products for abovementioned applications are summarized in Fig. 1-10. For these applications, modularity provides the system with redundancy for reliable operation [91], flexibility for high performance [95] and product standardization for low lifecycle cost [88, 96, 97]. To reap the benefits, module specifications (e.g. form factor, footprints, etc.) and communication between modules should be clearly defined by the system designers so that module designers produce standardized converters by complying with the specifications. This coordinates with the objective of Distributed-Power Open Standards Alliance (DOSA) [89], an industrial

organization striving to establish standards for DC/DC converter modules. The control and communication of converter modules working in parallel has been discussed in [98-102], and will be discussed in Chapter 5. The module specifications are defined primarily by packaging considerations such as thermal, interconnections, manufacturing economics, etc. [88].

Fig. 1-11. Onboard power distribution and management system with modular power converters [103]. The form factor of each module is constrained by the chassis. The entire chassis is enclosed, thus all modules are natural convection cooled. To avoid overheating, there is loss budget specified for each module.

Specifically, this work aims at designing modular power converters for aerospace applications, where the form factor of each module is determined by the chassis, the loss budget is determined by system thermal management limit and the cooling is natural convection. A commercial onboard power distribution and management system is shown in Fig. 1-11 to demonstrate the system assembly and constraints. The power distribution and management system use solid-state power controllers to increase the reliability by eliminating lower reliability components. To maximize system capacity and reveal performance potential under such constrains, the nominal power is not specified and is to be maximized herein. Optimization of power electronics converters, either single-objective optimization focusing on efficiency [9] or power density [21], or multi-objective optimization focusing on efficiency-power density [5, 24], efficiency-cost [30] or other key performance measures [33, 78], has been widely used and discussed for decades. However, these

design approaches cannot be directly applied, because the objective functions (efficiency and power density) in aforementioned literatures are design constraints (loss and form factor), and the primary objective function is nominal power herein. Only a few literatures [38, 39] discuss nominal power maximization for modular converters. This work uses BLPP to formulate the nominal power maximization problem, and the approach will be presented in Chapter 3. This approach not only renders the optimal converter design, but also quantitatively evaluates influence of design constrains (form factor, loss budget, etc.) and compares converter topologies. For evaluating influence of design constrains, an issue frequently discussed between system-level and module-level designers., this work compares the maximal nominal power of a converter module that has doubled height and loss budget with that of two converter modules working in parallel. The results and discussion will be elaborated in Chapter 5.

#### 1.4 Organization of This Work

This work discusses the design framework, models, control and modularity issues of form-factor-constrained, loss-budget-limited modular power converters for aerospace applications. It is organized as follows.

Chapter 1 introduced the background application and presents literature surveys on design framework for power electronics converters and modular converters.

Chapter 2 presents characterization of SiC MOSFETs with focus on its switching transients under various temperatures in a phase-leg configuration, a key test of which the results are used in converter design to model the switching loss. It is proposed to conduct two tests to accurately

characterize the switching transients. The test setup, the testing results and data processing are elaborated.

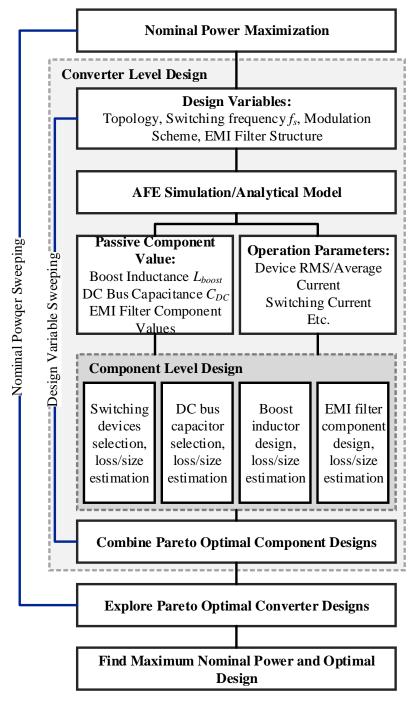

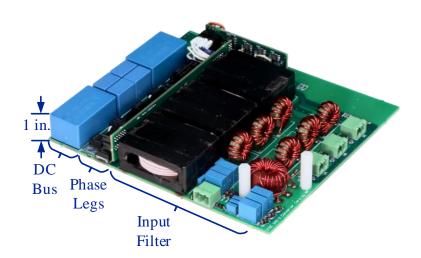

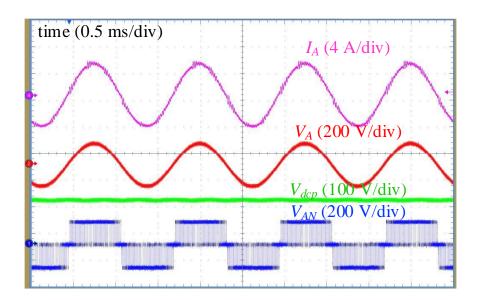

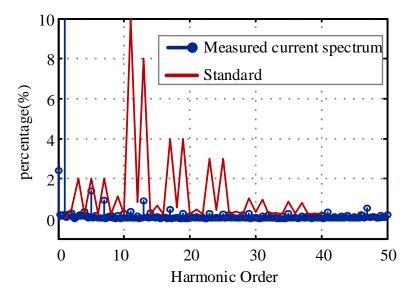

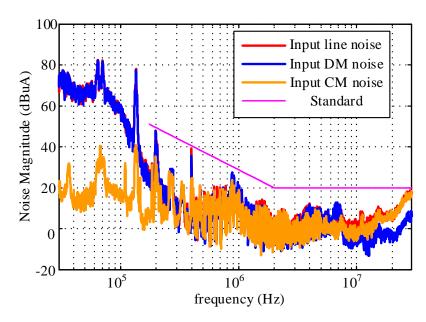

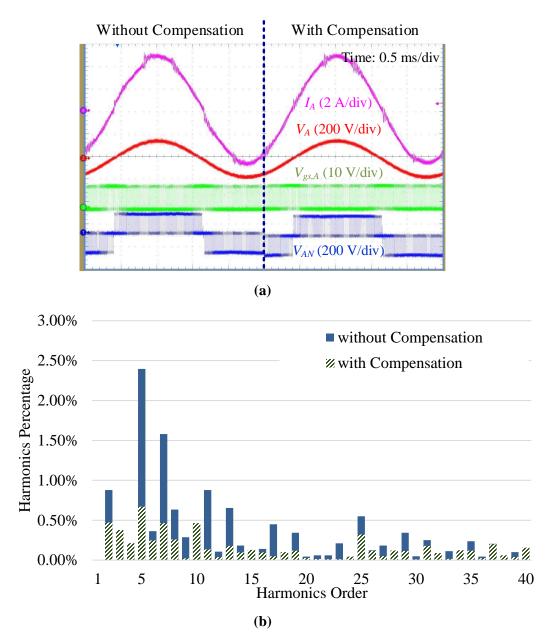

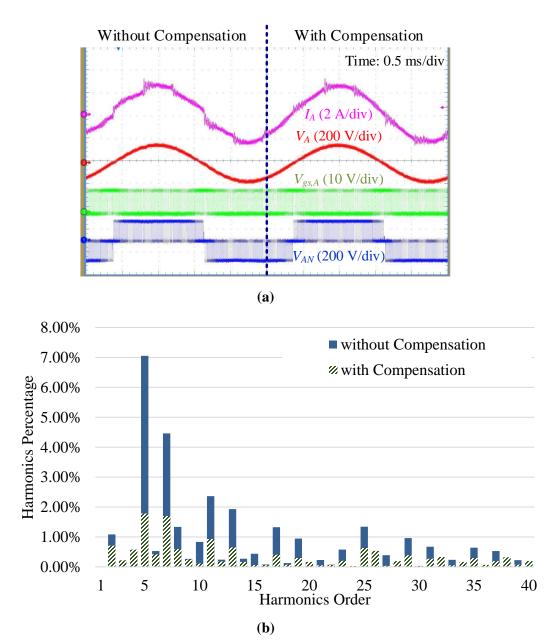

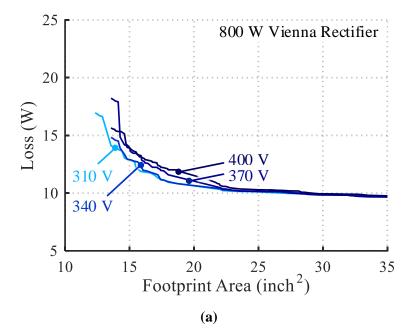

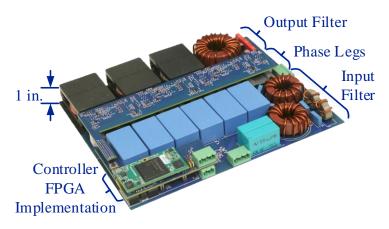

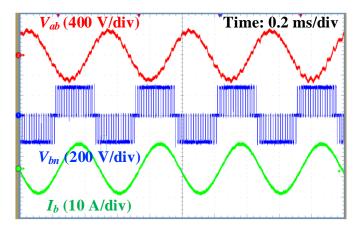

Chapter 3 focuses on the nominal power optimization of a form-factor-constrained loss-budget-limited active front-end converter (AFE). The nominal power optimization problem is converted to a sets of loss-size multi-objective optimization problems by using BLPP. The loss-size multi-objective problem is formulated using BLPP so that all the components are optimized locally and concurrently. The models for converter and component design are elaborated. A 1.2 kW Vienna rectifier prototype is constructed based on the design procedure, which validates the models and the procedure. Furthermore, a control method is proposed to compensate the turn-off delay of MOSFETs in Vienna rectifiers. The method is experimentally verified.

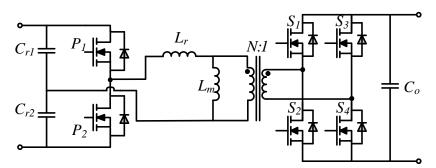

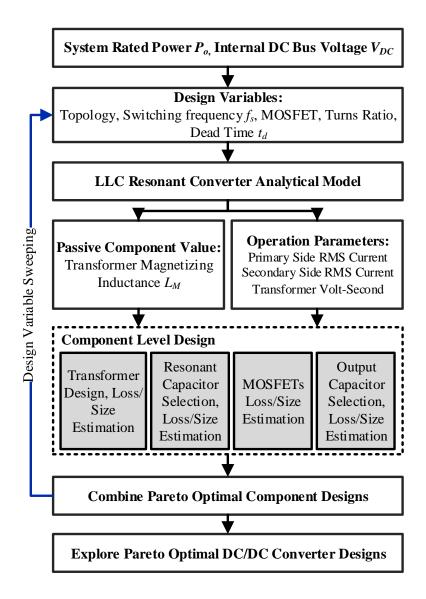

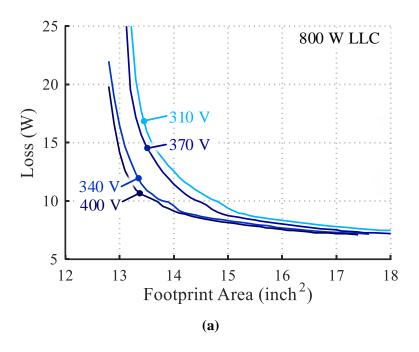

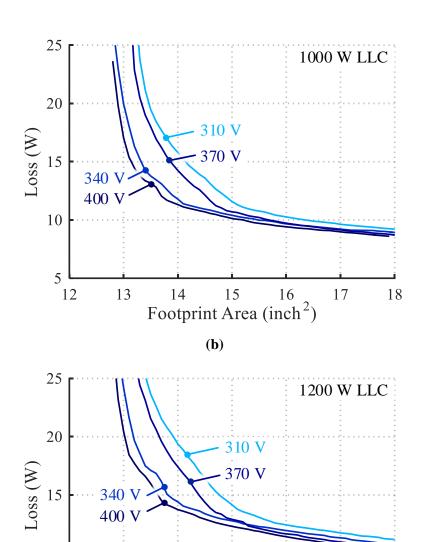

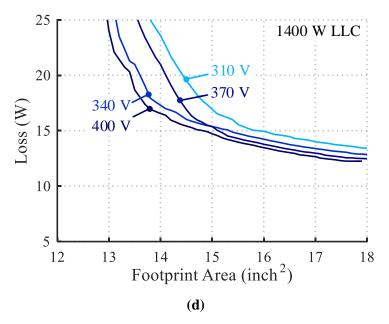

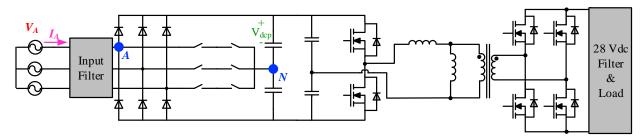

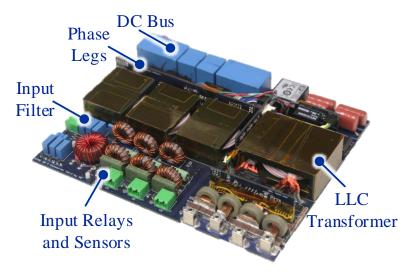

Chapter 4 extends the design of a single stage converter discussed in Chapter 3 to a two-stage isolated converter. The converter system consists of an AFE and an isolated dc/dc converter. However, the design constraints apply to the entire system. To deal with the two stages, another BLPP is cascaded to the design presented in Chapter 3. Models with attention paid to component model of dc/dc stage are detailed. Furthermore, the influence of the interconnecting dc bus voltage, a critical parameter to both stages, is studied. A 1.2 kW prototype consists of a Vienna rectifier and an LLC resonant converter is constructed. The testing results are presented.

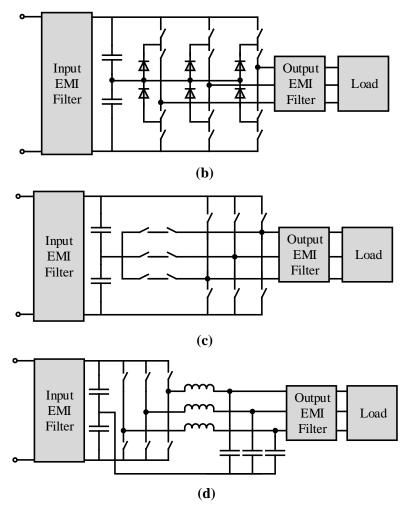

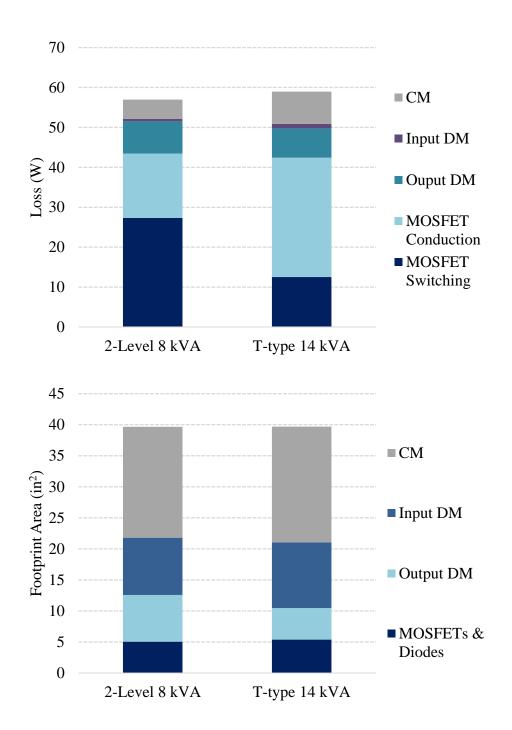

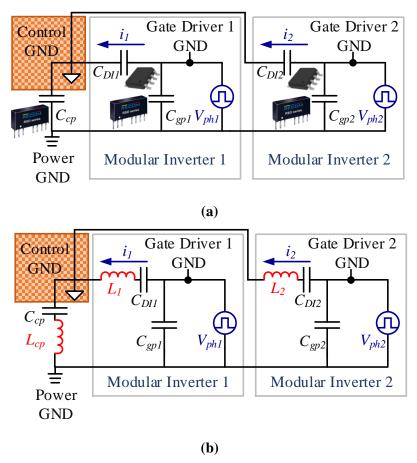

Chapter 5 presents the design and control of a modular inverter. Four topology including three hard-switching topologies and one soft-switching topology are considered, and their performance is compared by their maximum nominal power. Regarding modularity of power converter, an investigation on influence of form factor on maximum nominal power is presented. Besides converter design, the control architecture for paralleling the inverter modules is discussed. EMI

issues associated with parallel operation is analyzed. The testing results of a single module as well as paralleled modules are presented.

Chapter 6 concludes this work and proposes future work.

# Chapter 2. Measurement and Characterization of SiC MOSFET Switching Transients

#### 2.1 Chapter Introduction and Prior Art

Fig. 2-1. Wide-bandgap power semiconductor device feature superior performance. It enhances performance of power converters with different power levels.

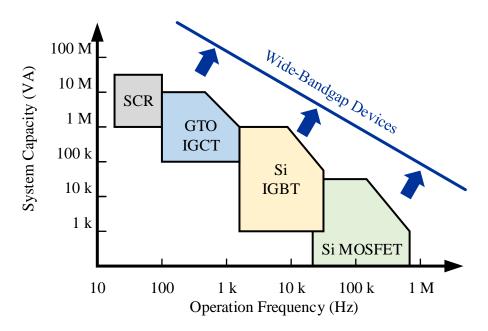

Wide-bandgap (WBG) semiconductor devices have been the main driving force of recent power electronics advancements [31, 104]. They are pushing the performance boundary from wattlevel applications to mega-watt-level applications thanks to their ability to operate at high breakdown voltage, wide temperature range and high switching frequency. The trend is depicted by Fig. 2-1. Specifically, for low voltage applications (blocking voltage less than 400 V), researchers have demonstrated converters that achieved boosted efficiency [105] and higher power density [104] thanks to the use of gallium nitride (GaN) MOSFETs. While for medium voltage

applications (greater than 400 V but less than 10 kV), silicon carbide (SiC) MOSFETs show superior conduction and switching performance in a wide temperature range [106]. Besides performance enhancement [39] as of GaN-based converters, SiC-based converters feature simple thermal management [107], reduced manufacture cost and lifetime cost [31]. For high voltage applications (greater than 10 kV), SiC MOSFET and IGBT [108] are potential replacements for GTO, IGCT and SCR. [109, 110] report using 15 kV SiC MOSFETs in a solid-state transformer for grid applications. To exploit benefits of WBG semiconductor devices, a comprehensive loss characterization, upon which circuit designers estimates semiconductor loss and optimize converter performance [56, 57, 59, 111, 112], is necessary. For conduction loss, on-resistance vs. temperature information provided in datasheets is normally accurate enough. However, characterizing switching loss is challenging, for the loss is highly dependent of testing condition and circuit parasitic [112]. In addition, reverse recovery loss from body diodes (PIN type, intrinsic) in SiC MOSFETs, which varies with switching current, transition speed, temperature and many other conditions, complicates the characterization [56, 57, 113]. Therefore, circuit designers usually conduct double pulse test (DPT) to measure switching loss. This chapter focuses on SiC MOSFETs switching transient study and loss characterization under 25 °C to 150 °C. Although only SiC MOSFETs are under test, the setup and the switching loss mechanism that are analyzed in this chapter apply to Si and GaN devices.

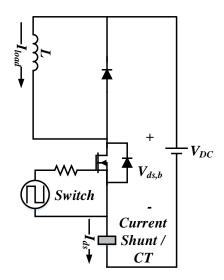

Fig. 2-2. Double pulse tester using diode as commutating device.

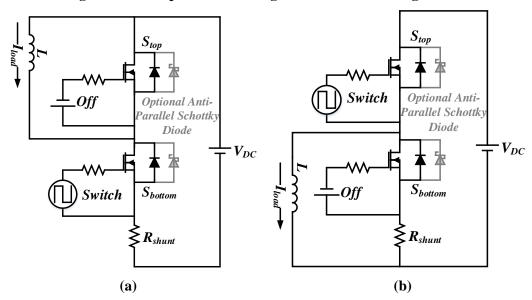

Fig. 2-3. (a) Bottom-device-switching test schematic. (b) Top-device-switching test schematic. Note that anti-paralleled Schottky diodes are optional.

Specifically, this chapter starts with the DPT setup for characterizing SiC MOSFETs that are in a phase-leg configuration. In most literatures [56-59], DPT circuits use diodes as top device for freewheeling and MOSFETs on the bottom as device under test (DUT) (configuration shown in Fig. 2-2). The current flowing through the DUT is measured by a low inductance shunt resistor [59] or a current transformer [57], and the drain-to-source voltage is measured by a voltage probe.

The switching energy is calculated from integrating the product of DUT voltage and current over time under the assumption that the freewheeling diode (top device) is "lossless". However, it will be shown in this chapter that there is considerable loss dissipated in top device no matter what type the device is. Furthermore, this configuration does not reflect the switching loss in a converter phase leg that consists of two MOSFETs owning to the unaccounted reverse recovery loss of body diode. To characterize the switching loss in a phase-leg configuration throughly, two tests are needed, namely, one with top device switching and the other with bottom device switching, (schematics shown in Fig. 2-3 (a) and (b) respectively). The top-device-switching configuration [113] (shown in Fig. 2-3 (b)) is a direct measurement of reverse recovery behavior of bottom device, and it shares the same equipment with the bottom-device-switching configuration. Comparing to other test setups for reverse recovery characterization, where either indirect current measurement (e.g. derive reverse recovery behavior of top device through measurements of bottom device in Fig. 2-3 (a)) [57] or an additional current measurement [114] is required, the bottom-device-switching configuration is accurate and easy-to-use.

With the aforementioned setup, the switching and reverse recovery characteristics of various SiC MOSFETs (2<sup>nd</sup> and 3<sup>rd</sup> generation devices from Wolfspeed) is studied. Ref. [57] reported the reverse recovery characteristics of CREE's 1<sup>st</sup> generation device (CPMF1200S080B). The influence of switching voltage, switching current, di/dt and temperature is thoroughly studied. Other literatures reported modeling of reverse recovery loss by different approaches. Ref. [56] proposed a physics-based reverse recovery model while [59] proposed a numerical model extracted from testing results. This chapter focused on evaluating devices with different die size (different die sizes but the same generation) and with different technologies (2<sup>nd</sup> and 3<sup>rd</sup> generation

from Wolfspeed) in a wide temperature range (25  $^{\circ}$ C ~ 150  $^{\circ}$ C). The loss related to charging the nonlinear junction capacitors and reverse recovery is analyzed in detail, which serves as fundamental for future switching loss modeling.

The testing results are used to model the switching loss in converter design that is presented in Chapter 3, Chapter 4 and Chapter 5.

# 2.2 Hardware Setup for Top-Device-Switching and Bottom-Device-Switching Tests

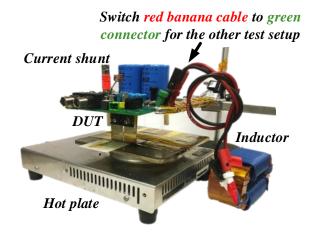

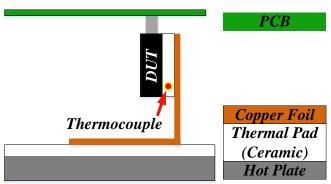

Fig. 2-4. Hardware setup of the two tests. They share the same hardware. Changing the inductor and gate signal connection changes the test type.

#### Fig. 2-5. Heating setup of the DUT.

The two tests share the same hardware, and the hardware setup is shown in Fig. 2-4. The connection of inductor and gate signals need to be changed for different tests. Optional diodes could be mounted in parallel with the MOSFETs for evaluating necessity of anti-parallel diodes. In addition, the device under test (DUT) is attached to a hot plate for junction temperature control, and a thermocouple is attached closely to the DUT to monitor the junction temperature (configuration shown in Fig. 2-5). For current measurement, a low inductance, high bandwidth current shunt (T&M Research Products SSDN-10) is used. For drain-to-source voltage measurement, a high voltage passive probe (Tektronix TPP0850) is used. The measurement ground is fixed at source of bottom device for both tests. All switches are driven by IXDN614CI (up to 35 V, 14 A) gate drivers. The gate resistance is changed for difference devices to keep the same *di/dt* during turn-on. Driving voltage is 20 V/ -5 V for 2<sup>nd</sup> generation devices and 15 V/ -5 V for 3<sup>rd</sup> generation device.

# 2.3 Analysis on Switching Transients

This section presents the data processing and results of the tests. Four devices from Wolfspeed: C2M0080120D (1200 V, 80 m $\Omega$ ), C2M0040120D (1200 V, 40 m $\Omega$ ), C2M0025120D (1200 V, 25 m $\Omega$ ) and C3M0065090D (900 V, 65 m $\Omega$ ) are tested. The first three are of the same technology (Wolfspeed's 2<sup>nd</sup> generation) but different die size. The latter is of the newest technology (3<sup>rd</sup> generation) and similar die size with C2M0080120D. These devices are tested under 540 V switching voltage (typical DC bus voltage on a modern airplane [39]), 2 ~ 36 A current and 25 ~ 150 °C junction temperature. In this work, the switch that is kept off during the test is termed

"commutating switch", and the other is termed "switching switch". The switch that is between positive rail and ac terminal is termed "top switch" or  $S_{top}$ , and the other is termed "bottom switch" or  $S_{bottom}$ .

In this section, the testing results and post-testing data processing of C2M0025120D is discussed as an example. The waveform analysis and post-testing data processing applies to other devices.

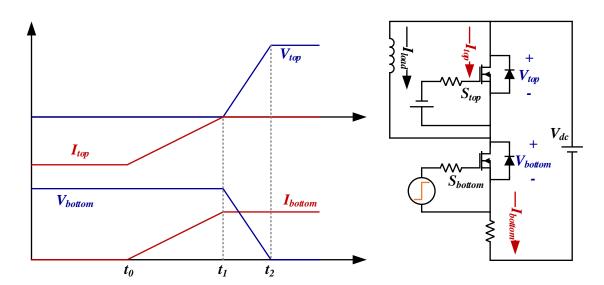

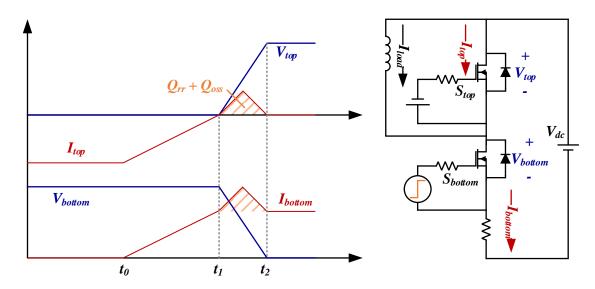

#### 2.3.1 Analysis of Turn-on Transient Based on Simplified Waveforms

This section analyzes the turn-on transients with simplified waveforms. First, assume the output capacitance of the two MOSFETs is zero, and there is no reverse recovery effect from the body diodes. Assume without losing generality, a bottom-device-switching test is conducted, and the switching switch (bottom switch) is turning on. The ideal waveforms of the turn-on transients and the corresponding schematic are depicted in Fig. 2-6. As  $I_{top}$  reaches zero,  $V_{top}$  starts to rise. The changing rate of both  $I_{top}$  and  $V_{top}$  is controlled by gate voltage. Because either  $I_{top}$  or  $V_{top}$  is zero at any time, there is no energy dissipated from or stored in the top switch. The energy dissipated from the bottom switch ( $E_{on,ideal}$ ) is induced by the overlap of voltage and current and is calculated by:

$$E_{on,ideal} = \int_{t_0}^{t_2} V_{bottom}(t) I_{bottom}(t) dt$$

(13).

In this chapter, the loss induced by overlap of voltage and current during switching switch turn-on is termed voltage-current overlap loss,  $E_{overlap}$ .

Fig. 2-6. Ideal current and voltage waveforms (assuming zero output capacitance and no reverse recovery effect) during turn-on of bottom switch.

Considering the reverse recovery effect of body diode and output capacitance of the MOSFETs, additional current that represents the reverse recovery charge and output capacitor charge going into the top switch is observed, and this phenomenon is depicted in Fig. 2-7. The "current bump" is observed when voltage of top device is building up (between  $t_1$  and  $t_2$ ). Charge is needed to remove the minority carriers from the body diode and to charge the output capacitor. The charge is provided by the dc source. The excessive energy ( $E_{dc,excessive}$ ) associated with providing the charge is calculated by:

$$E_{dc,excessive} = \int_{t_{1}}^{t_{2}} V_{top}(t) I_{top}(t) + V_{bottom}(t) (I_{bottom}(t) - I_{load}) dt = \int_{t_{1}}^{t_{2}} V_{top}(t) I_{top}(t) + V_{bottom}(t) I_{top}(t) dt = V_{dc} \int_{t_{1}}^{t_{2}} I_{top}(t) dt$$

(14).

Part of  $E_{dc,total}$  is stored in the output capacitor of top switch (also the commutating switch in this analysis), and the rest is dissipated. Term  $\int_{t_1}^{t_2} I_{top}(t)dt$  in (14) represents the total charge ( $Q_{total}$ )

provided by the dc source, including reverse recovery charge  $(Q_{rr})$  and charge in the output capacitor of commutating switch  $(Q_{oss})$ .

$$Q_{total} = \int_{t_{I}}^{t_{2}} I_{top}(t)dt = Q_{rr} + Q_{oss}$$

(15).

However, there is no practical method to separate  $Q_{rr}$  and  $Q_{oss}$  in real measurement. Therefore, datasheet information is used to calculate  $Q_{oss}$ :

$$Q_{oss}(V_{ds}) = \int_{0}^{V_{ds}} C_{oss}(v) dv$$

(16),

where  $Q_{oss}$  is a function of drain-to-source voltage  $V_{ds}$ . Then,  $Q_{rr}$  is calculated by:

$$Q_{rr} = Q_{total} - Q_{oss}(V_{dc}) \tag{17}.$$

Fig. 2-7. Voltage and current waveforms considering the reverse recovery effect and output capacitor. The "current bump" represents the charge for reverse recovery effect and output capacitor.

The aforementioned analysis is the basis of quantifying the loss from various loss mechanisms, namely, reverse recovery loss ( $E_{rr}$ ) of the body diode, output capacitor energy dissipated in channel

of switching switch ( $E_{oss,channel}$ ), commutating device capacitive charge induced loss ( $E_{oss,induced}$ , different from  $E_{oss,channel}$ ) and voltage-current overlap loss ( $E_{overlap}$ ).

## ightharpoonup Reverse recovery loss, $E_{rr}$

The reverse recovery loss is calculated by:

$$E_{rr} = V_{dc}Q_{rr} \tag{18}.$$

All the reverse recovery charge is provided by the dc source and will not return to the circuit (unlike charge stored in the output capacitor).

## ightharpoonup Output capacitor loss, $E_{oss,channel}$

The output capacitor loss  $E_{oss,channel}$  represents the energy stored in the output capacitor of switching switch ( $S_{bottom}$  in Fig. 2-7) and dissipated in the channel during device turn-on. It cannot be measured by external sensors (e.g. current shunt shown in Fig. 2-3) as the energy is dissipated internally. It is calculated using datasheet information:

$$E_{oss,channel} = \int_{0}^{V_{dc}} C_{oss}(v)vdv$$

(19),

where  $C_{oss}(v)$  represents the output capacitance at drain-to-source voltage v and can be got in datasheet.

#### $\triangleright$ Capacitive charge induced loss, $E_{oss,induced}$

The capacitive charge induced loss  $E_{oss,induced}$  measures the loss induced by charging the output capacitor of the commutating device, e.g.  $S_{top}$  in Fig. 2-10 (a). The charging of output capacitor is modeled as a dc source providing charge to a nonlinear capacitor. The energy provided by the dc source for charging the capacitor is calculated by:

$$E_{total oss} = V_{dc} Q_{oss} \tag{20},$$

where  $Q_{oss}$  is calculated by (16). The energy stored in the capacitor is  $E_{oss}$  (equals to  $E_{oss,channel}$ ), thus the capacitive charge induced loss is calculated by:

$$E_{oss,induced} = E_{total,oss} - E_{oss} = V_{dc}Q_{oss} - \int_{0}^{V_{dc}} C_{oss}(v)vdv$$

(21).

If the output capacitor is linear, i.e. not varying with the voltage, the capacitive charge induced loss will equal to the energy stored in the capacitor. However, owning to the nonlinearity, they are not equal. Equation (21) must be used to accurately quantify the loss.

## ► Voltage-current overlap loss, $E_{overlap}$

The rest of the energy dissipation is caused by the overlap of drain-to-source voltage and current.

The total turn-on loss  $(E_{on})$  is separated into four parts by their originating source:

$$E_{on} = E_{rr} + E_{oss,channel} + E_{oss,induced} + E_{overlap}$$

(22).

The loss mechanisms and calculation is summarized in TABLE I.

TABLE I. ORIGINS OF TURN-ON LOSS AND THEIR PROPERTIES

|                   | Origin                                                         | Dissipated in    | Related equations |

|-------------------|----------------------------------------------------------------|------------------|-------------------|

| $E_{rr}$          | Reverse recovery effect of body diode of commutating switch    | Both switches    | (18)              |

| $E_{oss,channel}$ | Capacitive energy of switching switch                          | Switching switch | (19)              |

| $E_{oss,induced}$ | Capacitive charge of commutating switch                        | Both switch      | (21)              |

| $E_{overlap}$     | Overlap of voltage and current during switching switch turn-on | Switching switch | (27)              |

## 2.3.2 Analysis of Turn-on Transients Using Measured Waveforms

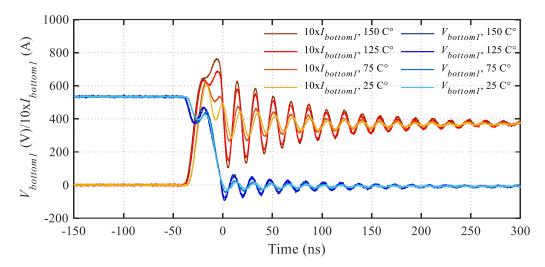

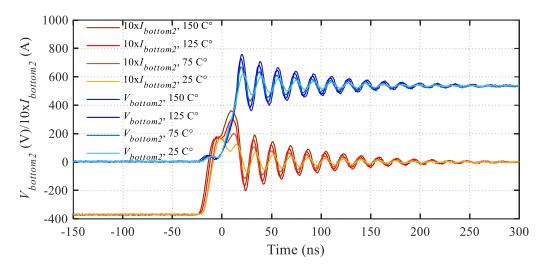

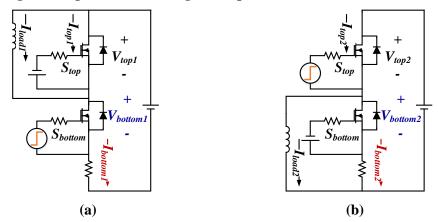

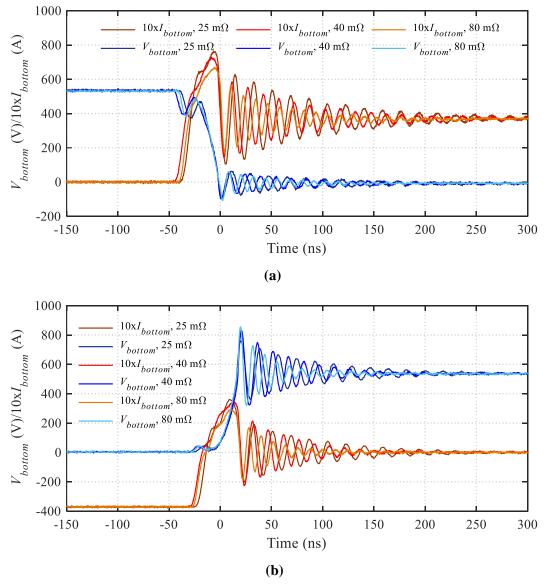

Fig. 2-8 and Fig. 2-9 show the waveforms during bottom device turn-on in bottom-device-switching tests and top device turn-on in top-device-switching tests, prospectively. The switching current is 36 A and voltage is 540 V. The corresponding test schematics are shown in Fig. 2-10.

The waveforms in Fig. 2-8 shows the turn-on drain-to-source voltage ( $V_{bottom1}$ ) and current ( $I_{bottom1}$ ) of the switching switch (bottom switch).  $I_{bottom1}$  rises as the gate signal is applied. When  $I_{bottom1}$  reaches load current, the same instant when  $I_{bottom2}$  in Fig. 2-9 reaches zero,  $V_{bottom1}$  starts to fall. The energy dissipated in the bottom device ( $E_{oss,channel}$  cannot be measured by the setup) is calculated by:

$$E_I = \int V_{bottomI}(t)I_{bottomI}(t)dt \tag{23}.$$

The integral interval should last until the ringing on voltage and current is well damped.

As is discussed in previous section (section 2.3.1), it is necessary to measure the current and voltage of the commutating device during device turn-on to get a complete loss characterization. This is done by the top-device-switching test (the schematic is shown in Fig. 2-10 (b)), and the waveforms are captured during top device turn-on. The energy flows into the commutating device is calculated by:

$$E_2 = \int V_{bottom2}(t)I_{bottom2}(t)dt \tag{24},$$

where waveforms of  $V_{bottom2}$  and  $I_{bottom2}$  are depicted in Fig. 2-9. The waveforms represents the drain-to-source voltage and current of commutating switch ( $S_{bottom}$  in Fig. 2-10 (b)) during turn-on of switching switch ( $S_{top}$  in Fig. 2-10 (b)), which resembles the voltage and current of  $S_{top}$  in the

bottom-device-switching test (Fig. 2-10 (a)). Part of  $E_2$  is stored in the output capacitor of  $S_{top}$ , because  $S_{top}$  is blocking the dc bus voltage. The other part is dissipated. The stored energy equals to  $E_{oss}$  (calculated in (19)).

Considering the capacitive energy of switching switch dissipated but not measured, and the energy stored in output capacitor of commutating, the total energy dissipated during device turn-on is:

$$E_{on} = E_1 + E_{oss,channel} + E_2 - E_{oss} = E_1 + E_2$$

(25).

Fig. 2-8. Bottom-device-switching test, bottom device turns on at 540 V, 36 A.

Fig. 2-9. Top-device-switching test, top device turns on at 540 V, 36 A.

Fig. 2-10. (a) Test setup for Fig. 2-8. (b) Test setup for Fig. 2-9.

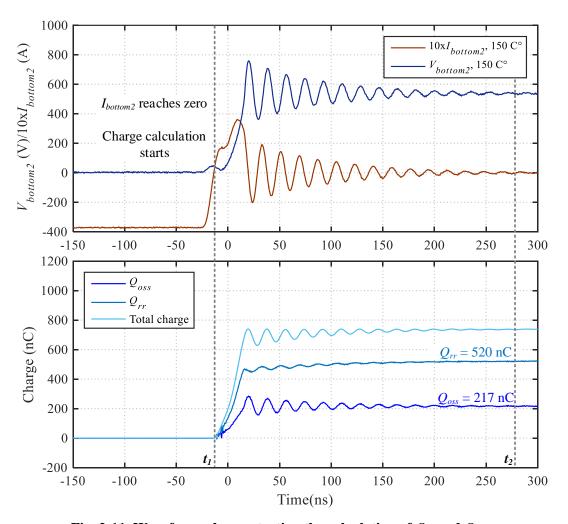

Furthermore, the measured waveforms are used to quantify the four types of loss described in section 2.3.1, namely,  $E_{rr}$ ,  $E_{oss,channel}$ ,  $E_{oss,induced}$  and  $E_{overlap}$ . The total charge ( $Q_{total}$ ) is calculated using the measured current in top-device-switching test. An example is depicted in Fig. 2-11. The  $Q_{total}$  is calculated as:

$$Q_{total} = \int_{t_l}^{t_2} I_{bottom2}(t) dt$$

(26).

Using (16) and (17), the output capacitor charge  $Q_{oss}$  and reverse recovery charge  $Q_{rr}$  are calculated accordingly. With this information and (18), (19) and (21),  $E_{rr}$ ,  $E_{oss,channel}$  and  $E_{oss,induced}$  are calculated. The  $E_{overlap}$  is expressed by:

$$E_{overlap} = E_{on} - E_{rr} - E_{oss,channel} - E_{oss,induced}$$

$$= E_{I} + E_{2} - V_{dc}Q_{rr} - \int_{0}^{V_{dc}} C_{oss}(v)vdv - (V_{dc}Q_{oss} - \int_{0}^{V_{dc}} C_{oss}(v)vdv)$$

$$= E_{I} + E_{2} - V_{dc}(Q_{rr} + Q_{oss}) = E_{I} + E_{2} - V_{dc}\int_{t_{I}}^{t_{2}} I_{bottom2}(t)dt$$

(27).

Fig. 2-11. Waveforms demonstrating the calculation of  $Q_{rr}$  and  $Q_{oss}$ .

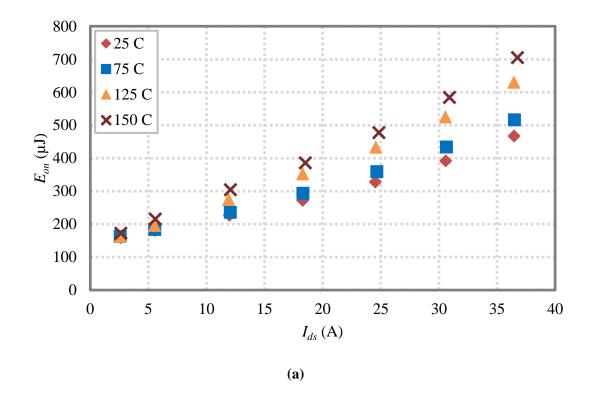

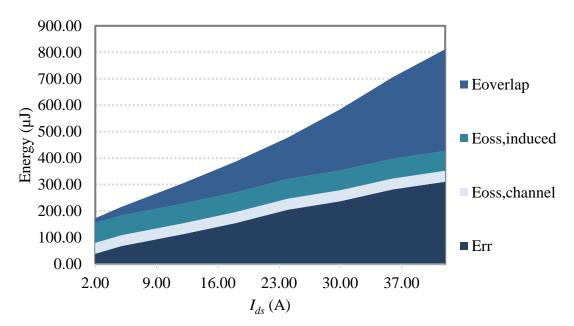

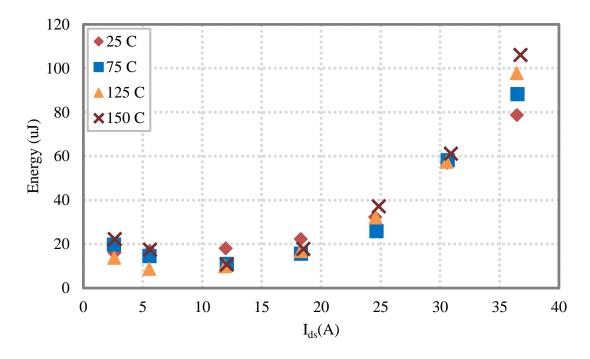

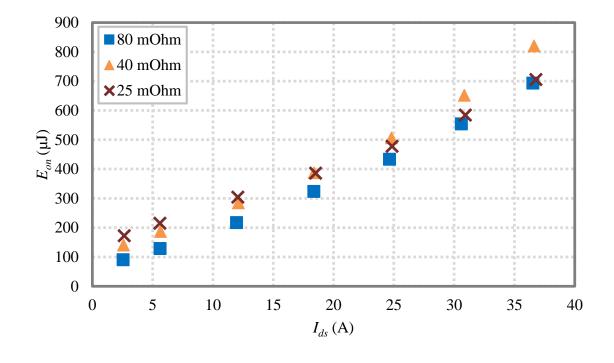

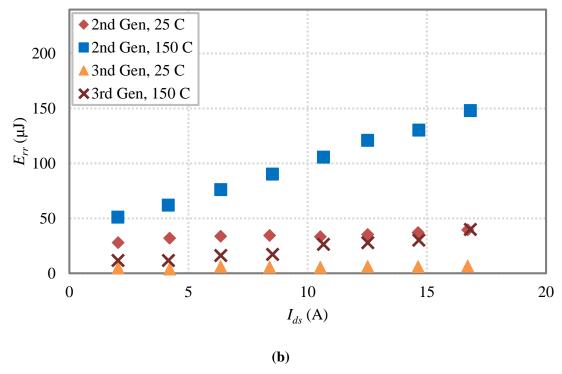

The tests are conducted under various current levels and device temperatures. The results of turn-on energy ( $E_{on}$ , calculated by (25)), the reverse recovery loss ( $E_{rr}$ , calculated by (18)) and voltage-current overlap loss ( $E_{overlap}$ , calculated by (27)) are summarized in Fig. 2-12 (a), (b) and (c) respectively. The  $E_{oss,channel}$  (calculated by (19)) and  $E_{oss,induced}$  (calculated by (21)) are constant and not depicted. They are 41.4  $\mu$ J and 74.4  $\mu$ J respectively (note that  $E_{oss,induced} > E_{oss,channel}$ ) for the device under test (CREE C2M0025120D).

Fig. 2-12. Energy dissipation related to turn-on of C2M0025120D. (a) Turn-on loss,  $E_{on}$ . (b) Reverse recovery loss,  $E_{rr}$ . (c) Voltage-current overlap loss,  $E_{overlap}$ .

As temperatures rises, the turn-on loss  $E_{on}$  increases. As is observed from Fig. 2-12 (b) and (c), major loss increase is from aggravated  $E_{rr}$ . The  $E_{overlap}$  stays constant at elevated temperatures. This matches with the waveforms in Fig. 2-8 and Fig. 2-9 that the di/dt and dv/dt stays constant but the amplitude of the "current bump" increases as temperature increases. In [9, 59], it is assumed that the voltage-current overlap loss is determined by gate speed and is independent of other factors (temperature, reverse recovery charge, etc.), an assumption served as foundation of most piecewise linear switching model [9, 59]. This observation backs the switching models in aforementioned literatures.

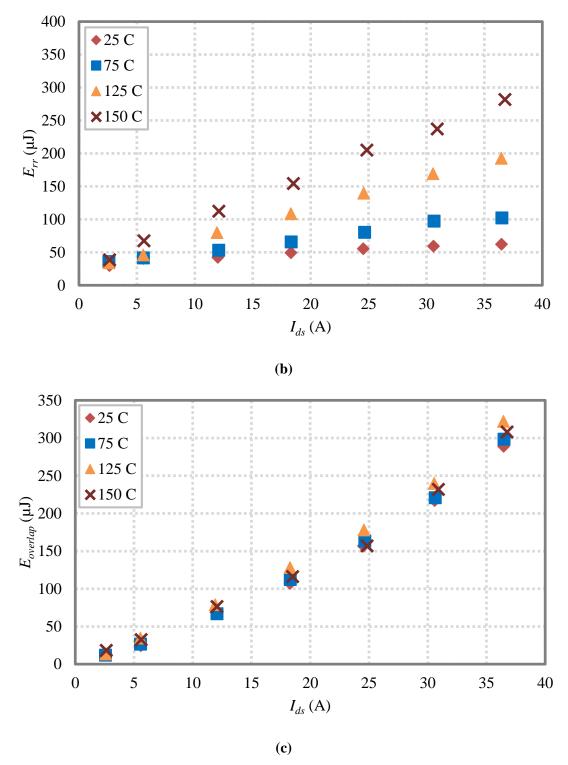

The energy breakdown of the turn-on loss of the DUT at 150 °C is depicted in Fig. 2-13. The  $E_{rr}$  and  $E_{overlap}$  dominate the turn-on energy.

Fig. 2-13. Turn-on energy breakdown of C2M0025120D, tested with 540 V voltage and 150 C° temperature.

Furthermore, the energy dissipated in the commutating switch ( $E_{commutating}$ ) is nontrivial. It is expressed as:

$$E_{commutating} = E_2 - E_{oss} (28),$$

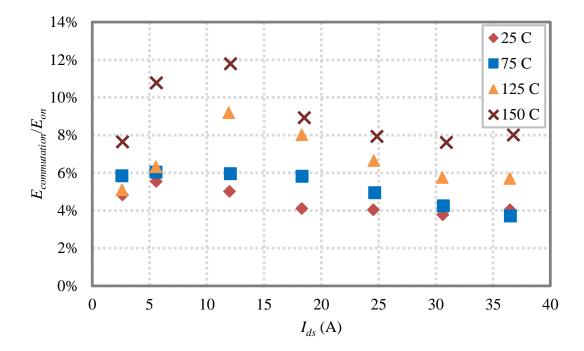

where  $E_2$  is calculated by (24) and  $E_{oss}$  is calculated by (19). It is 4 % to 12 % of the total turn-on loss for phase leg consisting of CREE C2M0025120D MOSFETs (depicted in Fig. 2-14). For C2M0040120D devices, it is up to 13 %. For C2M0080120D MOSFETs, it is up to 19 %. As  $E_{commutating}$  can only be directly measured by the top-device-switching test, it is necessary to conduct it to get an accurate and complete result.

Fig. 2-14. The percentage of  $E_{communitation}$  over  $E_{on}$  vs. current. The results of C2M0025120D device is shown here.

## 2.3.3 Analysis of Switching Transients during Device Turn-off

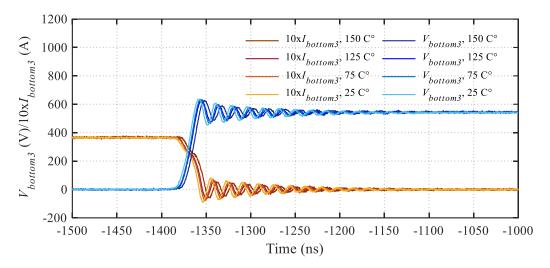

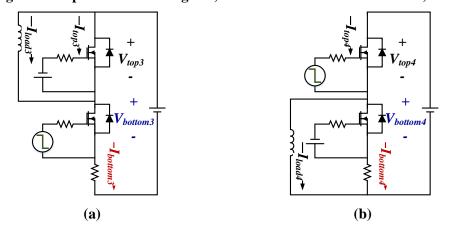

To measure the turn-off loss, both bottom-device-switching test and top-device-switching test are conducted, and the measured waveforms are shown in Fig. 2-15 and Fig. 2-16 respectively.

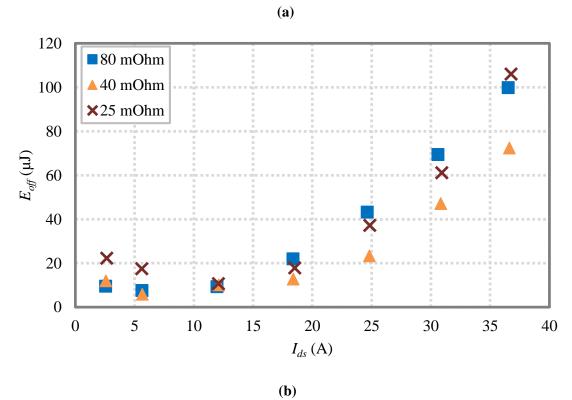

The bottom-device-switching tests measure the energy related to turn-off of the switching switch. The energy consists of the energy dissipated owning to voltage-current overlap and the energy stored in the output capacitor of switching device. The turn-off loss  $E_{off}$  is calculated by:

$$E_{off} = \int V_{bottom3}(t) I_{bottom3}(t) dt - E_{oss}$$

(29),

where  $V_{bottom3}$  and  $I_{bottom3}$  are shown in Fig. 2-15, and  $E_{oss}$  is calculated by (19). The measured  $E_{off}$  under various temperatures and current levels are summarized in Fig. 2-18. The temperature does not have big influence on turn-off loss.

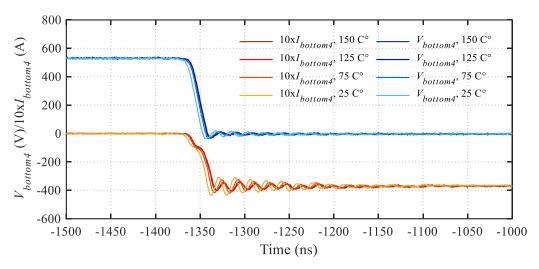

The top-device-switching tests measure the energy returned from the output capacitor of the commutating device to the circuit (load inductor or source), as the voltage and current have opposite polarity during the transient (shown in Fig. 2-16). The energy was stored during the turn-on of switching switch (described in section 2.3.1). This test can be used to check if the probes are calibrated and deskewed properly, as the returned energy should be equal to  $E_{oss}$ .

Fig. 2-15. Bottom-device-switching test, bottom device turns off at 540 V, 36 A.

Fig. 2-16. Top-device-switching test, bottom device turns off at 540 V, 36 A.

Fig. 2-17. (a) Test setup for Fig. 2-15. (b) Test setup for Fig. 2-16.

Fig. 2-18. Turn-off loss of C2M0025120D,  $E_{off}$ .

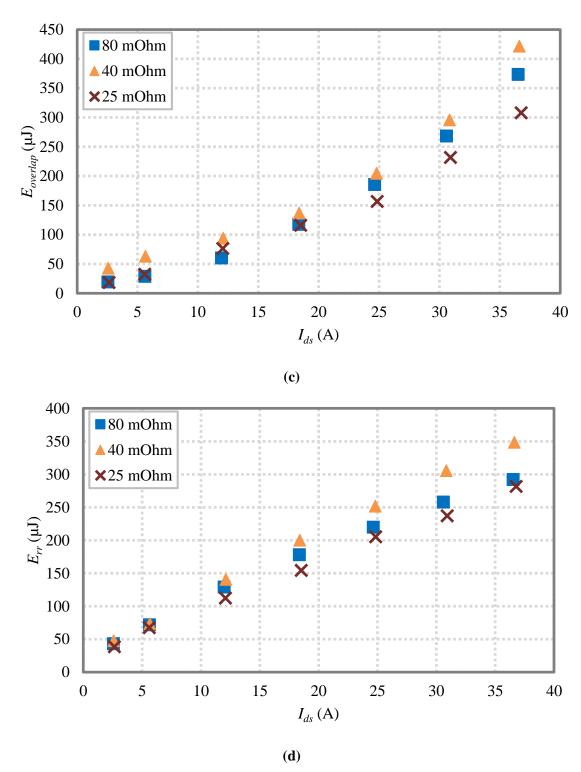

# **2.4** Comparison between Devices with Different Die Sizes

In this section, switching waveforms of MOSFETs with different die sizes (25 m $\Omega$ , 40 m $\Omega$  and 80 m $\Omega$ ) are compared. Their part numbers are C2M0025120D, C2M0040120D and C2M0080120D respectively. Fig. 2-19 shows the transient waveforms of the devices under test at 36 A, 540 V at 150 °C. Despite of different die sizes and junction capacitance, their di/dt and dv/dt are similar. In addition, the turn-on loss ( $E_{on}$ ) and reverse recovery loss ( $E_{rr}$ ) are depicted in Fig. 2-20 (a) and (b). Although 25 m $\Omega$  device (of the largest die size) is the lossiest at current levels below 20 A, 40 m $\Omega$  device dissipates the most energy at higher current owning to its highest reverse recovery induced loss (demonstrated in Fig. 2-20 (b)). One explanation to this is that,

besides the aforementioned factors, the reverse recovery is related with the total number of active device cells (active die size) as well as the current density in each cell. This observation indicates that larger die size (or junction capacitance) does not necessarily associate with higher switching loss. Device candidates should be carefully tested and/or modeled when designing converters.

Fig. 2-19. Voltage and current waveforms of devices with different die sizes (C2M0025120D, C2M0040120D and C2M0080120D) under 150 C°. (a) Bottom-device-switching test, bottom device turn-on. (b) Top-device-switching test, top device turn-on.

Fig. 2-20. (a) Turn-on loss of the DUTs at 150 °C,  $E_{on}$ . (b) Turn-off loss of the DUTs at 150 °C,  $E_{off}$ . (b) Voltage-current overlap loss of of the DUTs at 150 °C,  $E_{overlap}$ . (b) Revere recovery induced loss of DUTs at 150 °C,  $E_{rr}$ .

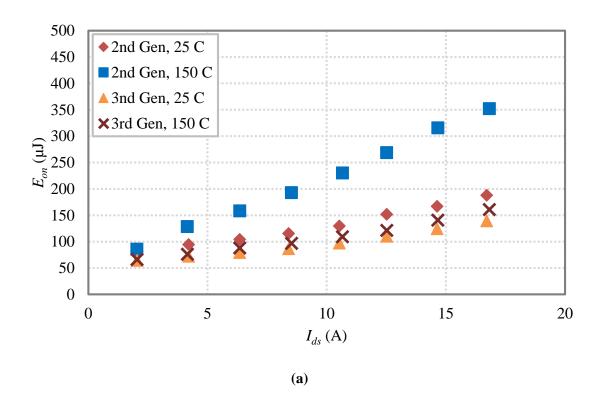

# 2.5 Comparison between 2<sup>nd</sup> and 3<sup>rd</sup> Generation Devices

A comparison of Wolfspeed's 2<sup>nd</sup> generation device (C2M0080120D) and 3<sup>rd</sup> generation device (C3M0065090D) is presented in this section. The two DUTs are of similar die size and junction capacitance. However, they perform differently at high junction temperature. The difference lies in the reverse recovery induced loss, which is depicted in Fig. 2-21 (b). Despite comparable augmentation ratio of reverse recovery induced loss, the 3<sup>rd</sup> generation device enjoys minute reverse recovery charge partially thanks to its thinner n- drift layer (though it has lower voltage rating). For applications that requires blocking voltage less than 600 V, e.g. 540 V dc bus voltage in modern aircrafts, the third generation device is a better fit than its 2<sup>nd</sup> generation counterpart.

Fig. 2-21. Comparison between CREE  $2^{nd}$  and  $3^{rd}$  generation devices. (a) Turn-on loss of 2nd and 3rd generation device,  $E_{on}$ . (b) Revere recovery induced loss of 2nd and 3rd generation devices,  $E_{rr}$ .

# 2.6 Chapter Conclusion

This work uses two tests, namely, top-device-switching and bottom-device-switching tests, to characterize switching of MOSFETs accurately. Its necessity is backed by theoretical analysis and experimental results (without conducting top-device-switching the test, an error up to 19 % was found). Detailed data processing is presented, where partitioning turn-on loss is in focus. The results show that, with the same driving circuit, voltage-current overlap induced loss does not change much when junction temperature changes while reverse recovery induced loss increases at elevated temperature. The turn-on loss partition and analysis suggest that modeling turn-on loss should be partitioned into three segments, namely, voltage-current overlap modeling, capacitive

charge modeling and reverse recovery modeling. Furthermore, the tests have been conducted in a wide temperature range (25  $^{\circ}$ C  $^{\circ}$ C) with different MOSFETs (various die sizes and technologies). The testing results show the complexity of relating die size to switching loss. In addition, the comparison between 2<sup>nd</sup> and 3<sup>rd</sup> generation devices demonstrates the superiority of 3<sup>rd</sup> generation devices.

Chapter 3. Nominal Power Maximization of Power

Converters – An Active Front-End Converter Case Study

## 3.1 Chapter Introduction and Prior Art

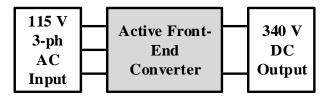

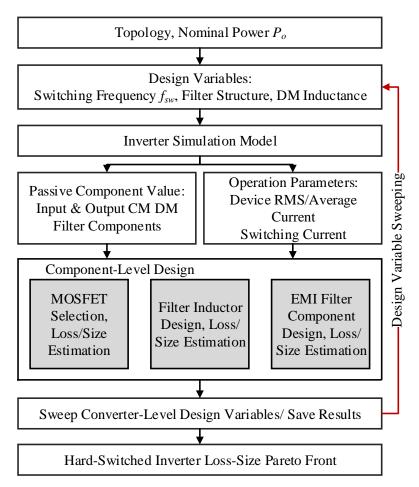

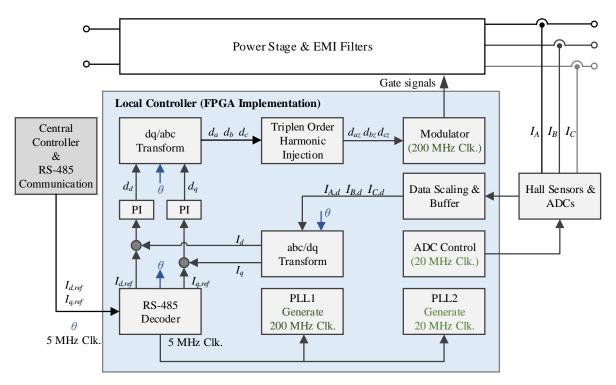

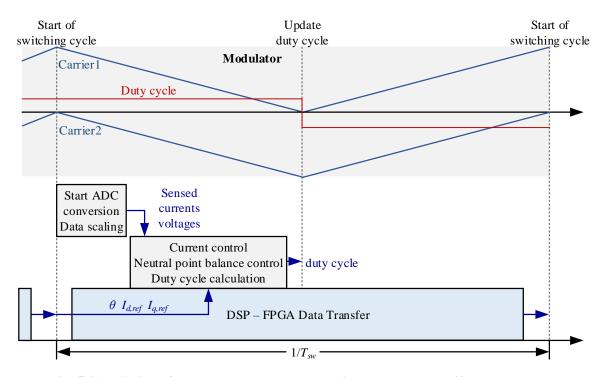

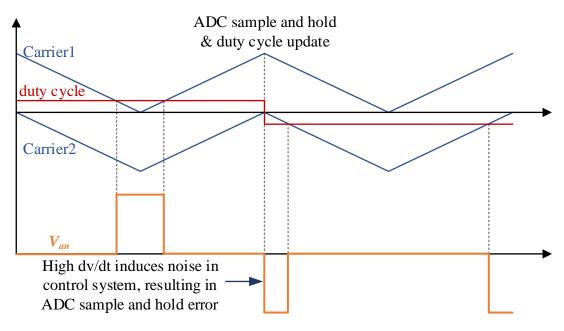

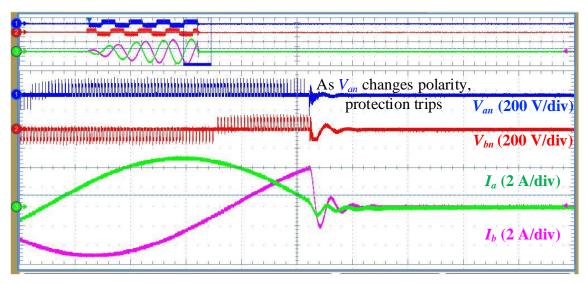

This chapter focuses on design of modular active front-end converters that mount to racks and can work in parallel to allow scalability. In this design, converter form factor is fixed by dimensions of chassis racks. Furthermore, thermal management and electromagnetic interference (EMI) are of great importance to system integration, which renders a set of electrical and mechanical design constraints. Although this scenario is frequently seen in commercial converter design [115, 116], few literatures talk about design approach considering all the constraints while optimizing the performance. This chapter presents a novel approach for designing form-factorconstrained power electronics converters. The design objective is to maximize nominal power of the power supply unit under the constraints of form-factor, heat dissipation, EMI and cooling. Designing for maximum nominal power unveils the potential of modular power converters given the practical limitations and leads to optimal system design. Specifically, a three-phase active front-end converter for aerospace applications is under investigation. The system schematic is shown in Fig. 3-1, and the specifications and design constrains are listed in TABLE II. The bilevel integrated system synthesis (BLPP) introduced in Chapter 1 is used to frame the design procedure.

Fig. 3-1. System under investigation. The active front-end converter converts 115 Vac variables frequency three-phase input to 340 Vdc output (internal output, not connected to any bus).

TABLE II. SINGLE-PHASE AFE CONVERTER TARGETS AND SPECIFICATIONS

| Items                  | Target/Specification                  |  |

|------------------------|---------------------------------------|--|

| Input Voltage          | Single phase 115 Vac                  |  |

| Input Frequency        | 360 Hz ~ 800 Hz                       |  |

| Output Voltage         | 340 V                                 |  |

| Output Power           | TBD                                   |  |

| Loss budget            | 18 W                                  |  |

| Form Factor            | $35 \text{ in}^2 \times 1 \text{ in}$ |  |

| Cooling                | Free Convection Air-Cooling           |  |

| Power Quality Standard | DO-160E                               |  |

| EMI Standard           | DO-160E                               |  |

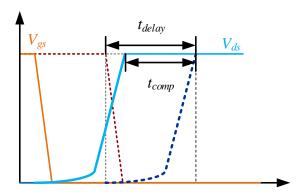

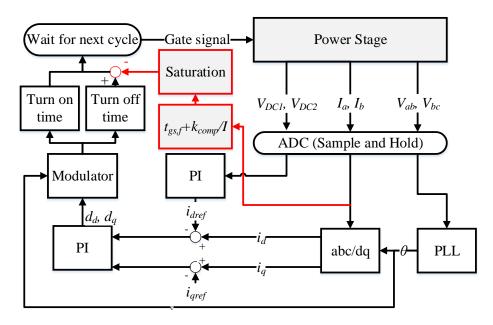

Besides converter design, a control method is proposed to improve input power quality for the constructed prototype (a Vienna rectifier) in order to meet power quality standard in question. The power quality issue caused by junction capacitors of diodes and active switches in Vienna rectifiers has been reported in [33, 117]. [33] claims that charging and discharging of junction capacitors results in "turn-off delay" in phase leg output voltage, and it distorts the input current. Both literatures use a feedforward loop to compensate the delay time, but with different models for delay time calculation. Ref. [33] uses a numerical model extracted from experimental observation. Although the model is accurate, its extraction is time-consuming. On the other hand, [117] derives an analytical model based on the assumption that voltage rising slope is constant during turn-off.

However, as it will be shown in this chapter, the aforementioned assumption is inaccurate owning to non-linear junction capacitance, and the model should be modified. In this chapter, a delay time model based on datasheet information is developed, upon which the control method for power quality improvement is proposed and experimentally verified.

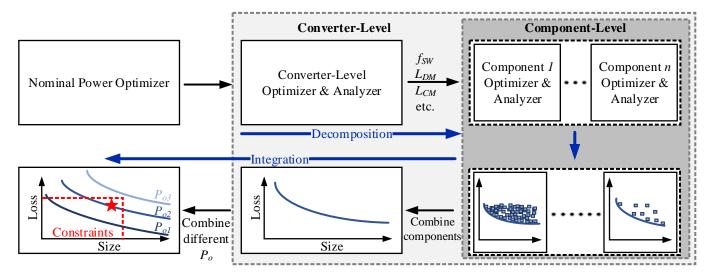

## 3.2 Nominal Power Maximization for Form-Factor-Constrained Converter

## 3.2.1 Bi-level programming problem (BLPP) for Nominal Power Maximization

The nominal power maximization is an optimization problem, of which the typical formulation is

$$\min/\max F(x) \tag{30},$$

$$s.t. g(x) \le 0 \tag{31},$$

where  $F(x) = [F_1(x) \cdots F_z(x)]^T$  are the objective functions,  $x = [x_1 \cdots x_i \cdots x_n]^T$  is the design vector consisting of the design variables, and  $g(x) = [g_1(x) \cdots g_n(x)]^T$  represent design constraints [7]. Using a single-level optimization framework (framework depicted in Fig. 1-6), the nominal power maximization problem is described as:

$$\max P_{\text{nominal}}(x) \tag{32},$$

s.t.

$$g(x) \le 0$$

(33).

In the above expression,  $P_{nominal}(x)$  is the nominal power to be maximized, and it is a function of vector x, which consists of design variables in a converter, e.g. topology, switching frequency,

component selection, etc. g(x) stands for the design constraints such as form factor, loss budget and EMI standard. Despite the simple form, it is hard to formulate this maximization problem owning to the complication of linking converter design variables to its nominal power. Therefore, this work proposes to translate the problem into a BLPP [83] problem of which the upper-level optimization is formulated as:

$$\max P_{\text{nominal}}(x_{upper}, y_{lower}) = p_{\text{nominal}} \text{ where } x_{upper} = p_{\text{nominal}}$$

(34),

s.t.

$$G(x_{upper}, y_{lower}) = [P_{loss}(x_{upper}, y_{lower}) - 18 \quad A_{converter}(x_{upper}, y_{lower}) - 35]^T \le 0$$

(35),

where the objective function, nominal power, equals to the upper-level design variable ( $x_{upper}$ ),  $p_{nominal}$ , and  $y_{lower}$  is defined by the lower-level optimization described below:

$$\min f(x_{upper}, z) = [P_{loss}(x_{upper}, z) \quad A_{converter}(x_{upper}, z)]^{T}$$

(36),

$$s.t. g(x_{upper}, z) \le 0 \tag{37},$$

$$y_{lower} \in \arg\min\{f(x_{upper}, z) = [P_{loss}(x_{upper}, z) \quad V_{converter}(x_{upper}, z)]^T : g(x_{upper}, z)\}$$

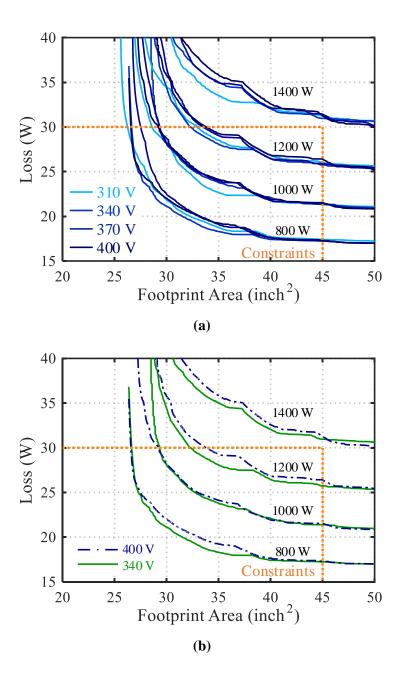

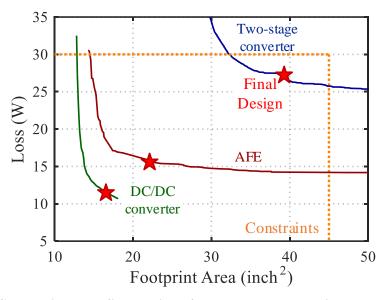

(38),

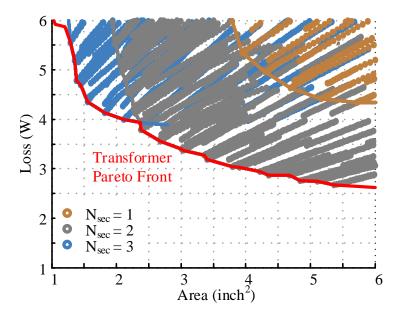

where z is the design vector,  $P_{loss}$  represents converter loss,  $A_{converter}$  represents converter area and  $g(x_{upper}, z)$  represents all design constraints except loss and form factor limitations. The solution to the lower-level problem is  $y_{lower}$ . The lower-level optimization, per se, is a loss-size multi-optimization problem, which have been widely discussed and used in power converter design [5, 24, 31]. Multiple Pareto optimal designs, i.e.  $y_{lower}$  consisting of a group of design vectors that leads to Pareto optimal  $f(x_{upper}, z)$ , are expected. The bi-level nominal power maximization problem is visualized in Fig. 3-2.

Fig. 3-2. Bi-level optimization framework for nominal power maximization.

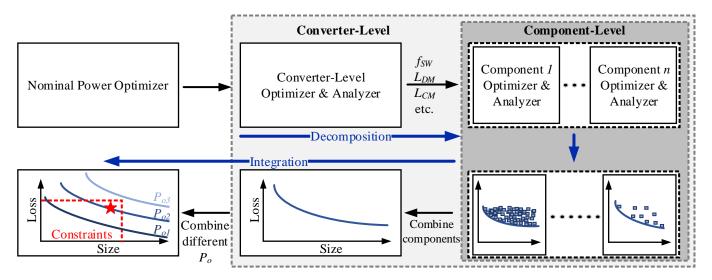

#### 3.2.2 BLPP for Converter Loss-Size Multi-Objective Optimization

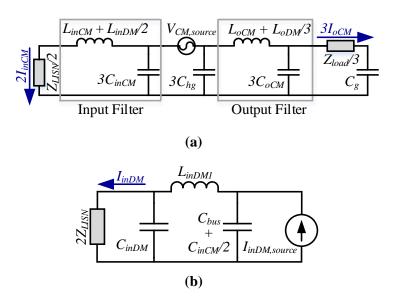

Instead of single-level optimization framework, this work applies BLPP to the loss-size optimization. The loss-size optimization problem is decomposed into converter-level (upper-level) and component-level (lower-level) so that all components are optimized locally and concurrently, and the framework is depicted in Fig. 3-3. The converter-level optimization problem is formulated as:

$$\min f_{converter}(p_{no\min al}, x_{converter}, y_{comp}) = \left[\sum_{i=1}^{n} P_{loss,i}(p_{no\min al}, x_{converter}, y_{comp,i}) - \sum_{i=1}^{n} A_{i}(p_{no\min al}, x_{converter}, y_{comp,i})\right]^{T}$$

(39),

s.t.

$$g_{converter}(p_{nominal}, x_{converter}, y_{comp}) \le 0$$

(40),

where  $x_{converter}$  is the converter-level design vector consists of switching frequency, EMI filter parameters (structure, inductance and capacitance),  $P_{loss,i}$  represents loss,  $A_i$  represents area of the i<sup>th</sup> component and  $g_{converter}(p_{nominal}, x_{converter}, y_{comp})$  represents all design constraints except loss and form factor limitations.

Each component-level optimization is formulated as:

$$\min f_{comp,i}(w_{converter}, z_i) = [P_{loss,i}(w_{converter}, z_i) \quad A_i(w_{converter}, z_i)]^T$$

(41),

s.t.

$$g_{comp,i}(w_{converter}, z_i) \le 0$$

(42),

$$y_{lower,i} \in \arg\min\{f_{comp,i}(w_{converter}, z_i) = [P_{loss,i}(w_{converter}, z_i) \quad A_i(w_{converter}, z_i)]^T : g_{comp,i}(w_{converter}, z_i)\}$$

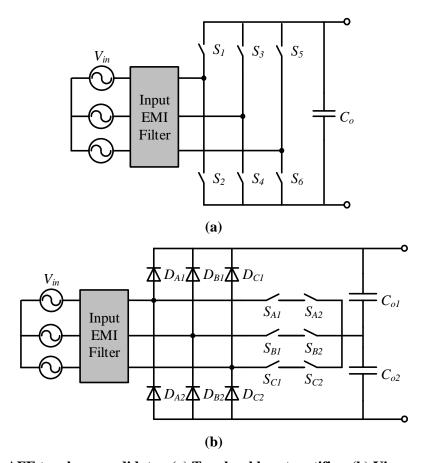

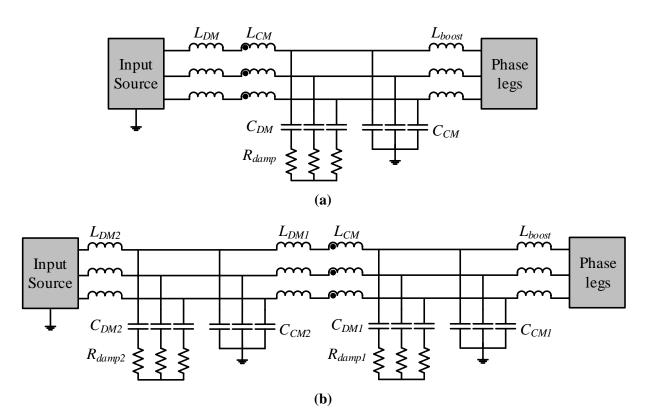

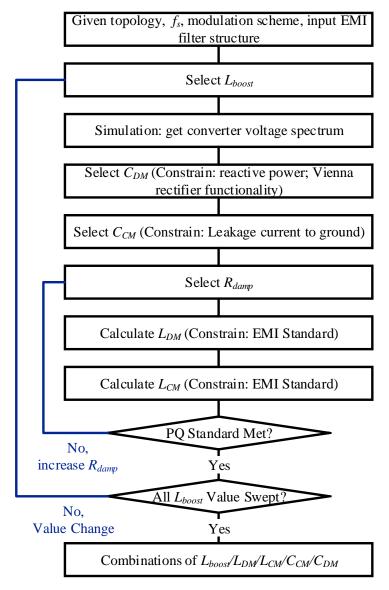

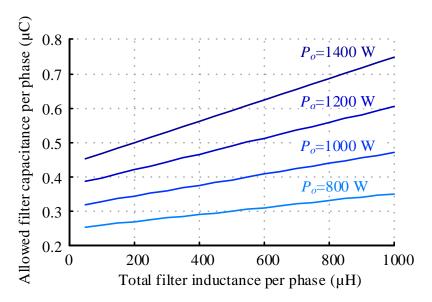

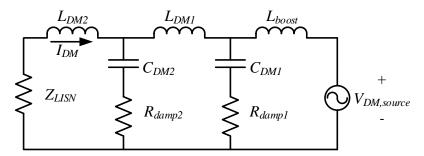

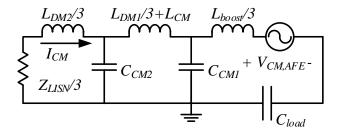

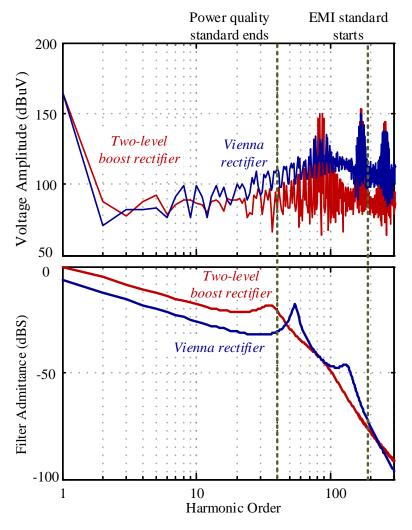

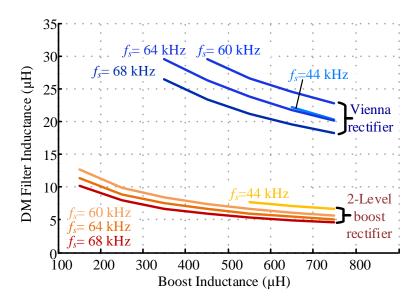

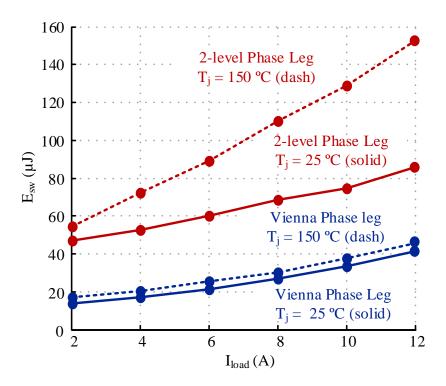

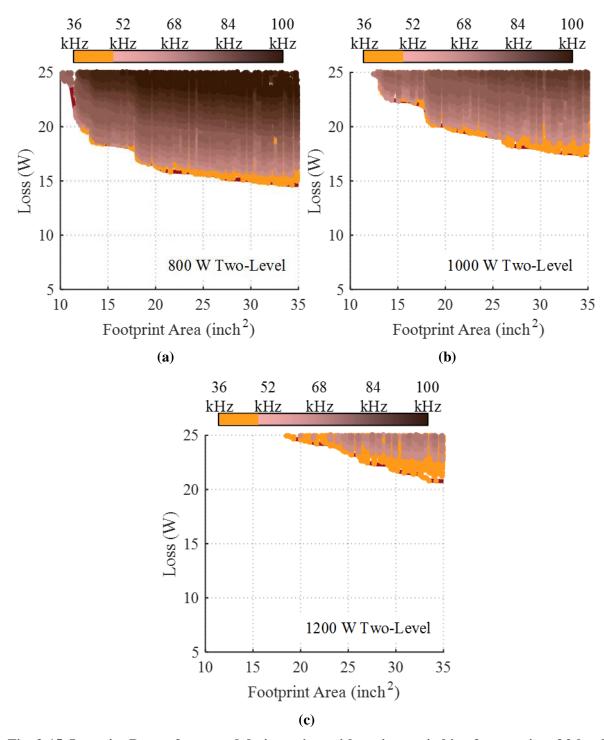

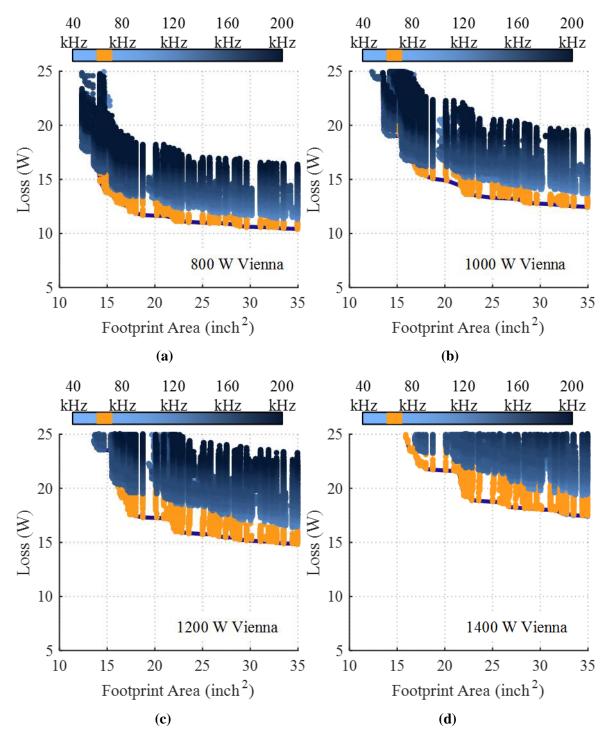

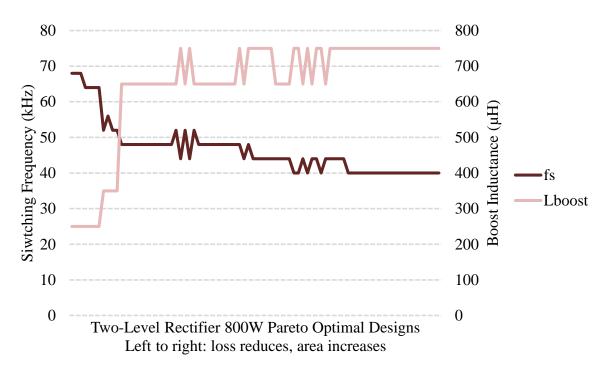

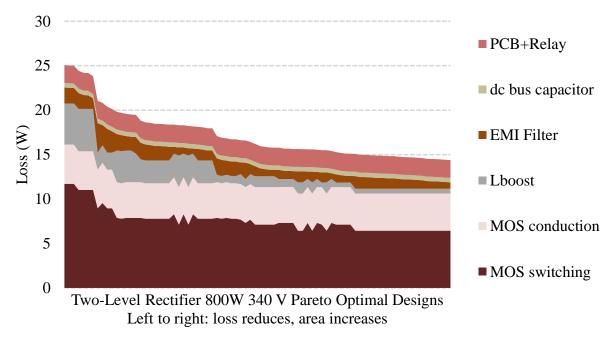

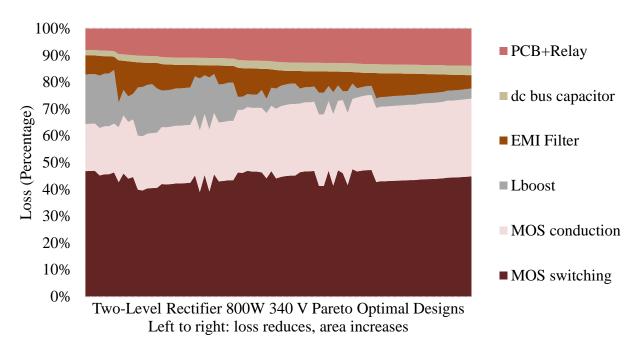

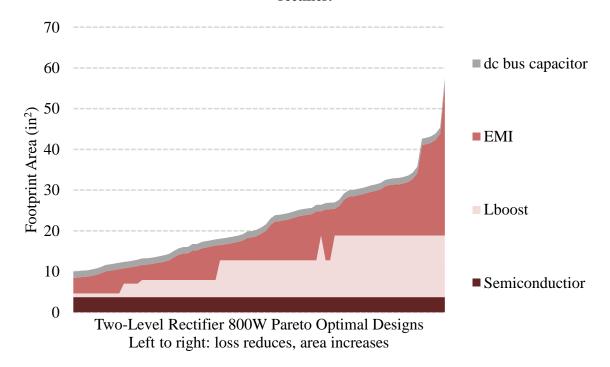

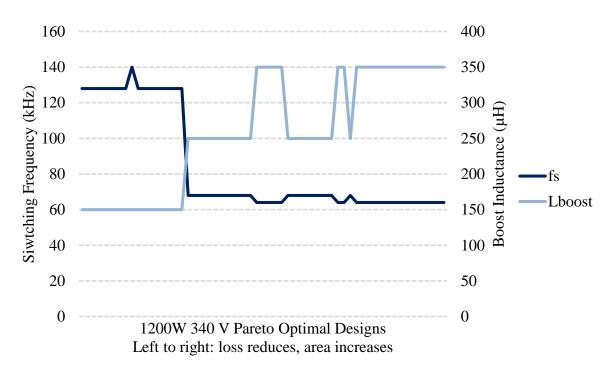

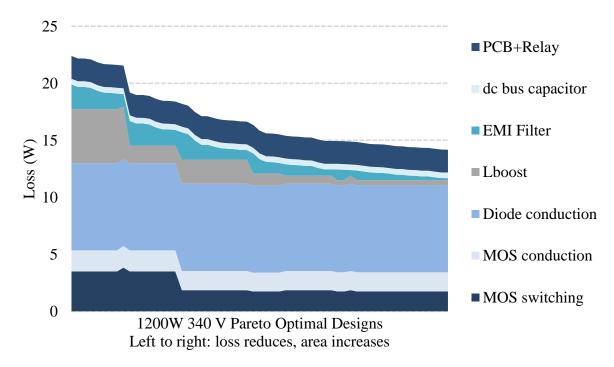

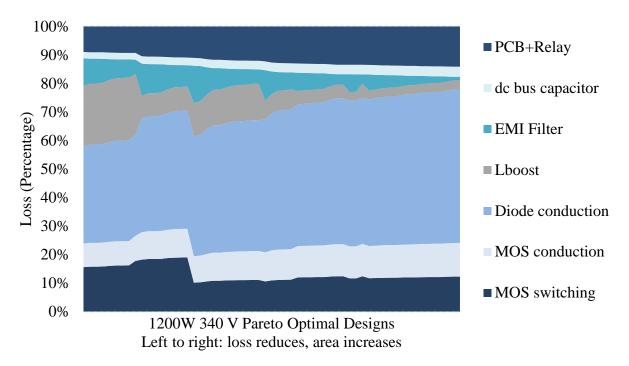

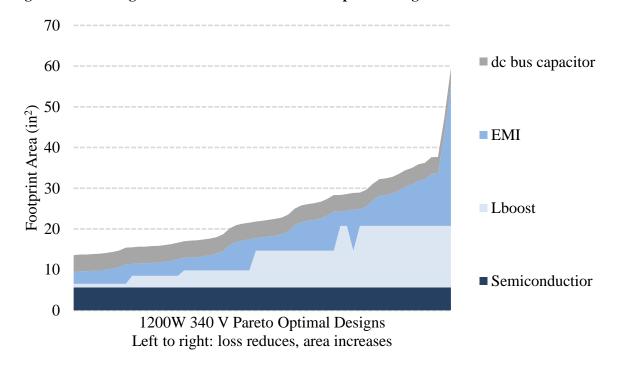

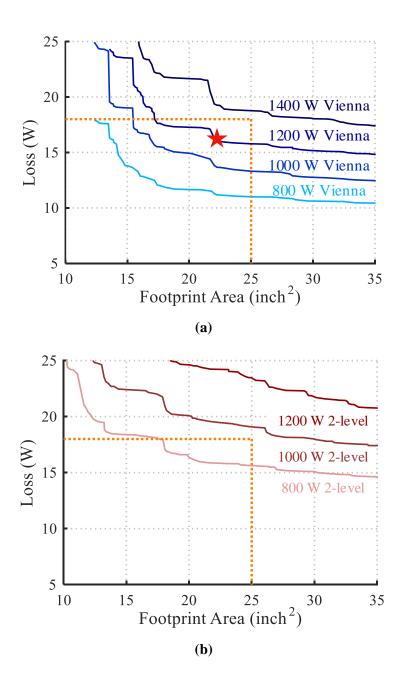

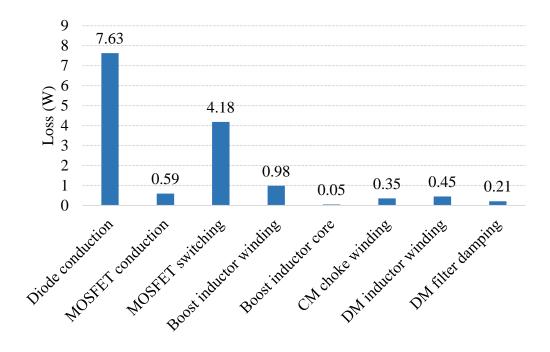

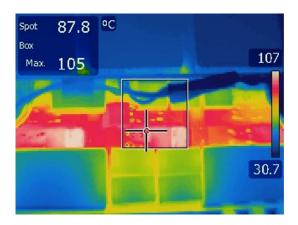

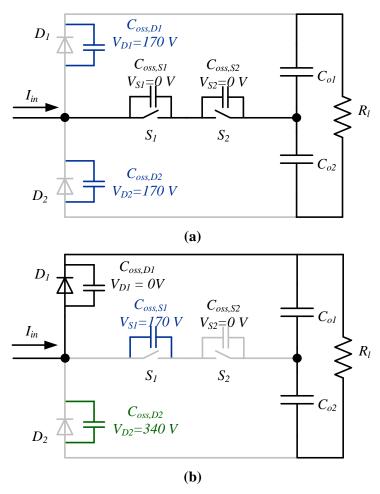

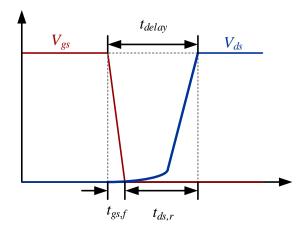

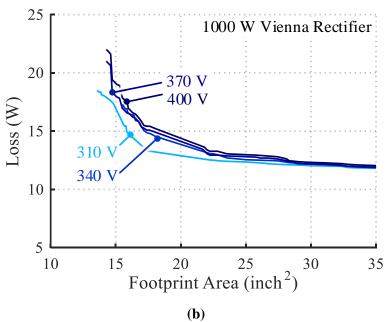

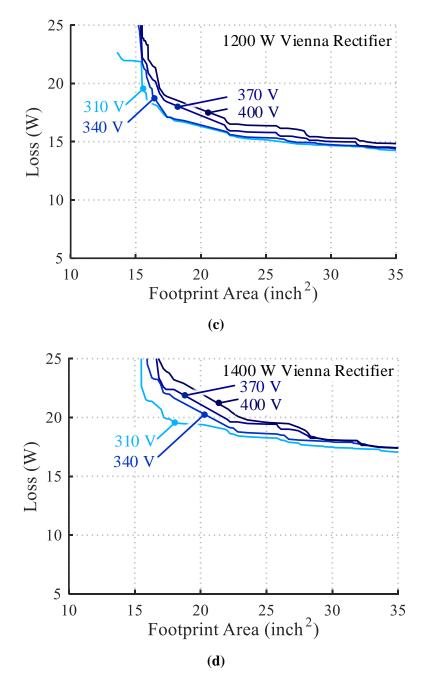

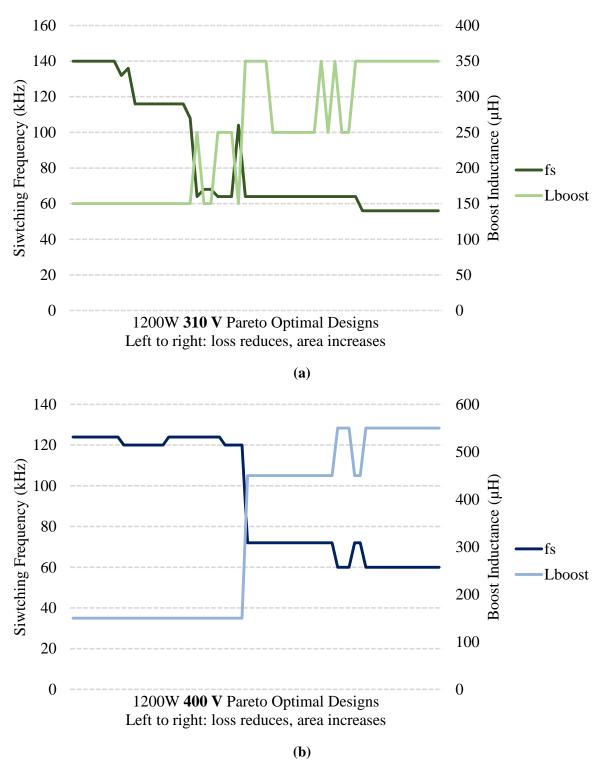

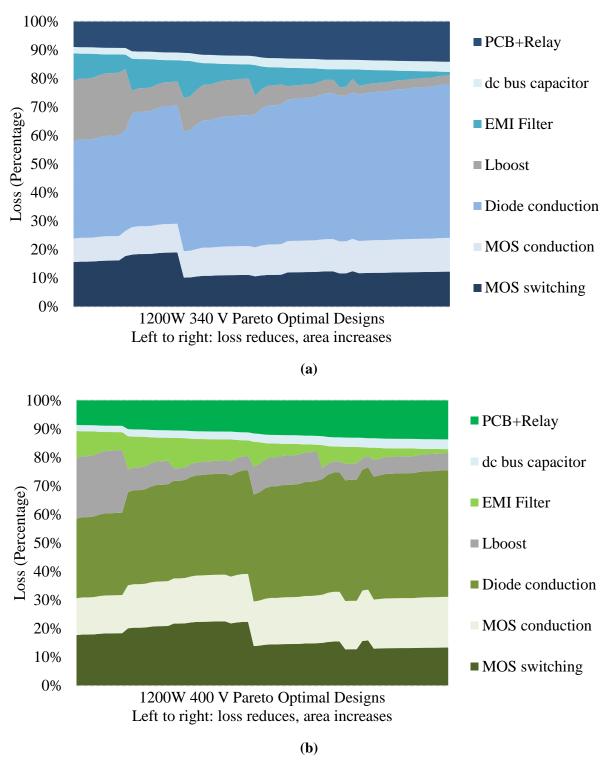

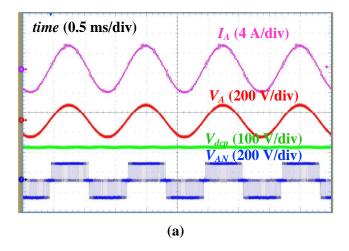

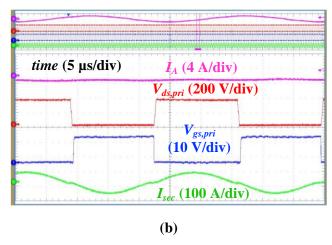

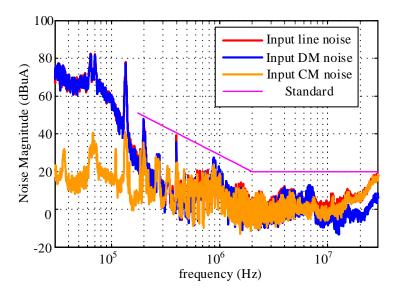

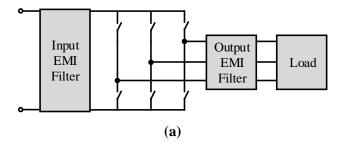

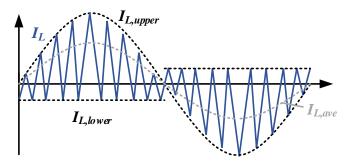

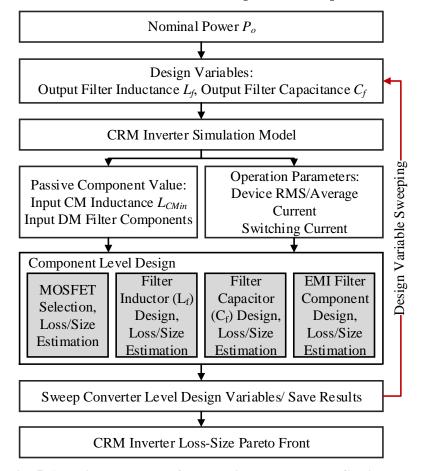

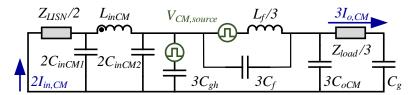

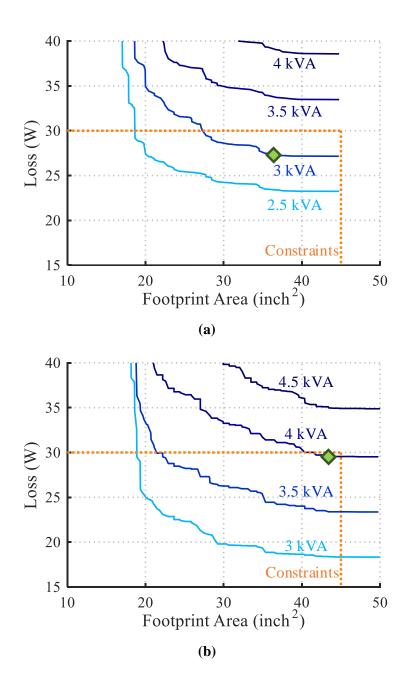

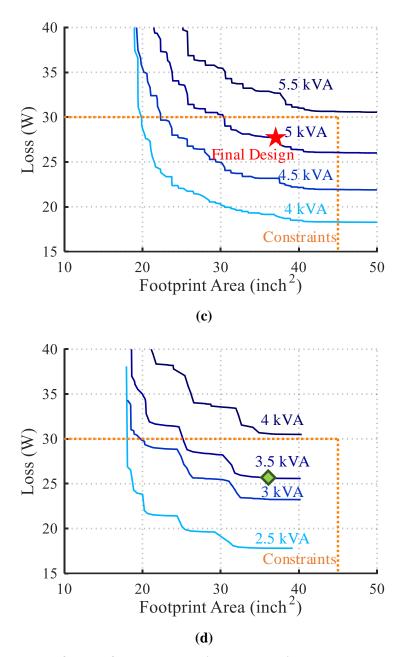

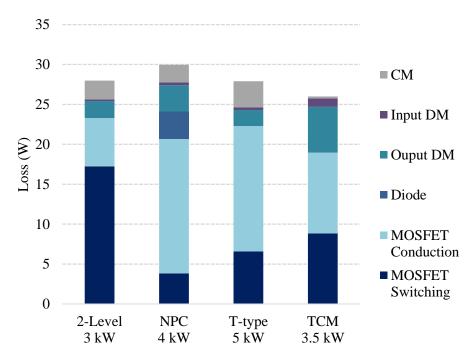

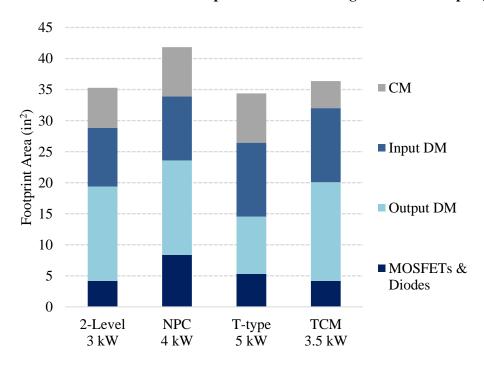

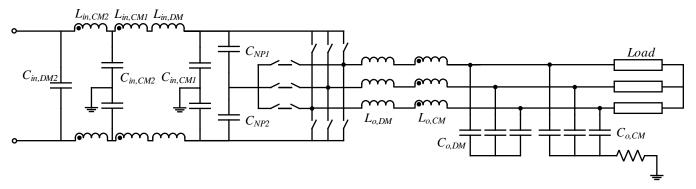

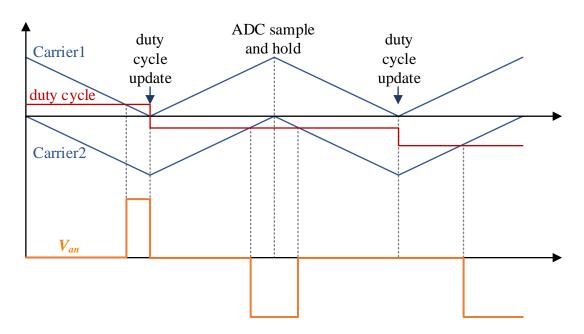

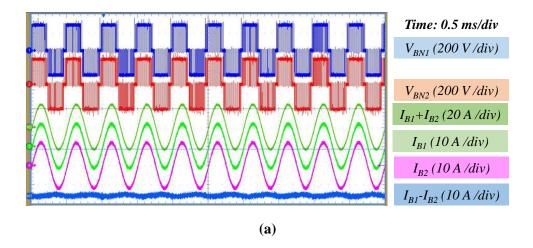

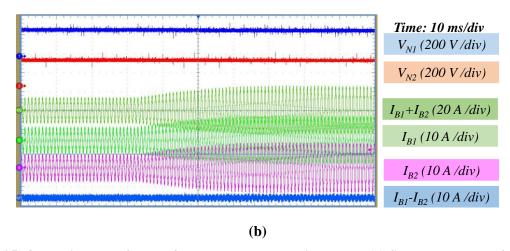

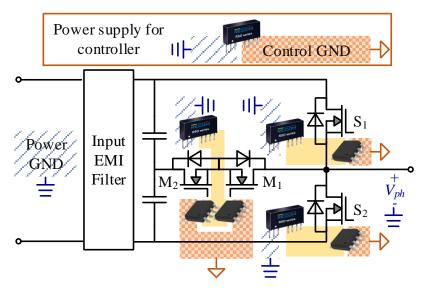

$$(43),$$