#### Popcorn Linux: A Compiler and Runtime for Execution Migration Between Heterogeneous-ISA Architectures

Robert F. Lyerly

Dissertation submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

> Doctor of Philosophy in Computer Engineering

Binoy Ravindran, Chair Changhee Jung Cameron D. Patterson Paul E. Plassmann Haibo Zeng

March 22, 2019 Blacksburg, Virginia

Keywords: heterogeneous architectures, compilers, runtime systems Copyright 2019, Robert F. Lyerly

#### Popcorn Linux: A Compiler and Runtime for State Transformation Between Heterogeneous-ISA Architectures

# Robert F. Lyerly ABSTRACT

In recent years there has been a proliferation of parallel and heterogeneous architectures. As chip designers have hit fundamental limits in traditional processor scaling, they have begun rethinking processor architecture from the ground up. In addition to creating new classes of processors, chip designers have revisited CPU microarchitecture in order to target different computing contexts. CPUs have been optimized for low-power smartphones and extended for high-performance computing in order to achieve better performance and energy efficiency for heavy computational tasks. Although heterogeneity adds significant complexity to both hardware and software, recent works have shown tremendous power and performance benefits obtainable through specialization. It is clear that emerging systems will be increasingly heterogeneous.

Many of these emerging systems couple together cores of different instruction set architectures (ISA), due to both market forces and the potential performance and power benefits in optimizing application execution. However, differently from symmetric multiprocessors or even asymmetric single-ISA multiprocessors, natively compiled applications cannot freely migrate between heterogeneous-ISA processors. This is due to the fact that applications are compiled to an instruction set architecture-specific format which is incompatible on other instruction set architectures. This creates serious limitations, as execution migration is a fundamental mechanism used by schedulers to reach performance or fairness goals, allows applications to migrate between heterogeneous-ISA CPUs in order to accelerate parallel applications or even leverage ISA-heterogeneity for security benefits.

This dissertation describes system software for automatically migrating natively compiled applications across heterogeneous-ISA processors. This dissertation describes the implementation and evaluation of a complete software stack on commodity scale heterogeneous-ISA CPUs, emulating datacenters with heterogeneous-ISA systems or future systems that tightly integrate heterogeneous-ISA CPUs via point-to-point interconnect. This dissertation describes a compiler which builds applications for heterogeneous-ISA execution migration. The compiler generates machine code for every architecture in the system and lays out the application's code and data in a common format. In addition, the compiler generates metadata used by a state transformation runtime to dynamically transform thread execution state between ISA-specific formats, allowing application threads to migrate between different ISAs.

The compiler and runtime is evaluated in conjunction with a replicated-kernel operating system, which provides thread migration and distributed shared virtual memory across heterogeneous-ISA processors. This redesigned software stack is evaluated on a setup containing and ARM and an x86 processor interconnected via point-to-point interconnect over PCIe. This dissertation shows that sub-millisecond state transformation is achievable. Ad-

ditionally, it shows that for a datacenter-like workload using benchmarks from the NAS Parallel Benchmark suite, the system can trade some performance for up to a 66% reduction in energy and up to an 11% reduction in energy-delay product.

This dissertation then describes an exploration into using hardware transactional memory (HTM) to maximize scheduling flexibility. Because applications can only migrate between ISAs at program locations with specific properties, there may be a significant delay between when the scheduler wishes to migrate an application and when the application can respond to the migration request. In order to reduce this migration response time, this dissertation describes compiler instrumentation which uses HTM to allow the scheduler to force applications to roll back to the most recently encountered program location suitable for migration. This is evaluated both in terms of overhead and responsiveness to migration requests.

In addition to showing the viability of the infrastructure for optimizing workload placement in a heterogeneous-ISA datacenter, this dissertation also demonstrates utilizing the infrastructure to accelerate multithreaded applications. This dissertation describes a new OpenMP runtime named libopenpop that is optimized for executing applications in heterogeneous-ISA systems with distributed shared virtual memory. The runtime utilizes synchronization primitives that enable scale-out execution across rack-scale systems and new work distribution mechanisms that predict the best partitioning of parallel work across CPUs with diverse architectural characteristics. libopenpop demonstrates sizable improvements over a naïve OpenMP implementation – a 38x improvement in multi-server barrier latency, a 5.4x improvement in multi-server data reductions and a geometric mean speedup of 4.04x for scalable applications in an 8-node x86-64 cluster. For a heterogeneous system composed of a highly-clocked x86 server and a highly-parallel ARM server, libopenpop delivers up to a 4.7x speedup and a geometric mean speedup of 41% across benchmarks from several benchmark suites versus the best single-node homogeneous execution.

Finally, this dissertation describes leveraging the compiler and state transformation runtime to provide enhanced security for applications. Because the compiler provides detailed information about the stack layout of applications, it can be leveraged to defend against exploits such as stack smashing attacks and return-oriented programming attacks. This dissertation describes Chameleon, a runtime which uses the compiler and state transformation infrastructure to continuously re-randomize the stack layout and code of vulnerable applications to thwart attackers. Chameleon attaches to applications using existing operating system interfaces and periodically switches the application to new randomized stack layouts and code by rewriting the stack. Chameleon enhances security with little overhead – it disrupts a geometric mean 76.32% of code gadgets in benchmark binaries, randomizes stack element locations with geometric mean 3 potential randomized locations, and has 1.1% overhead when re-randomizing every 50 milliseconds, making it extremely difficult for attackers to exploit target applications.

This work is supported in part by ONR under grants N00014-13-1-0317, N00014-16-1-2711, and N00014-18-1-2022, and NAVSEA/NEEC under grants 3003279297 and N00174-16-C-0018.

#### Popcorn Linux: A Compiler and Runtime for State Transformation Between Heterogeneous-ISA Architectures

Robert F. Lyerly

GENERAL AUDIENCE ABSTRACT

Computer processors have experienced unprecedented performance improvements over the past 50 years. However, due to physical limitations of how processors execute, in recent years this performance growth has started to slow. In order to continue scaling performance, chip designers have begun diversifying processor designs to meet different performance and power consumption targets. Processors specialized for different contexts use various instruction set architectures (ISAs), the operations made available for use by the hardware. Programs built for one instruction set architecture are not compatible with others, requiring developers to build complex applications to manually bridge the gap. This leads to brittle applications and prevents the system software managing the processors from adapting workloads to match processor characteristics.

This dissertation presents the Popcorn Linux system software which provides transparent support for running applications across computers composed of processors of multiple ISAs. Popcorn Linux provides the ability to migrate applications between these processors without requiring developers to add any application instrumentation – the system software manages all the details of building and migrating applications. An evaluation of Popcorn Linux shows that transparently migrating applications between diverse processors provides power and performance benefits in a variety of scenarios. Additionally, this dissertation describes leveraging the Popcorn Linux software infrastructure to harden applications against attackers seeking to hijack applications for malicious purposes.

### Dedication

To my parents David and Mary Denton; my brother Matt; and Rebecca.

### Acknowledgments

I would like to thank my advisor, Professor Binoy Ravindran, for helping to guide me throughout my Ph.D. In addition helping me grow as a software engineer and researcher, he taught me how to deal with setbacks throughout life. He showed me how to laugh when things are not going as planned and he always knew when to provide support, empathy and encouragement for the path forward. The road was full of ups and downs, but he was always there to support me through it all.

In addition to Professor Ravindran, I would like to thank my committee members Professor Changhee Jung, Professor Cameron Patterson, Professor Paul Plassmann and Professor Haibo Zeng for providing valuable insights and feedback on my work. Additionally I would like to thank Professor Changwoo Min and Professor Christopher Rossbach for providing an outside perspective and new ideas about my work.

I also would like to thank the many SSRG friends I've made over the years – in rough chronological order, Dr. Alastair Murray, Dr. Antonio Barbalace, Ben Shelton, Kevin Burns, Dr. Sachin Hirve, Curt Albert, Duane Niles, Dr. Pierre Olivier, Christopher Jelesnianski, Anthony Carno, Ho-Ren Chuang, Ian Roessle, Josh Bockenek, Dr. (now Professor) Sang-Hoon Kim and Yihan Pang. The camaraderie helped all of us through the late nights and tough times – without you all it would have been a much tougher and much less fun journey.

I would like to thank my friends who are too innumerable to name but whom all made sure to laugh at the fact that I was still in school.

I would like to thank Rebecca, without whom I do not think I would have made it all the way through. Her kindness and support is unmatched; she was always ready with encouragement and was willing to sacrifice when I had to prioritize work. She is more than I could hope for. I would also like to thank George, who always made me smile, even when he was chewing through cords.

Finally I would like to thank my parents and my brother. The reason I have made it this far is due to them trailblazing a path in too many ways to count. They have always been there for encouragement and support. I can count on them for anything, and they have given me the opportunity to pursue my goals without obstacle.

### Contents

| 1 | Intr | oduction                                                     | 1  |

|---|------|--------------------------------------------------------------|----|

|   | 1.1  | Motivation                                                   | 1  |

|   |      | 1.1.1 Heterogeneous Datacenters                              | 2  |

|   |      | 1.1.2 Heterogeneous-ISA CMPs and Tightly-Coupled Systems     | 3  |

|   |      | 1.1.3 Challenges                                             | 3  |

|   | 1.2  | Thesis Contributions                                         | 4  |

|   |      | 1.2.1 Popcorn Compiler Toolchain                             | 7  |

|   |      | 1.2.2 State Transformation Runtime                           | 7  |

|   |      | 1.2.3 Scale-Out and Heterogeneous OpenMP                     | 8  |

|   |      | 1.2.4 State Transformation for Runtime Re-randomization      | 8  |

|   | 1.3  | Thesis Organization                                          | 9  |

| 2 | Rela | ated Work                                                    | 10 |

|   | 2.1  | Compiler and Runtime Support for Heterogeneous Architectures | 10 |

|   | 2.2  | State Transformation                                         | 11 |

|   | 2.3  | Heterogeneous-ISA Execution Migration                        | 13 |

|   | 2.4  | Scaling Applications to Rack-Scale Systems                   | 15 |

|   | 2.5  | Work Distribution in Heterogeneous Systems                   | 16 |

|   | 2.6  | Runtime Re-randomization                                     | 17 |

| 3 | Bac  | kground 2                                                    | 20 |

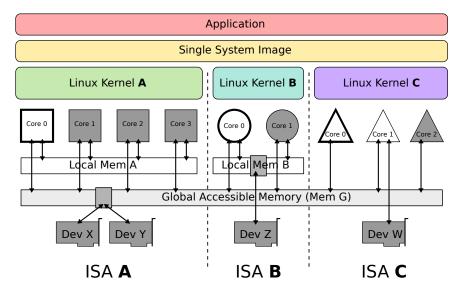

|   | 3.1  | Replicated-Kernel Operating Systems                          | 21 |

|   |      | 3.1.1 Thread Migration                              | 22 |

|---|------|-----------------------------------------------------|----|

|   |      | 3.1.2 Distributed Shared Virtual Memory             | 23 |

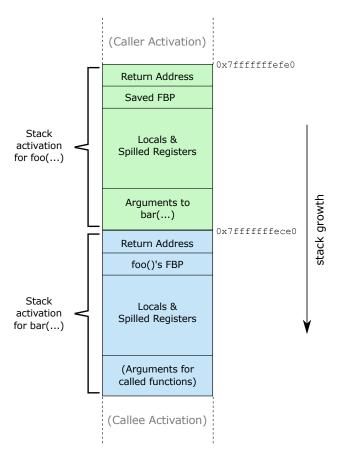

|   | 3.2  | Application State                                   | 25 |

|   |      | 3.2.1 Formalization                                 | 25 |

|   |      | 3.2.2 Laying Out Application State                  | 26 |

|   |      | 3.2.3 ISA-specific State                            | 28 |

|   | 3.3  | Expectations of the Compiler and Runtime            | 31 |

| 4 | Pop  | ocorn Compiler Toolchain 3                          | 3  |

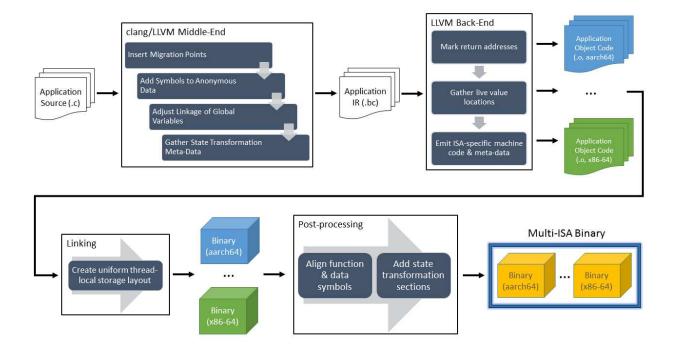

|   | 4.1  | Building Multi-ISA Binaries                         | 33 |

|   | 4.2  | Inserting Migration Points                          | 36 |

|   | 4.3  | Instrumenting the IR of the Application             | 37 |

|   | 4.4  | Augmenting Compiler Backend Analyses                | 39 |

|   |      | 4.4.1 Program Location                              | 39 |

|   |      | 4.4.2 Live Value Locations                          | 39 |

|   |      | 4.4.3 Live Value Semantic Information               | 11 |

|   |      | 4.4.4 Architecture-Specific Live Values             | 12 |

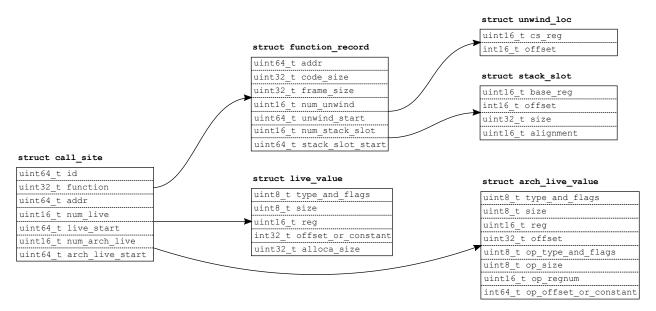

|   | 4.5  | Generating State Transformation Metadata            | 12 |

| 5 | Stat | te Transformation Runtime 4                         | l6 |

|   | 5.1  | Preparing for Transformation at Application Startup | 17 |

|   | 5.2  | Transformation                                      | 19 |

|   |      | 5.2.1 Finding Activations on the Current Stack      | 50 |

|   |      | 5.2.2 Transforming Activations                      | 51 |

|   |      | 5.2.3 Handling Pointers to the Stack                | 54 |

|   | 5.3  | Migration and Resuming Execution                    | 55 |

|   | 5.4  | Debugging Cross-ISA Execution                       | 56 |

| 6 | Eva  | luation 5                                           | 7  |

|   | 6.1  | Experimental Setup                                  | 57 |

|   | 6.2 | State Transformation Microbenchmarks                          | 58  |

|---|-----|---------------------------------------------------------------|-----|

|   | 6.3 | Single-Application Costs                                      | 64  |

|   | 6.4 | Alternative Migration Approaches                              | 66  |

|   | 6.5 | Optimizing Multiprogrammed Workloads                          | 67  |

| 7 | Low | ver Migration Response Time Via Hardware Transactional Memory | 73  |

|   | 7.1 | Background                                                    | 75  |

|   | 7.2 | Design                                                        | 76  |

|   |     | 7.2.1 Lightweight Instrumentation                             | 78  |

|   |     | 7.2.2 Automatically Tuning Instrumentation                    | 85  |

|   | 7.3 | Implementation                                                | 86  |

|   | 7.4 | Evaluation                                                    | 87  |

|   |     | 7.4.1 Overhead                                                | 87  |

|   |     | 7.4.2 Migration Response Time                                 | 89  |

|   | 7.5 | Discussion                                                    | 90  |

| 8 | Sca | ling OpenMP Across Non-Cache-Coherent Domains                 | 91  |

|   | 8.1 | Profiling Software Memory Consistency Overheads               | 92  |

|   | 8.2 | Design of a Distributed OpenMP Runtime                        | 93  |

|   |     | 8.2.1 Distributed OpenMP Execution                            | 94  |

|   |     | 8.2.2 Optimizing OpenMP Primitives                            | 96  |

|   |     | 8.2.3 Using OpenMP Efficiently                                | 99  |

|   | 8.3 | Implementation                                                | 101 |

| 9 | Sca | le-out OpenMP Evaluation                                      | 102 |

|   | 9.1 | Microbenchmarks                                               | 103 |

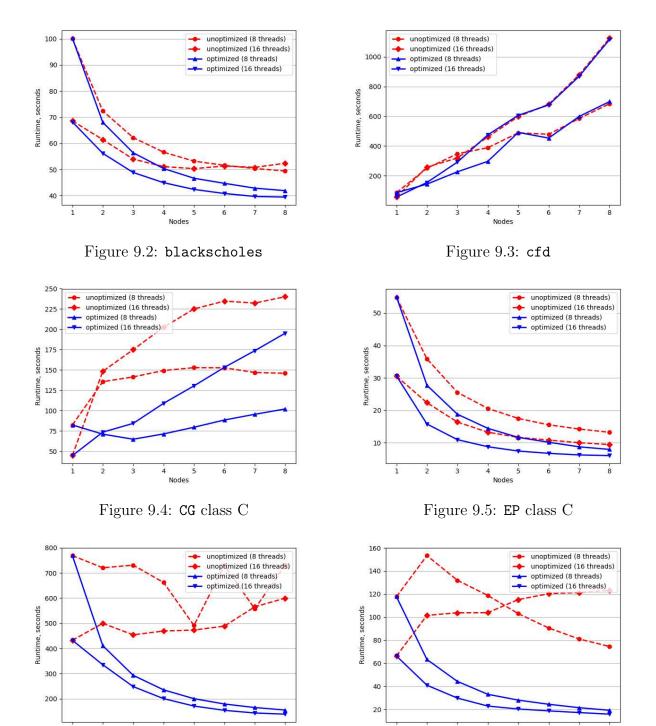

|   | 9.2 | Benchmark Performance                                         | 104 |

|   | 9.3 | Performance Characterization                                  | 104 |

|   | 0.4 | D. W. I                                                       | 100 |

| <b>10</b> ] | Hete | erogeneous OpenMP                          | 108 |

|-------------|------|--------------------------------------------|-----|

| -           | 10.1 | Mechanisms for Heterogeneous-ISA Execution | 109 |

|             |      | 10.1.1 Cross-node Execution                | 109 |

|             |      | 10.1.2 Workload Distribution               | 110 |

|             |      | 10.1.3 Cross-node static scheduler         | 110 |

|             |      | 10.1.4 Cross-node dynamic scheduler        | 110 |

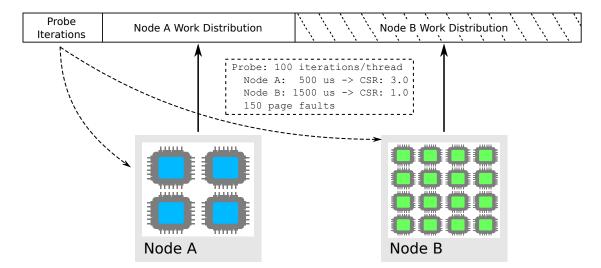

|             |      | 10.1.5 HetProbe scheduler                  | 111 |

| -           | 10.2 | Workload Distribution Decisions            | 112 |

| -           | 10.3 | Implementation                             | 116 |

| 11 ]        | Hete | erogeneous OpenMP Evaluation               | 117 |

| -           | 11.1 | Experimental Setup                         | 117 |

| -           | 11.2 | Results                                    | 119 |

| -           | 11.3 | Discussion                                 | 124 |

| <b>12</b> ( | Cha  | meleon – Runtime Re-randomization          | 126 |

| -           | 12.1 | Background                                 | 126 |

| -           | 12.2 | Threat Model                               | 128 |

| -           | 12.3 | System Architecture                        | 128 |

| -           | 12.4 | Code Randomization                         | 131 |

| -           | 12.5 | Serving Code Pages                         | 135 |

| -           | 12.6 | Re-randomizing the Target                  | 136 |

| <b>13</b> ] | Eval | luation – Chameleon                        | 140 |

| -           | 13.1 | Security Analysis                          | 141 |

|             |      | 13.1.1 Target Randomization                | 141 |

|             |      | 13.1.2 Chameleon                           | 144 |

| -           | 13.2 | Performance                                | 146 |

| -           | 13.3 | Case Study: nginx                          | 149 |

| _           | 13.4 | Discussion                                 | 151 |

| 14 Conclusions and Future We | ork 15                                            |

|------------------------------|---------------------------------------------------|

| 14.1 Future Work             |                                                   |

| 14.1.1 Heterogeneous-ISA     | State Transformation and Execution Migration . 15 |

| 14.1.2 OpenMP for Non-       | Cache-Coherent Domains                            |

| 14.1.3 Runtime Re-rando      | mization                                          |

| Bibliography                 | 158                                               |

## List of Figures

| 3.1 | Replicated-kernel OS architecture and application interface                                                                                                                                                                                                      | 22 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Page coherency protocol. Pages permissions are maintained similarly to a cache-coherency protocol to provide consistent views of memory across processor islands. Multiple nodes may map a page as readable, but only a single node may map the page as writable | 24 |

| 3.3 | Stack frame layout. The stack includes call frames for function foo(), which calls function bar()                                                                                                                                                                | 30 |

| 4.1 | Popcorn compiler toolchain                                                                                                                                                                                                                                       | 34 |

| 4.2 | Uninstrumented LLVM bitcode                                                                                                                                                                                                                                      | 38 |

| 4.3 | Instrumented LLVM bitcode                                                                                                                                                                                                                                        | 38 |

| 4.4 | Metadata emitted by the compiler. Each type of structure (e.g., call_site, function_record) is contained in its own section                                                                                                                                      | 43 |

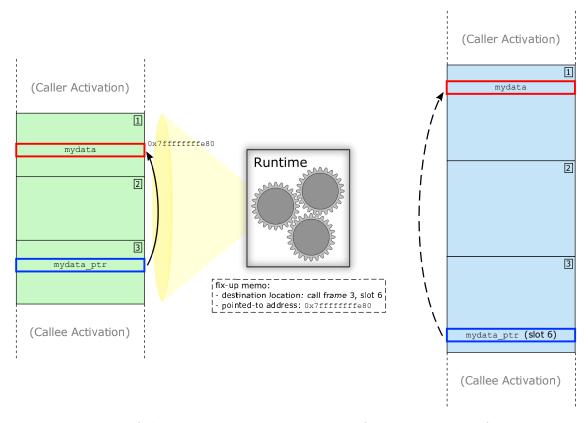

| 5.1 | An example of the state transformation runtime copying live values between source (AArch64) and destination (x86-64) activations                                                                                                                                 | 53 |

| 5.2 | Example of the runtime observing and transforming a pointer for the destination activation                                                                                                                                                                       | 55 |

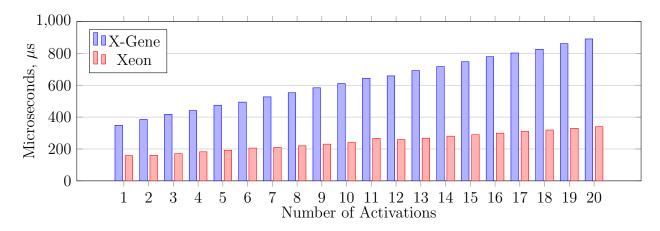

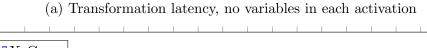

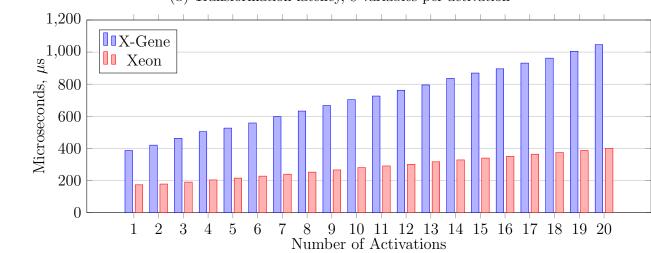

| 6.1 | State transformation latency                                                                                                                                                                                                                                     | 60 |

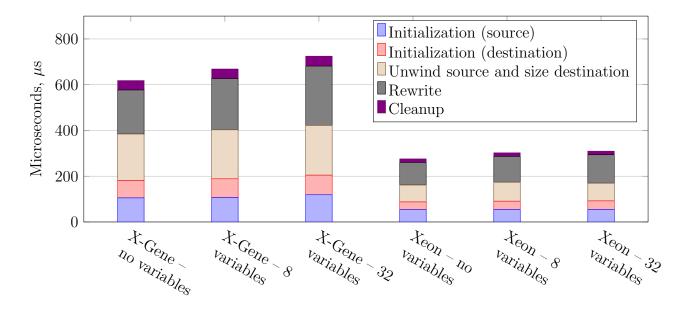

| 6.2 | Time spent in each phase of state transformation                                                                                                                                                                                                                 | 61 |

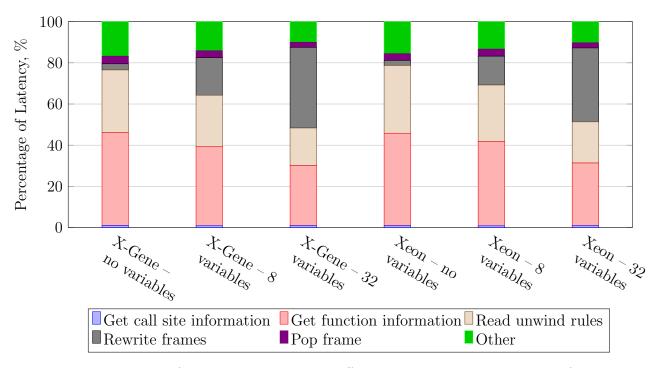

| 6.3 | Percentage of time spent executing different actions during state transformation                                                                                                                                                                                 | 61 |

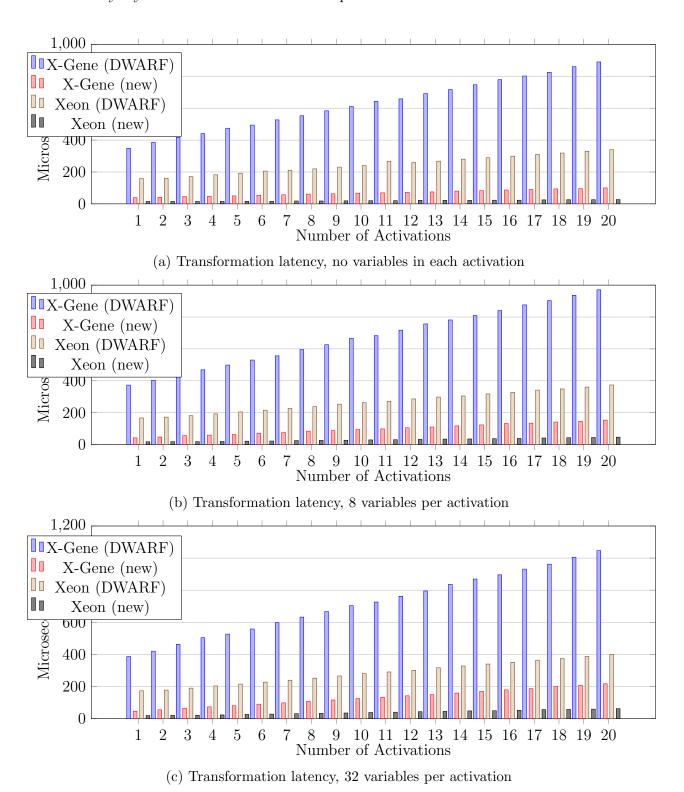

| 6.4 | State transformation latency after removing DWARF debugging information                                                                                                                                                                                          | 63 |

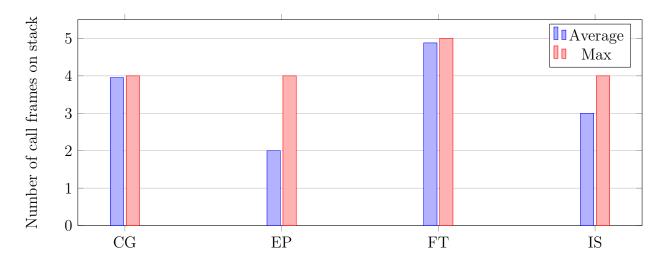

| 6.5 | Average and maximum stack depths for benchmarks from the NPB benchmark suite                                                                                                                                                                                     | 65 |

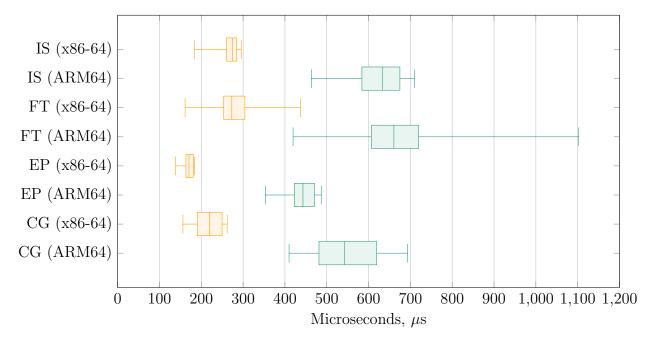

| 0.0  | plications. Box-and-whisker plots show the minimum, 1st quartile, median, 3rd quartile, and maximum observed transformation latencies                                                                                                                                                                                                                                         | 65         |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

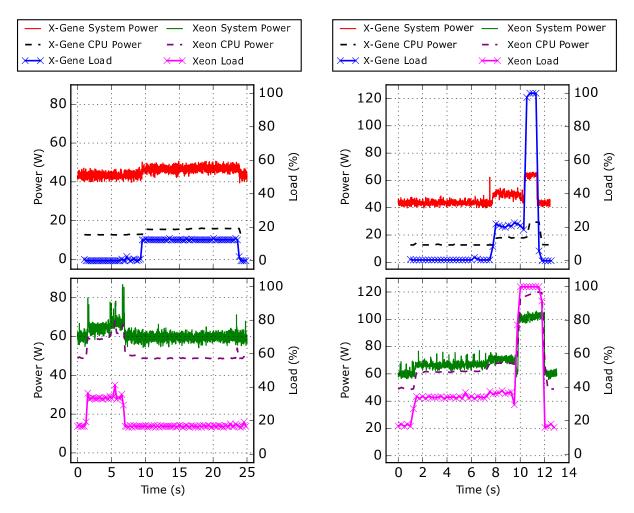

| 6.7  | Comparison of Popcorn Linux and PadMig execution time and power consumption for IS class B. The x-axis shows the total execution time for each system. The left y-axis shows instantaneous power consumption in Watts and the right y-axis shows CPU load. The top row shows power consumption and CPU load for the X-Gene, while the bottom row shows the same for the Xeon. | 68         |

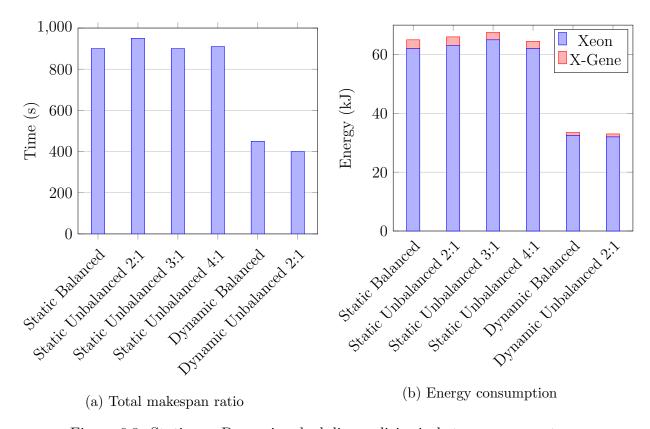

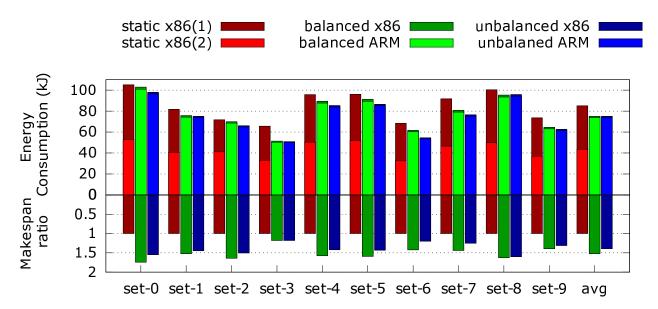

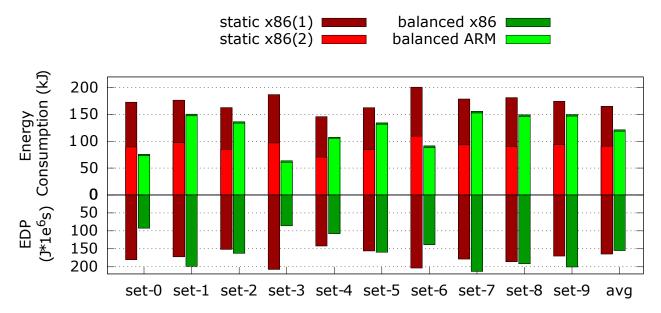

| 6.8  | Static vs. Dynamic scheduling policies in heterogeneous setup                                                                                                                                                                                                                                                                                                                 | 70         |

| 6.9  | Energy consumption and makespan ratio for several single-application arrival patterns                                                                                                                                                                                                                                                                                         | 71         |

| 6.10 | Energy consumption and makespan ratio for several clustered-application arrival patterns. Results for Dynamic Unbalanced policy are not shown as they differ by less than 1% from the Dynamic Balanced policy                                                                                                                                                                 | 72         |

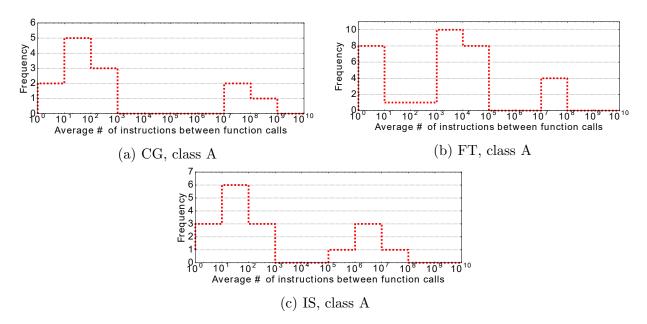

| 7.1  | Distribution of number of instructions between migration points                                                                                                                                                                                                                                                                                                               | <b>7</b> 4 |

| 7.2  | LLVM bitcode instrumented with transactional execution at a migration point                                                                                                                                                                                                                                                                                                   | 77         |

| 7.3  | If-else control flow in LLVM bitcode                                                                                                                                                                                                                                                                                                                                          | 80         |

| 7.4  | Transforming loop to hit instrumentation every 16 iterations                                                                                                                                                                                                                                                                                                                  | 81         |

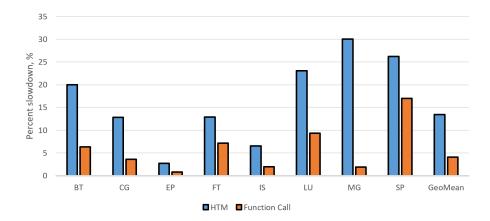

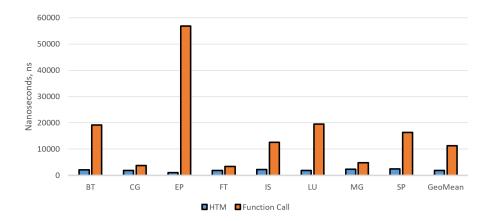

| 7.5  | Overhead of instrumentation for HTM and inserting extra migration library call-outs                                                                                                                                                                                                                                                                                           | 88         |

| 7.6  | Median migration request response time                                                                                                                                                                                                                                                                                                                                        | 89         |

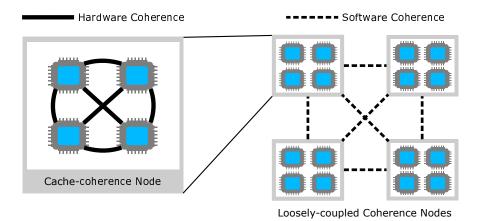

| 8.1  | System composed of non-cache-coherent domains. Within a domain, the hardware provides cache coherency and a consistent view of memory. Between domains, however, software (e.g., user-developed, runtime, OS) must provide memory consistency – for libopenpop, Popcorn Linux's page consistency protocol provides sequential consistency between domains                     | 92         |

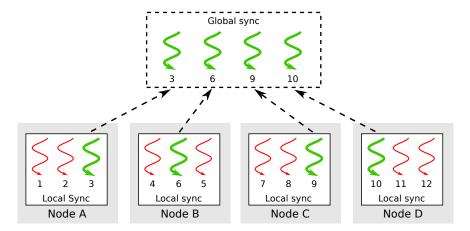

| 8.2  | libopenpop's thread hierarchy. In this setup, libopenpop has placed 3 threads (numbered 1-12) on each node. For synchronization, threads on a node elect a leader (green) to represent the node at the global level. Non-leader threads (red) wait for the leader using local synchronization to avoid cross-node data accesses.                                              | 95         |

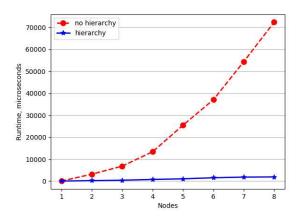

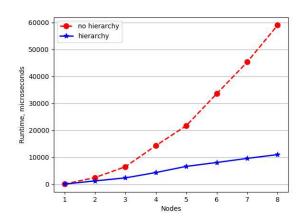

| 9.1  | Evaluation of OpenMP primitives with and without the thread hierarchy                                                                                                                                                                                                                                                                                                         | 103        |

| 0.2  | hlackscholes                                                                                                                                                                                                                                                                                                                                                                  | 105        |

| 9.3  | cfd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 105 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 9.4  | CG class C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 105 |

| 9.5  | EP class C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 105 |

| 9.6  | kmeans                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 105 |

| 9.7  | lavaMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 105 |

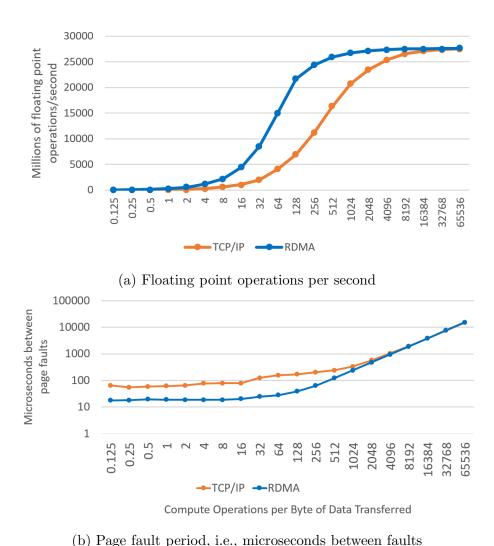

| 10.1 | Performance metrics observed when varying the number of compute operations per byte of data transferred over the interconnect. For example, a 16 on the x-axis means 16 math operations were executed per transferred byte or 65536 operations per page.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 114 |

| 10.2 | HetProbe scheduler. A small number of probe iterations are distributed at the beginning of the work-sharing region to determine core speed ratios of nodes in the system. Using the results, the runtime decides either to run all iterations on one of the nodes or distribute work across nodes according to the calculated core speed ratio (shown here)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 115 |

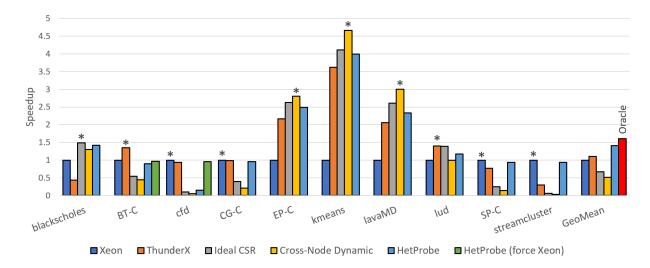

| 11.1 | Speedup of benchmarks versus running homogeneously on Xeon (values less than one indicate slowdowns). Asterisks mark the best workload distribution configuration for each benchmark. "Cross-Node Dynamic" provides the best performance across applications that benefit from leveraging both CPUs (blackscholes, EP-C, kmeans, lavaMD), but causes significant slowdowns for those that do not. "HetProbe" achieves similar performance to Ideal CSR and Cross-Node Dynamic for the four scalable applications but falls back to a single CPU for applications that cause significant DSM communication and hence have worse cross-node performance. For geometric mean, "Oracle" is the average of the configurations marked by asterisks, i.e., what a developer who had explored all such possible workload distribution configurations through extensive profiling would choose. | 120 |

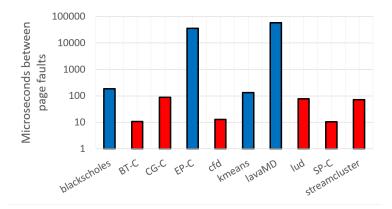

| 11.2 | Page fault periods used to determine whether cross-node execution is beneficial. Red bars (cross-node execution not profitable) are below the RDMA threshold indicated in Section 10.2, blue are above.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 121 |

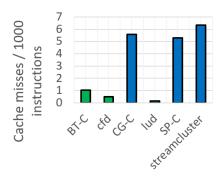

| 11.3 | Cache misses for applications not executed across nodes. Green bars (including lud) indicate the application was run on the ThunderX, blue were run on the Xeon.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 121 |

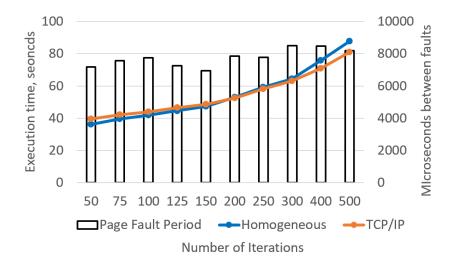

| 11.4 | Execution time (lines, left axis) and page fault period (bars, right axis) when varying the number of iterations of blackscholes. "Homogeneous" refers to Xeon configuration, "TCP/IP" refers to using HetProbe over TCP/IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 121 |

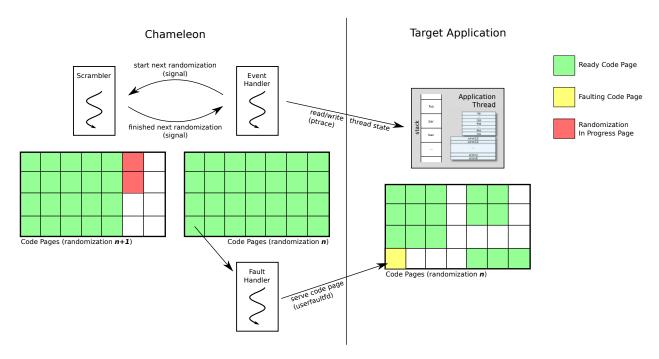

| 12.1 | Chameleon runtime system. An event handler thread waits for events in a target application thread (e.g., signals), interrupts the target thread, and read-s/writes the target thread's execution state (registers, stack) using ptrace. A scrambler thread concurrently prepares the next set of randomized code for the next re-randomization. A fault handler thread responds to page faults in the target by passing pages from the current code randomization to the kernel through userfaultfd | 130  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

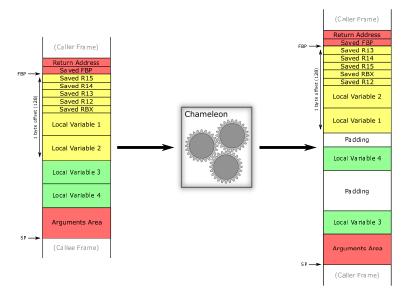

| 12.2 | Frame randomization. Chameleon cannot randomize the locations of the return address, saved frame base pointer and call arguments. Chameleon can permute the ordering of callee-save register locations and stack slots whose offsets can be encoded in a single byte. Chameleon can place the remaining slots at arbitrary locations, including adding padding between slots                                                                                                                        | 134  |

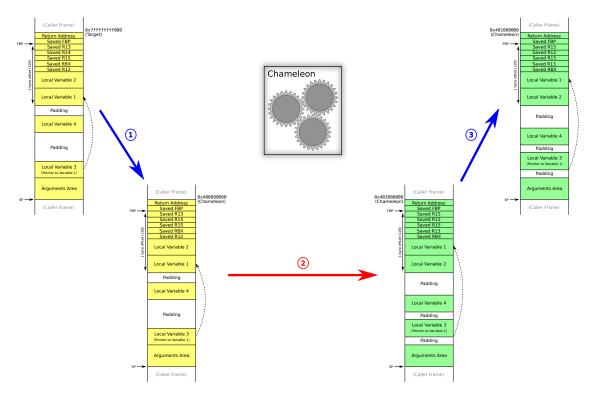

| 12.3 | Re-randomizing the stack layout. Chameleon (1) reads the target's current execution state, (2) transforms the state from the previous randomization to the new randomization, including reifying pointers to the stack in the target's address space to reference the newly randomized locations, and (3) write the execution state back into the target's context and drop the previous code pages                                                                                                 | .137 |

| 13.1 | Number of gadgets found. Non-trivial gadgets are gadgets that include more than just one instruction, i.e., more than just the control flow instruction                                                                                                                                                                                                                                                                                                                                             | 142  |

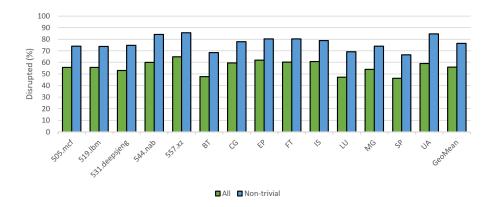

| 13.2 | Percent of gadgets disrupted by Chameleon's code randomization                                                                                                                                                                                                                                                                                                                                                                                                                                      | 142  |

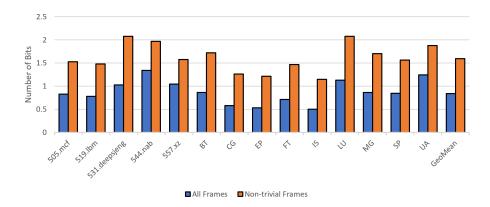

| 13.3 | Average number of bits of entropy for a stack element across all functions within each binary. Bits of entropy quantify in how many possible locations a stack element may be post-randomization – for example, 2 bits of entropy mean the stack element could be in $2^2=4$ possible locations with a $\frac{1}{4}=25\%$ chance of guessing the location                                                                                                                                           | 143  |

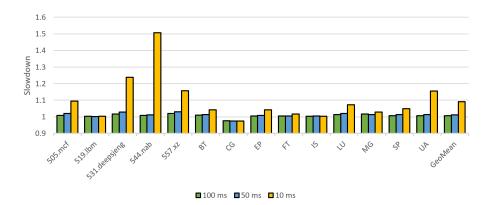

| 13.4 | Overhead when running applications under Chameleon compared to unsupervised execution. Overheads rise with smaller re-randomization periods, but are negligible in most cases. With 10 millisecond re-randomization period, some benchmarks exhibit high overheads due to waiting for the scrambler to finish generating the next set of randomized code                                                                                                                                            | 147  |

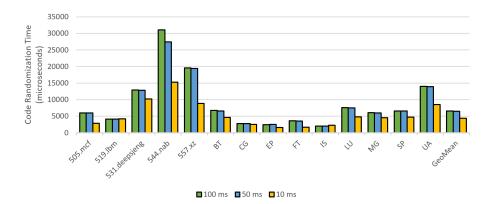

| 13.5 | Average time to complete a single code randomization. Randomization time is correlated with the code size of each application. As the re-randomization period gets shorter, the scrambler thread spends less time sleeping and therefore maintains a higher clock frequency, hence a smaller time to randomize                                                                                                                                                                                      | 1.40 |

|      | code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 148  |

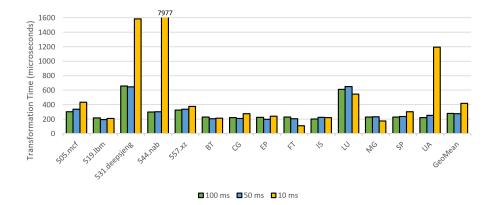

| 13.6 | Time to atomically switch the target from the previous randomization to the   |     |

|------|-------------------------------------------------------------------------------|-----|

|      | next randomization, including transforming the stack and dropp the existing   |     |

|      | code pages. As the randomization period gets smaller, transformation bal-     |     |

|      | loon in several case (deepsjeng, nab, UA) as the transformation thread blocks |     |

|      | waiting for the scrambler to finish randomizing the code and generating slot  |     |

|      | remapping information                                                         | 149 |

### List of Tables

| 6.1  | specification of Processors in Experimental Setup There are two hardware threads per core, but hyperthreading was disabled for our experiments                                                                      | 58  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.2  | Time required for executing individual actions on the Xeon                                                                                                                                                          | 66  |

| 10.1 | Experimental setup                                                                                                                                                                                                  | 113 |

| 11.1 | Core speed ratios calculated by HetProbe scheduler. Used by Ideal CSR and HetProbe configurations. Without the HetProbe scheduler, developers would have to manually determine these values via extensive profiling | 118 |

| 11.2 | Baseline execution times in seconds when run on Xeon with 16 threads using the static scheduler                                                                                                                     | 118 |

| 13.1 | Complete list of system calls invoked by Chameleon. Calls marked with * are only used by compel only to communicate with the target when initializing. Calls marked with † are only used for userfaultfd            | 145 |

| 13.2 | Original execution times of benchmarks, in seconds, without Chameleon                                                                                                                                               | 146 |

### Chapter 1

#### Introduction

#### 1.1 Motivation

In recent years, there has been a shift towards increasing parallelism and heterogeneity in processor design [188, 189]. As traditional uniprocessors have hit the clock speed, power, instruction-level parallelism and complexity walls, chip designers have been forced to rethink computer architecture from the ground up. This has led to an explosion in new architectures such as graphics processing units (GPUs), digital signal processors (DSPs) and field-programmable gate arrays (FPGAs). Additionally, general-purpose CPUs have been re-architected in order to meet energy and performance goals for varying form factors [107, 59, 15, 74, 17, 16]. It is clear that emerging computer systems will be increasingly heterogeneous in order to achieve better energy efficiency and higher performance.

Recently there has been a tremendous amount of change in CPU microarchitecture in order to reach different power and performance targets. With the advent of smartphones, CPU designers have built processors that strike a balance between low power and reasonable performance [107, 47]. The high-performance computing (HPC) community has embraced CPU heterogeneity, with several of the top supercomputers in the Top500 list [193] mixing symmetric chip-multiprocessors (CMP) with general-purpose and OS-capable [149] many-core accelerators. Additionally, the HPC community has begun to include energy efficiency as a primary design goal as they realized they could not continue scaling the number of cores at current power consumption levels [75]. Chip designers have even begun to include heterogeneous CPU cores together on a single die in order to achieve high performance and energy efficiency for a variety of workloads [95, 141, 107, 15].

Due to the history of how different CPUs were created and the technology limitations of their time, many commodity scale CPUs utilize different instruction set architectures (ISA) [157]. The ISA defines the hardware-software interface and provides a fundamental definition of how software can execute on a given processor. This definition includes how data is encoded

into binary representations, how memory is arranged for execution and what instructions are available, among other aspects. The ISA is fixed for a particular CPU and thus the job of a compiler is to map an application written in a source code language like C onto a processor's ISA. ISAs are not interoperable and therefore it is impossible for applications compiled for one ISA to be run on another ISA with today's compilers, operating systems and runtimes.

However, because CPUs that target different power and performance goals often use different ISAs, systems composed of such heterogeneous-ISA CPUs provide an attractive means for optimizing a variety of workloads. For example, application migration is desirable in such systems in order to achieve higher performance and improved energy efficiency [155, 123, 204, 197, 127, 27]. Application migration allows the system software to optimize how a given workload executes in the system to best utilize the available compute resources, e.g., placing applications in consideration of architectural characteristics or multiprogrammed environments. Without application migration across heterogeneous-ISA CPUs, the system has limited ability to adapt to application or workload characteristics and may miss out on significant benefits. Thus, it is imperative that new techniques are developed to enable execution migration across heterogeneous-ISA CPUs as they become increasingly interwoven into the same systems, i.e., racks, servers or even systems-on-chips.

#### 1.1.1 Heterogeneous Datacenters

The x86 instruction set architecture is the most widely used processor in datacenters to-day [136, 166, 106]. Recently, however, there has been a push to introduce the ARM ISA into the server space. Multiple chip vendors including AMD [11], Qualcomm [148], Ampere [74] and Cavium [48] are producing ARM processors for datacenters and the cloud. Additionally, there is increasing vendor support behind the POWER ISA, with IBM forming the OpenPOWER foundation by partnering with companies such as Google, NVIDIA, Mellanox and others [80]. Interest in alternative processor architectures is driven by increasing availability of ARM and POWER cloud offerings [137, 126, 55, 56] in addition to traditional x86 services. These new processor architectures promise higher energy proportionality [28], meaning more performance per watt and increased computing power per rack (i.e., compute density).

Reducing electricity costs has become one of the most important concerns for datacenter operators today [209]. Datacenter hardware and software designers have proposed many techniques for improving energy efficiency while maintaining acceptable computational capacity [192, 209, 204, 198]. There are several software-based approaches that are effective for conserving energy, including load balancing and consolidation. Load balancing spreads applications evenly across nodes so that no nodes are over-saturated and each server consumes a reduced amount of power. Consolidation instead groups tasks on the minimal number of nodes required so that service-level agreements (e.g., latency requirements) can be met. The remaining servers are subsequently placed in a low-power state. Both solutions require

migrating applications between nodes to dynamically adjust the computational capacity of the datacenter with time-varying workloads. How can datacenter operators leverage these techniques in datacenters with increasing ISA diversity?

#### 1.1.2 Heterogeneous-ISA CMPs and Tightly-Coupled Systems

Recent works have demonstrated significant advantages for execution migration between tightly-coupled cores that utilize the same ISA but with heterogeneous microarchitectures [95, 141, 187, 107, 123, 158, 108, 163, 179]. Existing mechanisms for execution migration in symmetric multiprocessors (SMP) work without modification for these new processors because all cores share the same ISA and are interconnected via cache-coherent shared memory. In asymmetric chip multiprocessors (ACMP), execution migration can be used to accelerate both serial and parallel portions of applications with higher energy efficiency [158, 108, 163, 179].

More recent works by DeVuyst et al. [70] and Venkat et al. [197, 195] show that there are further performance and energy benefits obtained by migrating between heterogeneous-ISA cores versus ACMPs. Applications may exhibit affinities for certain ISAs based on characteristics of code generated by the compiler, such as register pressure, memory addressing modes, floating-point and SIMD computation, etc. Additionally, because emerging heterogeneous-ISA CPUs have vastly different macro- and micro-architectures [74, 159, 97, 59, 100], they also provide different levels of performance, energy efficiency and parallelism to accelerate applications with diverse execution profiles – tightly coupling such processors together can provide significant performance benefits [27]. Finally, migrating execution between heterogeneous-ISA cores can provide a defense against security exploits such as return-oriented programming attacks [196]. However, past works simulate a cache-coherent shared memory processor with heterogeneous-ISA cores [70, 196] or couple together overlapping-ISA CPUs [27]. How are applications built and migrated between fully-diverse heterogeneous-ISA processors in commodity scale systems?

#### 1.1.3 Challenges

These fundamental changes in processor design have forced developers to rethink how emerging heterogeneous systems are programmed. Utilizing heterogeneous-ISA CPUs places a large burden on developers because they can no longer use a shared-memory programming model [8]. Instead, developers must reason about application structure and memory layout in order to obtain maximum performance [150, 92, 91]. Because these processors have distinct ISAs, source code compiled for one processor is not able to be run on another. This harms programmability because developers must manually partition applications into pieces and coordinate computation and data movement across architectures. It also hinders system adaptability because the system software cannot freely schedule applications to meet performance or fairness goals [155, 209].

One solution for heterogeneous-ISA execution is to use a language-level virtual machine, e.g., a Java virtual machine [128]. When using language VMs, the application is maintained in an architecture-independent intermediate format which the VM interprets to execute the application. Because the VM has complete knowledge of the application's execution, including code and data format, it can migrate applications between architectures [83, 84, 88, 54]. However, using these approaches requires applications be rewritten in the interpreted language. Many datacenter applications, e.g., Redis [164], are written using natively-compiled languages such as C and C++ in order to apply aggressive optimizations. Re-writing the application in an interpreted language is a non-starter due to the loss of control – for example, Java applications are required to use garbage collection for memory management. Additionally, many VM-level techniques for migration rely on language-level mechanisms (e.g., object serialization [154]), which are demonstrated to have high overheads.

Therefore, as heterogeneity becomes ubiquitous in all computing contexts it becomes increasingly important to develop new techniques for seamless execution migration across heterogeneous-ISA processors for natively-compiled applications.

#### 1.2 Thesis Contributions

This dissertation presents a full software stack for enabling execution migration across heterogeneous-ISA architectures. The prototype, named Popcorn Linux, includes an operating system, compiler and runtime which seamlessly migrates applications between an ARM and an x86 processor interconnected over a high speed network. This work describes the design and implementation of the compiler and runtime components of Popcorn Linux, named the Popcorn compiler toolchain and state transformation runtime. These components are presented, which build applications and enable migration between heterogeneous-ISA CPUs using capabilities provided by Popcorn Linux's OS. In addition to the core infrastructure, this dissertation describes leveraging Popcorn Linux for accelerating multithreaded applications and for hardening applications against security exploits. This dissertation makes the following contributions:

- The design and implementation of the Popcorn compiler toolchain. The toolchain builds applications suitable for migration by adjusting data and code layout, and by automatically inserting migration points into the generated machine code. Additionally, the compiler performs offline analysis to provide metadata for dynamic state transformation. The toolchain builds multi-ISA binaries which the OS uses to recreate an application's virtual address space across heterogeneous-ISA CPUs.

- The design and implementation of the state transformation runtime. The state transformation runtime transforms execution state between ISA-specific formats so that threads of an application can migrate between architectures. It additionally provides

a mechanism for initiating migration and for bootstrapping execution after the application has migrated to the destination architecture. The runtime provides submillisecond transformation latencies for benchmarks from the NAS Parallel Benchmark (NPB) suite on an x86 and an ARMv8 CPU. Using Popcorn Linux (compiler, runtime, OS), the dissertation demonstrates a 30% reduction in energy and an 11% reduction in energy-delay product when load-balancing a multiprogrammed workload on top of server-class x86-64 and ARMv8 CPUs.

- An exploration of using hardware transactional memory (HTM) to improve scheduler responsiveness. Because applications cannot migrate at arbitrary locations, extensions to the Popcorn compiler instrument generated code with transactional execution. This allows the scheduler to abort speculative execution and roll back to the most recently encountered migration point, enabling high responsiveness to scheduling requests. This dissertation shows that using HTM reduces migration response time to 1.9 microseconds but adds a geometric mean 13.45% overhead for benchmarks from NPB.

- The design and implementation of libopenpop, an OpenMP runtime optimized for running multithreaded applications parallelized using OpenMP across systems running Popcorn Linux. libopenpop optimizes multithreaded synchronization for distributed shared virtual memory systems like Popcorn Linux and utilizes new workload distribution mechanisms to ideally leverage the compute capabilities of heterogeneous CPUs. Using OpenMP benchmarks from NPB, Rodinia and PARSEC, libopenpop achieves a geometric mean 4.04x speedup for scalable application on a small homogeneous cluster. For a heterogeneous system composed of an x86-64 server and a high core count ARMv8 server connected via InfiniBand, libopenpop achieves up to a 4.7x speedup and a 41% geometric mean speedup.

- The design an implementation of Chameleon, a runtime re-randomization framework for preventing stack smashing and return-oriented programming attacks. Chameleon leverages the Popcorn compiler infrastructure to continuously randomize the stack layout and code of target applications, transforming a thread's execution state to match the new randomization. Using Chameleon on benchmarks from SPEC CPU 2017 and NPB, Chameleon disrupts a geometric mean 76.32% of code gadgets, randomizes stack elements to on average one of three possible locations, and randomizes with an overhead of 1.1% for a 50 millisecond re-randomization period.

Previous works present compiler and runtime systems for cross-ISA execution migration in order to perform a design space exploration for heterogeneous-ISA chip multiprocessors [70, 196]. These works simulate a heterogeneous-ISA CMP with cache-coherent shared memory, allowing the authors to demonstrate power and performance benefits of leveraging multiple ISAs. However, no such CMP exists at the commodity-scale at the time of writing this dissertation. Many ISAs are proprietary [13, 14] and even for open-license ISAs, their

cache implementations have compatibility issues due to ISA-specific memory consistency semantics [176, 10]. This dissertation instead proposes system software for cross-ISA execution migration in systems composed of commodity scale hardware. While some of the Popcorn compiler and run-time system components have similarities with DeVuyst et al. [70] and Venkat and Tullsen [197], there are significant differences. In particular, the Popcorn compiler and state transformation runtime are co-designed with the Popcorn Linux OS to implement thread migration and memory consistency across non-cache-coherence heterogeneous-ISA CPUs. This requires new low-level mechanisms for interacting with the OS, including insertion of migration points, performing state transformation, initiating thread migration and bootstrapping execution post-migration. The compiler also differs in that it does not attempt to create a common stack layout but instead fixes up references to stack elements at runtime. Additionally, the Popcorn compiler toolchain and state transformation handles runtime migration for multithreaded applications, which are not explored by previous works including [197]. A detailed discussion of the differences between the dissertation and [70, 197] is presented in Chapter 2. Thus, to the best of our knowledge Popcorn Linux (OS, compiler, runtime) is the first complete software architecture providing the ability to transparently migrate threads of execution between commodity scale heterogeneous-ISA CPUs at runtime without any application changes.

Using Popcorn Linux allows developers to more easily target future heterogeneous-ISA CPU systems. In particular, because Popcorn Linux extends the shared memory abstraction across non-cache-coherent CPUs, developers can re-use existing parallel programming models (e.g., OpenMP [38] or Cilk [37]) and easily gain the benefits of heterogeneity. Existing multithreaded applications work as-is on Popcorn Linux; developers do not have to rewrite applications in a new programming model or environment to target new architectures. However, tuning applications to best take advantage of heterogeneous CPU systems poses a substantial challenge, as applications (and phases within applications) map differently to each architecture and cause different amounts of memory consistency communication over the network. libopenpop helps developers overcome these challenges by both minimizing cross-node synchronization traffic and by automatically distributing parallel work in consideration of system characteristics. Thus, Popcorn Linux helps developers regain programmability while simultaneously allowing them to easily benefit from advances in computer architecture.

Finally, the prevalence of security exploits is leading to new ideas on how to thwart attackers. In particular, security experts have begun devising new methods to prevent attackers from gaining control over applications or leaking sensitive information. One successful approach is to use randomization [34, 66, 203] to prevent the attacker from utilizing program structure to attack vulnerable applications. Because the Popcorn Linux compiler generates rich stack layout metadata and the state transformation runtime is proven to rewrite thread execution state with small latencies, this infrastructure can be repurposed into a security context to implement efficient and robust randomization.

#### 1.2.1 Popcorn Compiler Toolchain

This dissertation presents the Popcorn compiler toolchain, which builds multi-ISA binaries suitable for migration across heterogeneous-ISA boundaries. The toolchain natively compiles applications written in C and C++ for all ISAs in the system using a common frontend and ISA-specific backends. The compiler automatically inserts migration points into the source code at function call sites. The compiler runs several analyses over an intermediate representation of the application to gather live data that must be transformed between ISA-specific formats. The compiler generates metadata (added as extra sections in the multi-ISA binary) describing the code and live data locations emitted for each architecture. The linker aligns global data in a common format (including thread-local storage), and a final post-processing step optimizes the application for efficient state transformation. The compiler is built using clang and LLVM [160] for compilation and GNU gold [86] for linking. The Popcorn compiler builds multi-ISA binaries with minimal changes to the core data layout mechanisms of the compiler, which allows our implementation to be more easily ported to new architectures unlike previous works [70, 197].

#### 1.2.2 State Transformation Runtime

This dissertation presents a state transformation runtime for efficiently translating execution state of threads between ISA-specific formats. The runtime cooperates with the operating system scheduler to decide at which points to migrate. After the scheduler requests a migration, the runtime attaches to a thread's stack and begins state transformation. Using the metadata generated by the compiler, the state transformation runtime efficiently reconstructs the thread's current live function activations in the format expected by the destination ISA, including transforming a thread's register state, call frames and pointers to other stack objects. After reconstructing the stack, the runtime invokes the OS's thread migration mechanism and bootstraps on the destination architecture to resume normal execution. This dissertation also develops a methodology for invoking migration for multi-threaded applications in a real system. This dissertation describe how threads cooperate with the OS both before and after migration for seamless migration. It describes how the state transformation runtime attaches to and transforms an individual thread's state. Using this setup, this dissertation demonstrates that state transformation can be performed in under a millisecond, and oftentimes under several hundred microseconds, for real applications from the NAS Parallel Benchmarks suite [23]. Additionally, this dissertation presents an evaluation of Popcorn Linux that demonstrates up to a 66% reduction in energy and up to an 11% reduction in energy-delay product [119] for a multiprogrammed, datacenter-like workload.

#### 1.2.3 Scale-Out and Heterogeneous OpenMP

This dissertation presents the design of an OpenMP [38] runtime named libopenpop optimized for systems composed of non-cache-coherent CPUs connected via distributed shared memory. In particular, libopenpop rebuilds many of the core components of OpenMP to prevent excessive overheads when running across multiple non-cache-coherent CPUs, where each CPU is designated as its own domain. libopenpop establishes a hierarchy of threads across CPUs and breaks OpenMP functionality down into local and global components. Using the hierarchy allows libopenpop to minimize the number of threads synchronizing on global data and therefore minimizes the amount of data movement required for synchronization. Using this thread hierarchy, libopenpop optimizes synchronization primitives like barriers, reductions and work distribution mechanisms. On a small cluster, libopenpop demonstrates a 38x speedup in multi-server barrier latency, a 5.4x speedup in multi-server reduction latency, and a geometric mean speedup of 4.04x for scalable applications.

In addition to refactoring the OpenMP runtime for scalability across non-cache-coherent CPUs, libopenpop introduces new parallel work distribution primitives that allow the OpenMP runtime to adapt parallel execution to best leverage the heterogeneous CPUs comprising the system. libopenpop monitors data movement (i.e., page transfers in distributed shared memory systems) and execution characteristics during parallel execution. Using this information, libopenpop determines whether to execute parallel computation across multiple CPUs or distribute work to only a single CPU. In the former case, libopenpop determines how much work to give each CPU to balance performance and minimize execution time. In the latter case, libopenpop automatically determines which CPU is best suited for a given computation. For an x86 machine and ARM machine interconnected via Infiniband, libopenpop demonstrates up to a 4.7x speedup and a geometric mean speedup of 41% over the best single-node homogeneous execution.

#### 1.2.4 State Transformation for Runtime Re-randomization

This dissertation presents Chameleon, a runtime re-randomization framework that utilizes the Popcorn compiler to continuously re-randomize the stack layout and code of applications. Chameleon is an out-of-band framework, meaning that it executes in an entirely separate context from the target application and attaches to it via existing operating system interfaces. Chameleon's goal is continuously change the application's state so as to thwart exploits such as stack smashing attacks [152] and return-oriented programming (ROP) exploits [177]. Chameleon continuously generates new sets of randomized application code for target applications. Periodically, Chameleon pauses the target application and atomically switches it to the newly randomized code, transforming the target application's execution state from the previously randomized layout to the newly randomized layout. In this way, would-be attackers have a diminishing window of time in which to discover how Chameleon has laid out the application's state, craft an exploit and launch the attack. Chameleon dis-

rupts a geometric mean 76.32% of gadgets discovered by a gadget finding tool in benchmark binaries. Additionally, Chameleon can randomize the locations of stack elements to an average of 3 different locations per stack element, forcing the attacker guess where buffers are located with low probability. Finally, Chameleon provides these security benefits with low overhead – a geometric mean 1.1% overhead when re-randomizing the target application every 50 milliseconds. This is significantly better than other dynamic binary instrumentation (DBI) solutions, which add 14.9% or greater overhead [66, 203, 196].

#### 1.3 Thesis Organization

This dissertation is organized as follows. The dissertation first describes the core Popcorn compiler infrastructure, including compiler and state transformation runtime. Next, the dissertation describes how the infrastructure is leveraged for accelerating multithreaded applications. The dissertation finally describes how the infrastructure is leveraged for enhancing the security of applications. Chapter 2 summarizes related work in each of the aforementioned areas, including execution migration in heterogeneous-ISA systems, scale-out/heterogeneous parallel execution and security. Chapter 3 describes Popcorn Linux, the replicated kernel operating system used to provide execution migration across ISA boundaries. It also formalizes the state of an application and describes the requirements for the compiler and state transformation runtime. Chapter 4 describes the Popcorn compiler toolchain which is used to analyze and build applications for cross-ISA migration. Chapter 5 describes the state transformation runtime and how threads migrate between architectures. Chapter 6 evaluates overheads associated with the state transformation runtime and energy benefits obtained when using execution migration in a datacenter context. Chapter 7 describes an exploration into using HTM to reduce migration response time. Chapter 8 describes libopenpop, including how it restructures OpenMP execution for cross-node execution. Chapter 9 evaluates scaling out OpenMP execution on a cluster. Chapter 10 describes how libopenpop makes workload distribution decisions in heterogeneous CPU systems. Chapter 11 evaluates libopenpop's ability to leverage diverse CPU architectures. Chapter 12 describes Chameleon and how it uses the Popcorn compiler infrastructure to implement continuous re-randomization. Chapter 13 evaluates the security and performance properties of Chameleon. Finally, Chapter 14 concludes and describes future work in each of these areas.

### Chapter 2

#### Related Work

# 2.1 Compiler and Runtime Support for Heterogeneous Architectures

Traditionally, developers have programmed heterogeneous architectures using a variety of programming models and languages. NVIDIA's CUDA [150] provides a programming language for NVIDIA GPUs. Using CUDA, developers partition their application into host (CPU) and device (GPU) code. Device code is offloaded to the GPU, and users must provide memory consistency by manually moving data between host and device memory spaces. More recently, CUDA offers managed shared memory between the host and device, but provides limited consistency guarantees. Thus, execution is offloaded to devices only at predefined locations and cannot be adapted in the face of changing workload conditions. OpenCL [92], OpenMP 4.0 [38] and OpenACC [153] offload computation to different target processors, but suffer from the same limitations as CUDA. Popcorn Linux provides strong memory consistency guarantees using distributed shared virtual memory and does not require applications to be partitioned between devices.

Saha et al. [170] describe an OS mechanism for shared memory between single-ISA heterogeneous cores interconnected over PCIe. Their programming model allows developers to open shared memory windows between the interconnected processors. These windows have a relaxed consistency, requiring developers to insert synchronization points to make memory writes visible across the PCIe bus. However, this programming model does not enable execution migration between interconnected processors, but rather uses a similar partitioning approach to CUDA. Popcorn Linux provides stronger consistency guarantees and flexible execution migration.

The Message Passing Interface (MPI) [91] provides a portable API for parallel processing using message passing for communication between processes. Processes execute in sepa-

rate address spaces but can share memory by manually sending and receiving data. The OpenMPI implementation [81] of the MPI standard supports serializing and de-serializing memory into ISA-specific formats, hiding cross-architecture data representation issues behind the interface. However MPI does not support execution migration at arbitrary points – developers manually insert data transfers and coordinate execution across processes on different machines within the application source code. Similarly to the programming models listed above, this hinders programmability and the flexibility of the system to adapt to changing workload conditions.  $PC^3$  [76] uses a modified C/MPI compiler to instrument MPI applications for execution migration in a cluster and uses checkpointing to transfer state. However developers must manually annotate checkpointing locations and the compiler only accepts MPI applications that have well-typed code. Furthermore, the checkpointing system requires annotating data with descriptors as the data comes into and goes out of scope, adding significant runtime overhead for metadata collection in addition to checkpointing costs. Popcorn Linux allows efficient and flexible execution migration between processors and distributed shared virtual memory.