# AN AUTOMATIC TEST GENERATION METHOD FOR CHIP-LEVEL CIRCUIT DESCRIPTIONS

by

Daniel Scott Barclay

Thesis submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of Master of Science

in

Electrical Engineering

#### APPROVED:

James R. Armstrong, Chairman

Joseph G. Tront

Charles E. Nunnally

February 6, 1987 Blacksburg, Virginia

# AN AUTOMATIC TEST GENERATION METHOD FOR CHIP-LEVEL CIRCUIT DESCRIPTIONS

by

Daniel Scott Barclay James R. Armstrong, Chairman Electrical Engineering (ABSTRACT)

An automatic method generates tests for circuits described in a hardware description language (HDL). The input description is in a non-procedural subset of VHDL, with a simplified periodoriented timing model. The fault model, based on previous research, includes micro-operation and control statement faults. The test method uses path-tracing, working directly from the circuit description, not a derived graph or table. Artificial intelligence problem-solving techniques of goals and goal solving are used to represent and manipulate sensitization, justification, and propagation requirements. Backtracking is used to recover from incorrect choices. The method is implemented in ProLog, an artificial intelligence language. Results of this experimental ProLog implementation are summarized and analyzed for strengths and weaknesses of the test method. Suggestions are included to counter the weaknesses. A user's manual is included for the experimental implementation.

# **Table of Contents**

| Introduction                                  |

|-----------------------------------------------|

| Contents 2                                    |

|                                               |

| Literature Review                             |

| Gate Level Methods                            |

| Register Connection Level Methods             |

| Register Transfer Level Methods               |

| Graph Methods                                 |

| Hardware Description Language Methods         |

| ·                                             |

| Test Method                                   |

| Hardware Description Language Characteristics |

| VHDL Subset                                   |

| HDL Terminology                               |

| Fault Models                                  |

| Original Fault Model                          |

| Modified Fault Model 16                       |

| Results of Modified Fault Model          | 17 |

|------------------------------------------|----|

| General Approach to Solving              | 17 |

| Goals and Data Structures                | 19 |

| Actions                                  | 21 |

| Listing Faults                           | 21 |

| Selecting Basic Tests                    | 22 |

| STUCKTHEN/STUCKELSE Test                 | 22 |

| DEADCLAUSE test                          | 22 |

| ASSNCNTL Test                            | 23 |

| Micro-Operation Test                     | 23 |

| Solving for a Test Vector                | 24 |

| Backtracking                             | 25 |

| Solving Goals                            | 25 |

| Base Times and Substitution              | 32 |

| Loop Cuts                                | 33 |

| Fault Awareness                          | 33 |

| Two-Phase Tests                          | 34 |

| Enhancements                             | 35 |

| Simple Controllability and Observability | 35 |

| Conflict Checks                          | 36 |

| Object Value Substitution                | 36 |

| Solved and Decided Goal Lists            | 37 |

| DND2 VIO checks                          | 38 |

| Unsolved Goal List Sorting               | 38 |

|                                          |    |

| Results                               | 40 |

|---------------------------------------|----|

| Experimental Implementation of Method | 40 |

| Some Implementation Details           | 40 |

| Circuit Models Used 4                                                                                                                                                                                                          | 2                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| ADDER 4                                                                                                                                                                                                                        | 4                                    |

| ADDR2 4                                                                                                                                                                                                                        | 4                                    |

| CCNT2 4                                                                                                                                                                                                                        | 4                                    |

| СКТА 4                                                                                                                                                                                                                         | 4                                    |

| СКТСУ 4                                                                                                                                                                                                                        | 5                                    |

| CNTR 4                                                                                                                                                                                                                         | 5                                    |

| CNTRV                                                                                                                                                                                                                          | 5                                    |

| DFF                                                                                                                                                                                                                            | 6                                    |

| FNTST                                                                                                                                                                                                                          | 6                                    |

| PRTY                                                                                                                                                                                                                           | 6                                    |

| SHFT                                                                                                                                                                                                                           | 6                                    |

| SHFTV                                                                                                                                                                                                                          | 7                                    |

| UARTO                                                                                                                                                                                                                          | 7                                    |

|                                                                                                                                                                                                                                |                                      |

| Test Generation Results 4                                                                                                                                                                                                      | 7                                    |

| Test Generation Results    4      Sample Model Results    4                                                                                                                                                                    |                                      |

|                                                                                                                                                                                                                                | 9                                    |

| Sample Model Results 4                                                                                                                                                                                                         | 9                                    |

| Sample Model Results    4      ADDER    5                                                                                                                                                                                      | 9<br>0<br>0                          |

| Sample Model Results    4      ADDER    5      ADDR2    5                                                                                                                                                                      | 9<br>0<br>0                          |

| Sample Model Results4ADDER5ADDR25CCNT25CKTA5                                                                                                                                                                                   | 9<br>0<br>0                          |

| Sample Model Results4ADDER5ADDR25CCNT25CKTA5                                                                                                                                                                                   | 9<br>0<br>0<br>1<br>2                |

| Sample Model Results4ADDER5ADDR25CCNT25CKTA5CKTCV5                                                                                                                                                                             | 9<br>0<br>0<br>1<br>2<br>3           |

| Sample Model Results4ADDER5ADDR25CCNT25CKTA5CKTCV5CNTR5                                                                                                                                                                        | 9<br>0<br>0<br>1<br>2<br>3<br>3      |

| Sample Model Results       4         ADDER       5         ADDR2       5         CCNT2       5         CKTA       5         CKTCV       5         CNTR       5         CNTRV       5                                           | 9<br>0<br>0<br>1<br>2<br>3<br>3<br>3 |

| Sample Model Results       4         ADDER       5         ADDR2       5         CCNT2       5         CKTA       5         CKTCV       5         CNTR       5         DFF       5                                             | 9<br>0<br>0<br>1<br>2<br>3<br>3<br>4 |

| Sample Model Results       4         ADDER       5         ADDR2       5         CCNT2       5         CKTA       5         CKTCV       5         CNTR       5         CNTRV       5         DFF       5         FNTST       5 | 9<br>0<br>1<br>2<br>3<br>3<br>4<br>4 |

| UARTO                                     | 55 |

|-------------------------------------------|----|

| Summary                                   | 55 |

| Execution Speed                           | 56 |

|                                           |    |

| Analysis and Suggestions                  | 57 |

| Fault Awareness and Reuse Avoidance       | 57 |

| Stuck-At Versus Assignment Control Faults | 58 |

| Reconvergent Fanout                       | 59 |

| Forward Implication                       | 59 |

| Time Choice Strategy                      | 60 |

| Two-Phase Tests and Time Choices          | 61 |

| Inequality Solving and Dummy Variables    | 61 |

| New Framework                             | 62 |

| The Need for a New Framework              | 62 |

| State Vector Style                        | 63 |

| PODEM-Style Searching                     | 64 |

| Decision Numbers                          | 64 |

|                                           |    |

| Conclusions                               | 65 |

|                                           |    |

| References                                | 66 |

|                                           |    |

| USER'S Manual                             | 69 |

| Introduction to User's Manual             | 69 |

| VHDL Subset Allowed                       | 69 |

| Using Other VHDL Constructs               | 70 |

| Translating into Internal Form            | 71 |

| Declarations                              | 71 |

| Expressions               | 2 |

|---------------------------|---|

| Values                    | 2 |

| Expression Elements       | 2 |

| Statements                | 3 |

| Running the Programs      | 6 |

| Generating Test Vectors   | 0 |

| Displaying the Fault List | 0 |

| Tracing Goal Solving      | 0 |

| Breakpoints               | 1 |

| Keeping a Log             | 2 |

| Exiting Prolog            | 2 |

| Modifying the Fault Model | 2 |

| Circu | it Models and Fault Lists | 83 |

|-------|---------------------------|----|

| L     | ADDER Description         | 85 |

|       | ADDER Fault List          | 86 |

| 1     | ADDR2 Description         | 87 |

|       | ADDR2 Fault List          | 90 |

| (     | CCNT2 Description         | 93 |

| (     | CCNT2 Fault List          | 97 |

| (     | CKTA Description          | 98 |

| l     | CKTA Fault List           | 01 |

| (     | CKTCV Description 1       | 02 |

| (     | CKTCV Fault List 1        | 06 |

| (     | CNTR Description 1        | 07 |

| (     | CNTR Fault List           | 09 |

| (     | CNTRV Description 1       | 11 |

| (     | CNTRV Fault List          | 13 |

| DFF Description   | 114 |

|-------------------|-----|

| DFF Fault List    | 117 |

| FNTST Description | 119 |

| FNTST Fault List  | 121 |

| PRTY Description  | 122 |

| PRTY Fault List   | 123 |

| SHFT Description  | 125 |

| SHFT Fault List   | 130 |

| SHFTV Description | 132 |

| SHFTV Fault List  | 135 |

| UARTO Description | 137 |

| UARTO Fault List  | 140 |

|                   |     |

| Vita | 141 |

|------|-----|

|------|-----|

.

# List of Illustrations

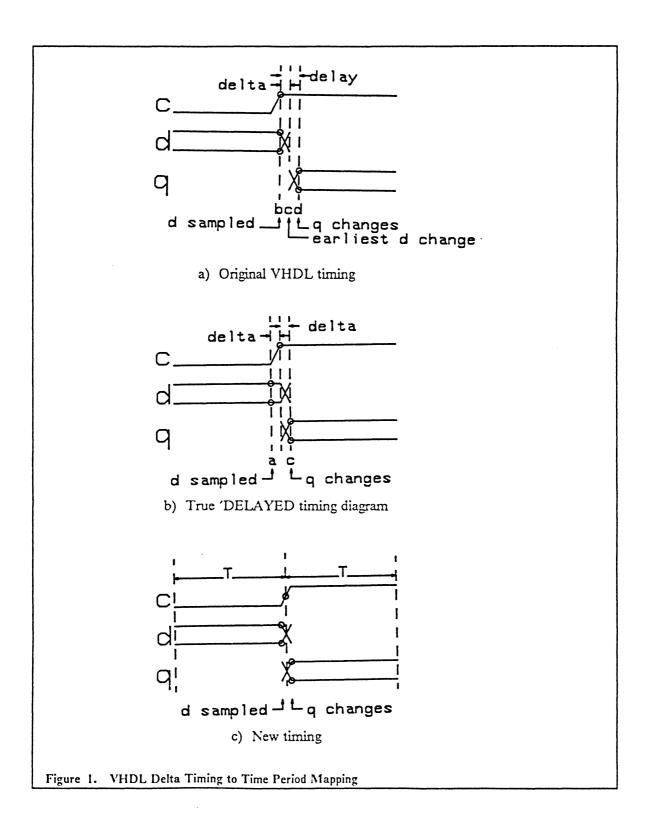

| Figure | 1. VHDL Delta Timing to Time Period Mapping | 11  |

|--------|---------------------------------------------|-----|

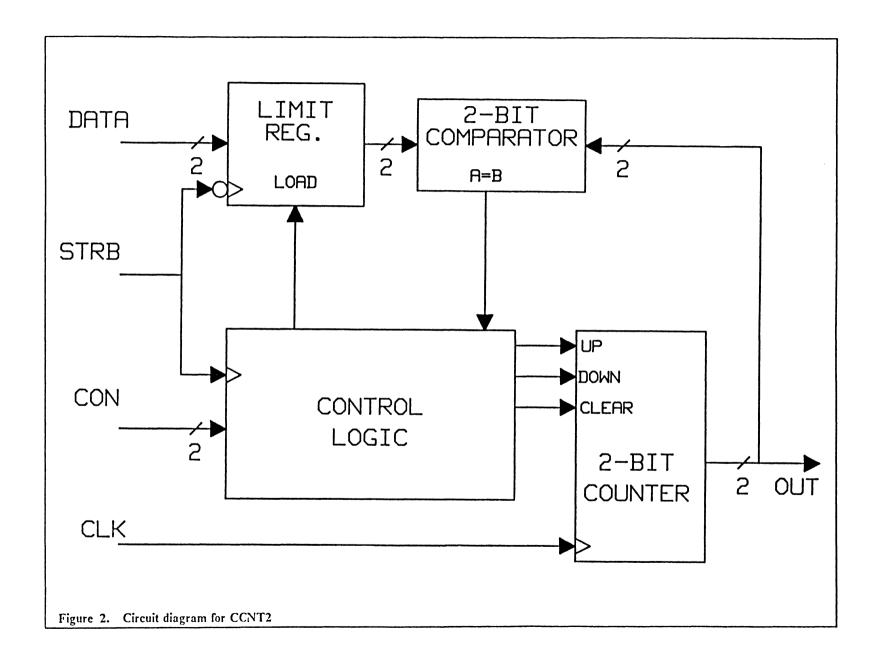

| Figure | 2. Circuit diagram for CCNT2                | 96  |

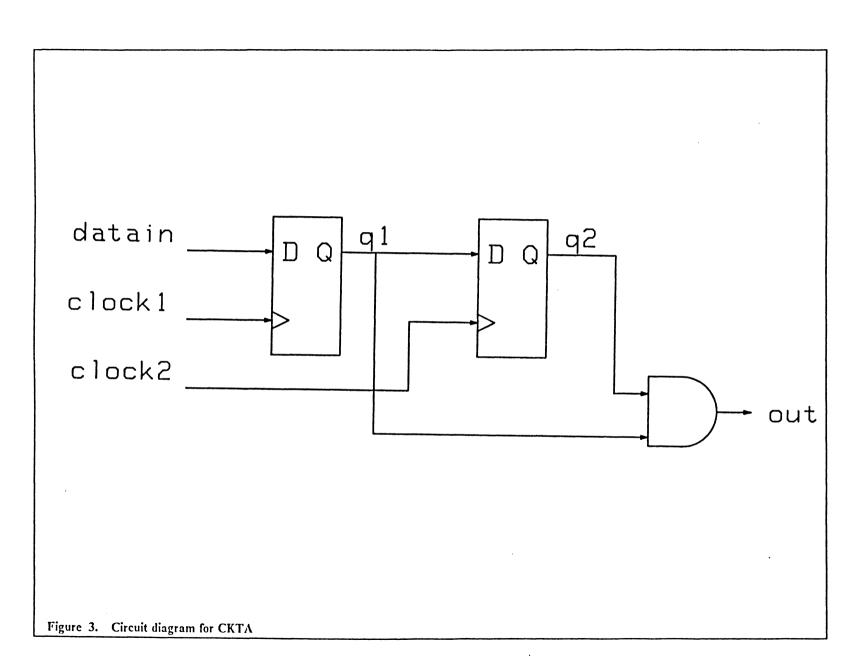

| Figure | 3. Circuit diagram for CKTA                 | 100 |

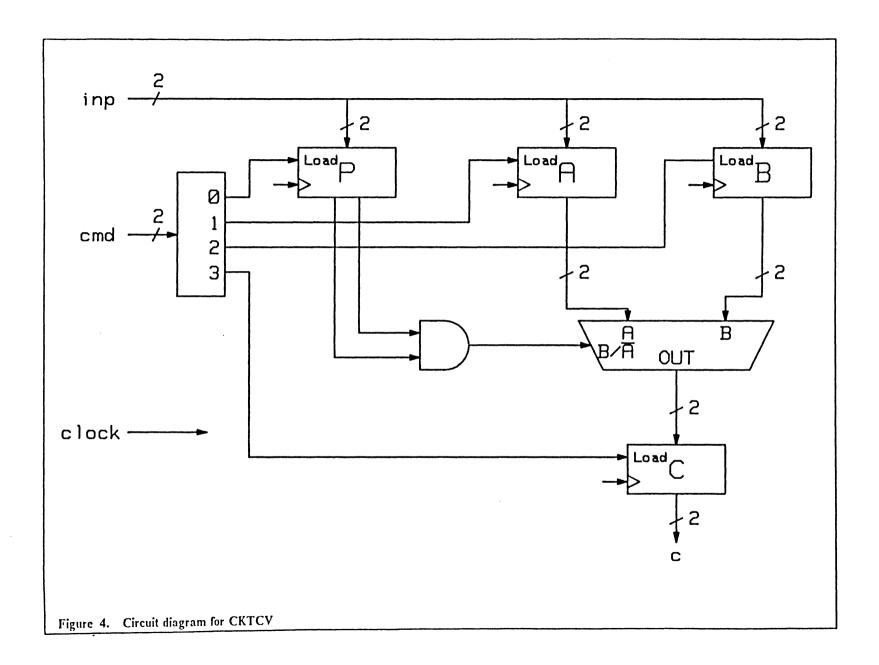

| Figure | 4. Circuit diagram for CKTCV                | 105 |

# List of Tables

| Table | 1. Sample models used           | 43 |

|-------|---------------------------------|----|

| Table | 2. Test generation results      | 48 |

| Table | 3. Micro-Operations Available.  | 74 |

| Table | 4. Summary of Translation Rules | 77 |

| Table | 5. ProLog source files          | 78 |

# Chapter 1

# Introduction

As circuit design and simulation has evolved from the gate level to the chip level to handle increasing circuit complexities, fault modeling and automatic test generation have lagged behind.

When digital circuits were described only at the gate level. Circuit faults were modeled with the classical stuck-at fault model, i.e. gate inputs or outputs became stuck at a logic one or a logic zero. Roth's D-algorithm [1] and direct enhancements [2,3,4] generated tests for stuck-at faults from a combinational gate-level description. The D-algorithm was also extended to test sequential gate-level circuits [5,6].

At the register connection level, the description consists of connected devices such as registers, counters, multiplexors, ALUs, etc., where these devices are description primitives for simulation efficiency and are not hierarchically constructed from gates. Typically, stuck-at models are used at this level. Test generation methods for this level are usually based on the D-algorithm [7,8,9].

With AHPL [10] and similar register transfer languages (RTLs), circuit descriptions no longer directly reflect circuit structure. This level required new fault models. Su [11, 12, 13, 14, 15, 16] developed fault models and a test generation method for RTL descriptions.

Recently, with the introduction of hardware description languages (RTLs) such as GSP [17, 18], GSP2 [19, 20], and VHDL [21, 22], circuit description has reached the chip level, where circuits are described as a whole, not as a hierarchy of low-level primitives, in a syntax similar to a computer program. Chip-level modeling also requires new fault models. Recent fault modeling research [22, 23, 24] gives a chip-level fault model derived from HDL constructs.

This chip-level fault model provides the basis for a chip-level test generation method. The fault model tells to how to sensitize chip-level faults, and the definition of the HDL in which a circuit is described tells how to complete tests given the sensitization requirements.

### **Contents**

This thesis describes an approach to test generation for chip level models, including the HDL and fault model used, the test generation strategy, the current implementation and results, and suggestions for improvement.

Chapter II, "Literature Review", is a review of previous methods and techniques used in automatic test generation, from gate-level methods to other chip-level method.

Chapter III, "Test Method", describes the test method. It outlines the overall strategy, general test generation, special cases, and efficiency enhancements.

Chapter IV, "Results", describes the current implementation and reviews results of running test generation on some small models.

Chapter V, "Analysis and Suggestions", analyzes test generation results and suggests some improvements.

Chapter VI, "Conclusions", gives conclusions about the test method method.

Appendix A, "USER'S Manual", describes how to use the ProLog implementation.

Appendix B, "Circuit Models and Fault Lists", lists VHDL and internal-form descriptions of the circuit models used in this research, and gives faults lists for the circuit models, including brief comments on successes and failures.

# Chapter 2

# Literature Review

# Gate Level Methods

Original automatic test generation work was done at the gate level.

Probably the most important development in automatic test generation was the Roth's Dalgorithm [1]. The D-algorithm is based on D-calculus, in which D represents a good value of 1 and a faulty value of 0,  $\overline{D}$  represents a good value of 0 and a faulty value of 1, and gate functions are redefined in terms of D or  $\overline{D}$  (in addition to only 0 and 1). D-calculus provides for defining the effects of a stuck-at fault, and is used by many subsequent test methods. The D-algorithm uses the structure of a circuit to propagate faulty values through the circuit, and to justify values needed on internal lines. Justification may require choices, which in turn may lead to conflicts. The Dalgorithm uses backtracking when conflicts are discovered, as with all subsequent methods.

The D-algorithm was adapted for sequential gate-level circuits. Kobu treated sequential subcircuits (i.e. flip-flops) as primitive elements [6]. Roth used a heuristic loop-cut method to cut combinational feedback loops in gate-level circuits [5]. Both methods are based on changing the sequential problem to a combinational one, by making multiple copies of the combinational portion of the circuit, cut at the state variables, and running combinational test generation on the resulting iterated circuit.

Goel [2] presents a method called PODEM, designed to handle reconvergent fanout, a problem on which the D-algorithm bogs down. Goel uses Roth's D-notation and D-propagation, but uses a more efficient control structure to implicitly search the space of all possible tests. He used the "branch and bound" method of searching to manipulate primary inputs to find a test, with heuristics to improve the efficiency of the search.

The 9-V (for nine logic values) algorithm [4] is another method addressing reconvergent fanout. For multiple path tracing (needed when there is reconvergent fanout), propagating a value through a gate sometimes needs a fixed 0 or 1 on inputs of the gate, and sometimes needs another D or  $\overline{D}$ . The D-algorithm tries each choice separately, backtracking when one fails. The 9-V algorithm uses additional logic values to represent each combination of choices, so less backtracking is required.

## **Register Connection Level Methods**

Above the gate level is the register level, where circuit primitives are functional units such as registers, counters, multiplexors, ALUs, etc. (That is, these devices are not modeled hierarchically in terms of gates.)

Shteingart, Nagle, and Grason [7] present RTG, a register-level stuck-at test generator. RTG uses high-level modeling of sequential elements for simulation and test generation efficiency. Specifically, sequential components are modeled using primitive functions such as clear, load, etc., and are not constructed from gates. RTG uses the D-algorithm-based 9-V algorithm, extended to handle clock pulses, to work on the combinational portion of a sequential circuit. RTG has a global approach to sequential test generation. One key element is that it runs combinational test

generation on several time slices at once. (That is, it does not work progressively on adjacent time slices). When working with sequential circuits, a test generator must be careful about getting into endless loops by moving data values around in sequential feedback loops, or by returning to the same state. When loading a register, RTG checks that the register was not encountered before when justifying the current test.

Marlett [8, 9] presents a method called EBT. The main elements are two-period truth tables for sequential circuits and a unidirectional time flow for test vector generation.

The two-period truth tables relate the inputs, clocks, and outputs for sequential circuits. For a typical rising-edge-triggered device, the edge sensitivity is represented as a low value in the first period and a high in the second period. Required inputs are given in the first period, and outputs are given in the second period. Thus, the current state is related to previous period inputs and state.

EBT works backwards, generating the last test vector first, and the first one last. Instead of working bidirectionally forwards (for propagation) and backwards (for justification) from the time of the actual internal fault detection at the site of the fault, EBT works from detection at an output pin back to the first justification step. The purpose was to gather all constraints for a given time period at once, for better conflict detection. Marlett also uses decision numbers to improve back-tracking. At a conflict, decision numbers associated with node values are used to find the most recent related decision; backtracking skips to that point, bypassing decisions known to be unrelated.

### **Register Transfer Level Methods**

Above the register level is the register transfer level, in which the description consists of a sequence of instructions, and does not necessarily reflect the structure of the actual circuit.

Stephen Su has done work at register-transfer level [11, 12, 13, 14, 15, 16]. Lin and Su [11, 12] describe the S-algorithm. Their work is based on an AHPL-style [10] control structure. They use a fault model based on possible failure modes of the various elements of the RTL description.

They use symbolic execution to find expressions representing good and bad result values in terms of register and input values. This execution includes path constraints, values needed to select an execution path through particular statements. They then select input values such that the path constraints are satisfied and the results for good and bad execution differ. If such values are found, they constitute a test.

## Graph Methods

Work has been done using various types of system graphs. However, most methods apply only to microprocessors, and are not useful for general circuits [26, 27, 28].

Abadir and Reghbati [29] propose a path-tracing test method for circuit modeled as connected modules, where the function of each module is described with binary decision trees. Binary decision trees are a concise description of a module, considerably denser that truth tables for typical circuits. The authors define current and next state variables, to treat sequential circuits as combinational ones. Module testing involves testing each branch of the binary decision tree describing each bit of the module. Faults are stuck lines and functional faults, stuck-at perturbations of the binary decision trees. Tests generation is based on the D-algorithm, modified for sequentiality. It runs on time frames, with checks to ensure trying only a finite number of internal states.

# Hardware Description Language Methods

Most recently, circuits have begun to be described at the chip level [30], with hardware description languages (HDLs). Levendel and Menon [31] generalize the D-algorithm to apply to "CHDL" descriptions of circuits. They derive D-propagation cubes for boolean switching expressions, and also for non-switching operations such as shifting and addition. They analyze IF and CASE control statements controlling transfers to switching expressions to derive D-propagation information. However, instead of these derived D-propation cubes, they use the structure of the CHDL description for test generation. They consider procedural (sequential) and non-procedural (concurrent) interpretations of an HDL description. For procedural interpretation, they use a method similar to Su's symbolic execution [11].

R. Khorram [32] worked on test generation from models described in a procedural HDL which executes once per clock cycle. Khorram breaks testing into several parts: testing a particular statement, justifying required local inputs, activating the HDL statement, and propagating statement result to an output. Testing the statement refers to selecting values to test the variables or operations in the statement. Justification, as in other test methods, involves finding primary input values to get the required values to the statement under test. Activating a statement refers to presetting any conditions necessary to execute the HDL statement (e.g. the control expression of an IF statement). Propagation, also as expected, involves determining how to get local test results to an output. Khorram's method does stuck-at tests, plus functional tests for operators.

Khorram's justification involves finding a statement to load a variable, if the variable is not a primary input. This can lead to other required values, if the variable is loaded from other variables. Propagation involves finding a statement to move the fault syndrome closer to an output, unless the fault syndrome is not at a primary output. Similarly, propagation can imply other required values which must be justified. Since conflicts may crop up, backtracking is used, and Khorram suggests using heuristics to select choices.

# Chapter 3 Test Method

The method described here is a automatic test generation method for the chip level. The test method accepts an HDL description of a circuit, and uses a chip-level fault model to enumerate and sensitize faults. As opposed to more abstractly algorithmic methods, the test method directly examines the circuit description to justify and propagate values, as a test engineer might to generate tests manually. The method uses goals and goal solving, artificial intelligence problem-solving techniques, to represent and satisfy original, intermediate, and final test requirements.

# Hardware Description Language Characteristics

The test generation method works from a data-flow description of a circuit in an asynchronous block-structured concurrent HDL. Block-structured means that conditional execution is described with IF and CASE statements, not with GOTO or other branch statements (as in a register transfer language). Concurrent (or non-procedural) means that statements execute in parallel, and that only

inputs and state variables are involved. (There are no temporary variables that can take on different values sequentially through the description.) Asynchronous means that the description "executes" continuously (or equivalently, each statement executes whenever any of its input variables changes). (A synchronous description would execute once for each system clock period and so cannot model asynchronous clocks.)

#### VHDL Subset

VHDL, the Department of Defense's VHSIC Hardware Description Language [21], was adopted as the input language to define HDL details. Since VHDL is such a powerful language, and since only concurrent data-flow descriptions are considered, only a small subset of VHDL is handled, and timing assumptions are made to fit our timing model.

The method uses a simple period-based timing model, since it considers only functional tests and not timing tests. Primary inputs are set to values at the beginning of a time period and are held for the period. Clock inputs that require a rising edge require two time periods: one with a 0 immediately followed by one with a 1 (falling edges require a 1 followed by a 0). Primary outputs are sampled at the end of each period (before the next period's inputs are set). These periods are long enough for all signal propagation to complete and stabilize. This is the same style used in RTG [7], Marlett's EBT [8,9] and Khorram's work [32].

VHDL's delta timing is simplified to fit our time-period model. In VHDL, transitions are detected with the 'STABLE attribute [21]. The expression " x'STABLE " is false immediately after x changes, and true otherwise. 'STABLE is usually used as in

IF clk='1' AND NOT clk'STABLE THEN

q <= d AFTER delay;</pre>

to model a synchronous clock. In the example, a rising edge on clk would latch the value of d into q. Right after clk rises, the assignment statement executes. After the delay, q takes on its assigned value. (If no delay is specified, a infinitesimal delay of delta is used.) The timing is as in part a of Figure 1 on page 11. Note that as written the example takes the value of d right after the clock changes. Since with the propagation and hold times of real circuits, d will not change immediately if it is an output of another edge-clocked latch, an equivalent construction is:

IF clk='1' AND NOT clk'STABLE THEN

q <= d'DELAYED AFTER delay;</pre>

which changes the timing to that of part b of Figure 1.

To fit the period timing model, the following is assumed:

- when a signal's value changes from one period to the next, 'STABLE is false for that signal

- for any object other than the clock, in the IF statement or in any statement in the THEN clause, the previous period's value is used

- any object assigned as the result of an edge clock (in the THEN clause) takes on its new value in the second time period

Thus, the assumed timing is as in part c of Figure 1. The statement is said to execute in the previous period, though the value is actually assigned in the second period (this is arbitrary; this particular choice reduces special cases in the implementation).

The VHDL subset includes only signal objects and not variable objects. (Signals have a constant value during one pass through the description, representing state variables. Variables can take on several values sequentially at different points in the description. Thus, the value of a variable is not uniquely specified by the time (or which simulation pass); it must be qualified by position in the code.)

Objects may be bits or bit vectors. Values are 0 and 1, plus X (don't-care) in test generation. (Z, high-impedance, is not implemented.) Many other types can be mapped into these two. Booleans can be translated to bits, and integers to bit vectors (especially in CASE statement selection expressions).

Statement may be IFs, CASEs, or simple assignments. (This excludes all loops, and any function or submodule declarations. Loops are sequential, and require variables, which are not implemented.)

The test method assumes that all assignments to a signal refer to the same driver for the signal. Single drivers are assumed to avoid bus resolution functions, which are commonly expressed algorithmically with a loop, and which typically use Z values which are not currently implemented. This assumption is equivalent to placing all assignments to a given object within one process statement, sensitive to everything.

The subset includes most basic operations on data: boolean operations AND, OR, XOR, NOT, and EQV on bits and bit vectors, and EQ and NOTEQ operations for bit vectors; unsigned arithmetic operations ADD, SUB, less than and less than or equal for bit vectors; concatenation of bit vectors in expressions; and slices (subvectors) and elements of objects and expressions, except for slices of destination objects or using a slice as an edge clock.

Because of the time period model, all sequential logic must be modeled explicitly, with using cross-connected gates or other combinational feedback. This is a minor restriction, since a chip-level model would not have such feedback anyway.

Appendix A, the User's Manual, contains other details of these restrictions and assumptions.

#### HDL Terminology

The following terms refer to various elements of the VHDL [21] description of a circuit:.

literal: a value appearing right in the code; in " x < = '1'", " '1' " is a literal.

object: VHDL's term for simulation variable; VHDL has signals and variables as classes of objects; only signals are used here.

expression: object(s) and/or literal(s) combined with micro-operations; an expression may be arbitrarily complex, or may consist of a single object or single literal.

subexpression: an expression within an expression, as an argument to a micro-operation; in "IF a AND (b OR c) THEN...", subexpressions are " a ", "(b OR c)", " b ", and " c ".

source expression: the expression in an assignment statement, whose value is loaded into the destination object when the assignment statement executes.

destination object: (of an assignment statement): the object (to the left of the < =) set when the assignment statement executes.

control expression: the conditional expression of an IF statement or the selection expression of a CASE statement, which controls which THEN, ELSE, or WHEN clause executes.

conditional expression: the control statement of an IF statement; if its value is true, the statements under the THEN clause execute; if false, the ELSE executes.

selection expression: the control expression of a CASE statement; if its value matches a value in a WHEN phrase list, the statements under the WHEN clause execute.

clause: a set of statements under one branch of a control statement.

THEN clause: the statements under the THEN of an IF statement.

ELSE clause: the statements under the ELSE of an IF statement.

WHEN clause: the statements under a WHEN of a CASE statement.

WHEN phrase: the value(s) after the WHEN keyword which specify what value(s) is needed to execute the associated WHEN clause.

parent statement: the control statement controlling a statement.

under: controlled by; a statement is under a (control) statement if it is controlled by that statement.

under 'STABLE: under an IF statement with a 'STABLE; controlled by an edge clock.

top-level statement: a statement not under any other statement; top-level statements effectively execute all the time, and do not need any conditions set to execute.

## Fault Models

Gate-level stuck-at fault are insufficient at the chip level. A correspondingly high-level fault was needed for chip-level test generation.

#### **Original Fault Model**

Chip-level fault models were first presented by J. R. Armstrong [23]. He suggested microoperation and control faults. For a micro-operation fault, a micro-operation in the description fails to some other operation. As a heuristic, the dual of the operation was used, where defined. Though unusual, this choice has some hardware correspondence [24]. For a control fault, a branch functions incorrectly. For example, a conditional branch becomes inverted or unconditional, or an unconditional branch fails. A. K. Gupta used these fault models for chip-level test generation [24]. He used GSP [17, 18], an assembly language-style HDL, for fault simulation. Using manual test generation for a 3700-gate signal processing chip, these chip-level faults gave 88.6% coverage of gate-level stuck-at faults [24, 34]. Other fault simulation with GSP yielded coverages near 90% [34, 35].

#### **Modified Fault Model**

Gupta's control faults were modified to fit the constructs of a block-structured HDL [35]. The resulting faults are:

STUCKTHEN and STUCKELSE: An IF statement becomes stuck one way or the other, as if the conditional expression became stuck true or false.

DEADCLAUSE: A WHEN clause in a CASE statement fails to execute when it is selected.

(A STUCKCLAUSE fault might seem more consistent, but DEADCLAUSE should give better coverage. To test for STUCKCLAUSE faults on n clauses (n > 2), only 2 tests are needed: execute clause 1 (to detect stuck at clause 2 through stuck at clause n), and execute clause 2 (to cover stuck at clause 1). A test for a dead clause fault tries to execute the faulty clause, so it takes n tests to test n clauses. Using n tests should yield better coverage then 2 tests).

ASSNCNTL: For an ASSNCNTL (assignment control) fault, an assignment statement fails to execute (i.e. the assigned object is not changed). This addition was to improve coverage; a pure transfer (with no micro-operations) would not be tested directly without this fault type.

MICRO-OP: A micro-operation fails to some other operation. Each micro-operation may have several fault modes.

#### **Results of Modified Fault Model**

Additional experiments were done to verify this modified fault model [25]. Models for 11 small/medium-size circuits (12 to 91 gates, 44 average; plus 0 to 16 flip-flops, 6 average) were written in GSP2, a block-structured language [19]. Using this fault model, tests were derived manually from the chip-level models using the chip-level fault models. These tests were run on gate-level models of the same circuits, yielding an average coverage of 92.4%. Thus, the modifica-tions seem valid.

# General Approach to Solving

The chip-level test method is a path-tracing method that works directly from the HDL description of a circuit. After sensitizing the fault, path-tracing test generation must propagate the fault syndrome to an output and justify any needed interal values back to inputs. The particular HDL constructs in a description are used directly to justify and propagate values.

In a gate-level model, the inputs and state variables determine the outputs, through internal node values. This holds for chip-level descriptions, except for what constitutes a node. In a gatelevel mode, nodes (or nets) are gate inputs and outputs. In an HDL description, nodes correspond to objects, micro-operations, and whether statements execute (particularly, those statements under control statements dependent on expression values). Chip-level test generation works with these virtual nodes.

Justification: Justification involves working backwards to set inputs such that internal node values are satisfied. Khorram [32] separates justification of object and expression values from activation of statements. Our method considers these all justification.

Justifying expression values parallels combinational gate-level justification. An expression may consists of a micro-operation and its argument expressions. Justifying the expression's value requires selecting values for the arguments such that the micro-operation computes the desired value, much as gate inputs are selected to justify the gate output value.

To justify a value in an object, the circuit description is searched for an assignment statement to use to load the value into the object. The statement must be executed, and its source expression must be set to the value to be loaded. These requirements must be justified in turn. In general, the object could be loaded in a time period previous to when it is needed. The choice of when to load the value is separate from the choice of which statement to use.

To justify the execution of a statement, any IF or CASE statements controlling the statement must be executed, and any control expressions must be set appropriately, and justified in turn.

**Propagation:** Propagation involves using the fault syndrome at some place to affect another object, eventually moving it to an output.

Propagating an object value is similar to gate-level propagation of a state variable with fanout. Since the object can be used in expressions, an appearance in an expression is selected, and the fault syndrome is propagated through the expression. Also, since the object may hold its value over time, the time to observe the value must be chosen.

Propagating fault syndromes through micro-operations in expressions parallels propagation through a gate with a fanout of one. The value of the micro-operation's other argument is selected to pass a fault syndrome as the result of the micro-operation.

For an assignment statement source expression, the fault syndrome can be propagated to the assigned object by executing the statement. For a control expression, the faulty value affects execution (i.e. the good value executes one clause and the faulty value executes another clause). This execution difference is detected by its effects on an object assigned different values by assignment statements within the affected clauses. Expressions in these assignment statement may have to be set to ensure that the affected object gets different values in each case.

Sequentiality and Time Choices: Since HDL descriptions are in general sequential, justification and propagation involve choosing when to load objects. The time choice strategy is to assign each load event its own time designation, determine how to accomplish the load, and then decide exactly when to do the load relative to other load events. The time designation is called a base time. Constraints such that one load must precede another are expressed by saying that the former's base time be less than the latter's. At some point, the absolute offset between them is decided.

### Goals and Data Structures

The test method is implemented with goals. Goals are an artificial intelligence problem-solving technique used to break a problem into small pieces. Goals are used to represent and manipulate the requirements of a problem. The test method uses goals to represent basic sensitization requirements, derived justification and propagation requirements, and final test vector specifications. There are eleven types of goals to represent these requirements:

- 1. Preload goals:

- a. VIO (Value in Object): Need value in object at time.

- b. VIE (Value in Expression): Need expression equal to value at time.

- 2. Execution goals

- a. EXEC (Execute): Execute statement at time.

- b. DNE (Do Not Execute): Don't execute statement at time.

- c. EXG: (Execute Given): Execute statement at time given that set of statements execute.

- 3. Observation goals:

- a. OBSOBJ (Observe Object): Observe value in object at time for good value or bad value

- b. OBSEXPR (Observe Expression): Observe (sub)expression at time for good value or bad value

- c. OBSEXEC (Observe Execution): Observe execution of clauses of statement at time, expecting good or bad clauses to execute.

- 4. Preserve goals:

- a. DND2 (Do Not Disturb, Multiple): Preserve value in object loaded at time1 until time2.

- b. DND1 (Do Not Disturb, Single): Preserve value in object at period time.

- 5. TR (Time Relation): Specify time relation time  $1 \le time 2$  or time 1 = time 2.

VIO and VIE goals are used to load objects and set expression values. EXEC and EXG goals are used to activate statements. OBSOBJ and OBSEXPR specify where a fault syndrome currently is. OBSEXEC specifies a fault-induced difference of execution to be detected. TR goals represent constraints on when to load object or to propagate results. DND2, DND1, and DNE goals are ensure consistency by ensuring that loaded values are not overwritten.

Times are represented as a base time and an offset, in the form  $tn \pm m$ . Base times refer to arbitrary time periods. The offset refers to time periods relative to the base time. For example, t1+3 refers to the third period after period t1. Until decided and explicitly specified, there is no implied relation between different base times; they may be the same period or different periods.

The value of an object at a certain time is referred to by specifying the object name and the time. For example, x@t3-1 refers to the value of object x at time period t3-1.

There are two representations for expressions. One refers to expressions and subexpressions within the circuit description, for example, "the expression in statement 5," or " the left subexpression of the right subexpression of statement 7." (The latter example could refer to "x AND y" in "(a AND b) XOR ((x AND y) OR z).") Position codes are used, as in "5-" or "7RL", for example. The left/right nomenclature is based on the parse tree of an expression. The position code method can specify where to expect a fault syndrome, for OBSEXPR goals, or where a faulty micro-operation is. This is similar to numbering nodes in a gate-level circuit.

However, the position code method can only refer to expressions and subexpressions existing in the description. The method must be able to construct new expressions which might never occur in the description. For example, to make x and y different, one could require that " $x \neq y$ " be true, but " $x \neq y$ " might never occur in the description. To represent such expressions, a parse tree representing the expression is constructed and manipulated. To be able to refer to different objects at different times, times are associated with individual objects instead of the whole expression, for example in " $x@t0-1 \neq y@t1$ ." Associating times with objects in expressions is called *time-tagging* the expression. This second form of expressions is used in VIE expression fields, and in OBSOBJ and OBSEXPR value fields.

# Actions

The test method uses the chip-level fault models to list faults and to select "basic tests" for faults.

#### Listing Faults

Faults are listed by traversing the circuit description and listing faults for each HDL item. IF statements are listed for STUCKTHEN and STUCKELSE tests. CASE statement clauses are listed for DEADCLAUSE tests. Assignment statements are listed for ASSNCNTL tests. Each expression in the description is traversed to find micro-operations to test. For each micro-operation found, its fault cases are looked up and listed for testing.

#### **Selecting Basic Tests**

Basic tests are the sensitization requirements for faults, and are represented with goals. Basic tests for each fault are derived from the fault model. Base time t0 is chosen to refer to the time the internal test occurs (as opposed to when results are propagated to a primary output).

#### STUCKTHEN/STUCKELSE Test

A STUCKTHEN fault is sensitized by trying to execute the ELSE clause, by executing the IF statement and setting the conditional expression false. An EXEC goal specifies to execute the IF statement. A VIE goal sets the expression false: the IF statement control expression is copied, is time-tagged with t0 (the time of the basic test), and is set false with the VIE goal.

The fault is detected by observing which clause executes. An OBSEXEC goal specifies to detect whether the statement's THEN clause (indicating faulty operation) or ELSE clause (indicating good operation) executes at t0.

A test for STUCKELSE is similar, with the expression set true, to try to execute the THEN clause, and with the OBSEXEC good and bad clauses reversed.

#### **DEADCLAUSE** test

A DEADCLAUSE fault is sensitized by trying to execute the clause. A WHEN clause is executed by executing the CASE statement and having the selection expression equal to one of the values given in the WHEN phrase (usually a single value). An EXEC goal specifies to execute the CASE statement at time t0. To set the conditional expression, an expression of the form "(e = v1)OR  $(e = v2) \dots (e = vn)$ " is made, where e is a copy of the selection expression, and v1..vn are values in the WHEN phrase, any of which selects the clause. This expression is time tagged with t0, and specified to be true using a VIE goal. Thus, the selection expression will be set to one of the WHEN phrase values.

The fault is detected by observing whether the clause actually executes. An OBSEXEC goal specifies the CASE statement, the time (t0), and specifies that good execution would be the tested clause and bad execution would be nothing. (That is, nothing under the CASE statement would execute.)

#### ASSNCNTL Test

An assignment control fault is sensitized by executing the statement with an EXEC goal, and detected with an OBSEXEC goal. The OBSEXEC goal specifies that the statement will execute for good operation, and will not for bad operation. (This OBSEXEC will observe execution by trying to load a value using the assignment statement.)

#### Micro-Operation Test

A micro-operation fault is sensitized by setting the arguments of the operation such that the result of the good micro-operation differs from the result of the bad micro-operation (i.e.,  $f_{good}(arguments) \neq f_{bad}(arguments)$ ). To simplify this selection of values, a condition is given in a lookup table for each micro-operation fault case. This condition is expressed as an expression of the micro-operation's arguments which must have a required value. For example, for " < arg1 > AND < arg2 > " failing to " < arg1 > OR < arg2 > ", the condition is < arg1 >  $\neq$  < arg2 > . The lookup table rules construct an expression using the micro-operation's arguments. This expression is time-tagged with t0 (test time), and put in a VIE goal with the required value. When the VIE is solved, necessary conditions will be satisfied.

The micro-operation's result is detected with an OBSEXPR goal. The OBSEXPR specifies the position of the micro-operation, and specifies the good and bad values. The expected good and

bad results are simply the good function of the arguments and the bad function of them, respectively. The lookup table specifies this, or may specify a fixed value, if already constrained by the input condition.

#### Solving for a Test Vector

The test generation is done in the goal-solving phase. This solving phase takes the basic test goals and recursively solves them into goals representing the test vectors for a fault. Goals are solved by breaking them into subgoals which will accomplish the original goal, using rules for each goal type which take into account the circuit description.

The solving phase maintains an unsolved goal stack. Basic test goals are initially placed on this stack. As goals are picked off the stack, they examined. A goal may be primitive, inherently solved, solvable, or unsolvable.

*Primitive Goals:* A goal is primitive if it specifies a needed input pin value or an expected output pin value. Obviously, input pins can be directly controlled and output pins can be directly observed, so primitive goals are added to the test vector.

Inherently Solved Goals: A goal is inherently solved if nothing needs to be done. A goal requiring that x = x be true would be inherently solved; whatever x is, x = x is true. Nothing is done for inherently solved goals, since they are solved.

Solvable Goals: A goal is solvable if it can be accomplished by specifying several other goals. Most goals are solvable with subgoals. For example, a VIE goal requiring a AND b = 1 can be solved with VIE a = 1 and VIE b = 1. For solvable goals, the new subgoals are added to the unsolved goal stack, so they can be solved in turn. Frequently, there is a choice of how to solve a goal.

When one choice is made, the other options are noted so they can be tried later in case the original choice leads to a conflict.

Unsolvable Goals: A goal is unsolvable if there is no way to satisfy the goal. An example would be a VIO goal requiring one value in an object when the object has already been assigned a different value. This is also called a conflict. When an unsolvable goal is encountered, solving "backtracks" to the most recent choice point and selects a new option.

#### **Backtracking**

Backtracking is a technique to back up and try other options after encountering a conflict. At each point at which there is a choice of what to do, one option is chosen, and the others are saved. At a conflict, execution backs up to the most recent choice (restoring the state to what it was before that choice), and the next remaining untried option at that choice point is chosen. If no options remain, backtracking proceeds to the previous choice point.

In the test method, there are choices about how to solve goals. There is a choice of when to load an object or propagate a value. There may be multiple paths usable to load an object. There may be a choice of object values which will give the needed value for an expression.

Conflicts occur when a goal cannot be solved. Two goals may require conflicting (i.e. different) values in the same object at the same time. An execute goal may clash with a do not execute goal for the same statement at the same time. An unsolvable goal is considered a conflict.

#### Solving Goals

The various types of goals are solved as follows:

Solving VIO (Value in Object) goals: A VIO goal specifies that some object needs a certain value at some time. If the object is a primary input, the VIO is primitive, and becomes part of the test vector.

If the object is not a primary input, the object must be loaded, using an assignment statement, by the time the value is needed. A new base time is allocated to represent the time period in which the object is actually loaded, and is specified to be less than or equal to the time at which the value is needed. The statement must be executed, and its source expression must be set to the value given in the VIO goal. For an asynchronous statement (not under a 'STABLE), an EXEC goal specifies to execute the statement at the new base time, and a VIE goal specifies the needed value for the source expression at the new base time. For a synchronous statement (one controlled by a 'STABLE), the VIE applies in the previous time period (i.e. the new base time minus one period), before the clock edge. With the convention for when a synchronous statement executes, the EXEC goal also specifies this previous period. Finally, a DND2 goal specifies to preserve the value from the new base time (when it was loaded) to the time in the VIE goal (when it is needed).

Solving VIE (Value in Expression) Goals: A VIE goal requires a given expression of time-tagged objects, literals, and micro-operations to have a certain value. VIE goals are solved by selecting values for objects such that the expression has the needed value. There are several VIE cases.

If the expression is a just a literal value (i.e., no objects or operations) which is the same as the needed value, the VIE is inherently solved.

If the expression is a literal value different from the needed value, the VIE is unsolvable.

If the expression is a single object, the VIE is solved with a VIO requiring the value in that object, at the time with the time-tagged object. This case simply rewrites the VIE as a VIO.

The main case is when the expression consists of a micro-operation and its arguments. In this case, values are selected for the arguments to give the needed result. Since the arguments are in general expressions, a VIE goal specifies the selected value for each argument expression. There may be several combinations of values to give the needed result, so when one is chosen, the others are noted for backtracking.

Solving EXEC (Execute) Goals: An EXEC goal specifies to execute a statement at a particular time. Since EXEC goals are a special case of EXG goals, they are solved in terms of EXG goals (see "Solving EXG Goals (Execute statement given statement list)", below).

Solving EXG Goals (Execute statement given statement list): An EXG goal is used to execute a statement assuming that some higher-level statements already execute. EXGs are use for solving OBSEXEC goals, and for solving EXEC goals.

EXG goals are used mainly in solving OBSEXEC goals. An OBSEXEC goal specifies which clauses of a control statement execute for good and faulty operation. To detect execution, an assignment statement within the clause must execute to affect some object. The assignment may be nested under other IFs or CASEs, so values must be set to execute that assignment. For example, in

consider a test for statement s1 stuck at ELSE. Statement s1 would be executed with an EXEC goal, the control expression " a AND b" would be set true with a VIE goal to try to execute the THEN clause, and an OBSEXEC goal would specify good execution as the THEN clause and bad execution as the ELSE clause. If s5 is chosen to detect execution (by setting z), then s5 will execute whenever the THEN clause executes. However, if statement s3 is chosen to detect execution of the THEN clause (by changing the value in x), the expression "c OR d" must be set true.

EXG goals are used to set up such conditions needed to execute statements under a clause. In this example, an EXG goal would specify to execute s3 given that s1's THEN clause executes. The THEN clause is specified as s2 and s5, since execution of either s2 or s5 indicates that the THEN clause executed. (An EXEC s3 goal would be wrong, because s3 is not to be executed all the time, just if s1's THEN executes.) Solving this EXG would set " c OR d " true. If s5 is used, the EXG goal would be used to execute s5 given that s2 and s5 execute. In this case, no further goals are necessary.

EXG goals are also used to solve EXEC goals. If an EXG goal's given list consists of top-level statements (which always execute), solving the EXG goal will ensure that the statement executes. Thus, EXEC is a special case of EXG. (That is, the EXG goal executes the statement if the top-level statements execute. The top-level statements execute under any conditions. Therefore, the statement will always be executed.) An EXEC is solved by making an EXG goal, specifying the top-level statements as the assumed list.

EXG goals are solved as follows:

If the needed statement is in the list of given statements, the EXG is inherently solved (e.g. if it says execute s2 assuming that s1, s2, and s3 execute, s2 can be assumed to execute, so it is inherently solved.) This is the termination case.

Otherwise, the parent of the needed statement must be executed, and the clause containing the needed statement must be sensitized. The parent is executed with an EXG goal, specifying the same given statements. The clause is sensitized with a VIE goal. If the statement is in the THEN clause of an IF statement, the VIE sets the conditional expression true. If in the ELSE clause, it sets it false. If in a WHEN clause of a CASE statement, The VIE sets the expression "(e = v1) AND (e = v2) ... (e = vn)" true, where e in the selection expression and v1..vn are the values in the WHEN phrase, so that the selection expression has one of the WHEN values. This activates the clause if the CASE executes.

Solving DNE Goals (Don't execute statement at time): A DNE goal specifies to ensure that a statement does not execute at some time (e.g., to avoid changing a value in an object).

A DNE for a top-level statement is unsolvable, since a top-level statement always executes.

28

A statement can be avoided by avoiding its parent statement, or by desensitizing its parent clause (the parent statements's clause which contains the statement to avoid). The parent is avoided with a DNE for the parent statement. If that fails, the parent clause can be desensitized by setting the control expression's value with a VIE goal. For a statement under a THEN, the conditional expression is set false; for ELSE, it is set true. For a statement in a WHEN clause, the selection expression for the CASE statement must be set so that its value is not one of the WHEN phrase values which would select the WHEN clause. To specify this requirement, the expression and v1..vn are WHEN values which could select the clause. This expression will be true only if the selection expression value is *not* one of the values for the WHEN clause. Thus, setting the expression true will ensure that if the control statement executes, the WHEN clause containing the statement will not execute.

Note that a DNE is the negation of an EXEC goal. An EXEC goal executes the parent and sensitizes the parent's clause; a DNE goal avoids the parent, or desensitizes the parent clause.

Solving OBSOBJ Goals (Observe object value at time1): An OBSOBJ goal specifies to observe the fault syndrome in some object at some time, with the the expected good and faulty values.

An OBSOBJ is primitive if the object is an output. Obviously, a fault syndrome at an output is directly observable. Such an OBSOBJ becomes part of the test vector.

If the object is not a primary output, the object's value must be observed indirectly by propagating the fault syndrome towards an output. The object value may be used in a source expression in an assignment that loads another object, or may be used in a control expression to affect execution. A new base time is selected as the time to use the value in the object and a TR goal specifies that this new time be equal to or after the time the fault syndrome appears in the object. An OBSEXPR is used to further propagate the fault syndrome within the expression using the object. The OBSEXPR refers to the position of the object within the expression, the time, and the good and faulty values. A DND2 goal specifies not to disturb the object's value until it is observed. Solving OBSEXPR Goals (Observe expression value at time1): OBSEXPR specifies a particular (sub)expression whose value to observe. This is equivalent to knowing a gate has a D or  $\overline{D}$  on it, and trying to propagate the value through combinational logic. The value in a subexpression is propagated up through expression operations, and then observed. There are several cases for OBSEXPR solving:

If the expression is the argument of a unary micro-operation, the propagated results are simply f(good) and f(bad), where f is the micro-operation. A new OBSEXPR is issued, referring now to the micro-operation, at the same time, and with the new good and bad values.

The binary case is a more complicated. The other argument of the micro-operation may need to be constrained. This constraint is expressed with a VIE goal, specifying a value for a symbolic expression constructed using the other argument. As in the unary case, the resultant values must be computed as a function of both the fault syndrome and the other argument. Finally, a new OBSEXPR is issued, pointing to the micro-operation, and specifying the newly-computed good and bad values.

If the expression to be observed is not an argument of a micro-operation, it is an assignment statement source expression or a control statement control expression.

For an assignment source expression, the fault syndrome can be loaded into some other object. An EXEC goal is used to execute the assignment statement, and an OBSOBJ goal specifies to observe the fault syndrome now in the object. (If the assignment statement is under a 'STABLE, the OBSOBJ specifies the following time period, since the value of the source expression before the clock edge will only show up in the destination object after the clock edge.)

For a control statement, the good vs. bad values affect which clauses execute. In an IF statement a good vs. bad value of 0 vs. 1 becomes ELSE vs.THEN, and 1 vs. 0 becomes THEN vs. ELSE. An OBSEXEC for the control statement specifies THEN vs. ELSE or ELSE vs. THEN as good vs. bad execution. For a CASE statement, the good value will select one clause, and the bad value will select another. An OBSEXEC specifies these clauses.

Solving OBSEXEC Goals (Observe execution of clauses of statement): OBSEXEC goals are used to observe the execution path, which cannot be observed directly, by observing its effects on some object. An OBSEXEC specifies a control statement and two of its clauses (one possibly empty) to check.

First, one of the objects loaded by statements under either of the two clauses is picked (alternates are saved for backtracking). Next, a statement assigning to that object is picked from each clause. These statements are used to load one value if the good clause executes and another if the bad clause executes. In a variation, only one statement from one of the clauses is picked, and no statements in the other clause are executed. Thus, the old value will be changed if that clause executes. The choice of statements is also subject to backtracking.

When two statements are selected, a VIE goal is used to specify that the source expression be different, by requiring  $e1 \neq e2$ , where e1 is one statement's source expression and e2 is the other's. An EXG goal for each ensures that each executes if its respective clause executes (the statements may be nested under other control statements). An OBSOBJ goal checks the resulting value. (For one statement, the VIE sets the object's old value to be not equal to the value the statement would load.)

Solving DND2 Goals (Preserve value in object from time1 to time2): DND2 specifies to preserve a value in an object from a start period to an end period. Most DND2 goals are issued with two different base times; thus, they cannot be solved until the accompanying TR goal is solved and one base time is represented in terms of the other. A DND2 is solved with a DND1 for each period in the DND2 interval.

Solving DND1 Goals (Preserve value in object at time): DND1 specifies to preserve a value in an object for a single time period. A DND1 is solved by finding all statements assigning to the object, and using a DNE for each to avoid executing it. In case the DNE fails, a VIE is used to set the source expression of a statement to the value already in the object, so if the statement executes, it reloads the value already in the object, thus preserving that value.

The statement that initially loads the value in the object must not be disallowed. DND2 and DND1 goals also include this loading statement. When a DND2 goal for an interval is solved with DND1 goals for each period in the interval, the DND1 goal for the first period (when the object was loaded) has a first-period flag set. When a DND1 goal is solved with DNEs for each statement that could disturb the object, if the DND1 is for the first period, no DNE is issued for the loading statement.

Solving TR Goals (Timing Relations): Time relation goals specify constraints between different base times. There are two forms: (TR t1  $\leq$  t2) and (TR t1 = t2).

A (TR t1  $\leq$  t2) goal specifies that time t1 be less than or equal to time t2. Usually (but not necessarily), each time is a base time with zero offset. The TR goal is solved by picking an offset between the times that satisfies the constraint. For example, (TR t1 + 1  $\leq$  t2) could be solved with t1 + 1 = t2, t1 + 1 = t2-1, t1 + 1 = t2-2, etc. When an offset is selected, a TR = goal is issued to unify one base time to some offset from the other. The offset is arbitrarily limited to some maximum.

A TR = goal is a very special case. It specifies one base time in terms of the other. To "solve" a TR = goal, all occurrences of one base time in all solved and unsolved goals are substituted in terms of the other base time. This binds the base times together. If time substitution leads to any conflicts, the TR = is unsolvable, and leads to backtracking (usually to try a different offset from the TR  $\leq$  goal).

### Base Times and Substitution

Recall that base times are names for arbitrary time periods. The test base time is t0. As base times are created, the index is incremented (i.e. the next is t1, then t2, etc.) When two times are unified with a TR = goal, the substitution is in terms of the one with the lower index, (e.g. t2 and  $t5 \rightarrow t2$  and  $t2\pm offset$ ). Thus, all final times will be in terms of t0; the offsets may range from negative to positive, which may be unfamiliar, but time labels are arbitrary anyway.

# Loop Cuts

Test generation for sequential circuits must deal with sequential feedback. Sequential feedback can lead to loops, in which an object is used to load itself, or the value in an object is propagated back to the object. Such loops waste effort, and can trap automatic test generation.

To sense and avoid loops, VIO and VIE goals, and OBSOBJ and OBSEXPR goals have an extra parameter. For a VIO or VIE goal, this parameter is a list of objects loaded from the current object or expression. The list specifies that the current VIO or VIE goal results from justifying values in these other objects. A register must not be loaded from itself, directly or indirectly. If the object to be loaded appears in the list, it means a loop was just completed. Under this condition, the VIO goal fails as unsolvable, to try another path. Solving a VIO goal adds the object to the path, and the VIE goal passes the path information on to the VIO goals it can lead to. OBSOBJ and OBSEXPR goals work similarly, checking that the fault syndrome is not loaded back into any place it has been.

## Fault Awareness

Test generation must keep track of the fault to ensure a correct test. This makes goal solving more complex. The goal solving rules given above assume correct operation, and must be modified to handle goal-solving correctly in the presence of a fault. Most modifications avoid using the faulty item to preload before the test, or to propagate results afterwards. Without checks, using the faulty item to test itself could mask out the fault. However, these checks preventing use of the statement or micro-operation must be overridden to use the statement or micro-operation once to test it.

For a STUCKTHEN fault, statements in the ELSE clause cannot be executed, and no statement in the THEN clause can be avoided if the IF statement executes. STUCKELSE faults are similar. For a DEADCLAUSE fault, no statement in the clause can be executed. Unless overridden, EXEC solving checks that the statement is not directly in a clause which cannot execute. DNE solving will only issue a DNE for the parent statement, and not try to desensitize the parent clause if the statement is in a STUCK clause.

For an ASSNCNTL fault, the statement cannot be used to preload or observe, since it may be faulty. Unless overridden, EXEC solving also checks that there is no ASSNCNTL fault on a statement.

Micro-operation faults usually are not a problem, but a faulty micro-operation must not be used to preload or propagate its own test. When an expression is copied from the description (i.e. to make a VIE goal), the faulty operation is marked. So marked, it cannot be used, so it is never reused where it should not be.

# Two-Phase Tests

One part of the fault model that causes problems is the ASSNCNTL fault. The standard test is to preload one value v1 into the destination object, try to load a new value v2 ( $\neq$  v1) by executing the assignment statement with the source expression set to v2, and observe the resulting value in the object. If the assignment is the only assignment to the object, there is no other assignment with which to load the first value into the object. If the faulty statement is used to preload the first value, one cannot be sure the object is loaded, since the statement may fail. For example, if an object x has a value of 1 (random initialization), and one tries to load a 0 and then load a 1, the original 1 will be in x, and one will think the statement works.

The solution is to do a "two-phase" test. In a two-phase test, value v1 is loaded and the object is observed for v1; then v2 is loaded, and the object is observed. (Actually, because of a limitation, this becomes a three-phase test: load v1, check v1; load v1 again, load v2, and check v2. Value v1 is loaded again because observing v1 may destroy the v1 in the object, for example, observing a bit in a serial-output shift register.)

Two-phase tests are implemented in OBSEXEC solving. Normally, OBSEXEC goal uses a VIE goal to specify to preload one value, another VIE goal to set the source expression, an EXEC

goal to execute the statement, and an OBSOBJ goal to observe the value. If the ASSNCNTL statement is the only assignment to the object, the OBSEXEC solving issues an extra VIE goal to load the value and an extra OBSOBJ goal to verify that value. These two goals are issued for a new, totally independent base time. (I.e., the new base time will never be constrained with a TR goal, and will never be substituted in terms of t0. This will effectively yield two tests which can be done in any order.)

Control faults can require two-phase tests, when all statements that load an object are under a faulty control statement. If all assignments to an object are under a faulty IF statement, or in a dead WHEN clause, OBSEXEC also initiates a two-phase test.

# Enhancements

Several enhancements added to basic solving strategy speed up execution.

### Simple Controllability and Observability

Crude controllability and observability estimates are used to select justification and propagation paths. These estimates are simple input and output distance measures. Input distance of an object is the "distance" from an input, measured as the number of assignments needed to get to the object. Input pins have distance zero, objects loaded from inputs have distance 1, objects loaded from distance-1 objects have distance 2, etc. Similar measures are used for output distance. However, this definition does not specify how to count objects in control expressions. They obviously affect how easily objects can be loaded, but are harder to count since they are indirectly related. Unspecified distances are counted as infinity for now.

When selecting an assignment statement to use to load an object to solve a VIO goal, the assignment with the most controllable source expression is chosen first. When selecting a use of an object (in some expression) when solving an OBSOBJ goal, the one loading the object with the best observability is selected first. When picking an object to use to detect execution when solving an OBSEXEC goal, the most observable object is picked first.

### Conflict Checks

Additional conflict checks are done to catch conflicts more quickly. The basic check is for two VIO goals for the same object at the same time requiring different values. This is sufficient for correctness, but is inefficient. One additional check is for an EXEC goal and a DNE goal at the same time for the same statement. (This would eventually be caught when selecting corresponding object values to set control expressions, but this saves the work and time spent selecting those values.) Other new checks are for unsolvable goals, such as VIE goals with impossible combinations of expressions and values, or DNE goals for top-level statements.

Conflict checks are significant because of when they are done. Subgoals returned from solving a goal are checked immediately, to catch conflicts or impossible goals then, instead of considerably later when the subgoals are examined for solving. Compatibility is also checked immediately after time substitution, since many conflicts appear then.

### **Object Value Substitution**

Related to conflict checks is the substitution of known object values in expressions. Substitution is done to simplify VIE expressions, when the value of any object in the expression is known, to determine that the VIE goal is unsolvable or inherently solved. Also, since OBSOBJ and OBSEXPR good vs. faulty values are represented as expressions of argument values, these expressions are substituted to resolve them to literal values by the time all goals are solved. Known object values are substituted in goals when the goals are returned as subgoals, and again when each goal is solved (to substitute any values decided in between). This substitution corresponds to (partial) forward implication.

# Solved and Decided Goal Lists