# SOFT-SWITCHING TECHNIQUES FOR HIGH-POWER PWM CONVERTERS

by

Hengchun Mao

Dissertation submitted to the Faculty of the

Virginia Polytechnic Institute and State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in

**Electrical Engineering**

APPROVED:

Fred C. Lee, Chairman

Dusan Boyojevic

Douglas J. Nelson

Dan Y. Chen

Alex Q. Huang

December 6, 1996

Blacksburg, Virginia

Key Words: PWM converters, Soft-switching, Zero-voltage switching, zero-current switching

LD 5655 1856 1996 M368 c.2

# SOFT-SWITCHING TECHNIQUES FOR HIGH-POWER PWM CONVERTERS

by

Hengchun Mao

Fred C. Lee, Chairman

Electrical Engineering

(ABSTRACT)

Soft-switching techniques can significantly reduce the switching loss and switching stresses of the power semiconductor devices in a power converter. This work presents several soft-switching topologies for high power PWM converters. These new topologies achieve soft-switching functions with minimum increase of device voltage/current stresses and converter circulating energy, and thus have advantages over conventional techniques in efficiency, power density, reliability, and cost of power converters.

The improved zero-current transition (ZCT) converters achieve zero-current switching at both turn-on and turn-off for all main switches and auxiliary switches. These converters significantly reduce the switching loss and stress of the power semiconductor devices, while have a voltage/current stress and circulating energy similar to a PWM converter's. The analysis, design, and experimental verification are presented.

The three-phase zero-voltage transition (ZVT) boost rectifiers/voltage source inverters are developed with simple auxiliary circuits. Unlike most existing three-phase soft-switching techniques, these new topologies achieve soft-switching functions without overcharging the resonant inductors, and realize the benefits of soft-switching operation with minimum extra main switch turn-offs and fixed auxiliary circuit control timing. The operation principles of the developed techniques are experimentally verified, and their efficiency performances are evaluated with experiments and computer simulation.

The three-phase ZVT buck rectifier topologies developed in this work achieves zero-voltage turn-on for all main switches with an optimum modulation schemes and simple auxiliary circuits. The auxiliary circuits, which are connected directly to each main switch, can also absorb the parasitic resonance of the bridge arms, and keep the voltage stress of the power devices at the minimum. The analysis and simulation results are presented to verify the converter operation.

New ZVT dc-link schemes for three-phase ac-dc-ac converters are investigated. With coordinated control of the ac-dc converter and the dc-ac converter, a set of simple auxiliary circuit can provide soft-switching function for all switches in both the ac-dc converter and the dc-ac converter. The power loss in the auxiliary circuit is also significantly lower than existing dc-link soft-switching schemes. Simulation with experimentally obtained device switching loss data proves that significant efficiency improvement can be achieved with the new ZVT dc-link techniques.

New ZVT and ZCT techniques for three-level converters are also developed. The auxiliary circuits are not in the main power path, and allow the converters to be controlled with optimum PWM schemes. Analysis and simulation results are presented to demonstrate the operation principles and advantages of soft switching in three-level converters.

To my wife and son

#### Acknowledgments

I would like to express my sincere gratitude to my advisor, Dr. Fred C. Lee, for his guidance, encouragement, and support throughout the course of this work. His extensive knowledge and creative thinking have been an invaluable help.

I gratefully thank Dr. Dusan Borojevic for many enlightening discussions and suggestions. I thank Dr. Dan Y. Chen, Dr. Alex Q. Huang, and Dr. D. J. Nelson for their valuable contributions as members of my advisory committee.

I am indebted to all my fellow students at Virginia Power Electronics Center. Their friendship has made my stay in the Ph. D. program enjoyable. Especially, I thank Dr. Vlatko Vlatkovic, Dr. Yiming Jiang, Dr. Guichao Hua, Mr. Carlos Cuadros, and Mr. Richard Zhang for fruitful discussions, and Mr. Xunwei Zhou, Mr. Heping Dai, Ms. Qiong Li, Mr. Jingdong Zhang, Mr. Dong Ho Lee, Mr. Mohummet Cosan, and Mr. Ravindra Ambatiputi for their help with the experiments and simulations.

I am grateful to VPEC staff, Ms. Teresa Shaw, Ms. Evelyn Martin, Ms. Linda Rush, Mr. Jeffrey Batson, Mr. Jiyuan Luan, Ms Tammy Hiner, and Mr. Bill Cockey for their assistance and cooperation.

I thank my father, Jizhong Mao, and my mother, Lianyu Tang, who brought me up and encouraged my pursuit of higher knowledge.

Acknowledgments v

Finally, I would like to thank my wife, Xuezhong Jia, for her love, encouragement and support.

This work was supported by Kollmorgen - Artus, France, and Westinghouse Science and Technology Center, Pittsburg.

Acknowledgments

## TABLE OF CONTENTS

| 1. | INTRODUCTION                                                                                           | 1  |

|----|--------------------------------------------------------------------------------------------------------|----|

|    | 1.1 Background                                                                                         | 1  |

|    | 1.1.1 Soft-Switching Techniques in DC-DC Converters                                                    | 2  |

|    | 1.1.2 Soft-Switching Techniques in Three-Phase Converters                                              | 3  |

|    | 1.1.3 Soft-Switching Techniques in Multi-Level Converters                                              | 9  |

|    | 1.1.4 Control and Small-Signal Modeling of Three-Phase Converters                                      | 10 |

|    | 1.2 Present Work                                                                                       | 12 |

|    | 1.3 Dissertation Outline                                                                               | 14 |

| 2. | IMPROVED ZERO-CURRENT TRANSITION CONVERTERS FOR HIGH-POWER APPLICATIONS                                | 16 |

|    | 2.1 Introduction                                                                                       | 16 |

|    | 2.2 Improved Zero-Current Transition Boost Converter                                                   | 19 |

|    | 2.3 State-Plane Analysis of ZCT Operation                                                              | 25 |

|    | 2.4 Extension of Improved ZCT Schemes to Other Converters                                              | 30 |

|    | 2.5 Design of Auxiliary Circuit and Test Results                                                       | 36 |

|    | 2.6 Conclusions                                                                                        | 47 |

| 3. | THREE-PHASE ZERO-VOLTAGE TRANSITION BOOST RECTIFIER VOLTAGE SOURCE INVERTERS                           |    |

|    | 3.1 Introduction                                                                                       | 48 |

|    | 3.2 Space Vector Modulation Schemes and Generalized PWM Cells in Th<br>Phase Voltage Source Converters |    |

|    | 3.3 Novel Three-Phase ZVT Boost Rectifier/Voltage Source Inverter                                      | 63 |

|    | 3.3.1 Topology Development                                                                             | 63 |

|    |                                                                                                        |    |

|              | 3.3.2 Operation of Bi-Directional ZVT Three-Phase Boost Rectifier/\ Source Inverter                   | •                                        |

|--------------|-------------------------------------------------------------------------------------------------------|------------------------------------------|

|              | 3.3.3 Auxiliary Circuit Design and Experimental Results                                               | 82                                       |

|              | 3.3.4 Topology Evaluation                                                                             | 84                                       |

|              | 3.3.5 Conclusions                                                                                     | 93                                       |

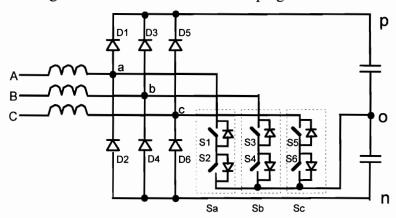

|              | 3.4 Soft-Switched Three-Phase Boost Rectifiers/Voltage Source Inve<br>Reduced Auxiliary Switch Stress |                                          |

|              | 3.4.1 Topology Development                                                                            | 95                                       |

|              | 3.4.2 Soft-Switching Operation                                                                        | 100                                      |

|              | 3.4.3 Converter Design Issues                                                                         | 106                                      |

|              | 3.4.4 Experimental and Simulation Results                                                             | 109                                      |

|              | 3.4.5 Improvement on Soft-Switching Topology                                                          | 115                                      |

|              | 3.4.6 Modified Topology for Rectifier Applications                                                    | 117                                      |

|              | 3.4.7 Conclusions                                                                                     | 119                                      |

| 4.           | THREE-PHASE ZERO-VOLTAGE TRANSITION BUCK AND BU                                                       |                                          |

| 4.           | BOOST RECTIFIERS                                                                                      | 120                                      |

| 4.           | BOOST RECTIFIERS                                                                                      | 120                                      |

| 4.           | BOOST RECTIFIERS                                                                                      | 120<br>120<br>124                        |

| 4.           | 4.1 Introduction                                                                                      | 120<br>120<br>124<br>fiers128            |

| 4.           | 4.1 Introduction                                                                                      | 120120124 fiers128132                    |

| 4.           | 4.1 Introduction                                                                                      | 120120124 fiers128132                    |

| 4.           | 4.1 Introduction                                                                                      | 120120124 fiers128132                    |

|              | 4.1 Introduction                                                                                      | 120120124 fiers128132141143              |

|              | 4.1 Introduction                                                                                      | 120120124 fiers128132141143 FHREE144     |

|              | 4.1 Introduction                                                                                      | 120120124 fiers128132141143 FHREE144     |

| <b>4. 5.</b> | 4.1 Introduction                                                                                      | 120120124 fiers128132141143  FHREE144144 |

|    | 5.4 ZVT DC-Link Schemes for Systems with a Boost Rectifier                           | 159 |

|----|--------------------------------------------------------------------------------------|-----|

|    | 5.4.1 Introduction                                                                   | 159 |

|    | 5.4.2 A New ZVT DC-Link Schemes                                                      | 161 |

|    | 5.5 Conclusions                                                                      | 171 |

|    |                                                                                      |     |

| 6. | SOFT-SWITCHING THREE-LEVEL PWM CONVERTERS FOR HIGH<br>POWER APPLICATIONS             |     |

|    | 6.1 Introduction                                                                     | 172 |

|    | 6.2 Multi-Level Two-Quadrant Boost Chopper                                           | 174 |

|    | 6.2.1 Introduction                                                                   | 174 |

|    | 6.2.2 Multi-Level Two-Quadrant Boost Choppers                                        | 179 |

|    | 6.2.3 Operation of Three-Level Two-Quadrant Boost Chopper                            | 182 |

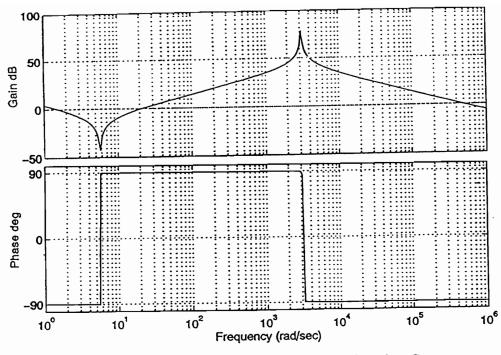

|    | 6.2.4 Small-Signal Modeling and Chopper Control                                      | 189 |

|    | 6.2.5 Simulation Results                                                             | 196 |

|    | 6.2.6 Soft-Switching Techniques for Two-Quadrant Boost Choppers                      | 199 |

|    | 6.3 Soft-Switching Techniques of Three-Level Three-Phase PWM Voltag Source Inverters |     |

|    | 6.3.1 Introduction                                                                   | 204 |

|    | 6.3.2 Space Vector Modulation and PWM Cells in Three-Level Three-Phase PWM Inverters |     |

|    | 6.3.3 Soft-Switching Topologies for Three-Level Inverters                            |     |

|    | 6.4 Three-Phase Three-Level Zero-Voltage-Transition Boost Rectifiers                 | 209 |

|    | 6.4.1 Introduction                                                                   | 209 |

|    | 6.4.2 Topology Description                                                           | 212 |

|    | 6.4.3 Topology Evaluation                                                            | 219 |

|    | 6.5 Conclusions                                                                      | 224 |

|    |                                                                                      |     |

| 7. | CONCLUSIONS AND FUTURE WORK                                                          | 225 |

|    | 7.1 Conclusions                                                                      | 225 |

|    |                                                                                      |     |

| 7.2 Suggestions for Future Work |                                                      | 228 |  |

|---------------------------------|------------------------------------------------------|-----|--|

|                                 |                                                      |     |  |

| REFERENCES                      |                                                      | 229 |  |

| APPENDIX. A                     | POWER LOSS MODELS OF IGBT DEVICES USED IN SIMULATION |     |  |

| VITA                            |                                                      | 250 |  |

Table of Contents

### LIST OF ILLUSTRATIONS

| Figure 2.1  | Existing ZCT PWM Boost Converter                                                        | 18 |

|-------------|-----------------------------------------------------------------------------------------|----|

| Figure 2.2  | An Improved ZCT PWM Converter                                                           | 21 |

| Figure 2.3  | Operating Stages in the Soft-Switching Commutation                                      | 22 |

| Figure 2.4  | High-Frequency Equivalent Circuits of ZCT Boost Converter                               | 26 |

| Figure 2.5  | Comparison of State-Plane Trajectories                                                  | 28 |

| Figure 2.6  | PWM Cell and ZCT Cells                                                                  | 31 |

| Figure 2.7  | Examples of Several ZCT Converters                                                      | 32 |

| Figure 2.8  | ZCT Topologies Bridge-Type Circuits                                                     | 34 |

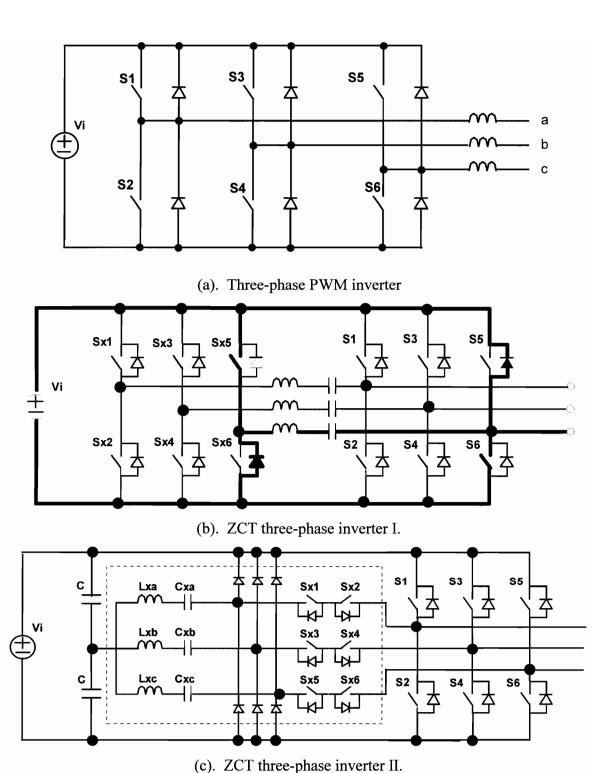

| Figure 2.9  | ZCT Three-Phase Inverters                                                               | 35 |

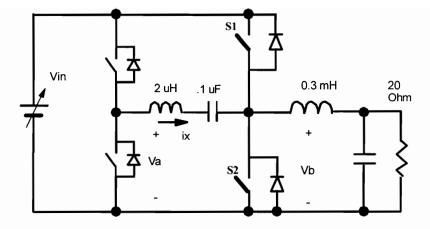

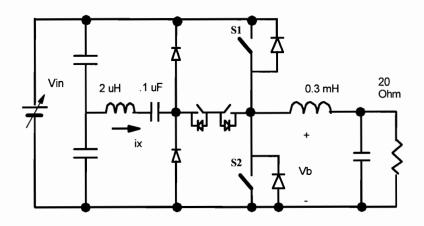

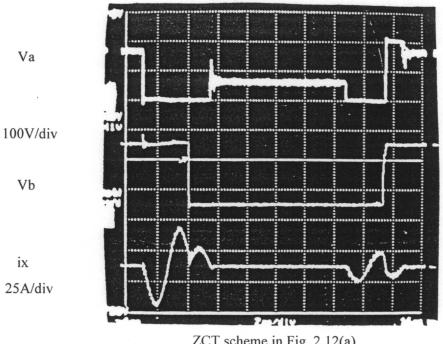

| Figure 2.10 | ZCT Test Circuit with a High Power IGBT Module                                          | 39 |

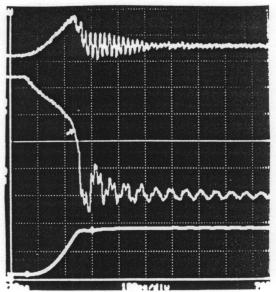

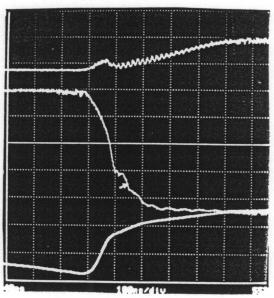

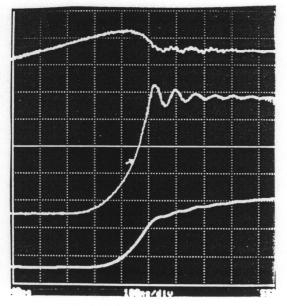

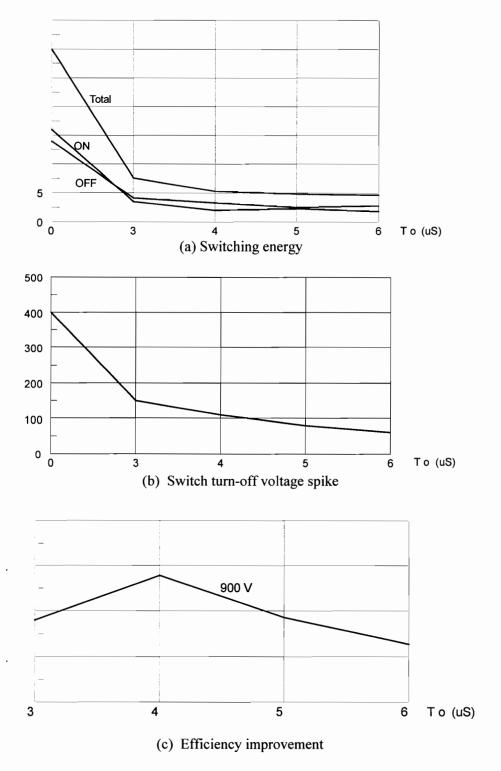

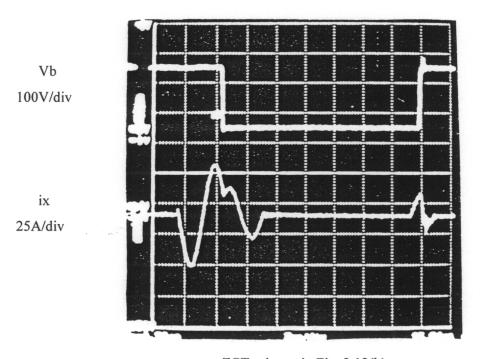

| Figure 2.11 | Typical Switching Waveforms under Soft Switching and Hard Switchin                      |    |

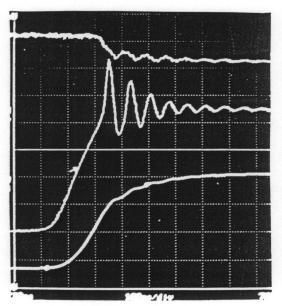

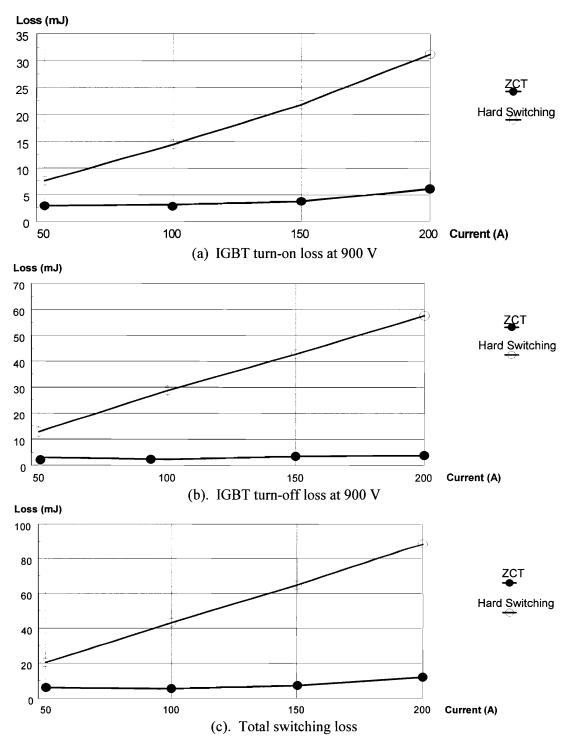

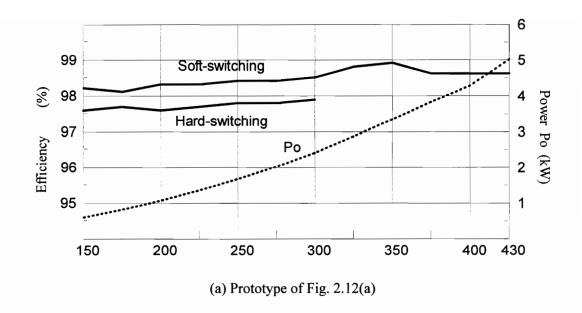

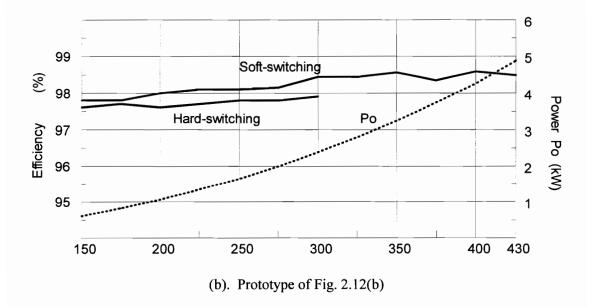

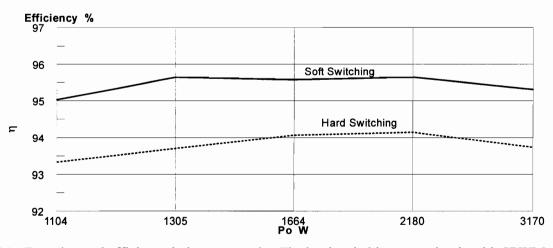

| Figure 2.12 | Switching losses and Efficiency Improvement at 900 V, 100 A                             | 41 |

| Figure 2.13 | Switching Losses at 900 V with Different Currents                                       | 42 |

| Figure 2.14 | Experimental ZCT Circuits with MCTs                                                     | 44 |

| Figure 2.15 | MCT Converter Experimental Waveforms                                                    | 45 |

| Figure 2.16 | Measured Efficiency of MCT Converters                                                   | 46 |

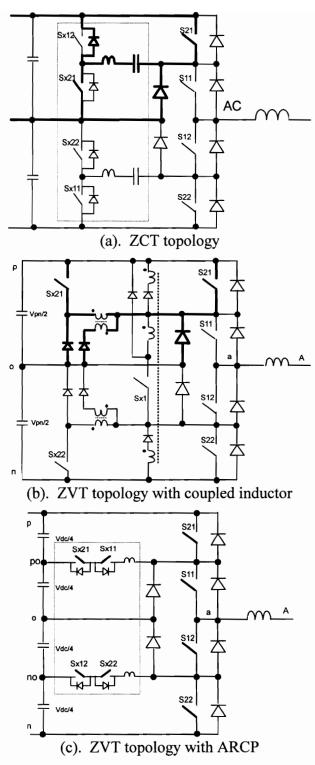

| Figure 3.1  | Existing Soft-Switched Three-Phase Voltage Source Inverters/Boost Rectifiers            | 51 |

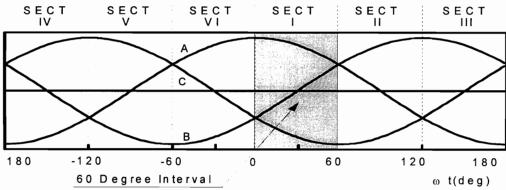

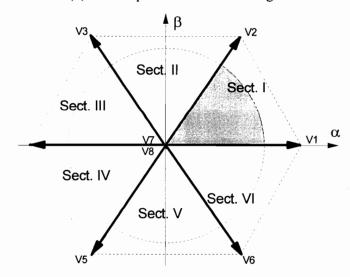

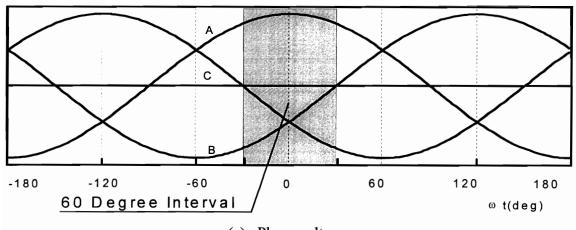

| Figure 3.2  | Three-Phase Voltages and Voltage Space Vectors in a Three-Phase Voltage Source Inverter | 57 |

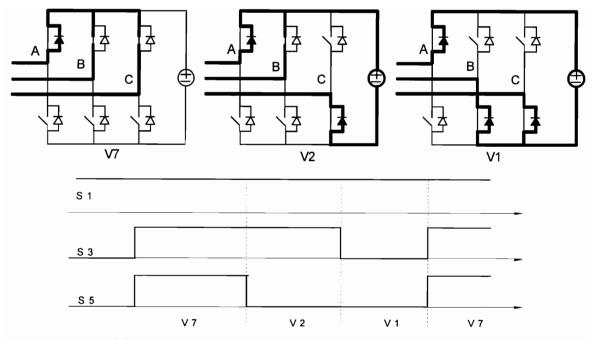

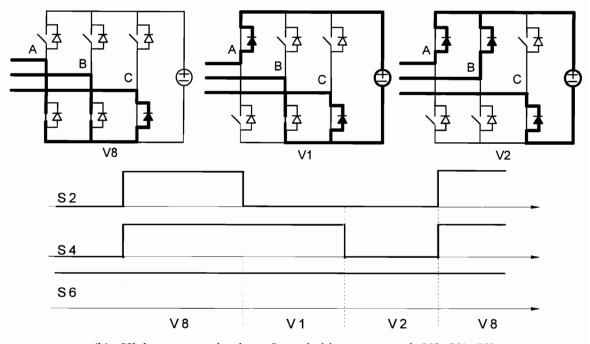

| Figure 3.3  | SVM Scheme in Rectifier Mode ( in Sector I)                                             | 59 |

| Figure 3.4  | SVM Scheme in Inverter Mode ( in Sector I)                                              | 60 |

| Figure 3.5  | Generalized PWM Cells in a Three-Phase VSC                                              | 62 |

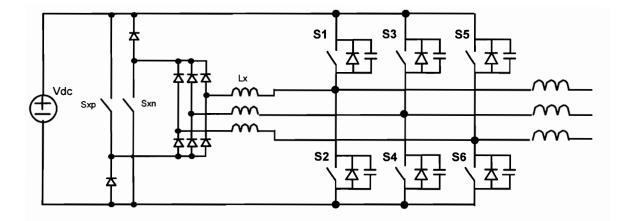

| Figure 3.6  | An Intuitive ZVT Three-Phase Voltage Source Inverter                                    | 64 |

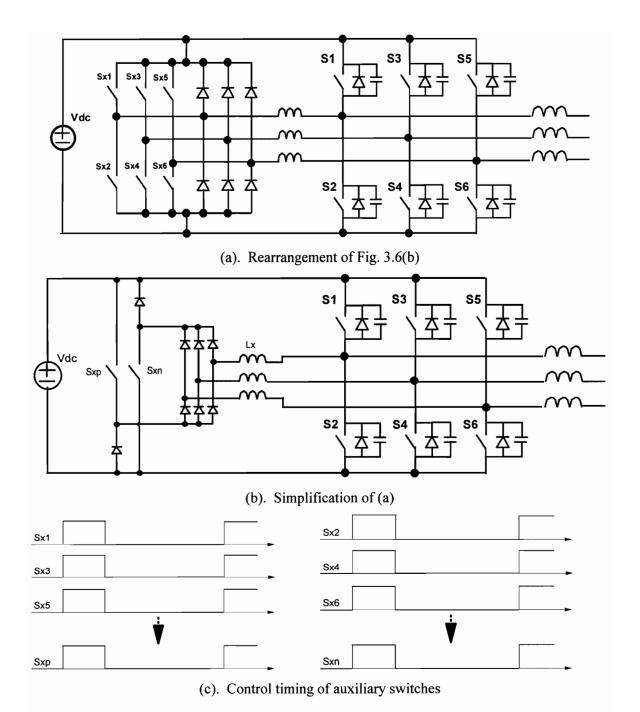

| Figure 3.7  | Simplification of Three-Phase ZVT Topology                                              | 67 |

|             |                                                                                         |    |

| Figure 3.8  | Turn-On Commutation for Fig. 3.7(b)                                                                                                 | 69  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 3.9  | Another Simple ZVT Topology for Three-Phase Boost Rectifiers                                                                        | 71  |

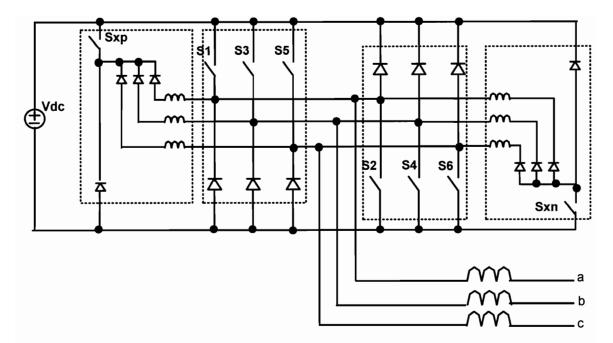

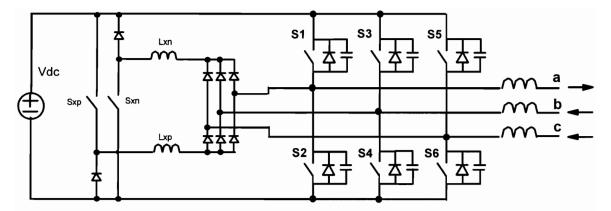

| Figure 3.10 | A Practical Soft-Switching Three-Phase Boost Rectifier/Voltage Source Inverter                                                      | 72  |

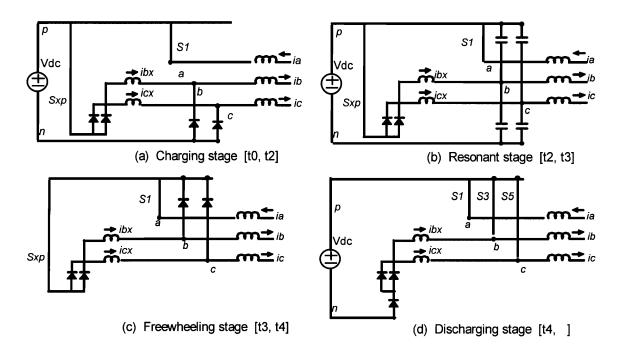

| Figure 3.11 | A ZVT Commutation in Rectifier Mode                                                                                                 | 74  |

| Figure 3.12 | Waveforms of ZVT Commutation in Rectifier Mode                                                                                      | 76  |

| Figure 3.13 | A Turn-On Commutation in Inverter Mode                                                                                              | .78 |

| Figure 3.14 | Key Waveforms of Turn-On Commutation in Inverter Mode                                                                               | 79  |

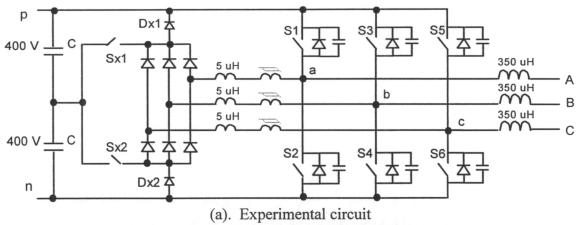

| Figure 3.15 | Experimental Circuit Implementation.                                                                                                | .85 |

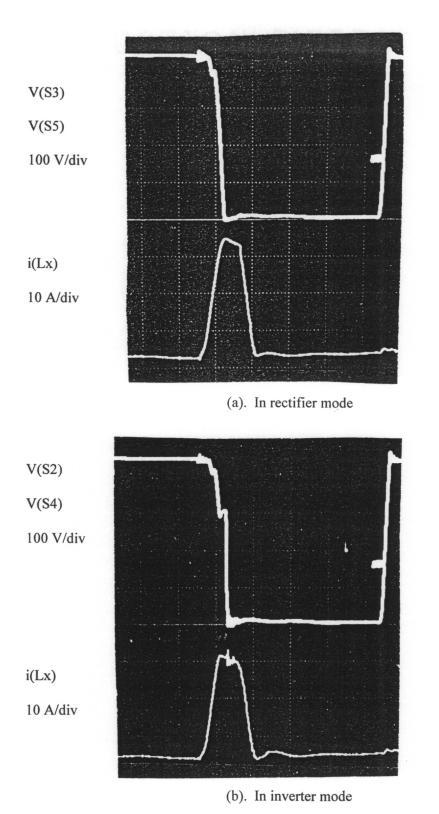

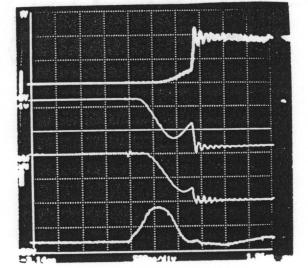

| Figure 3.16 | Experimental Waveforms of Turn-On Commutation                                                                                       | 86  |

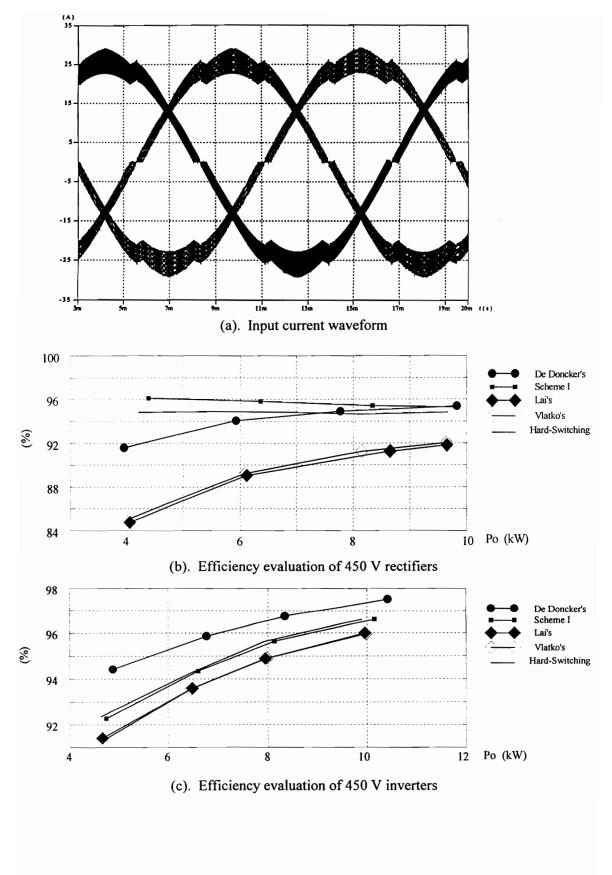

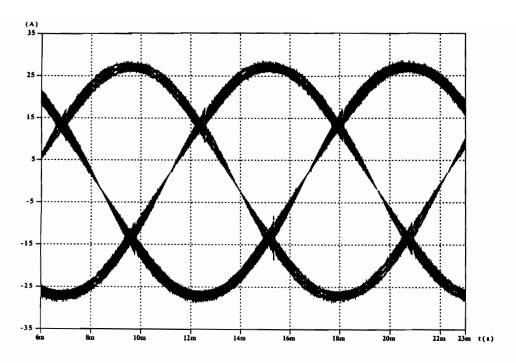

| Figure 3.17 | Simulation Results                                                                                                                  | 91  |

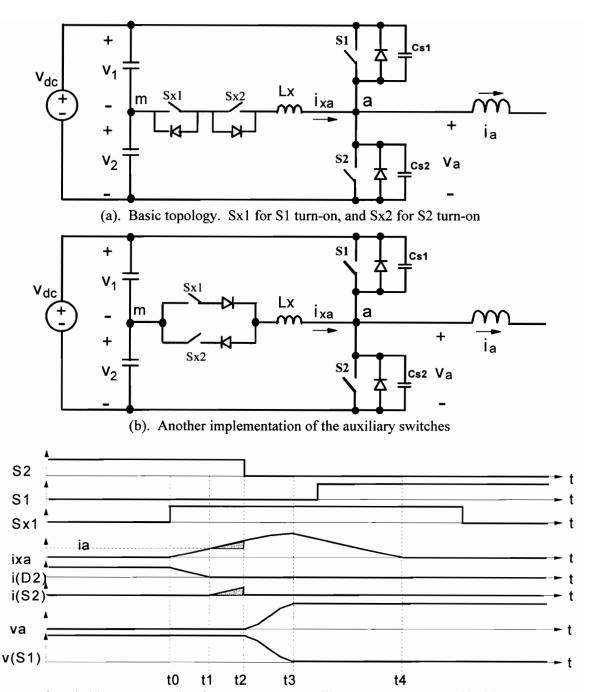

| Figure 3.18 | A Modified ZVT Cell for Bridge-Type Circuit                                                                                         | 96  |

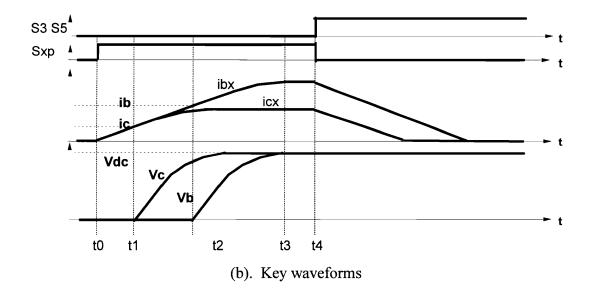

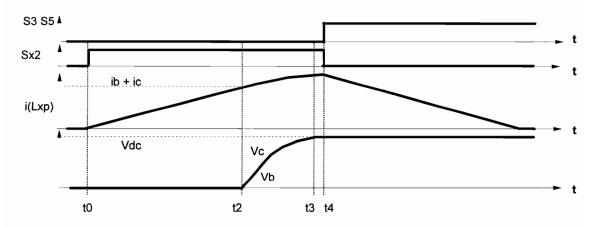

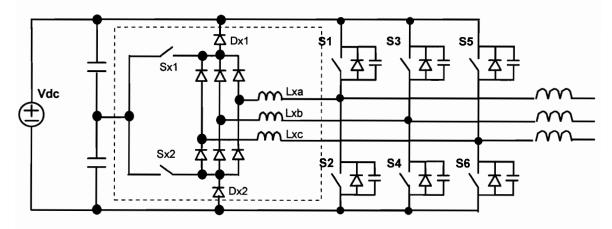

| Figure 3.19 | Topology Development of Soft-Switching Three-Phase Boost Rectifier/<br>Voltage Source Inverter with Reduced Auxiliary Switch Stress |     |

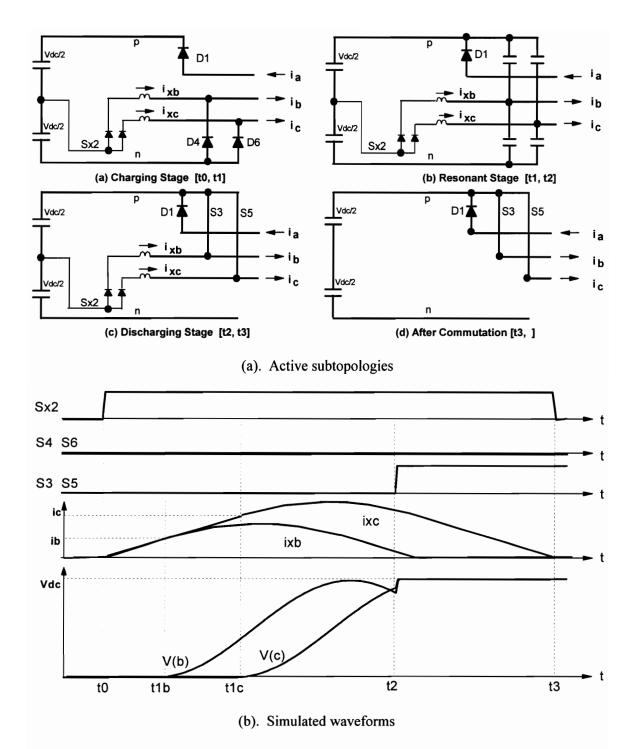

| Figure 3.20 | Soft-Switching Commutation in Inverter Mode                                                                                         | 102 |

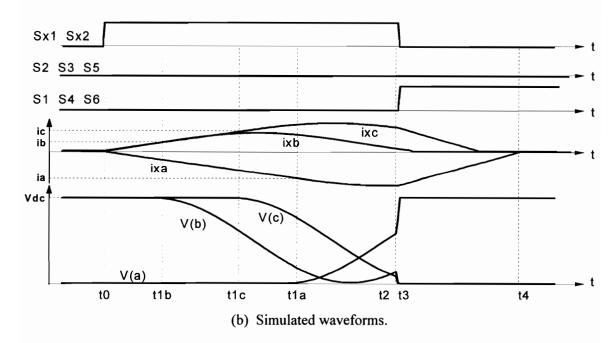

| Figure 3.21 | Soft-Switching Commutation in Rectifier Mode                                                                                        | 105 |

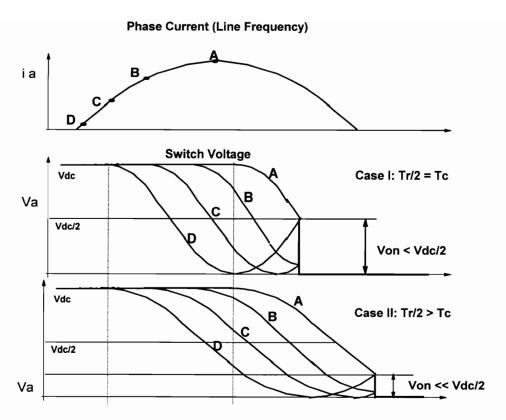

| Figure 3.22 | Switch Turn-On Voltage and Energy Loss as a Function of Snubber Capacitance                                                         | 108 |

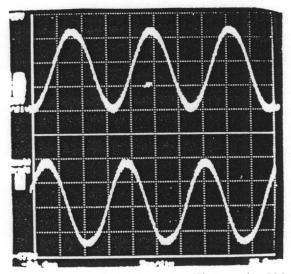

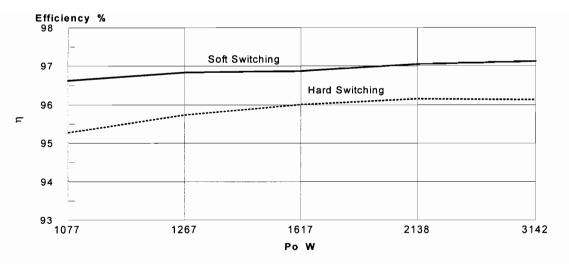

| Figure 3.23 | A Prototype Converter and Experimental Results                                                                                      | 111 |

| Figure 3.24 | Efficiency Evaluation With Simulation                                                                                               | 114 |

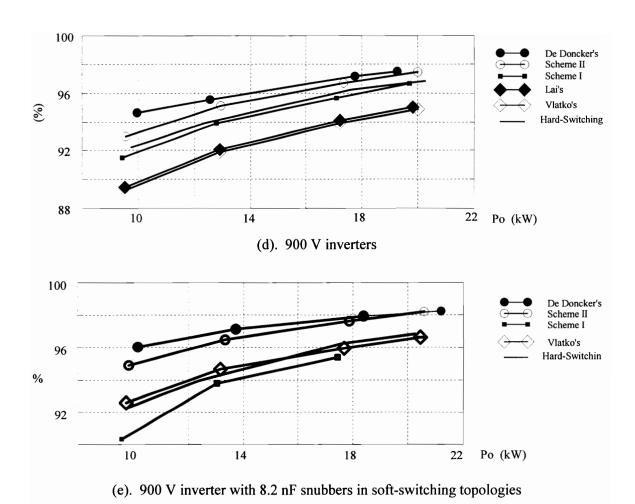

| Figure 3.25 | A ZVT Topology with Coupled Saturable Inductors                                                                                     | 116 |

| Figure 3.26 | A Simple Three-Phase Boost Rectifier with Modified Auxiliary Circuit                                                                | 118 |

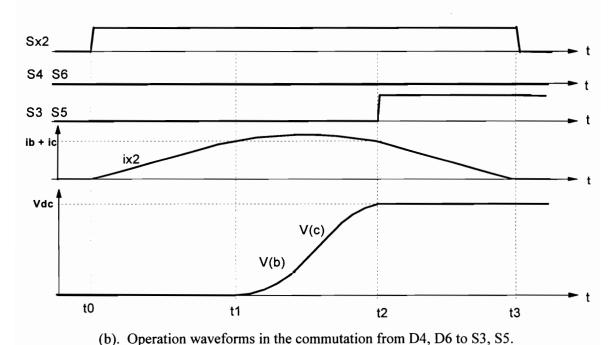

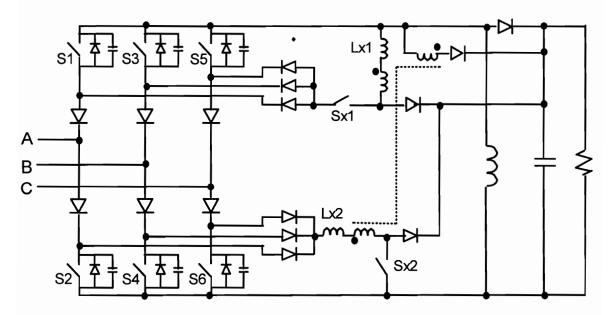

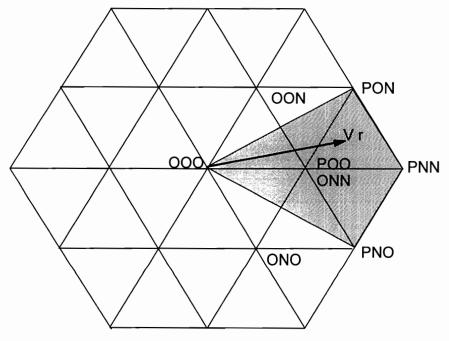

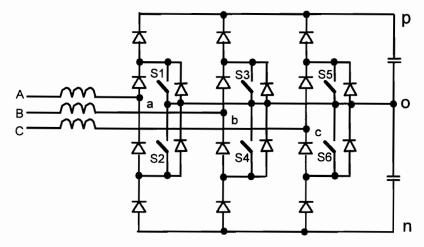

| Figure 4.1  | Three-Phase Current Source Rectifiers                                                                                               | 121 |

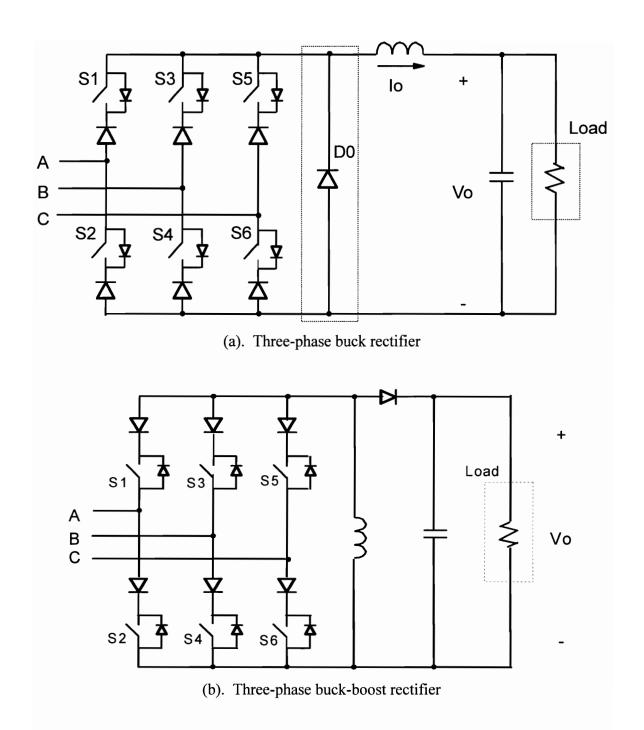

| Figure 4.2  | Current Space Vectors in a Three-Phase Buck Rectifier                                                                               | 125 |

| Figure 4.3  | SVM Scheme and Generalized PWM Cells                                                                                                | 127 |

| Figure 4.4  | Existing Soft-Switching Techniques for Three-Phase Buck Rectifiers                                                                  | 130 |

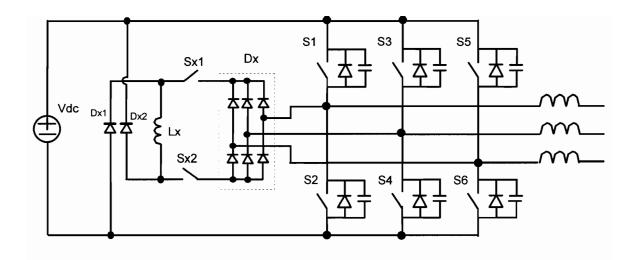

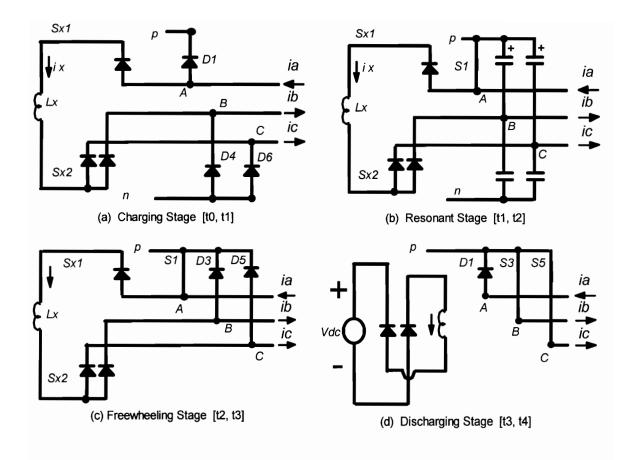

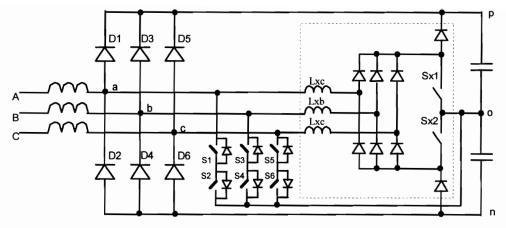

| Figure 4.5  | A New ZVT Topology of Three-Phase Buck Rectifier                                                                                    | 133 |

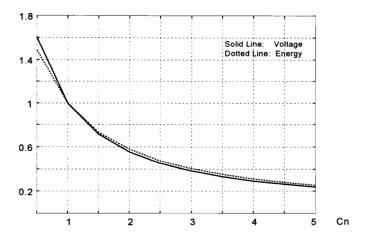

| Figure 4.6  | Operating Stages During the ZVT Commutation                                                                                         | 135 |

| Figure 4.7  | Key Waveforms of the ZVT Commutation in Buck Rectifier                                                                              | 137 |

|             |                                                                                                                                     |     |

Table of Contents xii

| Figure 4.8  | Simulation Results of ZVT Buck Rectifier                             | .139  |

|-------------|----------------------------------------------------------------------|-------|

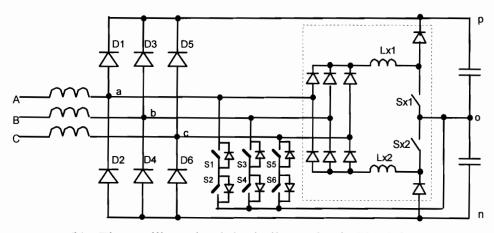

| Figure 4.9  | Modified Three-Phase ZVT Buck Rectifier                              | 140   |

| Figure 4.10 | Three-Phase ZVT Buck-Boost Rectifiers                                | 142   |

| Figure 5.1  | Soft-Switching DC-Link AC-DC-AC Converter with a Diode Rectifier     | . 147 |

| Figure 5.2  | Operating Stages in Soft-Switching Turn-Off Transition               | .149  |

| Figure 5.3  | Key Waveforms in the Soft-switching Commutations                     | . 150 |

| Figure 5.4  | A Modified Soft-Switching DC-Link Topology with a Diode Rectifier    | . 152 |

| Figure 5.5  | Output Voltages and Currents                                         | .156  |

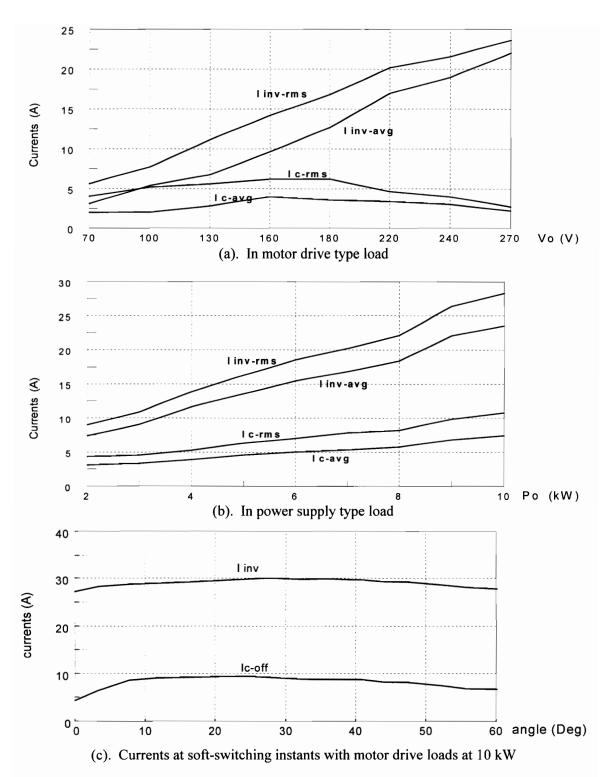

| Figure 5.6  | S0 Currents vs Inverter Currents                                     | .157  |

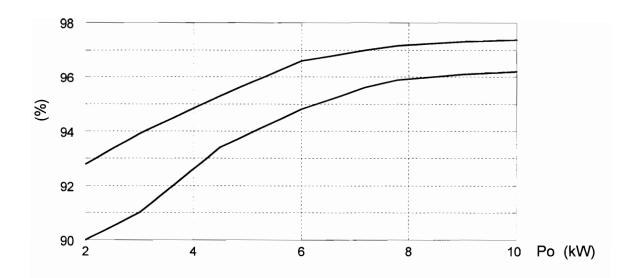

| Figure 5.7  | Efficiency Evaluation with Motor-Type Load                           | . 158 |

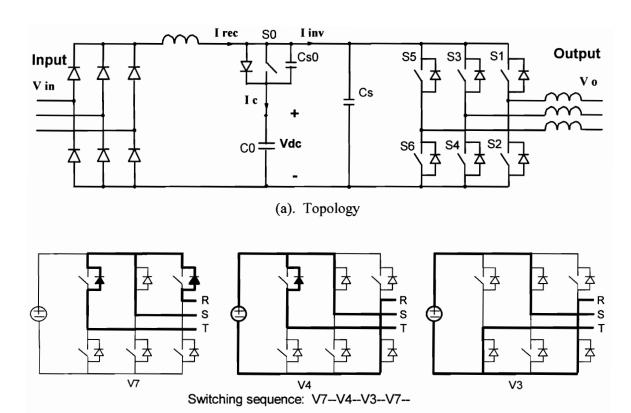

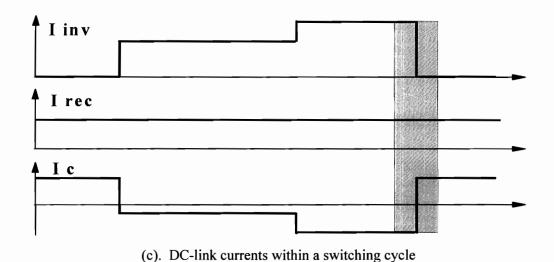

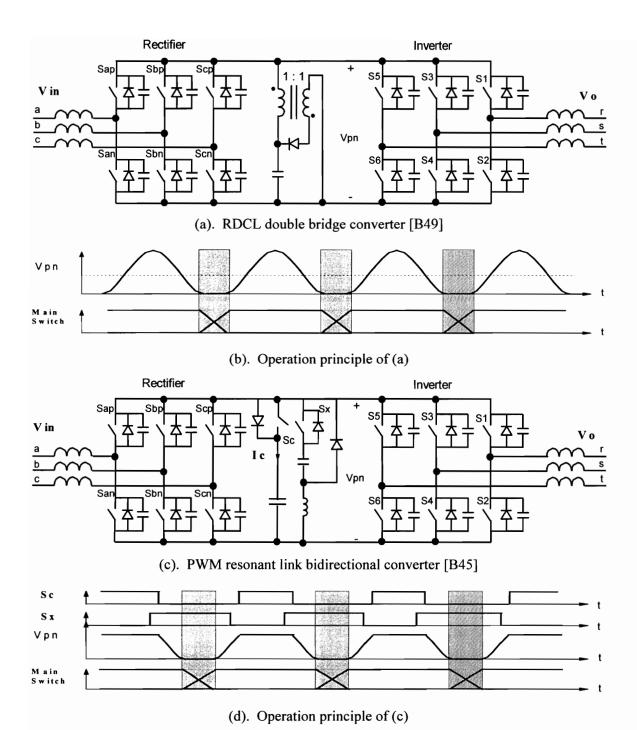

| Figure 5.8  | Existing Three-Phase AC-DC-AC Soft-Switching Power Converters        | . 160 |

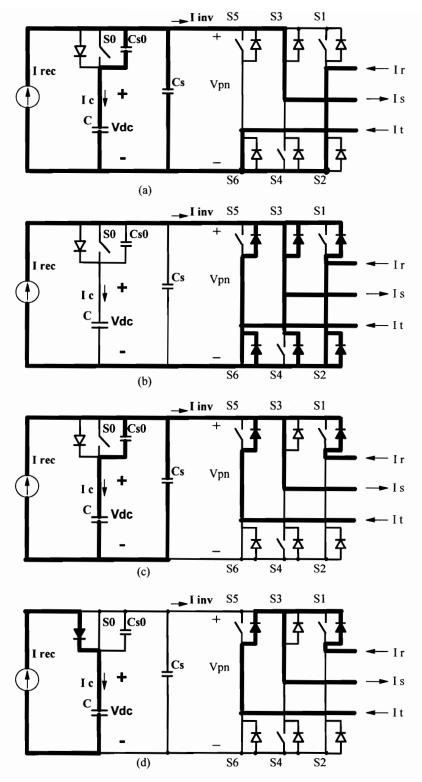

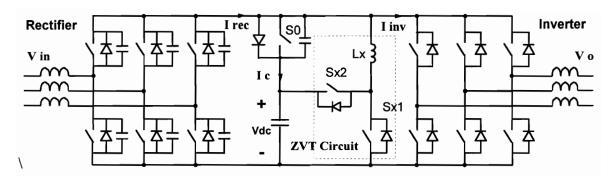

| Figure 5.9  | A New Zero-Voltage Transition DC-Link Three-Phase AC-DC-AC Converter | 162   |

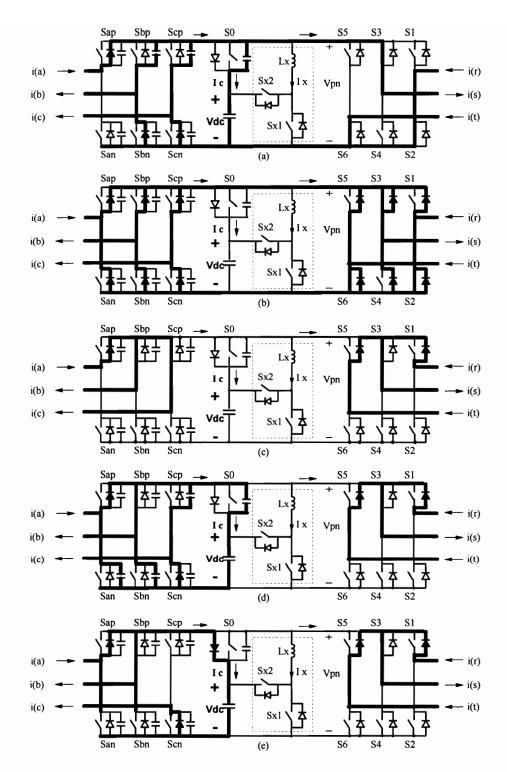

| Figure 5.10 | Operating Stages in the ZVT Commutation                              | 166   |

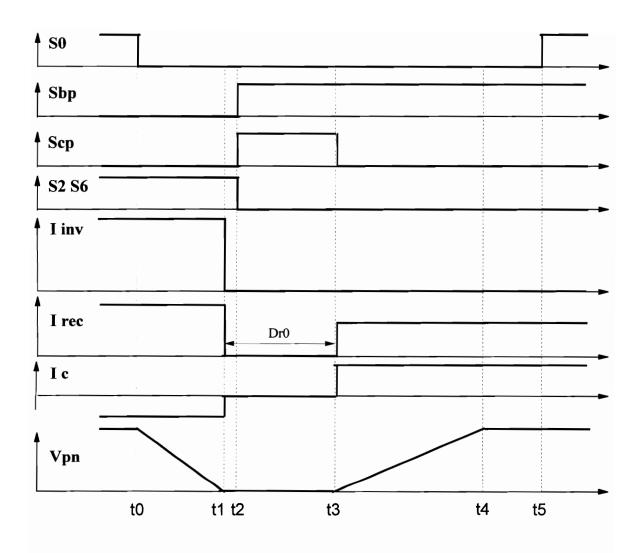

| Figure 5.11 | Key Waveforms of the ZVT Commutation                                 | 167   |

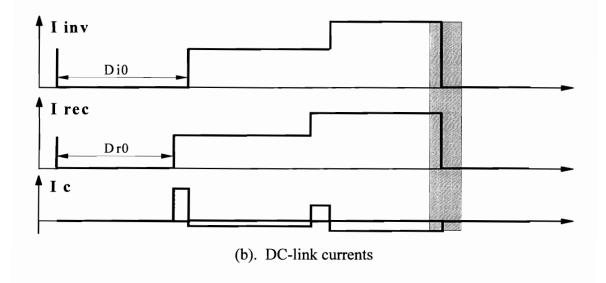

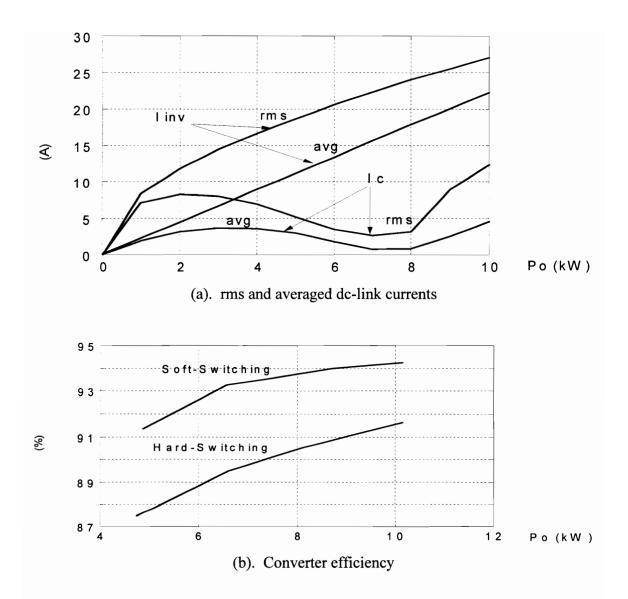

| Figure 5.12 | Simulated DC-Link Currents and Converter Efficiency                  | .170  |

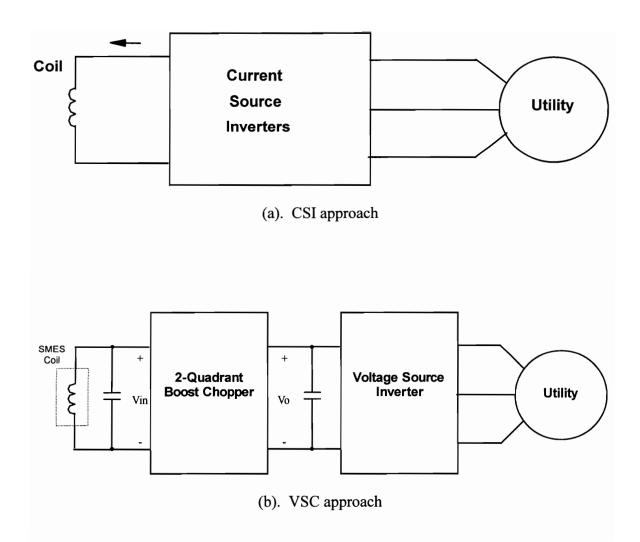

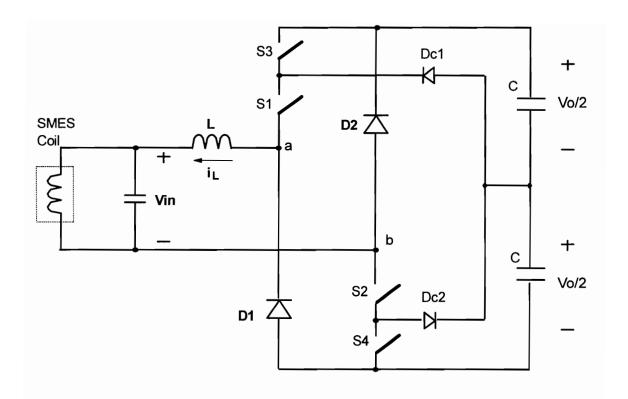

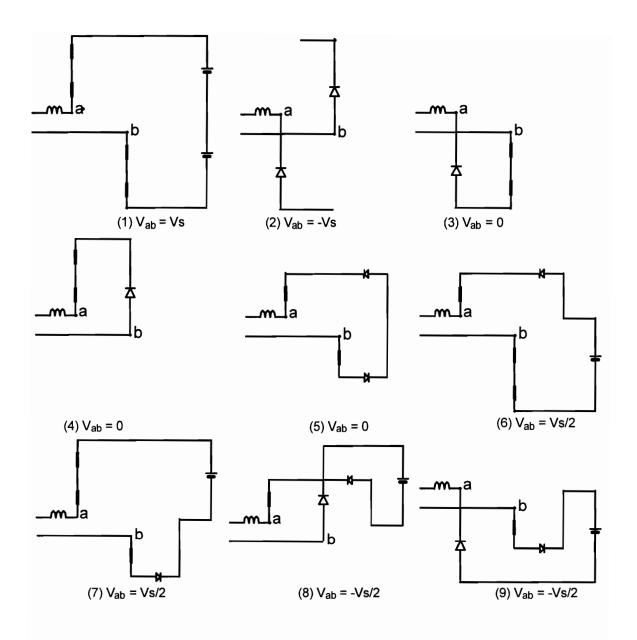

| Figure 6.1  | Power Conditioning Systems for SMES                                  | .175  |

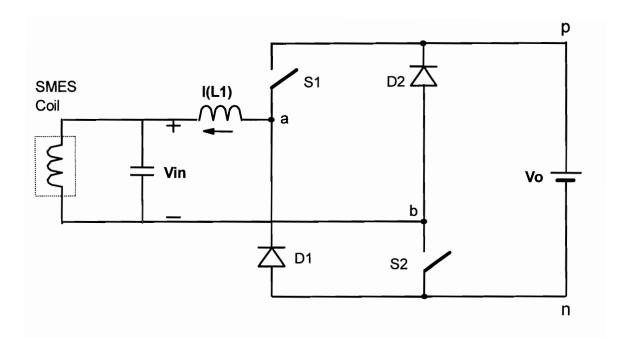

| Figure 6.2  | Schematic of Two-Quadrant Boost Chopper                              | . 177 |

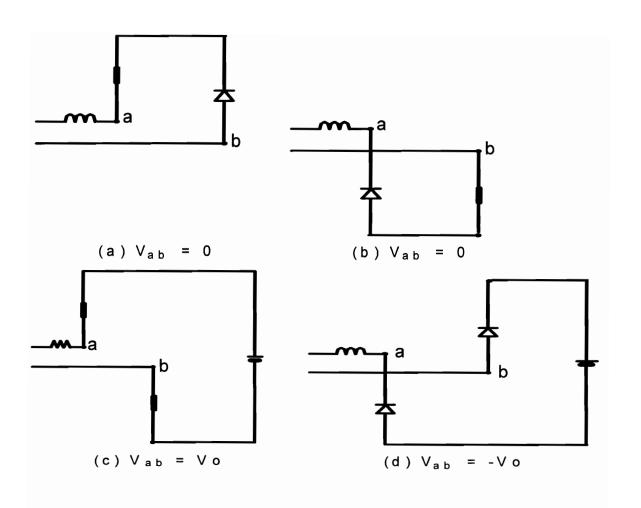

| Figure 6.3  | Subtopologies of Two-Quadrant Boost Chopper                          | .178  |

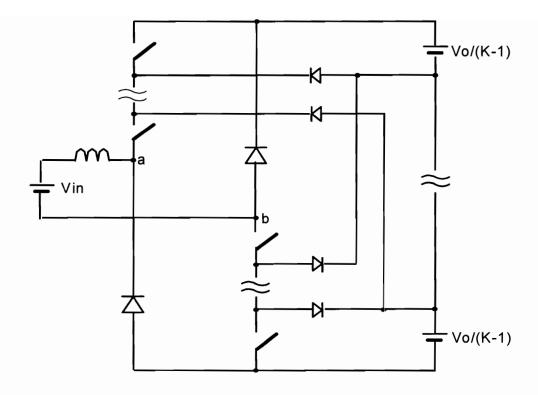

| Figure 6.4  | Multi-Level Two-Quadrant Boost Chopper                               | .180  |

| Figure 6.5  | Three-Level Two-Quadrant Boost Chopper                               | 181   |

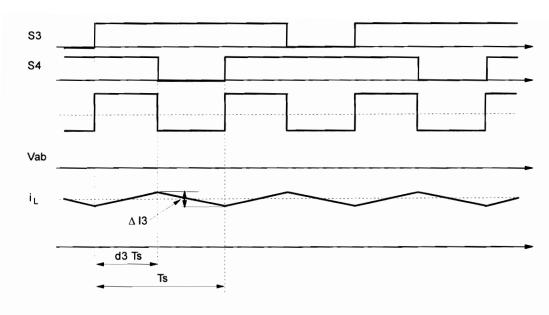

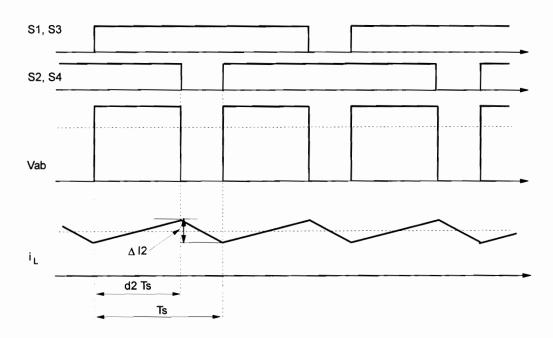

| Figure 6.6  | Subtopologies of Three-Level Two-Quadrant Chopper                    | 184   |

| Figure 6.7  | Key Waveforms of Two-Quadrant Choppers                               | . 187 |

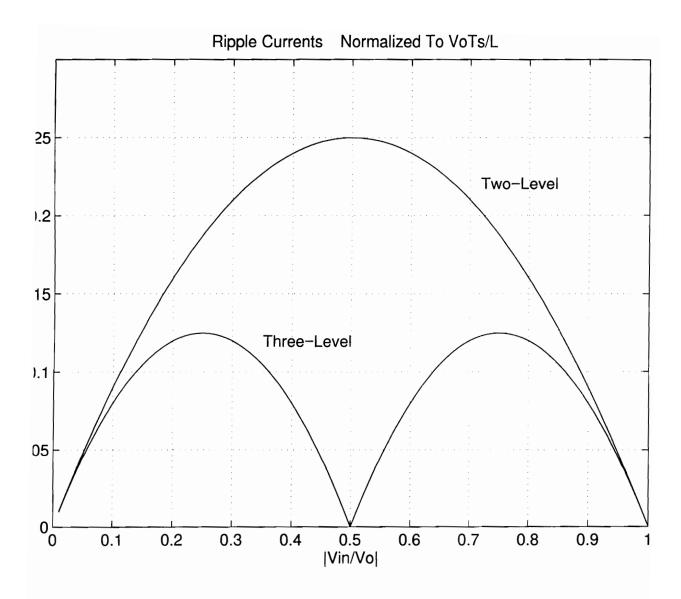

| Figure 6.8  | Normalized Peak-Peak Inductor Current Ripple                         | 188   |

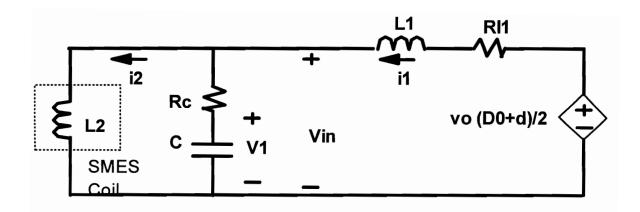

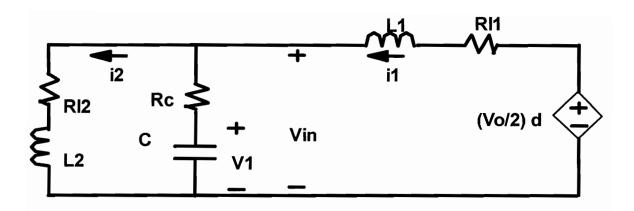

| Figure 6.9  | Average Model of Three-Level Chopper                                 | . 192 |

| Figure 6.10 | Small-Signal Model of Three-Level Two-Quadrant Choppers              | 194   |

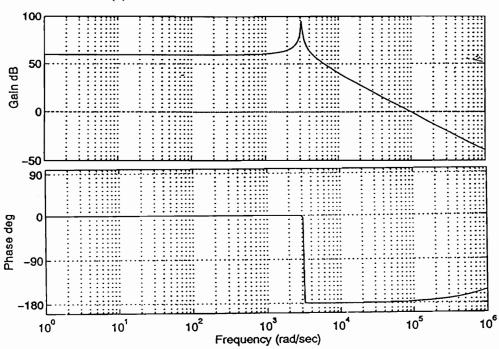

| Figure 6.11 | Power Stage Small-Signal transfer Functions                          | 195   |

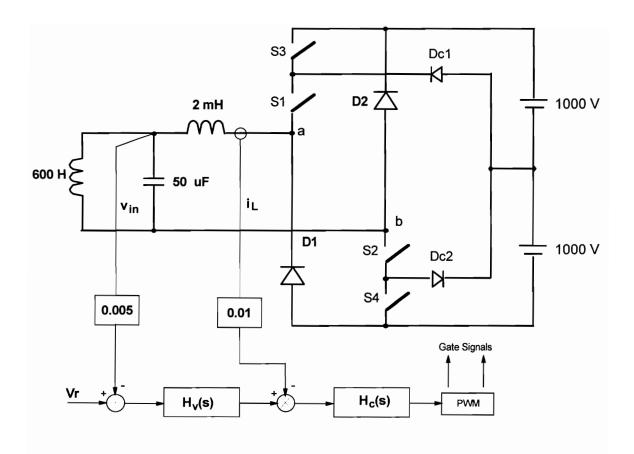

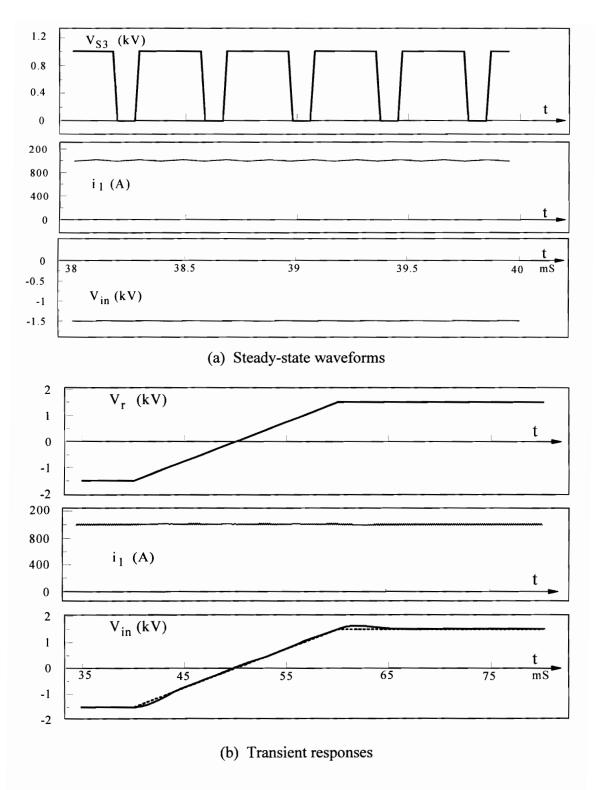

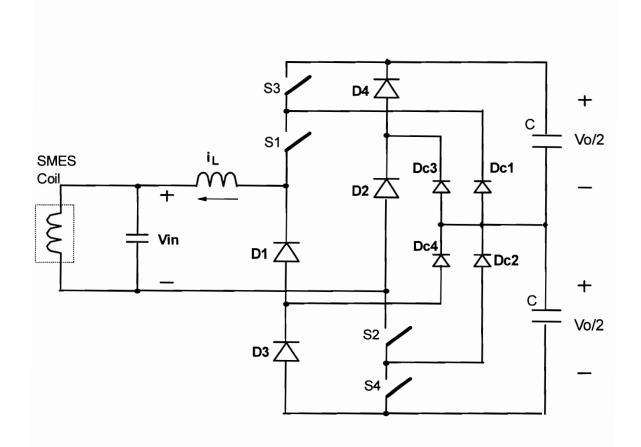

| Figure 6.12 | Prototype Converter Used in the Simulation                           | . 197 |

|             |                                                                      |       |

| Figure 6.13 | Simulation Results                                                       | 198  |

|-------------|--------------------------------------------------------------------------|------|

| Figure 6.14 | Three-Level Chopper with Reduced Diode Voltages                          | 199  |

| Figure 6.15 | Soft-Switched Two-Quadrant Choppers                                      | .202 |

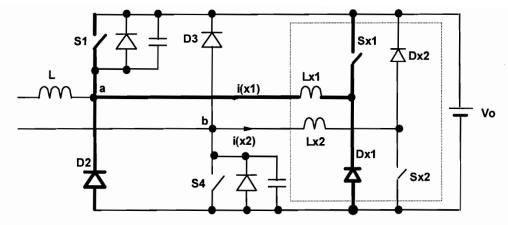

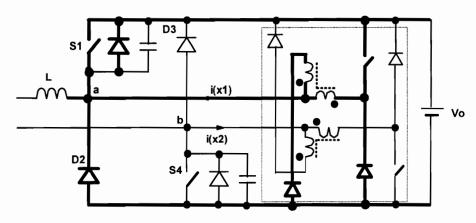

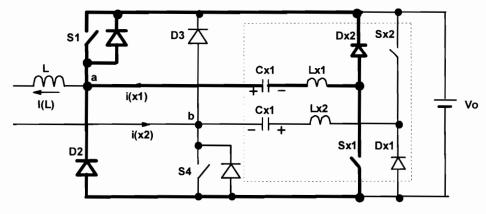

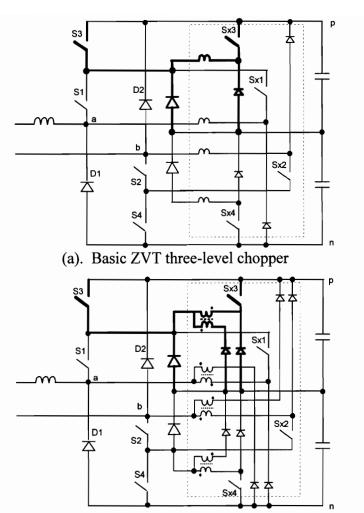

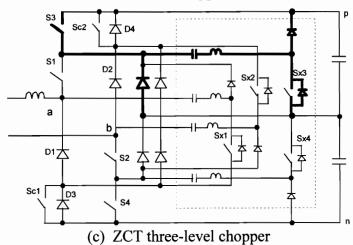

| Figure 6.16 | Soft-Switched Three-Level Two-Quadrant Choppers                          | 203  |

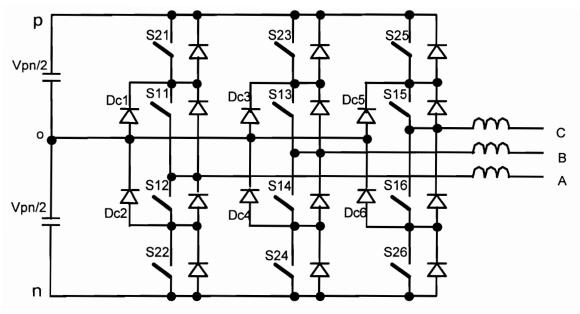

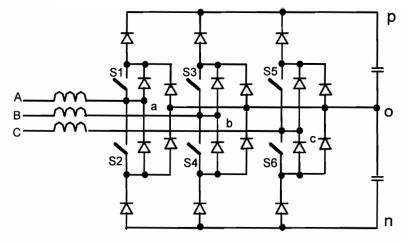

| Figure 6.17 | Three-Phase Three-Level Inverter and Its Space Vectors                   | .205 |

| Figure 6.18 | PWM Cells in a Three-Level Inverter Leg                                  | 207  |

| Figure 6.19 | Soft-switched Three-Level Inverter Leg.                                  | 208  |

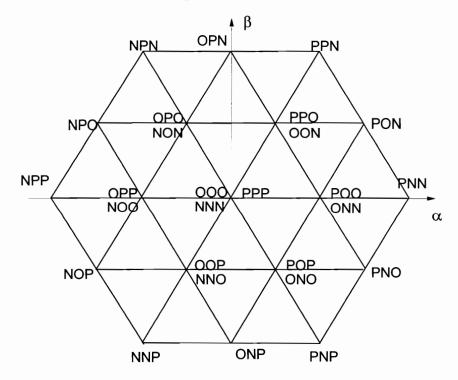

| Figure 6.20 | Active Voltage Space Vectors of Three-Level Rectifier in a 60° Interval. | 210  |

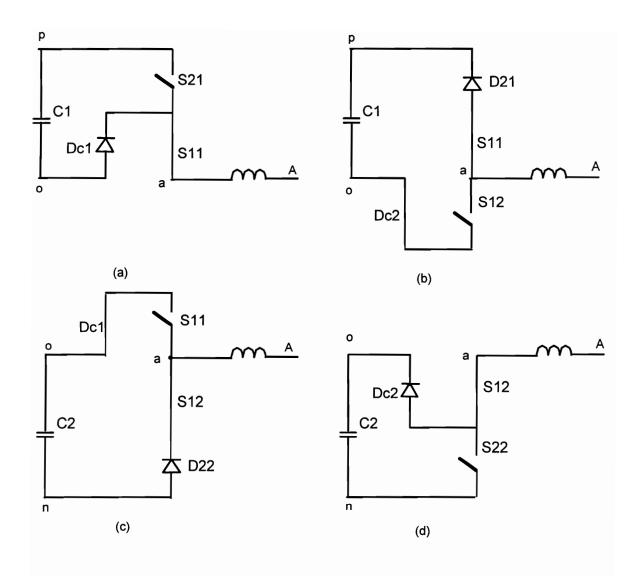

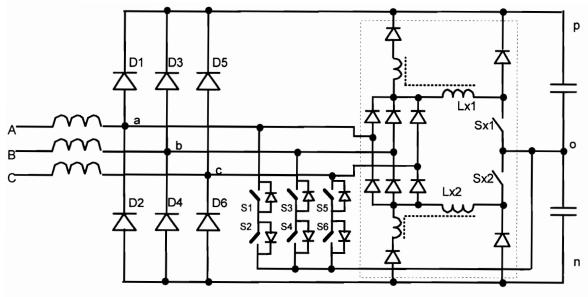

| Figure 6.21 | Topology development of Three-Phase Three-Level Rectifier                | 211  |

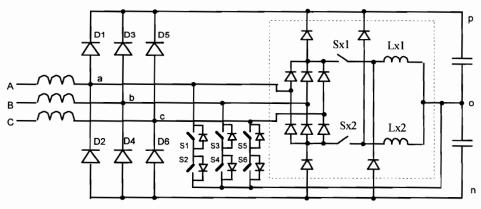

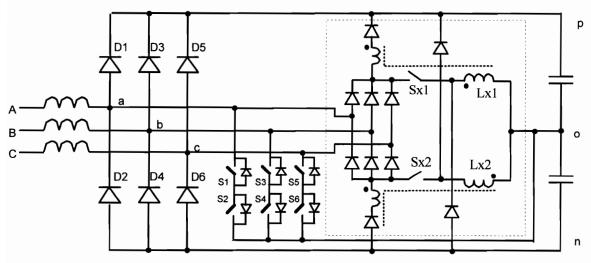

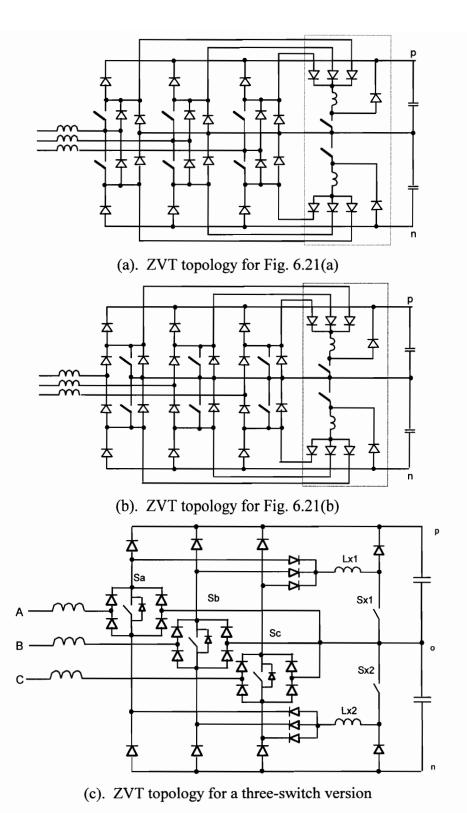

| Figure 6.22 | Zero-Voltage Transition Three-Phase Three-Level Rectifiers               | 214  |

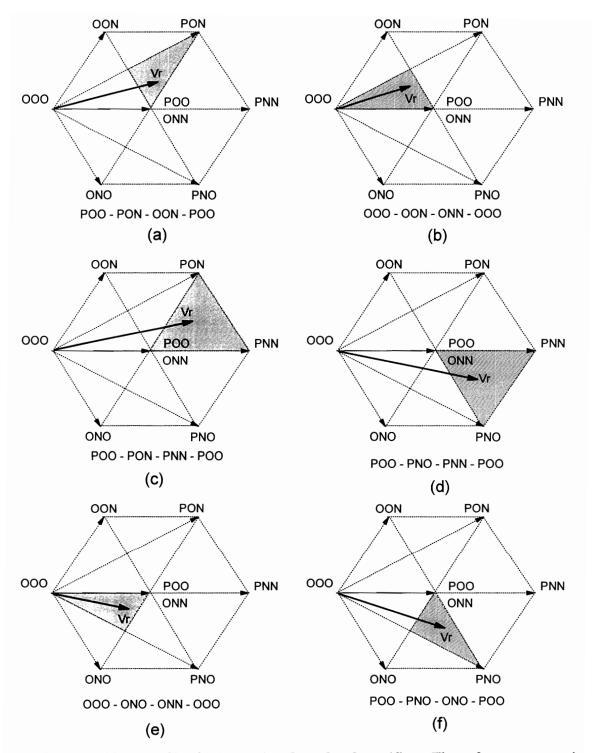

| Figure 6.23 | An SVM Scheme for Three-Level Rectifier                                  | 215  |

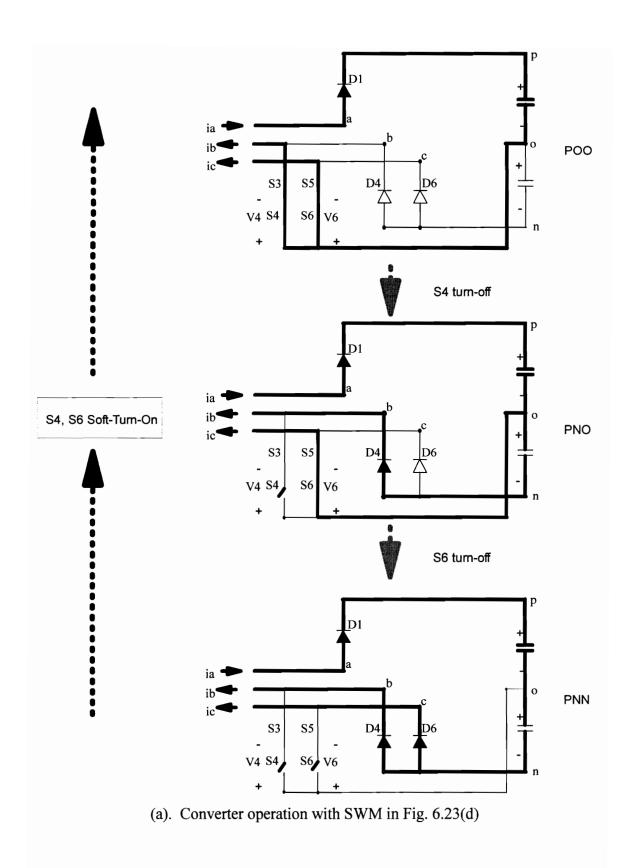

| Figure 6.24 | Soft-Switching Operation of a ZVT Three-Level Boost rectifier            | 218  |

| Figure 6.25 | ZVT Three-Level Rectifiers with Coupled Inductors                        | 220  |

| Figure 6.26 | Other Forms of ZVT Three-Level Rectifiers                                | 221  |

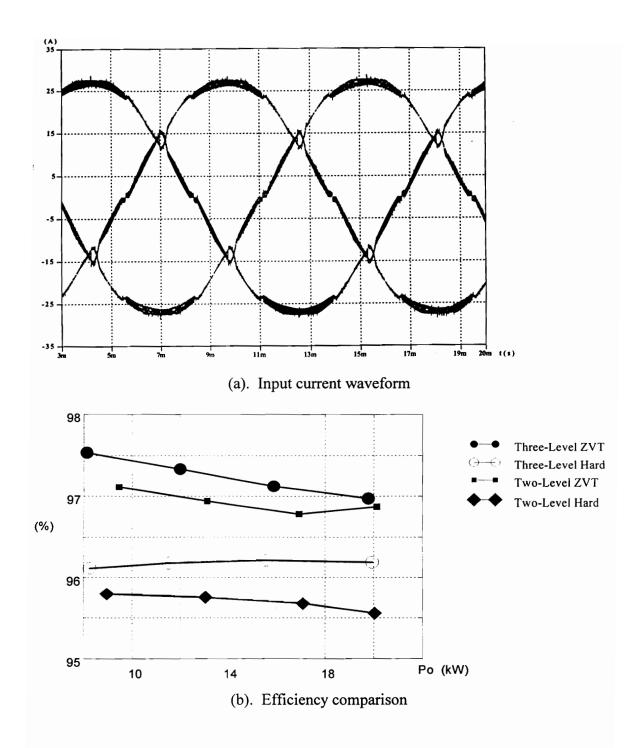

| Figure 6.27 | Simulation Results of Three-Level ZVT Rectifier                          | 223  |

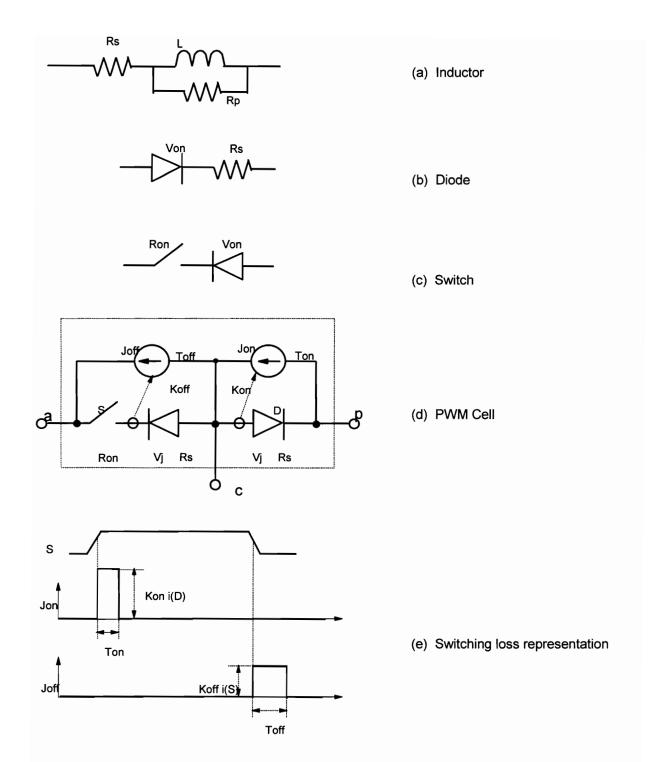

| Figure A.1  | Loss Model of Major Devices                                              | .244 |

Table of Contents xiv

### LIST OF TABLES

| Table 3.1 | Feature Comparison of Soft-Switching Three-Phase Inverters | . 81 |

|-----------|------------------------------------------------------------|------|

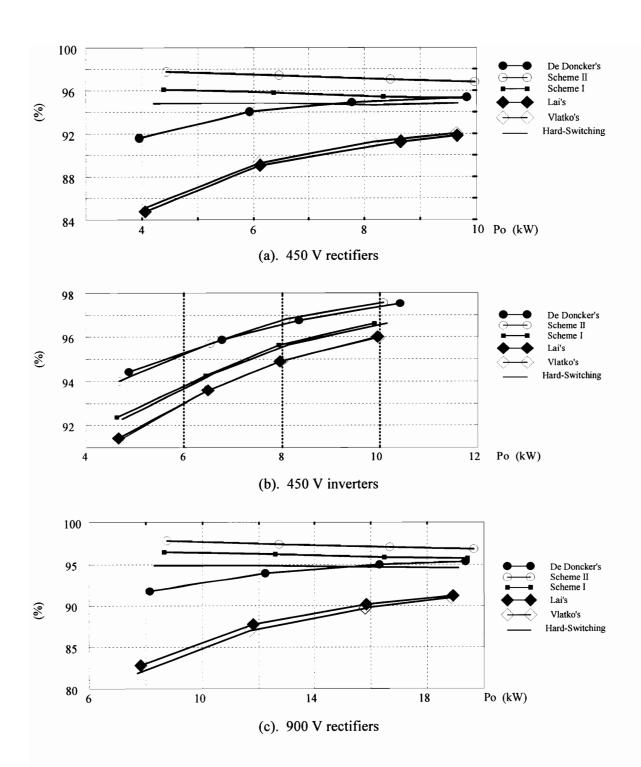

| Table 3.2 | Switch Loss Model Parameters Used in the Simulation        | 88   |

| Table 6.1 | Control Strategies of Three-Level Chopper                  | .185 |

| Table 6.2 | Parameters of the Average Model                            | 193  |

| Table A.1 | Switching Losses of IXGK50N60AU1                           | 246  |

| Table A.2 | Switching Losses of CM50 DY-24H                            | .247 |

Table of Contents xv

#### 1 INTRODUCTION

#### 1.1 BACKGROUND

Modern power supplies are required to provide high-quality power to their loads, and have a small physical size and weight. The switching frequency of a PWM power converter has profound effect on the converter power density and its electrical performances, because it practically determines the values of its reactive components, and limits the maximum bandwidth of the control loops (and thus the system dynamic performance). High-frequency operation of power converters is highly desired in many applications. However, the high-switching-frequency operation of a PWM converter is retarded by the high switching losses of power devices, and the high switching stresses caused by circuit parasitics (stray inductance, junction capacitance, etc.). The switching loss and stress problem is more pronounced in high power converters due to the poor switching characteristics and large physical size of high power semiconductor devices. Soft-switching techniques shape the switch voltage or current to zero before the switching action of power switches, thus avoiding the concurrent high voltage and high current in the switching transition. The benefits of soft switching can be summarized as:

- Low switching losses due to small overlap of the switch voltage and current;

- Low di/dt and dv/dt, and thus low voltage spike and EMI (electromagnetic interference) emissions;

- High reliability due to the favorable switching condition;

- Possible cost reduction due to the reduced voltage and current ratings of power semiconductor devices, and smaller values of reactive components.

Soft switching is an effective means to solve or alleviate switching losses and stress problems. Various soft-switching techniques have been developed in recent years, and are summarized in the following part of this section.

#### 1.1.1 SOFT-SWITCHING TECHNIQUES IN DC-DC CONVERTERS

Soft-switching techniques in dc-dc converters have evolved from resonant converters (RC), quasi-resonant converters (QRC), multi-resonant converters (MRC), and soft-switched PWM converters to soft-transition PWM converters, including zero-voltage transition (ZVT) and zero-current transition (ZCT) techniques [A27]-[A37]. These softswitching techniques can be classified into two categories: zero-voltage switching (ZVS), including ZVS RC, ZVS QRC, ZVS MRC and ZVT, and zero-current switching (ZCS), including ZCS RC, ZCS QRC, and ZCT. ZVS reduces or even eliminates the turn-on losses by shaping the switch voltage to zero prior to its turn-on, while ZCS reduces the turn-off loss by shaping the current of a switch to zero prior to its turn-off. RCs, QRCs and MRCs utilize reactive components, including parasitic elements in the practical circuit, to achieve soft-switching power conversion in a resonant fashion, and usually do not require extra active switches. On the other hand, ZVT and ZCT use additional auxiliary switches to control the resonance between the reactive components, and affect the converter operation only during the turn-on or turn-off switching transition. Although RCs, QRCs, and MRCs seem simple topologically, they suffer from high voltage/current stress and circulating energy compared to their PWM counterparts, and are used mainly in low power applications.

In medium to high power converters, ZVT and ZCT are more preferable than other soft switching schemes, because they achieve soft switching with minimum switch voltage/current stresses and minimum converter circulating energy, and incorporate the widely accepted PWM control. The switches used for high power applications are mainly minority carrier devices, such as IGBTs, MCTs and GTOs. The major switching loss in these devices is usually the switch turn-off loss, which can be reduced by zero-current turn-off. However, the turn-on loss (including diode reverse recovery loss) is also significant, especially in high voltage devices. An optimum soft-switching scheme for a specific converter can only be determined by the switch devices used. Generally, a

successful soft switching scheme for high power applications should have minimum voltage stress for all switches, significantly reduced turn-off loss, and very small diode reverse recovery. The soft switching of auxiliary switches is also desired in very-highpower applications. The ZVT topology in [A32] eliminates the switch turn-on loss and diode reverse recovery. However, both the main switch and the auxiliary switch are turned off with high current, which limits its application in high power applications. The topology presented in [A41] operates in a similar manner as the ZVT in [A32], has a capacitor snubber to reduce the auxiliary switch turn-off loss. Coupled inductors are adopted in [A33] [A34] to reduce the turn-off current of the auxiliary switch to the magnetizing current of the coupled inductor, which is much smaller than the main inductor current. However, the design of the coupled inductor is complex, and accurate and operating-condition-dependent control timing in the soft-switching transients is required to achieve zero-voltage turn-on. In all these ZVT topologies, the turn-off loss of the main switch is not tackled directly. Although snubber capacitors can be used to reduce switch turn-off loss, the effect of a snubber sized for high frequency operation is usually marginal for high power devices [A1] [A13]. The ZCT topology in [A35] reduces the main switch turn-off loss significantly, but does not reduce the turn-on loss and diode reverse recovery. In addition, it requires the auxiliary switch to be turned off with high current. Therefore, the existing ZCT technique is not suitable for high-power applications either.

#### 1.1.2 SOFT-SWITCHING TECHNIQUES IN THREE-PHASE CONVERTERS

Three-phase PWM converters are the high-power topology most widely used in practice. According to power conversion requirements, three-phase converters are categorized as inverters (dc-ac converters), rectifiers (ac-dc converters) and cycloconverters (ac-ac converters). Cycloconverters are rarely used nowadays except in some extremely high power applications, and are not included in this work. Inverters are

widely used in motor drives, uninterruptible power supplies, and many other applications. Power factor correction (PFC) converters, i.e. rectifiers with active input current control, are replacing conventional diode or thyristor rectifiers in many applications due to the forthcoming stringent power quality regulation. Up to now, most research effort in the field of three-phase converters has been focused on inverters. However, high-switching-frequency operation is usually more important in PFC converters than in inverters, because PFC converters need to achieve high-quality current control with small reactive components, which are not important factors in most inverter applications. Soft-switching techniques, which are important to inverters in reducing current (torque) ripple and acoustic noise, and improving control performance through the use of high switching frequencies, are more critical in rectifier applications.

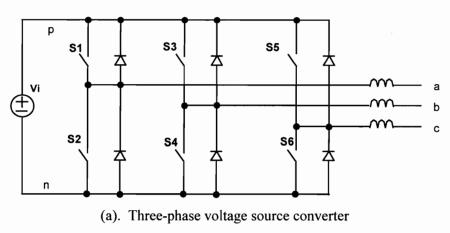

Three-phase voltage source converters, including voltage source inverters and boost rectifiers, are widely used nowadays. In unidirectional power flow and low power end applications, discontinuous current mode (DCM) single-switch PFC schemes are usually used [B1]-[B4]. The soft-switching techniques in dc-dc converter can be easily adopted in these rectifiers [B5]. Due to the DCM operation of the converters, the active switch has a very small turn-on loss, but is subject to high turn-off loss. [B6] incorporated the ZCT scheme in [A35] to reduce the switch turn-off loss, achieving high converter efficiency. [B7] proposes a method to combine three single-phase PFC converters into a three-phase boost rectifier, in which soft-switching techniques in dc-dc converters, such as ZVT and ZCT, can also be directly used. In higher power levels, full-bridge type topologies, which are used in inverters also, are usually used due to their better current quality and higher efficiency. Most soft switching techniques in bridge type converters are shared by both inverters and rectifiers, and can be classified into two categories: dclink commutation schemes [B8]-[B23] and ac side commutation schemes [B24]-[B31]. The dc-link commutation schemes have an inductor or switch in the dc link to separate the bridge switches from the stiff dc-link voltage source, and incorporate a resonant circuit across the dc link to shape the voltage of all bridge switches to zero at the same

time. The resonant dc link (RDCL) converter proposed in [B9] operates similarly to the ZVS QRC techniques used in dc-dc converters. With a resonant inductor in the dc link, and resonant capacitors across all bridge switches, the dc-link voltage is made to resonate at high frequencies to create zero-voltage conditions regularly, and the bridge switches are switched only during the zero link voltage period. Discrete pulse modulation (DPM) schemes, such as  $\Sigma$ - $\Delta$  modulation, are used to synthesize the output voltages without hindering the soft-switching operation [B35]. One of major disadvantages of the RDCL technique is the high voltage stress of the main switches: each main switch is required to block up to 2.5 times the dc source voltage. In addition, the DPM control, which is more complex than the conventional PWM control, requires a dc-link resonant frequency 8~10 times higher than the switching frequency in a PWM converter for a comparable spectral performance [B34] [B37] [B38], which is usually impractical. The actively clamped version of RDCL reduces the switch voltage stress to around 1.5 times dc source voltage by a clamp circuit. However, a large amount of energy is circulated in the clamp circuit, and DPM control is still required. Some techniques are tried to provide PWM control to RDCL [B39]. However, the PWM range is severely limited, and the switching loss is increased significantly. Many other resonant link topologies are also proposed in recent years. Some are reviewed in [B34], and demonstrate no significant improvement over hard-switching converters.

Several other dc-link commutation topologies avoid the high voltage stress and DPM control by putting the resonant components out of the main power path, in order to enable PWM control. The parallel resonant dc link (PRDCL) [B13] reduces the voltage stress and circulating energy in RDCL by using a dc-link switch. The resonant circuit, paralleled across the inverter bridge, is actuated only when soft-switching action is required to create zero-voltage turn-on condition for the main bridge switches. However, the auxiliary circuit is complex: four additional switches, one in the dc link and three in the resonant circuit, are required in this topology. These auxiliary switches are turned off with high current, and one of them has a high voltage stress. Another PRDCL scheme in

[B14] simplifies the resonant circuit slightly by eliminating one auxiliary switch. The quasi-resonant dc link (QRDCL) converter in [B15] requires only two auxiliary switches, and one of the auxiliary switches is turned on and off with zero current. However, the control timing for the auxiliary circuit is complex and difficult to adjust for a wide load range. The ZVT and ZCT dc-link commutation techniques proposed first in [B16] adopt the ZVT and ZCT concepts to the dc link, and simplify the auxiliary switch control requirement. [B17] proposes to incorporate the control of the dc-link switch into the PWM scheme, so that the total switching losses can be minimized. The simple topology proposed in [B19] uses a snubber capacitor to reduce the auxiliary switch turn-off loss, but the dc-link switch turn-off loss and auxiliary circuit conduction loss are increased due to the overcharged and bi-directional resonant inductor current. Coupled-inductors are used in [B21] [B22] to reduce the auxiliary switch turn-off current. PWM control, usually with certain modifications to the conventional schemes [B17] [B41], is used in these soft-switching topologies, so the device voltage stress and converter circulating energy are comparable to their hard-switching PWM counterparts. One distinctive feature of these dc-link PWM soft-switching schemes is that fewer auxiliary switches than the main switches are required. However, the dc-link switch has to conduct the main inverter current, and is turned off with high current in every switching cycle; its conduction loss and switching loss are even much higher than a main switch's. As a result, the implementation of the auxiliary circuit is quite complex, and efficiency improvement of soft switching is curtailed significantly by the power loss of the dc-link switch. One exception is the ZVT boost rectifiers proposed in [B8], where the dc-link switch is changed into a diode, and thus has a much lower power loss. The dc-link diode also provides short-through protection for the main switches, and enhances the converter reliability. However, negative dc-link current is blocked by the dc-link diode, making bidirectional power flow impossible. These dc-link commutation schemes are attractive in relatively low power applications.

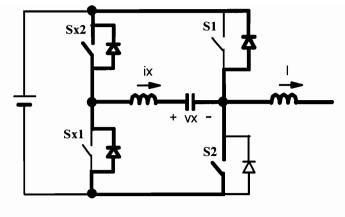

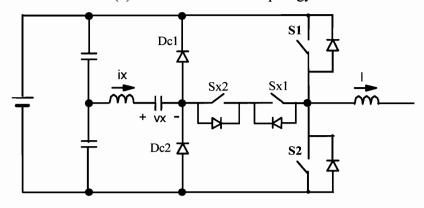

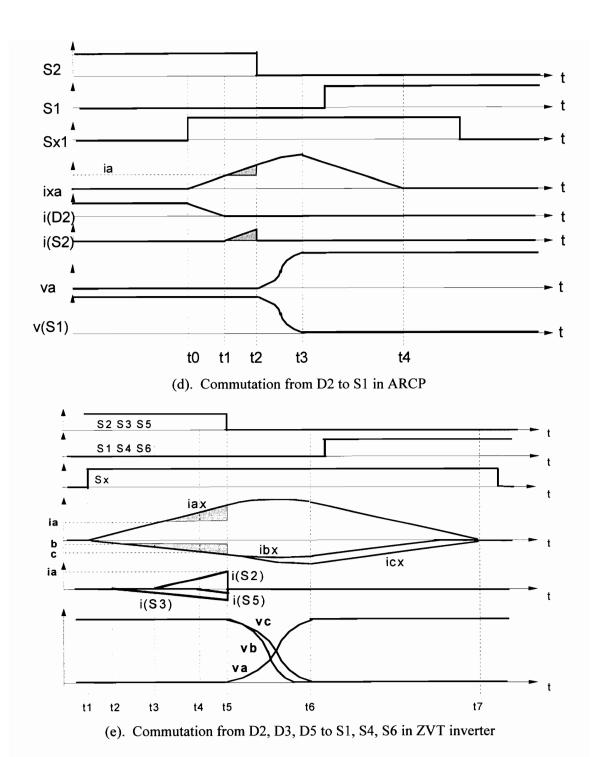

In higher power level, it is generally desired to place the auxiliary circuit out of the main power path to reduce its power loss. Then the soft-switching circuit can be put at the ac side of the main bridge. Each main switch can have a functionally independent auxiliary circuit to provide soft switching condition [B26] [B28]. Although the number of auxiliary switches in ac side commutation schemes is increased compared to the dclink commutation schemes, each auxiliary switch has a much lower power loss and is turned off with zero or small current, and consequently has a simpler and lower-cost implementation. The auxiliary resonant commutated pole (ARCP) inverter [B26] [B27] achieves zero-voltage turn-on for all main switches without significant modification to the modulation schemes. A distinctive feature of ARCP is that the auxiliary switches block only half the dc-link voltage, and are turned off with zero current, therefore having a very low power loss. The ZVT topology in [B28] applies the ZVT technique in [A33] directly to each main switch in a configuration similar to the soft-switching scheme in [B22]. The conduction loss and turn-off loss of the auxiliary switches are smaller than those occurring with the basic ZVT topology proposed in [A32]. However, the switch turn-off loss in these two topologies is only indirectly tackled by snubber capacitors, which are not very effective in high-power, high-frequency operations. Besides, high snubber capacitance also causes high voltage/current distortion due to the "zero current clamp" effect, and reduces the dc-link voltage utilization due to the increased dwell time [E33] [E34]. It is realized that the turn-off loss of switches is a more severe problem than the turn-on loss in many high power applications, and a ZCS topology was proposed in [B43] to solve the switch turn-off loss and diode reverse recovery problems, but it has several shortcomings:

- Two auxiliary switches are placed in the dc link, and are turned off with high current, therefore causing high conduction loss and turn-off loss;

- A resonant inductor of considerable inductance is in series with each main switch, and therefore causes high power loss and excessively high voltage stress if zero-current switching is not achieved for any reason;

• The turn-offs of all switches are synchronized, which generally requires more switching action than is necessary with the optimum PWM strategy.

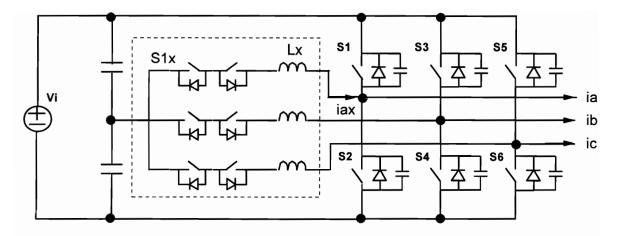

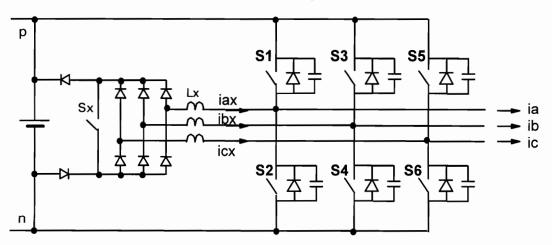

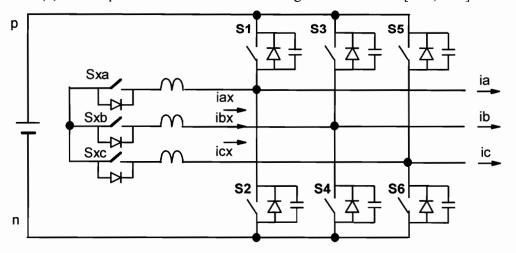

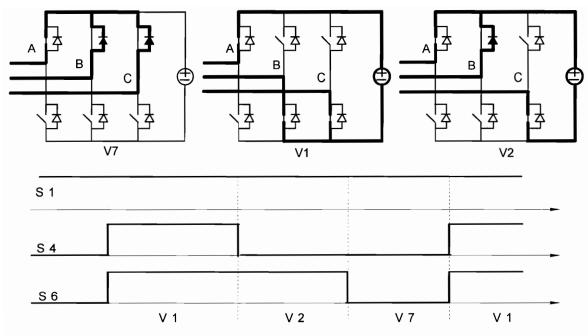

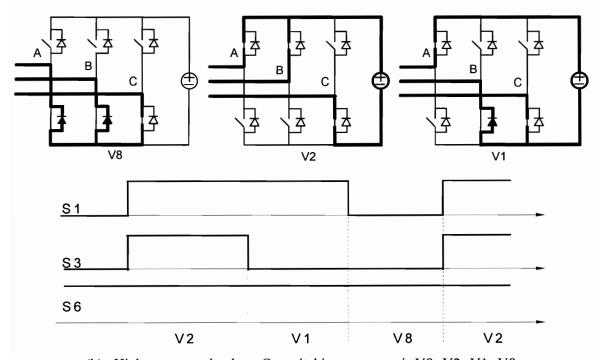

In medium power applications, one of the major drawbacks shared by the above acside commutation schemes is that six auxiliary switches are required, and their control timing changes with phase currents. As a result, the converter implementation and control are complex and not cost-effective. A three-phase ZVT topology is proposed in [B29] to simplify these topologies. If the turn-on instants of all main switches is synchronized, only one auxiliary switch is required to provide soft-switching function for all six main switches, so the topology becomes much simpler. This simplified ZVT topology is controlled with a modified SVM scheme [B42]. The drawback is that the total turn-off currents of the main switches are much increased, and the auxiliary switch has a high conduction loss. The so-called resonant snubber based soft-switching inverter (RS³) [B30] [B31] achieves a similar performance but requires at least three auxiliary switches.

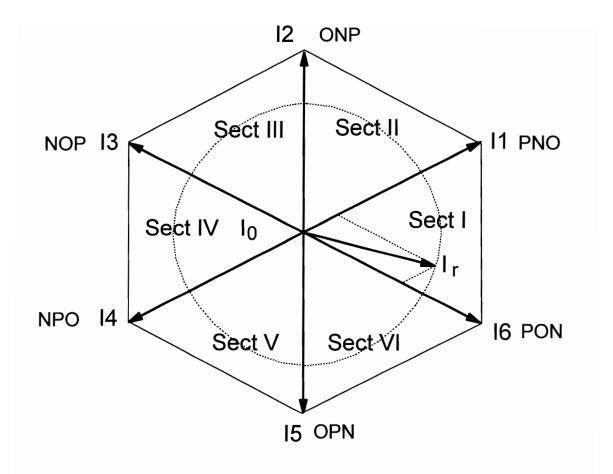

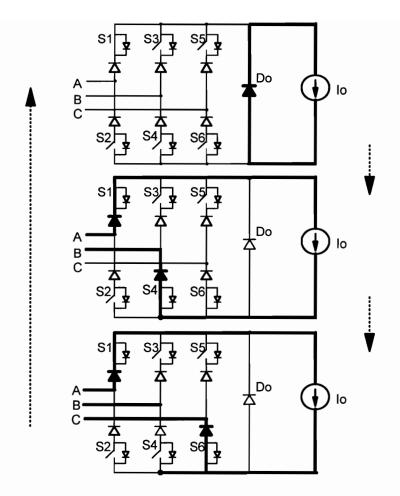

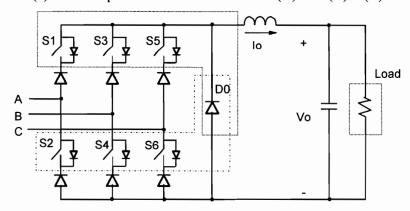

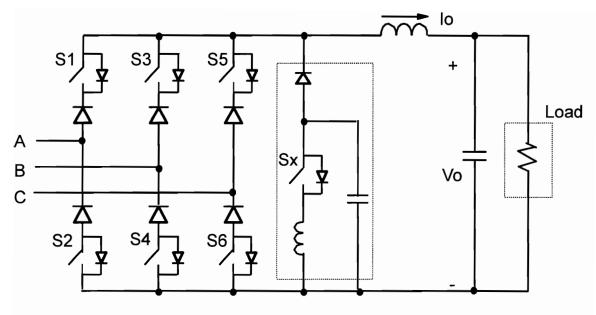

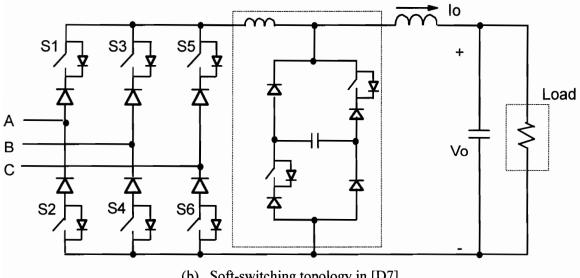

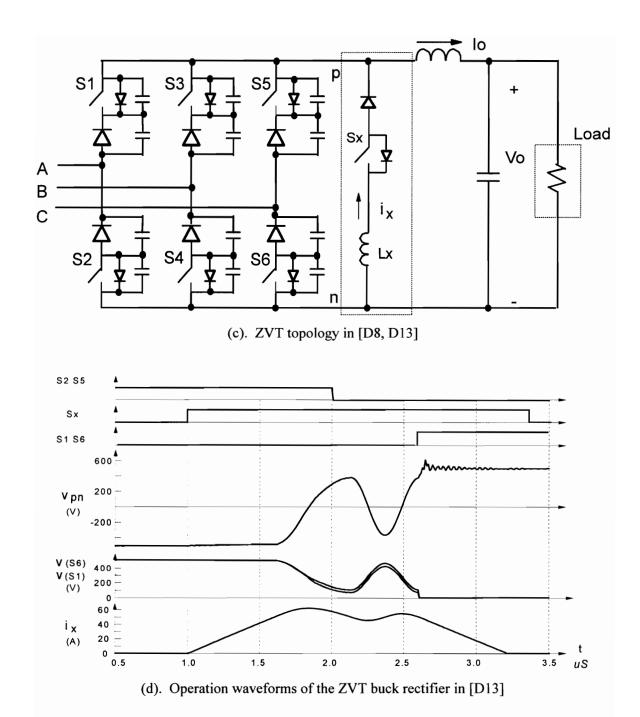

Compared with voltage source converters, the soft switching of current source converters (including current source inverters, buck and buck-boost rectifiers) has not been well studied. The resonant link approach [D1]-[D5] has serious drawbacks similar to those of RDCL in [B9] [B10]. Recently, several soft-switching topologies for PWM current source inverters/buck rectifiers were investigated in [D6]-[D10] [D13]. However, these topologies have the following shortcomings:

• The soft-switching circuits are connected to the dc-link, and cannot absorb the parasitic inductance energy in the bridge arms. This might be acceptable for very high power applications where GTOs are used as main switches. However, in lower power applications, each bridge arm is usually implemented as a uni-directional voltage device, such as IGBTs, MOSFETs or MCTs, and a diode in series, then the energy of the switch junction capacitance, plus snubber capacitance if any, is trapped by the diode, and the resonance between the junction capacitance and stray inductance in the bridge arms causes high voltage spike and power dissipation to the switch [D13].

• The soft-switching circuits usually have a resonant tank (a capacitor and an inductor), require complex control timing, and produce higher than minimum voltage/current stress. Especially, the switch voltage stress depends on the soft-switching timing in some of these topologies, making them difficult to use.

The ZVS single-stage buck rectifier in [D11] [D12] utilizes the same soft-switching technique as the ZVS full-bridge dc-dc converters, and provides zero-voltage turn-on for all main switches without additional components. However, twelve main switches are required, and the converter offers no cost and efficiency improvement over a conventional two-stage approach, i.e. a boost rectifier plus a full-bridge dc-dc converter, since all switches in the single-stage approach have to be designed according to both the peak voltage stress at high line and the peak current stress at low line. Besides, the conduction loss of the primary switches is increased due to the increased circulating current.

#### 1.1.3 SOFT-SWITCHING TECHNIQUES IN MULTI-LEVEL CONVERTERS

The popularity of multi-level power conversion is ever-increasing in high-power applications, because it can reduce the switching loss of power switches and the current ripple of the bulk inductors, and enhance the voltage sharing of series switches. Various three-phase and dc-dc multi-level topologies are proposed in [C1]-[C6] [C16] [C17], and various control aspects are investigated in [C8] [C14]. Soft switching also plays a very important role in multi-level converters. [C17]-[C19] proposed several soft-switching topologies for multi-level dc-dc converters. A ZVT three-level three-phase boost rectifier is proposed in [B44]. However, the auxiliary switch in this topology needs to block full output voltage, which is twice the voltage requirement of the main switches. Also, all three phase currents are switched in every switching cycle, causing more than the optimum switch turn-off loss. [C20] introduces the ZVS concept similar to in [B23] into three-level inverters. However, two additional switches placed in the main power path

have high power loss. [C21] proposes a soft-switching topology similar to the ARCP, but the auxiliary switches are required to block higher voltage than the main switches. Besides, the switch turn-off loss is not directly tackled in these ZVS schemes.

## 1.1.4 CONTROL AND SMALL-SIGNAL MODELING OF THREE-PHASE CONVERTERS

In addition to power stage topology study, another important aspect of power converter is the control and modeling of power stage, which is related to this work, especially in the three-phase converters, but not directly covered in this dissertation. Most modeling techniques in dc-dc converters are based on the state-space averaging technique [E10], while a PWM switch model practically equivalent to the state-space averaging technique is proposed in [E11]. The effect of switch nonlinearities, such as storage modulation and switch saturation voltage, is also modeled in [E11] [E12]. The effect of the soft-switching (ZVT) operation is modeled using the circuit averaging technique, for dc-dc converters in [E13], and for three-phase ZVT boost rectifiers in [E14].

The modeling and control of three-phase converters are included in three categories: modulation, power stage modeling, and controller design. Various modulation schemes are presented in [E1]-[E6] [E37]. [E7]-[E9] compare the performances of some modulation schemes. [E15] introduces a method to model switches in three-phase converters as ideal transformers, and then apply the d-q transformation to each part of the converters. [E16] directly applies the d-q transformation to the system equations of three-phase converters, and derives the converter models in the d-q coordinates. [E17] [E29] introduce d-q coordinates modeling of three-phase buck rectifiers. Different control schemes are discussed in [E19] [E20] [E23]-[E31]. Most modeling techniques in three-phase converters are based on the d-q transformation, and the resulting d-q model of a three-phase converter consists of two coupled channels: d channel and q channel, each having a structure similar to a dc-dc converter. Due to the cross coupling of these two

channels, the control design of three-phase converters is more or less a trial-and-error process. [E38] proposes to model a three-phase converter at its "averaged" operating point, and the three-phase converter model developed shows the same dynamics as the d-channel in the d-q model, but has the simple structure of a dc-dc converter. Another control issue is the interaction of subsystems in a complex power converter system. The interaction of dc-dc converter systems has been studied in [E31] [E36], and its basic concept can be extended to three-phase power converters. The interaction analysis of the dc-link interface can directly adopt the dc-dc converter techniques in [E31]. However, the interaction analysis of the three-phase interface, such as between an EMI input filter and a three-phase PWM rectifier, is much more complex. This problem is addressed briefly in [E29] for buck rectifiers, and is analyzed in [E37] for general converters with a simple converter model. The effects of some power device nonlinearities on three-phase converters are discussed in [E34] [E35].

#### 1.2 PRESENT WORK

The primary objective of this work is to study soft-switching schemes for different power converter topologies in high-power applications. Due to the difference in operation requirements and power semiconductor characteristics, no single soft-switching scheme is suitable for all applications. This dissertation proposes and verifies several new high-power soft-switching topologies for dc-dc and three-phase power converters. These topologies improve the existing soft-switching techniques in the following aspects:

- (a). PWM control of the converter is still kept. At the same switching frequency, PWM control can achieve a better control performance than any other control schemes. With PWM control, the switch voltage/current stress and circulating energy in a soft-switching converter are also minimized.

- (b). All auxiliary circuit components are not in the main power path, and have low power loss.

- (c). The modification to optimum PWM schemes is minimized, and the resonant inductor overcharging is eliminated in three-phase converters, so the extra main switch turn-off and its related power losses are also minimized.

- (d). The soft-switching functions are achieved with simple auxiliary circuit control timing. The control timing of the auxiliary circuit is fixed for all operating conditions, so extra current/voltage sensing is not required, and the soft-switching operation is more reliable.

Several new ZCT schemes are proposed to provide zero-current turn-on and turn-off for all switches, including the auxiliary switches, in a PWM converter, so the switching loss and stress of the switches can be significantly reduced. Experimental results prove that the switching loss and voltage spike of high power IGBT modules can be reduced by more than 80% with the improved ZCT technique. The proposed schemes are suitable for very high power applications, where the switching loss and stress need to be kept at minimum.

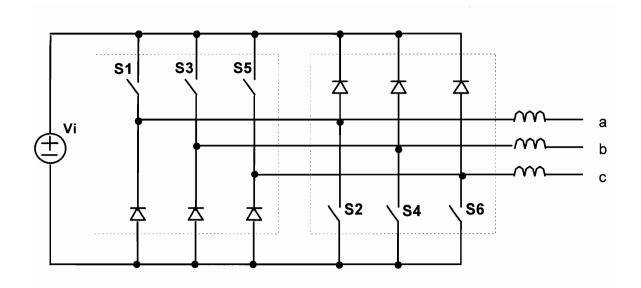

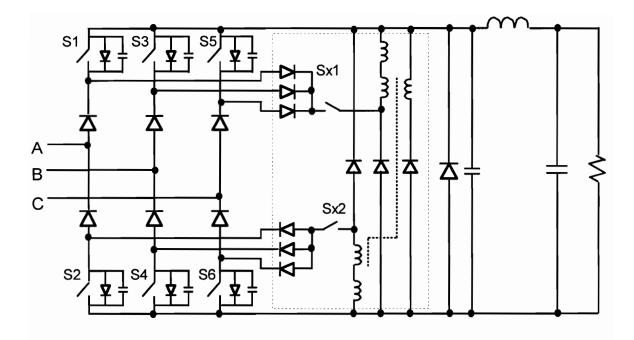

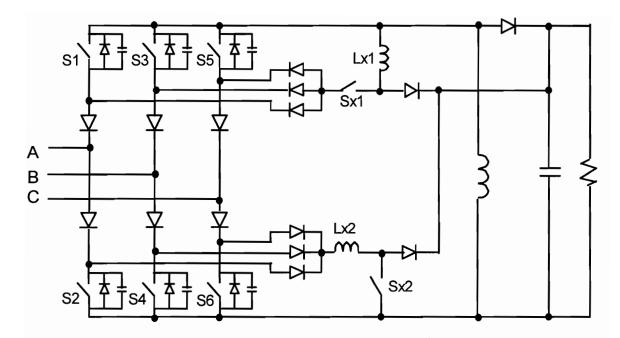

Several simplified ZVT schemes for three-phase PWM converters are proposed. The switch turn-on instants in three phases are synchronized by PWM schemes, so that the switches and diodes in a three-phase converter can be divided into a top group and a bottom group. The ZVT principle is then applied to each group of the switches and diodes, instead of to each switch/diode pair. As a result, the auxiliary circuit can be simplified, while still achieving soft turn-on for all main switches. Different implementations of the soft-switching circuits for three-phase boost rectifiers/voltage source inverters, buck rectifiers, and buck-boost rectifiers are investigated. The operation principle and efficiency improvement of the proposed ZVT soft-switching schemes are verified by experimental and simulation results.

New soft-switching dc-link scheme is also investigated for three-phase ac-dc-ac PWM converter systems. By coordinating the control of the ac-dc converter with the dc-ac converter, a simple dc-link auxiliary circuit can provide soft-switching function for all switches in both the rectifier and the inverter. The power loss of the auxiliary circuit is much lower than in other dc-link soft-switching schemes, which further increases the efficiency improvement and reduces the cost of the auxiliary circuit.

A new multi-level two-quadrant boost chopper structure is explored for superconductive magnetic energy storage (SMES) and motor drive applications, which demonstrates a significant performance improvement over a two-level chopper with the same power stage parameters on switching loss, current ripple, and voltage sharing. Softswitching schemes for three-phase three-level PWM inverters are developed with the concept of ZVT and ZCT cells. Simplified ZVT topologies for three-phase three-level PWM rectifiers are also investigated with switch turn-on synchronized SVM schemes.

#### 1.3 DISSERTATION OUTLINE

This dissertation is arranged as follows:

Chapter 2 describes improved zero-current transition techniques for high-power applications. With modified control timing and topologies, the proposed ZCT techniques achieve soft turn-on and turn-off for all switches without increasing the switch voltage stress and hindering PWM control. An MCT converter and an IGBT test circuit are tested, and demonstrate a significant switching loss and switching stress reduction, and efficiency improvement.

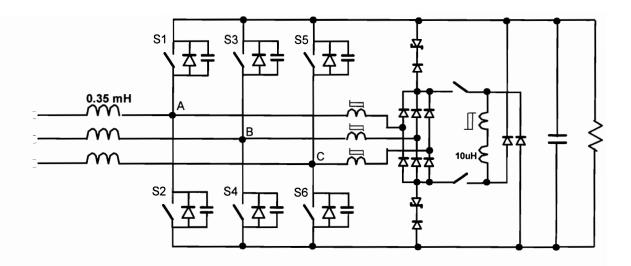

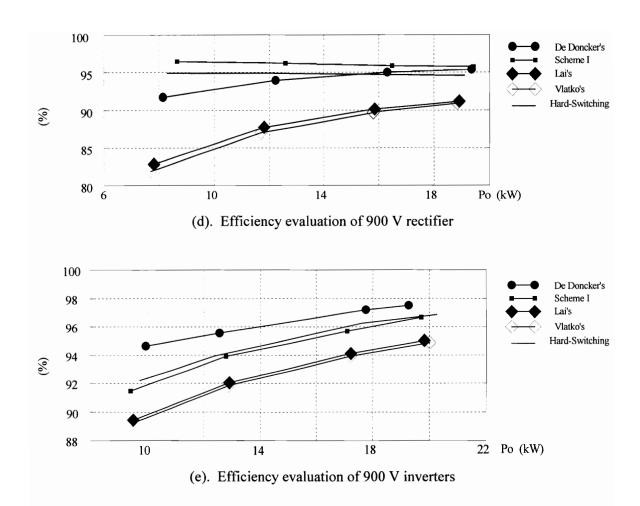

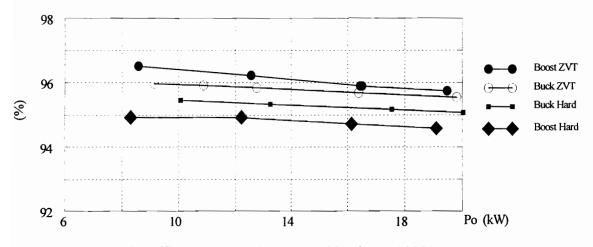

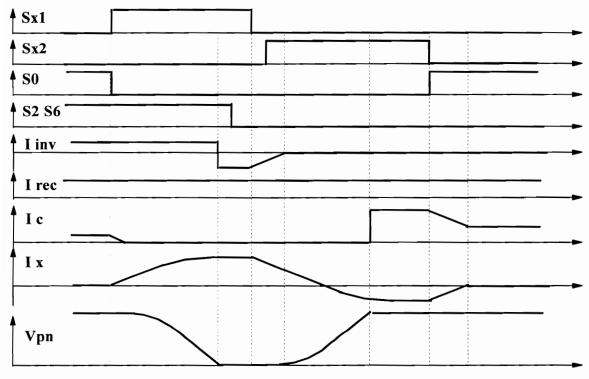

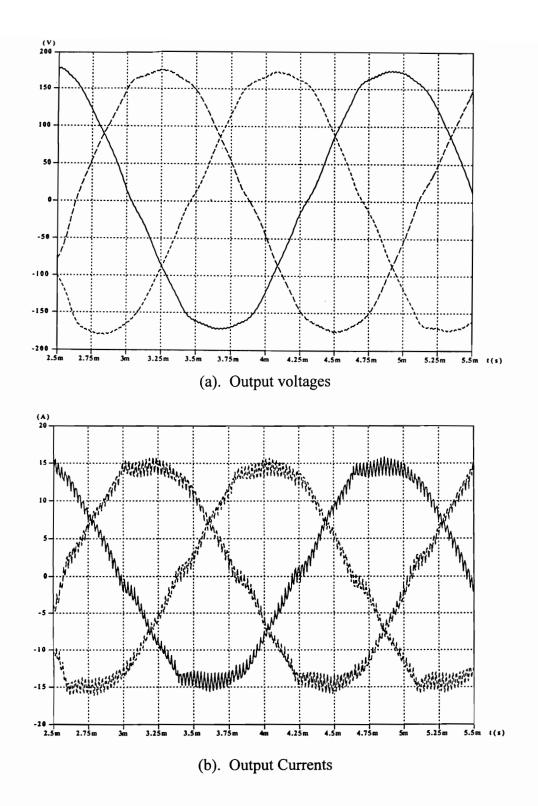

Chapter 3 investigates simplified zero-voltage transition circuits for three-phase voltage source inverters and boost rectifiers. Space vector modulation schemes are arranged to synchronize the active switch turn-on in each switching cycle, so that simple auxiliary circuits can be used to provide soft-switching turn-on for all main switches. Experimental results verify the operation principle of the ZVT schemes, and demonstrate significant efficiency improvement. Two test configurations are simulated to evaluate the performance of the proposed ZVT circuits and compare the efficiencies of different hard-switching and soft-switching topologies under the same operating conditions. One is for 230 V ac, 450 V dc applications, and the other for 460 V ac, 900 V dc applications. Simple power loss models for the main power devices with experimentally obtained switching loss data are used in the switching model simulation. 1~2% efficiency improvement over the hard-switching operation is obtained in the simulation for the proposed ZVT schemes, which means around 30% converter power loss reduction, and possibly considerable cost reduction with a proper design.

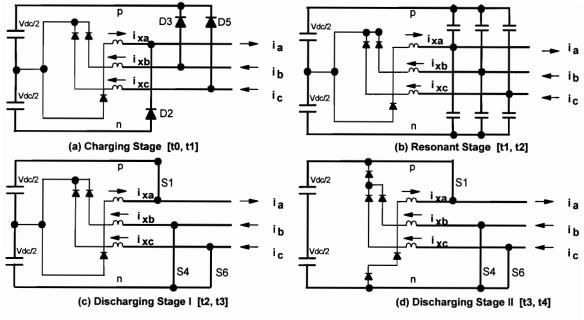

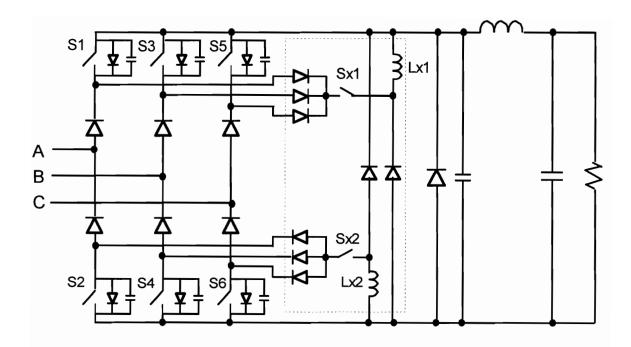

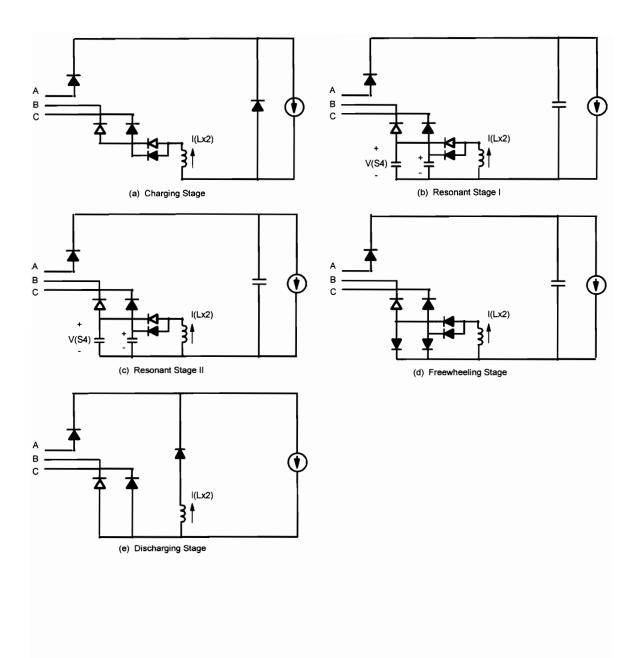

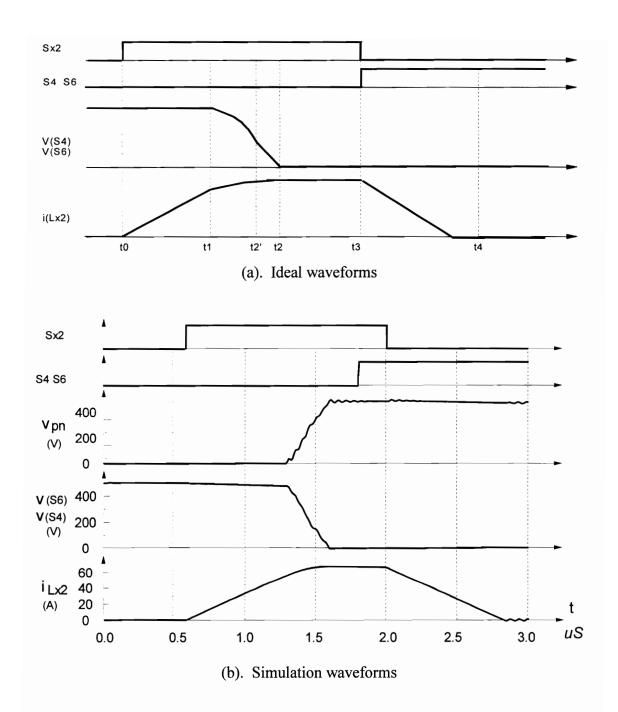

Chapter 4 presents several three-phase ZVT buck and buck-boost rectifiers. Similarly to in the ZVT VSI and boost rectifiers, the switch turn-on instants are synchronized in the three phases through the current SVM scheme, so only two auxiliary switches are required to achieve zero-voltage turn-on for all six main switches. The

operation and efficiency improvement of the soft-switching techniques are verified with simulation.

Chapter 5 investigates new soft-switching schemes for three-phase ac-dc-ac PWM power conversion systems. The soft-switching mechanism is applied to the dc link, which is common to the ac-dc converter (the rectifier) and the dc-ac converter (the inverter), so that a set of auxiliary circuit can be used to provide soft-switching functions to all switches. The power loss of the auxiliary circuit is also much lower than with other existing dc-link soft-switching schemes.

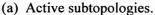

Chapter 6 presents novel techniques of multi-level power conversion. A new multi-level structure for two-quadrant boost choppers is proposed, and its PWM control scheme and small-signal model are developed. ZVT and ZCT techniques for the two-quadrant choppers are also discussed. PWM cells for three-phase three-level inverters are identified with careful examination of SVM schemes, and ZCT cell and ZVT cell concepts are used to derive soft-switching topologies for three-level inverters. Similarly to the technique used in Chapter 3, SVM schemes are arranged to synchronize switch turn-on in three-phase three-level boost rectifiers, and simple auxiliary circuits are developed to provide zero-voltage turn-on for main switches.

Conclusions of this work and suggestions for future work are given in Chapter 7.

#### 2 IMPROVED ZERO-CURRENT TRANSITION CONVERTERS FOR HIGH-POWER APPLICATIONS

#### 2.1 INTRODUCTION

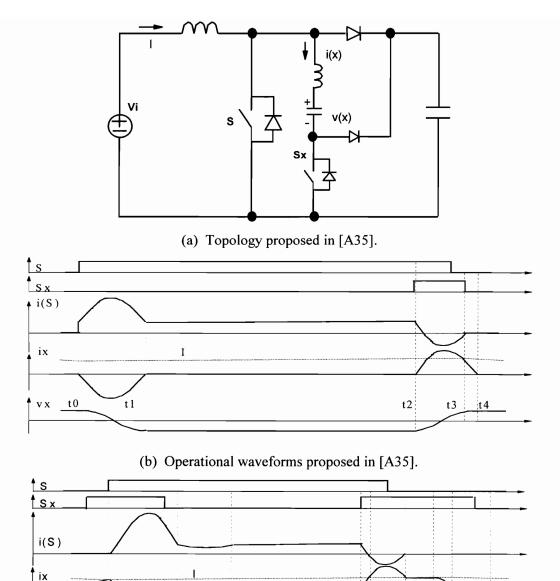

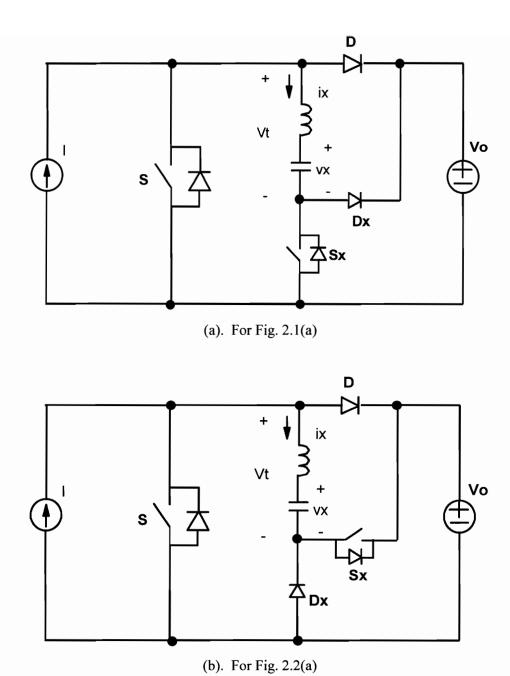

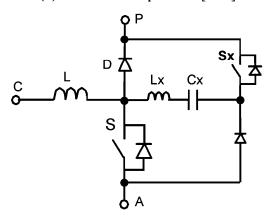

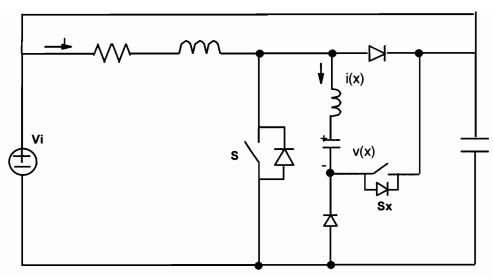

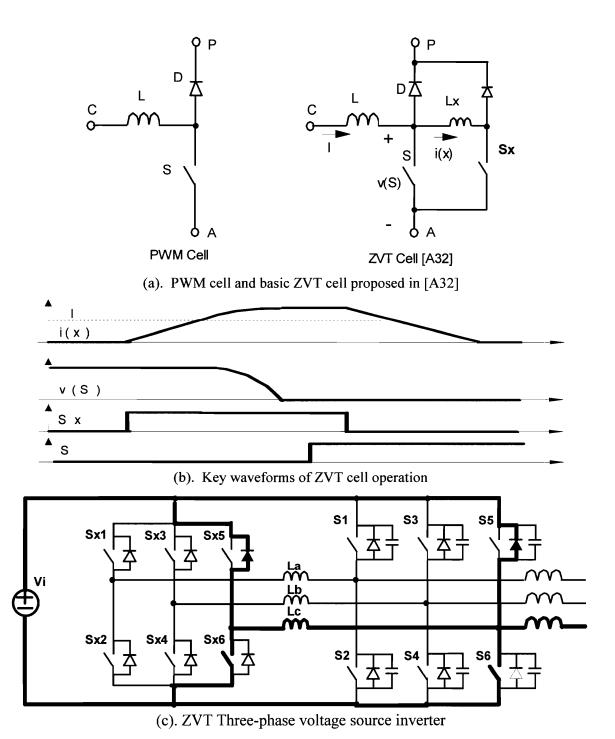

Power semiconductor switches in high power applications are subject to high switching stresses and switching losses. To alleviate these problems, significant derating of device voltage and current ratings and elaborate passive snubbers are usually used, and the switching frequency is limited to low-frequency ranges. Generally, a snubber circuit reduces the switching loss and switching stresses of the switches, but increases the total power loss in the converter. In recent years, various soft-switching techniques have been proposed to alleviate the switching loss and stress problems without resorting to bulky The effects of soft switching on power devices are and lossy passive snubbers. investigated in [A16]-[A25], which indicate significant performance improvements as well as cost, size, and weight reduction. A successful soft-switching scheme for highpower applications should reduce the switching losses, diode reverse recovery, and switching stress for all main and auxiliary switches without increasing the device voltage rating, because the device voltage margin is usually small, and the thermal management is very difficult. Most resonant converters, quasi-resonant converters, and multi-resonant converters are not suitable for high power applications due to the much increased voltage and current stresses. The recently developed zero-voltage transition (ZVT) [A32]-[A34], [A41] and zero-current transition (ZCT) [A35] PWM techniques incorporate the softswitching functions into PWM converters, so that the switching losses can be reduced with minimum voltage/current stresses and circulating energy. The ZCT technique significantly reduces the switch turn-off loss by forcing the switch current to zero prior to its turn-off. A ZCT boost converter proposed in [A35] is shown in Fig. 2.1(a), where the

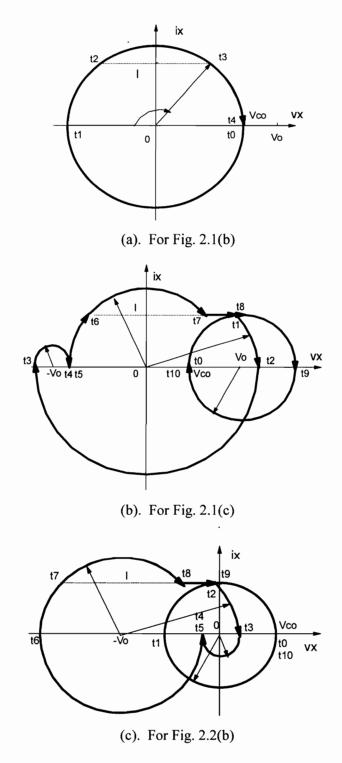

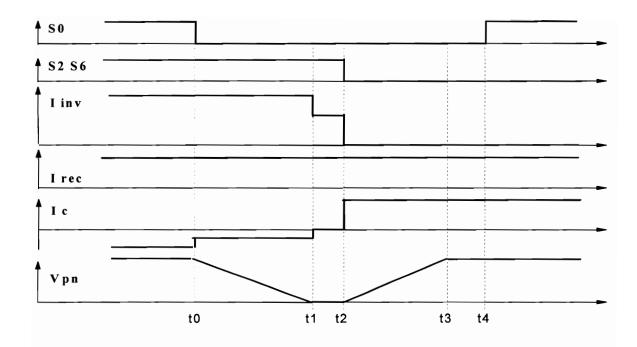

auxiliary circuit is shown within the dotted frame. The key waveforms of the circuit operation are shown in Fig. 2.1(b). As can be seen from Fig. 2.1(b), the current of the main switch is reduced to zero prior to its turn-off, so the switch turn-off loss is significantly reduced. However, the turn-on of the main switch is not affected by the auxiliary circuit, and severe diode reverse recovery causes high turn-on loss in the main switch. Moreover, the auxiliary switch turn-off current (at the moment  $t_3$ ) is the same as the inductor current I, i.e. the same as the main switch turn-off current in the hardswitched converter. Therefore, this scheme can achieve efficiency improvement only if Sx has a much lower turn-off loss than S (such as in the low-power and low-voltage applications, where MOSFETs with low turn-off loss can be used to implement the auxiliary switch). Additionally, power switch devices used in high-power applications, usually IGBTs, MCTs, and GTOs, have limited turn-off capability, so the auxiliary switch would often be of a similar size and cost as the main switch to turn off the required current. This ZCT scheme is not suitable for high-power applications. The current commutation techniques for SCR converters [A38] [A39] are not suitable for gate turnoff devices either, because they do not solve the diode reverse recovery problem, have high power loss in the auxiliary circuit, and some of them increase switch voltage stress or require switches to block negative voltage.

In this chapter, several new ZCT schemes are proposed to improve the ZCT technique in discussed in [A35]. With modified control and topology, all the main switches and the auxiliary switches are switched on and off under the zero-current condition, so the switching losses and stresses are reduced significantly. The zero-current switching of the auxiliary switches also allows the use of low-power rating device and low-conduction-loss devices, such as MCTs and IGBTs, in the auxiliary circuit. The soft switching schemes are discussed with the boost converter as an example, and are extended to other topologies through the concept of soft-switched PWM cells, since all PWM converters can be viewed as special connections of PWM cells.

(c) Waveforms with Proposed Modified Control.

**Existing ZCT PWM boost converter.** The main switch turn-on and auxiliary switch turn-off are in hard switching in (b). With a modified control, all switches can be switched under zero current, as shown in (c). However, the resonant current peak is much increased.

t5 t6

t8 t9

t10

t0 t1 t2

-Vo

t3

t4

# 2.2 IMPROVED ZERO-CURRENT-TRANSITION BOOST CONVERTER

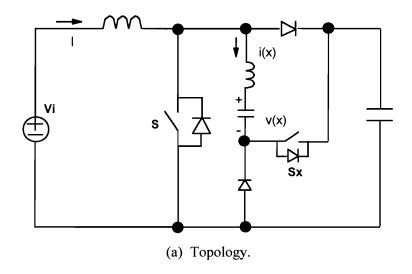

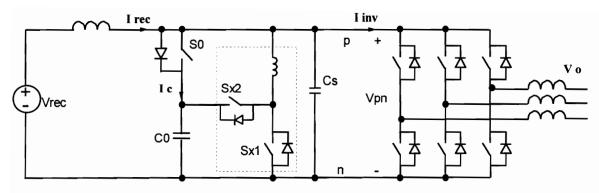

Up to now, all soft-switching PWM techniques reduce either the turn-on loss, or the turn-off loss of switches. ZVT techniques reduce or even eliminate the switch turn-on loss, and are attractive for devices with dominating turn-on loss, such as power MOSFETs. ZCT techniques reduce switch turn-off loss, and are more suitable for devices with dominating turn-off loss, such as GTOs. However, for the most widely used IGBTs, the distribution of the switching losses between turn-on and turn-off is devicedependent. Generally, turn-off loss is the dominating switching loss for low-voltage IGBTs. For high-voltage IGBTs, the switching loss distribution is more complex, and the turn-on loss is also significant due to the severe diode reverse recovery. Therefore, it would be of a great merit to develop a soft-switching scheme which could reduce both turn-on and turn-off losses, and thus could be effectively applied to different devices. This is especially important for very high power applications, where switching stress and loss are particularly annoying. The control of the ZCT topology shown in Fig. 2.1(a) can be modified to achieve this goal. The main switch turn-on current can be reduced to zero by the ZCT circuit, if the auxiliary switch is turned on before the main switch. Also, with a longer conduction time, the auxiliary switch current can be reduced to zero due to the resonance between Lx and Cx, so the auxiliary switch can be turned off under the zerocurrent condition also. Fig. 2.1(c) shows the key waveforms with this modified control. As can been seen, both the main switch and the auxiliary switch are turned on and off with zero current, so the switching losses of both switches can be reduced significantly. However, the current peak in the auxiliary circuit is very high, and causes high power loss. The current peak can be reduced by modifying the auxiliary circuit. The proposed new ZCT scheme is shown in Fig. 2.2(a). The modified auxiliary circuit, shown within the dotted frame, consists of resonant inductor Lx, resonant capacitor Cx, auxiliary switch Sx together with its anti-parallel diode Dx, and clamp diode Dc. This topology is similar to the one shown in Fig. 2.1(a), with a major difference only in the arrangement of the 2. Improved Zero-Current-Transition Converters for High Power Applications 19

auxiliary switch and clamp diode. However, as will be made clear later, the auxiliary circuit current peak of this topology is reduced, and the timing of the auxiliary switch is also much easier.

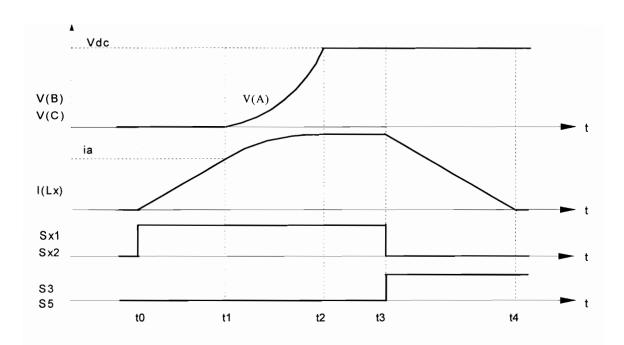

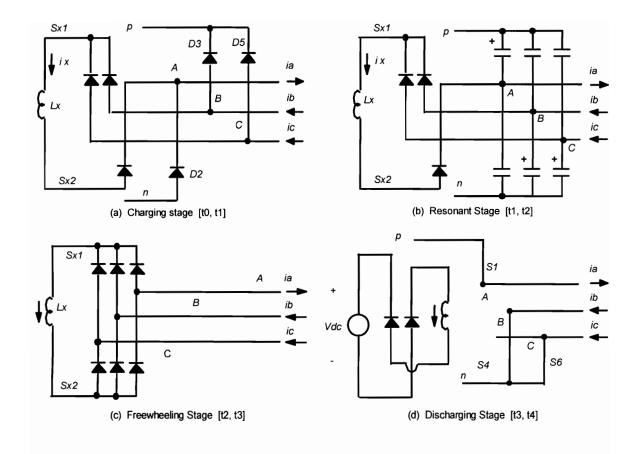

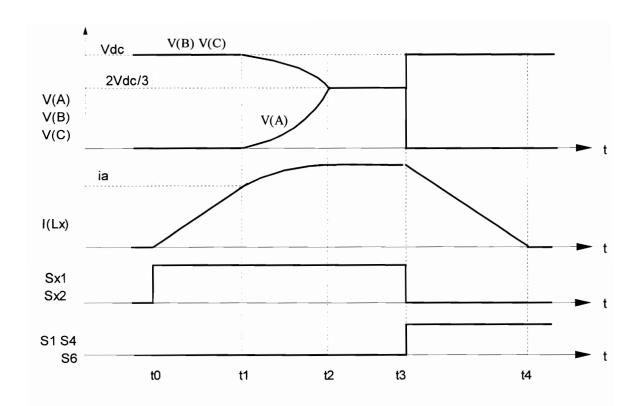

The operation of this converter is similar to its PWM counterpart's. The only difference is in the switch turn-on and turn-off transients, during which the auxiliary circuit is actuated to provide soft-switching conditions for the main switch S. The simulated waveforms during one switching period are shown in Fig. 2.2(b). During one switching period, the circuit goes through nine different stages, which are listed as (a) through (i) below, corresponding to the subtopologies in Fig. 2.3. The circuit parasitics, such as semiconductor junction capacitance and stray inductance, are included in the simulation but ignored in the following description. The operation description starts with switch turn-on transition. Before the main switch's turn-on, the inductor current I is conducted by the main diode, the auxiliary current I is zero, and I0 are assumed to be constant, due to the large capacitance and inductance involved.

- (a) Turn-On Transition I [t0, t2] At t0, Sx is turned on, starting the turn-on transition. The auxiliary resonant tank, consisting of Lx and Cx, begins to resonate. The auxiliary current ix resonates from zero to peak, and then decreases towards zero. When ix reaches zero at t1, the auxiliary circuit continues resonating, since the resonant capacitor voltage  $v_x$  is negative. Then, ix reverses its direction, and is conducted by Dx, the parallel diode of Sx. Afer this, Sx can be turned off under a zero-current and zero-voltage condition, with a much reduced power loss. As ix increases in positive value, the current of the main diode is diverted into the auxiliary circuit.

- (b) Turn-On Transition II [t2, t3] When ix reaches its positive peak at t2, the current in the main diode is reduced to zero. Then S is turned on under the zero-current condition at t2. The turn-on loss is reduced significantly, since the diode reverse recovery is basically eliminated, and the current rise rate of the switch after turn-on is limited by

(b) Operational waveforms.

**Figure 2.2 An improved ZCT PWM converter.** The auxiliary switch and auxiliary diode interchange their positions in Fig. 2.1(a). All switches are switched with zero current at both switch turn-on and turn-off, and the resonant current peak is lower than in Fig. 3.1(c).

Figure 2.3 Operating stages in the soft-switching commutation.

the resonant inductor. After t2, ix decreases rapidly towards zero, since now output voltage  $V_0$  is included in the resonant path.

- (c) Turn-On Transition III [t3, t4] At t3, ix returns to zero, and Dx is turned off naturally. Since the resonant capacitor voltage  $v_x$  is still positive, the auxiliary circuit continues resonating through the clamp diode Dc.

- (d) Switch-On Stage [t4, t5] When i<sub>x</sub> returns to zero again at t4, Dc is turned off naturally. The auxiliary circuit stops resonating, and is disconnected from the main circuit functionally. The converter resumes its PWM operation. The duration of this stage is determined by the PWM control.

- (e) Turn-Off Transition I [t5, t7] Before the main switch is turned off, Sx is turned on at t5. The resonant tank starts to resonate again. The resonant path includes Lx, Cx, and output voltage  $V_0$ . Current  $i_x$  is negative, with its magnitude increasing from zero to peak, and then decreasing. When  $i_x$  returns to zero at t6, Sx is turned off under the zero-current condition. Since the resonant capacitor voltage  $v_x$  is less than  $-V_0$  at t6, the auxiliary circuit continues resonating after t6, the positive  $i_x$  is conducted by Dx, and the current of the main switch is diverted out into the auxiliary circuit. Since Dx clamps the voltage of Sx at practically zero, the turn-off loss of Sx is largely eliminated.

- (f) Turn-Off Transition II [t7, t8] At t7,  $i_x$  reaches I, and the main switch current is reduced to zero, so S is turned off under a zero-current condition. As  $i_x$  keeps increasing after t7, the surplus current will flow through the antiparallel diode of S, and clamp the voltage across S at zero. The gate signal of S can be removed, without causing much turn-off loss.

- (g) Turn-Off Transition III [t8, t9] At t8,  $i_x$  falls to I, and the parallel diode of S stops conducting. Since the main diode is still reverse-biased, the main inductor current can only flow through the resonant tank, charging the resonant capacitor linearly.

- (h) Turn-Off Transition IV [t9, t10] At t9,  $v_x$  is discharged to zero, and the main diode starts to conduct. The resonant tank begins to resonate again. As  $i_x$  resonates towards zero, the current in the main diode increases gradually.

- (i) Diode On Stage [t10, ) When  $i_x$  returns to zero at t10, the auxiliary circuit stops resonating, and is disconnected from the main circuit functionally. The inductor current is conducted by the main diode, and the converter resumes its PWM operation. The duration of this stage is determined by the PWM control.

Ideally, the peak of  $i_x$  during the turn-on transition at t2 is the same as the input current I at t9 if the resonant circuit has no power loss. Any power loss in the resonant path will reduce the attainable resonant current peak at t2. However, I is actually smaller at t2 than at t9, considering the current ripple due to finite boost inductance. Therefore, the zero-current turn-on of the main switch is still achievable in a practical circuit. After the turn-on, the current increase rate is controlled by the resonant inductor, and this fact helps to reduce the switch turn-on loss further.

Another point to notice is that the auxiliary switch is always turned on and off with zero current, and thus has very low switching loss and stress. This fact allows devices with much lower current rating than the main switch to be used in the auxiliary circuit.

#### 2.3 STATE-PLANE ANALYSIS OF ZCT OPERATION

The operation of the ZCT topology involves an LC resonant tank, and needs a detailed analysis. Since the current of the boost inductor, I, and the voltage of the output capacitor,  $V_0$ , can be assumed constant during the short period when the auxiliary circuit is active, the high-frequency equivalent circuits of Fig. 2.1(a) and Fig. 2.2(a) are shown in Figs. 2.4(a) and (b), respectively. The resonant inductor current  $i_x$  and the resonant capacitor voltage  $v_x$  are chosen as state variables. Assuming all the components to be ideal, the governing differential equations for the resonant tank are:

$$\frac{di_x}{dt} = -\frac{1}{Lx}v_x + \frac{1}{Lx}V_t$$

$$\frac{dv_x}{dt} = \frac{1}{Cx}i_x$$

(2.1)

where  $V_t$  is the voltage across the resonant tank, and serves as the excitation to the resonant tank.  $V_t$  changes with the different operating stages of the power stage. For the operating stages shown in Fig. 2.3, in the intervals of [t0, t2], [t3, t4], and [t9, t10],  $V_t = 0$ ; in the intervals of [t2, t3], [t5, t7], [t7, t8],  $V_t = -V_o$ . In the intervals when the resonant tank is in series with the input current source,  $i_x$  is no longer a state variable, and the second equation in (2.1) alone determines the circuit behavior. In the intervals of [t4, t5] and after t10 until the switch turn-on in the next switching cycle, the resonant tank is functionally disconnected from the rest of the circuit, and  $i_x = 0$ . In the interval of [t8, t9],  $i_x = I$ . In a period of  $[t_k, t_{k+1}]$  in which  $V_t$  is constant and the LC tank is active, with the initial condition of  $v_x(t_k) = V_{xk}$  and  $i_x(t_k) = I_{xk}$ , the solution to the above equations are:

$$v_{x}(t) = Z_{o}I_{xk}\sin(\omega_{o}(t - t_{k})) + (V_{xk} - V_{t})\cos(\omega_{o}(t - t_{k})) + V_{t}$$

$$i_{x}(t) = I_{xk}\cos(\omega_{o}(t - t_{k})) - \frac{V_{xk} - V_{t}}{Z_{o}}\sin(\omega_{o}(t - t_{k}))$$

(2.2)

Figure 2.4 High-frequency equivalent circuits of ZCT boost converters. The input inductor can be treated as a current source, and the output capacitor can be treated as a voltage source in the soft-switching transition.

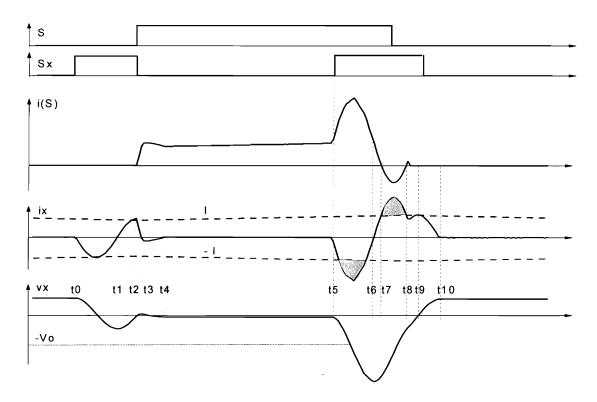

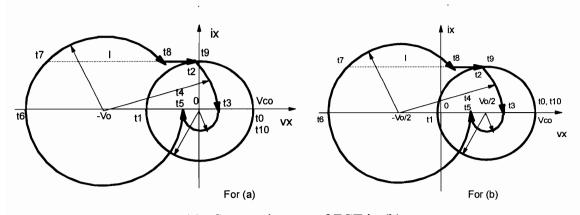

The above solution can be used to draw the state-plane trajectories of the ZCT circuit in ix - vx plane, which are more convenient to illustrate the circuit operation than waveforms [A27]. The state plane trajectories for the ZCT schemes discussed before are shown in Fig. 2.5, which clearly illustrates the functional differences among the three The time instants (t0, t1, t2, ...) in Figs. 2.5(a), 2.5(b) and 2.5(c) ZCT schemes. correspond to the time instants shown in Figs. 2.1(b), 2.1(c) and 2.2(b). The main switch or the main diode current is determined by  $I - i_x$ . The current is conducted by the parallel diode of the main switch when  $I - i_x$  is negative. During the resonance, the state plane trajectory is part of a circle, and the radius of the circle determines the resonant tank energy and its associated conduction loss in the auxiliary circuit. Fig. 2.5(a) shows the previous ZCT operation of Figs. 2.1(a) and (b). Obviously, the reverse recovery of the main diode and the turn-on of the main switch are not affected by the ZCT circuit, and could produce high power loss in a practical circuit. The turn-off current of the auxiliary switch is I, which is the same as the turn-off current of the main switch in a hardswitching converter. Besides, the timing of the auxiliary switch directly determines the auxiliary circuit current peak, and is critical to the circuit operation. The state-plane trajectories of the ZCT topology shown in Fig. 2.1(a) with the modified control in Fig. 2.1(c) are shown in Fig. 2.5(b). All devices are now turned on and off with zero current, but the resonant circle is much larger. Besides, the timing of the auxiliary switch is still critical. The operation of the improved ZCT circuit, shown in Fig. 2.5(c), has a smaller resonant circle, so less resonant tank energy and less power loss are required. In addition, the auxiliary switch can always be turned off after being turned on for half the resonant cycle of  $T_0 = 2\pi \sqrt{L_x C_x}$ , so its control timing is independent of the circuit operation. This property significantly simplifies the control design.

One distinctive advantage of these ZCT topologies is that all switch devices are switched under the zero-current condition. Therefore, switching losses are reduced to a large degree, so a better utilization of switches can be achieved at high switching

Figure 2.5 Comparison of state-plane trajectories. (c) has a smaller circle in the turn-off than (b), which means less energy and power loss in the auxiliary circuit.

frequencies. In addition, snubber circuits for di/dt and dv/dt limitations used in hard-switching converters are no longer required, and gate drive circuits can be simplified. These factors are especially significant for GTOs, whose snubber and gate drive circuits take a large portion of converter power loss and cost. The auxiliary switch has almost no switching loss and switching stress either, since it is turned on and turned off always with a zero-current condition. Low conduction voltage drop devices, such as GTOs, MCTs and IGBTs, can be used in the auxiliary circuit to reduce its conduction loss.

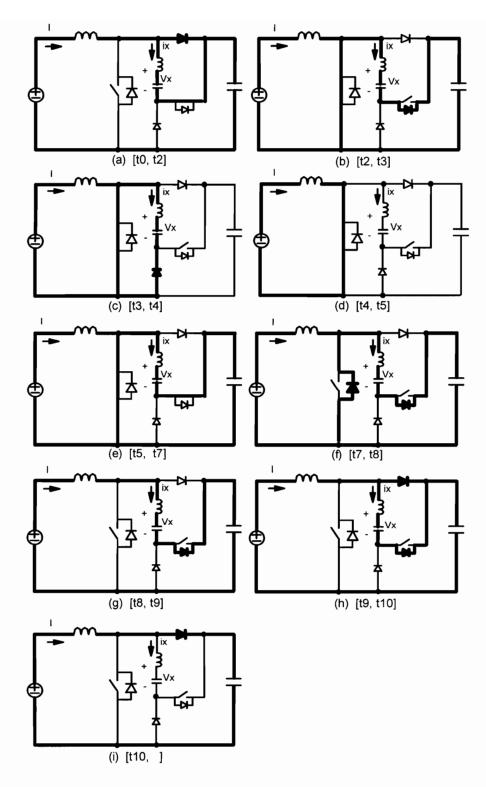

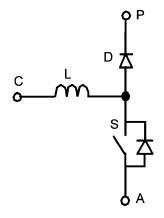

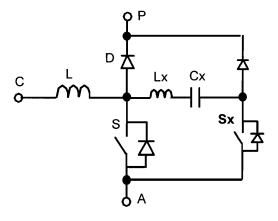

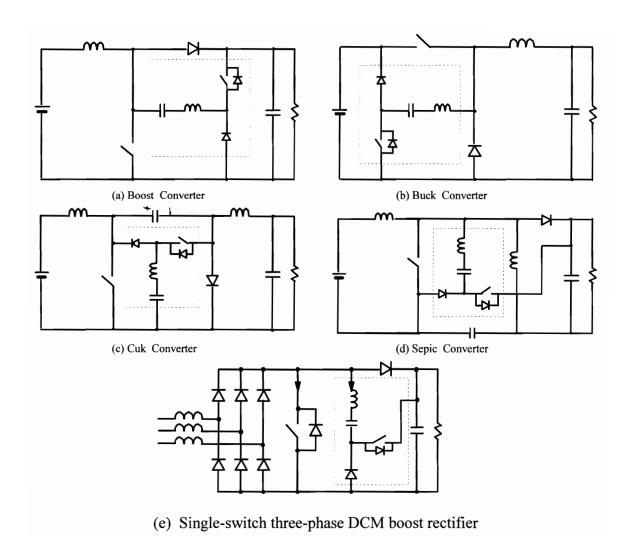

### 2.4 EXTENSION OF IMPROVED ZCT SCHEMES TO OTHER CONVERTERS

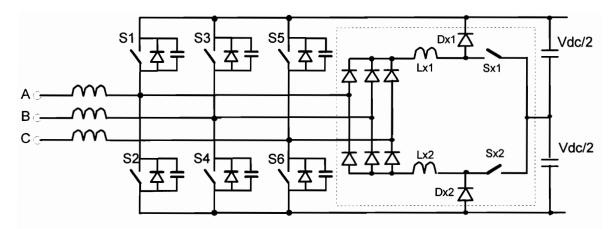

The proposed ZCT schemes achieve a similar switching loss reduction of resonant converters in PWM converters without increasing the voltage/current stress of switches, and are therefore suitable for high power applications. It is well known that any PWM converter can be viewed as special connections of the PWM cells, each consisting of a switch and a diode connected in a totem pole fashion, such as S and D in Figs. 2.1(a) and 2.2(a). The ZCT topologies in Figs. 2.2(a) and 2.5(a) can be used as ZCT cells to derive soft-switching converters in other topologies. The PWM cell and ZCT cells are illustrated in Fig. 2.6. By replacing every PWM cells in PWM converters with a ZCT cell, different ZCT converters can be easily derived. Several examples of dc-dc converters with the ZCT scheme presented in Fig. 2.2(a) are shown in Figs. 2.7(a) through (d). For some single-switch three-phase rectifiers, such as the DCM (discontinuous current mode) boost rectifier, this ZCT scheme can be directly applied to the PWM cell also, as is shown in Fig. 2.7(e). Since the switch turn-on loss is negligible in DCM converters, the auxiliary switch can be actuated only for switch turn-off commutation. In this case, the performance of the ZCT cell in Fig. 2.6(b) would be the same as the one shown in Fig. 2.6(c).