### Impact of Device Parametric Tolerances on Current Sharing Behavior of a SiC Half-Bridge Power Module

Grace R. Watt

Thesis submitted to the faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

Master of Science In Electrical Engineering

Rolando Burgos, Chair Khai D. Ngo Guo-Quan Lu Christina M. DiMarino

December 9, 2019 Blacksburg, Virginia

*Keywords:* SiC MOSFET, power module packaging, flexible PCB, current sharing, symmetrical direct bonded copper (DBC) layout, diode-less module, multi-chip module, device parametric tolerances, package parasitics, vertical GaN

Copyright 2019, Grace R. Watt

## Impact of Device Parametric Tolerances on Current Sharing Behavior of a SiC Half-Bridge Power Module

#### Grace R. Watt

This paper describes the design, fabrication, and testing of a 1.2 kV, 6.5 m $\Omega$ , half-bridge, SiC MOSFET power module to evaluate the impact of parametric device tolerances on electrical and thermal performance. Paralleling power devices increases current handling capability for the same bus voltage. However, inherent parametric differences among dies leads to unbalanced current sharing causing overstress and overheating. In this design, a symmetrical DBC layout is utilized to balance parasitic inductances in the current pathways of paralleled dies to isolate the impact of parametric tolerances. In addition, the paper investigates the benefits of flexible PCB in place of wire bonds for the gate loop interconnection to reduce and minimize the gate loop inductance. The balanced modules have dies with similar threshold voltages while the unbalanced modules have dies with unbalanced threshold voltages to force unbalanced current sharing. The modules were placed into a clamped inductive DPT and a continuous, boost converter. Rogowski coils looped under the wire bonds of the bottom switch dies to observe current behavior. Four modules performed continuously for least 10 minutes at 200 V, 37.6 A input, at 30 kHz with 50% duty cycle. The modules could not perform for multiple minutes at 250 V with 47.7 A (23 A/die). The energy loss differential for a ~17% difference in threshold voltage ranged from 4.52% (~10 μJ) to -30.9% (~30  $\mu$ J). The energy loss differential for a~0.5% difference in  $V_{th}$  ranged from -2.26%  $(\sim 8 \mu J)$  to 5.66%  $(\sim 10 \mu J)$ . The loss differential was dependent on whether current unbalance due to on-state resistance compensated current unbalance due to threshold voltage. While device parametric tolerances are inherent, if the higher threshold voltage devices can be paired with devices that have higher on-state resistance, the overall loss differential may perform similarly to well-matched dies. Lastly, the most consistently performing unbalanced module with 17.7% difference in  $V_{th}$  had 119.9  $\mu$ J more energy loss and was 22.2°C hotter during continuous testing than the most consistently performing balanced module with 0.6% difference in  $V_{th}$ .

# Impact of Device Parametric Tolerances on Current Sharing Behavior of a SiC Half-Bridge Power Module

#### Grace R. Watt

#### GENERAL AUDIENCE ABSTRACT

This paper describes the design, construction, and testing of advanced power devices for use in electric vehicles. Power devices are necessary to supply electricity to different parts of the vehicle; for example, energy is stored in a battery as direct current (DC) power, but the motor requires alternating current (AC) power. Therefore, power electronics can alter the energy to be delivered as DC or AC. In order to carry more power, multiple devices can be used together just as 10 people can carry more weight than 1 person. However, because the devices are not perfect, there can be slight differences in the performance of one device to another. One device may have to carry more current than another device which could cause failure earlier than intended. In this research project, multiple power devices were placed into a package, or "module." In a control module, the devices were selected with similar properties to one another. In an experimental module, the devices were selected with properties very different from one another. It was determined that the when the devices were 17.7% difference, there was 119.9 µJ more energy loss and it was 22.2°C hotter than when the difference was only 0.6%. However, the severity of the difference was dependent on how multiple device characteristics interacted with one another. It may be possible to compensate some of the impact of device differences in one characteristic with opposing differences in another device characteristic.

#### Acknowledgements

I would firstly like to acknowledge the financial support provided by the U.S. Department of Energy Advanced Manufacturing Office through the Wide Bandgap Generation (WBGen) Fellowship at the Center for Power Electronics Systems (CPES) at Virginia Tech (<a href="http://www.eng.vt.edu/WBGen">http://www.eng.vt.edu/WBGen</a>).

The team at General Motors, specifically Marko Jaksic and Mehrdad Teimor, were incredibly supportive and knowledgeable throughout my project. I want to acknowledge the support of General Motors and the Department of Energy, Office of Energy Efficiency and Renewable Energy (EERE), under award number DE-EE0007285, Highly Integrated Wide Bandgap Power Module for Next Generation Plug-in Vehicles.

Thank you to Dr. Rolando Burgos for his guidance in my research and navigating graduate studies. I was always grateful for the perspective he has gained from extensive experience on various power electronics projects which honed the questions I asked in research and the directions I took. Thank you to Dr. Lu and his students, Chao Ding, Langbing Lui, and Shengchang Lu. They provided invaluable expertise and recommendations for use of the sintering paste and other materials in my module. Thank you for Dr. Christina DiMarino for her expertise on packaging. It is exciting to see packaging research growing at CPES and I look forward to the contributions her team will enable. Thank you for Dr. Ngo for his research questions and guidance while I was a student at CPES. He took the time to care about my research and my life, even sharing peppers with me and offering bitter melon which I could not handle.

Significant gratitude goes to Slavko Mocevic, Amy Romero, and Joe Kozak who mentored me in my research and in graduate life. Slavko spent many hours with me going over my test setups and results and discussing theory. While I might have appreciated some sugar-coated feedback at times, his honesty and willingness to ask the difficult questions was invaluable. When I could not 100% understand my setup, normally something would break as he warned. When he reminded me of the progress I was making, I gained the confidence I needed to keep going. Thank you to Joe for all our complex conversations related to work culture, friends and relationships, religion,

or other topics in which we both enjoyed going deeper. Joe cares deeply for people and I was immensely grateful for his willingness to do the work to make graduate life increasingly better.

I cannot say enough about Emma Raszmann and how critical her friendship is to me as both a researcher and young professional. She provided patience and a lack of judgment with me that was necessary when I had doubts and questions in the research, duh. She also spent hours with me discussing life and the joys and grief it brought us whether over a drink at Cabo Fish Taco or coffee or soccer. I am thrilled for wherever her path will lead.

Special thanks to Shengchang for his willingness to enjoy Disneyland and go back for fireworks! Thanks to David Nam and Tianyu Zhao who were part of the "packaging team," as we lamented the challenges of packaging that others did not understand. We also enjoyed fun times together in our packaging team gathering complete with karaoke and delicious food.

I also want to thank many friends from CPES including Shuo, Bo, Tianyu, Sizhan, Bo Wen, Jianghui and Ye, David, Josh, Lee, John, Michael, Cong and Jiewen, Ibrahim and Danny, Daniel, Vladamir, even Chris and too many others to name.

Thank you to Genesis Alvarez who was a roommate and friend beginning during recruitment weekend and through graduation. We shared so many important moments both when school and life were so difficult and when we were having breakthroughs. I will miss our movie nights and talks and cooking and crying and laughing. We really did so much together whether it was talking about faith or playing soccer, you were dear to me. Also thank you to Sherin Abraham who joined Gen and I in our 2<sup>nd</sup> year. She ended up being such a great addition to the apartment with her laughter, energy, and conversation. She has a kind and strong heart and she is going to go far! I feel like I learned so much about life from Sherin and am excited for where God takes her.

I must acknowledge Gravitate and BCF for their role in my life while at Blacksburg. Each Thursday was a highlight of my week; laughing and digging in deep into scripture, sharing a meal and checking in on everyone, and having a community that cared deeply and understood me deeply. Christine and Russell also went above and beyond in their care for me and I will, beautifully, never be able to repay them. Thank you to Angela and Meredith for weekly meetings and all the ladies for the joy you gave me which I really cannot express.

Thank you to Na, Trish, Marianne, Audri, Yan, Teresa, David, and Linda who care so genuinely and thoroughly for us. These people brought joy to me whenever I was upstairs or when we had meals together. I would have gone barefoot at my wedding without Trish. Na, Elianne, and Annabelle as well as Dad and Grandma were like a family away from home even though we were only friends for half the time I was there. You invited me into your home and lives, and I know God has amazing plans for your family.

To LAIGSA and SHPE, especially the executive board for LAIGSA, you all were friends and co-workers in a community that was dear to me. I learned so much from working with you about how to run an organization and care for graduate students. Whether we were setting up for salsa, the holiday party, or many of our tailgates, I found our time together to be a refuge. The soccer teams mattered to me and I felt so incredibly honored to join our team.

Lastly, and perhaps most important, I must thank Jesus and my family and dearest friends. Without you, I would have curled up into a permanent cry ball the first semester. While it was difficult, the lessons I learned and love that carried me through have changed my life. I hope you can know how much your support means. Kyle, I love you and you are a patient, patient boyfriend, fiancé, and now husband.

## Contents

| Chapte | r 1   | Introduction                                                    | 1  |

|--------|-------|-----------------------------------------------------------------|----|

| 1.1    | Elec  | etric Vehicles                                                  | 1  |

| 1.2    | Pow   | ver Electronics for Electric Vehicles                           | 4  |

|        | 1.2.1 | Semiconductors                                                  | 4  |

|        | 1.2.2 | Wide Band Gap Power Semiconductor Devices                       | 6  |

|        | 1.2.3 | Quasistatic Behavior of MOSFETs                                 | 8  |

|        | 1.2.4 | Dynamic Behavior of MOSFETs                                     | 11 |

| 1.3    | Mul   | ti-Chip Power Module Packaging                                  | 21 |

| 1.4    | Res   | earch Motivations and Objectives                                | 23 |

|        | 1.4.1 | Device Parametric Tolerances                                    | 25 |

|        | 1.4.2 | Package Parasitics                                              | 29 |

|        | 1.4.3 | Objective                                                       | 33 |

| Chapte | r 2   | Design of a Balanced Power Module for Automotive Applications   | 36 |

| 2.1    | Intro | oduction                                                        | 36 |

| 2.2    | Surv  | vey of Power Module Packaging Techniques and Limitations        | 36 |

| 2.3    | Mod   | lule Design                                                     | 38 |

| 7      | 2.3.1 | Symmetrical/Balanced DBC Pattern and Current Sharing Simulation | 38 |

|        | 2.3.2 | Die Placement based on Threshold Voltage                        | 40 |

|        | 2.3.3 | Flexible PCB for Gate Connection                                | 46 |

| 2      | 2.3.4 | Use of the Body Diode in SiC MOSFET                             | 50 |

| Chapte | r 3   | Power Module Fabrication                                        | 52 |

| 3.1    | Pacl  | kage Material Selection                                         | 52 |

| 3      | 3.1.1 | Substrate Selection                                             | 53 |

| 3      | 3.1.2 | Attachment Selection                                            | 53 |

| 3      | 3.1.3 | Housing and Encapsulant Selection                               | 55 |

| 3.2    | Mod   | lule Fabrication                                                | 55 |

| 3      | 3.2.1 | Substrate Patterning and Cutting                                | 55 |

| 3.2.2     | Attachment Material Heat Profiles               | 57   |

|-----------|-------------------------------------------------|------|

| 3.2.3     | Die Attachment                                  | 58   |

| 3.2.4     | Die Interconnection                             | 61   |

| 3.2.5     | Flexible PCB Attachment                         | 64   |

| 3.2.6     | Power Terminals                                 | 70   |

| 3.2.7     | Thermal Management                              | 73   |

| 3.2.8     | Housing and Encapsulant                         | 75   |

| 3.2.9     | Summary of Fabricated Module Yield              | 80   |

| Chapter 4 | Power Module Characterization                   | 82   |

| 4.1 Stati | c Characterization                              | 82   |

| 4.1.1     | Introduction                                    | 82   |

| 4.1.2     | Static Results                                  | 83   |

| 4.2 Dyn   | amic Characterization                           | 87   |

| 4.2.1     | Introduction                                    | 87   |

| 4.2.2     | Gate Driver Design                              | 89   |

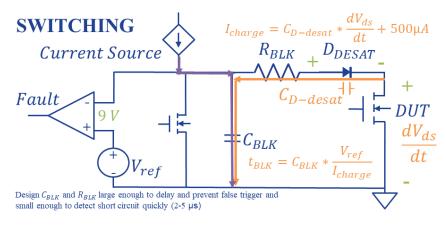

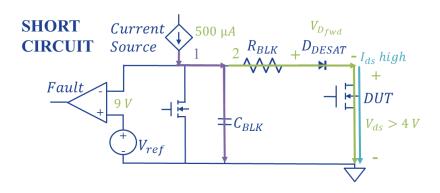

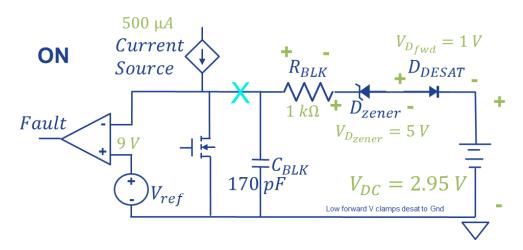

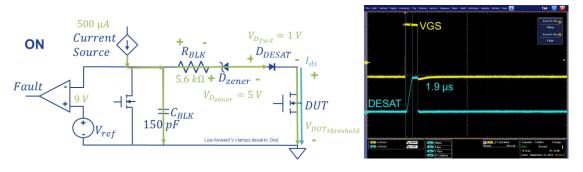

| 4.2.3     | Desaturation Circuit for Overcurrent Protection | 91   |

| 4.2.4     | Tuning the Desaturation Circuit                 | 95   |

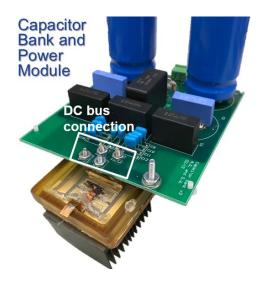

| 4.2.5     | Capacitor Bank                                  | 98   |

| 4.2.6     | Low Voltage Switching Test Results              | 100  |

| 4.2.7     | 600 V Switching Test Results                    | 103  |

| Chapter 5 | Power Module Thermal Testing                    | 113  |

| 5.1 Intro | oduction                                        | 113  |

| 5.1.1     | Heat Removal and Thermal Resistance Estimation  | 114  |

| 5.1.2     | Junction Temperature Estimation                 | 117  |

| 5.2 Con   | tinuous Test Setup                              | 123  |

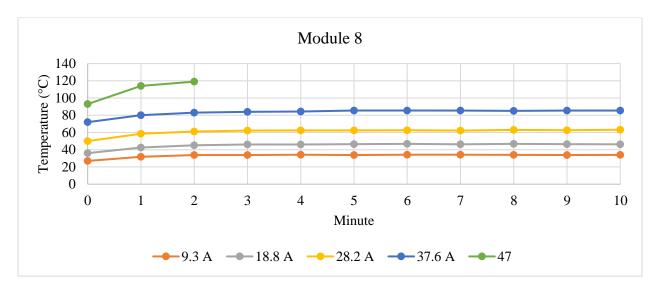

| 5.3 Con   | tinuous Test Results                            | 125  |

| 5.4 Con   | tinuous Thermal Test Results                    | 135  |

| Chantar 6 | Conclusion                                      | 1/13 |

| Appendix A      | Evaluation of an Automated Modeling Tool Applied to New 600 V, 2 A Vert | ical |

|-----------------|-------------------------------------------------------------------------|------|

| Gallium Nitride | e (GaN) Transistors                                                     | 148  |

| Bibliography    |                                                                         | 166  |

## List of Figures

| Figure 1-1. Passenger electric car stock globally from Fig. 1.1 of Global EV Outlook 2019 [7] |

|-----------------------------------------------------------------------------------------------|

|                                                                                               |

| Figure 1-2. Outlook for EV growth from EV30@30 Scenario Fig. 2 Global EV Outlook [7] 2        |

| Figure 1-3. Influence of charging option on customer purchase of EVs [2]                      |

| Figure 1-4. Block diagram of an electric vehicle powertrain [2]                               |

| Figure 1-5. Energy bandgaps of different types of materials                                   |

| Figure 1-6. Material properties comparison of Si, SiC, and GaN                                |

| Figure 1-7. Device capacitance definitions                                                    |

| Figure 1-8. Step-by-step walkthrough of the gate charge plot                                  |

| Figure 1-9. Ideal turn-on and turn-off waveforms for a MOSFET [18]                            |

| Figure 1-10. Impact of input capacitance on turn-on delay                                     |

| Figure 1-11. Rise of the drain current as the transistor turns on                             |

| Figure. 1-12. Miller plateau as the transistor turns on                                       |

| Figure. 1-13. Final behavior as the transistor turns on                                       |

| Figure. 1-14. Turn-off delay as the gate source bias drops                                    |

| Figure. 1-15. Miller plateau as the transistor turns off                                      |

| Figure. 1-16. Fall of the drain current as the transistor turns off                           |

| Figure 1-17. Final reduction of gate-source bias as transistor turns off                      |

| Figure 1-18. Functions of a power module package with an example of a commerical power        |

| nodule (CREE CAS120M12BM2)22                                                                  |

| Figure 1-19. A power module package and chip are analogous to the human body and brain [30]                  |

|--------------------------------------------------------------------------------------------------------------|

| 31]                                                                                                          |

| Figure 1-20. Increased current carrying capacity with paralleled dies                                        |

| Figure 1-21. Device parametric tolerances can lead to unbalanced current sharing                             |

| Figure 1-22. Package parasitics can lead to unbalanced current sharing                                       |

| Figure 1-23. Simulation of static and dynamic unbalanced current sharing                                     |

| Figure 1-24. Impact of unbalanced threshold voltages on a) turn-on and b) turn-off behavior o                |

| discrete SiC MOSFETs [20]                                                                                    |

| Figure 1-25. Impact of unbalanced on-state resistance on a) turn-on, b) turn-off, and c) on-state            |

| behavior of discrete SiC MOSFETs [20]                                                                        |

| Figure 1-26. Thermal impact of unbalanced current sharing in discrete SiC MOSFET device                      |

|                                                                                                              |

| Figure 1-27. a) Multi-chip half-bride power module with assymetrical pathway impedance fo                    |

| paralleled dies where $L_{C4}>L_{C3}>L_{C2}>L_{C1}$ and b) Improved current sharing after adjusting the wire |

| bonds [34]                                                                                                   |

| Figure 1-28. Impact of switching loop stray inductance mismatch on a) turn-on and b) turn-of                 |

| behavior of discrete SiC MOSFETs [20]                                                                        |

| Figure 1-29. Impact of common source stray inductance mismatch on a) turn-on and b) turn-of                  |

| behavior of discrete SiC MOSFETs [20]                                                                        |

| Figure 1-30. Addition of auxiliary source connection reduced dynamic current imbalance from                  |

| a) to c) during turn-on and from b) to d) during turn-off [20]                                               |

| Figure 1-31. Thermal comparison of a module with unbalanced and balanced parasitic              |

|-------------------------------------------------------------------------------------------------|

| inductances [37]                                                                                |

| Figure 1-32. Symmetrical DBC layout with DC- trace wraparound                                   |

| Figure 1-33. Fabricated 1.2 kV, 6.5 m $\Omega$ SiC half-bridge power module                     |

| Figure 2-1. Symmetrical DBC layout for symmetrical parasitic inductance in the current          |

| pathway                                                                                         |

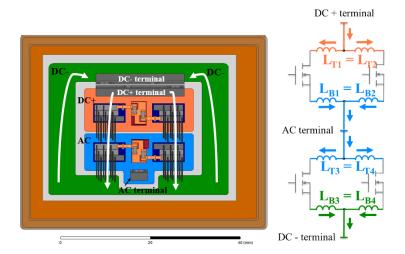

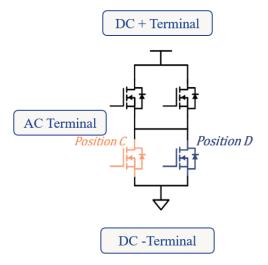

| Figure 2-2. Dies in Position C and D in parallel act as the bottom side switching device 39     |

| Figure 2-3. Simulation of the current sharing characteristics for a symmetrical and non-        |

| symmetrical design                                                                              |

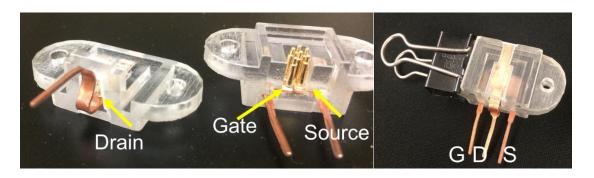

| Figure 2-4. 3-terminal test fixture for characterizing bare die                                 |

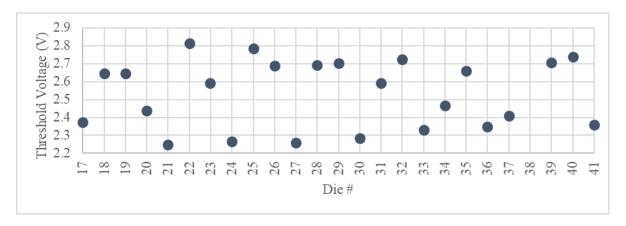

| Figure 2-5. Threshold voltages of bare dies measured with the Keysight B1505a curve tracer      |

| 41                                                                                              |

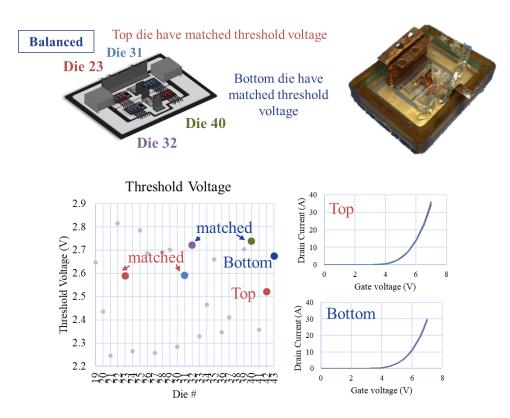

| Figure 2-6. Die selection for a balanced power module (4) based on threshold voltages 42        |

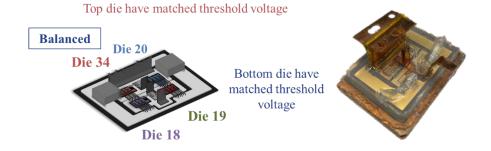

| Figure 2-7. Die selection for a balanced power module (6) based on threshold voltages 43        |

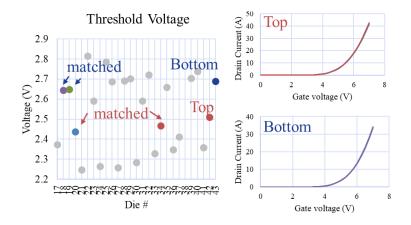

| Figure 2-8. Die selection for a unbalanced power module (8) based on threshold voltages 43      |

| Figure 2-9. Die selection for a unbalanced power module (9) based on threshold voltages 44      |

| Figure 2-10. On-state resistance measurements of a subset of the CREE dies; high resistance     |

| due to the wires and pins of the test fixture                                                   |

| Figure 2-11. Resistances of bare die across multiple tests repeated with the same parameters 45 |

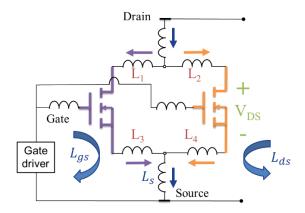

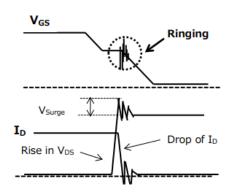

| Figure 2-12. With a shared source inductance, gate and power loops are coupled and Lgs is       |

| large 46                                                                                        |

| Figure 2-13. Voltage surge in $V_{ds}$ and gate inductance can cause gate ringing which may lead  |

|---------------------------------------------------------------------------------------------------|

| to unintentional turn on and turn off [55]                                                        |

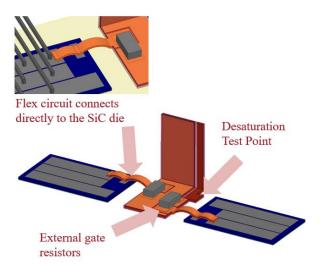

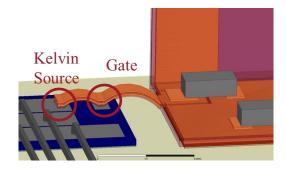

| Figure 2-14. Connection of flexible PCB to die and substrate                                      |

| Figure 2-15. Overlap of kelvin source and gate planes reduces loop inductance                     |

| Figure 2-16. Comparison of flexible PCB and wire bond inductances simulated in Ansys Q3D          |

|                                                                                                   |

| Figure 2-17. Adding kelvin source connection decouples the gate and power loops and reduces       |

| Lgs                                                                                               |

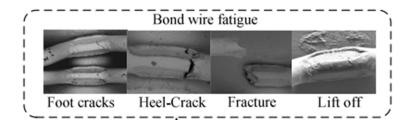

| Figure 2-18. Wire bond failure mechanisms [58]                                                    |

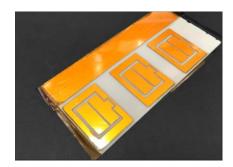

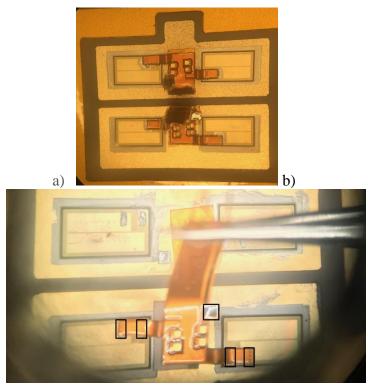

| Figure 2-19. a) Top view of the flexible PCB from Altium designer, b) bottom view of the          |

| fabricated flexible PCB, and c) substrate with dies displaying connection points for flexible PCB |

|                                                                                                   |

| Figure 3-1. Elements of a package                                                                 |

| Figure 3-2. Partially etched DBC pattern with ferric chloride etching machine                     |

| Figure 3-3. Patterned substrate after etching of unwanted metal using a Kapton tape mask 56       |

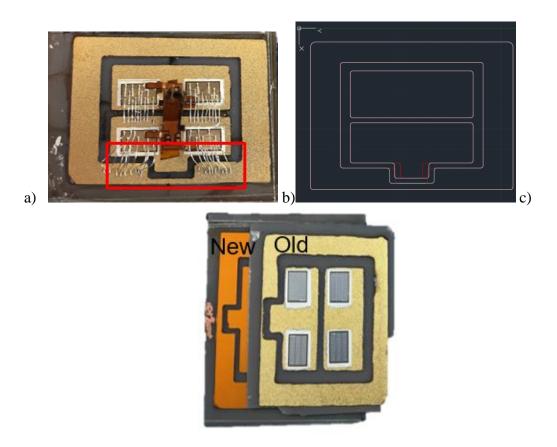

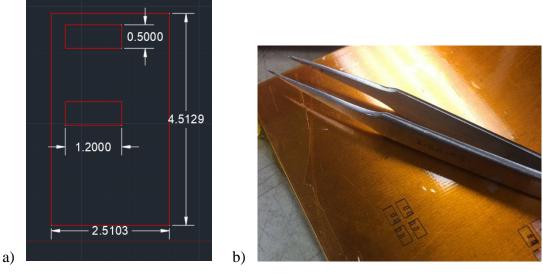

| Figure 3-4. Undesirable bend in bottom device wires b. new design (white) vs old design (red)     |

| c. New vs old substrate pattern                                                                   |

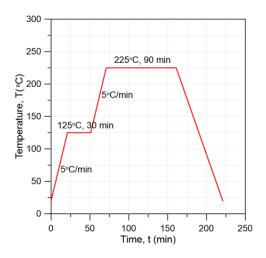

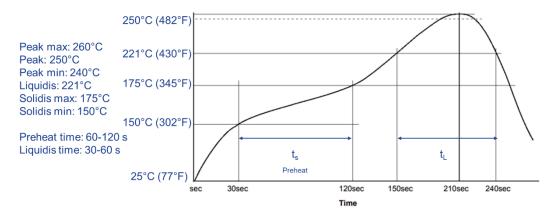

| Figure 3-5. Heat profile for Kyocera nanosilver paste sintered under P=0                          |

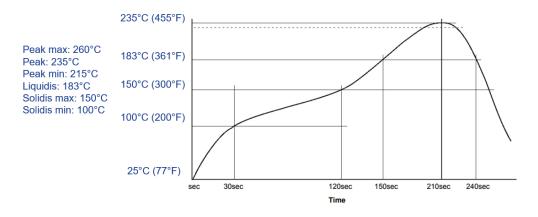

| Figure 3-6. Heat profile for Sn96.3/Ag3.7 [69, 70]                                                |

| Figure 3-7. Heat profile for Sn63/Pb37 [71]                                                       |

| Figure 3-8. Laser-cut Kapton mask placed on DBC substrate                                         |

| Figure 3-9. Sinter paste printed into Kapton mask                                                 |

| Figure 3-10. Dies are placed onto printed sinter paste squares and Kapton mask is removed 60        |

|-----------------------------------------------------------------------------------------------------|

| Figure 3-11. Substrate placed onto programmable hotplate                                            |

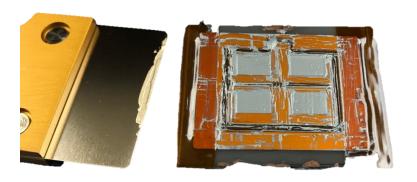

| Figure 3-12. Die shear test with the Nordson DAGE 4000 Multipurpose Bondtester 61                   |

| Figure 3-13. Sheared die with bottom side coated in cured nanosilver sinter paste                   |

| Figure 3-14. tpt HB30 Heavy Wire Bonder                                                             |

| Figure 3-15. 8 cascaded wire bonds per die                                                          |

| Figure 3-16. Wire bonds tall enough to fit Rogowski coil loops underneath                           |

| Figure 3-17. Microscopic view of the pull test                                                      |

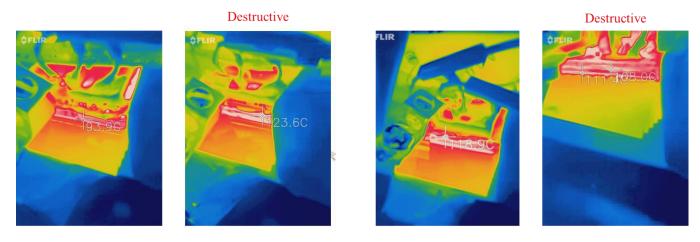

| Figure 3-18. Destructive wire pull test results                                                     |

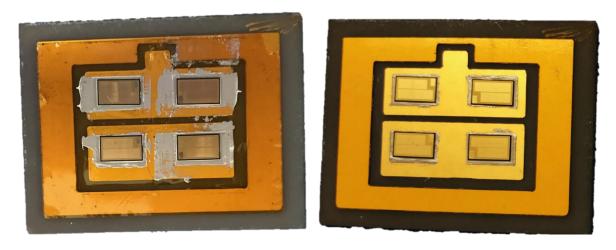

| Figure 3-19. Connections with sinter method                                                         |

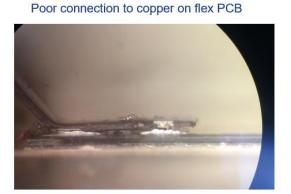

| Figure 3-20. Microscopic image of sinter paste not adhering to aluminum surface of die 65           |

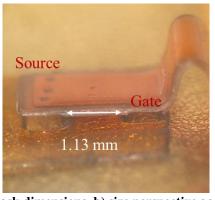

| Figure 3-21. Die with nickel:gold topcoat and space around the gate terminal                        |

| Figure 3-22. a) Laser-cut Kapton mask dimensions, b) size perspective against tweezers, and c)      |

| only 1.13 mm between gate and source of the die                                                     |

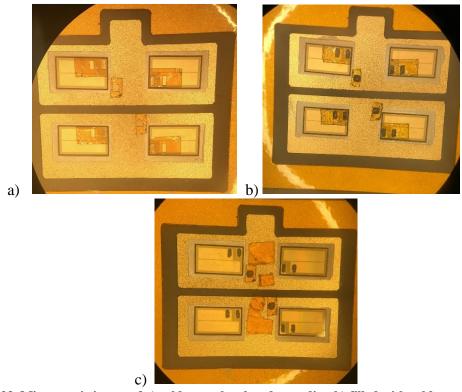

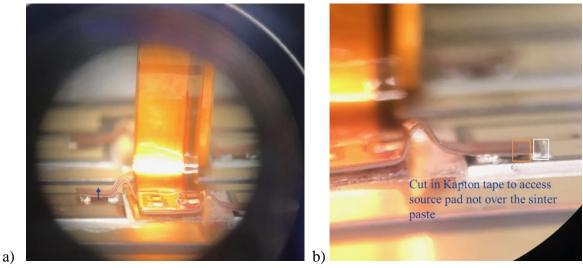

| Figure 3-23. Microscopic image of a) solder masks placed onto dies, b) filled with solder paste     |

| and c) masks removed with double-sided Kapton tape placed on substrate below flexible PCB 67        |

| Figure 3-24. Microscopic image of a) flexible PCB secured onto die and substrate and b)             |

| tweezers used to carefully align flexible PCB pads onto the source and gate of the parallel dies 68 |

| Figure 3-25. Microscopic image of a) flexible PCB flap pulled upward by elastic force and b)        |

| shifted flap away from the source and gate pads of the die                                          |

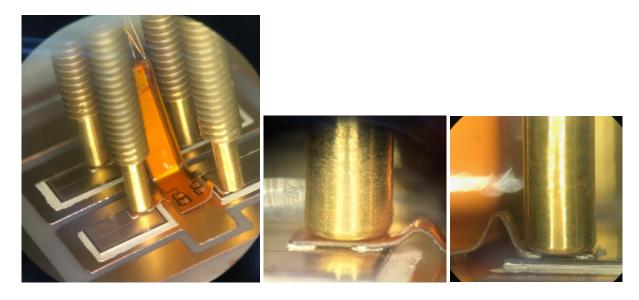

| Figure 3-26. Fixture for use during curing of the flexible PCB connection                           |

| Figure 3-27. Microscopic images of screws flush against the flexible PCB flaps                      |

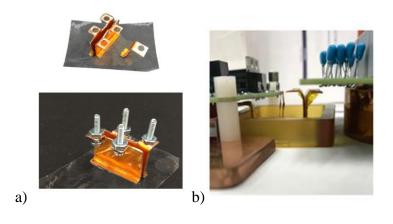

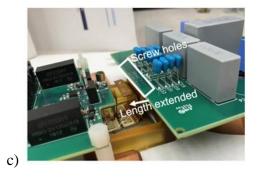

| Figure 3-28. Original design of power terminals to interface with vias on the capacitor bank      |

|---------------------------------------------------------------------------------------------------|

| board                                                                                             |

| Figure 3-29. a. New design of power terminals with screw connections; b. the power terminals      |

| sit flush against the capacitor bank board c. which required updates including adding screw holes |

| and extending the board                                                                           |

| Figure 3-30. Updated design (Altium) of the capacitor bank replacing the via connection with      |

| screws                                                                                            |

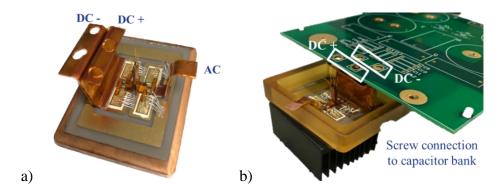

| Figure 3-31. a) Final design of the power terminals b) which interface with the capacitor bank    |

| using screws                                                                                      |

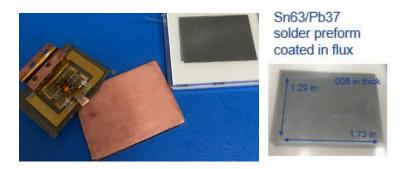

| Figure 3-32. Solder preform sits between the baseplate and the DBC                                |

| Figure 3-33. Baseplate attachment process for the two test samples and x-ray image of the         |

| sample                                                                                            |

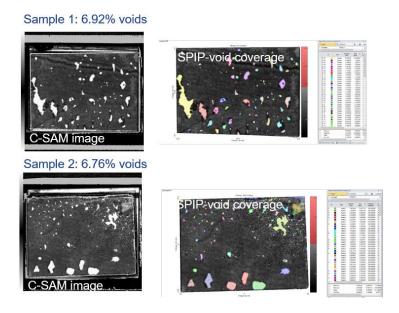

| Figure 3-34. C-SAM image of the voids in the solder attachment to the baseplate74                 |

| Figure 3-35. Processing for attaching the baseplate to the power module with cured layer          |

| displayed                                                                                         |

| Figure 3-36. Approximate dimensions of housing to rest on the baseplate and edge of the           |

| substrate                                                                                         |

| Figure 3-37. Duratron U1000 PEI material and housing machined by Virginia Tech 76                 |

| Figure 3-38. Attachment of housing with generic sealant                                           |

|                                                                                                   |

| Figure 3-39. a. Two parts of encapsulant are mixed producing bubbles b-c. Bubbles are removed     |

| using a vacuum d. Encapsulant is poured into the module producing bubbles e. Bubbles are          |

| removed f. Encapsulant is cured at 70°C for 4 hours                                               |

| Figure 3-40. a. Rogowksi coil coated in Kapton tape for protection against scratching b                      |

|--------------------------------------------------------------------------------------------------------------|

| Rogwoski coil looping through plastic tubing and under bottom switch wire bonds                              |

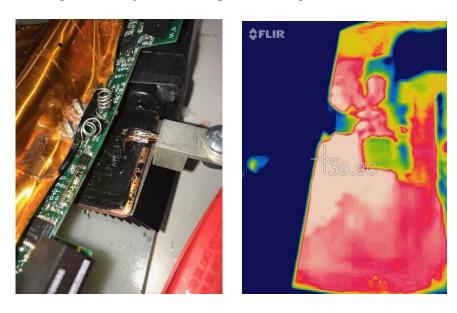

| Figure 3-41. Module 9 alternative encapsulation technique for black surface IR camera                        |

| compatibility                                                                                                |

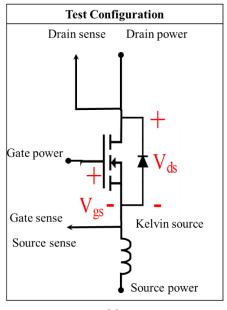

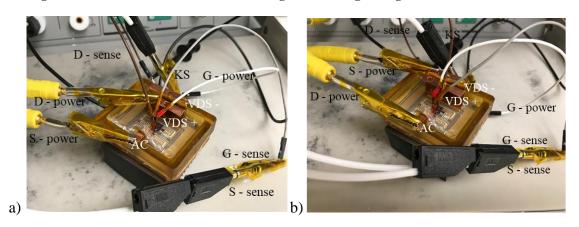

| Figure 4-1. Static characterization test configuration using the Agilent B1505A curve tracer 83              |

| Figure 4-2. Static characterization test set up using the Agilent B1505A curve tracer 83                     |

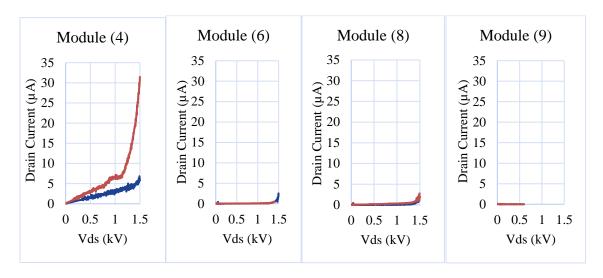

| Figure 4-3. Breakdown voltage with threshold of either 1.5 kV or 100 µA leakage current; top                 |

| switch is red, bottom switch is blue                                                                         |

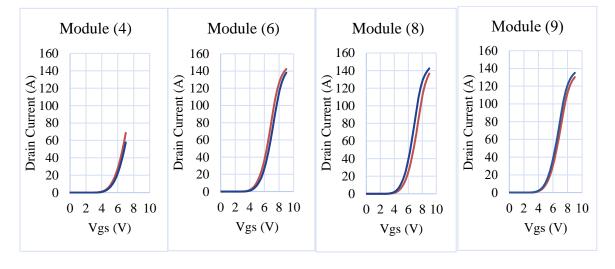

| Figure 4-4. Transfer characteristics with 10 V applied across V <sub>ds</sub> ; top switch is red, botton    |

| switch is blue                                                                                               |

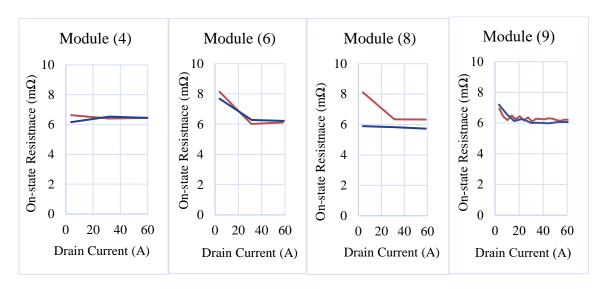

| Figure 4-5. On-state resistance with 15 V applied across $V_{\rm gs}$ ; top switch is red, bottom switch i   |

| blue                                                                                                         |

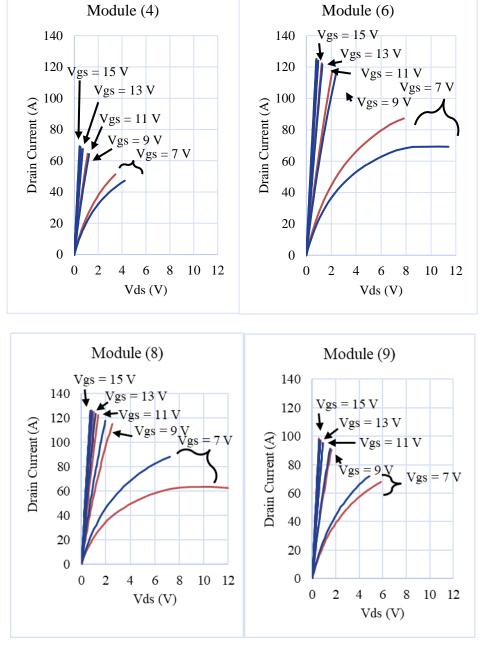

| Figure 4-6. Output characteristics with a 7, 9, 11, 13, and 15 V applied to $V_{\rm gs}$ ; top switch is red |

| bottom switch is blue                                                                                        |

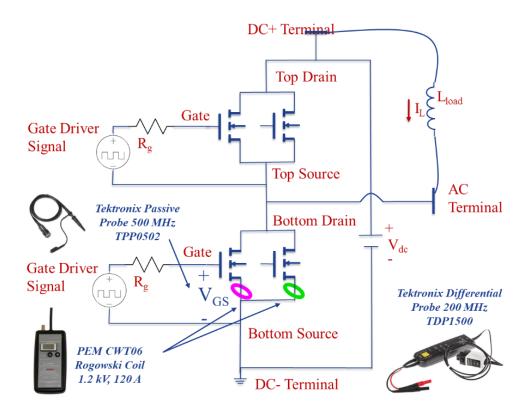

| Figure 4-7. Double pulse test setup with die current monitoring                                              |

| Figure 4-8. Rogowski coil interface with module                                                              |

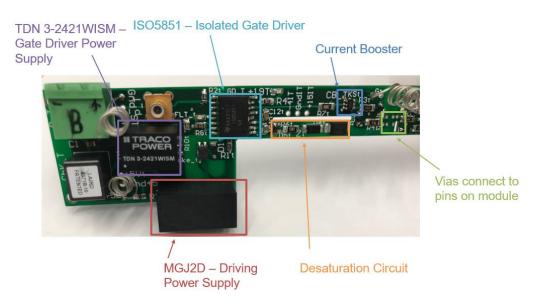

| Figure 4-9. Gate driver with top and bottom switch circuitry designed to be thin for the                     |

| placement of the Rogowski coils                                                                              |

| Figure 4-10. Pins of the flexible PCB interface with vias on the board                                       |

| Figure 4-11. Gate driver board layout                                                                        |

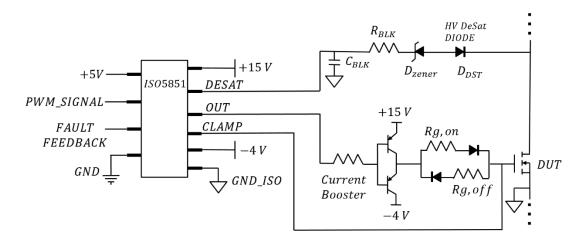

| Figure 4-12. Simplified schematic of the driving circuit                                                     |

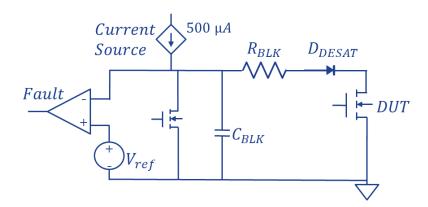

| Figure 4-13. Example schematic of a desaturation circuit                                                     |

|    | Figure 4-14. Desaturation circuit behavior during device ON and OFF states                 | . 93 |

|----|--------------------------------------------------------------------------------------------|------|

|    | Figure 4-15. Desaturation circuit behavior during device switching                         | . 94 |

|    | Figure 4-16. Desaturation circuit behavior during a short circuit event                    | . 94 |

|    | Figure 4-17. Desaturation circuit for this gate driver after tuning                        | . 95 |

|    | Figure 4-18. Tuning desaturation response time with blanking capacitor                     | . 96 |

|    | Figure 4-19. Tuning the diode voltages and desaturation threshold voltage                  | . 97 |

|    | Figure 4-20. Validating desaturation threshold voltage                                     | . 97 |

|    | Figure 4-21. Approximate current for the desaturation threshold voltage based on the out   | put  |

| cı | urves for the dies[83]                                                                     | . 98 |

|    | Figure 4-22. Power module screws into capacitor bank board with screw for load induc       | ctor |

| cc | onnection                                                                                  | . 99 |

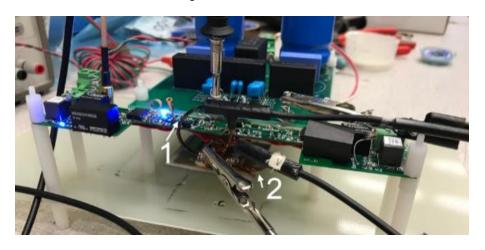

|    | Figure 4-23. Test set up with Rogowski coils through the wire bonds of the bottom side die | e of |

| a  | partially fabricated module                                                                | . 99 |

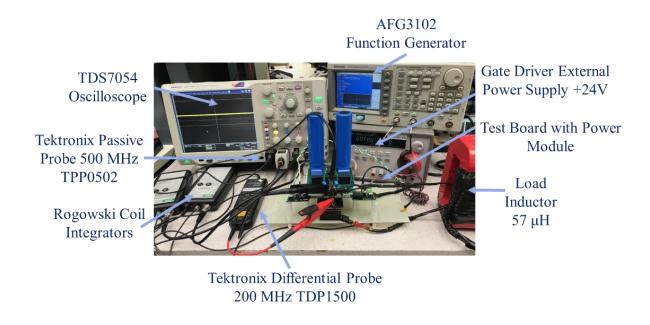

|    | Figure 4-24. Test set up for dynamic characterization of module                            | 100  |

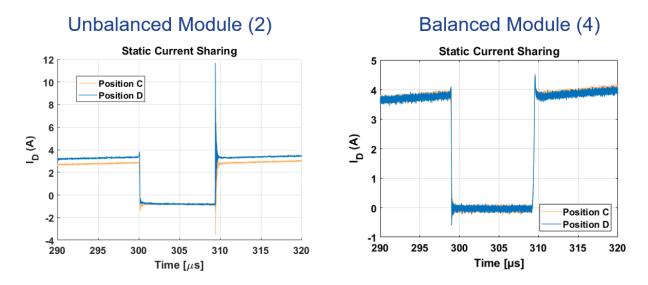

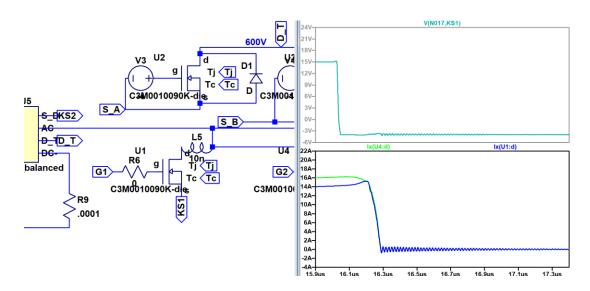

|    | Figure 4-25. Static current sharing for unbalanced and balanced modules                    | 101  |

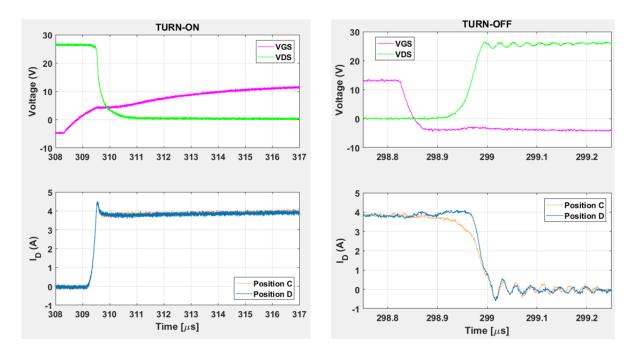

|    | Figure 4-26. Balanced module (4) turn on and turn off behavior                             | 102  |

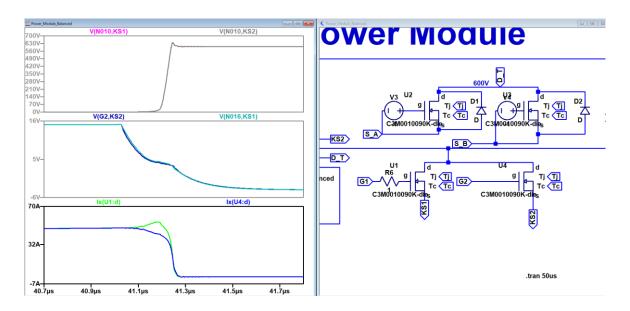

|    | Figure 4-27. Unbalanced module (2) turn on and turn off behavior                           | 103  |

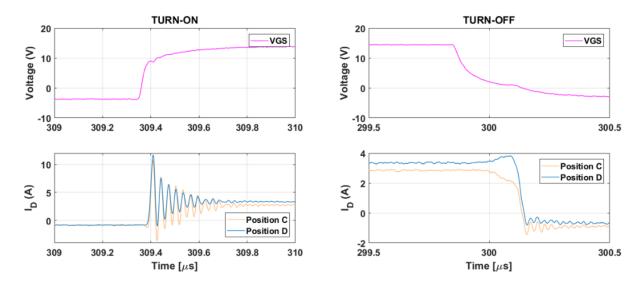

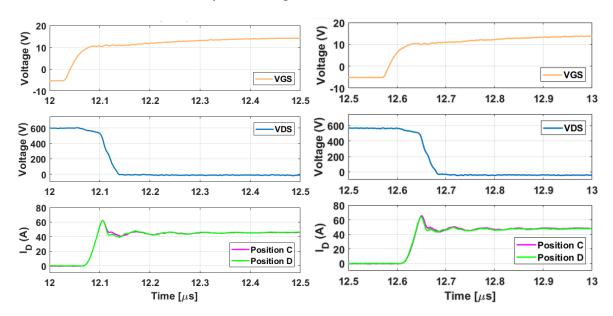

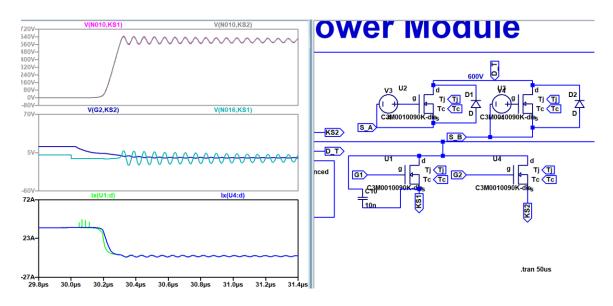

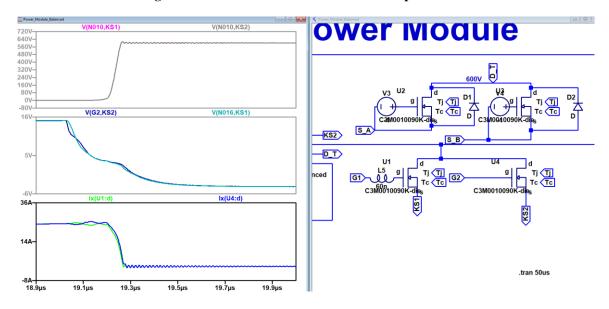

|    | Figure 4-28. 600 V DPT results for balanced modules 4 and 6                                | 103  |

|    | Figure 4-29. 600 V DPT results for unbalanced modules 8 and 9                              | 104  |

|    | Figure 4-30. 600 V DPT turn-on results for balanced modules 4 and 6                        | 104  |

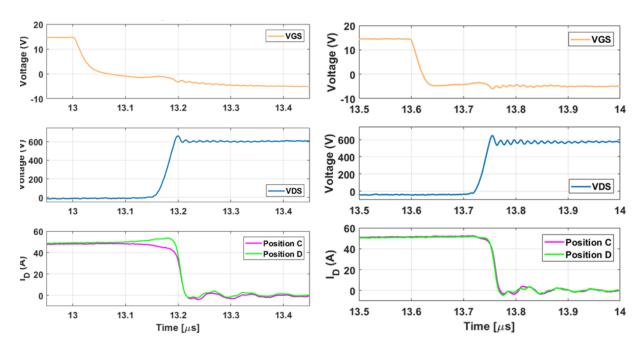

|    | Figure 4-31. 600 V DPT turn-off results for balanced modules 4 and 6                       | 105  |

|    | Figure 4-32. 600 V DPT turn-on results for unbalanced modules 8 and 9                      | 106  |

| Figure 4-33. 600 V DPT turn-off results for unbalanced modules 8 and 9 107                     |

|------------------------------------------------------------------------------------------------|

| Figure 4-34. Simulation of unbalanced Rg in paralleled dies                                    |

| Figure 4-35. Simulation of unbalanced Cds in paralleled dies                                   |

| Figure 4-36. Simulation of unbalanced Lgs in paralleled dies                                   |

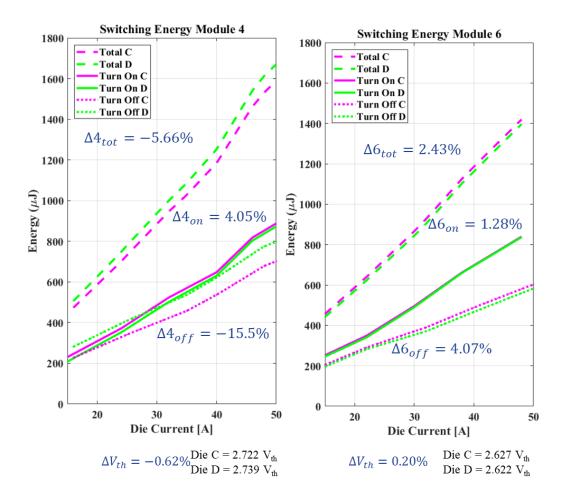

| Figure 4-37. Simulation of unbalanced Lds in paralleled dies                                   |

| Figure 4-38. 600 V DPT switching energy for balanced modules 4 and 6 with percent              |

| differences                                                                                    |

| Figure 4-39. 600 V DPT switching energy for unbalanced modules 8 and 9 with percent            |

| differences 112                                                                                |

| Figure 5-1. Equivalent thermal resistances for each layer from junction to ambient assuming    |

| lumped capacity                                                                                |

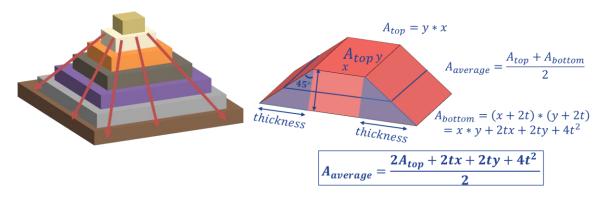

| Figure 5-2. 0° and 45° heat spreading throughout the module                                    |

| Figure 5-3. Calculating the approximate area for the 45° heat spreading case                   |

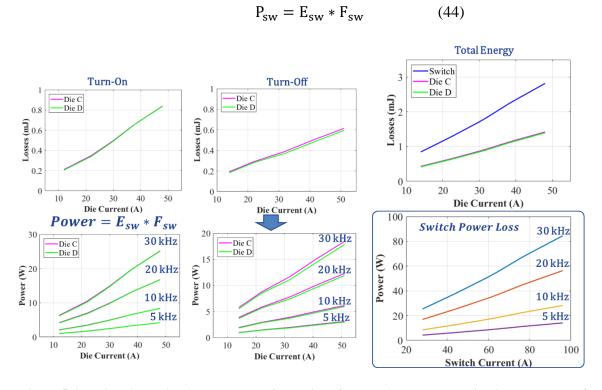

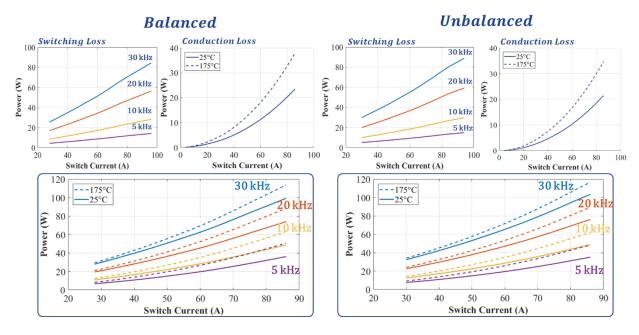

| Figure 5-4. Estimating switching power loss for various frequencies based on switching energy  |

| loss for balanced module 6                                                                     |

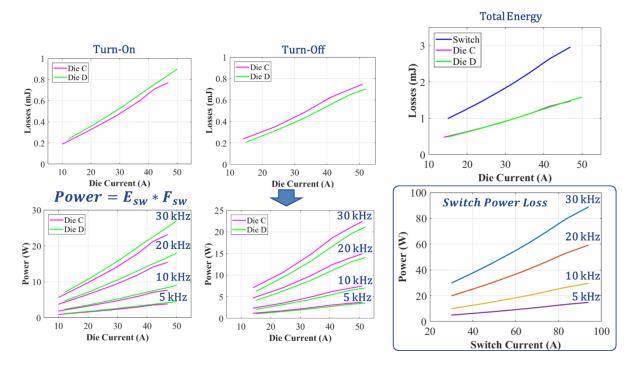

| Figure 5-5. Estimating switching power loss for various frequencies based on switching energy  |

| loss for unbalanced module 8                                                                   |

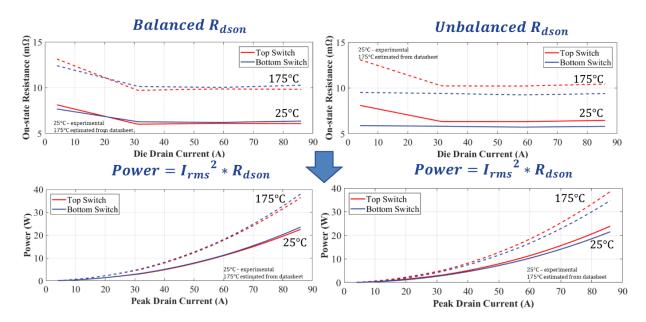

| Figure 5-6. Estimating conduction power loss for various rms drain currents for balanced       |

| module 6 and unbalanced module 8                                                               |

| Figure 5-7. Estimating total power loss for various operating points for balanced module 6 and |

| unbalanced module 8                                                                            |

| Figure 5-8. Estimating junction temperature for various operating points for balanced module 6 |

|------------------------------------------------------------------------------------------------|

| and unbalanced module 8                                                                        |

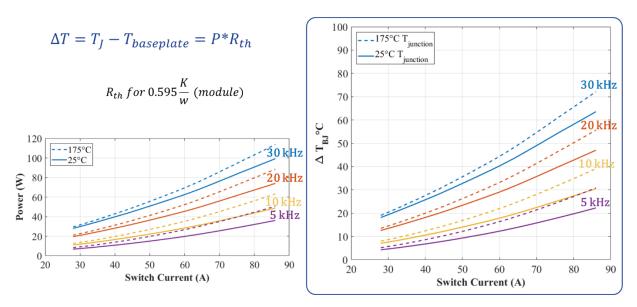

| Figure 5-9. Fully fabricated module with heat sink and black liquid tape covering the face of  |

| the baseplate                                                                                  |

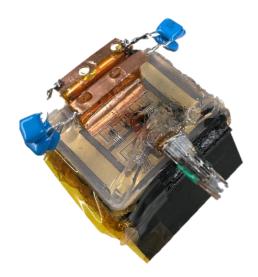

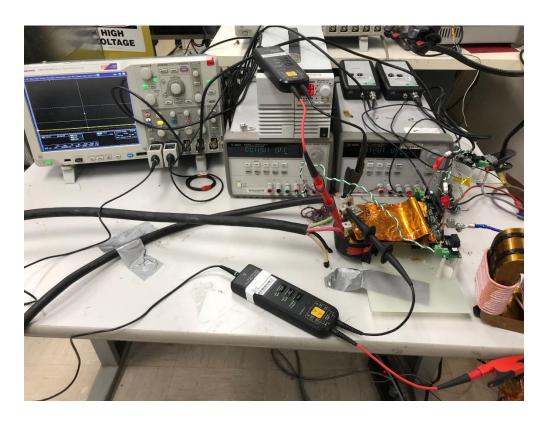

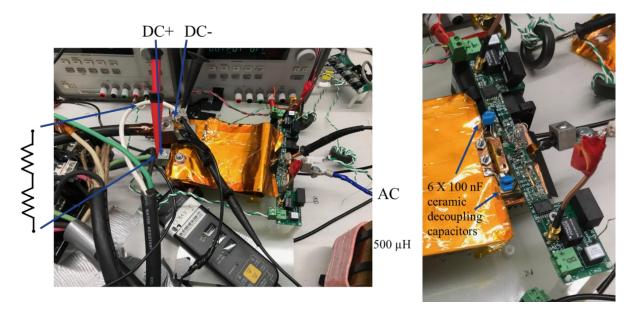

| Figure 5-10. Continuous, boost, test setup with equipment indicated                            |

| Figure 5-11. Continuous, boost, test setup with some equipment shown                           |

| Figure 5-12. Closer image of the continuous, boost, test setup with busbar connection 125      |

| Figure 5-13. Continuous test results for balanced 6 and unbalanced module 8 at 250 V, 47.7 A   |

| input                                                                                          |

| Figure 5-14. Continuous test results for balanced modules 4 and 6 at 200 V, 37.7 A input 126   |

| Figure 5-15. Continuous test results for unbalanced modules 8 and 9 at 200 V, 37.7 A input     |

|                                                                                                |

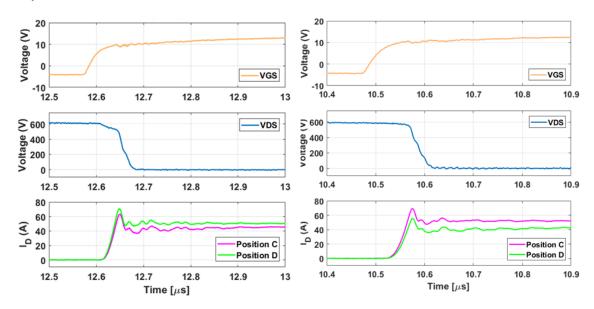

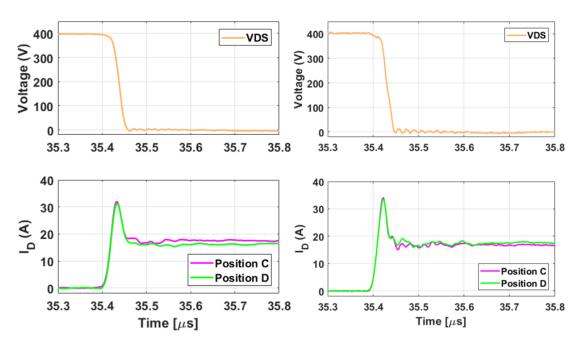

| Figure 5-16. Continuous test turn-on results for balanced modules 4 and 6 at 200 V, 37.7 A     |

| input                                                                                          |

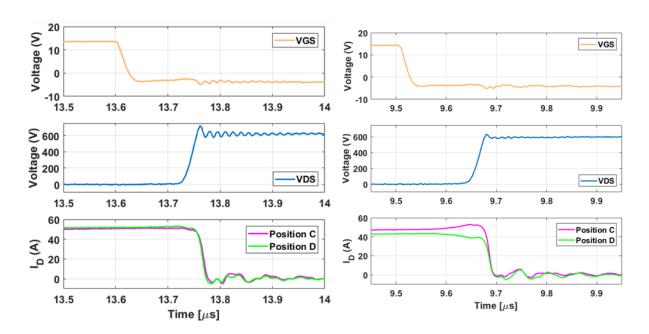

| Figure 5-17. Continuous test turn-off results for balanced modules 4 and 6 at 200 V, 37.7 A    |

| input                                                                                          |

| Figure 5-18. Continuous static results for balanced modules 4 and 6 at 200 V, 37.7 A input129  |

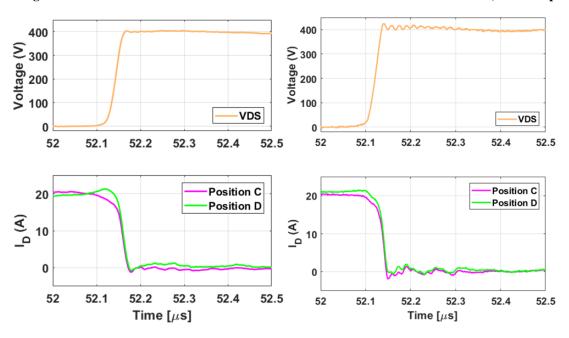

| Figure 5-19. Continuous test turn-on results for unbalanced modules 8 and 9 at 200 V, 37.7 A   |

| input                                                                                          |

| Figure 5-20. Continuous test turn-off results for unbalanced modules 8 and 9 at 200 V, 37.7 A  |

| input, 400 V, 18.85 A output                                                                   |

| Figure 5-21. Continuous static results for unbalanced modules 8 and 9 at 200 V, 37.7 A input |

|----------------------------------------------------------------------------------------------|

|                                                                                              |

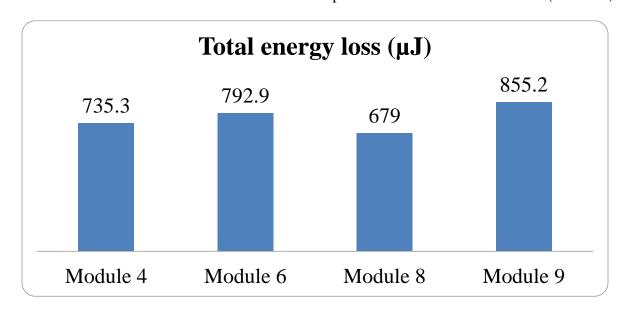

| Figure 5-22. Total energy loss for all continuously tested modules                           |

| Figure 5-23. Energy loss for all continuously tested modules                                 |

| Figure 5-24. Thermal test setup for continuous test of modules                               |

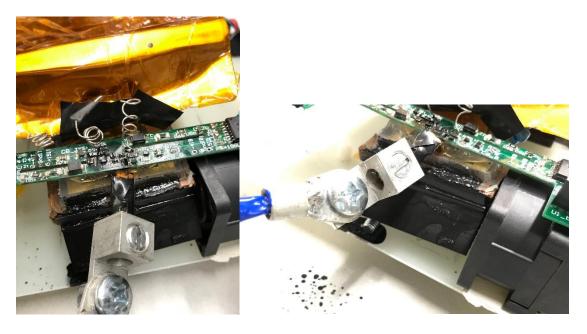

| Figure 5-25. After ~5 minutes, the module reached thermal equilibrium                        |

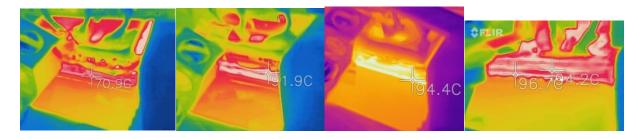

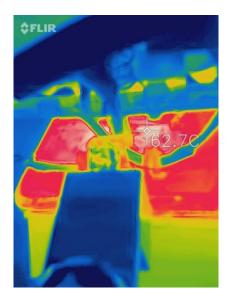

| Figure 5-26. Thermal image of modules 4, 6, 8, and 9 at 200 V, 37.7 A input, 400 V, 18.85    |

| output                                                                                       |

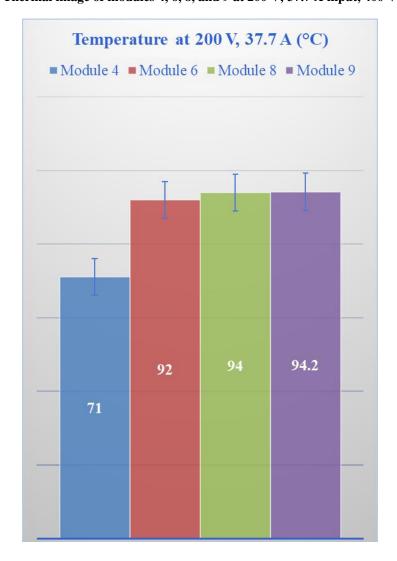

| Figure 5-27. Comparison of module 4, 6, 8, and 9 temperature for 200 V, 37.7 A input, 400 V  |

| 18.85 A output                                                                               |

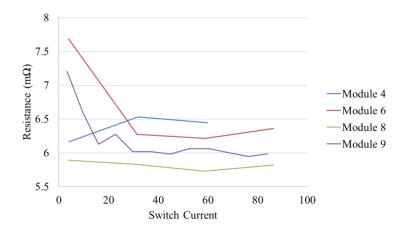

| Figure 5-28. On-state resistance for modules 4, 6, 8, and 9 across switching current 13      |

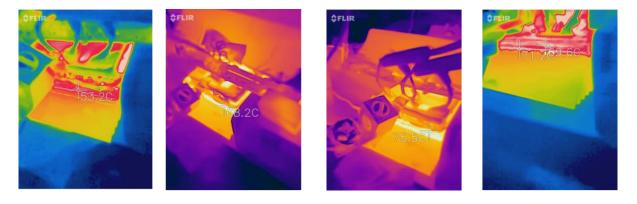

| Figure 5-29. Thermal image of modules 4, 6, 8, and 9 at 150 V, 28.3 A input, 300 V, 14.15    |

|                                                                                              |

| Figure 5-30. Thermal image of modules 4, 6, 8, and 9 at 250 V, 47.7 A input, 400 V, 18.85    |

| output NOT NECESSARILY AT THERMAL EQILIBRIUM                                                 |

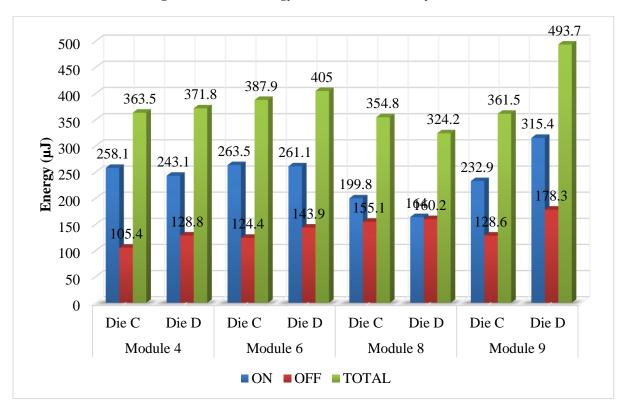

| Figure 5-31. Module 6 after experiencing thermal runaway after 2-3 minutes at 250 V, 47.7    |

| input, 500 V, 23.86 A output                                                                 |

| Figure 5-32. Thermal setup and image of module 9 from the side angle run at low power 14     |

| Figure 5-33. Thermal setup and image of module 9 from the front angle run at low power . 14  |

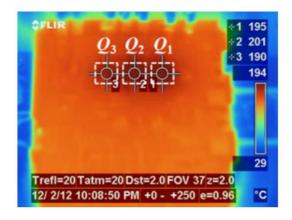

| Figure 5-34. Thermal performance of paralleled die a high-temperature, high-frequence        |

| continuous test                                                                              |

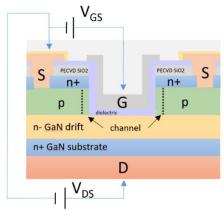

| Figure A-1. Approximate Vertical Trench MOSFET Structure                                     |

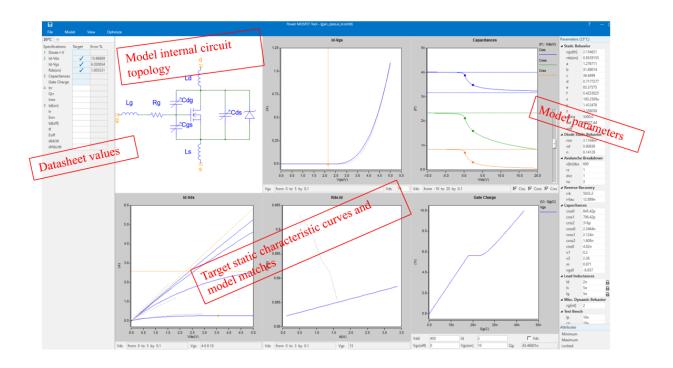

| Figure A-2. Power MOSFET Tool User Interface with static characteristic curves                         |

|--------------------------------------------------------------------------------------------------------|

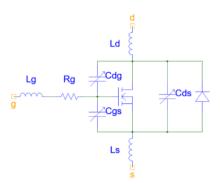

| Figure A-3. Saber <i>Power MOSFET Tool</i> Subcircuit Model                                            |

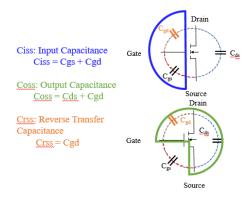

| Figure A-4. Device capacitance definitions                                                             |

| Figure A-5. Double-pulse test schematic                                                                |

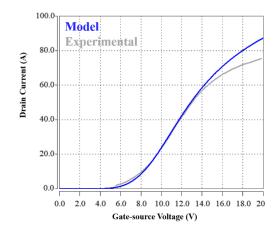

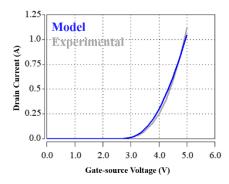

| Figure A-6. Saber® (blue) overlaid on experimental (gray) SiC transfer characteristics                 |

| comparison measured with a drain-source voltage of 1 V at 25°C                                         |

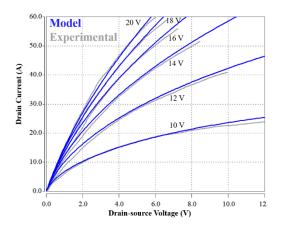

| Figure A-7. Saber® (blue) overlaid on experimental (gray) SiC output characteristics                   |

| comparison measured at various gate-source voltages at 25°C                                            |

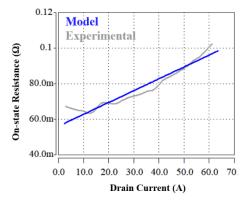

| Figure A-8. Saber® (blue) overlaid on experimental (gray) SiC on-state resistance comparison           |

| measured with a gate-source voltage of 20 V at 25°C                                                    |

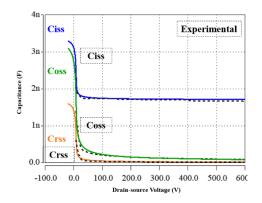

| Figure A-9. Saber® (color) overlaid on experimental (dash) SiC capacitance curve comparison            |

| at 25°C                                                                                                |

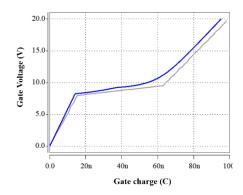

| Figure A-10. Saber® (blue) overlaid on experimental (gray) SiC gate charge curve comparison            |

| at 25°C                                                                                                |

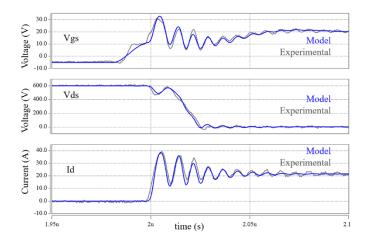

| Figure A-11. Saber® (blue) overlaid on experimental (gray) Monolith SiC turn-on waveforms              |

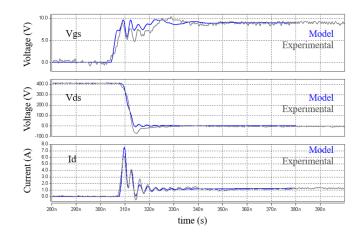

| at a drain-source voltage of 600 V, a 20 A load current, and 3.01 $\Omega$ gate resistance at 25°C 157 |

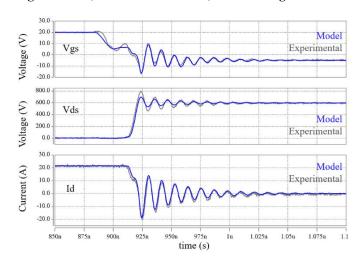

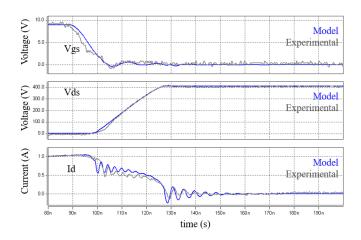

| Figure A-12. Saber® (blue) overlaid on experimental (gray) Monolith SiC turn-off at a drain-           |

| source voltage of 600 V, a 20 A load current, and 3.01 $\Omega$ gate resistance at 25°C                |

| Figure A-13. Saber® (blue) overlaid on experimental (gray) Vertical GaN transfer                       |

| characteristics comparison measured with a drain-source voltage of 10 V at 25°C                        |

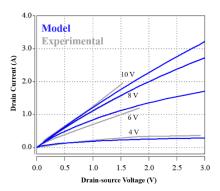

| Figure A-14. Saber® (blue) overlaid on experimental (gray) Vertical GaN output characteristics         |

| comparison measured at various gate-source voltages at 25°C                                            |

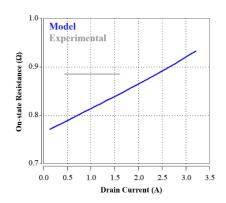

| Figure A-15. Saber® (blue) overlaid on experimental (gray) Vertical GaN Rds (on)                     |

|------------------------------------------------------------------------------------------------------|

| characteristics comparison measured with a gate-source voltage of 10 V at 25°C 159                   |

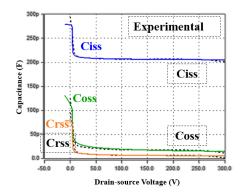

| Figure A-16. Saber® (color) overlaid on experimental (dash) Vertical GaN capacitance curve           |

| comparison at 25°C                                                                                   |

| Figure A-17. Saber® Vertical GaN gate charge model curve at 25°C                                     |

| Figure A-18. Saber® double pulse test set up with optimized parasitic elements                       |

| Figure A-19. Saber® (blue) overlaid on experimental (gray) GaN turn-on waveforms with                |

| optimized parasitic circuit elements at a drain-source voltage of 400 V, a 1 A load current, and 2.5 |

| Ω gate resistance at 25°C                                                                            |

| Figure A-20. Saber® (blue) overlaid on experimental (gray) GaN turn-off waveforms with               |

| optimized parasitic circuit elements at a drain-source voltage of 400 V, a 1 A load current, and 2.5 |

| $\Omega$ gate resistance at 25°C                                                                     |

#### Chapter 1 Introduction

#### 1.1 Electric Vehicles

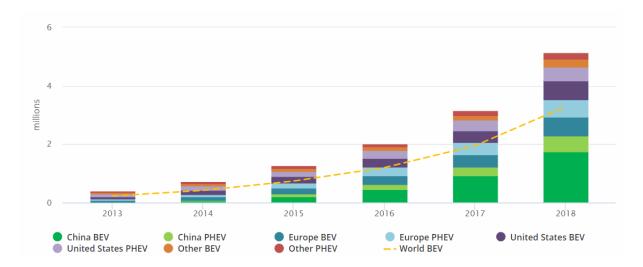

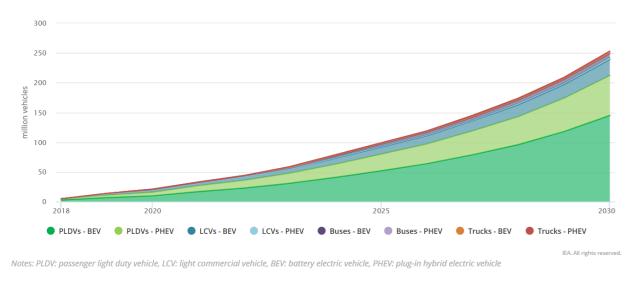

The demand for electrical vehicles (EVs), whether pure electric (no engine) or hybrid (HEV), is driven by a desire to reduce the impact of car emissions on the environment, lower operating costs, increase fuel efficiency, and improve overall performance [1-5]. In December 2018, nearly 50,000 EV were sold in the US which pushed the estimated total number of EVs to over 350k in 2018 alone. This followed a trend in monthly sales gain demonstrating that EVs are increasingly popular. As of July 2019, the total sales worldwide in 2019 alone were over 1 million [6]. According to the 2019 Global EV Outlook, the 2018 global EV stock which includes battery electric vehicles and plug-in electric vehicles was over 5 million and they estimate that the total stock will continue increasing to over 250 million by 2030 (Figure 1-1-Figure 1-2). An increasing demand for EVs encourages improvement in the operating systems particular to EVs to increase the margin of benefit over conventional vehicles.

Figure 1-1. Passenger electric car stock globally from Fig. 1.1 of Global EV Outlook 2019 [7]

Figure 1-2. Outlook for EV growth from EV30@30 Scenario Fig. 2 Global EV Outlook [7]

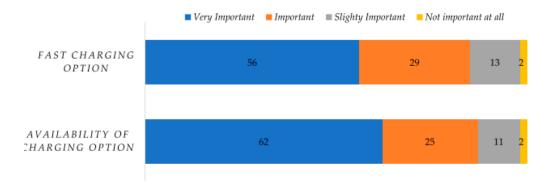

One downside of EVs compared to conventional vehicles is their range which may be anywhere from tens of miles to over two hundred on a single charge [8]. Another downside is the time is takes to charge compared to filling a tank of gas; forty five minutes at a Level 3 public station and 3-9 hours at home [8]. Therefore, barriers to electric vehicle adoption involve the efficiency and speed of storing and utilizing the energy.

Figure 4. Influence of charging option on customer purchase of EVs [75].

Figure 1-3. Influence of charging option on customer purchase of EVs [2]

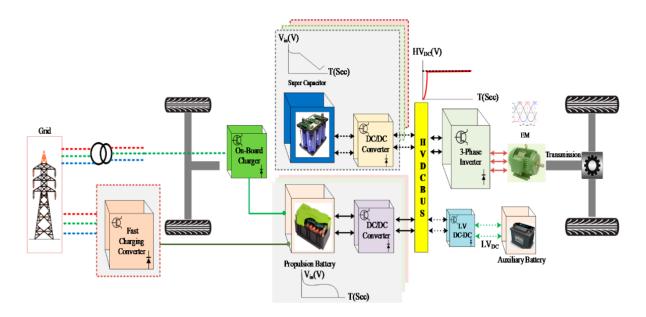

When choosing a vehicle, customers often want reliability, driving range, safety, comfort, and high road performance [9, 10] (Figure 1-3). These performance goals are highly dependent on the powertrain and more advanced technology is necessary to increase the benefit of EVs and HEVs [2, 5] (Figure 1-4).

Figure 1-4. Block diagram of an electric vehicle powertrain [2]

Specifically, an efficient and lightweight drivetrain, which works in conjunction with the engine to move the wheels, can increase the desirability of an EV [10, 11]. A benefit of using an electrified

drivetrain is that electric vehicles can convert 67% of electrical power to the wheels while conventional vehicles can only convert 15% of the gasoline to the wheels [12]. A critical element of the technology that allows for improved efficiency and use of electricity to drive the motor, are called power electronics [9].

#### 1.2 Power Electronics for Electric Vehicles

Power electronics is the study of systems that process and control the flow of electric power using electronic circuits [13-15]. The system will process a power input of a specific form and magnitude and output power to meet design specifications. One type of power electronics system is called a converter, which increases or decreases the magnitude of direct current (DC) power. Another common type is an inverter which changes DC power to alternating current (AC) power.

Parts of an EV require different magnitudes and forms of power. For example, energy is stored as direct current (DC) power in batteries while the motor requires alternating current (AC) power to run. Vehicles include low voltage, high voltage as well as primary and auxiliary battery packs and therefore, DC-DC converters are required to step up and step down power while traction inverters in an electrified drive-train ensure the DC power is changed to the appropriately rated AC power necessary for running the motor [2, 4, 5, 10, 16]. The traction inverter can also capture energy from regenerative braking to charge the battery; another function that increases the efficiency of EVs [2, 4, 9].

#### 1.2.1 Semiconductors

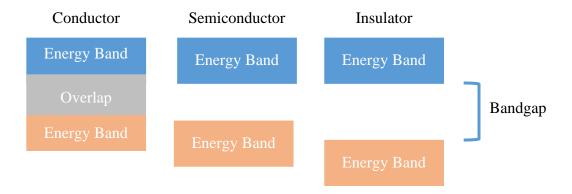

A key component of inverters and converters are semiconductors which have values of electric conductivity in between that of insulators and conductors. Insulators prevent the flow the electric charges; while conductors allow electric charges flow freely (Figure 1-5).

Figure 1-5. Energy bandgaps of different types of materials

Electrons are confined to energy bands and cannot exist in the space between the energy bands. In conductors, the energy bands overlap, and thus, there is no space or band gap within the material where electrons cannot travel. Insulators, on the other hand, have such a wide gap between energy bands that no electron has enough energy to cross and move freely between bands. In semiconductors, the band gap is narrow enough that, given enough energy, an electron could jump from one energy band to the next. Therefore, semiconductors are useful in certain applications because they can behave as either conductors or insulators depending on how much energy the engineer provides. In particular, the semiconductors can act like switches which conduct for a time, then stop conducting for a time. Depending on how these are designed, switches can redirect the flow of current. This is a necessary step for realizing a primary goal of power electronics: controlling the outgoing energy form [17].

The switches involved in this research are called metal-oxide-semiconductor field effect transistors (MOSFETs), which fall under a subcategory of switches primarily used in power

applications. MOSFETs work like a water pipe with a door; energy is required to open the door to control how much water flows through the pipe, the constraints of which are determined by the properties of the MOSFET. Specifically, MOSFETs and similar power devices are made from different semiconductor materials which could include silicon (Si), silicon carbide (SiC), and gallium nitride (GaN). The most utilized semiconductor switches in industry are currently made with silicon (Si IGBTs). SiC and GaN have a wider band gap and are becoming more popular.

#### 1.2.2 Wide Band Gap Power Semiconductor Devices

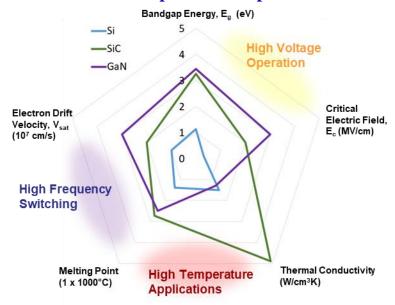

Si transistors are conventionally the semiconductor material used in power electronic systems. Both Si MOSFETs and Si (insulated-gate bipolar transistors) IGBTs are useful for various applications. For example, Si IGBTs can handle high voltage (5 kV) and current (1 kA) but with limited frequency (100 kHz) while Si MOSFETs can perform in the MHz range but high on-state resistance increases conduction losses with higher blocking voltages limiting applications to below 600V [18]. Semiconductors that have a wide electric gap between the conduction and valence band, commonly referred to as wide band gap (WBG) devices, can potentially perform more quickly and efficiently at higher temperatures, frequencies, and power than silicon (Si) [19]. One reason is that the unipolar structure of SiC MOSFETs removes the tail current which contribute to higher switching losses and lower frequency in Si IGBTs [20]. The material property comparison of Si, SiC, and GaN help explain the higher performance of the WBG semiconductors (Table 1 and Figure 1-6) [21-25].

Table 1. Material Properties for Si, SiC, and GaN

| Parameter | Si | 4H-SiC | 2H-GaN |

|-----------|----|--------|--------|

|           |    |        |        |

| Bandgap Energy, $E_g$ (eV)                                      | 1.12                 | 3.26                 | 3.44                  |

|-----------------------------------------------------------------|----------------------|----------------------|-----------------------|

| Relative Permittivity/Dielectric constant, $\epsilon_s$         | 11.8                 | 10                   | 9.5                   |

| Critical Electric Field, E <sub>c</sub> (MV/cm)                 | 0.3                  | 2.0                  | 3.0                   |

| Electron saturated drift velocity, $V_{sat}(10^7 \text{ cm/s})$ | 1.0                  | 2.0                  | 3.0                   |

| Thermal Conductivity (W/cm <sup>3</sup> K)                      | 1.5                  | 4.9                  | 1.3                   |

| Intrinsic Carrier Density, n <sub>i</sub> (cm <sup>-3</sup> )   | 1.5x10 <sup>10</sup> | 8.2x10 <sup>-9</sup> | 1.0x10 <sup>-10</sup> |

| Electron Mobility (cm <sup>2</sup> /V-sec)                      | 1450                 | 900                  | 2000                  |

#### **Material Properties Comparison**

Figure 1-6. Material properties comparison of Si, SiC, and GaN

A wider band gap means that the semiconductor requires more energy to jump an electron from the valence to the conduction band which is defined by the critical electric field. The higher critical electric field of SiC and GaN allow for higher blocking voltages. This means that the devices can be thinner with higher doped drift layers which lowers the on-state resistance [18, 26]. In addition, when the temperature increases, electrons gain energy and require less to the make the jump. Therefore, with higher temperatures, the likelihood of electrons unintentionally jumping to the

conduction band increases which limits the operating temperature. With a wider band gap, the operating temperature can be higher without unintentionally exciting electrons to the conduction band. Thermal conductivity describes the ability of a material to transfer heat so SiC and GaN are better at dissipating heat. Combined with a higher melting point, wide band gap materials can perform at higher temperatures than Si. The disadvantages of GaN compared to SiC include the poorer thermal conductivity which makes SiC better suited for high temperature applications. Lastly, both SiC and GaN have higher electron drift velocity than Si; GaN has the highest value qualifying it as the most suitable material for higher switching frequency operation [26, 27].

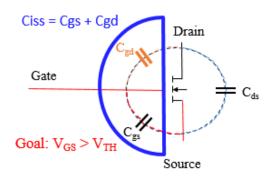

#### 1.2.3 Quasistatic Behavior of MOSFETs

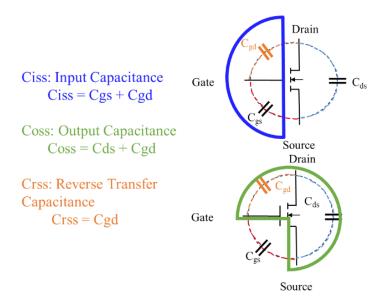

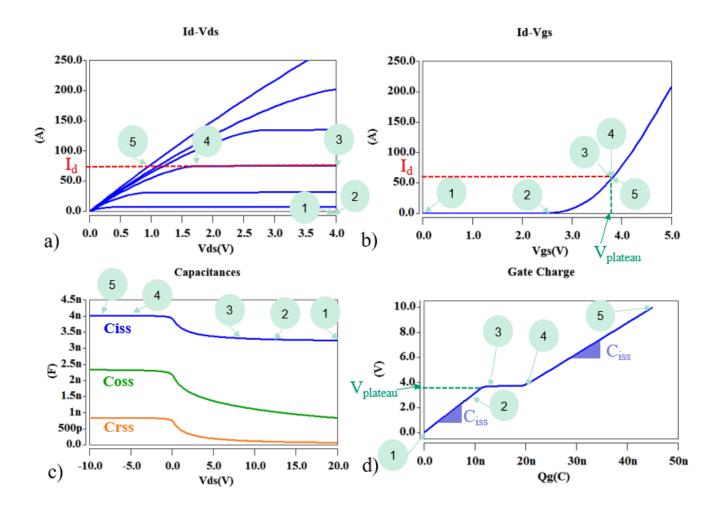

The behavior of MOSFETs is often presented in a few different plots which include: a) output curves, the drain current,  $I_d$ , as the drain-source voltage,  $V_{ds}$ , increases for various gate-source voltages,  $V_{gs}$ , b) transfer curve, the drain current,  $I_d$ , as the device turns on with increasing gate-source for a given drain-source voltage,  $V_{ds}$ , c) capacitance values (Figure 1-7) with increasing drain-source voltage,  $V_{ds}$ , and d) the gate voltage,  $V_{gs}$ , as the gate charge increases.

Figure 1-7. Device capacitance definitions

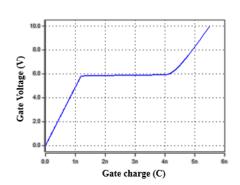

In fact, the behavior observed in the output,  $I_d$  vs.  $V_{ds}$ , and transfer,  $I_d$  vs.  $V_{gs}$ , characteristic curves and the capacitance curves of a transistor relate to one another as presented in Figure 1-7; the segments of the gate-charge plot (Figure 1-8d) allow for validation of a transistor's static behavior presented in a datasheet or in a model. Understanding the relationship among the behavioral curves increases the likelihood of an accurate model and can occasionally draw attention to inconsistencies in datasheets or models [28].

Figure 1-8. Step-by-step walkthrough of the gate charge plot

During turn-on operation, from points 1 to 2, the gate voltage,  $V_{gs}$ , rises (d) until the device starts to conduct the load current (b) which implies that the bias across the drain and source,  $V_{ds}$ , is high and constant (a). The rise rate is determined by the low input capacitance characteristic of high  $V_{ds}$  (c). At the end of this segment, from points 2 to 3, the device turns on and begins to conduct current (b). During the second segment, from points 3 to 4, the saturation of the drain current in the Id- $V_{ds}$  view leads to a clamping of  $V_{gs}$ , at the Miller plateau (d). The drain current remains constant as  $V_{ds}$  drops (a). The difference in slope between the saturation region and quasilinear at the knee point (a) is less pronounced in SiC than Si due to low transconductance [29]. In

the last segment, from points 4 to 5, the rise of  $V_{gs}$ , is less steep than in the low charge region (d) because it now depends on the high input capacitance characteristic at low  $V_{ds}$  (c). The device is now fully on, conducting the full load current.

Important notes regarding device behavior and the gate charge plot include the fact that only the capacitances seen by the gate,  $C_{gd}$  and  $C_{gs}$ , impact the gate charge plot; it is not impacted by the drain source capacitance,  $C_{ds}$ , nor the gate resistance (Figure 1-7). The height of the Miller plateau must match the magnitude of  $V_{gs}$  required to sustain the load current while the width is determined by the charge under the  $C_{iss}$  curve from  $V_{ds}$  to the bias remaining between drain and source once the device has entered the quasi-linear region. The Miller plateau is flat if the saturation region is flat in the output curves. Reasons for a slanted Miller plateau include a rise in junction temperature during the measurement, or channel length modulation that makes the output saturation region non-flat. A more in-depth discussion of the gate-charge plots, characteristics of the Miller plateau, and identifying inconsistencies in datasheets is available in [28].

#### 1.2.4 Dynamic Behavior of MOSFETs

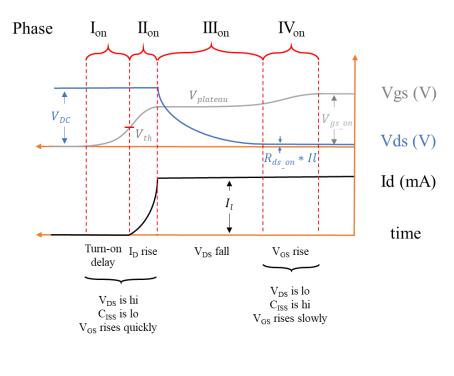

The switching waveforms include but are not limited to the turn-on and turn-off delay, the rise and fall times, and reverse-recovery behavior of the diode. The switching speeds depend on the parasitic capacitance and inductance values [18]. Figure 1-9 presents ideal waveforms for turn-on and turn-off behavior of MOSFETs. This plot does not demonstrate ringing and overshoots that can occur from parasitic impedances.

Figure 1-9. Ideal turn-on and turn-off waveforms for a MOSFET [18]

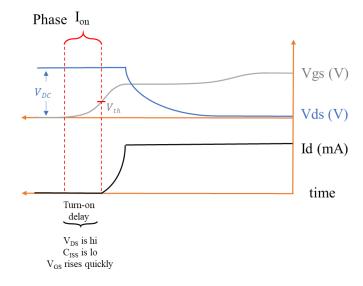

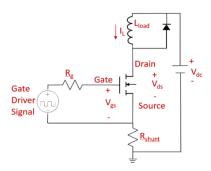

#### (a) Phase Ion: Turn-On Delay

Specifically, the turn-on delay occurs as the input capacitance charges and  $V_{gs}$ , starts to rise with the goal of surpassing the threshold voltage,  $V_{th}$ , thus creating a channel for current to flow from the drain to the source,  $I_d$  (Figure 1-10).  $V_{gs}$  is defined in relation to its on-state bias magnitude (3). Until  $I_d$  can flow, the bias between  $V_{ds}$ , remains high at the bus voltage,  $V_{dc}$  (1). The turn-on delay time,  $td_{on}$ , is proportional to the magnitude of  $C_{iss}$ , and the gate resistance,  $R_g$  (4) [18].

$$V_{ds} = V_{dc} (1)$$

$$I_d = 0 (2)$$

$$V_{gs} = Vgs_{on} \left[ 1 - e^{\left( -\frac{t}{R_g C_{iss}} \right)} \right]$$

(3)

$$td_{on} = R_g C_{iss} \ln \left[ \frac{Vgs_{on}}{(Vgs_{on} - V_{th})} \right]$$

(4)

Figure 1-10. Impact of input capacitance on turn-on delay

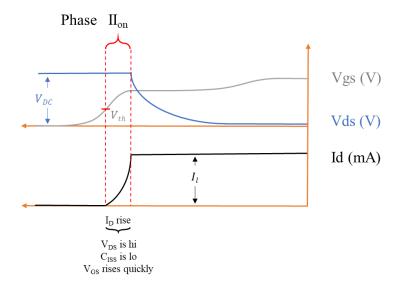

#### (b) Phase II<sub>on</sub>: Drain Current Rise

The goal for phase II of the turn-on process is a transfer of current from the freewheeling diode to the MOSFET.  $I_d$  rises in proportion to the transconductance,  $g_{fs}$ , and  $V_{gs}(6)$ .  $V_{gs}$  begins to flatten after surpassing  $V_{th}$  (Figure 1-11.) at the Miller plateau or  $V_{plateau}$ ; the gate current is directed towards charging  $C_{gd}$ , a process which impacts the rise time of the current,  $t_{ir}(8)$ .

$$V_{ds} = V_{dc} \tag{5}$$

$$I_d = g_{fs}(V_{gs}, V_{ds}) * V_{gs}$$

(6)

$$V_{gs} = Vgs_{on} \left[ 1 - e^{\left( -\frac{t}{R_g C_{iss}} \right)} \right] \tag{7}$$

$$t_{ir} = R_g C_{iss} \ln \left[ \frac{Vgs_{on} - V_{th}}{Vgs_{on} - V_{plateau}} \right]$$

(8)

Figure 1-11. Rise of the drain current as the transistor turns on

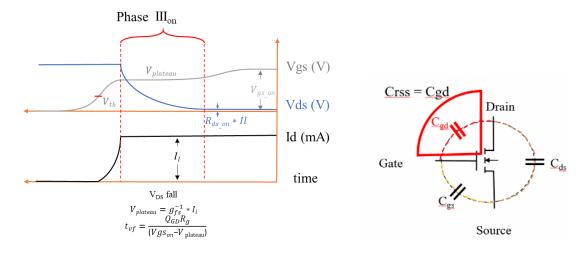

# (c) Phase IIIon: Drain Source Voltage Fall and Miller Plateau

In phase III, the freewheeling diode stops conducting and starts blocking voltage and thus,  $V_{ds}$  drops to its on-state value,  $V_{gs_{on}}$ , consisting of the on-state resistance,  $Rds_{on}$ , and the load current,  $I_L$  (11).  $V_{gs}$  hits the Miller plateau as  $C_{gd}$  charges with  $I_d$  deviating away from  $C_{gs}$  (Figure. 1-12). The rate (9) and time (12) for  $V_{ds}$  to fall is dependent on  $C_{gd}$ . Additionally, a reverse recovery overshoot is common in the falling  $V_{ds}$  waveform steadying out to the on-state value.

$$\frac{dV_{ds}}{dt} = \frac{Vgs_{on}-V_{\text{plateau}}}{R_gC_{GD}} \tag{9}$$

$$I_d = I_L \tag{10}$$

$$V_{gs} = V_{\text{plateau}} = \frac{I_L}{g_{fs}} \tag{11}$$

$$t_{vf} = \frac{Q_{GD}R_g}{(VgS_{on}-V_{\text{plateau}})} \tag{12}$$

Figure. 1-12. Miller plateau as the transistor turns on

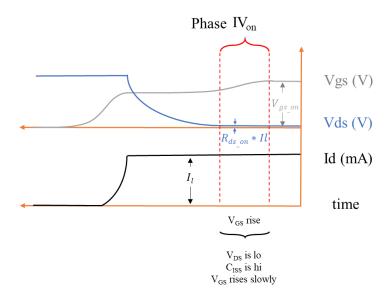

# (d) Phase IVon: Increase Bias from Gate to Source

In the last phase of the turn-on process,  $V_{gs}$  increases to its on-state value and  $I_d$  is equivalent to  $I_L$  (14).  $V_{ds}$  is small, but not zero (typically < 5V), due to the on-state resistance which allows a small amount of leakage current to flow (13) (Figure. 1-13).  $C_{iss}$  is high because of the low  $V_{ds}$  (Figure 1-8c).

$$V_{ds} = Rds_{on} * I_L (13)$$

$$I_d = I_L \tag{14}$$

$$t = R_g C_{iss} (15)$$

Figure. 1-13. Final behavior as the transistor turns on

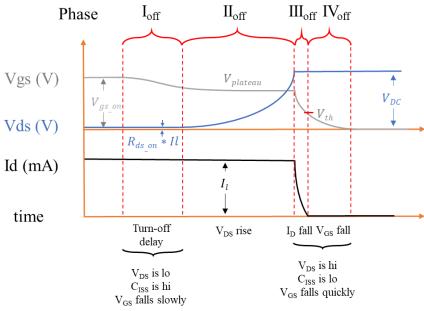

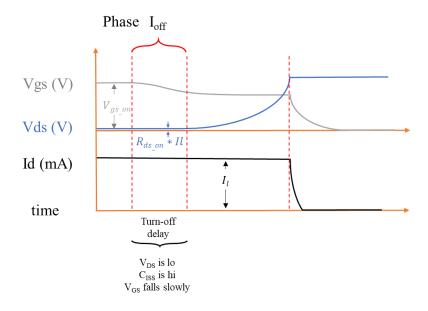

# (e) Phase Ioff: Turn-Off Delay

The first step of the turn off process is reducing the applied  $V_{gs}$  to zero.  $V_{gs}$  then starts to drop back to the Miller plateau (18) (Figure. 1-14). The time delay until turn-off,  $td_{off}$ , is proportional to  $C_{iss}$  (19).  $V_{ds}$  and  $I_{d}$  remain at their on-state magnitudes (16, 17).

$$V_{ds} = Rds_{on} * I_L \tag{16}$$

$$I_d = I_L \tag{17}$$

$$V_{gs} = Vgs_{on} e^{\left(-\frac{t}{R_gC_{lss}}\right)}$$

(18)

$$td_{off} = R_g C_{iss} \ln \left[ \frac{Vgs_{on}}{V_{\text{plateau}}} \right]$$

(19)

Figure. 1-14. Turn-off delay as the gate source bias drops

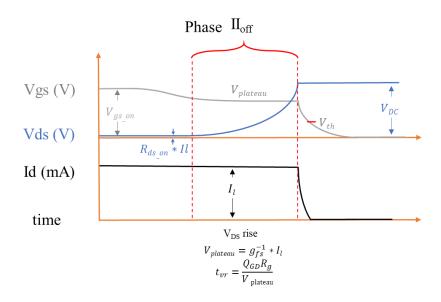

# (f) Phase II<sub>off</sub>: Bias between the drain and source increases

As  $V_{gs}$  steadies at the Miller plateau (22),  $V_{ds}$  begins to increase (Figure. 1-15) at a rate inversely proportional to the gate resistance and reverse transfer capacitance (20) whereas the time for the voltage fall,  $t_{vr}$ , has the opposite proportionality (23).  $I_d$  remains at  $I_L$  (21) although the freewheeling diode begins to pull current from the MOSFET channel.

$$\frac{dV_{ds}}{dt} = \frac{V_{\text{plateau}}}{R_g C_{GD}} \tag{20}$$

$$I_d = I_L \tag{21}$$

$$V_{gs} = V_{\text{plateau}} = \frac{I_L}{g_{fs}}$$

(22)

$$t_{vr} = \frac{Q_{GD}R_g}{V_{\text{plateau}}} \tag{23}$$

Figure. 1-15. Miller plateau as the transistor turns off

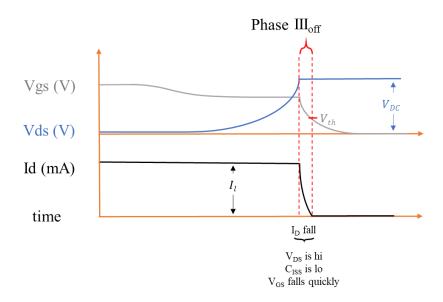

# (g) Phase IIIoff: Drain current falls

After the transistor leaves the saturation region,  $I_d$  fully transfers to the freewheeling diode.  $V_{gs}$  continues to decrease until it reaches  $V_{th}$  (26). This is a result of the discharging  $C_{iss}$  and thus the time for the current to fall,  $t_{ir}$ , is dependent on  $C_{iss}$  (27) and the magnitude is proportional to the transconductance and  $V_{gs}$  (25). Lastly,  $V_{ds}$  remains clamped to the bus voltage (24) (Figure. 1-16).

$$V_{ds} = V_{dc} \tag{24}$$

$$I_d = g_{fs}(V_{gs}, V_{ds}) * V_{gs}$$

(25)

$$V_{gs} = V_{\text{plateau}} e^{\left(-\frac{t}{R_g C_{iss}}\right)}$$

(26)

$$t_{ir} = R_g C_{iss} \ln \left[ \frac{V_{\text{plateau}}}{Vth} \right]$$

(27)

Figure. 1-16. Fall of the drain current as the transistor turns off

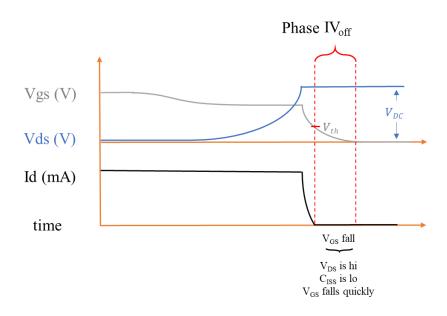

# (h) Phase $IV_{\text{off}}$ : Gate source bias falls, transistor off

As  $V_{gs}$  falls to zero,  $C_{iss}$  fully discharges. The load current is now fully transferred to the freewheeling diode and the transistor drain current is zero (29).  $V_{ds}$  remains high at the bus voltage magnitude (28) (Figure 1-17).

$$V_{ds} = V_{dc} (28)$$

$$I_d = 0 (29)$$

Figure 1-17. Final reduction of gate-source bias as transistor turns off

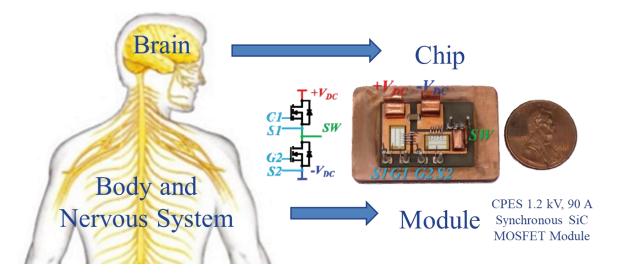

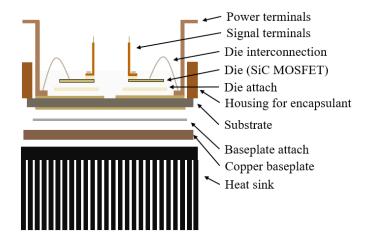

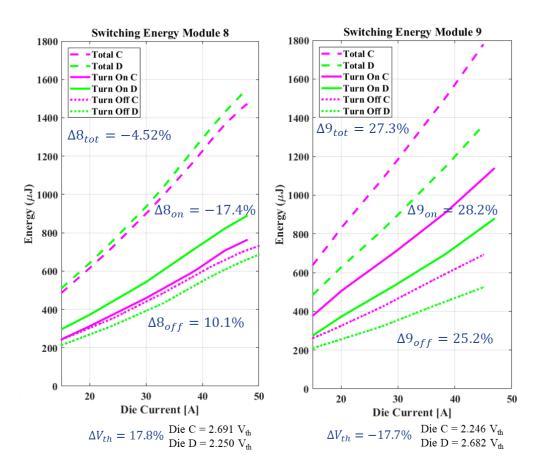

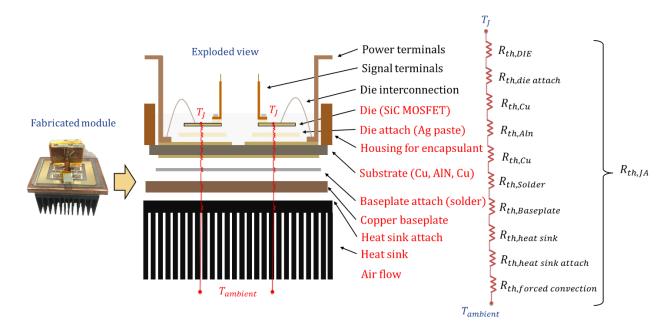

# 1.3 Multi-Chip Power Module Packaging

Power modules provide a support structure around semiconductor chips so that they can perform reliably over time. Without a module, the chip could suffer from electrical, thermal, or mechanical breakdown. In addition, chips require interconnections in order to integrate the chip into the rest of the system. Therefore, packages provide protection for the semiconductors while also providing power and signal distribution according to the application of the chip (Figure 1-18). For further understanding, compare a brain to the chip and the human body and nervous system to the power module; the brain is powerful but could not function without the body and nervous system which protect the brain and connect it to the rest of the body systems (Figure 1-19) [30]. The brain's purpose can be executed in various applications because it is protected and interconnected.

Figure 1-18. Functions of a power module package with an example of a commercial power module (CREE CAS120M12BM2)

Figure 1-19. A power module package and chip are analogous to the human body and brain [30, 31]

Packaging and integration are essential to meeting the aggressive size, weight, efficiency, power, and cost requirements for 21st-century electronic energy systems. While packages exist for Si and often WBG devices are placed into these packages, they are not optimized to take advantage of the benefits of SiC and GaN. In general, power devices are one of, if not the most expensive and critical element of many circuits. While they could be utilized in their bare die form, they are often packaged in modules which are specially designed to protect them and the surrounding elements of the circuit. The application of this research is electric vehicles where compact systems

are necessary to regulate hundreds or thousands of volts while minimizing additional weight added to the moving vehicle.

Another benefit of packaging devices is that higher power modules can be designed while managing thermal performance; simply using a larger die would increase power capacity but with considerably poorer thermal performance and inefficiency across the die. Electric vehicles have high ambient temperature surrounding the power electronics demanding devices that can perform well at high temperatures. In addition, thermal management systems cannot be too bulky or heavy as the car must be lightweight to travel. Therefore, this research is intended to study and improve the design of power modules to be used in electric vehicles.

# 1.4 Research Motivations and Objectives

High current SiC MOSFET power modules are becoming global solutions in load harsh power electronics systems such as renewable energy generation, automotive and rail-traction applications [32]. Paralleling dies in multi-chip modules or paralleling discrete SiC MOSFETs increases the current rating of power modules while also allowing for high power with fewer die (Figure 1-20); paralleling die can also reduce conduction losses by ensuring the devices operate in the linear region [20, 26, 33, 34].

Figure 1-20. Increased current carrying capacity with paralleled dies

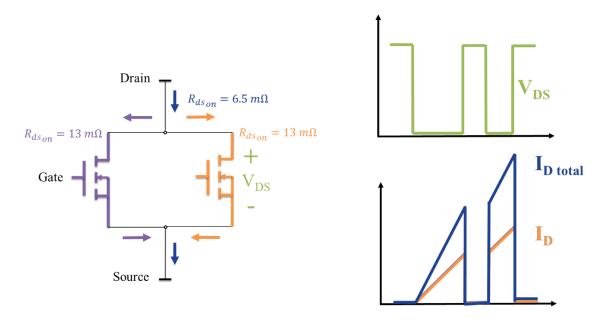

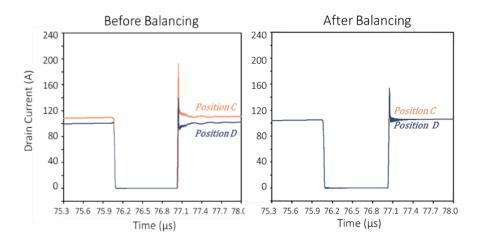

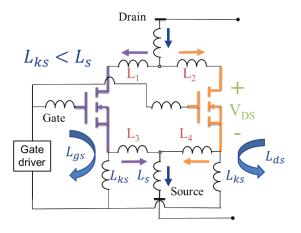

However, variations in the device parametrics can lead to unbalanced current sharing of the paralleled dies (Figure 1-21-Figure 1-23). In addition, differences in the impedance of the current pathways can also lead to mismatched current overshoots and ringing as well as mismatched rates of increase during static, on-state current sharing (Figure 1-22-Figure 1-23) [20, 35]. Improving performance of paralleled die include but are not limited to adjusting the length of the wire bonds, active gate driver control, and use of auxiliary source connection [20].

Figure 1-21. Device parametric tolerances can lead to unbalanced current sharing

# **Package Parasitics**

Figure 1-22. Package parasitics can lead to unbalanced current sharing

Figure 1-23. Simulation of static and dynamic unbalanced current sharing

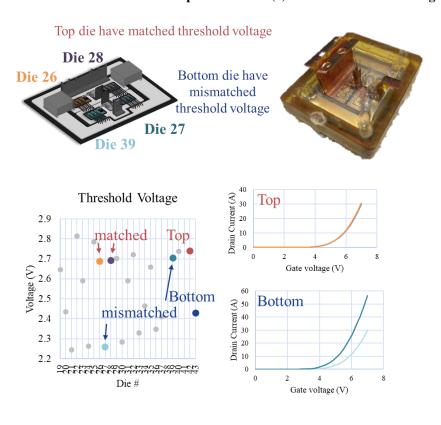

### 1.4.1 Device Parametric Tolerances

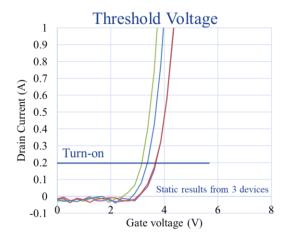

The threshold voltage of MOSFETs results from nonidealities in the interface or oxide; due to developing manufacturing techniques of SiC, variations occur in the threshold voltages of these

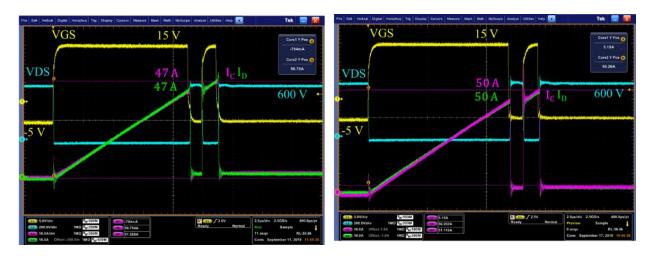

devices [20]. Mismatch in the threshold voltages of paralleled dies causes them to turn on at different times, thereby sending the majority of the current through one device momentarily [20, 34]. Threshold voltage mismatch would be apparent in the dynamic switching behavior of the devices (Figure 1-21-Figure 1-24).

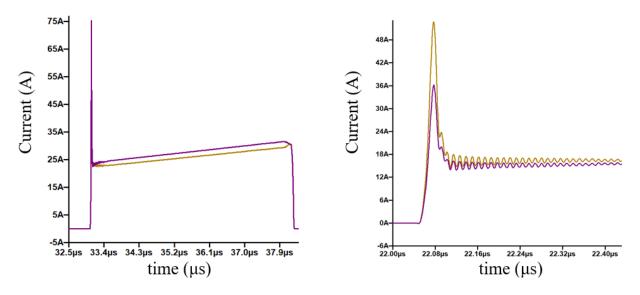

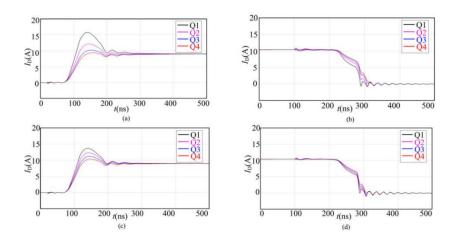

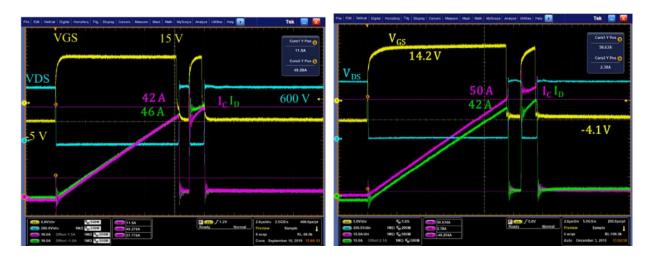

Figure 1-24. Impact of unbalanced threshold voltages on a) turn-on and b) turn-off behavior of discrete SiC MOSFETs [20]

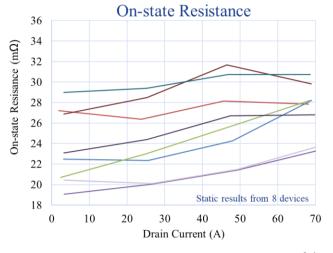

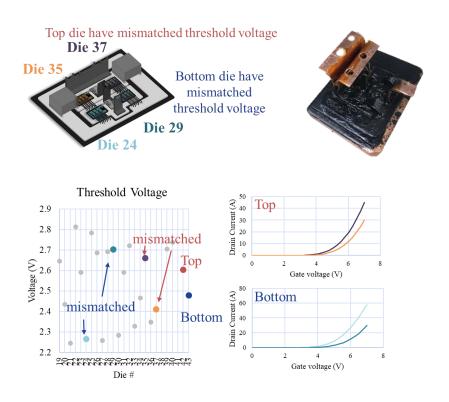

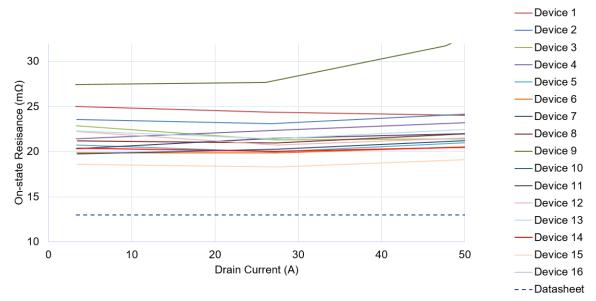

Static current sharing is dependent on the pathway impedances composed of inductance and on-state resistance [20]. If any of the impedance parameters of the pathways are mismatched, current distribution among the dies can be unequal (Figure 1-22). Variations in on-state current sharing are typically attributable to a mismatch in on-state resistance of individual die (Figure 1-25).

On-state resistance mismatch may also contribute to unbalanced switching and conduction losses (Figure 1-25). However, the impact of this effect may be limited for devices with positive temperature coefficient [35].

Figure 1-25. Impact of unbalanced on-state resistance on a) turn-on, b) turn-off, and c) on-state behavior of discrete SiC MOSFETs [20]

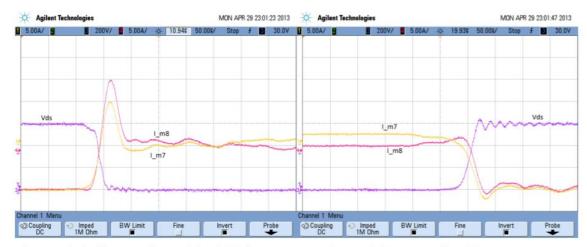

A paper evaluated the electrical and thermal impact of discrete device parametric tolerances [36]. It determined that differences in on-state resistance for paralleled devices led to the most significant unbalance in the current sharing. On the other hand, if the on-state resistances were well-matched, the threshold voltage had less of an impact on current sharing unbalance. In a boost

test with devices that were balanced in both on-state resistance and threshold voltage, one device presented higher switching losses and higher temperature (Figure 1-26). The unbalance in switching losses was attributed to a likely mismatch in parasitic inductance in the current pathway [36].

Fig. 15: Switching transients of the dc/dc boost converter's parallel-connected MOSFETs

Fig. 16: Thermal image of the parallel-connected MOSFET of the dc/dc boost converter

Figure 1-26. Thermal impact of unbalanced current sharing in discrete SiC MOSFET devices

# 1.4.2 Package Parasitics

When the current pathways have similar impedances, the current should increase at the same rate and experience the same overshoot. This ultimately means that neither die is experiencing more current stress than the other, which leads to improved reliability and prevents catastrophic failures. When not balanced, each die will experience different current loads especially during turn-on [34].

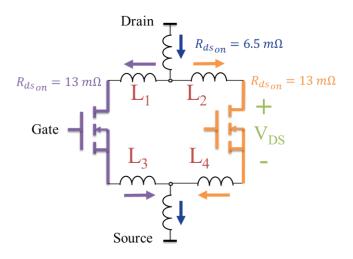

Mismatch of the parasitic impedances in current pathways can lead to unbalanced stress throughout modules which could contribute to poorer reliability. Often, the geometry of the DBC leads to asymmetrical pathway impedance for parallel dies as seen in Figure 1-27. While a symmetrical DBC is favorable for current sharing behavior, this is difficult to achieve with a large numbers of devices and can also poorly utilize space and may put additional constraints on the thermal management of the system [20, 35]. Another source of unbalanced static or dynamic current sharing may be electrical couplings between power and gate loops [34]. One reason for designing a module with such coupling is to create a negative feedback path for the gate loop. A method for mitigating this unbalance is offsetting the impedance of the pathway with varying lengths of wire bonds where impedance increase with the length of the wire [34]. Compensating the unbalance with wire bonds led to better dynamic current sharing (Figure 1-27b).

Figure 1-27. a) Multi-chip half-bride power module with assymetrical pathway impedance for paralleled dies where  $L_{C4}>L_{C3}>L_{C2}>L_{C1}$  and b) Improved current sharing after adjusting the wire bonds [34]

Both common source and switching loop stray inductance can negatively impact current sharing behavior of paralleled dies. Mismatched switching loop stray inductance may cause unbalanced current sharing during the on-state (Figure 1-28). However, the impact of pathway inductance mismatch is often less significant than on-state resistance mismatch in static current sharing [20].

Figure 1-28. Impact of switching loop stray inductance mismatch on a) turn-on and b) turn-off behavior of discrete SiC MOSFETs [20]

Common source stray inductance has the most negative impact on dynamic current sharing compared to switching loop stray inductance (Figure 1-29). Because switching losses have a significant impact on module performance, this effect is problematic and deserves investigation and mitigation as many have done [20, 26, 34, 35]. One such solution was addition of an auxiliary source connection to reduce the impact of current coupling between the gate and power loops (Figure 1-30).

Figure 1-29. Impact of common source stray inductance mismatch on a) turn-on and b) turn-off behavior of discrete SiC MOSFETs [20]

Figure 1-30. Addition of auxiliary source connection reduced dynamic current imbalance from a) to c) during turn-on and from b) to d) during turn-off [20]

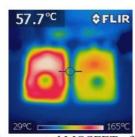

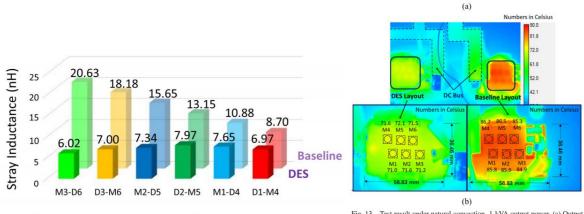

Similar research evaluated the thermal impact of symmetrical parasitic inductances for a multichip module [37]; the research compared a conventional module to a module with symmetrical power loop inductances and found that balancing parasitic inductances helped balance heating of the paralleled chips. The method for balanced inductances utilized a set of DC terminals in parallel with those in the conventional, baseline layout. By creating balanced inductances, the new method helps mitigate large voltage overshoot and unbalanced dynamic current sharing (Figure 1-31). This paper found improved thermal performance in balancing the parasitic inductances but did not evaluate the impact of device parametric tolerances.

Fig. 4. Power-loop inductance comparison.

Fig. 13. Test result under natural convection, 1-kVA output power. (a) Output current (time: 4 ms/div). (b) Temperature distribution.

Figure 1-31. Thermal comparison of a module with unbalanced and balanced parasitic inductances [37]

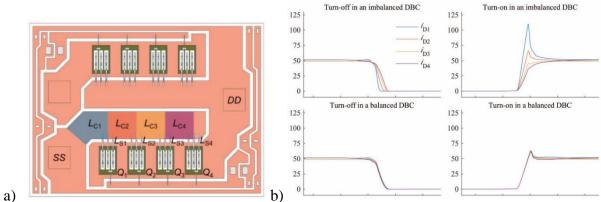

### 1.4.3 Objective

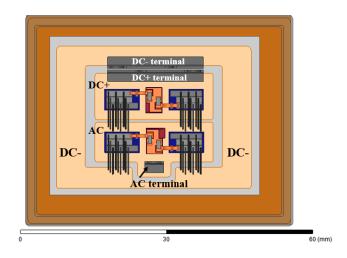

In this thesis, the primary objective is to observe the impact of device parameter tolerances on the current sharing behavior of modules with paralleled dies. In order to mitigate the impact of package parasitics, the DBC pattern is designed symmetrically so that the impedances of the traces are similar (Figure 1-32). In practice, a perfectly symmetrical DBC is challenging for more than 2 devices and could also increase the demands of the thermal management system; however, the primary area of interest in this research is the impact of mismatched device characteristics and therefore is an acceptable design [35, 38]. The control power module has dies with similar threshold voltages to further increase the likelihood of balanced current sharing. The die in the experimental power module has die selected with dissimilar threshold voltages, forcing current through one die before the other. The on-state resistances of the bare die were too difficult to characterize without a functional probing station and therefore, this parametric difference could not be controlled.

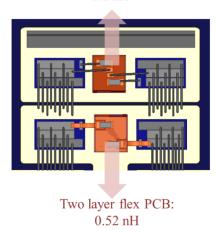

Another method of interest to reduce the gate loop inductance is the use of flexible PCB as the gate, drain, and kelvin source interconnection [39]. Replacing classical wire bonds with flexible PCB or other planar technologies has been shown to increase power density and reduce loop inductance [40, 41]. A low gate loop inductance reduces the potential impact of parasitic resonance [42-44].

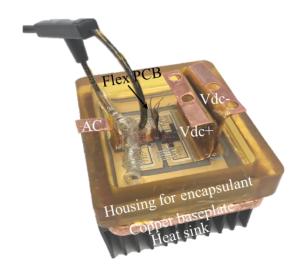

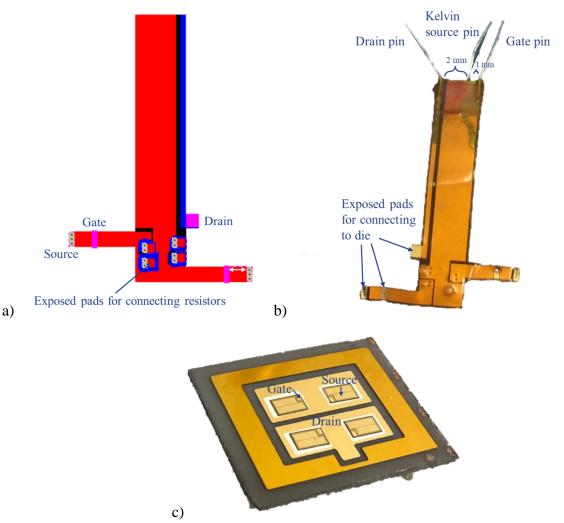

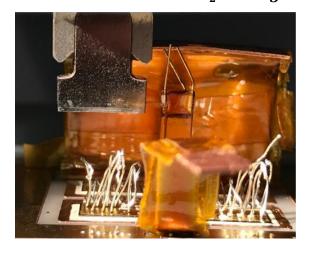

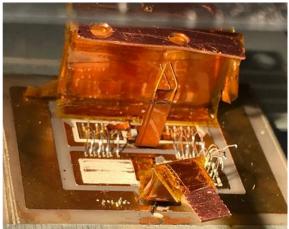

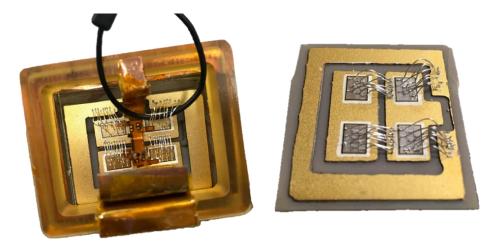

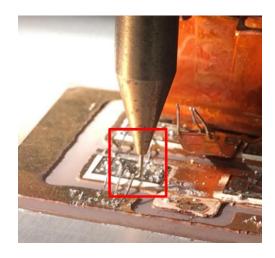

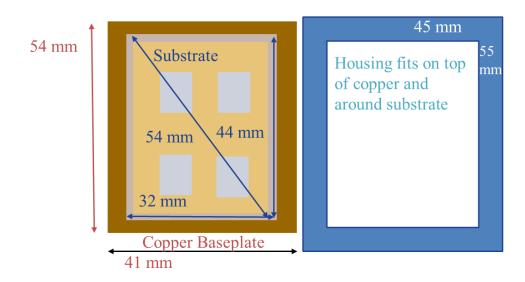

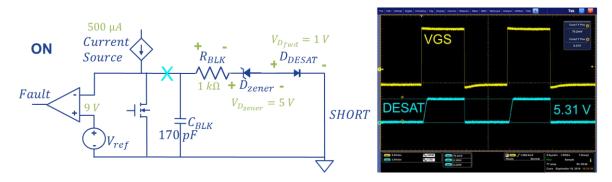

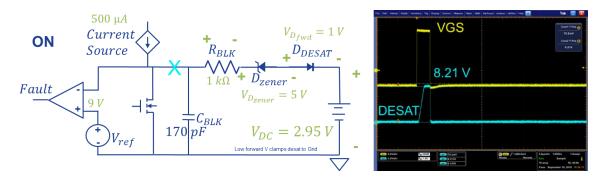

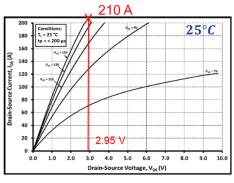

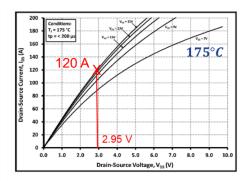

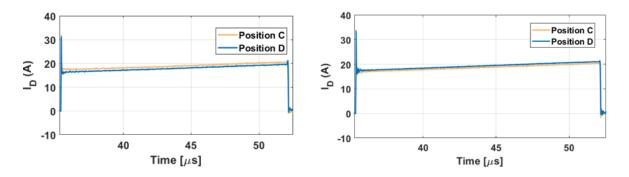

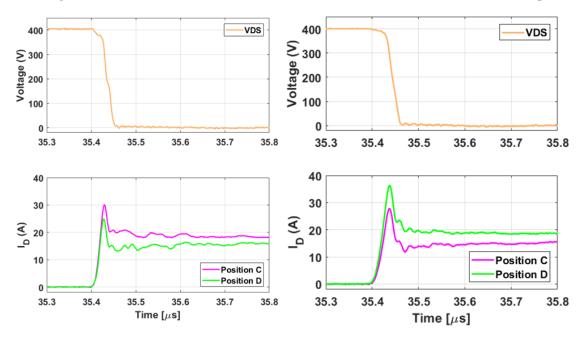

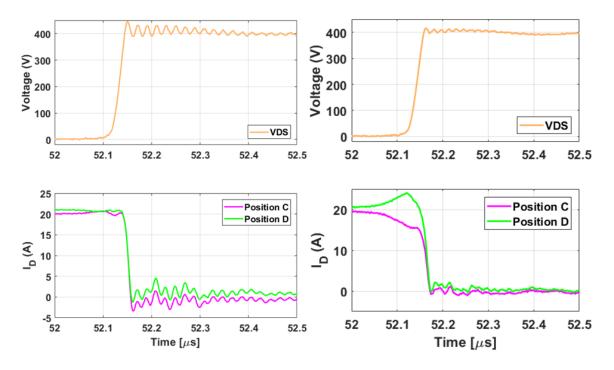

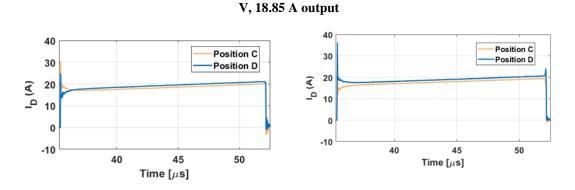

Figure 1-32. Symmetrical DBC layout with DC- trace wraparound