# Optimal and Approximate Algorithms for the Multiple-Lots-per-Carrier Scheduling and Integrated Automated Material Handling and Lot Scheduling Problems in 300mm Wafer Fabs

Lixin Wang

Dissertation submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

> Doctor of Philosophy in Industrial and Systems Engineering

Dr. Subhash C. Sarin, Chair Dr. Kimberly P. Ellis Dr. Barbara Fraticelli Dr. Robert Hendricks

August 20, 2008

Blacksburg, Virginia

Keywords: Multiple Lots per Carrier Scheduling, Integrated AMHS and Lot Scheduling, Makespan, Total Completion Time, AMHS, 300mm Wafer Fabs

Copyright 2008, Lixin Wang

# Optimal and Approximate Algorithms for the Multiple-Lots-per-Carrier Scheduling and Integrated Automated Material Handling and Lot Scheduling Problems in 300mm Wafer Fabs

## Lixin Wang

## (Abstract)

The latest generation of semiconductor wafer fabs produce Integrated Circuits (ICs) on silicon wafers of 300mm diameter. In this dissertation, we address the following two types of (new) scheduling problems that are encountered in this generation of wafer fabs: multiple-lots-per-carrier scheduling problem (MLCSP) and integrated automated material handling and lot scheduling problem (IMHLSP). We consider several variations of the MLCSP depending upon the number of machines used, the prevailing processing technology of the machines, and the type of objective functions involved. For the IMHLSP, we study two instances, one with infinite number of vehicles and the other with finite number of vehicles.

We begin by introducing a single-machine, multiple-lots-per-carrier with single-waferprocessing-technology scheduling problem for the objective of minimizing the total completion time (MLCSP1). The wafer carrier is a front-opening unified pod (FOUP) that can hold a limited number of wafers. The problem is easy to solve when all the lots are of the same size. For the case of different lot sizes, we first relax the carrier (FOUP) capacity and propose a dynamic programming-based algorithm, called RelaxFOUP-DP, which enables a quick determination of its optimal solution that serves as a lower bound for the problem with limited FOUP capacity. Then, a branch-and-bound algorithm, designated as MLCSP1-B&B, is developed that relies on the lower bound determined by the RelaxFOUP-DP algorithm. Numerical tests indicate that MLCSP1-B&B finds optimal solutions much faster than the direct solution of the MLCSP1 model by the AMPL CPLEX 10.1 Solver. In fact, for the medium and low density problems, the MLCSP1-B&B algorithm finds optimal solutions at the starting node (node zero) itself.

Next, we consider a single-machine, multiple-lots-per-carrier with single-carrierprocessing-technology scheduling problem for the objective of minimizing total completion time (MLCSP2). As for the case of MLCSP1, the optimal solution for the case in which all the lots are of the same size can be obtained easily. For the case of different lot sizes, we determine a lower bound and an upper bound for the problem and prove the worst-case ratios for them.

Subsequently we analyze a two-machine flow shop, multiple-lots-per-carrier with singlewafer-processing-technology scheduling problem for the objective of minimizing the makespan (MLCSP3). We first consider a relaxed version of this problem, and transform the original problem to a two-machine flow shop lot streaming problem. Then, we propose algorithms to find the optimal capacitated sublot sizes for the case of lots with (1) the same ratio of processing times, and, (2) different ratios of processing times on the machines. Since the optimal solutions obtained from the lot streaming problem may not be feasible to the MLCSP3, we develop heuristic methods based on the heuristic procedures for the bin packing problem. We develop four heuristic procedures for lots with the same ratio of processing times, and another four procedures for lots with different ratios of processing times on the machines. Results of our numerical experimentation are presented that show that our heuristic procedures generate almost optimal solutions in a matter of a few seconds.

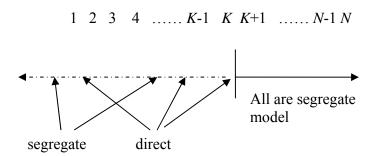

Next, we address the integrated automated material handling and lot scheduling problem (IMHLSP) in the presence of infinite number of vehicles. We, first, propose a new strong hybrid model, which has the advantages of both segregate and direct models. In the segregate model, a job is always transferred to the stocker after its completion at a station, while in the direct model, it is transferred to the next machine in case that machine can accommodate the jobs; otherwise, the job will stay at current station. The decisions involved in the strong hybrid model are the sequence in which to process the lots and a

selection between the segregate and direct models for each lot, whichever optimizes system performance. We show that, under certain conditions about the processing times of the lots, the problem can be approximated by the cases of either infinite buffer or zero-buffer at the machines. Hence, we consider all three cases of the IMHLSP in this chapter, namely, infinite buffer, zero-buffer, and limited buffer sizes. For the strong hybrid model with limited buffer size, we propose a branch-and-bound algorithm, which uses a modified Johnson's algorithm to determine a lower bound. Two upper bounds for this algorithm are also determined. Results of our numerical investigation indicate that our algorithm finds optimal solutions faster than the direct solution of the IMHLSP model by the AMPL CPLEX 10.1 Solver. Experimental results also indicate that for the same problem size, the times required to solve the IMHLSP model with interbay movements are larger than those for intrabay movements.

Finally, we investigate the IMHLSP in the presence of limited number of vehicles. Due to the complex nature of the underlying problem, we analyze small-size versions of this problem and develop algorithms for their solution. For some of these problems, we can find optimal solutions in polynomial time. Also, based on our analysis on small-size systems, we have shown why some real-time dispatching (RTD) rules used in real fabs are expected to perform well while not the others. In addition, we also propose some new and promising RTD rules based on our study.

# Acknowledgement

First and foremost, I would like to express my sincere gratitude to my advisor, Dr. Subhash C. Sarin, for his invaluable guidance, support, motivation and expertise throughout the entire progress of my dissertation research. I have learnt so much from working with him and taking classes from him. His patience has endured my obstinate anxiety during the countless hours in research meetings. I specially appreciate his great help and encouragement during the last several months while I was in transition from a student to a full time engineer. I want to offer my heart-felt thanks to my committee member, Dr. Kimberly Ellis, who has helped me in many ways, including and beyond my dissertation. It has been pleasant experience to be a teaching assistant for her. I owe much to my committee member, Dr. Barbara Fraticelli, for her kindness and encouragement during our discussions. She is such a considerate person. I also want to give thanks to my committee member, Dr. Robert Hendricks for his brain-storming style discussions with me about semiconductor industry. His opinions and observations from his years of experience in semiconductor industry have been very valuable.

I am extremely grateful to my friends in Blacksburg for making my life here so wonderful. I enjoyed being a roommate with Chengbin Zhu and Wenwei Zhong. Thanks to my good friends: Ming Chen, Weiping Chen, Ming Cheng, Ying Fu, Cheng Guo, Seonki Kim, Feng Li, Lingrui Liao, Yunkai Lu, Shunying Qiu, Xiangshan Tong, Yong Yang, Yuqiang Wang, Liming Yao, Xiaomei Zhu, Yueqin Zhao, ..., thank you all for the good times we shared.

Finally, I am indebted to my family members for their unconditional love and constant support. I thank my wife (Lingling Zhuang) for resigning her job with Intel (Shanghai) and accompanying me to Blacksburg for years. She may not be conversant with my research area but she understands me and has always been there for me no matter what. I thank my lovely baby boy, Kenneth Yichen Wang. He brings happiness and joys to my life everyday. I thank my parents-in-law (Guizhang Zhuang and Cuihua Wang) for taking

care of my newborn baby. Without them, it would have been impossible for me to finish my study in time. I appreciate my parents (Mingren Wang and Shibao Zhu) and grandfather (Zhangxiu Wang) for their understanding and tolerance in accepting my absence from home for all these years. I appreciate my sisters (Xuewei Wang and Xueping Wang) for taking care of my parents and grandfather when I have not been around. I would like to dedicate this dissertation to my family members, as an infinitesimal return for their love and support.

# Table of Contents

| Chapter 1: Introduction                                                      | 1            |

|------------------------------------------------------------------------------|--------------|

| 1.1 Background and motivation                                                | 1            |

| 1.2 Scope of dissertation                                                    | 7            |

| 1.3 Research methodology                                                     | 9            |

| 1.4 Research objectives                                                      |              |

| 1.5 Organization of dissertation                                             | 11           |

| Chapter 2: Minimizing Total Completion Time for Single Machine MLCS          | P with       |

| Single-Wafer-Processing-Technology (MLCSP1)                                  |              |

| 2.1 Introduction                                                             |              |

| 2.2 Literature review                                                        |              |

| 2.2.1 Multiple-Order-per-Job (MOJ) problem                                   | 17           |

| 2.2.2 Batching and scheduling problem                                        |              |

| 2.2.3 Bin packing (BP) problem                                               |              |

| As described in Section 2.1, the bin packing problem is a part of the MLCS   | SP           |

| problem for carrier formation. The presence of the bin packing proble        | em within    |

| the context of the MLCSP makes it a more difficult problem to addre          | ss; and it   |

| is thus more amenable for the use of a heuristic for its solution            |              |

| 2.3 Model formulation and development of some structural properties          |              |

| 2.4 A problem with infinite FOUP capacity                                    |              |

| 2.4.1 Some structural properties                                             |              |

| 2.4.2 Optimal solution for the lots of the same size                         |              |

| 2.4.3 An algorithm for the case of lots of different sizes                   | 40           |

| 2.5 A problem with finite FOUP capacity                                      | 44           |

| 2.5.1 Optimal solution for the MLCSP1 with lots of the same size             |              |

| 2.5.2 A branch-and-bound algorithm for the MLCSP1 with lots of differen      | t sizes . 45 |

| 2.6 Numerical experimentation                                                | 51           |

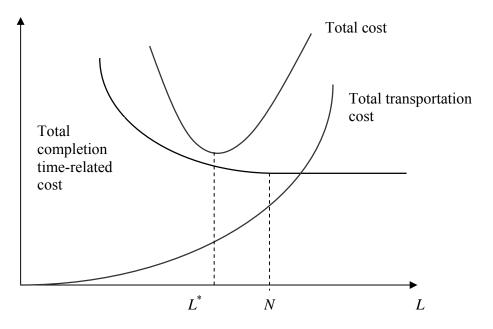

| 2.7 Determination of optimal number of carriers L considering transportation | cost 56      |

| 2.8 Conclusions                                                              | 57           |

| Chapter 3: Minimizing Total Completion Time for Single Machine MLCSP with       | a     |

|---------------------------------------------------------------------------------|-------|

| Single-Carrier-Processing-Technology (MLCSP2)                                   | 59    |

| 3.1 Introduction                                                                | 59    |

| 3.2 A mathematical model for the MLCSP2                                         | 59    |

| 3.3 Structural properties                                                       | 62    |

| 3.4 Determination and analysis of a lower bound and an upper bound              | 66    |

| 3.4.1 Determination of a lower bound                                            | 66    |

| 3.4.2 Determination of an upper bound                                           | 68    |

| 3.5 Conclusions                                                                 | 69    |

| Chapter 4: Minimizing Makespan for a 2-machine Flow Shop                        | 70    |

| MLCSP with Single-Wafer-Processing (MLCSP3)                                     | 70    |

| 4.1 Introduction                                                                | 70    |

| 4.2 Methodology for the solution of MLCSP3                                      | 70    |

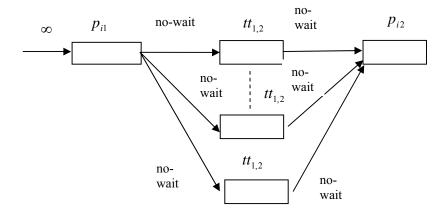

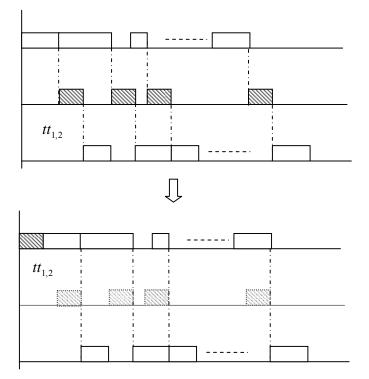

| 4.2.1 An equivalent lot streaming problem                                       | 74    |

| 4.2.2 Solution methodology for MLCSP3-2                                         | 76    |

| 4.3 Lots with identical processing times ( $\rho_{ij} = \rho_j$ , $c_i = c$ )   | 78    |

| 4.3.1 Uncapacitated sublot sizes                                                | 78    |

| 4.3.2 Capacitated sublot sizes                                                  | 80    |

| 4.4 Lots with different processing times                                        | 82    |

| 4.4.1 Same ratio of processing time per wafer on machine 2 to that on machine 1 | 1     |

| $(c_i = c) \dots$                                                               | 84    |

| 4.4.2 Different ratios of processing times of products on machine 2 to those on |       |

| machine 1 $(c_i \neq c_j)$                                                      | 96    |

| 4.5 Adjustment heuristics                                                       | . 109 |

| 4.5.1 Lots with the same ratio of processing times $(c_i = c)$                  | . 109 |

| 4.5.2 Lots with different ratios of processing times $(c_i \neq c_j)$           | . 110 |

| 4.6 Numerical experimentation                                                   | . 112 |

| 4.7 Conclusions                                                                 | . 115 |

| Chapter 5: Minimization of Makespan for an Integrated AMHS and Lot Schedu       | ıling |

| Problem (IMHLSP) with Infinite Vehicle Capacity                                 | . 117 |

|                                                                                 |       |

| 5.1 Introduction                                                            | 117          |

|-----------------------------------------------------------------------------|--------------|

| 5.1.1 Important control issues of an AMHS                                   | 119          |

| 5.1.2 Lot scheduling                                                        | 120          |

| 5.1.3 Integration of lot delivery and scheduling                            | 121          |

| 5.1.4 Problem statement                                                     | 123          |

| 5.2 Literature review                                                       |              |

| 5.2.1 The IMHLSP in 200 mm fabs                                             |              |

| 5.2.2 The IMHLSP in 300 mm fabs                                             | 125          |

| 5.2.3 The IMHLSP in other domains                                           | 129          |

| 5.2.4 Conclusions                                                           | 133          |

| 5.3 Problem classification and mathematical models                          |              |

| 5.3.1 AMHS Operating Model                                                  |              |

| 5.3.2 Mathematical models                                                   |              |

| 5.4 Solution methodologies                                                  | 141          |

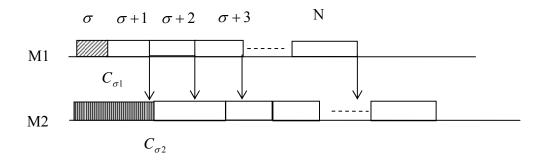

| 5.4.1 Infinite buffers                                                      | 143          |

| 5.4.2 Zero buffer                                                           |              |

| 5.4.3 Limited buffer of size b                                              |              |

| 5.5 Numerical experimentation                                               |              |

| 5.6 Extension to multiple-machine intrabay and the entire interbay/intrabay | y AMHS 166   |

| 5.7 Conclusions                                                             |              |

| Chapter 6: Minimization of Makespan for Integrated Automated Materi         | ial Handling |

| and Lot Scheduling Problem (IMHLSP) with Finite Vehicle Capacity            | 169          |

| 6.1. Introduction                                                           |              |

| 6.2. Mathematical Models for the IMHLSP with finite vehicles                |              |

| 6.3 RTD (Real Time Dispatching) rules                                       | 174          |

| 6.3 One-machine IMHLSP problem                                              |              |

| 6.3.1 One-vehicle zero-buffer problem                                       |              |

| 6.3.2 One-vehicle one-buffer problem                                        |              |

| 6.3.3 One-vehicle two-buffer problem                                        |              |

| 6.3.4 Two-vehicle zero-buffer problem                                       |              |

| 6.3.5 Two-vehicle one-buffer problem                                        |              |

| 6.5 Two-machine integration problem        |  |

|--------------------------------------------|--|

| 6.5.1 Zero-buffer problem                  |  |

| 6.5.2 One-buffer problem                   |  |

| 6.6 General AMHS system                    |  |

| 6.6.1 Direct model                         |  |

| 6.6.2 Segregate model                      |  |

| 6.7 Conclusions                            |  |

| Chapter 7: Conclusions and Future Research |  |

| 7.1 Conclusions                            |  |

| 7.2 Future research                        |  |

| References                                 |  |

# List of Figures

| Figure 1.1: The stages of semiconductor manufacturing                                        | 2    |

|----------------------------------------------------------------------------------------------|------|

| Figure 1.2: A simplified 16-step production process with re-entrant flow in wafer            |      |

| fabrication                                                                                  | 3    |

| Figure 1.3: Market forecast by wafer size                                                    | 4    |

| Figure 1.4: Increasing cost of wafer fabs                                                    | 4    |

| Figure 1.5: The decision making hierarchy in wafer fabs                                      | 5    |

| Figure 1.6: The decision making hierarchy in wafer fabs                                      | 9    |

| Figure 1.7: The decision making hierarchy in wafer fabs                                      | . 10 |

| Figure 2.1: The usable area of a 300mm wafer is over twice that of a 200mm wafer             | . 12 |

| Figure 2.2: A front-opening unified pod (FOUP)                                               | . 13 |

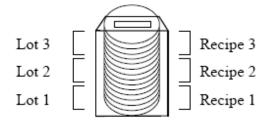

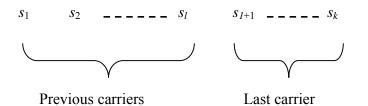

| Figure 2.3: Multiple-lots-per-carrier                                                        | . 14 |

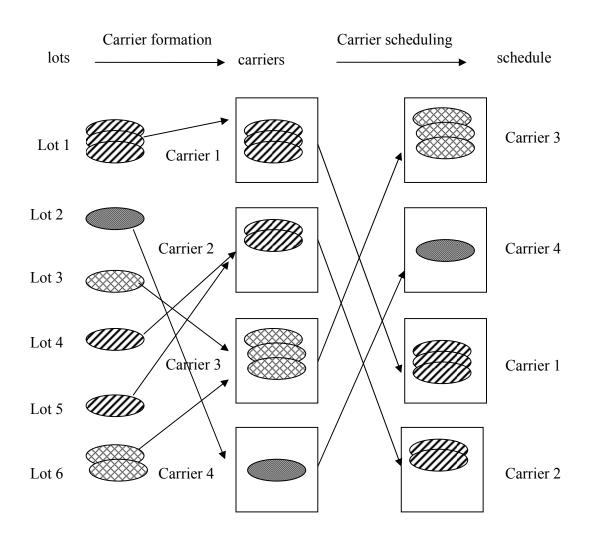

| Figure 2.4: Illustration of the MLCSP                                                        | . 15 |

| Figure 2.5: Schedule S' with insertion of carrier <i>l</i> in front of carrier <i>k</i>      | . 24 |

| Figure 2.6: The relationship between the number of carriers and total completion time        | . 26 |

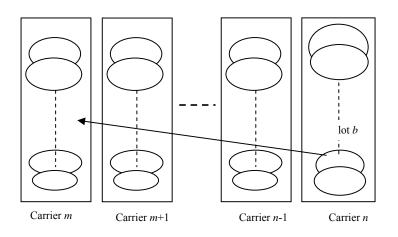

| Figure 2.7: A switch of lot <i>a</i> and lot <i>b</i> between carriers <i>m</i> and <i>n</i> | . 28 |

| Figure 2.8: Schedule S' with lot b removed from carrier n and included in carrier m          | . 30 |

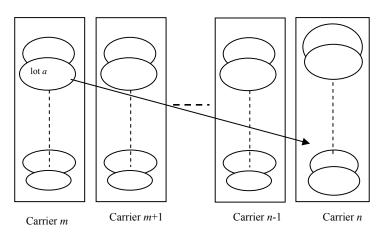

| Figure 2.9: Schedule S' with a lot a removed from carrier m and included in carrier n        | . 32 |

| Figure 2.10: Schedule S' with lot $b$ removed from carrier $n$ and included in carrier $m$   | . 34 |

| Figure 2.11: Schedule S' with a lot $a$ removed from carrier $m$ and included in carrier $n$ | . 36 |

| Figure 2.12: The distribution of the number of lots in each carrier                          | . 37 |

| Figure 2.13: Illustration of the impact due to a change in carrier size                      | . 38 |

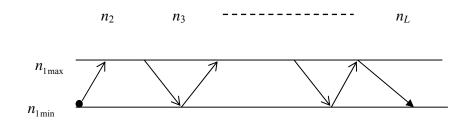

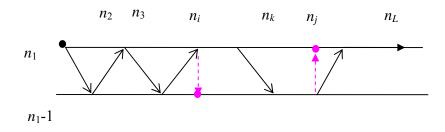

| Figure 2.14: The forward DP recursion                                                        | . 41 |

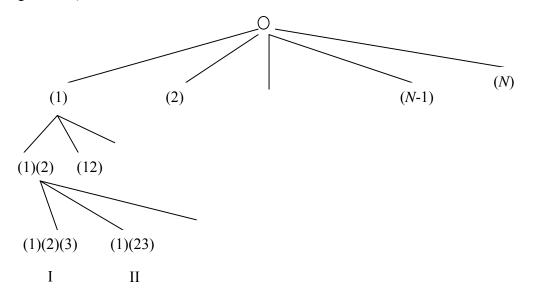

| Figure 2.15: Methods I and II for adding a lot to a carrier                                  | . 46 |

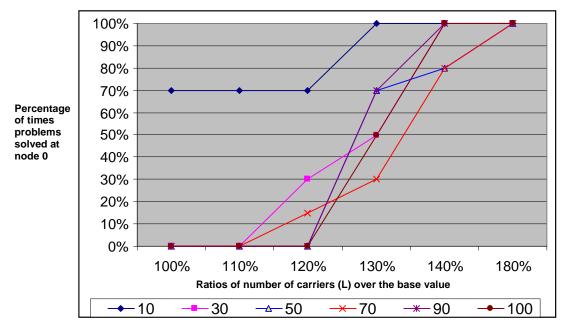

| Figure 2.16: Percentage of times MLCSP1-B&B solves the problem at node 0 as with             |      |

| increasing number of carriers (L)                                                            | . 54 |

| Figure 2.17: Relationship between total completion time-related, transportation, and to      | otal |

| costs with number of carriers L                                                              | . 56 |

| Figure 3.1: Transformation of the original problem to the GAP                                | . 61 |

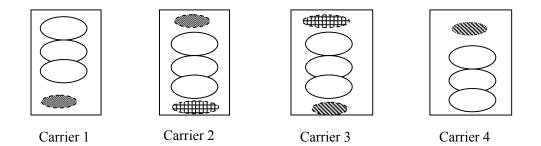

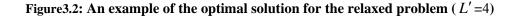

| Figure 3.2: An example of the optimal solution for the relaxed problem $(L'=4)$                   | 67   |

|---------------------------------------------------------------------------------------------------|------|

| Figure 3.3: An example for the adjustment of the optimal solution for the relaxed                 |      |

| problem ( $L' = 4$ )                                                                              | 67   |

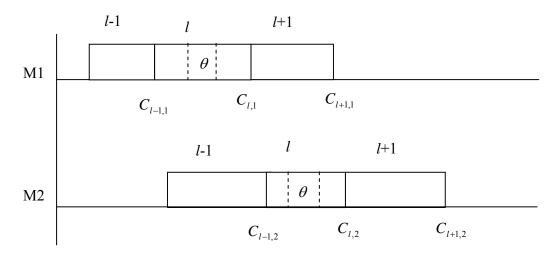

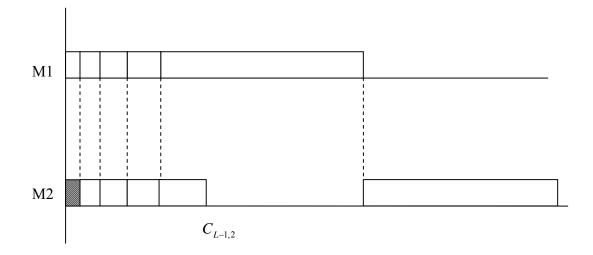

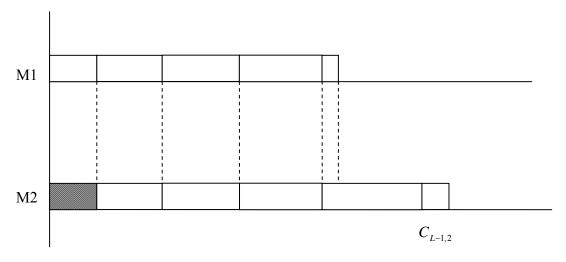

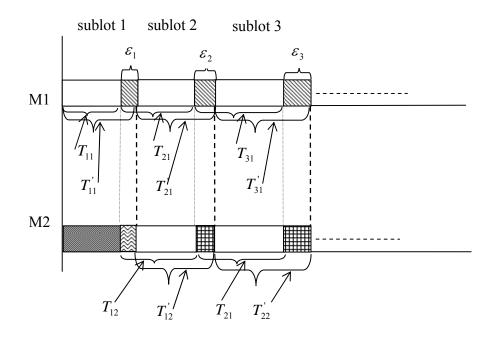

| Figure 4.1: Schedule S with an empty carrier                                                      | 73   |

| Figure 4.2: Schedule S' when none of the carriers is empty                                        | 74   |

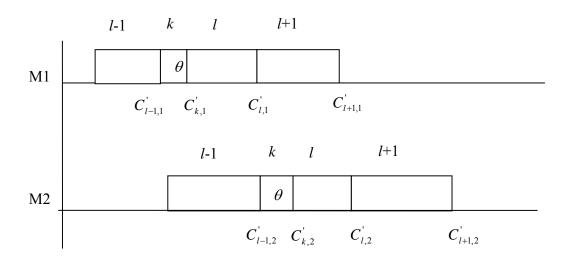

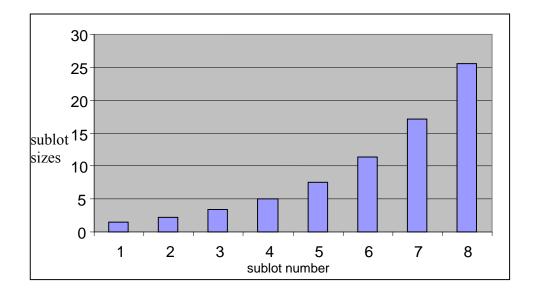

| Figure 4.3: Flow chart of the heuristic procedure for the MLCSP3                                  | 77   |

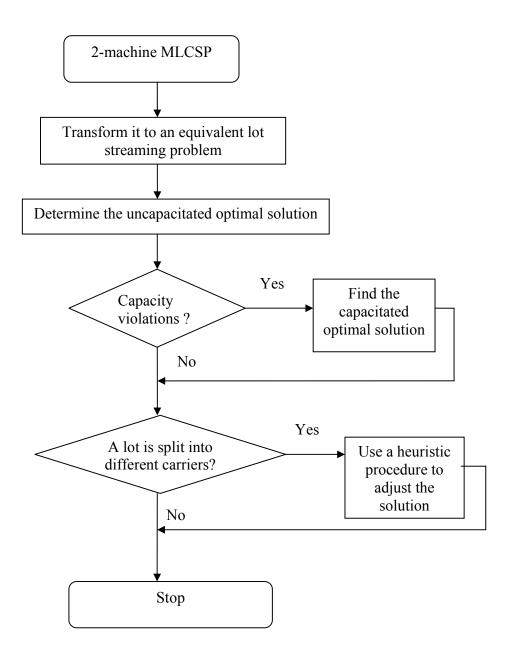

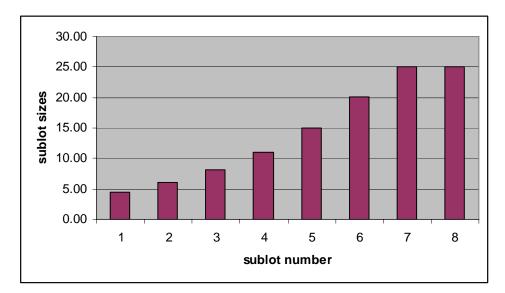

| Figure 4.4: Sublot sizes for <i>c</i> =1.25 and <i>L</i> =8                                       | 79   |

| Figure 4.5: Compact block structure of optimal sublot sizes                                       | 79   |

| Figure 4.6: An illustration of the optimal capacitated sublot sizes with $c=1.25$ and $L=8$       | 3 81 |

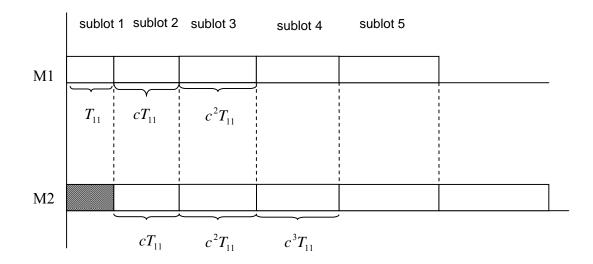

| Figure 4.7: The geometric distribution of the processing times                                    | 87   |

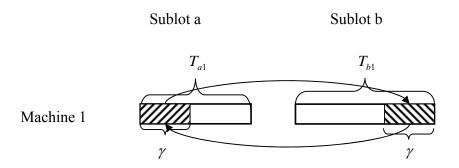

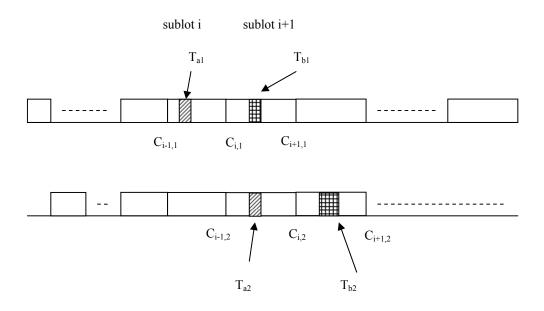

| Figure 4.8: Exchange of parts from sublots <i>a</i> and <i>b</i> with processing time of $\gamma$ | 90   |

| Figure 4.9: Construction of another solution S'                                                   | 94   |

| Figure 4.10: Exchange of products between sublots <i>a</i> and <i>b</i>                           | 98   |

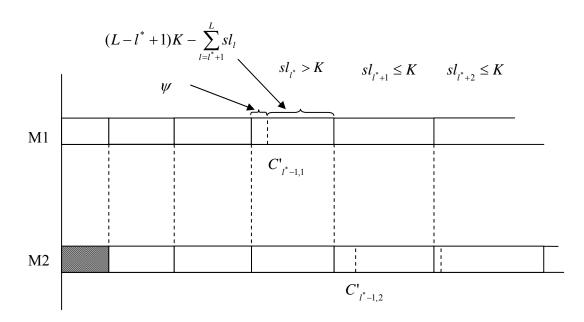

| Figure 4.11: A compact schedule if the first sublot is small                                      | 100  |

| Figure 4.12: A compact schedule if the first sublot size is large                                 | 100  |

| Figure 4.13: The change in the compact block structure when $sl_1$ increases                      | 103  |

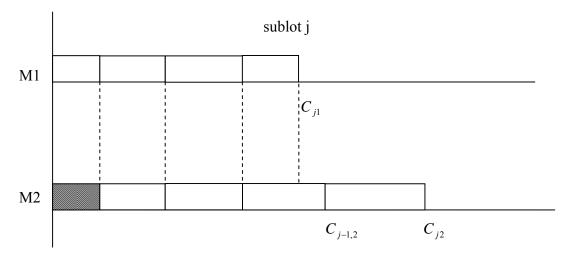

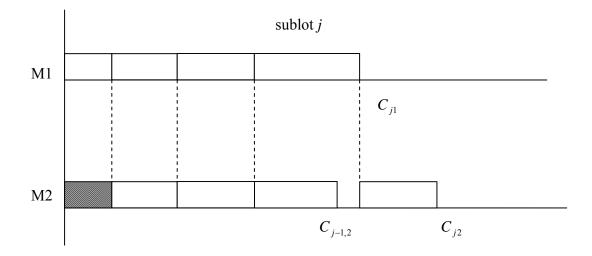

| Figure 4.14: The schedule when $C_{j-1,2} > C_{j1}$                                               | 104  |

| Figure 4.15: The schedule when $C_{j-1,2} < C_{j1}$                                               | 105  |

| Figure 5.1: A front opening unified pod (FOUP)                                                    | 117  |

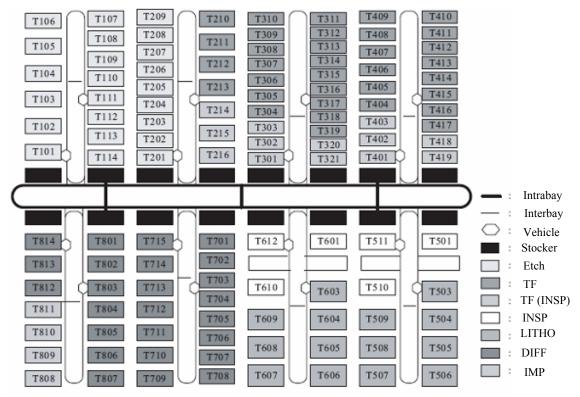

| Figure 5.2: A snapshot of AMHS in a 300mm fab                                                     | 118  |

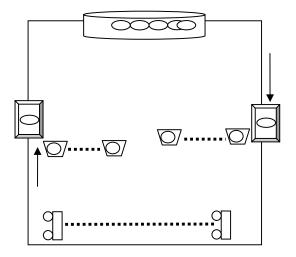

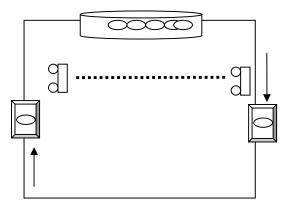

| Figure 5.3: A simplified AMHS layout                                                              | 118  |

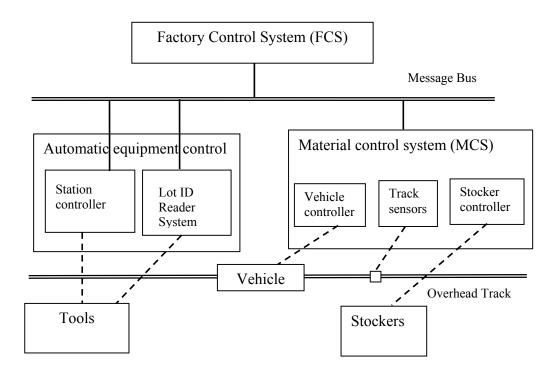

| Figure 5.4: The FCS and MCS control framework                                                     | 121  |

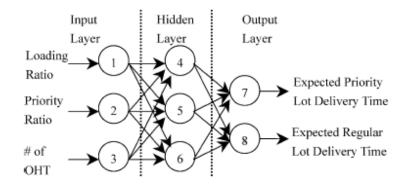

| Figure 5.5: A three-layer neural-network model                                                    | 128  |

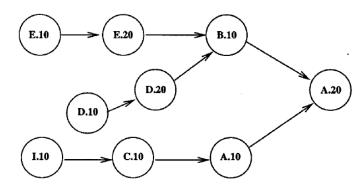

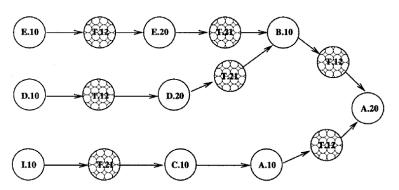

| Figure 5.6: The operational network for a complex product                                         | 132  |

| Figure 5.7: The operational network for a complex product including the transportation            | n    |

| operation                                                                                         | 132  |

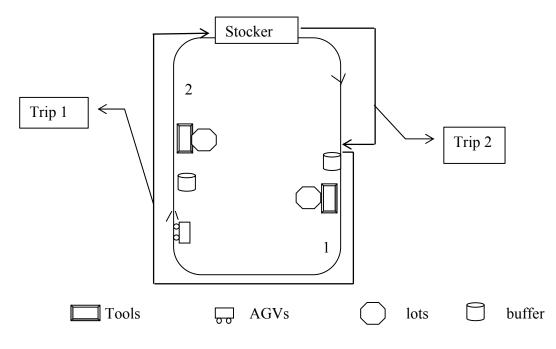

| Figure 5.8: A segregate model                                                                     | 134  |

| Figure 5.9: A direct model                                                                        | 135  |

| Figure 5.10: A model for the entire AMHS                                                          | 137  |

| Figure 5.11: An intrabay AMHS with infinite buffers                                               | 143  |

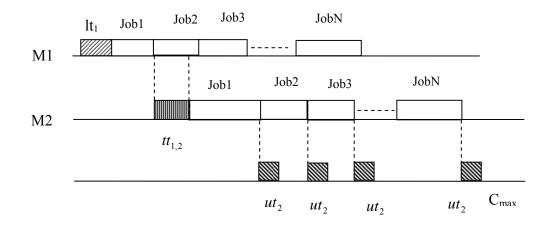

| Figure 5.12: The optimal makespan for direct model with infinite buffers           | 144 |

|------------------------------------------------------------------------------------|-----|

| Figure 5.13: An intrabay AMHS for zero buffers                                     | 145 |

| Figure 5.14: A illustration of segregate model for zero buffer at machine 2        | 146 |

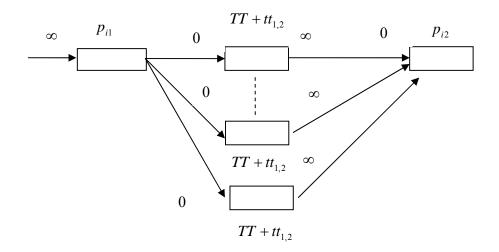

| Figure 5.15: An illustration of the intrabay direct AMHS model with zero buffer    | 148 |

| Figure 5.16: Transformation of the direct model to a no-wait 2-machine flow shop   | 149 |

| Figure 5.17: An illustration of the weak hybrid model                              | 152 |

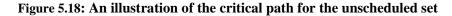

| Figure 5.18: An illustration of the critical path for the unscheduled set          | 159 |

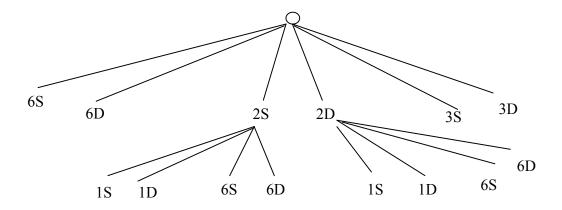

| Figure 5.19: An illustration of node generation for the proposed Strong-B&B algori | thm |

|                                                                                    | 160 |

| Figure 5.20: The case in which node ID-JD is fathomed                              | 161 |

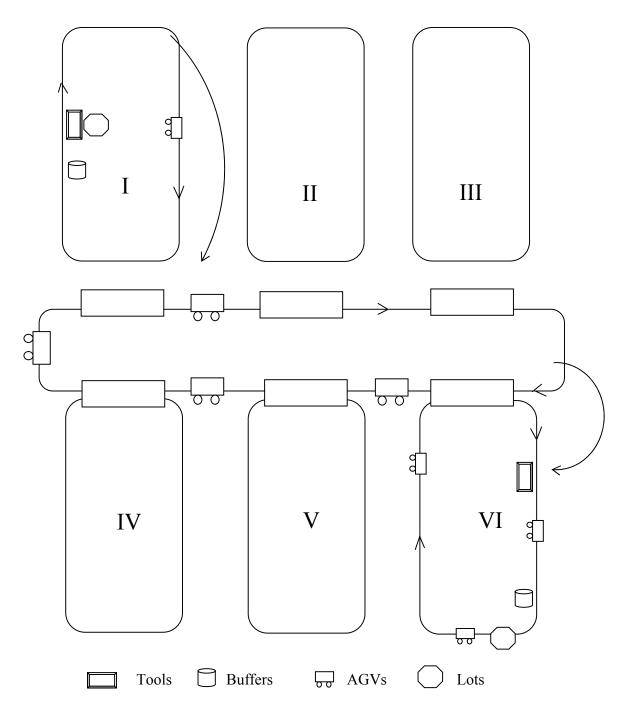

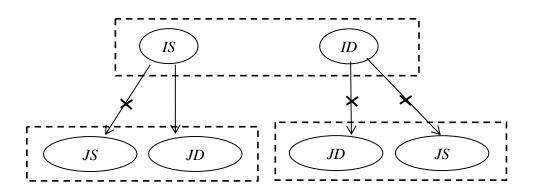

| Figure 5.21: An illustration of the multiple-machine intrabay AMHS                 | 166 |

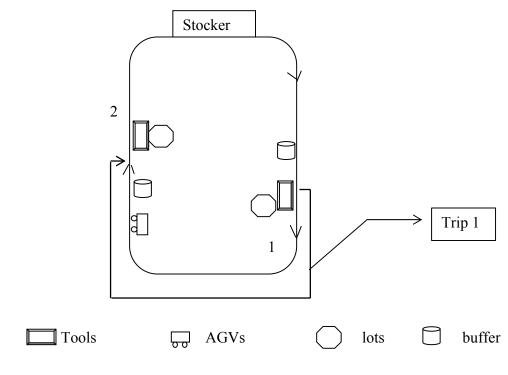

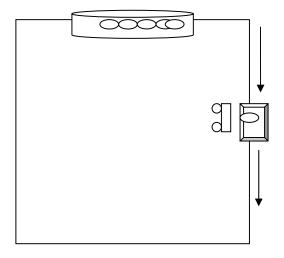

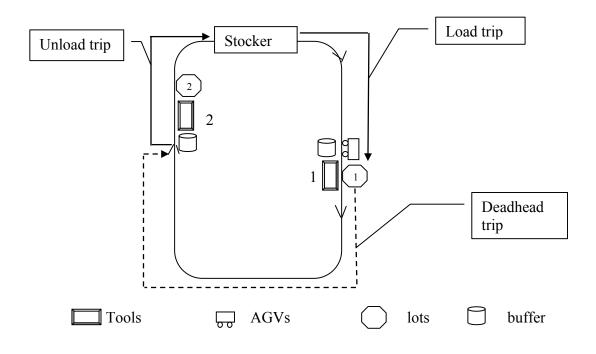

| Figure 6.1: One-machine, one-vehicle zero-buffer problem                           | 177 |

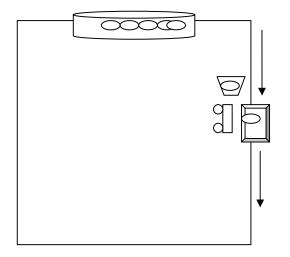

| Figure 6.2: One-machine, one-vehicle one-buffer problem                            | 178 |

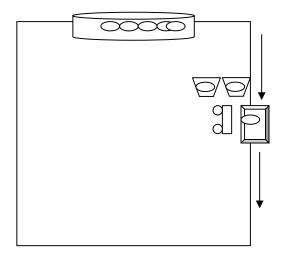

| Figure 6.3: One-machine, one-vehicle two-buffer problem                            | 180 |

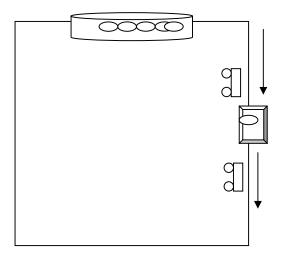

| Figure 6.4: One-machine, two-vehicle zero-buffer problem                           | 182 |

| Figure 6.5: One-machine, two-vehicle one-buffer problem                            | 184 |

| Figure 6.6: Illustration of the LS policy                                          | 186 |

| Figure 6.7: Two-machine, one-vehicle zero-buffer problem                           | 187 |

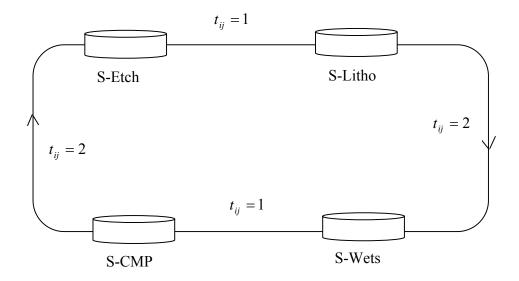

| Figure 6.8: A simple interbay AMHS system                                          | 198 |

# List of Tables

| Table 1.1: Descriptions of the four sub-problems of the MLCSP                     | 8   |

|-----------------------------------------------------------------------------------|-----|

| Table 2.1: An example to illustrate RelaxFOUP-DP algorithm                        | 41  |

| Table 2.2: Data used in numerical experimentation for problem MLCSP1              | 52  |

| Table 2.3: The average cpu times required to find optimal solutions by MLCSP1-B&  | zВ  |

| and the AMPL CPLEX 10.1 solver                                                    | 53  |

| Table 2.4: Percentage of times MLCSP1-B&B solves the problem at node 0            | 55  |

| Table 3.1: Data for a counter example ( $\rho = 1$ )                              | 63  |

| Table 3.2: An optimal solution to the bin packing problem                         | 63  |

| Table 3.3: An optimal solution to the original problem                            | 64  |

| Table 4.1: Data for Example 4-1                                                   | 97  |

| Table 4.2: Schedule for Example 4-1 obtained by applying the above procedure      | 97  |

| Table 4.3: Data used in numerical experimentation for problem MLCSP3              | 112 |

| Table 4.4: The experimental results for the solution of MLCSP3 when the lots have | the |

| same ratio of processing times <sup>†</sup>                                       | 113 |

| Table 4.5: The experimental results for the solution of MLCSP3 when the lots have |     |

| different ratios of processing times <sup><math>\dagger</math></sup>              | 113 |

| Table 4.6: The experimental results for the solution of MLCSP3 when the lots have | the |

| same ratio of processing times <sup>†</sup>                                       | 115 |

| Table 4.7: The experimental results for the solution of MLCSP3 when the lots have |     |

| different ratios of processing times <sup><math>\dagger</math></sup>              | 115 |

| Table 5.1: Data for Example 1                                                     | 151 |

| Table 5.2: Data for Example 2                                                     | 151 |

| Table 5.3: Data used in numerical experimentation                                 | 163 |

| Table 5.4: The average cpu times required to find optimal solutions by Strong-B&B | and |

| the AMPL CPLEX 10.1 solver for strong hybrid model with intrabay movements        | 164 |

| Table 5.5: The average cpu times required to find optimal solutions by Strong-B&B | and |

| the AMPL CPLEX 10.1 solver for strong hybrid model with interbay movements        | 165 |

| Table 6.1: The most common RTD rules used in 300mm fabs                           | 174 |

| Table 6.2: The travel time $t_{ij}$ matrix                                |     |

|---------------------------------------------------------------------------|-----|

| Table 6.3: Our recommended RTD rules and the RTD rules used in 300mm fabs | 200 |

# Chapter 1: Introduction

#### 1.1 Background and motivation

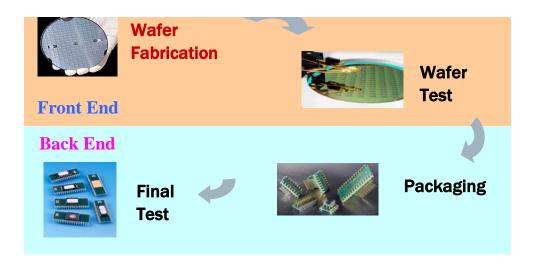

Semiconductor manufacturing is the process of creating integrated circuits (ICs), or chips, that are used in a variety of electrical and electronic devices. The process starts from a pure semiconductor material (the most commonly used material is silicon) and ends with packaged chips ready for shipment to customers. It consists of four main stages: wafer fabrication, wafer test, packaging and final test (see Figure 1.1). The manufacturing of wafers in which a cylindrical ingot (high purity crystalline silicon) is sliced with an inner diameter diamond coated blade and polished to form wafers, is usually done by a specialized company and is considered outside of these four stages. Wafer fabrication generally refers to the process of building integrated circuits on silicon wafers and is performed in highly specialized facilities referred to as fabs. Wafer testing takes place in between various processing steps and verifies if the wafers are good for acceptance or are damaged from previous processing steps, and need repair or are to be disposed of. Next, a wafer is broken into individual die and each undergoes requisite processes and becomes a device which is able to perform the functions for which it is designed. This is the packaging stage. Finally, the devices are subjected to a variety of electrical tests to determine if they function properly. At the packaging and final test stages, the processing units are individual die (chips), and not a wafer. Thus, wafer fabrication and wafer test are usually referred to as front-end processing while packaging and final test are called back-end processing (Plummer et al. 2000).

Figure 1.1: The stages of semiconductor manufacturing

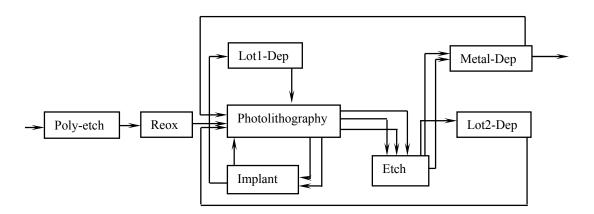

Of the four stages, wafer fabrication requires the longest time (usually 6 to 8 weeks), uses the most resources, and is the most value-added stage. More importantly, wafer fabrication has been called one of the most complex processes in the manufacturing domain. A single product may contain as many as 1600 steps and a fab can produce as many as 200 products. Machines differ widely from each other. Some are capable of only serial processing, such as photolithography and etching, while others permit batch processing, such as furnaces and ovens used in diffusion, oxidation and ion implantation. Processing times can vary from 1 hour to 24 hours depending on the process involved, and sequence-dependent setups are not unusual. Wafers are built in layers with each layer undergoing sophisticated processing at multiple processors, like steppers. As these machines are rather expensive (up to 30 million dollars), there are only a very limited number of them in a fab. Therefore, wafer lots have to revisit these machines for the processing of different layers. This gives rise to the characteristic re-entrant flow, with wafers at different stages of processing having to compete for time on the same machine (see Figure 1.2). Specific requirements for the lots, such as lot dedication to ensure that all (or at least critical) layers of a lot are processed at the same stepper only add to the complexity of the situation.

Figure 1.2: A simplified 16-step production process with re-entrant flow in wafer fabrication

The capital expense for a wafer fab (most of which is for equipment) can be as high as 3 billion dollars. Furthermore, the equipment is, typically, replaced with newer generations in  $5\sim10$  years. Thus, in order to gain profits from this huge investment, wafer fabs must utilize the equipment as much as possible. On the other hand, the semiconductor industry is also facing strong competition. Most of the players have identical abilities to undertake research and development of new products (except for Intel, which has unmatched advantage over its competitors (Wilson 2007)). Thus, to survive in the market, fabs must be able to reduce manufacturing costs. The following three methods have been implemented to reduce manufacturing costs in fabs.

## (i) Achievement of economic of scale

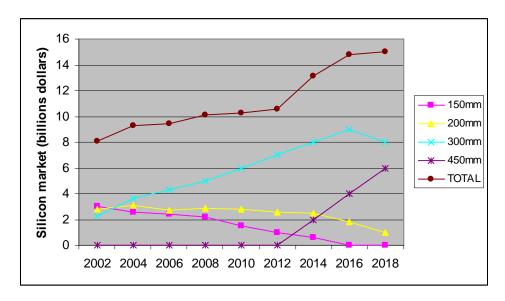

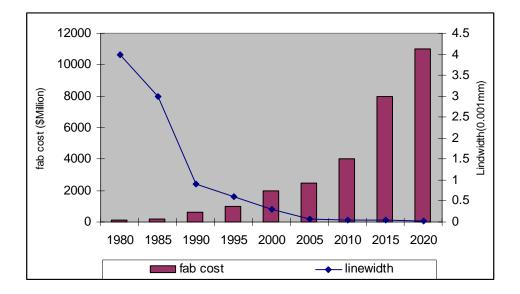

When wafer size (the diameter of a wafer) increases, the number of dies or chips that are built on the wafer increases dramatically. Thus, the number of chips produced increases without using more wafers. Consequently, the cost per chip decreases. Semiconductor manufacturers have been consistently experiencing this trend (see Figure 1.3) (SEMATECH 2005). On the other hand, increment of wafer size also leads to increment in investment on the equipment in the fab (see Figure 1.4) (SEMATECH 2005). This further increases the pressure of reducing manufacturing cost. Thus, this method itself is not enough to drive cost down.

Figure 1.3: Market forecast by wafer size

Figure 1.4: Increasing cost of wafer fabs (SEMATECH 2005)

### (ii) Applications of management science and operations research techniques

The application of industrial engineering/operation research techniques in wafer fabrication started four decades ago, almost from the day the first fab in the world was

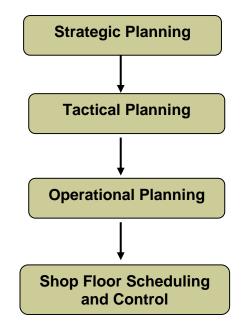

built. For the implementation of these techniques, a decision-making hierarchy is used, which comprises of four levels: strategic planning, tactical planning, operational planning and shop floor scheduling and control (see Figure 1.5). The strategic planning level pertains to long term decision making (generally for 3-10 years). The types of decisions that are considered at this level include selection of the location of a facility, determination of the required capacity, selection of products and technology to use. The tactical planning level addresses decisions over a shorter time horizon (generally from 6 months to 3 years). It includes determination of workforce levels, process routings and production rates. The operational planning level covers decisions that are made for a planning horizon of 1 week - 6 months. These include allocation of jobs to machines and determination of lot sizes in which to process the jobs, overtime usage, and amount of subcontracting/outsourcing. The lowest level, belonging to the shop floor operations, mostly involves decisions pertaining to the scheduling and control of work over a period that spans from real-time to one week. These also include determination of processing lot sizes, lot release strategies, processing sequence as well as the dispatching of lots to the machines (determination of starting times).

Figure 1.5: The decision making hierarchy in wafer fabs

#### (iii) Implementation of the Toyota Production System (TPS)

For more than 30 years, Toyota Motor Corporation has followed a production system that has enabled it to increase quality, double capacity, produce a wider variety of models in a given factory, and change the mix on a dime. In 2007, Toyota surpassed General Motors Corporation in becoming the largest automobile manufacturer in the world. But more importantly, Toyota's approach to mass production has produced bountiful profits. It became the first in the automobile history to gain profit over 10 billion dollars in one year. The Toyota Production System (TPS) is so successful that it has been widely applied in other industries, such as restaurant, aircraft manufacturing, banking and finance, among others.

After working hard on methods (i) and (ii) described above, and having not succeeded as expected, recently, scholars and executives found a glimmer of hope from the TPS. Christensen et al. (2008) have reported their innovative work to emulate the TPS, and have applied its principles to a logic fab belonging to an integrated device manufacturer (IDM). The four principle rules of the TPS, in summary, are (1) highly specify activities, (2) clearly define the transfer of material and information, (3) keep the pathway for every product and service simple and direct, and (4) detect and solve problems where and when they happen, using the scientific method (Spear and Bowen 1999). After 7 months, it is reported that the company was able to reduce the manufacturing cost per wafer by 12 percent and the cycle time by 67 percent, without investing in new equipment or changing product design.

It should be noted that there have not been many examples reported in the literature about successful implementation of the TPS in fabs, especially memory fabs. Logic and foundry fabs are high mix/high volume fabs, while a memory fab involves fewer products. The system which works well in a logic fab may not be promising in a memory fab, which is a low mix/high volume fab. However, we believe that the TPS will eventually bring new economics to semiconductor manufacturing while, at the current stage, it has just been a start.

#### **1.2 Scope of dissertation**

In this dissertation, we focus on the scheduling problems arising from the 300mm wafer fabs. Thus, it is a combination of methods (i) and (ii) (at the shop floor scheduling and control level of the decision making hierarchy) to reduce the manufacturing costs mentioned above. Two types of scheduling problems are addressed. The first of these is the multiple-lots-per-carrier scheduling problem (MLCSP). Since a 300mm wafer is much larger than a 200mm wafer, the size of a lot (a group of wafers processed in the fab as a non-split entity) may be less than the capacity of a carrier K (K=25 wafers). Therefore to reduce the number of carriers needed, which would save the cost of carriers, and more importantly, reduce the number of movements undertaken by the Automated Material Handling Systems (AMHS), one idea is to include more than one lot in a carrier, thus leading to the MLCSP. It involves decisions pertaining to which lots to include in the carrier as well as the sequence in which to process the carriers on the machines. Depending on the processing technology employed, number of machines involved, and the objective function used, the MLCSP can be further classified into four sub-problems: single-machine MLCSP with single-wafer-processing-technology and the objective of minimizing total completion time (MLCSP1), single-machine MLCSP with singlecarrier-processing-technology and the objective of minimizing total completion time (MLCSP2), two-machine flow shop MLCSP with single-wafer-processing-technology and the objective of minimizing makespan (MLCSP3), and two-machine flow shop MLCSP with single-carrier-processing-technology and the objective of minimizing the makespan (MLCSP4). MLCSP4 is equivalent to the bin packing problem, thus it is not considered in this study. These four sub-problems are summarized in table 1.1.

| Table 1.1 Descriptions of the four sub-problems of the MLCSP |           |                           |                  |              |

|--------------------------------------------------------------|-----------|---------------------------|------------------|--------------|

| Category                                                     | Number of | Machine processing        | Performance      | Presented in |

|                                                              | machines  | technology                | measure          | this study?  |

|                                                              |           |                           |                  |              |

| MLCSP1                                                       | 1         | Single wafer processing   | Total completion | Yes          |

|                                                              |           |                           | time             |              |

| MLCSP2                                                       | 1         | Single carrier processing | Total completion | Yes          |

|                                                              |           |                           | time             |              |

| MLCSP3                                                       | 2         | Single wafer processing   | Makespan         | Yes          |

| MLCSP4                                                       | 2         | Single carrier processing | Makespan         | No           |

Table 1.1 Descriptions of the four sub-problems of the MLCSP

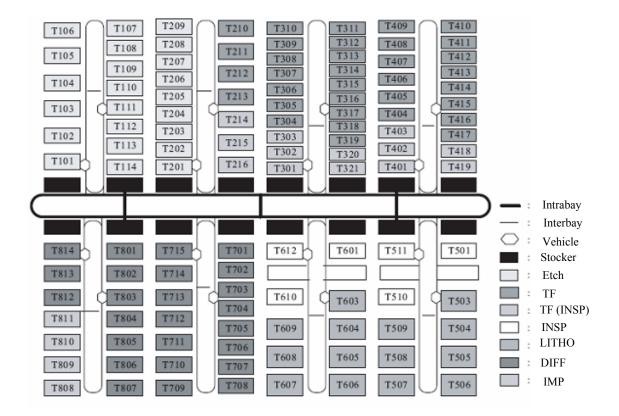

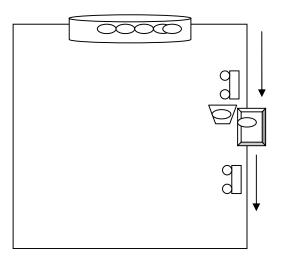

The second problem that we address is the integrated AMHS scheduling and lot scheduling problem (IMHLSP). A 300mm fab is also a fully automated fab where the AMHS is responsible for every movement of a lot from a machine to another machine or to a temporary storage (see Figure 1.6). Manual carrying of a carrier is minimized. The AMHS scheduling and lot scheduling is closely inter-related. Lot scheduling provides delivery requests and impacts operational control of the AMHS. The AMHS scheduling, especially vehicle scheduling, provides the release time for processing lots on downstream machines. Therefore, a schedule determined by integrating AMHS delivery issues and lot scheduling will perform better than that determined by considering these two aspects independently from the view point of overall fab performance metrics, such as cycle time, and throughput rate, among others. The IMHLSP can be further classified into two sub-problems: IMHLSP with infinite vehicle capacity and IMHLSP with finite vehicle capacity. If enough vehicles are operated in a 300mm fab, it can be viewed to operate under infinite vehicle capacity. Otherwise, we have the case of finite vehicle capacity. For both of these sub-problems, the decisions pertain to determining the sequence in which to process the lots on the machines and the movements of vehicles from one machine to another.

Figure 1.6 A simplified AMHS layout

## 1.3 Research methodology

This study mainly focuses on the scheduling level of the hierarchical structure described in Section 1.1. Therefore, we make the following two assumptions: (1) The fab planning has been in place. That is, the numbers of tools, tool layout, number of products and the desired fab throughput have all been determined. (2) The AMHS is at stable stage. This means that the AMHS is running well and does not need significant changes. The AMHS layout is not to be revised. The number of vehicles and vehicle routing are also known.

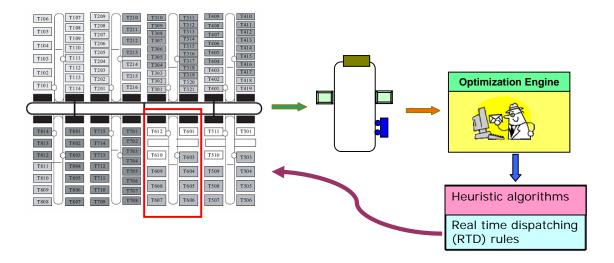

The scheduling problem in a 300mm fab is an extremely large-size problem. It involves hundreds of machines, thousands of processing steps, and work-in-process (WIP) of the order of tens of thousand of wafers. It is not realistic to study such a large-size problem as a whole. Thus, in this study, we start with a small-size problem. This small-size problem

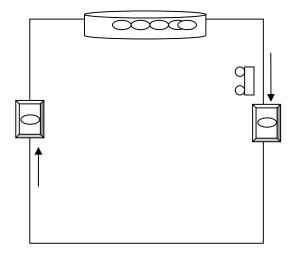

has one to two machines, and one to two vehicles. The advantage of focusing on the small-size problem is that it would enable identification of inherent properties that could potentially be exploited for the solution of large-size problems as well via the development of optimum seeking methods or real-time dispatching (RTD) rules. The graphical depiction of a wafer fab is shown in Figure 1.7. The fab, presented on the left, is approximated in our study by a system consisting of one or two machines. The solution methodology is depicted by blocks on the right side with their eventual implementation in the entire fab.

Figure 1.7 Schematic of the research methodologies in this study

#### **1.4 Research objectives**

The primary objective of our work is to provide insights and effective solution methodologies for the two types of new scheduling problems encountered in 300mm fabs, namely, MLCSP and IMHLSP. These two problems are faced in real-life environments and have drawn the attention of engineers and management teams. However, very few results have been reported on these problems. Through this dissertation research, we provide optimal or near-optimal solutions for these problems, which, at the same time, are easy to implement in real-life fabs. On the other hand, through this pioneering work, we hope to promote the interest of others as well to work further on these and related problems.

The specific objectives of our research work are as follows:

- To study the impact of including multiple lots in a carrier on the performance measure of total completion time and makespan, where the lots are processed either on a single machine or a two-machine flow shop, and the machines use either a single-wafer-processing technology or single-carrier-processing technology, and to develop efficient solution methodologies to determine an optimal formation of the carriers and the sequence in which to process them.

- To obtain insights into the integration of AMHS scheduling and lot scheduling for the cases with infinite and finite number of vehicles in the 300mm fabs, and to develop effective methodologies for solving small-size problems as well as to develop fast solution procedure for implementation in real-life fabs.

## 1.5 Organization of dissertation

The rest of this dissertation is organized as follows. In Chapter 2, we discuss the MLCSP1. After formulating the integer programming model, we present some structural properties as well as an efficient branch-and-bound algorithm to solve this problem. Chapter 3 addresses the MLCSP2. We determine a lower bound and upper bound for this problem. The worst case analyses are also presented for both of these bounds. In Chapter 4, we address the MLCSP3, which is first transformed to a two-machine flow shop lot streaming problem. After the lot streaming problem is solved optimally, heuristic procedures are used to transform the solutions obtained to a feasible solution to the original problem. We analyze the IMHLSP with infinite vehicle capacity in Chapter 5, and propose a new AMHS operation model, namely, the Strong Hybrid model. A branch-and-bound algorithm is presented to implement the Strong Hybrid model in a two-machine environment. In Chapter 6, we determine a closed-form expression for small-size IMHLSP for finite vehicle capacity, and recommend several real-time dispatching rules for real-size problems that rely on our analysis of the problem. Finally, we conclude this study in Chapter 7.

# Chapter 2: Minimizing Total Completion Time for Single Machine MLCSP with Single-Wafer-Processing-Technology (MLCSP1)

#### 2.1 Introduction

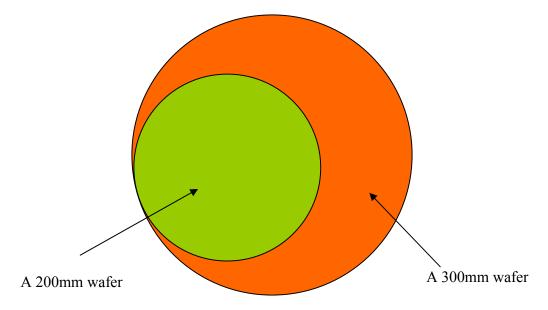

The latest generation of semiconductor wafer fabs produce Integrated Circuits (ICs) on silicon wafers of 300 mm diameter. The area of a 300 mm wafer is 2.25 times larger than that of an older generation 200mm wafer. Furthermore, 300mm wafers have over twice the usable area of 200mm wafers (please see Figure 2.1), thereby delivering up to 2.6 times the number of chips produced on a 200mm wafer (United Microelectronics Corporation 2008). This, in turn, requires use of fewer wafers to produce a certain number of chips.

Figure 2.1: The usable area of a 300mm wafer is over twice that of a 200mm wafer

Generally, there are two types of wafer fabs, namely, high volume/low mix, and high volume/high mix. Most of the memory-chip manufacturers belong to the first category, and include manufacturers like Qimonda, Micron, Samsung, among others. A high volume/low mix fab produces several products with 40k to 50k WSPM (Wafer Shipment

per Month). According to the ITRS (International Technology Roadmap for Semiconductors) (2006), a high mix fab can be characterized as follows: presence of more than 50 products with many in small lots of 1 - 10 wafers; and production of an average of less than 50 wafers between reticle changes for each lithography equipment. Examples of high volume/high mix fabs include ASIC (Application Specific Integration Circuit) fabs like Analog Devices, and foundries like TSMC (Taiwan Semiconductor Manufacturing Corporation).

The semiconductor industry has established an international standard to transfer wafers between tools in a 300 mm wafer fab. Wafers are carried by a FOUP (Front-Opening Unified Pod, Figure 2.2). This standard carrier has the capacity of 25 wafers. As noted earlier, in a high volume/high mix fab, there are many lots of small size with less than 25 wafers in them. If a FOUP holds only one such lot, it has great ramifications on the transactions and storage loading capabilities of the interbay and intrabay AMHS (Automated Material Handling System) (more information about the AMHS used in a 300mm fab can be found in Chapter 5). Besides, it reduces output of a workstation (as a result of more frequent loading/unloading operations performed).

Figure 2.2: A front-opening unified pod (FOUP)

One of the ways to address this issue and improve the output of a workstation of a high volume/high mix fab is to use multiple-lots-per-carrier (ITRS 2006 and 300 mm Integrated Vision for Semiconductor Factories 1999), as shown in Figure 2.3. This strategy aims to minimize the problems described above by loading similar lots, with potentially different processing conditions but with the same process flow, into one carrier. There are two ways of mixing lots under this strategy. One way is to combine lots with the same process flow, but with partially different processing conditions such as

metallization layers or wiring patterns. The second way is to combine more than one lot in a carrier, all of which have the same process flow, but some having additional process steps as optional processes. For the first alternative, a process equipment must have the capability to set different processing conditions (different recipes) for each lot or for a subset of the wafers in a carrier. For the second alternative, the process equipment used in the optional process step must have the capability to selectively process one or more wafers in a particular carrier, and leave the other wafers in the carrier unprocessed.

Figure 2.3: Multiple-lots-per-carrier

For the high volume/low mix fabs, there is no advantage of mixing production lots in a carrier. However, it is not uncommon to group engineering lots (i.e., new technology lots, or test lots) in a carrier in such a fab (Fu 2007). This is mainly due to small sizes of engineering lots (much less than 25 wafers, usually 1-3 wafers) as well as shorter completion time requirements.

We consider two types of dependencies between lot processing time and carrier processing time, namely, *single-wafer-processing* and *single-carrier-processing*. Single wafer processing occurs on various tools, such as a photolithography stepper, in which a single wafer is processed at-a-time. Thus, the processing time for a carrier depends on the total number of wafers of the lots in the carrier. Under single carrier processing, the carrier's processing time is independent of the number of wafers it holds. An example of single carrier processing is the operation of a wet sink, wherein the entire carrier (FOUP) of wafers is processed simultaneously when the carrier is submerged in a liquid solution.

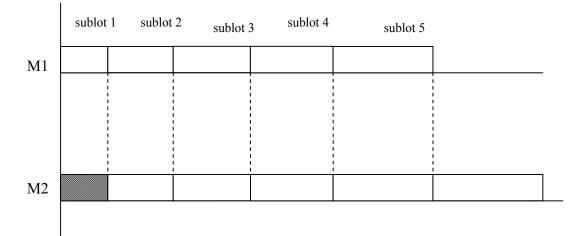

Figure 2.4: Illustration of the MLCSP

To tackle the multiple-lots-per-carrier scheduling problem (designated MLCSP) that is described above for the high volume/high mix fabs or for the special instances of the high volume/low mix fabs, we define it precisely as follows: given a number of partial lots, group them into a given or unrestricted number of carriers, and find a sequence in which to process the carriers on a machine in order to minimize a performance measure such as makespan or total completion time of the lots. The MLCSP is different from traditional scheduling problem in that it requires two types of decisions, namely, carrier formation and carrier sequencing. The formation of carriers from lots, and their sequence for processing by a machine (or a workstation) is depicted in Figure 2.4.

In this chapter, we address the single-machine MLCSP with single-wafer-processing, and designate it as MLCSP1. The performance measure that is considered is the total completion time of the lots. The single machine MLCSP with single-carrier-processing and for the objective of minimizing the total completion time, designated as MLCSP2, will be presented in Chapter 3, while the two-machine MLCSP with single-wafer-processing for the objective of minimizing the makespan, designated as MLCSP3, will be discussed in Chapter 4.

The rest of this chapter is organized as follows. In Section 2.2, we present the research work from the literature that is related to the MLCSP. We, then, formulate an integer programming model for this problem in Section 2.3. By relaxing the capacity of the FOUP, we first derive some useful properties. These properties are used to determine optimal solution for the case of same-size lots. For the case of different lot sizes, we propose a dynamic programming-based algorithm to obtain an optimal solution. This work is presented in Section 2.4. In the presence of limited FOUP capacity (i.e., the original problem), when all the lots are of the same size, the optimal solution for the case when the FOUP capacity is relaxed, is also optimal for this case. When the lots of different sizes are considered, the problem becomes difficult to solve, and we develop a branch-and-bound algorithm for its solution. It relies on a lower bound found by using the DP-algorithm presented in Section 2.4. This work is presented in Section 2.5. Results of our computational experimentation on the use of the proposed branch-and-bound method for the solution of our problem are presented in Section 2.6. In Section 2.7, we explore determination of optimal total cost if the number of carriers is not given. Finally, we conclude this chapter in Section 2.8.

### 2.2 Literature review

The semiconductor industry has transited from a 200 mm fab to a 300 mm fab. As a result, there are many new scheduling problems related to the 300 mm fabs that are still open. To the best of our knowledge, there has not been any study conducted on the MLCSP problem. However, a similar problem, called multiple-orders-per-job (MOJ)

problem, has been addressed in the context of a 300 mm fab by several researchers. Also, the traditional batching and scheduling problem, which has been addressed extensively in the literature, is related to the MLCSP. In addition, the carrier formation part of the MLCSP problem is similar to the bin packing problem. We, briefly, review work on these problems next.

#### 2.2.1 Multiple-Order-per-Job (MOJ) problem

The Multiple-Order-per-Job (MOJ) problem has been addressed by Qu (2004). He developed a nonlinear integer programming model for the general MOJ problem, which was then reformulated as a linear integer programming (IP) model for the objective of minimizing the total weighted tardiness in a single-machine environment. A number of heuristic approaches, including genetic algorithm (GA) and tabu search (TS), were employed due to computational intractability of the IP model. He has presented experimental results, which demonstrate that their heuristic approaches can find good quality solutions in a reasonable amount of computational time. Similar results can be found in Qu and Mason (2004a, 2004b and 2005), and Kutanoglu et al. (2004).

In a follow-up work, Erramilli and Mason (2006) investigated the MOJ problem in a single batch-processing machine environment. The objective of their study was to minimize the total weighted tardiness of orders. They developed a mixed integer programming model for the problem. A new simulated annealing-based heuristic is used, which is demonstrated to solve the problem within 4% of optimality in a few minutes.

Laub et al. (2007) have extended the MOJ problem to a two-machine flow shop. A heuristic procedure was proposed to minimize the makespan. First, the heuristic procedure relaxes the constraint that the entire order can only be assigned to one job. The relaxed problem becomes a two-machine lot streaming problem, which can be solved easily. The optimal solution to the lot streaming problem is a lower bound for the original problem. Using the heuristic procedure, the orders are re-assigned to the jobs so that one

entire order is assigned to only one job. It has been shown that this heuristic procedure obtains solutions within 2% of the lower bound.

It should be noted that even in a foundry fab, it cannot be guaranteed that all or a large percent of customer orders will be less than 25 wafers. When a customer order is larger than 25 wafers, we can not simply separate it into two parts: the splinters (leftover items after an order is divided by 25) and the entire carriers (consisting of 25 wafers), and then, schedule them separately, with the splinters possibly grouped with other splinters. Thus, the MOJ problem actually addresses a scenario which may have limited realistic applications.

The MOJ problem also assumes that all the orders require the same processing times. However, for the MLCSP, lots in the same carrier may require different processing conditions (and as a result different processing times) as described in section 2.1 and studied in Chapter 4. Thus, even though the MLCSP is different from the MOJ problem, yet the MOJ problem can provide useful insights for our study of the MLCSP.

### 2.2.2 Batching and scheduling problem

Another type of problem which is related to the MLCSP is batching and scheduling problem. The motivation for batching the jobs is to gain efficiency because it may be cheaper or faster to process the jobs in a batch than to process them individually. In a *family scheduling model*, jobs are partitioned into families according to their similarity so that no setup is required for a job if it belongs to the family of the previously processed jobs (see Potts and Kovalyov (2000), and Webster and Baker (1995)). In this model, a batch is a maximal set of jobs that are scheduled contiguously on a machine and share a setup.

There are two variants of the family scheduling model depending on when the jobs become available (either for dispatching to a customer or for processing on the next machine). Under *batch availability*, a job becomes available only when the complete

batch to which it belongs has been processed. An alternative assumption is *job availability* (i.e., *item availability*), in which a job becomes available immediately after its processing is completed.

Another batching situation is when *a batching machine* is capable of processing several jobs simultaneously. This is called *batch processing model*. Our MLCSP is similar to batch processing model. However, it differs in the following three ways:

- (1) the capacity of a batching machine is the maximum number of jobs that can be processed at any one time while the capacity of a carrier is the maximum number of wafers (not lots) the carrier can hold

- (2) in a batching machine, each job occupies the same capacity while in MLCSP, each lot will have different lot sizes

- (3) in a batching machine, the processing time of the batch is fixed and is independent of the number of jobs in the batch. This is called a *fixed* batch processor. For any regular performance measure, it is desirable to use batches of the maximum possible size for as long as possible. Such a schedule is called a *full-batch* schedule. A more complicated version is that in which the processing time of a batch is the longest among the processing times of the jobs in the batch. For MLCSP, the carrier processing time is either a fixed amount (single-carrier-processing) or is the sum of the processing times of the wafers in the carrier (single-wafer-processing).

In the literature, one special type of batch processing model, in which jobs have nonidentical sizes and no setup required in the context of a single machine environment, has been studied. When makespan is considered, Damodaran et al. (2006) have proposed a genetic algorithm for this problem, and have applied it to a set of randomly generated instances. The results obtained using their algorithm were compared with those obtained using a simulated annealing approach of Melouk et al. (2004) and a commercial solver. The results indicate that the proposed algorithm is able to arrive at near-optimal makespan values with shorter run times than those for the other approaches. For this same type of batch processing model, when the total completion time or mean flow times are considered, Uzsoy (1994) has presented a branch-and-bound procedure. However, the computational burden of this algorithm rapidly becomes excessive. Azizoglu and Webster (2000 and 2001) have proposed a branch-and-bound algorithm to minimize the total weighted completion time. This algorithm has been shown to generate optimal solutions to problems of up to 25 jobs in reasonable cpu times. Using results from the bin-packing problems, Uzsoy (1994) and Ghazvini and Dupont (1998) have suggested a number of heuristics for these problems. Computational experiments show that they are capable of rapidly obtaining near-optimal solutions. When incompatible job families are considered, Dobson and Nambimadom (2001) have presented an integer programming formulation, and have used it to generate a lower bound using a partial LP relaxation. Several heuristics have also been compared and analyzed in detail.

Besides the MOJ problem, batching and scheduling problem is another type of problem that is relevant to the MLCSP. Though they are different in several ways, the methodologies commonly used to analyze the batching and scheduling problem, such as branch-and-bound algorithm and dynamic programming (DP), can be adopted to our research.

### 2.2.3 Bin packing (BP) problem

The bin packing (BP) problem can be stated as follows: given a positive integer number of bins of capacity W and a list of n items of integer sizes  $L = \{l_1, l_2, ..., l_n\} (0 \le l_i \le W)$ , assign the items to the bins so that the capacity of the bins is not exceeded and the number of bins used is minimized.

The bin-packing problem belongs to the class of NP-hard problems (Garey and Johnson 1979), and it is not likely that a polynomial time algorithm can be found to solve this problem optimally. Coffman et al (1996) have provided an excellent survey of the methods used for this problem. Three commonly used methods are as follows:

- (1) Exact method: Martello and Toth (1990) have proposed a branch-and-bound procedure Martello and Toth Procedure (MTP) which has become a basic reference for use in most comparative studies. Scholl et al. (1997) proposed another exact method BISON (bin packing solution procedure) which makes use of several bounds, reduction procedures, heuristics, and a branch-and-bound procedure using a new branching scheme. Later, Schwerin and Wascher (1999) showed that the MTP provides significantly better results by using the bound derived from the cutting stock problem. Valerio de Carvalho (1999) presented an exact algorithm based on column generation-based exact algorithm for the cutting stock problem and has shown its effectiveness for some classes of bin packing problem instances.

- (2) Heuristics: Simchi-Levi (1994) has shown that the first-fit decreasing (FFD) and the best-fit decreasing (BFD) heuristics have an absolute performance ratio of 1.5, and that this value is the best possible for the bin-packing problem.

- (3) Metaheuristics: Hubscher and Glover (1994) have proposed a tabu search with influential diversification algorithm for bin packing problem, while, Falkenauer (1996) has described a hybrid grouping genetic algorithm (HGGA) for this problem.

As described in Section 2.1, the bin packing problem is a part of the MLCSP problem for carrier formation. The presence of the bin packing problem within the context of the MLCSP makes it a more difficult problem to address; and it is thus more amenable for the use of a heuristic for its solution.

#### 2.3 Model formulation and development of some structural properties

We make the following assumptions. Processing time per wafer is identical for different lots, which means that all the lots belong to the same product type. Setup time is negligible in comparison to the processing time. The objective function is to minimize the total completion time for lots, i.e., the average cycle time, which is a critical performance measure for any manufacturing system, and especially for a semiconductor manufacturer.

## Parameters:

- *N*: total number of lots

- L: total number of carriers available to be formed, obviously L < N

- $s_i$ : size for lot *i* (i.e., number of wafers), i = 1, ..., N

- $w_i$ : weight for lot i, i = 1, ..., N

- *K*: FOUP carrier capacity (usually, *K*= 25 wafers)

- $\rho$  : processing time per wafer at the machine

- $C_i$ : completion time for lot *i*, *i* =1, ..., N

- $F_k$ : completion time for carrier k, k=1, ..., L

- $n_k$ : number of lots in carrier k, k = 1, ..., L

- $J_k$ : set of lots forming carrier k, k=1, ..., L

- *H* : a big positive number

- O: set of all lots available to be scheduled

- *P* : set of already scheduled lots,  $P \subseteq O$

- $N_P$ : number of lots belonging to P

- $L_P$ : number of carriers formed by P

- $\theta_1$ : cost per time unit of completion time

- $\theta_2$ : cost per carrier for transportation

### Decision Variables:

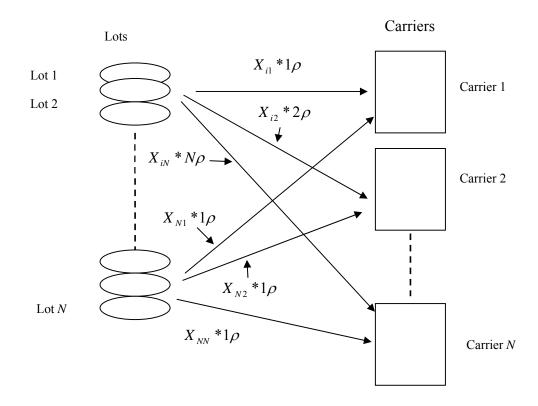

$$X_{ik} = \begin{cases} 1, & \text{if lot } i \text{ is assigned to carrier } k, i=1,...,N, k=1,...,L \\ 0, & \text{otherwise.} \end{cases}$$

$$Y_k = \begin{cases} 1, & \text{if carrier } k \text{ is not empty,} \\ 0, & \text{otherwise.} \end{cases}$$

We can formulate a mathematical model for MLCSP1 as follows.

3.7

### Model MLCSP1

Minimize

$$\sum_{i=1}^{N} C_i$$

Subject to

$$\sum_{k=1}^{L} X_{ik} = 1, \quad \forall i = 1, ..., N$$

(2.1)

$$\sum_{i=1}^{N} (X_{ik} * s_i) \le K, \quad \forall k = 1, ..., L$$

(2.2)

$$F_{k} = \sum_{l=1}^{k} \sum_{i=1}^{N} (X_{il} * s_{i} \rho), k=1, 2, ..., L$$

(2.3)

$$C_i \ge F_k - H(1 - X_{ik}), \quad \forall i = 1, ..., N, k = 1, ..., L$$

(2.4)

(We can let *H* equal to the maximum possible mackespan value, i.e.,  $H = \sum_{i=1}^{N} s_i \rho$ )

$X_{ik}$  binary,  $C_i, F_k \ge 0, \quad \forall i=1, ..., N, k=1, ..., L$  (2.5)

Constraint set (2.1) assigns each lot to one carrier only, and constraint set (2.2) makes sure that FOUP capacity K is not violated. For single-wafer-processing-technology, the processing time of a carrier is determined by the sum of the processing times of the lots contained in it, and all the lots contained in it have the same completion time. These are enforced by Constraint sets (2.3) and (2.4), respectively. Note that each carrier is identical to each other. Thus in the model, we can use arbitrary sequence of carriers, I, 2, ..., *L*. The decision variable  $X_{ik}$  automatically enforces the best carrier formation and sequencing.

Model MLCSP1 is an integer programming model involving a large number H. As such, it is not computationally efficient to solve this model directly. Next, we develop some structural properties that afford an effective and efficient methodology for the solution of the MLCSP1.

**Proposition 2.1**: In the optimal solution for MLCSP1, each carrier contains at least one lot.

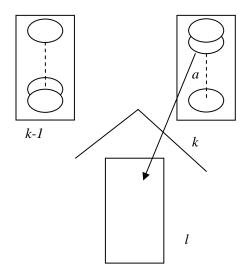

Figure 2.5: Schedule S' with insertion of carrier *l* in front of carrier *k*

*Proof:* This can be proved by contradiction. Suppose in the optimal schedule *S*, there is one empty carrier *l*. Thus, there is at least one carrier containing more than one lot since  $L \le N$ . Without loss of generality, we construct another schedule *S'* by inserting the empty carrier *l* in front of carrier *k*, which has more than one lot (see Figure 2.5). Remove one lot, *a*, from carrier *k* and put it in carrier *l*. Since this change does not affect the completion times of the lots in other carriers except for those in *l* and *k*, we will only need to consider the change in the sum of the completion times for the lots in carriers *l* and *k*. Let  $F_{k-1}$  represent completion time of carrier *k*-1. The sum of the completion times of the lots in *S*,

$$sum1(l,k) = n_k * (\sum_{i \in J_k} s_i \rho + F_{k-1})$$

While for S', the sum of the completion times of the lots,

$$sum2(l,k) = (s_a \rho + F_{k-1}) + (n_k - 1) * (s_a \rho + F_{k-1} + \sum_{i \in J_k \setminus a} s_i \rho).$$

Note that  $sum1(l,k) - sum2(l,k) = \sum_{i \in J_k \setminus a} s_i \rho > 0$ , which contradicts the fact that S is

optimal.

**Corollary 2.1**: A lower bound (LB) on the total completion time can be obtained by using *N* carriers, i.e., with each carrier containing exactly one lot.

It is known that the shortest processing time first (SPT) rule minimizes the total completion time for single machine. We can, thus, arrange the lots by non-decreasing order of their sizes, and re-index them by j=1, 2, ..., N. The lower bound can, thus, be calculated as

$$LB = \sum_{j=1}^{N} (N - j + 1) * s_{j} \rho$$

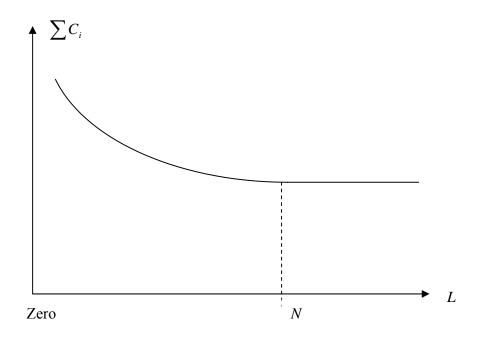

From Proposition 2.1, we can pictorially represent the relationship between the number of carriers used and the resulting total completion time (see Figure 2.6). However, note that the transportation task for the AMHS increases with an increment in the number of carriers. Therefore, usually, the number of carriers to be configured, L, is given, and L < N. Such a L can be determined by using historical Manufacturing Execution System (MES) data in the fab.

Figure 2.6: The relationship between the number of carriers and total completion time

Proposition 2.2: The MLCSP1 problem is NP-hard.

Proof: We can reformulate the mathematical model as

Minimize

$$\sum_{i=1}^{N} \sum_{k=1}^{L} (X_{ik} * \sum_{l=1}^{K} \sum_{i=1}^{N} (X_{il} * s_i \rho))$$

Subject to

$$\sum_{k=1}^{L} X_{ik} = 1 \quad \forall i = 1, 2, ..., N$$

(2.6)

$$\sum_{i=1}^{N} (X_{ik} * s_i) \le K \quad \forall k = 1, 2, ..., L$$

(2.7)

Note that it is a quadratic generalized assignment problem (GAP), and a quadratic assignment problem is known to be a NP-hard problem (Fisher et al. 1986).

**Proposition 2.3**: In an optimal solution, the carriers appear in non-decreasing order of the ratios of the total time required to process the wafers contained in a carrier and the

number of lots in the corresponding carrier, i.e.,  $\frac{\sum_{i \in J_j} s_i \rho}{n_j}$ .

*Proof*: By definition,  $\sum C_i = \sum_{j=1}^{L} (n_j * F_j)$ . For each carrier *j*, we have completion time

of  $F_j$ , processing time of  $\sum_{i \in J_j} s_i \rho$  and "weight" of  $n_j$ . The result follows by the fact that the shortest weighted processing time (SWPT) sequence minimizes the total weighted completion time for a single machine (see Pinedo 2005).

In accordance with Proposition 2.3, once each carrier has been configured, the optimal sequence of these carriers can be determined easily.

Note that, in accordance with Proposition 2.1, the lots are spread over all *L* carriers in an optimal solution. Therefore, in an optimal solution obtained by relaxing FOUP capacity, FOUP capacity (i.e., 25 wafers) will not likely be violated severely. Thus, if the optimal solution obtained for the FOUP capacity-relaxed problem is not optimal, it provides a good lower bound for the original (i.e., FOUP capacitated) MLCSP problem.

### 2.4 A problem with infinite FOUP capacity

### 2.4.1 Some structural properties

**Proposition 2.4:** In an optimal solution,  $\max_{i \in J_m} s_i \le \min_{j \in J_n} s_j$ , where carrier *m* immediately preceds carrier *n*.

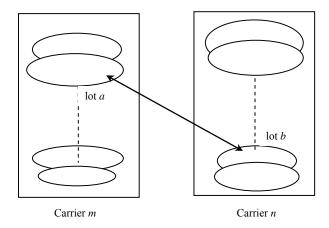

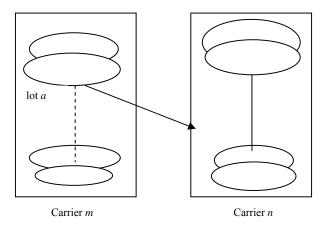

*Proof:* Suppose in an optimal schedule *S*, carrier *m* immediately precedes carrier *n*, and there exist two lots *a* and *b*,  $a \in J_m$ ,  $b \in J_n$ , such that  $s_a > s_b$ . Since the carriers have unlimited capacities, we can exchange lots *a* and *b* (see Figure 2.7). Call this schedule *S'*. We want to show *S'* to be better than *S*, which would contradict the fact that *S* is optimal. Since a switch of these two lots does not affect the completion times of other carriers, we only need to consider the sum of completion times for lots in carriers *m* and *n*. Let *F<sub>l</sub>* be the completion time of carrier *l*, which immediately precedes carrier *m* in the optimal solution.

Before the switch,

$$sum1(m,n) = n_m(F_l + \rho \sum_{i \in J_m} s_i) + n_n(F_l + \rho \sum_{i \in J_m} s_i + \rho \sum_{j \in J_n} s_j)$$

=  $n_m(F_l + \rho \sum_{\substack{i \in J_m \ i \notin a}} s_i + \rho s_a) + n_n(F_l + \rho \sum_{i \in J_m} s_i + \rho \sum_{j \in J_n} s_j).$

After the switch,

$$sum2(m,n) = n_m(F_l + \rho \sum_{\substack{i \in J_m \\ i \notin a}} s_i + \rho s_b) + n_n(F_l + \rho \sum_{\substack{i \in J_m \\ i \notin a}} s_i + \rho s_b + \rho \sum_{\substack{j \in J_n \\ j \notin b}} s_j + \rho s_a)$$

=  $n_m(F_l + \rho \sum_{\substack{i \in J_m \\ i \notin a}} s_i + \rho s_b) + n_n(F_l + \rho \sum_{i \in J_m} s_i + \rho \sum_{j \in J_n} s_j).$

We have,  $sum1(m,n) - sum2(m,n) = \rho n_m (s_a - s_b) > 0$ . Thus, S' is strictly better than S.

Figure 2.7: A switch of lot *a* and lot *b* between carriers *m* and *n*

**Corollary 2.2:** In an optimal solution, starting from the first carrier, the lots appear in the carriers in the non-decreasing order of their sizes.

**Proposition 2.5**: In an optimal solution,  $\frac{\sum_{j \in J_n} s_j}{s_b} \le n_m + 1$  for a lot  $b \in J_n$ , where carrier *m*

immediately precedes carrier n.

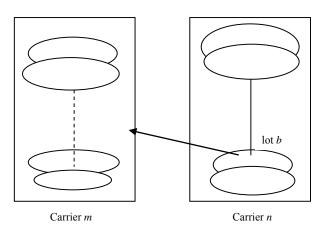

*Proof*: Assume the contrary; that is, in an optimal schedule, S, with two consecutive carriers m and n, m preceding n,  $\frac{\sum_{j \in J_n} s_j}{s_b} > n_m + 1$  for a lot  $b \in J_n$ . Since FOUP has

unlimited capacity, construct another schedule S' by removing lot b from carrier n and including it in carrier m (see Figure 2.8). Again,  $F_l$  is defined as before, and we consider the net change in completion times of carriers m and n only as those of the others are unaffected.

Before the change, we have

$$sum1(m,n) = n_m(F_l + \rho \sum_{i \in J_m} s_i) + n_n(F_l + \rho \sum_{i \in J_m} s_i + \rho \sum_{j \in J_n} s_j)$$

=  $n_m(F_l + \rho \sum_{i \in J_m} s_i) + n_n(F_l + \rho \sum_{i \in J_m} s_i + \rho \sum_{\substack{j \in J_n \\ j \neq b}} s_j + \rho s_b).$

After the change, we have

$$sum2(m,n) = (n_m + 1)(F_l + \rho \sum_{i \in J_m} s_i + \rho s_b) + (n_n - 1)(F_l + \rho \sum_{i \in J_m} s_i + \rho s_b + \rho \sum_{\substack{j \in J_n \\ j \neq b}} s_j)$$

=  $n_m(F_l + \rho \sum_{i \in J_m} s_i) + n_m s_b \rho + (F_l + \rho \sum_{i \in J_m} s_i) + s_b \rho + n_n(F_l + \rho \sum_{i \in J_m} s_i + \rho \sum_{j \in J_n} s_j)$

$- (F_l + \rho \sum_{i \in J_m} s_i + \rho \sum_{j \in J_n} s_j).$

Moreover,

$$sum1(m,n) - sum2(m,n) = -n_{m}s_{b}\rho - (F_{l} + \rho \sum_{i \in J_{m}}s_{i}) - s_{b}\rho + (F_{l} + \rho \sum_{i \in J_{m}}s_{i}) + \rho \sum_{j \in J_{n}}s_{j}$$

$$= -\rho(n_{m} + 1)s_{b} + \rho \sum_{j \in J_{n}}s_{j} > 0,$$

implying a contradiction.

Figure 2.8: Schedule S' with lot b removed from carrier n and included in carrier m

**Corollary 2.3** For two consecutive carriers *m* and *n*, in an optimal solution, where carrier *m* precedes *n*, , the following relationship holds:  $n_n \le n_m + 1$ .

*Proof*: It follows from Proposition 2.5, and the fact that  $n_n \leq \frac{\sum_{j \in J_n} s_j}{\min_{j \in J_n} s_j}$ .

Note that the only situation under which  $n_n = \frac{\sum_{j \in J_n} s_j}{\min_{j \in J_n} s_j}$  would hold is when all the lots in

carrier *n* are of the same size.

Proposition 2.6

$$n_{m\min} = \left[\frac{(N - \sum_{i=1}^{m-1} n_i) - \frac{(L-m)(L-m+1)}{2}}{(L-m+1)}\right], \text{ for } m=1,\dots,L-1$$

*Proof*: Based on the fact that  $n_m + 1 \ge n_n$ , with carrier *m* immediately preceding carrier *n*, the minimum  $n_m$  value is achieved when  $n_{k+1} = n_k + 1$ , k=m, m+1, ...N-1. Thus, the total number of lots after carrier *m*, including carrier *m* is

$$\sum_{i=m}^{L} n_i = \sum_{i=m}^{L} (n_{m\min} + (i-m)) = n_{m\min} (L-m+1) + \frac{(L-m)(L-m+1)}{2}$$

Since

$$\sum_{i=1}^{m-1} n_i + n_{m\min} (L - m + 1) + \frac{(L - m)(L - m + 1)}{2} = N$$

, we have

$$n_{m\min} = \left[ \frac{(N - \sum_{i=1}^{m-1} n_i) - \frac{(L - m)(L - m + 1)}{2}}{(L - m + 1)} \right] \text{ as } n_{m\min} \text{ can only be integer. } \blacksquare$$