## Automated Runtime Analysis and Adaptation for Scalable Heterogeneous Computing

#### Ahmed E. Helal

Dissertation submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

> Doctor of Philosophy in Computer Engineering

Wu-chun Feng, Chair Yasser Y. Hanafy Changhee Jung Changwoo Min Leyla Nazhandali

December 3, 2019 Blacksburg, Virginia

Keywords: Parallel Architectures, Accelerators, Heterogeneous Computing, Performance Modeling, Runtime Adaptation, Scheduling, Performance Portability, MPI, GPU, LLVM Copyright 2019, Ahmed E. Helal

## Automated Runtime Analysis and Adaptation for Scalable Heterogeneous Computing

Ahmed E. Helal

(ABSTRACT)

In the last decade, there have been tectonic shifts in computer hardware because of reaching the physical limits of the sequential CPU performance. As a consequence, current high-performance computing (HPC) systems integrate a wide variety of compute resources with different capabilities and execution models, ranging from multi-core CPUs to many-core accelerators. While such heterogeneous systems can enable dramatic acceleration of user applications, extracting optimal performance via manual analysis and optimization is a complicated and time-consuming process.

This dissertation presents graph-structured program representations to reason about the performance bottlenecks on modern HPC systems and to guide novel automation frameworks for performance analysis and modeling and runtime adaptation. The proposed program representations exploit domain knowledge and capture the inherent computation and communication patterns in user applications, at multiple levels of computational granularity, via compiler analysis and dynamic instrumentation. The empirical results demonstrate that the introduced modeling frameworks accurately estimate the realizable parallel performance and scalability of a given sequential code when ported to heterogeneous HPC systems. As a result, these frameworks enable efficient workload distribution schemes that utilize all the available compute resources in a performance-proportional way. In addition, the proposed runtime adaptation frameworks significantly improve the end-to-end performance of important real-world applications which suffer from limited parallelism and fine-grained data dependencies. Specifically, compared to the state-of-the-art methods, such an adaptive parallel execution achieves up to an order-of-magnitude speedup on the target HPC systems while preserving the inherent data dependencies of user applications.

## Automated Runtime Analysis and Adaptation for Scalable Heterogeneous Computing

#### Ahmed E. Helal

#### (GENERAL AUDIENCE ABSTRACT)

Current supercomputers integrate a massive number of heterogeneous compute units with varying speed, computational throughput, memory bandwidth, and memory access latency. This trend represents a major challenge to end users, as their applications have been designed from the ground up to primarily exploit homogeneous CPUs. While heterogeneous systems can deliver several orders of magnitude speedup compared to traditional CPU-based systems, end users need extensive software and hardware expertise as well as significant time and effort to efficiently utilize all the available compute resources.

To streamline such a daunting process, this dissertation presents automated frameworks for analyzing and modeling the performance on parallel architectures and for transforming the execution of user applications at runtime. The proposed frameworks incorporate domain knowledge and adapt to the input data and the underlying hardware using novel static and dynamic analyses. The experimental results show the efficacy of the introduced frameworks across many important application domains, such as computational fluid dynamics (CFD), and computer-aided design (CAD). In particular, the adaptive execution approach on heterogeneous systems achieves up to an order-of-magnitude speedup over the optimized parallel implementations.

To my brother, Ali, who gave me my first thousand books.

## Acknowledgments

I was fortunate to work with many wonderful people who made this Ph.D. endeavor a memorable and enjoyable time. I would like to thank Dr. Wu-chun Feng, Dr. Changhee Jung, and Dr. Yasser Hanafy for providing me with a multitude of opportunities to learn and to grow. I am grateful for their guidance, assistance, and support, which have been instrumental in my development as an independent researcher. I would especially like to thank Dr. Feng for empowering me to pursue my research ideas, to effectively communicate my work, and to set the highest expectations for myself.

I wish to thank Dr. Changwoo Min and Dr. Leyla Nazhandali for serving on my committee. I appreciate their insightful comments and feedback on my dissertation.

My thanks to Dr. Ashwin Aji, Dr. Michael Chu, and Dr. Bradford Beckmann (AMD Research) for their assistance and support during our research collaboration. I am grateful to Dr. Amr Bayoumi (AAST) for introducing me to the field of high-performance computing and for his help during the early days of this Ph.D. journey.

I would also like to thank the members of the Synergy Lab at Virginia Tech for their valuable feedback and assistance during my graduate studies. I would especially like to thank Paul Sathre, Vignesh Adhinarayanan, and Dr. Mark Gardner for many interesting and helpful discussions regarding this work.

My thanks to Dr. Yasser Hanafy, Dr. Sedki Riad, and the faculty and staff of the ECE department at Virginia Tech for making my VT-MENA and Prasad fellowships possible.

I am deeply grateful to all my family members and friends. I believe that without your encouragement and support, none of this work would have been accomplished.

Funding Acknowledgment. This work was supported in part by the Air Force Office of Scientific Research (AFOSR) Computational Mathematics Program via Grant No. FA9550-12-1-0442, NSF I/UCRC IIP-1266245 via the NSF Center for High-Performance Reconfigurable Computing (CHREC), NSF CAREER Award (1750503), the DOE PathForward program, and the Synergistic Environments for Experimental Computing (SEEC) Center via a seed grant from the Institute for Critical Technology and Applied Science (ICTAS), an institute dedicated to transformative, interdisciplinary research for a sustainable future. My thanks to Advanced Research Computing (ARC) at Virginia Tech for providing the computational resources used in this work.

**Declaration of Collaboration.** In addition to my committee members, this dissertation benefited from the following collaborators:

- Dr. Ashwin Aji, Dr. Michael Chu, and Dr. Bradford Beckmann (AMD Research) contributed to the work in Chapter 5.

- Dr. Amr Bayoumi (AAST) contributed to the work in Chapter 6.

- Paul Sathre contributed to the work in Chapter 7. In addition, several members of the Synergy Lab at Virginia Tech, including Kaixi Hou and Sriram Chivukula, contributed to the development of MetaMorph's prototype.

## Contents

| 1 | Intr | roduction                                                    | 1  |

|---|------|--------------------------------------------------------------|----|

|   | 1.1  | Research Problems                                            | 1  |

|   | 1.2  | Thesis Statement                                             | 3  |

|   | 1.3  | Methodology                                                  | 4  |

|   | 1.4  | Contributions                                                | 5  |

|   |      | 1.4.1 Automated Program Analysis for Performance Modeling    | 5  |

|   |      | 1.4.2 Runtime Adaptation for Scalable Performance            | 7  |

|   |      | 1.4.3 Interoperability Middleware for Simultaneous Execution | 8  |

|   | 1.5  | Dissertation Outline                                         | 9  |

| 2 | Bac  | ekground and Related Work                                    | 10 |

|   | 2.1  | HPC Programming Models                                       | 10 |

|   | 2.2  | Massively Parallel HPC Architectures                         | 12 |

|   | 2.3  | Performance Modeling on HPC Systems                          | 14 |

|   |      | 2.3.1 Analytical Modeling                                    | 14 |

|   |      | 2.3.2 Simulation                                             | 15 |

|   |     | 2.3.3  | Automated Performance Prediction                               | 15 |

|---|-----|--------|----------------------------------------------------------------|----|

|   |     | 2.3.4  | Communication and Scalability Analysis                         | 17 |

|   | 2.4 | Data I | Dependency Management on Massively Parallel HPC Architectures  | 19 |

| 3 | Au  | tomate | ed Estimation of Execution Cost on Heterogeneous Architectures | 8  |

|   |     |        |                                                                | 22 |

|   | 3.1 | Introd | uction                                                         | 22 |

|   |     | 3.1.1  | AutoMatch: The First-Order Framework                           | 24 |

|   |     | 3.1.2  | Contributions                                                  | 26 |

|   | 3.2 | AutoN  | Match Approach                                                 | 27 |

|   |     | 3.2.1  | Hardware Architecture Model                                    | 27 |

|   |     | 3.2.2  | Inferring the Architectural Specifications                     | 29 |

|   |     | 3.2.3  | Compiler-based Application Analysis                            | 31 |

|   |     | 3.2.4  | Analytical Modeling                                            | 36 |

|   | 3.3 | Evalua | ation                                                          | 38 |

|   |     | 3.3.1  | Performance Forecasting and Analysis Case study                | 39 |

|   |     | 3.3.2  | Workload Distribution Case Study                               | 45 |

|   |     | 3.3.3  | Discussion                                                     | 46 |

|   | 3.4 | Concl  | usion                                                          | 47 |

| 4 | Au  | ıtomat | ed Estimation of Communication Cost and Scalability            | 49 |

|   | 4.1 | Introd | uction                                                         | 49 |

|   |     | 111    | Comm Analyzor Framowork                                        | 51 |

|     | 4.1.2   | Contributions                           | 52 |

|-----|---------|-----------------------------------------|----|

| 4.2 | Backg   | round                                   | 53 |

|     | 4.2.1   | Distributed-Memory Execution Model      | 53 |

|     | 4.2.2   | Simple Estimation of Communication Cost | 54 |

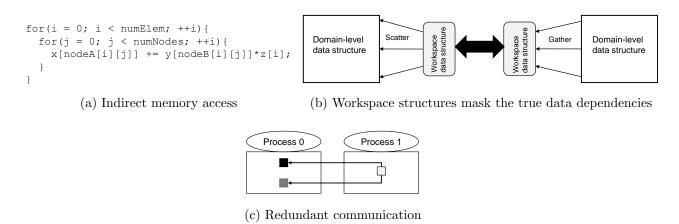

| 4.3 | Challe  | enges                                   | 55 |

|     | 4.3.1   | Indirect Memory Access                  | 55 |

|     | 4.3.2   | Workspace Data Structures               | 55 |

|     | 4.3.3   | Singleton Data Items                    | 56 |

|     | 4.3.4   | Redundant Communication                 | 56 |

| 4.4 | Comm    | nAnalyzer Approach                      | 57 |

|     | 4.4.1   | Communication Characterization          | 59 |

|     | 4.4.2   | Communication Cost Estimation           | 61 |

|     | 4.4.3   | Implementation and Complexity           | 66 |

| 4.5 | Efficie | ency Roofline Model                     | 67 |

| 4.6 | Evalua  | ation                                   | 69 |

|     | 4.6.1   | Experimental Setup                      | 70 |

|     | 4.6.2   | Benchmarks                              | 73 |

|     | 4.6.3   | MiniGhost and Heat2D                    | 74 |

|     | 4.6.4   | LULESH                                  | 76 |

|     | 4.6.5   | K-means                                 | 78 |

| 4.7 | Discus  | ssion                                   | 79 |

|   | 4.8  | Conclusion                                                        | 80 |

|---|------|-------------------------------------------------------------------|----|

| 5 | Eff  | icient Dependency Management on Massively Data-Parallel Architec- |    |

|   | ture | es 8                                                              | 82 |

|   | 5.1  | Introduction                                                      | 82 |

|   | 5.2  | Background and Motivation                                         | 85 |

|   | 5.3  | Adaptive Task Aggregation (ATA)                                   | 87 |

|   |      | 5.3.1 Hierarchical DAG Transformation                             | 88 |

|   |      | 5.3.2 Hierarchical DAG Execution on GPUs                          | 90 |

|   |      | 5.3.3 Task Aggregation Policies                                   | 94 |

|   | 5.4  | Evaluation                                                        | 98 |

|   |      | 5.4.1 Experimental Setup                                          | 99 |

|   |      | 5.4.2 Experimental Results                                        | 02 |

|   |      | 5.4.3 End-to-End Application Performance                          | 06 |

|   | 5.5  | Discussion                                                        | 07 |

|   | 5.6  | Conclusion                                                        | 08 |

| 6 | Sca  | alable Execution of Irregular Data-Dependent Computations 10      | 09 |

|   | 6.1  | Introduction                                                      | 09 |

|   | 6.2  | Background                                                        | 11 |

|   | 6.3  | SPICE Profiling and Modeling                                      | 13 |

|   |      |                                                                   | 13 |

|   |      |                                                                   | 14 |

|   |     | 6.3.3  | SPICE Performance Models                                                                                                                       | 115 |

|---|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

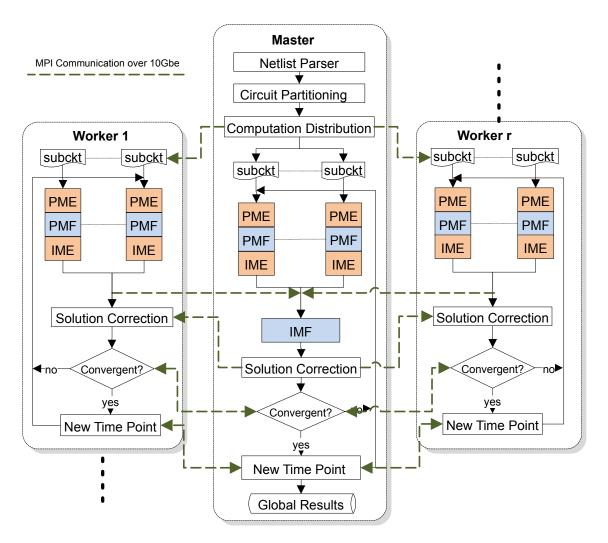

|   | 6.4 | SPICE  | E-H Approach                                                                                                                                   | 117 |

|   |     | 6.4.1  | Adaptive Parallel Execution on Heterogeneous Distributed-memory                                                                                |     |

|   |     |        | Systems                                                                                                                                        | 118 |

|   |     | 6.4.2  | Adaptive Circuit Partitioning and Distribution                                                                                                 | 120 |

|   |     | 6.4.3  | Kernel-Architecture Matching                                                                                                                   | 123 |

|   | 6.5 | Evalua | ation                                                                                                                                          | 126 |

|   | 6.6 | Conclu | asion                                                                                                                                          | 129 |

| 7 | Int | eroper | ation on Heterogeneous HPC Systems                                                                                                             | 130 |

|   | 7.1 | Introd | $ uction \ldots \ldots$ | 130 |

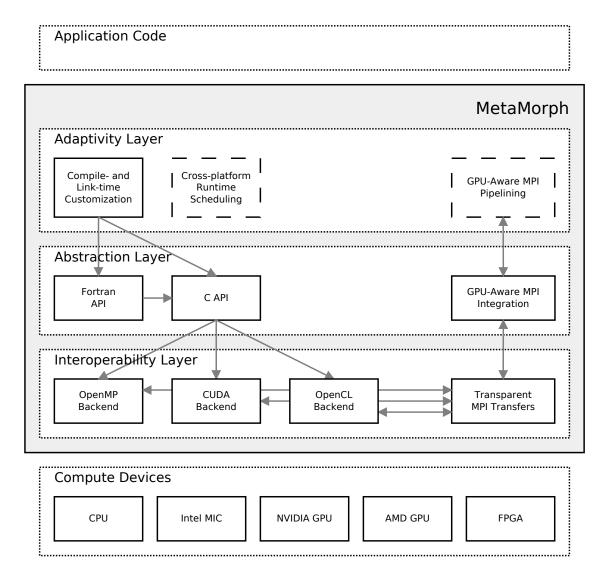

|   | 7.2 | Design | Philosophy                                                                                                                                     | 133 |

|   |     | 7.2.1  | Interoperability Layer                                                                                                                         | 134 |

|   |     | 7.2.2  | Abstraction Layer                                                                                                                              | 136 |

|   |     | 7.2.3  | Adaptivity Layer                                                                                                                               | 138 |

|   | 7.3 | Protot | ype Implementation                                                                                                                             | 139 |

|   |     | 7.3.1  | Programming Models                                                                                                                             | 139 |

|   |     | 7.3.2  | Top-Level User API                                                                                                                             | 139 |

|   |     | 7.3.3  | Accelerator Back-Ends                                                                                                                          | 145 |

|   | 7.4 | Evalua | ation                                                                                                                                          | 146 |

|   |     | 7.4.1  | Applications                                                                                                                                   | 146 |

|   |     | 7.4.2  | Programmability and Productivity                                                                                                               | 148 |

|    |       | 7.4.3 Experimental Results | 150 |

|----|-------|----------------------------|-----|

|    | 7.5   | Conclusion                 | 155 |

| 8  | Con   | nclusion and Future Work   | 156 |

|    | 8.1   | Dissertation Summary       | 157 |

|    | 8.2   | Future Work                | 158 |

| Bi | bliog | graphy                     | 160 |

# List of Figures

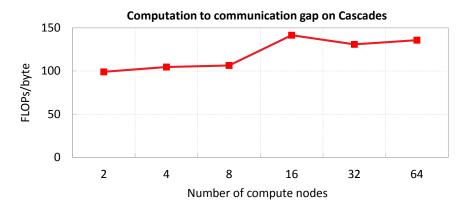

| 1.1 | The gap between the computation and communication costs on the Cascades       |    |

|-----|-------------------------------------------------------------------------------|----|

|     | cluster at Virginia Tech                                                      | 2  |

| 1.2 | Overview of the proposed methodology                                          | 4  |

| 1.3 | Dissertation overview                                                         | 5  |

| 2.1 | VEGA GPU architecture                                                         | 12 |

| 2.2 | GPU kernel                                                                    | 13 |

| 2.3 | The execution of a BSP superstep                                              | 13 |

| 3.1 | Overview of AutoMatch framework                                               | 24 |

| 3.2 | The abstract hardware architecture                                            | 28 |

| 3.3 | The design and implementation of AutoMatch compiler                           | 31 |

| 3.4 | The ASAP schedule of the application operations on a theoretical architecture |    |

|     | with infinite resources                                                       | 32 |

| 3.5 | LRU stack distance analysis example                                           | 34 |

| 3.6 | Detection of global synchronization                                           | 36 |

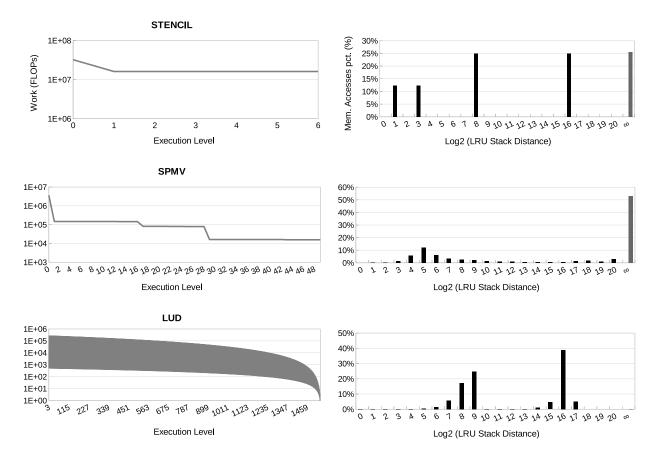

| 3.7 | Parallelism and LRU stack distance profiles                                   | 40 |

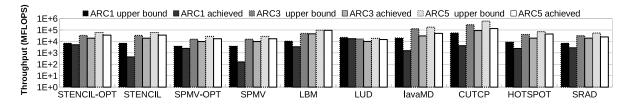

| 3.8  | Achieved performance vs. AutoMatch's upper bounds                                                                      | 41 |

|------|------------------------------------------------------------------------------------------------------------------------|----|

| 3.9  | AutoMatch's prediction of execution bottlenecks                                                                        | 42 |

| 3.10 | The prediction sensitivity of AutoMatch                                                                                | 45 |

| 3.11 | The performance of compute kernels with the different workload distribution strategies: Default, AutoMatch, and Oracle | 47 |

| 4.1  | Overview of CommAnalyzer framework                                                                                     | 51 |

| 4.2  | The SPMD execution model                                                                                               | 54 |

| 4.3  | Simple estimation of communication cost for matrix multiplication                                                      | 54 |

| 4.4  | Challenges for estimating the communication cost                                                                       | 55 |

| 4.5  | An example of value-flow chain detection                                                                               | 61 |

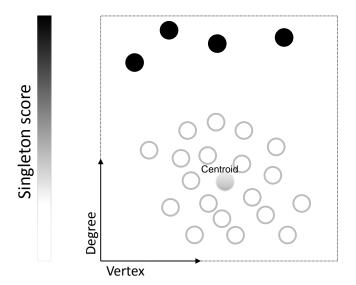

| 4.6  | Automated detection of singleton values (with extreme connectivity) using the threshold-based scoring algorithm.       | 64 |

| 4.7  | Value decomposition using graph clustering and partitioning algorithms                                                 | 65 |

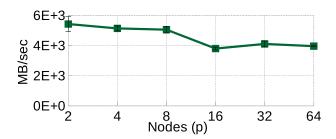

| 4.8  | The effective bisection bandwidth per node                                                                             | 72 |

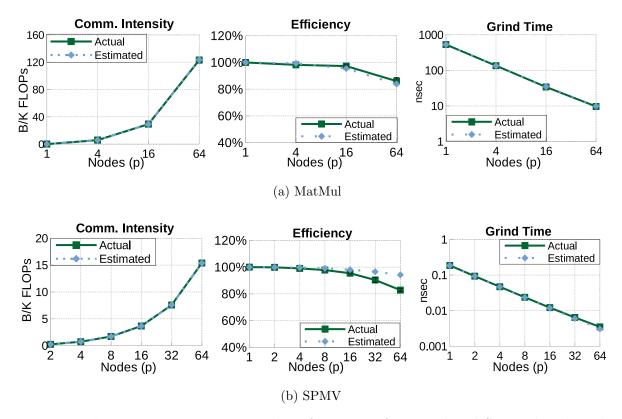

| 4.9  | The communication cost and performance of MatMul and SPMV benchmarks.                                                  | 74 |

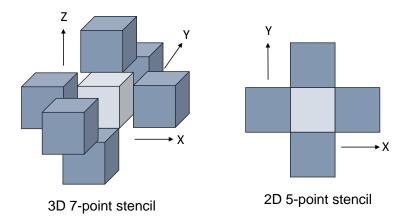

| 4.10 | The finite difference stencils used in MiniGhost and Heat2D                                                            | 75 |

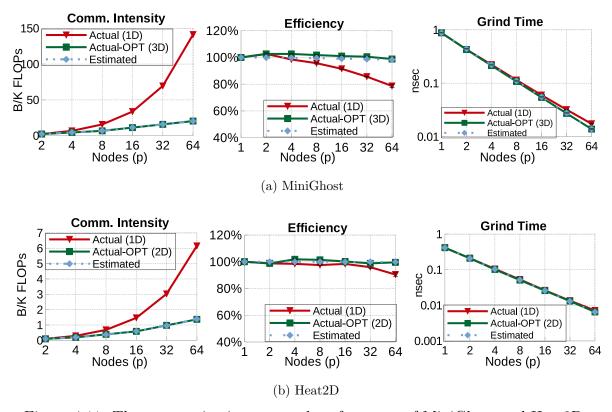

| 4.11 | The communication cost and performance of MiniGhost and Heat2D                                                         | 76 |

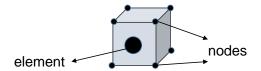

| 4.12 | LULESH uses an unstructured, hexa-hedral mesh with two centering                                                       | 77 |

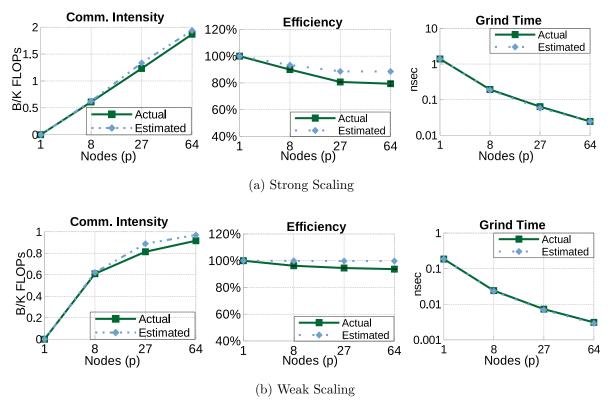

| 4.13 | The communication cost and performance of LULESH                                                                       | 78 |

| 4.14 | The communication cost and performance of K-means                                                                      | 79 |

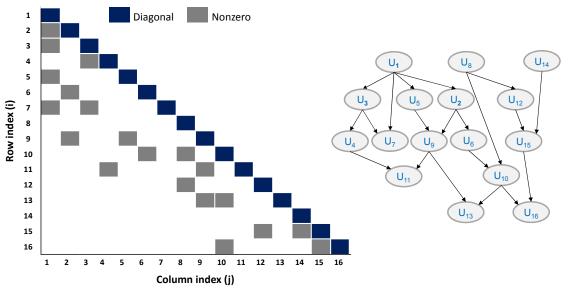

| 5 1  | A triangular matrix and the corresponding DAG for SpTS                                                                 | 86 |

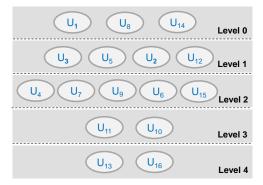

| 5.2  | The BSP (level-set) execution of the DAG in Figure 5.1                                                                                                                                                                                                                                                   | 87  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

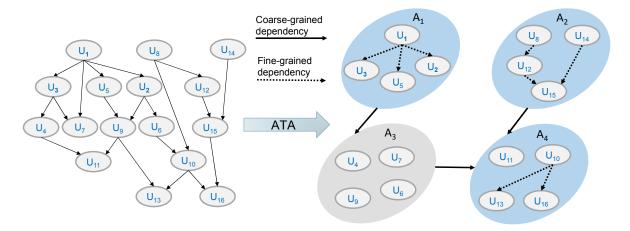

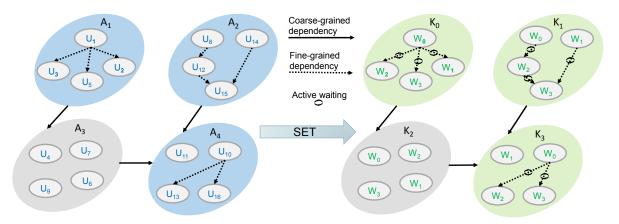

| 5.3  | ATA transformation of the application DAG in Figure 5.1 for hierarchical execution and dependency management. The adaptive tasks $A_1$ , $A_2$ , and $A_4$ require fine-grained dependency tracking and resolution, while $A_3$ can be executed as a data-parallel kernel                                | 89  |

| 5.4  | SET scheduling of the hierarchical DAG in Figure 5.3. Each adaptive $(A)$ task executes as a GPU kernel $(K)$ with fine-grained dependency management using active waiting when deemed necessary. SET scheduling ensures forward progress by mapping the user $(U)$ tasks to the worker wavefronts $(W)$ | 92  |

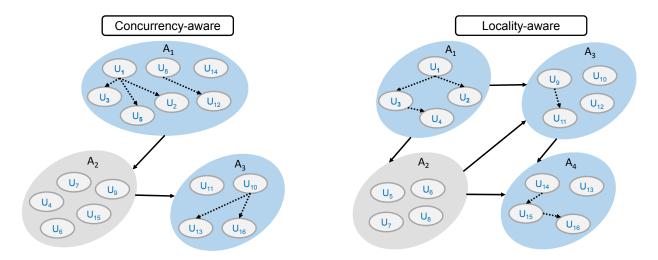

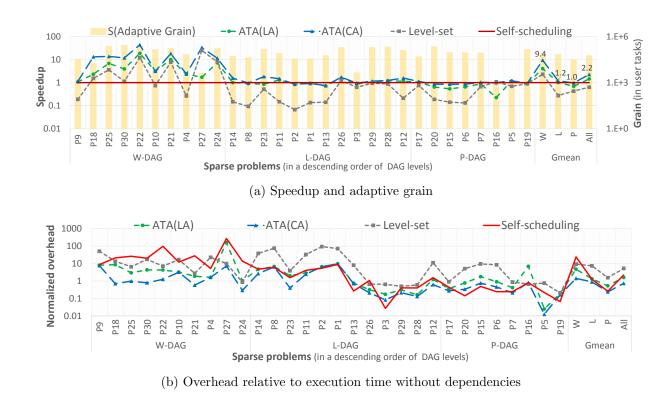

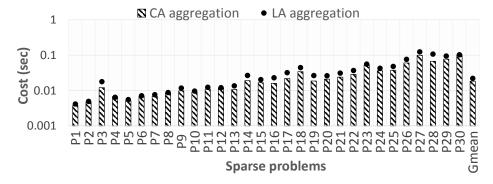

| 5.5  | Concurrency- and locality-aware aggregations of the application DAG in Figure 5.1. The adaptive task granularity is four                                                                                                                                                                                 | 98  |

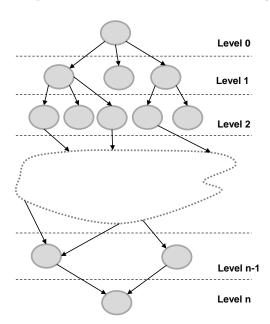

| 5.6  | An example of the different DAG classes. The x-axis shows the number of user tasks, while the y-axis represents the DAG levels (critical path)                                                                                                                                                           | 101 |

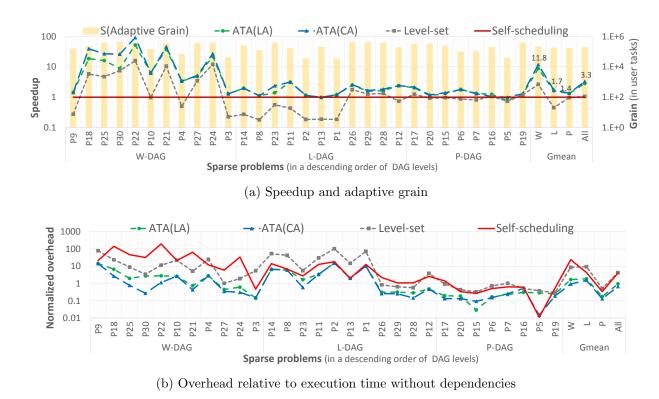

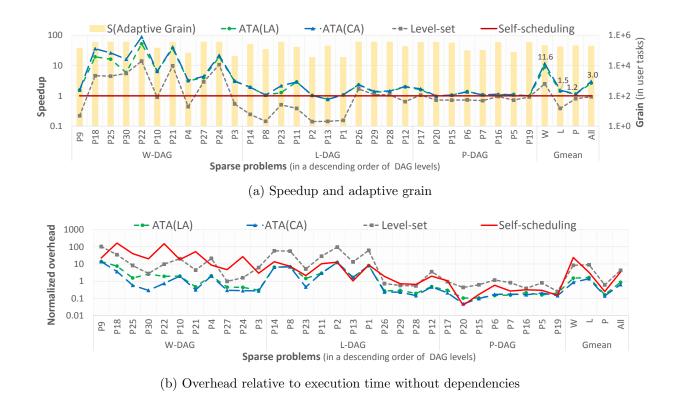

| 5.7  | The performance and overhead of SpTS (push traversal) kernels using the different execution approaches on VEGA-FE.                                                                                                                                                                                       | 103 |

| 5.8  | The performance and overhead of SpTS (pull traversal) kernels using the different execution approaches on VEGA-FE.                                                                                                                                                                                       | 104 |

| 5.9  | The performance and overhead of SpILU0 (pull traversal) using the different execution approaches on VEGA-FE.                                                                                                                                                                                             | 105 |

| 5.10 | The cost of hierarchical DAG transformation using the different task aggregation policies                                                                                                                                                                                                                | 106 |

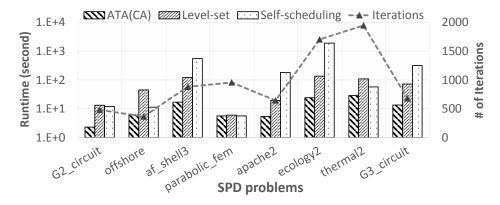

| 5.11 | The performance of PCG solver on VEGA-FE                                                                                                                                                                                                                                                                 | 107 |

| 6.1  | SPICE transient analysis                                                                                                                                                                                                                                                                                 | 112 |

| 6.2  | An overview of SPICE-H framework                                                                                                                                                                                                                                                                         | 118 |

| 6.3  | The trend of the optimal number of partitions, $m^*$ , for $n = 100,000$ circuit equations/unknowns                                                         | 122 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

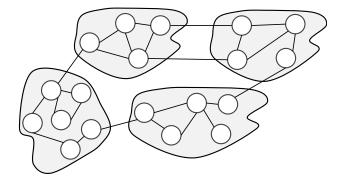

| 6.4  | SPICE-H generates a hypergraph program representation for adaptive parallel execution of the target application                                             | 122 |

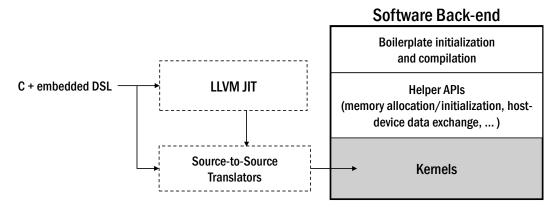

| 7.1  | MetaMorph uses a modular, layered design to hide the complexity of executing on and interoperating across a range of compute platforms. <sup>1</sup>        | 133 |

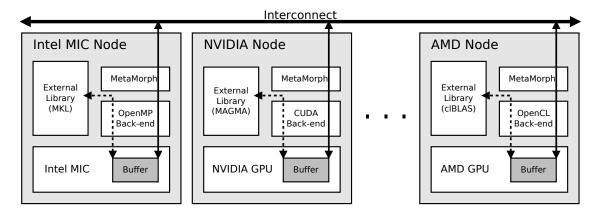

| 7.2  | MetaMorph provides interoperability both with external libraries in a node (dashed lines) and across nodes with varying hardware (solid lines)              | 135 |

| 7.3  | MetaMorph accelerates the development of new operations and kernels                                                                                         | 137 |

| 7.4  | Overview of the main user API exposed by MetaMorph                                                                                                          | 140 |

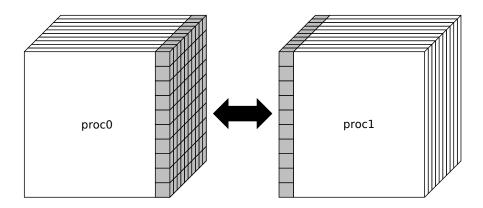

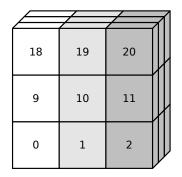

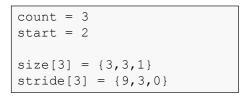

| 7.5  | Neighboring processes must exchange boundary data every iteration                                                                                           | 142 |

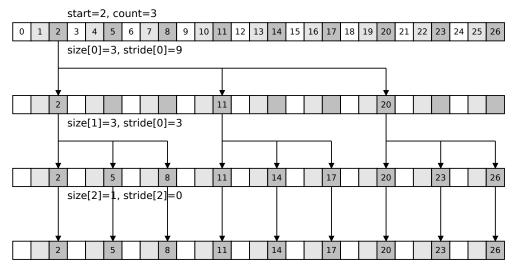

| 7.6  | Face description data structure and hierarchical index computation                                                                                          | 143 |

| 7.7  | MetaMorph's compute APIs that are used to accelerate the target applications                                                                                | 150 |

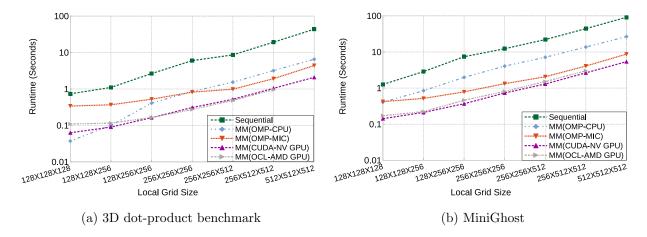

| 7.8  | The performance of target applications with the different MetaMorph (MM) back-ends on the experimental cluster.                                             | 152 |

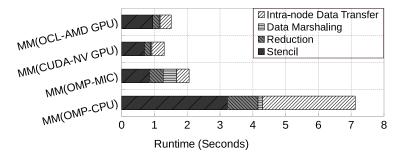

| 7.9  | The runtime distribution of MiniGhost using a 256X256X512 local grid with the different MetaMorph (MM) back-ends on the experimental cluster                | 153 |

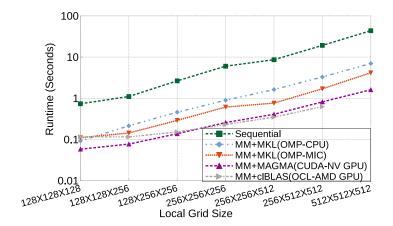

| 7.10 | The performance of the 3D dot-product benchmark on the different Meta-Morph (MM) backends with platform-specific BLAS libraries on the experimental cluster | 154 |

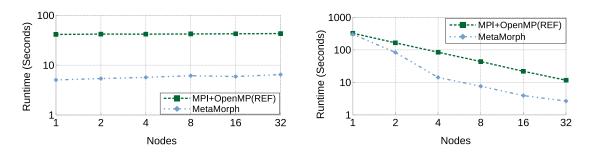

| 7.11 | The scalability analysis of MiniGhost on the HokieSpeed cluster with Meta-<br>Morph vs. the reference MPI+OpenMP implementation                             | 155 |

## List of Tables

| 2.1 | Comparison of recent performance prediction tools for heterogeneous HPC     |     |

|-----|-----------------------------------------------------------------------------|-----|

|     | architectures (CPUs and GPUs)                                               | 16  |

| 3.1 | The specifications of target hardware architectures                         | 30  |

| 3.2 | Rodinia and Parboil workloads                                               | 39  |

| 4.1 | Target HPC benchmarks and applications                                      | 70  |

| 4.2 | The size of value communication graph (VCG)                                 | 72  |

| 5.1 | Characteristics of the sparse problems                                      | 100 |

| 5.2 | Target GPU architectures                                                    | 101 |

| 6.1 | Performance parameters of cg1.4xlarge instances                             | 114 |

| 6.2 | Test Circuits                                                               | 127 |

| 6.3 | The characteristics of target simulators                                    | 127 |

| 6.4 | Performance of SPICE-H                                                      | 128 |

| 7.1 | The number of effective code lines changed/added to accelerate the baseline |     |

|     | MPI implementation                                                          | 150 |

| 7.2 | The experimental cluster's configurations | <br>151 |

|-----|-------------------------------------------|---------|

| 7.3 | The CPU-GPU cluster's configurations      | <br>151 |

# List of Abbreviations and Acronyms

**API** Application Programming Interface.

ATA Adaptive Task Aggregation.

**BLAS** Basic Linear Algebra Subprograms.

**BSP** Bulk Synchronous Parallel.

**CAD** Computer-Aided Design.

**CFD** Computational Fluid Dynamics.

CSC Compressed Sparse Column.

**CSR** Compressed Sparse Row.

CU Compute Unit.

**CUDA** Compute Unified Device Architecture.

**DAG** Directed Acyclic Graph.

**DSL** Domain Specific Language.

FLOPS Floating-Point Operations per Second.

**GPU** Graphics Processing Unit.

**HPC** High-Performance Computing.

**HSA** Heterogeneous System Architecture.

**IR** Intermediate Representation.

LRU Least Recently Used.

MIC Many Integrated Cores.

MPI Message Passing Interface.

**NR** Newton-Raphson.

OpenCL Open Computing Language.

OpenMP Open Multi-Processing.

**PCG** Preconditioned Conjugate Gradient.

**PT** Persistent Threads.

**SET** Sorted Eager Task.

**SIMD** Single Instruction Multiple Data.

**SPICE** Simulation Program with Integrated Circuit Emphasis.

**SpILU** Sparse Incomplete Lower-Upper factorization or decomposition.

**SPMD** Single Program Multiple Data.

**SpTS** Sparse Triangular Solve.

SSA Static Single Assignment.

VCG Value Communication Graph.

VFC Value-Flow Chain.

## Chapter 1

## Introduction

The availability of scalable computing resources has been crucial for advancing scientific discovery by empowering researchers to simulate complex physical phenomena and to analyze the multitudes of available data. For decades, high-performance computing (HPC) systems were homogeneous based on clusters of sequential CPUs [157]. With the end of frequency scaling [185], computer architectures have shifted to parallel processing on a single chip using a diverse set of compute resources, memory subsystems, and execution models. As a result, HPC systems evolved to incorporate an array of heterogeneous parallel devices, ranging from general-purpose processors to specialized accelerators. For example, the Summit supercomputer [86] integrates 48 latency-optimized cores, 30,720 throughput-oriented cores, and 3,840 high-density (tensor) cores in each node, delivering billions to quadrillions of floating-point operations per second (FLOPS) with different precision and accuracy characteristics.

### 1.1 Research Problems

To meet the ever-increasing demand for computing power, end users need to efficiently utilize current (and future) HPC systems by tackling three main challenges: heterogeneity, scalability, and interoperability.

Heterogeneity. The diversity of parallel architectures and execution models has complicated the design and development of high-performance applications, as end users have to decide which architecture, programming language, algorithm, and implementation technique are the most suitable for their applications, which in turn requires significant hardware and software expertise. In addition, extracting optimal performance demands manual design-, compile-, and run-time analysis and optimization for each underlying hardware architecture, which consumes significant time and effort. Therefore, while the hardware performance continued to improve according to Moore's Law, as a result of the transistor scaling, user applications typically attain a fraction of the theoretical performance. Furthermore, the transistor scaling is expected to reach the limits of lithography over the next decade [71], effectively ending Moore's Law and leading to the era of extreme heterogeneity [191, 192], where improving the application performance necessitates specialization across the whole software and hardware stack.

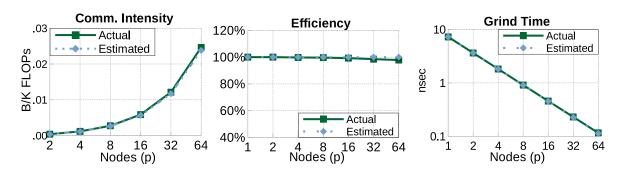

Figure 1.1: The gap between the computation and communication costs on the Cascades cluster at Virginia Tech.

Scalability. HPC systems suffer from an increasing gap between the computation and communication costs [24]. Our experiments demonstrate that the cost of data transfers, both within a node and across nodes, can be orders of magnitude higher than the cost of compute operations [82, 80, 78]. For example, Figure 1.1 shows that the computation to communication gap on Cascades, which is an HPC cluster at Virginia Tech, can be more than two orders of magnitude. Worse, such a gap increases with the number of nodes/processes

because of the contention on the shared network and memory bandwidth. As a consequence, the scalability of user applications on HPC systems is limited by the communication cost. Unfortunately, estimating and realizing the minimum communication of a given application is extremely challenging for end users, as it requires comprehensive application and architecture knowledge and demands significant manual analysis and optimization. Moreover, in parallel applications, the communication arise from the inherent data dependencies between the computational tasks. Therefore, most efforts to parallelize irregular computations with fine-grained data dependencies has had limited scalability [79, 83], although such computations constitute the core kernels in many important application domains, such as computational fluid dynamics (CFD), computer-aided design (CAD), and data analytics.

Interoperability. Parallel architectures are changing faster than parallel programming models and software. Thus, heterogeneous HPC systems require hybrid programming models and various optimization approaches to exploit their potential performance and energy efficiency. Dealing with interoperation between different devices and programming models is a tedious and error-prone task for end users. While many approaches have been proposed to abstract the hardware details, such as directive-based programming models [146, 145] and portable runtime systems [180, 129], they come with a performance penalty or lack performance portability across different platforms [79].

### 1.2 Thesis Statement

To streamline the transition of scientific applications to the exascale era of heterogeneous billion-way parallelism, this dissertation presents novel program analyses and adaptive execution approaches. The central thesis is: graph-structured program representations, which communicate the inherent application characteristics and the complex interdependencies to the execution environment, enable automated runtime analysis and adaptation methods that significantly improve the performance, scalability, and interoperability on heterogeneous HPC systems.

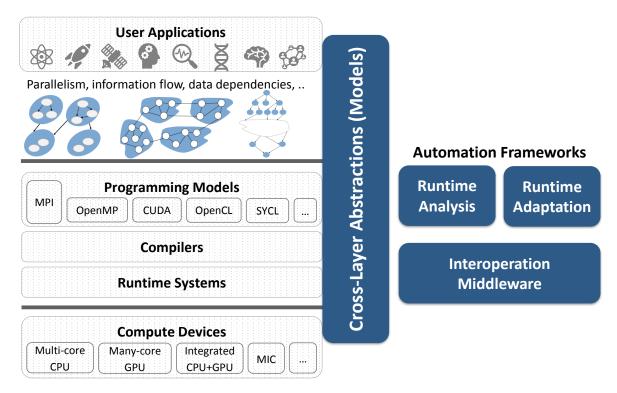

## 1.3 Methodology

Figure 1.2 depicts the proposed methodology to enable (1) automated generation of parallel performance and scalability models for sequential codes, (2) scalable execution of compute operations with fine-grained data dependencies, and (3) interoperation and workload distribution across heterogeneous parallel architectures. To bridge the semantic gap between user applications and HPC platforms, we construct graph-structured program representations that capture the inherent application characteristics and the complex (many-to-many) interdependencies at multiple levels of computational granularity. These program representations allow the generation of cross-layer abstractions (models) to reason about the performance bottlenecks on heterogeneous parallel architectures, which makes it possible to appropriately map the application kernels to the underlying hardware architectures for maximum performance via our novel frameworks [80, 82, 83, 78, 79] for performance analysis, runtime adaptation, and interoperation.

Figure 1.2: Overview of the proposed methodology.

The experimental results demonstrate that the introduced methods can deliver multiplicative performance gains for real-world applications, even when such applications suffer from limited parallelism and fine-grained data dependencies. Due to the ubiquity of heterogeneous computing, the proposed runtime analysis and adaptation approaches are applicable not only to the target HPC platforms, but also to embedded and mobile computing systems.

### 1.4 Contributions

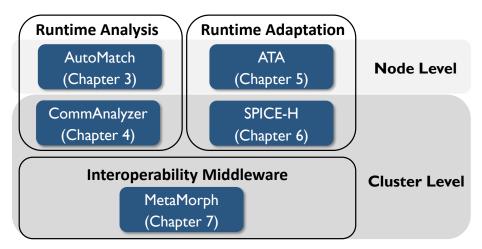

This dissertation tackles the heterogeneity, scalability, and interoperability challenges of modern HPC systems via innovative approaches for automated program analysis and runtime adaptation. To this end, we demonstrate that graph-structured program representations are powerful abstractions to reason about the performance bottlenecks not only on a single HPC node, but also on multi-node HPC systems. Figure 1.3 presents a summary of the research artifacts and contributions, which are detailed below.

Figure 1.3: Dissertation overview.

### 1.4.1 Automated Program Analysis for Performance Modeling

#### Automated Estimation of Execution Cost on Heterogeneous Architectures

Projecting the relative performance of a given code across different types of HPC architectures plays a critical role in the design and development of high-performance applications.

Unlike the previous "black-box" approaches that rely on the performance of a training set of parallel applications, the proposed AutoMatch framework [80] automatically projects the relative parallel performance of sequential codes across multi-core CPUs and many-core GPUs. Specifically, AutoMatch constructs a graph-structured program representation at the instruction level and uses a hybrid (static and dynamic) analysis to estimate the best dependencypreserving parallel schedule of target programs. As a result, AutoMatch enables a runtime workload distribution scheme that simultaneously utilizes the different hardware architectures within an HPC node in a performance-proportional way, i.e., the architecture with higher performance is assigned more workload. For a set of open-source HPC applications with different characteristics, AutoMatch turns out to be very effective, identifying the performance upper-bound of sequential applications across five different HPC architectures. In addition, AutoMatch's workload distribution scheme achieves approximately 90% of the performance of the profiling-driven oracle [80]. Furthermore, AutoMatch indicates that the predicted speedup by the previous "black-box" performance modeling approaches can be misleading, due to the lack of a diverse set of reference training applications along with their equally-optimized parallel implementations for each architecture type.

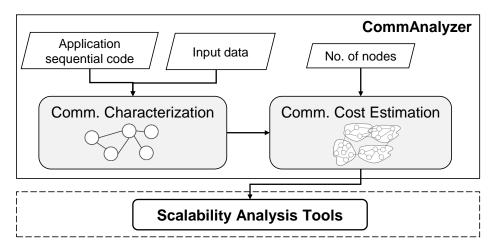

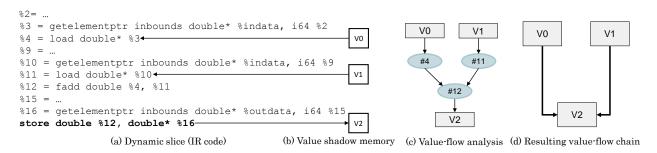

#### Automated Estimation of Communication Cost and Scalability

The proposed CommAnalyzer framework [82] is a novel and automated approach for estimating the communication cost of sequential codes when ported to HPC clusters, which makes it possible to project the scalability upper-bound of the effective distributed-memory implementation before even developing one. CommAnalyzer instruments the sequential code to precisely capture the inherent flow of program values (information) through multiple levels of access indirection to construct a value communication graph (VCG). Next, it uses graph analytic algorithms to project the communication cost of VCG on distributed-memory models. Thus, CommAnalyzer is applicable for both regular and irregular problems and works also for programs that cannot be auto-parallelized. The experiments with real-world HPC

applications demonstrate the utility of CommAnalyzer in estimating the minimum communication cost with more than 95% accuracy on average [82]. As a result, CommAnalyzer enables the development of optimized distributed-memory implementations that realize the estimated communication and scalability bounds [82].

#### 1.4.2 Runtime Adaptation for Scalable Performance

While regular applications (e.g., dense linear algebra and structured grids) have demonstrated scalable speedup in the heterogeneous computing era, irregular applications still suffer from limited scalability due to the inherent synchronization and communication cost. Thus, the HPC community is moving to use irregular benchmarks for the procurement and ranking of HPC systems [59, 134]. This dissertation proposes runtime adaptation approaches for efficient parallel execution of irregular computations with fine-grained data dependencies. Such workloads are extremely challenging for acceleration on heterogeneous HPC systems as the dispatch, scheduling, communication, and synchronization cost becomes the dominant performance bottleneck compared to the execution cost of compute operations.

#### Efficient Dependency Management on Massively Data-Parallel Architectures

Many-core architectures, such as GPUs, have a massive number of throughput-oriented compute units that are primarily designed to support data-parallel execution. Consequently, irregular computations with fine-grained data dependencies suffer from limited performance on these architectures, due to the substantial overhead required to schedule the computations and to manage their data dependencies. We propose the adaptive task aggregation (ATA) framework [83] to efficiently execute such irregular computations on massively data-parallel architectures. ATA represents the data-dependent computations as a hierarchical directed acyclic graph (DAG), where nodes are multi-grained application tasks and edges are their aggregated data dependencies. Unlike previous approaches, ATA is aware of the dependency

structure of input problems and the processing overhead on target architectures. Therefore, it adapts the parallel execution at runtime by selecting the appropriate task granularity and by managing data dependencies at multiple execution levels. On a gamut of representative problems with different data-dependency structures, ATA significantly outperforms the existing GPU task-execution approaches, achieving a geometric mean speedup of  $2.2 \times 3.7 \times 3.7$

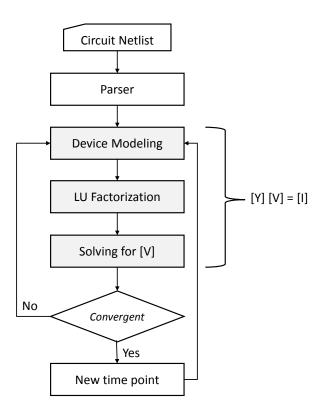

#### Scalable Execution of Irregular Data-Dependent Computations

We propose SPICE-H [78], a heterogeneous distributed-memory framework for a representative irregular application with limited and data-dependent parallelism, namely transistor-level circuit simulation [135]. The target application has been traditionally restricted to a single homogeneous architecture because of the sequential dependencies between its fine-grained compute operations. SPICE-H constructs a hypergraph program representation at the application level to drive compensation-based algorithms for program transformation that greatly reduce the communication and synchronization overhead as well as increase the available parallelism. Unlike prior work, our framework uses model-driven runtime analysis and adaptation to (1) find the optimal workload partitioning and load balancing, and (2) map the partitioned kernels to the most suitable architecture that matches their characteristics. The experimental results on Amazon EC2 heterogeneous cloud demonstrate an order-of-magnitude speedup compared to the optimized multi-threaded implementations [78].

### 1.4.3 Interoperability Middleware for Simultaneous Execution

Parallel architectures are changing more rapidly than parallel programming models, and until now, there has been no universal programming model that provides both functional portability and performance portability. We present MetaMorph [79], a lightweight middle-

ware that resides between user applications and hardware platforms to allow interoperability and workload distribution across heterogeneous compute resources.

MetaMorph addresses the challenges of programming heterogeneous architectures through its core design principles: abstraction, interoperability, and adaptability. First, it provides high performance and abstraction using a highly-optimized back-end layer and a light-weight interface layer that does not require significant application re-factoring. Second, MetaMorph supports interoperability across different hardware accelerators and with existing code. Most importantly, MetaMorph is designed to exploit runtime information to improve the performance even more by providing access to all hardware devices present in a system to enable simultaneous execution and workload distribution. The experimental evaluation shows that MetaMorph reduces the development time, while delivering performance and interoperation across an array of heterogeneous devices, including multi-core CPUs, Intel Many Integrated Cores (MICs), AMD GPUs, and NVIDIA GPUs. In particular, MetaMorph enables a simultaneous execution approach that effectively uses all the heterogeneous resources in the target HPC systems [79].

### 1.5 Dissertation Outline

The rest of the dissertation is organized as follows. Chapter 2 presents the background and related work. Chapters 3 and 4 detail our research on projecting the parallel performance and scalability of sequential codes. Chapter 5 describes our runtime adaptation framework for dependency management on massively parallel GPU architectures. Chapter 6 attacks the problem of scaling irregular data-dependent computations on heterogeneous HPC clouds. Chapter 7 presents our middleware framework which provides interoperation and simultaneous access to the available compute resources in an HPC system. Finally, Chapter 8 summarizes the dissertation and outlines the future research opportunities.

## Chapter 2

## Background and Related Work

## 2.1 HPC Programming Models

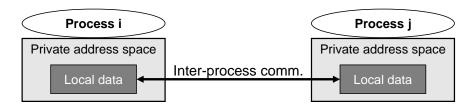

With the end of frequency scaling and the shift to parallel and heterogeneous computing, developing software has become much more complex [185]. While the Message Passing Interface (MPI) remains the de facto standard for programming distributed-memory systems [56, 20], many approaches have been proposed to address the challenges of programming shared-memory parallel architectures by abstracting their hardware details. This section discusses the related parallel programming models and runtime systems.

Directive-based programming models, such as OpenMP (Open Multi-Processing) [146] and OpenACC (Open Accelerator) [145], move the burden of explicit thread management, workload partitioning and scheduling, data movement across the memory hierarchy, and interthread communication and synchronization to the compiler. While OpenMP and OpenACC abstract away complex details and provide a convenient interface to describe the parallelism to the compiler, achieving acceptable performance requires deep understanding of the underlying hardware architecture, runtime system, compiler limitations, and a number of complex directive specifications. Moreover, the programmer must use thread-safe functions, eliminate

inter-thread data dependencies, avoid pointer aliasing, and manage access to shared variables and data structures. In addition, the high-level abstraction of directive-based programming can come with a performance penalty [199, 196, 95, 50] compared to low-level programming models, such as OpenCL (Open Computing Language) [133] and CUDA (Compute Unified Device Architecture) [141].

Portable runtime systems, such as OpenCL [180] and OCCA [129], provide a kernel specification language and a runtime compilation and execution environment on multiple heterogeneous platforms. Although these approaches support functional portability, performance portability is not guaranteed, as the application developers need to modify and optimize the kernel implementation for each target hardware platform to achieve the required performance. Moreover, these approaches have relatively lower programmability in comparison with directive-based programming, as the programmer must explicitly manage all the hardware control operations, such as memory allocation, data transfer, thread creation/destruction, and synchronization.

Domain-specific libraries provide both abstraction and high performance for a set of kernels and algorithms in a target domain. However, this often comes with the cost of complicated installations and extensive application refactoring. For example, MAGMA [58] provides highly optimized and intelligently scheduled BLAS (Basic Linear Algebra Subprograms) kernels, but due to the dependency on external libraries is difficult to install, configure, and tune, and it does not yet provide unified or consistent capability across its many-core implementations. Although MAGMA supports multi-GPU BLAS kernels, there is no built-in support for interoperability across different hardware accelerators. PARALUTION [124] and ViennaCL [164] provide iterative solvers and preconditioners for many important application domains, such as computational fluid dynamics (CFD), and support various multi-core and many-core architectures. However, these solver frameworks require recasting the application to use complex cases and object types, which presents a barrier to the incremental porting of user applications.

In summary, directive-based programming models trade performance with high-level abstraction, while low-level languages and portable runtime systems can achieve high performance with the cost of low programmability and explicit hardware control. Domain-specific libraries can achieve high-level abstraction and high performance, but only for a set of algorithms in a specific domain and with a significant application re-factoring, complicated installation, and steep learning curve.

## 2.2 Massively Parallel HPC Architectures

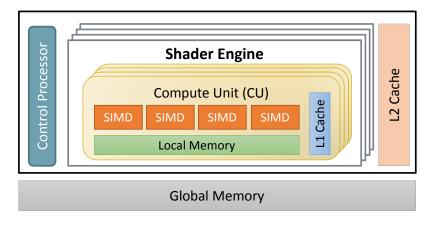

Here, we use graphics processing units (GPUs), which are the most popular accelerators in modern HPC systems [130], and the OpenCL terminology to describe massively parallel architectures and their execution models.

Figure 2.1 depicts the recent VEGA GPU architecture from AMD [10], which consists of multiple compute units (CUs) organized into shader engines (SEs). Each CU contains single-instruction, multiple-data (SIMD) processing elements. SEs share global memory and level-2 (L2) cache, while CUs have their own dedicated local memory and level-1 (L1) cache. At runtime, the control/command processor (CP) dispatches the workload (kernels) to the available SEs and their CUs.

Figure 2.1: VEGA GPU architecture.

Figure 2.2: GPU kernel.

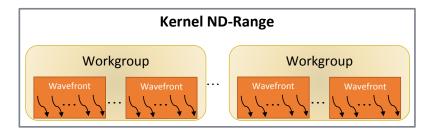

Like GPU hardware, GPU kernels have a hierarchical thread organization, as shown in Figure 2.2, consisting of workgroups of multiple wavefronts. The SIMD elements execute each wavefront in lockstep; thus, wavefronts are the basic scheduling units.

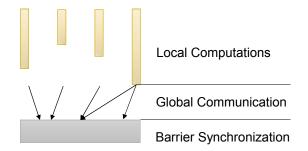

Massively parallel GPUs provide fundamental support for the bulk synchronous parallel (BSP) execution model [189], where the computations proceed in data-parallel supersteps. Figure 2.3 depicts a BSP superstep which consists of three phases: local computations on each CU, global communication (data exchange) via main memory, and barrier synchronization.

Figure 2.3: The execution of a BSP superstep.

In BSP execution, the computations in each superstep must be independent and can be executed in any order. To improve workload balance, each CU should perform a similar amount of operations. Moreover, GPUs require massive computations in each superstep to utilize the available compute resources and to hide the long memory-access latency. Due to these limitations, the efficient BSP execution of irregular applications with variable and data-dependent parallelism is challenging.

## 2.3 Performance Modeling on HPC Systems

There are many approaches and substantial prior work for performance modeling on HPC systems that can be classified into four categories: analytical modeling, simulation, automated performance prediction, and communication and scalability analysis.

### 2.3.1 Analytical Modeling

Analytical modeling maps the application and execution environment into a set of parameters and mathematical expressions that can be evaluated to predict important performance metrics, such as the execution time. While analytical modeling provides useful insights into the application performance by capturing the complex interactions between the HPC platform, application, and input data [200, 92], it requires tedious manual analysis of both the target applications and hardware architectures. Typically, there is a tradeoff between the accuracy of an analytical model and the number of its parameters. While complex performance models have higher accuracy levels, they require extensive analysis and are harder to generalize to different types of hardware architectures. The Roofline model [200] and LogP model family [47, 7] are popular modeling approaches that provide a high-level view of the application performance using a few parameters; however, they abstract away critical factors, such as the parallelism, data locality, and synchronization overhead.

Empirical models [92, 30] use profiling and statistical analysis to calculate the critical coefficients that are hard to derive from manual analysis. Therefore, while such models can predict the actual performance of an application on a particular architecture with high accuracy, they require the availability of both the target hardware and optimized parallel code.

To explore the algorithmic and architectural design space, Spafford and Vetter present AS-PEN [176], a language for describing formal application and machine models. PALM [186] simplifies the performance modeling process by supporting the generation of standard analytical models from annotated source code. Snavely et al. [175] provide a framework to

generate analytical performance models from the execution and communication traces of HPC applications and the abstract machine profiles.

#### 2.3.2 Simulation

Hardware simulators, such as Sniper [31] and gem5 [25, 153], can provide accurate performance prediction and detailed information about the application behavior without the availability of target hardware architectures. However, they need the parallel application code and typically consume significant time and compute/memory resources. In addition, the predicted performance depends on the ability of end users to prallelize and optimize the application to the simulated architecture. Similarly, distributed-memory simulators (e.g., LogGOPSim [91] and DIMEMAS [160]) incorporate detailed network and architecture models to estimate the communication time and performance from the compute/communication traces of parallel code. MUSA [73] adopts a multi-level simulation approach with different levels of hardware details, simulation cost, and simulation accuracy. In addition, it identifies and simulates the representative application phases to reduce the overall simulation time.

#### 2.3.3 Automated Performance Prediction

Recently, several tools have been proposed to automate the performance modeling and prediction using program analysis and machine-learning. Table 2.1 summarizes the comparison of the state-of-art performance prediction tools for heterogeneous HPC architectures.

COMPASS [114] generates a structured performance model from the parallel application code using static analysis. However, the user must annotate the code to indicate the available parallelism and required data movement to generate an accurate model. Otherwise, COMPASS may generate a conservative parallelism profile, due to the difficulty of alias analyses [111, 156]. Therefore, COMPASS does not work well for irregular applications whose computation and memory access patterns are data-dependent.

Table 2.1: Comparison of recent performance prediction tools for heterogeneous HPC architectures (CPUs and GPUs)

|                          | COMPASS [114]   | XAPP [13]        | AutoMatch            |

|--------------------------|-----------------|------------------|----------------------|

| Input code               | Annotated       | Sequential       | Sequential           |

| Features extraction      | Static analysis | Dynamic analysis | Hybrid analysis      |

| Machine model generation | By users        | Training data    | Micro-benchmarking   |

| Performance modeling     | ASPEN model     | Machine-learning | Execution Cost model |

| Cache-awareness          | No              | Yes              | Yes                  |

| Usability                | Low             | High             | High                 |

| Application generality   | Low             | High             | High                 |

| HW generality            | High            | Low              | High                 |

| The tool speed           | Fast            | Slow             | Moderate             |

XAPP [13] uses machine-learning (ML) to find the correlation between the CPU execution profile of the application and the GPU speedup. Therefore, XAPP is heavily influenced by the training data, and its prediction accuracy depends on the availability of a diverse set of applications along with their optimized GPU implementations. So, extending XAPP to new architecture types requires huge effort to rewrite and re-optimize each training application to the target architectures. Moreover, to predict the performance on a specific GPU device, the user needs to run all the training applications on this device, which takes days. Such long-running model generation of ML-based tools end up being orders of magnitude slower than our AutoMatch framework, which generates the device parameters using micro-benchmarks that takes few minutes. In addition, XAPP's predicted speedup is not the speedup upper-bound, and it depends on which optimization techniques are applied in the training applications.

Kismet [97] predicts the potential speedup of sequential applications on multi-core processors. It instruments the code to build the self-parallelism profile, and estimates the memory access latency by profiling the application on a CPU cache simulator. Kismet optimistically assumes

that the memory bandwidth is scalable with the number of threads, which is unrealistic assumption especially for massively parallel architectures such as GPUs. Therefore, its predicted speedup is unattainable at higher core counts and for memory-bound workloads. As an alternative, Parallel Prophet [107] predicts the speedup of the annotated code on multi-core CPUs. Unlike Kismet, it does not require parallelism discovery, but relies on user annotations to identify the available parallelism. To build the performance model, Parallel Prophet collects architectural parameters such as instruction counts and cache misses through hardware performance counters, which requires the availability of the target CPUs and the parallel (or annotated) code.

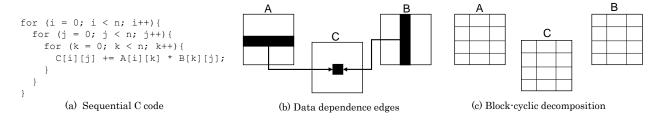

### 2.3.4 Communication and Scalability Analysis

#### Communication Cost Estimation

Several approaches have been proposed for estimating the communication cost of sequential codes to enable code generation for distributed-memory platforms [87, 201, 77]. The FORTRAN-D compiler [87] uses static data-dependence analysis to detect the communication between different sections/parts of a data array, which is partitioned according to a user-specified decomposition technique. However, this approach suffers from communication overestimation, and it is limited to regular applications. Similarly, Gupta et al. [77] adopt a compile-time, data-dependence analysis for estimating the communication of sequential codes, which is only applicable for regular problems with array-based data structures. The SUIF compiler [201] solves the communication overestimation problem using the exact static data-flow analysis, but it is limited to affine loop nests with regular memory access pattern, where dependencies between loop iterations and memory locations can be detected at compile time. In contrast, our CommAnalyzer framework predicts the communication between program values regardless of the underlying data structures and without any user-specified decomposition techniques using a combination of novel dynamic analyses and graph analytics. Thus, CommAnalyzer is applicable to a wide range of regular and irregular applications.

While the above approaches estimate the communication cost using the single program, multiple data (SPMD) execution model, which is by far the dominant approach on HPC systems [56, 20], Bondhugula [28] presents a polyhedral framework to estimate the communication when there is no fixed data ownership, i.e., the data can move between compute nodes according to the distribution of the computations and data dependencies. However, this approach is limited to regular applications with affine loop nests as well.

#### Communication Pattern Detection

Identifying the communication patterns of HPC applications is helpful in the design-space exploration of both the system architectures and parallel algorithms. Several tools [163, 105] have been proposed for the detection of MPI communication patterns by finding a match between the actual inter-process communication and a set of known communication templates/patterns. These tools instrument the MPI implementation to capture the interprocess communication and to generate the communication matrix across MPI processes, and then they recognize existing communication patterns in the communication matrix. In particular, AChax [163] can identify multiple communication patterns (such as nearest neighbor, sweep/wavefront, broadcast, and reduction) in the communication matrix and generate a parametrized communication model for the actual communication based on a combination of the detected communication patterns.

#### Scalability Analysis

The scalability analysis tools [18, 209, 29, 33] project the performance of a given MPI implementation at a massive scale based on small-scale experiments. Typically, these tools extract the communication, computation, and/or memory traces of MPI applications using dynamic instrumentation and profiling. Therefore, they require the distributed-memory parallel implementations and at least a single node of the target cluster to predict the performance on multiple nodes. TAU [173] and HPC toolkit [3] are integrated frameworks for portable

performance analysis, profiling, and visualization. Similar to scalability analysis tools, their main goal is to simplify the performance analysis and diagnosis of the existing MPI code, rather than estimating the potential performance at a large scale before investing effort and time in developing the distributed-memory implementation of the original applications.

## 2.4 Data Dependency Management on Massively Parallel HPC Architectures

There is a large body of prior work on optimizing irregular applications for massively parallel architectures. This section focuses on irregular applications that suffer from *fine-grained data dependencies*, which limit their parallel performance and scalability on these architectures. Such applications are naturally represented as directed acyclic graphs (DAGs), where nodes are compute tasks and edges are data dependencies across tasks, to expose parallel tasks.

Researchers have designed many software and hardware frameworks to improve the performance of *data-dependent* computations on massively *data-parallel* architectures, such as many-core GPUs. In the following, we discuss the state-of-the-art dependency management frameworks.

Juggler [23] is a data dependency management scheme for GPUs that maintains task queues on the different compute units and employs persistent workers (workgroups) to execute ready tasks and to resolve the data dependencies of waiting tasks. Other frameworks [178, 179, 210] adopt a similar execution model with persistent threads (PT) on GPUs. PT execution significantly reduces GPU resource utilization and limits the latency hiding ability of GPU hardware schedulers. While GPUs require massive multithreading to hide the execution and memory access latencies [66, 161, 10], PT execution only runs one worker per compute unit. Therefore, such frameworks typically achieve a limited performance improvement compared to the traditional data-parallel execution (for example, 1.05 to 1.30-fold speedup [23])

with portability issues across different GPU devices. Conversely, our ATA framework executes multiple workers per compute unit to maximize the utilization of GPU resources and to expose the inherent parallelism of user applications. Moreover, achieving workload balance using distributed task queues is difficult and requires significant processing overhead. As a result, PT execution approaches typically execute user tasks at the granularity of workgroups. In contrast, ATA leverages the existing hardware schedulers for GPUs, which perform dynamic resource management across active wavefronts, to reduce the idle/waiting time by concurrently executing the available tasks in user applications and mapping them to active wavefronts. Furthermore, ATA can support a wide range of granularity, ranging from wavefronts to workgroups.

Alternatively, several runtime systems for task management [15, 21, 67, 154] support irregular applications by launching each user task as a parallel kernel and by using device streams or queues to manage data dependencies across kernels. In such systems, the task launch overhead is on the order of microseconds, and the dependency management using streams (queues) only supports a finite number of pending dependencies. Thus, these approaches are limited to irregular applications with coarse-grained tasks, where the dependency management overhead is a fraction of the overall execution time. Specifically, StarPU [15] and Legion [21] schedule the data-dependent computations on heterogeneous architectures with multiple CPUs and GPUs, and consider a single device (CPU or GPU) as a worker. Furthermore, these runtime systems manage data dependencies on the host, which introduces significant host-device communication and synchronization overhead.

Pagoda [207] and GeMTC [109] adopt a centralized scheduling approach to execute independent application tasks on GPUs using a resident kernel, which distributes ready tasks to compute units at the wavefront granularity. However, these frameworks assume that all the dispatched tasks are ready for execution and do not support dependency tracking and resolution. Specifically, they rely on the host to send ready tasks to the GPU after their dependencies are resolved. Therefore, Pagoda and GeMTC suffer from host-device communication which is limited by the PCI-E bandwidth.

Prior software systems [62, 37, 187, 61] improve the performance of dynamic parallelism, where a GPU kernel can launch child kernels, by aggregating the *independent* work-items across child kernels to amortize the kernel launch overhead; however, these techniques are not suitable to execute application DAGs with many-to-many relationships (dependencies) between the predecessor and successor tasks. Conversely, in our ATA framework, work aggregation is used to execute irregular applications with *data-dependent* tasks both within and across GPU kernels, which requires efficient mechanisms to track the progress of active tasks and to determine when waiting tasks are ready for execution. Hence, ATA aggregates *data-dependent* work across user tasks with a strict partial execution order and then enforces this order using hierarchical dependency management and low-latency task scheduling.

Alternatively, hardware approaches [2, 147, 194, 195] aggregate and execute data-dependent computations on many-core GPUs using dedicated hardware units or specialized workgroup (thread-block) schedulers. Unlike these approaches, the proposed ATA framework works on current GPU architectures without needing special hardware modifications. In addition, it supports a finer task granularity than workgroups.

## Chapter 3

# Automated Estimation of Execution Cost on Heterogeneous Architectures

## 3.1 Introduction

With the end of Dennard scaling, the performance of sequential CPUs hit the power wall, thus making it hard to improve the performance by increasing the clock frequency [185]. To meet the ever-increasing demand for computing performance, driven by the multitude of data sets, computer architectures have shifted to parallel processing. However, unlike the sequential computing era, there is no de facto standard for hardware acceleration. Instead, the parallel architecture landscape is in flux as new platforms are emerging to meet the needs of new workloads. Therefore, current (and future) HPC systems contain a wide variety of heterogeneous computing resources, ranging from general-purpose CPUs to specialized accelerators, due to both the diversity of the computational kernels in the applications and the lack of a single architecture meeting all of their requirements [24].

Porting sequential applications to heterogeneous HPC systems for achieving high performance requires extensive software and hardware expertise to manually analyze the target

architectures and applications not only to estimate the potential speedup, but also to make efficient use of all the different compute resources in these systems. To streamline such a daunting task, end users need appropriate tools and frameworks to automatically predict the potential application performance on heterogeneous HPC systems. Therefore, researchers have created several tools classified into two categories: automated performance modeling and machine-learning performance prediction.

Automated performance modeling tools [97, 107, 114] use static and/or dynamic analysis to construct a performance model of the target application and hardware architecture, which is then used to predict the potential speedup. However, these tools are either limited to homogenous HPC systems, with traditional multi-core processors, or require code annotations to indicate the available parallelism and data movement, which might not be possible for non-expert users. In addition, tools based only on static analysis do not work well for irregular applications, whose computation and memory access patterns are data-dependent, due to the difficulty of alias analysis [111, 156].

On the other hand, machine-learning performance prediction tools [13, 17] adopt a "black-box" approach and are heavily influenced by the training data. Thus, their prediction accuracy depends on the availability of a diverse set of training applications along with their optimized parallel implementations for every target architecture, which is often hard to find [115]. Apart from that, the predicted speedup is not the speedup upper-bound, and even worse it depends on which optimization techniques are applied to the reference heterogeneous implementations of training applications. Unfortunately, open-source heterogeneous applications and benchmark suites are usually not equally-optimized for each architecture type [115, 181]. For this reason, machine-learning approaches may not be suitable to predict the relative performance between different architecture types despite the required expertise and effort to collect the ideal training set and the significant time for training. Given all this, there is a compelling need for a more practical approach to serve a wide range of the users of HPC systems.

#### 3.1.1 AutoMatch: The First-Order Framework

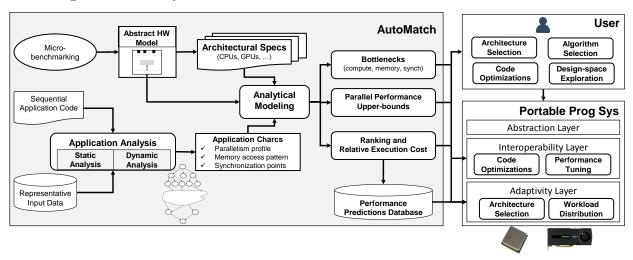

This chapter presents AutoMatch, an automated framework for matching of computational kernels to heterogeneous HPC architectures. Figure 3.1 shows the proposed framework which analyzes a given sequential application code and constructs a graph-structured program representation at the instruction level to estimate the benefits of porting such an application to heterogeneous HPC systems.

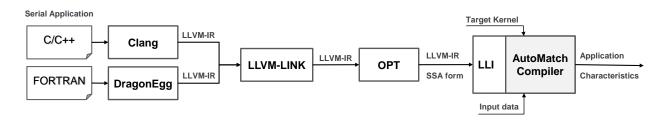

Figure 3.1: Overview of AutoMatch framework.

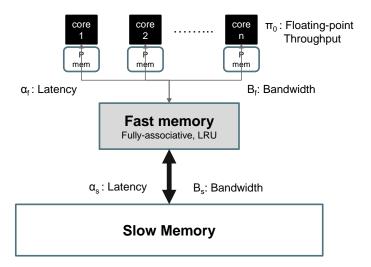

First, AutoMatch generates the architectural specifications via micro-benchmarking to instantiate an abstract hardware model for each architecture in the target heterogeneous system. Second, it leverages compiler-based static and dynamic analysis techniques to quantify the maximum parallelism, the maximum data locality, and the minimum synchronization of the sequential code for estimating the *upper bounds* of the parallel performance on the different architectures. Third, AutoMatch generates high-level analytical models which combine the abstract hardware model, application characteristics, and architectural specifications to predict the potential parallel performance on different types of hardware devices. This performance prediction is then used to estimate the relative execution cost across a set of different architectures, including multi-core CPUs and many-core GPUs, thereby driving a workload distribution scheme, which enables end users to efficiently exploit the available heterogeneous devices in an HPC system.

It is important to note that AutoMatch is designed as a *first-order* framework for users to estimate the potential parallel performance of their sequential applications on heterogeneous HPC systems in the early stages of the development process, i.e., without having to pay the high cost of developing the optimized parallel code (or painfully collecting training data) for every target architecture. While our automatically-generated models are simple, they work well for predicting the relative performance across different architectures and the best workload distribution strategy.

#### Use Cases

AutoMatch accelerates the development process of user applications and supports the emerging programming systems for performance portability and interoperability across different accelerators (such as MetaMorph [79], which is discussed in Chapter 7).

Architecture Selection. AutoMatch predicts the relative ranking of parallel heterogeneous architectures for sequential application codes. It serves not only those who either have not determined the target device or cannot afford to buy multiple candidate devices, especially when the application and inputs are often changed, but also those who lack enough expertise to develop the optimized parallel implementation for each architecture type. Furthermore, AutoMatch's ranking of target hardware architectures enables the adaptivity layer of portable programming systems to select the best performing architecture at runtime.

Algorithm Selection. AutoMatch predicts the upper bounds on parallel performance of a given sequential application code by finding the best dependency-preserving schedule of its operations, which performs the same operations as the sequential algorithm but in a different order. If AutoMatch's prediction of the original algorithm is already good enough, the user can save the time to consider other algorithms. Conversely, if the predicted performance is unsatisfactory, it motivates the user to explore/develop different algorithms. Nevertheless, AutoMatch can still play a critical role even for this case. The user can analyze the sequential code of different algorithms using AutoMatch to estimate the upper bounds on their parallel performance beforehand without developing the optimized parallel code(s).

Code Optimizations. AutoMatch provides detailed information about the inherent parallelism, data locality, and performance bottlenecks of the sequential application code to help users to decide on the best parallelization strategy and optimization techniques for their applications. Moreover, since it is often hard to find reference applications that are equally-optimized for each architecture type [115], AutoMatch's prediction of the performance upper bounds serve as a reference to show how close the parallel implementation is to the best possible performance. That way, AutoMatch can guide not only manual code optimization, but also the customization/tuning of the different backends of portable programming systems.

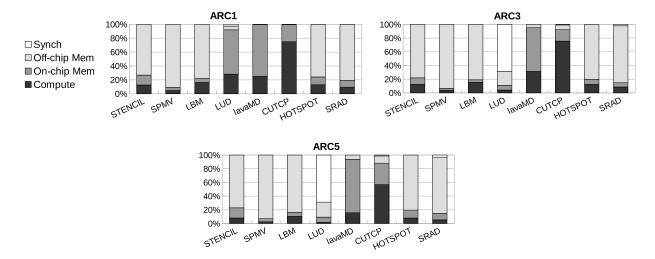

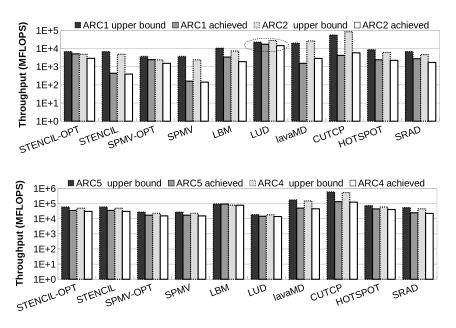

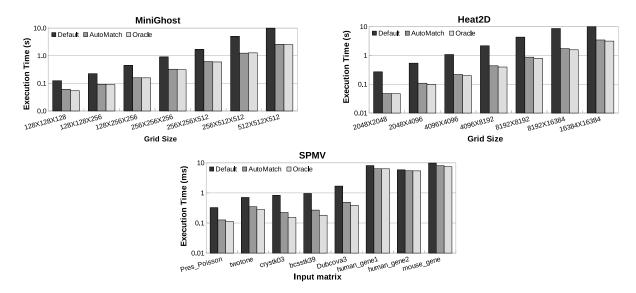

Workload Distribution. AutoMatch's estimation of the relative performance (execution cost) on heterogeneous systems promotes the development of a runtime workload distribution on top of programming systems that support the seamless execution of parallel applications on multiple heterogeneous devices (e.g., MetaMorph [79]) to efficiently exploit the available compute resources across these devices.