### Algorithms and Low Cost Architectures for Trace Buffer-Based Silicon Debug

#### Sandesh Prabhakar

Thesis submitted to the faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

Master of Science In

**Computer Engineering**

Michael S. Hsiao, Chair Christopher L. Wyatt Patrick Schaumont

December 1, 2009 Blacksburg, Virginia

Keywords: Silicon Debug, Logic Implications, Trace selection, State Restoration, Trace

Compression

Copyright ©2009, Sandesh Prabhakar

### Algorithms and Low Cost Architectures for Trace Buffer-Based Silicon Debug

Sandesh Prabhakar

#### **ABSTRACT**

An effective silicon debug technique uses a trace buffer to monitor and capture a portion of the circuit response during its functional, post-silicon operation. Due to the limited space of the available trace buffer, selection of the critical trace signals plays an important role in both minimizing the number of signals traced and maximizing the observability/restorability of other untraced signals during post-silicon validation. In this thesis, a new method is proposed for trace buffer signal selection for the purpose of postsilicon debug. The selection is performed by favoring those signals with the most number of implications that are not implied by other signals. Then, based on the values of the traced signals during silicon debug, an algorithm which uses a SAT-based multi-node implication engine is introduced to restore the values of untraced signals across multiple time-frames. A new multiplexer-based trace signal interconnection scheme and a new heuristic for trace signal selection based on implication-based correlation are also described. By this approach, we can effectively trace twice as many signals with the same trace buffer width. A SAT-based greedy heuristic is also proposed to prune the selected trace signal list further to take into account those multi-node implications. A state restoration algorithm is developed for the multiplexer-based trace signal interconnection scheme. Experimental results show that the proposed approaches select the trace signals effectively, giving a high restoration percentage compared with other techniques. We finally propose a lossless compression technique to increase the capacity of the trace buffer. We propose real-time compression of the trace data using Frequency-Directed Run-Length (FDR) code. In addition, we also propose source transformation functions, namely difference vector computation, efficient ordering of trace flip-flops and alternate vector reversal that reduces the entropy of the trace data, making them more amenable for compression. The order of the trace flip-flops is computed off-chip using a probabilistic algorithm. The difference vector computation and alternate vector reversal are implemented on-chip and incurs negligible hardware overhead. Experimental results for sequential benchmark circuits shows that this method gives a better compression percentage compared to dictionary-based techniques and yields up to 3X improvement in the diagnostic capability. We also observe that the area overhead of the proposed approach is less compared to dictionary-based compression techniques.

Acknowledgments

I want to express my sincere gratitude to my advisor Professor Michael Hsiao for his

continued guidance, motivation and encouragement throughout the duration of my

research. I want to thank him for giving me the opportunity to work with him and for

introducing me to the world of research. I will always cherish my interactions with him

for several important things that I have learned about research and life as a whole. This

work would not have been possible without his advice and encouragement at each stage

of my graduate student life. I am also highly grateful to Professor Christopher Wyatt and

Professor Patrick Schaumont for agreeing to be a part of my Masters committee.

I will always treasure my interaction with team-mates at PROACTIVE research lab for

their help and useful suggestions.

I am grateful to Craig Borden and Alec Shen for giving me the opportunity to intern at

Qualcomm Inc. and work on interesting DFT and digital design projects.

I want to thank Claudia Angelini for giving me challenging opportunities in the area of

DFT during my tenure at ST Microelectronics.

I want to thank my parents, sister and all family members and friends for their words of

encouragement, love and support.

Finally, I am grateful to God for always being there for me in my endeavor to become a

better person.

December 1, 2009

Sandesh Prabhakar

iv

## Contents

| List of | Figure | S                                                   | VII  |

|---------|--------|-----------------------------------------------------|------|

| List of | Tables |                                                     | ix   |

| 1       | Introd | uction                                              | 1    |

| 2       | Backg  | round                                               | 5    |

|         | 2.1    | Digital Integrated Circuit (IC) Development Process | . 5  |

|         | 2.2    | Need for Silicon Debug                              | . 7  |

|         | 2.3    | Silicon Debug                                       | . 7  |

|         | 2.4    | Static Logic Implications                           | 10   |

|         | 2.5    | SAT-based Boolean Constraint Propagation (BCP)      | . 15 |

|         | 2.6    | Restoration Ratio and Restoration Percentage        | 17   |

|         | 2.7    | Data Compression Codes                              | . 17 |

|         | 2.8    | Frequency Directed Run-length (FDR) Code            | 18   |

|         | 2.9    | Source Transformation                               | . 19 |

|         | 2.10   | Diagnosis and Compression Quality Metrics           | . 19 |

|         | 2.11   | Entropy                                             | . 20 |

|         | 2.12   | Average Hamming Distance and Toggling Percentage    | . 21 |

| 3       | Non-n  | nultiplexed Trace Selection and State Restoration   | 22   |

|         | 3.1    | Problem Formulation                                 | . 22 |

|         | 3.2    | New Trace Signal Selection                          | . 22 |

|         | 3.3    | State Restoration from Traced Signals               | 25   |

|         | 3.4    | Experimental Results                                | . 27 |

|         | 3.5    | Summary                                             | . 38 |

| 4       | Multip | plexed Trace Selection and State Restoration        | 39   |

|         | 4.1    | Problem Formulation                                 | . 39 |

|         | 4.2    | Implication-based Correlation                       | . 40 |

|         | 4.3    | Modified State Restoration Algorithm                | 46   |

|        | 4.4     | Multi-node implication-based trace list pruning        | 50<br>54<br>55 |

|--------|---------|--------------------------------------------------------|----------------|

|        | 4.5     | Experimental Results                                   | . 50           |

|        | 4.6     | Summary                                                | . 54           |

| 5      | Trace   | Compression using Source Transformation over FDR codes | 55             |

|        | 5.1     | The Proposed Approach                                  | . 55           |

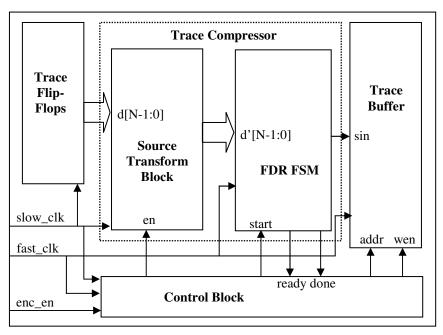

|        | 5.2     | The Compression Hardware                               | 60             |

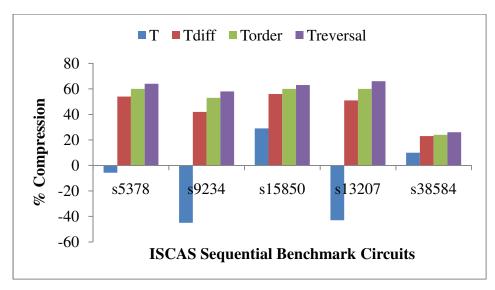

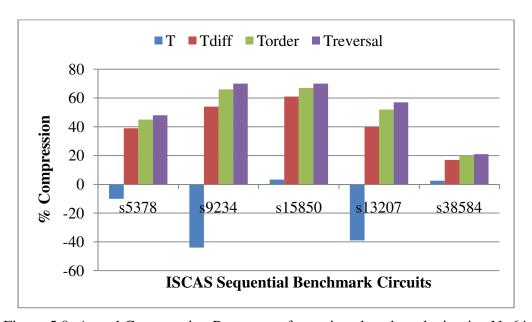

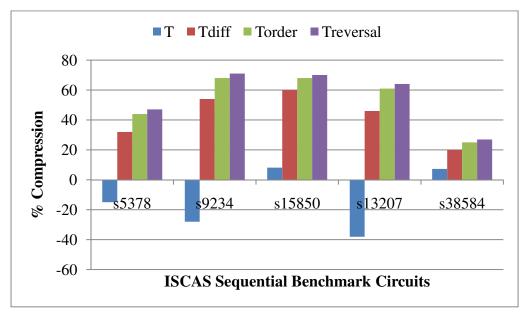

|        | 5.3     | Experimental Results                                   | 63             |

|        | 5.4     | Summary                                                | . 68           |

| 6      | Concl   | usion and Future Work                                  | 69             |

| Biblio | ography |                                                        | 71             |

# List of Figures

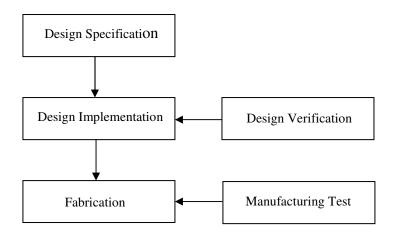

| 2.1  | Digital IC Development Process                                           |

|------|--------------------------------------------------------------------------|

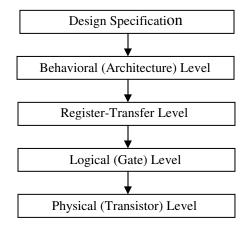

| 2.2  | Design Implementation Hierarchy 6                                        |

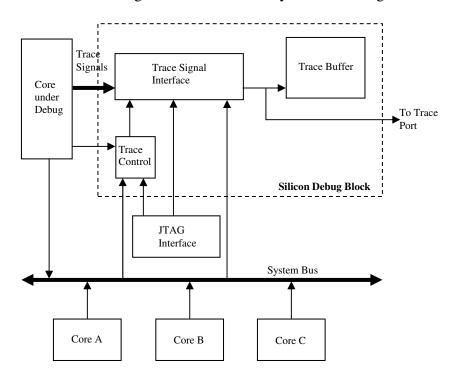

| 2.3  | Trace buffer-based Silicon Debug Architecture                            |

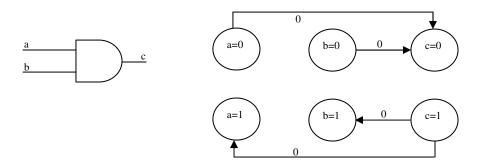

| 2.4  | Implication Graph Example                                                |

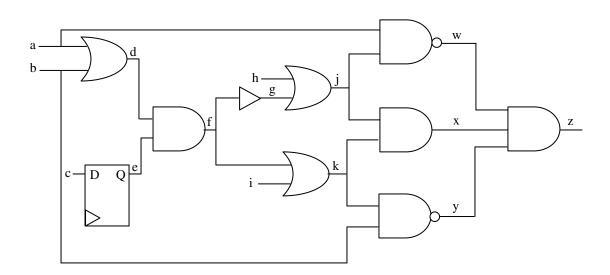

| 2.5  | Sequential Circuit Fragment                                              |

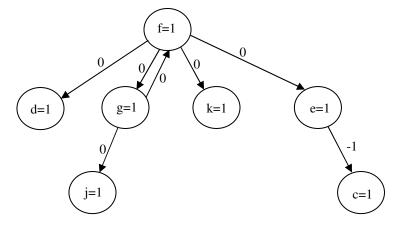

| 2.6  | Direct Implications for f=1                                              |

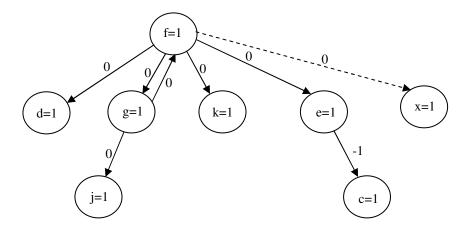

| 2.7  | Adding Indirect Implications for f=114                                   |

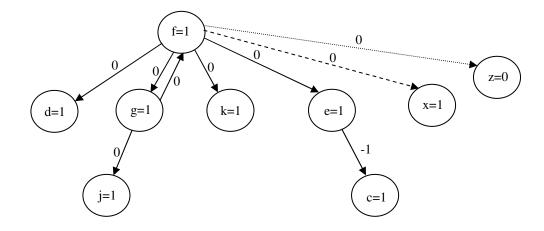

| 2.8  | Adding Extended Backward Implications for f=1                            |

| 2.9  | Boolean Constraint Propagation                                           |

| 2.10 | An FDR coding example                                                    |

| 3.1  | State Restoration- Forward and Backward Learning                         |

| 3.2  | TR <sub>all</sub> vs. TB width                                           |

| 3.3  | TR <sub>FFs</sub> vs. TB width                                           |

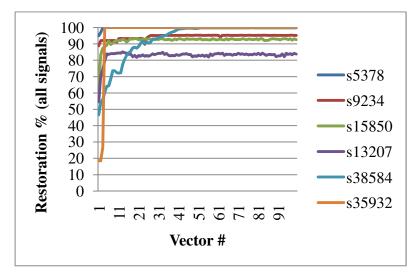

| 3.4  | Restoration % (all) vs. vector # for TB width=8                          |

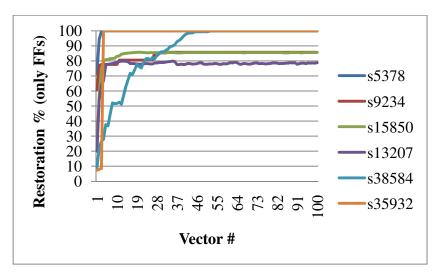

| 3.5  | Restoration % (FFs) vs. vector # for TB width=8                          |

| 3.6  | Restoration % (all) vs. vector # for TB width=16                         |

| 3.7  | Restoration % (FFs) vs. vector # for TB width=16                         |

| 3.8  | Restoration % (all) vs. vector # for TB width=32                         |

| 3.9  | Restoration % (FFs) vs. vector # for TB width=32                         |

| 3.10 | Restoration % (all) vs. vector # for TB width=64                         |

| 3.11 | Restoration % (FFs) vs. vector # for TB width=64                         |

| 3.12 | Restoration % (all) vs. vector # for TB width=128                        |

| 3.13 | Restoration % (FFs) vs. vector # for TB width=128                        |

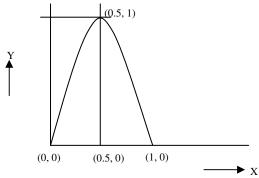

| 4.1  | Balance Factor                                                           |

| 4.2  | Implication-based Correlation                                            |

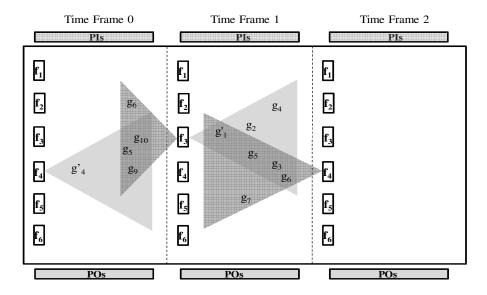

| 4.3  | Modified State Restoration                                               |

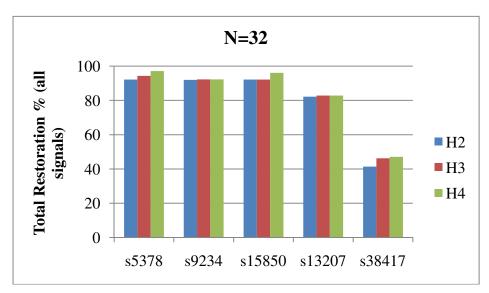

| 4.4  | Total Restoration Percentage (TR <sub>all</sub> ) for Benchmark Circuits |

| 5.1  | Transforming T to T <sub>diff</sub>                                      |

| 5.2  | Transforming T <sub>diff</sub> to T <sub>order</sub>                     |

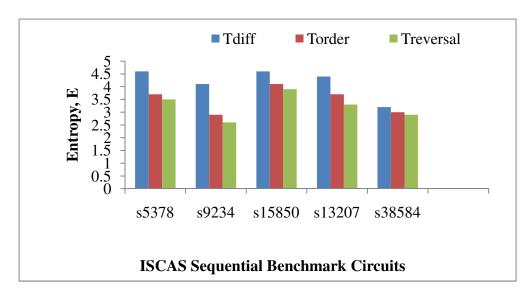

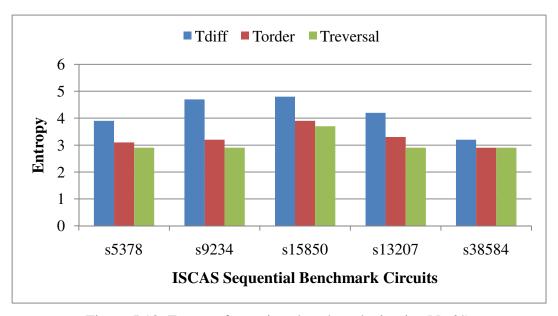

| 5.3  | Entropy for various Benchmark circuits (N=32)                 | 9  |

|------|---------------------------------------------------------------|----|

| 5.4  | Transforming T <sub>order</sub> to T <sub>reversal</sub>      | 0  |

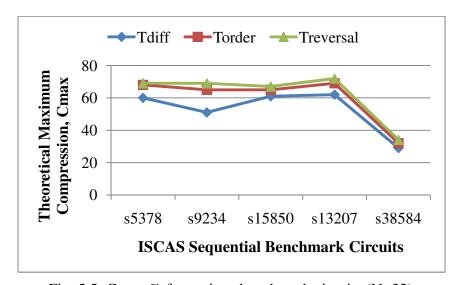

| 5.5  | Cmax % for various benchmark circuits (N=32)6                 | 0  |

| 5.6  | Trace Compressor Architecture                                 | 2  |

| 5.7  | Actual Compression % for various benchmark circuits (N=32)    | 54 |

| 5.8  | Actual Compression % for various benchmark circuits (N=64)    | 6  |

| 5.9  | Actual Compression % for various benchmark circuits (N=128) 6 | 6  |

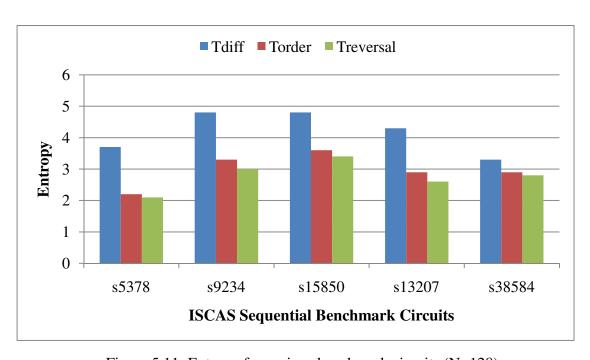

| 5.10 | Entropy for various Benchmark circuits (N=64)                 | 7  |

| 5.11 | Entropy for various Benchmark circuits (N=128)                | 7  |

## List of Tables

| 3.1  | Experimental Results (Trace Buffer Width=8)29                                            |

|------|------------------------------------------------------------------------------------------|

| 3.2  | Experimental Results (Trace Buffer Width=16)                                             |

| 3.3  | Experimental Results (Trace Buffer Width=32)                                             |

| 3.4  | Experimental Results (Trace Buffer Width=64)                                             |

| 3.5  | Experimental Results (Trace Buffer Width=128)                                            |

| 3.6  | Experimental Results -Poor (P) vs. our Algo (A) for first 10 vectors 30                  |

| 3.7  | Forward Learning (H <sub>1</sub> ) vs. Backward Learning (H <sub>2</sub> ) (N=8)         |

| 3.8  | Forward Learning (H <sub>1</sub> ) vs. Backward Learning (H <sub>2</sub> ) (N=16)        |

| 3.9  | Forward Learning (H <sub>1</sub> ) vs. Backward Learning (H <sub>2</sub> ) (N=32)37      |

| 3.10 | Forward Learning (H <sub>1</sub> ) vs. Backward Learning (H <sub>2</sub> ) (N=64)        |

| 3.11 | Forward Learning (H <sub>1</sub> ) vs. Backward Learning (H <sub>2</sub> ) (N=128) 37    |

| 4.1  | Results (H <sub>1</sub> : non-mux+FL+PI, H <sub>2</sub> : non-mux+FL+BL+PI+PO)           |

| 4.2  | Results (H <sub>2</sub> : non-multiplexed, H <sub>3</sub> : multiplexed)                 |

| 4.3  | Results (H <sub>3</sub> : multiplexed, H <sub>4</sub> :H <sub>3</sub> +multi-node impl.) |

| 4.4  | Results (No Trace, Random vs. our Algorithms)                                            |

| 5.1  | Average Toggling Percentage                                                              |

| 5.2  | Compression results (#Vectors=1000)                                                      |

| 5.3  | GZIP vs. Our approach                                                                    |

| 5.4  | Area Overhead of Compressor                                                              |

## Chapter 1

### Introduction

Pre-silicon verification and post-silicon manufacturing test play an important role in guaranteeing the integrated circuit (IC) product quality. Pre-silicon verification techniques like formal verification and simulation-based functional validation are commonly used to verify if the design implementation matches the specification. Manufacturing test is used to screen out the fabrication defects that affect the IC behavior. With the growing complexity of system-on-chip (SOC) designs, pre-silicon verification and manufacturing test are becoming more challenging than ever. Many functional bugs may remain undetected after pre-silicon verification and several defects may escape the manufacturing test. The increasing demand for shorter time-to-market has made the discovery of these undetected bugs and defects even more critical. In-system silicon debug techniques using design for debug (DFD) hardware are employed to identify the root cause of first silicon failures.

There are several working groups who are involved in the standardization of on-chip debug processes and instruments [52]. Two existing types of silicon debug techniques are: scan-based and trace buffer-based. In the scan-based approach, the design's existing test structure comprising of JTAG and scan chains are re-used. The captured data from the internal state elements corresponding to specific triggering events are off-loaded (or dumped) through the scan chains. In [6] and [7], the authors discuss the identification of failing state elements from the scan dump data using post-processing algorithms. In [5], the backward and forward logic implications of the scan-dump values are used to restore more circuit gate values. However, many complex, non repeatable bugs may only manifest themselves after long period of operations, making repeated scan dump-based debug approach costly and cumbersome for silicon debug. A trace buffer-based technique is employed to acquire continuous data wherein an embedded logic analyzer (ELA) [8] is used to sample internal signal data into on-chip trace buffers. Then, state restoration software [9] reconstructs the internal signal values from the off-loaded trace data.

The amount of data which can be acquired by the trace buffer is limited by the buffer's depth and width. The buffer's depth limits the number of samples that can be stored and the width limits the number of trace signals which can be sampled and recorded in each clock cycle [3]. Methods for ELA design improvement were proposed in [4], [8] and [10]-[12]. The area of the trace buffer memory is limited. Thus it is highly desirable to select the best trace signals which can maximize the restoration of missing signal values. In [1], [2] and [3], trace selection and state restoration algorithms were proposed which uses restorability metrics that consider both the topology and behavior of logic gates. In [25] an interconnection fabric design for tracing signals was proposed which comprised of a multiplexer network and a non-blocking concentration network. The motivation in [25] was that it is not necessary to observe uncorrelated signals concurrently. However, in many cases it is essential to observe uncorrelated signals concurrently since these uncorrelated signals do not imply each other. On the other hand, it may not be necessary to trace highly correlated signals concurrently since one signal might restore (imply) the other. Another disadvantage of [25] is the area overhead of the multiplexer tree and the crossbar switches.

Trace compression techniques can be used to increase the storage efficiency of the trace buffer. Such techniques were proposed in [13]-[15] to increase the number of trace signal samples. In [14], dictionary-based algorithms such as Lempel-Ziv (LZ77) and its variants LZ78, LZW and word-based dynamic Lempel-Ziv (WDLZW) are used. In [39], a LZ-based data compression algorithm was used for program trace compression. A drawback of using a complete dictionary is that the size of the dictionary can become very large, resulting in too much overhead for the on-chip compressor.

#### Contributions of this thesis:

Our main objectives are to maximize the restoration of missing internal signals using a minimum number of trace signals and to increase the storage efficiency of the trace buffer. The **first contribution** of this thesis is a new algorithm using a logic implication-based [16] learning approach to intelligently select the trace signals. We favor selecting

those signals which contain more implications that are not implied by other signals. We show that our trace selection method is efficient and is able to achieve better restoration than other techniques. Then, based on the values of the traced signals during silicon debug, we introduce an algorithm which uses a SAT-based multi-node implication engine to restore the values of untraced signals across multiple time-frames. Experimental results for sequential benchmark circuits showed that the proposed approach selects the trace signals effectively, giving a high restoration percentage compared with other techniques. Our **second contribution** is another algorithm which uses the correlation between the forward and backward implications of flip-flops (trace signals) across two consecutive time-frames as a parameter to intelligently select two sets of trace signals. The two sets of trace signals are then multiplexed such that the first set is traced during even timeframes and the second set is traced during odd time-frames. Our primary motivation is that the signal pairs with high implication-based correlation between them need not be traced concurrently. As a result, we can effectively trace twice as many signals with the same trace buffer width. We show that our new trace selection method is efficient and gives a better restoration percentage compared to previous techniques. We also propose a SAT-based greedy heuristic to prune the selected trace signal list, thus considering some corner cases where multi-node implications play a major role during state restoration. This further improves the restoration percentage for a few circuits.

Trace compression techniques [13-15] are used to increase the storage efficiency of the trace buffer. Golomb code [31] and FDR code [32] belong to the variable-to-variable category of lossless data compression codes. To obtain a high compression percentage with minimal hardware overhead, we propose enhancements for FDR codes that can be implemented with minimal hardware overhead. We implement source transformation functions on the captured data before encoding the data using the FDR codes. Source transformation functions convert the captured data into reduced entropy data-set and hence improve the achievable compression percentage. We show that our approach achieves better compression percentage compared to dictionary-based techniques. Moreover, the area overhead of our trace compressor is less compared to dictionary-based codes and yields up to 3X improvement in the diagnostic capability. This is our third contribution.

#### Organization of this thesis:

The rest of the thesis is organized as follows:

- Chapter 2: This chapter describes various silicon debug techniques used currently in the industry to identify the root cause of first silicon failures. It surveys the various trace selection, trace compression and state restoration schemes proposed in literature. This chapter also gives an overview of static logic implications and various compression techniques and defines parameters used to evaluate the quality of trace selection and trace compression.

- Chapter 3: This chapter discusses the proposed approach for non-multiplexed trace buffer signal selection and introduces a SAT-based heuristic for state restoration.

- Chapter 4: This chapter discusses the proposed approach for multiplexer-based trace signal selection and introduces a SAT-based greedy heuristic for pruning the selected trace signal list further. It also explains the state restoration algorithm for the new multiplexer-based scheme.

- Chapter 5: This chapter discusses the proposed source transformation functions for Frequency-Directed Run-Length (FDR) codes. It also presents hardware implementation scheme for the proposed trace data compression scheme.

- Chapter 6: This chapter concludes the thesis.

### Chapter 2

## Background

This chapter introduces the various steps involved in the development of a digital integrated circuit (IC). It also gives an overview of the various silicon debug techniques used currently in the industry and briefly introduces the trace selection, trace compression and state restoration schemes proposed in literature. Finally, it describes concepts such as static logic implications, SAT-based Boolean constraint propagation, dictionary and adaptive/dynamic code-based compression techniques, entropy, hamming distance and Burrows-Wheeler source transformation that we use in this thesis.

#### 2.1 Digital Integrated Circuit (IC) Development Process

Figure 2.1 shows the steps involved in the development of a digital integrated circuit (IC) [33]. We explain each of these steps below:

Design Specification: Design specification is defined as the formulation of a VLSI device requirement in the form of a design documentation or behavioral reference model based on a customer or project need.

Design Implementation: Design implementation is a process of transforming a higher level description of a design into a lower level description. Figure 2.2 shows the steps involved in the design implementation. Starting from a design specification, a behavioral (architecture) level description is developed in a hardware description language (HDL) or as a C program. The design is then described at the register-transfer level (RTL). The RTL is then synthesized to produce the gate-level design of the circuit. Finally, the gate-level design is transformed to a physical-level description in order to obtain the physical placement and interconnection of the transistors in the VLSI device prior to fabrication. Verification is important at each stage of the design implementation to ensure that the functionality of the final design meets the design specifications including the timing and operating frequency specifications.

Design Verification: Design verification, also known as pre-silicon verification is a predictive analysis to check the correctness of the design implementation against its

specification. When a design error is found, modifications to the design are necessary and design verification must be repeated. Two commonly used verification techniques are: 1) formal verification and 2) simulation.

*Design Fabrication:* Design fabrication is a multiple-step sequence of photographic and chemical processing steps during which electronic circuits are gradually created on a wafer made of pure semiconducting material.

Manufacturing Test: Manufacturing test is a test which is applied to each fabricated circuit to detect physical defects such as shorts and opens and timing defects. The test procedure is based on the design specification and fault models associated with the implementation technology.

Figure 2.1: Digital IC development process

Figure 2.2: Design implementation hierarchy

#### 2.2 Need for Silicon Debug

The time required for design verification in the pre-silicon stage is increasing with the growing complexity of integrated circuits. Insufficient verification may fail to detect design errors. Moreover, the accuracy of circuit models is inadequate to ensure the first silicon to be error free. Therefore, design verification has a definite impact on time-to-market and hence is economically significant, and it is important that the undetected design bugs are fixed as soon as the first silicon is available. In recent years, silicon debug has emerged as a key technique to detect and locate design errors in silicon. Even when the design is correct, defects may be introduced during the fabrication due to impurities. In other words, not all chips manufactured from the same design may be defect-free. Manufacturing test attempts to capture those defective parts. However, the defect may be located in a corner-case region for which there are few or no tests. In such cases, the chip may pass the manufacturing test and be shipped as if it was good. When put into a system, the chip may malfunction whenever the defect is exercised. In this case, silicon debug is likewise necessary to detect and locate the source of the problem.

#### 2.3 Silicon Debug

In-system silicon debug techniques are employed to identify the root cause of first silicon failures. Silicon debug can be defined as the process of finding, locating and identifying design bugs in the post-silicon phase [18]. Three techniques used for silicon debug are: 1) physical probing, 2) scan-based and 3) trace buffer-based. Silicon debug can be divided into two main steps: data acquisition and analysis. A type of physical probing technique which uses time-resolved photo emission [20] is widely used to acquire circuit data for failure analysis. However, the decreasing feature size and growing complexity of designs make this technique cumbersome for data acquisition. The debug methods based on internal scan chains have been used extensively for debugging complex digital ICs [19]. Scan-based debug concepts have emerged from the manufacturing test research. In the scan-based approach, the internal scan chains are reused wherein the captured data from the internal state elements corresponding to specific triggering events are off-loaded (or dumped) through the scan chains. In [6-7], the authors discuss post-processing algorithms

which can be used to identify the failing state elements from the scan dump data. In [5] a method was proposed which utilizes backward and forward logic implications of the scan-dump values to restore more circuit gate values. However, many complex, non repeatable bugs may only manifest themselves after a long period of operations. Moreover, to complete a scan dump while continuing the real-time execution, it is necessary to double buffer the state elements in the scan chain, thus leading to unacceptable area penalty. This makes repeated scan dump-based debug approach costly and cumbersome for silicon debug. The trace buffer-based approach is a complementary technique which can be used to acquire continuous data. This debug technique has been influenced by software debugging used in embedded systems [22]. An embedded logic analyzer (ELA) [8] is used for sampling internal signal data into on-chip trace buffers. This is followed by a post processing stage [9] wherein the sampled data is off-loaded for analysis to reconstruct internal signal values and identify functional bugs.

Figure 2.3: Trace buffer-based silicon debug architecture

Figure 2.3 shows an example of trace buffer-based debug architecture. The trace signal interface shown in the figure is used to transfer the trace signals to on-chip trace buffers and/or off-chip trace ports for diagnosis. A trace control unit controls the start and stop of

the tracing, in which the control mechanism can be configured through JTAG interface. The trace buffer-based debug methods can be broadly classified as: special-purpose or generic. The special-purpose method [23-24] is applicable to embedded processors. The generic method is applicable to any type of custom SOCs [11, 17]. Another classification is based on centralized tracing or distributed sampling. In centralized tracing, one trace buffer is used per SOC (with different interconnect topologies between the embedded cores and the trace buffer) [17, 23, 24]. In distributed sampling the trace buffers are allocated to individual cores [11]. Regardless of the above classification, the primary benefit of the trace buffer-based method is that it provides real-time visibility to the circuit under debug (CUD) and enables in-field at-speed debug. The amount of data which can be acquired by the trace buffer is limited by two parameters: the buffer's depth and width. The former limits the number of samples that can be stored and the latter limits the number of trace signals which can be sampled and recorded in each clock cycle [3]. The space of the available trace buffer memory is normally very limited and hence only a small number of internal signals can be observed together real-time.

The selection of the critical trace signals which can maximize the restoration of the missing signal values is highly desirable. In [1-3], algorithms were proposed for trace signal selection and state restoration using restorability metrics that consider both the topology and behavior of logic gates. Ko et al. [3] used the state restoration concept to select the best signals that can eventually restore maximum number of other signals and hence improve the observability of the circuit under debug (CUD). Liu et al. [1] proposed refinements to take care of a few limitations in [3]. The restorability formulation in [1] and [3] is probabilistic in nature. The restorability calculation is computationally intensive since the restorability for all flip-flops is recomputed for every iteration.

The interconnection fabric used to interconnect trace signals to the trace buffers and/or trace ports involves non-trivial area overhead. The existing solutions [26-28] use pipelined multiplexer (MUX) trees for the interconnection fabric design. However, these ad-hoc techniques limits the visibility to the circuit under debug (CUD) since any signal going through the same multiplexer cannot be observed concurrently. In [25], an interconnection fabric design was proposed to take care of the above problem. It consisted of two main parts: 1) a MUX network that connects those mutually-exclusive

tapped signals, which can be designated by designers and/or extracted automatically based on structural analysis; 2) a non-blocking concentration network that is able to transfer any m out of n inputs ( $m \le n$ ) to the trace buffers/ports. The motivation in [25] was that it is not necessary to observe uncorrelated signals concurrently. However, in many cases it is essential to observe uncorrelated signals concurrently since these uncorrelated signals do not imply each other. On the other hand, it may not be necessary to trace highly correlated signals concurrently since one signal might restore (imply) the other. Another disadvantage of [25] is the area overhead of the multiplexer tree and the crossbar switches.

Trace compression [13-15] is another sought-after method to increase the number of trace signal samples, thus increasing the storage efficiency of the trace buffer. In [14] dictionary-based algorithms (LZ77 and its variants) were used. A dedicated fast parallel search engine called content addressable memory (CAM) was used in [14] in order to perform fast search in hardware between the incoming symbol and the dictionary entries. The main limitation of dictionary-based method proposed in [6] was the large area overhead due to different content-addressable memory (CAM) sizes. A LZ-based data compression algorithm was used in [39] for program trace compression, however the area overhead was large.

In the subsequent sections, we define and explain a few concepts that we use in this thesis.

#### 2.4 Static Logic Implications

Let us consider a circuit with n gates. Logic implications determine the effect of assigning logic values (0 or 1) to one or more gates in the circuit. The implications are stored using a directed implication graph G(V, E) where  $V(vertices) \varepsilon$  the set of 2n nodes corresponding to both value assignments (0 and 1) and  $E(edges) \varepsilon$  single-node implications. For sequential circuits, each edge is annotated with an integer weight w that indicates the number of time frames that this implication spans. For example, consider an AND gate and its implication graph, shown in Figure 2.4. The AND gate has three signals, a, b, and c and the associated implication graph has six nodes. An edge in the

implication graph indicates the implication relationship and the annotated weight indicates the number of time-frames spanned by the implication. From Figure 2.4, clearly c=1 has two implications: b=1 and a=1 and the edge weight is 0.

Static logic implications can be sub-divided into direct, indirect and extended backward implications [16, 33]. Indirect and extended backward implications use logic simulation as well as the contra-positive and transitive laws extensively. These learned implications are thus non-trivial.

Figure 2.4: Implication graph example

We define a few terms and concepts for single-node implications which we use for the discussion:

- a) [N,v,t]: Assign logic value v to gate N in time frame t.

- b)  $[N,v,t_1] \rightarrow [M,w,t_2]$ : Assigning logic value v to gate N in time frame  $t_1$  would imply a logic value w to gate M in time frame  $t_2$ .

- c) DI[N,v,t]: Set of direct implications resulting from assigning node N in time frame t to value v. For t=0, DI[N,v,t] is simply represented as DI[N,v] or DI[N=v].

- d) IND[N,v,t]: Set of indirect implications resulting from assigning node N in time frame t to value v. For t=0, IND[N,v,t] is simply represented as IND[N,v] or IND[N=v].

- e) EB[N,v,t]: Set of extended backward implications resulting from assigning node N in time frame t to value v. For t=0, EB[N,v,t] is simply represented as EB[N,v] or EB[N=v].

- f) Impl[N,v,t]: Set of single-node implications resulting from assigning node N in time frame t to value v. For t=0, Impl[N,v,t] is simply represented as Impl[N,v] or Impl[N=v]. Note that  $Impl[N,v,t] = DI[N,v,t] \cup IND[N,v,t] \cup EB[N,v,t]$ .

- g) Transitive law: If  $[M,w] \rightarrow [N,v,t_1]$  AND  $[N,v] \rightarrow [L,y,t_2]$ , then  $[M,w] \rightarrow [L,y,t_1+t_2]$ . In set notation, if  $[N,v,t_1] \in Impl[M,w]$  and  $[L,y,t_2] \in Impl[N,v]$ , then  $[L,y,t_1+t_2] \in Impl[M,w]$ .

- h) Contrapositive law: If  $[M,w] \rightarrow [N,v,t]$ , then  $[N,v'] \rightarrow [M,w',-t]$ . In set notation, if  $[N,v,t] \in Impl[M,w]$ , then  $[M,w',-t] \in Impl[N,v']$ .

- i) Conflicting assignments: If  $[M,w] \rightarrow [N,v,t]$  AND  $[M,w] \rightarrow [N,v',t]$ , then [M,w] is an impossible setting. This means that M is a constant node holding the value w' permanently.

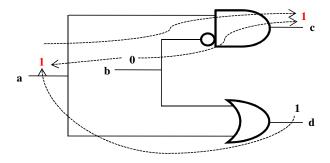

Figure 2.5: Sequential circuit fragment

We illustrate the direct, indirect and extended backward implications using the following example. Consider gate f=1 in the sequential circuit fragment shown in Figure 2.5. Let  $Impl[f=1]=\Phi$  initially:

1. *Direct Implications:* In Figure 2.5, g and k are directly connected to gate f. Clearly, f=1 would directly imply g=k=1. Moreover, f=1 has two implications: d=1 and e=1. Let DI[f=1] denote the set containing direct implications for f=1. Thus,  $DI[f=1]=\{(f,1,0), (g,1,0), (k,1,0), (d,1,0), (e,1,0)\}$ . Similarly, the direct

implications for g=1,  $DI[g=1]=\{(g,1,0),(j,1,0),(f,1,0)\}$ . These implications are stored in the form of a graph, where each node represents a gate (with a logic value). A directed edge between two nodes represents an implication, and a weight along an edge represents the relative time frame associated with the implication. The graph shown in Figure 2.6 represents a portion of direct implications for f=1 in this example. The complete set of implications resulting from setting f=1 can be obtained by applying *transitive law* and traversing the graph rooted at node f=1. Computing the set of all nodes reachable from this root node (f=1) (transitive closure on f=1) would return the set DI[f=1]. Thus, the complete set of direct implications using the implication graph shown in the figure for f=1 is  $DI[f=1]=\{(f,1,0),(d,1,0),(e,1,0),(g,1,0),(k,1,0),(j,1,0),(c,1,-1)\}$ . After learning direct implications,  $Impl[f=1]=Impl[f=1] \cup DI[f=1]$ .

- 2. *Indirect implications:* Note that neither *j*=1 nor *k*=1 implies a logic value on gate *x* individually. However, if they are taken collectively, they imply *x*=1. Thus, indirectly, *f*=1 would imply *x*=1. This is an indirect implication of *f*=1, and it can be computed by performing a logic simulation on the current set of implications of the root node on the circuit. In this example, by inserting the implications of *f*=1 into the circuit, followed by a run of logic simulation, *x*=1 would be obtained as a result. Thus, *IND*[*f*=1]={(*x*,1,0)} and *Impl*[*f*=1]=*Impl*[*f*=1]∪*IND*[*f*=1]. This new implication is then added as an additional outgoing dashed edge from *f*=1 in the implication graph as shown in Figure 2.7. Another nontrivial implication that can be inferred from each indirect implication is based on the contrapositive law. Since [*f*,1]→[*x*,1,0], by contrapositive law, [*x*,0]→[*f*,0,0].

- 3. Extended backward (EB) implications: The unjustified implied nodes in the implication list can be used to learn more implications, known as extended backward implications for any single node. Using the same circuit shown in Figure 1 again, in the implication list of f=1, d=1 is an unjustified gate because none of d's inputs has been implied to a logic value of 1. Thus, d is a candidate for the application of EB implications. To obtain EB implications on d, a transitive closure is first performed for each of its unspecified inputs. In this case, Impl[a=1] and Impl[b=1] are first computed. The implications of f=1 are logic

simulated *together* with each of d's unspecified input's implication sets in turn, creating a set of newly found logic assignments for each input of the chosen unjustified gate. For this example, when the implications of (a=1) and (f=1) are simulated, the new assignments  $(set_a)$  found include (w,0,0) and (z,0,0). Similarly, for the combined implication set of (b=1) and (f=1), the new assignments  $(set_b)$  found include (y,0,0) and (z,0,0). All logic assignments that are not already in Impl[f=1] which are common to  $set_a$  and  $set_b$  are the EB implications. These new implications are added as new edges to the original node f=1. Thus,  $EB[f=1]=\{(z,0,0)\}$  and  $Impl[f=1]=Impl[f=1]\cup EB[f=1]$ . In this running example, because (z,0,0) is common in  $set_a$  and  $set_b$ , it is a new implication. The corresponding new implication graph is illustrated in Figure 2.8, where the new implication is shown as a dotted edge.

Figure 2.6: Direct implications for f=1

Figure 2.7: Adding indirect implications for f=1

Figure 2.8: Adding extended backward implications for f=1

#### 2.5 SAT-based Boolean Constraint Propagation (BCP)

The implication graph stores only the single node implications, i.e., one node implying another node. For determining multi-node implications, i.e., a set of nodes together implying a single node, we use a SAT-based approach. We illustrate this method using an example. Every Boolean formula can be expressed in *conjunctive normal form (CNF)*. For the circuit shown in Figure 2.9 the CNF formula can be expressed as:

$$(\neg a \lor b \lor c) \land (a \lor \neg c) \land (\neg b \lor \neg c) \land (\neg a \lor d) \land (\neg b \lor d) \land (a \lor b \lor \neg d)$$

Suppose we wish to determine the multi-node implications of the signal assignments b=0 and d=1. We use *Boolean Constraint Propagation (BCP)* to quickly identify the multi-node implications. First, set b=0 and d=1 in the above CNF formula. It gets simplified to:  $(\neg a \lor c) \land (a \lor \neg c) \land (1) \land (1) \land (a)$

The sixth clause has become a *unit clause* (a clause with one unassigned/free literal). Therefore a=1 is an implication. Next, set a=1 in the simplified CNF formula. It gets simplified to:

$$(c) \wedge (1) \wedge (1) \wedge (1) \wedge (1) \wedge (1)$$

The first clause is now a unit clause, hence c=1 is an implication. Since all the other clauses are *satisfied* (clause evaluates to 1), we stop and conclude that  $\{a=1, c=1\}$  are the multi-node implications of b=0 and d=1. In other words, if S is the set containing the signal assignments b=0 and d=1, i.e.  $S=\{b=0, d=1\}$ , then BCP(S) =  $\{a=1, c=1\}$  Note that

if any clause evaluates to 0 (i.e. *unsatisfied*) we conclude that a conflict has occurred and hence the given set of signal assignments S do not have any multi-node implications, i.e.,  $BCP(S) = \Phi$ . For the same circuit,  $\{d=1\}$  is the single-node implication of the signal assignment  $S = \{a=1\}$ .

Figure 2.9: Boolean Constraint Propagation

We define a few terms for single-node [16] and multi-node implications which we use in the following:

- j) Impl[N, v, t]: Set of single-node implications resulting from assigning node N in time frame t to value v.

- k) Impl[N,t]: Set of single-node implications resulting from assigning node N in time frame t to value v and v respectively (i.e., Impl[N,v,t]  $\cup$  Impl[N,v,t]).

- l) BCP(S): Set of multi-node implications resulting from assigning nodes  $N_1, N_2, ..., N_n$  in time frame t to values  $v_1, v_2, ..., v_n$  respectively, where  $S = \{N_b, v_b, t\}_{i=1,2,..n}$

- m)  $Impl_f[N, t]$ : Set of single-node forward implications in time frame t resulting from assigning node N in time frame t to value v and v respectively.

- n) Impl<sub>b</sub>[N, t]: Set of single-node backward implications in time frame t-l resulting from assigning node N in time frame t to value v and v' respectively.

#### 2.6 Restoration Ratio and Restoration Percentage

In [1] and [3], a parameter called *restoration ratio* (*RR*) is used as an evaluation metric to measure the quality of the trace signals selected. It is calculated as:

$$RR = \frac{N_{traced(FFs)} + N_{restored(FFs)}}{N_{traced(FFs)}}$$

(2.1)

Where  $N_{traced(FFs)}$  and  $N_{restored(FFs)}$  are the number of traced states and the number of restored states respectively across all the time-frames under consideration.

We define a new parameter called *restoration percentage* to measure the quality of trace signal selection more coherently. Total restoration percentage for all signals (including flip-flops) is calculated as:

$$TR_{all} = \frac{N_{traced(FFs)} + N_{restored(all)}}{N_{total(all)}} \times 100$$

(2.2)

Where  $N_{restored(all)}$  is the number of restored signals in the circuit including PIs.  $N_{total(all)}$  is the total number of signals in the circuit.

The restoration percentage for only flip-flops is calculated as:

$$TR_{FFs} = \frac{N_{traced(FFs)} + N_{restored(FFs)}}{N_{total(FFs)}} \times 100$$

(2.3)

Where  $N_{total(FFs)}$  is the total number of flip-flops in the circuit.

$TR_{all}$  and  $TR_{FFs}$  are the total restoration percentages calculated across all the time-frames. Equations (2.2) and (2.3) can also be used to determine the individual restoration percentages for each time-frame.

#### 2.7 Data Compression Codes

Lossless data compression codes are classified into four categories depending on whether the symbols have a fixed size or a variable size, and whether the code-words have a fixed size or a variable size. Dictionary-based codes belong to fixed-to-fixed codes. A drawback of using a complete dictionary is that the size of the dictionary can become very large, resulting in too much overhead for the on-chip compressor. Huffman code [33, 41] and run-length code [33, 40] are fixed-to-variable and variable-to-fixed codes, respectively. Adaptive/dynamic statistical coding algorithms, such as Huffman coding [33, 41] can provide a greater compression ratio but implementing them in hardware can incur exorbitant real estate cost. Golomb code [31] and FDR code [32] belong to the variable-to-variable category. Both have evolved from the run-length code and are able to achieve greater compression. Since it was shown in [37] that FDR code is superior to Golomb code, we use FDR code in our work.

#### 2.8 Frequency Directed Run-length (FDR) Code

Since our technique enhances FDR codes, we will briefly describe them. A detailed description is available elsewhere [32]. In FDR coding scheme, runs of zero's are encoded as shown in Figure 2.10. Here, labels  $A_i$  (i=1,2, ...) is used to represent a *Group* and the corresponding group prefix is shown in the column labeled *Group prefix*. The total number of code-words in a group  $A_i$  is  $2^i$ . To encode a given run of zeros, a codeword is constructed by concatenating the *group prefix* and a *tail*. For example, the sequence 000001 (Run-length=5) is encoded as 1011 (Group prefix=10, tail=11). We will now illustrate a more complex example.

| Group | Run-   | Group  | Tail | Codeword |

|-------|--------|--------|------|----------|

|       | length | prefix |      |          |

|       | 0      |        | 0    | 00       |

| $A_1$ | 1      | 0      | 1    | 01       |

|       | 2      |        | 00   | 1000     |

|       | 3      |        | 01   | 1001     |

| $A_2$ | 4      | 10     | 10   | 1010     |

|       | 5      |        | 11   | 1011     |

|       | 6      |        | 000  | 110000   |

|       | 7      |        | 001  | 110001   |

|       | 8      |        | 010  | 110010   |

|       | 9      |        | 011  | 110011   |

| $A_3$ | 10     | 110    | 100  | 110100   |

|       | 11     |        | 101  | 110101   |

|       | 12     |        | 110  | 110110   |

|       | 13     |        | 111  | 110111   |

| •••   | •••    | •••    |      | •••      |

Figure 2.10: An FDR coding example

**Example 1**. Let the un-encoded sequence be  $T = 0001 \ 000001 \ 1 \ 00001 \ 000001 \ 00000001$  001 00000001 001. The run-lengths of zeroes in this un-encoded sequence are 3, 5, 0, 4, 4, 6, 2, 7, and 2. From Fig. 1 we obtain the encoded sequence,  $T_E = 1001 \ 1011 \ 001010 \ 1010 \ 110000 \ 1000 \ 110001 \ 1000$ .

#### 2.9 Source Transformation

Source transformation refers to the idea of transforming un-encoded data set T into a new data set, T, which is more amenable for compression. Burrows-Wheeler transform [38] (BWT) is a widely used transformation that, when used on top of run length encoding, can give very impressive compression ratio. Bzip2 employs BWT transforms.

#### 2.10 Diagnosis and Compression Quality Metrics

We use the following parameters to evaluate the quality of trace compression obtained using our proposed approach. Diagnostic Resolution and Compression Percentage: For trace compression, we consider the trace data set as an  $n \times N$  matrix, where n is the total number of time-frames and N is the total number of trace flip-flops. Each row represents the current state of the trace flip-flops. T refers to the un-encoded sequence obtained from the  $n \times N$  matrix by concatenating the n rows.  $T_E$  is used to refer to the encoded trace data sequence. Diagnostic Resolution  $(D_R)$  is defined by:

$$D_R = \frac{S_U}{S_E} = \frac{n \times N}{S_E} \tag{2.4}$$

where  $S_U$  is the size of T (i.e., the number of bits in the un-encoded sequence T) and  $S_E$  is the size of  $T_E$  (i.e., the number of bits in the encoded sequence  $T_E$ )

In other words, we can trace N signals using an  $N/D_R$  wide trace buffer. Thus, the diagnostic capability is improved by  $D_R$  times.

Compression percentage (*C*) is defined by:

$$C = (1 - \frac{1}{D_R}) \times 100 \tag{2.5}$$

For the un-encoded sequence of Example 1,  $S_U = 42$  and  $S_E = 38$ . Hence,  $D_R = S_U/S_E = 42/38 = 1.105$ , and  $C = (1-1/D_R) \times 100 = (1-1/1.105) \times 100 = 9.5\%$ .

#### 2.11 Entropy

In information theory, entropy of a stream of data quantifies the overall information stored in that data. The entropy [36], *E*, of trace buffer data is defined as:

$$E = -\sum_{i=0}^{n} p_{i} \log_{2} (p_{i})$$

(2.6)

where  $p_i$  is the probability of occurrence of a symbol  $X_i$ . Entropy can be used to compute the theoretical limits for achieving maximum compression using any encoding technique. For a variable-to-variable encoding, the theoretical maximum compression is:

$$C_{max} = (S_l - E) / (S_l) \tag{2.7}$$

where E is the entropy and  $S_l$  is the average symbol length defined as:

$$S_l = \sum_{i=0}^{n} p_i * |X_i|$$

(2.8)

where  $p_i$  is the probability of occurrence of the symbol  $X_i$  and  $|X_i|$  is the length of  $X_i$ . Clearly from Equation (2.7), the maximum compression is inversely proportional to the entropy. The computation of entropy and theoretical maximum compression is illustrated in the example below.

**Example 2.** Let us consider the un-encoded sequence T of Example 1. Let  $t_i$  be the total number of times run-length i occurs. For our example,  $t_0=1$ ,  $t_1=0$ ,  $t_2=2$ ,  $t_3=1$ ,  $t_4=2$ ,  $t_5=1$ ,  $t_6=1$ ,  $t_7=1$ ,  $t_8=0$ . Let R be the total number of run-lengths. Thus,  $R=\sum_{i=0}^8 t_i=9$ . The probability of occurrence of run-length i is  $p_i=t_i/R$ . Thus,  $p_0=1/9=0.11$ ,  $p_1=0$ ,  $p_2=2/9=0.22$ ,  $p_3=1/9=0.11$ ,  $p_4=2/9=0.22$ ,  $p_5=1/9=0.11$ ,  $p_6=1/9=0.11$ ,  $p_7=1/9=0.11$ ,  $p_8=0.11$ From Equation (2.6), the entropy is  $E = \sum_{i=0}^{8} p_i \log_2(p_i) = -(0.11 \log_2(0.11) + 0.22 \log_2(0.11))$  $(0.22) + 0.11log_2 (0.11) + 0.22log_2 (0.22) + 0.11log_2 (0.11) + 0.$ (0.11)) = 2.79. The length of run-length i is  $|X_i|=i+1$  if the run-length sequence end with a 1, otherwise  $|X_i|=i$ . For example, 001 has a run-length of 2, but the size is 3 including the 1 at the end. However, if we have an un-encoded sequence which ends with a zero, say 001 0001 00, the size of the last run-length will be 2 since it does not have a terminating 1. For our example, from Equation (2.8) the average symbol length  $S_l = \sum_{i=0}^{8} p_i * |Xi| =$  $(p_0*|X_0| + p_2*|X_2| + p_3*|X_3| + p_4*|X_4| + p_5*|X_5| + p_6*|X_6| + p_7*|X_7|) = (0.11*1 + 0.22*3 + 0.22*3)$ 0.11\*4 + 0.22\*5 + 0.11\*6 + 0.11\*7 + 0.11\*8 = 4.62. Thus, from Equation (2.7) the theoretical maximum compression,  $C_{max} = (S_l-E)/(S_l) = (4.62-2.79)/(4.62) = 0.396$ , i.e., 39.6%.

### 2.12 Average Hamming Distance and Toggling Percentage

The Hamming distance, H, between two strings of equal length is the number of positions at which the corresponding symbols are different. For the  $n \times N$  matrix, let the Hamming distance between two successive rows k and k+1 be  $H_k$ . Note that  $0 \le H_k \le N$ , where N is the total number of trace flip-flops. This means that  $H_k$  trace flip-flops out of the total N trace flip-flops toggle between the successive rows k and k+1.

The average Hamming distance for the trace data set represented by the  $n \times N$  matrix is given by:

$$H_{avg} = \frac{\sum_{i=1}^{n-1} D_i}{n-1} \tag{2.9}$$

The average toggling percentage for the trace data set represented by the  $n \times N$  matrix is given by:

$$TP_{avg} = \frac{H_{avg}}{N} \times 100 \tag{2.10}$$

### Chapter 3

### Non-multiplexed Trace Selection and State

### Restoration

This chapter is organized as follows. Section 3.1 formulates the problem. Section 3.2 discusses the proposed approach for non-multiplexed trace signal selection. Section 3.3 introduces the algorithm used for state restoration. Section 3.4 reports experimental results, and Section 3.5 summarizes the observation.

#### 3.1 Problem Formulation

Let G represent the set of all gates in the circuit and S represent the set of trace signals to be selected. We define the problem statement as follows: Find the smallest subset of signals  $S \subseteq G$  such that  $\forall legal \ valuations \ r$  of S, the values of the signals in G-S can be restored.

In other words, our main objective is to maximize the restoration of missing internal signals using a minimum number of trace signals. In general, if we know all the primary input (PI) and current internal state element (flip-flop) values, it is possible to determine all the internal signal values through simple logic simulation. However, since the trace buffer capacity is limited in large designs, it is not possible to trace all the flip-flops. Hence, our objective is to select the best subset of flip-flops  $f_{i,i=1,2,...,N}$  as trace signals such that most of the missing internal signal values can be restored. Throughout the paper we will assume that all PI values are known.

#### 3.2 New Trace Signal Selection

In our trace signal selection algorithm, we use the number of single node implications (for both 0 and 1 assignment) per flip-flop  $N_{f_{i,i=1,2,...N}}$  as our trace signal selection restorability metric. First, we determine direct, indirect and extended backward implications [16] across a combinational time-frame and store them in an implication

graph. Next, we order the flip-flops  $f_{i, where i \in I, 2, ..., N}$  in the descending order of the total number of implications for both 0 and 1 assignment and term it as set  $O_i$ . Let us assume that the  $PI_{i, i=1,2...,p}$  (p primary inputs) values are known. We define *checked implications*  $CI(f_k)$  of a flip-flop  $f_k$  in the ordered set  $O_i$  as those implications which are also implied by the primary inputs in the set  $U_{i \in I, 2, ..., p}$   $Impl[PI_{i, 0}]$  and other flip-flops in the set  $U_{i \in I, 2, ..., k-1}$   $Impl[f_{i, 0}]$ . In other words,

$$CI(f_k) = Impl[f_k, 0] \cap \{(U_{i \in I, 2, \dots, k-1} Impl[f_i, 0]) \cup (U_{i \in I, 2, \dots, p} Impl[PI_i, 0])\}$$

(3.1)

We define the *unchecked implications*  $UI(f_k)$  of a flip-flop  $f_k$  in the set  $O_i$  as those implications which are not implied by those in the set  $(U_{i \in I, 2, ..., k-1}Impl[f_i, 0])U(U_{i \in I, 2, ..., p}Impl[PI_i, 0])$ . In other words,

$$UI(f_k) = Impl[f_k, 0] - CI(f_k)$$

(3.2)

To prune the ordering further, we remove the *checked implications* corresponding to each flip-flop from the sorted list and order them again in the descending order of number of *unchecked implications* and term it as set  $O_f$ . Based on a given trace buffer width n < N, where N is the total number of flip-flops, we select the first n flip-flops from the set  $O_f$  as our trace signals. The basic idea is that the number of internal signals which can be restored using a flip-flop (trace signal) is directly proportional to the number of *unchecked implications* of that flip-flop. Hence, by ordering the flip-flops on the basis of number of *unchecked implications*, we aim to select the flip-flops which yield the best restorability individually. We will illustrate the trace signal selection method using the following example. Let us consider a circuit with one primary input  $PI_I$ , three flip-flops  $f_I$ ,  $f_2$ ,  $f_3$  and six gates  $g_1$ ,  $g_2$ ,  $g_3$ ,  $g_4$ ,  $g_5$ ,  $g_6$ . Suppose we obtain the following information from the implication graph:

```

Impl[PI_{I},0,0]: {PI_{I}=0, g_{6}=1}

Impl[PI_{I},1,0]: {PI_{I}=1, g_{6}=0}

Impl[f_{I},0,0]: {f_{I}=0, g_{I}=1, g_{2}=1, g_{3}=0, g_{5}=1}

Impl[f_{I},1,0]: {f_{I}=1, g_{I}=1, g_{2}=0, g_{3}=0, g_{4}=1}

Impl[f_{2},0,0]: {f_{2}=0, g_{I}=1, g_{2}=1, g_{3}=1}

Impl[f_{2},1,0]: {f_{2}=1, g_{I}=1, g_{2}=0, g_{3}=1, g_{4}=1}

Impl[f_{3},0,0]: {f_{3}=0, g_{I}=0, g_{3}=1}

```

Impl[

$$f_3$$

,1,0]: { $f_3$ =1,  $g_1$ =1,  $g_2$ =0,  $g_4$ =0}

Thus, we get:

$$Impl[PI_1,0]=Impl[PI_1,0,0]\cup Impl[PI_1,1,0]: \{PI_1=0, PI_1=1, g_6=0, g_6=1\}$$

$$Impl[f_1,0]=Impl[f_1,0,0] \cup Impl[f_1,1,0]: \{f_1=1,f_1=0,g_1=1,g_2=1,g_2=0,g_3=0,g_4=1,g_5=1\}$$

$$Impl[f_2,0]=Impl[f_2,0,0] \cup Impl[f_2,1,0]: \{f_2=1,f_2=0,g_1=1,g_2=1,g_2=0,g_3=1,g_4=1\}$$

$$Impl[f_3,0]=Impl[f_3,0,0] \cup Impl[f_3,1,0]: \{f_3=1,f_3=0,g_1=1,g_1=0,g_2=0,g_3=1,g_4=0\}$$

$$N_{f1} = |\text{Impl}[f_1, 0]| = 8, N_{f2} = |\text{Impl}[f_2, 0]| = 7, N_{f3} = |\text{Impl}[f_3, 0]| = 7$$

On ordering the flip-flops in the descending order of number of implications for both 0 and 1 assignment, we get  $O_i = \{f_I, f_2, f_3\}$ . Since  $f_I$  has the most number of implications, we will start with this flip-flop. Then we remove the *checked implications* from  $f_I$ ,  $f_2$  and  $f_3$ . Using Equations (3.1) and (3.2), we get:

$$CI(f_1)$$

= Impl[ $f_1$ ,0] $\cap$  Impl[ $PI_1$ ,0]= $\boldsymbol{\Phi}$

$$UI(f_1)=Impl[f_1,0]-CI(f_1):\{f_1=1,f_1=0,g_1=1,g_2=1,g_2=0,g_3=0,g_4=1,g_5=1\}$$

$$CI(f_2)=Impl[f_2,0]\cap (Impl[f_1,0]\cup Impl[PI_1,0]):\{g_1=1, g_2=1, g_2=0, g_4=1\}$$

$$UI(f_2)=Impl[f_2,0]-CI(f_2):\{f_2=1, f_2=0, g_3=1\}$$

$$CI(f_3)=Impl[f_3,0]\cap (Impl[f_2,0]\cup Impl[f_1,0]\cup Impl[PI_1,0]):\{g_1=1, g_2=0, g_3=1\}$$

$$UI(f_3)=Impl[f_3,0]-CI(f_3):\{f_3=1, f_3=0, g_1=0, g_4=0\}$$

Next, we set the implications to be the unchecked ones:

$$Impl[f_1,0]=UI(f_1): \{f_1=1, f_1=0, g_1=1, g_2=1, g_2=0, g_3=0, g_4=1, g_5=1\}$$

Impl[

$$f_2$$

,0]= $UI(f_2)$ : { $f_2$ =1,  $f_2$ =0,  $g_3$ =1}

Impl

$$[f_3,0]=UI(f_3)$$

:  $\{f_3=1, f_3=0, g_1=0, g_4=0\}$

$$N_{f1}=|\text{Impl}[f_1,0]|=8, N_{f2}=|\text{Impl}[f_2,0]|=3, N_{f3}=|\text{Impl}[f_3,0]|=4$$

On ordering the flip-flops in the descending order of number of *unchecked implications* for both 0 and 1 assignment, we get  $O_f = \{f_1, f_3, f_2\}$ . If we assume that the trace buffer width is 2, we will select  $f_1$ ,  $f_3$  as our trace signals.

#### Algorithm 3.1: Unchecked implication-based trace signal selection

- 1. Compute direct, indirect and extended backward implications and store them in an implication graph.

- 2.  $O_i = Set \ of flip-flops \ f_{i,where \ i \in I,2,...,N}$  in the descending order of number of implications  $|Impl[f_i,0]|_{where \ i \in I,2,...,N}$

```

3. reference_list = U<sub>i∈1,2,...,p</sub> Impl[PI<sub>i</sub>,0];

4. for each (flip-flop f<sub>i where i∈1,2,...,N</sub>)

for each (implication m ∈ Impl[f<sub>i</sub>,0] )

if (m∩reference_list ≠ Φ) then

Impl[f<sub>i</sub>,0] = Impl[f<sub>i</sub>,0]-m;

else

reference_list = reference_list ∪ m;

```

- 5.  $O_f$  = Set of flip-flops  $f_{i, where i \in 1, 2, ..., N}$  in the descending order of number of unchecked implications  $|Impl[f_i O]|_{where i \in 1, 2, ..., N}$

- 6. If trace buffer width=n, select first n flip-flops from the set  $O_f$  as trace signals.

We measure the quality of trace signals selected by Algorithm 3.1 using the two parameters defined in Section 2.6, *Restoration Ratio* and *Restoration Percentage*. In the next section, we present a novel state restoration algorithm which is used to obtain the above evaluation metrics.

#### 3.3 State Restoration from Traced Signals

Our main objective is to maximize the number of internal signals which can be restored using the selected trace signal data. Given the traced signal values, we use a SAT-based multi-node implication based approach discussed in Section 2.5 to determine the restored signals across several time frames. For each time frame ke0,1,2...T we provide the SAT-based multi-node implication engine a signal assignment set  $S_k=S_{PI} \cup S_t$ , where  $S_{PI}$  is the set containing PI values and  $S_t$  is the set containing the current state values of the selected traced flip-flops in time frame k. We enlarge the set  $S_k$  for each time frame by including current state values of non-traced flops determined using *forward* and *backward learning*, which are defined as follows:

Forward Learning: For a signal assignment set  $S_{k-1}$  in time frame k-1, if {signal g=v} $\epsilon$ BCP( $S_{k-1}$ ) and g is the fan-in signal of non-traced flip-flop f, then for time frame k,  $S_k=S_k \cup \{f=v\}$ .

Backward Learning: For a set of trace flip-flops  $\{f_1, f_2,....,f_n\}$  and the corresponding fanin signals  $\{g_1, g_2,...,g_n\}$ , if in time frame k the current state values of the traced flip-flops are  $v_1, v_2,...,v_n$ , then in time frame k-1,  $S_{k-1}=S_{k-1}\cup\{g_1=v_1, g_2=v_2,..., g_n=v_n\}$ . If  $\{signal\ g=v\}\in BCP(S_{k-1})$  and g is the fan-in signal of non-traced flip-flop f, then for time frame k,  $S_k=S_k\cup\{f=v\}$ .

For time frame k, suppose  $S_f$  is the set of non-trace flip-flop assignments determined by forward learning and  $S_b$  is the set of non-trace flip-flop assignments determined by backward learning. Then, for time frame k,  $S_k = S_{PI} \cup S_t \cup S_f \cup S_b$

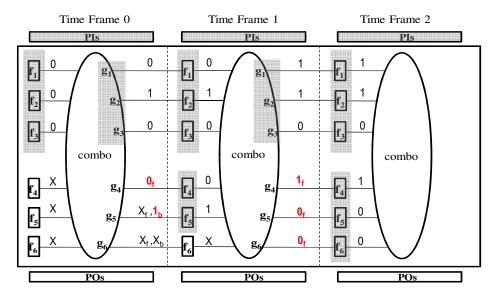

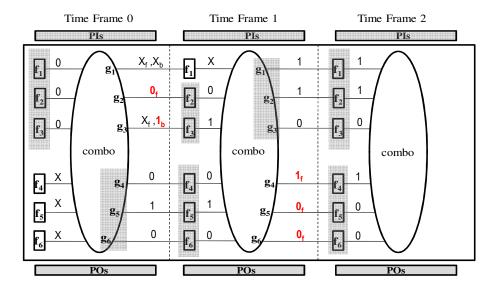

We use Figure 3.1 to illustrate the concept of forward and backward learning. Figure 3.1 shows a 3-frame expansion of a sequential circuit. Let us assume that the trace flip-flops are  $\{f_1, f_2, f_3\}$ , the non-trace flip-flops are  $\{f_4, f_5, f_6\}$  and the PIs are  $\{p_1, p_2, ..., p_n\}$  assigned to values  $v_1$ ,  $v_2$ ,...,  $v_n$  respectively. The gates  $g_1$ ,  $g_2$ ,  $g_3$ ,  $g_4$ ,  $g_5$ ,  $g_6$  are the input signals of  $f_1$ ,  $f_2$ ,  $f_3$ ,  $f_4$ ,  $f_5$ ,  $f_6$  respectively. For time-frame 0, the signal assignment set  $S_0 = S_{PI} \cup S_t$ , where  $S_t = \{f_1 = 0, f_2 = 0, f_3 = 0\}$ . Suppose  $\{g_4 = 0\}\epsilon$  BCP $(S_0)$ . Since  $g_4$  is the input signal of non-trace flip-flop  $f_4$ , the next state of  $f_4$  is learned to be 0 by forward learning, i.e.  $S_f = \{f_4 = 0\}$ . Therefore, in time frame 1,  $S_1 = S_1 \cup S_f = S \cup \{f_4 = 0\}$ . Note that the subscript f for the values 0<sub>f</sub>, 1<sub>f</sub> and X<sub>f</sub> indicate the values learned by forward learning. If the current state values of traced flip-flops  $\{f_1, f_2, f_3\}$  in time-frame 1 are  $\{0,1,0\}$ , then in time frame 0,  $S_0 = S_{P_1} \cup S_t \cup \{g_1 = 0, g_2 = 1, g_3 = 0\}$  where  $S_t = \{f_1 = 0, f_2 = 0, f_3 = 0\}$ . Suppose  $\{g_5 = 1\} \in BCP(S_0)$ . Since  $g_5$  is the input signal of non-trace flip-flop  $f_5$ , the next state of  $f_5$  is learned to be 1 by backward learning, i.e.  $S_b = \{f_5 = 1\}$ . Therefore, in time frame 1,  $S_1 = S_1 \cup S_b = S_1 \cup \{f_5 = 1\}$ . Note that the subscript b for the values  $0_b$ ,  $1_b$  and  $X_b$  indicate the values learned by backward learning. Hence, considering both forward and backward learning for time frame 1, we get  $S_1 = S_1 \cup S_2 \cup S_b = S_1 \cup \{f_4=0\} \cup \{f_5=1\}$ . Similarly, for time frame 2,  $S_2=$  $S_2 \cup S_t \cup S_b = S_2 \cup \{f_4 = 1, f_5 = 0, f_6 = 0\} \cup \{\boldsymbol{\Phi}\}.$

Finally, we determine the multi-node implications  $BCP(S_k)$  for these assignments in time frame k using our SAT-based implication engine and count the number of restored internal signals. *Restoration Ratio* and *Restoration Percentage* are then calculated using equations described in Section 2.6. We also vary the trace buffer width and observe the effect on the restoration percentage across a set of 100 vectors (time-frames) for each

circuit. The experimental results are given in the next section. Algorithm 3.2 gives an overview of our state restoration approach.

#### **Algorithm 3.2:** State restoration using multi-node implications

- 1.  $trace\_signal\_list = flip-flops f_{i, where i \in 1, 2, ..., n}$

- 2. **for each** (vector  $V_{i, where i \in 0.1, 2, ..., T}$ )

Perform logic simulation using  $V_i$ ;

Signal assignment set  $S_i = S_{PI} \cup S_t \cup S_f \cup S_b$ ;

Perform SAT-based multi-node implications  $BCP(S_i)$

$N_{restored(all)}$  = number of signals including the PIs implied to either 0 or 1.

$N_{restored(FFs)}$  = number of non-trace flip-flops implied to either 0 or 1.

Use equations provided in Section II to calculate restoration ratio and restoration percentage.

Figure 3.1: State Restoration-Forward and Backward Learning

#### 3.4 Experimental Results

The above algorithms were written in C++ and experiments were conducted for ISCAS'89 sequential benchmark circuits on a Linux workstation with 2GB RAM. The results are reported in Tables 3.1-3.5. During state restoration, we do not assume any knowledge of an initial state other than the traced signals. We consider five different

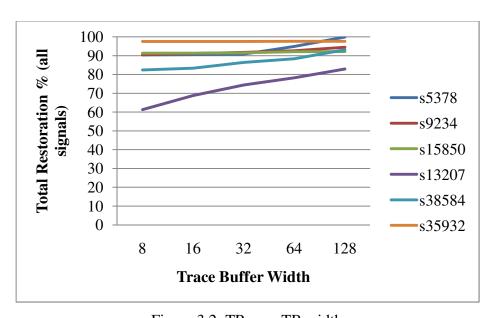

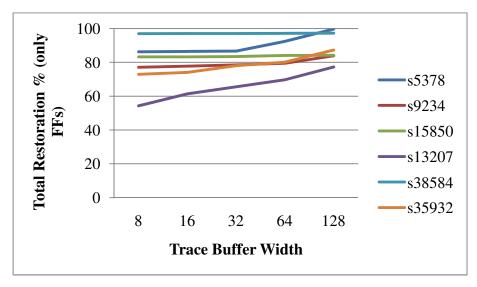

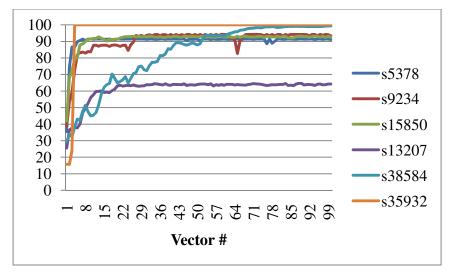

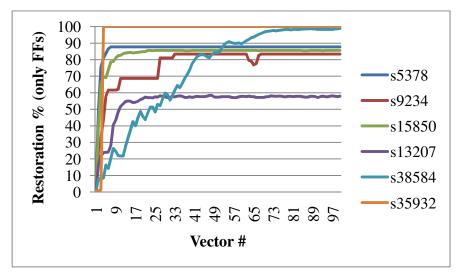

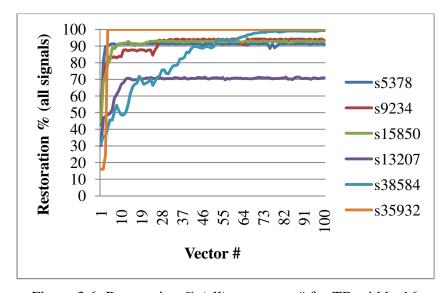

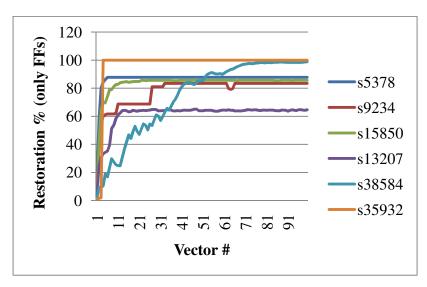

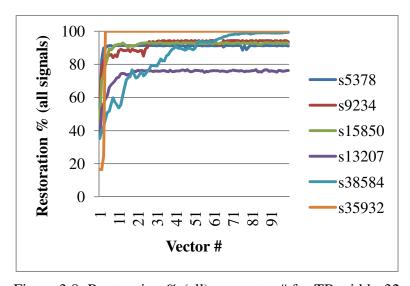

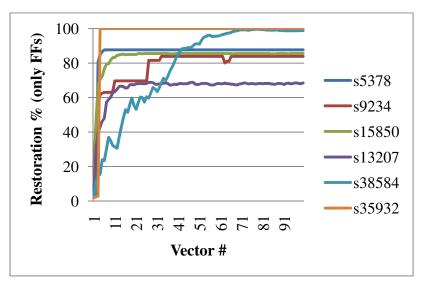

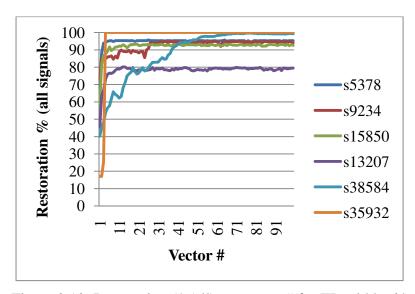

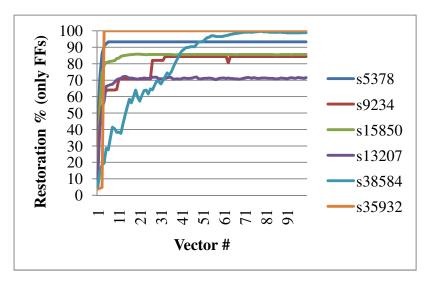

trace buffer widths: 8, 16, 32, 64 and 128. The trace buffer depth is assumed to be 100 in contrast to [1] in which the trace buffer depth is assumed to be 4k. Note that less restoration is possible in the beginning and more restoration toward the end of the vector sequence since more values can be learned later from the earlier vectors. Therefore, each random pattern used for our experiments has 100 vectors each for a more competitive comparison. We compare our results with [1] using the parameter RR (Restoration Ratio). For a sanity check, we also perform an experiment in which we perform a poor trace signal selection by selecting flip-flops with the least number of unchecked implications. We compare the total restoration percentage  $TR_{all}(P)$  obtained by the poor trace signal selection with total restoration percentage  $TR_{all}(A)$  obtained by the proposed trace signal selection algorithm for the first 10 vectors for different trace buffer widths reported in Table 3.6. Tables 3.1-3.5 give the results for trace buffer widths of 8, 16, 32, 64 and 128 using only forward learning and assuming that the primary input values are known. For each circuit, the first two columns give the total number of flip-flops in the circuit and number of vectors considered respectively, followed by restoration ratio (RR) obtained in [1], the trace signal execution time in [1], the restoration ratio (RR) obtained by our method, total restoration percentage (only flip-flops) across 100 vectors ( $TR_{FFs}$ ), total restoration percentage (all gates) across 100 vectors  $(TR_{all})$ , the restoration percentage (only flip-flops) obtained in the final vector ( $FR_{FFs}$ ), the restoration percentage (all gates) obtained in the final vector  $(FR_{all})$ , and the trace selection execution time. Compared to [1] our approach has a better restoration ratio (RR). We also observe that our approach is considerably faster for all circuits than [1]. For example, consider s15850 of Table 3.1 with only 8 traced signals; we achieved a high RR of 55.6 and execution time of only 17.9 seconds as compared to a RR of 19.93 and execution time of 298.9 seconds achieved by [1]. Note that the trace selection execution time in our method is independent of the trace buffer width and depth, but only on the circuit size. In s15850, we were able to restore 92.6% of all signals with only 8 trace signals. We were able to achieve high restoration percentage  $(FR_{all})$  for all circuits, sometimes with only 8 or 16 trace signals. We can observe that with an increase in the trace buffer width (toward 128) the restoration percentage also tends to increase, as expected. For s35932 and s38584, the restoration percentage approaches 100 percent as we approach the final vector. Figure 3.2

and Figure 3.3 illustrate this graphically. For a trace buffer width of 32, this trend is illustrated graphically in Figure 3.8 and Figure 3.9.

Table 3.6 compares our method with the poor trace signal selection. Results for the first 10 vectors, which are the hardest to restore (e.g., initial state of non-trace FFs is unknown), are reported. Our restoration percentage  $TR_{all}(A)$  is superior than the  $TR_{all}(P)$  obtained using the poor selection of trace signals for all trace buffer widths. Among the circuits, s35932 is a special case: similar results were observed for both cases, since the number of unchecked implications per flip-flop is uniformly distributed in this circuit.

Finally, Tables 3.7-3.11 compare the results obtained using forward learning only (H<sub>1</sub>) with the results obtained using both forward learning and backward learning (H<sub>2</sub>) for trace buffer widths of 8, 16, 32, 64 and 128. Clearly, backward learning further improves the restoration percentage. For example, consider s38584 in Table 3.9 for a trace buffer width of 32, H<sub>2</sub> achieved a high restoration percentage (TR<sub>all</sub>) of 92.9% as compared to a restoration percentage (TR<sub>all</sub>) of only 86.4% achieved using H<sub>1</sub>.

Table 3.1: Experimental Results (Trace Buffer Width=8)

| Name   | #FFs | #Vec. | RR <sub>old</sub> | Time <sub>old</sub> (s) | RR <sub>new</sub> | TR <sub>FFs</sub> | TR <sub>all</sub> | FR <sub>FFs</sub> | FR <sub>all</sub> | Time <sub>new</sub> (s) |

|--------|------|-------|-------------------|-------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------------|

| s5378  | 179  | 100   | 14.68             | 14.3                    | 19.3              | 86.3              | 90.4              | 87.7              | 91.1              | 1.3                     |

| s9234  | 211  | 100   | 4.767             | 26.3                    | 20.3              | 77.1              | 90.5              | 83.4              | 93.4              | 9.6                     |

| s15850 | 534  | 100   | 19.93             | 298.9                   | 55.6              | 83.2              | 91.3              | 85.6              | 92.6              | 17.9                    |

| s13207 | 638  | 100   | -                 | -                       | 43.3              | 54.3              | 61.3              | 57.9              | 64.2              | 16.8                    |

| s38584 | 1426 | 100   | 19.24             | 388.6                   | 130.1             | 72.9              | 82.4              | 98.8              | 99.3              | 726                     |

| s35932 | 1728 | 100   | 64.0              | 1407.6                  | 209.6             | 97.0              | 97.6              | 100               | 100               | 193                     |

Table 3.2: Experimental Results (Trace Buffer Width=16)

| Name   | #FFs | #Vec. | $RR_{old}$ | Time <sub>old</sub> (s) | RR <sub>new</sub> | $TR_{FFs}$ | $TR_{all}$ | $FR_{FFs}$ | FR <sub>all</sub> | Time <sub>new</sub> (sec) |

|--------|------|-------|------------|-------------------------|-------------------|------------|------------|------------|-------------------|---------------------------|

| s5378  | 179  | 100   | 8.996      | 35.9                    | 9.7               | 86.5       | 90.6       | 87.7       | 91.1              | 1.4                       |

| s9234  | 211  | 100   | 7.182      | 75.2                    | 10.3              | 77.8       | 91.2       | 83.4       | 93.4              | 9.5                       |

| s15850 | 534  | 100   | 24.22      | 764.4                   | 27.8              | 83.3       | 91.33      | 85.6       | 92.6              | 18.0                      |

| s13207 | 638  | 100   | -          | -                       | 24.5              | 61.4       | 68.8       | 64.6       | 70.9              | 16.9                      |

| s38584 | 1426 | 100   | 13.96      | 802.9                   | 66.02             | 74.1       | 83.3       | 98.8       | 99.3              | 726                       |

| s35932 | 1728 | 100   | 38.13      | 5251.1                  | 104.8             | 97.04      | 97.56      | 100        | 100               | 195                       |

Table 3.3: Experimental Results (Trace Buffer Width=32)

| Name   | #FFs | #Vec. | RR <sub>old</sub> | Time <sub>old</sub> (s) | RR <sub>new</sub> | $TR_{FFs}$ | TR <sub>all</sub> | $FR_{FFs}$ | FR <sub>all</sub> | Time <sub>new</sub> (s) |

|--------|------|-------|-------------------|-------------------------|-------------------|------------|-------------------|------------|-------------------|-------------------------|

| s5378  | 179  | 100   | 4.726             | 74.9                    | 4.84              | 86.7       | 90.8              | 87.7       | 91.1              | 1.3                     |

| s9234  | 211  | 100   | 4.672             | 148.2                   | 5.2               | 78.5       | 91.8              | 83.9       | 93.6              | 9.5                     |

| s15850 | 534  | 100   | 13.3              | 1654.6                  | 13.9              | 83.5       | 91.5              | 85.6       | 92.6              | 17.9                    |

| s13207 | 638  | 100   | -                 | -                       | 13.1              | 65.6       | 74.4              | 68.5       | 76.3              | 16.9                    |

| s38584 | 1426 | 100   | 8.679             | 2826.0                  | 34.8              | 78.1       | 86.4              | 98.8       | 99.3              | 726                     |

| s35932 | 1728 | 100   | 21.06             | 10496.2                 | 52.4              | 97.07      | 97.57             | 100        | 100               | 194                     |

Table 3.4: Experimental Results (Trace Buffer Width=64)

| Name   | #FFs | #Vec. | RR <sub>old</sub> | Time <sub>old</sub> (s) | RR <sub>new</sub> | TR <sub>FFs</sub> | TR <sub>all</sub> | FR <sub>FFs</sub> | FR <sub>all</sub> | Time <sub>new</sub> (s) |

|--------|------|-------|-------------------|-------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------------|

| s5378  | 179  | 100   | i                 | -                       | 2.6               | 92.4              | 94.9              | 93.3              | 95.3              | 1.5                     |

| s9234  | 211  | 100   | -                 | -                       | 2.6               | 79.5              | 92.6              | 84.4              | 94.0              | 9.7                     |

| s15850 | 534  | 100   | -                 | -                       | 7.0               | 84.1              | 92.1              | 85.6              | 92.6              | 18.1                    |

| s13207 | 638  | 100   | -                 | -                       | 6.9               | 69.7              | 78.2              | 71.5              | 79.5              | 16.9                    |

| s38584 | 1426 | 100   | -                 | -                       | 17.8              | 80.1              | 88.4              | 98.8              | 99.3              | 723                     |

| s35932 | 1728 | 100   | -                 | -                       | 26.2              | 97.13             | 97.59             | 100               | 100               | 194                     |

Table 3.5: Experimental Results (Trace Buffer Width=128)

| Name   | #FFs | #Vec. | $RR_{old}$ | Time <sub>old</sub> (s) | RR <sub>new</sub> | TR <sub>FFs</sub> | TR <sub>all</sub> | FR <sub>FFs</sub> | FR <sub>all</sub> | Time <sub>new</sub> (s) |

|--------|------|-------|------------|-------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------------|

| s5378  | 179  | 100   | -          | -                       | 1.4               | 99.7              | 99.9              | 100               | 100               | 1.4                     |

| s9234  | 211  | 100   | -          | -                       | 1.4               | 83.9              | 94.5              | 85.8              | 95.2              | 9.9                     |

| s15850 | 534  | 100   | -          | -                       | 3.5               | 84.2              | 92.2              | 85.6              | 92.6              | 19.8                    |

| s13207 | 638  | 100   | -          | -                       | 3.9               | 77.3              | 82.9              | 78.8              | 83.7              | 18.8                    |

| s38584 | 1426 | 100   | -          | -                       | 9.7               | 87.3              | 93.1              | 99.9              | 99.8              | 785                     |

| s35932 | 1728 | 100   | -          | -                       | 13.13             | 97.24             | 97.64             | 100               | 100               | 215                     |

Table 3.6: Experimental Results-Poor (P) vs. our Algo (A) for the first 10 vectors

| Name   | TB W                  | idth=8        | TB Wi                 | dth=16        | TB Wi                 | dth=32        | TB Wi                 | dth=64        | TB Wio                | dth=128       |

|--------|-----------------------|---------------|-----------------------|---------------|-----------------------|---------------|-----------------------|---------------|-----------------------|---------------|

|        | TR <sub>all</sub> (P) | $TR_{all}(A)$ |

| s5378  | 73.7                  | 82.8          | 74.2                  | 84.9          | 81.5                  | 86.3          | 84.1                  | 91.5          | 95.5                  | 99.2          |