## High-Frequency Oriented Design of Gallium-Nitride (GaN)

## **Based High Power Density Converters**

## Bingyao Sun

Dissertation submitted to the faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

Doctor of Philosophy In Electrical Engineering

Rolando Burgos Dushan Boroyevich Jih-Sheng Lai Vassilis Kekatos Guo-Quan Lu

2018. 08. 10 Blacksburg, Virginia

Keywords: Gallium-Nitride (GaN), gate driver, inverter, LLC resonant converter, magnetic integration, electromagnetic interference (EMI)

© 2018, Bingyao Sun

## High-Frequency Oriented Design of Gallium-Nitride (GaN)

## **Based High Power Density Converters**

## Bingyao Sun

## **Abstract**

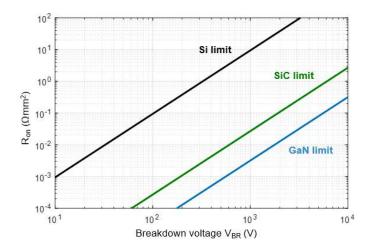

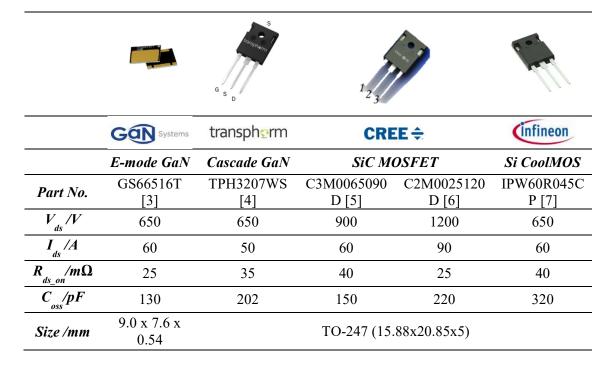

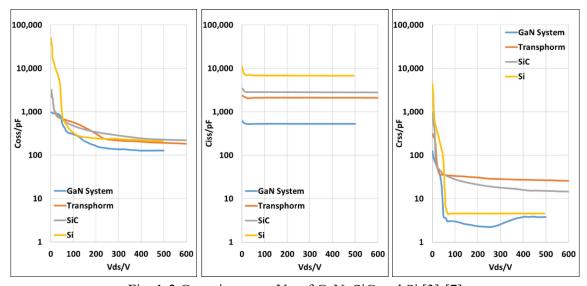

The wide-bandgap (WBG) devices, like gallium nitride (GaN) and silicon carbide (SiC) devices have proven to be a driving force of the development of the power conversion technology. Thanks to their distinct advantages over silicon (Si) devices including the faster switching speed and lower switching losses, WBG-based power converter can adopt a higher switching frequency and pursue higher power density and higher efficiency.

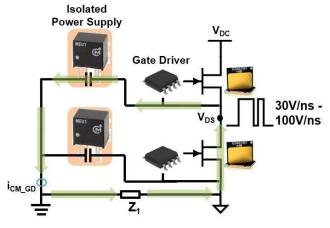

As a trade-off of the advantages, there also exist the high-frequency-oriented challenges in the adoption of the GaN HEMT under research, including narrow safe gate operating area, increased switching overshoot, increased electromagnetic interference (EMI) in the gate loop and the power stages, the lack of the modules of packages for high current application, high gate oscillation under parallel operation. The dissertation is developed to addressed the all the challenges above to fully explore the potential of the GaN HEMTs.

Due to the increased EMI emission in the gate loop, a small isolated capacitor in the gate driver power supply is needed to build a high-impedance barrier in the loop to protect the gate driver from interference. A 2 W dual-output gate driver power supply with ultra-low isolation capacitor for 650 V GaN-based half bridge is presented, featuring a PCB-embedded transformer substrate, achieving 85% efficiency, 1.6 pF isolation capacitor with 72 W/ir<sup>3</sup>

power density. The effectiveness of the EMI reduction using the proposed power supply is demonstrated.

The design consideration to build a compact 650 V GaN switching cell is presented then to address the challenges in the PCB layout and the thermal management. With the switching cell, a compact 1 kW 400 Vdc three-phase inverter is built and can operate with 500 kHz switching frequency. With the inverter, the high switching frequency effects on the inverter efficiency, volume, EMI emission and filter design are assessed to demonstrate the tradeoff of the adoption of high switching frequency in the motor drive application. In order to reduce the inverter CM EMI emission above 10 MHz, an active gate driver for 650 V GaN HEMT is proposed to control the dv/dt during turn-on and turn-off independently. With the control strategy, the penalty from the switching loss can be reduced.

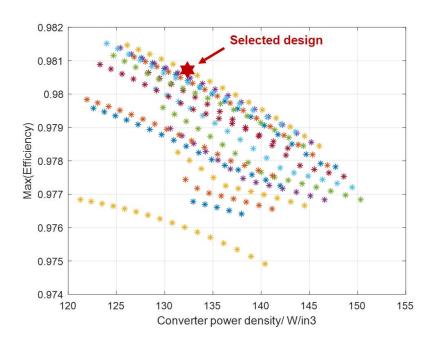

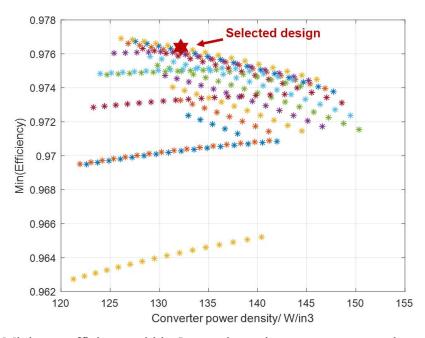

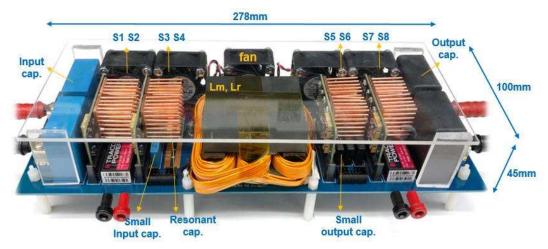

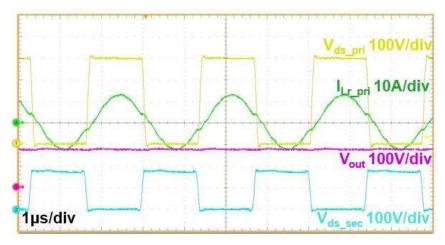

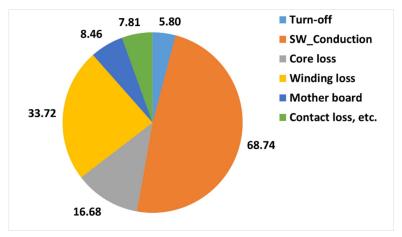

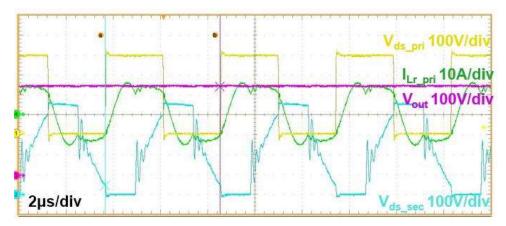

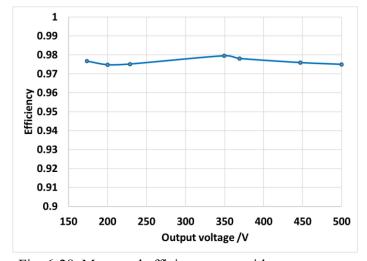

To build a high current power converter, paralleling devices is a normal approach. The dissertation comes up with the switching cell design using paralleled two and four 650 V GaN HEMTs with minimized and symmetric gate and power loop. The commutation between the paralleled HEMTs is analyzed, based on which the effects from the passive components on the gate oscillation are quantified. With the switching cell using paralleled GaN HEMTs, a 10 kW LLC resonant converter with the integrated litz-wire transformer is designed, achieving 97.9 % efficiency and 131 W/in³ power density. The design consideration to build the novel litz-wire transformer operated at 400 kHz switching frequency is also presented.

In all, this work focuses on providing effective solutions or guidelines to adopt the 650 V GaN HEMT in the high frequency, high power density, high efficiency power conversion and demonstrates the advance of the GaN HEMTs in the hard-switched and soft-switched power converters.

## High-Frequency Oriented Design of Gallium-Nitride (GaN)

## **Based High Power Density Converters**

## Bingyao Sun

### **General Audience Abstract**

Silicon (Si) -based power semiconductor has developed several decades and achieved numerous outstanding performances, contributing a fast development of the power electronics. While the theatrical limit of the silicon semiconductor is almost reached limiting the progress speed to purse the high-efficiency, high-density high-reliability power conversion, the new material, including gallium-nitride (GaN) and silicon-carbide (SiC), based semiconductor, becomes the driven force to retain the development.

Compared with Si-based device, GaN and SiC device own a faster switching speed and a lower on-resistance, enabling the adoption of high switching frequency and the possibility to increase the efficiency, power density and dynamic response. The GaN-based semiconductor is explored to be an even promising game changer than SiC device thanks to a higher theoretical ceiling. However, to adopt GaN-based semiconductors and fully utilize its benefits with high switching frequency, there are numerous high-frequency-oriented challenges, including high frequency oscillation at device termination, increased electromagnetic interference (EMI), the lack of the modules of packages for high current application, high frequency oscillation under parallel operation.

The dissertation is developed to address the key high-frequency-oriented challenges to adopt GaN-based semiconductors in the power conversion and come up with the novel design strategy and analysis for high-switching-frequency power conversion using GaN devices.

To the reduce the increased EMI emission in the gate loop, a novel PCB-embedded transformer structure is proposed to maintain a low isolation capacitor in the gate driver power supply for the GaN phase leg. With the proposed technique, the dual-output gate driver power supply can achieve high efficiency (85%), ultra-low isolation capacitor (1.6 pF) with high power density (72 W/in<sup>3</sup>).

To reduce the high frequency oscillation at the GaN device termination, the strategy to layout GaN devices and its gate driver is proposed with corresponding thermal management A compact structure for three-phase inverter is then presented, operating with a very high switching frequency (500 kHz). Within the inverter, the high switching frequency effects on the inverter performances are assessed to demonstrate the tradeoff and bottle neck to adopt high switching frequency in the motor drive application. In order to reduce the inverter EMI emission at high frequency (>10 MHz), an active gate driver for GaN device is proposed for the active dv/dt control strategy.

To build a high current power converter, the strategy to parallel GaN devices is proposed in the dissertation with the analysis on the commutation between the paralleled GaN devices. A high-frequency high-current litz-wire transformer structure for LLC resonant converter is presented with modeling and optimization. With the technique, a 10 kW LLC resonant converter achieves high efficiency (97.9 %) and high power density (131 W/in<sup>3</sup>)

## Acknowledgement

I would like to express my sincere gratitude to my advisor, Dr. Burgos for his guidance, patience and encouragement. He constantly shared his profound knowledge and rich experience with me during my five-year Ph.D. life at Virginia Tech. He is also very supportive, considerate and responsible person, who provides valuable suggestions and insights to me. I will be always grateful for his generous advices for my research and career.

I would like to acknowledge my committee members: Dr. Dushan Boroyevich, Dr. Jih-Sheng Lai, Dr. Vassilis Kekatos and Dr. Guo-Quan Lu for their support, comments and suggestions. I would also like to thank the CPES administrative staff, Ms. Marianne Hawthorne, Ms. Teresa Shaw, Ms. Trish Rose, Ms. Linda Long, Mr. David Gilham, and Ms. Lauren Shutt for their support and help during my time at CPES. I would like to thank Dr. Hement Bishnoi, Dr. Xuning Zhang, Dr. Fang Luo, Dr. Ting Ge, Dr. Zichen Miao, Mr. Bin Li, Mr. Shishuo Zhao, Mr. Chen Li, Dr. Kai Li, Mr. Tao Liu, Mr. Ruiyang Qin, Dr. Igor Cvetkovic, Dr. Qiong Wang, Dr. Chi Li, Dr. Jun Wang, Dr. Chao Fei, Dr. Chen Fang, Dr. Zhengyang Liu, Dr. Xiucheng Huang, Dr. Dongbin Hou, Dr. Yuchen Yang, Ms. Christina DiMarino, Dr. Niloofar Rashidimehrabadi, Ms. Ye Tang, Mr. Jianghui Yu, Ms. Le Wang, Mr. Keyao Sun, Mr. Slavko Mocevic, Ms. Nidhi Haryani, Dr. Ali Marzoughi, Mr. Sung Jae Ohn, Ms. Yingying Gui, Mr. Mohamed Ahmed, Mr. Junjie Feng, Mr. Zhengrong Huang, Ms. Virginia Li, Dr. Ming Lu, Dr. Yi Yan, Mr. Joseph Kozak, Mr. Shan Gao, for their help, companions and friendship. This journey becomes much more wonderful with these friends around and I will cherish our happy memories always.

With much love and gratitude, I want to thank my parents for their endless love and support. I would not have been able to have these achievements without their unfailing support and continuous encouragement. I wish I can be their proud as always.

I would also like to thank my boyfriend, Dr. Qingrui Liu, for his love and understanding. Throughout the years, he is always by my side, encourages and supports me. With his companion, every day is a good day and I feel grateful to have him by my side.

Special thanks to the SAFRAN and ABB cooperate research for the funding of my research.

## **Table of Contents**

| Chapter 1. Introduction                                                           | 1 |

|-----------------------------------------------------------------------------------|---|

| 1.1 Advantages of Gallium-Nitride high-electron-mobility transistors              | 1 |

| 1.2 Challenges Using GaN HEMTs                                                    | 5 |

| 1.2.1 Challenges using the e-mode GaN HEMTs in question                           | 5 |

| 1.2.2 Gate drive power supply design for GaN1                                     | 0 |

| 1.2.3 Motor drive design using GaN (hard-switched topology)                       | 2 |

| 1.2.4 Active gate driver design for GaN-based inverter                            | 4 |

| 1.2.5 LLC resonant converter design using GaN HEMTs (Soft-switching topology)1    | 5 |

| 1.3 Contributions and accomplishments                                             | 8 |

| 1.4 Proposed Dissertation Outline                                                 | 1 |

| Chapter 2. Ultra-low Input-Output Capacitance PCB-Embedded Dual-Output Gate-Drive |   |

| Power Supply for 650 V GaN-Based Half-Bridges2                                    | 4 |

| 2.1 Circuit Design and Operation Mode Selection                                   | 5 |

| 2.1.1 Topology selection                                                          | 5 |

| 2.1.2 Operating modes of the active-clamp flyback                                 | 7 |

| 2.1.3 Circuit design                                                              | 1 |

| 2.2 PCB-Embedded Transformer Design and Optimization                              | 3 |

| 2.2.1 PCB-embedded transformer structure                                          | 3 |

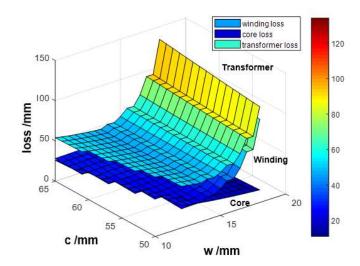

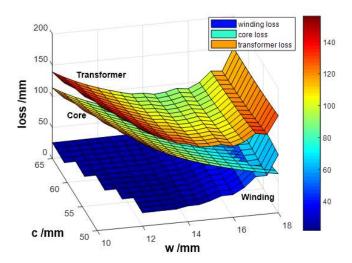

| 2.2.2 Transformer model and optimization                                      | 38        |

|-------------------------------------------------------------------------------|-----------|

| 2.2.3 Optimization results                                                    | 40        |

| 2.3 Transformer Fabrication and Converter Assembly                            | 43        |

| 2.3.1 Embedding of transformer core                                           | 43        |

| 2.3.2 Winding fabrication                                                     | 44        |

| 2.3.3 Converter assembly                                                      | 45        |

| 2.4 Evaluation and characteristics of the Gate Drive Power Supply             | 47        |

| 2.4.1 Electrical characteristics                                              | 47        |

| 2.4.2 EMI measurement                                                         | 51        |

| 2.4.3 Thermal reliability                                                     | 53        |

| 2.5 Summary and Conclusions                                                   | 55        |

| Chapter 3. High Switching Frequency 3-Phase GaN-Based Inverter Design         | 56        |

| 3.1 Compact GaN-based inverter design                                         | 57        |

| 3.2.1 Modular design of a GaN HEMT phase leg                                  | 57        |

| 3.2.2 Switching loss characterization                                         | 59        |

| 3.2.3 Thermal management                                                      | 60        |

| 3.2.4 Compact inverter structure                                              | 62        |

| 3.2.5 Experimental verification of the design consideration                   | 62        |

| 3.2 Assessment of switching frequency effect on the efficiency and power cell | volume of |

| GaN-based inverter                                                            | 64        |

| 3.3 Assessment of switching frequency effect on the EMI emission and filter | design of  |

|-----------------------------------------------------------------------------|------------|

| GaN-based inverter                                                          | 67         |

| 3.3.1 Switching frequency effect on EMI emissions                           | 67         |

| 3.3.2 EMI filter design using the EMI unterminated behavioral model         | 68         |

| 3.3.3 Switching frequency effect on EMI filter volume                       | 71         |

| 3.4 Summary and conclusions                                                 | 74         |

| Chapter 4. Active Gate Driver Design of 650V GaN HEMT                       | 75         |

| 4.1 Proposed dv/dt Control Technique                                        | 76         |

| 4.1.1 Idea to control dv/dt                                                 | 76         |

| 4.1.2 Proposed turn-off control circuit                                     | 81         |

| 4.1.3 Proposed turn-on control circuit                                      | 82         |

| 4.1.4 Simulation verification                                               | 84         |

| 4.2 Circuit design                                                          | 87         |

| 4.2.1 BJT selection and layout consideration                                | 87         |

| 4.2.2 Control source circuit design                                         | 88         |

| 4.3 Experimental Verification of Active Gate Driver                         | 90         |

| 4.3.1 DPT with C <sub>M</sub> without BJT                                   | 90         |

| 4.3.2 DPT with different dv/dt at turn-on with active dv/dt control         | 93         |

| 4.3.3 DPT with different dv/dt at turn-off with active gate control         | 95         |

| 4.3.4 Comparison on DPT between with the proposed method and with diff      | erent gate |

| resistance                                                                  | 96         |

| 4.4 Summary and Conclusions9                                                                           | <b>)</b> 9 |

|--------------------------------------------------------------------------------------------------------|------------|

| Chapter 5. Design and Analysis of 650 V 12.5 m $\Omega$ / 6.25 m $\Omega$ Half Bridge Using Paralleled | 1          |

| GaN HEMTs10                                                                                            | )2         |

| 5.1 Proposed design for paralleling two and four GaN HEMTs10                                           | )3         |

| 5.1.1 Power loop design10                                                                              | )4         |

| 5.1.2 Gate loop design                                                                                 | )5         |

| 5.1.3 Thermal management                                                                               | )9         |

| 5.2 Evaluation of the designed switching cells                                                         | 13         |

| 5.2.1 Dynamic characteristics                                                                          | ١3         |

| 5.2.2 Thermal resistance evaluation                                                                    | 20         |

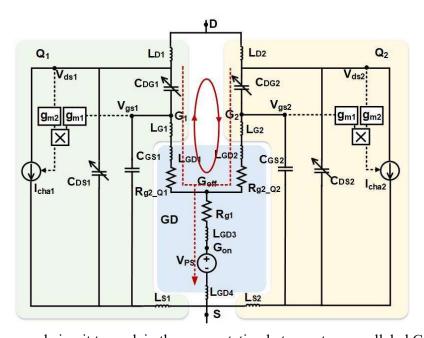

| 5.3 Analysis on the commutation during turn-on transient with paralleled GaN HEMTs 12                  | 22         |

| 5.3.1 Proposed simplified equivalent circuit                                                           | 23         |

| 5.3.2 Assessment of the effects from the passive components on the gate oscillation12                  | 26         |

| 5.4 Summary and conclusion                                                                             | 29         |

| Chapter 6. 10 kW DC-DC Converter Using Paralleled GaN                                                  | 30         |

| 6.1 Transformer design                                                                                 | 32         |

| 6.2 Transformer model and optimization                                                                 | 34         |

| 6.2.1 Inductance and core loss model                                                                   | 34         |

| 6.2.2 Litz wire AC winding loss model                                                                  | 37         |

| 6.2.4 Optimization14                                                                                   | <b>1</b> 1 |

| 6.3 Experiment Results14                                                                               | 16         |

| 6.3.1 Converter design using the switching cell of the paralleled GaN | 146 |

|-----------------------------------------------------------------------|-----|

| 6.3.2 Efficiency measurements                                         | 147 |

| 6.4 Summary and conclusions                                           | 150 |

| Chapter 7. Conclusions                                                | 151 |

| Reference                                                             | 154 |

# **List of Figures**

| Fig. 1-1 Theoretical on-resistance vs blocking voltage capability for Si, SiC and GaN [1]2     |

|------------------------------------------------------------------------------------------------|

| Fig. 1-2 Capacitance vs V <sub>ds</sub> of GaN, SiC and Si [3]-[7]                             |

| Fig. 1-3 EMI emission propagation path in the gate driver loops6                               |

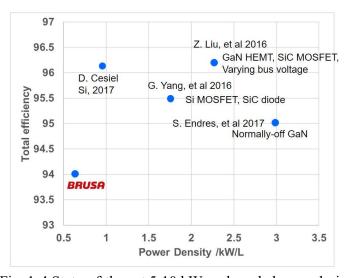

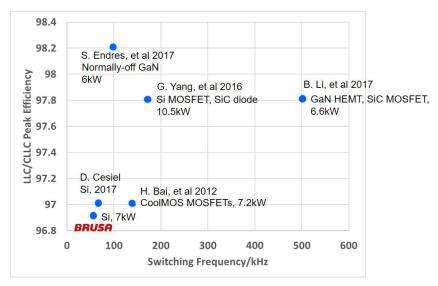

| Fig. 1-4 State-of-the-art 5-10 kW on-board charger design                                      |

| Fig. 1-5 State-of-the-art DC/DC stage performance for on-board charger                         |

| Fig. 2-1 Active-clamp flyback topology                                                         |

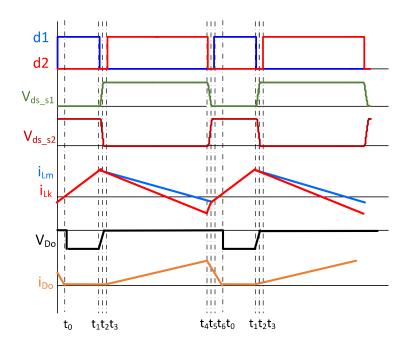

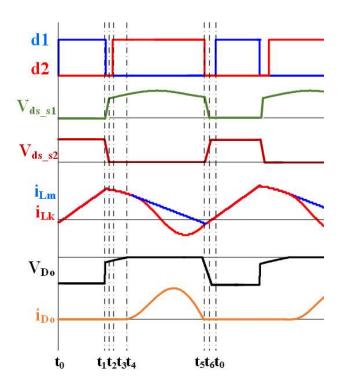

| Fig. 2-2 Operation of continuous current mode of the active clamp flyback28                    |

| Fig. 2-3 Operation of critical current mode of the active clamp flyback29                      |

| Fig. 2-4 Resonant operation mode in active-clamp flyback                                       |

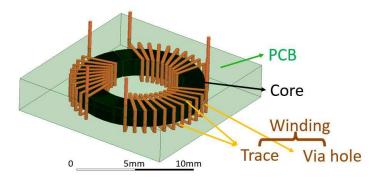

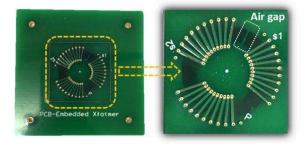

| Fig. 2-5 PCB-embedded transformer structure illustration                                       |

| Fig. 2-6 Top and front view of the PCB-embedded transformer35                                  |

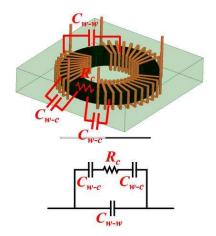

| Fig. 2-7 Isolation capacitance illustration in the structure                                   |

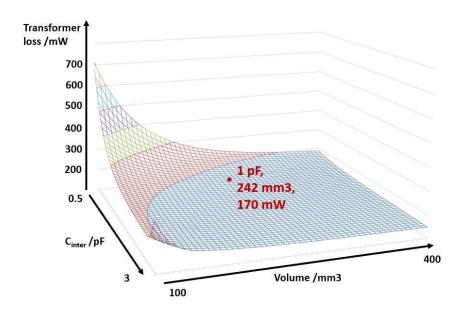

| Fig. 2-8 Pareto surface within loss, isolation capacitance, and volume for the transformer     |

| design41                                                                                       |

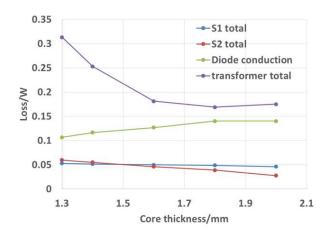

| Fig. 2-9 Loss analysis for different <i>h</i> , with 1 MHz switching frequency42               |

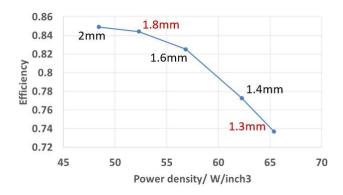

| Fig. 2-10 Efficiency estimation vs power density for different h, with 1 MHz switching         |

| frequency                                                                                      |

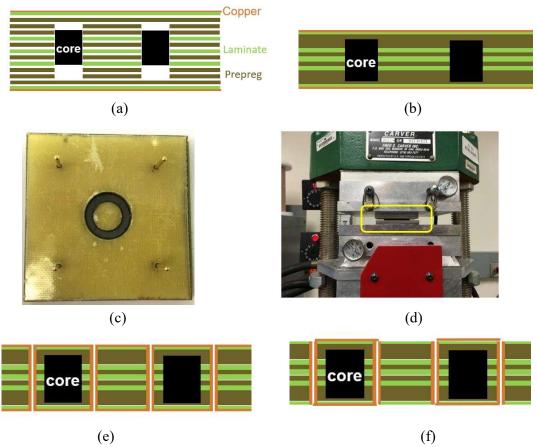

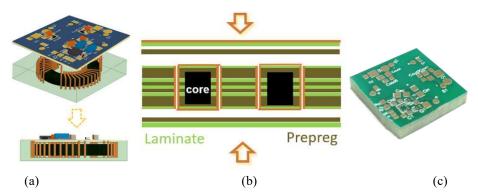

| Fig. 2-11 (a) Layer stack before PCB lamination; (b) PCB after lamination; (c) one sample      |

| during layer stack before lamination; (d) one sample is under dual stage pressure cycle; (e)   |

| Via-hole construction after PCB lamination; (f) winding construction44                         |

| Fig. 2-12 PCB-embedded transformer                                                             |

| Fig. 2-13 (a) Converter assembly with the transformer substrate; (b) PCB lamination to connect |

| the transformer and the circuit; (c) Converter after the assembly46                            |

| Fig. 2-14 Active-clamp flyback with the PCB-embedded transformer substrate                 | 48     |

|--------------------------------------------------------------------------------------------|--------|

| Fig. 2-15 Circuit layer and the power loop (black dash line) when S <sub>1</sub> turns off | 48     |

| Fig. 2-16 Thermal distribution under full load                                             | 48     |

| Fig. 2-17 Efficiency under different load                                                  | 49     |

| Fig. 2-18 Experimental waveforms of the gate drive power supply with 1 MHz switch          | ching  |

| frequency.                                                                                 | 50     |

| Fig. 2-19 Setup to measure i <sub>CM_GD</sub> with 650V GaN HMETs                          | 51     |

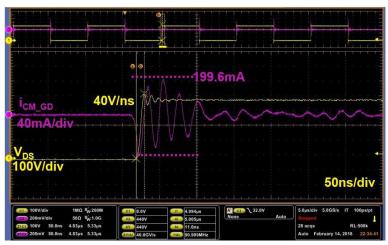

| Fig. 2-20 Transient waveforms using MEJ2S0509SC                                            | 52     |

| Fig. 2-21 Transient waveforms using proposed gate driver power supply                      | 52     |

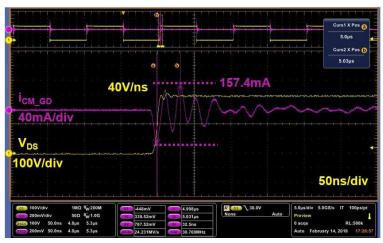

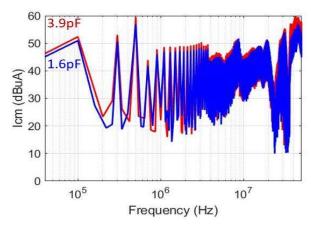

| Fig. 2-22 i <sub>CM_GD</sub> comparison using the proposed design and MEJ2S0509SC          | 53     |

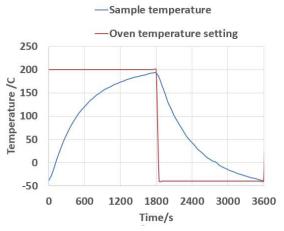

| Fig. 2-23 Sample temperature in one cycle                                                  | 54     |

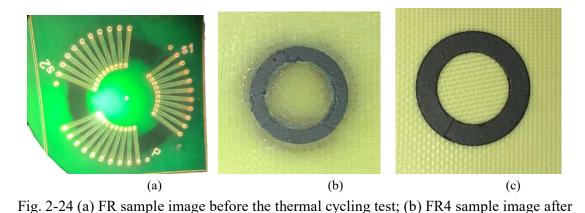

| Fig. 2-24 (a) FR sample image before the thermal cycling test; (b) FR4 sample image after  | er the |

| thermal cycling test; (c) MEGTRON 2 sample image after the thermal cycling test            | 54     |

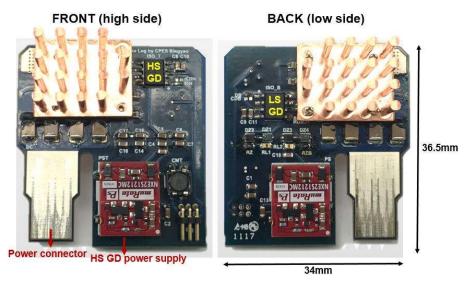

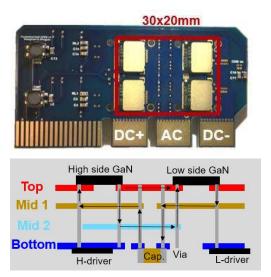

| Fig. 3-1 Back-to back power loop design                                                    | 57     |

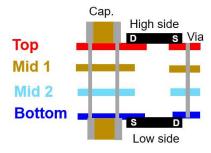

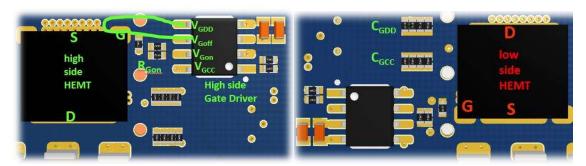

| Fig. 3-2 Gate loop design of the GaN phase leg; left: top layer with high-side HEMT, r     | ight:  |

| bottom layer with low-side HEMT                                                            | 58     |

| Fig. 3-3 Designed GaN half bridge module                                                   | 58     |

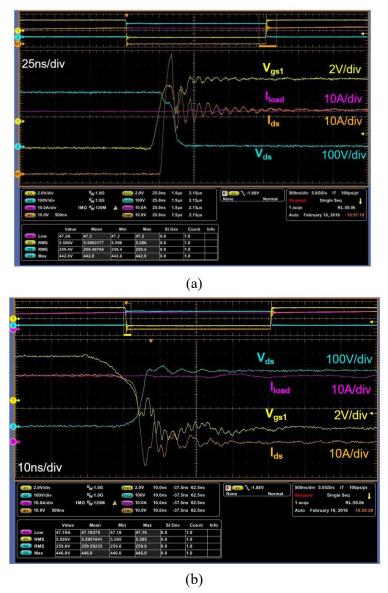

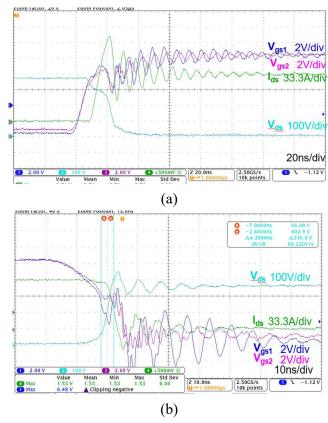

| Fig. 3-4 Transient waveforms of the turn-on (a) and turn-off (b) under 400 Vdc, 50 A       | load   |

| current with 1 $\Omega$ turn-on resistor and 0 $\Omega$ turn-off resistor                  | 59     |

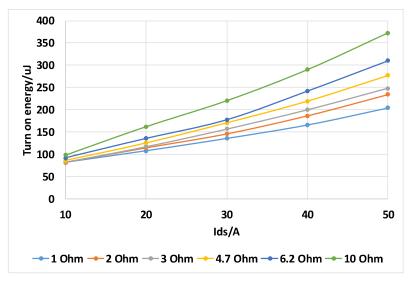

| Fig. 3-5 Turn-on energy with different load current                                        | 60     |

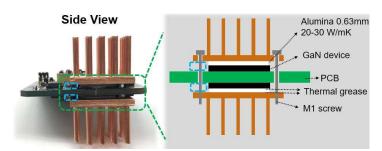

| Fig. 3-6 Thermal solution for the designed GaN half bridge                                 | 61     |

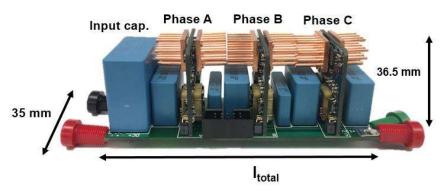

| Fig. 3-7 Proposed compact three-phase inverter structure                                   | 62     |

| Fig. 3-8 Test setup of the three-phase inverter                                            | 63     |

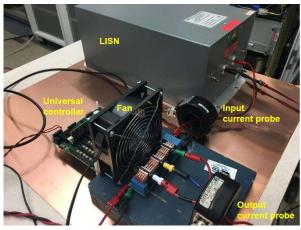

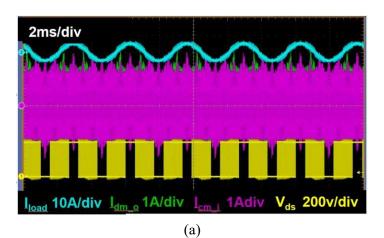

| Fig. 3-9 Transient waveforms under 500 kHz switching frequency                             | 64     |

| Fig. 3-10 Thermal distribution under 500 kHz switching frequency                        | 64          |

|-----------------------------------------------------------------------------------------|-------------|

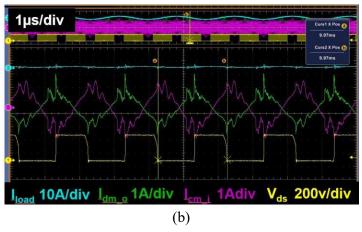

| Fig. 3-11 Estimated loss and efficiency with different switching frequency              | 65          |

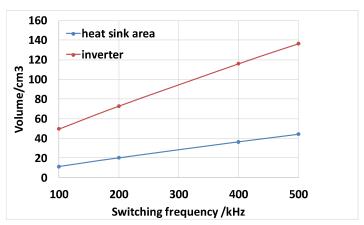

| Fig. 3-12 Estimated heat sink volume and the inverter power cell volume with            | n different |

| switching frequency                                                                     | 66          |

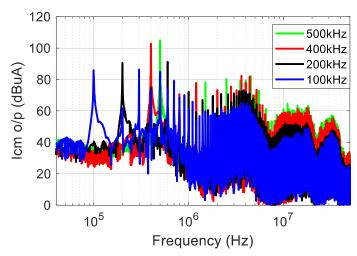

| Fig. 3-13 Output DM noise spectrum comparison                                           | 67          |

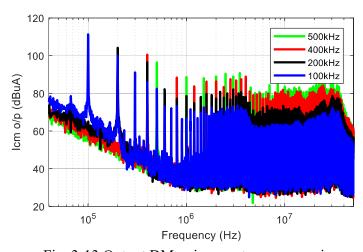

| Fig. 3-14 Output CM noise spectrum comparison.                                          | 68          |

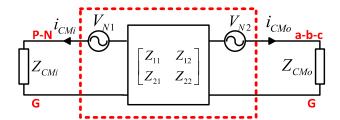

| Fig. 3-15 Unterminated EMI behavioral model                                             | 69          |

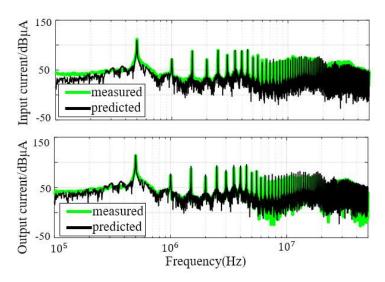

| Fig. 3-16 Comparison between the measurements and the predictions of the C              | 3aN-based   |

| inverter without EMI filters.                                                           | 70          |

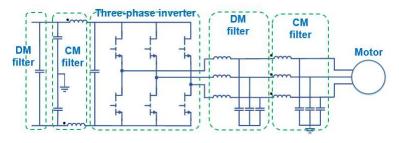

| Fig. 3-17 Filter design topology                                                        | 70          |

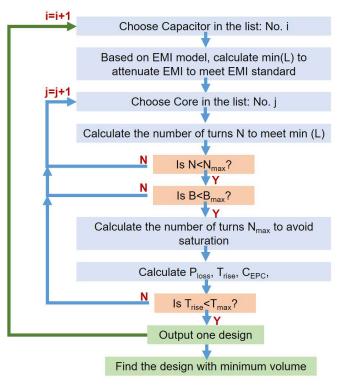

| Fig. 3-18 Filter optimization process.                                                  | 71          |

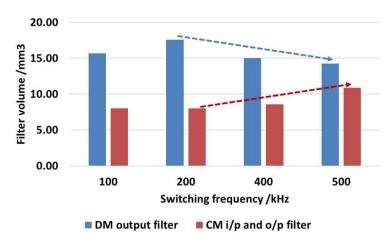

| Fig. 3-19 Filter design under different switching frequency                             | 73          |

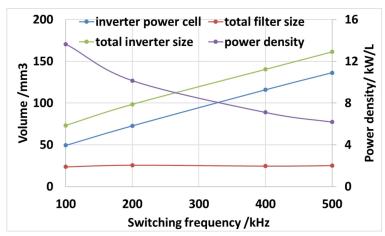

| Fig. 3-20 Switching frequency effect on the inverter volume and power density           | 73          |

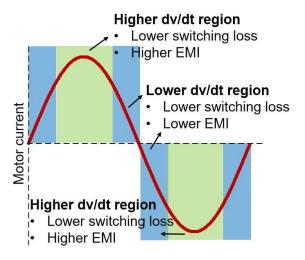

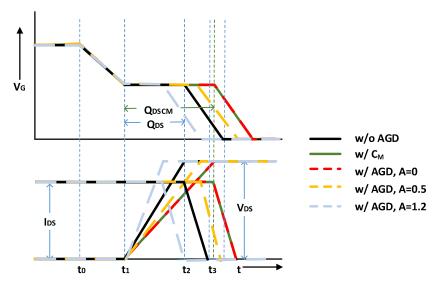

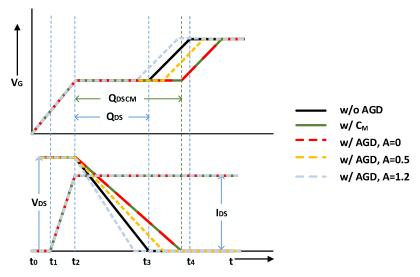

| Fig. 4-1 Active dv/dt control strategy for CM EMI reduction                             | 75          |

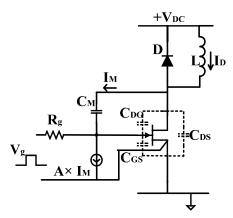

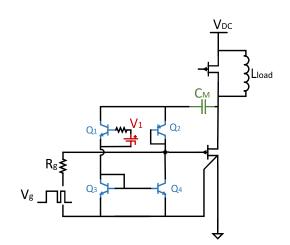

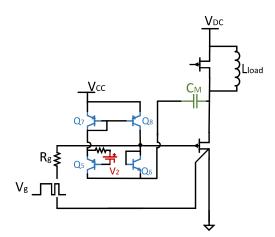

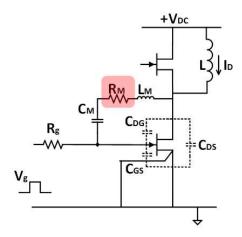

| Fig. 4-2 Circuit to achieve a varying and controllable dv/dt                            | 78          |

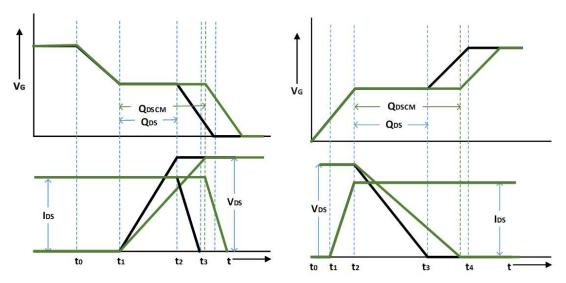

| Fig. 4-3 Simplified turn-off (left) and turn-on (right) waveforms with the extra Miller | r capacitor |

| C <sub>M</sub>                                                                          | 78          |

| Fig. 4-4 Simplified turn-off waveforms with the active gate driver                      | 80          |

| Fig. 4-5 Simplified turn-on waveforms with the active gate driver                       | 80          |

| Fig. 4-6 Proposed turn-off dv/dt control circuit                                        | 81          |

| Fig. 4-7 Proposed turn-on dv/dt control circuit.                                        | 82          |

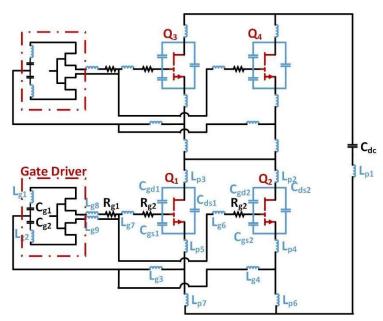

| Fig. 4-8 Complete circuit of the proposed active gate driver for GaN HEMT               | 83          |

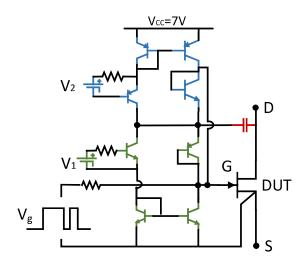

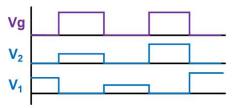

| Fig. 4-9 Logic between V <sub>1</sub> , V <sub>2</sub> and V <sub>g</sub>               | 83          |

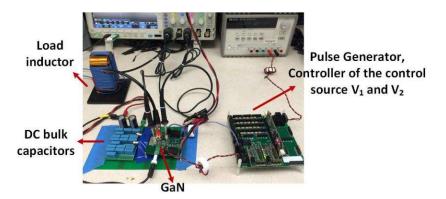

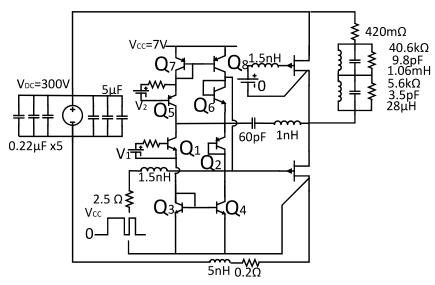

| Fig. 4-10 DPT setup with the active gate driver                                         | 84          |

| Fig. 4-11 Vertical layout of a phase leg GaN to achieve ultra-low power loop inductance85                            |

|----------------------------------------------------------------------------------------------------------------------|

| Fig. 4-12 Simulation circuit with the active control circuit                                                         |

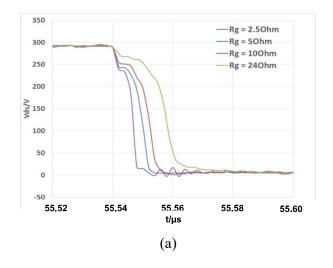

| Fig. 4-13 (a) transient waveform in active circuit during turn-off; (b) the turn off waveforms                       |

| with different dv/dt                                                                                                 |

| Fig. 4-14 (a) transient waveform in active circuit during turn-on; (b) the turn off waveforms                        |

| with different dv/dt                                                                                                 |

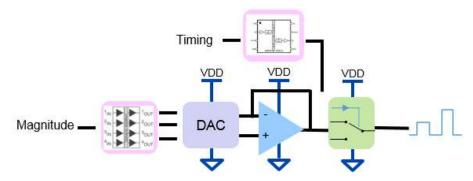

| Fig. 4-15 Proposed control source circuit for V <sub>1</sub> and V <sub>2</sub> , where 'Magnitude' and 'Timing' are |

| digital signals89                                                                                                    |

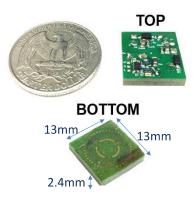

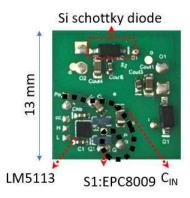

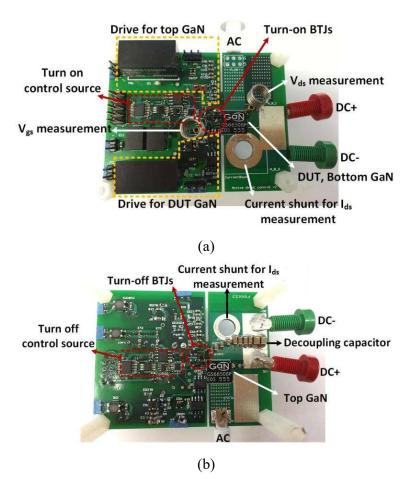

| Fig. 4-16 Hardware for Double pulse test with active dv/dt control circuit (a) top view; (b)                         |

| bottom view90                                                                                                        |

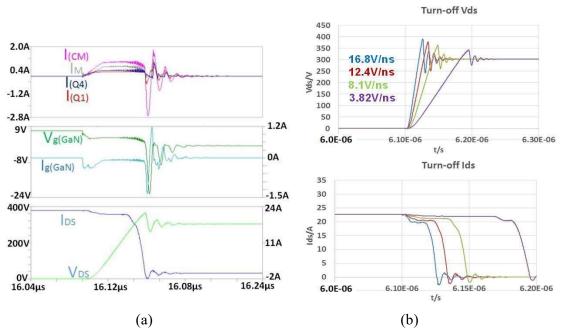

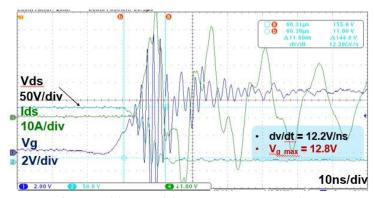

| Fig. 4-17 Turn-on waveforms with $C_M$ without BJTs at 150 V dc, 8 A, $C_M = 22 pF$ , $R_M = 0$ ;.91                 |

| Fig. 4-18 R <sub>M</sub> added to attenuate the gate oscillation induced by C <sub>M</sub> 91                        |

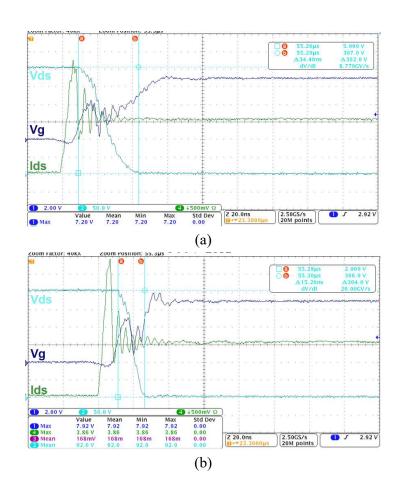

| Fig. 4-19 DPT results with C <sub>M</sub> without BJTs: (a) turn-off (b) turn-on waveforms at 300 V dc,              |

| $8 \text{ A}, C_M = 47 \text{pF}, R_M = 22 \Omega.$ 92                                                               |

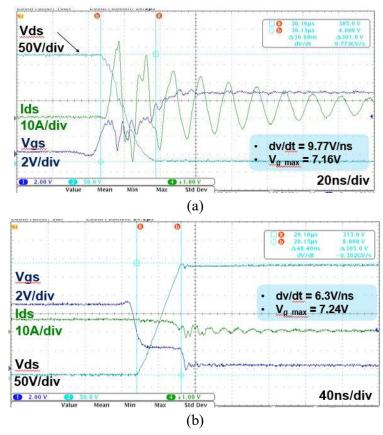

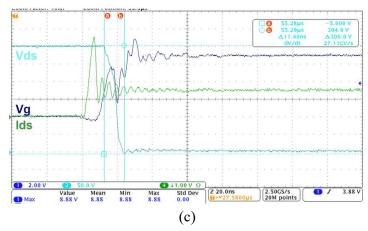

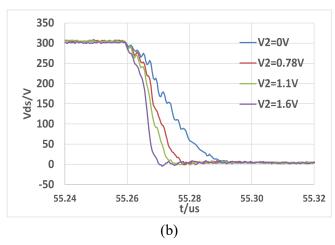

| Fig. 4-20 DPT turn-on waveforms at 300 V dc 15 A load current with active dv/dt control (a)                          |

| $V_2 = 0 \text{ V}$ ; (b) $V_2 = 1.1 \text{ V}$ ; (b) $V_2 = 1.6 \text{ V}$ 95                                       |

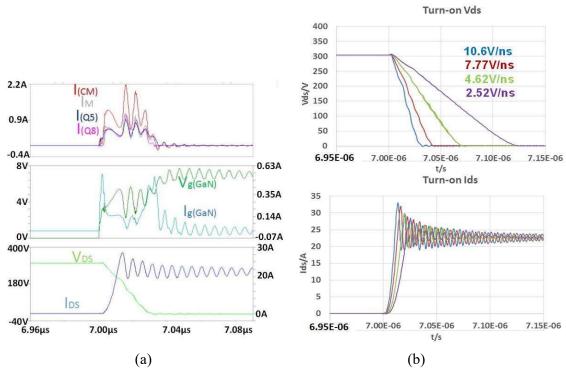

| Fig. 4-21 DPT turn-off waveforms at 300 V dc 15 A load current with active dv/dt control (a)                         |

| $V_1 = 0 V$ ; (b) $V_1 = 1.1 V$ ; (c) $V_1 = 1.8 V$ 96                                                               |

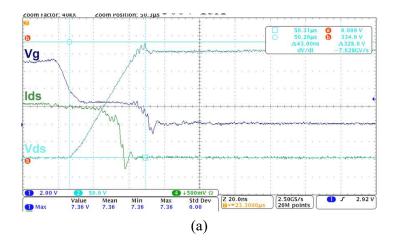

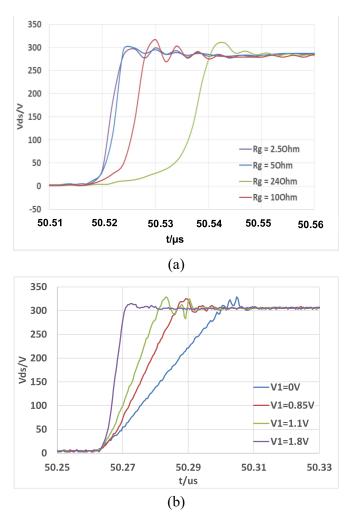

| Fig. 4-22 DPT turn-on $V_{ds}$ waveforms at 300 V dc 15 A load current (a) with different gate                       |

| resistors, (b) with active gate driver98                                                                             |

| Fig. 4-23 DPT turn-off $V_{ds}$ waveforms at 300 V dc 15 A load current (a) with different gate                      |

| resistors, (b) with active gate driver                                                                               |

| Fig. 5-1 Schematic of the phase leg of two paralleled GaN HEMTs103                                                   |

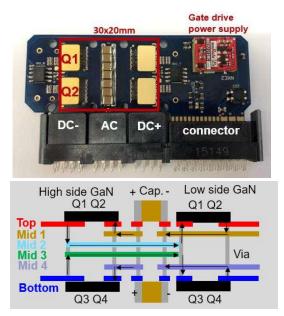

| Fig. 5-2 Power loop design of the phase leg with two paralleled GaN HEMTs104                                         |

| Fig. 5-3 Power loop design of the phase leg with four paralleled GaN HEMTs105                                               |

|-----------------------------------------------------------------------------------------------------------------------------|

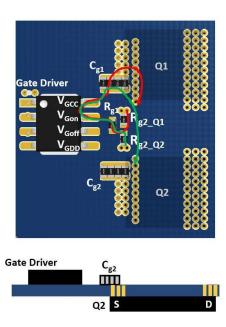

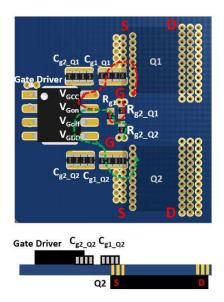

| Fig. 5-4 Turn-on gate loop with only one set of decoupling capacitor                                                        |

| Fig. 5-5 Proposed symmetric gate driver loop with minimized loop inductance106                                              |

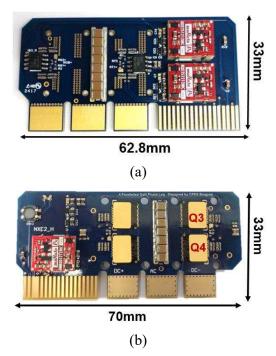

| Fig. 5-6 Back view of the designed switching cell with two (a) and four (b) GaN HEMTs                                       |

| paralleled                                                                                                                  |

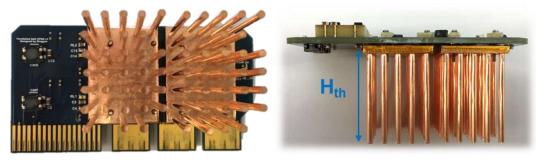

| Fig. 5-7 Heat sink mounted on the switching cells                                                                           |

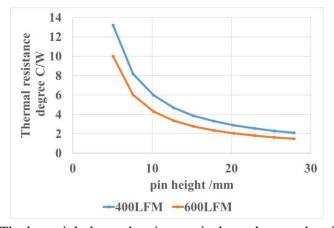

| Fig. 5-8 The heat sink thermal resistance is dependent on the pin height110                                                 |

| Fig. 5-9 Front and back view of the heat sink design for the switching cell using four paralleled                           |

| GaN HEMTs111                                                                                                                |

| Fig. 5-10 Side view of the heat sink design for the switching cell using four paralleled GaN                                |

| HEMTs                                                                                                                       |

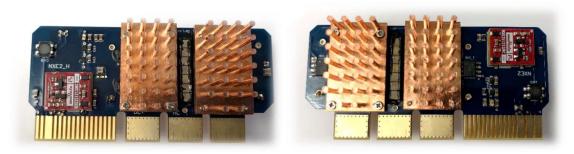

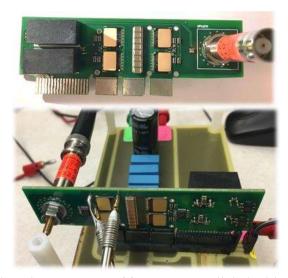

| Fig. 5-11 First version of the switching cell with two paralleled GaN HEMTs112                                              |

| Fig. 5-12 First version of the switching cell with four paralleled GaN HEMTs112                                             |

| Fig. 5-13 Curved-fin heat sink design for the first-version switching cell                                                  |

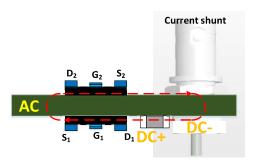

| Fig. 5-14 Double pulse test setup of two GaN paralleled with the current shunt114                                           |

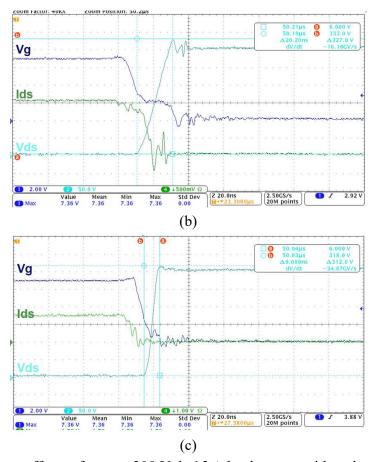

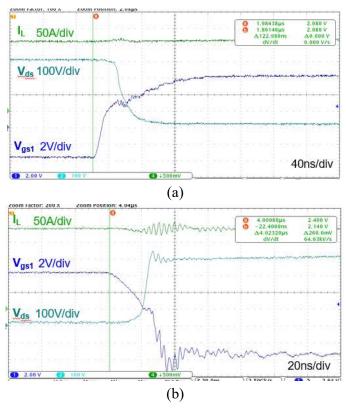

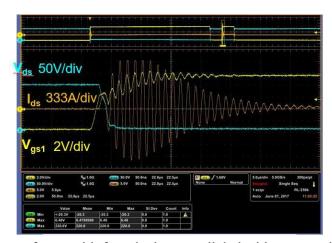

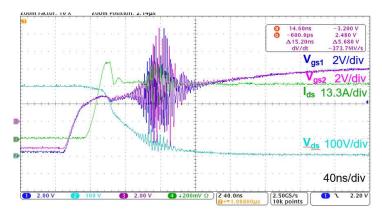

| Fig. 5-15 DPT waveforms with two devices paralleled $V_{dc}$ = 400V, $I_{ds}$ =100A, $R_{g2}$ =1 $\Omega$ , $R_{g1}$ =0:    |

| (a): turn-on, (b): turn-off                                                                                                 |

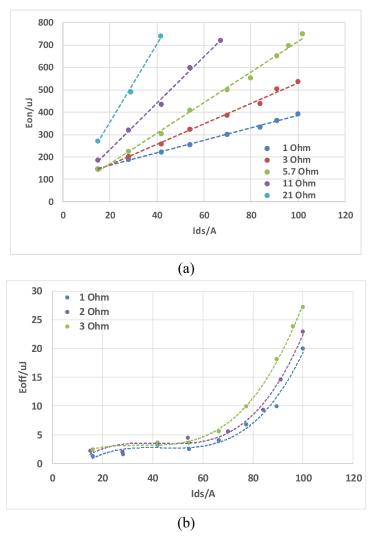

| Fig. 5-16 (a): Turn-on and (b) turn-off loss estimation with different R <sub>on</sub> and R <sub>off</sub> 115             |

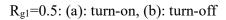

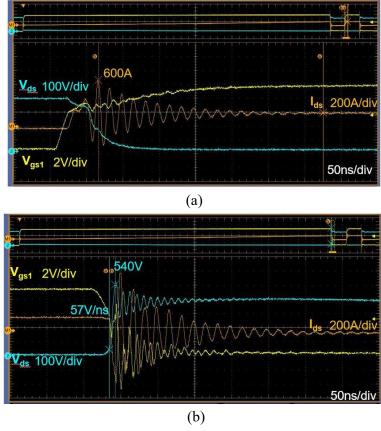

| Fig. 5-17 DPT waveforms with four devices paralleled $V_{dc}$ = 400V, $I_{ds}$ =200A, $R_{g2}$ =1 $\Omega$ , $R_{g1}$ =0.5: |

| (a): turn-on, (b): turn-off                                                                                                 |

| Fig. 5-18 Double pulse test setup of four GaN paralleled with the current shunt116                                          |

| Fig. 5-19 DPT waveforms with four devices paralleled with current shunt $V_{dc}$ = 200V, $I_{ds}$ =60A,                     |

| $R_{g2}=1\Omega, R_{g1}=0.5$                                                                                                |

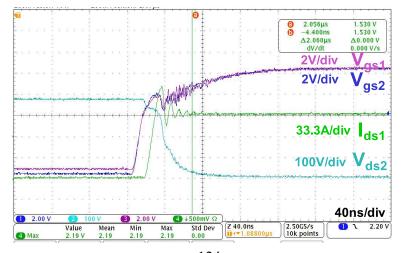

| Fig. 5-20 DPT waveforms with four devices paralleled with current shunt removed, $V_{dc}$ = 200V,                          |

|----------------------------------------------------------------------------------------------------------------------------|

| $I_{ds}$ =60A, $R_{g2}$ =1 $\Omega$ , $R_{g1}$ =0.5                                                                        |

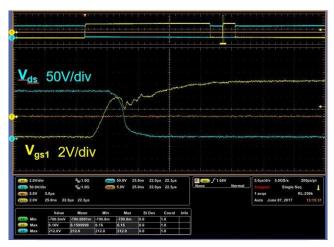

| Fig. 5-21 DPT waveforms with four devices paralleled with current shunt $V_{dc}$ = 400V,                                   |

| $I_{ds}$ =200A, $R_{g2}$ =1 $\Omega$ , $R_{g1}$ =3.9: (a): turn-on, (b): turn-off                                          |

| Fig. 5-22 Turn-on loss estimation with four paralleled GaN, compared with one and two                                      |

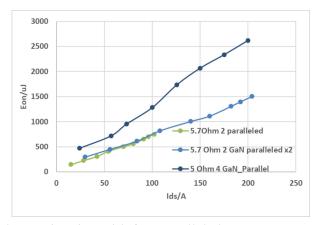

| switching cells two paralleled GaN                                                                                         |

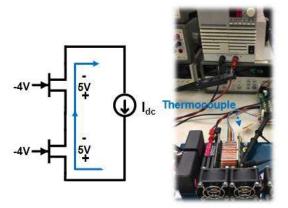

| Fig. 5-23 Setup to measure the heat sink thermal resistance                                                                |

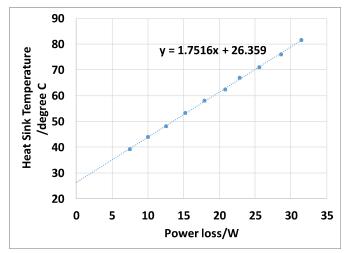

| Fig. 5-24 Heat sink temperature vs device loss for the switching cell using two paralleled GaN                             |

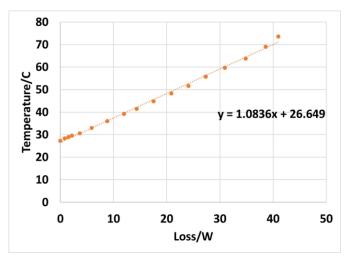

| HEMTs                                                                                                                      |

| Fig. 5-25 Heat sink temperature vs device loss for the switching cell using four paralleled GaN                            |

| HEMTs                                                                                                                      |

| Fig. 5-26 Double pulse test waveforms with Vdc= 400V, $I_{ds}$ = 42A, $R_{g2}$ =1 $\Omega$ , $R_{g1}$ = 20 $\Omega$ 123    |

| Fig. 5-27 Proposed circuit to explain the commutation between two paralleled GaN HEMTs                                     |

|                                                                                                                            |

| Fig. 5-28 Double pulse test waveforms with Vdc= 400V, $I_{ds}$ = 100A, $R_{g2}$ =1 $\Omega$ , $R_{g1}$ = 4.7 $\Omega$ .125 |

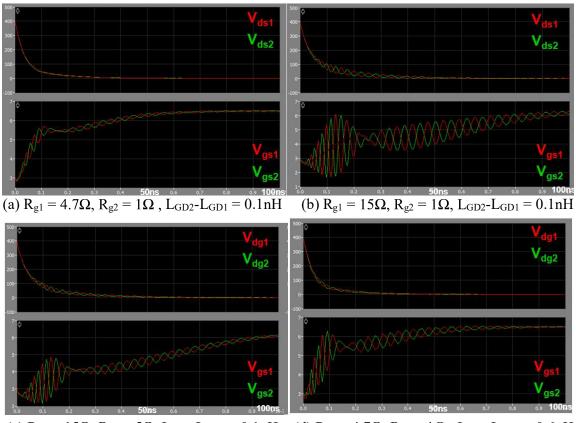

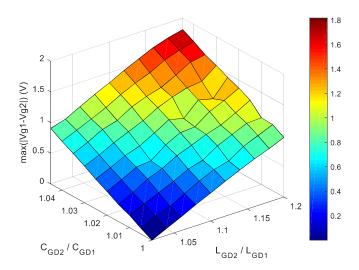

| Fig. 5-29 Simulated $V_{ds}$ and $V_{gs}$ in miller plateau duration with different passive component                      |

| values                                                                                                                     |

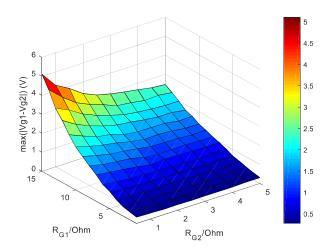

| Fig. 5-30 Predicted gate oscillation with different gate resistors ( $C_{DG2} = 1.02C_{DG1}$ , $L_{GD1} = 1.4nH$           |

| $L_{GD2}-L_{GD1} = 0.1$ nH, varying $R_{g1}$ $R_{g2}$                                                                      |

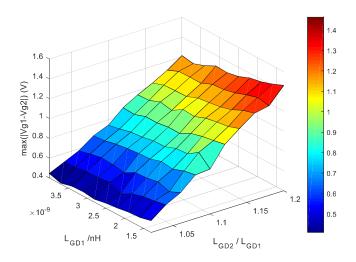

| Fig. 5-31 Predicted gate oscillation with different gate resistors and gate loop inductances (R <sub>g1</sub>              |

| $=4.7\Omega, R_{g2}=1\Omega,)$                                                                                             |

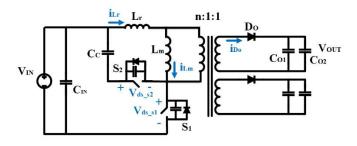

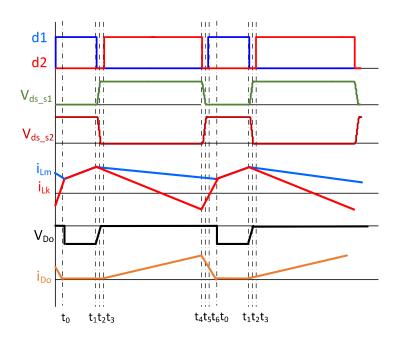

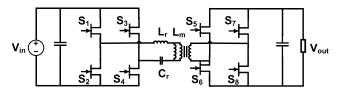

| Fig. 6-1 Schematic of the LLC resonant converter                                                                           |

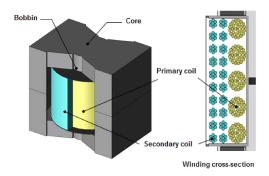

| Fig. 6-2 Common litz-wire transformer structure based on EQ or ER core130                                                  |

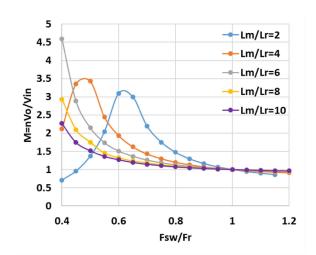

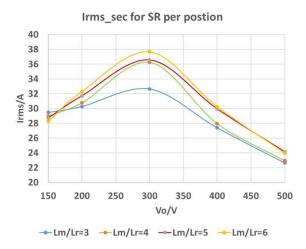

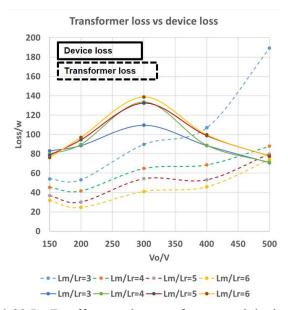

| Fig. 6-3 L <sub>m</sub> /L <sub>r</sub> effect on the converter gain and the switching frequency range131                  |

| Fig. 6-4 Core with controlled center leg gap and the horizontal winding arrangement (turns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ratio 8:3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

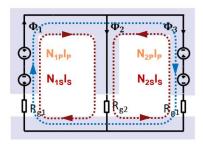

| Fig. 6-5 Magnetic circuit of the transformer in Fig. 6-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

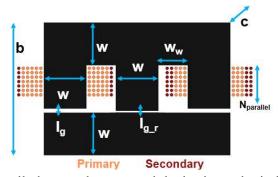

| Fig. 6-6 Core with controlled center leg width and the vertical winding arrangement (turns ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8:3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

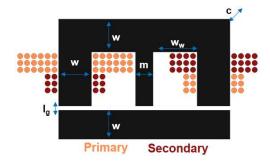

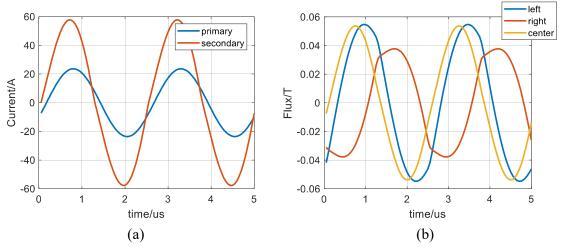

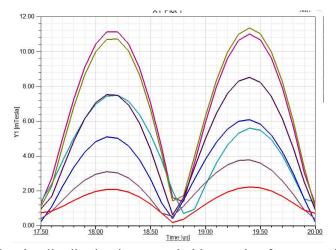

| Fig. 6-7 (a) Primary and secondary current when $f_{sw}=f_r=400 \text{kHz}$ (b) corresponding flux density                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| in each leg of the core ( $N_{1P} = 5$ , $N_{2P} = 3$ , $N_{1S} = 1$ , $N_{2S} = 2$ , $w = 14.5 mm$ , $c = 60 mm$ , $L_m = 33 \mu H$ ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $L_m/L_r = 5$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

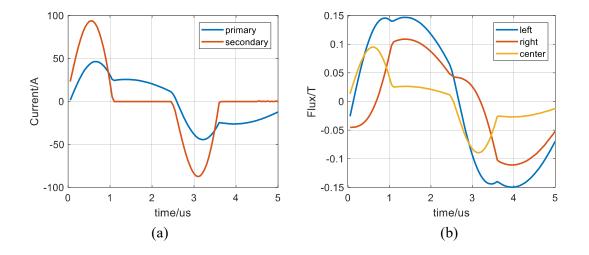

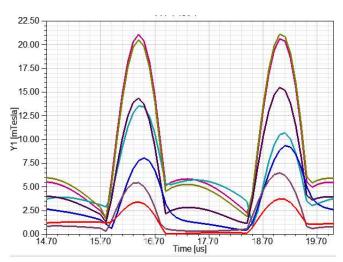

| Fig. 6-8 (a) Primary and secondary current when $f_{sw}$ =200kHz $<$ $f_r$ =400kHz, (b) corresponding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| flux density in each leg of the core $(N_{1P} = 5, N_{2P} = 3, N_{1S} = 1, N_{2S} = 2, w = 14.5 mm, c = 60 mm$ |

| $L_m = 33 \mu H, L_m/L_r = 5)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

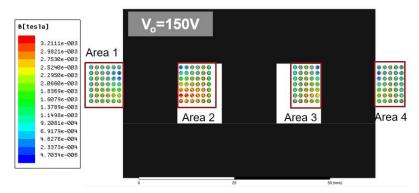

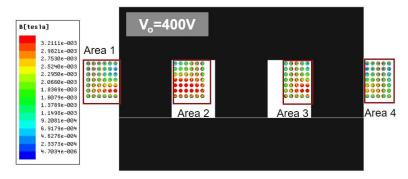

| Fig. 6-9 Transient flux density distribution on the winding area when f <sub>sw</sub> =f <sub>r</sub> =400kHz138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Fig. 6-10 Flux density distribution in one switching cycle of seven typical points at the winding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Area 1 when $f_{sw}=f_r=400kHz$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Fig. 6-11 Transient flux density distribution on the winding area when $f_{sw} < f_r = 400 \text{kHz} \dots 138$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Fig. 6-12 Flux density distribution in one switching cycle of seven typical points at the winding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Area 1 when f <sub>sw</sub> <f<sub>r=400kHz</f<sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Fig. 6-13 AC winding loss calculation process based on (6.10)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

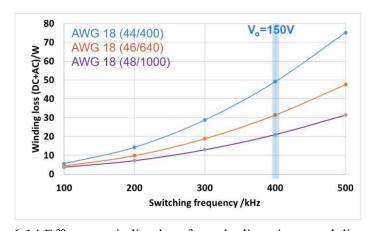

| Fig. 6-14 Effect on winding loss from the litz-wire strand diameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

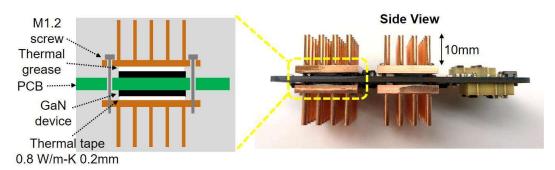

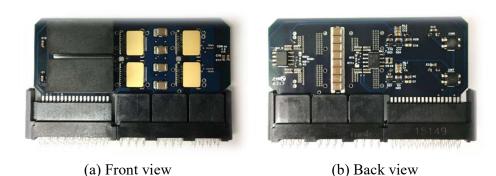

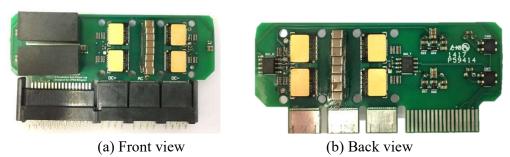

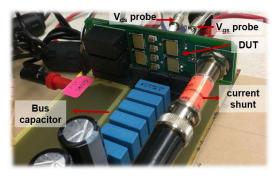

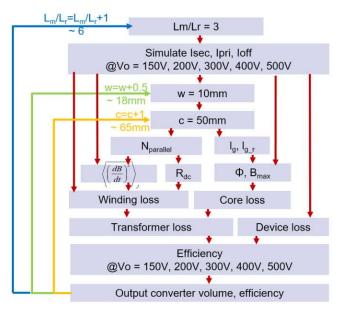

| Fig. 6-15 Optimization process of the litz-wire transformer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |