## Evaluation and Analysis on the Effect of Power Module Architecture on Common Mode Electromagnetic Interference

Taha Moaz

Thesis submitted to the faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

Master of Science In Electrical Engineering

Christina DiMarino (Chair) Richard Zhang Dushan Boroyevich

> May 2<sup>nd</sup> 2023 Arlington, Virginia

Keywords: Conducted electromagnetic interference, Electromagnetic interference (EMI), Semiconductor packaging, Silicon carbide (SiC), Wide bandgap power semiconductor devices.

© 2023, Taha Moaz

## Evaluation and Analysis on the Effect of Power Module Architecture on Common Mode Electromagnetic Interference Taha Moaz

#### ABSTRACT

Wide bandgap (WBG) semiconductor devices are becoming increasing popular in power electronics applications. However, WBG semiconductor devices generate a substantial amount of conducted electromagnetic interference (EMI) compared to silicon (Si) devices due to their ability to operate at higher switching frequencies, higher operating voltages and faster slew rates. This thesis explores and analyzes EMI mitigation techniques that can be applied to a power module architecture at the packaging level.

In this thesis, the EMI footprint of four different module architectures is measured experimentally. A time domain LTspice simulation model of the experimental test setup is then built. The common mode (CM) EMI emissions that escape the baseplate of the module into the converter is then examined through the simulation. The simulation is used to explore the CM noise footprint of eight additional module architectures that were found in literature. The EMI trends and the underlying mitigation principle for the twelve modules is explained by highlighting key differences in the architectures using common mode equivalent modelling and substitution and superposition theorem. The work aims to help future module designers by not only comparing the EMI performance of the majority of module architectures available in literature but by also providing an analysis methodology that can be used to understand the EMI behavior of any new module architecture that has not been discussed. Although silicon carbide (SiC) modules are used for this study, the results are applicable for any WBG device.

## Evaluation and Analysis on the Effect of Power Module Architecture on Common Mode Electromagnetic Interference

Taha Moaz

#### GENERAL AUDIENCE ABSTRACT

As society moves towards the electric grid of the future, there have been increasing calls for high efficiency, high power density, and low electromagnetic interference (EMI) power electronic converters. EMI is a big problem when using wide-bandgap (WBG) devices as these devices can switch very quickly and handle higher voltages when compared to silicon devices. In this study, ways to reduce EMI in a WBG power module through twelve different types of packaging are explored. Four WBG power modules are designed and fabricated in the lab, whereas a simulation model was created to study the EMI behavior of the remaining eight power module. The EMI behavior of these modules is explained using common mode (CM) equivalent modeling and substitution and superposition theorem. This study is important because WBG devices are becoming more and more popular in power electronic applications. The author hopes the findings and analysis presented in this paper can help future module designers reduce the EMI footprint of modules they design. To my parents Tahir and Asma Moaz, my sisters Urva and Rida Fatimah, and to my relatives and friends who supported me throughout my academic career.

#### ACKNOWLEDGEMENTS

With sincere appreciation in my heart, I would like to express my gratitude and appreciation to the plethora of people who supported me along the way, without whom this thesis would not have been possible.

I am very grateful to my advisor Professor Christina DiMarino for her guidance and support over the past two years. When I started at CPES, I did not have a good understanding of power electronics, let alone packaging and electromagnetic interference. Dr. DiMarino took time out of her busy schedule to help me improve my understanding of packaging, molding me into the researcher I am today. I am grateful for her dedication to my growth as an engineer and for the countless hours she has spent to help me broaden my world view. I want to thank her for giving me the opportunity to come to Virginia Tech and be a part of the establishment of the CPES Arlington Lab.

I would also like to thank the rest of my committee members, Dr. Richard Zhang and Dr. Dushan Boroyevich, for their helpful feedback and thought-provoking questions. The insights they provided greatly influenced my research skills to be what they are today. I would also like to thank Dr. Igor Cvetkovic for his valuable comments and suggestions during ESRDC meetings. I am also grateful for the CPES staff, including Mr. Vladimir Mitrovic, Mr. Matthew Scanland, Mr. David Gilham, Mr. Neil Croy, Ms. Audri Cunningham, Ms. Teresa Rose, Ms. Brandy Grim, Ms. Na Ren, Ms. Yan Sun, Mr. Dennis Grove, and Mr. Emmet Howard for their technical support and assistance.

The success of my degree was also enabled by my colleagues and friends at CPES. I am grateful for the friendship of Mr. Narayanan Rajagopal, Mr. Jack Knoll, Mr. He Song, Mr. Haris Bin Ashraf, Mr. Vladimir Mitrovic, Ms. Marie Lawson, Mr. Jesi Miranda-Santos, Mr. Mark

Cairnie, Mr. Benjamin Lyon, Ms. Anagha Mudki, Ms. Danielle Lester, Ms. Sharifa Sharfeldden, Mr. Jayesh Motwani, Mr. Minh Ngo, Mr. Matthias Spieler, Mr. Aakash Kamalapur, Mr. Arash Nazari, Mr. Sri Naga Vinay Mutyala, Ms. Qian Li, Ms. Aishworya Roy, Mr. Yu Chen, Mr. Milad Abtin, Ms. Shivani Nair, Mr. Jiaxiong Yu, and countless others who made my time at CPES special. I am once again grateful for the help of Mr. Narayanan Rajagopal in the packaging of the module architectures.

I would also like to thank the professors and the students at the LUMS University who introduced me to the world of power electronics. I am especially grateful to Dr. Hassan Abbas Khan for mentoring me after my undergraduate and graduate students Mr. Muhammad Anees, Mr. Uzair Ahmad, Mr. Hassan Fatimi, Mr Asad Nawaz, Mr. Hasnain Shah, Mr. Sajid Hussain and Mr. Abdur Raheem who taught me everything from soldering, to debugging, to testing circuits and PCBs. I am also thankful to Mr. Muhammad Mujtaba and Mr. Afzal Ahmad for their friendship.

My deepest appreciation goes toward my father Tahir Moaz and mother Asma Moaz, who has always been there with their love, support, understanding, and encouragement for all my endeavors. I am forever in dept to my parents for teaching me the value of a good education and providing me with the means to attain one. Your love and encouragement have been the most valuable thing in my life. I am also extremely grateful to my sisters Urva Fatimah and Rida Fatimah for always inspiring me to work harder. I could not have asked for more supportive sisters. I would also like to thank all my relatives for their love and support throughout my life.

This work was supported by the Office of Naval Research (ONR) and the Army Research Labatory (ARL). This work was supported by the Office of Naval Research (ONR) with the grant number N00014-16-1-2956 and grant number N00014-21-1-2124. Approved, DCN# 543-810-23 DISTRIBUTION STATEMENT A. Approved for public release, distribution unlimited. This

work was supported by the Army Research Laboratory (ARL) with grant number W911NF2020280.

# **Table of Contents**

| Chapte | er 1: Introduction                           | 1 |

|--------|----------------------------------------------|---|

| 1.1    | Background                                   | 1 |

| 1.2    | Literature Survey                            | 4 |

| Chapte | er 2: Introduction to Module Architectures1  | 0 |

| 2.1    | Introduction 1                               | 0 |

| 2.2    | Module Layout 1                              | 0 |

| 2.3    | Module Variations Fabricated 1               | 2 |

| 2.4    | Module Variations Simulated 1                | 7 |

| Chapte | er 3: Experimental Test Setup and Results 2  | 2 |

| 3.1    | Introduction                                 | 2 |

| 3.2    | Test Setup                                   | 2 |

| 3.3    | Time Domain Measurement                      | 5 |

| 3.4    | Baseplate Noise Current                      | 7 |

| 3.5    | Input Noise Current                          | 9 |

| 3.6    | Preliminary Efficiency and Switching Results | 2 |

| Chapte | er 4: Simulation and Modeling Techniques     | 5 |

| 4.1    | Introduction                                 | 5 |

| 4.2    | Time Domain Simulation                       | 5 |

| 4.3    | Common Mode Equivalent Modeling 4            | 7 |

| 4.3.1 Two Parallel Wires with Asymmetric Impedances                  | 47    |

|----------------------------------------------------------------------|-------|

| 4.3.2 Module Architectures                                           | 49    |

| 4.3.3 Test Setup Schematic                                           | 70    |

| 4.4 Substitution and Superposition Principle                         | 72    |

| Chapter 5: Module Architecture Analysis and Guidelines               | 75    |

| 5.1 Introduction                                                     | 75    |

| 5.2 Effect of Stacked Substrate                                      | 75    |

| 5.3 Effect of Connecting CM screen to DC node in Module Architecture | 82    |

| 5.4 Comparison of CM Screen (DC Node) Module Architectures           | 89    |

| 5.5 Effect of Integrating Decoupling Capacitors $(C_D)$ into Module  | 97    |

| 5.6 Effect of Integrating Filter Capacitors $(C_y)$ into Module      | 102   |

| 5.7 Lowest EMI Modules                                               | 108   |

| Chapter 6: Conclusion and Future Work                                | . 110 |

| 6.1 Introduction                                                     | 110   |

| 6.2 Summary                                                          | 110   |

| 6.3 Future Work                                                      | . 111 |

| Appendix A1: Obtaining Experimental EMI Measurements                 | . 113 |

| A.1 Introduction                                                     | . 113 |

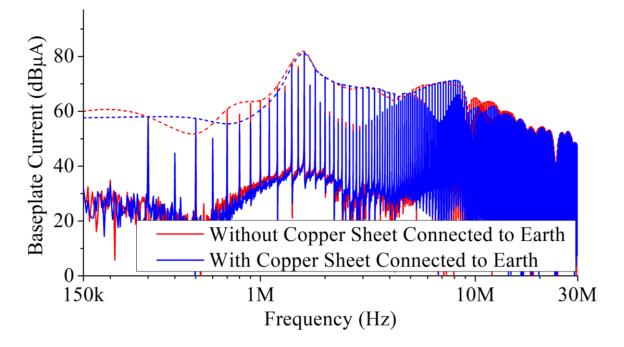

| A.2 Effect of Earthing on EMI Measurement                            | . 113 |

| A.3 Effect of Probes on EMI Measurement                              | . 115 |

| B | Bibliography                                   | 127 |

|---|------------------------------------------------|-----|

|   | A.7 Confirming Repeatability of EMI Results    | 124 |

|   | A.6 ADC bit Resolution and Sampling Time       | 123 |

|   | A.5 Effect of Time Window on EMI Measurement   | 120 |

|   | A.4 Effect of Input Voltage on EMI Measurement | 119 |

# List of Figures

| Figure 1: Intrinsic device properties of silicon (Si, Green), gallium nitride (GaN, Purple), and           |

|------------------------------------------------------------------------------------------------------------|

| silicon carbide (SiC, Blue)                                                                                |

| Figure 2: (a) Circuit schematic of 10 kV, 120 A SiC MOSFET/JBS module in PEBB based IMU                    |

| (b) ground current (c) inductor current from [10]                                                          |

| Figure 3: Module architectures explored in literature                                                      |

| Figure 4: (a) Top view, and (b) side view of common-mode screen module                                     |

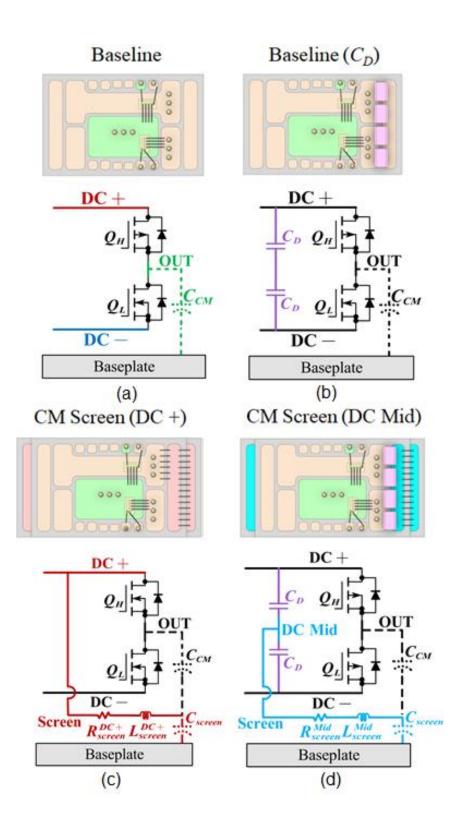

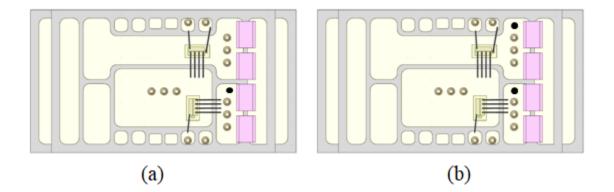

| Figure 5: Variation of the module (a) Baseline module with no common-mode (CM) screen (b)                  |

| Baseline module with no CM screen but with decoupling capacitors, (c) CM screen module with                |

| screening layer connected to DC+, and (d) CM screen module with screening layer connected to               |

| DC Mid                                                                                                     |

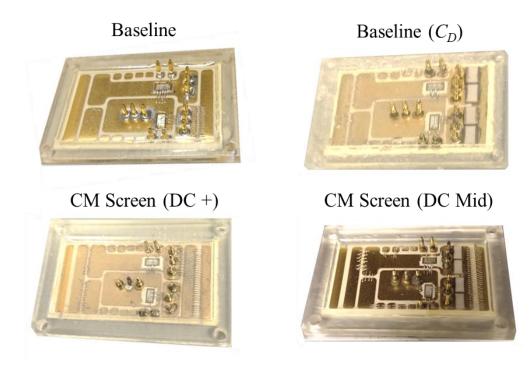

| Figure 6: Images of the fabricated CM screen module prototypes17                                           |

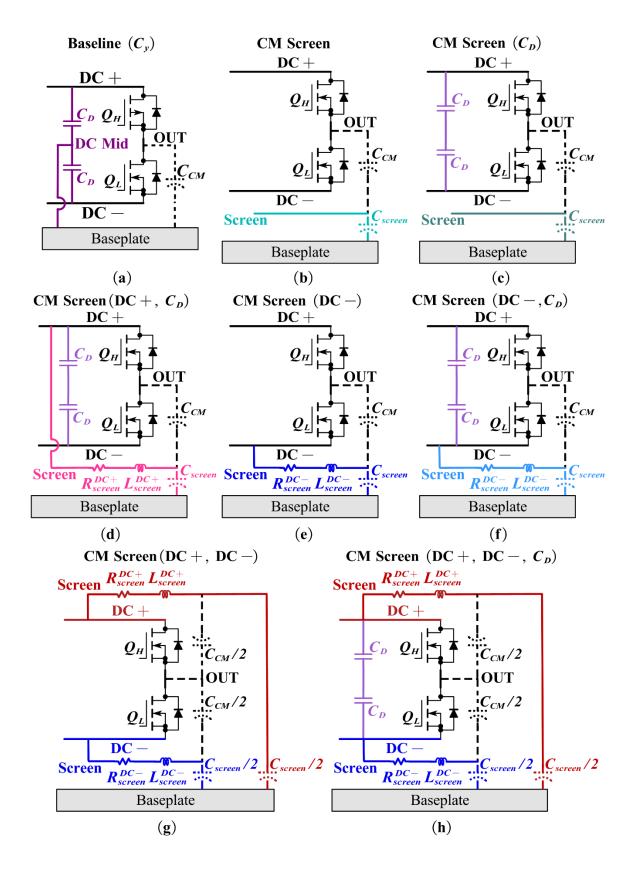

| Figure 7: Eight additional module architectures studied through simulation                                 |

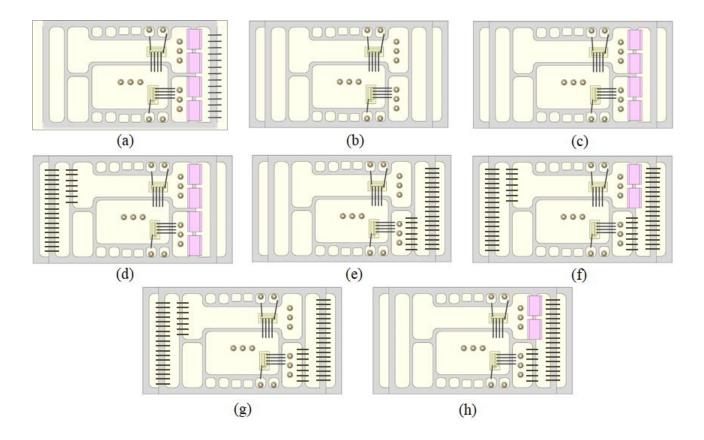

| Figure 8: Hypothetical module layouts for the eight additional module architectures                        |

| Figure 9: Hypothetical module layouts for (a CM Screen (DC-, <i>CD</i> ) and (b) CM Screen (DC+,           |

| DC-, <b><i>CD</i></b> ) with vias to ensue DC Mid node inside module                                       |

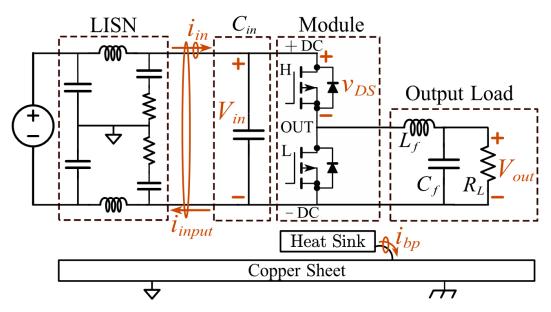

| Figure 10: Simplified schematic of EMI test setup for the buck converter                                   |

| Figure 11: Hardware setup of EMI testbed for buck converter                                                |

| Figure 12: Zoomed-in time domain waveforms for the Baseline module architecture showing (a)                |

| high-side SiC MOSFET $QH$ drain-source voltage $vDS$ and (b) noise current $ibp$                           |

| Figure 13: Frequency spectra of noise current <i>ibp</i> for (a) Baseline and CM Screen (DC+) module,      |

| (b) Baseline ( <b><i>CD</i></b> ) and CM Screen (DC Mid) module, and (c) the CM Screen (DC+) and CM Screen |

| (DC Mid) module                                                                                            |

| Figure 14: Time domain waveform for <i>ibp</i> during device (a) turn-on and (b) turn-off for module |  |  |

|------------------------------------------------------------------------------------------------------|--|--|

| architecture: Baseline (Black), Baseline (CD) (Brown), CM Screen (DC+) (Red), and CM Screen          |  |  |

| (DC Mid) (Light Blue)                                                                                |  |  |

| Figure 15: Frequency spectra of noise current <i>iinput</i> for (a) Baseline and CM Screen (DC+)     |  |  |

| module, (b) the Baseline ( <i>CD</i> ) and CM Screen (DC Mid) module, and (c) CM Screen (DC+) and    |  |  |

| CM Screen (DC Mid) module                                                                            |  |  |

| Figure 16: Switching Characteristics (a) Falling Edge (b) Rising Edge                                |  |  |

| Figure 17: (a) Simulation model of test setup with the Baseline module architecture (b)              |  |  |

| Comparison of the hardware (Black) and simulation (Blue) results for the frequency spectra of        |  |  |

| noise current <i>ibp</i> for the Baseline module                                                     |  |  |

| Figure 18: Simulation schematic of the twelve module architectures explored                          |  |  |

| Figure 19: Comparison of the hardware and time domain simulation results for the frequency           |  |  |

| spectra of noise current $ibp$ for (a) the Baseline (CD), (b) the CM Screen (DC+) and (c) CM         |  |  |

| Screen (DC Mid) modules                                                                              |  |  |

| Figure 20: Frequency spectra of noise current <i>ibp</i> from simulation for (a) the Baseline and CM |  |  |

| Screen (DC+) modules, (b) the Baseline ( $C_D$ ) and CM Screen (DC Mid) modules, and (c) the CM      |  |  |

| Screen (DC+) and CM Screen (DC Mid) modules                                                          |  |  |

| Figure 21: (a) Parallel wires with asymmetric impedances (b) CEM of parallel wires with              |  |  |

| asymmetric impedances                                                                                |  |  |

| Figure 22: (a) Generalized module architecture with generalized impedances (b) partitioning the      |  |  |

| module architecture for equivalent circuit model derivation                                          |  |  |

| Figure 23: Common mode equivalent model (CEM) of simplifed module architectures                      |  |  |

| Figure 24: Common mode equivalent model for test setup schematic shown in Figure 17(a) 71            |  |  |

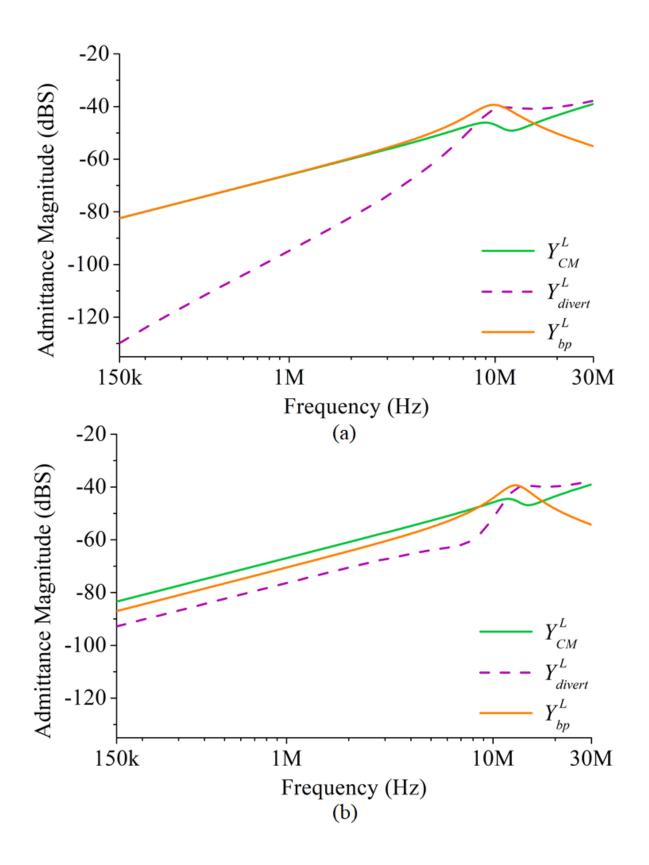

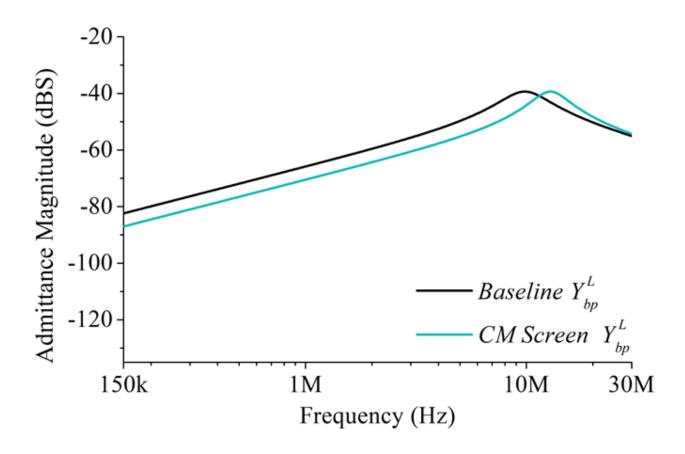

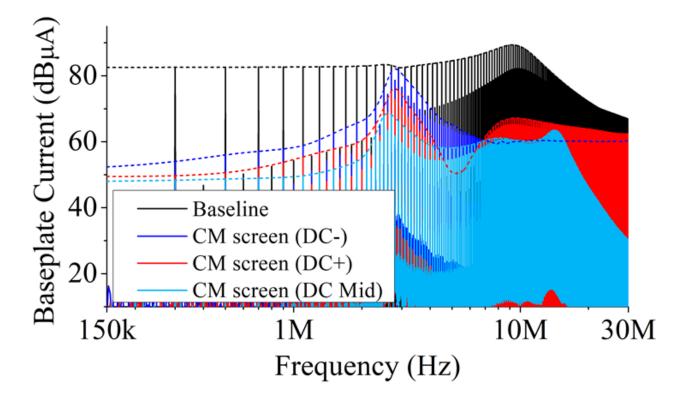

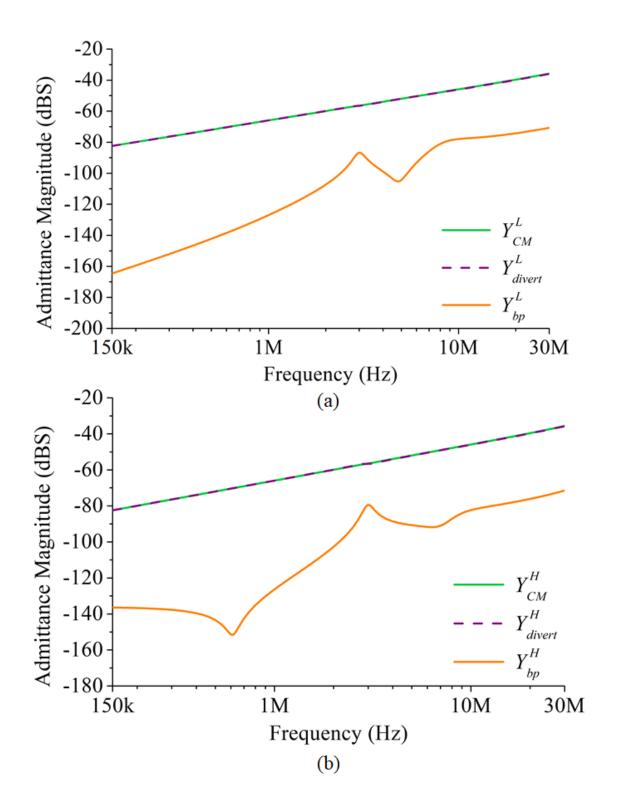

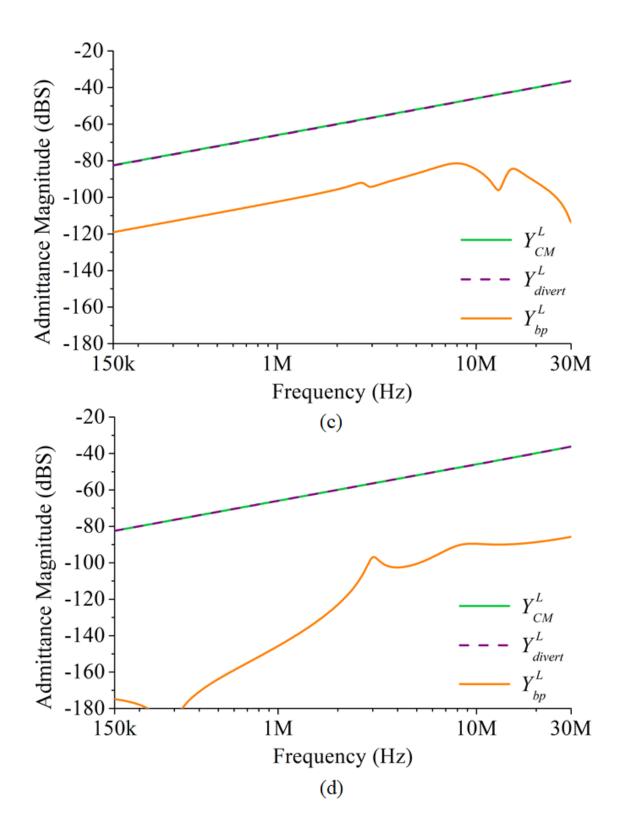

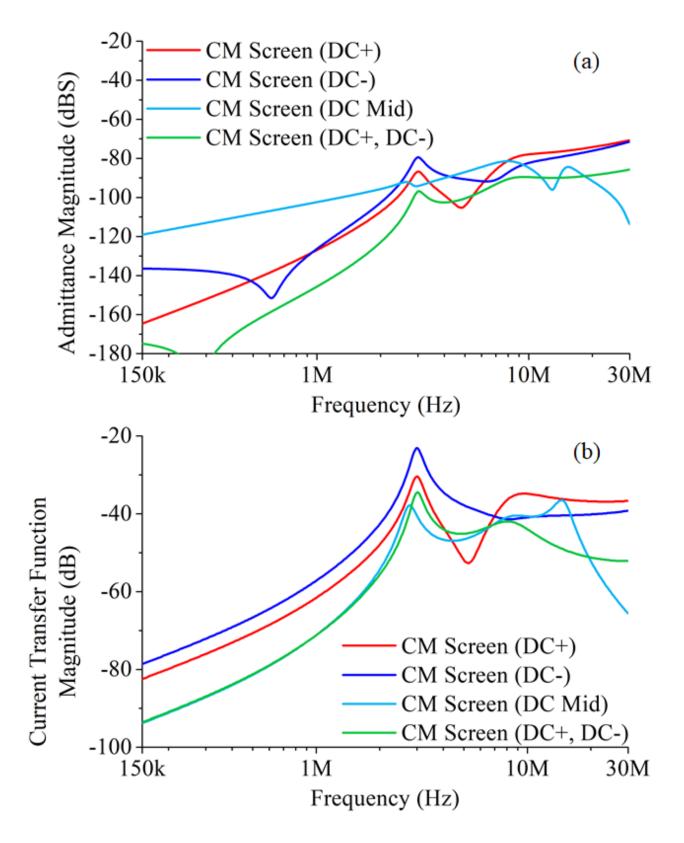

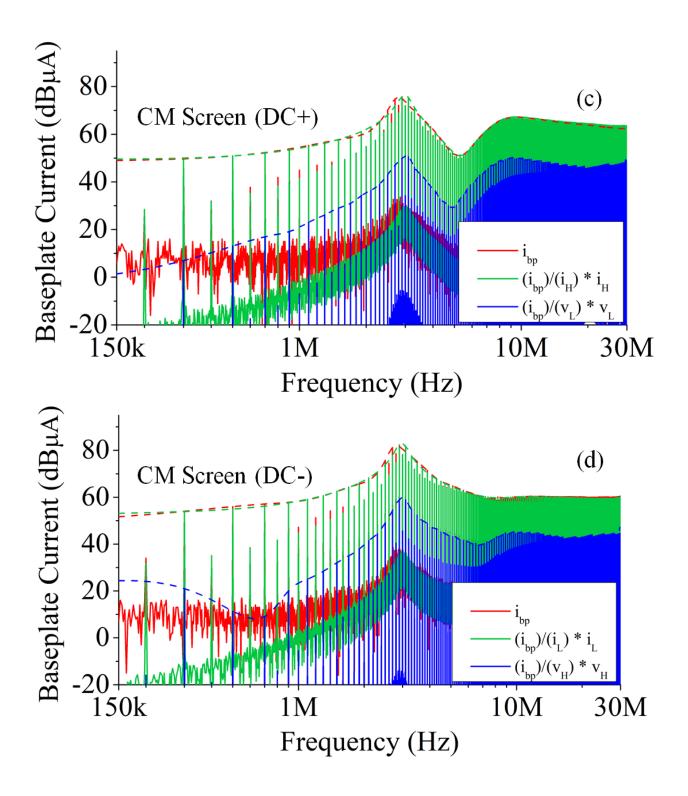

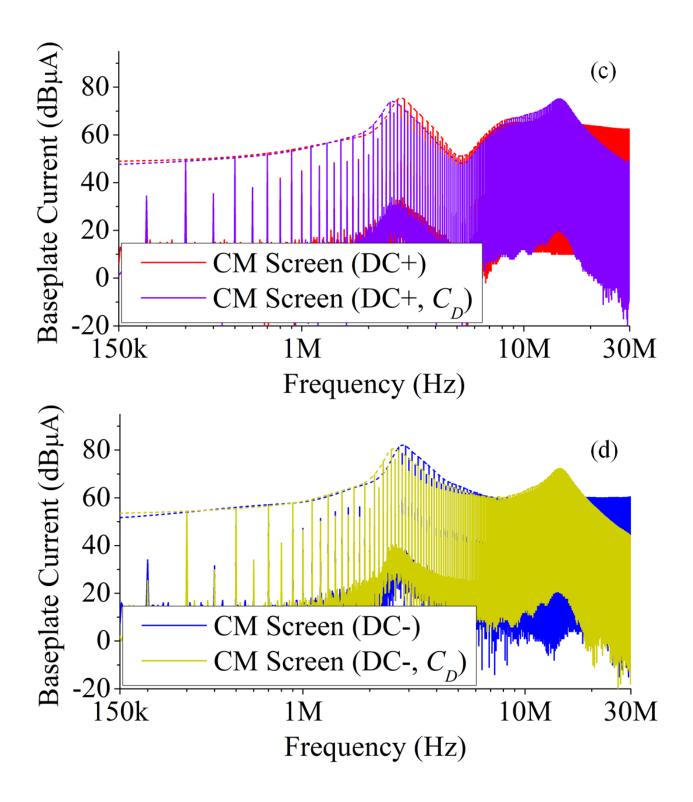

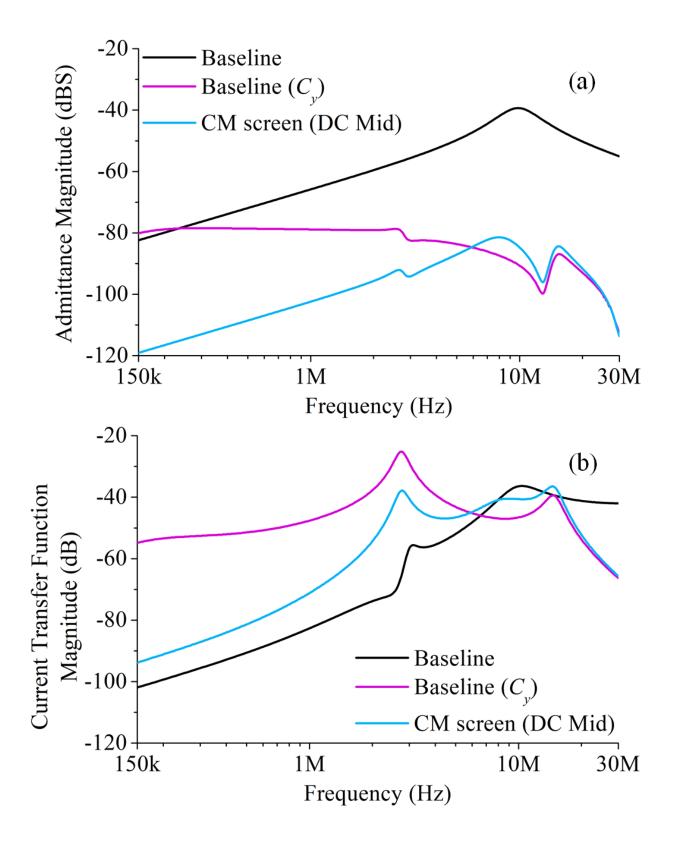

Figure 25: (a) Simulation model for CM Screen (DC+) module (b) simulation model after substitution theorm (c) superposition state used to study the effect of di/dt (d) superposition state used to study the effect of dv/dt.....74 Figure 26: Frequency spectrum of Baseline module (black), CM Screen module (teal) architecture. Figure 27: Converter schematic showing path taken by noise current *iCM* flowing through *CCM* Figure 28: Admittance seen by current *iCM* (Green), *idivert* (Purple), and *ibp* (Orange) as a function of voltage source  $\nu L$  for (a) Baseline module (b) CM Screen module architecture. ..... 81 Figure 29: Admittance seen by current *ibp* as a function of voltage source  $\nu L$  for (a) Baseline Figure 30: Noise generated at the baseplate with Baseline module (Black), and (a) CM Screen (DC-) module (Blue), CM Screen (DC+) module (Red) and CM Screen (DC Mid) module (Light Figure 31: Converter schematic showing path taken by noise current *iCM* flowing through *CCM* due to (a) voltage source  $\nu L$  in CM Screen (DC+) module (b) voltage source  $\nu H$  in CM Screen (DC-) module (c) voltage source  $\nu L$  in CM Screen (DC Mid) module and (d) voltage source  $\nu L$ Figure 32: Admittance seen by current *iCM* (Green), *idivert* (Purple), and *ibp* (Orange) as a function of voltage source  $\nu L$  for (a) CM Screen (DC+) (b) CM Screen (DC-) (c) CM Screen (DC Figure 33: Noise current *ibp* for CM Screen (DC-) (Blue), CM Screen (DC+) (Red), CM Screen

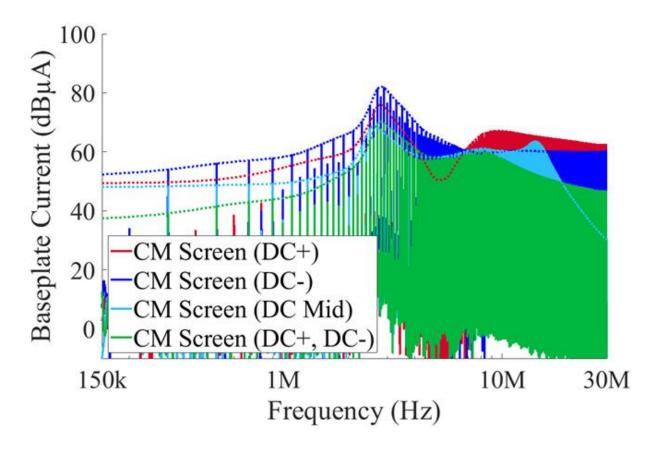

| Figure 34: (a) Admittance transfer function and (b) Current transfer function for all four CM                   |  |  |

|-----------------------------------------------------------------------------------------------------------------|--|--|

| Screen module architecture                                                                                      |  |  |

| Figure 35: Converter schematic showing path taken by noise current <i>iCM</i> flowing through <i>CCM</i>        |  |  |

| due to (a) current source <i>iH</i> in CM Screen (DC+) module (b) current source <i>iL</i> in CM Screen (DC-    |  |  |

| ) module (c) current source <i>iH</i> in CM Screen (DC Mid) module and (d) current source <i>iH</i> in CM       |  |  |

| Screen (DC+, DC-) module                                                                                        |  |  |

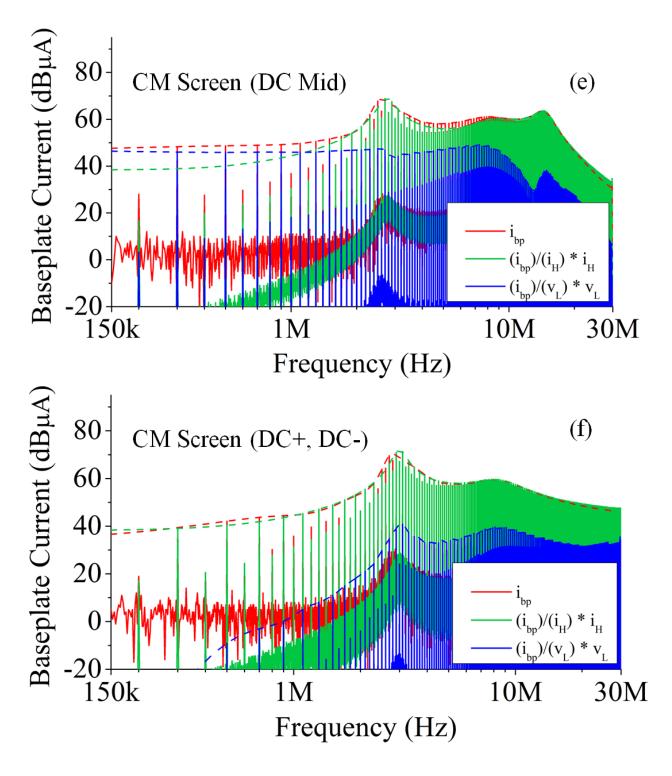

| Figure 36: Frequency spectrum of noise current <i>ibp</i> (Red), product of current transfer function           |  |  |

| and current source $iH$ (Green) and product of admittance transfer function and voltage source $\nu L$          |  |  |

| (Blue) for (a) Baseline module (b) CM Screen (DC+) module (c) CM Screen (DC-) module (d)                        |  |  |

| CM Screen (DC Mid) module and (e) CM Screen (DC+, DC-) module                                                   |  |  |

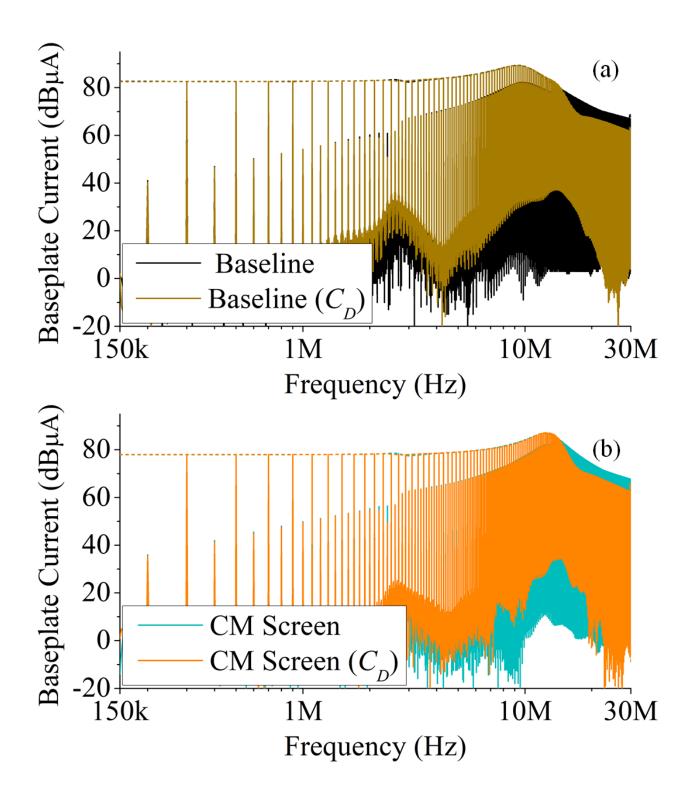

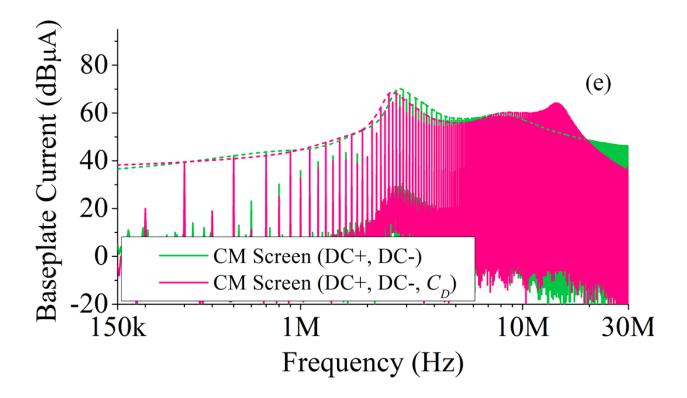

| Figure 37: Noise generated at the baseplate with (a) Baseline module (Black), and Baseline ( <b><i>CD</i></b> ) |  |  |

| module (Brown) (b) CM Screen module (Teal), and CM Screen ( <i>CD</i> ) module (Orange) (c) CM                  |  |  |

| Screen (DC+) module (Red), and CM Screen (DC+, <i>CD</i> ) module (Purple) (d) CM Screen (DC-)                  |  |  |

| module (Blue), and CM Screen (DC-, <i>CD</i> ) module (Yellow) (e) CM Screen (DC+, DC-) module                  |  |  |

| (Green) and CM Screen (DC+, DC-, <i>CD</i> ) module (Pink)                                                      |  |  |

| Figure 38: Parasitic inductances that resonate with (a) integrated decoupling capacitors $C_D$                  |  |  |

| resulting in the change of slope of roll off at ~13.5 MHz (b) PCB decoupling capacitors $C_{PCB}$ and           |  |  |

| integrated decoupling capacitors $C_D$ resulting in peak at ~2.7 MHz                                            |  |  |

| Figure 39: Experimental results showing the effect of integrating decoupling capacitors into                    |  |  |

| module on slew rate and ringing in Baseline and Baseline ( <i>CD</i> ) module                                   |  |  |

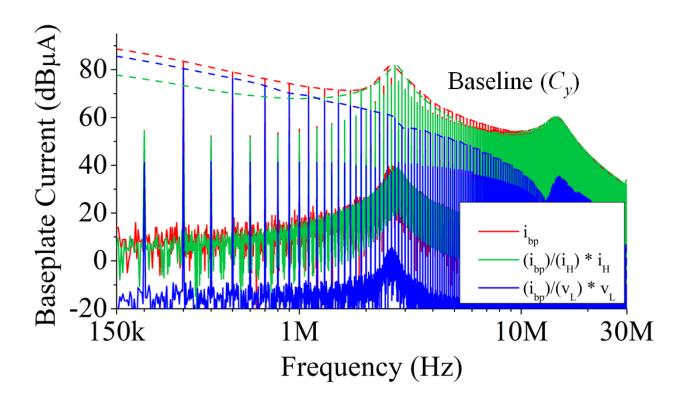

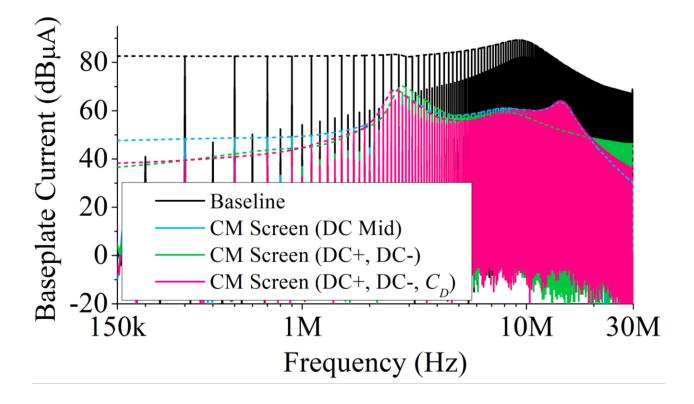

| Figure 40: Noise generated at the baseplate with (a) Baseline module (Black), and Baseline ( $Cy$ )             |  |  |

| module (Purple) (b) Baseline module (Black) and CM Screen (DC Mid) module (Light Blue) 104                      |  |  |

| Figure 41: Frequency Spectrum of noise current <i>ibp</i> (Blue), product of current transfer function      |

|-------------------------------------------------------------------------------------------------------------|

| and current source $iH$ (Green) and product of admittance transfer function and voltage source $\nu L$      |

| (Red) for Baseline $(C_y)$ module                                                                           |

| Figure 42: (a) Admittance transfer function $Ybp$ and (b) Current transfer function $Kbp$ for               |

| Baseline module (Black), Baseline ( $C_y$ ) module (Purple) and CM Screen (DC Mid) module (Light            |

| Blue) architecture                                                                                          |

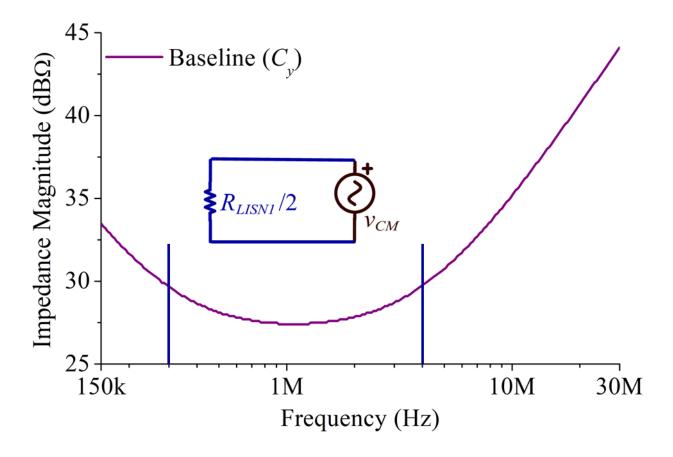

| Figure 43: Impedance seen by $\nu CM$ for Baseline ( $C_y$ ) module in the conducted EMI frequency          |

| range. Frequency range 300 kHz to 4 MHz marked on x-axis                                                    |

| Figure 44: EMI footprint at baseplate of Baseline module (Black), CM Screen (DC Mid) module                 |

| (Light Blue), CM Screen (DC+, DC-) module (Green) and CM Screen (DC+, DC-, C <sub>D</sub> ) module          |

| (Pink)                                                                                                      |

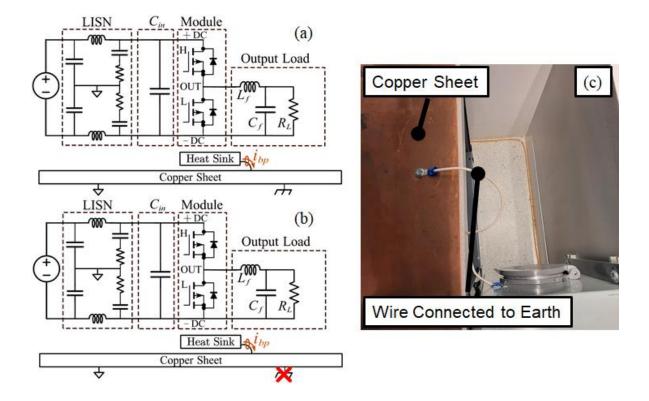

| Figure 45: (a) Converter schematic with earth connection (b) Converter schematic without earth              |

| connection (c) earth connection made to copper sheet in hardware                                            |

| Figure 46: EMI noise measurements at baseplate <i>ibp</i> without (red) and with (blue) copper sheet        |

| connected to earth                                                                                          |

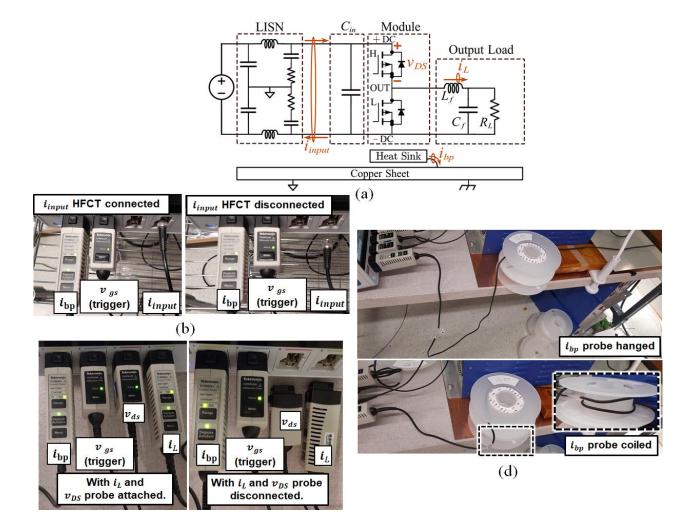

| Figure 47: (a) Converter schematic showing placement of all probes (b) Connection and                       |

| disconnection of <i>iinput</i> measurement probe (c) Connection and disconnection of $\nu ds$ and <i>iL</i> |

| measurement probe (d) orientation of <i>ibp</i> probe hanged and coiled                                     |

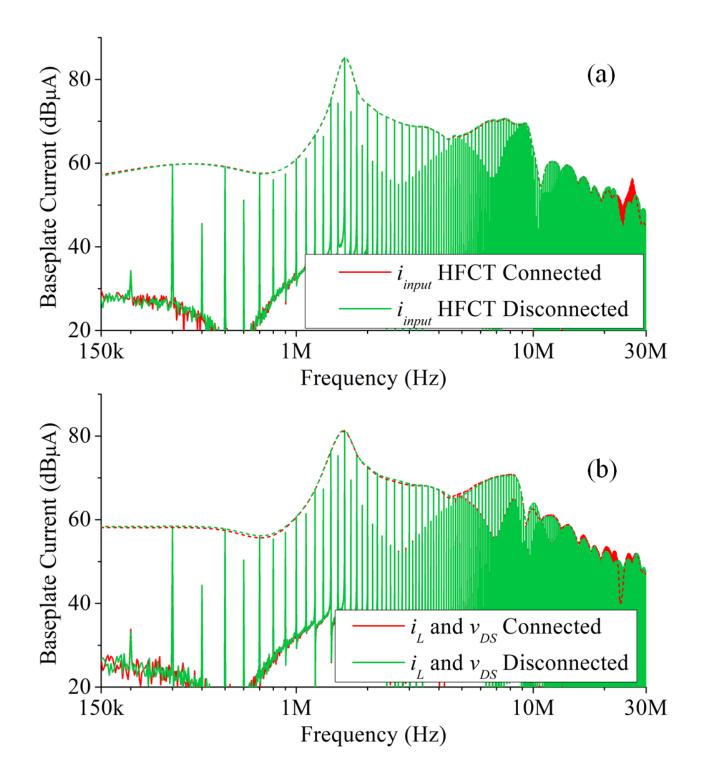

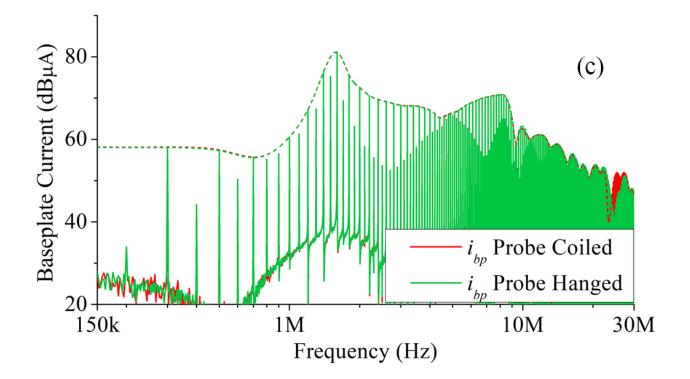

| Figure 48: EMI frequency spectrum with (a) connection and disconnection of <i>iinput</i>                    |

| measurement probe (b) connection and disconnection of $vds$ and $iL$ measurement probe (c)                  |

| orientation of <i>ibp</i> probe hanged and coiled                                                           |

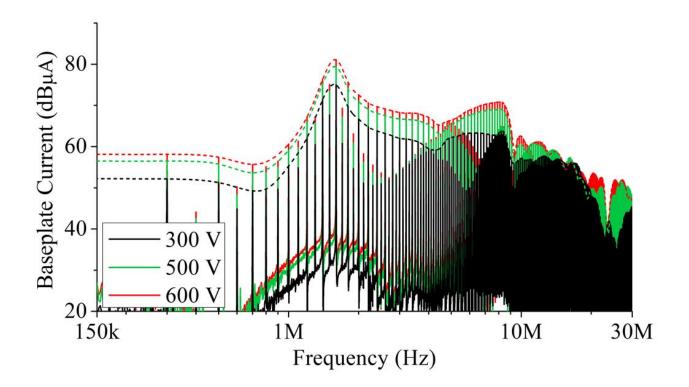

| Figure 49: EMI frequency spectrum with input voltage increased to 300 V (black), 500 V (green),             |

| and 600 V (red)                                                                                             |

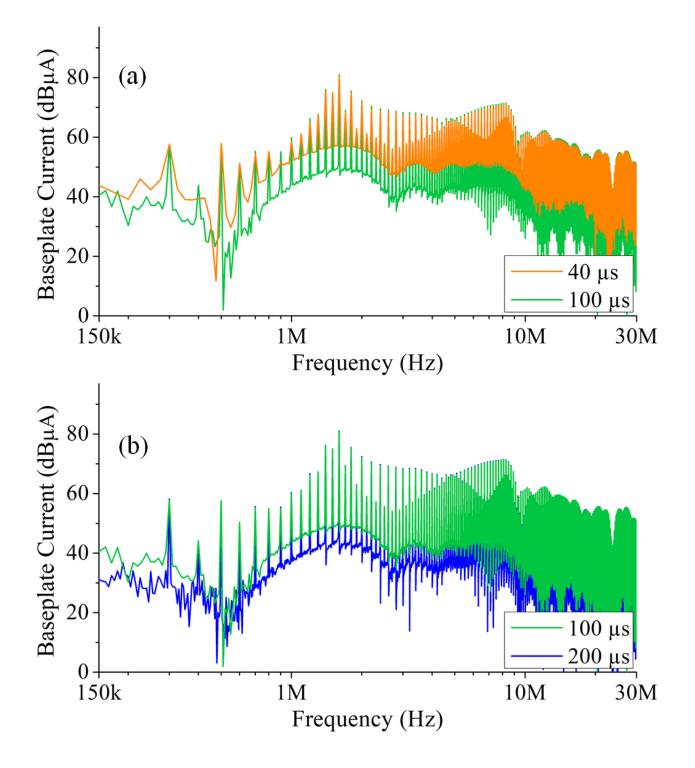

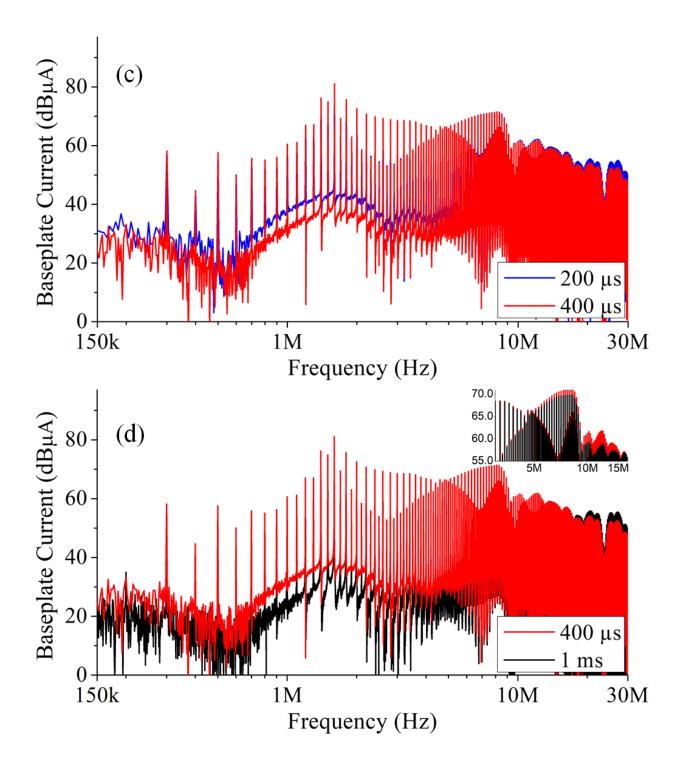

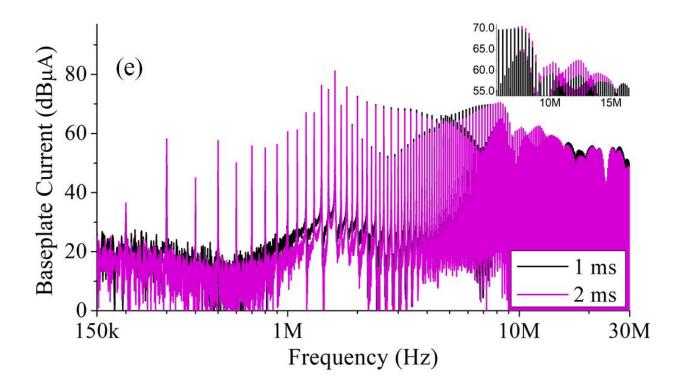

| Figure 50: Effect of varying time window used to record time domain waveforms     | 123 |

|-----------------------------------------------------------------------------------|-----|

| Figure 51: Methodology used to confirm EMI results were repeatable and consistent | 126 |

## List of Tables

| Table 1: Summary of Setup Specifications                                               | 23   |

|----------------------------------------------------------------------------------------|------|

| Table 2: Switching Characteristics and Efficiency                                      | 33   |

| Table 3: Summary of Simulation Parameters                                              | 37   |

| Table 4: Summary of Module Architecture Parameters                                     | 41   |

| Table 5: Value of Equivalent CEM Capacitance Ceq                                       | 69   |

| Table 6: Sampling Frequency and ADC bit resolution options available in oscilloscope M | SO54 |

|                                                                                        | 124  |

## **Chapter 1: Introduction**

### 1.1 Background

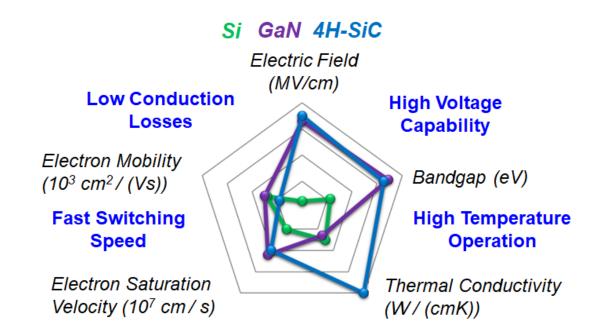

The leading semiconductor choice for power electronics applications has been silicon (Si) for several decades [1]. Although Si-based power electronics provides the benefit of being mature and well-established, the technology is gradually reaching its limitations [2]. Wide-band gap (WBG) semiconductor devices have recently started to attract attention in power electronics due to their higher operating temperatures, faster switching speeds, higher voltage breakdown capability, and lower conduction losses [2], [3]. The intrinsic device properties of silicon (Si, green), and WBG devices such as gallium nitride (GaN, purple) and silicon carbide (SiC, blue) are shown in Figure 1.

Figure 1: Intrinsic device properties of silicon (Si, Green), gallium nitride (GaN, Purple), and silicon carbide (SiC, Blue)

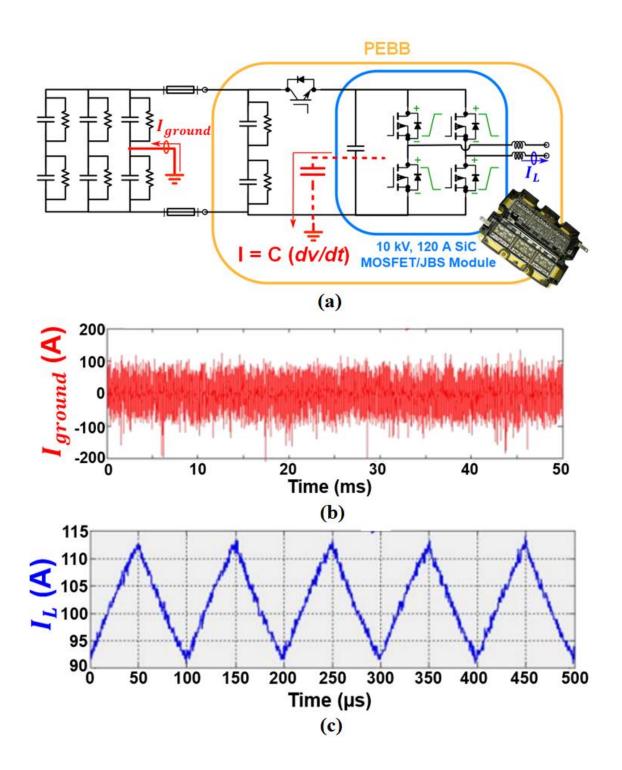

The higher voltage capability, higher operating temperatures, lower conduction losses, and faster switching speeds of WBG devices result in higher efficiency and power density designs; however, the higher operating frequency, and higher operating voltages also result in faster slew rates, which results in a larger electromagnetic interference (EMI) footprint of the system [4]–[9]. An example of an EMI issue limiting the performance of WBG devices can be found in [10], where a 10 kV, 120 A SiC MOSFET/JBS full bridge module [11] was run in a power electronic building block (PEBB) based impedance measurement unit (IMU) as shown in Figure 2(a). The converter could not be run at full voltage or rated power levels due to EMI issues. It can be seen in Figure 2(b) that the peak of the noise current flowing into the ground through the parasitic capacitance across the direct bonded copper (DBC) substrate in the power module was comparable to the current flowing through the inductor going to the output load (Figure 2(c)). The noise current contaminated the ground of the converter and was causing the controller to malfunction, limiting the operating conditions of the converter. It can therefore be concluded that properly addressing EMI issues is crucial to ensure that the advantages of WBG devices are not undermined. Since the noise current was flowing through the parasitic capacitance across the DBC substrate in the power module, it has therefore become necessary that EMI mitigation is considered in the initial design stages of the power modules.

In this work, the effect of the power module architecture on the common mode (CM) EMI generated by WBG devices is studied. The EMI emissions of a total of twelve different module architectures found in literature are explored, and different analysis techniques are used to explain and compare the EMI spectrum generated by each module.

Figure 2: (a) Circuit schematic of 10 kV, 120 A SiC MOSFET/JBS module in PEBB based IMU (b) ground current (c) inductor current from [10].

### **1.2 Literature Survey**

Over the past decade, research efforts have been concentrated on mitigating CM noise issues in WBG devices at various levels of the converter. Solutions such as CM chokes and EMI filters are often implemented at the input of the converter to minimize the amount of CM current flowing into the system [12]–[19]. In [20], a CM filter is integrated inside the module package. These solutions increase the weight and volume of the system and limit the efficiency and power density of the converters [12], [21]. For example, the addition of an EMI filter can occupy nearly one-third of the volume of the converter [22]. Other CM current solutions involve the use of active gate drivers to minimize issues related to CM current [23]. Slowing down the slew rates can reduce noise generated, but also increases switching losses [24]. Active gate drivers employ slew rate control to help achieve a balance between switching losses and EMI noise, but can increase the complexity of the circuitry and controls of the converters [23], [25]. Snubber circuits and ferrite beads can also be used to dampen voltage and current oscillation, which results in lower EMI [26]–[30].

Less work has been dedicated to studying and mitigating CM current at the power module packaging level. It should be noted that reducing the EMI generated at the packaging level will not eliminate the need for a filter, but would minimize the amount of noise that will need to be filtered at the converter level. With the rise of WBG devices, the layout and design of power modules have garnered attention due to the higher sensitivity of WBG devices to parasitic inductances and capacitances [31]–[33]. Since CM current is worsened by these parasitics, which are related to the power module design, EMI mitigation and containment solutions at the package level are being investigated [34].

When it comes to reducing CM noise inside the package, a large portion of the literature is focused on minimizing the power-loop and gate-loop inductances that lead to ringing during switching events. A popular way to reduce the impact of stray inductances is to integrate decoupling capacitors inside the module to reduce the commutation loop [35]. Other designers have attempted to reduce the dv/dt of the module by embedding gate resistors to slow down the fast switching transients [36] or embedding resistor-capacitor (RC) snubbers and ferrite beads to reduce voltage ringing during switching events [37]. These techniques help mitigate CM current by reducing the switching speed; this approach offsets the benefits offered by WBG devices.

Other studies have focused on the capacitive coupling to the baseplate to mitigate the flow of CM current. The literature has proposed mitigating CM current by reducing the capacitive coupling of the switching-node to the baseplate present in the power module [38]. In traditional power modules, an insulated substrate is patterned to form a half-bridge configuration, with the switching-node pad being a significant portion of the footprint. This switching-node pad has capacitive coupling across the substrate insulation to the baseplate, creating a critical path for CM current to flow through. This capacitive coupling can be reduced either by shrinking the footprint of the switching-node or increasing the thickness of the insulation dielectric [39]. Other techniques include removing regions of the insulated substrate's bottom copper layer and replacing it with low-permittivity material [40], and canceling the CM current through the baseplate of a singlephase inverter with the input and output impedances of the EMI testbed being made to be [41], [42]. This CM current cancellation is achieved by manipulating the ratio between the switchingnode capacitance and the equivalent baseplate capacitance. In addition, it has been shown that reducing the switching-node capacitance of the module and balancing the DC+ and DC- rail parasitics help reduce CM current by minimizing differential mode (DM) to CM conversion [43].

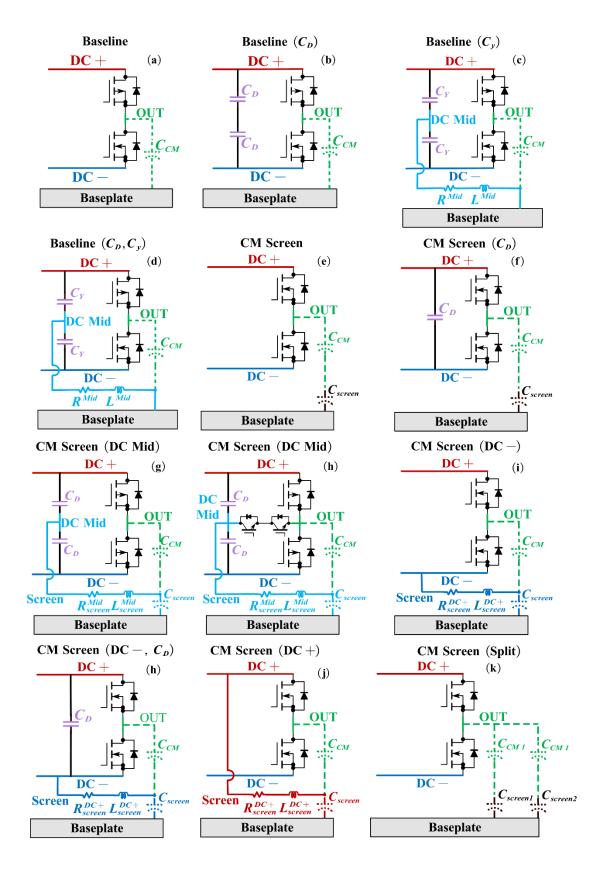

A review of the half bridge module architectures that have been used in literature to explore EMI mitigation at the module packaging level is now presented. In [44], the effect on the EMI performance of a GaN high-electron-mobility transistor (HEMTs) based half-bridge power module is studied with the integration of CM filter capacitors and decoupling capacitors — module architectures similar to Baseline ( $C_D$ ) (Figure 3(b)) and Baseline ( $C_V$ ) (Figure 3(c)). Compared to the Baseline architecture (Figure 3(a)), the integration of decoupling capacitors into the module results in mitigation in the CM noise generated in the 40 MHz to 100 MHz range. The integration of CM filter capacitors resulted in significant CM noise reduction in the conducted EMI frequency range. A Baseline  $(C_D, C_v)$  architecture (Figure 3(d)), module architecture obtained by combining Figure 3(b) and Figure 3(c), is eventually recommended. In [45], CM filtering capacitors are integrated directly into a SiC JFET based half-bridge power module, resulting in a module architecture similar to Baseline ( $C_{\nu}$ ) shown in Figure 3(c). The EMI performance of the module architecture is compared to a standard Baseline module (Figure 3(a)) by measuring the noise at the line impedance stabilization network (LISN). The highest peak in the EMI spectrum for the noise generated by the Baseline  $(C_y)$  architecture showed a mitigation of 10 dB compared to the highest peak in the EMI spectrum of the Baseline module. An average mitigation of 6 dB was measured compared to the Baseline module architecture between 100 kHz to 1MHz. In [46], the EMI performance of a configuration similar to the Baseline  $(C_D)$  module architecture (Figure 3(a)) is simulated in a IGBT based half bridge chopper circuit. For the Baseline  $(C_D)$  module, the value of decoupling capacitors is varied from 0 to 1 µF and effect on the CM noise generated is simulated. It was observed that the addition of the decoupling capacitors reduces the high frequency noise peaks in the CM noise frequency spectrum, but introduces an additional peak in the frequency spectrum at lower frequencies. CM filtering capacitors are then added across the module terminals,

along with the decoupling capacitors, and the EMI footprint of the converter is experimentally tested. Significant mitigation was seen in the CM noise beyond 3 MHz. A Baseline ( $C_D$ ,  $C_y$ ) (Figure 3(d)) architecture is recommended. In [47], Baseline ( $C_D$ ) and Baseline ( $C_y$ ) are proposed; however, the integration of capacitors is not discussed. Instead the paper proposes modifying the module geometry and using the parasitic capacitances inside the module to obtain a somewhat similar effect. The architectures are tested as a half bridge operating in a boost converter topology.

Module architectures in literature that use stacked substrates for a lower EMI footprint are now discussed. In [48], the EMI footprint of a SiC half-bridge power module switched in a boost converter configuration is measured with four different module architectures: Baseline (Figure 3(a)), CM Screen (Figure 3(e)), CM Screen ( $C_D$ ) (Figure 3(f)) and CM Screen (DC Mid) (Figure 3(g)). The EMI footprints of these four module architectures is compared and the CM Screen (DC Mid) architecture is concluded to have the lowest CM EMI in the conducted EMI frequency range — a mitigation of more than 15 dB over a wide frequency range. Although experimental results are provided, analysis of the noise reduction and frequency spectrum for each module architecture is not provided. In [47], the CM Screen (Figure 3(e)) and CM Screen ( $C_D$ ) (Figure 3(f)) architectures are proposed and tested with half-bridge power modules operating in a boost converter topology. The integration of decoupling capacitors into the architecture for the CM Screen  $(C_D)$  is not discussed; however, a somewhat similar effect is achieved by modifying the geometry to take advantage of the module's parasitic capacitances. In [49], the EMI performance of a CM Screen (Figure 3(e)) and a CM Screen (DC Mid) (Figure 3(g)) architecture is compared in the time domain. The largest peak of the noise generated by the CM Screen (DC Mid) module architecture was measured to be ten times lower than the largest peak for the CM Screen module architecture. Little analysis on the mitigation seen is provided. In [50], the EMI performance of a

stacked substrate module architecture for a T-Type NPC power module (Figure 3(h)), made using a hybrid combination of SiC MOSFETs and Si IGBTs, is compared to a baseline single substrate T-Type NPC module architecture. The stacked substrate introduced into the module architecture is intended to act as an EMI shield and is connected to a fixed potential formed by the series connection of decoupling capacitors — a configuration reminiscent of CM Screen (DC Mid) (Figure 3(g)) from an EMI point of view. Experimental results showed a mitigation of up to 21 dB. Although analysis of the EMI results is presented, the analysis is done for a T-Type NPC power module and insights gained are not easily applicable to a half bridge module. In [51], a stacked substrate for half bridge applications is proposed with a CM Screen (DC-) (Figure 3(i)) and CM Screen (DC+) (Figure 3(j)) architecture. No EMI analysis of the architectures is presented. In [52] and [53], a stacked substrate half-bridge power module with a CM Screen (DC-,  $C_D$ ) architecture (Figure 3(h)) is presented and the EMI performance is compared to a commercially available module with similar specifications. Experimental results showed an average mitigation of up to 14 dB and 25 dB in the noise voltage measured at the LISN, respectively. In [54], local shielding solutions to reduce CM current at the input of a GaN HEMT based half-bridge inverter leg are proposed and attenuation in the CM noise spectra is observed. An architecture similar to the CM Screen (DC+) (Figure 3(j)) architecture is explored. Shielding is also applied to the gate driver and between the thermal pad and the heatsink. A total noise reduction of up to 17 dB was observed. In [37], [40], [55] the CM screen / baseplate in the module architecture was split. All portions of the split CM screen were left floating. This technique can be used to obtain module architectures similar to Figure 3(k).

Figure 3: Module architectures explored in literature

## **Chapter 2: Introduction to Module Architectures**

#### 2.1 Introduction

This chapter introduces the twelve module architectures whose EMI footprint would be explored in this thesis. The hardware implementation of four of the module architectures is presented. The hypothetical designs that could be used to implement the remaining eight module architectures is also presented.

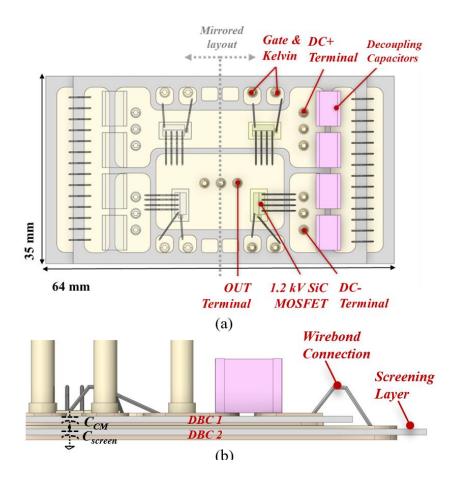

## 2.2 Module Layout

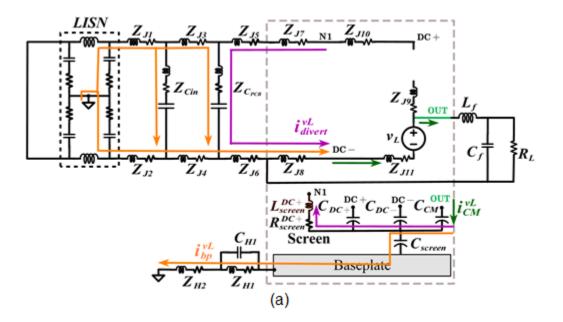

To study the impact of the CM screen, a new module design was developed. The design allows for testing the CM screen under different design conditions and provides insight into the effectiveness of containing CM current within the module. Figure 4(a) shows the topside view of the layout where 1.2 kV, 40 m $\Omega$  SiC MOSFETs are used in the half-bridge module. The DC+, DC– and OUT terminal placements are kept consistent between module variations, while allowing the flexibility to connect the screen to different DC nodes.

A side view of the CM screen module is shown in Figure 4(b). The module uses two 0.35mm-thick alumina DBC substrates stacked together to create the screening layer. Wire bonds are used to electrically connect the top copper layer to the screening layer. This layout enables paralleling of many wire bonds to reduce the impedance to the screening layer.

In the literature, the CM screen is not only used to contain CM current, but also as a path for the commutation loop [52]. This enables a reduction in the power-loop inductance through magnetic field cancellation, which enables cleaner switching events that reduce EMI [52]. To avoid variations in the EMI due to changes in the power-loop inductances, all of the proposed modules have the commutation loop on the top side of DBC 1 (Figure 4(b)). This allows for the screening layer to be used only to divert CM current and not to serve as part of commutation loop. This enables modification of the screening layer while keeping the power loop inductance consistent between a baseline and CM screen design. ANSYS Q3D simulations show that the power-loop inductance with and without the decoupling capacitors inside the module is 3.5 nH at 100 MHz, respectively.

The switching-node capacitance across DBC 1 to the screening layer is denoted as  $C_{CM}$ . The screening layer capacitance across DBC 2 to the baseplate is denoted as  $C_{screen}$ . Furthermore,  $C_{CM}$  is 80.2 pF, and  $C_{screen}$  is 436.9 pF for all the module variations. The module design also allows for two paralleled 10 nF decoupling capacitors to be placed in series to minimize the power-loop inductance and form the DC Mid node.

Figure 4: (a) Top view, and (b) side view of common-mode screen module.

## 2.3 Module Variations Fabricated

The amount of CM current that will be diverted to the DC–bus depends on the highfrequency impedance of the screening layer. For the CM screen to be effective, condition (1) has to be satisfied [48]:

$$Z_{screen} \ll Z_{bp} \tag{1}$$

where  $Z_{screen}$  is the impedance of the CM screen to the desired DC node and  $Z_{bp}$  is the impedance from the CM screen to the module baseplate. For the case of the CM screen (DC+) and (DC Mid) module in Figure 5(c) and (d),  $Z_{screen}$  can be respectively written as:

$$Z_{screen}^{DC+} = j\omega L_{screen}^{DC+} + R_{screen}^{DC+}$$

<sup>(2)</sup>

$$Z_{screen}^{Mid} = j\omega L_{screen}^{Mid} + R_{screen}^{Mid} + Z_{C_p}$$

(3)

where  $L_{screen}^{DC+}$ ,  $R_{screen}^{DC+}$  and  $L_{screen}^{Mid}$ ,  $R_{screen}^{Mid}$  are the equivalent inductance and resistance of the wire bonds connecting the screening layer to DC+ and DC Mid nodes, respectively; and  $Z_{C_D}$ is the impedance of the decoupling capacitors. For Figure 5(d),  $Z_{C_D}$  will be defined as:

$$Z_{C_D} = \frac{1}{j\omega C_D} \tag{4}$$

where  $C_D$  is the equivalent capacitance of the decoupling capacitors between the DC Mid and DC+ or DC- nodes respectively.

In both architectures, the impedance to the baseplate can be given as:

$$Z_{bp} = \frac{1}{j\omega C_{screen}} \tag{5}$$

where  $C_{screen}$  is the screening-layer capacitance across DBC 2 to the baseplate of the module. Using (2), (3), and (5), the inequality of (1) for the two CM screen modules becomes:

$$j\omega L_{screen}^{DC+} + R_{screen}^{DC+} \ll \frac{1}{j\omega C_{screen}}$$

(6)

$$j\omega L_{screen}^{Mid} + R_{screen}^{Mid} + Z_{C_D} \ll \frac{1}{j\omega C_{screen}}$$

(7)

where  $Z_{C_D}$  is defined according to equation (4). It can be seen from (6) and (7) that it is critical to reduce the parasitic inductance and resistance of the CM screen to be effective in redirecting the CM current to its connected DC node. For the case of the CM screen (DC Mid) module, the decoupling capacitor  $C_D$  (20 nF) was selected to be greater than 50 times  $C_{screen}$  (436.9 pF) to better divert the CM current from flowing towards the baseplate of the module to the DC Mid node [56]. It should be noted that integrating the decoupling capacitors  $C_D$  into the module increases the footprint of DBC 2 and the value of  $C_{screen}$ . For this work, compact ceramic capacitors with high capacitance values were selected to balance the trade-offs between  $C_{screen}$  and  $C_D$ . Furthermore, the capacitors are COG type, which means they are stable with variations in temperature and voltage. This allows the CM screen to have the same effectiveness under different voltage and temperature profiles.

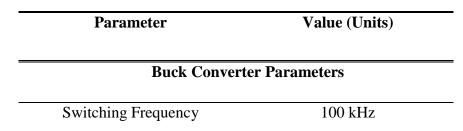

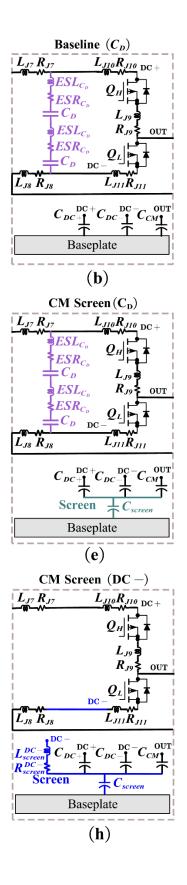

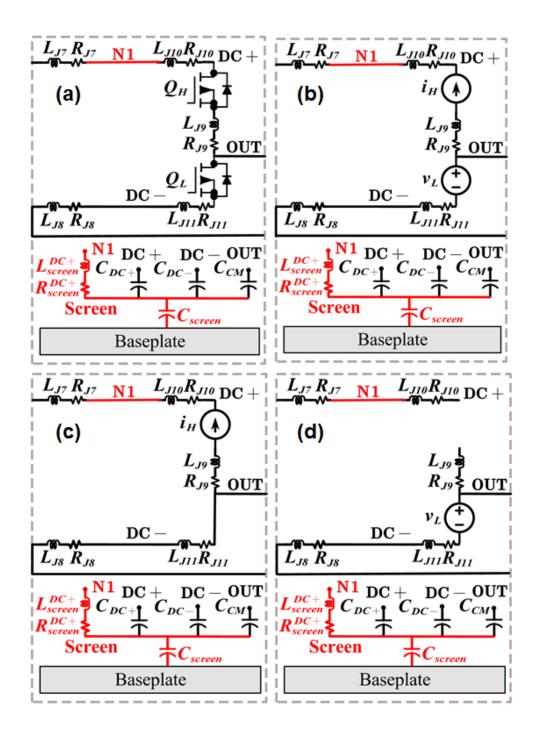

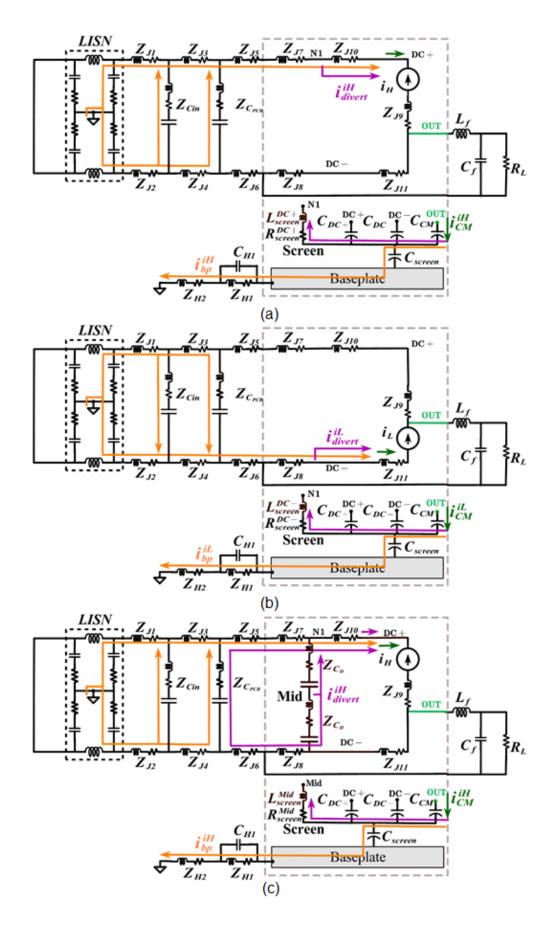

With the module design established, four design variations (shown in Figure 5) were developed to study the impact of the module architecture on CM noise reduction. The variations are:

• **Baseline Module:** This variation only uses DBC 1. The OUT node is coupled to the baseplate through the switching-node capacitance  $C_{CM}$  (Figure 5(a)).

• **Baseline**  $(C_D)$  **Module:** This variation is the same as the baseline design but with the addition of integrated decoupling capacitors (Figure 5(b)).

• *CM Screen (DC+) Module:* DBC 1 and DBC 2 form a screening layer connected to the DC+ node. The DC+ node is coupled to the baseplate through  $C_{screen}$  (Figure 5(c)). There are no integrated decoupling capacitors in this module. The architecture also serves as the CM screen counterpart to the Baseline module.

• *CM Screen (DC Mid) Module:* Two series decoupling capacitors are included to create the midpoint DC Mid. DBC 1 and DBC 2 form a screening layer connected to the DC Mid node. The DC Mid is coupled to the baseplate through  $C_{screen}$  (Figure 5(d)). This architecture is the CM screen counterpart to the Baseline ( $C_D$ ) module.

In Figure 5, the high-side and low-side SiC MOSFET dies in the half-bridge schematic are referred to as  $Q_H$  and  $Q_L$ , respectively. The final module prototypes are shown in Figure 6. Testing

these modules will provide a better understanding of the EMI mitigation associated with redirecting the CM current to different parts of the DC-bus.

Figure 5: Variation of the module (a) Baseline module with no common-mode (CM) screen (b) Baseline module with no CM screen but with decoupling capacitors, (c) CM screen module with screening layer connected to DC+, and (d) CM screen module with screening layer connected to DC Mid.

Figure 6: Images of the fabricated CM screen module prototypes.

### 2.4 Module Variations Simulated

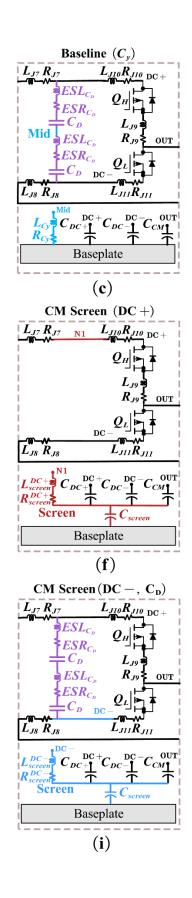

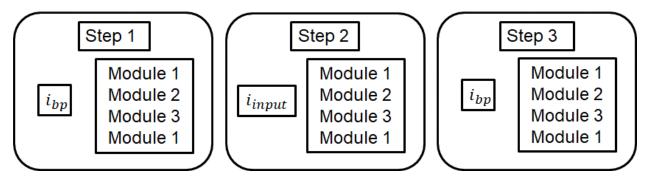

In addition to the four module architectures studied experimentally, eight additional module architectures were simulated to evaluate and understand EMI mitigation using packaging techniques in more detail. The eight module architectures studied are shown in Figure 7. It should be noted that all eight architectures can be fabricated through packaging techniques; however, they were not made due to time limitations.

• **Baseline**  $(C_y)$  **Module:** This variation is the same as the Baseline  $(C_D)$  design, but the Mid node formed by the addition of integrated decoupling capacitors is shorted to the baseplate (Figure 7(a) and Figure 8(a)).

• *CM Screen Module:* DBC 1 and DBC 2 are stacked together to form a screening layer; however, the screening layer is not connected to the any node and left floating. The

architecture serves to show only the effect of stacked substrates on the generated EMI (Figure 7(b) and Figure 8(b)).

• *CM Screen* ( $C_D$ ) *Module:* This variation is the same as the CM Screen design, but with the addition of integrated decoupling capacitors (Figure 7(c) and Figure 8(c)).

• *CM Screen (DC+, C<sub>D</sub>) Module:* This variation is the same as the CM Screen (DC+) design but with the addition of integrated decoupling capacitors (Figure 7(d) and Figure 8(d)).

• *CM Screen (DC-) Module:* DBC 1 and DBC 2 form a screening layer connected to the DC- node. The DC- node is coupled to the baseplate through *C<sub>screen</sub>* (Figure 7(e) and Figure 8(e)). There are no integrated decoupling capacitors in this module.

• *CM Screen (DC-, C<sub>D</sub>) Module:* This variation is the same as CM Screen (DC-) design but with the addition of integrated decoupling capacitors (Figure 7(f) and Figure 8(f) or Figure 9(a)).

• *CM Screen (DC+, DC-) Module:* DBC 1 and DBC 2 form a screening layer that is split similar to what is shown in Figure 3(k). One half is connected to the DC+ node and the other half is connected to DC- node. The screening layer is split such that the OUT node has a capacitive coupling to each pad of the screening layer equal to half of capacitance  $C_{CM}$ , and the capacitive coupling each pad of the screening layer has to the baseplate is equal to half of the capacitance  $C_{screen}$ . There are no integrated decoupling capacitors in this module (Figure 7(g) and Figure 8(g)).

• *CM Screen (DC+, DC-, C<sub>D</sub>) Module:* This variation is the same as CM Screen (DC-) design, but with the addition of integrated decoupling capacitors (Figure 7(h) and Figure 8(h) or Figure 9(b)).

18

In Figure 7, the high-side and low-side SiC MOSFET dies in the half-bridge schematic are referred to as  $Q_H$  and  $Q_L$ , respectively. Simulating the EMI behavior of these eight module architectures along with the four previously described will provide a better understanding of the EMI mitigation option available at the packaging level. Figure 8 shows hypothetical module layouts for the architectures shown in Figure 7. It should be noted that in Figure 8(f) and (h), the midpoint node has been removed as it was not needed. However, if needed inside the module vias can be used as shown in Figure 9.

Figure 7: Eight additional module architectures studied through simulation

Figure 8: Hypothetical module layouts for the eight additional module architectures

Figure 9: Hypothetical module layouts for (a CM Screen (DC-,  $C_D$ ) and (b) CM Screen (DC+, DC-,  $C_D$ ) with vias to ensue DC Mid node inside module

# **Chapter 3: Experimental Test Setup and Results**

## 3.1 Introduction

The chapter introduces the test setup that was used for experimenting the four implemented module architectures. EMI noise results at the baseplate and the input of the converter with the four implemented module architectures are also presented. The chapter concludes with a preliminary slew rate and efficiency analysis that was done for these four implemented module architectures.

## 3.2 Test Setup

A test setup was developed to evaluate the level of noise mitigation introduced by each of the module architectures. Experimental results are only obtained for the modules introduced in Section 2.3. The designed testbed switches each module as a buck converter operating at a switching frequency of 100 kHz. All experiments are conducted at an input/output voltage of 600/300 V. The setup is comprised of four main subsystems: LISN, input capacitor  $C_{in}$ , power module, and output load. Figure 10 shows the simplified schematic of the setup and outlines the aforementioned subsystems. Details of the various components used in each subsystem have been provided in Table 1. Figure 10 also highlights the measurements recorded for analysis: drain-tosource voltage  $v_{DS}$  for the high-side switch  $Q_H$ , voltage across output load  $V_{out}$ , voltage across input capacitor bank  $V_{in}$ , current flowing at input of converter  $i_{in}$ , noise current that escapes through the module baseplate into the converter  $i_{bp}$ , and CM noise current at the input of the converter  $i_{input}$ . The noise  $i_{bp}$  and  $i_{input}$  is measured for all four module architectures using the same test setup and testing conditions with only the modules swapped. The results presented were consistent and repeatable using the test setup described. The noise current  $i_{bp}$  was measured to experimentally quantify the noise generated by the module that escapes through the baseplate into the converter. It was measured using the method described in [38]. To measure  $i_{bp}$ , the module baseplate is clamped onto a heatsink that is physically separated from the copper sheet with the help of non-conductive separators. Current flowing through a conducting wire connecting the heatsink and copper sheet is then measured. The noise current  $i_{input}$  is measured to empirically verify the effect of changing the module architecture on the noise flowing at the input of the converter. The noise current  $i_{input}$  is measured with a high frequency current transformer (HFCT) clamped around the input terminals of the converter.

Figure 10: Simplified schematic of EMI test setup for the buck converter.

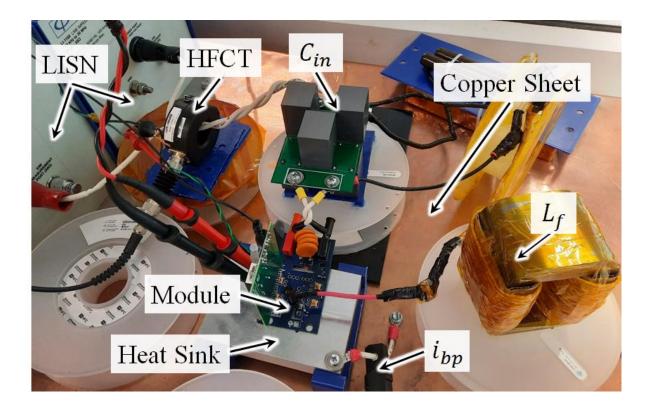

**Table 1: Summary of Setup Specifications**

#### $V_{in}$ / $V_{out}$

| Test Setup Parameters                                       |                                     |  |  |  |

|-------------------------------------------------------------|-------------------------------------|--|--|--|

| LISN                                                        | LISN LI-1100C                       |  |  |  |

| C <sub>in</sub>                                             | 90 µF                               |  |  |  |

| $C_f$                                                       | 100 µF                              |  |  |  |

| $L_f$                                                       | 750 µF                              |  |  |  |

| $R_L$                                                       | 22 Ω                                |  |  |  |

| Measurement Probes                                          |                                     |  |  |  |

| $i_{in}, i_{bp}$                                            | Tektronix TCP0030A, 120 MHz         |  |  |  |

| i <sub>input</sub>                                          | input ETS-Lindgren 91550–1, 100 MHz |  |  |  |

| $v_{DS}$ , $V_{in}$ and $V_{out}$ Tektronix THDP0200, 200 M |                                     |  |  |  |

The testbed was operated at room temperature and all measurements reported were recorded during the electrical steady state. Details of the measurement probes used are provided in Table 1. The analysis in this work is limited to the conducted EMI frequency range (150 kHz to 30 MHz). The measurement probes used were confirmed to have a bandwidth that would allow accurate measurement in the frequency range mentioned. The hardware implementation of the testbed is shown in Figure 11. The copper sheet used in the test setup is connected to earth potential. The time domain measurements for baseplate noise current  $i_{bp}$  and input noise current  $i_{input}$  were recorded using a rectangular time window of 400 µs, and a sampling frequency of 1.5625 GS/s. The analysis presented is limited to the conducted EMI frequency range, i.e. 150 kHz to 30 MHz.

Figure 11: Hardware setup of EMI testbed for buck converter.

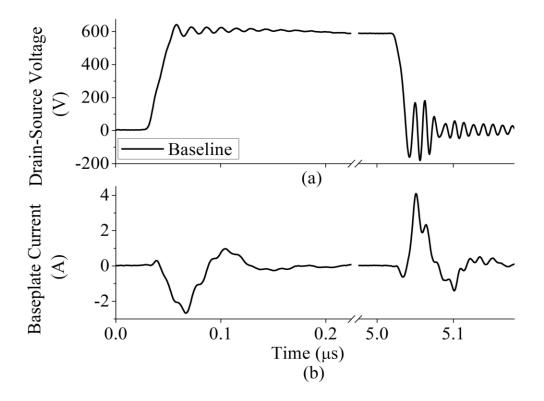

## **3.3** Time Domain Measurement

The relationship between voltage  $v_{DS}$ , switching-node capacitance  $C_{CM}$ , and generated noise current  $i_{bp}$  is explained using the Baseline module architecture shown in Figure 5(a). Figure 12(a) shows the zoomed-in time domain waveform for voltage  $v_{DS}$ , and Figure 12(b) shows the noise current  $i_{bp}$  being generated at the same instance in time. In the experiments performed, the direction of current is taken as positive if the current is flowing from the heat sink toward the copper sheet, and is taken as negative if it is flowing in the reverse direction.

From Figure 12(a), during the turn-off transient  $v_{DS}$  increases to 600 V at a slew rate of 25.6 V/ns. During this event, the change in potential at the OUT terminal discharges parasitic capacitor  $C_{CM}$ , causing the current to flow from the module baseplate to the switching-node. During the

voltage transition, a CM current flows from the copper sheet to the OUT terminal, resulting in the discharging of  $C_{CM}$  (Figure 12(b)). A negative peak of 2.7 A is observed.

During the turn-on transient  $v_{DS}$  falls from 600 V to 0 V at a slew rate of 39.3 V/ns. During this event, the change in potential at the OUT terminal charges parasitic capacitor  $C_{CM}$ , causing current to flow from the switching-node to the copper sheet. A positive current peak of 4.1 A is seen during the falling  $v_{DS}$  transient in Figure 12. The different current peaks during the rising and falling transitions occur due to different rising and falling slew rates. The turn on transient has a higher dv/dt, and hence a larger CM current through the baseplate.

Figure 12: Zoomed-in time domain waveforms for the Baseline module architecture showing (a) high-side SiC MOSFET  $Q_H$  drain-source voltage  $v_{DS}$  and (b) noise current  $i_{bp}$ .

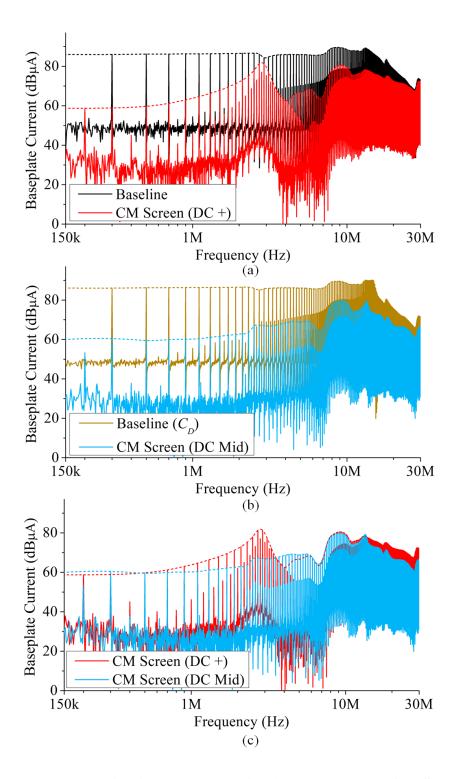

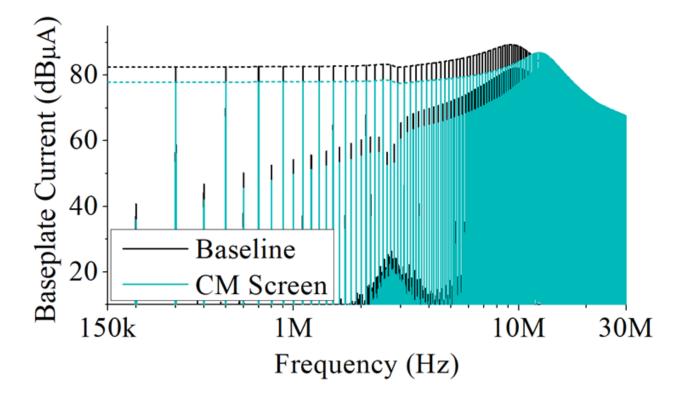

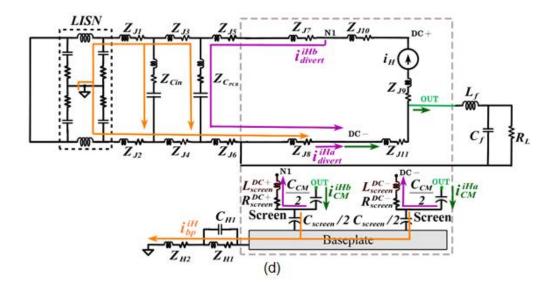

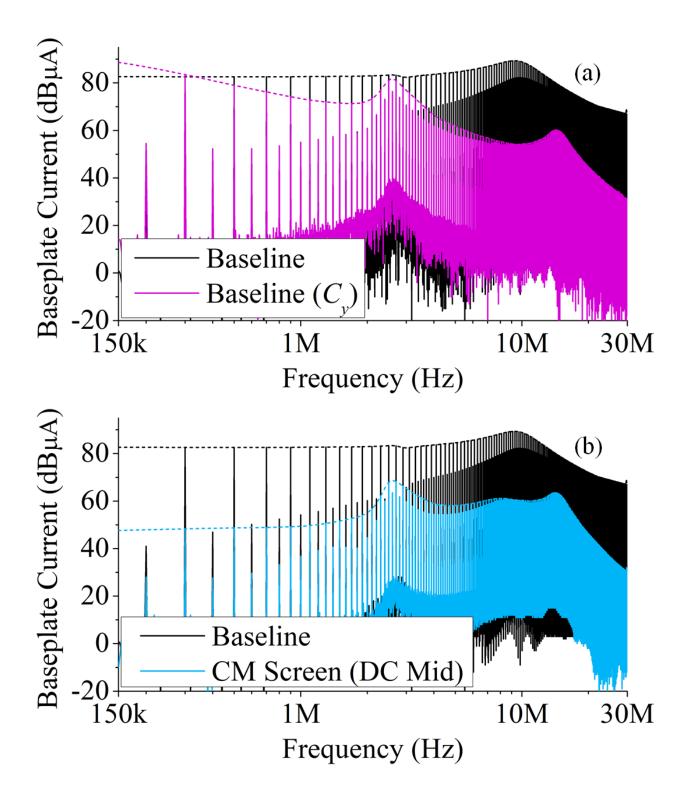

## 3.4 Baseplate Noise Current

The frequency spectra of the noise current  $i_{bp}$  for different module architectures are shown in Figure 13. In Figure 13(a) and (b), the two baseline modules are compared to their CM screen counterpart to observe how integrating a CM screen into the module affects the noise generated at the baseplate. The results confirm that the introduction of the CM screen into the architecture caused noise to be redirected to the respective connected DC node. In both scenarios, a maximum noise reduction of 26 dB is noted, due to the redirection of a portion of noise  $i_{bp}$  to the connected DC node. A minimum noise reduction of 21 dB and 26 dB is noted in the 150 kHz – 1.1 MHz frequency range for the Figure 13(a) and Figure 13(b) module, respectively.

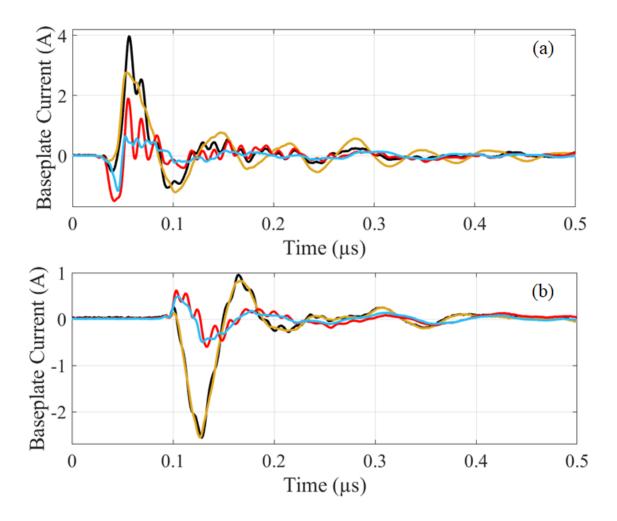

In Figure 13(c), the  $i_{bp}$  generated by the two CM screen architectures is compared. Results show a maximum mitigation of 13 dB. No significant noise reduction is noted in the 150 kHz to 1.1 MHz frequency range. The mitigation observed can be attributed to the symmetric decoupling capacitances between the DC+ and DC– nodes and the screening layer [43], [57], [58]. This is discussed in more detail later in this thesis. The mitigation seen at frequencies larger than 10 MHz can be linked to the smaller current commutation loop, due to the integrated decoupling capacitors. As previously stated, the power-loop inductance inside the module will reduce from 7.5 nH to 3.5 nH, due to the addition of decoupling capacitors. The measured time domain waveforms for the baseplate noise current of the four module architectures is shown in Figure 14.

Figure 13: Frequency spectra of noise current  $i_{bp}$  for (a) Baseline and CM Screen (DC+) module, (b) Baseline ( $C_D$ ) and CM Screen (DC Mid) module, and (c) the CM Screen (DC+) and CM Screen (DC Mid) module.

Figure 14: Time domain waveform for  $i_{bp}$  during device (a) turn-on and (b) turn-off for module architecture: Baseline (Black), Baseline ( $C_D$ ) (Brown), CM Screen (DC+) (Red), and CM Screen (DC Mid) (Light Blue).

## 3.5 Input Noise Current

Similar to the comparison done for  $i_{bp}$ , the effect of module architecture on the noise current  $i_{input}$  is also investigated. A maximum noise mitigation of 17 dB and 26 dB is observed between the Baseline and CM Screen (DC+) module (Figure 15(a)), and the Baseline ( $C_D$ ) and CM Screen (DC Mid) module (Figure 15(b)), respectively. A minimum noise reduction of 10 dB is noted in the 150 kHz – 1.1 MHz frequency range for both the comparisons. Larger mitigation is seen in the Baseline ( $C_D$ ) module and its CM screen counterpart at frequencies greater than 10 MHz.

In Figure 15(c),  $i_{input}$  generated by the two CM screen architectures is compared. A maximum mitigation of 18 dB is observed. No significant noise reduction is noted in the 150 kHz - 1.1 MHzfrequency range. It is important to note that the noise mitigation seen in  $i_{input}$  is different from the mitigation seen in  $i_{bp}$ , and that  $i_{input}$  has slightly larger magnitudes in the frequency spectrum compared to  $i_{bp}$ . The noise current  $i_{bp}$  is the noise generated by the module that escapes though the baseplate into the converter and — with the module being the major source of noise generated — is responsible for a significant portion of  $i_{input}$ , but not all of it. In particular, noise current  $i_{input}$  also incorporates the effect of CM noise generated due to unbalanced impedances inside the converter. Detail on the impact of asymmetries in a buck converter on CM noise generated can be found in [59]. Another example of CM noise that the noise current  $i_{input}$  incorporates is the noise flowing through parasitic capacitances outside the module that the converter may have to the copper sheet. The time domain waveform for  $i_{input}$  could not be included due to the limitations of the measurement probe used to measure the CM noise at the input of the converter. The high frequency current transformer (ETS-Lindgren 91550-1, 100 MHz) used to measure the noise  $i_{input}$  does not output the actual current waveform. Post-processing has to be done in frequency domain — as detailed in the documentation of the probe — before the actual frequency spectrum of  $i_{input}$  can be observed.

Figure 15: Frequency spectra of noise current  $i_{input}$  for (a) Baseline and CM Screen (DC+) module, (b) the Baseline ( $C_D$ ) and CM Screen (DC Mid) module, and (c) CM Screen (DC+) and CM Screen (DC Mid) module.

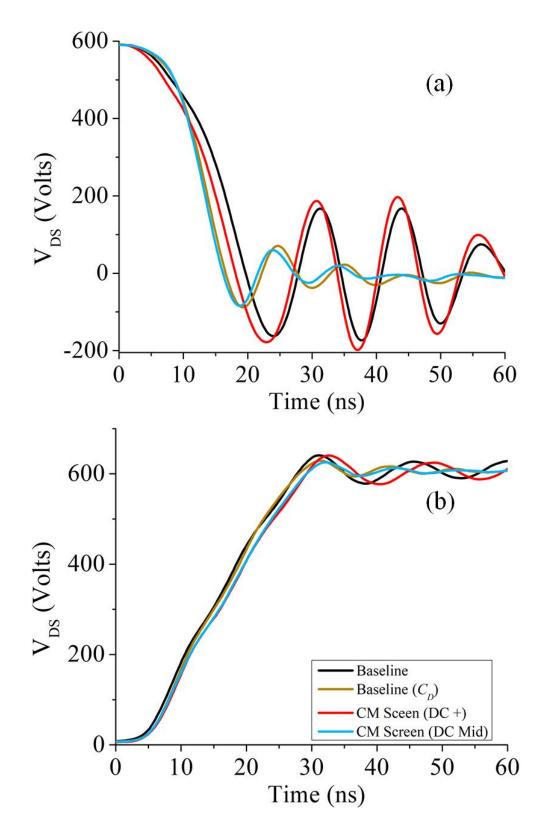

## **3.6** Preliminary Efficiency and Switching Results

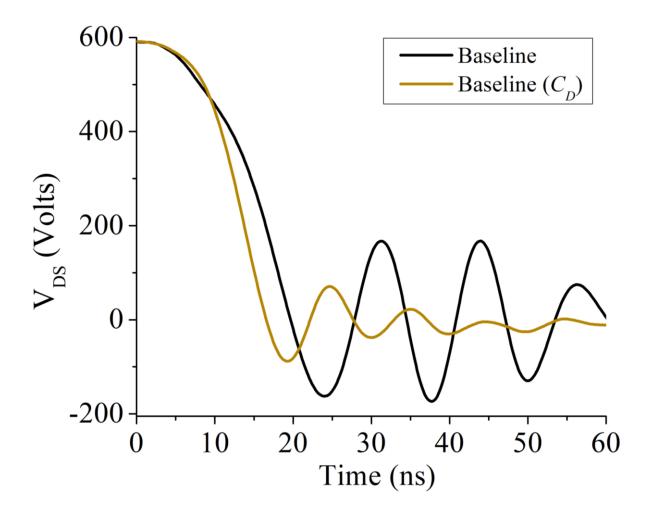

The impact of the CM screen architectures on converter efficiency and device slew rates was also investigated. The slew rates for the modules were measured across the drain-to-source voltage  $v_{DS}$  for MOSFET  $Q_H$ . The efficiency and slew rate measurements were made using a rectangular time window of 800 µs, with a sampling frequency of 6.25 GS/s. The output from the measurement probes  $i_{in}$  and  $V_{in}/V_{out}$  were measured using probes of bandwidth 20 MHz and 5 MHz, respectively. The efficiency measurements were made a total of five times and the median value is reported in the analysis. The slew rates were measured using probes of bandwidth 250 MHz. Table 2 lists the converter efficiencies and slew rates for each module variation. The efficiencies are reported as a percentage increase and decrease, while keeping the Baseline module as a reference. Comparing the efficiency of the Baseline module to the CM Screen (DC+) module, a decrease of 0.3 % is seen. This decrease in efficiency can be attributed to the increased  $C_{oss}$  of the module. Having the CM screen shorted with the DC+ node results in  $C_{CM}$  being in parallel with the  $C_{oss}$  of the SiC die, thereby increasing the output capacitance of the high-side switch.

Compared to the Baseline module, the Baseline ( $C_D$ ) and CM Screen (DC Mid) show an increase in efficiency. This increase can be explained by investigating the trends observed in the slew rates in Table 2. The Baseline ( $C_D$ ) module shows a 47% larger falling slew rate. This increased slew rate can be attributed to the reduced current commutation loop that occurs due to the addition of the decoupling capacitors. Similarly, the CM Screen (DC Mid) module demonstrates a 59% faster falling slew rate. The shorter turn-on time results in lower switching losses and, therefore, an increase in the overall efficiency of the converter. The rising and falling edges for the module architectures are showing in Figure 16.

|                        | ~ ~ ~ ~                                          | Slew Rate (V/ns) |         |

|------------------------|--------------------------------------------------|------------------|---------|

| Module<br>Architecture | Converter Efficiency<br>w.r.t Baseline<br>Module | Rising           | Falling |

| Baseline               | N.A.                                             | 25.6             | 39.3    |

| Baseline $(C_D)$       | 0.2% increase                                    | 27.1             | 57.9    |

| CM Screen (DC+)        | 0.3% decrease                                    | 24.9             | 41.4    |

| CM Screen (DC Mid)     | 0.5% increase                                    | 25.3             | 62.3    |

## Table 2: Switching Characteristics and Efficiency

Figure 16: Switching Characteristics (a) Falling Edge (b) Rising Edge

# **Chapter 4: Simulation and Modeling Techniques**

## 4.1 Introduction

The chapter introduces the simulation and modeling techniques that can be used to explain the EMI results discussed in the previous chapter. The simulation and modeling techniques that were primarily chosen are the: time domain simulation, CM equivalent modeling, and substitution and superposition theorem.

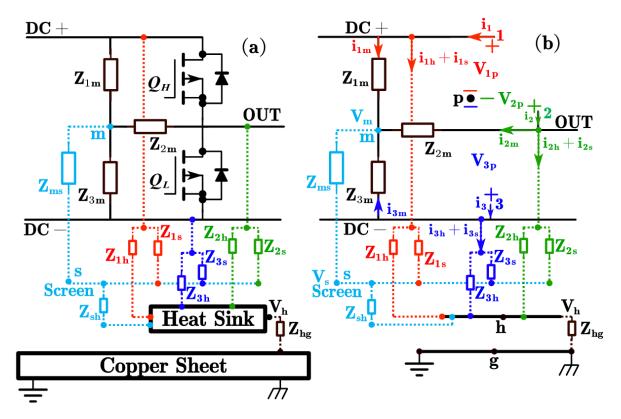

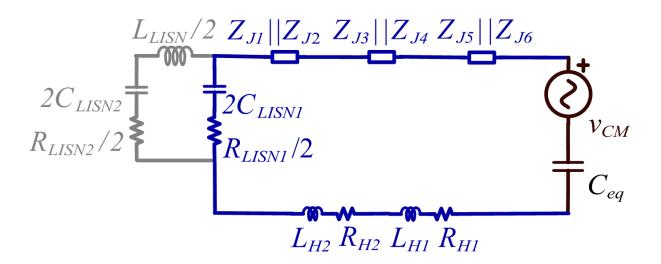

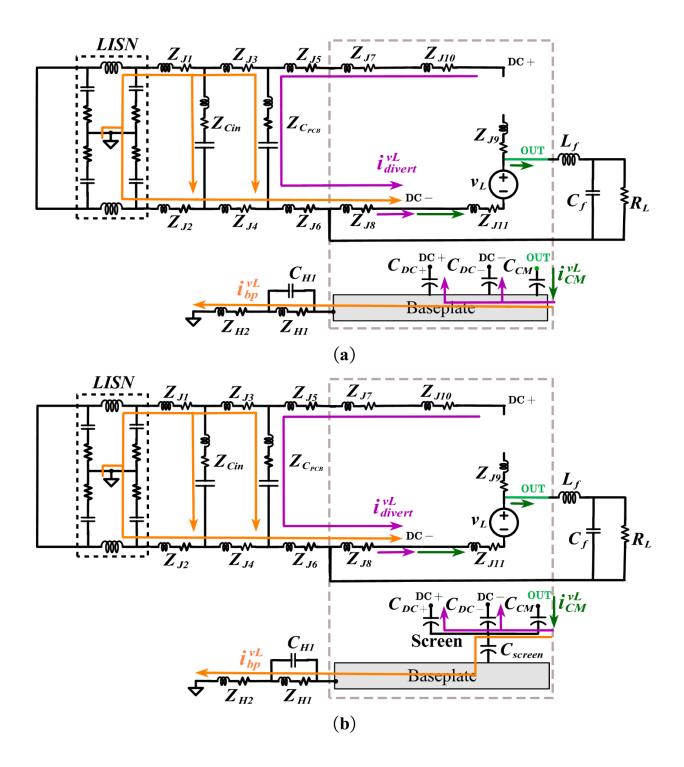

## 4.2 Time Domain Simulation

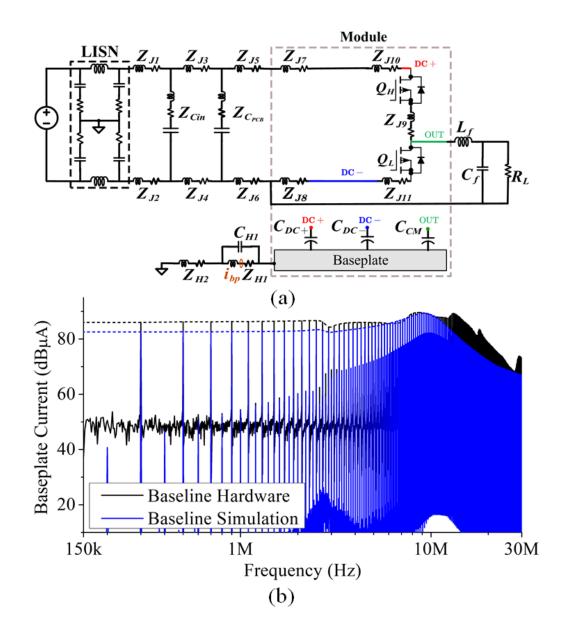

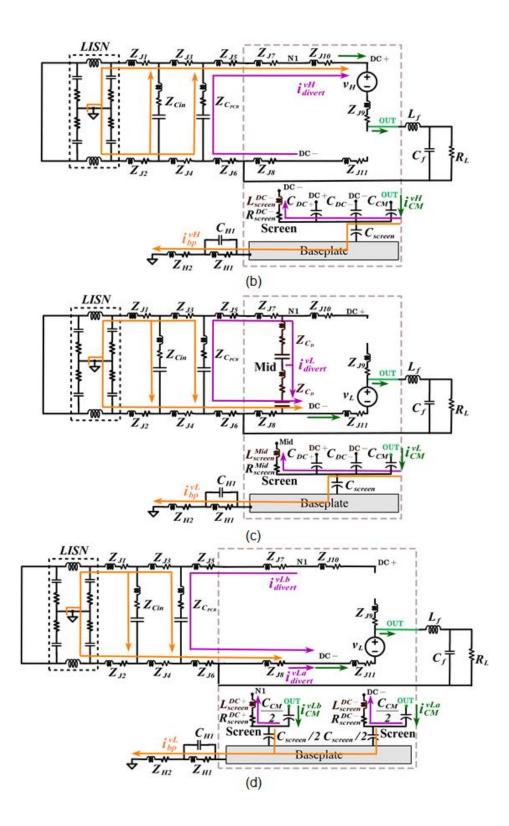

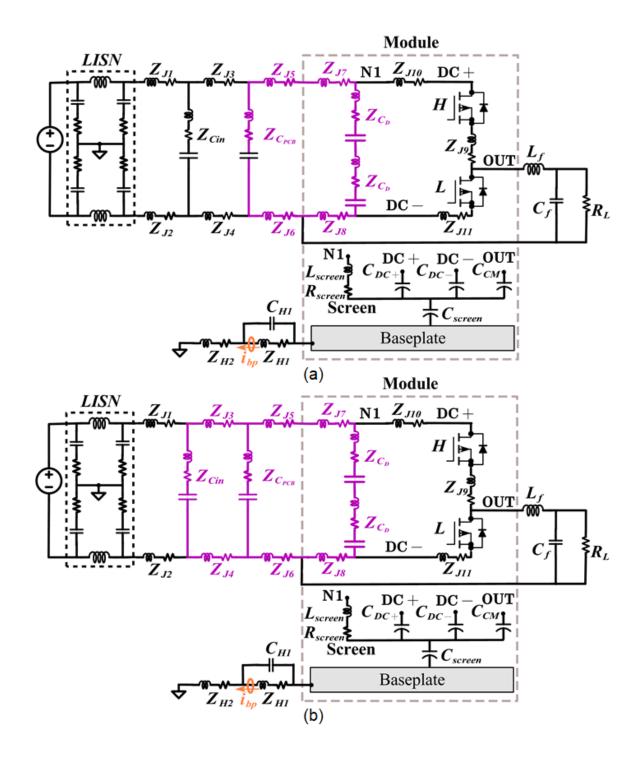

Based on the hardware results presented in Figure 13, a simulation model was created for the test setup. Figure 17(a) shows the simulation model with the Baseline module. In Figure 17(a),  $Z_{Cin}$  and  $Z_{C_{PCB}}$  are the total impedances of the input capacitor bank  $C_{in}$  and the decoupling capacitors  $C_{PCB}$ , installed on the PCB board used to interface the module with the rest of the converter. The impedances  $Z_{Cin}$  and  $Z_{C_{PCB}}$  incorporate the equivalent series inductance (ESL) and equivalent series resistance (ESR) of the capacitors. The impedances  $Z_{Jx}$  where  $x = \{1 - 6\}$ represent the parasitic impedances of the wires connecting the LISN to  $Z_{Cin}$ ,  $Z_{Cin}$  to  $Z_{C_{PCB}}$ , and of the PCB interfacing  $Z_{C_{PCB}}$  to the module architecture.

The impedances  $Z_{H1}$  and  $Z_{H2}$  are the parasitic impedances of the wire connecting the heat sink to the copper sheet, and of the copper sheet used in the EMI test setup. The capacitance  $C_{H1}$ is the parasitic capacitance between the heat sink raised through non-conductive separators and the copper sheet. Estimates of these impedances were obtained using the methodology detailed in [60] with an Agilent 4294A precision impedance analyzer. The simulated noise current  $i_{bp}$  is the current flowing through the impedance  $Z_{H1}$ . The impedances  $Z_{Iy}$  where  $y = \{7 - 11\}$  model the parasitic inductances and resistances inside the module. Capacitances  $C_{DC+}$ ,  $C_{DC-}$ , and  $C_{CM}$  are the parasitic capacitances the DC+, DC–, and OUT terminal (Figure 4) have to the baseplate from across the DBC substrate. Estimates of the values of  $Z_{Jy}$  were extracted using ANSYS Q3D, whereas  $C_{DC+}$ ,  $C_{DC-}$ , and  $C_{CM}$  were measured with the impedance analyzer. The SiC device LTspice model provided by the manufacturer was used for the simulation. The values used for these parameters are shown in Table 3. It should also be noted that the impedances  $Z_{Jx}$  (where  $x \in$ 1,2,3 ..., shown in Figure 17(a)) relate to the resistances  $R_{Jx}$  and inductances  $L_{Jx}$  (shown in Table 5) according to:

$$Z_{Jx} = R_{Jx} + j\omega L_{Jx} \tag{8}$$

The impedances  $Z_{Cin}$  and  $Z_{CPCB}$  (shown in Figure 17(a)) relate to the parameters shown in Table 3 according to:

$$Z_{Cin} = ESR_{C_{in}} + j\omega ESL_{C_{in}} + \frac{1}{j\omega C_{in}}$$

(9)

$$Z_{C_{PCB}} = ESR_{PCB} + j\omega ESL_{PCB} + \frac{1}{j\omega C_{PCB}}$$

(10)

Figure 17: (a) Simulation model of test setup with the Baseline module architecture (b) Comparison of the hardware (Black) and simulation (Blue) results for the frequency spectra of noise current  $i_{bp}$  for the Baseline module.

| Parameter       | Value (Units)   | Parameter          | Value (Units)  |

|-----------------|-----------------|--------------------|----------------|

| $Q_1$ and $Q_2$ | CPM2-1200-0040B | LISN               | CISPR Standard |

| C <sub>in</sub> | 93.6 µF         | ESR <sub>Cin</sub> | 15.59 mΩ       |

| ESL <sub>Cin</sub> | 1 nH      | $C_{PCB}$              | 34 nF                 |

|--------------------|-----------|------------------------|-----------------------|

| ESL <sub>PCB</sub> | 5.6 nH    | ESR <sub>PCB</sub>     | 35.42 mΩ              |

| $L_{j1}$           | 120.78 nH | $R_{j1}$               | 150 mΩ                |

| $L_{j2}$           | 167.48 nH | $R_{j2}$               | 180 mΩ                |

| $L_{j3}$           | 24.47 nH  | <i>R</i> <sub>j3</sub> | $80 \mathrm{m}\Omega$ |

| $L_{j4}$           | 52.47 nH  | $R_{j4}$               | $80 \mathrm{m}\Omega$ |

| $L_{j5}$           | 8 nH      | $R_{j5}$               | 82 mΩ                 |

| $L_{j6}$           | 3 nH      | $R_{j6}$               | 180 mΩ                |

| $L_F$              | 750 µH    | $C_{f}$                | 100 µF                |

| $R_L$              | 22.1 Ω    | $C_{H1}$               | 6.36 pF               |

| $L_{H1}$           | 105 nH    | $R_{H1}$               | 10 mΩ                 |

| L <sub>H2</sub>    | 650 nH    | $R_{H2}$               | 0.5 Ω                 |

|                    |           |                        |                       |

In Figure 17(b), the hardware and simulation results for the Baseline module is compared. The frequency spectrum is obtained by running the time domain simulation, followed by the fast Fourier transform (FFT). Between 150 kHz to 10 MHz, a maximum difference of 4 dB was observed in the frequency spectrum. Beyond 10 MHz, the ability of the simulation to predict the noise magnitude decreases and a maximum difference of 10 dB was observed. This is a result of using linear, lumped circuit elements to model parasitics inside the converter and the module, and the die model used not being accurate at high frequencies [61]–[63]. However, although the ability of the simulation to predict the noise magnitude decreases beyond 10 MHz, Figure 17(b) shows that the model reasonably predicts trends seen in the frequency spectrum: a relatively flat frequency spectrum until the frequency of ~9.9 MHz, beyond which a roll-off is observed.

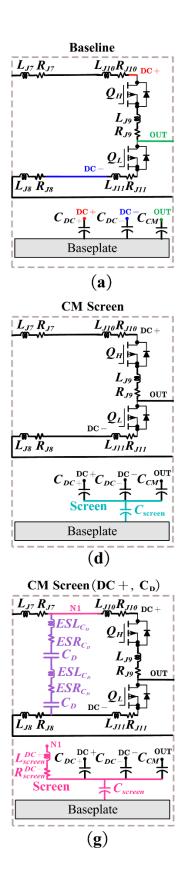

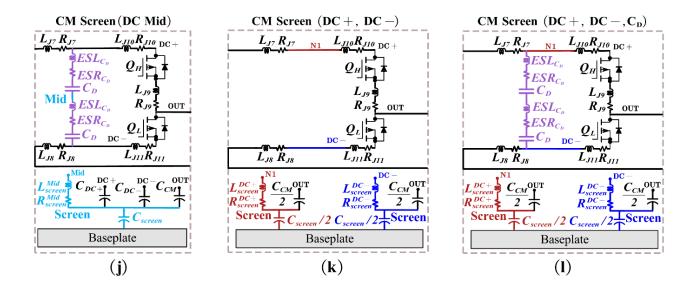

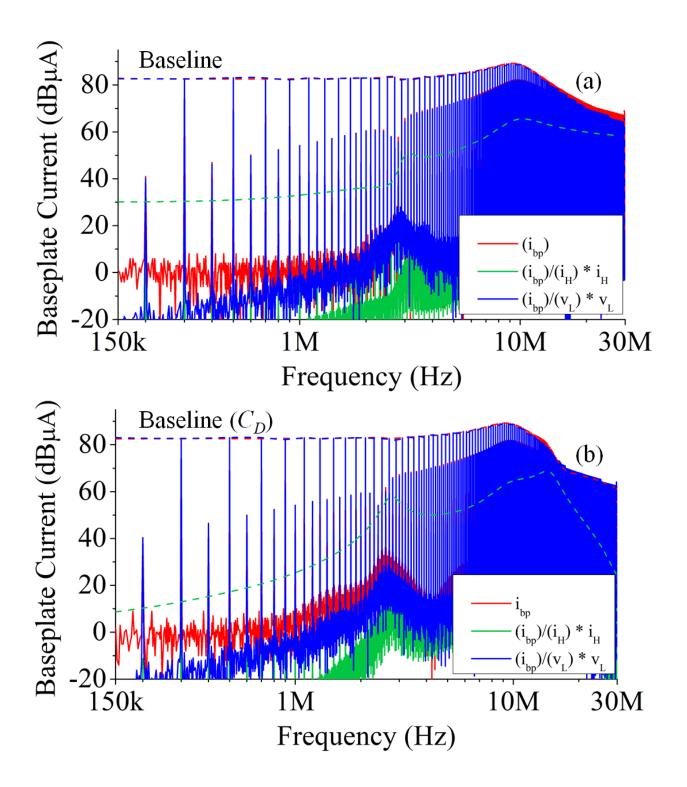

Similar to the Baseline module, simulation models for the remaining eleven modules were also built. The simulation models for the twelve module architectures are shown in Figure 18. The values for various parasitics are shown in Table 4. Figure 18(a)-(c) shows the three baseline architectures: Baseline, Baseline ( $C_D$ ), and Baseline ( $C_y$ ). Figure 18(b) differs from Figure 18(a) in that the decoupling capacitors  $C_D$  (along with the equivalent series resistance ESR and inductance ESL) have been integrated into the module architecture. Figure 18(c) differs from the other two baseline architectures in that the baseplate is shorted to the DC mid node created by the series connection of the decoupling capacitors.

Figure 18(d)-(l) shows the nine different CM screen module architectures studied. The module architectures primarily differ based on what node the CM screen is connected to and whether the architecture has decoupling capacitors. In Figure 18(d) and (e) the CM screen is left floating. CM Screen ( $C_D$ ) (Figure 18(e)) differs from the CM Screen (Figure 18(d)) in that the decoupling capacitors  $C_D$  (along with the equivalent series resistance ESR and inductance ESL) have been integrated into the module architecture.

Figure 18: Simulation schematic of the twelve module architectures explored.

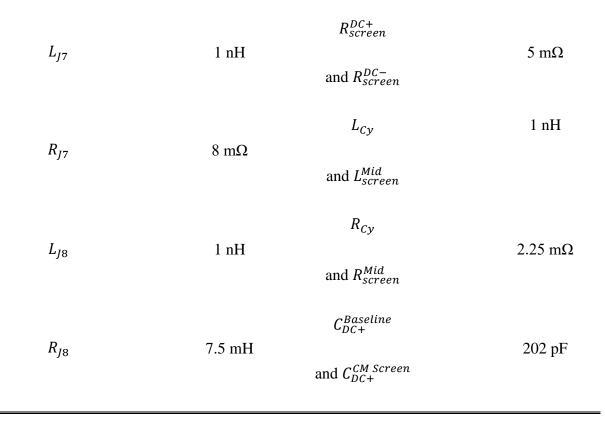

| Parameter           | Value (Units) | Parameter                                    | Value (Units) |

|---------------------|---------------|----------------------------------------------|---------------|

| C <sub>D</sub>      | 14.56 nF      | L <sub>J9</sub>                              | 3.7 nH        |

| ESR <sub>CD</sub>   | 9.9 mΩ        | $R_{J9}$                                     | 8 mΩ          |

| $ESL_{C_D}$         | 0.25 nH       | L <sub>J10</sub>                             | 3 nH          |

| C <sub>DC+</sub>    | 166.3 pF      | $R_{J10}$                                    | 8 mΩ          |

| C <sub>DC</sub> -   | 24 pF         | <i>L</i> <sub><i>J</i>11</sub>               | 3.1 nH        |

| C <sub>Mid</sub>    | 35.71 pF      | <i>R</i> <sub><i>J</i>11</sub>               | 7.5 mΩ        |

| С <sub>СМ</sub>     | 80.2 pF       | L <sub>J12</sub>                             | 1 nH          |

| C <sub>screen</sub> | 436.9 pF      | $L_{screen}^{DC+}$<br>and $L_{screen}^{DC-}$ | 3.35 nH       |

The schematics shown in Figure 18(f)-(i) differ from one another based on whether the screen is connected to a positive or negative DC node (labelled N1 or DC-) and whether decoupling capacitors  $C_D$  (along with the equivalent series resistance ESR and inductance ESL) have been integrated into the module. Figure 18(j) shows a CM screen module in which the screen is connected to the Mid node, a DC node created by the series connection of the decoupling capacitors  $C_D$ . Figure 18(k) and (l) show module architectures in which the screening layer below the switching node OUT has been split into two halves. Half the screening layer is connected to a positive DC node N1 and the other half is connected to a negative DC node DC-. The schematics in Figure 18(k) and (l) differ from one another based on the addition of decoupling capacitors. It should again be noted that although in Figure 18(e), (g), (i) and (l) a Mid node has been created by the series connection of the decoupling capacitors, this has been done for the sake of uniformity in

the module architecture and to facilitate ease of understanding. The Mid node is not needed for these module architectures and a single decoupling capacitor can also be used.

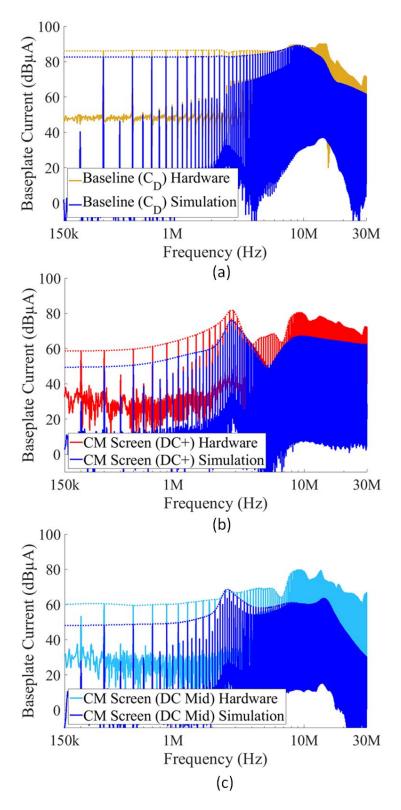

In Figure 19(a), the hardware and simulation results for the Baseline and Baseline ( $C_D$ ) modules are compared. Between 150 kHz to 10 MHz, a maximum difference of 4 dB was observed in both frequency spectrums. Beyond 10 MHz, a maximum difference of 13 dB was observed for the Baseline and Baseline ( $C_D$ ) modules. Although the accuracy of the simulation has decreased beyond 10 MHz, it can be seen from Figure 19(a) that the model can predict the trends seen in the frequency spectrum accurately: (1) a relatively flat frequency spectrum is seen until the frequency of ~9.9 MHz, beyond which a roll-off is observed, and (2) a change in the slope of the roll-of occurring at ~13.5 MHz.

In Figure 19(c) and (d) the hardware and simulation results for the CM Screen (DC+) and CM Screen (DC Mid) modules are compared. Results show that between 150 kHz to 4 MHz for the CM Screen (DC+) module, and 150 kHz to 7 MHz for the CM Screen (DC Mid) module; a maximum difference of 12 dB was observed between the hardware and simulation results. From 4 MHz to 7 MHz a maximum difference of 17 dB, and beyond 7 MHz a maximum difference of 14 dB is observed for the CM Screen (DC+) module between the hardware and simulation. The CM Screen (DC Mid) module shows a maximum difference of 20 dB from 7 MHz to 18 MHz between the hardware and simulation results. Similar to the baseline architectures, although the simulation was not able to predict the magnitudes of the frequency spectrum with high fidelity, the model was able to imitate the trends seen with reasonable accuracy: (1) the peak in the frequency spectrum at ~2.7 MHz, (2) the roll-off frequency beginning at a frequency of ~8.29 MHz, and (3) a change in the slope of the roll-of occurring at ~13.5 MHz for the CM Screen (DC Mid) module.

Figure 19: Comparison of the hardware and time domain simulation results for the frequency spectra of noise current  $i_{bp}$  for (a) the Baseline ( $C_D$ ), (b) the CM Screen (DC+) and (c) CM Screen (DC Mid) modules.

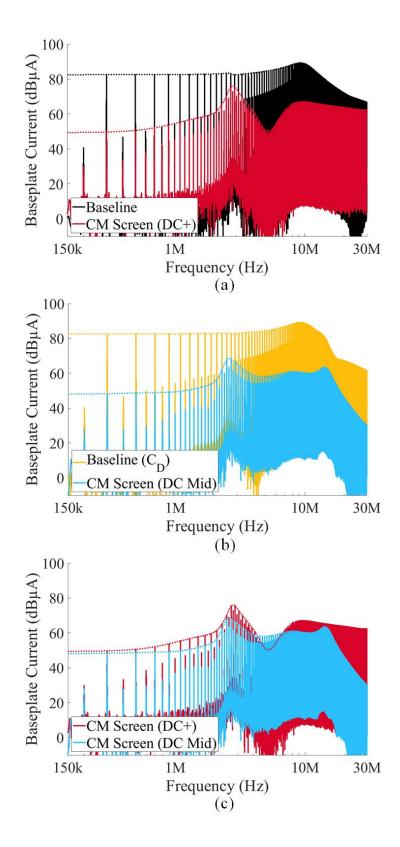

The frequency spectra of the noise current  $i_{bp}$  for the four experimentally tested module architectures are compared through simulation in Figure 20. In Figure 20(a) and (b), the two baseline modules are compared to their CM screen counterparts, similar to Figure 13(a) and (b). In both scenarios, a maximum noise reduction of 35 dB is noted, which is a 35% increase compared to the hardware results. In Figure 20(c), the  $i_{bp}$  generated by the two CM Screen architectures is compared. Although hardware results showed a maximum mitigation of 13 dB between 2.7 MHz and 2.9 MHz, the simulation results show a maximum mitigation of 9 dB, a 30% decrease. The simulation also predicts a high level of mitigation with the CM Screen (DC Mid) module at frequencies larger than 13.5 MHz. It can again be observed that the simulation was not able to predict the mitigation magnitudes in the frequency spectrum with high fidelity: an error of upto 35%; however, the simulation was able to imitate the mitigation trends seen in Figure 13 with reasonable accuracy. For example, in Figure 20(c), the CM Screen (DC+) and CM Screen (DC Mid) modules show similar mitigation trends in the frequency spectrums in the 150 kHz to 500 kHz frequency range. Similarly, the peak in the frequency spectrum at ~2.7 MHz for the CM Screen (DC+) module slightly shifts to a lower frequency for the CM Screen (DC Mid) module. A change in slope in the frequency spectrum of the CM Screen (DC Mid) module at ~13.5 MHz is also predicted by the simulation resulting in the module having lower EMI compared to the CM Screen (DC+) module. The justification for why these trends occur will be presented in Chapter 5. Any prediction about noise mitigation between module architectures made by the LTspice simulation below 10 MHz will be assumed to have an error of 35%.

Figure 20: Frequency spectra of noise current  $i_{bp}$  from simulation for (a) the Baseline and CM Screen (DC+) modules, (b) the Baseline ( $C_D$ ) and CM Screen (DC Mid) modules, and (c) the CM Screen (DC+) and CM Screen (DC Mid) modules.

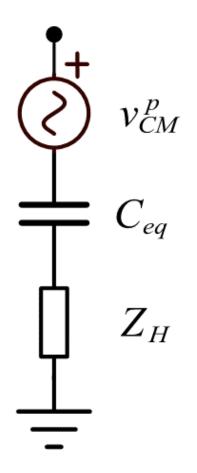

## 4.3 Common Mode Equivalent Modeling

A common mode equivalent model (CEM) for the test setup is now derived. Since the time domain simulation model in Figure 17(a) is a good approximation of the experimental test setup, the CEM for the simulation model is derived, using the methodology presented in [39], [59], [64].

### 4.3.1 Two Parallel Wires with Asymmetric Impedances

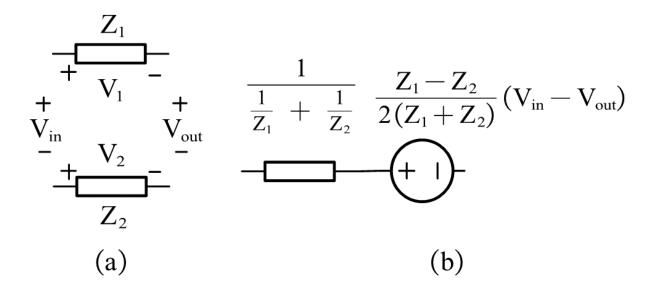

To derive the CEM of the test setup schematic, the CEM equations of two parallel wires with asymmetric impedances is first derived using the methodology presented in [59]. Two parallel wires with asymmetric impedances are shown in Figure 21(a). The system of equations that define the circuit schematic shown in Figure 21(a) is:

$$\begin{bmatrix} V_1 \\ V_2 \end{bmatrix} = \begin{bmatrix} Z_1 & 0 \\ 0 & Z_2 \end{bmatrix} \begin{bmatrix} i_1 \\ i_2 \end{bmatrix}$$

(11)

Using the transform definitions for  $T_N^i$  and  $T_N^v$  and the methodology detailed in [59], the system of equations (11) is decomposed into a system of differential mode (DM) and CM equations. From [59], the linear transformation matrices  $T_N^i$  and  $T_N^v$  can be expressed as (12) and (13):

$$T_{N}^{i} = \begin{bmatrix} \frac{1}{2} & -\frac{1}{2} \\ 1 & 1 \end{bmatrix}$$

(12)

$$T_N^{\nu} = \begin{bmatrix} 1 & -1\\ \frac{1}{2} & \frac{1}{2} \end{bmatrix}$$

(13)

Decomposing system of equations (11) by making substitution  $i_{\alpha} = (T_N^i)^{-1} i_{DCM}$  for line currents and left multiplying by  $T_N^v$ , system of equations (14) is obtained:

$$\begin{bmatrix} v_{12} \\ v_{CM} \end{bmatrix} = \begin{bmatrix} 1 & -1 \\ \frac{1}{2} & \frac{1}{2} \end{bmatrix} \begin{bmatrix} Z_1 & 0 \\ 0 & Z_2 \end{bmatrix} \begin{bmatrix} \frac{1}{2} & -\frac{1}{2} \\ 1 & 1 \end{bmatrix}^{-1} \begin{bmatrix} i_{12} \\ i_{CM} \end{bmatrix}$$

(14)

Solving and simplifying system of equations (14), system of equations (15) is obtained: