# Simulation of Large-Scale System-Level Models

by

# Vikrampal Chadha

Thesis submitted to the Faculty of the

Virginia Polytechnic Institute and State University

in partial fulfillment of the requirements for the degree of

Master of Science

in

**Electrical Engineering**

APPROVED:

Dr. N. J. Davis IV, Chairman

Dr. J. R. Armstrong

Dr. F. G. Gray

September, 1994

Blacksburg, Virginia

## Simulation of Large-Scale System-Level Models

by

Vikrampal Chadha

Dr Nathaniel J. Davis IV, Chairman

Electrical Engineering

(ABSTRACT)

In this thesis, the efficient simulation of large-scale system-level VHDL models is analyzed. The system-level models chosen for the investigation are multicomputer networks, which are scalable up to thousands of processing nodes. Initially, a classification of parallel processing architectures is presented along with performance criteria and design issues related to the various interconnection network topologies. Communication and synchronization issues of MIMD systems are explored. A major limitation of planar tree structures is discussed along with a solution to help alleviate the problem, which is to make use of the binary *fat-tree*. Practical aspects of efficiently simulating large behavioral and structural models (using the fat-tree model as a case study), on a uniprocessor system are analyzed. The system resources of the workstation used to perform the simulations are carefully monitored to see where resource utilization problems usually occur. The size of the model is increased and the run time of the simulation compared with that of smaller sized models. A memory threshold level is detected after which memory resource contention problems occur and the simulation efficiency declines.

One of the problems observed in simulating complex models is the fact that simulation runs take a very long time to execute. A multicomputer using the fat-tree interconnection network is proposed as a suitable architecture for the distributed simulation of VHDL models. Various algorithms used for the parallel discrete event simulation (PDES) of VHDL models are evaluated. The feasibility of this approach is evaluated by analyzing the factors affecting the performance of the proposed architecture. The number of hops a message takes to travel from one processor to another in the fat-tree is used to estimate the time of an event message between two processors. The roll-back and communication costs amongst the processing nodes are taken into consideration when evaluating the speedup of the simulation time of a VHDL model, simulated over multiple processors. The speedup of the simulation obtained by using the fat-tree topology is compared with the results obtained with a linear array of processors. The future inclusion of the "shared variable" into the language and its impact on the implementation of parallel simulators on multicomputer networks is analyzed.

# Acknowledgments

I would like to express a deep sense of gratitude towards my advisor, Dr Nathaniel J. Davis IV, for working with me to help further my educational goals. I consider myself very fortunate to have had as a mentor, someone with the rare insight and wisdom who knew how to make me bring out the best in myself by encouraging me to fully explore those ideas that I found to be the most fascinating. In the process, I learnt a great deal and thoroughly enjoyed the research experience which led to the completion of this thesis.

Thanks are also due to my committee members, Dr J. R. Armstrong and Dr. F. G. Gray for their guidance and participation. There were numerous researchers and students around the world who spent so much of their time in helping me that I was worried that their work would suffer as a result!. I would especially like to thank Dr Peter Ashenden at the University of Adelaide, Australia, Paolo Faraboschi at the University of Genoa, Italy and Frederic Petrot at the University et Marie Curie, France for their patience in answering all my questions (and there were many!), and their quick responses at some crucial moments.

I would like to dedicate this thesis to my parents who have always been my greatest source of inspiration and who helped make this dream of mine come true.

# **Table of Contents**

| Abstract                                                 | ii  |

|----------------------------------------------------------|-----|

| Acknowledgements                                         | iii |

| List of Figures.                                         | vi  |

| List of Tables                                           | ix  |

| 1. Introduction                                          | 1   |

| 1.1 Research Goals                                       | 2   |

| 1.2 Outline of Thesis                                    | 3   |

| 2. Overview of Multicomputer Networks                    | 5   |

| 2.1 Introduction                                         | 5   |

| 2.2 Classification of Parallel Processing Architectures  | 6   |

| 2.2.1 Granularity                                        | 8   |

| 2.2.2 Coupling                                           | 8   |

| 2.3 Interconnection Topologies for Multicomputer Systems | 8   |

| 2.3.1 Performance Criteria                               | 9   |

| 2.3.1.1 Latency                                          | 9   |

| 2.3.1.2 Bandwidth                                        | 9   |

| 2.3.1.3 Cost                                             | 9   |

| 2.3.1.4 Reliability                                      | 9   |

| 2.3.2 Design Considerations                              | 10  |

| 2.3.2.1 Topology                                         | 10  |

| 2.3.2.2 Operation Mode                                   | 12  |

| 2.3.2.3 Switching Strategy                               | 12  |

| 2.4 Communication and Synchronization Issues             | 13  |

| 2.4.1 Synchronization Issues in Shared Memory Computers  | 14  |

|    | 2.4.2 Synchronization Issues in Distributed Memory Computers | 16 |

|----|--------------------------------------------------------------|----|

|    | 2.5 Scalability of Parallel Processing Systems               | 17 |

|    | 2.5.1 Network Scaling Factors                                | 18 |

|    | 2.5.1.1 Node Degree                                          | 18 |

|    | 2.5.1.2 Network Diameter                                     | 19 |

|    | 2.5.1.3 Bisection Width                                      | 19 |

|    | 2.6 Summary                                                  | 20 |

| 3. | Design of a Single Processing Node                           | 21 |

|    | 3.1 Introduction.                                            | 21 |

|    | 3.2 Evolution of RISC Microprocessor Architectures           | 22 |

|    | 3.3 Instruction Set Architecture of the 32-bit DLX Processor | 24 |

|    | 3.4 Instruction Format.                                      | 26 |

|    | 3.5 Basic Steps of Execution.                                | 27 |

|    | 3.6 Structural Level VHDL Model of the Datapath              | 30 |

|    | 3.7 Processor Bus Architecture                               | 32 |

|    | 3.8 Cache Design Issues                                      | 33 |

|    | 3.9 Instruction Level Parallelism.                           | 40 |

|    | 3.10 Conclusions.                                            | 43 |

| 4. | Model of the Fat-tree Interconnection Network                | 44 |

|    | 4.1 Introduction.                                            | 44 |

|    | 4.2 Tree Terminology                                         | 45 |

|    | 4.3 Tree-based Structures                                    | 46 |

|    | 4.4 Universal Fat Trees.                                     | 46 |

|    | 4.5. VHDL model of the Fat Tree                              | 49 |

|    | 4.6 Dynamic Instruction Frequency Counts                     | 52 |

|    | 4.7 System Resource Utilization.                             | 56 |

|    | 4.7.1. VHDL Source Code Optimization                         | 57 |

| 4.7.2. Monitoring System Resources                                | 59             |

|-------------------------------------------------------------------|----------------|

| 4.8 Conclusions                                                   | 63             |

| 5. Parallel Simulation of VHDL models over a Fat-tree Interconnec | tion Network65 |

| 5.1 Introduction                                                  | 65             |

| 5.2 VHDL Parallel Discrete Event Simulation                       | 66             |

| 5.2.1 Sequential Discrete Event Simulation                        | 66             |

| 5.2.2 Centralized-queue Algorithms                                | 67             |

| 5.2.3 Distributed-time Algorithms                                 | 67             |

| 5.2.3.1 Conservative Distributed-time Algorithms                  | 67             |

| 5.2.3.2 Optimistic Distributed-time Algorithms                    | 68             |

| 5.3 The VHDL Parallelism Analyzer                                 | 68             |

| 5.4 Experimental Results and Analysis                             | 70             |

| 5.5 VHDL Language Extensions for System-level Modeling            | 81             |

| 5.6 Conclusions                                                   | 84             |

| 6. Conclusions                                                    | 86             |

| 6.1 Summary of Research Work                                      | 87             |

| 6.2 Future Work                                                   | 90             |

| Appendix A.                                                       | 91             |

| Bibliography                                                      | 93             |

# **List of Figures**

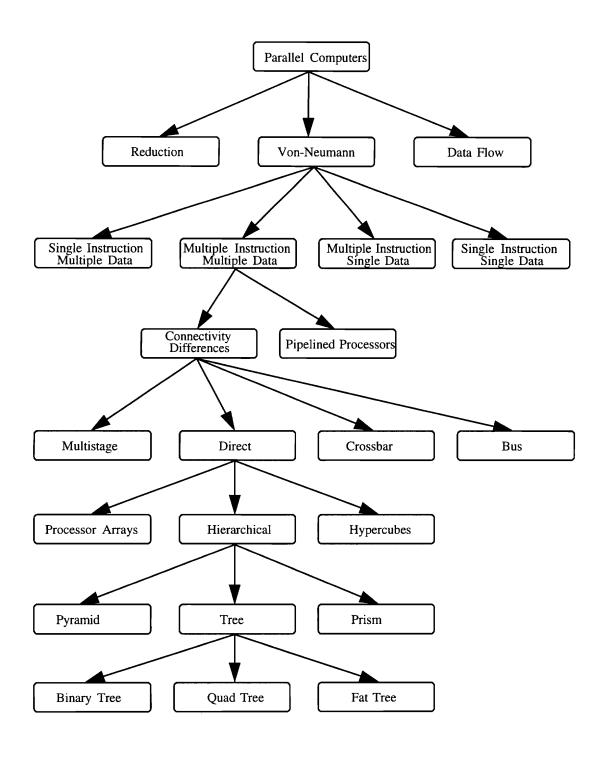

| Figure 2.1  | Classification of Parallel Processing Architectures                                  | 8  |

|-------------|--------------------------------------------------------------------------------------|----|

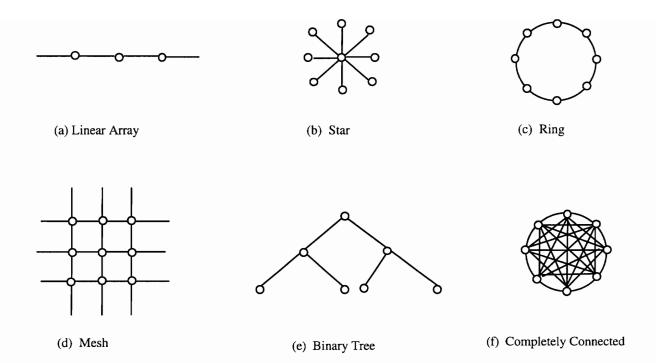

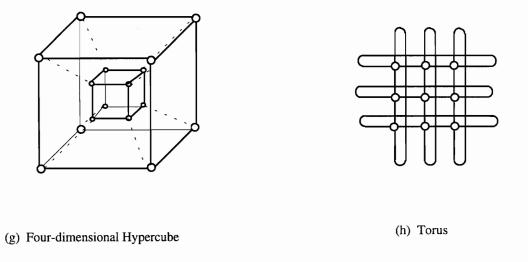

| Figure 2.2  | Static interconnection topologies                                                    | 12 |

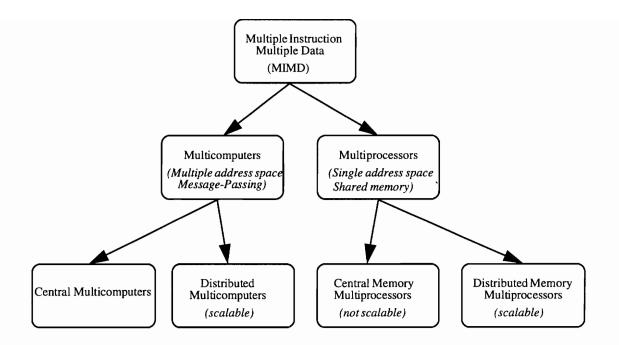

| Figure 2.3  | Taxonomy of MIMD Computers                                                           | 16 |

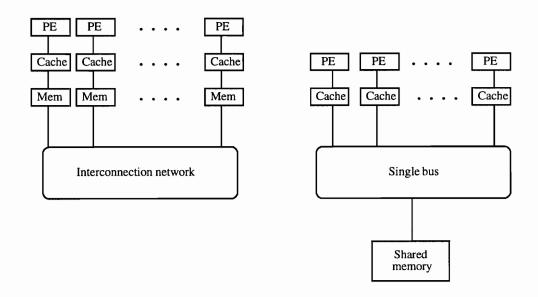

| Figure 2.4  | (a) MIMD system with distributed memory                                              | 6  |

| Figure 2.4  | (b) MIMD system with shared memory                                                   | 16 |

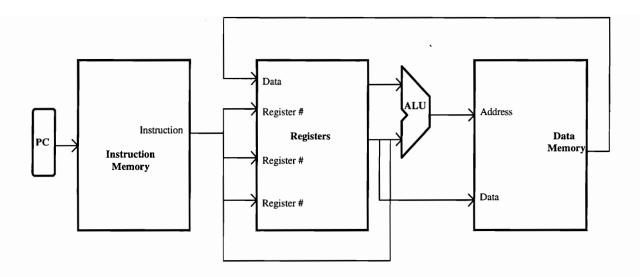

| Figure 3.1  | An abstract view of the implementation of the processor subset                       | 30 |

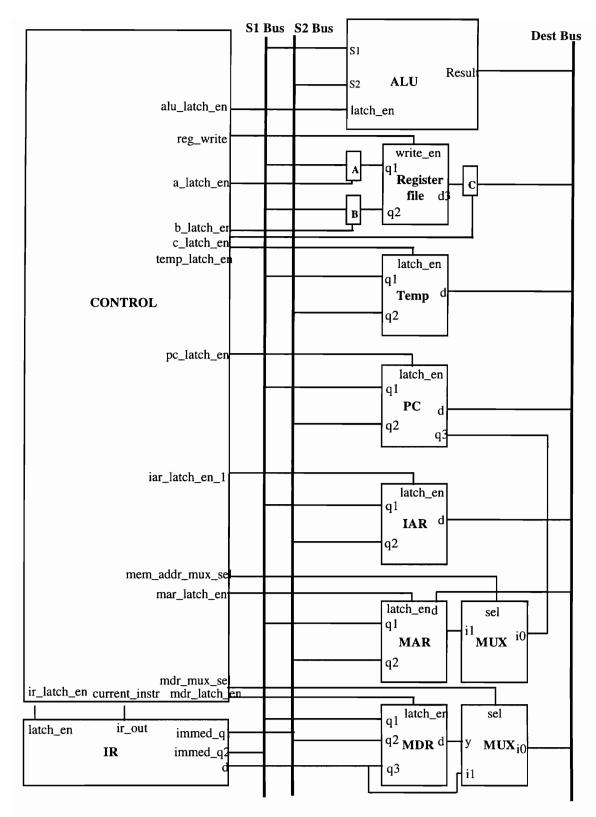

| Figure 3.2  | Block diagram of the 32-bit DLX processor                                            | 33 |

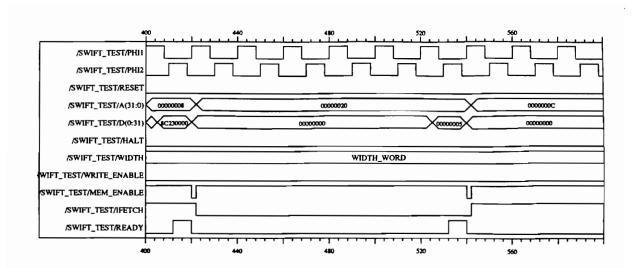

| Figure 3.3  | Processor bus read transaction.                                                      | 36 |

| Figure 3.4  | Processor bus write transaction.                                                     | 36 |

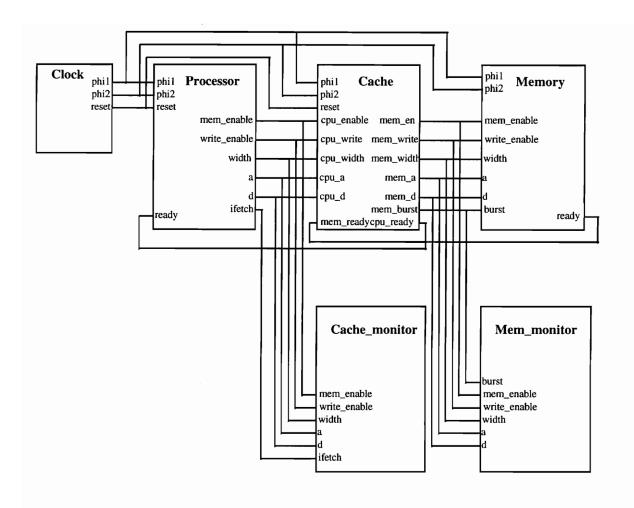

| Figure 3.5  | Block diagram of the SWIFT processor with cache and memory modules                   | 39 |

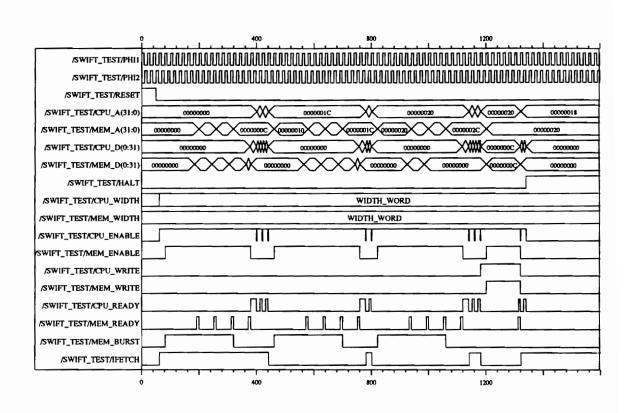

| Figure 3.6  | Processor write to cache (write-through)                                             | 40 |

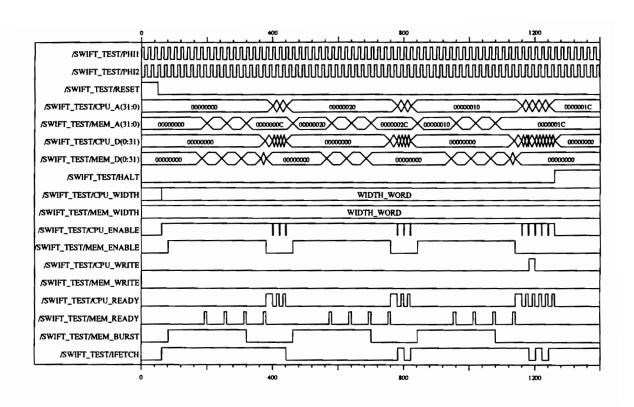

| Figure 3.7  | Processor write to cache (write-back)                                                | 41 |

| Figure 3.8  | Output result of a loop, used to add a scalar value to a vector in memory            | 14 |

| Figure 3.9  | Output result of a loop after scheduling and unrolling operations                    | 44 |

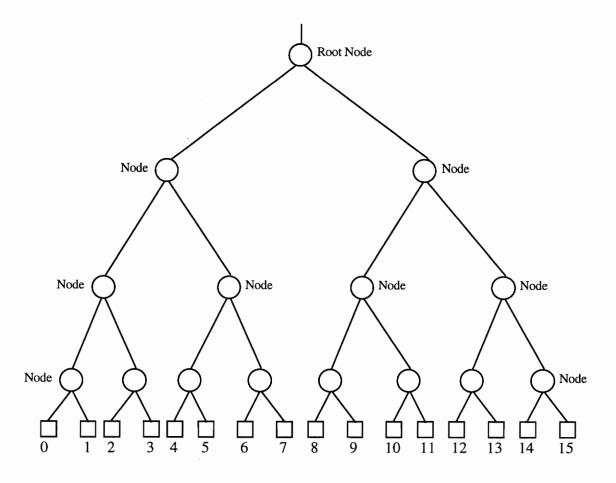

| Figure 4.1  | A complete binary tree where all the switches have one parent and two children       | 19 |

| Figure 4.2. | Hop count of the messages, and message path for a 16-node fat tree                   | 53 |

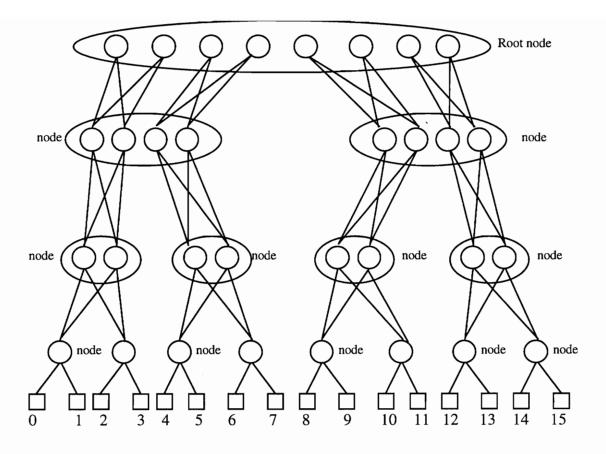

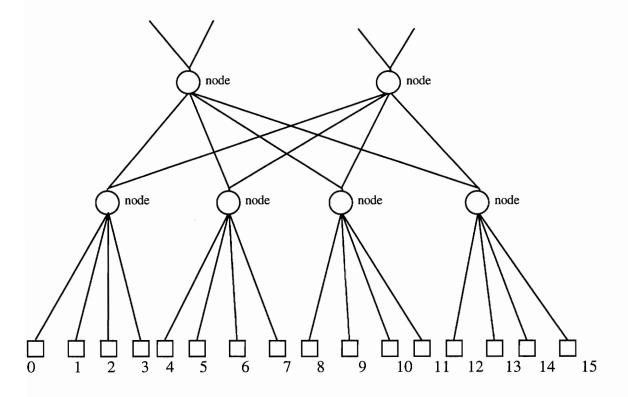

| Figure 4.3  | A 16-node binary fat-tree, where all non-root switches have two parents              | 55 |

| Figure 4.4  | A 16-node quadtree, where all non-root switches have two parents and four children   | 56 |

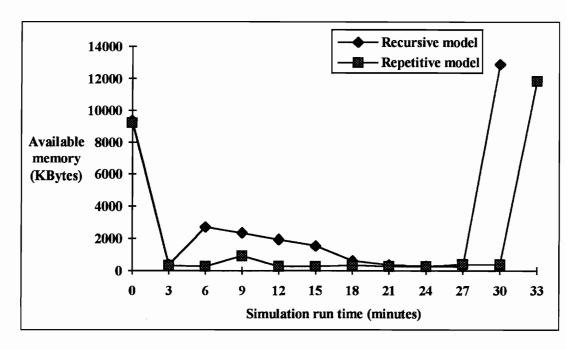

| Figure 4.5  | Comparison of the available memory resources for a 32-node fat-tree when a           |    |

|             | recursive structure is used and when a non-recursive (repetitive) structure is used6 | 53 |

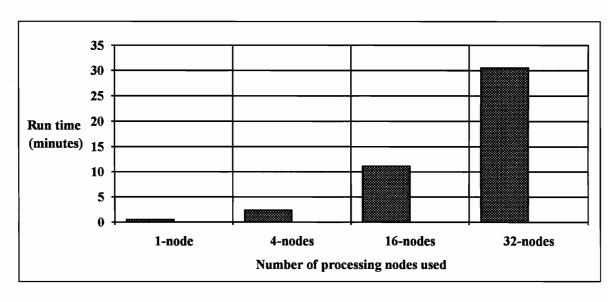

| Figure 4.6   | The run time is seen to increase in a non-linear way, due to memory contention, |

|--------------|---------------------------------------------------------------------------------|

|              | with an increase in the size of the fat-tree model                              |

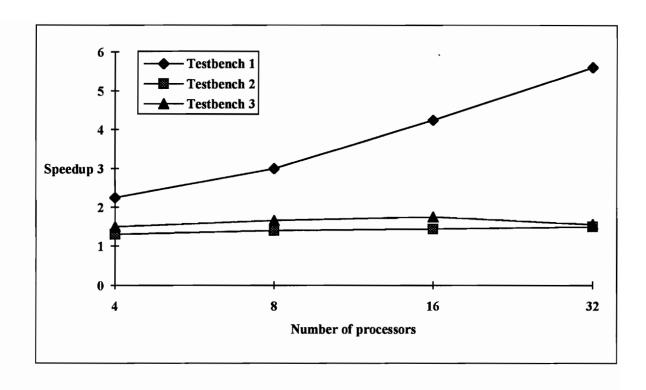

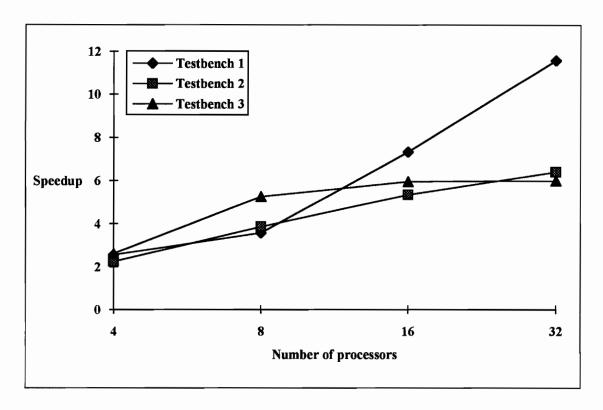

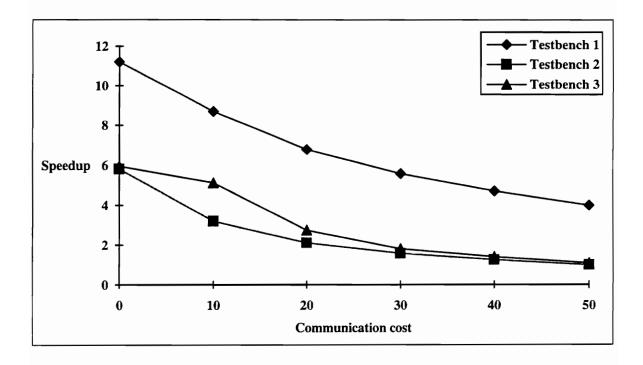

| Figure 5.1.  | Performance of a centralized-queue algorithm on fat-trees of different sizes72  |

| Figure 5.2.  | Performance of a distributed-time algorithm on fat-trees of different sizes74   |

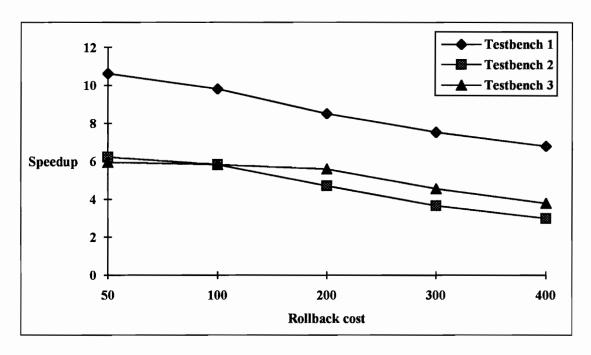

| Figure 5.3.  | Performance of an optimistic distributed-time algorithm of a 32-node            |

|              | fat-tree with increasing rollback costs                                         |

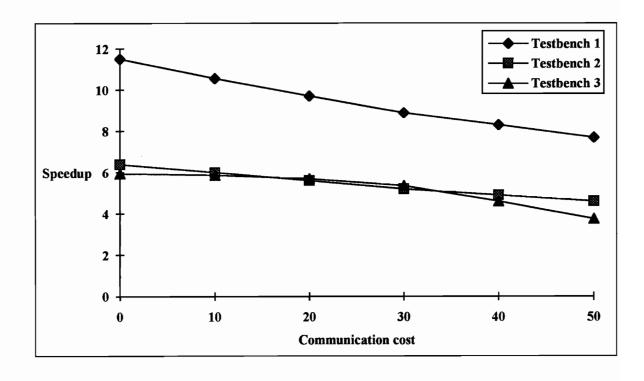

| Figure 5.4 I | Performance of an optimistic distributed-time algorithm of a 32-node            |

|              | fat-tree with increasing communication costs                                    |

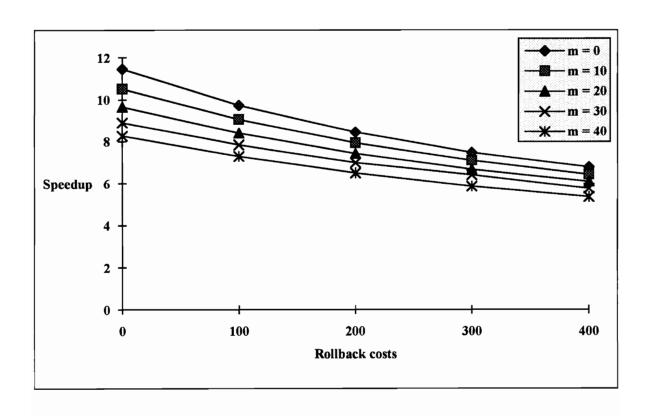

| Figure 5.5 I | Performance of an optimistic distributed-time algorithm of a 32-node            |

| 1            | fat-tree with increasing communication and rollback costs                       |

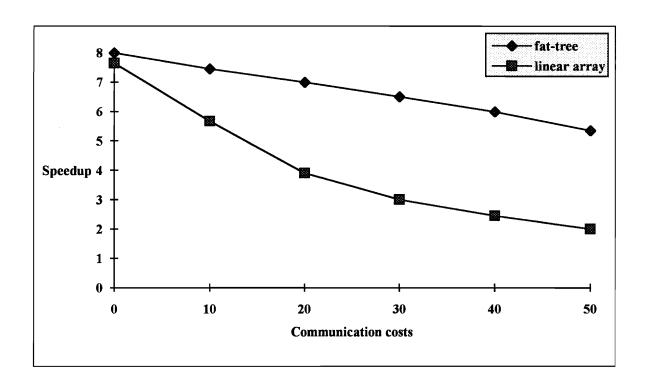

| Figure 5.6 I | Performance of an optimistic distributed-time algorithm of a 32                 |

| p            | processor linear array with increasing communication costs                      |

| Figure 5.7.  | Comparison of the performance decline between a 32-node fat-tree                |

| ;            | and a 32-node linear array with increasing communication costs80                |

# **List of Tables**

| Table 2.1 | Network Scaling Factors                                                              | 2  |

|-----------|--------------------------------------------------------------------------------------|----|

| Table 3.1 | Comparison of the major features of some of the older CISC architectures             | 5  |

| Table 3.2 | Comparison of the major features of some of the recent RISC architectures            | 25 |

| Table 3.3 | A list of the instructions used by the Swift (DLX) processor model                   | 7  |

| Table 4.1 | Dynamic instruction mix statistics of parallel benchmark programs                    | 7  |

| Table 4.2 | Dynamic instruction mix statistics of benchmark programs run on a uniprocessor5      | 8  |

| Table 4.3 | Dynamic instruction frequency counts obtained from the execution of a                |    |

|           | test program on the VHDL model of the 32-node fat-tree multicomputer5                | 9  |

| Table 4.4 | A report on memory paging and swapping information generated using                   |    |

|           | the <i>vmstat</i> command, for a 16-node fat-tree simulation on a Sun Sparksation 26 | 1  |

| Table 4.5 | A report on memory paging and swapping information generated using                   |    |

|           | the <i>vmstat</i> command, for a 32-node fat-tree simulation on a Sun Sparksation 26 | 1  |

| Table 5.1 | Static and dynamic information on the VHDL models used in the tests                  | 0  |

| Table 5.2 | Results obtained with Centralized and Distributed-time algorithms                    |    |

|           | (rollback cost and communication cost are not considered)                            | 3  |

## Chapter 1

### Introduction

During the last decade, we have seen a major growth in the performance of low-cost computers that are based on microprocessor technology. This growth is expected to continue into the foreseeable future due to the continuing progress in increasing the density of the VLSI chips from which modern computers are constructed. In the early 1980's, microprocessor performance became a major research area with focus on quantitative metrics such as instruction execution rates and instruction counts. Sophisticated architectural techniques which had been in widespread use in large mainframes and supercomputers were incorporated into the microprocessors. The introduction of processors with a simple instruction set made it easier to migrate these techniques to the microprocessor.

During the next five years, we should see an increasing number of scalable parallel processing systems being built from these high-performance off-the-shelf microprocessors. These systems will be used to help solve the kind of single, large-scale problems (where N, the number of unknowns, is large) that overly tax the computational power of the fastest single-processor machines available today.

Multicomputers are types of parallel processing system that consist of multiple processing nodes connected by a communication network. Each processor, also referred to as a node or a processing element, has computing, memory, and communication resources. The computing resources perform the processing assigned to the node. The memory stores both program and data. The communication facilities are used to transmit and receive data from other processing nodes.

#### 1.1 Research Goals

Since its introduction as a hardware description language, the VHDL language has been used only to a limited extent to model large-scale parallel processing systems. VHDL models of multicomputer networks have mainly been used to model the routing among the interconnecting switches found at the nodes of the network. The following issues are investigated in order to gain an insight into the modeling of (increasingly) complex systems with the VHDL hardware description language.

- i) In order to study the suitability of using VHDL in the design of system-level models of increasing complexity, a 32-node multicomputer network based on the fat-tree architecture, with structural-level processing nodes is simulated. The processor in each computer node is tightly coupled to a memory that is physically separate and logically private from the memories of the other node computers. Interprocessor communication in the multicomputer occurs by routing messages through the interconnection network. As the size of the multicomputer model is increased from 4 to 32 processing nodes, the resources of the workstation used to perform the simulation are carefully monitored. An analysis is performed on the type of resource contention problems which occur when simulating large and complex models and the impact that these problems have on the run time of the simulation.

- ii) Another aspect of the research focuses on the nature of the parallel algorithms used to program massively parallel processing systems. The von Neumann model of a computer is limited by all the communications between the central processing unit and the memory unit proceeding along what is essentially a single interconnection line, the so-called "von Neumann bottleneck." A negative aspect of this single link on the speed of a computer is not confined only to its limited capacity. In fact, the entire algorithm design process is adversely affected since we are forced to think about computational processes in sequential terms. If the dynamic instruction frequency mix of a given parallel program could be recorded from simulating the VHDL model of the multicomputer network, it would provide us with valuable information about the demands made on the processing nodes, in terms of whether the programs

are more "control" intensive or "ALU intensive." The information obtained would allow designers of future generations of microprocessors to make enhancements to better accommodate the needs of the processors used in these massively parallel processing systems.

iii) One of the problems associated with the discrete event simulation of large models is the fact that simulation runs take a very long time to execute. Parallel discrete event simulation (PDES) techniques can be used to simulate large VHDL models on parallel processing systems. Experiments are performed to evaluate the feasibility of using the fat-tree architecture to perform the parallel simulation of VHDL models and determine if a speedup in simulation time would be obtained over simulating the models on a single processor. In the case of optimistic distributed time algorithms, communication latency issues and the cost of message *rollback* are also included in the analysis in order to determine the effect of these factors on the performance of the fat-tree multicomputer network.

#### 1.2 Outline of Thesis

In Chapter 2, an overview of multicomputer networks is presented. A classification of parallel processing architectures is provided along with performance criteria and design issues related to the various interconnection network topologies. Communication and synchronization issues of MIMD systems are analyzed. The factors affecting the scalability of parallel processing systems are then discussed. The chapter concludes with an overview of factors used to determine how performance characteristics scale with the number of processors being interconnected, using a specific network topology.

Chapter 3 describes the VHDL model of the processing node used in the multicomputer network.

The structural-level VHDL model is based on the DLX processor, a 32-bit reduced instruction set processor described in [1]. The reasons for choosing this processor are discussed. The fact that parallel

algorithms make efficient use of the memory hierarchy is considered in the design, by providing a cache memory in each processing node. Instruction level parallelism is explored with a suitable test case.

Chapter 4 begins with a series of definitions used to describe trees in graph theory. Examples are provided of earlier research projects which utilized tree-based structures. A major limitation of the planar tree structures is analyzed, along with a solution which is to make use of the *binary fat-tree* to help alleviate the problem. The inclusion of structural-level processing nodes in the model of the fat-tree multicomputer, described in Chapter 4, has a useful consequence. The dynamic instruction frequency mix of a given parallel program can be measured.

A practical aspect of efficiently simulating large behavioral and structural models, (using the fat-tree model as a case study), on a uniprocessor system is analyzed. The system resources of the workstation used to perform the simulations are carefully monitored to see where resource utilization problems usually occur. The size of the model is increased and the run time of the simulation compared with that of smaller sized models. A memory threshold level is detected after which memory resource contention problems occur, and the simulation efficiency declines.

One of the problems observed in simulating complex models is that simulation runs take a very long amount of time to execute. The trend is for run times to lengthen, since the combinatorial complexity of circuits is out-stripping performance improvements in computers. In Chapter 5, a multicomputer using the fat-tree interconnection network is evaluated as a suitable architecture for the parallel simulation of VHDL models. Various algorithms used for the parallel discrete event simulation (PDES) of VHDL models are explored. The feasibility of this approach is carried out by analyzing the factors affecting the performance of the proposed architecture. Results obtained from simulating the model of the fat-tree multicomputer network, described in Chapter 4, are used to provide details about the interconnecting links between the various processing nodes. The number of hops a message takes to travel from one processor to another in the fat-tree is used to estimate the time of an event message between two processors. The *roll-back* cost and the cost of communication amongst the processing nodes are taken into consideration

when evaluating the *speedup* of the simulation time of a VHDL model, simulated over multiple processors. The speedup of the simulation of a VHDL model using the fat-tree topology is compared with the results obtained with a linear array topology.

The future inclusion of the "shared variable" into the language and its impact on the implementation of parallel simulators on multicomputer networks is analyzed. Conclusions drawn from the results obtained in the previous chapters are presented in Chapter 6.

## Chapter 2

## **Overview of Multicomputer Networks**

#### 2.1 Introduction

During the last decade, we have seen a major growth in the performance of low-cost computers that are based on microprocessor technology. This growth is expected to continue into the foreseeable future due to the continuing progress in increasing the density of the VLSI chips from which modern computers are constructed.

During the next five years, we should see an increasing number of parallel processing systems built from these high-performance off-the-shelf microprocessors. These systems will be used to help solve the kind of single, large-scale problems (where N, the number of unknowns, is large) that overly tax the computational power of the fastest single-processor machines available today. Examples of computationaly intensive problems include scientific simulation modeling, advanced computer-aided design, and real-time image processing of large-scale database and information retrieval operations [2].

In this chapter, an overview of multicomputer networks is presented. A classification of parallel processing architectures is provided along with performance criteria and design issues related to the various interconnection network topologies. Communication and synchronization issues of MIMD systems are analyzed. The factors affecting the scalability of parallel processing systems are then discussed. The chapter concludes with an overview of the factors used to determine how performance characteristics scale with the number of processors being interconnected, using a specific network topology.

### 2.2 Classification of Parallel Processing Architectures

The most widely used scheme to classify the different type of processing systems was developed by Flynn [3]. It provides a four-way classification, in terms of whether one or several processors execute instructions on one or several streams of data. This scheme, though simplistic in nature, has endured the passage of time, probably because our understanding of multicomputers is still too primitive to replace it with a more definitive one.

In the case of one or more processors operating on multiple streams of data, Flynn's classification is given below:

SIMD (Single Instruction Multiple Data Stream) -- A network with only one controller although each processor works with information stored in its own and nearby memories. An example of such a system is the Connection Machine (CM-2) built by Thinking Machines Corporation which consists of a bit-slice array of up to 65,536 processing elements [2].

MIMD (Multiple Instruction Multiple Data Stream) -- A network where each processor has its own controller and can work in a completely asynchronous way, allowing multiple threads to be executed in an autonomous manner. Intel's mesh-connected Paragon system uses this model to connect its processing nodes [2]. Figure 2.1 shows a hierarchical classification of parallel processing architectures, with the MIMD model divided into a number of subclasses. Data parallelism refers to the situation where the same operation executes over a large array of data. Dataflow computers emphasize a high degree of parallelism at the fine-grain instruction level. Reduction computers are based on a demand driven mechanism which initiates an operation based on the demand for its result by other computations.

A mix of SIMD and MIMD leads to the SPMD (Single Program Multiple Data) model in which each processor executes the same SIMD program on its local data, but with an individual flow of control. In this way, the computation may be switched between SIMD lock step and MIMD asynchronous operation, based on the structure of the SPMD program. Generally, SPMD is regarded to be more of a MIMD programming style (SIMD programming on an MIMD machine) rather than a distinct classification.

Figure 2.1 Classification of Parallel Processing Architectures

There are a number of other important distinctions to be considered which could be used to categorize parallel processing systems [4]. Among them are:

- 2.2.1 Granularity -- The amount of processing and communication in the system needs to be balanced in order to obtain optimal performance. An important factor that helps determine the optimal topology is the way in which the application is partitioned into individual processing tasks. The *granularity* or *grain size* is the average size of each processor's subtask, measured in number of instructions executed in a program segment. The grain size of the partition is the metric used to define the size of each processing task. In processing data, for example, processing could be done at the bit level, vector and matrix level, record level, file level and so on. A relatively small number of powerful processors would generally be used for coarse-grain parallelism with information rarely being passed from one processor to the other. At the other extreme we find fine-grain parallelism where a large number of less powerful processors are used to execute programs with a large amount of communication between the processors.

- 2.2.2 Coupling -- The degree of coupling between the processing elements is another method commonly used to classify parallel processing systems. A system is considered to be tightly coupled if the processors share a common memory, as in the case of multiprocessors, or if the communication between the processors is good (irrespective of the underlying hardware/software mechanisms), as in the case of multicomputers. A loosely coupled system would have its processing elements located at greater distances from one another, as can be seen with a workstation cluster (used for distributed computing).

The issue of whether the system has been designed to be used for general purpose computing or special purpose applications (digital signal processing, for example) and the different amounts and types of synchronization amongst processors are other factors which help in the overall classification.

### 2.3 Interconnection Topologies for Multicomputer Systems

Multicomputers are types of parallel processing systems that consist of multiple processing nodes connected by a communication network. Each processor, also referred to as a node or a processing element, has computing, memory and communication resources. The computing resources perform the processing assigned to the node. The memory stores both program and data. The communication facilities are used to transmit and receive data from other processing nodes.

#### 2.3.1 Performance Criteria

The issues related to the performance of an interconnection network connecting a set of processing nodes are the following [5]:

2.3.1.1 Latency -- The message latency is the amount of time it takes a single message to travel between two processors. This performance metric depends on the time it takes a processor to prepare the message which is to be transmitted, the distance that the message has to travel, the amount of traffic prevalent in the network at that time and the length of time taken by the receiving node to process the message.

2.3.1.2 Bandwidth -- The bandwidth helps indicate how much traffic a network can handle. It is defined as the mean number of active memory modules in one transfer cycle of the interconnection network [6]. The message locality should be kept as high as possible to help preserve the available bandwidth and reduce the possibility of congestion due to too much message traffic in the network at any particular time.

2.3.1.3 Cost -- There are a number of factors which affect the cost of a network. The number of overall links (wires) in the network is a factor to be measured as each physical connection adds to the overall cost. The number of links required per node is also a cost factor. Additionally, the physical layout should also be as efficient as possible as packaging complexity adds to the cost. If the routers are locally controlled

and are of a fixed degree, the cost can be minimized. Also, if the network can be built from easily available components, the cost can be greatly reduced.

2.3.1.4 Reliability -- The reliability of a network is an important factor which has to be carefully considered in the case of interconnection networks, where the elements may number in the thousands and the possibility of component failure is quite high. The fault-tolerance of the network can be improved by providing multiple paths to connect processing nodes to each other. In the event of a failure in any link of the network, another path could be used and the network could continue to function in a fault-tolerant manner.

#### 2.3.2 Design Considerations

The processors and memory of a multicomputer's processing nodes are essentially the same as those that are used in single processor machines. The distinguishing feature in the case of the multicomputer processing nodes is the support for interprocessor communication that is used to enable the sharing of data between the nodes through the message-passing mechanism. Thus, the overall performance of the system is heavily dependent on the interconnection networks performance. The topology of an interconnection network defines the placement and the number of the communication links which are used to join the processing nodes in a multicomputer system. Figure 2.2 shows some of the popular *static* interconnection topologies in use today. The designer of an interconnection network has to consider a number of design issues and make a trade-off between these issues before selecting a particular topology [7]. The issues involved in making the decision are as follows:

2.3.2.1 Topology -- The interconnection network can be broadly categorized as being static or dynamic, with each class being further broken down into their own subclasses.

Figure 2.2 Static interconnection topologies

Static topologies are formed from point-to-point direct connections which will not change during program execution. They are used for fixed connections among subsystems of a centralized system or multiple computing nodes of a distributed system. They have been effectively used for problems with predictable communication patterns. Static topologies can be further classified based on the number of dimensions required for their layout. An example of a one-dimensional topology is the linear array. Two-dimensional topologies include the ring, star, tree and mesh. Three-dimensional topologies include the completely connected chordal ring and 3-cube-connected-cycles.

Dynamic topologies are implemented with switched channels, which are dynamically configured to match the communication demand in user programs. They have been found to be suitable for a wider range of problems than static topologies, but at a higher cost. They include buses, crossbar switches and multistage networks, which are often used in shared memory multiprocessors. Dynamic topologies are classified based on the number of stages that exist in the communication links between the nodes. A single-stage network has each communication link connected only to processing nodes. Processing nodes that do not have a direct link between them have to pass data through intermediate nodes when they want to communicate with each other. The individual links in this communication path are directly connected to pairs of processing nodes and hence these networks are also called direct networks. A multistage network consists of more than one stage of switching elements and is usually capable of connecting an arbitrary input terminal to an arbitrary output terminal.

2.3.2.2 Operation mode -- Networks can be classified as being synchronous or asynchronous, based on their mode of operation. *Synchronous* communication is used for processing in cases where communication paths are established synchronously for data manipulation functions or instruction broadcasts. The regularity of the data enables the same operations to be applied in parallel by all the processing elements, constraining hardware processes to perform in "lock-step." *Asynchronous* communication is needed for multiple processers in which communication is performed dynamically. The

individual processing elements can compete for common resources. Furthermore, the processing elements can communicate and cooperate with each other in order to improve the utilization of available resources.

2.3.2.3 Switching Strategy -- There are three techniques commonly used to transmit messages between processing nodes. The message can be transmitted as a whole, as in *circuit switching*, where an exclusive independent virtual circuit is established for a source/destination pair. This is accomplished by a signaling message. The path once established, is unavailable to any other source/destination pair until both the original source and destination agree to stop communicating with each other. After a path is set up, no further signaling for addressing purposes is required. One of the drawbacks of circuit switching is the fact that no communication is possible between any other source/destination pair if that pair needs to use any of the lines which are currently being used by an already established circuit.

In packet switching, the message is broken down into a series of small packets and then each packet is transmitted through the network from the source to the destination. The basic idea is to improve channel utilization by freeing up the channels on a path during periods in which the source and destination nodes are not communicating with one another. In the store-and-forward method, packets are routed towards their destination node without establishing a path beforehand. The packets are passed through a series of intermediate nodes. Each intermediate node receives the packets in a buffer (or store facility) where the node examines the packet's header information to determine where to forward the packet so that it gets closer to its final destination. The time it takes to receive and examine the packet headers and the time the message has to wait before a proper communication link becomes available are the main factors which affect the transmission time of a message.

Another method used to switch messages is *wormhole routing* (or cut-through switching) [8]. This method tries to combine the positive features of both circuit switching, as well as packet switching. The first packet of the message contains status information such as the source, destination and the message length. An intermediate node which receives this first packet examines it to determine where it is headed.

Each time a packet is forwarded through the network, additional packets of the message are transmitted. Wormhole routing, thus attempts to pipeline a message through the network at a grain size determined by the time required for routing at each intermediate node. If the packet encounters busy channels at the various intermediate nodes, it behaves like a packet switched network. On the other hand, if all the intermediate nodes are free, it behaves like a circuit switched network.

### 2.4 Communication and Synchronization Issues

The issue of how processors should communicate data is very important since the method employed affects the programming model as well as the communication cost [9]. There is a class of machines which use a single address space, commonly known as multiprocessors. These machines use the shared-memory model which allows the processors to directly reference data from the memory which could be either centralized or distributed, based on the physical location of the memory with respect to the processors. Centralized shared memory models are typically used by small-scale bus based multiprocessing systems. To enable the shared memory model to be used with a scalable architecture, the memory has to be distributed independently of its logical sharing. This approach is known as the distributed shared memory model and is used by the Cray T3D machine which uses the 3-dimensional torus topology to connect the processors together [10].

Most of the large scale multicomputers built to-date have used the message-passing model for communication due to the fact that they are simpler to build than the shared memory model. However, with the message-passing model, the compiler (or programmer) has to partition a program into separate processes that communicate explicitly, by sending messages rather than implicitly through memory. Figure 2.3 and 2.4 show a break-up of the MIMD classification into multicomputers and multiprocessors [2].

Figure 2.3 Taxonomy of MIMD Computers

Fig 2.4 (a) MIMD system with distributed memory

(b) MIMD system with shared memory

#### 2.4.1 Synchronization Issues in Shared Memory Computers

When a number of processors are acting concurrently, problems can arise when they try to read or modify the same data. A shared data object may be manipulated by operations that are implemented as sequences of events. If two processors concurrently perform such operations on the same data object, then one of them might be exposed to intermediate values produced by the other, and unpredictable results may occur. A concrete example would be in a situation where there is a stack or circular buffer that could be accessed simultaneously by two processors. One of the processors might modify the top of stack index and, before it has a chance to use this altered index to access data, the other processor could further modify the top of stack index resulting in the first processor producing incorrect results since it had unintentionally used the wrong data.

To prevent different processors from trying to access the same data simultaneously, a type of synchronization scheme known as "mutual exclusion" can be used. Mutual exclusion should be implemented in the "critical section" of the code so that access to the portions of code dealing with shared variables is given to only one competing process at a time. The problem with this method is that it can cause extensive delays when there are a large number of competing processes. The state when only one of the processors is in its critical section at any time is called "safe." However, there is always the possibility of creating a circular wait state called "deadlock," in which processes are waiting for events that cannot occur. The solution to the problem of mutual exclusion and deadlock is tricky. A state can occur where a process might wait forever for permission to enter its critical section and thereby "starve." To prevent this situation from occurring, a method for mutual exclusion can be adopted in which prioritization of the processes takes place such that a process that has been waiting for a long time will get precedence over a process that has recently tried to access the shared variable.

The classic mutual exclusion algorithms generally use "busy waiting," a method in which the competing processes for a critical section constantly seek to gain access to the section. Lamport's Bakery algorithm solves the problem of starvation by prioritizing the processes in a first-come-first-served basis

when they try to access their critical section [11]. A problem with this method is that the prioritized queue could become arbitrarily large and cause an overflow.

The synchronization of parallel processes could be carried out by low-level primitives at the machine instruction level. Implementing atomic (indivisible) instructions in hardware significantly eases the software designers task. The exchange instruction (EXG) found in the Motorola 68000 family and the SWAP instruction found in the SPARC architecture use a set of three actions which are indivisible. Test and Set instructions are also indivisible. Hence, the synchronization is blocking in nature since it allows only one process to be active at one time, blocking the actions of all the others. This is therefore also the type of "busy waiting" mutual exclusion method discussed above.

Semaphores, a mutual exclusion scheme invented by Dijkstra [12], uses a pair of higher level primitives that operate on non-negative integer variables called semaphores. The entry and exit into the critical section are encapsulated by these high-level primitives, thereby disallowing the critical section to be interrupted by other processes through their operation.

#### 2.4.2 Synchronization Issues in Distributed Memory Multicomputers

Distributed memory multicomputers consist of processor-memory pairs connected together by an interconnection network. Machines of this form typically have multiple address spaces and are commonly known as multicomputers. They use the message-passing model to communicate data between the processors. Machines like the mesh-connected Intel Paragon, TMCs fat-tree connected CM-5 and the hypercube connected network by NCUBE are examples of systems which use this form of communication [13]. In the case of message-passing computers, there is more self-synchronization than seen in communication through shared variables. If a message is not received for some reason after it has been sent or if it is overwritten by another message, then this creates a problem and the message has to be resent. In a message-passing parallel program, the constituent parallel parts or processes communicate via communication channels rather than through shared variables as is the case with shared-memory

systems. A channel provides a communication path between two processes and can be considered to be an abstraction of a physical communication link. In synchronous message-passing, each channel provides a direct link between two processes, and the sender blocks (or gets delayed) until the other process has received the message. The exchange of a message thus represents a synchronization point between the two processes.

## 2.5 Scalability of Parallel Processing Systems

Scalability is a common objective in the design of parallel processing systems. The term scalability has been interpreted in different ways by different people. People involved in algorithm design tend to view scalability in the context of the problem size, while people who work at the system level (hardware designers) tend to make the implicit assumption that the problem is scalable and then try to find an architecture on which to implement it. Thus the computer architect would define a scalable parallel computer to be one in which the interconnection scheme (and thus the number of processors) can be expanded without hurting the performance characteristic.

In 1967, Amdahl [14] put forth an argument which stated that even when the fraction of serial work in a given problem is small, say s, the maximum speedup obtainable from even an infinite number of parallel processors is only 1/s. It can be clearly seen that in this argument the notion of scalability is closely tied to notion of speedup. With this point in mind, a scalable architecture would have to exhibit speedup linearly proportional to p, the number of processors used. However, this point of view does not cover the whole picture. The problem here is that the speedup could be of two types, simple speedup which keeps the problem size fixed and scaled speedup which allows the problem size to grow with the machine size.

In the first case, Amdahl's law is seen to hold true. It has been shown that even a small number of sequential operations can significantly limit the speedup achievable by a parallel computer. For example, if 10 percent of the operations have to be performed sequentially, then even with an infinite number of

processors, the time required for the overall operation of the problem cannot be reduced by more than a factor of 10. The validity of this argument led to research in the area of massively parallel processing being in a dormant state for a very long time.

It was only after the problem was looked at from a different perspective, that there was renewed interest in this area. It was seen that when a faster computer was provided to solve a problem, it was usually not used just to solve the problem faster, but instead to solve a larger problem in roughly the same amount of time. Thus, scaled speedup allows the problem size (as measured by its serial complexity) to increase linearly with the number of processors. Because the opportunity for parallelism tends to grow with the size of the problem, the percentage of time required for the operations to be done in parallel tends to grow more rapidly than the serial time. A problem may grow either because a more complex system is being analyzed or because the same system is being analyzed to a higher degree of accuracy.

#### 2.5.1 Network scaling factors

There are several factors which are used to determine how performance characteristics scale with the number of processors being interconnected using a specific network topology. A network can be represented by the graph of a finite number of nodes linked by directed or undirected edges [2]. The number of nodes in a graph is called the network size. Some of the factors are as follows:

2.5.1.1 Node Degree -- The number of edges (links or channels) incident on a node is called the node degree. It reflects the number of I/O ports required per node and helps in determining the cost of the node. Thus, the node degree should be kept as small as possible. A constant node degree is highly desirable in order to achieve modularity in building blocks for scalable systems.

2.5.1.2 Network Diameter -- This is the maximum number of communication links that must be traversed to transmit a message between any source/destination pair along a shortest path. It places an upper bound

Chapter 2 20

on the delay required to propagate information throughout the network. It should be as small as possible to enable efficient communication through the network.

2.5.1.3 Bisection Width -- When a network is cut into two halves, the minimum number of edges (channels) along the cut is called the channel bisection width. It is used to help provide an indication about the maximum communication bandwidth along the bisection of a network.

Table 2.1 shows how the performance characteristics of interconnection networks scale with the number of processors being connected. The hypercube topology has high connectivity and a low network latency through the connection of each of the N processing elements to log N neighbors. It can be seen that the wire cost increases by log N while the latency is reduced by log N /  $\sqrt{N}$ . The mesh topology is relatively inexpensive, but the network diameter increases by a factor of  $\sqrt{N}$ , a high rate of increase, which is not very suitable since the maximum delay of a message from one of N processors to another should be as small as possible. The tree topology appears to be a good compromise, as it's latency is the same as that of a cube, while it's wire cost is the same as that of a mesh since it's node degree is independent of N. In fact, fat tree networks are considered "universal" in the sense that they can efficiently simulate any other network of the same volume [15]. In the table shown, networks with a higher performance are shown towards the top while networks which cost less are shown towards the bottom [7].

#### 2.6 Summary

In this chapter, an overview of multicomputer networks was presented. A classification of parallel processing architectures was provided along with performance criteria and design issues related to the various interconnection network topologies. Communication and synchronization issues of MIMD systems were analyzed. Scalability problems were discussed with respect to Amdahls Law and the factors affecting the scalability of parallel processing systems were enumerated. In the next chapter, various design issues related to the development of a single processing node, used in a message-passing multicomputer network, are addressed in detail.

Chapter 2 21

**Table 2.1 Network Scaling Factors** (Interconnection network tradeoffs showing how performance characteristics scale with the number of processors (N) being connected).

| Network<br>type      | Node<br>Degree | Network<br>Diameter | Number of links | Bisection<br>Width | Connectivity            | Wire Cost      |

|----------------------|----------------|---------------------|-----------------|--------------------|-------------------------|----------------|

| Linear<br>Array      | 2              | N - 1               | N - 1           | 1                  | 2 nearest neighbors     | N              |

| Star                 | N - 1          | 2                   | N - 1           | LN/2J              | 1                       | N              |

| Ring                 | 2              | LN/2                | N               | 2                  | 2 nearest neighbors     | N              |

| 2-D Mesh             | 4              | √N                  | 2N - 2√N        | √N                 | 4 nearest neighbors     | N              |

| Binary Tree          | 3              | log N               | N - 1           | 1                  | 3 nearest neighbors     | N              |

| Completely connected | N - 1          | 1                   | N(N -1)/2       | (N/2) <sup>2</sup> | any to any              | N <sup>2</sup> |

| Hypercube            | log N          | log N               | N logN/2        | N/2                | log N nearest neighbors | N logN         |

| 2-D Torus            | 4              | 2[√N/2]             | 2N              | 2√N                | 4 neighbors             | N              |

## Chapter 3

## **Design of A Single Processing Node**

#### 3.1 Introduction

In the early 1980's, microprocessor performance became a major research area with focus on quantitative metrics such as instruction execution rates and instruction counts. Sophisticated architectural techniques, which had been in widespread use in large mainframes and supercomputers, were incorporated into the microprocessors. For example, pipelining and high-performance memories had been used by supercomputers for many years. The introduction of RISC processors with a simple instruction set made it easier to migrate these techniques to the microprocessor.

This chapter describes the VHDL model of the processing nodes which will be used in the fat-tree multicomputer network. The structural and behavioral level VHDL models of the processing node are based on the DLX processor, a 32-bit reduced instruction set processor detailed in [1]. The reasons for choosing a RISC-based processor are pointed out. The instruction set of the DLX processor is described, along with the instruction format used by the processor. The efficient use of the memory hierarchy by parallel algorithms is considered in the design, with the result that each processing node has an individual cache memory included in it. In Section 3.9, the use of instruction level parallelism to decrease the cycles per instruction (CPI) of the processor and thereby improve its performance is explored with a suitable test-bench program.

### 3.2 Evolution of RISC Microprocessor Architectures

In the mid-seventies, studies were carried out by computer architects to study the frequency of the various instructions performed by complex computers of the time. It was observed that even the most sophisticated computers executed mostly simple instructions. The RISC-II microprocessor, designed at U.C. Berkeley in 1984, was a 32-bit microprocessor with 138 registers and a 330 ns cycle time. The MIPS design, initiated by Hennessey, was a 32-bit microprocessor with 16 registers and a 500 ns cycle time. The Swift (Simulation of Widely Interconnected Fat-Trees) processor is an alias for the DLX processor [1], which is similar to the commercially available MIPS R2000 processor. Table 3.1 shows a comparison of the major features of some of the older complex instruction set somputer (CISC) architectures. There were wide differences between the microprocessor architectures in their instruction size, data alignment, data addressing modes, page size and integer registers. Table 3.2 shows a comparison of the same set of features in the case of the more recent load/store architectures which are also known as reduced instruction set computer (RISC) architectures. In this table, there is a significant difference noticed in comparison to Table 3.1, with many of the features being identical in the various processors examined. Furthermore, RISC processors have fewer and simpler types of instructions than CISC processors and, consequently, a RISC instruction requires less processing logic to interpret than a CISC instruction. The higher instruction execution rate of RISC processors with their simple instruction sets and optimized software primitives are important reasons for the present trend towards RISC processors in parallel processing systems. In this thesis, the DLX processor has been chosen as the processing element to be included in the fat-tree multicomputer due to its features being very similar to those found in some of the commercially available reduced instruction set processors, as seen in Table 3.2. Some of the features seen most often in RISC-based processors are the following:

- Single cycle execution -- Most instructions are executed in a single machine cycle.

- Hardwired control with little or no microcode -- Microcode adds a level of complexity and raises the number of the cycles per instruction (CPI).

Table 3.1 Comparison of the major features of some of the older CISC architectures

|                          | IBM 360/370 | Intel 8086       | M68000               | DEC VAX      |

|--------------------------|-------------|------------------|----------------------|--------------|

| Date announced           | 1964/1970   | 1978             | 1980                 | 1977         |

| Instruction size (bits)  | 16,32,48    | 8,16,24,,48      | 16,32,48,64,80       | 8,16,24,,432 |

| Data alignment           | Yes/No      | No               | Yes (16-bit aligned) | No           |

| Data addressing modes    | 4           | 5                | 9                    | ≥ 14         |

| Page size                | 4 KB        |                  | .25 to 32 KB         | 0.5 KB       |

| Integer registers (size, | 16 GPR × 32 | 8 dedicated data | 8 data and 8 address | 15 GPR × 32  |

| model, number)           | bits        | × 16 bits        | ×32 bits             | bits         |

Table 3.2 Comparison of the major features of some of the recent RISC architectures (from [1])

|                         | Swift (DLX)   | Intel i860                              | MIPS R2000    | SPARC                   |

|-------------------------|---------------|-----------------------------------------|---------------|-------------------------|

| Date announced          | 1990          | 1989                                    | 1986          | 1987                    |

| Instruction size (bits) | 32            | 32                                      | 32            | 32                      |

| Data alignment          | Aligned       | Aligned                                 | Aligned       | Aligned                 |

| Data addressing         | 1 (16-bit     | 2 (16-bit                               | 1 (16-bit     | 2 (13-bit               |

| modes                   | displacement) | displacement,                           | displacement) | displacement,           |

|                         |               | indexed mode)                           |               | indexed mode)           |

| Page size               | 4 KB          | 4 KB                                    | 4 KB          | 4 KB                    |

| Integer registers       | 31 GPR × 32   | $31 \text{ GPR} \times 32 \text{ bits}$ | 31 GPR × 32   | 31 GPR $\times$ 32 bits |

| (size, model,           | bits          |                                         | bits          |                         |

| number)                 |               |                                         |               |                         |

- Load/Store, register to register design -- All computational instructions involve registers. Memory

accesses are made with only load and store instructions.

- Simple fixed-format instructions with few addressing modes -- All instructions are the same length (typically 32-bits) and have just a few ways to address memory.

- Pipelining -- The instruction set allows for the processing of several instructions at the same time.

- High performance memory -- RISC machines usually have at least 32 general-purpose registers and large cache memories.

#### 3.3 Instruction Set Architecture of the 32-bit DLX Processor

The DLX processor has thirty-two 32-bit general-purpose registers (GPRs). By convention, the value of register R0 is zero and it is a read-only register. All memory references are through loads or stores between memory and the general purpose registers. Accesses involving the GPRs can be to a halfword, or a word, and any of the GPRs may be loaded or stored, except that loading R0 has no effect. All ALU instructions are register-register instructions. The operations include simple arithmetic and logical operations: add, subtract, AND, OR, XOR, and shifts.

There are also compare instructions, which compare the contents of two registers  $(=, \neq, <, >, \leq, \geq)$ . If the condition is true, these instructions place a 1 in the destination register; otherwise they place the value 0. Since a register is 'set' by these operations, they are called set-equal, set-not-equal, set-less-than and so on.

Control is handled through a set of jumps and a set of branches. The jump instructions are differentiated by the two ways to specify the destination address and by whether or not a link is made. All branches are conditional. The branch condition is specified by the instruction, which may test the register source for zero or non-zero. The value found in the register could be a data value or the result of a compare. The branch target address is specified with a 16-bit signed offset that is added to the program counter. Table 3.3 shows a list of the instructions used by the processor. The instruction type is followed

**Table 3.3** A list of the instructions used by the Swift (DLX) processor model - Load and store instructions, arithmetic/logical instructions, and control-flow instructions.

| Instruction type/opcode | Instruction name                                                      | Example<br>Instruction        | Instruction meaning                                                                                                                              |

|-------------------------|-----------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| LH, SH                  | Load halfword,<br>store halfword                                      | LH R1,40(R3)<br>SH 2(R2),R3   | R1 $\leftarrow$ <sub>32</sub> (M[40+R3] <sub>0</sub> ) <sup>16</sup> ##M[40+R3] ##M[41+R3] M[2+R2] $\leftarrow$ <sub>16</sub> R3 <sub>1631</sub> |

| LW, SW                  | Load word,<br>store word                                              | LW R1,10(R0)<br>SW 5(R4),R3   | $R1 \leftarrow_{32} M[10+0]$<br>$M[5+R4] \leftarrow_{32} R3$                                                                                     |

| ADD, ADDI               | Add, add immediate                                                    | ADD R1,R2,R3<br>ADDI R1.R2.#3 | $R1 \leftarrow R2 + R3$ $R1 \leftarrow R2 + 3$                                                                                                   |

| SUB, SUBI               | Subtract, subtract immediate                                          | SUB R1,R2,R3<br>SUBI R1,R2,#3 | $R1 \leftarrow R2 - R3$ $R1 \leftarrow R2 - 3$                                                                                                   |

| AND, ANDI               | And, and immediate                                                    | AND R1,R2,R3                  | R1 ← R2 & R3                                                                                                                                     |

| OR, XOR                 | Or, exclusive or,                                                     | OR R1,R2,R3                   | R1 ← R2   R3                                                                                                                                     |

| LHI                     | Load high immediate                                                   | LHI R1, #42                   | $R1 \leftarrow 42##0^{16}$                                                                                                                       |

| SLL, SRL, SRA           | Shift left logical, shift right logical, shift right arithmetic       | SLL R1,R2,#5                  | R1 ← R2 << 5                                                                                                                                     |

| SLT, SGT,<br>SEQ,SNE    | Set less than, set greater<br>than, set equal to, set not<br>equal to | SLT R1,R2,R3                  | if (R2 <r3) <math="" r1="">\leftarrow 1 else R1 <math>\leftarrow</math> 0</r3)>                                                                  |

| BEQZ, BNEZ              | Branch GPR equal to zero,<br>branch GPR not equal to zero             | BEQZ R4, name                 | if (R4==0) PC $\leftarrow$ name;<br>((PC+4) - 2 <sup>15</sup> ) =< name <<br>((PC+4) + 2 <sup>15</sup> )                                         |

| J, JR                   | Jump, jump register                                                   | JR R3                         | PC ← R3                                                                                                                                          |

| JAL, JALR               | Jump and link, Jump and link register                                 | JALR R2                       | R31 ← PC + 4;<br>PC ← R2                                                                                                                         |

by the instruction name and an example instruction has been provided along with its meaning to make it easy to understand.

## 3.4 Instruction Format

The layout of the instruction word is called the instruction format. The selection of an instruction set requires a delicate balance between the number of instructions needed to execute a program, the number of clock-cycles needed by an instruction, and the speed of the clock. The instruction set is divided into three types of instruction formats. They are as follows:

The R-type (register) instruction is exactly 32 bits in length (the same size as that of a data word) and is used for ALU operations. The fields of this format are:

| 0 | 5  | 6 10 | 11 15 | 16 70 | 21   | 31 |

|---|----|------|-------|-------|------|----|

|   | ор | rs1  | rs2   | rd    | func |    |

The op field is the opcode, rs1 and rs2 are the source register addresses, rd is the destination register address and the func field selects the variation of the operation in the op field.

The I-type (immediate) instruction is used primarily for data transfer operations. The fields of this format are:

| 0 | 5  | 6 10 | 11 15 | 16 | 31    |

|---|----|------|-------|----|-------|

|   | op | rs1  | rd    |    | immed |

The op field is the opcode, rs1 is the source register address, rd is the destination register address and the immed field is an immediate displacement.

## rd ← rs1 op immed

It can be observed that the formats of the R-type and I-type instructions are similar. The first three fields of these two formats have the same length with the fourth field in the I-type instruction being equal in length to the last two fields of the R-type instruction. The first field (the opcode), is used to distinguish between these two formats. Each format is assigned a set of values in this field so that the hardware

knows whether to treat the last half of the instructions as two fields (R-type) or as a single field (I-type).

The conditional branch instructions use the I-type instruction format.

The J-type (jump) instruction format is the simplest of the three types. It consists of the first 6 bits used for the opcode and the rest of the bits are used for the address field and can be used for both jump and jump-and-link instructions.

# 3.5 Basic Steps of Execution

The processor contains the hardware components for processing instructions and data. It consists of a control unit and a datapath which together supervise and implement the various data processing tasks. The control unit is the part that effects the retrieval of instructions in proper sequence, the interpretation of each instruction, and the application of the proper signals to the arithmetic units and the other parts.

All instructions start by using the program counter to supply the instruction address to the instruction memory. After the instruction is fetched, the register operands used by the instruction are determined by examining the appropriate fields of that instruction. Once the register operands have been fetched, they can be operated on to compute a memory address (for a load or store), to compute an arithmetic result (from an integer arithmetic-logic instruction), or a compare (branch). If the instruction is an arithmetic-logic instruction, the result from the ALU must be written to the result register. If the operation is a load or a store, the ALU result is used as an address to either store a value from the register or load a value from memory into the registers. The result from the ALU or memory is written back into the register file. Branches require the use of the ALU output to determine the next instruction address, which requires some control logic. Figure 3.1 displays an abstract view of the implementation of the processor subset. For the processor instruction set, all instructions can be broken down into five basic steps as follows:

Figure 3.1 An abstract view of the implementation of the processor subset, showing the major functional units and the connections between them.

### i) Instruction fetch step

$MAR \leftarrow PC$

-- Send the program counter (PC) to a memory that contains

$IR \leftarrow M[MAR]$

-- the code to fetch the instruction

## ii) Instruction decode/register fetch step

$A \leftarrow Rs1$

-- Decode the instruction and access the register file to

$B \leftarrow Rs2$

-- read the instructions

$PC \leftarrow PC + 4$

-- Increment the PC to point to the next instruction

## iii) Execution/effective address step

The ALU operates on the operands, performing one of three functions depending on the instruction type (as discussed earlier):

## Memory reference

MAR  $\leftarrow$  A + (IR<sub>16</sub>)<sup>16</sup> ## IR<sub>16..31</sub> -- The ALU adds the operands to form the effective address

$MDR \leftarrow Rd$

-- The memory data register (MDR) is loaded for a store

# **ALU Instruction**

ALU  $\leftarrow$  A or (B or (IR<sub>16</sub>)<sup>16</sup> ## IR<sub>16..31</sub>) --The ALU performs the operation specified by the opcode

-- on the value in A and on the value in B or the sign-

-- extended immediate

## Branch/Jump

ALU  $\leftarrow$  A or (B or (IR<sub>16</sub>)<sup>16</sup> ## IR<sub>16..31</sub>) -- The ALU adds the PC to the sign-extended immediate

Cond  $\leftarrow$  (A op 0)

-- value to compute the address of the branch target

#### iv) Memory access/branch completion step

A memory reference instruction will need to access the memory containing the data to complete a store or get a word that is being loaded. An arithmetic logic instruction must write the data from the ALU back into a register.

MDR  $\leftarrow$  M[MAR] -- If the instruction is a load, data returns from memory

or  $M[MAR] \leftarrow MDR$  -- If the instruction is a store, data is written to memory

If (cond)  $PC \leftarrow ALU_{output}$  (branch) -- If the instruction branches, the PC is replaced with the

-- branch destination address

### v) Write-back step

$RD \leftarrow ALU_{output}$  or MDR -- Write the result into the register file, whether coming from -- the memory or from the ALU

## 3.6 VHDL Model of the Datapath

The datapath within the DLX computer consists of the execution units such as the arithmetic logic units, the registers, and the communication paths between them. Figure 3.2 shows a block diagram of the major functional units and the major connections between them. The paths for control are seen from the control unit to the ALU and the various registers. The paths for data transfer are seen between the S1 bus, S2 bus, Dest bus and the various components. The processor uses three buses: S1, S2 and Dest. The only path from the S1 and S2 buses to the Dest bus is through the ALU. It has two operand input ports, a result output and condition code output ports.

The behavior of the ALU has been implemented using a VHDL process statement, which is sensitive to changes on the operand and command input ports [16]. There are three condition code (CC) register bits which are updated after each arithmetic or logical instruction. The zero bit is set if the result is zero. The negative bit is set if the result of an arithmetic instruction is negative, and is undefined after logical instructions. The overflow bit is set if the result of an arithmetic instruction exceeds the bounds of representable integers, and is also undefined after logical operations.

The register file consists of a set of registers that can be read and written by applying a register number to be accessed. From Figure 3.2 it can be seen that there are two read ports with two data bus outputs (q1 and q2), and the write port has a data input (d3). To write a register, three inputs need to be specified: a register number, the data to be written and a clock that controls the writing to the register.

Figure 3.2 Block diagram of the 32-bit DLX processor

The behavior of a register is implemented with a VHDL process statement. When any of the inputs change, the write port enabled is

checked first, and if asserted, the addressed data is fetched, and driven onto the corresponding data output bus. If the port is disabled, the data output bus driver is disconnected.

The function of a latch is to store a signal with the output being equal to the value of the stored state inside the element. It has an enable input bit, latch\_en, a bit vector input d, and a bit vector output q. When latch\_en is '1,' changes on d are transmitted through to q. When latch\_en changes to '0,' any new value on d is ignored, and the current value on q is maintained. In the datapath shown in Figure 3.2, there are latches on the two outputs of the register file (A and B) and a latch on the input (C).

A multiplexer performs the function of selecting as its output, one of its inputs, that is specified by a control. A two-input multiplexer could be specified with a select input bit, two bit vector inputs i0 and i1, and a bit-vector output y. A VHDL concurrent signal assignment statement, which uses the value of the select input to determine which of the two bit-vector inputs is passed through to the output.

The other registers which are part of the state of the machine are the program counter (PC) and the interrupt address register (IAR). The PC is a register used to hold the address of the current instruction being executed. The memory address register (MAR), memory data register (MDR) and temporary registers are used in the execution of instructions.

# 3.7 Processor Bus Architecture

The processor communicates with its memory over synchronous 32-bit address and data buses. The two clock inputs, phi1 and phi2, provide a two-phase non-overlapping clock for the processor. Each cycle of the phi1 clock defines one of threee bus states: Ti (idle), T1 or T2. Bus transactions consist of a T1 state followed by one or more T2 states, with Ti states between transactions.

During an idle state Ti, the processor places the memory address on the address bus to begin the transaction. The next state is a T1 state. After the leading edge of the phi1 clock, the processor asserts

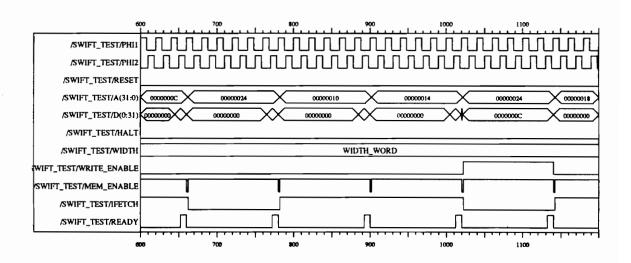

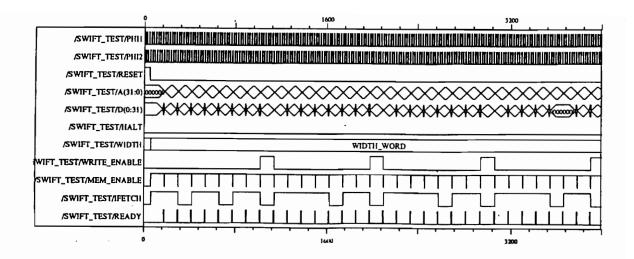

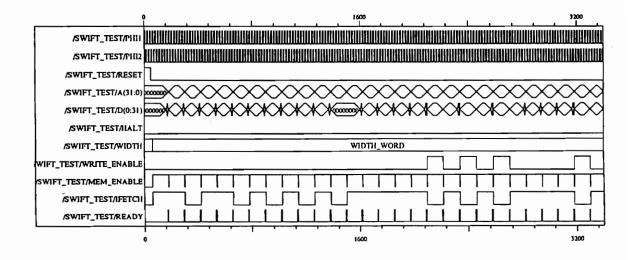

transaction. The processor also asserts the ifetch signal if it is reading instructions. It always leaves the write\_enable signal negated during read transactions. Figure 3.3 shows a memory read operation. The value to be read by the processor, (5), is put on the data bus at address 20. It can be seen that the ifetch signal is negated after the data has been read by the processor. Figure 3.4 shows a memory write operation. Write\_enable is seen to be asserted at the time that the value to be written, (C), is put on the data bus at address 24. This value has been obtained by adding the number 5 and 7 to obtain C (Hex). After the data has been written by the processor, the write\_enable signal is negated to indicate that the transaction is complete. At the end of the transaction there is a null signal assignment to the data bus port, indicating that the processor is disconnecting itself from the data bus. In the next section, the reasons for including a local cache memory in each processing node of a multicomputer are discussed.

# 3.8 Cache Design Issues