# Planar Magnetic Integration and Parasitic Effects for a 3 KW Bidirectional DC/DC Converter

### Jeremy Ferrell

Thesis submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

Masters of Science

In

Electrical Engineering

Approved:

|            | Jason Lai, Chairman |          |

|------------|---------------------|----------|

| Alex Huang |                     | Yilu Liu |

August 28 2002

Keywords: Planar, transformer, inductor, integration, parasitic, leakage inductance, trace inductance

Copyright 2002, Jeremy Ferrell

# Planar Magnetic Integration and Parasitic Effects for a 3 KW Bidirectional DC/DC Converter

### **Jeremy Ferrell**

### **Abstract**

Over the recent years many people have been trying to reduce the size and weight of magnetic components and thus the overall system [19]. One attempt at this is to increase the switching frequency of the system. However, this attempt has its limitations due to increased device switching losses. Device limitations usually confine this frequency to lower value than is desired.

An effective approach, reducing the size and weight is to use the planar magnetics for possible integration with the power circuit and thus eliminating the associated interconnections. Planar magnetics uses the printed circuit board as the windings. This will allow the magnetic component to be implemented into the circuit. The integration of the magnetic components and power circuit will decrease the number of connections, reduce the height, and ensure the parasitic repeatability. Having external connections can cause problems in the system. In this case the system must carry a large amount of current. The connections can cause heating from resistance and inductance of the connection. The planar approach also will decrease the height of the system. This is because the planar magnetic cores have a higher surface area with a decreased height. This can reduce the height of the system by 25 %- 50 % [ 19 ]. The parasitic repeatability is also a very important factor. In many cases the typology relies on the parasitic elements for energy storage. Since, the parasitic elements are mainly a result from the geometry of the system; and the planar system has the windings made from the printed circuit board, the parasitic elements will be very consistent through the manufacturing process. For topologies that rely on the parasitic elements for soft switching, the planar design can incorporate parasitic elements with the leakage components for the soft-switching requirement.

This thesis redefines the conventional term of leakage inductance as the sum of a set of lumped parasitic inductances and the transformer leakage inductance for the integrated planar magnetics and inverter power circuitry. For the conventional non-integrated transformer, either planar or non-planar, the leakage inductance is defined between two terminals of the transformer. However, for the integrated planar magnetics, the new lumped parasitic and leakage inductance should include the inverter switch and dc bus interconnections.

The transformer was first designed using a closed-form solution for a known geometry with different copper thickness. The calculated leakage inductance was then verified with finite element analysis and the impedance analyzer measurement. It was found that the theoretical calculation and the finite element analysis results agreed very well, but the measurement was more than one order of magnitude higher. This prompted the study of interconnect parasitics. With geometrical structure and proper termination and lumping, a set of parasitic inductances were defined, and the results were verified with measurements of both impedance analyzer and phase-shifted modulated full-bridge inverter testing.

In addition to parasitic inductance analysis, the flux distribution and associated thermal performance of the planar structure were also studied with finite element analysis. The resulting plots of flux distribution and temperature profile indicate the key locations of mechanical mounting and heat sinking. Overall the thesis covers essential design considerations in electrical, mechanical, and thermal aspects for the planar magnetics integration.

### Acknowledgements

I would like to express my sincere appreciation to my advisor Dr. Jason Lai. He not only has taught me a great amount in the power electronics field, but has also been an understanding and motivating advisor. He would always make time for his students, no matter how busy he was. Dr. Lai's imagination, creativity, and perseverance have been a great learning experience that can be used for my future in the power electronics industry.

I would also like to thank my other committee members, Dr. Alex Huang and Dr.Yilu Liu. Both of their classes and insight have been very appreciated during my time as a graduate student. They always wanted their students to learn to their fullest potential. Dr. Huang and Dr. Liu always made their lectures interesting and stimulating. I know the knowledge they have provided will be very useful in my future career.

I would like to acknowledge the rest of the CPES faculty and staff. All the people associated with this lab have encouraged and helped whenever possible. They all worked hard and enjoyed helping the students achieve their goals. All of the staff made me feel comfortable and welcomed from the first day I started in the CPES lab.

CPES will not be where it is today without the extensive knowledge and hard work from the students. No matter how busy the students were they would always take the time to answer a question or help me with a problem I was having. I feel sure that I would not have completed this thesis without the help from the students.

I would especially like to thank Troy Nergaard and Xudong Huang for their help on this project. Their knowledge proved to be very valuable. Many other students I would like to thank, Leonard Leslie for his intriguing discussions and Francisco Canales for his insight on many different subjects. Also, all the other students that have been friends and great colleagues, Cory, Carl, Lincoln, Elton, Chris, Jerry, Matt, Changrong, Tom, Marcelo, Sebastian, and Julie. Also, my friends outside of CPES reminded me that there is life outside of the lab.

I would like to thank my parents and brothers for their support and encouragement over all the years of my college career. They always supported my decision and sympathized with my hard work and late nights.

Finally, I would like to thank my wife Kristy. She has always stood behind me and supported me through my graduate studies. Even during the late nights and weekends that were required to complete my degree, she was always supportive and understanding.

The research reported in this thesis was made possible from the support of Ballard Electric Drives. Lizhi Zhu and Roy Davis provided a great amount of insight and understanding into the power electronics and automotive industry.

## **Table of Contents**

| Chapter 1 | Introduction                                             | 1        |

|-----------|----------------------------------------------------------|----------|

| 1.1.      | Overview of the Converter System                         | 1        |

| 1.2.      | Design Challenges                                        | 4        |

| 1.2.1     | . Temperature                                            | 4        |

| 1.2.2     | . Vibration                                              | 6        |

| 1.2.3     | . Operating Conditions                                   | 6        |

| Chapter 2 | Planar Transformer Design                                | <i>7</i> |

| 2.1.      | Introduction                                             | 7        |

| 2.2.      | Boost Mode Operation                                     | 8        |

| 2.3.      | Buck Mode Operation:                                     | 10       |

| 2.4.      | Skin Effect                                              | 10       |

| 2.5.      | Copper Weight:                                           | 11       |

| 2.6.      | Copper Loss:                                             | 14       |

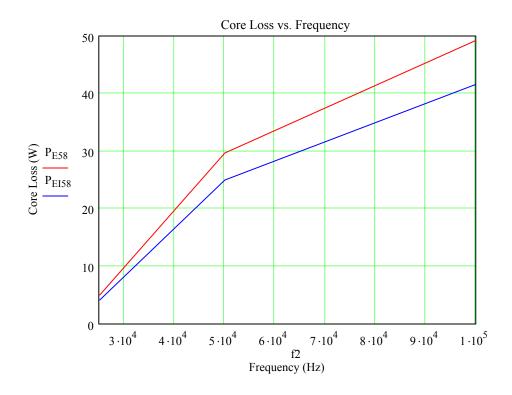

| 2.7.      | Core Loss:                                               | 16       |

| 2.8.      | Flux Density:                                            | 19       |

| 2.8.1     | Boost Mode                                               | 20       |

| 2.8.2     | Buck Mode                                                | 20       |

| 2.9.      | Conclusion                                               | 21       |

| Chapter 3 | B. Parasitic and Leakage Inductance                      | 23       |

| 3.1.      | Introduction                                             | 23       |

| 3.2.      | Transformer Leakage Inductance                           | 23       |

| 3.2.1     | . Theory                                                 | 23       |

| 3.2.2     | PCB Layout                                               | 24       |

| 3.3.      | Calculation                                              | 25       |

| 3.4.      | Maxwell™ Modeling for the Transformer Leakage Inductance | 29       |

| 3.4.1.     | Introduction                                | 29 |

|------------|---------------------------------------------|----|

| 3.4.2.     | Define Simulation                           | 30 |

| 3.4.3.     | Eddy Current Solver                         | 33 |

| 3.4.4.     | PEMag                                       | 37 |

| 3.4.5.     | Maxwell Simulation Conclusion.              | 41 |

| 3.5. Pa    | arasitic Inductance                         | 42 |

| 3.5.1.     | Theory                                      | 42 |

| 3.5.2.     | Inductance Source                           | 42 |

| 3.5.3.     | Calculation                                 | 44 |

| 3.6. In    | npedance Analyzer Measurements              | 45 |

| 3.6.1.     | Measurement Setup                           | 45 |

| 3.6.2.     | Equivalent circuits and measurement results | 46 |

| 3.6.3.     | Leakage Inductance derivation               | 49 |

| 3.7. Ci    | ircuit Simulation                           | 51 |

| 3.7.1.     | Introduction                                | 51 |

| 3.7.2.     | Theory                                      | 51 |

| 3.7.3.     | Conclusion                                  | 59 |

| 3.8. Ci    | ircuit Implementation                       | 59 |

| 3.8.1.     | Conclusion                                  | 63 |

| 3.9. Co    | onclusion                                   | 64 |

| Chanter 4  | Thermal Modeling                            | 65 |

| _          |                                             |    |

| 4.1. In    | troduction                                  | 65 |

| 4.2. M     | axwell™ Modeling                            | 65 |

| 4.3. Co    | onclusion                                   | 71 |

| Chapter 5. | Inductor Design                             |    |

| 5.1. In    | troductiontroduction                        | 72 |

| 5.2. Co    | ore selection                               | 73 |

| 5.2.1.     |                                             |    |

vii

| 5.3.         | EE58 Core                      | 75    |

|--------------|--------------------------------|-------|

| 5.3.         | . Turns                        | 75    |

| 5.3.         | Copper Weight                  | 77    |

| 5.4.         | EE64 Core                      | 78    |

| 5.4.         | . Turns                        | 78    |

| 5.3.1. Turns | 79                             |       |

| 5.5.         | Air Gap solutions              | 79    |

| 5.6.         | Layout                         | 83    |

| 5.7.         | Conclusion                     | 85    |

| Chapter      | 6. Conclusions and Future Work | 87    |

| 6.1.         | Conclusion                     | 87    |

| 6.2.         | Future Work                    | 89    |

| Appendi.     | A Transformer Design           | 90    |

| Appendi.     | B Parasitic Calculation        | . 103 |

| Appendi.     | C Inductor Design              | . 106 |

| Referenc     | es                             | . 111 |

| Vita         |                                | . 115 |

# **List of Figures**

| Figure 1-1. Bi-directional DC/DC converter                                    | 1  |

|-------------------------------------------------------------------------------|----|

| Figure 1-2. Buck Mode Operation                                               | 2  |

| Figure 1-3. Boost Mode Operation                                              | 3  |

| Figure 1-4. B-H curve for 3C90 ferrite                                        | 4  |

| Figure 1-5. Permeability vs. Temperature                                      | 5  |

| Figure 2-1. Thermal change with load                                          | 9  |

| Figure 2-2. Copper weight vs. frequency                                       | 11 |

| Figure 2-3. Schematic representation of transformer                           | 13 |

| Figure 2-4. Hysteresis loop                                                   | 17 |

| Figure 2-5. Core loss for EI configuration at 2500G                           | 19 |

| Figure 2-6. Boost mode waveforms                                              | 20 |

| Figure 2-7. Waveforms for buck mode                                           | 21 |

| Figure 3-1 Non-ideal transformer model                                        | 24 |

| Figure 3-2. PCB layout configurations                                         | 25 |

| Figure 3-3. 3-D view of transformer                                           | 26 |

| Figure 3-4 Leakage inductance calculated from the secondary                   | 28 |

| Figure 3-5. 3-D view of transformer                                           | 31 |

| Figure 3-6. 2-D transformer model                                             | 32 |

| Figure 3-7. 2-D PCB model                                                     | 32 |

| Figure 3-8. B-H for 3C90.                                                     | 33 |

| Figure 3-9. Mesh used in simulation                                           | 34 |

| Figure 3-10. Flux Density                                                     | 35 |

| Figure 3-11. Magnitude of flux density                                        | 36 |

| Figure 3-12. Magnitude of H-field                                             | 37 |

| Figure 3-13. PEMag simulation figure                                          | 38 |

| Figure 3-14. 2oz simulation results                                           | 40 |

| Figure 3-15. Simulation structures                                            | 40 |

| Figure 3-16. Leakage inductance when even current distribution is not assumed | 41 |

| Figure 3-17. PCB Layout                                                       | 43 |

| Figure 3-18. Schematic representation of parasitic inductance                  | 44 |

|--------------------------------------------------------------------------------|----|

| Figure 3-19. Measurement circuit 1                                             | 46 |

| Figure 3-20. Measurement circuit 2                                             | 47 |

| Figure 3-21. Equivalent circuit 3 for measuring the trace inductance           | 48 |

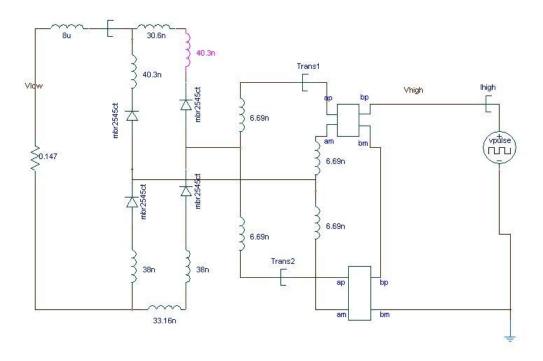

| Figure 3-22. Simulation schematic                                              | 52 |

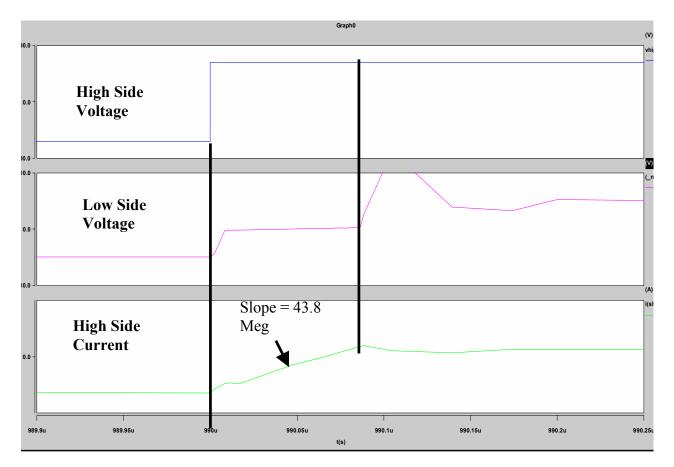

| Figure 3-23. High side waveforms.                                              | 52 |

| Figure 3-24. Saber simulation schematic with no trace inductance               | 54 |

| Figure 3-25. Saber simulation results with no trace inductance                 | 55 |

| Figure 3-26. Saber simulation results with no trace inductance                 | 56 |

| Figure 3-27. Saber schematic with trace inductance                             | 57 |

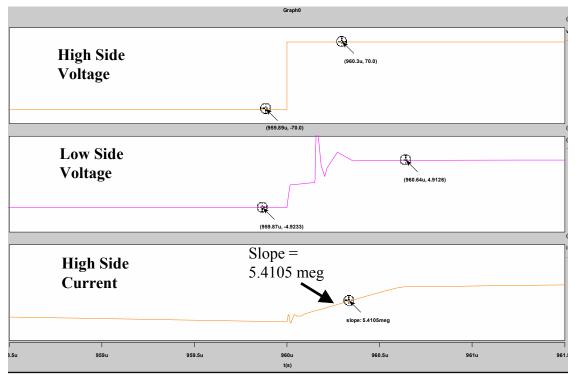

| Figure 3-28. Saber simulation with trace inductance.                           | 58 |

| Figure 3-29. Saber results adding trace inductance                             | 58 |

| Figure 3-30. Measurement setup                                                 | 60 |

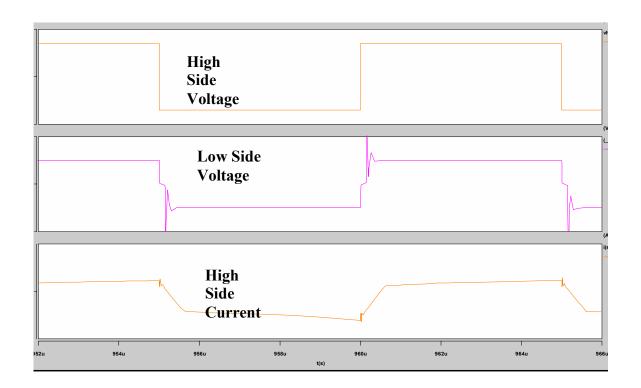

| Figure 3-31. Measurement Waveforms                                             | 61 |

| Figure 3-32. Measurement results for 89 kHz and 70 V input                     | 62 |

| Figure 3-33. Measurement results for 26 kHz switching frequency and 50 V input | 63 |

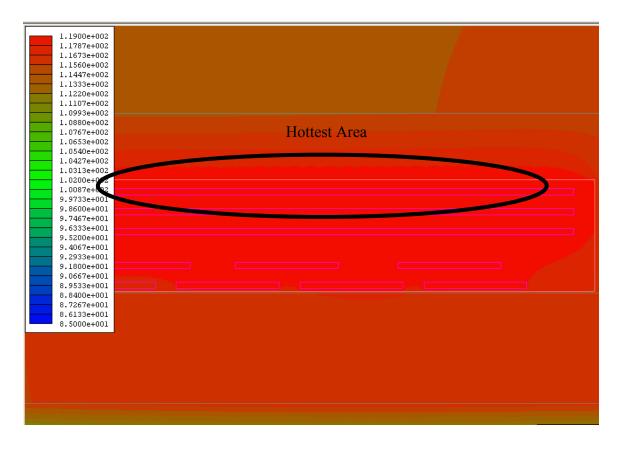

| Figure 4-1. Mesh used for thermal analysis                                     | 66 |

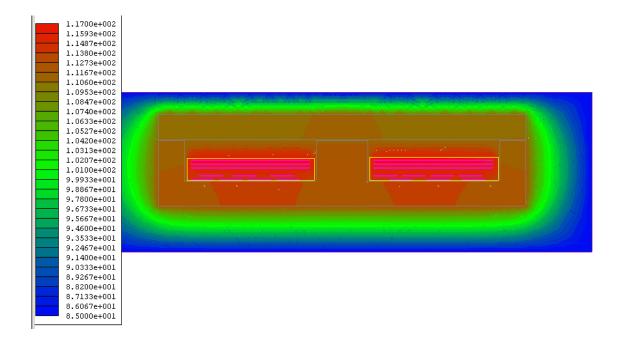

| Figure 4-2. Temperature distribution                                           | 67 |

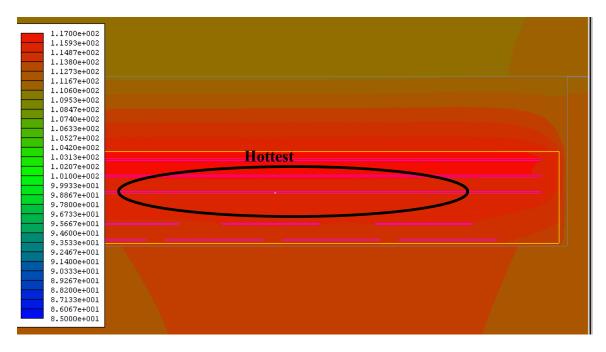

| Figure 4-3. Temperature of PCB area.                                           | 68 |

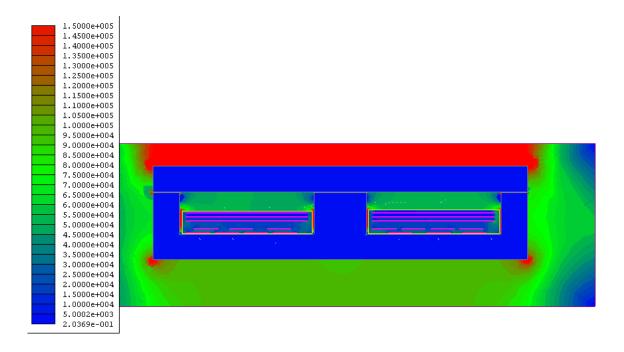

| Figure 4-4. Temperature gradient                                               | 69 |

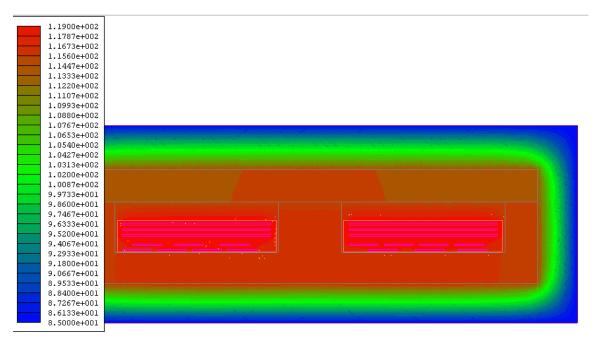

| Figure 4-5. Temperature distribution for 6 oz copper                           | 70 |

| Figure 4-6. Temperature of PCB area.                                           | 71 |

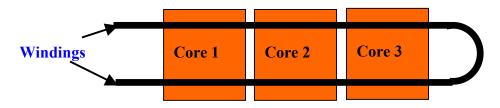

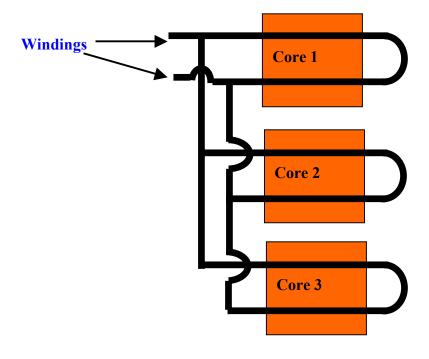

| Figure 5-1. Series core configuration.                                         | 73 |

| Figure 5-2. Parallel winding structure                                         | 74 |

| Figure 5-3. Flux fringing.                                                     | 76 |

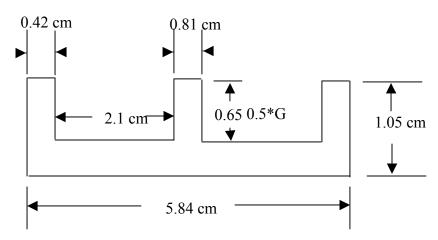

| Figure 5-4. Philips E58 core                                                   | 76 |

| Figure 5-5. E64 Core.                                                          | 78 |

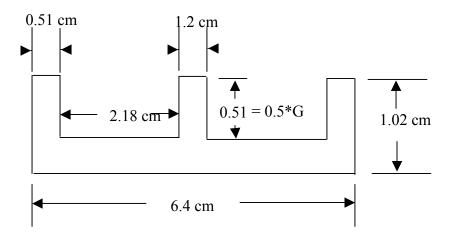

| Figure 5-6. Effective permeability depending on gap length                     | 81 |

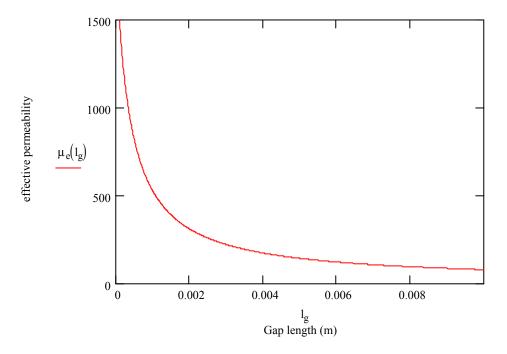

| Figure 5-7. Number of turns versus gap length                                  | 82 |

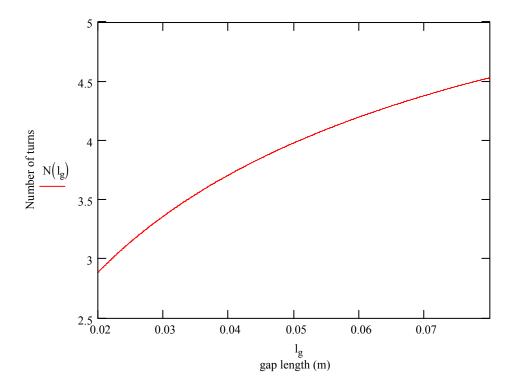

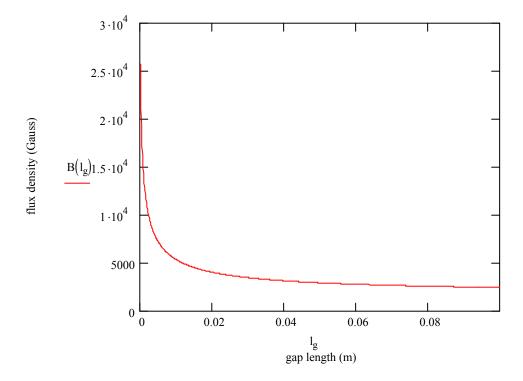

| Figure 5-8. Maximum flux density as a function of gap length                   | 83 |

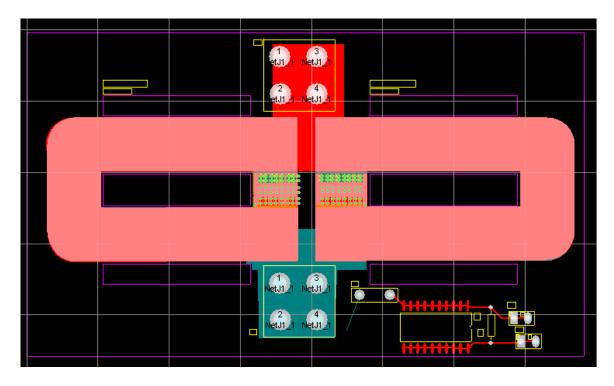

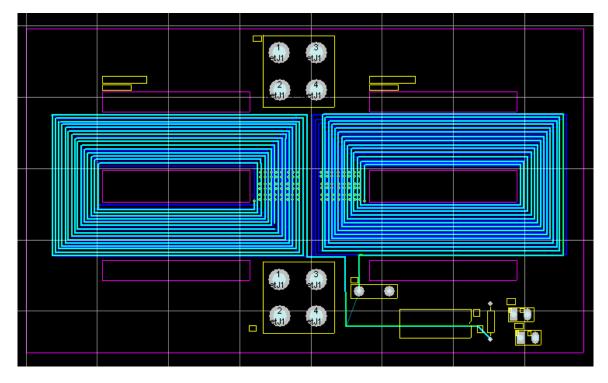

| Figure 5-9. PCB layout for inductor                                            | 84 |

| Figure 5-10.                                   | Auxiliary winding | configuration | <br>85 |

|------------------------------------------------|-------------------|---------------|--------|

| <i>O</i> · · · · · · · · · · · · · · · · · · · | J J               | <i>O</i>      |        |

List of Figures xi Jeremy Ferrell

## **List of Tables**

| Table 1-1. System Operation                      | 6  |

|--------------------------------------------------|----|

| Table 2-1. Transformer design specifications     | 8  |

| Table 2-2. Copper weight conclusion              | 14 |

| Table 2-3. Calculated winding resistances        | 16 |

| Table 2-4. Material Comparison                   | 18 |

| Table 3-1. $h_{\Delta}$ for different cases.     | 28 |

| Table 3-2. Calculated leakage inductance         | 29 |

| Table 3-3. Calculated trace inductances          | 45 |

| Table 3-4. Inductance measurements               | 48 |

| Table 3-5. Measurement equations                 | 50 |

| Table 3-6. Inductances using different equations | 50 |

| Table 3-7. Measurement Results                   | 64 |

| Table 4-1. 2 oz copper parameters                | 67 |

| Table 4-2. 6oz copper parameters                 | 69 |

| Table 5-1. Planar inductor specifications        | 72 |

| Table 5-2. Core summary                          | 79 |

## **Chapter 1.** Introduction

The effective use of the magnetic components is essential to the successful operation of any switching power supply. It depends on the application to determine what the most important parameter that is to be controlled. In some cases, the most important parameter is the cost. In this case the planar design might not provide as much benefit as the wire wound transformer. In other cases, the parasitic repeatability and low profile is the most important parameter, the planar design is a better choice. In many cases the use of planar magnetics would not be beneficial to the implementation of the product. It was decided for this particular work that the planar design was needed to achieve the parasitic repeatability, weight, size, and thermal management encountered in its working environment.

### 1.1. Overview of the Converter System

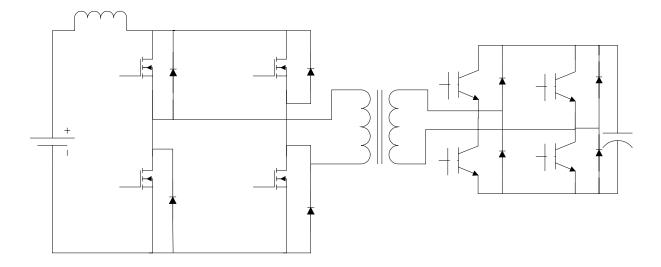

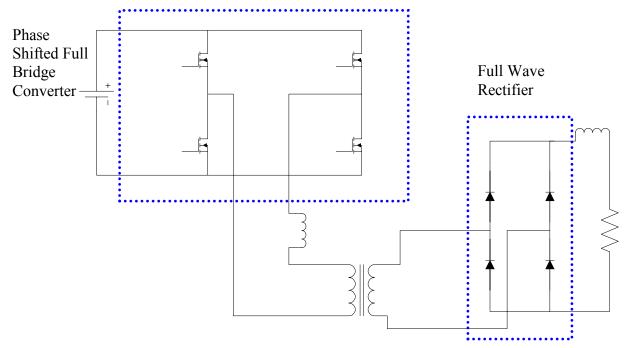

This work investigated a 3 kW bi-directional DC-DC converter to be used in an automotive application. A bi-directional converter implies that the system can operate as both a boost converter and a buck converter, depending on the direction of power flow. Figure 1-1 shows the basic circuit diagram for the bi-directional converter [ 12 ] [ 14 ].

Figure 1-1. Bi-directional DC/DC converter

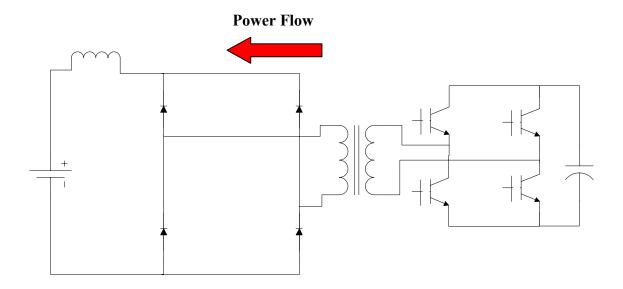

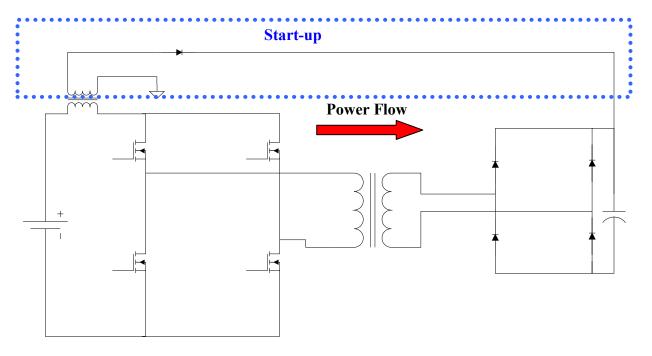

This typology is very useful as a battery charger to supplement an alternative energy source. A battery is added to an alternative energy systems because currently the alternative energy sources are very expensive. Therefore, they are sized to handle the continuous load, and the battery is sized to handle any transients in the system. This configuration will minimize the overall cost of the system. When the alternative energy source such as solar cells or a fuel cell is operating and the load is low, the battery can be charged. In this case the system will operate as buck converter. The inductor is used as a filter to ensure that the battery only receives a DC voltage and current. Figure 1-2 shows a schematic of the system operating in buck mode. However, when the load is higher than the alternative energy source can supply, then the battery can supply the extra energy required, and the system will operate in boost mode. This mode will transfer energy from the battery to the load.

Figure 1-2. Buck Mode Operation

Figure 1-3 shows a schematic of the system operating in boost mode. In boost mode the inductor is used as the boost inductor. It should be noticed that during the startup condition the output capacitor behaves like a short-circuit, and there is a need to use a coupled inductor to operate the converter as a flyback converter, to help build up the capacitor voltage. The flyback converter operation will be disabled after the capacitor voltage is higher than the input voltage multiplied by the turns-ratio of the coupled inductor.

Figure 1-3. Boost Mode Operation

During both modes of operation the battery must be closely monitored. In the buck mode the battery should not be overcharged and during the boost mode the battery cannot sustain the load for an extended period of time.

The scope of the project is to design and integrate, the planar magnetics into the bidirectional converter, and not design a control scheme for battery protection.

## 1.2. Design Challenges

Since this work was to be implemented in an automotive application, the operating environment is much harsher than many other applications. These conditions can have adverse effects on the magnetic design and reliability. If the environment is not taken into account during the design process then the reliability of the system will be very low.

#### **1.2.1.** Temperature

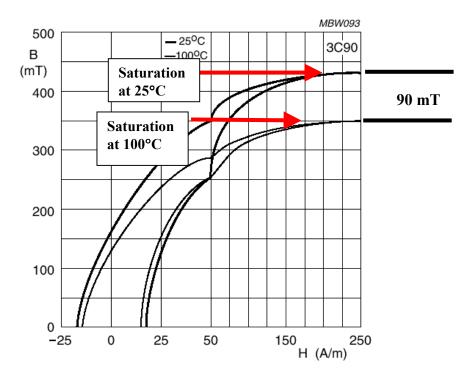

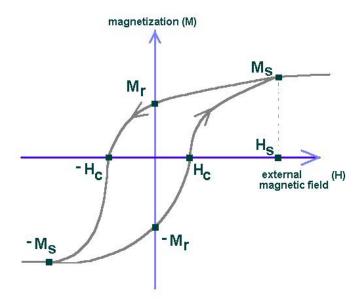

The magnetic components were expected to operate at an ambient temperature of 85°C. This temperature causes many different problems in the design. First, the magnetic properties change with temperature. Figure 1-4 shows the B-H curve for 3C90 ferrite material made by Philips. This figure proves that the saturation flux density will decrease by 90 mT as the temperature changes from 25°C to 100°C. Since the ambient is 85°C, the maximum flux density that can be allowed has to be decreased to avoid saturation of the magnetic component.

Figure 1-4. B-H curve for 3C90 ferrite

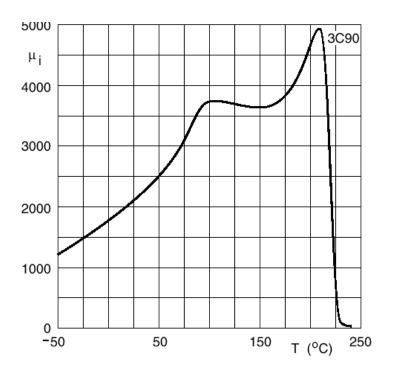

Another change in the ferrite material is the initial permeability of the material. Since the inductance is related to the permeability of the ferrite, the inductance will change as the

temperature changes. This not only affects the inductance of the inductor but also affects the leakage inductance of the transformer. Figure 1-5 shows how the initial permeability can change with temperature.

Figure 1-5. Permeability vs. Temperature

Since planar magnetics use the printed circuit board (PCB) as the windings, the breakdown temperature of the insulation material must also be considered. The insulation material is commonly rated by the glass transition temperature. This is the temperature at which the insulation material starts to change its properties. For that reason the system should not reach this temperature. Two different FR4 materials are currently being implemented in PCBs. The first is FR406, which has a glass transition temperature of 170 °C. The second is FR408, which has a glass transition temperature of 180°C. With an ambient temperature of 85°C it will take a temperature rise of 85°C-95°C to reach the glass transition temperature. The thermal expansion is another important factor to be considered to ensure a highly reliable system. FR4 has a very similar thermal expansion coefficient as copper. This implies that over time the printed circuit

board (PCB) will not separate due to the thermal cycles of the system. As the copper expands with heating the FR4 will also expand at nearly the same rate. If a different insulation material is used then the thermal expansion must be considered for long term reliability.

#### 1.2.2. Vibration

The automotive environment is one with excessive vibration. The vibration must be considered in the mounting scheme, so the ferrite material does not crack. If the ferrite material cracks, then the inductance will be much different from what was designed. For the mounting to be successful the magnetic cores have to be securely fastened together and mounted to a heat sink. Also, the PCB should not be allowed to move freely inside the core. This presents a challenge for the inductor that must have a gap to achieve the required inductance.

#### 1.2.3. Operating Conditions

The operation of the system will have large transients that could saturate the magnetic components. When the automobile is accelerating, the system will be required to supply a large amount of power to the load. During the coasting time the system will be able to return to a more manageable level. For this reason the worst case condition has to be found and then designed, to ensure the magnetic components will not saturate and cause the system to fail. Table 1-1 shows the predicted operational patterns of the system.

Table 1-1. System Operation

|                   | Power Flow | Vin     | Vout        | Max LV<br>Current | Load Pattern                                  |

|-------------------|------------|---------|-------------|-------------------|-----------------------------------------------|

| <b>Buck Mode</b>  | HV→LV      | 7- 16 V | 200 – 450 V | 150 A pk          | Continuous                                    |

| <b>Boost Mode</b> | LV→HV      | 7- 15 V | 240–450 V   | 350 A pk          | $5 \text{ s on } \rightarrow 5 \text{ s off}$ |

## **Chapter 2.** Planar Transformer Design

#### 2.1. Introduction

The planar transformer design resembles the standard transformer design in many aspects. The volt-seconds applied must not saturate the ferromagnetic material, during the worst-case condition. However, the copper design is slightly different, and the window utilization is also different. Since the copper used in the design is the PCB windings instead of copper wire, the insulation will be much thicker; therefore, the cooling requirement will be different. Another difference is the window utilization, which is the amount of area the copper fills the magnetic core. In a standard core this number must be much less than one to allow for manufacturing. In a planar design, the manufacturing process is easily repeated and the window utilization can be further extended if necessary.

Table 2-1 highlights the design specifications for the planar transformer. The planar transformer offers many benefits over the traditional transformer in size, weight, thermal management, and manufacturing. In order for the planar transformer, to exceed the traditional transformer, the number of copper layers the PCB uses must be minimized. To do this the primary number of turns is kept to one, therefore the secondary number of turns is fourteen. This deviates slightly from the traditional transformer design, which decides the number of turns after the core has been picked. A typical transformer design is to find an area product that uses the volt-second limit to ensure that the core does not saturate and the amount of window area needed to fit the copper wire. In the planar transformer this method does not give an optimal design. The main reason is that window area for the copper windings will be different in a planar transformer than a traditional transformer.

Table 2-1. Transformer design specifications

| Turns ratio              | 1:14                  |  |  |

|--------------------------|-----------------------|--|--|

| Galvanic isolation       | 1800 Vac for 1 minute |  |  |

| Core temperature rise    | 15 °C                 |  |  |

| Winding temperature rise | 20 °C                 |  |  |

| Heat sink temperature    | 85 °C                 |  |  |

| Leakage Inductance       | 5 μH from high side   |  |  |

Since this transformer operates in both boost and buck mode, the first step is to find the mode that has the highest rms current. This current will be used to design the copper thickness according to the given temperature rises in Table 2-1.

### 2.2. Boost Mode Operation

In boost mode the duty cycle is given by (1), and the rms current can be expressed as a function of the duty cycle, as shown in (2). [6]

$$D = 1 - N \frac{Vin}{Vout} \tag{1}$$

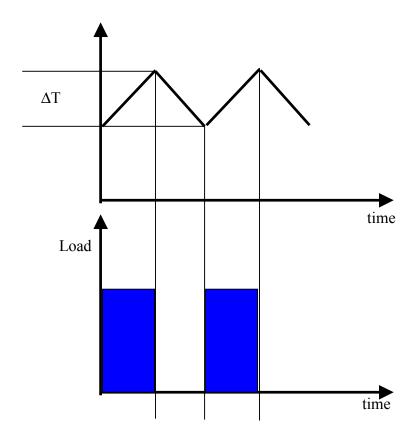

The largest duty cycle results when Vin is minimum at 7 V and Vout is maximum at 450 V. Using N = 14 the highest duty cycle in boost mode is D = 0.782. Using (2) the rms current is obtained as 309 A. However, in boost mode the load has a profile with 5 second on and 5 second off. As long as the circuit does not reach the thermal steady state limit, during this time, the load duty cycle can also be taken into account. Given that copper has a high thermal conductivity, it will get hot during the time the load is on. However, the insulating material (FR4) has much lower thermal conductivity [13]. The result of the system is that only a slight change in temperature resulting from the load change. Figure 2-1 shows the thermal cycle of the transformer. As long as the  $\Delta T$  is not too large, the transformer will not have a thermal breakdown. The limiting factor in the thermal breakdown is the FR4 material that is used as

insulation. FR406 has a glass transition temperature of 170 °C [ 10 ]. The glass transition temperature is the temperature that the material will start to change properties. FR408 has a glass transition temperature of 180 °C [ 10 ]. Both of these materials are available as PCB insulation. The higher glass transition temperature will allow for a higher  $\Delta T$  but the cost will also be higher. Equation ( 3 ) takes the load duty cycle,  $D_{load}$ , into account, which leads to the rms current in boost mode to be 219 A. Here  $D_{load}$  is assumed to be 0.5.

$$I_{rms} = I_{PK} \sqrt{D} \tag{2}$$

$$I_{rms} = I_{PK} \sqrt{D_{Boost} * D_{load}} \tag{3}$$

Figure 2-1. Thermal change with load

### 2.3. Buck Mode Operation:

The same procedure was used to find the worst case current during buck mode operation. The duty cycle for buck mode is given by equation (4) [6]. In buck mode the power is flowing from the high voltage side to the low voltage side. Therefore, Vin used in equation (4) is actually Vout given in Table 1-1. Also, Vout in equation (4) is actually Vin from Table 1-1. The highest duty cycle in buck mode will occur when the input voltage is minimum and the output voltage in maximum. Using the numbers from Table 1-1, the duty cycle will be greater than one. Because the buck mode operation occurs only when the bus voltage is sufficiently high, and the battery voltage is fully charged, it can be assumed that the minimum input voltage is 240 and the maximum output voltage is 15. With a turns-ratio of 14, the maximum buck mode duty cycle will be 0.875. Using equation (2) the worst-case rms current becomes 140 A. This analysis proves that during boost mode operation the current will be highest, and therefore the copper should be designed using the boost mode specifications.

$$D_{buck} = \frac{Vout}{Vin}N\tag{4}$$

#### 2.4. Skin Effect

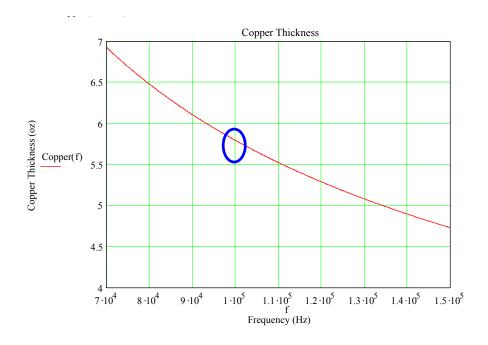

Since, the converter is switching at 100 kHz and operating in a high current condition, the skin effect becomes a concern. Skin effect is caused by current that flows in a conductor, creates an eddy current. This eddy current creates flux that opposes the flux from the transformer current. The opposing flux tends to reduce the current density towards the center of the conductor and increases the current density at the outsides of the conductor [6]. If the skin effect is not taken into consideration, then the current density will become too high towards the outer edges of the conductor and results in excess heating and increased resistance [23]. Equation (5) shows the standard skin depth equation. The skin depth is how far the current will penetrate the conductor [6]. Using standard numbers for resistivity (@25°C) and permeability, the skin depth is 0.2 mm at 100 kHz. Since 1 oz/ft², of copper is 0.0014 inch thick, 0.2 mm

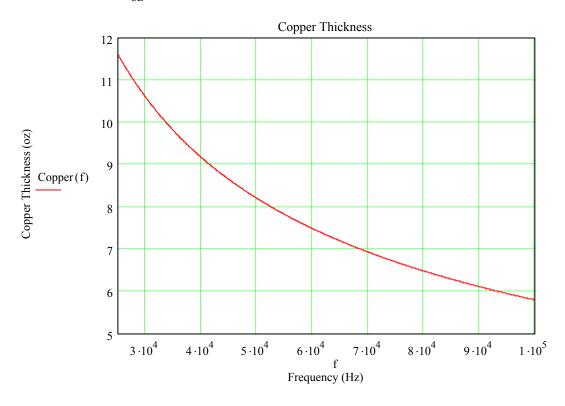

corresponds to 5.8 oz/ ft<sup>2</sup> of copper. From this analysis the copper weight should be limited to 6 oz/ft<sup>2</sup> if the switching frequency is kept at 100 kHz. If the copper weight is chosen above this, then the current will not utilize all of the copper area and therefore provide no additional benefit. Figure 2-2 shows the thickness of copper at different switching frequencies.

$$\delta = \sqrt{\frac{\rho}{\pi f \mu}} \quad (m) \tag{5}$$

ρ = Resistivity of copper (1.673x10<sup>-8</sup> Ω\*m) μ = Permeability  $μ_0*μ_r$  (4πx10<sup>-7</sup> H/m)

Figure 2-2. Copper weight vs. frequency

#### Copper Weight: 2.5.

The copper weight for the rest of the design is limited to the 6 oz/ft<sup>2</sup> on each layer to utilize as much of the copper as possible. This copper weight limits the core selection and the transformer configuration. The 6 oz/ft<sup>2</sup> copper must have the current carrying capability for 219  $A_{rms}$  (Boost Mode), for the given width. Using the empirical formulas shown in (6) and (7) the copper trace widths can be found [1].

$$CopperArea = \left(\frac{Irms}{k * t^{0.44}}\right)^{0.725} \tag{6}$$

$$TraceWidth = \frac{CopperArea}{CopperThickness}$$

(7)

k = 0.24 (internal layer) k=0.48 (external layer)

t=temperature rise (°C)

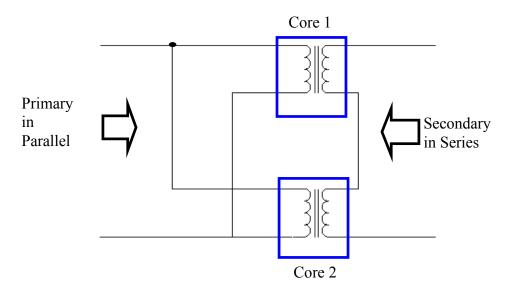

An E58 planar core by Philips has a window width of 21.05 mm  $\rightarrow$  0.829 in  $\rightarrow$  829 mils. To allow for tolerances given by the PCB manufacturer, core manufacturer, and for the core to easily fit in the PCB, a window width of 725 mils was used for calculations. The primary is only one turn and the trace width is limited to a maximum of 725 mils. This width is still not wide enough to handle the required current. For this reason two transformer cores were used with the primary winding in parallel. This configuration will assume the current splits evenly between the two transformer cores. The current should splits evenly because using the PCB, very good symmetry can be achieved between the two transformer cores. Using equations (6) and (7), with the rms current of 219/2 = 109.5 A, the copper weight is found to be 18 oz/  $ft^2$ . Because of PCB manufacturing limitations and skin depth requirements, the design splits the 18 oz/ft<sup>2</sup> in three layers of 6 oz/ft<sup>2</sup> [23]. All the three layers are connected together in a parallel configuration. Since the PCB integrates the transformer and the inverter, no vias were used to make this copper connection. Instead the through-hole pads from the MOSFETs were used. Using the MOSFET pads instead of vias will reduce the cost. Separating the layers will cause minor problems during maximum load operation. The problem that can arise during operation is that the current will not share equally among all three layers. This is due to the proximity and skin effect. The proximity effect will insure that the current does not distribute evenly. It has been found in [23] that using three parallel layers is better than having one thick layer. The reason is that the current density will be higher, closer to the high magnetic field region. The high magnetic field region is between the primary and secondary layers. This implies that the temperature of the inner layers will be hotter than the outer layers. However, 100 kHz is still a

relatively low frequency and the current distribution should not be a major concern. Using three separate layers is still more effective than using one layer of 18 oz copper.

The temperature rise used for this calculation was 30 °C and the required winding temperature rise given in Table 2-1 was 20 °C. The reason for this difference is that the formulas given in (6) and (7) are for circuit boards that are not attached to a heatsink. In this project, the PCB will be additionally cooled through the ferrite core to the heatsink. This additional cooling is accounted for in the 10 °C temperature rise that was used.

The secondary trace widths were found in a similar fashion. Since the secondary had 14 turns the space between the traces had to also be taken into account. Also, with the secondary, an even number of layers had to be used. This is because the windings would start from the outer portion of the core and wind towards the center. Once it has been wound to the center it must go down one layer and wind back towards the outer portion of the core to connect with other components in the circuit board. The secondary current is 14 times lower than the primary current (15.6 A). Using this lower current, the trace thickness is much easier to achieve on the secondary than the primary. For this reason the secondary windings are wound in series, unlike the primary windings, which are wound in parallel. Figure 2-3 further illustrates this point.

Figure 2-3. Schematic representation of transformer

According to the StrataFLEX heavy weight copper design manual the minimum spacing / trace width is 3 mils for each ounce of copper [25]. For 6 oz. copper the minimum spacing /

trace width is 18 mils. Having the secondary in series makes each transformer have 7 turns instead of 14, if two layers are used this makes 3.5 turns per layer. Again using equations (6) and (7) and taking into account the space between traces gives a trace width of 146 mils and 35 mils spacing between the traces. Table 2-2 shows a summary of the transformer calculations. For the transformer to operate, 5 layers of 6 oz copper are needed, three for the primary and two for the secondary.

Table 2-2. Copper weight conclusion

|           | Temperature Rise | Width    | Copper<br>Weight     | Layers |

|-----------|------------------|----------|----------------------|--------|

| Primary   | 30 °C            | 725 mils | 6 oz/ft <sup>2</sup> | 3      |

| Secondary | 30 °C            | 146 mils | 6 oz/ft <sup>2</sup> | 2      |

### 2.6. Copper Loss:

To approximate the efficiency of the system, the copper losses are taken into account for the transformer section only. Equation (8) shows the basic equation for the DC resistance as a function of the coil geometry. The DC losses are then  $I^2R_{DC}$ . The mean length per turn (MLT) is defined as the average length for all the turns on either the primary or the secondary. It was approximated to be 0.13 m for the primary and the secondary. The primary copper cross sectional area for 6 oz copper is  $3.9 \times 10^{-6}$  m<sup>2</sup>, this is for each layer of the primary. The secondary copper cross sectional area for 6 oz copper is  $7.912 \times 10^{-7}$  m<sup>2</sup>. Equation (8) gives a result for the primary resistance of 0.56 m $\Omega$  for each layer, and a secondary resistance of 19 m $\Omega$ . This is for 7 turns on the secondary and one turn on the primary. Since the transformer structure uses two transformers the other transformer must also be considered. The primary is in parallel so the resistance will be divided by three for each transformer and then divided by two for two transformers, the secondary is in series and therefore its resistance should be multiplied by two.

$$R_{DC} = \rho \frac{MLT}{CopperArea*N}$$

$$\rho = \text{resistivity of copper } (\Omega*m)$$

$$MLT=MeanLengthPerTurn (m)$$

$$CopperArea (m^2)$$

$$N = \text{number of turns}$$

(8)

The primary current in each layer is  $\frac{219}{2*3}$  =36.5 A, which yields the copper loss for each layer of the primary to be 0.746 W. Considering three layers for each core, the loss sums to 2.238 W. For both cores, the total primary DC copper loss is 4.47 W. The secondary current is 15.6 A, and the loss for each core is 4.8 W. With two cores, the total DC loss for the secondary is 9.6 W. The AC resistance is more complicated and should be solved by using a finite element approach. An approximate formula is given in (9) [11]. The formula is given in  $\Omega$ / inch. To get the resistance we need to multiply by the mean length per turn and the number of turns. The 1.69 is a *fudge factor* that was based on experimental results. It accounts for proximity effect, at higher frequencies. A more accurate result can be obtained from finite element analysis. Using 0.146 mils for the secondary and 6 oz copper, the AC resistance at 100 kHz is 16 m $\Omega$  for the secondary for both transformers this is multiplied by two. Using 725 mils and 6 oz copper, the AC resistance of the primary is 0.4 m $\Omega$  for each layer the total primary resistance is divided by three for each core and then divided by two for the two transformers. The total resistance is the sum of the AC and DC resistance. Table 2-3 shows a summary of the different resistances and the total calculated resistance.

$$Rac(f) = \frac{\sqrt{\pi * \rho * \mu} \sqrt{f} * 1.69}{2*(w+d)} \quad (\Omega/\text{in})$$

$$w = \text{width of trace (inch)}$$

$$d = \text{trace height (inch)}$$

$$\mu = 3.192*10^{-8} \quad (\text{Weber/amp/in})$$

$$\rho = 6.787*10^{-7} \quad (\Omega/\text{in})$$

The copper losses are I<sup>2</sup>R losses. For the primary the total loss is 7.7 W and the secondary is 17.3 W. This will be the loss at the maximum load condition.

Table 2-3. Calculated winding resistances

|           | R <sub>AC</sub> @100 kHz (mΩ) | R <sub>AC</sub> @100<br>kHz (mΩ) | $R_{DC}$ (m $\Omega$ ) | $R_{DC}(m\Omega)$ | Total (mΩ) |

|-----------|-------------------------------|----------------------------------|------------------------|-------------------|------------|

| Primary   | 0.4 (perlayer)                | 0.0667 (total)                   | 0.56 (per layer)       | 0.093             | 0.16       |

| Secondary | 16 (per transformer)          | 32 (total)                       | 19 (per transformer)   | 38                | 70         |

#### 2.7. Core Loss:

The core loss of the transformer is dependent on the material that the core is made from, the switching frequency, the flux density, and the volume of the core. Core loss can be directly related to the area of the hysteresis loop of the magnetic material [6]. Figure 2-4 shows an example of a hysteresis loop for a magnetic material. As the hysteresis loop becomes more square, the area of the loop decreases, this in return will decrease the core loss. Equation (10) shows a simple expression for the energy loss per cycle [6].

Figure 2-4. Hysteresis loop

Equation (11) shows the basic formula for the core loss of a transformer. The constants A, α, and β all depend on the type of material that is used. This transformer was designed for Philips 3C90 material. For the EI58 core, the materials that are available are 3C90 and 3F3. 3C90 material does not provide the best core loss over all frequency ranges. This material is to be used for lower frequency applications. Philips recommends using 3C90 for frequencies up to 200 kHz and above 200 kHz 3F3 material should be used. The 3F3 is designed for up to 500 kHz. Both the 3F3 and the 3C90 material have similar core losses at 100 kHz. However, the 3F3 material is more expensive, for this reason the 3C90 was chosen to be the best material for this application. Table 2-4 shows a comparison of the 3F3 and 3C90 material. This table proves that the characteristics are very similar at 100 kHz.

Table 2-4. Material Comparison

| Material | B <sub>sat</sub> (mT) @25°C | B <sub>sat</sub> (mT) @100°C | $H_{C}(A/m)$ | $P_V (kW/m^3) @100kHz, 100 mT$ |

|----------|-----------------------------|------------------------------|--------------|--------------------------------|

| 3C90     | 450                         | 340                          | 15           | < 80                           |

| 3F3      | 450                         | 330                          | 15           | < 80                           |

$$P_{L} = A * B^{\alpha} * f^{\beta} * V$$

A= constant

B = flux density (G)

f= frequency (Hz)

V=volume (m^3)

$\alpha$ ,  $\beta$  constants

(11)

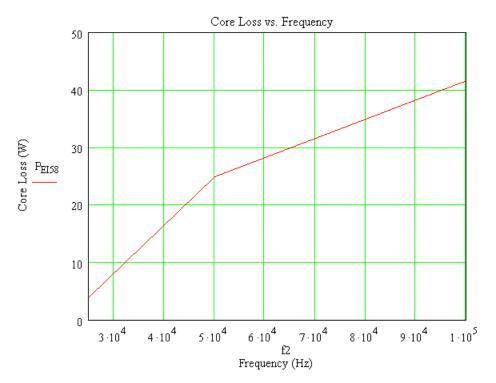

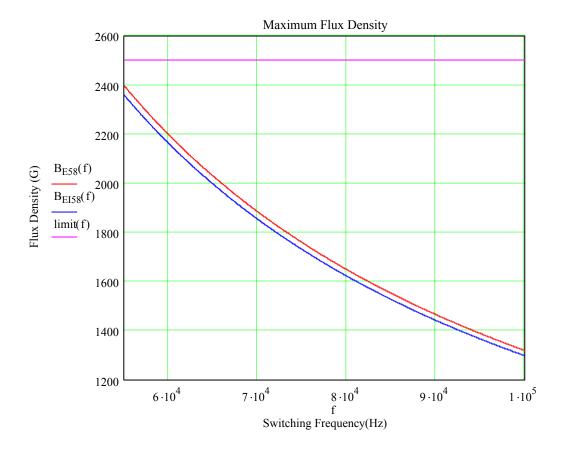

The core loss graph was obtained from the materials data sheet and then the resultant core loss was multiplied times the volume. The relationship for the core loss is that it will increase with the frequency and volume. However, the maximum flux density will decrease as the frequency is increased, because of Faraday's law ( $\Delta B = \frac{V\Delta t}{NA_E}$ ). Figure 2-5 shows the core loss for the EI58 configuration. This graph does include both transformer cores and the peak flux density is 2500 Gauss. This implies that if the transformer is not operating at maximum volt-seconds then the flux density will be decreased and the core loss will be decreased. The total core loss from the graph is 41.6 W at the maximum operating condition. If both the copper and core losses are considered the efficiency of the transformer should be 98% at full load.

Figure 2-5. Core loss for EI configuration at 2500G

## 2.8. Flux Density:

The flux density is derived from Faraday's law and shown in (12) [6].

$$\Delta B = \frac{V\Delta t}{NA_E} \text{ (Tesla)}$$

$$V\Delta t = \text{voltseconds}$$

$$N = \text{number of turns}$$

$$A_E = \text{cross sectional area (m}^2)$$

(12)

Since the transformer core is kept at 85°C the saturation flux density is decreased from the standard 25°C case. For the 3C90 material the saturation flux density is 3500 G at 100°C instead of 4400 G at 25°C. To prevent saturation of the transformer the design limited the maximum flux density to 2500 G (0.25 T).

#### 2.8.1. Boost Mode

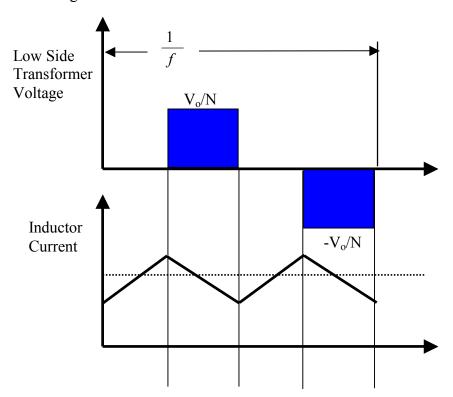

Figure 2-6 shows the voltage across the transformer and the current through the inductor during different switching states. The switching frequency was specified to be 100 kHz. This makes the volt-seconds across the transformer to be  $\frac{(1-D)V_o}{Nf}$ . Since the waveform across the transformer is a square wave, the volt-second is simply the voltage multiplied by the time. The worst case is when the duty cycle is minimum and the therefore the output voltage is minimum. Using equation (12) with the cross sectional area of 310 mm², the worst case flux density swing ( $\Delta$ B) is 0.4646Tesla (4646 Gauss). The flux density swing is not as much of a concern as the maximum flux density. For the square wave operation this is  $\Delta$ B/2 or 2323 Gauss. This is well below the design limit of 2500 G.

Figure 2-6. Boost mode waveforms

#### **2.8.2. Buck Mode**

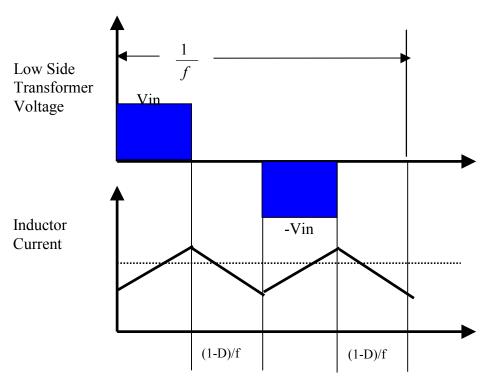

Figure 2-7 shows the voltage across the transformer and the inductor current for different switching times. During buck mode operation the volt-second is Vin\*D/f. For the primary Vin is actually Vout / N from Table 1-1. Given the specifications the worst case is when the output

voltage is 240 V, this results in a duty cycle of 0.875. Under this worst case the maximum flux density is 2117 G, which corresponds to a swing of 4234 G. This flux density is also below the design limit of 2500 G. During the boost mode operation the copper losses will be greater because the current will be much higher than in buck mode operation. Also, boost mode proved to have the highest flux density.

Figure 2-7. Waveforms for buck mode

#### 2.9. Conclusion

The planar transformer design is similar to the traditional wire wound design procedure. The planar transformer design still has to obey both Faraday's and Ampere's law. However, the traditional design uses an area-product design method that does not apply to the planar condition. Also, the copper weight is chosen differently than the circular wire size, because of the cooling requirement. In a wire wound transformer the insulation is very thin. This makes it difficult for cooling reasons. The planar configuration keeps the copper planes separated from each other, which in return results in better cooling.

Since the converter operates as both a boost converter and a buck converter, both conditions must be considered in the design. With boost mode carrying a higher current, the copper weight was designed based on the converter operating in boost mode. The cross sectional area of the core was also considered during the boost mode operation. This is because the flux density is greatest during the boost mode operating condition.

## **Chapter 3.** Parasitic and Leakage Inductance

#### 3.1. Introduction

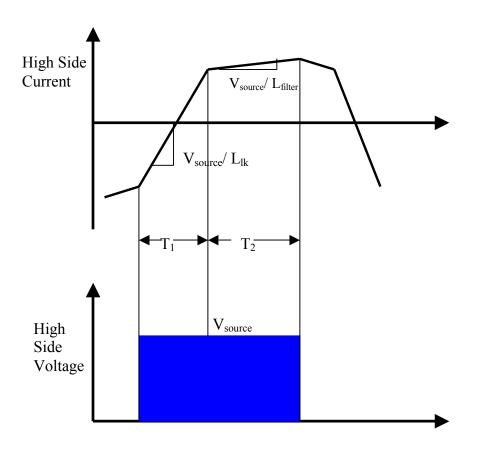

The leakage and parasitic inductances are often an undesirable component of the system. These inductances cause losses in the circuit that decreases the efficiency of the system. However, in this topology, soft switching was required. This implies that it can use the inductance to store energy, that permits zero voltage and zero current switching. It was shown in Table 2-1 that 5  $\mu$ H of inductance measured from the secondary side of the transformer was needed to store enough energy for soft switching over the desired load range. It is imperative that this inductance is accurately measured to ensure the soft switching will occur.

### 3.2. Transformer Leakage Inductance

#### **3.2.1.** Theory

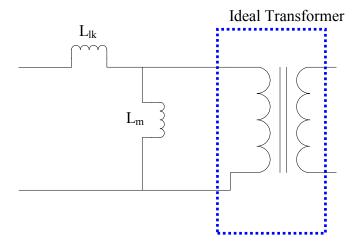

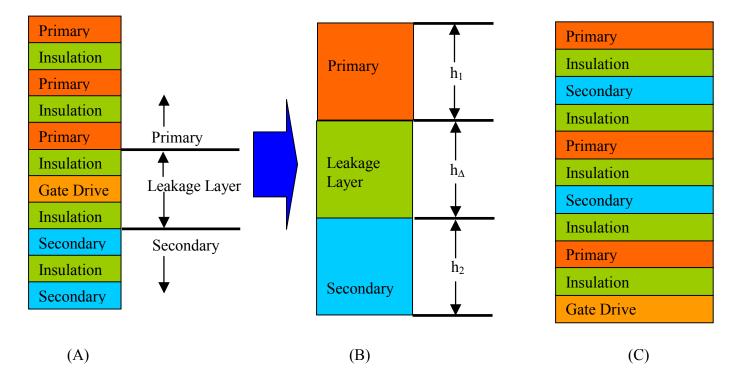

The flux that does not couple from the primary to the secondary, circulates within the transformer, this flux is termed leakage flux [6]. This flux creates an inductance according to equation (13). As the coupling between the primary and secondary decreases, the leakage flux increases and therefore the leakage inductance will increase. Figure 3-1 shows a model for the non-ideal transformer. The leakage inductance is represented by L<sub>lk</sub>, L<sub>m</sub> is the magnetizing inductance and the last section is an ideal transformer (perfect coupling). This project specified 5 µH of leakage inductance measured from the secondary. Traditionally, planar transformers use an interleaved structure [29]. An interleaved PCB structure means that each layer of the primary is placed between secondary layers as shown in Figure 3-2 C. The interleaved structure will create the best coupling and therefore the lowest leakage inductance. In this design, because the requirement of high leakage inductance, the interleaved structure is excluded to ensure the leakage inductance is high as possible.

Figure 3-1 Non-ideal transformer model

$$L = \frac{\Phi}{I} \tag{13}$$

φ = Flux (Weber) I=Current (A)

#### 3.2.2. PCB Layout

Figure 3-2 A shows the PCB layout configuration that was designed and tested. This configuration separates the primary from the secondary with an extra layer of insulation and copper that can be used to increase the leakage inductance. By separating the primary and secondary the coupling will decrease. The extra copper layer is used for the gate drive signals, which are separated from the transformer windings and only adds insulation between the primary and secondary of the transformer. The total distance between the primary and the secondary is referred to as the leakage layer. This structure can be estimated by the simpler structure shown in Figure 3-2 B. The estimated structure is not an exact representation. However, for the leakage inductance calculation it can give an accurate result

Figure 3-2. PCB layout configurations

### 3.3. Calculation

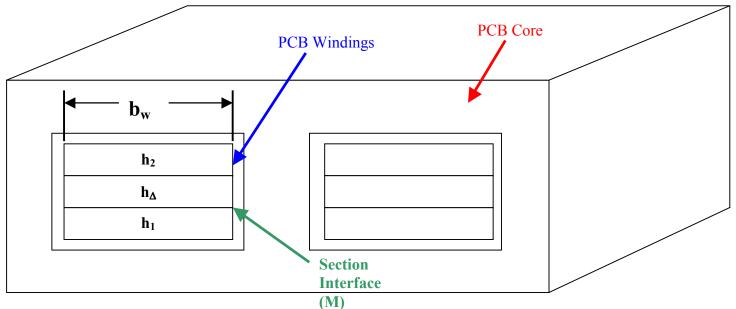

The leakage inductance is a result of energy storage in the transformer. In ideal transformers, no energy is stored and therefore the leakage inductance is zero. The energy storage in a transformer is given by equation (14) [21]. Figure 3-3 further describes the geometry of the transformer system.

$$EnergyStored = \frac{\mu_0}{2} \oint H^2 dx l_w b_w$$

(14)

$\mu_0$  = permeability of air (H/m)

H = field strength (A/m)

dx = thickness of winding (m)

$l_w = mean length of winding (m)$

$b_w$  = winding breadth (m)

Figure 3-3. 3-D view of transformer

Equation (14) can be further broken down into the energy storage from the primary, secondary, and the leakage layer. This equation is shown in (15). Since the energy is stored in an equivalent inductance the equation is equal to  $0.5*L*I^2$ . Setting (15) equal to this and simplifying, gives equation (16). Equation (16) is for a two winding structure. The formula would vary if more layers were constructed. For this case the PCB shown in Figure 3-2 A was estimated by Figure 3-2 B which only considers two windings.

$$EnergyStored = \frac{\mu_0 I_W b_W}{2} \left\{ \int_0^{h_1} \left( \frac{N_1 I_1 x}{b_W h_1} \right)^2 dx + \left( \frac{N_1 I_1 x}{b_W} \right)^2 h_{\Delta} + \int_0^{h_2} \left( \frac{N_2 I_2 x}{b_W h_2} \right)^2 dx \right\}$$

(15)

N = number turns

I = current(A)

h = thickness (m)

$$L_{lk} = \mu_o N^2 \frac{l_w}{b_w} \left( \frac{h_1 + h_2}{3} + h_\Delta \right)$$

(16)

$\mu_0$  (H/m)

$l_w$  = mean length of traces (m)

$b_w$  = width of primary trace (m)

If an interleaved structure is used, then equation (15) simplifies to equation (17). In (17) M is the number of section interfaces. This is the number of times that the primary is mated against the secondary layer. Using the interleaved PCB shown in Figure 3-2 C the number of section interfaces is 4.

$$L_{lk} = \mu_o \frac{N^2 l_w}{M^2 b_w} \left( \frac{\sum h_i}{3} + \sum h_{\Delta} \right)$$

(17)

$\mu_0$  (H/m)

$l_w$  = mean length of traces (m)

$b_w$  = width of primary trace (m)

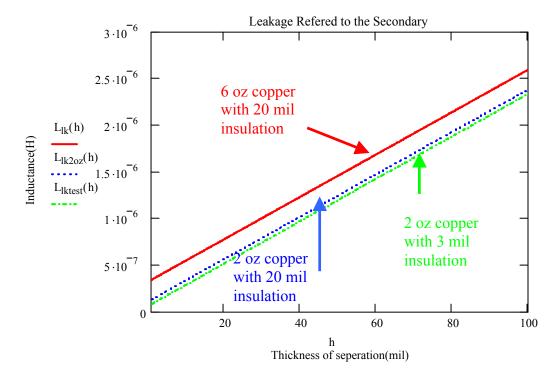

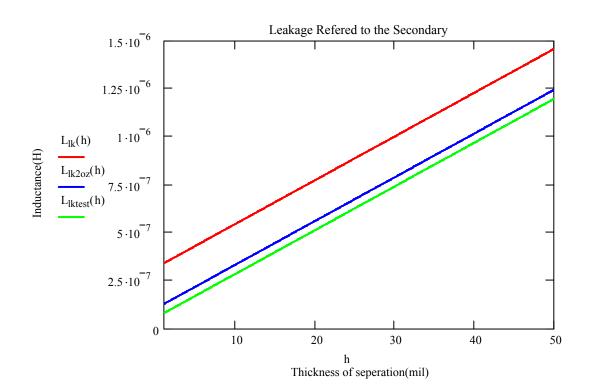

M = number of section interfaces

In (16) h<sub>1</sub> and h<sub>2</sub> are taken as the copper thickness only, it does not include the insulation between the layers, the insulation will be considered in the  $h_{\Delta}$  term. The ambiguous part of equation (16) is what to use for  $h_{\Delta}$  Figure 3-4 shows the leakage inductance as a function of the separation,  $h_{\Delta}$  in mils. The three different curves represent three different copper weights. The red solid line is using 6 oz copper and 20 mil insulation between each layer. The blue dashed line represents 2 oz copper and 20 mil spacing between each layer. The green dado line represents 2 oz copper on the outer two layers, 0.5 oz copper on the inner four layers, and 3 mils for each insulation layer. This graph proves that the leakage inductance will change between the different copper weights. However, given a fixed copper weight the insulation could be changed to adjust the leakage inductance. Since the primary and secondary both have insulation between them, the effective  $h_{\Delta}$  will be the leakage layer thickness plus the average for the insulation between primary layers and secondary layers. Table 3-1 shows the  $h_{\Delta}$  that should be used for calculating the leakage inductance for each case. For instance, in the 2 oz copper case with 20 mils of insulation the  $h_{\Delta}$  is 40 mils (leakage layer) of insulation between the primary and secondary then for the average of the primary will have the average of two layers of insulation  $\left(\frac{20+20}{2}\right)$  plus the average of the insulation between the secondary windings  $\left(\frac{20}{2}\right)$  plus one layer of copper from the secondary layer that is 2 oz weight and each oz is 1.4 mils thick, this gives a total of 72.8 mils.

Table 3-1.  $h_{\Delta}$  for different cases

| Case:                                        | h <sub>Δ</sub> (mils)                                         |

|----------------------------------------------|---------------------------------------------------------------|

| 2 oz outer, 0.5 oz inner, 3 mils insulation  | $3+3++0.5*1.4+\frac{3}{2}+\frac{3+3}{2}=11.2$                 |

| 2 oz copper, 20 mils insulation              | $20 + 20 + 1.4 * 2 + \frac{20}{2} + \frac{20 + 20}{2} = 72.8$ |

| 6 oz copper, 20 mils insulation              | $20 + 20 + 1.4 * 6 + \frac{20}{2} + \frac{20 + 20}{2} = 78.4$ |

| 6 oz copper, 20 mils insulation, interleaved | 20                                                            |

Figure 3-4 Leakage inductance calculated from the secondary

The final production PCB will be 6 oz copper with 20 mil insulation between each layer. Referring to equation ( 16 ) the leakage inductance is calculated to be  $2.1~\mu H$ . This is below the design requirement of  $5~\mu H$ . However, many estimations were used with this formula. To get a more accurate leakage inductance a finite element approach should be taken. Table 3-2 shows a summary for all the leakage inductances calculated at 100~kHz.

Table 3-2. Calculated leakage inductance

|                                              | Calculated Inductance (μH) |

|----------------------------------------------|----------------------------|

| 2 oz outer, 0.5 oz inner, 3 mils insulation  | 0.31                       |

| 2 oz copper, 20 mils insulation              | 1.76                       |

| 6 oz copper, 20 mils insulation              | 2.1                        |

| 6 oz copper, 20 mils insulation, interleaved | 0.134                      |

## 3.4. Maxwell™ Modeling for the Transformer Leakage Inductance

#### 3.4.1. Introduction

Maxwell software designed by Ansoft can be used to solve Maxwell's equations for both static and time varying fields with finite element analysis (FEM) method. The basic principle behind FEM is that it breaks up the problem into smaller sections, which are equilateral triangles. The fields can then be solved for 6 points on the triangle if a two dimensional problem is assumed. If a three-dimensional problem is used then the program will solve for ten points on the triangle. Equations (18)-(21) are the differential form of Maxwell's equations [2]. In these equations **B** is a vector representing the flux density, **E** is a vector representing the electric field, **D** is a vector that represents the electric flux density, finally **H** is a vector that represents the magnetic field intensity [2]. The first step in the process is to define a model that represents the transformer was chosen. Many different options are available. For this case a 2-D representation of the transformer. Although a more complete solution could be obtained from a 3-D simulation. However, the 3-D simulation is very time consuming and the precise solution is not always obtained. The problem with the 3-D simulation is that it must create many more triangles to solve the problem. Using the 3-D approach it might lose important accuracy of the fields between the windings. The advantage of the 3-D version is that it will model the sections of the transformer that are not covered by the ferrite core and the interconnection between the two cores.

$$\nabla X \vec{E} = -\frac{\partial \vec{B}}{\partial t} \tag{18}$$

$$\nabla X \vec{H} = J + \frac{\partial \vec{D}}{\partial t} \tag{19}$$

$$\nabla \bullet \vec{D} = \rho \tag{20}$$

$$\nabla \bullet \vec{B} = 0 \tag{21}$$

#### 3.4.2. Define Simulation

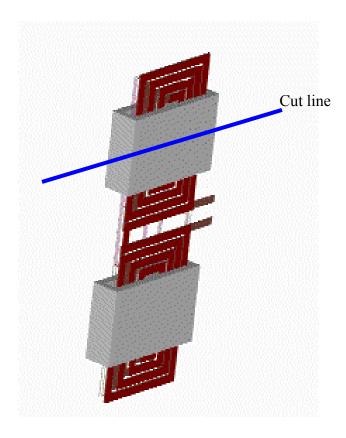

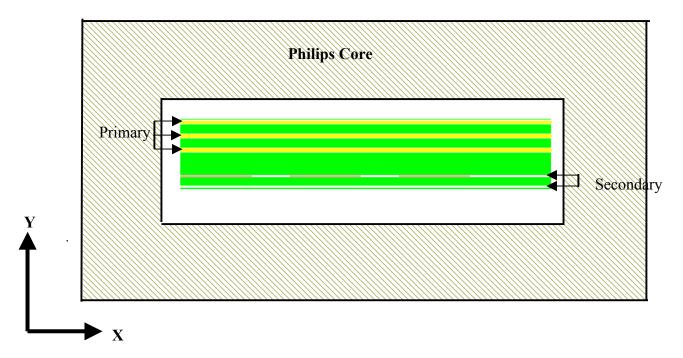

It is very important to accurately reflect the problem of interest. Since a two-dimensional problem was simulated, it was important to reflect the three-dimensional problem in two-dimensional space, and still have an accurate representation. To do this the transformer first had to be modeled in such a way that the problem shows symmetry. Figure 3-5 shows a three-dimensional view of the transformer structure. The three-dimensional structure does have symmetry and can be accurately modeled if the transformer was split through the transformer core. The blue cut line represents the point at which the transformer was split. Using this separation point only one transformer is modeled at a time. This simulation will not show any interactions that might occur as a result of the transformer system. However, it will show important magnetic field properties.

Figure 3-5. 3-D view of transformer

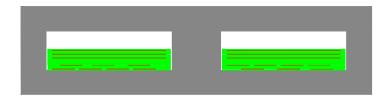

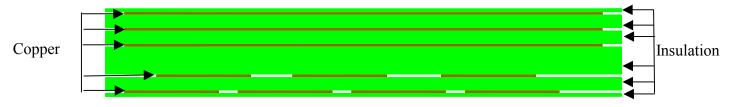

Using this scheme the calculations will assume that the transformer extends into infinity. Figure 3-6 shows the two-dimensional representation. In Figure 3-6 the gray area represents the ferrite core material, the green represents the insulation material, and the brown is a representation of the copper PCB traces. This is only a model of one core and it assumes that the core continues in the Z direction (into the page) for infinity.

31

Figure 3-6. 2-D transformer model

Figure 3-7 shows a closer view of one section of the PCB core. The top three thin brown layers are the primary layers. They are 0.0028 in thick, which represents 2 oz/ ft² of copper. This Autocad representation of the PCB and ferrite core can then be imported into the Maxwell's software package for further analysis.

Figure 3-7. 2-D PCB model

Once the drawings have been accurately represented, it is important to accurately represent the transformer system. For this system, many different simulations methods are available to find the leakage inductance and field representations. One is the magnetostatic solver. This one assumes a constant source as the input and solves the magnetic field inside the design space. This method is not used because the most important parameters are a result of an AC input. Another method is the eddy current solver. This solver inputs a sinusoidal input at a specific frequency and again solves the magnetic fields within the system. Another section of Maxwell is called PEMag which can easily solve for the parasitic elements of the system. This method will assume that the system is symmetric in the X-direction and the Z-direction when it makes the calculations.

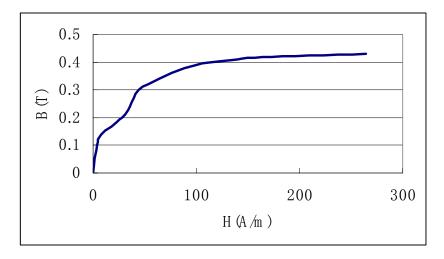

The materials used in the simulation must also be assigned. Here the 3C90 ferrite material from Philips is adopted. This material had to be defined so that the proper B-H characteristics were used in the simulations. Figure 3-8 shows the B-H curve that was entered into Maxwell..

Figure 3-8. B-H for 3C90

### 3.4.3. Eddy Current Solver

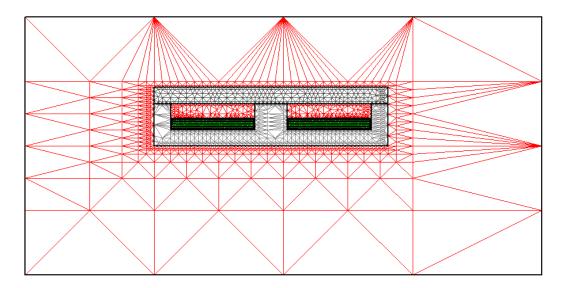

The eddy current solver can be used for finding the AC fields at a certain frequency. Since the converter is operating at 100 kHz, this was the main frequency of interest. The input to the system is a sine wave instead of a square wave that the transformer will operate at. The result should be very similar between a sine wave and a square wave, and can be used as a good approximation. The correct mesh, which is aset of triangles used for calculation, is very important when simulating any finite element problem. If the mesh is too fine, then the simulation will take much too long. If the mesh is too coarse then the result will not be accurate enough. Figure 3-9 shows the mesh that was used for all the simulations. The mesh was refined in the area of the PCB traces and insulation. This is because the fields in this area need to be known with relatively good accuracy.

Figure 3-9. Mesh used in simulation

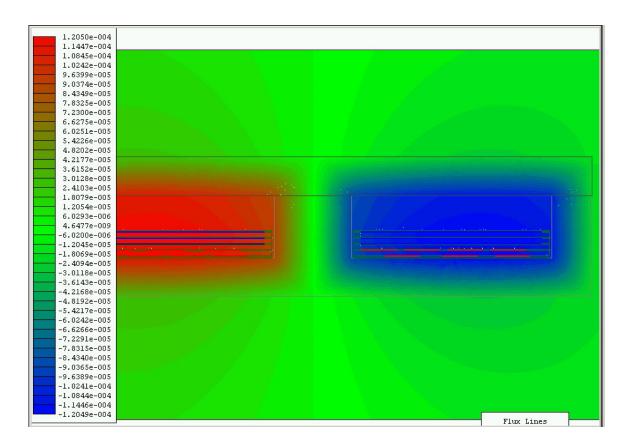

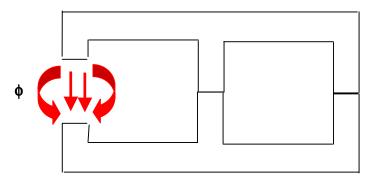

The main reason of the eddy current solver is to find the field intensities at different points in the core and windings. This will determine the current distributions, core hot spots, and many other transformer performance parameters. Figure 3-10 shows a contour plot of the flux inside of the transformer. The flux is both positive and negative. This is because the current is positive on the left side of the transformer and negative on the right side of the transformer. On the left side of Figure 3-10 the flux is in the positive direction and represented in red. On the right side of Figure 3-10 the flux is going in the opposite direction and represented in blue. The different shades of green represent near zero flux. This is the area outside of the core. It is desired that this flux is zero, because it can induce current in surrounding circuits. However, it is seen that the flux is very small outside of the core but not zero. The flux inside of the core is the greatest near the copper traces and decreases further away from these traces. This is because the flux is generated from the current flowing in the copper conductors.

Figure 3-10. Flux Density

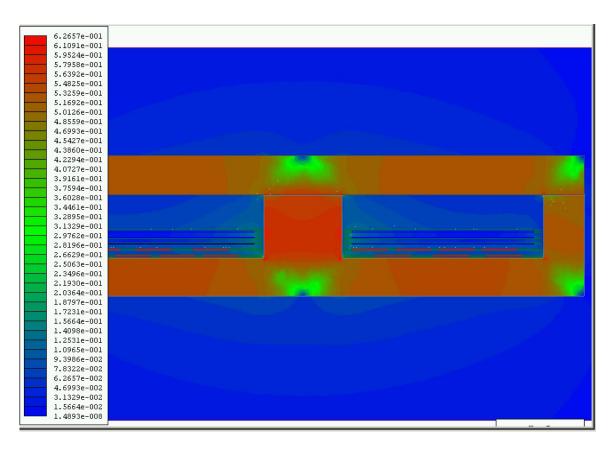

The magnitude of the flux density is another very important aspect of the transformer's performance. The flux density is directly related to the power loss of the transformer. Since, the power loss is also directly related to the temperature rise, the magnitude of the flux density can find the hot spots of the transformer. Figure 3-11 shows a contour plot of the flux density. This plot shows that the outer edges of the transformer and the center leg of the core will become the hottest parts of the transformer. These considerations should be taken into account when mounting the transformer. A mounting scheme should be devised in which the outer edges and the center should have ample force applied to the heatsink.

Figure 3-11. Magnitude of flux density

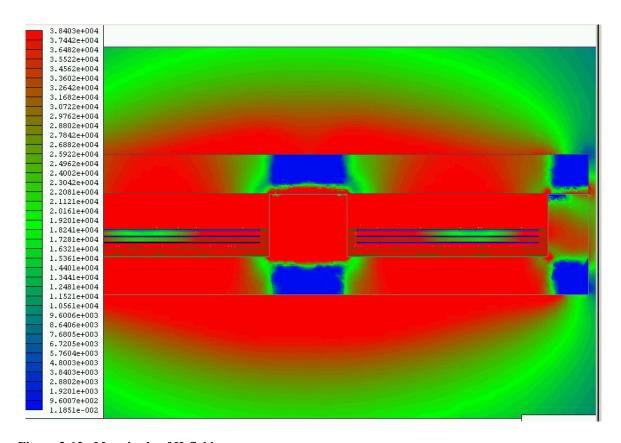

The final useful parameter of the eddy current solver is the magnitude of the H field. This parameter can be used to figure out the current distribution of the copper traces. The current distribution is essential to determine the heating of the PCB trace. One area of the trace carries all of the current then this area of the trace is much hotter and could break down the insulation in that area. Equation (22) shows that the current is related to the H field [6]. This implies that the greater the H field the greater the current will be in that area. Figure 3-12 shows a contour plot of the H-field.

Total current passing through interior of path =

$$\oint Hdl$$

(22)

H=magnetic field intensity

If this plot is examined closely in the area around the copper planes, it can be seen that the H-field is higher at the outer edges of the PCB traces. This simulation did not input current into the secondary. If this were done, then it could be seen that the H-field would greater between the

primary and secondary layers. This implies that the current will be higher at the outer edges of the PCB traces and the traces that are closer to the primary-secondary border.

Figure 3-12. Magnitude of H-field

#### **3.4.4. PEMag**

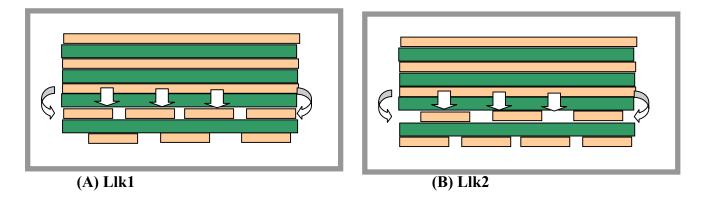

PEMag is a section of Maxwell that is specifically designed for analysis of transformer and inductors. It assumes that the structure is symmetrical and can solve for inductances, capacitances, and resistances from the given structure. PEMag is simply an interface to the two-dimensional finite element solver that has the predefined equations for solving the inductances, capacitances, and resistances. This program sweeps through the desired frequencies to find the parasitic elements at each frequency point. The disadvantage with using this software package is that it assumes a symmetrical structure in both the X-direction and the Z-direction. Figure 3-13 shows a picture of the structure that was used in this simulation. Since the transformer does not have an even number of turns per layer, it is not symmetrical in the X direction. One side will have four turns on the top secondary layer and the other side will have three turns on the top

secondary layer. However, the structure is symmetrical in the Z-direction and this assumption is valid. One major advantage of this program is that it already has the manufacture's cores and material properties predefined. Figure 3-13 shows a figure of an EI58 core with 3C90 material. Since it assumes that the structure is symmetrical in the X-direction, two different simulations are conducted. The first one is with the bottom secondary layer having three turns and the top secondary having four turns. The second one is with the bottom secondary having four turns and the top secondary having three turns. The actual transformer that was built will have a leakage inductance that is in the middle of these two cases. This is because the transformer that is built will have three top turns on one side and four top turns on the other side.

Figure 3-13. PEMag simulation figure

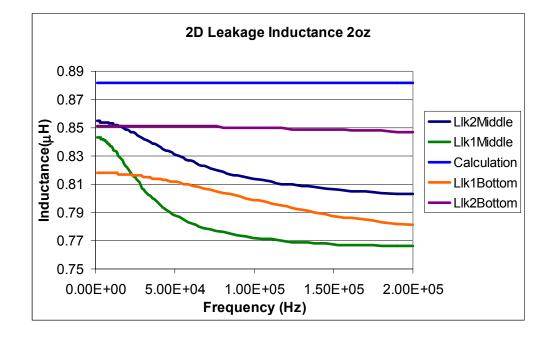

For the 2 oz copper case the leakage inductance was calculated for different simulations when the top secondary layer has three turns and when the top secondary layer has four turns. Figure 3-14 shows the simulation results along with the line for the calculated results. The simulation result is based on a two-dimensional field simulation. Llk1 represents the leakage inductance calculated when four traces were on the top secondary and three traces on the bottom secondary (Shown in Figure 3-15 A). Llk2 represents the leakage inductance with the top

secondary having three traces and the bottom secondary has four traces (Shown in Figure 3-15 B). The other designation is *Middle* and *Bottom* this specifies the placement of the PCB in the core. In the case that is denoted by *Middle* the PCB was placed in the middle of the window opening both in the vertical and horizontal positions. For the case denoted as *Bottom* the PCB was placed near the bottom of the window opening in the vertical position but still in the middle for the horizontal position. Noticing from Figure 3-14 the difference from the maximum simulation result and the minimum simulation result is 88 nH looking from the secondary side of the transformer. This gives an error of  $\pm 10\%$  for the single transformer case. This is reasonable considering that that the error of the program is 5%. The blue line represents the calculated result that was explained in the transformer design section (Table 3-2). This gives a greater result that the finite element approach. This is reasonable because the calculation used a onedimensional approach that lumped the primary together and the secondary together. The leakage was then computed based on the average spacing between the lumped primary and secondary. The lumping of the primary and secondary layers gives a reasonably accurate result. However, the two-dimensional finite element will consider more effects into the calculation. Also, from Figure 3-14 the Llk2 is greater than Llk1. This also is reasonable because Llk2 is the case that has the top secondary having three windings and the bottom secondary having four windings. This winding configuration will provide more leakage flux because the secondary does not have as much copper area on the layer that is closest to the primary. The lack of copper area allows more flux to escape and not couple from the primary to the secondary.

Figure 3-14. 2oz simulation results

Figure 3-15. Simulation structures

All of the above simulation results match relatively closely to the original lumped parameter model. The simulations were done with all of the primary layers connected in parallel. This implies that the current will distribute among these layers based only on the DC resistance. In the studied case, the windings are equal and the DC resistance is the same. If the DC resistance is the same then the current will share evenly. This is the same assumption that was made in the original calculation.

If all of the primary windings are separated and then shorted after the simulation has run, a better understanding of the current sharing and actual leakage inductance can be determined. As the previous section proved the inner layers will carry more current than the outer layers. Therefore the flux is higher for these sections. Figure 3-16 shows a graph of the leakage

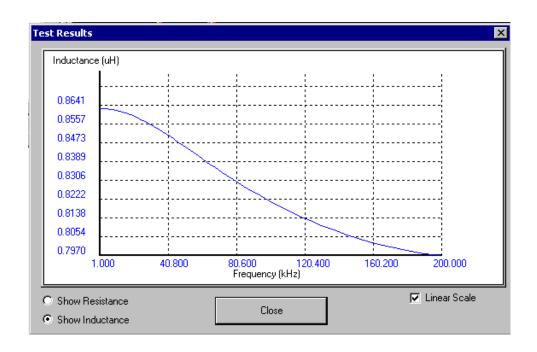

inductance referred to the secondary side. The model is for Llk2 case (Figure 3-15 B) with the PCB in the middle of the window opening. Comparing Figure 3-14 with Figure 3-16 the low frequency leakage inductance is the same for the Llk2middle case. As the frequency starts to increase the leakage inductance will start to drop off faster for the case when the current does not distribute evenly. It is not a drastic change because the frequency is limited to 200 kHz, which is relatively low frequency. At 100 kHz the leakage inductance is only different by 7 nH. Given the tolerance of the calculation, this is an acceptable difference.

Figure 3-16. Leakage inductance when even current distribution is not assumed

#### 3.4.5. Maxwell Simulation Conclusion

The eddy current solver has proven to be very valuable in observing the different field effects inside of the transformer. These effects can be used to better determine the temperature rise of both the copper traces and the ferrite core. Also the flux outside of the core can be useful in determining any radiated EMI that could induce noise on nearby components. The disadvantage of the eddy current solver is that it is not optimized for determining the parasitic elements of the transformer structure. For the parasitic elements, PEMag is much more convenient. PEMag solved for the leakage inductances and capacitances at the different

frequencies. The leakage inductance is the main parameter, and is proven to be very similar to the calculated result found in the previous chapter. This leakage inductance is only for one transformer. Since the secondary of the transformers are connected in series the total leakage inductance is doubled to form the total leakage inductance seen by the circuit.

#### 3.5. Parasitic Inductance

#### **3.5.1.** Theory

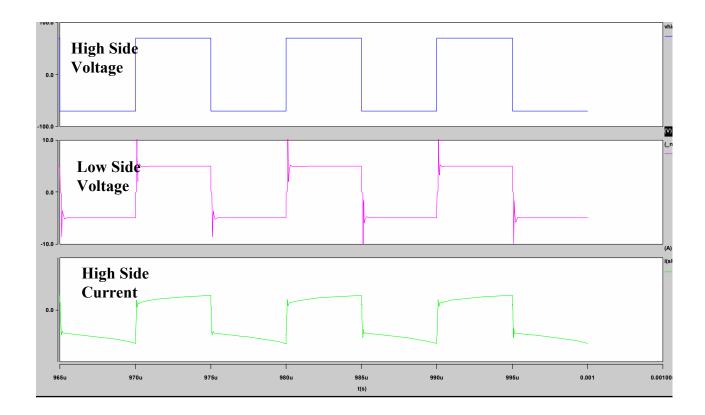

The leakage inductance was measured by shorting the primary through the device's footprint in the PCB. This implies that included with the leakage inductance, the self-inductance of the traces was also included in the measurement. The trace inductance can be very significant. This is because the trace inductance is on the primary side and the specification (5  $\mu$ H) was for the secondary side. This means that the trace inductance seen on the secondary side is multiplied by the turns ratio squared. In many cases this is not significant. However, in this design the turns ratio is large, and the reflected inductance could be significant. Since the turns ratio is 1:14, 1 nH of trace inductance on the primary is 0.2  $\mu$ H on the secondary. Depending the way the leakage was measured different trace inductances will be included.

#### 3.5.2. Inductance Source

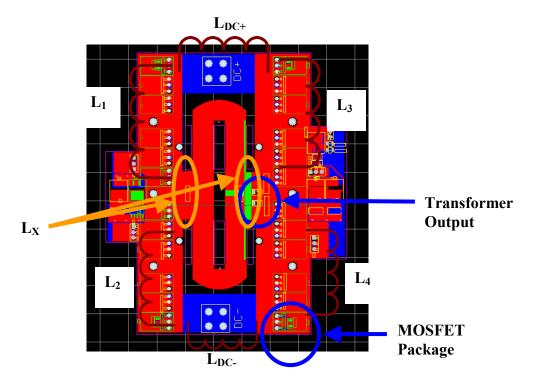

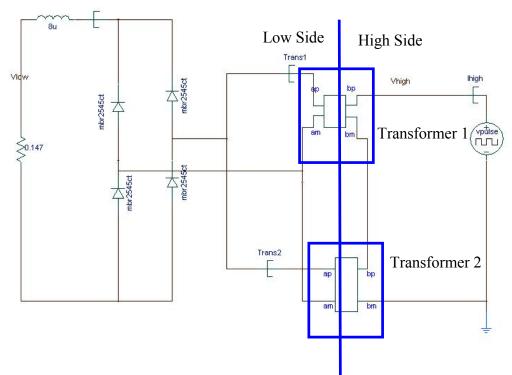

Figure 3-17 shows a screen capture of the PCB that was designed and tested.  $L_1$ ,  $L_2$ ,  $L_3$ ,  $L_4$ ,  $L_X$ ,  $L_{DC-}$  and  $L_{DC+}$  represent the lumped trace inductances that can be measured. The lumping method is based on the geometrical structure of the PCB traces. Unlike conventional definition of leakage inductance, which is normally referring to the transformer leakage inductance, it is obvious from the PCB capture that the circuit trace inductances can be far larger than the transformer leakage inductance. This figure also shows the device package, and that the device can be shorted by a very short copper strip from the drain of the MOSFET to the source of the MOSFET.

Figure 3-17. PCB Layout

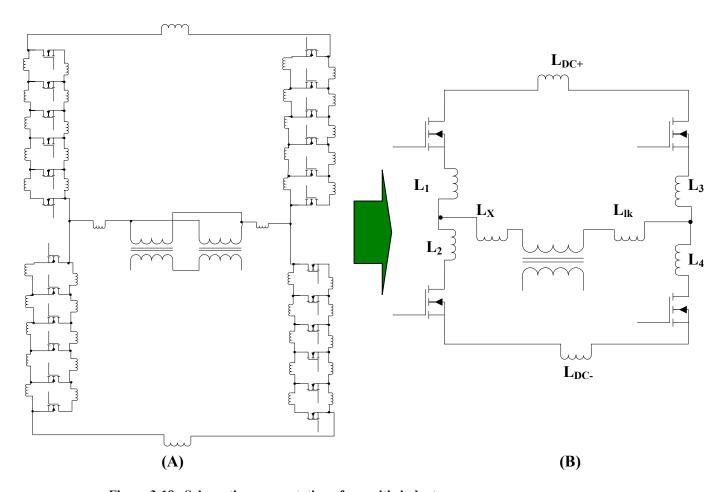

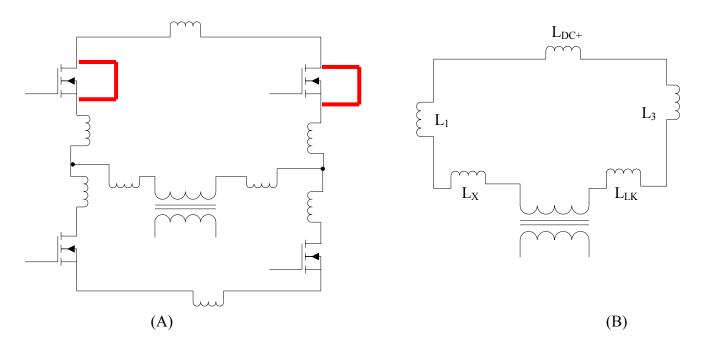

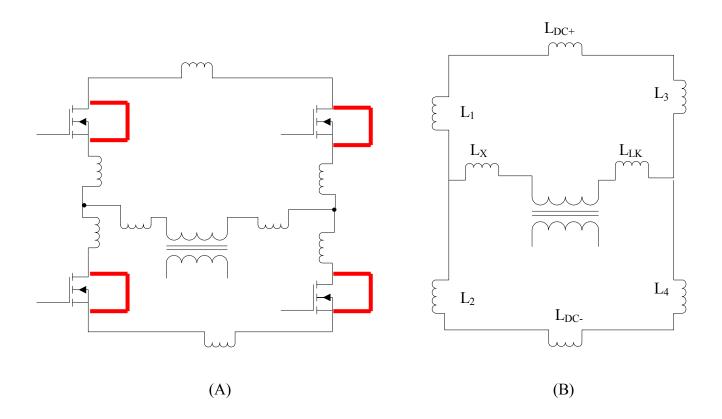

Many different inducances make up these the trace inductances. Each of the many inductances can be added together to form an equivalent inducance that can be calculated or measured. Figure 3-18 A shows the complete parasitic inductance circuit. Since the circuit has 6 MOSFETs in parallel, each one will create a parasitic inductance that will be placed in the measurement. If the 6 parallel MOSFETs are considered as one, and the inductance from each section are lumped, the result can be shown in Figure 3-18 B. Figure 3-18 B shows that the equivalent circuit comprises of six different inductances. However, Figure 3-17 shows that the layout has symmetry among a center axis. That center axis is the center of the transformer. Since self inductance is only a function of the geometry, Figure 3-18 B can further be reduced with reasonable accuracy by simple geometrical calculation. With symetry of geometry it can be reasonably assumed that  $L_1\cong L_2$ ,  $L_3\cong L_4$ , and  $L_{DC+}\cong L_{DC-}$  [8]. Physically  $L_1$ ,  $L_2$ ,  $L_3$ , and  $L_4$  represent lumped parasitic inductances of each device, which consist of six T0-247 MOSFETs;  $L_{DC+}$  and  $L_{DC-}$  represent parasitic inductances of the dc bus; and  $L_X$  represents the lumped interconnect parasitic inductance from the transformer to the ac terminal.

Figure 3-18. Schematic representation of parasitic inductance

#### 3.5.3. Calculation

Using formulas given by [8] a mathematical calculation for the trace inductance can be found. The self inductance of a copper sheet is given in (23). Inductance is dependent on the geometry of the structure but not on current [8] The widths of the  $L_2$  and  $L_4$  traces are 1.55 in., and the length is 7.4 in. The total thickness for the 2 oz. prototype this is 10 oz. To get  $L_2$  and  $L_4$  given in Figure 3-18 B the thickness can be obtained from three transformer primary layers in parallel, this gives 6 oz., plus the DC- is shorted to in input of the transformer which is 4 oz thick, this gives a total of 10 oz. The other section will be the  $L_{DC-}$  trace. This will be 4 oz of copper and 1.35 in wide and the length is 3 in. The calculation for  $L_X$  is 14 nH. If these inductance are reflected from the primary side of the transformer to the secondary side of the

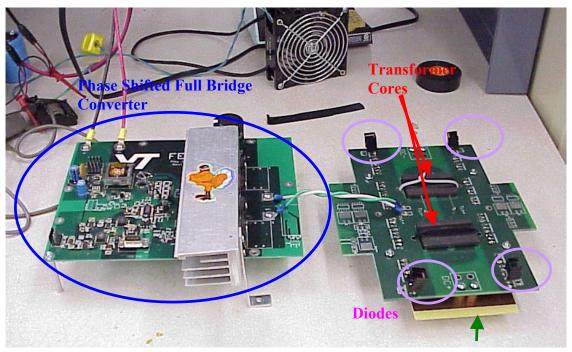

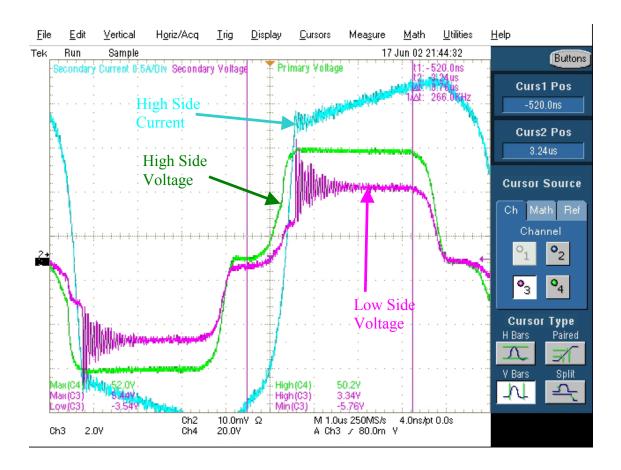

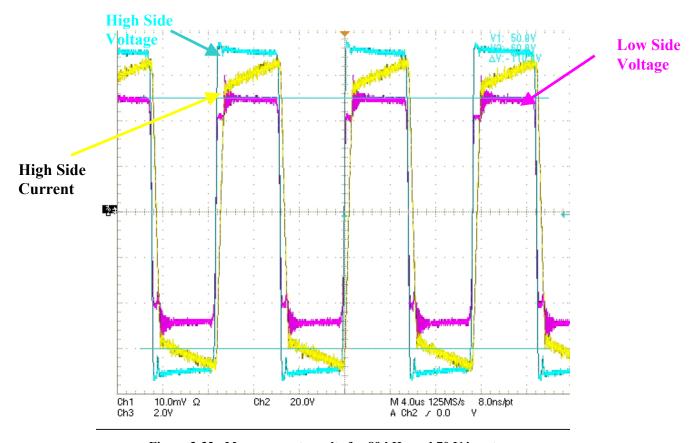

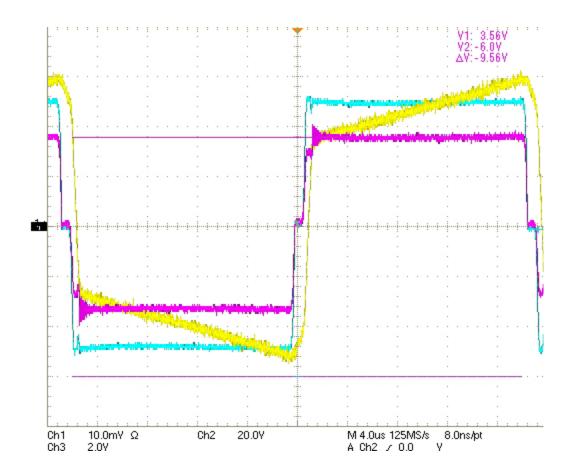

transformer, each must be multiplied by the turns ration squared (14<sup>2</sup>). The results of these calculations are shown in Table 3-3.