# GENERALIZED AVERAGE-CURRENT-MODE CONTROL OF SINGLE-PHASE AC-DC BOOST CONVERTERS WITH POWER FACTOR CORRECTION

by Konstantin P. Louganski

Dissertation submitted to the faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical Engineering

Dr. Jih-Sheng Lai, Chairman

Dr. Yilu Liu

Dr. Kwa-Sur Tam

Dr. Douglas K. Lindner

Dr. Douglas J. Nelson

April 23, 2007 Blacksburg, Virginia

Keywords: power factor correction, boost converter, leading phase admittance cancellation, input filter capacitor, active-front-end converter, multilevel converter, reactive power control

# GENERALIZED AVERAGE-CURRENT-MODE CONTROL OF SINGLE-PHASE AC-DC BOOST CONVERTERS WITH POWER FACTOR CORRECTION

Konstantin P. Louganski

#### Abstract

The dissertation presents a generalized average-current-mode control technique (GACMC), which is an extension of the average-current-mode control (ACMC) for single-phase ac-dc boost converters with power factor correction (PFC). Traditional ACMC is generalized in a sense that it offers improved performance in the form of significant reduction of the current control loop bandwidth requirement for a given line frequency in unidirectional and bidirectional boost PFC converters, and additional functionality in the form of reactive power control capability in bidirectional converters. These features allow using a relatively low switching frequency and slow-switching power devices such as insulated-gate bipolar transistors (IGBTs) in boost PFC converters, including those designed for higher ac line frequencies such as in aircraft power systems (360–800 Hz). In bidirectional boost PFC converters, including multilevel topologies, the GACMC offers a capability to supply a prescribed amount of reactive power (with leading or lagging current) independently of the dc load power, which allows the converter to be used as a static reactive power compensator in the power system.

A closed-loop dynamic model for the current control loop of the boost PFC converter with the ACMC has been developed. The model explains the structure of the converter input admittance, the current phase lead phenomenon, and lays the groundwork for development of the GACMC. The leading phase admittance cancellation (LPAC)

principle has been proposed to completely eliminate the current phase lead phenomenon and, consequently, the zero-crossing distortion in unidirectional converters. The LPAC technique has been adapted for active compensation of the input filter capacitor current in bidirectional boost PFC converters.

The dynamic model of the current control loop for bidirectional boost PFC converters was augmented to include a reactive power controller. The proposed control strategy enables the converter to process reactive power and, thus, be used as a reactive power compensator, independently of the converter operation as an ac-dc converter.

Multiple realizations of the reactive power controller have been identified and examined in a systematic way, along with their merits and limitations, including susceptibility to the ac line noise. Frequency response characteristics of reactive elements emulated by means of these realizations have been described.

Theoretical principles and practical solutions developed in this dissertation have been experimentally verified using unidirectional and bidirectional converter prototypes. Experimental results demonstrated validity of the theory and proposed practical implementations of the GACMC.

### Acknowledgments

I would like to thank Prof. Jason Lai for being my advisor and presenting me an opportunity to study and do research at the Future Energy Electronics Center at Virginia Tech. These years in the doctoral program filled with challenging classes, exciting projects, long evenings in the lab, and presenting my work at conferences were the time of my development as a power electronics specialist and a researcher.

I would like to thank Prof. K.-S. Tam and Prof. D. K. Lindner, members of my Ph.D. advisory committee, for making valuable comments that helped me make this work better.

I would like to thank Prof. Y. Liu and Prof. D. J. Nelson for serving as members of my Ph.D. advisory committee.

My appreciation goes to Brad Tomlinson and Alex Miller, undergraduate students, for their help with assembly of the hardware setup for my research. Mr. Gary Kerr was indispensable with his help and skills as a machinist.

Many thanks go to my fellow graduate students at the Future Energy Electronics Center, who made these years easier and more enjoyable in the atmosphere of fellowship and camaraderie.

Finally, my special thanks are to my family, relatives, and friends for their moral support and encouragement.

#### **Table of Contents**

| 1. | INTRODUCTION                                                         | 1  |

|----|----------------------------------------------------------------------|----|

|    | 1.1 MOTIVATION                                                       | 1  |

|    | 1.2 OVERVIEW OF THE PRESENT STATE OF TECHNOLOGY                      | 5  |

|    | 1.3 DISSERTATION OUTLINE AND MAJOR RESULTS                           | 10 |

| 2. | CURRENT PHASE LEAD COMPENSATION IN SINGLE-PHASE PFC BOOST            |    |

|    | CONVERTERS WITH A REDUCED SWITCHING FREQUENCY TO LINE FREQUENCY      |    |

|    | RATIO                                                                | 17 |

|    | 2.1 Introduction                                                     | 17 |

|    | 2.2 System Modeling.                                                 | 21 |

|    | 2.3 CURRENT PHASE LEAD COMPENSATION.                                 | 27 |

|    | 2.3.1 Current Reference Correction                                   | 27 |

|    | 2.3.2 Leading-Phase Admittance Cancellation                          | 32 |

|    | 2.3.3 Implementation of the LPAC                                     | 37 |

|    | 2.4 Experimental Results                                             | 43 |

|    | 2.5 Summary                                                          | 48 |

| 3. | ACTIVE COMPENSATION OF THE INPUT FILTER CAPACITOR CURRENT IN SINGLE- |    |

|    | PHASE PFC BOOST CONVERTERS                                           | 49 |

|    | 3.1 Introduction                                                     | 49 |

|    | 3.2 BIDIRECTIONAL PFC BOOST CONVERTER                                | 51 |

|    | 3.3 UNIDIRECTIONAL PFC BOOST CONVERTER                               | 62 |

|    | 3.4 Experimental Results                                             | 74 |

|    | 3.5 Summary                                                          | 78 |

| 4. | A SINGLE-PHASE MULTILEVEL ACTIVE-FRONT-END CONVERTER WITH REACTIVE   |    |

|    | POWER CONTROL                                                        | 79 |

|    | 4.1 Introduction                                                     | 79 |

|    | 4.2 Converter Modeling And Control                                   | 81 |

|    | 4.2.1 Modeling and Control for Unity Power Factor                    | 81 |

|    | 4.2.2 Reactive Power Control                                         |    |

|    | 4.2. CONVERTED DESIGN                                                | 02 |

|    | 4.4 Experimental Results                                          | 99  |

|----|-------------------------------------------------------------------|-----|

|    | 4.5 Summary                                                       | 106 |

| 5. | REACTIVE POWER CONTROL REALIZATIONS IN SINGLE-PHASE ACTIVE-FRONT- |     |

|    | END CONVERTERS                                                    | 107 |

|    | 5.1 Introduction                                                  | 107 |

|    | 5.2 REACTIVE POWER CONTROL                                        | 108 |

|    | 5.3 CONTROLLER REALIZATIONS                                       | 121 |

|    | 5.4 Noise Performance                                             |     |

|    | 5.5 Experimental Results                                          | 128 |

|    | 5.6 Summary                                                       | 133 |

| 6. | CONCLUSIONS                                                       | 135 |

| AP | PENDIX: CONVERTER PARAMETERS                                      | 141 |

| RE | FERENCES                                                          | 143 |

| Vľ | ΓΑ                                                                | 148 |

## **List of Figures**

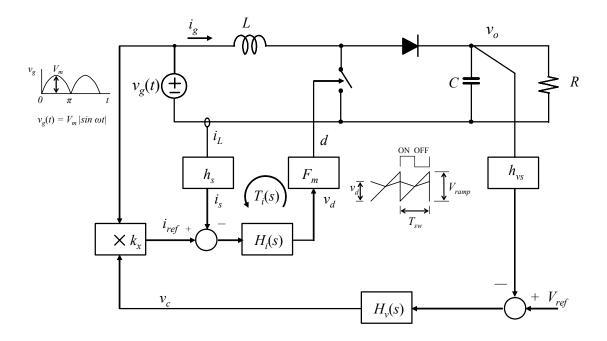

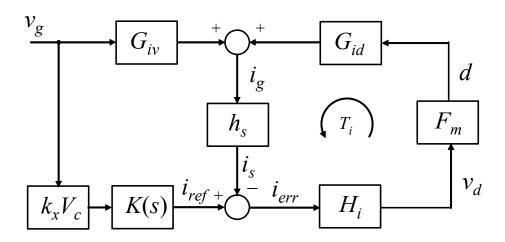

| Figure 2.1 PFC boost converter control diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

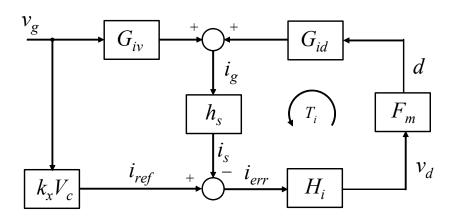

| Figure 2.2 PFC boost converter current loop control diagram in terms of transfer functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23    |

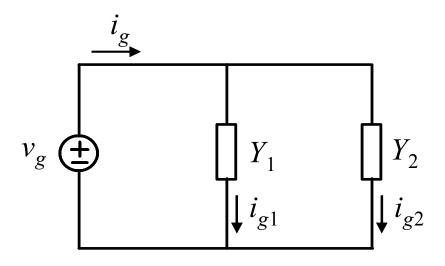

| Figure 2.3 Closed-loop input admittance represented by two branches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 26    |

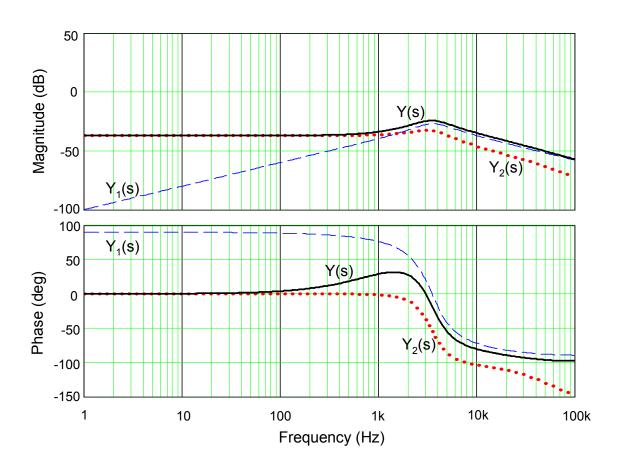

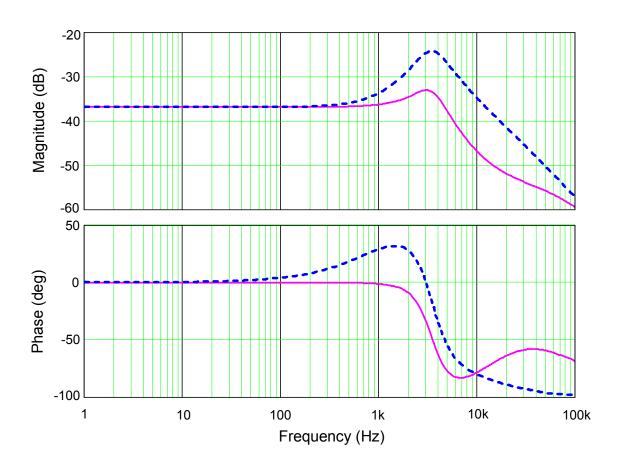

| Figure 2.4 Closed-loop input admittance and its components.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 28    |

| Figure 2.5 Current phase lead compensation using current reference correction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 29    |

| Figure 2.6 Closed-loop input admittance with current reference correction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31    |

| Figure 2.7 Two ways of implementing the leading-phase admittance cancellation for current phase admittance cancell | ad    |

| compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 34    |

| Figure 2.8 Elimination of the current phase lead by canceling the current in the leading-phase admitta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ance  |

| branch.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35    |

| Figure 2.9 Closed-loop input admittance with leading-phase admittance cancellation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 36    |

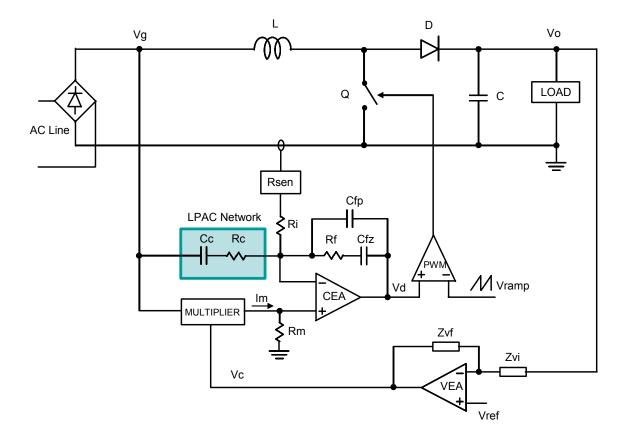

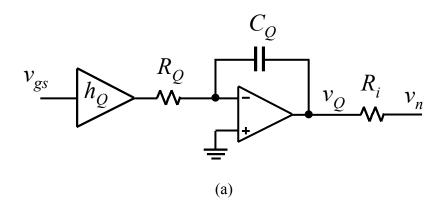

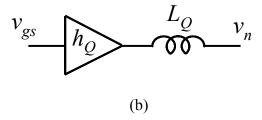

| Figure 2.10 Generic implementation of the LPAC as part of the current loop compensator circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 38    |

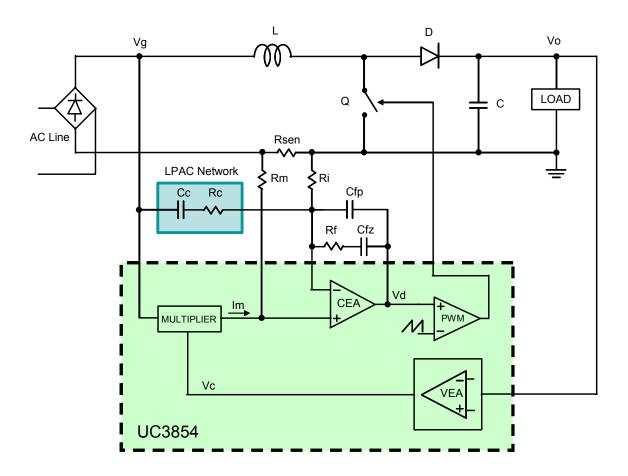

| Figure 2.11 The LPAC implementation in the UC3854-based controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40    |

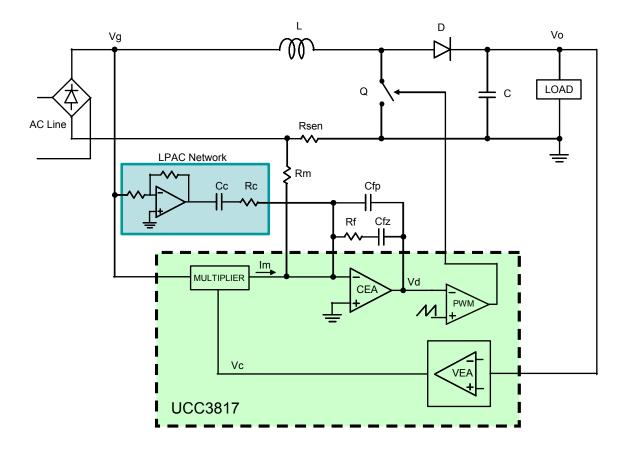

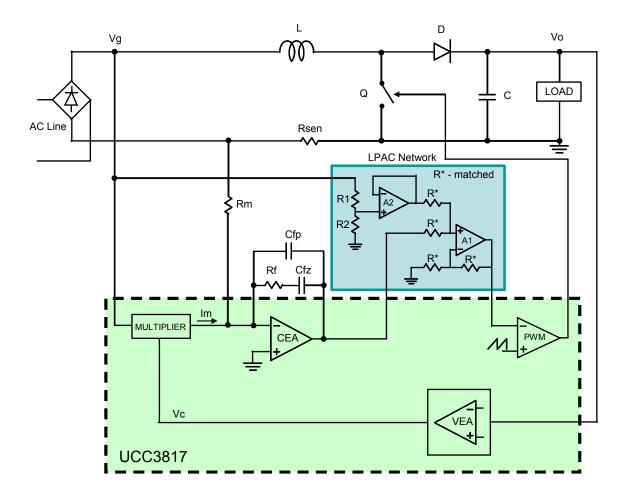

| Figure 2.12 The LPAC implementation in the UCC3817-based controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 41    |

| Figure 2.13 The LPAC implementation in the UCC3817-based controller without using a negative su                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ıpply |

| voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42    |

| Figure 2.14 Experimental setup used to verify the LPAC method.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 44    |

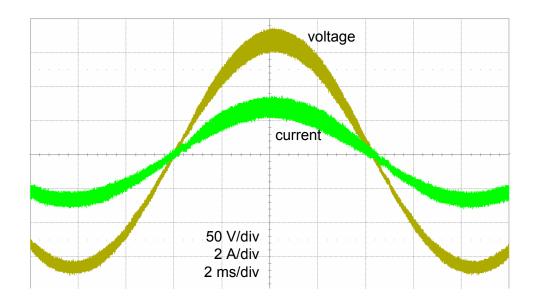

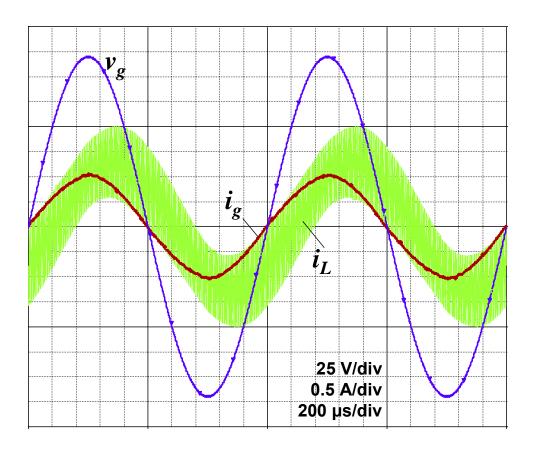

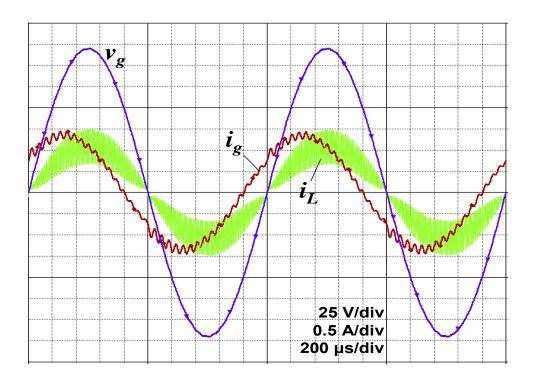

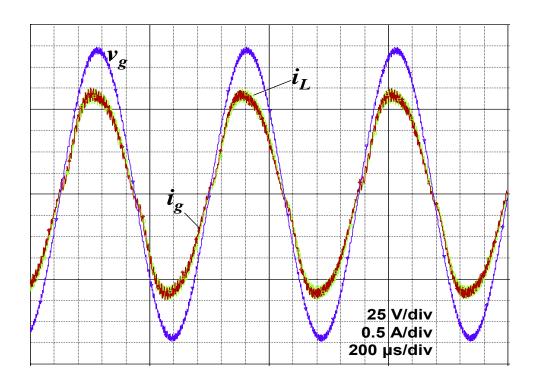

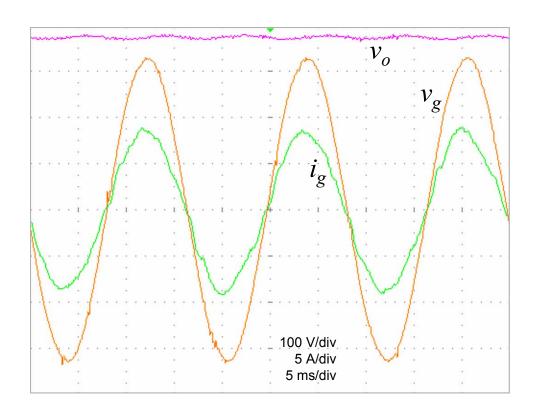

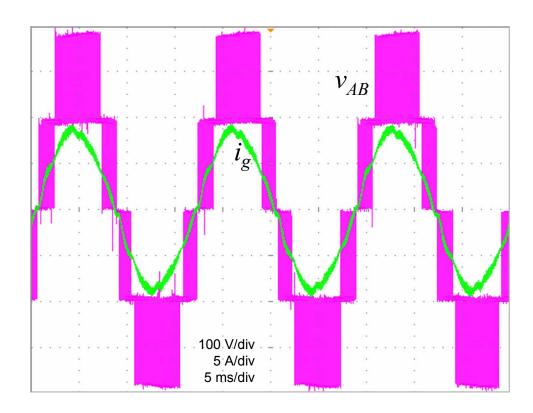

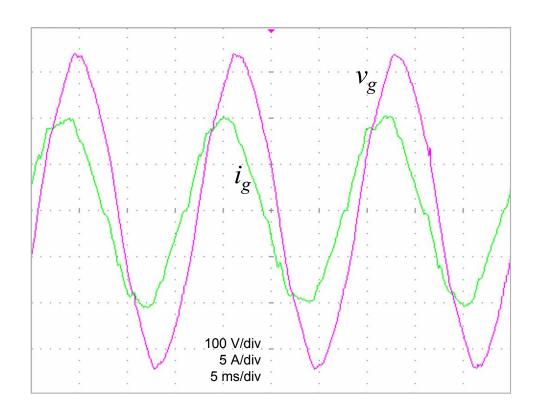

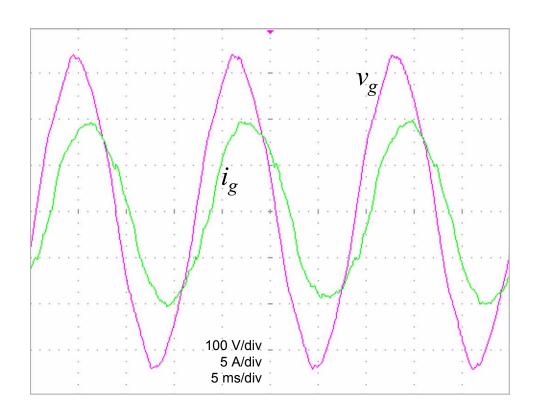

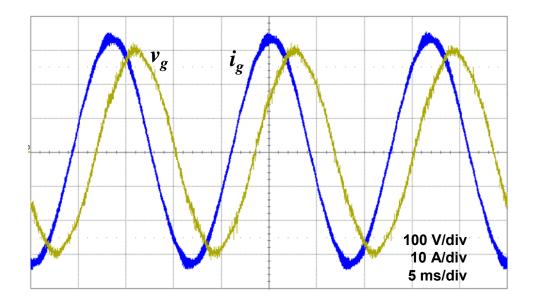

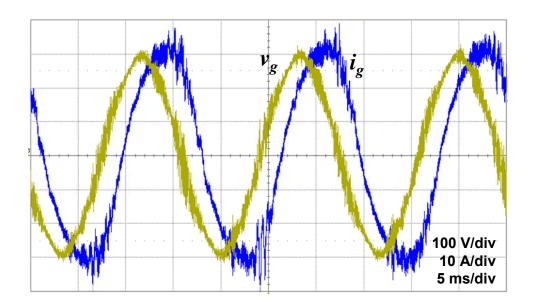

| Figure 2.15(a) Experimental converter waveforms: $f_{line} = 60 \text{ Hz}$ , $f_{sw} = 90 \text{ kHz}$ , standard controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 45    |

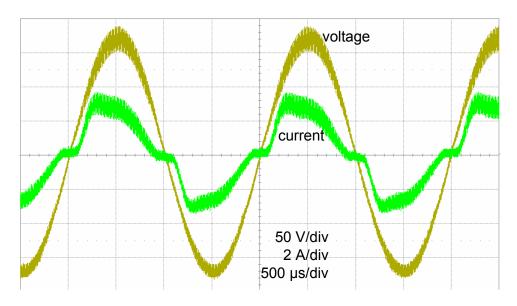

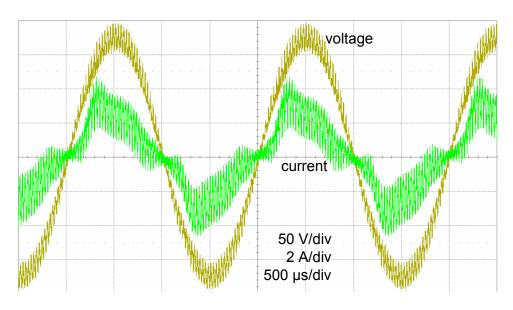

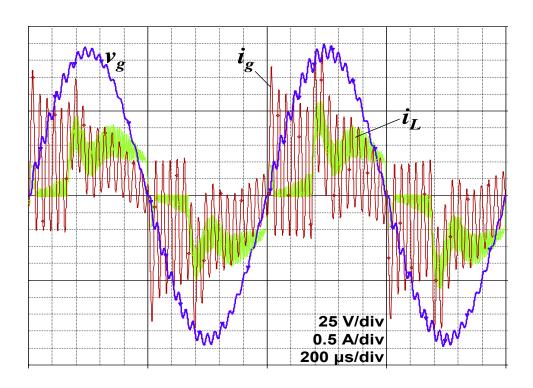

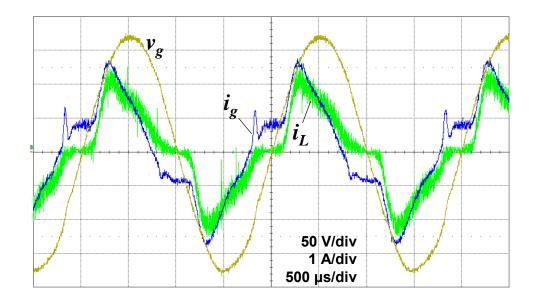

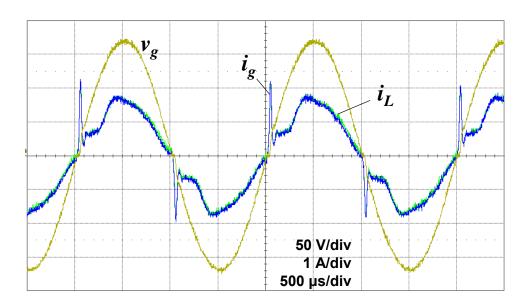

| <b>Figure 2.15(b)</b> Experimental converter waveforms: $f_{line} = 500 \text{ Hz}$ , $f_{sw} = 90 \text{ kHz}$ , standard controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 46    |

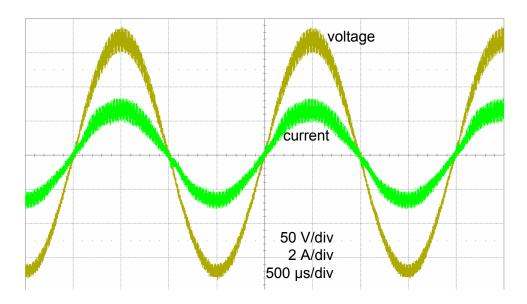

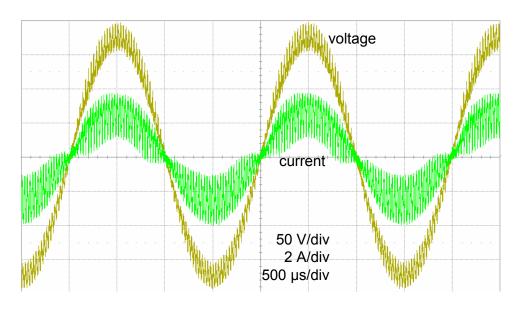

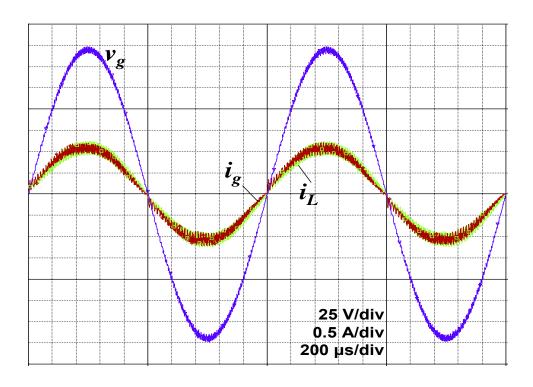

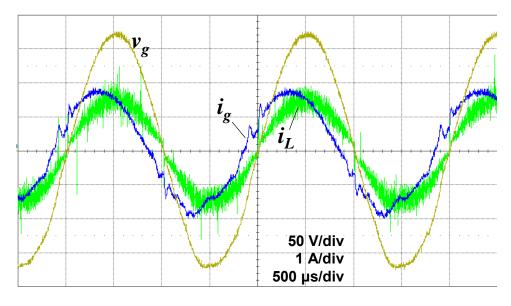

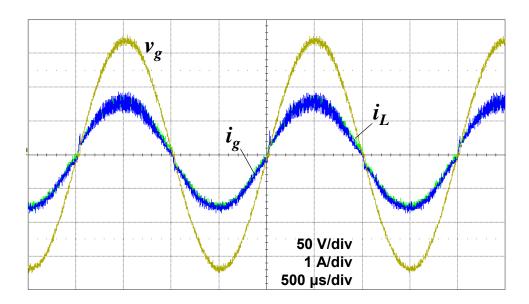

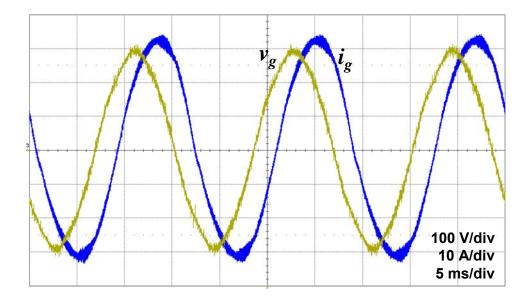

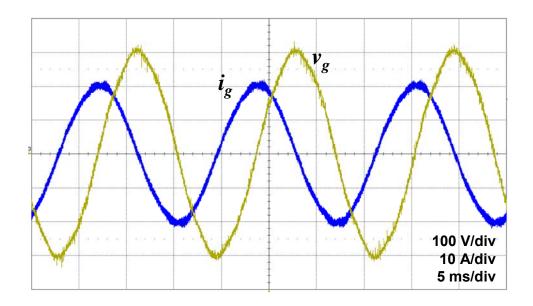

| Figure 2.15(c) Experimental converter waveforms: $f_{line} = 500 \text{ Hz}$ , $f_{sw} = 90 \text{ kHz}$ , with LPAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 46    |

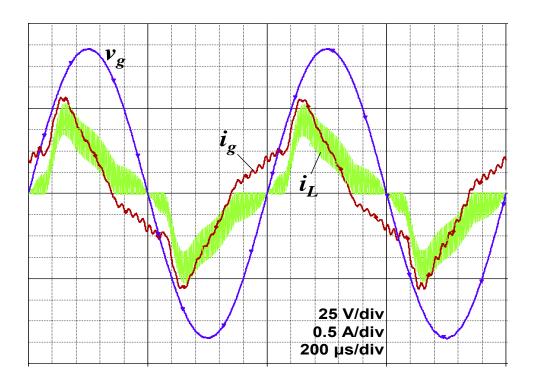

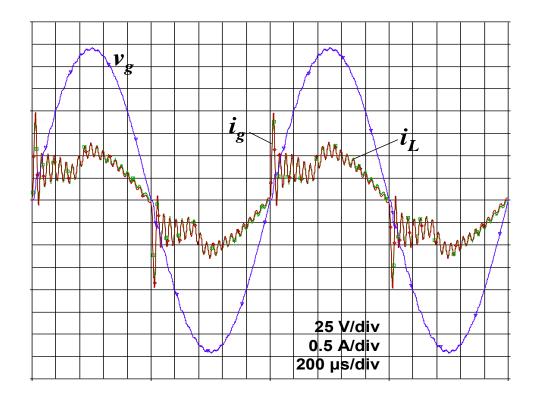

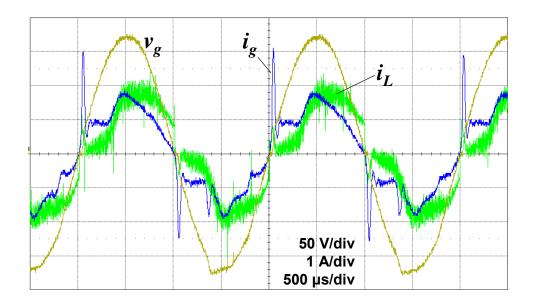

| <b>Figure 2.15(d)</b> Experimental converter waveforms: $f_{line} = 500 \text{ Hz}$ , $f_{sw} = 35 \text{ kHz}$ , standard controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 47    |

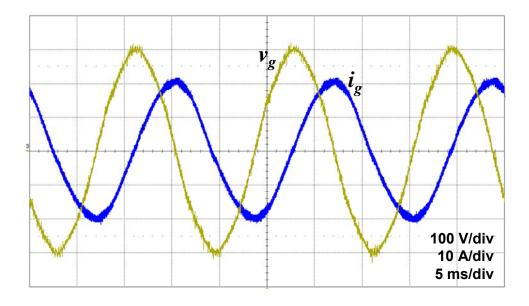

| Figure 2.15(e) Experimental converter waveforms: $f_{line} = 500 \text{ Hz}$ , $f_{sw} = 35 \text{ kHz}$ , with LPAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 47    |

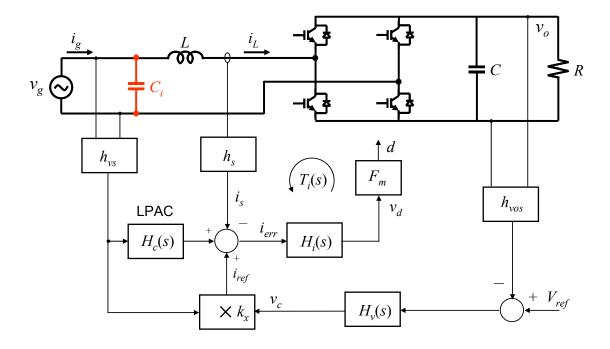

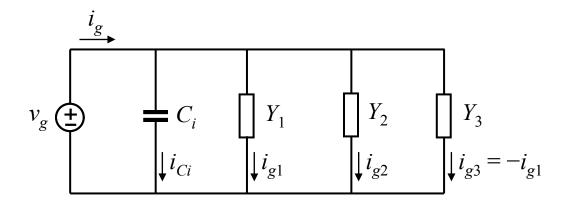

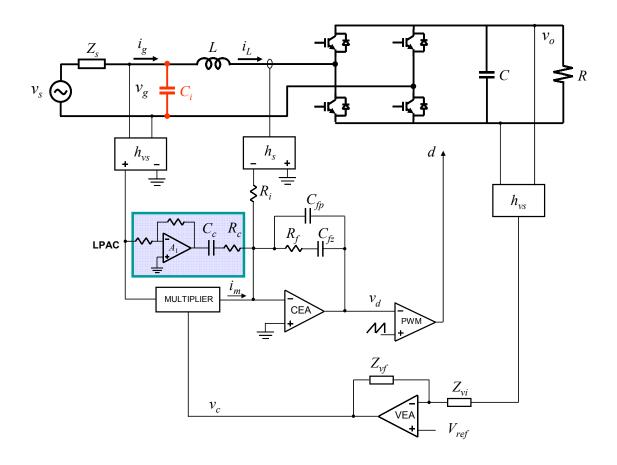

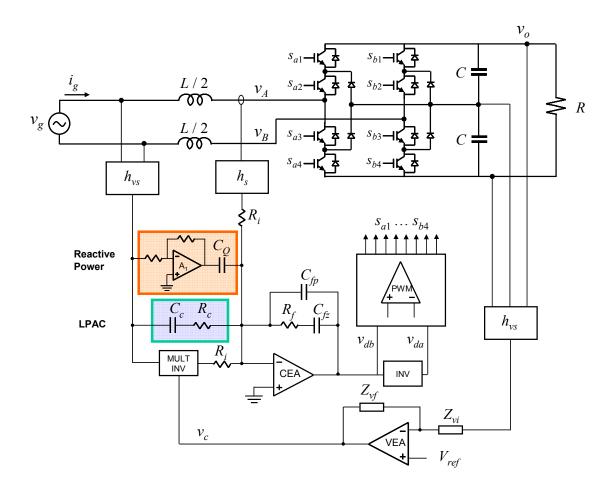

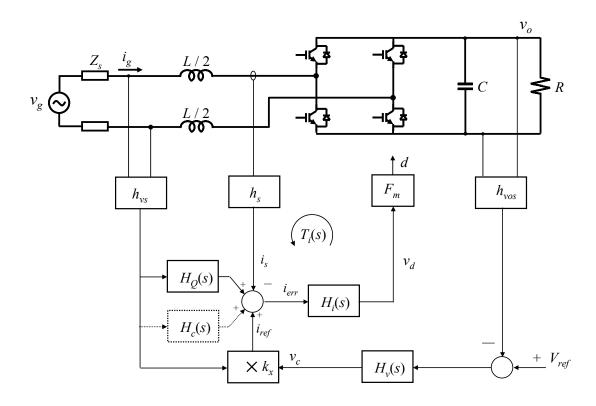

| Figure 3.1 Full-bridge PFC converter with an input filter capacitor and LPAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 52    |

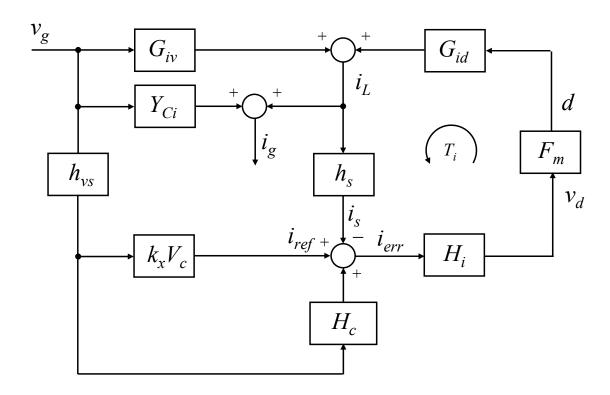

| Figure 3.2 Current loop control diagram of the converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 53    |

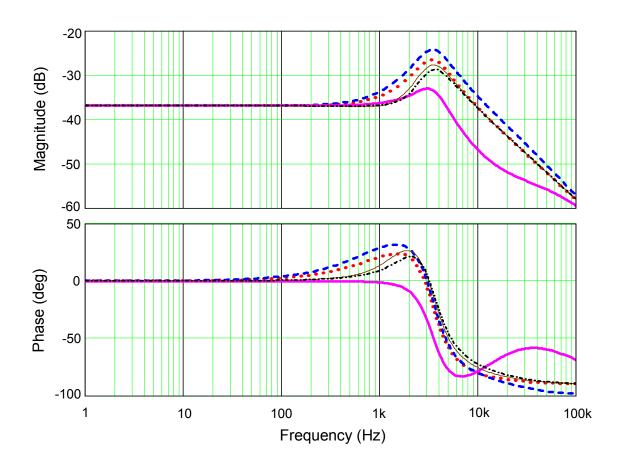

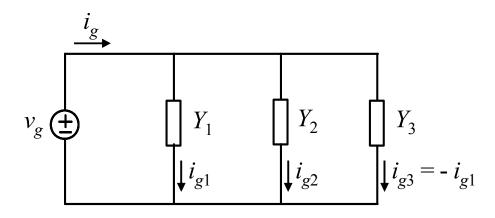

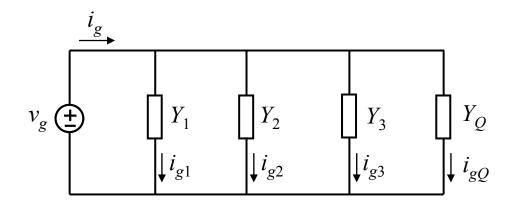

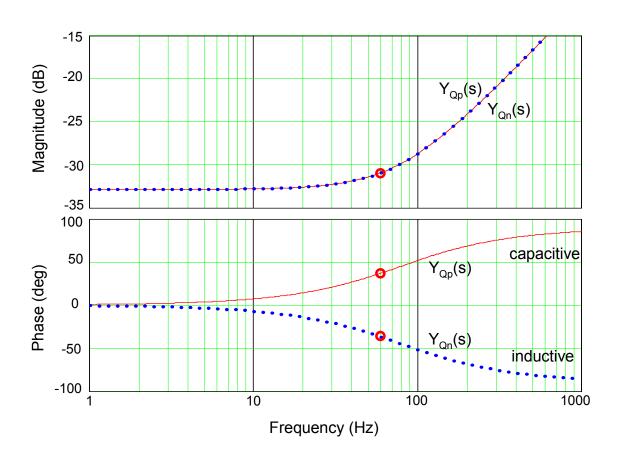

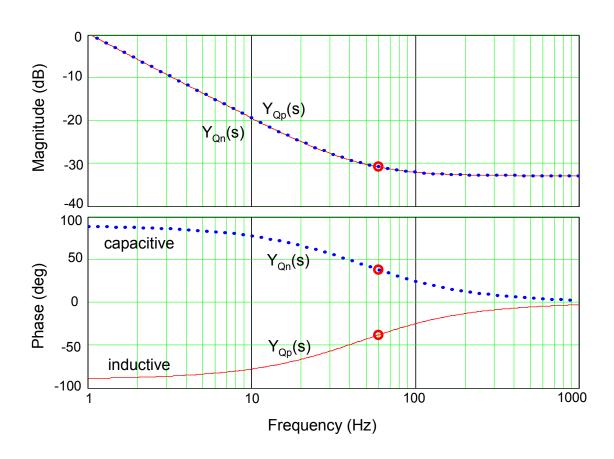

| Figure 3.3 Input admittance of the converter with the input filter capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55    |

| Figure 3.4 Implementation of the bidirectional PFC converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57    |

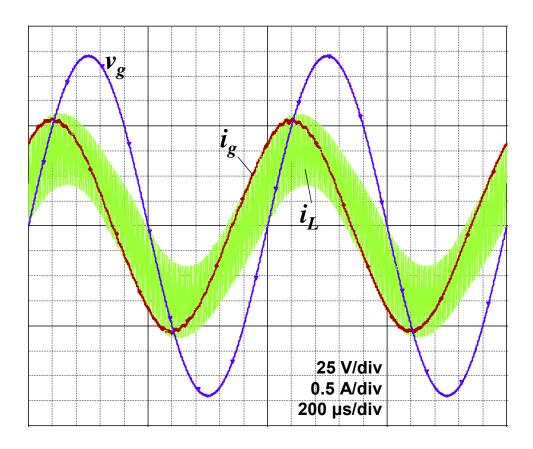

| Figure 3.5 Bidirectional PFC converter operation with a standard controller (without LPAC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 59    |

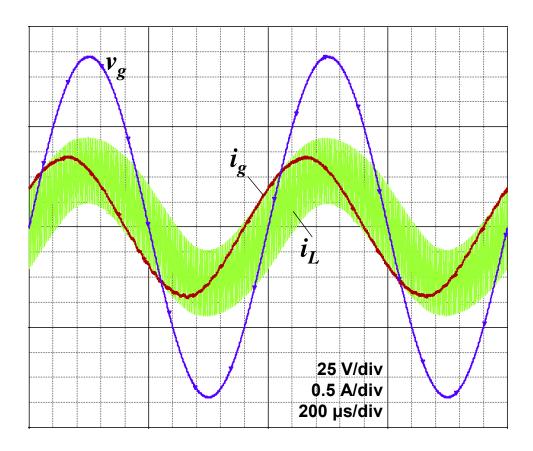

| Figure 3.6 Bidirectional PFC converter operation with LPAC-compensated inductor current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 60    |

| Figure 3.7 Bidirectional PFC converter operation with LPAC-compensated total current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 61    |

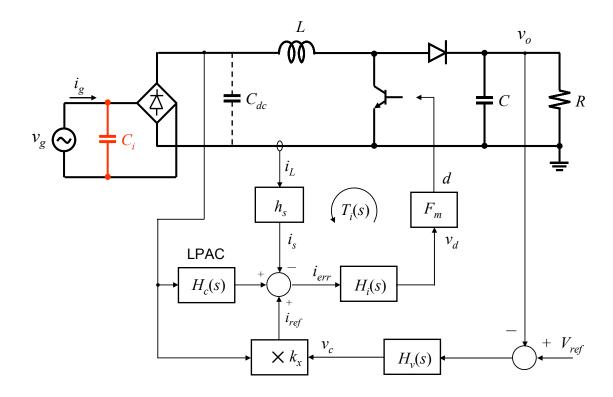

| Figure 3.8 Unidirectional PFC boost converter with an input filter capacitor and the LPAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63    |

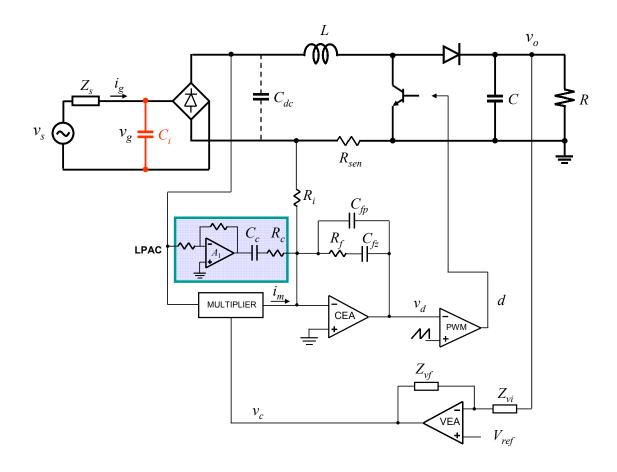

| Figure 3.9 Implementation of the unidirectional PFC boost converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 64    |

| Figure 3.10 Unidirectional PFC converter operation with a standard controller (no LPAC).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 67    |

| Figure 3.11 U | Unidirectional PFC converter operation with LPAC-compensated inductor current                  | 68 |

|---------------|------------------------------------------------------------------------------------------------|----|

| Figure 3.12 U | Unidirectional PFC converter, an attempt to compensate both inductor current and $C_i$ current | t. |

|               |                                                                                                | 69 |

| Figure 3.13 U | Unidirectional PFC converter, LPAC-compensated with a large $C_{dc}$                           | 71 |

| Figure 3.14 U | Unidirectional PFC converter, LPAC-compensated unity-power-factor operation                    | 72 |

| Figure 3.15 U | Unidirectional PFC converter, LPAC-compensated unity-power-factor operation                    | 73 |

| Figure 3.16 E | Experimental waveforms of the unidirectional PFC converter operation with a standard           |    |

| controller    | (no LPAC)                                                                                      | 75 |

| Figure 3.17 E | Experimental waveforms of the converter with LPAC-compensated inductor current                 | 75 |

| Figure 3.18 E | Experimental waveforms of the converter, an attempt to compensate both inductor current an     | nd |

| $C_i$ current |                                                                                                | 76 |

| Figure 3.19 E | Experimental waveforms of the converter, LPAC-compensated with a large $C_{dc}$                | 76 |

| Figure 3.20 E | Experimental waveforms of the converter, LPAC-compensated, operation with unity power          |    |

| factor        |                                                                                                | 77 |

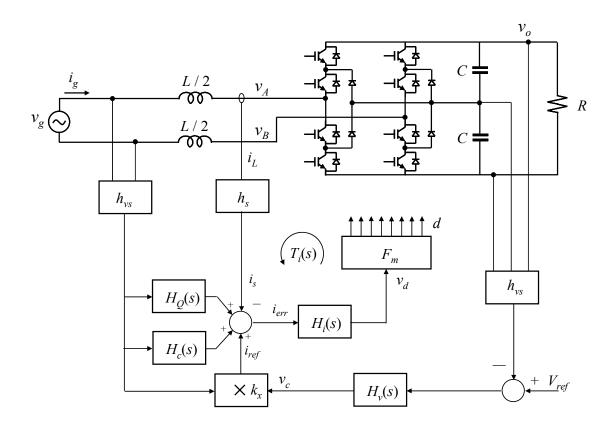

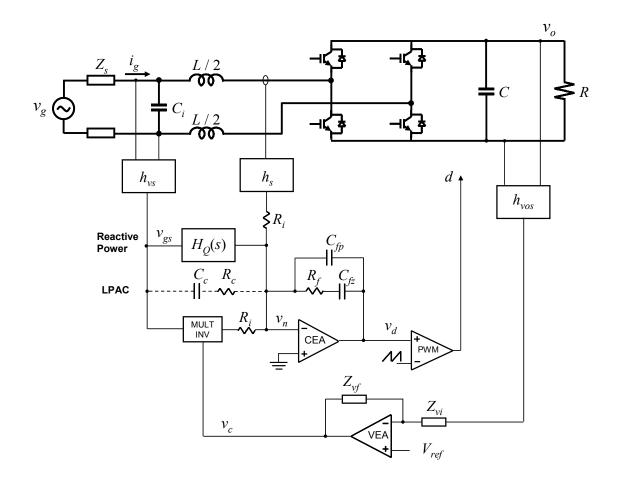

| Figure 4.1 Th | ne AFE converter and its control system.                                                       | 82 |

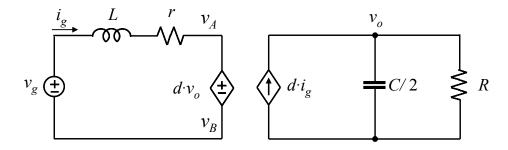

| Figure 4.2 Av | verage model of the AFE converter.                                                             | 83 |

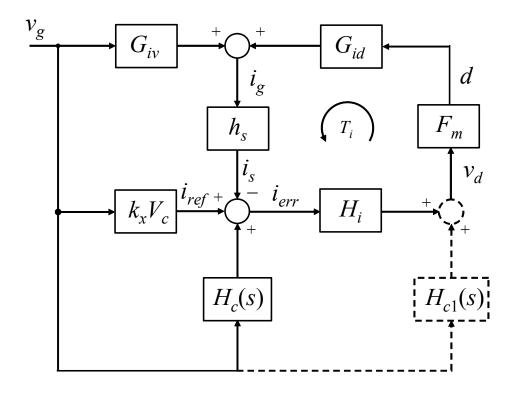

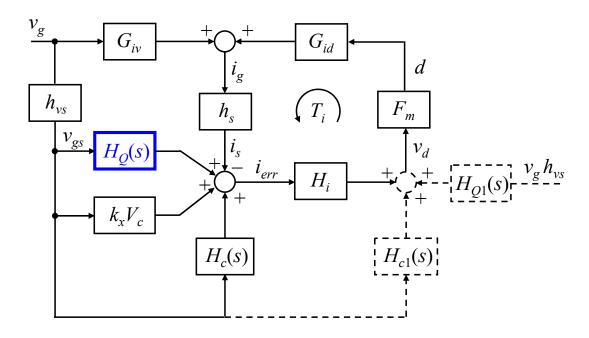

| Figure 4.3 Im | nplementation of the AFE converter control system.                                             | 87 |

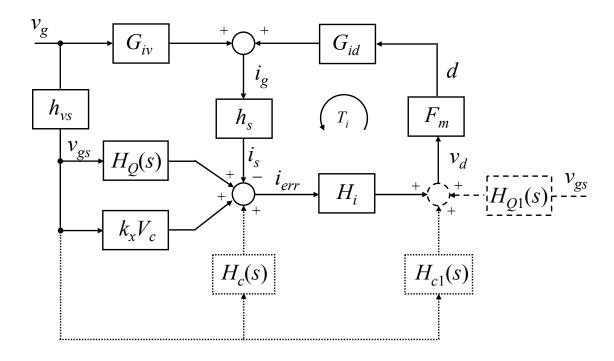

| Figure 4.4 In | put admittance components of the AFE converter with reactive power control.                    | 89 |

| Figure 4.5 Al | FE converter current loop control diagram with alternative implementations of the reactive     |    |

| power cor     | ntroler.                                                                                       | 91 |

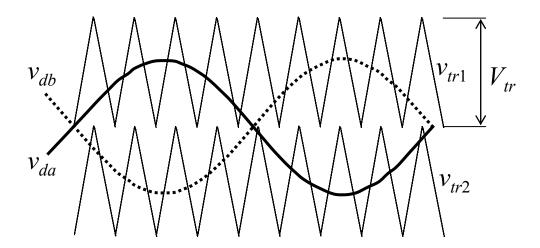

| Figure 4.6 M  | ultilevel PWM modulator input and carrier signals are used to produce gate driving signals.    |    |

|               |                                                                                                | 95 |

| Figure 4.7 Th | ne AFE converter operation with 20 kW real power and 10 kVA reactive (leading phase)           |    |

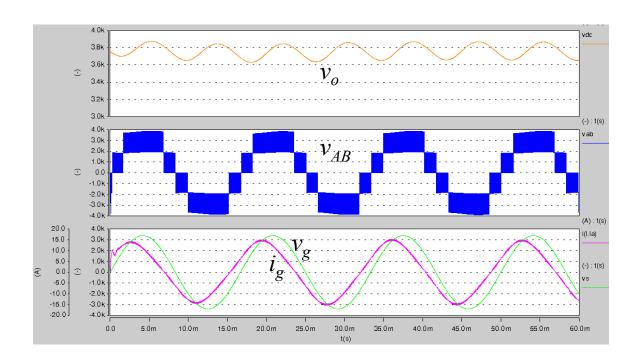

| power         |                                                                                                | 97 |

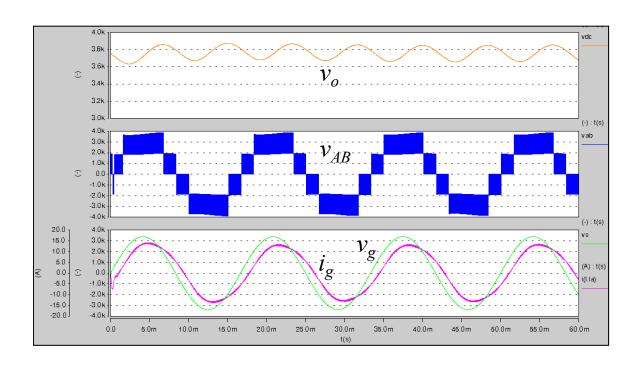

| Figure 4.8 Th | ne AFE converter operation with 20 kW real power and 10 kVA reactive (lagging phase)           |    |

| -             |                                                                                                |    |

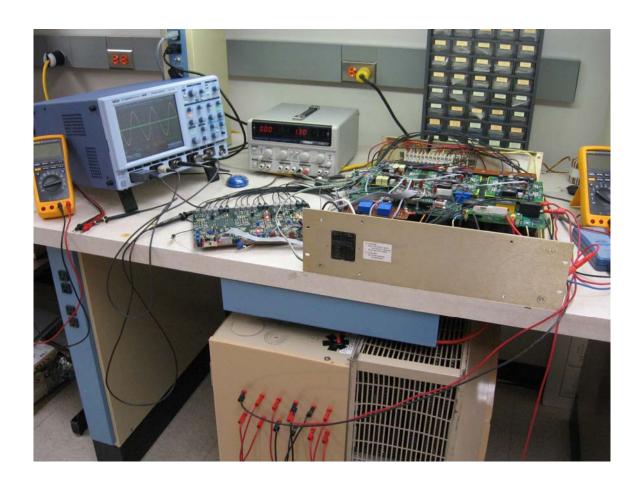

| Figure 4.9 Ex | sperimental setup used to verify the reactive power control principle                          | 00 |

| Figure 4.10 T | The AFE converter operating without LPAC has a leading phase of the line current               | 01 |

| Figure 4.11 U | Unity-power-factor operation of the converter operating with LPAC enabled 1                    | 02 |

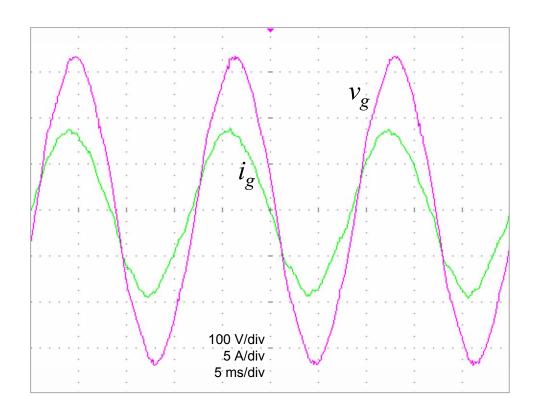

| Figure 4.12   | Current and voltage waveforms of the converter operating with unity power factor 1             | 03 |

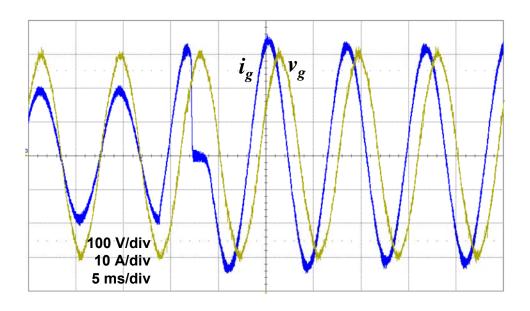

| o .           | Converter operation with 1.44 kW real power and 0.86 kVA reactive power (leading phase).       |    |

|               |                                                                                                |    |

|               | Converter operation with 1.44 kW real power and 0.86 kVA reactive power (lagging phase).       |    |

|               |                                                                                                | 05 |

| Figure 5.1 Al | FF converter control system                                                                    | 10 |

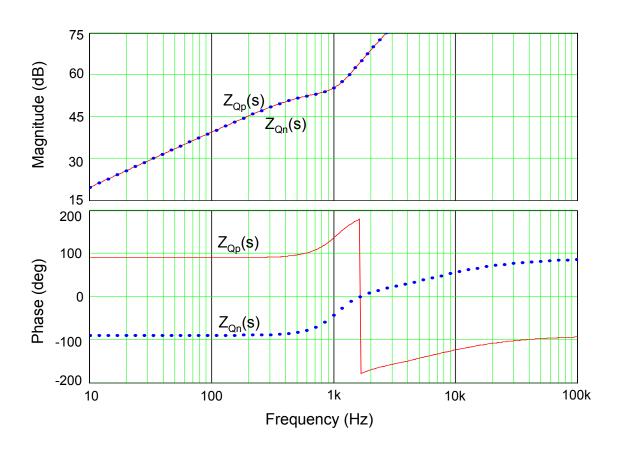

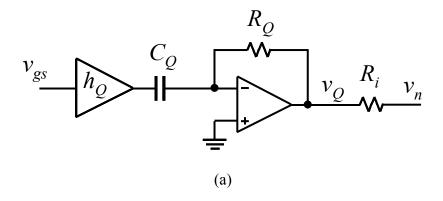

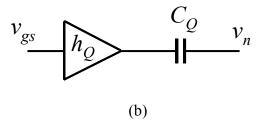

| Figure 5.2  | AFE converter current loop control diagram with alternative implementations of reactive por        | wer |

|-------------|----------------------------------------------------------------------------------------------------|-----|