Fabrication Refinements of Advanced Packaging Techniques for Medium-Voltage Wirebond-less Multi-Chip Power Modules

Danielle Kathryn Lester

A thesis submitted to the faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

> Master of Science In Electrical Engineering

Christina DiMarino (Chair) Guo-Quan Lu Jaime De La Ree

### June 8<sup>th</sup>, 2023 Arlington, Virginia

Keywords: SiC MOSFET, packaging, multi-chip power module, statistical tolerance analysis, wirebond-less interconnect

Copyright © 2023, Danielle Kathryn Lester

### Fabrication Refinements of Advanced Packaging Techniques for Medium-Voltage Wirebond-less Multi-Chip Power Modules

Danielle Kathryn Lester

### ABSTRACT

Three growing power electronics applications have massive requirements for properly operating their medium-voltage and high-voltage systems: electric transportation, renewable energy, and the power grid. Their needs include dense power systems with higher efficiency and higher voltage and current devices. This requires devices with higher switching frequencies to lower the size of the passives in the converter and devices that can withstand higher operating temperatures as components move closer together to improve power densities. Devices that achieve higher switching speeds and lower specific on-state resistances also reduce losses.

Wide bandgap devices (WBG) like silicon carbide (SiC) have a higher bandgap, higher electric field strength, higher thermal conductivity, and lower carrier concentration than silicon (Si). This allows for higher temperature operation, faster switching, higher voltage blocking, and lower power losses, directly meeting the requirements of the previously noted applications. However, the current packaging schemes are limiting the ability of SiC to operate in these applications by applying packaging schemes used for Si. Therefore, it is critical to use and refine advanced packaging techniques so that WBG devices can better operate and meet the growing demands of these power electronic applications.

Low-inductance, wirebond-less, high-density, scalable modules are possible due to advanced packaging methods. While beneficial to the operation and design, these techniques introduce new challenges to the fabrication process. This requires refinement to improve the yield of sandwich-structure modules with wirebond-less interconnects. For this module, encapsulated, silver-sintered substrates reduce the peak electric field within the package, improving the partial discharge inception voltage to meet insulation requirements. It is essential to have a uniform bondline between the substrates to achieve all bond connections and improve reliability. Silver sintering is also used to attach the molybdenum (Mo) post interconnects. These interconnects allow for sandwich-structure modules with low inductances; however, they have tolerance variation from manufacturing and bondline thicknesses, which become problematic for multi-chip power modules with an increased number of die and posts. The variation results in tilt, causing some posts to disconnect altogether. Additionally, soldering MCPMs involves a large thermal mass that the soldering reflow profile from a datasheet does not account for.

Ultimately, these fabrication concerns can result in misalignment or disconnected post interconnects to the top substrate. Post interconnect planarity and alignment are vital for this multi-chip power module to avoid open or shorted connections that can derate switch positions. This thesis aims to refine each packaging step in assembling a wirebondless, multi-chip power module. The bond uniformity of silver (Ag) sintering is addressed in dried preform and wet paste cases. The soldering methods are explored and improved by creating a modified reflow profile for large thermal masses and introducing pressure to reduce bondline variation and voiding content. The entire sandwich structure module is analyzed in a statistical tolerance analysis to understand which component introduces the most variation and height mismatch, providing insight as to which packaging techniques need further control to improve the yield of multi-chip power modules. Fabrication Refinements of Advanced Packaging Techniques for Medium-Voltage Wirebond-less Multi-Chip Power Modules

Danielle Kathryn Lester

### **GENERAL AUDIENCE ABSTRACT**

The electrification of many systems worldwide has increased the need for compact, efficient power electronics. Their applications span electric transportation, renewable energy systems, grid applications, and data centers, to name a few medium-voltage applications. Wide bandgap (WBG) semiconductors can outperform silicon in these applications, offering higher temperature robustness, higher efficiency performance, and higher voltage capabilities. The faster switching will reduce the size and weight of the converters containing these devices. However, using typical packaging schemes such as wirebonds will limit the potential of WBG devices in these applications.

Advanced packaging techniques have been developed to increase the electric field strength, reduce the power loop inductances, reduce electromagnetic interference from fast-switching transients, and improve the power densities of multi-chip power modules for medium voltage and current applications. However, these packaging techniques are not trivial to implement and have resulted in a low yield of these modules.

This thesis aims to refine each packaging step in assembling a wirebond-less, multichip power module. The bond uniformity of silver sintering is addressed in cases of dried preform and wet paste. The soldering methods are explored and improved by creating a modified reflow profile for large thermal masses and introducing pressure to reduce bondline variation and voiding content. The entire sandwich structure module is analyzed in a statistical tolerance analysis to understand which component introduces the most variation and height mismatch, providing insight as to which packaging techniques need further control to improve the yield of multi-chip power modules.

#### ACKNOWLEDGEMENTS

I would first like to thank the Bradley Endowment for its financial support through the Bradley Scholarship and Bradley Fellowship during my academic career. The ability to pursue my interests in electrical engineering without the fear of economic restriction has allowed my knowledge to grow deeper and more freely than I could have imagined. For this, I would like to thank Dr. Luke Lester for allowing me to experience all Virginia Tech has to offer and for seeing the potential in me for this great honor.

My advisor, Dr. Christina DiMarino, most influenced my graduate student career. She has been an incredible role model as an intelligent, respected, and inspirational female figure in power electronics. She always guided and challenged me to become a better researcher than the day before and has sparked a passion for power electronics packaging that I wouldn't have known existed. I will be forever grateful for her advice and the opportunity to be a part of the group of students she has created here at CPES.

I am incredibly grateful to Dr. Jaime De La Ree, who has been my greatest mentor and like family over the six years I have spent as an undergraduate and graduate student at Virginia Tech. No one has pushed me harder to become a better engineer, and I am grateful for every moment I have spent learning from him. He has taught me many valuable lessons, not just about electrical engineering, but about life, that I will cherish and remember for the rest of my time.

I owe many of my successes to Dr. DiMarino's students: Mark Cairnie, Narayan Rajagopal, and Jack Knoll. Mark Cairnie gave hours of his time to help me fabricate my first package, and I am amazed by his intelligence and ability to be a great teacher and friend. Narayan and Jack selflessly helped me become the engineer I am today by teaching me the knowledge and skills needed for my research. I am forever grateful not only for their advice but for their friendship. I would also like to thank another student, Minh Ngo, who introduced me to CPES and helped guide me into my graduate student role. Without him, I would not have been in this program today.

I have received support from many other students outside of my own advisor's group, specifically Dr. Guo-Quan Lu's students: Filip Boshkovski and Zichen Zhang. I want to thank them for their time and support in helping an electrical engineering student explore the critical knowledge of material science. Their willingness to help never went unnoticed, and I am very grateful for all their time and advice.

There are many people to thank who keep CPES running and have helped fuel my work from behind the scenes: David Gilham, Don Leber, Matthew Scandland, Neil Croy, Yan Sun, Karen Griffin, Audri Cunningham, and Brandy Grim.

I would also like to acknowledge the support from the project sponsors: The Bradley Department of Electrical and Computer Engineering Fellowship, Naval Air Systems Command (NAVAIR), and the Advanced Research Projects Agency-Energy (ARPA-E). I would also like to thank the generous donations from NBETech, DOWA METALTECH, and the National Institute of Advanced Industrial Science and Technology (AIST). NBETech provided all of the nano-silver sinter paste and nano-silver sinter preform used to fabricate every module. DOWA METALTECH provided the custom substrates, and AIST provided the 13 kV SiC MOSFETs.

Finally, I would like to thank my parents, Lori and Keith, my sisters, Lauren and Stephanie, and my brother-in-law Kyle, who have always supported me and been so proud. Their love never goes unnoticed. And for the person who has been by my side through all the ups and downs, supported me no matter the time of day, and loved me through all moments, happy and challenging, Miguel Escudero. No words will ever convey how grateful I am for you every day.

## **Table of Contents**

| СНАРТ  | ER 1   INTRODUCTION                                                            |

|--------|--------------------------------------------------------------------------------|

| 1.1    | Background1                                                                    |

| 1.2    | Survey of Multi-Chip Power Module Packaging Techniques                         |

| 1.2.   | 1 Overview of the Typical Packaging Components and Schemes                     |

| 1.2.2  | 2 Current Challenges of Package Interconnects for Medium-Voltage Multi-Chip    |

| Pow    | ver Modules                                                                    |

| 1.3    | Multi-Chip Power Module Overview and Motivations for Fabrication               |

| Refine | ements for Wirebond-Less Multi-Chip Power Modules                              |

| 1.3.   | 1 Multi-Chip Power Module Overview                                             |

| 1.3.2  | 2 Motivation for Fabrication Refinements of Multi-Chip Power Modules 20        |

| 1.4    | Research Objectives and Thesis Organization                                    |

| СНАРТ  | ER 2 FABRICATION CHALLENGES AND REFINEMENTS OF                                 |

| SINTER | RING IN WIREBOND-LESS MULTICHIP POWER MODULES                                  |

| 2.1    | Introduction                                                                   |

| 2.2    | Pressure-Assisted Large-Area Sintering Methodology of Patterned                |

| Subst  | rates for Multichip Power Modules25                                            |

| 2.2.   | 1 Previous Work on Pressure-Assisted Large-Area Sintering of Plain Substrates  |

|        |                                                                                |

| 2.2.2  | 2 Challenges of Pressure-Assisted Large-Area Sintering of Patterned Substrates |

|        |                                                                                |

| 2.2   | 2.3 A New Method for Pressure-Assisted Large-Area Sintering of Patterned    |      |

|-------|-----------------------------------------------------------------------------|------|

| Sul   | bstrates                                                                    | 31   |

| 2.3   | Analysis of Substrate Warpage during Pressure-Assisted Large-Area           |      |

| Sinte | ering                                                                       | 34   |

| 2.4   | Pressure-Less Nano-Silver Sintering of Molybdenum Post Interconnects        | . 46 |

| 2.5   | Pressure-Less Nano-Silver Sintering for Die Attach                          | 50   |

| 2.6   | Summary                                                                     | 51   |

| CHAP  | TER 3 FABRICATION CHALLENGES AND REFINEMENTS OF                             |      |

| SOLDI | ERING IN WIREBOND-LESS MULTICHIP POWER MODULES                              | 53   |

| 3.1   | Introduction                                                                | 53   |

| 3.2   | Alignment of Molybdenum Post Interconnects Before Soldering                 | 54   |

| 3.3   | Soldering of Multi-Chip Power Modules with Large Thermal Masses             | 55   |

| 3.4   | Pressure Soldering Techniques for Molybdenum Post Interconnects in          |      |

| Mult  | i-Chip Power Modules                                                        | 57   |

| 3.4   | .1 Pressure-Assisted Soldering Methodology                                  | 58   |

| 3.4   | .2 Pressure-Assisted Soldering Process                                      | 61   |

| 3.4   | .3 Pressure-Assisted Soldering Verification on a Mechanical Multi-Chip Powe | er   |

| Mo    | odule                                                                       | 64   |

| 3.5   | Soldering Techniques for the Proper Alignment of Spring Pin Terminal        | 5    |

| for M | Iulti-Chip Power Modules                                                    | 66   |

| 3.6   | Summary                                                                     | 69   |

|       | v                                                                           |      |

| СНАРТ | TER 4 STATISTICAL TOLERANCE ANALYSIS OF THE                         |

|-------|---------------------------------------------------------------------|

| SANDV | VICH-STRUCTURE MODULE WITH POST INTERCONNECTS                       |

| 4.1   | Introduction70                                                      |

| 4.2   | Motivation for a Statistical Tolerance Analysis Using a Monte Carlo |

| Simu  | lation                                                              |

| 4.3   | Monte Carlo Simulation for a Sandwich-Structure Multi-Chip Power    |

| Modu  | ıle76                                                               |

| 4.3.  | 1 Building the Monte Carlo Simulation77                             |

| 4.3.  | 2 Results from the Monte Carlo Simulation                           |

| 4.4   | ANOVA Analysis Using the Monte Carlo Simulation                     |

| 4.5   | Scalability of the Monte Carlo Analysis92                           |

| 4.6   | Summary                                                             |

| СНАРТ | TER 5 EXPERIMENTAL VALIDATION OF THE FABRICATION                    |

| REFIN | EMENTS AND STATISTICAL TOLERANCE ANALYSIS FOR THE                   |

| MULTI | CHIP POWER MODULE                                                   |

| 5.1   | Introduction                                                        |

| 5.2   | Two-Die Module Fabrication and Characterization100                  |

| 5.2.  | 1 Mechanical Two-Die Module Fabrication and Characterization 100    |

| 5.2.  | 2 Functional Two-Die Module Fabrication and Characterization 103    |

| 5.2.  | 3 Functional Two-Die Module Dynamic Characterization 108            |

| 5.3   | Multi-Chip Power Module Fabrication and Static Characterization 111 |

| 5.3          | .1 Mechanical Multi-Chip Power Module Fabrication 1         | 12  |

|--------------|-------------------------------------------------------------|-----|

| 5.3          | 2 Functional Multi-Chip Module Fabrication 1                | 14  |

| 5.3          | .3 Static Characterization of the Multi-Chip Power Module 1 | 16  |

|              |                                                             |     |

| 5.4          | Summary1                                                    | 118 |

| 5.4<br>CHAPT |                                                             |     |

|              |                                                             | 120 |

**REFERENCES 127**

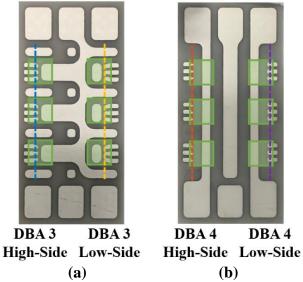

# List of Figures

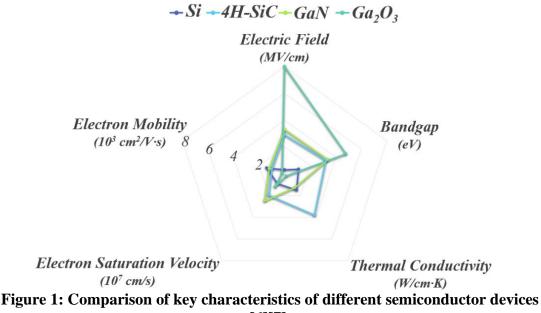

| Figure 1: Comparison of key characteristics of different semiconductor devices [6][7] 1  |

|------------------------------------------------------------------------------------------|

| Figure 2: Conventional power module packaging scheme with crucial components             |

| labeled [16]                                                                             |

| Figure 3: Various interconnects including (a) Al wirebonds [30] (b) Cu wirebonds [31]    |

| (c) Au wirebonds [32] (d) Flip-chip solder bumps [33] (e) Press-pack [34] (f) Fuzz       |

| buttons [35] (g) Cu clips [36] (h) Flexible PCB [37] and (i) Metal posts [21]7           |

| Figure 4: (a) Commercial 10 kV modules with wirebonds and their respective power loop    |

| inductance and power density [17], [18]. (b) CPES 10 kV modules with Mo post             |

| interconnects, and their respective parasitic inductance and power density improved from |

| the wirebonded modules [29], [53]15                                                      |

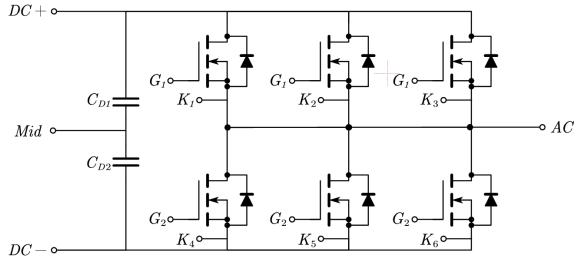

| Figure 5: Half-bridge circuit schematic of the MCPM in Figure 6 with six devices,        |

| separate kelvin connections, and embedded decoupling capacitors                          |

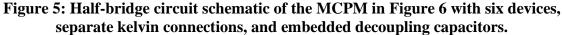

| Figure 6: Medium-voltage, multi-chip power module with stacked aluminum nitride,         |

| direct-bonded aluminum substrates, silver sinter bonds, molybdenum post interconnects,   |

| embedded decoupling capacitors, and spring pin terminals                                 |

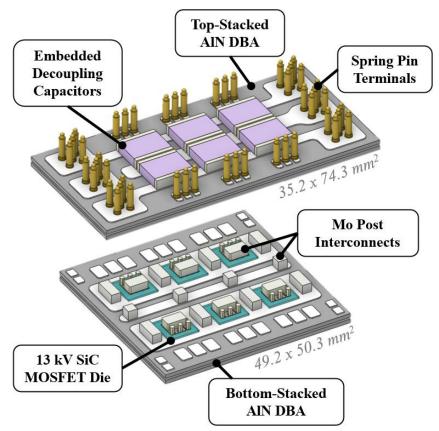

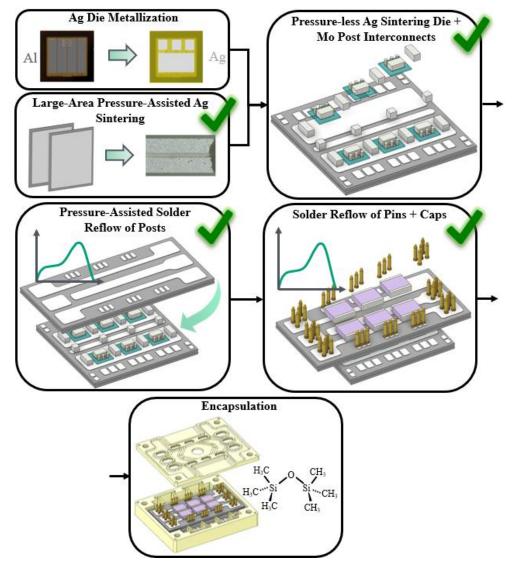

| Figure 7: Fabrication process for the multi-chip power module in [50] 18                 |

| Figure 8: Advanced packaging techniques and fabrication refinements developed for        |

| MCPMs                                                                                    |

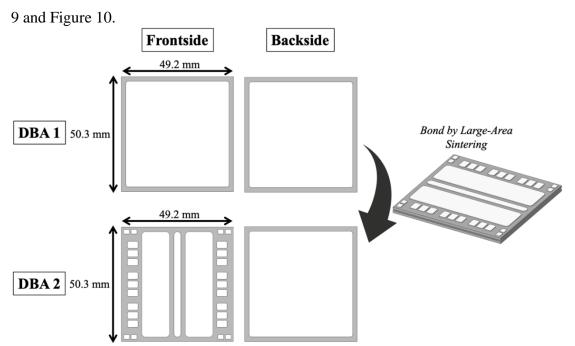

| Figure 9: DBA 1 and DBA 2 sizing, patterning, and stacking method                        |

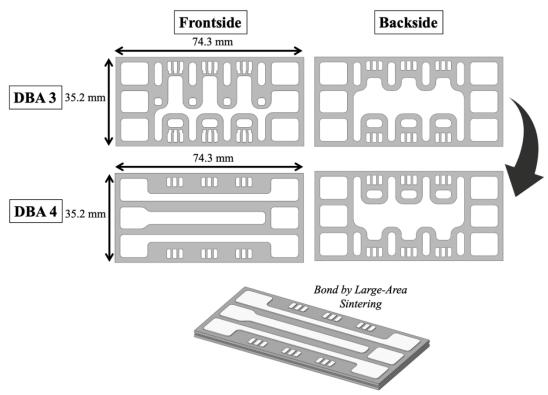

| Figure 10: DBA 3 and DBA 4 sizing, patterning, and stacking method                       |

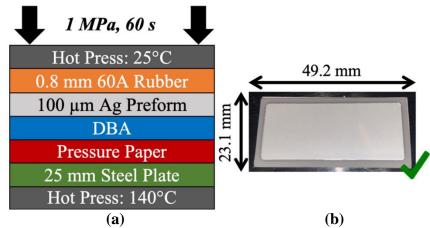

| Figure 11: (a) Previous method developed for large-area sintering of substrates by stamp   |

|--------------------------------------------------------------------------------------------|

| transferring Ag preform and (b) successful transfer with that method on a smaller, plain   |

| substrate                                                                                  |

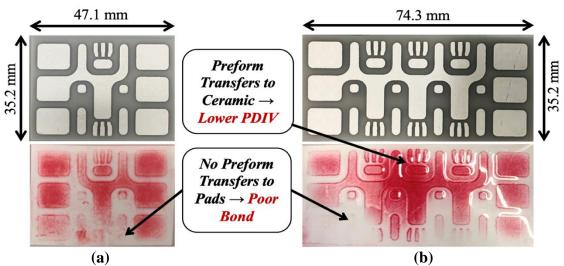

| Figure 12: (a) Non-uniform, two-die patterned substrate's pressure paper using the Ag      |

| preform stamp-transfer method developed for small, plain substrates. (b) Non-uniform,      |

| MCPM patterned substrate's pressure paper indicating a non-uniform preform transfer        |

| using the previous methods detailed                                                        |

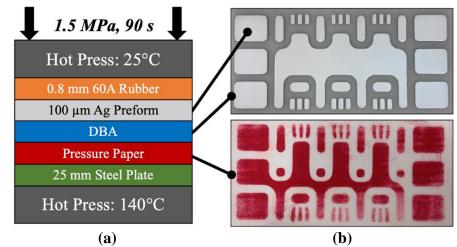

| Figure 13: (a) New transfer method with 1.5 MPa, 90 s, and 0.8 mm 60A (medium)             |

| rubber and (b) successful transfer of preform to substrate showing uniform pressure        |

| paper                                                                                      |

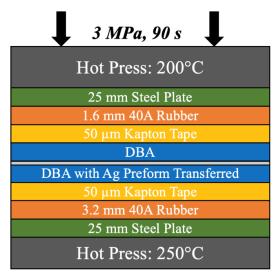

| Figure 14: Stack-up for the pressure-assisted sintering of large-area substrates in a      |

| pneumatic hot press                                                                        |

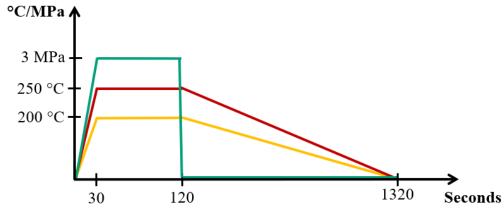

| Figure 15: Hot press pressure profile (green), bottom hot plate temperature profile (red), |

| and top hot plate temperature profile (yellow) for the ANSYS thermomechanical              |

| simulation of pressure-assisted silver sintering of stacked substrates                     |

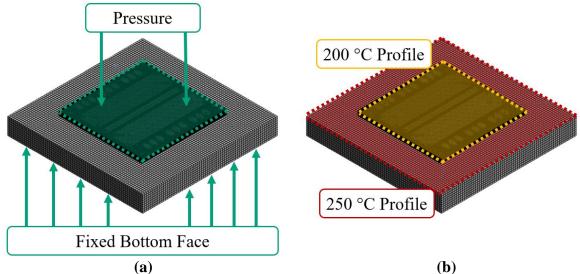

| Figure 16: (a) Pressure boundary conditions for DBA 1-DBA 2. (b) Temperature               |

| boundary conditions for DBA 1-DBA 2                                                        |

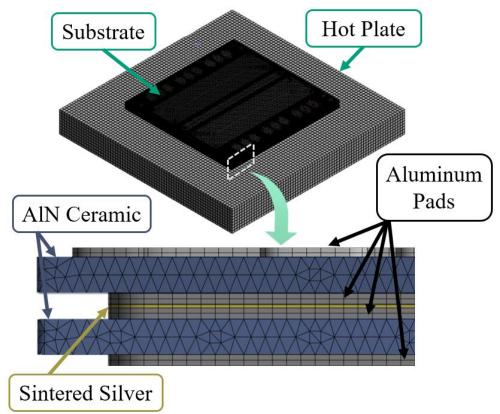

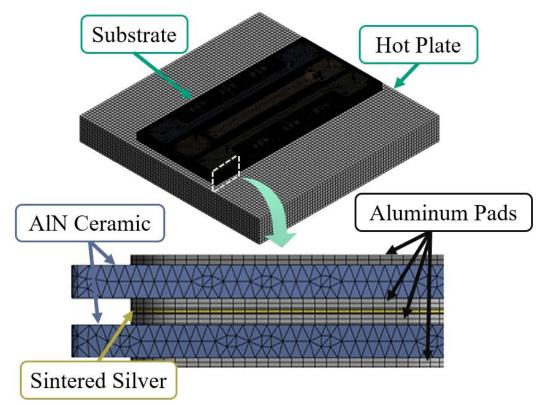

| Figure 17: Meshing for DBA 1-DBA 2 thermomechanical simulation                             |

| Figure 18: Meshing for DBA 3-DBA 4 thermomechanical simulation                             |

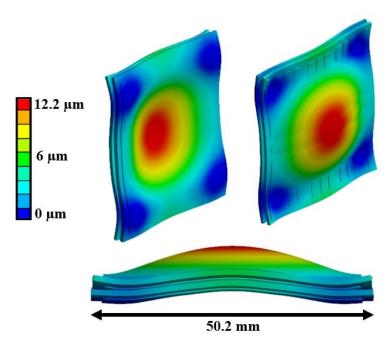

| Figure 19: DBA 1-DBA 2 ANSYS thermomechanical deformation results                          |

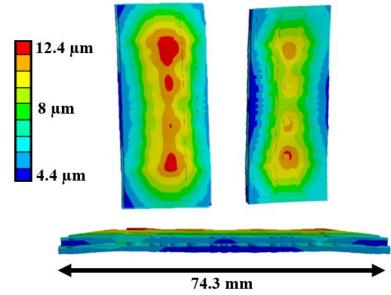

| Figure 20: DBA 3-DBA 4 ANSYS thermomechanical deformation results                          |

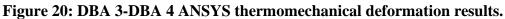

| Figure 21: MCPM substrates with their approximate scan locations for (a) DBA 1 high-       |

| side (blue) and low-side (yellow) and (b) DBA 2 high-side (orange) and low-side            |

| (purple), as well as approximate locations of the die in green. The color of the lines       |

|----------------------------------------------------------------------------------------------|

| corresponds to the graphs in Table 5                                                         |

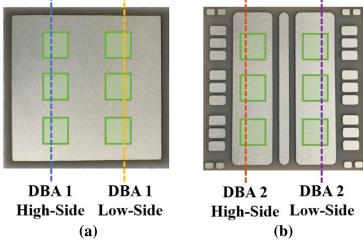

| Figure 22: MCPM substrates with their approximate scan locations for (a) DBA 3 high-         |

| side (blue) and low-side (yellow) and (b) DBA 4 high-side (orange) and low-side              |

| (purple), as well as approximate locations of the die in green. The color of the lines       |

| corresponds to the graphs in Table 5                                                         |

| Figure 23: Behavior summary of the substrate warpage after the pressure-assisted large-      |

| area sintering process, showing DBA 1 to DBA 2 warping concavely and DBA 3 to DBA            |

| 4 warping convexly                                                                           |

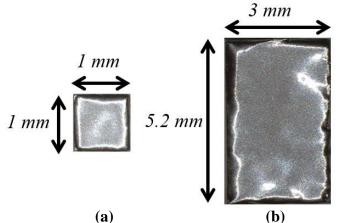

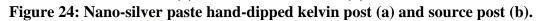

| Figure 24: Nano-silver paste hand-dipped kelvin post (a) and source post (b)                 |

| Figure 25: (a) Mo post interconnects (2 kelvin, 1 gate, and one source) on the SiC device    |

| placed by hand. (b) Mo post interconnects placed with the die bonder, highlighting the       |

| hand-dipped silver sinter bondlines                                                          |

| Figure 26: NBE Tech pressure-less silver sinter paste heating profile                        |

| Figure 27: (a) Screen printed sinter paste on DBA 2 with a clear image of a uniform,         |

| defect-less screen print, and (b) all die and posts placed on the substrate in the paste,    |

| highlighting the die placement with no paste on the sides of the die or the field grading.51 |

| Figure 28: Kyocera pressure-less silver sinter paste heating profile                         |

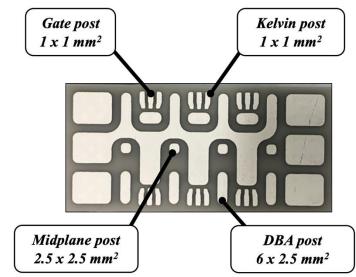

| Figure 29: DBA 3 substrate pattern with callouts to specific pads that posts align to (post  |

| sizes are noted below post name)                                                             |

| Figure 30: Glass slide with etched DBA pattern overlaid onto post interconnects to verify    |

| successful alignment for soldering                                                           |

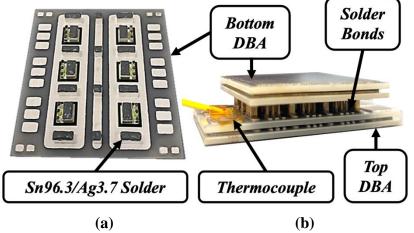

| Figure 31: (a) Solder paste on the sintered Mo posts. (b) The bottom DBA flipped onto       |

|---------------------------------------------------------------------------------------------|

| the top DBA with a thermocouple at the solder joint                                         |

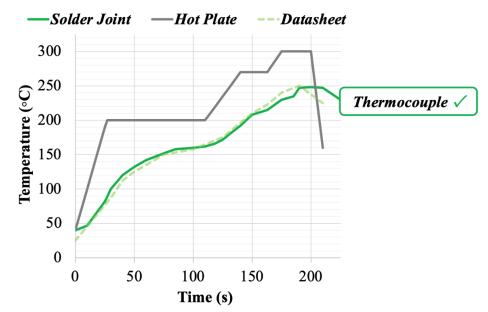

| Figure 32: Sn96.3/Ag3.7 solder-reflow profile of stack-up where the temperature at the      |

| solder joint location in the MCPM matches the recommended soldering profile                 |

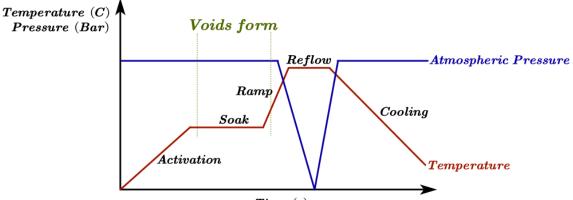

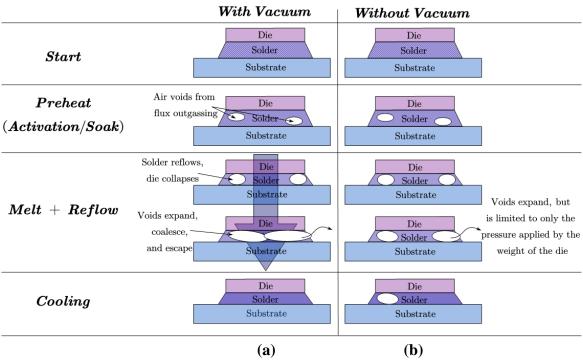

| Figure 33: Typical vacuum reflow soldering profile                                          |

| Figure 34: Solder reflow process when (a) a vacuum is applied and (b) without a vacuum,     |

| highlighting the behavior of the voids                                                      |

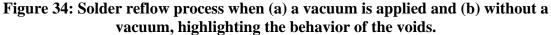

| Figure 35: Impact of voids on post tilt during (a) pressure-less solder reflow that results |

| in tilt versus (b) pressure-assisted solder reflow                                          |

| Figure 36: Visual representation of equation (4) during the external pressure-assisted      |

| soldering61                                                                                 |

| Figure 37: Steps to evaluate the benefit of pressure-assisted soldering for post-planarity, |

| specifically, measuring the post-height variation                                           |

| Figure 38: Average measured tilt across a singular post using the (a) pressure-less and (b) |

| pressure-assisted soldering methods shown in Figure 37. Noted below each are the            |

| variance and standard deviation of the measurements                                         |

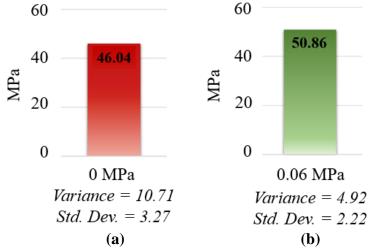

| Figure 39: Average shear strength of posts using the (a) pressure-less and (b) pressure-    |

| assisted soldering methods shown in Figure 37. Noted below each are the variance and        |

| standard deviation of the measurements                                                      |

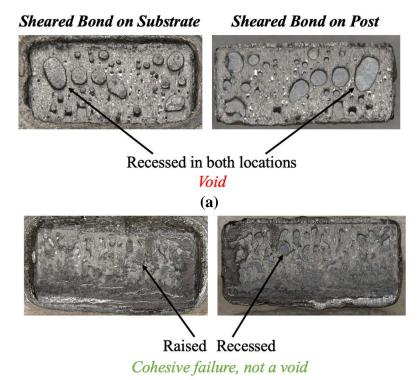

| Figure 40: (a) Pressure-less soldered bond showing the cavernous voids on both the          |

| substrate and post. (b) Pressure-assisted soldered bond with raised and recessed edges      |

| that piece together due to a cohesive failure, not a void                                   |

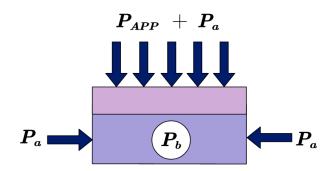

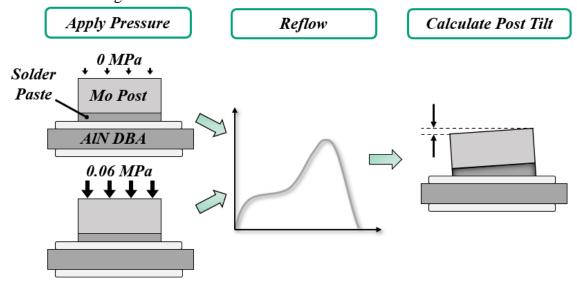

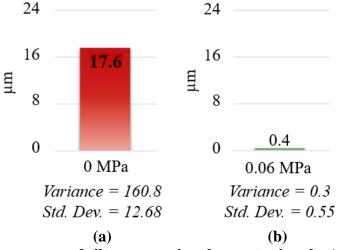

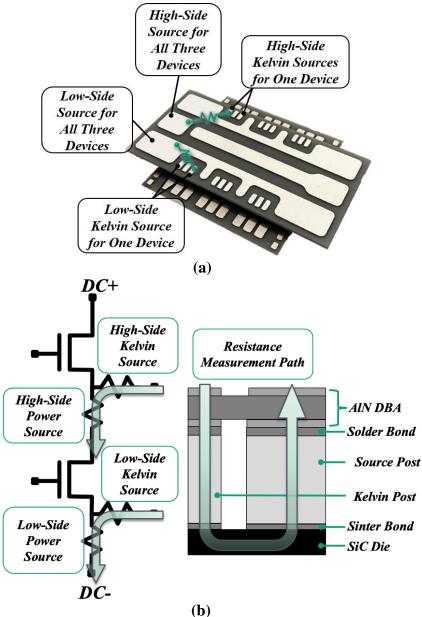

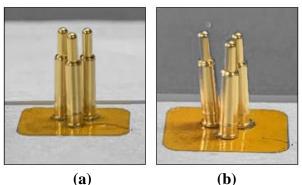

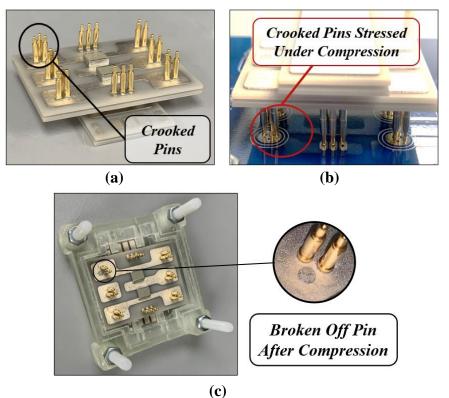

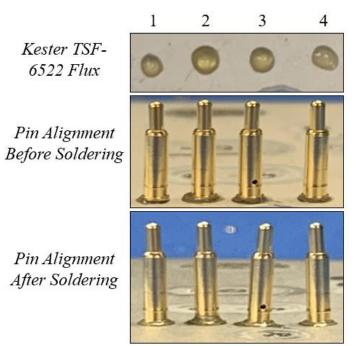

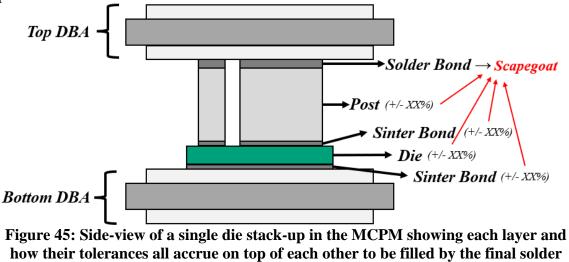

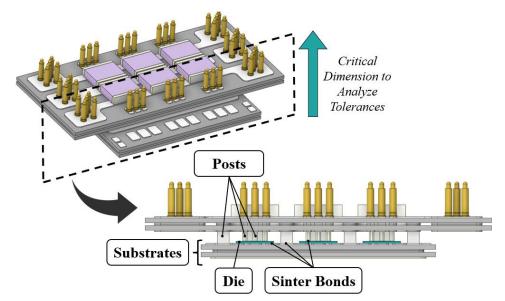

Figure 41: (a) Probe locations for resistance measurements from kelvin source to power source for two devices (one on the high-side and one on the low-side). (b) Resistance measurement path for soldered modules with and without pressure to verify the integrity Figure 42: (a) Spring pins placed before soldering in the convectional reflow oven and (b) Figure 43: (a) Two-die module with crooked spring pins. (b) Two-die module interfaced with the characterization board, showing crooked pins stressed under compression. (c) Figure 44: Testing the effect of tacky flux on keeping pins straight after solder reflow with (1) a small amount in a small area, (2) a large amount in a larger area, (3) a large Figure 45: Side-view of a single die stack-up in the MCPM showing each layer and how their tolerances all accrue on top of each other to be filled by the final solder bond. ..... 71 Figure 46: Side-view of MCPM consisting of four layers contributing to the tolerance Figure 47: Each component in the statistical tolerance analysis that has a distribution generated for the Monte Carlo simulation......77 Figure 49: Visual representation of the motivation to perform the Monte Carlo simulation using component mismatch from nominal heights since the goal is not perfectly machined

| Figure 50: Post height error from nominal probability density function and each post's   |

|------------------------------------------------------------------------------------------|

| kernel distribution                                                                      |

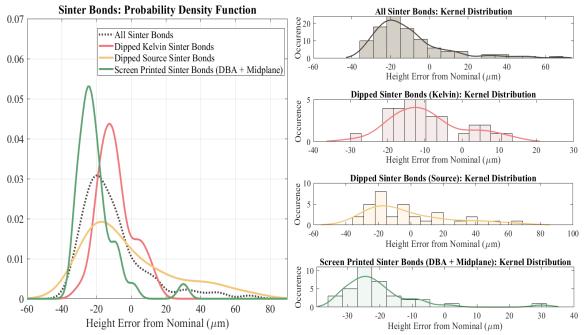

| Figure 51: Sinter bond height error from nominal probability density function and each   |

| sinter bond's kernel distribution                                                        |

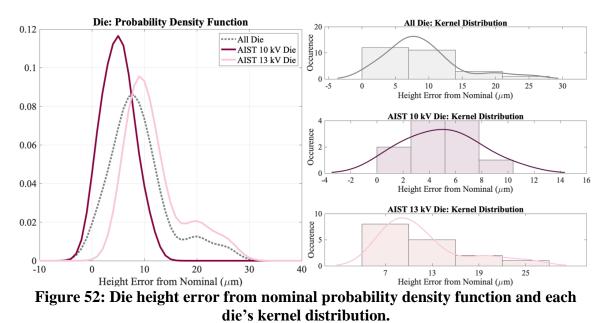

| Figure 52: Die height error from nominal probability density function and each die's     |

| kernel distribution                                                                      |

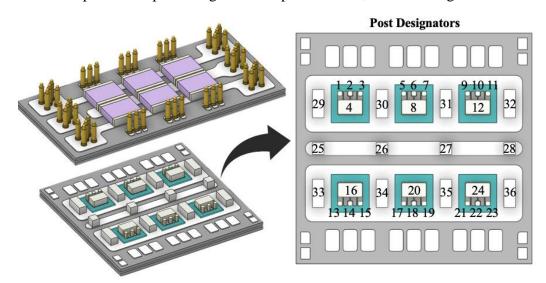

| Figure 53: Post designators for the 1x36 matrix in the Monte Carlo simulation. Each post |

| number corresponds to that column in the height mismatch matrix                          |

| Figure 54: Monte Carlo simulation: Random sampling of 18 screen-printed sinter bonds     |

| for an MCPM. Their height mismatches correspond to Table 10                              |

| Figure 55: Monte Carlo simulation: Random sampling of 6 die for an MCPM. Their           |

| height mismatches correspond to Table 11                                                 |

| Figure 56: Monte Carlo simulation: Random sampling of 24 hand-dipped sinter bonds for    |

| an MCPM. Their height mismatches correspond to Table 12                                  |

| Figure 57: Monte Carlo simulation: Random sampling of 36 posts for an MCPM. Their        |

| height mismatches correspond to Table 13                                                 |

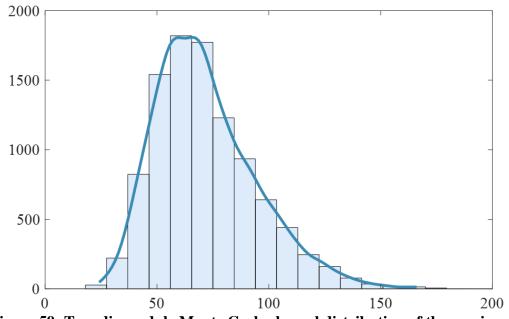

| Figure 58: Single die Monte Carlo simulation: kernel distribution of the maximum height  |

| mismatch for 10,000 modules                                                              |

| Figure 59: Two-die module Monte Carlo: kernel distribution of the maximum height         |

| mismatch for 10,000 modules                                                              |

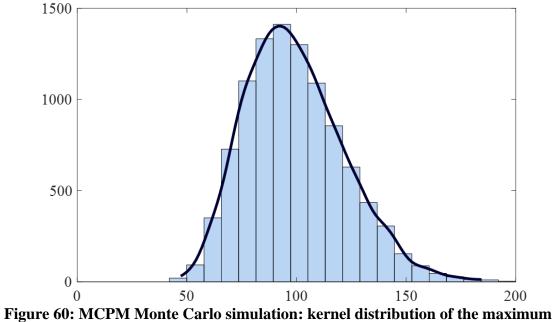

| Figure 60: MCPM Monte Carlo simulation: kernel distribution of the maximum height        |

| mismatch for 10,000 modules                                                              |

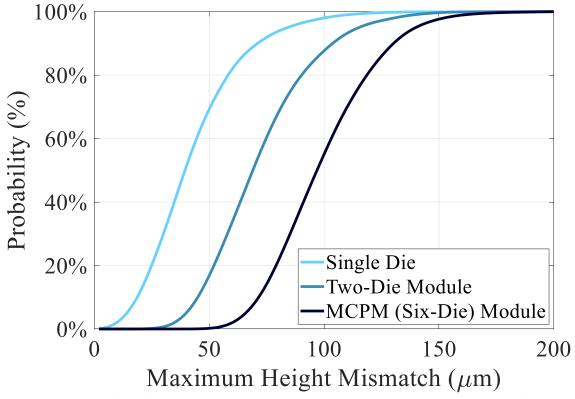

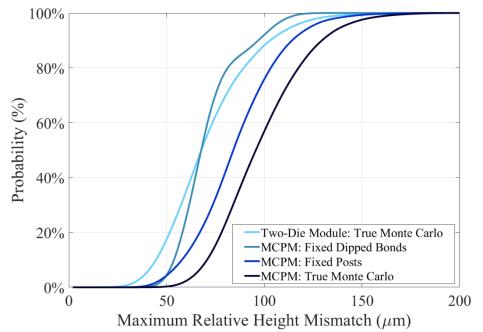

| Figure 61: CDF for the maximum relative height mismatch comprised of a distribution of                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10,000 randomly sampled modules from a Monte Carlo simulation                                                                                                                                                                                                                                                                                                      |

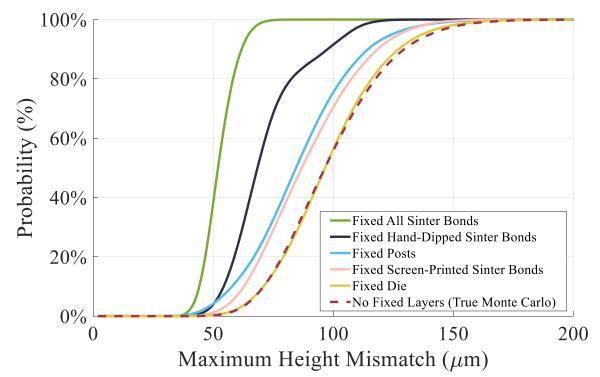

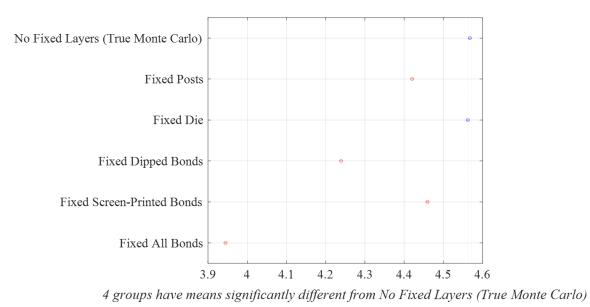

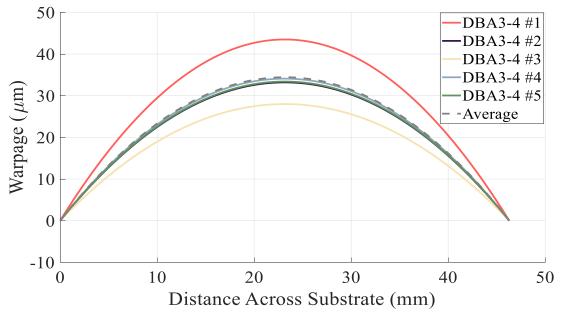

| Figure 62: MCPM cumulative density function (CDF) for relative height mismatch with                                                                                                                                                                                                                                                                                |

| different layers fixed at zero height mismatch (i.e., perfectly planar)                                                                                                                                                                                                                                                                                            |

| Figure 63: Visual interpretation of Tukey's HSD demonstrating that every layer of the                                                                                                                                                                                                                                                                              |

| module is statistically different from the randomly sampled module, meaning there is                                                                                                                                                                                                                                                                               |

| control authority over which each of those layers except the die                                                                                                                                                                                                                                                                                                   |

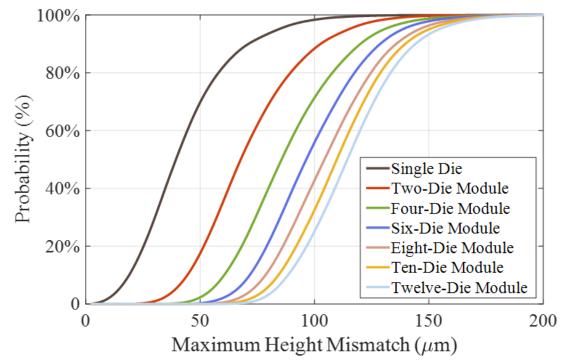

| Figure 64: CDF of the maximum height mismatch of different die counts ranging from a                                                                                                                                                                                                                                                                               |

| single die to a twelve-die module from left to right                                                                                                                                                                                                                                                                                                               |

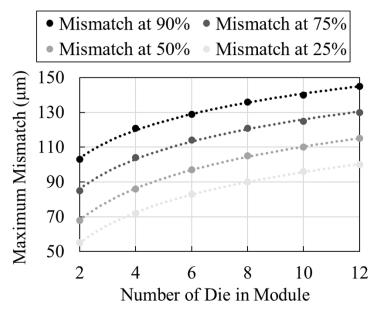

| Figure 65: Relationship between the maximum height mismatch across a module with a                                                                                                                                                                                                                                                                                 |

| certain number of die at varying percentages from top to bottom: 90%, 75%, 50%, and                                                                                                                                                                                                                                                                                |

| 25%                                                                                                                                                                                                                                                                                                                                                                |

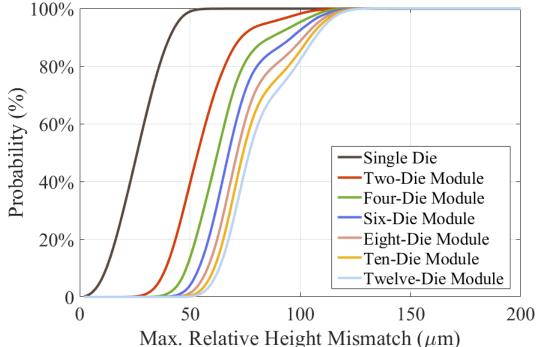

| Figure 66: CDF of the maximum height mismatch of different die counts ranging from a                                                                                                                                                                                                                                                                               |

| single die to a twelve die module from left to right using silver preform instead of hand-                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                    |

| dipped sinter bonds                                                                                                                                                                                                                                                                                                                                                |

| dipped sinter bonds                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                    |

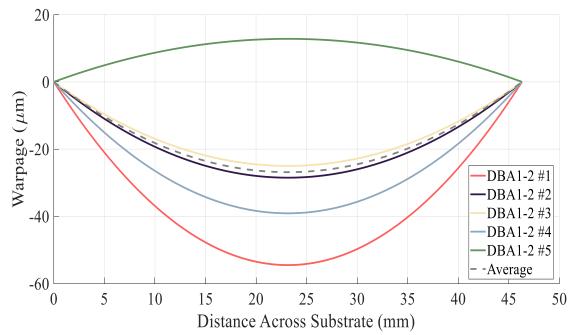

| Figure 67: Maximum warpage trends of each DBA1-DBA2 substrate pair after sintering,                                                                                                                                                                                                                                                                                |

| Figure 67: Maximum warpage trends of each DBA1-DBA2 substrate pair after sintering, with their average model used for the Monte Carlo represented by the dashed grey line.95                                                                                                                                                                                       |

| Figure 67: Maximum warpage trends of each DBA1-DBA2 substrate pair after sintering,<br>with their average model used for the Monte Carlo represented by the dashed grey line.95<br>Figure 68: Maximum warpage trends of each DBA3-DBA4 substrate pair after sintering,                                                                                             |

| Figure 67: Maximum warpage trends of each DBA1-DBA2 substrate pair after sintering,<br>with their average model used for the Monte Carlo represented by the dashed grey line.95<br>Figure 68: Maximum warpage trends of each DBA3-DBA4 substrate pair after sintering,<br>with their average model used for the Monte Carlo represented by the dashed grey line.96 |

| Figure 70: (a) Two-die SiC half-bridge power module with callouts of components. (b)          |

|-----------------------------------------------------------------------------------------------|

| Two-die module circuit diagram with one die per switch position                               |

| Figure 71: Fabrication steps of the semi-functional two-die module, with the colored          |

| boxes corresponding to the characterization curves in Figure 72 102                           |

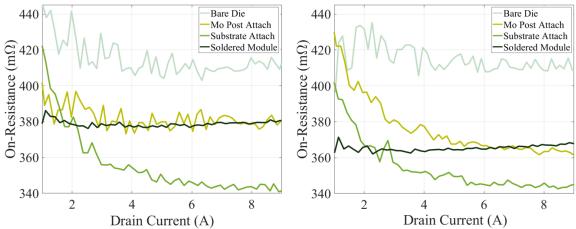

| Figure 72: Characterization curves of the bare device, the device with Mo posts attached,     |

| the devices + posts attached to the substrate, and the soldered module with spring-pin        |

| terminals102                                                                                  |

| Figure 73: Two-die module fabrication process 104                                             |

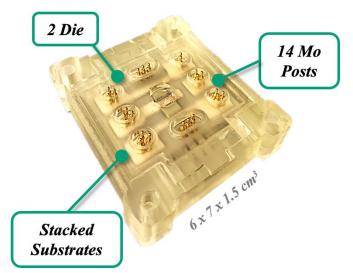

| Figure 74: Encapsulated, two-die, 13 kV SiC MOSFET, half-bridge power module with             |

| one die per switch position, stacked substrates, and 14 Mo posts 105                          |

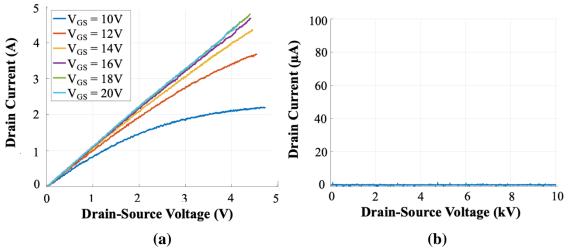

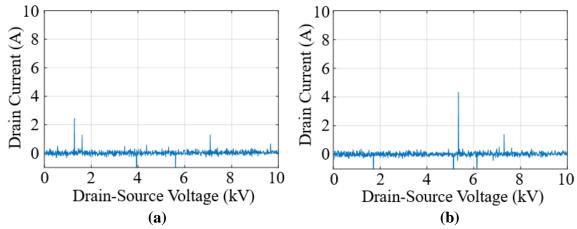

| Figure 75: Static characterization results, including (a) the forward characteristics of the  |

| packaged low-side device and (b) the breakdown voltage of the packaged low-side device        |

| up to 10 kV (limited by the curve tracer)                                                     |

| Figure 76: Fabricated 10 kV, AIST SiC half-bridge two-die power modules,                      |

| decapsulated106                                                                               |

| Figure 77: Double-pulse test setup circuit diagram and part information 109                   |

| Figure 78: Double-pulse test equipment setup and interface to the gate driver 109             |

| Figure 79: Double pulse test waveform for the 13 kV SiC module at 2.2 kV, 5 A, 100 m $\Omega$ |

| gate resistance, including a zoomed-in image of the drain-source voltage rise and fall. 110   |

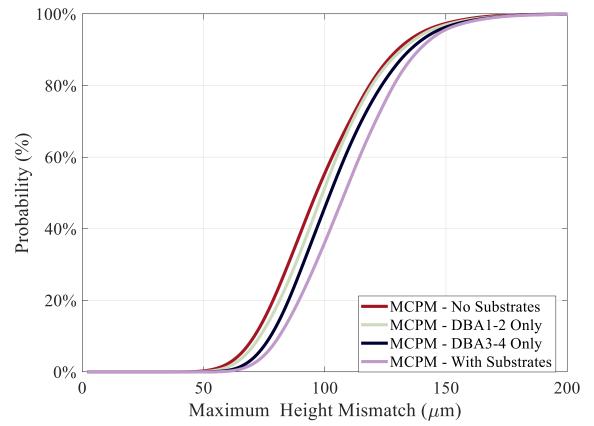

| Figure 80: CDFs of the Monte Carlo two-die module, fixed dipped posts for the MCPM,           |

| fixed posts for the MCPM, and Monte Carlo full module112                                      |

| Figure 81: Mechanical MCPM successfully fabricated using the refinements from              |

|--------------------------------------------------------------------------------------------|

| Chapter 2 and Chapter 3, as well as fixed posts from the Chapter 4 statistical tolerance   |

| analysis                                                                                   |

| Figure 82: Probe-tip locations to measure the shorted connection from the post to the stop |

| pad through the solder bond after reflow                                                   |

| Figure 83: Hardware fabrication steps for the functional, 13 kV SiC MOSFET MCPM.           |

|                                                                                            |

| Figure 84: MCPM (a) high-side and (b) low-side forward characteristics up to rated         |

| current (15 A) 117                                                                         |

| Figure 85: MCPM (a) high-side and (b) low-side breakdown voltage versus leakage            |

| current, up to 10 kV (limited by curve tracer)                                             |

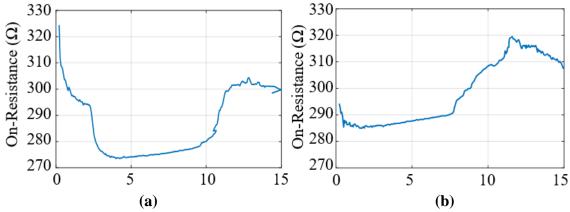

| Figure 86: MCPM (a) high-side and (b) low-side on-resistance up to rated current (15 A).   |

|                                                                                            |

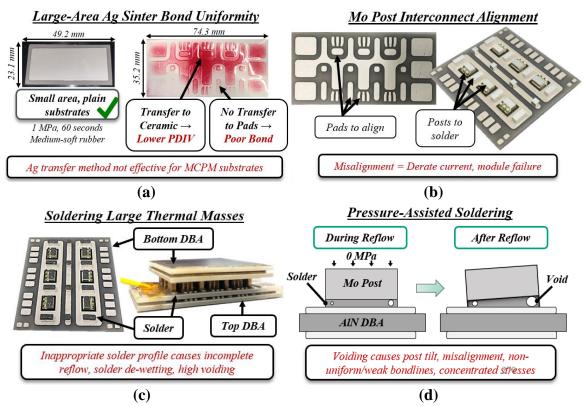

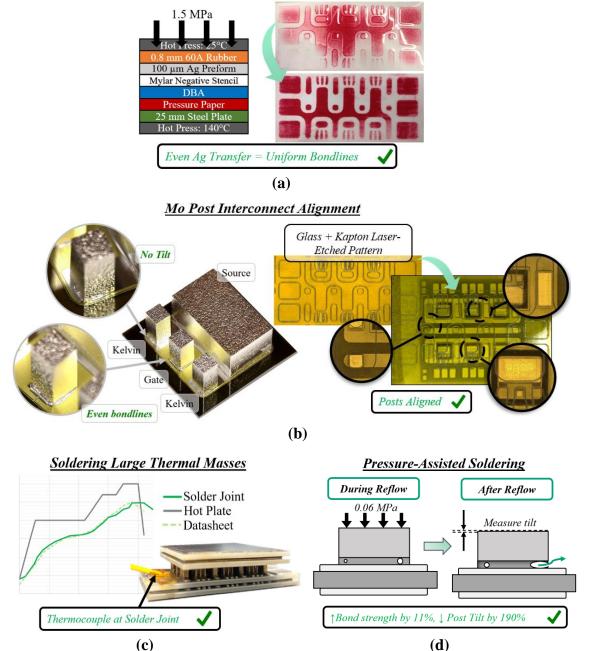

| Figure 87: Fabrication concerns for advanced packaging techniques in MCPMs,                |

| including (a) large-area silver sintering bond uniformity, (b) Mo post interconnect        |

| alignment, (c) soldering large thermal masses, and (d) pressure-assisted soldering 120     |

| Figure 88: Fabrication refinements for the fabrication concerns in Figure 87 regarding the |

| (a) large-area silver sintering bond uniformity, (b) Mo post interconnect alignment, (c)   |

| soldering large thermal masses, and (d) pressure-assisted soldering to improve the yield   |

| for MCPMs                                                                                  |

| Figure 89: Fabrication process with refined steps from this work noted with a green        |

| checkmark                                                                                  |

## List of Tables

| Table 1: AIST 13 kV SiC MOSFET Device Specifications                                  |

|---------------------------------------------------------------------------------------|

| Table 2: Evaluation of Pressure Sensitive Film with Pressure Varying From 1-2 MPa,    |

| Time From 60-90 Seconds, Thicknesses Varying From 0.8-1.6 mm, and Rubber              |

| Durometers of Medium-Soft, Medium, and Medium-Hard                                    |

| Table 3: ANSYS Workbench Simulation Parameters.    38                                 |

| Table 4: MCPM Substrate Metal Patterning Surface Areas as Referenced in Figure 9 and  |

| Figure 10                                                                             |

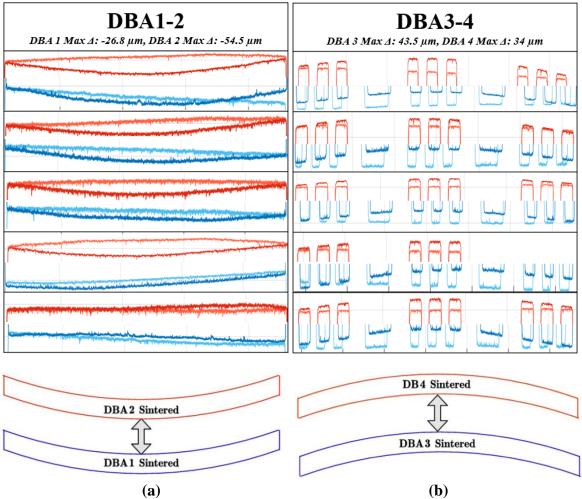

| Table 5: Pre-Sintered Pairings of Substrates for DBA 1 (High-Side Blue, Low-Side      |

| Yellow) to DBA 2 (High-Side Red, Low-Side Purple), and DBA 3 (High-Side Blue,         |

| Low-Side Yellow) to DBA 4 (High-Side Red, Low-Side Purple) with the Maximum           |

| Warpages Noted                                                                        |

| Table 6: Pressure-Assisted Sintering Substrate Warpage Results Showing Pre-Sintered   |

| Substrates (Light Blue and Light Red) to Post-Sintered Substrates (Dark Blue and Dark |

| Red). DBA 1 and DBA 3 are Shades of Blue, While DBA 2 and DBA 4 are Shades of         |

| Red                                                                                   |

| Table 7: Post Names and Sizes in the MCPM.    46                                      |

| Table 8: Kelvin Source to Power Source Resistances of Bonds Using Pressure-less and   |

| Pressure-assisted Soldering for the Mechanical MCPMs                                  |

| Table 9: Shear Tests From the Pins in Figure 44 Attached with Different Amounts of    |

| Tacky Flux                                                                            |

| Table 10: Screen-Printed Sinter Bond Height Mismatch Matrix Based on Locations in     |

| Figure 53                                                                             |

| Table 11: Die Height Mismatch Matrix Based on Locations in Figure 53                   |

|----------------------------------------------------------------------------------------|

| Table 12: Hand-Dipped Sinter Bond Height Mismatch Matrix Based on Locations in         |

| Figure 53                                                                              |

| Table 13: Post Height Mismatch Matrix Based on Locations in Figure 53                  |

| Table 14: Total Height Mismatch Matrix Across One MCPM Based on Locations in           |

| Figure 53 (Summation from Table 10 to Table 13)                                        |

| Table 15: Full-Module ANOVA Results from Different Fixed Components.       91          |

| Table 16: Tukey's HSD Ordered Letters Report for the MCPM Fixed Layer Treatments       |

| Compared to the Control Group (No Fixed Layers, True Monte Carlo)                      |

| Table 17: Packaging Process Details for the Multi-Chip Power Module Corresponding to   |

| Figure 7                                                                               |

| Table 18: Test Conditions for the Static Characterization of the Two-Die Modules 106   |

| Table 19: Static Characterization from the Six Two-Die Modules, Detailing the Bare Die |

| and Packaged Die Results                                                               |

| Table 20: AIST 13 kV Functional Bare Die Characterization Data    115                  |

| Table 21: Kelvin-Source to Power-Source Resistance Measurements to Verify all          |

| Connected Bonds 116                                                                    |

| Table 22: Kelvin-Source to Power Source Resistance Measurements of Only Solder         |

| Bonds                                                                                  |

### Chapter 1 Introduction

### 1.1 Background

Power electronics has shifted from the long-standing use of silicon (Si) devices to exploring the capabilities that wide bandgap (WBG) devices can offer for the field. The inherent properties of WBG devices, namely silicon carbide (SiC), allow them to outperform Si in several applications, as noted in Figure 1. The critical electric field is higher than Si, making SiC the top contender for medium-voltage and high-voltage applications. This increase in critical electrical field is accompanied by a size reduction of the chip, thus, reducing the gate area and ultimately lowering the gate charge. This is key for device operation at higher frequencies, allowing for lower on-state resistance, minimizing switching losses, and opening the door for applications that require efficient power conversion [1]–[4]. The high operating temperature combined with the high thermal conductivity allows SiC to have improved high-temperature performance while being more feasible to cool than Si devices [3], [5].

[6][7].

Various power devices have utilized Si as the foundation of power electronics, ranging from field-effect transistors (FET), bipolar-junction transistors (BJT), and gate bipolar junction transistors (IGBT). Si transistors have been extensively reviewed in academic research, the most extensive being the Si IGBT [5]-[7]. While these power modules have proved reliable and durable for low and medium voltages and high currents and have seasoned experts on their operation, growth, and manufacturability, these modules have quite a few limitations. As discussed previously, the switching speed of Si devices will limit these modules for the demands of efficient power conversion. Additionally, the maximum voltage rating of these modules' plateaus is 6.5 kV, rendering these modules useless for high-voltage applications such as renewable energy grid interfaces and all-electric ships [7]–[9]. Joining Si IGBT power modules in series to increase the rated blocking voltage can rectify this issue; however, this solution introduces many challenges, mainly concerning voltage stability and developing complicated control schemes [9]–[11]. Furthermore, to meet safety and reliability requirements, the modules in series or parallel need to be isolated and heavily derated, increasing the footprint of the converter and decrementing the overall power density [12].

However, this same argument can apply to the medium- and high-voltage SiC modules with lower current capabilities. The devices and modules need to be connected in parallel for these modules to reach the current levels that Si IGBTs have. Paralleling SiC devices or modules can introduce similar problems that the series of IGBTs present, now regarding current imbalances, but the same increased control complexity and lower power density from derating [11], [13], [14]. Additionally, the increased switching speed, compounded by the proximity of connected modules, can present unforeseen EMI concerns

that require careful consideration and testing [15]. These challenges have led to a growing interest in parallel devices within the package to increase power densities, uncomplicate the controls, and target reduced imbalances.

Nonetheless, the medium- and high-voltage SiC MOSFET application space has flourished despite these challenges for high-current applications. Commercially and academically developed packages highlight the promising potential that SiC and wide bandgap devices have during operation. It is essential to identify the current packaging layouts and materials used to successfully fabricate multi-chip power modules to explore the challenges of fabricating these modules given their voltage requirements and the increased complexity as the number of devices and components in these modules rises.

### 1.2 Survey of Multi-Chip Power Module Packaging Techniques

### 1.2.1 Overview of the Typical Packaging Components and Schemes

It has become apparent from the characteristics of WBG semiconductors that they can meet the demands of applications today for power electronics for high voltage, high current, high temperature, fast switching, high efficiency, and low losses. However, these devices cannot operate under all these conditions independently. The packaging of the devices is necessary to interface the device characteristics for use with the external world for these applications. The packaging of the device provides the enclosure to allow the device to reliably perform electrically, thermally, and mechanically. It involves understanding the physics, chemistry, and material science of all the components in a package to optimize the electrical and thermal. It can significantly impact the devices' performance, size, cost, and reliability [16].

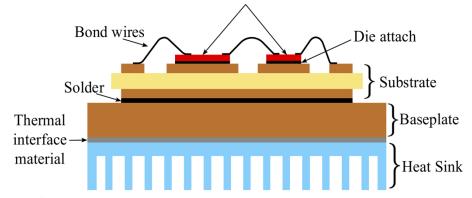

The conventional power module package is shown in Figure 2. It consists of a substrate attached to a baseplate with a thermal interface material. The baseplate's function is to dissipate heat generated from the package during operation. The substrate, typically an inorganic ceramic, provides mechanical support and electrical connections for the devices based on the substrate patterning. A common ceramic substrate is direct bonded copper (DBC), which consists of two copper layers with a ceramic sandwiched in-between for insulation and rigidity. There are also active metal brazing (AMB) substrates with silicon nitride and copper, which provide even more mechanical robustness than DBCs with less coefficient of thermal expansion (CTE) mismatch and better heat dissipation. This work focuses on a direct-bonded aluminum (DBA) type, which has better thermal performance than DBC and AMB substrates but slightly worse CTE than AMB. Power devices

Figure 2: Conventional power module packaging scheme with crucial components labeled [16].

The semiconductors are attached to the substrate using a die attach material such as epoxy, solder, and sinter. Conductive epoxy is less common for power electronics applications due to its limited thermomechanical performance. Soldering can be in the form of paste, preform, or wire and has been a conventional die attach method since the beginning of power electronics. Recently, methods have shifted to silver sintering techniques for a more reliable bond with higher thermal conductivity and less voiding content.

Interconnects form the connections within the package from the devices to terminals or other devices. These interconnects are typically wirebonds for the bare device, but some devices are compatible with flip-chip or ball grid array (BGA) interconnect methods. Methods to eliminate wirebonds within a package and replace them with more reliable interconnects have been investigated and will be a focus of this work.

Terminals are what allow the devices to interface with external applications. These can range from screw terminals, pins, springs, clamps, and more. These terminals can be permanently attached to their external environment, such as a gate driver or bus bar, for better attachment reliability, or they are clamped so that the package can be removed and serviced.

The encapsulation is crucial for improving electrical insulation for medium- and high-voltage modules. However, it is also beneficial to protect the device and internals of the package from the environment and thermomechanical shocks. The encapsulants are dielectric materials ranging from tolerant silicone gels to rigid epoxy molding compounds. The encapsulants are held within a plastic module housing material, or in some cases, the encapsulation material can be the entire device housing.

## **1.2.2** Current Challenges of Package Interconnects for Medium-Voltage Multi-Chip Power Modules

Multi-chip power modules (MCPMs) enable the series and paralleling of devices to achieve higher voltages and currents, respectively. Modules have reached up to 10 kV for SiC devices, but only a few hundred amps compared to high current Si IGBT

5

modules[17], [18]. It is important to lay out the module to reduce parasitic imbalances and the magnitude of the parasitics overall since SiC devices are more sensitive to imbalances and the magnitudes of parasitics due to the fast-switching nature of these devices [19].

The substrate of multi-chip power modules needs to be sized to have adequate heat spreading and reduce thermal coupling between chips. This can result in large substrates where the path between devices and the package terminals that interface with the gate driver and busbar becomes longer. The most common interconnect method across these substrates is the aluminum (AI) wirebond. Al wirebonds are cost-effective and have thoroughly developed manufacturing processes [20]. Wirebonds require pads to bond to laterally, increasing the substrate surface size and decreasing the power density [21]. The lengths of the wires increase to connect across the MCPM, increasing the parasitic inductance and force on the necking point, degrading the reliability and module performance [22], [23]. Additionally, wirebonds have low reliability for stressful thermomechanical environments. They are one of the significant causes of failure at elevated temperatures, which is not promising for WBG devices operating at higher temperatures than their Si counterpart [24]. Cracking and bending fatigue accumulates, and the wirebonds fail open once reaching their fusing current [22], [25], [26].

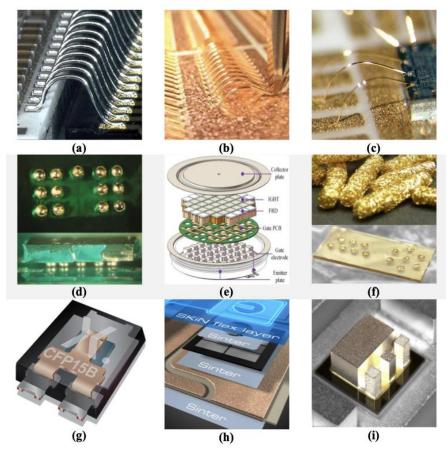

Wirebonds have a large inductance, and wirebonds across multi-chip power modules also introduce parasitic imbalances. It has known with Si IGBT wirebonded multichip modules that the overshoot can be almost 3.5 times greater than the rated value, significantly increasing losses [27]. With fast-switching SiC devices, higher losses compounded with imbalanced parasitics in multi-chip power modules can have catastrophic effects during converter-level operation and even during a double-pulse test of the package [28], [29]. This results in slowing the switching speeds to control the EMI and reduce the impact of parasitics, an undesirable result from attempting to package WBG devices as if they were traditional Si. Even though there are many concerns with using wirebonds for a multi-chip power module, especially for high voltage, it is the interconnect method used for commercial 10 kV power modules. These modules have 18 devices and parasitic inductances ranging from 16-37 nH, which is unideal for SiC 10 kV switching [29]. A promising variety of alternatives have been researched to address the consequences that wirebonds introduce for multi-chip power modules (Figure 3). The options include advanced wirebonding materials, flip-chip modules, pressure contacts, and vertical, three-dimensional interconnects.

Figure 3: Various interconnects including (a) Al wirebonds [30] (b) Cu wirebonds [31] (c) Au wirebonds [32] (d) Flip-chip solder bumps [33] (e) Press-pack [34] (f) Fuzz buttons [35] (g) Cu clips [36] (h) Flexible PCB [37] and (i) Metal posts [21].

Industry companies such as ABB, Siemens, Heraeus, and Danfoss have employed advanced wirebonding techniques and materials in power modules [38]. While it would be beneficial to analyze the module layout and impact of the wirebonds on the overall parasitics and parasitic imbalances, the inside details of the modules are usually protected. The interconnect methods can still be investigated. Materials instead of aluminum have increased the reliability of wirebonds [20], [38], [39]. Copper wirebonds have better power cycling results over aluminum and high electrical and thermal conductivity. While improvements to the bonding process have been made, there is a risk of damaging the device during bonding due to the hardness of copper to the fragile die surface [38], [39]. Additionally, the oxidation of copper cannot be ignored even at lower temperatures, which can complicate manufacturability [20], [38]. Gold wirebonds are resilient to corrosion, highly conductive, and easily adhere to many typical metal surfaces in the package, making it an easy choice in terms of performance. Still, the cost of gold (Au) is not always feasible for large-scale production of packages [38], [39]. Thus, there has been more effort in improving the performance of copper (Cu) and aluminum wirebonds rather than transitioning to gold.

Even though changing the materials of the wirebonds can provide better electrical performance and, in some instances, reduce the parasitic inductance slightly, it does not address the overall problem that multi-chip power modules face with imbalanced parasitics [27]. To reach higher currents, many devices are still connected parallel; thus, many wirebonds are still within the module. The layout becomes the primary method to reduce the parasitic influences of the wirebonds [40]. Wirebonds also eliminate any potential for double-sided cooling, which is essential to the future cooling of WBG devices [20].

Changing the material of the wirebonds or layouts to reduce parasitic inductance is therefore deemed a workaround for this analysis and not a solution.

Flip-chip bonding is an interconnect method that inherently reduces parasitic inductances. Flip-chip bonding consists of solder balls (or bumps) distributed across the device, which solder directly to the substrate pads. This vertical interconnect method results in a lower profile package and minimized area needed for lateral wirebond connections, improving the overall power density of the module [33],[41]. The solder bumps create a layer between the device's backside and the substrate, improving thermomechanical reliability and reducing CTE mismatch between the die and the substrate [38], [41]. However, there are still drawbacks to this interconnect technology for medium-voltage power modules. It also proves difficult for medium-voltage devices, given creepage and clearance requirements and requiring underfills with high dielectric strength to reduce the peak electric field between the chip and the substrate, and the highest voltage module (6.5 kV) had only undergone a leakage current experiment to verify operation [42].

Another interconnect which proves more promising for the overall interconnect reliability and performance for multi-chip power modules is accomplished by applying pressure. Press-packs utilize pressure contacts with dry spacers to form connections across arrays of devices. The technology reduces CTE mismatch by utilizing molybdenum spacers to interface between the die and the terminals. There is improved reliability for medium-voltage and high-power applications since the dry contact eliminates common failure mechanisms of mechanical bonding seen with wirebonds and solder [43]–[45]. They also allow the interconnects to take on a new responsibility within the package: heat transfer.

This newfound technique paves the way for double-sided cooling as the topside of the devices can now have a large interconnect to conduct heat efficiently [43].

However, these successful press-packs for Si are not always translatable to WBG devices like SiC. SiC devices have notably less area for their contacts [45], [46], and the press-pack relies on a dry contact, needing tight tolerances to ensure even contact across all devices and also ensuring there are no potential gaps, which are difficult to control given surface roughness of different components [43]. Dry contacts also restrict the encapsulates that can be used, requiring complicated gas insulation methods with lower breakdown strength than silicone gels [47].

It was noted earlier how impactful the parasitics are for SiC devices. While presspack modules can improve the magnitude and symmetry compared to wirebonded modules, press-pack modules tend to have a large form factor. Most of the modules cannot be insulated from the heat sink, and thus the inductance of the main power loop is still large [43], [44]. Additionally, while the layout of the devices can be symmetrical to aid in balancing, the actual contact strength relies on even pressure distribution [48]. Uneven distribution will result in disconnected devices, resulting in imbalanced current sharing, imbalanced thermal performance, imbalanced mechanical stresses, and overcurrent failures [34], [49].

Finally, 3-D interconnects led the way in producing multi-chip power modules that minimize the overall footprint by creating vertical packages. The interconnection can remain short, allowing for a decrease in inductance while allowing the spacing to be adjusted to accommodate high voltages by determining the clearance in vertical structures and reducing the peak electric field [50]. They also allow heat dissipation through the

10

topside of the device and open the door for more reliable double-sided cooling methods. Larger contact areas of 3-D interconnects decrease thermal and electrical resistance and increase the current-carrying capability. These 3-D interconnects include clips, pins, flexible circuit boards, PCB embedding, and metal posts.

Fuzz buttons are a dry contact used in press-packs instead of spacers. They act as a low-profile interconnect with compliance benefits and low parasitic inductances. Their compliance allows for more uniform pressure distribution than the rigid contacts in typical press-packs. Their small size also helps with adaption to the smaller size pads of SiC devices. However, these do not allow thermal conduction through them like metal posts do for double-sided cooling. Insulation is also a concern due to their low profile, and medium-and high-voltage packages need further insulation. The fuzz buttons were packaged with 1.2 kV devices but never experimentally verified. The typical insulation techniques are incompatible with fuzz buttons since they cannot be potted without degrading their flexible nature, and the alternative of hermetically sealed packages is costly [35], [46], [51].

More typical 3-D interconnects of metal posts have been utilized and are the main focus of this work. Mo posts enable low inductance designs and create sandwich-structure modules with high power density and good thermal conductivity for double-sided cooling [52], [53]. This is attractive for WBG devices due to the higher operating temperature than Si. Mo also has a low CTE (4.9 ppm/C) that is quite similar to SiC devices (3.7) as well as the aluminum nitride (AlN) substrates (5.3) [50], [54], [55].

These Mo post interconnects have been demonstrated in various modules [29], [52]–[54]. [54] utilizes Mo posts sintered to the die and substrates on one side of the double-sided cooled package and soldered to the other. Even though the CTE between the

substrate and interconnect selection reduces by choosing Mo posts, other materials in the package still dominate the thermomechanical stresses, and the failures manifest in the post bond. To reduce the thermomechanical stresses, a combination of Cu and Mo posts is needed, as well as the removal of the copper heat sinks. While this improved the thermomechanical reliability, the heat spreading of the package was sacrificed as the bonds of the post interconnects could not withstand the CTE of a Cu baseplate.

Similar work using only copper posts machined in a bridge-shape sought to improve a module's thermomechanical reliability and overall thermal cycling lifetime. During cycling, cracks still propagated in the bondline, indicating unresolved CTE mismatch between the interconnect and die. The complex shape of the interconnect further introduces fabrication and tolerance challenges and cost of manufacturability concerns [56]. Additionally, the wet contact choice of solder introduces thermomechanical stresses since there is a CTE mismatch to the copper post that significantly degrades during thermal cycling, which motivates the use of Mo [57].

Changing post materials from Cu to Mo has improved the CTE. However, more advanced material syntheses are investigated to improve compliance, one of the drawbacks of the rigid post interconnect. [58] explored a Cu-Mo-Cu gradient post to have improved CTE mismatch with Mo and the conductivity of the post with Cu. This module was only demonstrated as a single IGBT device. [59], [60] explored Mo-Cu and Mo plated with Au to reduce the CTE mismatch and create; however, the cost of these advanced material interconnects is a notable concern. Different interconnect shapes have also been explored for alleviating thermomechanical stresses at the bondlines [57]. Making an X-shaped or octagon-shaped post relieved stresses in simulation, but the better-performing shape in FEM analysis had worse reliability in the experiment, questioning the benefits of these complex post shapes. Additionally, these are for very short heights, and the stress reduction would not apply at the spacing required for medium-voltage operation.

The use of metal posts for medium-voltage power modules is limited to research [38]. It is important to investigate why these metal post interconnects are confined to modules from academia and their associated fabrication challenges, especially for the future of MCPMs.

# 1.3 Multi-Chip Power Module Overview and Motivations for Fabrication Refinements for Wirebond-Less Multi-Chip Power Modules

While the typical packaging scheme in Figure 2 is deemed "typical," that does not mean it should remain the best practice for the future of power electronics. Based on the advancements in interconnect technology, it is clear that the typical packaging schemes are not enough for the demands of power electronics applications today. It is impossible to achieve high voltage, high temperature, fast switching, and low loss power modules using these packaging schemes developed for Si devices regarding WBG devices. Advanced packaging techniques and designs are required to fabricate MCPMs for WBG devices such as SiC.

Improvements in packaging technologies have increased the feasibility of mediumvoltage SiC modules through low-inductance designs and electrical insulation techniques to achieve high-speed switching without significant overshoot [21], [61]–[63]. Additionally, without balancing parasitics, the paralleling of multiple die becomes challenging. The complications of connecting modules to increase the current or voltage rating within the converter have been discussed. Paralleling devices within the package are more attractive for higher power densities.

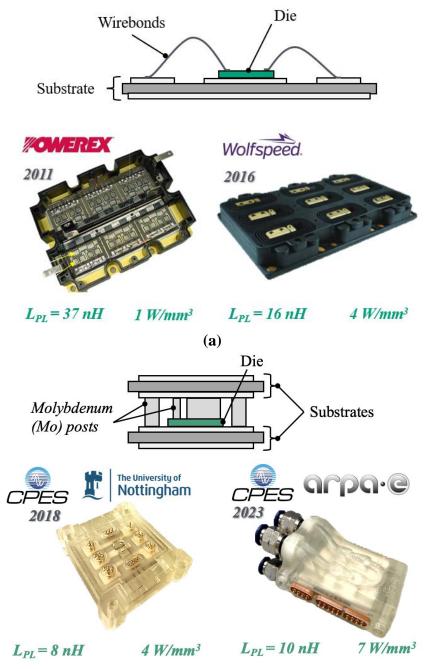

Figure 4(a) compares two commercial 10 kV MCPMs that utilize wirebond interconnects. Wirebonds need lateral pads to bond to while maintaining creepage and clearance requirements, resulting in large substrates and modules with significant power loop inductances. Figure 4(b) references two modules fabricated in the Center for Power Electronic Systems (CPES) that utilize Mo post interconnects between the die and the substrate. As shown, the shift from wirebonds to Mo posts allows for dense designs and vertical sandwich-structure modules with higher power density and lower parasitic inductances.

For SiC, the devices themselves can reach higher voltages than Si, but the paralleling of devices allows SiC to finally compete with the current ratings of Si IGBTs [64]. However, for proper operation, the module layout must be designed to balance parasitics between devices[65]. If the parasitics are imbalanced, the devices experience higher overshoots, higher losses, higher temperatures, and risk module failure [27], [65], [66]. The fabrication of these multi-chip power modules (MCPMs) is not trivial, and the next section will provide further insight into the design and fabrication of the MCPM from [50].

14

**(b)**

Figure 4: (a) Commercial 10 kV modules with wirebonds and their respective power loop inductance and power density [17], [18]. (b) CPES 10 kV modules with Mo post interconnects, and their respective parasitic inductance and power density improved from the wirebonded modules [29], [53].

## 1.3.1 Multi-Chip Power Module Overview

The MCPM that will be the focus of this work is a medium-voltage, SiC, sandwich-

structure, half-bridge power module developed by DiMarino at Virginia Tech Center for

Power Electronic Systems [29] (Figure 5). Medium-voltage SiC devices enable modules with simpler control schemes, improved power density, and higher efficiency than modules that require series connections to reach 10 kV blocking voltages [67]. The module utilizes a symmetrical layout of the devices, which aids in balancing parasitics and promotes even current-sharing across devices [65]. Because of this, the modules can ideally scale from one die per switch position to multiple die per switch position. Overall, the module design in Figure 6 utilizes stacked, pressure-assisted silver sintered substrates, Mo post interconnects, silver sinter die attach, and spring-pin terminals. The module is populated with 13 kV SiC devices from the National Institute of Advanced Industrial Science and Technology (AIST). The details of these devices are in Table 1. This section will detail the design and advanced packaging techniques used to fabricate the MCPM.

| <b>V</b> тн,мах | Size                                  | RDS,on                | Id,max | VTH   | Backside<br>Metallization | Frontside<br>Metallization |

|-----------------|---------------------------------------|-----------------------|--------|-------|---------------------------|----------------------------|

| 13 kV           | 6.94 x 6.94 x<br>0.35 mm <sup>3</sup> | $705 \text{ m}\Omega$ | 5 A    | 3.4 V | Gold                      | Silver                     |

Table 1: AIST 13 kV SiC MOSFET Device Specifications.

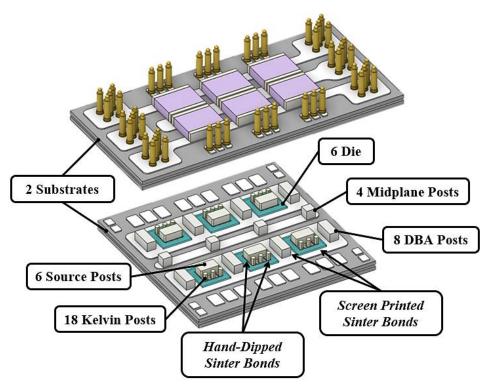

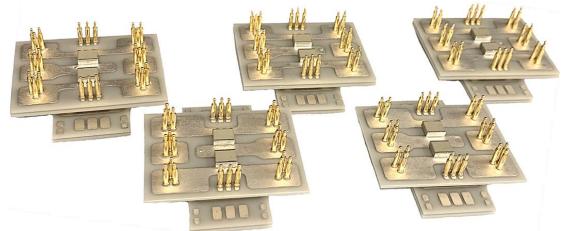

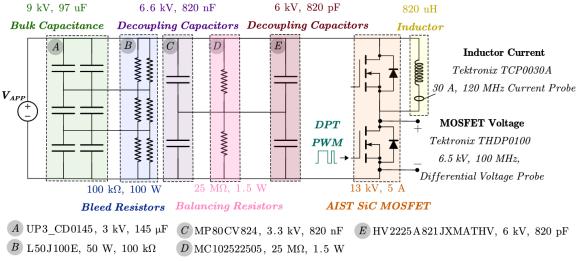

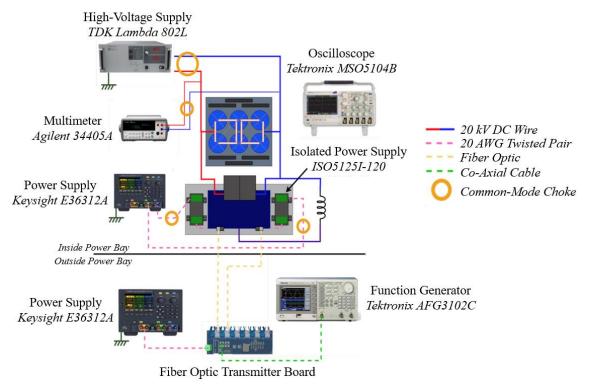

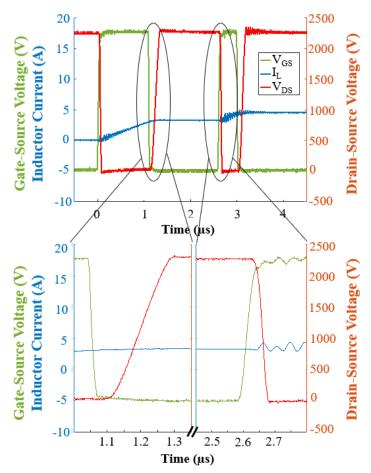

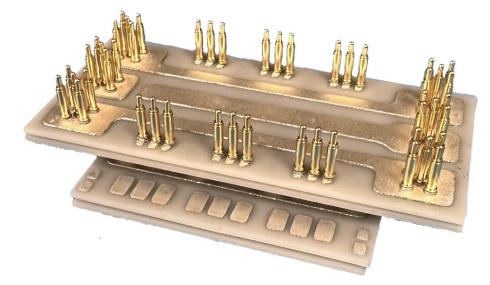

Figure 6: Medium-voltage, multi-chip power module with stacked aluminum nitride, direct-bonded aluminum substrates, silver sinter bonds, molybdenum post interconnects, embedded decoupling capacitors, and spring pin terminals.

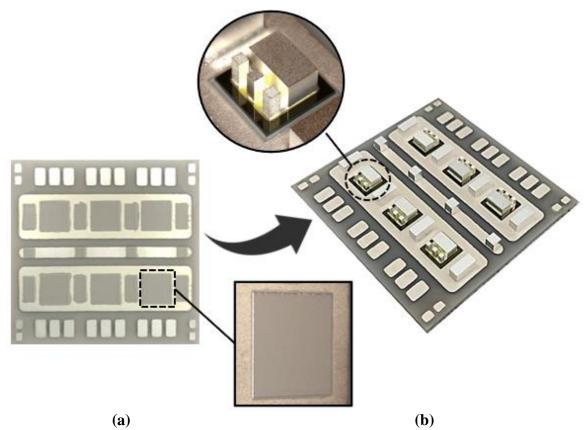

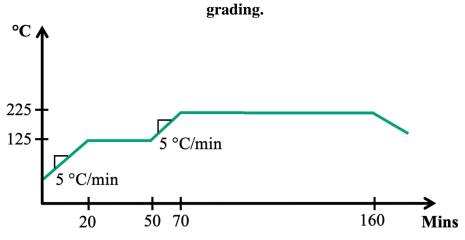

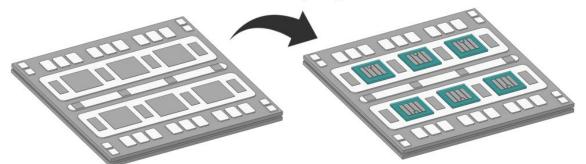

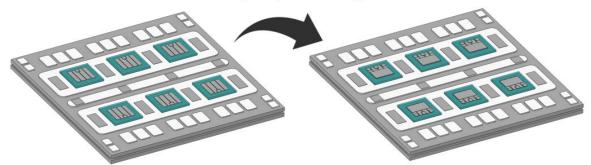

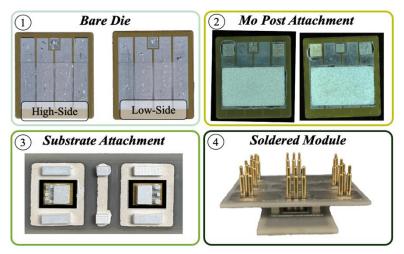

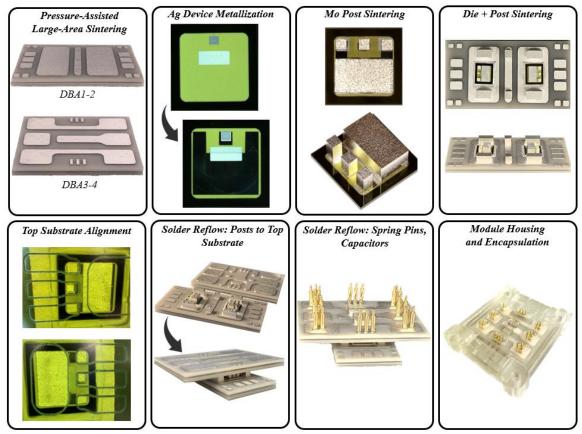

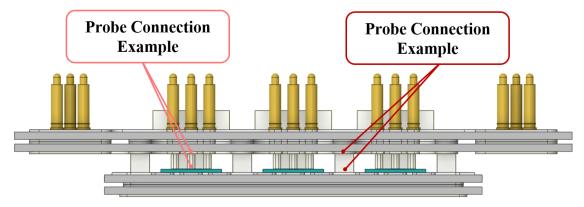

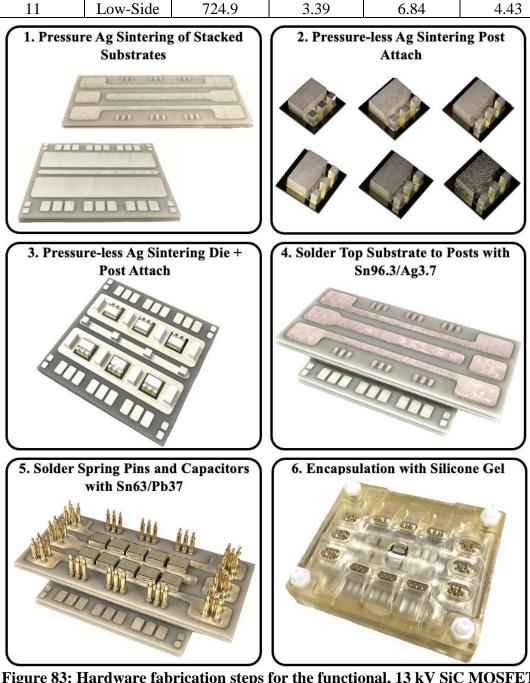

The fabrication process is broken down step-by-step in Figure 7. Two AlN DBA substrates are sintered under pressure for the bottom and top substrates. Encapsulated, stacked substrates with the midplane connecting to half of the maximum potential reduce the peak electric field seen by the triple points, increasing the PDIV to 16.8 kV [50]. Vias within the ceramic connect the aluminum pads electrically. This substrate design is crucial for the medium-voltage operation of 10 kV-13 kV SiC MCPMs.

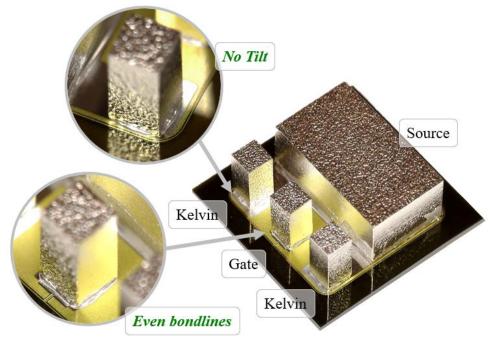

One of the critical components of the package design is the metal Mo posts interconnects for the gate, kelvin source, power source, drain, and midplane connections. Post interconnects attached using silver sintering within sandwich-structure modules enable low inductance, power-dense modules that allow double-sided cooling [52], [54].

While this module does not utilize double-sided cooling, the posts still enable the dense sandwich-structure module with low parasitics. This design is crucial to switch silicon carbide at high voltages with low overshoot. These posts are sintered to the die and the substrate using pressure-less silver sintering.

Figure 7: Fabrication process for the multi-chip power module in [50].

Nano-silver sinter paste is chosen to attach the posts to the die and the die to the substrate due to the low voiding and high thermal conductivity over typical solder alloys.

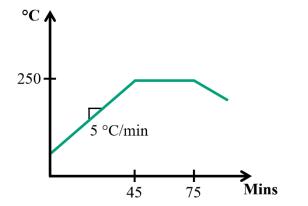

This is crucial since the SiC MOSFETs' drain side is the direct thermal path for conducting heat away from the device [68]. Silver sintering is also beneficial for building multi-chip, sandwich structure modules fabricated in sequential steps since the melting temperature of a sintered bond is 960 °C, and the sintering temperature of the paste is 250 °C. Using nano-silver sinter paste allows for the post interconnects to the die, the post interconnects to the substrate, and the die themselves to all be attached in separate steps without any bond degradation, easing the manufacturing process.

Three MOSFETs per switch position are symmetrically attached on the bottom DBA using pressure-less nano-silver sintering with additional posts for current conduction. The symmetrical layout of the devices and Mo posts allows for balanced parasitics and an easily scalable design.

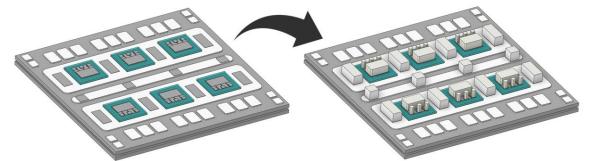

The top substrate connects to the molybdenum posts by pressure-assisted soldering. Solder is chosen for this connection because the top substrate is not in the thermal path; thus, the high thermal conductivity of sinter paste is unnecessary. Soldering the top substrate also allows for compliance between all the posts since it is not as rigid an attachment method as sintering. This is beneficial for relieving any thermomechanical stresses the module may see during operation [50].

The terminals of the module are gold spring pins. Spring pins are beneficial for balancing parasitics with ease of symmetrical layout. The pins compress to the field-graded busbar, sealing off the module from the air and reducing the in-air peak electric field, allowing for 6 mm spacing between pads [69]. Next to the spring pins, the module has embedded decoupling capacitors, which reduce the parasitic inductance seen by the devices during switching and lowering voltage overshoot. The capacitors also allow faster switching by connecting to an integrated common-mode screen to reduce EMI from these transients. The module is encapsulated in a silicone gel within a high-temperature resin housing through multiple degassing and curing steps to ensure a void-less enclosure [50].

In summary, these advanced packaging techniques allow for the successful design of medium voltage modules that have low inductance, reduced EMI, high PDIV, and paralleled SiC devices for higher current operation. However, while the techniques are necessary, their fabrication is not trivial, and it can introduce concerns about yield and manufacturability for these dense, sandwich-structure MCPMs with post interconnects.

#### **1.3.2 Motivation for Fabrication Refinements of Multi-Chip Power Modules**

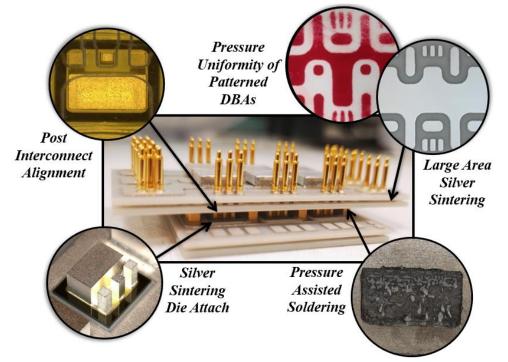

The advanced packaging techniques of the module, displayed in Figure 8, enable low-inductance, high-density, scalable modules. They also introduce new challenges to the fabrication process, requiring refinement to increase the yield of sandwich-structure modules with wirebond-less interconnects.

Figure 8: Advanced packaging techniques and fabrication refinements developed for MCPMs.

Encapsulated silver-sintered stacked substrates are used in medium-voltage packages to relieve the peak electric field at triple points, increasing the PDIV and module reliability [50]. Uniformity of the bondline in these stacked substrates is critical to the thermomechanical reliability of the package as well as ensuring electrical connections are sufficiently made. Unlike solder, which melts during reflow and smoothly coalesces to form a bond between two connections, any defects in the silver sinter bond before sintering will remain after the bond is formed, even during a pressure-assisted sintering process [70]. The sinter paste will not coalesce or bridge any gaps between connections, meaning the bondline must be determined precisely.

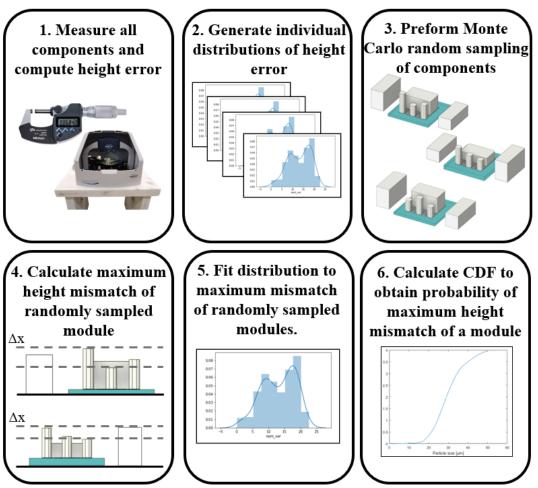

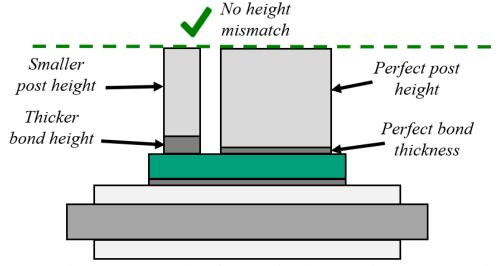

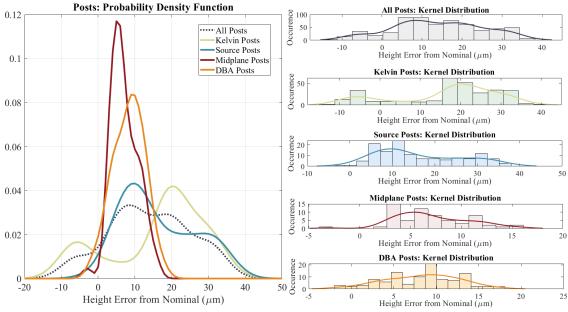

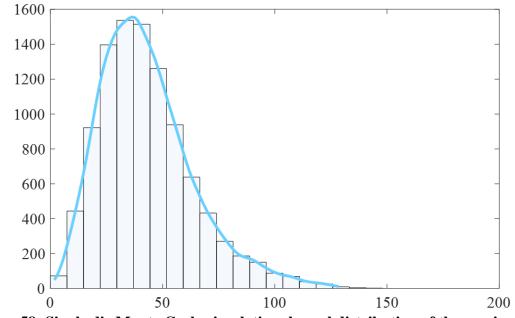

Post interconnects attached using silver sintering within sandwich-structure modules enable low inductance, power-dense modules that allow for double-sided cooling [52], [54]; however, machined post interconnects have non-negligible tolerances, which become more problematic as the number of posts scales up with increasing die in parallel for current scalability. Even if the post heights are identical, package assembly processes and attachment methods can tilt the posts. The phase change of the solder and unpredictable outgassing of solder flux during reflow can tilt the posts or render connections useless [71]. Alternatively, when the posts are placed in the sinter paste for the die interconnect attach, the bondline thickness can vary if placed with a different amount of pressure every time, creating a mismatch in the heights. The tilt can cause some of the smaller gate and kelvin posts to disconnect altogether.

Additionally, soldering MCPMs involve a large thermal mass for which the typically soldering reflow profile was not created. Temperatures and ramp rates need to be

scaled to reduce void creation and complete reflow; however, with increased temperatures and times to heat the large thermal mass, there is a chance for de-wetting the solder [72].